# TELEPHONE COMMUNICATION SYSTEMS

VOLUME III ELECTRONIC SWITCHING SYSTEMS

0

V 0 L

111

0

9

70

PREFACE

Connecting any two phones among the millions of subscribers is accomplished by telephone switching systems. The process, although not simple, is normally taken for granted in our everyday use of telephone services. This is indeed a compliment to the Bell System people who have developed, engineered, and maintained the many types of telephone systems. The switching equipment in the Central office is considered by many to be the heart of the telephone highway, for without it the telephone never would have progressed to the highly developed and integrated entity it is today.

Although the switching equipments may be considered the "heart," the other parts of the telephone network are equally important. For without the connecting wires and cables, the subscribers' equipment and the power plant, there could be no universal telephone network and no Direct Distance Dialing.

Switching is a highly dynamic field. From the first crude switching arrangements developed by the Holmes Electric Company in Boston in 1877 to the highly sophisticated No. 1 ESS system developed by the Bell System Laboratories in the early 1960's, the telephone switching system has indeed come a long way. What the future holds can only be speculated upon: on the horizon, we now see new developments, such as the use of satellites, lasers, and holography in communications.

Each subject covered in this text could be developed much more extensively; however, our objective is not to print a comprehensive treatise on telephony, but rather to treat each subject briefly presenting a general technical explanation of its operation and function.

This text has been prepared for Graduate Engineering Education courses presented at the Western Electric Corporate Education Center. Its contents are the result of over 12 years of development, starting from a group of handouts given to students and leading to the book we have today. Although much of the material and ideas were taken from various Bell System sources, a great deal of the book can be attributed to the members of the Graduate Engineering Education staff. Acting as writers, instructors, and editors, each diligently worked in assembling a well organized telephone communications text. Their collective efforts are sincerely appreciated, and are hereby gratefully acknowledged.

> J. E. GARRETT Manager, Graduate Engineering and Information Systems Education

Corporate Education Center Hopewell, New Jersey

#### TELEPHONE COMMUNICATION SYSTEMS

This material is prepared for training purposes only and is the property of Western Electric Company, Incorporated, and is loaned on condition that it be returned to the Company upon termination of employment or upon request by the Company prior thereto. No reproduction of this material, in whole or in part, and no disclosure of any part of this material to other than fellow employees, as may be necessary in connection with work assignments, may be made without prior permission in writing from the Company.

© 1970 Western Electric Company, Incorporated

Printed in U.S.A.

# TELEPHONE COMMUNICATION SYSTEMS

VOLUME III

Revised Edition 1970

CORPORATE EDUCATION CENTER WESTERN ELECTRIC CO., INC. HOPEWELL, NEW JERSEY

# TABLE OF CONTENTS

# VOLUME III

| CHAPTER | 9 | NO. 1                                                   | ELECTRONIC SWITCHING SYSTEM                                                                                                                                                                                                                                                                                              | 9.1                                                                                                      |

|---------|---|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|         |   | 9.5<br>9.6<br>9.7<br>9.8<br>9.9<br>9.10<br>9.11<br>9.12 | Introduction<br>Switching Logic In Solid State Devices<br>Program Store<br>Call Stores<br>Central Control<br>Bus System<br>Central Pulse Distributor<br>Scanners<br>Signal Distributor<br>Switching Network<br>Junctor, Trunk and Service Circuits<br>Master Control Center<br>Method of Operation - No Signal Processor | 9.1<br>9.11<br>9.18<br>9.35<br>9.49<br>9.80<br>9.82<br>9.90<br>9.100<br>9.106<br>9.134<br>9.140<br>9.153 |

# VOLUME I

| CHAPTER | 1 | BRIEF HISTORY OF COMMUNICATIONS | 1.1 |

|---------|---|---------------------------------|-----|

| CHAPTER | 2 | STATION EQUIPMENT               | 2.1 |

| CHAPTER | 3 | LOCAL MANUAL SYSTEMS            | 3.1 |

| CHAPTER | 4 | STEP-BY-STEP SYSTEMS            | 4.1 |

| CHAPTER | 5 | PANEL SWITCHING SYSTEM          | 5.1 |

#### VOLUME II

| CHAPTER   | 6  | PRINCIPLES OF CROSSBAR SWITCHING           | 6.1  |

|-----------|----|--------------------------------------------|------|

| CHAPTER   | 7  | NO. 1 CROSSBAR AND CROSSBAR TANDEM SYSTEMS | 7.1  |

| CHAPTER   | 8  | NO. 5 CROSSBAR SYSTEM                      | 8.1  |

| CHAPTER 1 | 10 | 4A TOLL SWITCHING SYSTEM                   | 10.1 |

# VOLUME IV

| CHAPTER 11 | DIRECT DISTANCE DIALING              | 11.1 |

|------------|--------------------------------------|------|

| CHAPTER 12 | TOLL SWITCHBOARDS                    | 12.1 |

| CHAPTER 13 | THE TRAFFIC SERVICE POSITION SYSTEMS | 13.1 |

| CHAPTER 14 | AUTOMATIC MESSAGE ACCOUNTING         | 14.1 |

# VOLUME V

| CHAPTER 15 | OUTSIDE PLANT FACILITIES       | 15.1 |

|------------|--------------------------------|------|

| CHAPTER 16 | CARRIER SYSTEMS                | 16.1 |

| CHAPTER 17 | VOICE FREQUENCY REPEATERS      | 17.1 |

| CHAPTER 18 | TELEPHONE POWER PLANTS         | 18.1 |

| CHAPTER 19 | CENTRAL OFFICE TEST FACILITIES | 19.1 |

#### CHAPTER 9

#### NO. 1 ELECTRONIC SWITCHING SYSTEM

#### 9.1 INTRODUCTION

The No. 1 ESS is an automatic telephone switching system that has

- (a) The capacity for serving up to 65,000 customer lines

- (b) Features which are expected to permit minimum maintenance

- (c) The ability to complete connections between subscribers in a fraction of the time required by electromechanical type switching systems.

- (d) The versatility to provide new features and services economically

The No. 1 ESS is a common control type system. It differs radically from electromechanical switching systems in the devices that it uses as well as in the techniques that it employs. Throughout the system, solid-state electronic devices are used extensively. Their high operating speeds permit a relatively small amount of equipment to perform all the control functions. A major feature is the greatly reduced time required to complete connections between customers.

Some of the basic techniques employed in this system are:

(a) <u>Stored program control</u>: The functions to be performed by the system are specified by programs consisting of appropriate combinations of precisely defined instructions. Examples of such instructions are: "Observe the supervisory state of a specified group of lines," "Add two specified quantities," and "Observe the sign of a specified quantity and decide accordingly which of two alternatives to follow." The program instructions, suitably encoded, are stored in a memory unit from which they are transmitted one at a time to the control circuitry for execution. Thus, the operation of the system can be altered considerably by program changes.

9.1

- (b) <u>Functional concentration</u>: The system equipment is concentrated in a small number of highly efficient units, each specialized in some broad system function such as control, input, output, memory, etc. The result is an overall system organization that is conceptually very simple.

- (c) <u>Time shared control</u>: A single control unit directs the operation of all other system units in accordance with the program instructions. Using electronic devices, this control unit can operate at speeds much higher than the rate at which events associated with a single call occur. Consequently, the control equipment is time-shared by all the calls handled by the system. This is accomplished by subdividing the work required to process a call into small segments and by interleaving these segments with those associated with other calls. In addition, certain operations can be performed concurrently on behalf of a number of calls.

- (d) <u>Modular design</u>: Traffic-dependent units are provided in modular blocks so that growth in a given office, or differences in traffic among offices, can be accommodated economically and conveniently.

- (e) <u>Plug-in equipment units</u>: In major portion of the equipment, circuit components such as transistors, resistors, etc., are mounted on circuit packs, which are plug-in units with printed wiring. Faulty circuit packs can be quickly replaced.

- (f) Duplication and automatic maintenance: To insure continuity of service, duplication of equipment is provided for a system unit (or portion thereof) whose failure would affect a large number of customers. This is true of most system units because of the functional concentration previously mentioned. Under normal conditions, both units of a duplicate pair operate side-by-side in response to the same input information but only one of the two is given active status. By continuously compairing the outputs of duplicate units and by other means, it is possible to detect the existence of a malfunction within the system. The unit at fault is automatically identified by appropriate programs and is taken out of service. While the system continues to provide telephone service, an appropriate diagnostic program submits the faulty unit to a thorough sequence of tests aimed at pinpointing the trouble within one or a few plug-in units. The results of the tests are printed out by the system via a teletypewriter. A "dictionary" is used by the

maintenance man to translate the diagnostic printout into the identity of the plug-in unit(s) at fault. Additional ease of maintenance results from the use of 7-foot, single-sided frames which eliminate the need for ladders.

Included among the features to be provided by this system are: 2- and 4-wire switching, local switching with connections to all types of systems, toll and tandem, switching, and special services such as CENTREX, wide area telephone service (WATS), and wide area data service (WADS).

Some of the new customer services which may be provided

are:

- (a) <u>Abbreviated or Speed Dialing</u>: A customer can place calls to one of a group of frequently called numbers by dialing an abbreviated code instead of the seven or more digits that would normally be required.

- (b) <u>Dial Conference</u>: A customer can establish a conference call, involving up to four parties, without operator assistance.

- (c) <u>Add-On</u>: A customer can add a third party to an established connection.

- (d) <u>Call Waiting Service</u>: A customer whose line is busy is informed that an incoming call is waiting. The customer is allowed to hold the present connection while answering the new call.

- (e) <u>Variable Transfer</u>: A customer activates this service by dialing a special code followed by the directory number of the station to which his incoming calls are to be transferred. The customer deactivates this service by dialing an appropriate code.

- (f) <u>Preset Transfer</u>: A customer activates this service by dialing a special code followed by a digit that specifies to which of eight stations all his incoming calls are to be transferred. The customer deactivates this service by dialing an appropriate code.

Floor space requirements are considerably less than equivalent installations of electromechanical systems.

This system is compatible with existing station equipment and existing local and toll switching machines. It may be used as a growth or dial replacement unit without the necessity of station modifications and with a minimum of trunking changes at the distant offices.

#### A. PRINCIPLES OF OPERATION

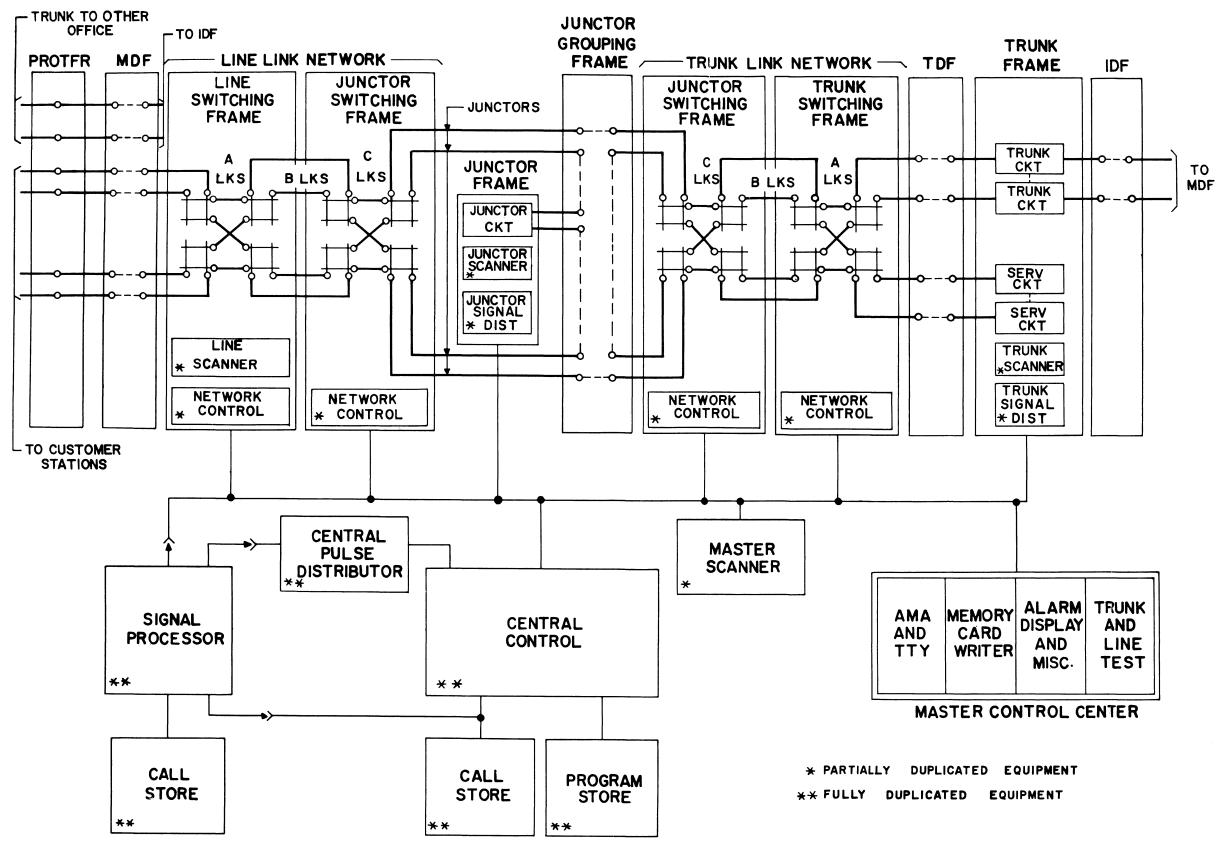

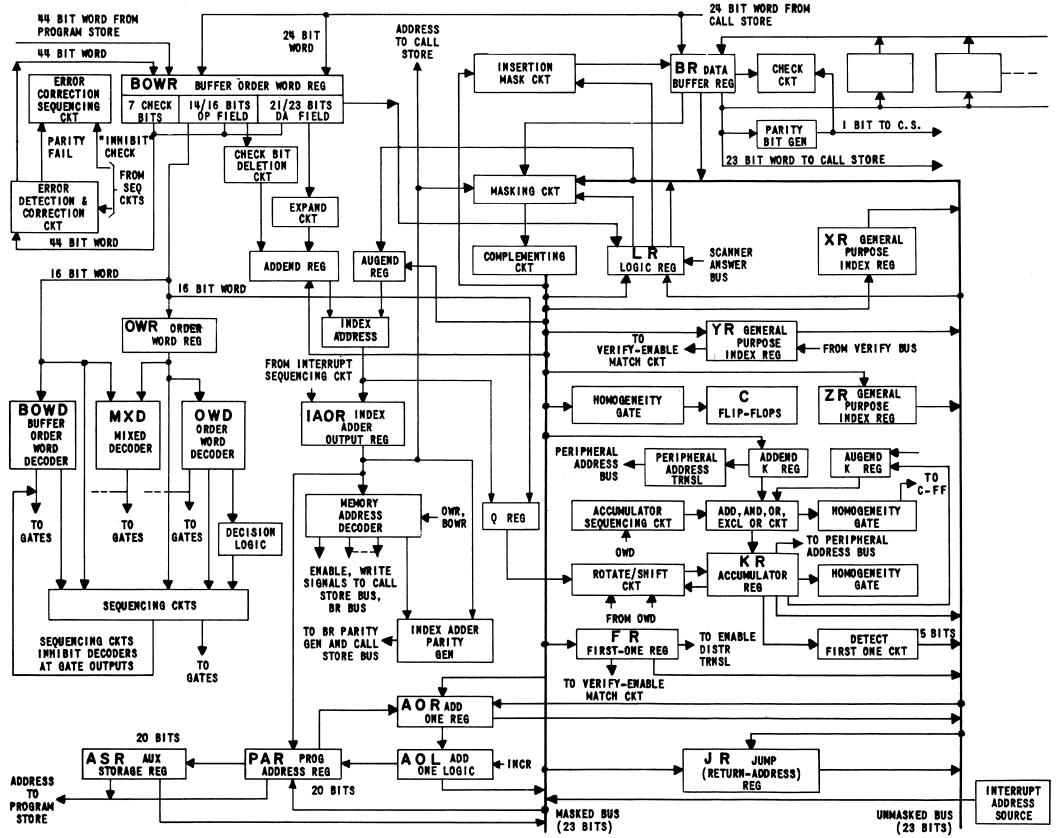

The major No. 1 ESS equipments and their corresponding functions are briefly described below (see Figure 9-1).

#### 1. Program Store

The program store (PS) stores the instructions that guide the system step-by-step in the performance of its operations. The PS also contains translation information regarding lines and trunks. This information is used to convert a directory number into an equipment location or vice versa. Translations are also used to derive routing and charging information, class of service, type of ringing, special services, and other items of fixed information pertaining to individual lines or trunks.

The PS is said to be a semipermanent memory because its contents can be altered only by external means.

#### 2. Call Store

The call store (CS) provides the means for recording various types of information that later can be read, altered, or erased. Since the CS can write as well as read information, it is said to be a temporary or erasable memory.

The CS derives its name from the fact that it is mainly used to store information relating to calls in progress. The stored information includes:

- (a) Busy-idle status of network links,

- (b) Digits being received,

- (c) Digits to be outpulsed,

- (d) Billing information to be recorded on an AMA magnetic tape, or

- (e) Results of diagnostic tests.

Figure 9-1 Block Diagram - No. 1 Electronic Switching System Another important use of the CS is associated with recent changes of translation information. The superseding information is stored in the temporary memory until it is incorporated in the translation information of the PS. This means that the system must always consult the recent change information of the CS before referring to the translation information in the PS.

3. Central Control

The central control (CC) is a high-speed dataprocessing unit that controls the actions of all other system units. It interprets and executes instructions received from the program store, normally, at the rate of one instruction every 5.5 usec. The execution of an instruction may involve:

- (a) An operation to be carried out within the CC itself, such as the addition or comparison of two quantities, or

- (b) A request to some other unit for action or information.

In all cases, the CC determines the location (or address) of the next instruction to be obtained from the program store (PS).

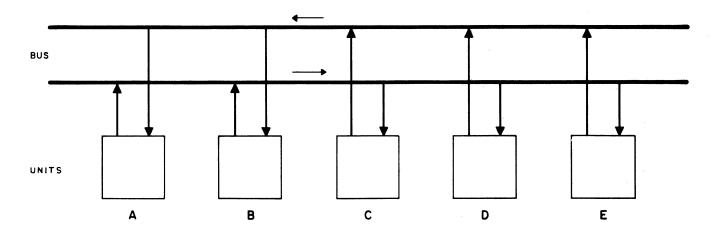

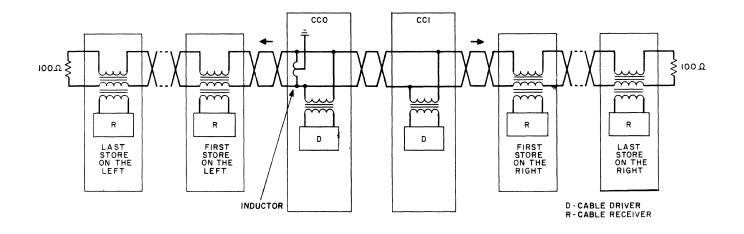

4. Bus System

A group of leads, referred to as a bus, provides a common highway that serves a multiplicity of units. A gating scheme allows the bus to be time-shared by the different units it serves.

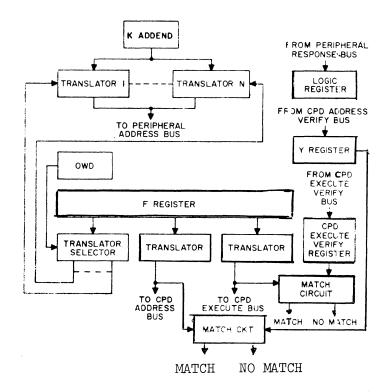

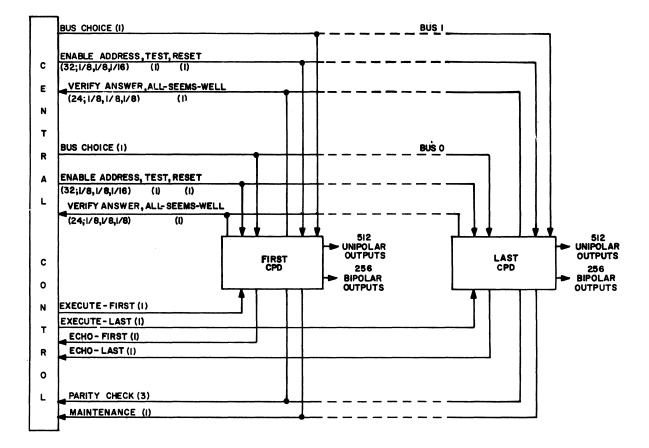

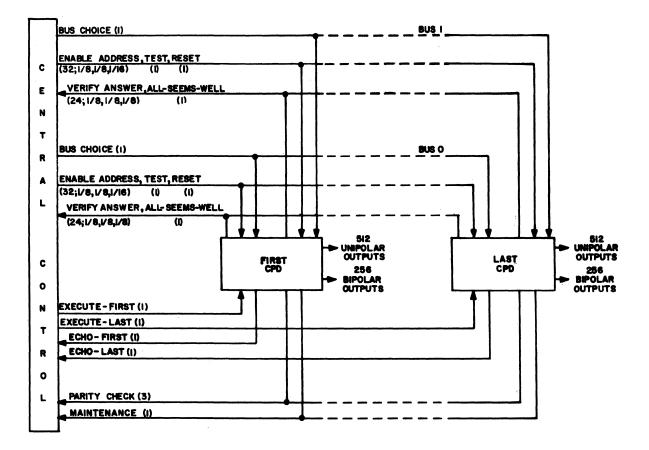

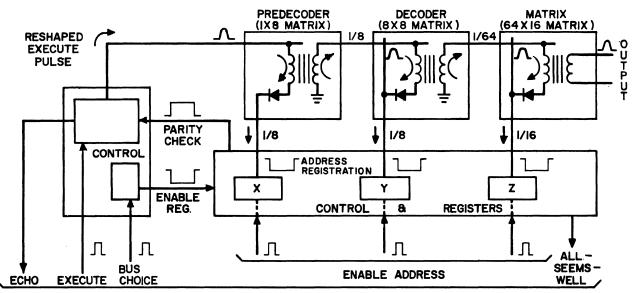

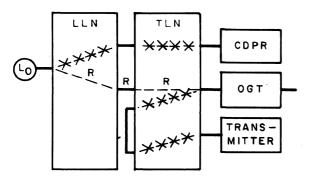

5. Central Pulse Distributor

The central pulse distributor (CPD) is used to transmit pulse signals for high-speed control actions. The signals are used to control:

- (a) Relays in trunk and service circuits such as dial pulse transmitters or digit receivers,

- (b) Various maintenance and test points, or

- (c) Lamps and relays in the master control center (MCC).

9.7

The CPD is also used to send enable pulses that activate scanners, signal distributors, network controllers, teletypewriters, and AMA recorders. These units are referred to as peripheral units. The transmission of information to peripheral units takes place over a common group of wires, or bus. An enable pulse from a CPD singles out the particular peripheral unit that must respond to the information on the common bus.

A CPD selects and pulses the particular output lead specified by information received from CC.

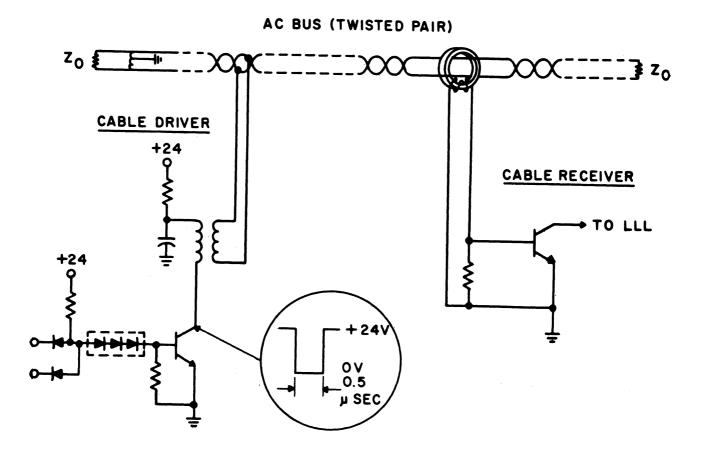

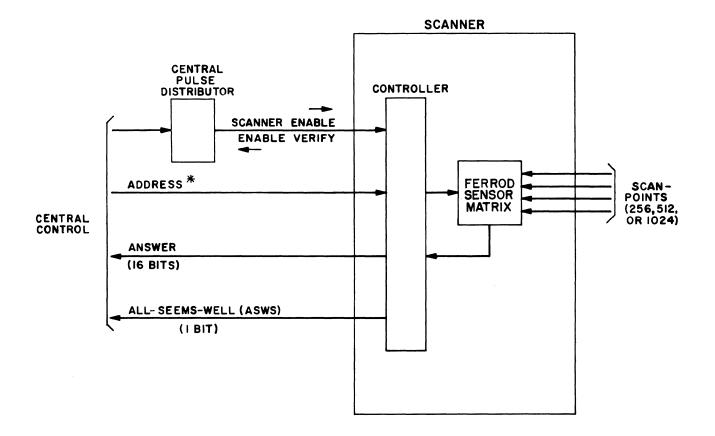

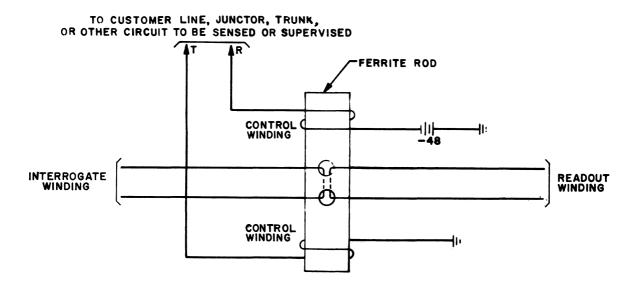

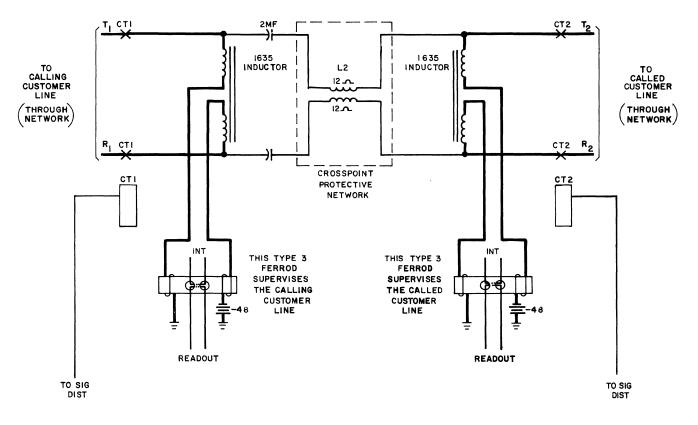

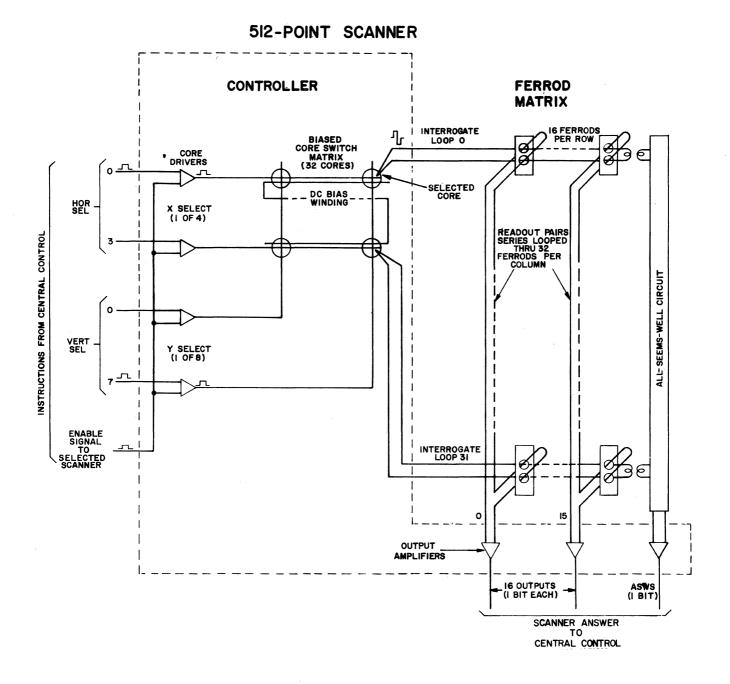

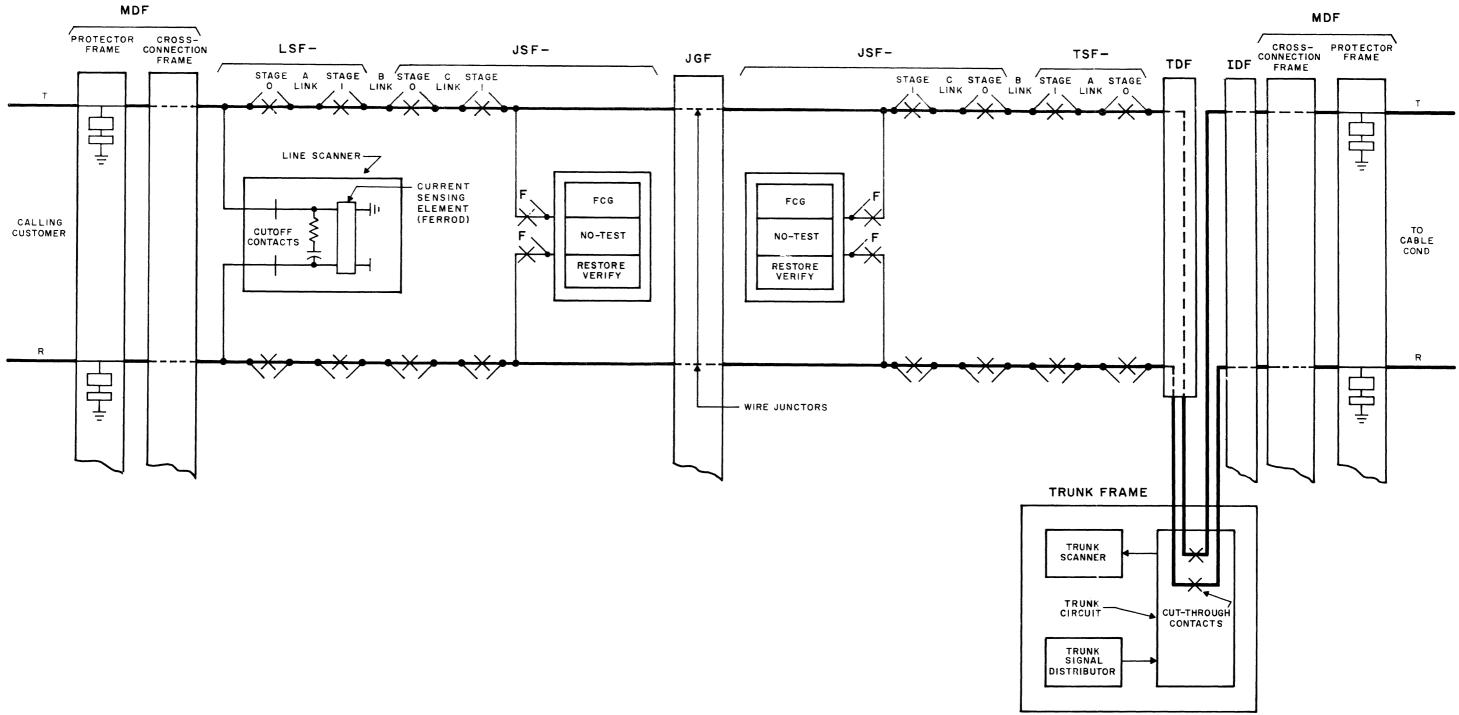

6. Scanners

The scanners are current sensing devices. The interrogate and readout wires of a scanner are similar to the primary-secondary windings of a transformer.

Line scanners and junctor scanners are used to supervise lines and junctor circuits, respectively. Trunk scanners supervise trunk circuits and service circuits. Via the master scanner, the system can observe various points within the individual units. This may be done for one of several reasons:

- (a) To perform a diagnostic test,

- (b) To verify the proper execution of an action previously requested, or

- (c) To recognize existing conditions in order to take appropriate steps.

The conditions observed are transmitted back to CC.

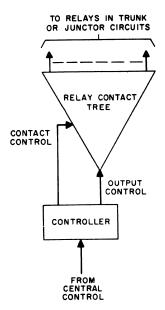

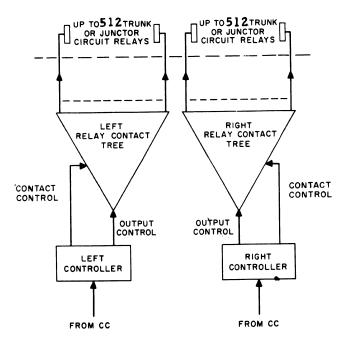

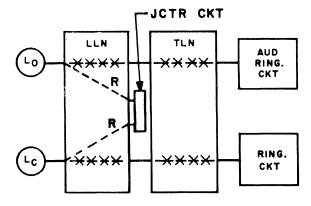

7. Signal Distributors

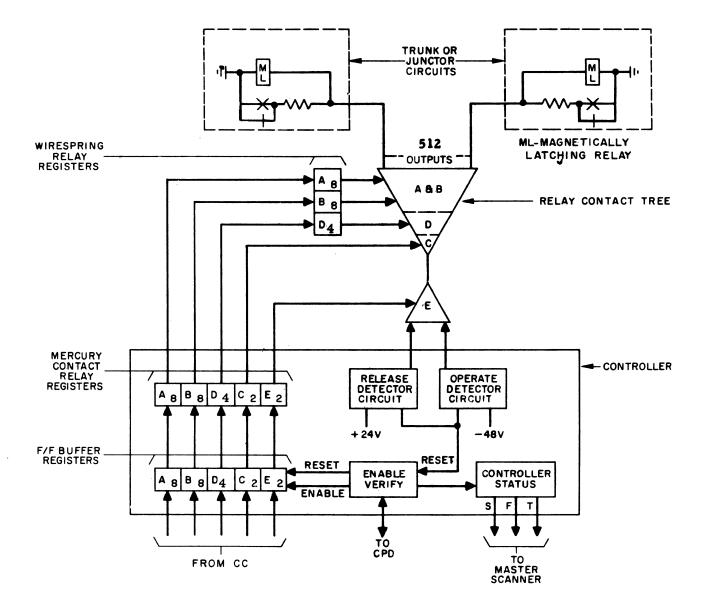

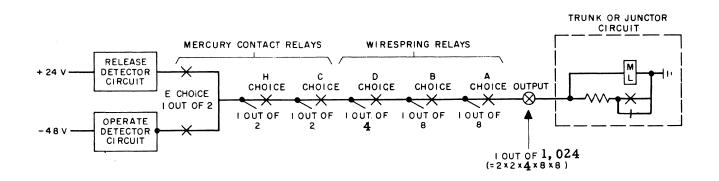

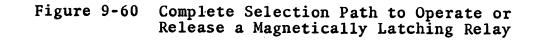

The signal distributors (SD) serve to operate or release magnetically latching relays in various junctor, trunk, or service circuits. Since they are mainly relay controlled, they are used only in applications with limited speed requirements.

An SD receives from CC information specifying a particular relay to be operated or released. The SD selects the appropriate lead and sends a signal to operate or release the relay.

#### 8. Switching Network

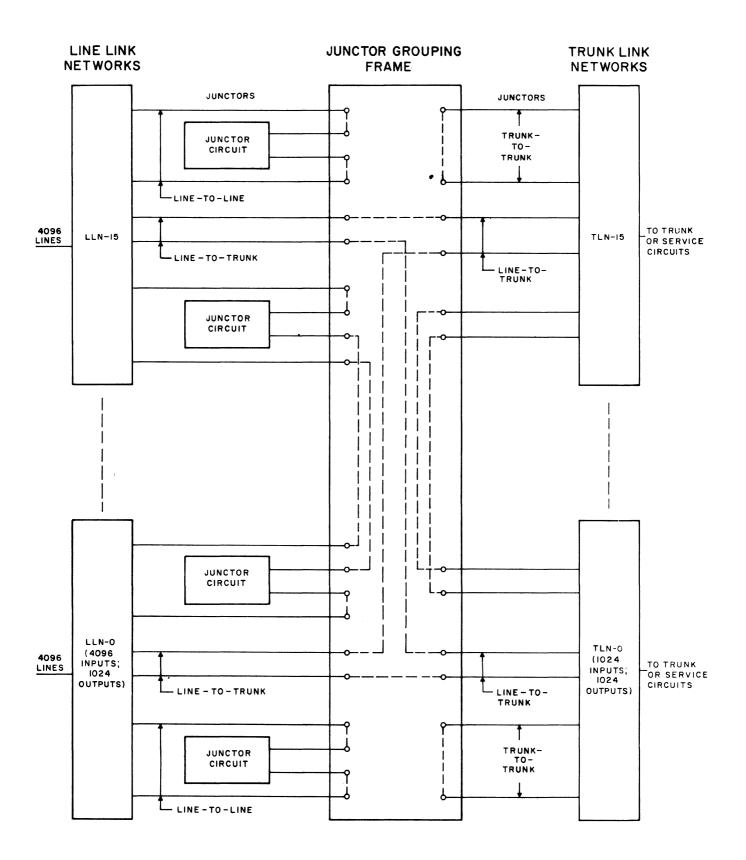

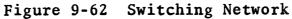

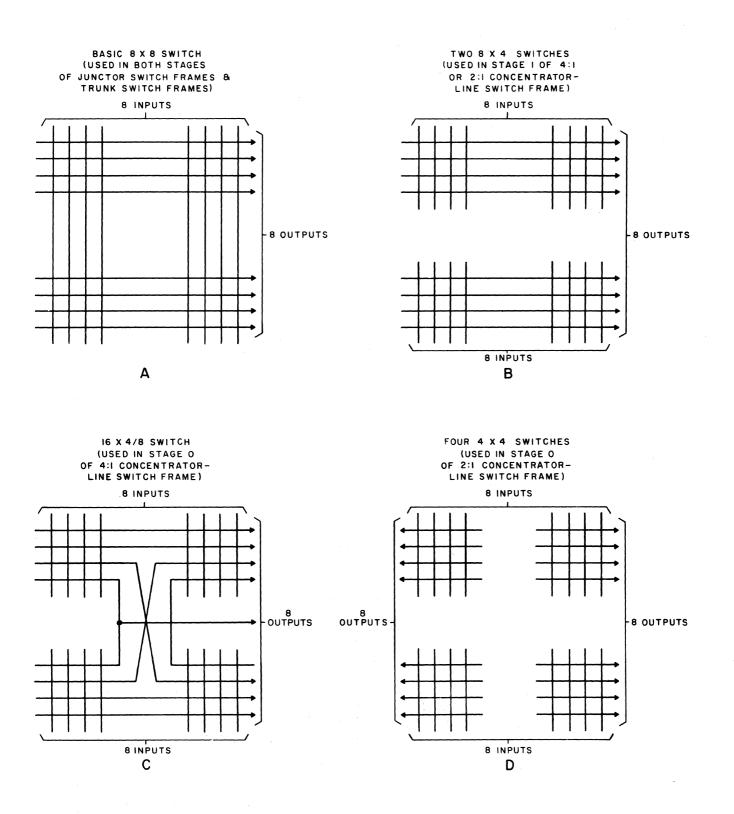

The switching network provides the means to connect lines, trunks, and various service circuits such as pulse receivers or transmitters. For any connection between two network terminations, the path required is determined by CC which then sends the appropriate information to the switching network.

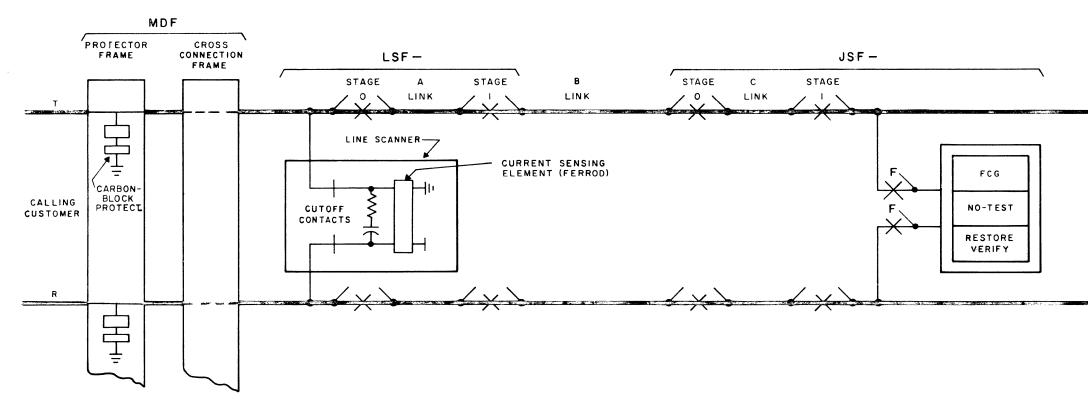

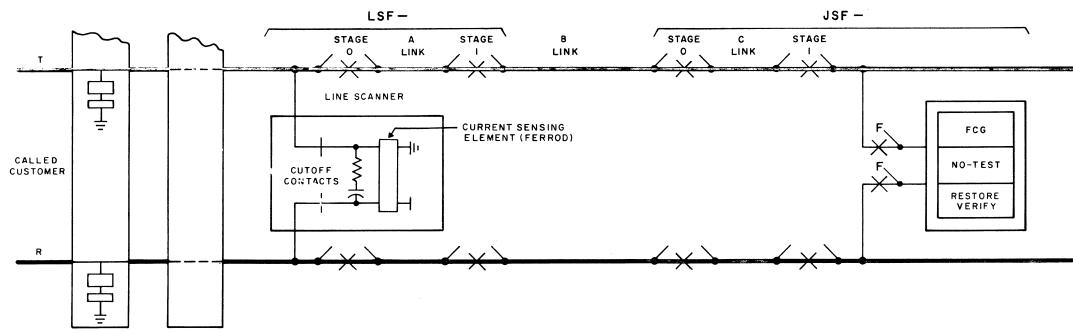

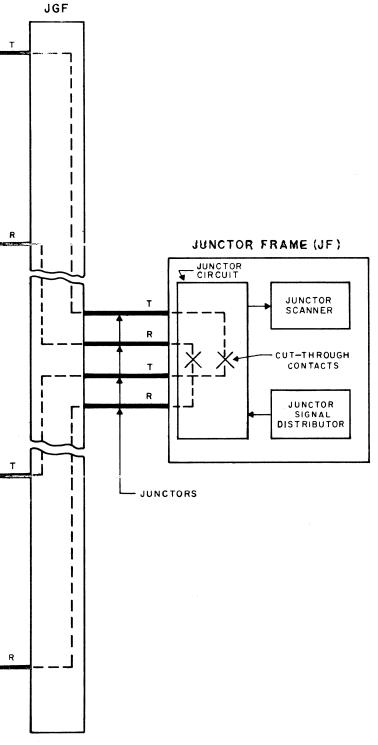

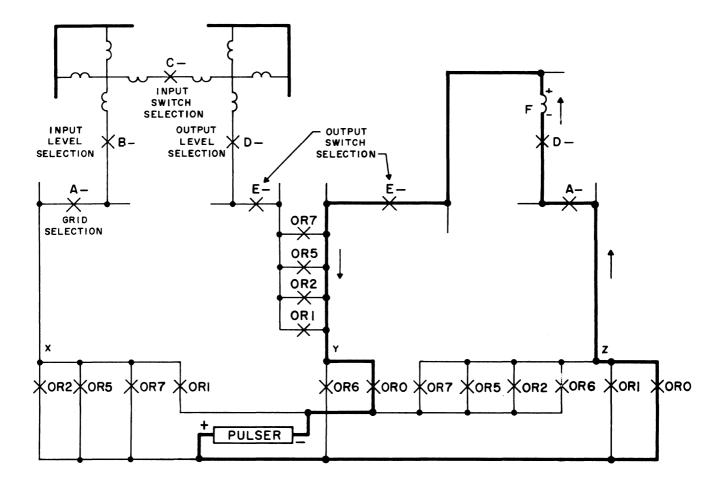

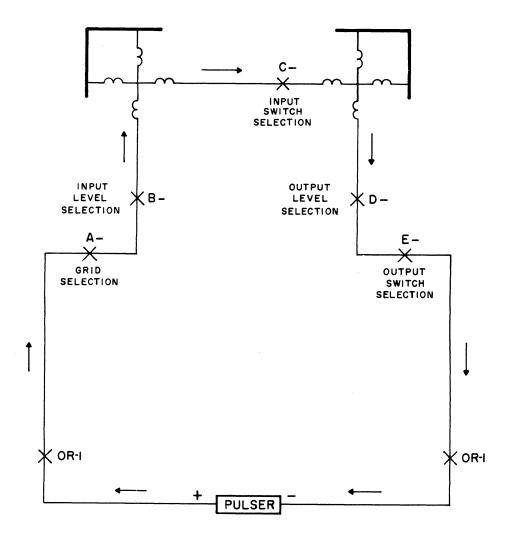

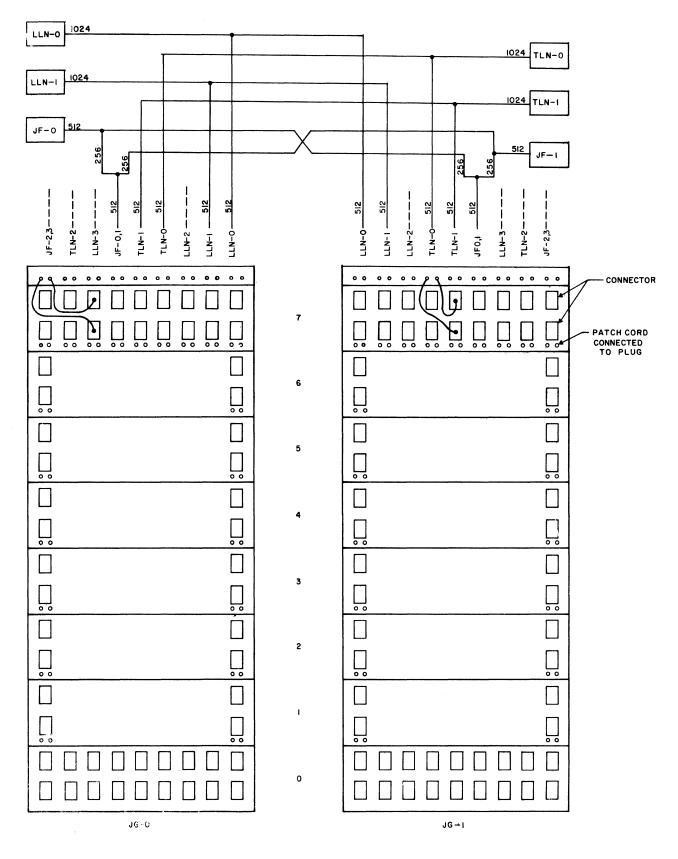

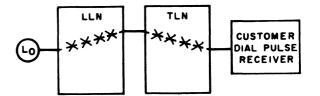

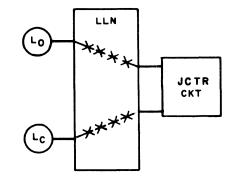

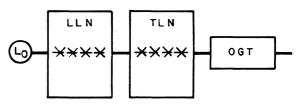

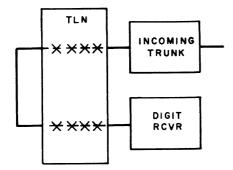

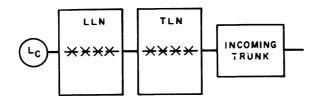

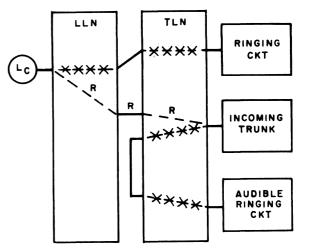

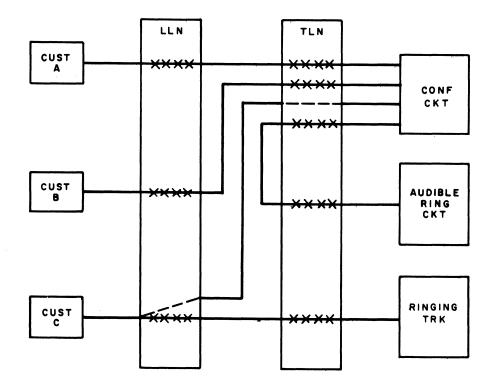

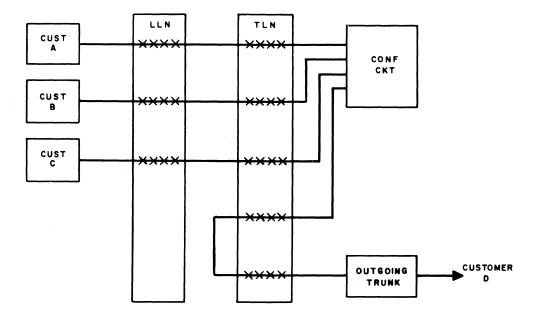

The switching network is made up of line link networks (LLN) and trunk link networks (TLN) interconnected by junctors. An LLN connects customer lines or PBX trunks to junctors. A TLN connects interoffice trunks or service circuits to junctors.

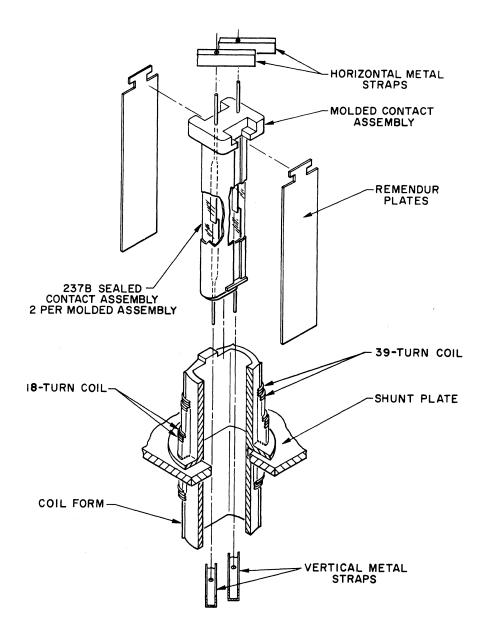

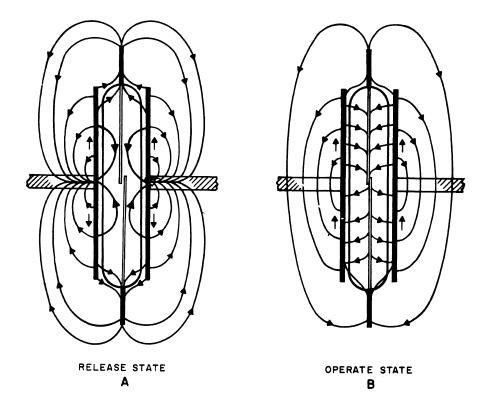

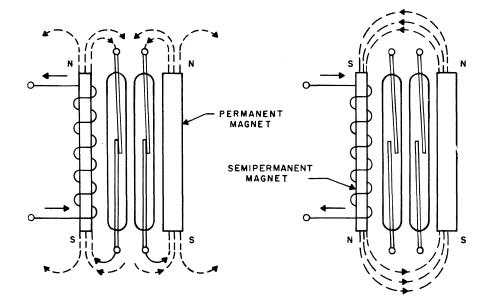

Each LLN or TLN involves four stages of switching, that is, a path through it involves three links connected by four pairs of metallic contacts or crosspoints (ferreeds).

#### 9. Trunk and Service Circuits

The trunk circuits of the No. 1 ESS are considerably simpler than those of electromechanical systems. Their functions are limited mainly to supervision and transmission. All other functions of conventional trunks such as pulsing, charging, timing, etc., are delegated either directly to the program control or to the service circuits, which in turn are under program control. Service circuits include customer dial pulse and TOUCH-TONE receivers, tone circuits, ringing circuits, circuits for transmitting or receiving information, coin control circuits and other similar circuits.

The detection of conditions within these circuits is done by CC via the trunk scanner. The control of relays and other devices within the trunk and service circuits is also done by CC using the trunk SD or the CPD. There are very few instances of autonomous control within trunk and service circuits.

#### 10. Master Control Center

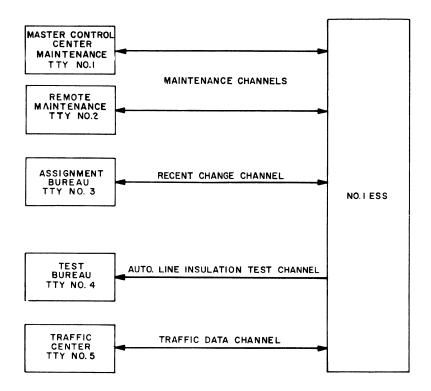

The master control center (MCC) is made up of five independent parts:

- (a) Teletypewriter system (TTY)

- (b) Automatic message accounting (AMA) recorder

- (c) Memory card writer

- (d) Alarms, displays and miscellaneous controls

(e) Trunk and line test panel.

A teletypewriter provides the means for obtaining information from the system in the form of a page printout and, conversely, for typing information into the system. Examples of inputs to the system are changes in translation information to be recorded temporarily in the recent change area of the CC CS and requests for various maintenance checks under program control. Examples of outputs from the system are results of routine maintenance checks and of diagnostic tests when errors or faults occur. Traffic records are collected and summarized in the CS. Periodically they are printed out via a teletypewriter. Requests for certain traffic records may be made by typing appropriate messages into the system via teletypewriter.

Automatic message accounting in the No. 1 ESS will be compatible with Bell System electronic data processing (EDP) centers. While a call is in progress, the billing information is accumulated in temporary memory. Later, it is transferred to a magnetic tape as a single assembled entry for the call. The entire process is under control of the program. The memory card writer is used to update periodically the translation information in the program store in order to incorporate recent changes recorded in the CS. By means of the memory card writer, the appropriate information is written on a spare set of memory cards by magnetizing or demagnetizing their magnetic spots, as required. These cards are then used to replace corresponding cards of the program store.

Lamp displays at the MCC show the status of major equipment units. When trouble occurs, audible and visible alarms are given and the general location of the trouble is indicated. Associated with the displays are keys and switches used in emergencies to assign active status to selected units. Keys for line load control and emergency manual service are also provided.

The trunk and line test panel contains facilities to remove from service any outgoing trunk, service circuit, or customer line and to test it. It is also used to dispose of permanent signals.

#### 9.2 SWITCHING LOGIC IN SOLID STATE DEVICES

Unlike the stepper switches in the Step-by-Step System and the motor-driven shafts, clutches and cams of the Panel System or the relays and the relay-like crossbar switches and the "electrical circuits" which operated them, the No. 1 ESS uses "logic circuits" to achieve connecting patterns in its switching process. To establish a talking path between telephones could be viewed as the stage-by-stage progression of simple logical relations AND and OR. For example, consider a lamp plugged into a wall socket controlled by a wall switch. The lamp will not light unless both the lamp switch AND the wall switch are turned on. On the other hand, take the action of the dome light of an automobile which lights if one of the front doors OR the other is opened. Relays can be wired to open or close contacts in the same fashion and these simple logical relations can be repeated as often as necessary to form a highly complex system that decides complicated logical questions.

#### A. LOGIC CIRCUITS

In switching systems, for every set of "inputs" there is a corresponding set of "outputs." The internal circuitry that connects inputs to outputs consists of paths interconnecting discrete-valued (digital) devices such as relays, diodes, transistors, etc. The function of these devices is to "switch" (open or close) the interconnecting paths in predetermined patterns as required by the input information. The simplest control conditions are two valued, that is, they are in an "on" or "off," "open" or "closed," condition. For this reason, switching circuits are based primarily on "two-valued devices." Another fundamental characteristic of switching systems is their ability to "remember," that is, remain in a certain state until changed by some means. "Memory" makes it possible to combine present inputs with past history so that the processing of information can take into account the time involved relationships.

#### **B. BINARY AND OCTAL NUMBERING SYSTEMS**

The No. 1 ESS uses both a binary and octal numbering system. The binary system employes only two digits - a "0" and a "1", and is readily adapted to two-condition type electronic switching components that operate in "on" and "off" modes. Programs in the form of binary digits are stored in the memory portions of the electronic switching system while equipment and circuit numbering arrangements are arranged in the octal system which uses a radix of eight. Both numbering systems, however, can readily be converted to either base and also to the decimal system.

#### C. SEMICONDUCTOR DEVICES

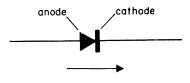

Semiconductor diodes and resistors are used for the No. 1 ESS AND and OR gate circuits. However, diodes do not provide either gain or inversion, consequently, other switching devices must be employed for these two purposes.

A diode behaves like a low resistance when forwardbiased and a high resistance, when back-biased. The low and high resistance states of a diode are often referred to as the "conducting" and the "nonconducting" states respectively. The change from one state to the other occurs in a few hundreds of a microsecond. Figure 9-2 shows the usual circuit symbol for a diode. The arrow points in the direction of the conventional current flow with a forward bias on the diode terminal. Diodes act as good conductors with

direction of conduction

Figure 9-2 Diode Symbol

forward bias voltage applied and perform as insulators with reverse potentials. A typical No. 1 ESS 10,000 line telephone office contains over 200,000 diodes of eight different types which are used for logic switching, energy storage, voltage level shifting, memory access isolation, voltage regulation and numerous other applications.

The transistor has a number of advantages over that of a tube; for example, it can operate at greater speeds, is more reliable and has a low power requirement. Like the semiconductor diode, the transistor is also used as a two-state device. It is, however, a much more versatile device than the diode because of its gain characteristics. But, whether it is used in an amplifier, an inverter, a flip-flop or a gate circuit, the transistor may be viewed as a switch. Furthermore, the impedance of this switch can be made to vary from tens of megohms to a fraction of an ohm, which at this low value, can be considered as approaching the ohmic value of a metallic contact. Switching times are in the order of 50 nanoseconds (a nanosecond is one billionth of a second).

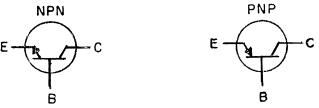

There are two basic types of transistors: N-P-N and P-N-P. The symbols for these two types are given in Figure 9-3.

Figure 9-3 Transistor Symbols

The No. 1 ESS makes exclusive use of the N-P-N transistor. However, except for a reversal in the direction of currents and in the polarity of voltages, the P-N-P transistor functions in the same manner. The transistor has three terminals; the emitter (E), the collector (C), and the base (B). A very rough analogy can be drawn between a transistor and a vacuum tube triode. In this analogy, the emitter corresponds to the cathode, the collector to the plate and the base to the grid. In the vacuum tube, the flow of electrons from the cathode to the plate is controlled by signal conditions applied to the grid; in the transistor, the flow of electrons from the emitter to the collector is controlled by signal conditions applied to the base.

#### D. BASIC CIRCUIT CONFIGURATIONS

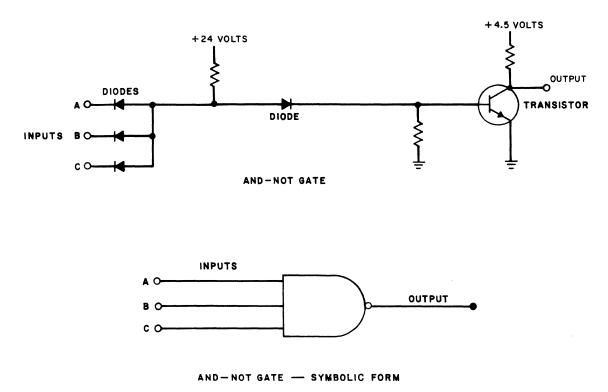

The basic building block for the circuitry of the No. 1 ESS is the <u>AND-NOT</u> (<u>NAND</u>) gate shown in Figure 9-4; it is generally known as low-level logic (LLL) circuit.

Figure 9-4 AND-NOT Gate Circuit

Its output is considered low (0 volts) when the inputs are high (+4.5 volts) and the output is high (+4.5 volts) whenever at least one of the inputs is low (0 volts). This building block is used in many circuit configurations classified as logic circuits and memory circuits. Consequently, the logic presented is referred to as the positive logic approach in circuit design.

Positive logic can be specified as the relatively more positive potential level of a two-state (binary) signal and is defined as being in the "1" state.

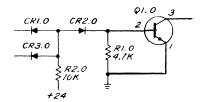

Figure 9-5 shows a typical 2-input NAND gate widely used in the No. 1 ESS. In this gate circuit resistance R2 provides a source of current which can be directed into the base of transistor Q or through either diode CR1 or CR3, depending upon the levels of the input signals.

#### Figure 9-5 2-Input NAND Gate

If both inputs are at a potential above +4V, the current will flow into Ql and cause it to conduct (ON) and keep the output below +0.5V. If either input is below +0.5V, the current will NOT flow into Ql due to the voltage threshold provided by CR2 and the base emitter diode of Ql. In this condition Ql is not conducting and the output is at a potential determined by the external load.

Diode CR1 also provides the turn-off time of Q1 by causing a large reverse base drive current when switching Q1 from its conducting to nonconducting state. Resistor R1 improves the noise and voltage threshold margins by reducing the dc impedance at the base of Q1 during its nonconducting state. Physically these circuit elements are mounted on printed wiring boards to form plug-in units; collectively they are called circuit packs. Also, they are abbreviated CPS which indicates Circuit Pack Schematic.

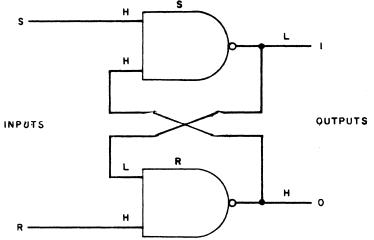

The <u>AND-NOT</u> gate can be used as a universal gate for logic and memory applications and is capable of realizing any switching function. For example, when two gates are connected as shown in Figure 9-6 a bistable or flip-flop condition is created. For instance, assume that inputs S and R are both high and that the circuit is in the reset state (output 0 high, output 1 low). Since both inputs of the S gate are high, its output is low; this in turn keeps one of the inputs of the R gate low and insures that its output is high. Thus, the flip-flop is stable in the reset state.

Figure 9-6 LLL Flip-Flop Gates

If the S input goes momentarily low, the output of the S gate goes high. This causes the output of the R gate to go low because both of its inputs are now high. Since the low output of the R gate is fed back to the input of the S gate, it insures that the output of the latter stays high even when the S input goes high again. The flip-flop is now stable in the set state. It will remain in this state until the R input goes low.

#### E. MAGNETIC CORES

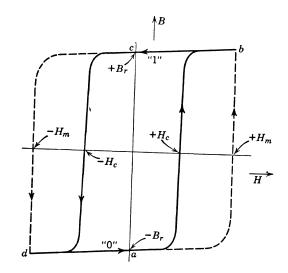

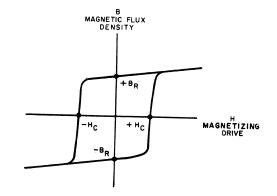

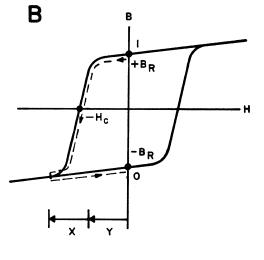

In recent years magnetic cores have been used extensively in memory systems. They have also been employed to a lesser extent in logic circuits. The cores generally used are ferromagnetic toroids and consist either of ceramic ferrite material or of ultra thin metallic tape wound on a nonferromagnetic spool. The distinguishing feature of these cores is a nearly rectangular or "square" hysteresis loop as shown in Figure 9-7.

Figure 9-7 Hysteresis Loop of a Switching Core

In order to switch a core, that is, change its position on the hysteresis loop, it is necessary to exceed a certain threshold of applied magnetizing force. Referring to Figure 9-7, if a magnetizing force is slowly varied between +Hm and -Hm and back again, the flux density variation is that indicated by the solid line. It is possible to operate the core in this manner when inputs to the core are changes of voltage levels. In practice, however, inputs to the core are almost always in the form of pulses. The positive value of the remanent flux +Br corresponds to the 1 state and the 0 state corresponds to the negative value of the remanent state -Br. The 0 state is marked by a and the 1 state is marked by c.

If the core is in 0 state and receives a pulse of short duration having a maximum magnetizing force of +Hm the core will be driven to a positive value of flux density indicated by point b. The path taken between points a, b depend upon the shape of the pulse.

If the variation of the magnetizing force is slow the path is that indicated by the solid line; if the variation of the magnetizing force is fast the path taken is that of the dotted line. Under practical conditions the path will lie somewhere between the two limits. Magnetic cores can perform functions of memory and logic. That the core has "memory" is indicated by its inherent characteristic to remain magnetized to saturation in either the positive or negative direction in the absence of a magnetizing force.

#### 9.3 PROGRAM STORE

The program store (PS) is a random access semipermanent memory used in the No. I ESS. The capacity of the store is 131.072 readout words of 44 bits each. Cycle time to reach any word is 5.5 usec. The information in the store consists of programs and other data which are used to process calls, translate line and trunk information and carry out maintenance procedures and diagnostic tests in the system. The number of PS's required varies from 2 to 6.

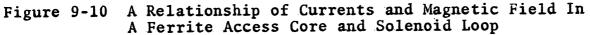

The program store uses twistor modules as the basic storage block. Stored information is in the form of magnetized or demagnetized small bar magnets on removable aluminum cards. The information is semipermanent in that it cannot be changed by any operations in the store including power shut off. To change the information the cards must be removed from the store and the new pattern recorded by means of a card writer.

#### A. APPARATUS ELEMENTS

1. Memory Cards

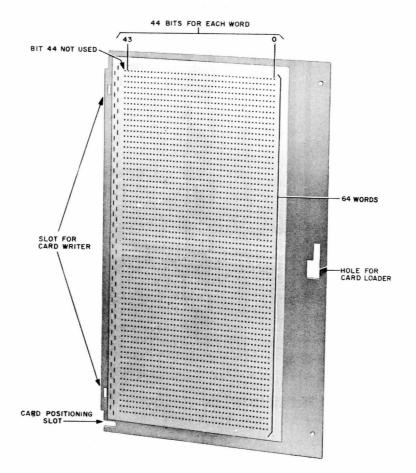

Information is stored in the form of bits (0's or l's) by magnetizing or demagnetizing small bar magnets mounted on aluminum memory cards. A memory card is shown in Figure 9-8; its dimensions are 6-5/8 by 11-1/4 inches.

Each card stores 64 words, each consisting of 44 bits. A 45th bit in each word location is not used for data storage. The 1A memory module holds 128 memory cards. The entire PS includes 16 memory modules. The distribution of words in the program store is summarized below:

- 1 memory card 64 words (44 bits each)

- 1 memory module 8,192 words (128 cards)

- 1 program store 131,072 words (16 modules)

#### Figure 9-8 Memory Card Containing 64 Words

#### 2. Memory Modules

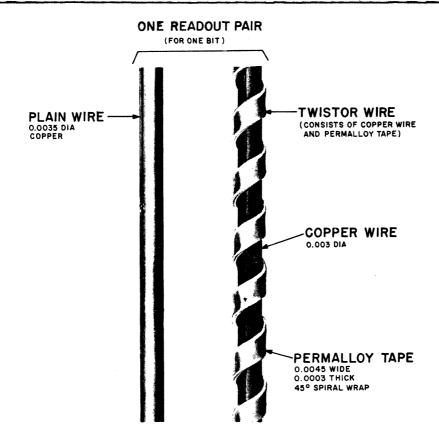

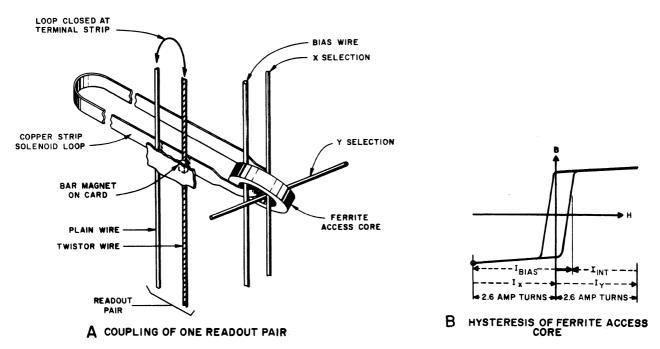

A basic element of the memory module is a 3-mil copper wire that is spiral-wrapped with a thin magnetic permalloy tape; this combination is known as a twistor wire. An enlarged view is shown in Figure 9-9. A plain wire parallels the twistor wire and is paired to it by a connection at one end of both wires. This pair forms the "sensing" or readout loop for one bit of a 44-bit word. The unshorted end of the pair is connected to readout circuitry outside the memory module unit. As shown in Figure 9-10A, the readout pair is perpendicular to a single-turn copper strip solenoid which is driven by a ferrite core. A

bar magnet (mounted on the metal card previously described) is placed at the intersection of the solenoid loop and the twistor wire. Both the permalloy tape and the ferrite core have squareloop magnetic characteristics shown in Figure 9-10B.

When the X and Y leads through the ferrite core are pulsed simultaneously, the combined X and Y drives exceed the continuous dc current through the bias wire. A change of flux takes place in the ferrite core and a pulse is induced in the solenoid loop. The current in the solenoid loop is used to interrogate the bit of information stored in the bar magnet. As explained in more detail in the following paragraphs, a 0 or a 1 output is obtained from the readout pair depending on whether the bar magnet has been magnetized or not.

If the magnet has not been magnetized, the readout is a 1. The permalloy tape provides a magnetic coupling between the solenoid loop and the twistor wire. The interrogating pulse in the solenoid loop induces a pulse in the twistor wire by switching the magnetic flux in the portion of the permalloy tape at the intersection of the twistor wire and the solenoid strip.

When current is removed from the X and Y leads, the ferrite core is restored to its initial magnetic condition by the dc current through the bias wire. The pulse induced in the solenoid loop is opposite in direction to the previous interrogate pulse. Consequently, the portion of permalloy tape at the intersection of the twistor wire and the solenoid strip is switched back to its initial magnetic polarity.

If the memory card magnet has been permanently magnetized, the readout from the twistor pair is a 0. The magnetic field due to the interrogate current in the solenoid loop merely aids the stronger field due to the magnetized bar magnet. Consequently, at the intersection of the twistor wire and the solenoid loop, the permalloy tape retains its initial magnetic polarity, and no voltage is induced in the twistor wire. When the ferrite core returns to its original condition, the pulse induced in the solenoid loop generates a magnetic field which is opposite to, but weaker than, the field due to the magnet. The permalloy tape retains its initial magnetic polarity.

The solenoid current is approximately 1.8 amperes for a duration of 2 usec. A 1 readout in the twistor wire is about 0.6 millivolts.

When a memory card is in place in a module, there are 64 solenoid loops associated with it, one for each row of 45 bar magnets. A pulse in a solenoid loop interrogates simultaneously the corresponding row of 45 magnets on the card.

A preassembled view of a plane of 64 solenoid loops is shown in Figure 9-11. The 64 solenoid loops are encapsulated in an insulated tape which is cemented over a permalloy sheet mounted on each side of the solenoid plane. The permalloy material improves the magnetic coupling between the solenoid loops and the twistor wires. Each solenoid loop parallels a word row of 45 memory magnets when the cards are in place.

There is a separate readout pair for each magnet position in a word row. Each readout pair crosses the same bit position in each of the sixty-four words on the card. The 45 readout pairs (one for each bit) are embedded in a flexible insulated tape. The readout pairs and the interrogating solenoid loops are arranged in a cross-gridded pattern. A miniature bar magnet is located at the intersection of a solenoid loop and a twistor wire when a memory card is properly inserted and positioned.

There are 65 "initializing" permanent magnets in two rows at one edge of the card. These permanent magnets are poled opposite to the memory magnets and are located-between memory magnet rows. They are used to give an initial magnetization to the twistor wire permalloy wraps between the magnet rows. This magnetization occurs as the initializing magnets pass over each twistor wire when the cards are inserted in the memory module. Setting up this magnetization results in improved readouts. The initializing magnets are also used in the external card writing operation to control the timing of the row-by-row magnetization of each memory card.

Figure 9-11 Relationship of Bar Magnets, Readout Pairs, and Solenoid Loops (Preassembled View) When the cards are in place in the module, there are two memory cards associated with each solenoid plane. There is one memory card on each side of a solenoid plane; therefore, 64 solenoid planes are used to read 128 cards in each module.

There are also two separate 45-pair readout tapes, A and B, one on each side of a solenoid plane. The pulsing of one solenoid loop results in the interrogation of two 44-bit words at the same time. One 44-bit word is located on the right card; the other word is on the same row in the left card. However, only one word is sent to central control as specified by the address received by the program store.

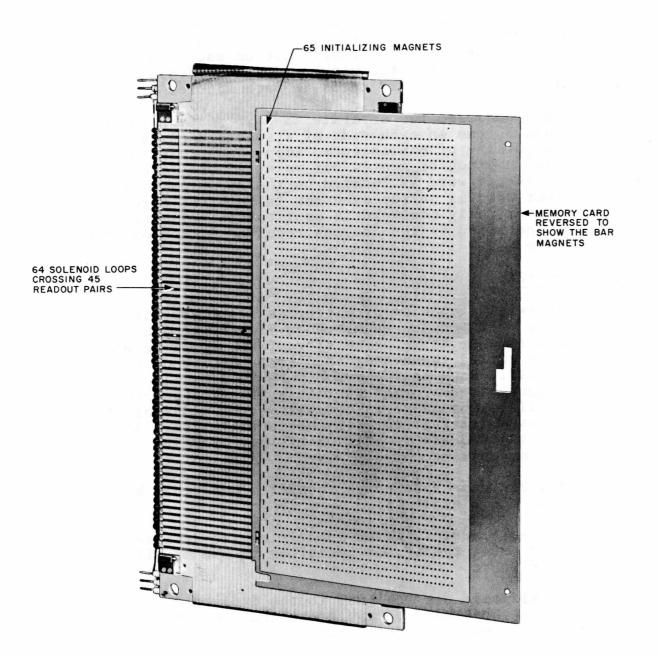

#### **B. MEMORY DUPLICATION**

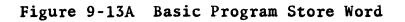

The 16 twistor modules of a program store are divided into two halves of 8 modules each. When viewed from the card inserting side of the program store frame the 8 modules on the left are called the H half and the 8 modules on the right, the G half. Each half of each program store is assigned a unique binary "name" containing two 1's and two 0's, such as 0110. This name is established by means of appropriate cross-wiring at the time of installation. A word to be read out is uniquely identified by the following information from central control:

- (a) A 4-bit name code which specifies the store half that contains the word

- (b) A 16-bit address which identifies the desired word among the 65,536 contained in the specified half-store.

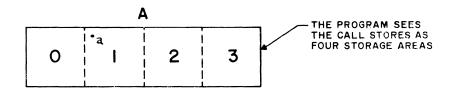

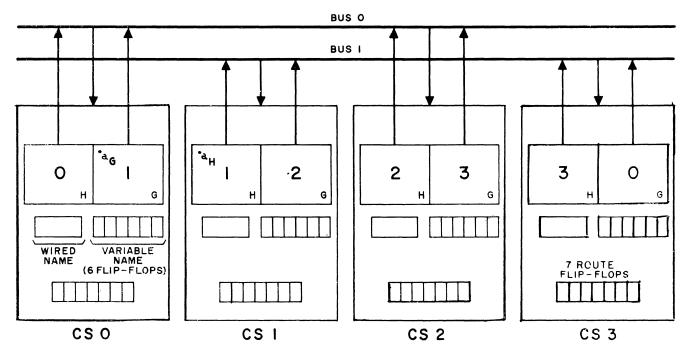

Identical names are assigned to the duplicate information blocks in the G half of one store and the H half of another store as shown in Figure 9-12B.

Normal nonmaintenance programs are written without considering duplication. In a 4-store office, although there are actually four pairs of duplicate information blocks  $(0_H, 0_G; 1_H, 1_G; 2_H, 2_G; and 3_H, 3_G)$ , the programs "see" only the four unduplicated blocks shown in Figure 9-12A. Assume that a program wants to read the word A in block 1. As shown in Figure 9-12B, there are actually two copies of this word available, one copy  $a_G$  in PS 0, and the other copy  $a_H$  in PS 2. CC identifies word a by means of a 20-bit address which is divided into a <u>4-bit name code K</u> to specify information block 1 and a <u>16-bit address A</u> to specify the word within information block 1. The name code K and the address A are transmitted by CC on both buses to all the PS's. However, only PS 0 and PS 2 will detect a match between the name code and a name internally assigned. As a result, only these two stores will use the address A. Within each of the two stores, the 16-bit address A received from the buses is supplemented by a seventeenth bit A16 to select the appropriate half store. In the example considered, PS 0 generates an A<sub>16</sub> = 1 in order to locate the word a<sub>G</sub>; PS 2 generates an A<sub>16</sub> = 0 to locate the word a<sub>H</sub>.

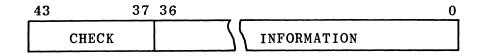

The basic 44-bit program store word in always organized into 7 checking bits and 37 information bits as shown in Figure 9-13A.

|      | PROGRAM STORE ADDRESS STRUCTURE |               |     |     |                           |            |     |     |       |                |      |    |   |     |      |     |      |    |   |      |    |

|------|---------------------------------|---------------|-----|-----|---------------------------|------------|-----|-----|-------|----------------|------|----|---|-----|------|-----|------|----|---|------|----|

|      | Ø. DIGIT                        |               |     |     |                           |            |     |     |       |                |      |    |   |     |      |     |      |    |   |      |    |

| 9.26 | BINARY CODE                     |               |     |     |                           |            |     |     |       |                |      |    |   |     |      |     |      |    |   |      |    |

|      | BIT POS ON BUS.                 | E21           | E20 | E19 | and the second statements | E16        | A15 |     | A13   | A12            | A11  |    |   |     |      | A6  | A5   |    |   |      | AO |

|      |                                 |               |     |     |                           | MOD        | IN  | 1/2 | STORE | 0 = R<br>1 = L | CARD | IN | А | 1/2 | MODI | ULE | WORD | ON | A | CARD |    |

|      | FUNCTION                        | PROGRAM STORE |     |     |                           |            |     |     |       |                |      |    |   |     |      |     |      |    |   |      |    |

|      |                                 |               |     |     |                           | 0=H<br>1=G |     |     |       |                |      |    |   |     |      |     |      |    |   |      |    |

Figure 9-13B Locating a Word in Program Store

1 ELECTRONIC SWITCHING SYSTEM

CH.

9

- NO.

#### C. ADDRESS STRUCTURE

The program store address structure is shown in Figure 9-13B. The addressing scheme used to select a single program store word uses twenty bits. These twenty bits originate from the central control program address register (PAR) and are pulsed out to a program store over the central control to the program store bus system. A component translating circuit of the PAR alters the four most significant bits of an address into a two out of four code called the K code. The resultant four bits appear on bus lead pairs E19 to E16 and must match the corresponding K code name wired into the program store half that contains the word to be selected. The PAR can be arranged for six bit selection of program stores in which case the K code would become a two out of six code and would be displayed as bits E21 to E16 in the PAR. If the K code derived from the address has a 0 bit in position E16 and H half will be selected, a 1 bit selects the G half. The next three bits (A15 to A13) are used to select the module location (all 0 bits equal module 0 while all 1 bits equal module 7) within the Program Store half. The following bit (A12) is used to determine which readout tape will be used the A side (Left) or the B side (Right). If this bit is 0 the B tape reads the right hand memory cards and if the bit is a 1 the A tape will read the left hand cards. Each module has 128 memory cards with the cards numbered 0 to 63 on the right and 64 to 127 on the left. The following six bits (All to A6) will select one of the 64 cards and the last six bits (A5 to A0) will select one of the 64 Program Store words on a card. Word 0 is located at the bottom of the card while word 63 is located at the top.

#### D. BUS INPUT AND OUTPUT CONTROL

Seven flip-flops within each PS control the inputs and outputs to and from the buses. These flip-flops operate as follows. A flip-flop RO allows the store to receive only from bus 0, if set; from bus 1, if reset. Two flip-flops, HSO and HSI, determine whether the normal readouts from the H half shall be sent on bus 0 and/or bus 1. These readouts can be sent on bus 0 if HSO is set; on bus 1 if HS1 is set. Similarly, two flip-flops GSO and GS1 determine whether the normal readouts from the G half shall be sent on bus 0 and/or bus 1. Two trouble flip-flops TBLO and TBL1, when set, disable both input and output communications between the PS and buses 0 and 1, respectively. The selection of input and output buses under normal conditions with an even number of program stores is shown in Figure 9-12B, Bus 1 supplies the address and receives the readout for a word such as  $a_G$  in PS 0. Bus 0 supplies the address and receives the readout for the duplicate copy aH. The same applies to all the other information blocks. This is also true for an odd number of program stores except for the highest numbered pair of H and G information blocks, both of which take the address from bus 0.

#### E. BASIC MEMORY UNIT

The decoder shown in Figure 9-14 compares the name code received with the names assigned to the two halves of a store. If a match is found, the decoder generates a seventeenth address bit  $A_{16}$  which is 0 for the H half, 1 for the G half. The complete address is stored in the address register to be used by the access circuits which select one

Figure 9-14 Basic Memory Unit

and only one ferrite access core. This is done by pulsing one of 256 X selection wires and one of 256 Y selection wires. The magnetic flux of the selected access core is changed and a pulse is induced in the associated solenoid loop. This pulse interrogates simultaneously two 44-bit words on two cards causing simultaneous readouts into two sets of readout loops which are fed to the readout circuits. Here a selection is made between A and B readouts on the basis of address bit  $A_{12}$  and a 44-bit output is generated for transmittal to the CC. An all-seems-well bit and a synchronizing bit are also transmitted to CC.

#### F. ACCESS CIRCUITS

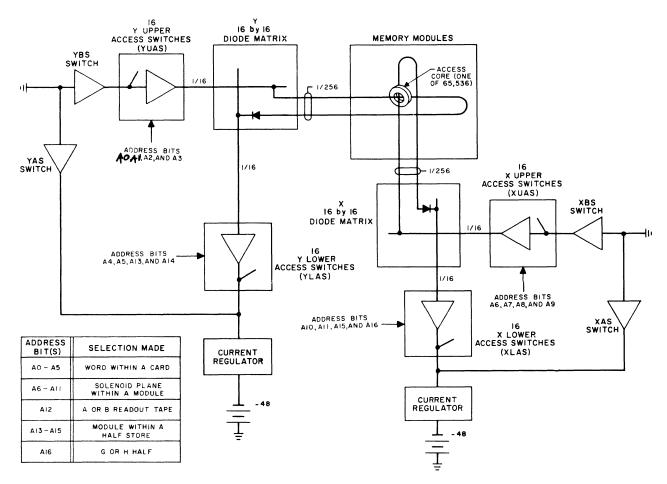

Figure 9-15 shows schematically how the selection of a single access core is achieved through the use of electronic switches. The 16 Y upper access switches (YUAS) on the left

Figure 9-15 Method of Selecting a Single Access Core

are controlled by the 16 possible combinations of the four address bits  $A_6$  to  $A_9$ . Current can flow through only one YUAS as selected by the four address bits. Similarly, only one of 16 Y lower access switches (YLAS) is closed. In the Y diode matrix, current can flow in only one of 16 horizontals and one of 16 verticals (the diodes eliminate the possibility of sneak paths). Thus, only one of 256 Y wires is pulsed. Similar considerations apply to the selection of one of 256 X wires. When a selection is made, the YAS and XAS switches open. This transfers the regulator current to the selection circuits. When the selection is completed, the normally closed YBS and XBS switches open, the YAS and XAS swithces close, and the current again is shunted to ground. Once the current transfer is completed, the YBS and XBS switches reclose. (All the upper and lower switches are now open.)

#### G. READOUT CIRCUITS

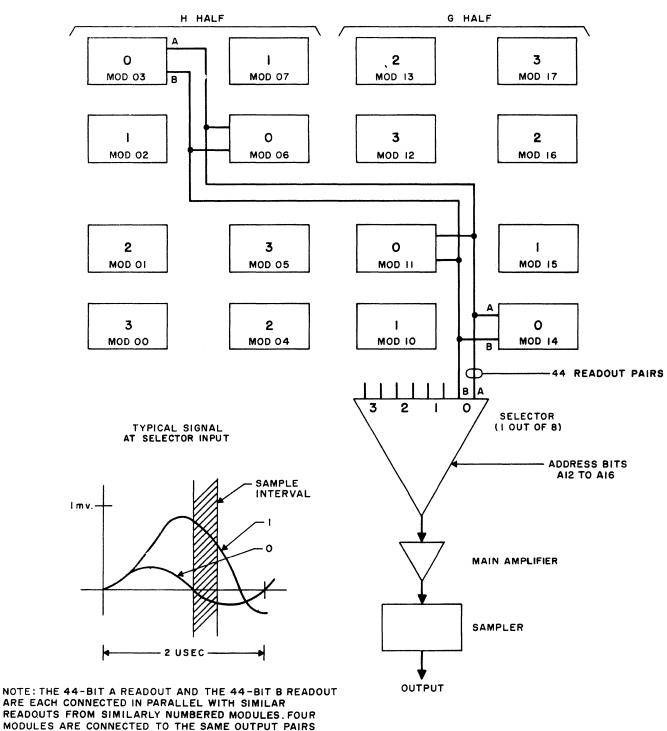

As shown in Figure 9-16, the A and B readout pairs of four similarly numbered modules are connected together to form a common output to a selector. Each readout pair is shorted at a terminal strip at one end of each module. Of the eight sets of readout pairs, only one is detected on the basis of bits  $A_{12}$  to  $A_{16}$ . With the arrangement described, when a readout takes place in one module, no X or Y current is present in any other module wired to the same readout pairs. This reduces the noise effects of an X or Y current on the selected readout.

#### H. MODES OF OPERATION

The main function of the program store is to supply the binary coded information necessary to operate the system. In addition to providing the system program, other modes of operation are necessary for diagnosing troubles within the store and to change the states of various operating conditions.

The address from central control to the program store via the address bus consists of 25 bits. These 25 bits indicate what type of operation the store is to perform, which store or stores are to respond, and the location of the information within the store. The input word structure is one sync bit, four K code bits, four mode bits, and 16 address bits.

TWISTOR MODULE ARRAY

IN EACH WIRING PATTERN.

9.31

# 1. Normal Mode

This mode is used during the routine operation of the central office when central control is obtaining program and translation information from the program store twistor modules. In a normal mode, the choice of address buses to receive on and the choice of answer buses to send on are completely flexible. The program stores are divided into two halves designated H and G. In a central office the information in the H-half of one store will be duplicated in the G-half of another store. During a normal mode, if all systems are functioning properly, two program stores will answer an address sent by central control; one from the H-half of one store and one from the G-half of another store. The information is the same from either store. The address sent to the two program stores can be sent on one bus or on separate buses, but each program store must answer on separate buses.

### 2. Maintenance Mode

This mode differs from a normal mode in that only one half of one store will respond to the address. In addition, the particular store designated in the maintenance mode will answer on the same bus on which it has received the address. In a maintenance mode the program store delivers a normal twistor readout, but the readout is used for diagnostic checks rather than for system instructions. For example, if an access switch is faulty, central control may instruct the program store to roster through a number of addresses to determine which ones are reading incorrectly and thereby locate the faulty access switch.

There are two maintenance modes, H maintenance and G maintenance. H maintenance instructs the program store to send the information requested in the address from the H side of the store. The G maintenance designates the information be sent from the G side of the program store.

# 3. Control Mode

In order to allow the system to observe or evaluate conditions within the program store and to permit these conditions to be altered a control mode is provided. The control mode is subdivided into a read control and a write control mode. No access or twistor readout occurs during a control mode.

### a. Read Control Mode

For the system to perform its diagnostic tests on the program store, it is necessary to know the status of a large number of points internal to the store. This information can be sent to central control via the bus pairs in the read control mode. The points checked consist of such things as the state of flip-flops, gates, timing packages, and any other conditions needed to locate troubles in a store. During a read control mode there is no drive supplied by the access to the twistor modules and therefore no memory readout. Instead the readout word normally sent to central control is replaced by a word composed of 44 read control bits. To increase the number of read control bits which can be sent, there are four groups of 44 bits, any group of which can be read out during a cycle. Thus, theoretically, the number of available read control bits is increased to 176. Actually only 160 bits can be used since the last four bits of each group are used to indicate which group is being read out. The groups of read control bits are called rows. The bus selection in a read control mode is identical to that of a maintenance mode; the program store must answer on the same bus on which it has received the address.

#### b. Write Control Mode

The write control mode permits central control to set up a desired set of conditions in the store via the address bus pairs. In a write control mode, no readout occurs from the program store. The function of a write control can be for either diagnostic purposes or the normal changing of routing for example, the routing of the program store buses. Since there are a number of functions the write control can perform, a steering bit is sent with the write control address to instruct the program store which condition to institute.

Generally, a cycle in the write control mode is followed by a read control to verify that the locations were actually written as specified by the write control mode.

Besides the internal points in a program store that are written by the write control mode there are internal points which are controlled directly by the central pulse distributor. This allows the system to maintain some control over a program store in the event of bus or store failure.

There are also internal points called scan points which are not read out by the read control mode. The scan points are handled in two ways. Part of them are permanently connected to the master scanner. The remainder of them can be connected to the master scanner through the monitor bus. The scan points that are permanently connected to the master scanner are critical circuit points that need continuous monitoring. Connection to the other scan points through the monitor bus is slow but makes it possible to diagnose troubles independent of the program store and the communication buses. Also, for some of the points in the store it is just not practical to monitor in any other manner.

There will be times when a program store will have to be brought back into service after it has been out of operation. Central control will try to do this automatically through the emergency alarm bus. If central control fails then the program store is put in operation manually. The manual control is done at the master control center. The master control center communicates to the store via the override leads.

## 9.4 CALL STORES

The call stores (CS) provide a temporary, or readwrite, type of memory; that is, they provide the means for recording information that later can be read, altered, or erased by the system. This temporary memory is used by the central control (CC) and the signal processors (SP). It serves to store information that is related mainly to the handling of telephone calls (hence, the name call store). The information stored in temporary memory includes:

- (a) Busy-idle status of customer lines, junctors, trunks, network links, etc.

- (b) Records of network terminations being used for each call in progress.

- (c) Digits received.

- (d) Digits to be outpulsed.

- (e) Customer billing information prior to recording on the automatic message accounting (AMA) tape.

- (f) Recent change information related to customer lines and trunks prior to updating the translation information in the program stores (PS).

- (g) Maintenance information related to programcontrolled diagnostic tests.

The information contained in a CS is organized in words of 24 bits as shown in Figure 9-17. One of these bits is used for parity checking. Each word occupies a word location uniquely identified by an address. Inputs from CC specify the operation to be performed (reading or writing), the address of the location involved, and, in the case of writing, the word to be written. The CS carries out the request and, in the case of reading, transmits to CC the word that it has read. The CS is also capable of performing special operations for control or maintenance purposes.

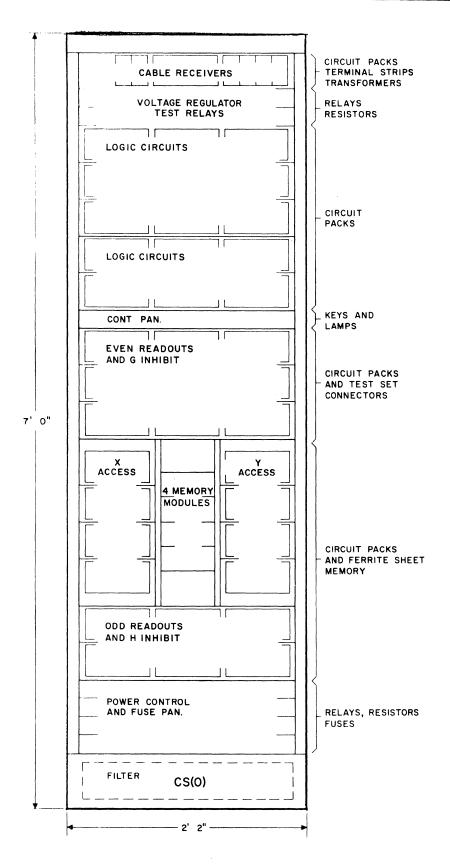

A single CS has 8,192 word locations, thus providing a total storage capacity of 196,608 bits. The shortest allowable time interval between consecutive store operations is 5.5 usec. The number of CS's needed depends on the office size. Taking duplication into account, the maximum number of CS's associated with the CC could be 39. Where SP's are provided, each pair of SP's may have up to eight CS's. A call store frame is shown in Figure 9-18.

An example of the storage requirements for a central office with 5,000 lines and 4,500 calls per busy hour is given below:

| Requirements independent of office size | 3,000 words                                |

|-----------------------------------------|--------------------------------------------|

| Call processing                         | 4,800 words                                |

| Network map                             | 2,400 words                                |

| Maintenance and administration          | 1,400 words<br>11,600 words (unduplicated) |

## Figure 9-17 Basic Call Store Word

## A. APPARATUS ELEMENTS

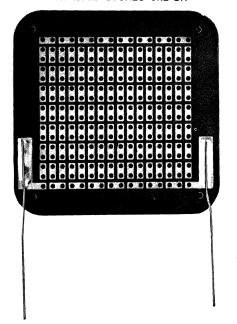

1. Ferrite Sheet

The basic storage element in the CS is the ferrite sheet shown in Figure 9-19. The ferrite sheet is approximately one inch square and 30 mils thick. Each sheet contains 256 holes in a 16 by 16 array. The holes are 25 mils in diameter and are placed on 50-mil centers.

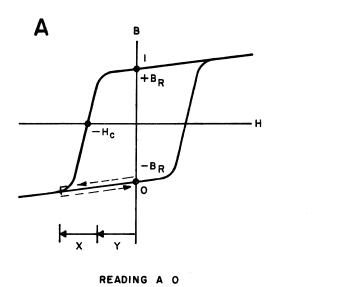

The ferrite sheet material (magnesium-manganese) has a square-loop magnetic characteristic (Figure 9-20). After the removal of a magnetizing drive, the ferrite material retains either a positive or a negative remanent magnetization,  $+B_R$  or  $-B_R$ . In order to "switch" or reverse the magnetization from  $-B_R$  to  $+B_R$ , it is necessary to apply a positive magnetizing drive that must exceed a threshold value,  $+H_C$ . Similarly, in order to switch from  $+B_R$  to  $-B_R$ , it is necessary to apply a negative drive that must exceed a threshold value,  $-H_C$ .

9.36

Figure 9-18 Call Store Frame Layout

9.37

256 HOLES IN A 16 BY 16 ARRAY EACH HOLE STORES ONE BIT

Figure 9-20 Square-Loop Characteristic

### Figure 9-19 Ferrite Sheet

If the ferrite material is in the remanent state  $+B_R$ , a negligible change in magnetization results from a positive drive or from a negative drive that does not exceed  $H_C$ . This is due to the fact that the upper and lower sides of the loop are almost horizontal. Similar considerations apply when the ferrite material is in the remanent state  $-B_R$  and the applied drive is negative or less than  $H_C$ .

A bit of information can be stored in the material immediately surrounding each hole of the ferrite sheet by magnetizing the material either clockwise or counterclockwise. One state of remanent magnetization is identified as the binary value 0 and the opposite state of remanent magnetization is identified as the binary value 1.

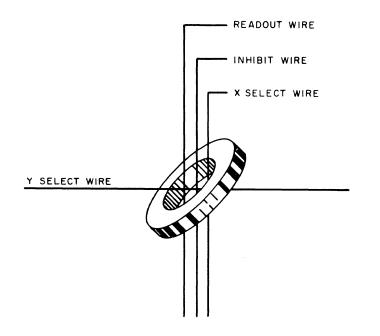

The ferrite sheet can be considered to be equivalent to an array of 256 miniature magnetic cores such as the one shown in Figure 9-21. Four wires are associated with each core: two select wires X and Y, a readout wire, and an inhibit wire.

THIS CORE IS EQUIVALENT TO ONE HOLE IN THE FERRITE SHEET

Figure 9-21 Principle of Memory Core Switching Operation

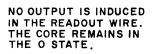

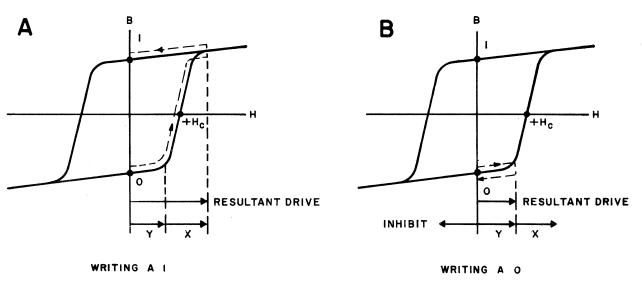

In order to read the binary content of a core, the X and Y wires are simultaneously pulsed, each with a current of 250 ma (Figure 9-22). The combined drive exceeds the threshold value and is applied in a negative direction. This drive tends to reset the core, that is, to put it in the remanent state associated with 0. If the core happens to be already in the 0 state, there is a negligible change in magnetization which results in a negligible output induced in the readout wire. On the other hand, if the core is initially in the 1 state, the combined X and Y drives cause a change in magnetization from  $+B_R$  to  $-B_R$ . This induces an output of approximately 50 millivolts in the readout wire. Thus, the presence or absence of an output in the readout wire indicates whether the core was initially in the 1 or 0 state. Regardless of its initial condition, the core is forced into the 0 state by the reading operation. For this reason, the core is said to have a destructive readout. The information, however, will be restored into the core by writing back whatever was read out.

READING A I

AN OUTPUT IS INDUCED IN THE READOUT WIRE. THE CORE CHANGES TO THE O STATE.

THE CORE IS INITIALLY IN THE O STATE AS A RESULT OF A READING OPERATION

Figure 9-22 Reading a Memory Core

THE CORE SWITCHES FROM THE O STATE TO THE I STATE. THE PRESENCE OF THE INHIBIT DRIVE PREVENTS THE CORE FROM SWITCHING TO THE I STATE.

Figure 9-23 Writing in a Memory Core

In order to write back a 1 (Figure 9-23A), the X and Y wires are again simultaneously pulsed, each with a current of 250 ma. The direction of the applied drive is now opposite to that used for reading. Consequently, the core is "set" or switched from state 0 to state 1. In order to write a 0 (Figure 9-23B), the X and Y wires are again pulsed in the positive direction; at the same time, the inhibit wire is pulsed in the negative direction. The combined drive due to the inhibit wire and to the X and Y wires is less than  $H_{C}$ . Consequently, the core is not switched and is left in state 0.

When new information is to be written into a core, a readout is performed first to force the core into the 0 state. Writing takes place then in the manner previously described. Whether a pulse is applied to the inhibit wire is determined, not by the bit that was read out, but by the bit to be written. If a 0 is to be written, an inhibit drive is applied.

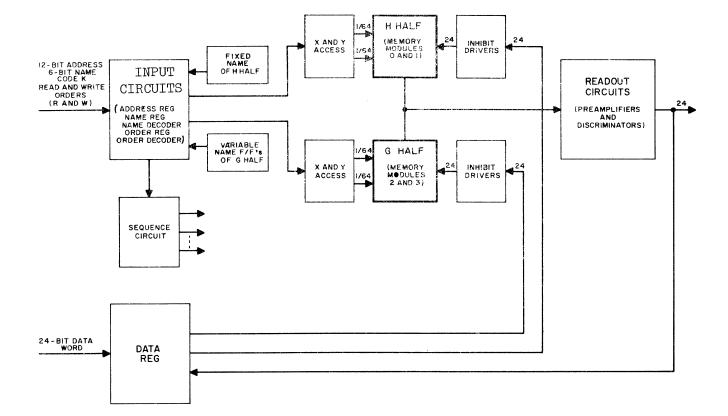

## B. BASIC MEMORY UNIT

As previously stated, the 8,192 word locations contained in a CS are divided into two information blocks known as the H half and the G half. Ferrite sheets of submodules 0 and 1 are in the G half and submodules 2 and 3 are in the H half. Each submodule contains 2,048 words. Each store-half has a 6-bit "name." The H half is assigned a fixed name by appropriate cross wiring at the time of installation. The G half, instead, is assigned a name by setting an appropriate combination on six flip-flops. The status of these name flip-flops can be changed under program control. This flexibility in identifying blocks of memory permits the physical location of the stored data to be changed to other call stores in case of trouble. Figure 9-24 illustrates the scheme for duplicated call store memory blocks.

| ſ | Н | G     | H | G  | H | G   | H | G | H  | $\left[ \left( \right] \right]$ |        | G H |              | G | HALF     |

|---|---|-------|---|----|---|-----|---|---|----|---------------------------------|--------|-----|--------------|---|----------|

|   | 0 | 0 1 2 |   | 2  | 3 | 3 4 |   |   |    | 3                               | 6      | 0   | MEMORY BLOCK |   |          |

| · | 0 | 0     | C | )1 | 0 | 2   | 0 | 3 | 04 | 1                               | $\Box$ | 35  | 3            | 6 | CS FRAME |

# Figure 9-24 Duplicated Call Store Memory Blocks

The addressing scheme used to select an individual word location requires 18 bits. The 12 least significant bits are used to select one of 4,096 words and the 6 most significant bits are used as K code bits which select the memory block with the matching K code name. The bit positions of the central control to call store bus, used for addressing are identified in the call store address structure shown in Figure 9-25.

| ſ | Ø DIGIT     |     |    |     |     |     |  |   |    |     |    |     |    |   |    |

|---|-------------|-----|----|-----|-----|-----|--|---|----|-----|----|-----|----|---|----|

|   | BINARY CODE |     |    |     |     |     |  |   |    |     | -  |     |    |   |    |

|   | BIT POS     | A17 |    |     | A12 | A11 |  |   |    |     |    |     |    | A | 00 |

|   | FUNCTION    |     | КС | ODE |     |     |  | 0 | NE | OUT | OF | 409 | 96 |   |    |

# Figure 9-25 Call Store Address Structure

The basic portion of a call store is shown in Figure 9-26. Within each CS, separate access circuits are provided for the G and H halves. If the name code K received by a CS matches the name of the H half or the G half, the appropriate access circuit is activated. The signals received on the order leads R and W determine whether a reading or writing operation is to be performed at the specified word location. Either operation is carried out in two stages.

# 1. Reading

During the first stage of a reading operation, access is gained to the desired word location by pulsing one of 64 X leads and one of 64 Y leads in the appropriate store half. The direction of the X and Y currents is such that each bit of the interrogated location is left in the 0 state. The signals from the memory modules go to the readout circuits where they are amplified and then submitted to discriminators. These determine whether each input is to be considered a 1 or a 0 and generate accordingly an appropriate output,

# Figure 9-26 Basic Call Store

The outputs of the readout circuits in the read operation are also stored in the data register. During the second stage of a reading operation, the information read out is written back as follows. The word location previously read is again selected by pulsing the same X and Y leads but in the opposite direction. Thus, the X and Y currents tend to write a 1 in each bit of the selected word location. However, any bit of the data register that is equal to 0 activates an associated inhibit drive which applies a pulse to an inhibit wire. This prevents the writing of a 1 in the corresponding bit position.

# 2. Writing

During the first stage of a writing operation, the specified word location is read out as previously described. However, the outputs of the readout circuits are not gated into the data register. Thus, the net effect of this first stage is to clear the specified word location. The data register is set by 24 bits received via the bus from CC. During the second stage, this information is written into the selected word location in the manner previously described. The sequence control generates all the necessary timing pulses.

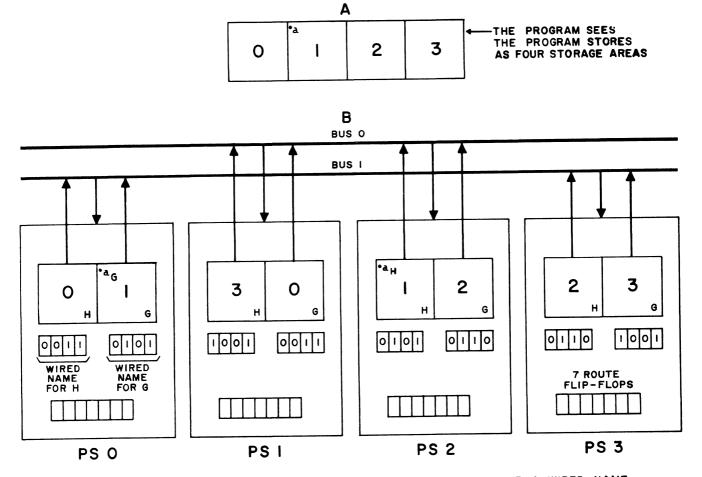

#### C. NORMAL INPUT-OUTPUT CONTROL

As previously described, each store-half information block is assigned a name of six bits. The purpose of this coding is to permit selective communication with a number of CS's using a common bus system. Figure 9-27B shows, as an example, four CS's connected to two duplicate buses. Normally, identical names are assigned to the duplicate information blocks in the G half of one store and the H half of the next store.

Nonmaintenance programs are written without taking into consideration that the information is duplicated. In the example considered, there are actually four pairs of duplicate information blocks:  $0_H$  and  $0_G$ ,  $1_H$  and  $1_G$ ,  $2_H$  and  $2_G$ , and  $3_H$  and  $3_G$ . However, the programs "see" only the four unduplicated information blocks shown in Figure 9-27A.

For example, assume that a program wants to read the word a in information block 1. As shown in Figure 9-27B, there are actually two copies of this word available, one copy  $a_G$  in CS 0 and the other copy  $a_H$  in CS 1. The CC identifies the word a by means of an 18-bit address which can be divided into a 6-bit name code K to specify information block 1, and a 12-bit address A to specify the word within information block 1. The name code K and the address A are transmitted by CC on both buses to all the CS's. However, only CS 0 and CS 1 will detect a match between the K code and a name internally assigned. As a result, only these two CS's will use the address A. In CS 0, the access circuit activated is that of the G half since its name matches the name code received. Similarly, in CS 1, the access circuit activated is that of the H half.

В

NOTE: THE H-HALF NAME OF EACH STORE IS WIRED AND FIXED. THE G-HALF NAME IS SET ON 6 FLIP-FLOPS AND IS VARIABLE.

Figure 9-27 Call Store Name and Route Flip-Flops

Seven route flip-flops within each CS control the inputs and outputs to and from the buses. A flip-flop R0 allows the store to receive only from bus 0, if set; from bus 1, if reset. Two flip-flops HSO and HS1 determine whether the normal readouts from the H half shall be sent on bus 0 and/or bus 1. These readouts can be sent on bus 0 if HSO is set, on bus 1 if HS1 is set. Similarly, two flip-flops GSO and GS1 determine whether the normal readouts from the G half shall be sent on bus 0 and/or bus 1. Two trouble flip-flops TBLO and TBL1, when set, disable both input and output communications between the CS and buses 0 and 1, respectively.

# D. INPUTS TO THE CALL STORE

Inputs to the call store consist of three sets coming from the Signal Distributor Applique, the Central Pulse Distributor, and the Central Control Circuits. Another input set consists of the +24 volt, -48 and ground for the store. The inputs from the Signal Distributor Applique Circuit have direct control of relays in the call store and the pulses from the CPD Circuit control certain flip-flops.

There are 53 Central Control Circuit inputs to the store comprised basically of five groups of information - six code bits, three mode bits, 12 address bits, three readwrite-parity bits and 24 data bits. There are two buses, bus 0 and bus 1 where the 53 inputs are duplicated.

Five synchronization pulses are provided by Central Control Circuit for these groups of information: one for the code-mode, one each for the address and read-write-parity group, and two for the data bits.

There are four varieties of output leads. The first uses twisted pair to carry dc signals from flip-flops, relays and voltage regulators to the ferrods of the Master Scanner Circuit. The second is a single wire power alarm and the third are test points for battery supplies, internal circuit modes, and the store field test set.

The fourth variety consists of 26 answer leads for the Central Control Circuit duplicated on bus 0 and bus 1. Twenty-four are the call store readouts, one the all-seemswell signal, and the last a sync pulse.

## E. MODES OF OPERATION

There are four basic modes of operation in a call store.

- (a) Normal mode In this mode, the call store serves as a memory for the system with ability to read and regenerate the contents of a selected word, or to erase the old contents and write in new information.

- (b) Maintenance mode This mode is almost identical to the normal mode. The normal mode has more flexibility based on K-code matches, while the maintenance mode has less selective options since the use of the K-code matches are limited. This mode is used when Central Control Circuit directs specified maintenance tests of certain locations in a particular store.

- (c) Control write The control write mode can alter the state of call store flip-flops. In addition, sections of the sequence control and memory circuits can be tested without fully addressing the modules.

- (d) Control read The states of key flip-flops and the absence or presence of store pulse points is noted and sent to Central Control Circuit.

- F. CALL STORE ORGANIZATION FOR DUPLICATION AND TROUBLE SWITCHING

The number of call stores needed, depends upon the size of the system. A large electronic central office might require as many as 6,000,000 bits of call store memory. However, one-half million bits might be adequate for a small office. Signal Processor Circuits when provided in an electronic central office, may use up to eight call stores for each pair of Signal Processors. Because stored information is duplicated for reliability, these totals include call stores required for complete duplication.

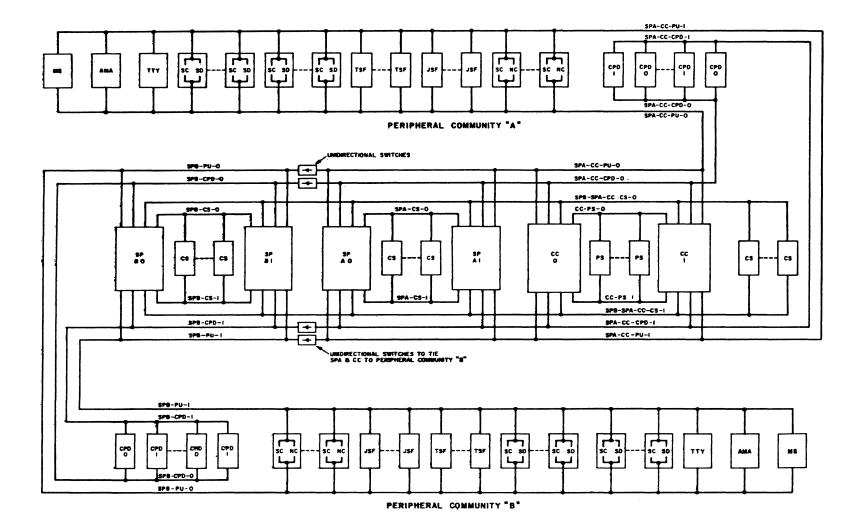

In the actual organization of the central office equipment, the call stores are grouped with Central Control, Signal Processor, and Program Store Circuits in a number of control communities as shown in Figure 9-28. Normally, the Central Control and Signal Processor Circuits operate simultaneously and independently; consequently, the Central Control Circuits and each pair of Signal Processor Circuits must have separate call stores of their own. It must be possible, however, for Central Control Circuits to stop a pair of Signal Processor Circuits and use their call stores. The Central Control Circuits have access to the call stores of a signal processor community via the Signal Processor Circuits in that community.

The control community consists of two duplicate Central Control Circuits and their call stores. The plan of Figure 9-28 also provides for up to two signal processor communities, each consisting of two duplicate Signal Processor Circuits and their call stores.

Two duplicate buses (CC-CS bus 0 and CC-CS bus 1) link together the Central Control Circuits, their call stores, and the Signal Processor Circuits. Each signal processor community has two duplicate buses (SP-CS bus 0 and SP-CS bus 1) linking its Signal Processor Circuits and call stores. Each bus consists of 53 pairs to the call stores and 26 pairs from the call stores. Each call store can communicate on either or both duplicate buses, regardless of whether it is working with a Central Control or a Signal Processor circuit.

Figure 9-28 Office With Two Pairs of Signal Processors

9.48

9 - NO. 1 ELECTRONIC SWITCHING SYSTEM

CH.

## 9.5 CENTRAL CONTROL

## 1. General

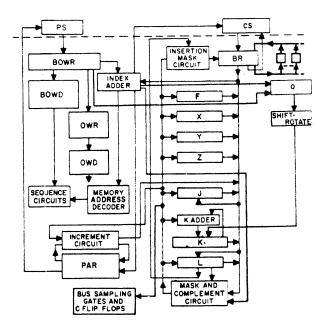

<u>Central Control</u> (CC) is the primary data processing unit of the No. 1 Electronic Switching System. Its purpose is to execute a program or sequence of instructions obtained from a program store. Under direction of the program, the central control receives input information from lines and trunks via the scanners, performs logical and arithmetical operations, and causes basic actions to be carried out in all parts of the system in the process of completing telephone calls and diagnosing system troubles.

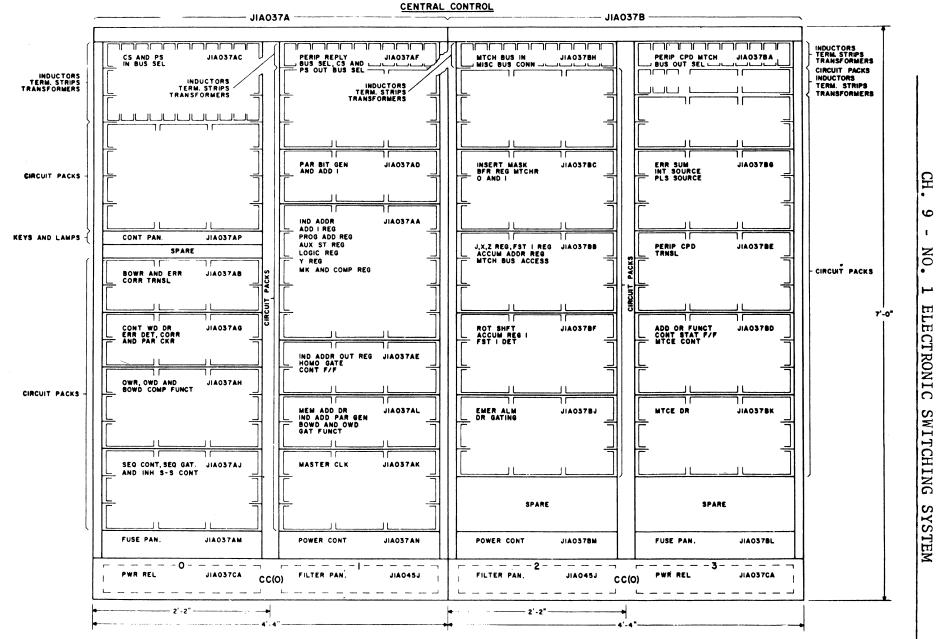

The logic circuits used in the central control are assembled on 4-by 7-inch printed circuit boards which plug into rack-mounted connectors. Four 7-foot bays house the equipment for central control. Various types of boards (commonly called packages) provide logic gates, flip-flop register elements, amplifiers, etc. The boards are interconnected to form specific logic functions by wiring together the terminals associated with the connectors. External communications between the CC and other system units are conducted over twisted pair cables which are connected to receiving or transmitting gates in the respective units.

### 2. General Method of Operation

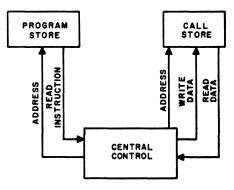

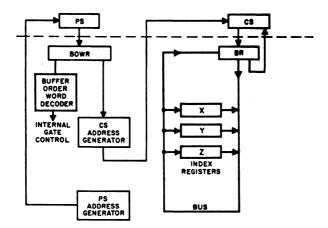

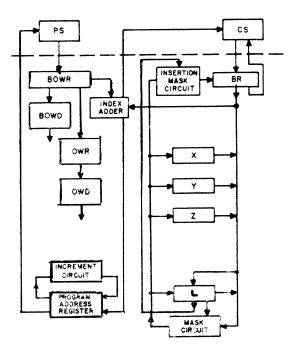

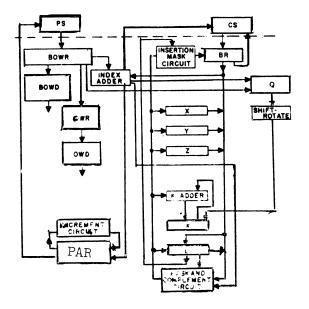

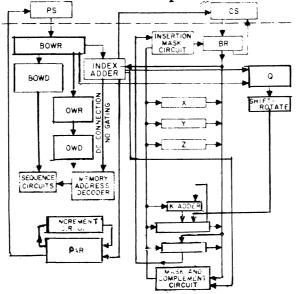

The object of the central control is to carry out the stored program that has been provided for the system. The stored program is composed of sequences of instructions, each carrying out a data processing step (or steps) that contribute to the task to be performed. The order structure is defined to be the repertoire of instructions from which programs are constructed. Figure 9-29 shows the basic data processor of the No. 1 ESS. This consists of Central Control, Program Store, and Call Store. As will be seen later, the central control also deals with peripheral equipment, but the basic data processing operations are associated with the two stores.

Figure 9-29 Block Diagram of Data Processor

The program store contains the programs for both call processing and system maintenance. In addition, each customer line has associated with it a number of translation constants. These constants are stored as translation words in the program store. In the face of system troubles, the program and translation words must be retained. Accordingly, the program store is a semipermanent memory which is not altered in the course of program execution. It may be addressed in order to read out instructions and data, but it may not be written into.

Temporary, or destructible, memory is provided in the call store. It contains call processing data that changes as calls are established and terminated in the system.

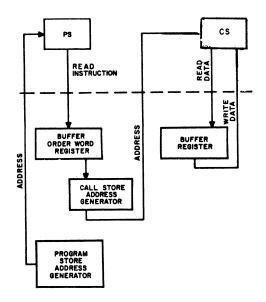

To provide optimum data processing capability, the central control can simultaneously address the program store to request an instruction, and the call store for a data operation.

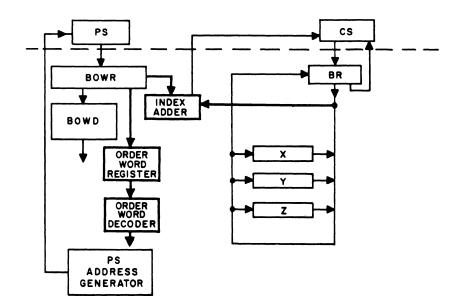

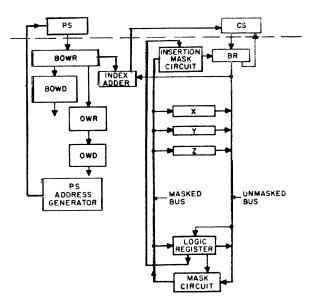

We, therefore, have as the most basic elements of central control the items shown in Figure 9-30, namely a Program Store Address Generator, a Program Store Data Reception Center, (Buffer Order Word Register), a Call Store Address Generator, and a call store data reception and data transmission register (Buffer Register). The call

Figure 9-30 Basic Elements of Central Control - Part 1

store address generator will be described later. The buffer register serves both as a recipient of information from the call store and as a source of information to be transmitted to the call store.

## A. INDEXING

As shown in Figure 9-31, the Buffer Order Word Register has associated with it, a buffer order word decoder so that gates may be controlled on the basis of the instructions read from the program store. Instructions are coded pieces of information used to specify for central control the operations that it must perform. Central control performs the operations by gating information from one place to another internally, and by sending signals out to the units which it controls, such as the call stores and peripheral In order to be able to manipulate information reunits. ceived from the call store, CC must contain a number of internal registers (indexing registers X, Y, Z). These indexing registers are nothing more than flip-flop groups that can store a binary word of information.

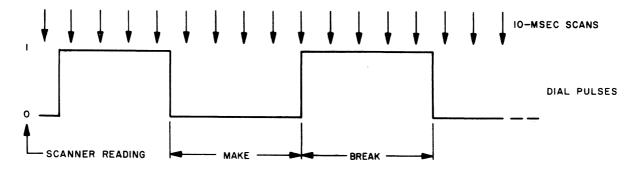

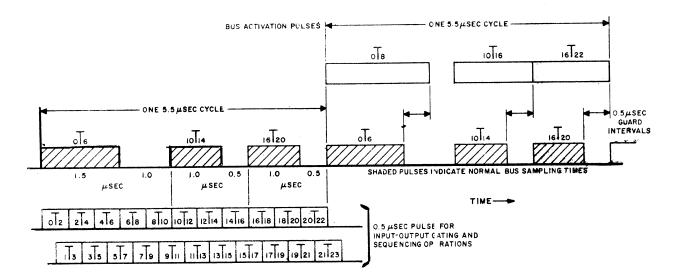

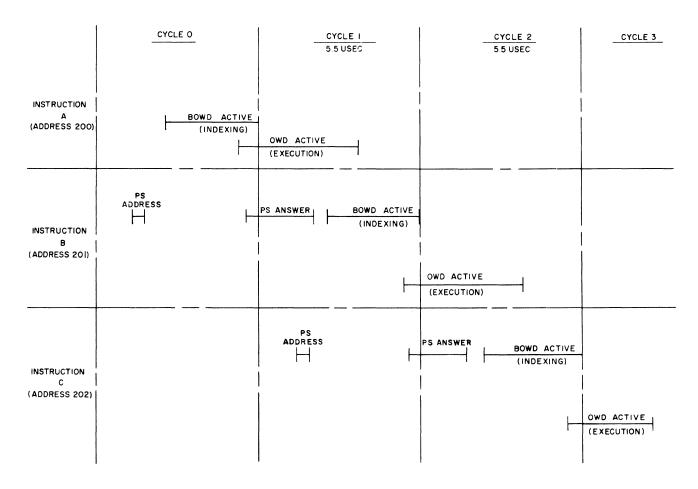

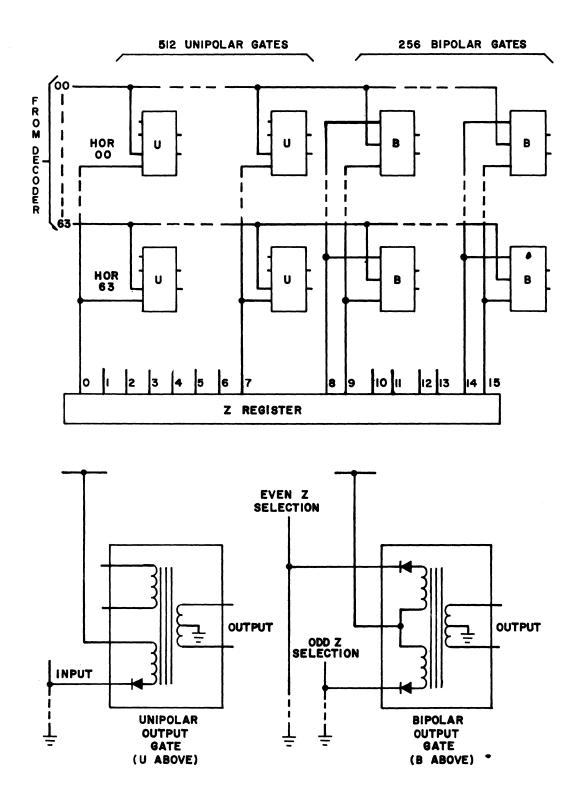

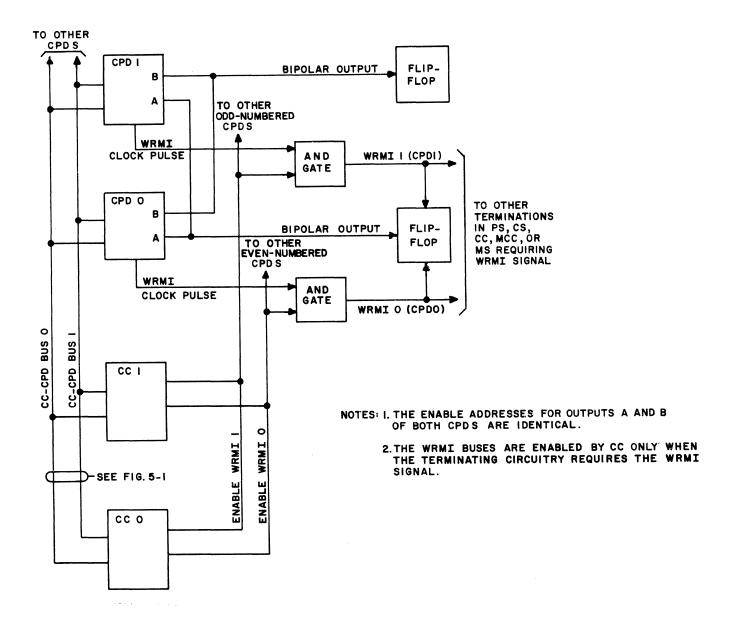

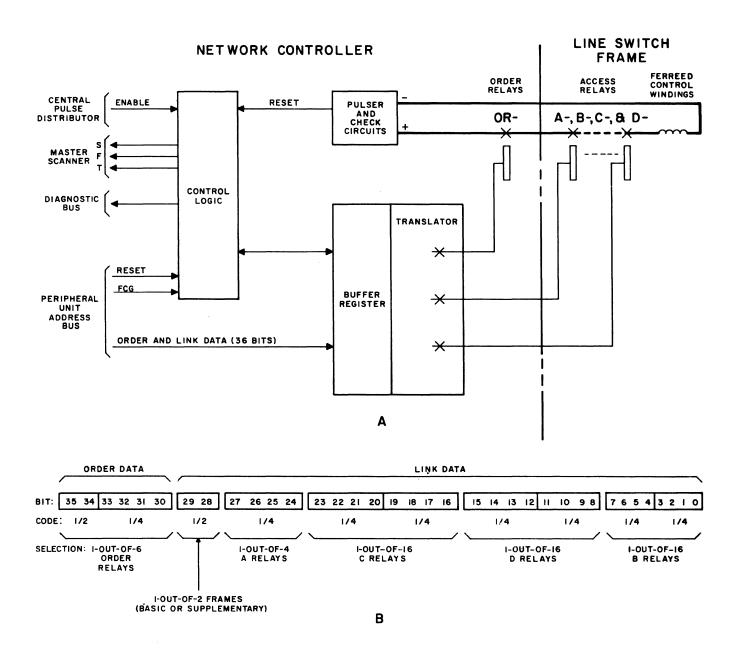

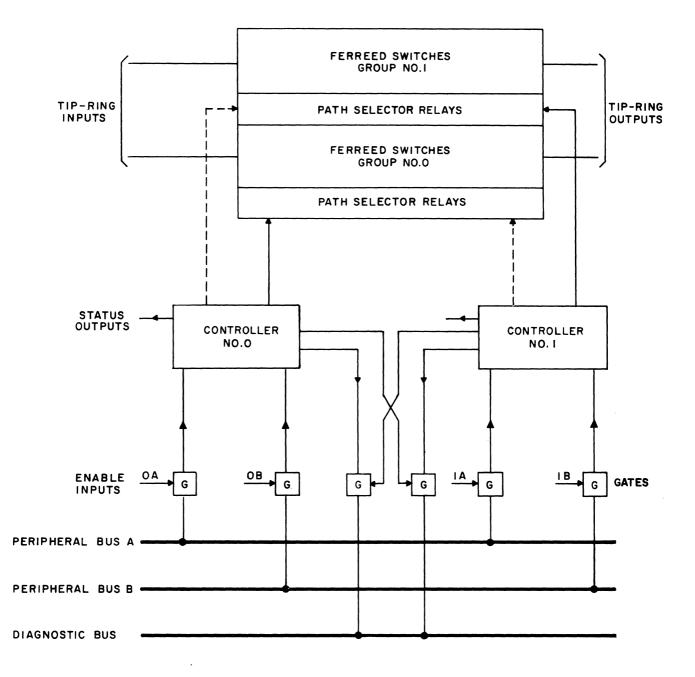

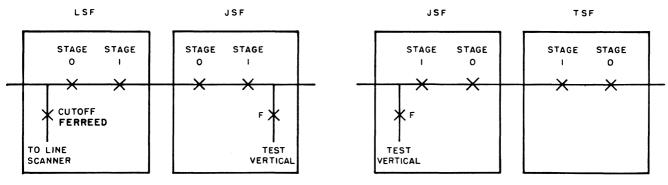

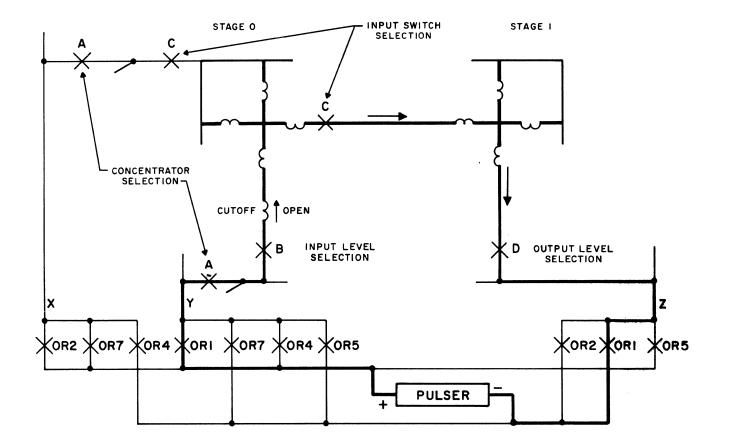

All index registers are 23 bits long. In terms of hardware, they become 24 bits long because there are two flip-flops on a single circuit package. In general, the extra flip-flop is not always usable for some disassociated function because a common gating input lead is used for