Am29030<sup>™</sup> and Am29035<sup>™</sup> Microprocessors User's Manual and Data Sheet Advanced Micro Devices

# Am29030<sup>™</sup> and Am29035<sup>™</sup> Microprocessors User's Manual and Data Sheet

ADVANCED MICRO DEVICES

© 1991 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warranties of merchantability or fitness for a particular application. AMD® assumes no responsibility for the use of any circuitry other than the circuitry embodied in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

AMD is a registered trademark of Advanced Micro Devices, Incorporated. Am29000, Am29005, Am29030, Am29035, Am29050, 29K, Laser29K, HighC29K, Scalable Clocking, and Branch Target Cache are trademarks of Advanced Micro Devices, Inc. PostScript is a registered trademark of Adobe Systems, Inc.

PostScript is a registered trademark of Adobe Systems, Inc.

XRAY29K is a registered trademark of Microtec Research, Inc.

Fusion29K is a registered servicemark of Advanced Micro Devices, Incorporated.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# **TABLE OF CONTENTS**

| Preface   | Introduction and Overview P-1                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

|           | The Am29030™ and Am29035™ RISC Microprocessors P-1                                                                                          |

|           | Design Philosophy                                                                                                                           |

|           | Optimum Performance                                                                                                                         |

|           | Performance Leverage P-2                                                                                                                    |

|           | Conclusion                                                                                                                                  |

|           | Purpose of this Manual P-3                                                                                                                  |

|           | Intended Audience                                                                                                                           |

|           | Am29030™ and Am29035™ Microprocessors User's Manual Overview P-3                                                                            |

|           | 29K™ Family Documentation                                                                                                                   |

|           | Related Publications                                                                                                                        |

|           |                                                                                                                                             |

| Chapter 1 | Features and Performance1-1                                                                                                                 |

|           | 1.1 Distinctive Characteristics 1-1                                                                                                         |

|           | 1.1.1 Am29030 Microprocessor                                                                                                                |

|           | 1.1.2 Am29035 Microprocessor 1-2                                                                                                            |

|           | 1.1.3 Feature Summary 1-2                                                                                                                   |

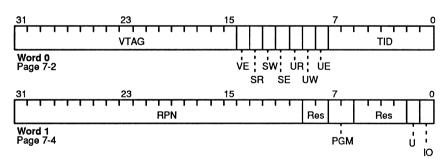

|           | 1.2 Key Features and Benefits       1-2         1.2.1 Large, On-Chip Instruction Cache       1-3                                            |

|           | 1.2.2 Scalable Clocking Technology                                                                                                          |

|           | 1.2.3 Narrow Read Interface 1-4                                                                                                             |

|           | 1.2.4 Programmable Bus Sizing 1-4                                                                                                           |

|           | 1.2.5 Streamlined System Interface 1-4                                                                                                      |

|           | 1.2.6         Pin-, Bus-, and Software-Compatibility         1-5           1.2.7         Wide Range of Price/Performance Points         1-5 |

|           | 1.2.8 Complete Development and Support Environment                                                                                          |

|           | 1.3 Performance Overview                                                                                                                    |

|           | 1.3.1 Instruction Timing 1-6                                                                                                                |

|           | 1.3.2 Pipelining                                                                                                                            |

|           | 1.3.3         Instruction Cache         1-7           1.3.4         Instruction Set Overview         1-7                                    |

|           | 1.3.5 Data Formats                                                                                                                          |

|           | 1.3.6 Protection                                                                                                                            |

|           | 1.3.7 Memory Management 1-8                                                                                                                 |

|           | 1.3.8 Interrupts and Traps 1-8                                                                                                              |

|           | 1.4 Debugging and Testing 1-8                                                                                                               |

| Chapter 2 | Programming                                                                                                                                 |

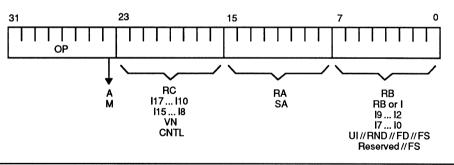

|           | 2.1 Instruction Set                                                                                                                         |

|           | 2.1.1 Integer Arithmetic 2-1                                                                                                                |

|           |                                                                                                                                             |

|              | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8<br>2.1.9<br>2.1.10 | Compare<br>Logical<br>Shift<br>Data Movement<br>Constant<br>Floating Point<br>Branch<br>Miscellaneous<br>Reserved Instructions                                                                                                                                                                                        | 2-4<br>2-4<br>2-5<br>2-5<br>2-7<br>2-8       |

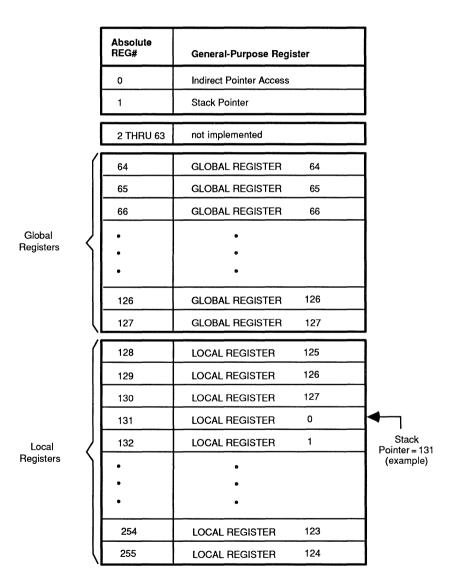

|--------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

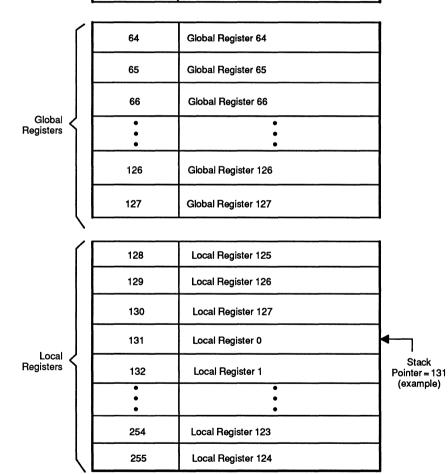

| 2.2          | 2 Registe<br>2.2.1<br>2.2.2                                                    | er Model<br>General-Purpose Registers<br>2.2.1.1 Register Addressing<br>2.2.1.2 Global Registers<br>2.2.1.3 Local Registers<br>2.2.1.4 Local-Register Stack Pointer<br>Special-Purpose Registers                                                                                                                      | 2-9<br>2-9<br>2-9<br>2-11<br>2-11            |

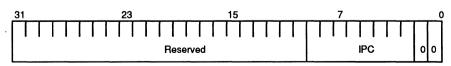

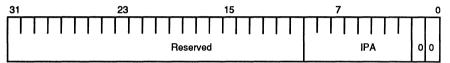

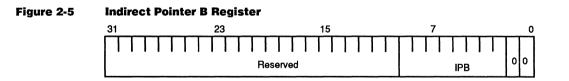

| 2.3          | Addres<br>2.3.1<br>2.3.2<br>2.3.3                                              | sing Registers Indirectly<br>Indirect Pointer C (IPC, Register 128)<br>Indirect Pointer A (IPA, Register 129)<br>Indirect Pointer B (IPB, Register 130)                                                                                                                                                               | 2-13<br>2-13<br>2-14                         |

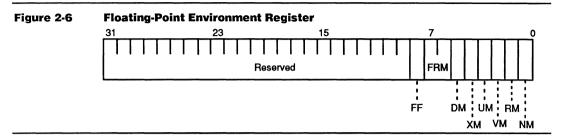

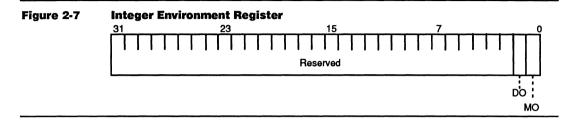

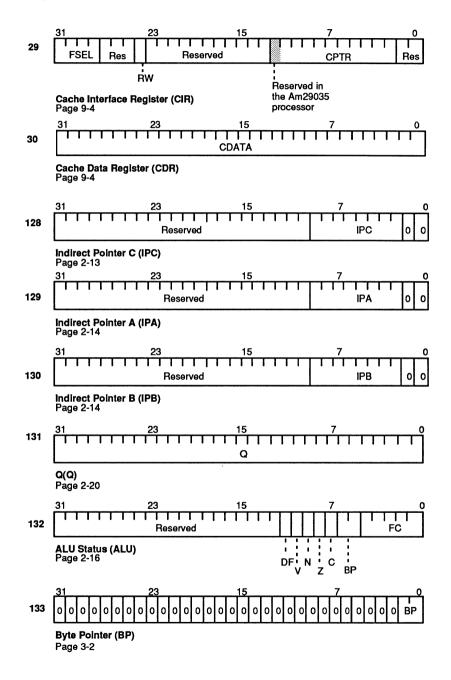

| 2.4          | Instruct<br>2.4.1<br>2.4.2                                                     | ion Environment<br>Floating-Point Environment (FPE, Register 160)<br>Integer Environment (INTE, Register 161)                                                                                                                                                                                                         | 2-15                                         |

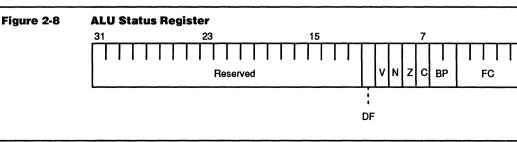

| 2.5          | 5 Status<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.4<br>2.5.5                          | Results of Instructions       ALU Status (ALU, Register 132)         Arithmetic Operation Status Results       Arithmetic Operation Status Results         Logical Operation Status (FPS, Register 162)       Floating-Point Status Results         Floating-Point Status Results       Floating-Point Status Results | 2-16<br>2-17<br>2-18<br>2-18                 |

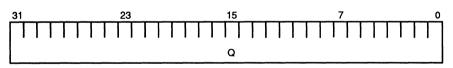

| 2.6          | integer<br>2.6.1<br>2.6.2<br>2.6.3                                             | Multiplication and Division         Q (Q, Register 131)         Multiplication         Division                                                                                                                                                                                                                       | 2-20<br>2-20                                 |

| 2.7          | I Need<br>2.7.1<br>2.7.2<br>2.7.3<br>2.7.4<br>2.7.5<br>2.7.6                   | an Instruction to<br>Run-Time Checking<br>Operating-System Calls<br>Multiprecision Integer Operations<br>Complementing a Boolean<br>Large Jump and Call Ranges<br>NO-OPs                                                                                                                                              | 2-24<br>2-25<br>2-25<br>2-25<br>2-25<br>2-26 |

| 2.8          | Virtual<br>2.8.1<br>2.8.2                                                      | Arithmetic Processor<br>Trapping Arithmetic Instructions<br>Virtual Registers                                                                                                                                                                                                                                         | 2-27                                         |

| 2.9          | Multipr                                                                        | ocessing                                                                                                                                                                                                                                                                                                              | 2-27                                         |

| Chapter 3 Da |                                                                                | its and Handling                                                                                                                                                                                                                                                                                                      |                                              |

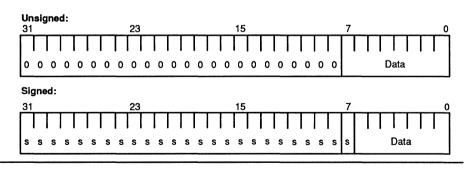

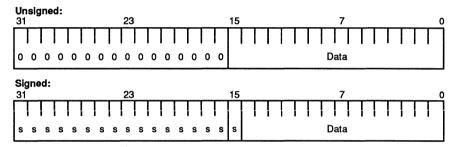

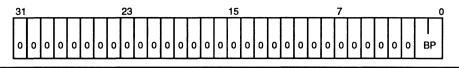

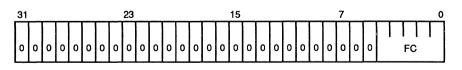

| 3.1          | Integer<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                    | Data Types         Character Data         Half-Word Operations         Byte Pointer (BP, Register 133)         Bit Strings         3.1.4.1 Funnel Shift Count (FC, Register 134)                                                                                                                                      | 3-1<br>3-2<br>3-2<br>3-3                     |

|           |                                                                                           | 3.1.5<br>3.1.6<br>3.1.7                                                                                                                                                           | Character-String Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-4<br>3-4                                                                                                                                      |

|-----------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

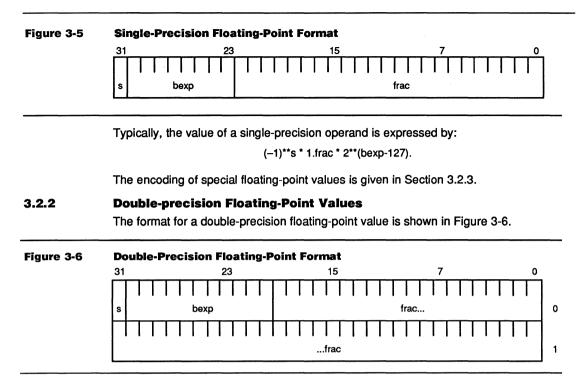

|           | 3.2                                                                                       | Floating<br>3.2.1<br>3.2.2<br>3.2.3                                                                                                                                               | g-Point Data Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-5<br>3-5<br>3-6<br>3-6<br>3-6<br>3-6<br>3-7<br>3-7                                                                                            |

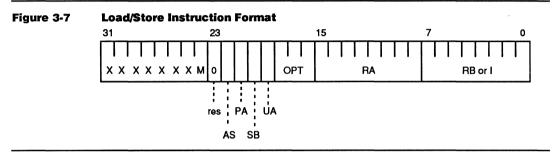

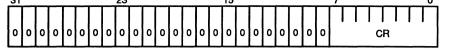

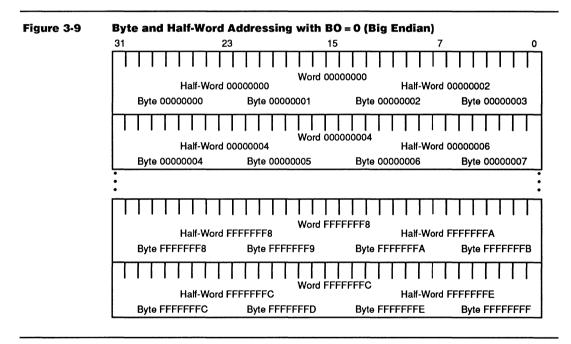

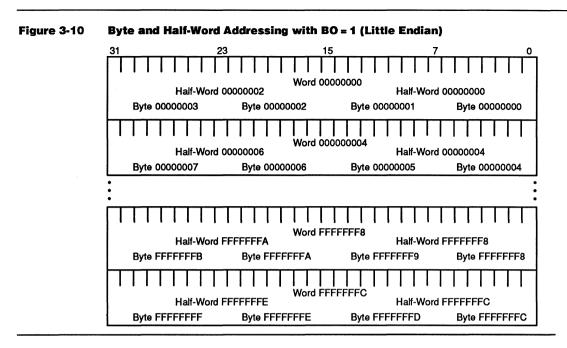

|           | 3.3                                                                                       | Externa<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.6<br>3.3.7                                                                                                   | Address Spaces       3         Address Spaces       3         Load/Store Instruction Format       3         Load Operations       3         Store Operations       3         Multiple Accesses       3         3.3.5.1 Load/Store Count Remaining (CR, Register 135)       3         3.3.5.2 Movement of Large Data Blocks       3         Option Bits       3         3.3.7.1 Byte and Half-Word Addressing       3         3.3.7.2 Byte and Half-Word Accesses       3         3.3.7.3 Alignment of Words and Half-Words       3         3.3.7.4 Alignment of Instructions       3                                                                                                                                                           | 3-7<br>3-8<br>3-9<br>-10<br>-11<br>-12<br>-13<br>-13<br>-13<br>-14<br>-15                                                                       |

|           |                                                                                           |                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                 |

| Chapter 4 | Pro                                                                                       |                                                                                                                                                                                   | Linkage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

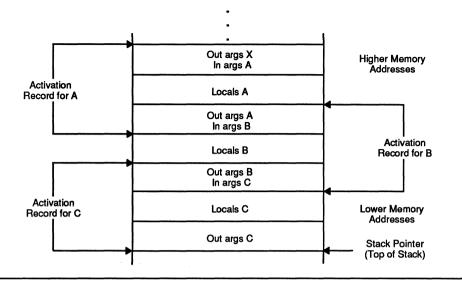

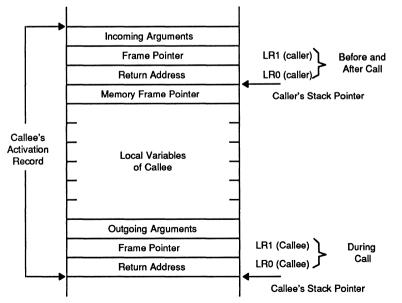

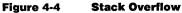

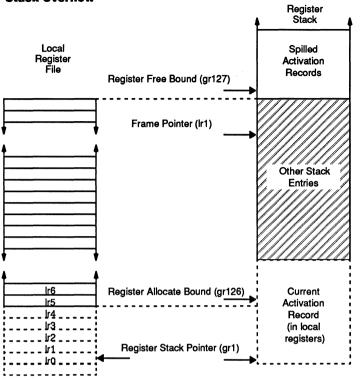

| Chapter 4 | 4.1                                                                                       | Run-Tir<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                                                                                                                       | ne Stack Organization and Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-1<br>4-1<br>4-3<br>4-4<br>4-5                                                                                                                 |

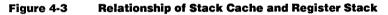

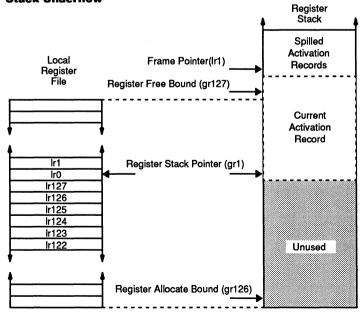

| Chapter 4 | 4.1                                                                                       | Run-Tir<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Procedu<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10                                 | ne Stack Organization and Use       2         Management of the Run-time Stack       2         The Register Stack       2         Local Registers as a Stack Cache       2         The Memory Stack       2         ure Linkage Conventions       2         Argument Passing       2         Procedure Prologue       2         Spill Handler       4         Return Values       4         Procedure Epilogue       4         Fill Handlers       4         The Register Stack Leaf Frame       4         Local Variables and Memory-Stack Frames       4         Static Link Pointer       4         Transparent Procedures       4                                                                                                          | 4-1<br>4-3<br>4-4<br>4-5<br>4-7<br>4-8<br>4-7<br>4-8<br>-10<br>-11<br>-11<br>-11<br>-12<br>-13<br>-13                                           |

| Chapter 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                             | Run-Tir<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Procedu<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>Register                     | ne Stack Organization and Use       4         Management of the Run-time Stack       4         The Register Stack       4         Local Registers as a Stack Cache       4         The Memory Stack       4         ure Linkage Conventions       4         Argument Passing       4         Procedure Prologue       4         Spill Handler       4         Return Values       4         Procedure Epilogue       4         Fill Handlers       4         The Register Stack Leaf Frame       4         Local Variables and Memory-Stack Frames       4         Static Link Pointer       4         Transparent Procedures       4         Arguster Convention       4                                                                      | 4-1<br>4-3<br>4-4<br>4-5<br>4-7<br>4-8<br>4-7<br>4-8<br>-10<br>-10<br>-11<br>-12<br>-13<br>-13<br>-13                                           |

| Chapter 4 | 4.1<br>4.2<br>4.3<br>4.4                                                                  | Run-Tir<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Procedd<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>Registe<br>Example           | ne Stack Organization and Use       2         Management of the Run-time Stack       2         The Register Stack       2         Local Registers as a Stack Cache       2         The Memory Stack       2         ure Linkage Conventions       2         Argument Passing       2         Procedure Prologue       2         Spill Handler       4         Return Values       4         Procedure Epilogue       4         Fill Handlers       4         The Register Stack Leaf Frame       4         Local Variables and Memory-Stack Frames       4         Static Link Pointer       4         Transparent Procedures       4                                                                                                          | 4-1<br>4-3<br>4-4<br>4-5<br>4-7<br>4-8<br>4-7<br>4-8<br>4-7<br>4-8<br>4-7<br>4-8<br>-10<br>-10<br>-11<br>-11<br>-12<br>-13<br>-13<br>-13<br>-14 |

| Chapter 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>               | Run-Tir<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Procedd<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>Registe<br>Exampl<br>Trace-E | me Stack Organization and Use       4         Management of the Run-time Stack       4         The Register Stack       4         Local Registers as a Stack Cache       4         The Memory Stack       4         ure Linkage Conventions       4         Argument Passing       4         Procedure Prologue       4         Spill Handler       4         Return Values       4         Fill Handlers       4         The Register Stack Leaf Frame       4         Local Variables and Memory-Stack Frames       4         Static Link Pointer       4         Transparent Procedures       4         e of a Complex Procedure Call       4                                                                                               | 4-1<br>4-3<br>4-4<br>4-5<br>-10<br>-11<br>-11<br>-12<br>-13<br>-13<br>-14<br>-15                                                                |

|           | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>               | Run-Tir<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Proceed<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>Registe<br>Exampl<br>Trace-E | me Stack Organization and Use       4         Management of the Run-time Stack       4         The Register Stack       4         Local Registers as a Stack Cache       4         The Memory Stack       4         ure Linkage Conventions       4         Argument Passing       4         Procedure Prologue       4         Spill Handler       4         Return Values       4         Fill Handlers       4         Fill Handlers       4         The Register Stack Leaf Frame       4         Local Variables and Memory-Stack Frames       4         Static Link Pointer       4         Transparent Procedures       4         ar Usage Convention       4         Be of a Complex Procedure Call       4                            | 4-1<br>4-3<br>4-4<br>4-5<br>4-7<br>4-8<br>4-7<br>4-8<br>4-7<br>-10<br>-10<br>-11<br>-12<br>-13<br>-13<br>-13<br>-14<br>-15<br>-15<br>-1         |

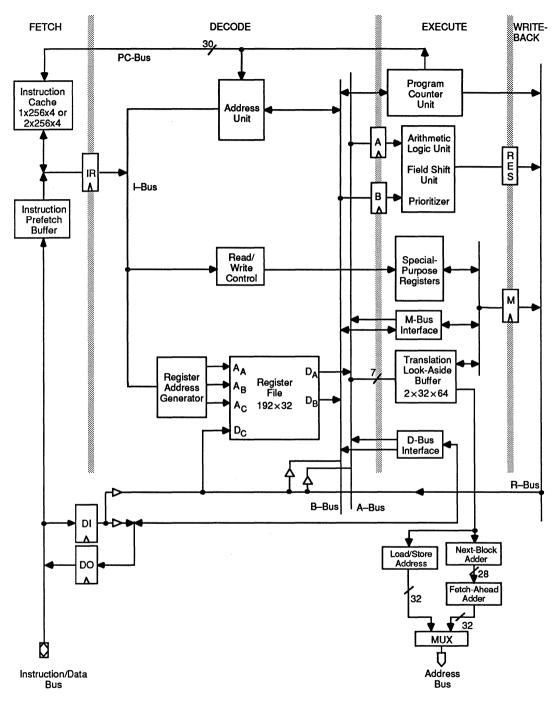

|           | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>Pipe</li> </ul> | Run-Tir<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Procedu<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>Registe<br>Exampl<br>Trace-E | me Stack Organization and Use       4         Management of the Run-time Stack       4         The Register Stack       4         Local Registers as a Stack Cache       4         The Memory Stack       4         ure Linkage Conventions       4         Argument Passing       4         Procedure Prologue       4         Spill Handler       4         Return Values       4         Procedure Epilogue       4         Fill Handlers       4         The Register Stack Leaf Frame       4         Local Variables and Memory-Stack Frames       4         Static Link Pointer       4         Transparent Procedures       4         er Usage Convention       4         Back Tags       4         and Instruction Scheduling       4 | 4-1<br>4-3<br>4-4<br>4-5<br>4-7<br>4-8<br>4-7<br>4-8<br>4-7<br>4-8<br>4-7<br>-10<br>-11<br>-12<br>-13<br>-13<br>-14<br>-15<br>5-1               |

|           | 5.4 Delayed Branch 5-4                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 5.5 Overlapped Loads and Stores 5-5                                                                                                                                                                                                                                                                                                                                                          |

|           | 5.6 Delayed Effects of Registers 5-6                                                                                                                                                                                                                                                                                                                                                         |

| Chapter 6 | System Protection                                                                                                                                                                                                                                                                                                                                                                            |

|           | 6.1 User and Supervisor Modes         6-1           6.1.1 Supervisor Mode         6-1           6.1.2 User Mode         6-1                                                                                                                                                                                                                                                                  |

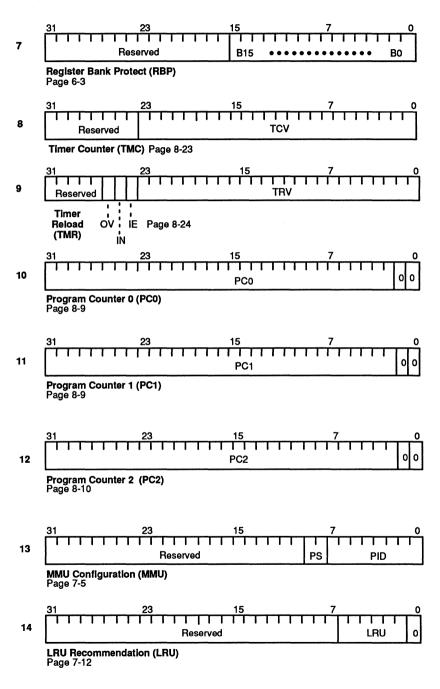

|           | 6.2 Register Protection       6-2         6.2.1 Register Bank Protect (RBP, Register 7)       6-3                                                                                                                                                                                                                                                                                            |

|           | 6.3 Memory Protection                                                                                                                                                                                                                                                                                                                                                                        |

|           | 6.4 External Access Protection                                                                                                                                                                                                                                                                                                                                                               |

| Chapter 7 | Memory Management                                                                                                                                                                                                                                                                                                                                                                            |

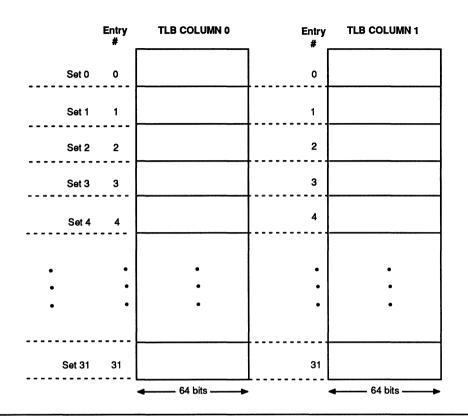

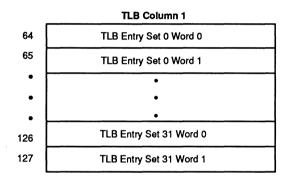

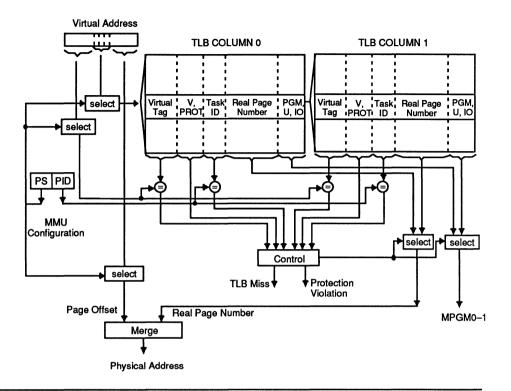

|           | 7.1 Translation Look-Aside Buffer 7-1                                                                                                                                                                                                                                                                                                                                                        |

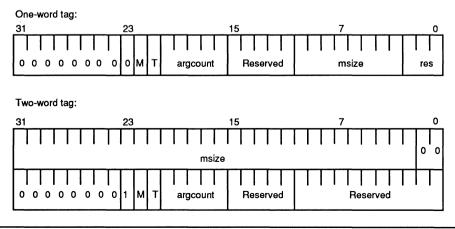

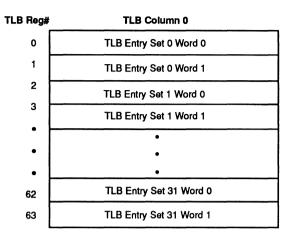

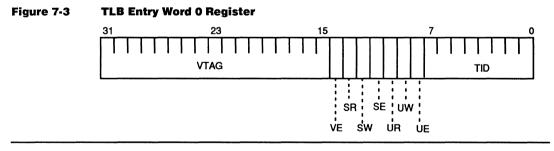

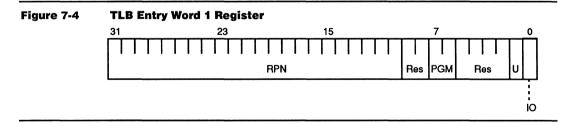

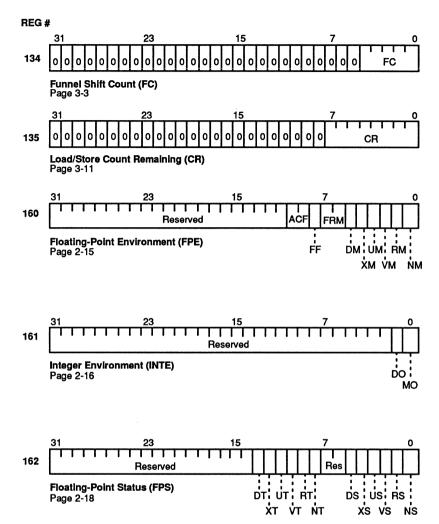

|           | 7.2         TLB Registers         7-1           7.2.1         TLB Entry Word 0         7-2           7.2.2         TLB Entry Word 1         7-4                                                                                                                                                                                                                                              |

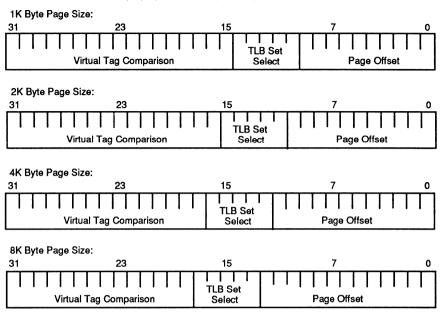

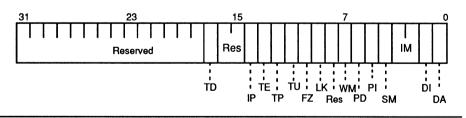

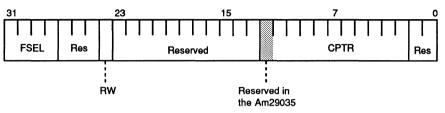

| ,         | 7.3 Address Translation Controls       7-5         7.3.1 Enabling and Disabling Address Translation       7-5         7.3.2 MMU Configuration Register (MMU, Register 13)       7-5                                                                                                                                                                                                          |

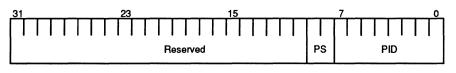

|           | 7.4       Address Translation Description       7-6         7.4.1       Virtual Address Structure       7-6         7.4.2       Address-Translation Process       7-6         7.4.3       Successful and Unsuccessful Translations       7-9         7.4.4       Instruction Cache Considerations       7-9         7.4.5       Selecting the Virtual Page Size       7-10                   |

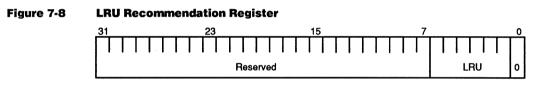

|           | 7.5       Handling TLB Misses       7-11         7.5.1       TLB Reload       7-11         7.5.2       LRU Recommendation (LRU, Register 14)       7-12         7.5.3       Page Reference and Change Information       7-12         7.5.4       Warm Start       7-13         7.5.5       Minimum Number of Resident Pages       7-13                                                       |

|           | 7.6 Invalidating TLB Entries                                                                                                                                                                                                                                                                                                                                                                 |

| Chapter 8 | Interrupts and Traps8-1                                                                                                                                                                                                                                                                                                                                                                      |

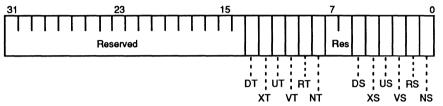

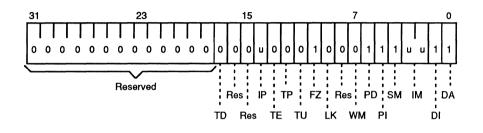

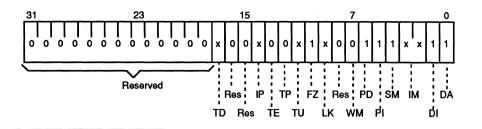

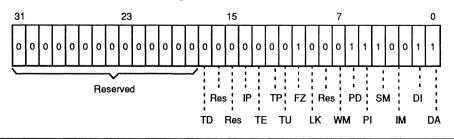

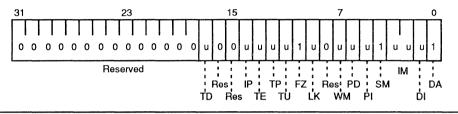

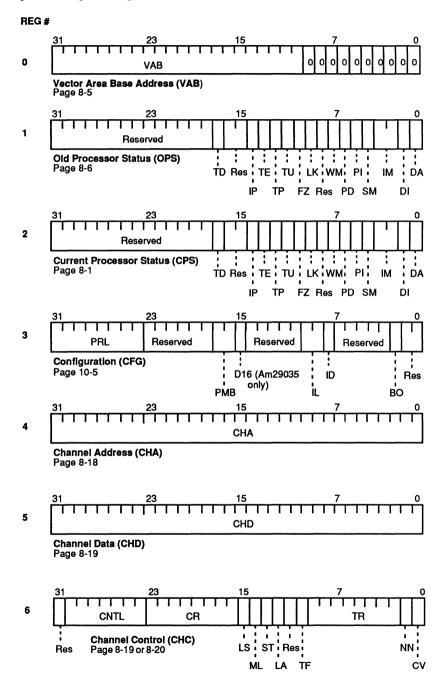

|           | 8.1         Overview         8-1           8.1.1         Current Processor Status (CPS, Register 2)         8-1           8.1.2         Interrupts         8-2           8.1.3         Traps         8-4           8.1.4         External Interrupts and Traps         8-4           8.1.5         Wait Mode         8-4                                                                     |

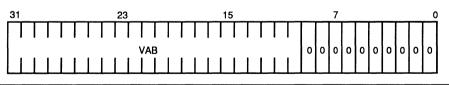

|           | 8.2         Vector Area         8-5           8.2.1         Vector Area Base Address (VAB, Register 0)         8-5           8.2.2         Vector Numbers         8-6                                                                                                                                                                                                                        |

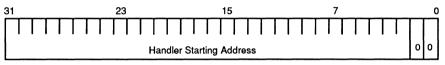

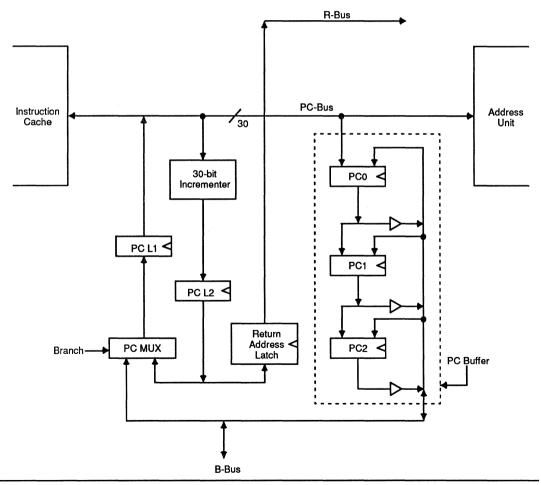

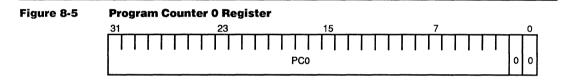

|           | 8.3       Interrupt and Trap Handling       8-6         8.3.1       Old Processor Status (OPS, Register 1)       8-6         8.3.2       The Program Counter Stack       8-6         8.3.2.1       Program Counter O (PC0, Register 10)       8-6         8.3.2.2       Program Counter 1 (PC1, Register 11)       8-6         8.3.2.3       Program Counter 2 (PC2, Register 12)       8-10 |

|            |      | 8.3.3<br>8.3.4<br>8.3.5<br>8.3.6                              | Taking an Interrupt or Trap         Returning from an Interrupt or Trap         Lightweight Interrupt Processing         Simulation of Interrupts and Traps                                                                                                                  | 8-11<br>8-13                                       |

|------------|------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|            | 8.4  | WARN<br>8.4.1                                                 | Trap WARN Input                                                                                                                                                                                                                                                              |                                                    |

|            | 8.5  | Sequer                                                        | ncing of Interrupts and Traps                                                                                                                                                                                                                                                | 8-15                                               |

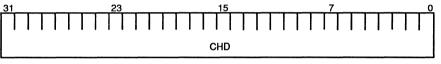

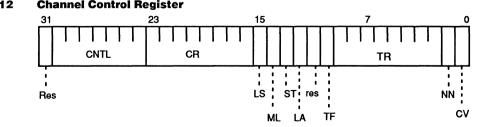

|            | 8.6  | Except<br>8.6.1<br>8.6.2                                      | ion Reporting and Restarting<br>Instruction Exceptions<br>Restarting Faulting External Accesses<br>8.6.2.1 Channel Address (CHA, Register 4)<br>8.6.2.2 Channel Data (CHD, Register 5)<br>8.6.2.3 Channel Control (CHC, Register 6)                                          | 8-17<br>8-17<br>8-18<br>8-19                       |

|            |      | 8.6.3<br>8.6.4<br>8.6.5<br>8.6.6                              | Integer Exceptions                                                                                                                                                                                                                                                           | 8-20<br>8-21<br>8-21                               |

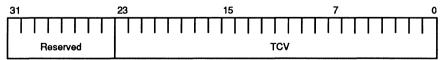

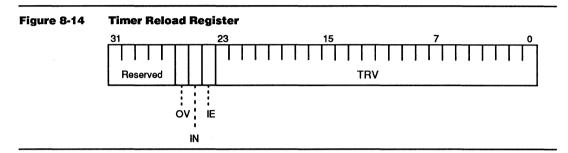

|            | 8.7  | Timer F<br>8.7.1<br>8.7.2<br>8.7.3<br>8.7.4<br>8.7.5<br>8.7.6 | Facility         Timer Facility Operation         Timer Facility Initialization         Handling Timer Interrupts         Timer Facility Uses         Timer Counter (TMC, Register 8)         Timer Reload (TMR, Register 9)                                                 | 8-22<br>8-22<br>8-23<br>8-23<br>8-23               |

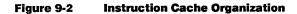

| Chapter 9  | Inst | ruction                                                       | Cache Operation                                                                                                                                                                                                                                                              | . 9-1                                              |

|            | 9.1  | Instruct                                                      | ion Cache Overview                                                                                                                                                                                                                                                           | . 9-1                                              |

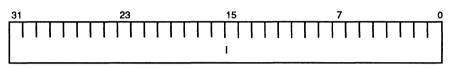

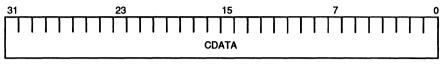

|            | 9.2  | Access<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4                    | ing Cache Fields<br>Instruction Words<br>Address Tag and Status Information<br>Cache Interface Register (CIR, Register 29)<br>Cache Data Register (CDR, Register 30)                                                                                                         | .9-3<br>.9-3<br>.9-4                               |

|            | 9.3  | Cache                                                         | Hits and Misses                                                                                                                                                                                                                                                              | . 9-5                                              |

|            |      | 9.4.1<br>9.4.2<br>9.4.3<br>9.4.4                              | al Fetching and Cache Reload<br>Cache Replacement<br>Overview of External Instruction Fetching<br>The Instruction Fetch Pointer<br>Cache Misses During Sequential Instruction Fetching                                                                                       | . 9-6<br>. 9-6<br>. 9-7<br>. 9-7                   |

|            |      | 9.5.1<br>9.5.2<br>9.5.3<br>9.5.4<br>9.5.5                     | ion Prefetching<br>Operation During Prefetching<br>The Role of the Prefetch Buffer<br>Terminating Instruction Prefetching Because of a Cache Hit<br>Terminating Instruction Prefetching Because of a Branch<br>Collisions Between Instruction Fetching and Loads or Stores . | . 9-7<br>. 9-8<br>. 9-8<br>. 9-8<br>. 9-8<br>. 9-9 |

|            | 9.6  | Cacne                                                         |                                                                                                                                                                                                                                                                              | . 9-9                                              |

| Chapter 10 | Sys  | tem Inte                                                      | erface                                                                                                                                                                                                                                                                       | 10-1                                               |

|            | 10.1 | -                                                             | Description                                                                                                                                                                                                                                                                  |                                                    |

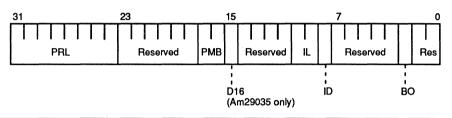

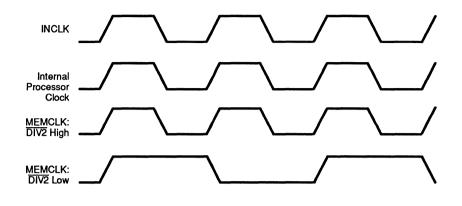

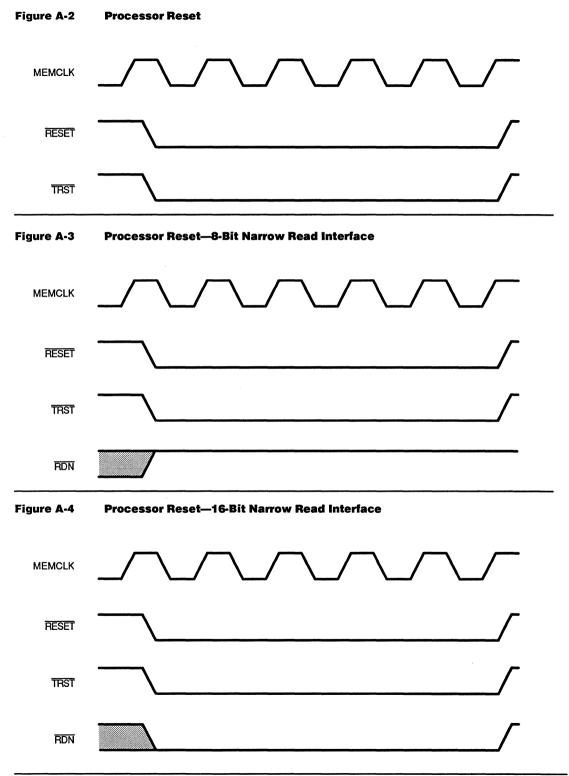

|            | 10.2 | 10.2.1<br>10.2.2                                              | sor Reset and Initialization<br>Configuration (CFG, Register 3)<br>Reset Mode<br>Am29035 Processor Initialization Considerations                                                                                                                                             | 10-5<br>10-7                                       |

|            | 10.3 |                                                               |                                                                                                                                                                                                                                                                              | 10-8<br>10-8                                       |

|            |      |                                                               |                                                                                                                                                                                                                                                                              |                                                    |

|            |                                                               | 10.3.1                                                                                                                                    | Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                             | 10-9                                                                                                                                                                 |

|------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 10.4                                                          | Bus Dese                                                                                                                                  | cription                                                                                                                                                                                                                                                                                                                                                                                                                              | 10-9                                                                                                                                                                 |

|            |                                                               | 10.4.1                                                                                                                                    | Bus Overview                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                      |

|            |                                                               | 10.4.2                                                                                                                                    | User-Defined Signals                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

|            |                                                               | 10.4.3                                                                                                                                    | Instruction Accesses                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

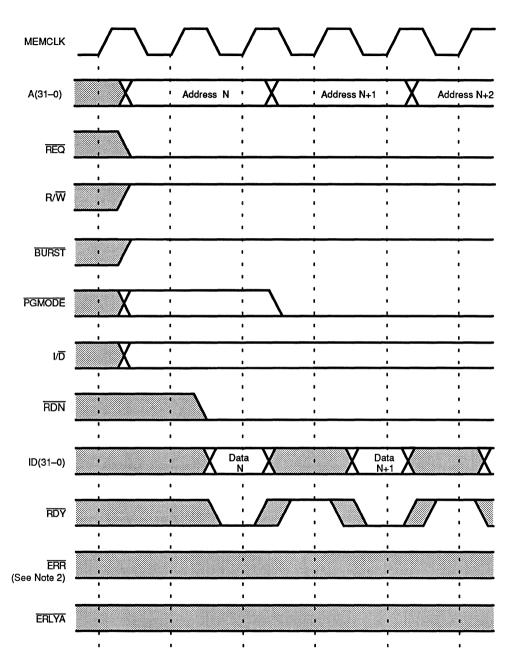

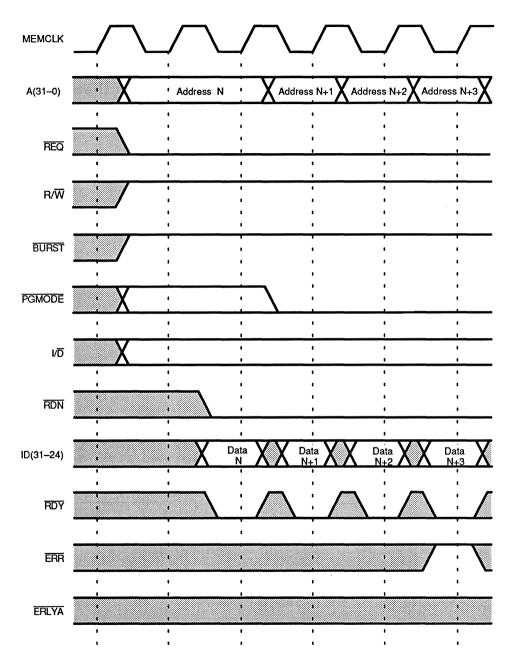

|            |                                                               | 10.4.4<br>10.4.5                                                                                                                          | Read-Only Memories                                                                                                                                                                                                                                                                                                                                                                                                                    | 10-10<br>10-11                                                                                                                                                       |

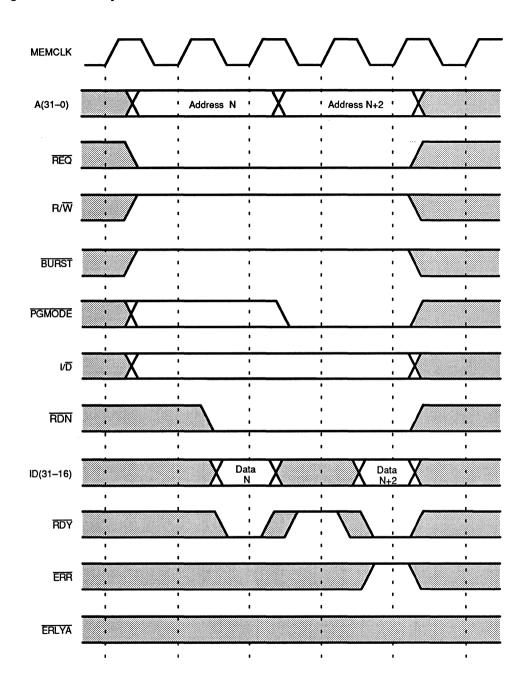

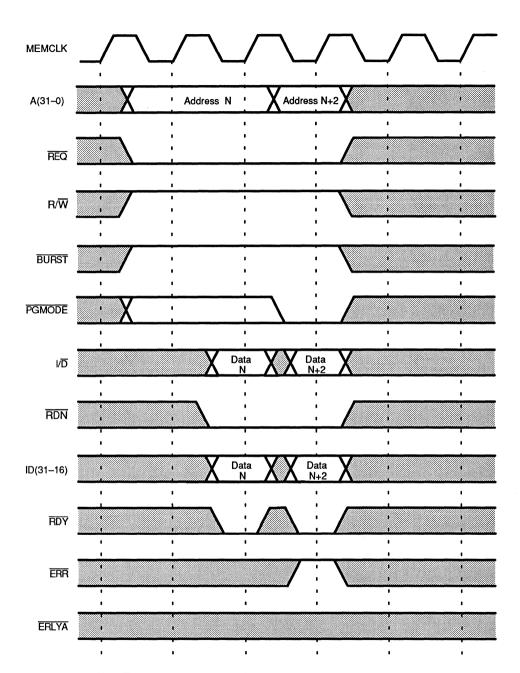

|            |                                                               | 10.4.5                                                                                                                                    | 10.4.5.1 Narrow Read Interface                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

|            |                                                               |                                                                                                                                           | 10.4.5.2 8-Bit Narrow Accesses                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

|            |                                                               |                                                                                                                                           | 10.4.5.3 16-Bit Narrow Accesses                                                                                                                                                                                                                                                                                                                                                                                                       | 10-12                                                                                                                                                                |

|            |                                                               |                                                                                                                                           | 10.4.5.4 ROM Address Mapping                                                                                                                                                                                                                                                                                                                                                                                                          | 10-13                                                                                                                                                                |

|            |                                                               | 10.4.6                                                                                                                                    | Programmable Bus Sizing (Am29035 Processor Only)                                                                                                                                                                                                                                                                                                                                                                                      | 10-13                                                                                                                                                                |

|            |                                                               | 10.4.7                                                                                                                                    | Reporting Errors                                                                                                                                                                                                                                                                                                                                                                                                                      | 10-14                                                                                                                                                                |

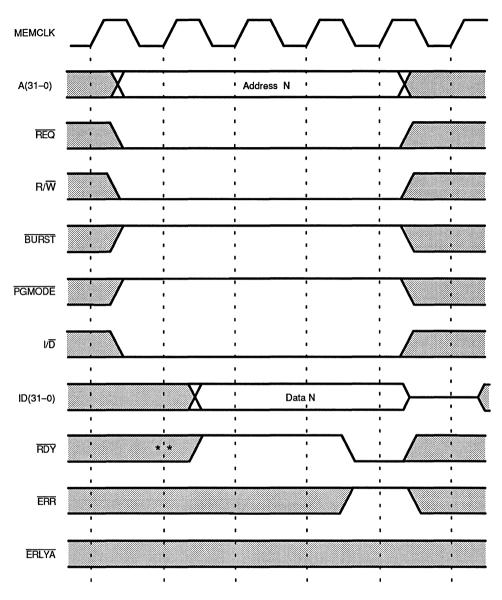

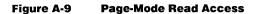

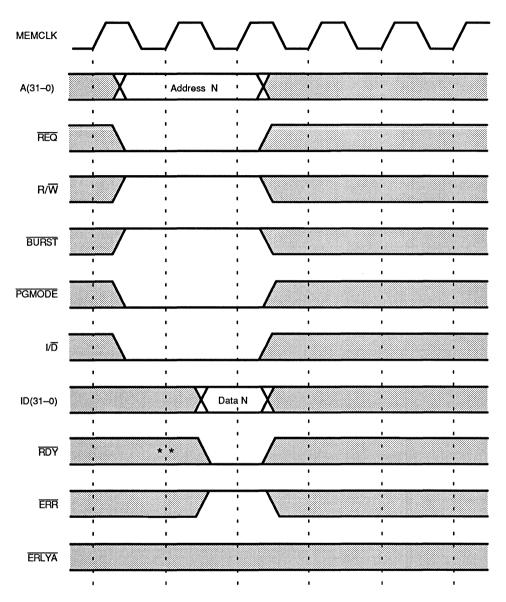

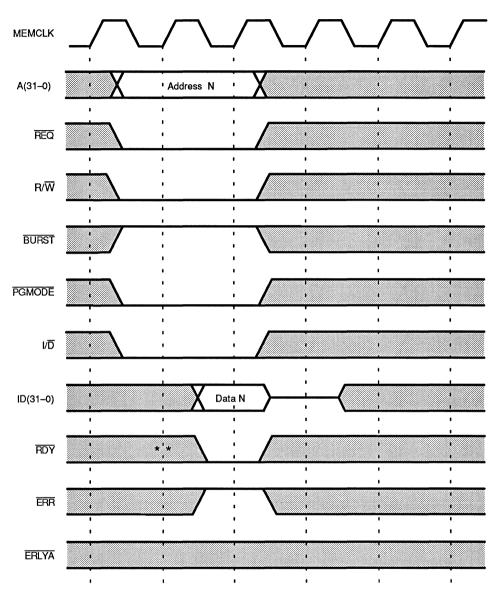

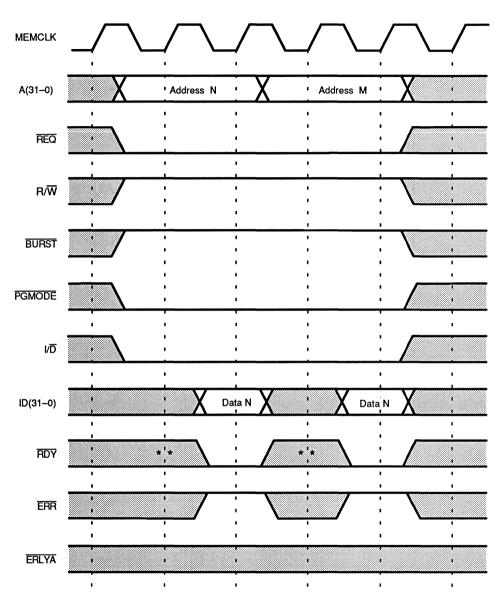

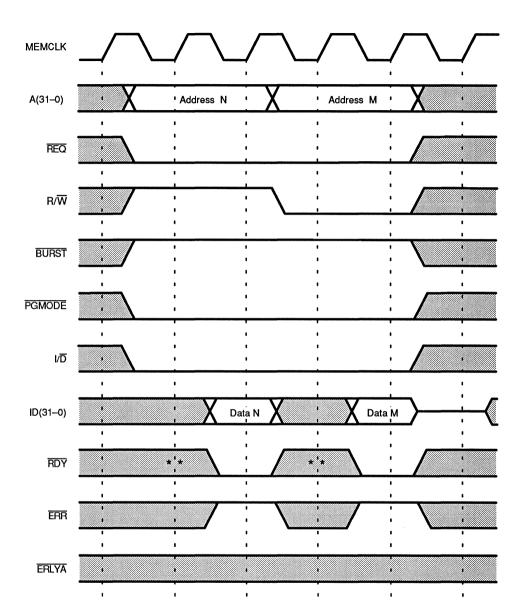

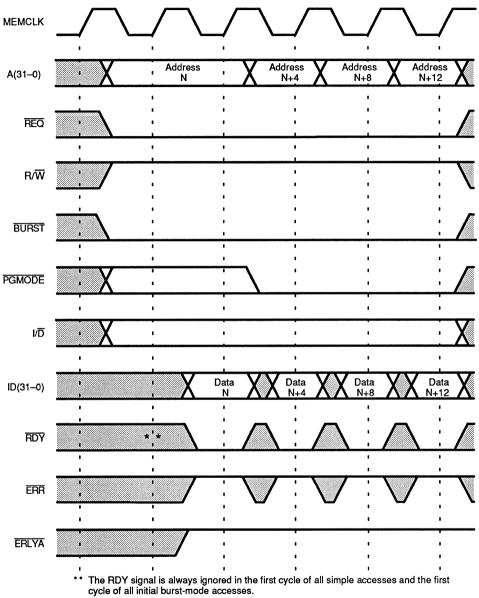

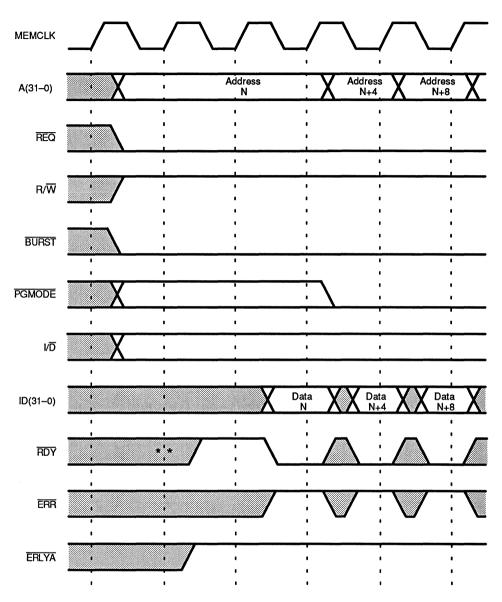

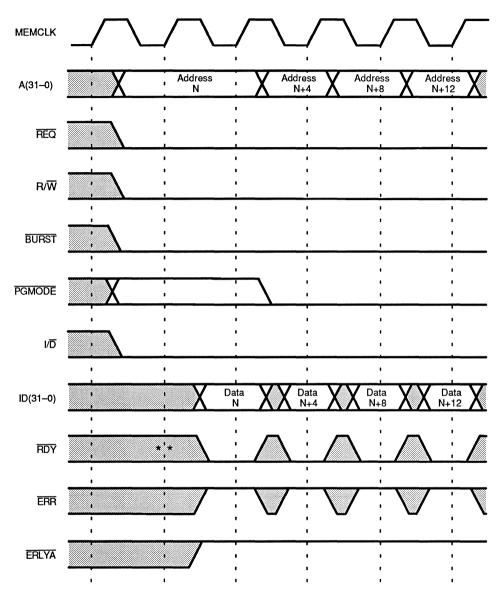

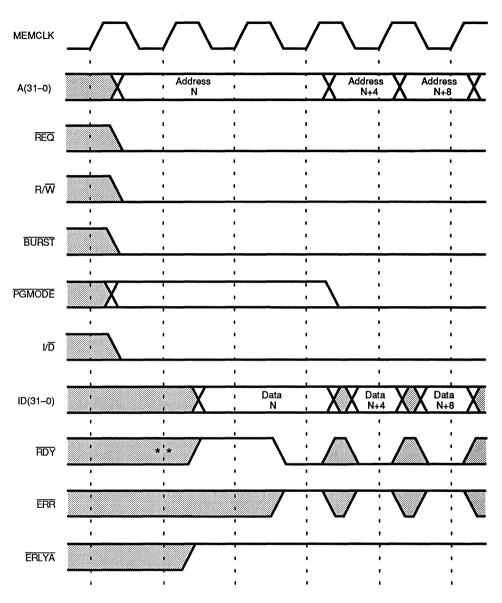

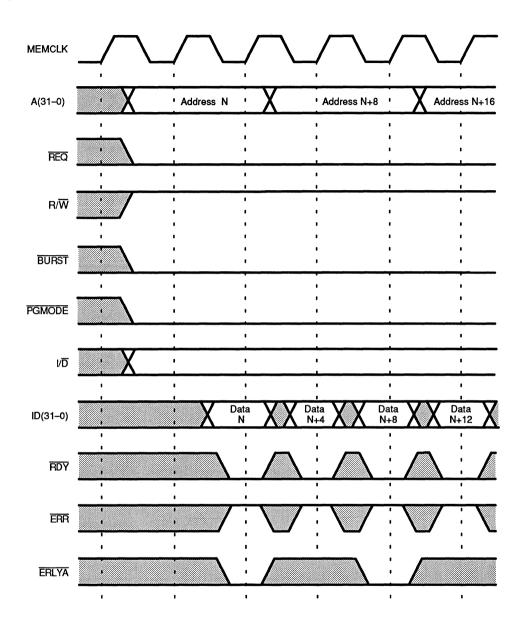

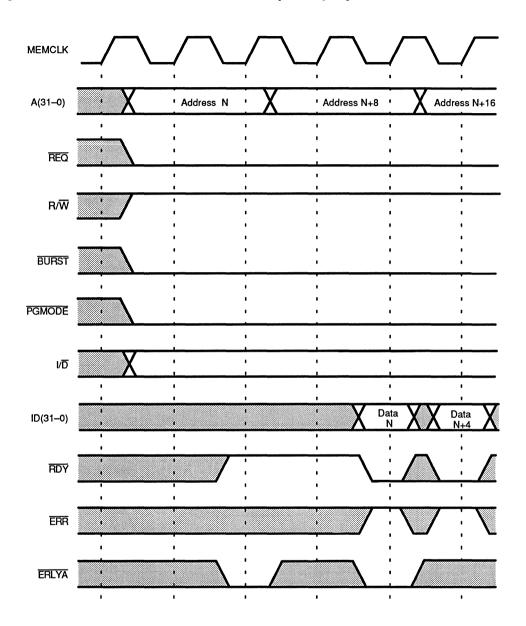

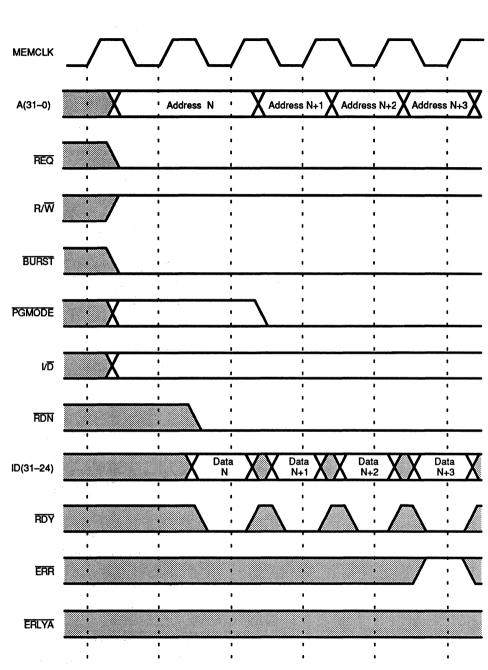

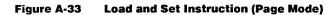

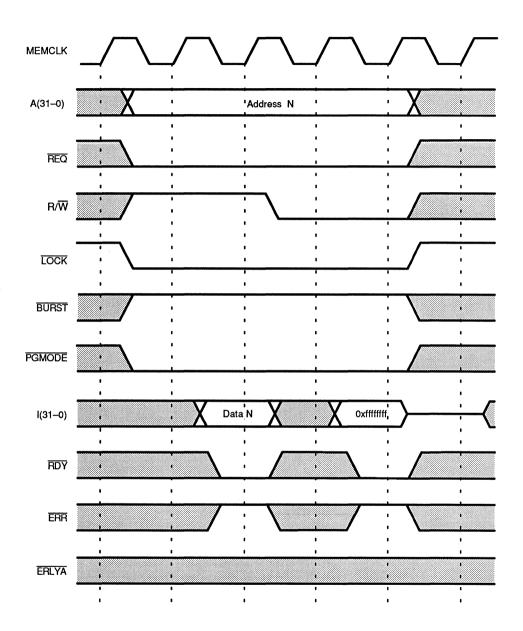

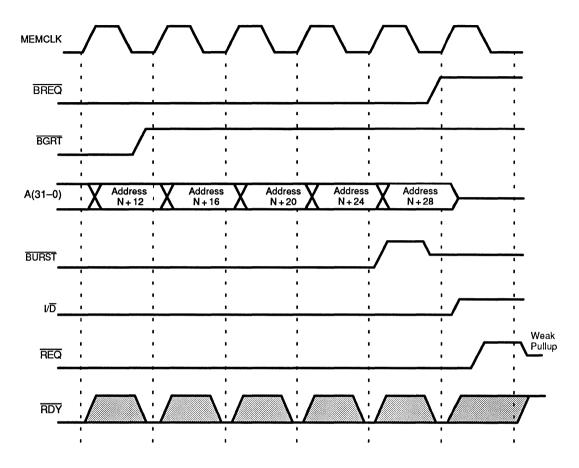

|            |                                                               | 10.4.8                                                                                                                                    | Access Protocols                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                      |

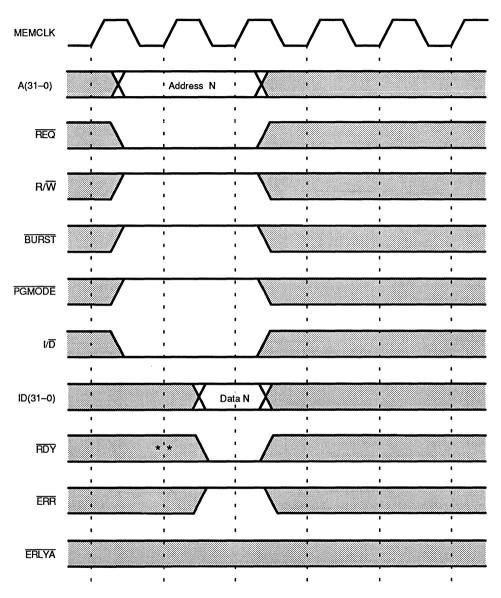

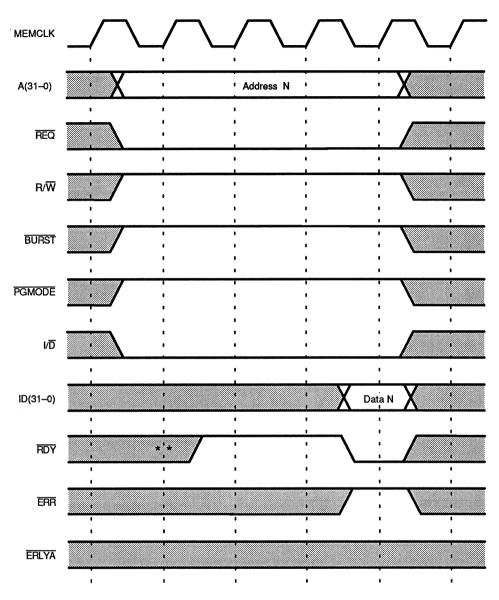

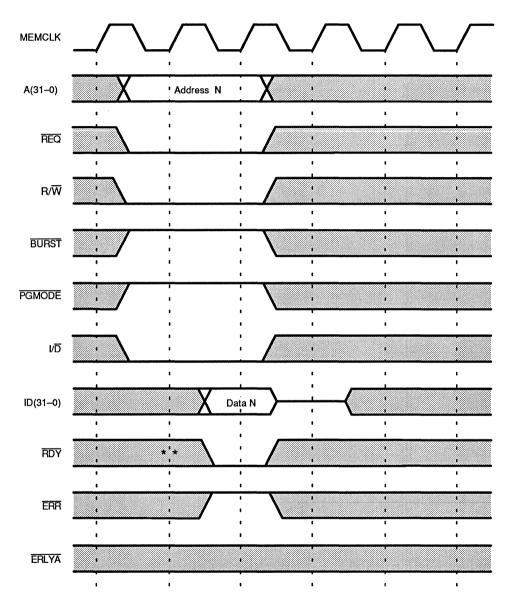

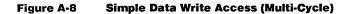

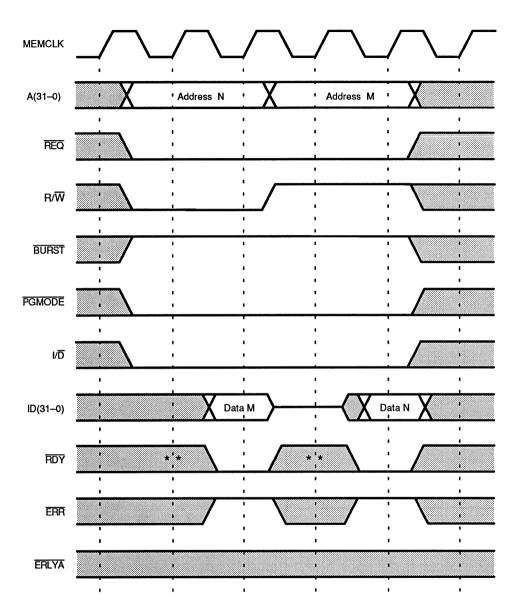

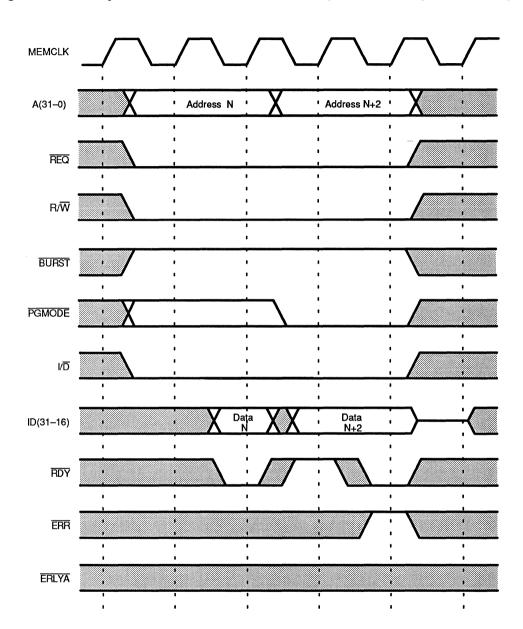

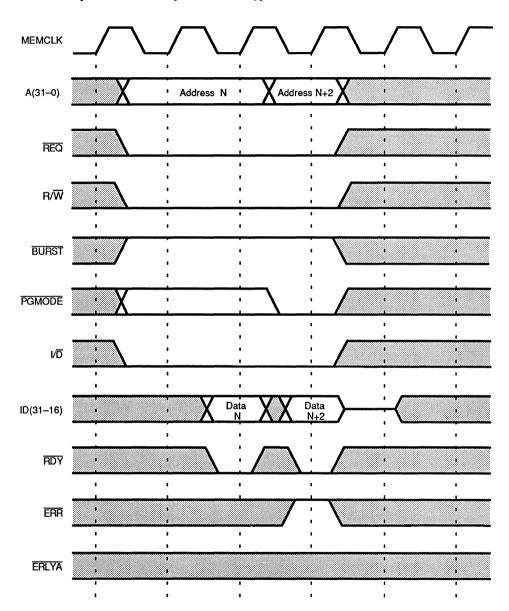

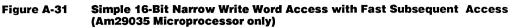

|            |                                                               | 10.4.9                                                                                                                                    | 10.4.8.1         Page-Mode Accesses           Simple Accesses                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                      |

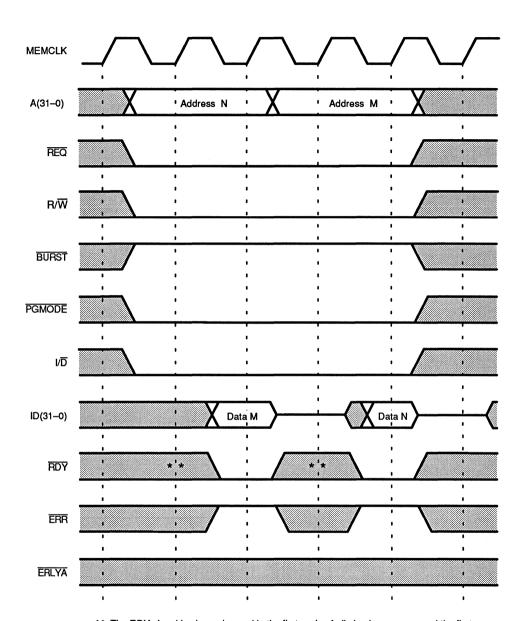

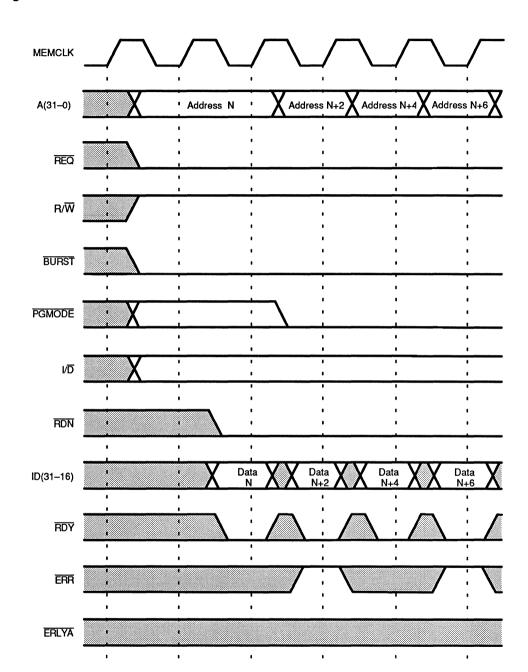

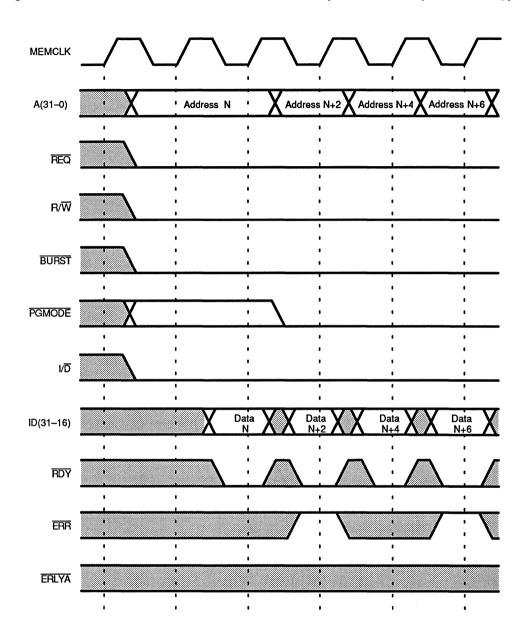

|            |                                                               | 10.4.9                                                                                                                                    | Burst-Mode Accesses                                                                                                                                                                                                                                                                                                                                                                                                                   | 10-15                                                                                                                                                                |

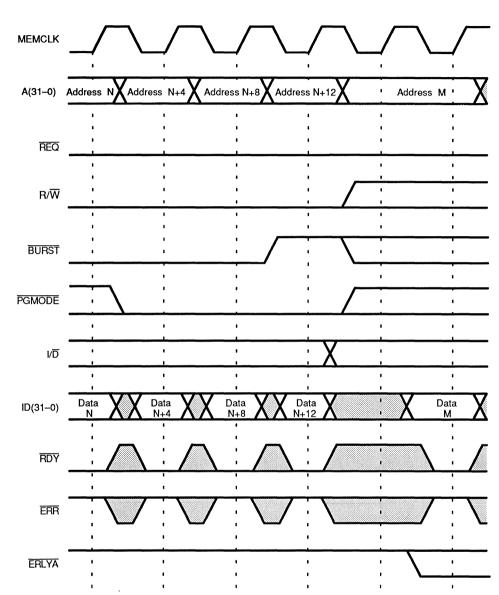

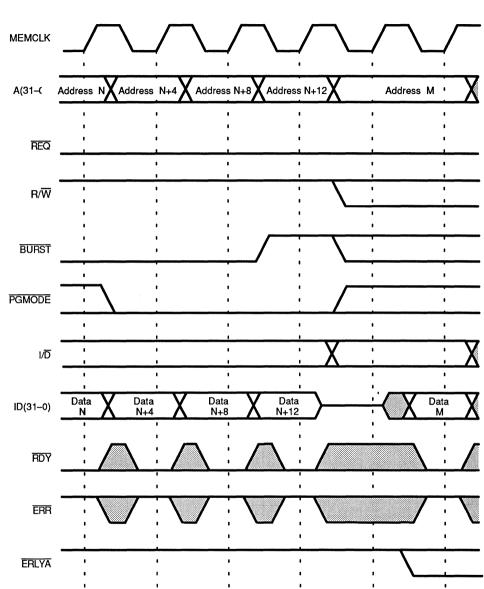

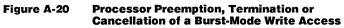

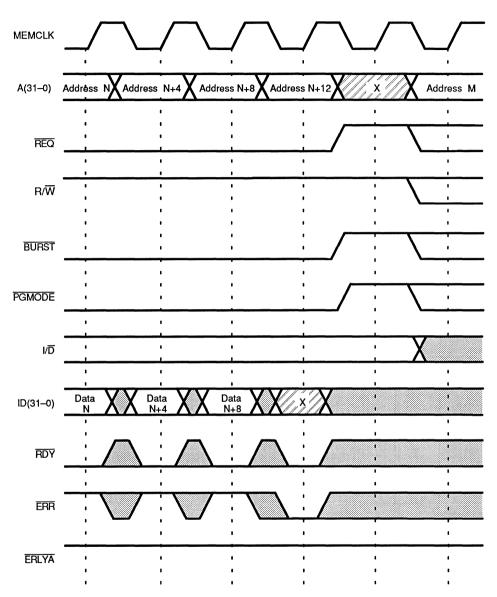

|            |                                                               | 10.4.10                                                                                                                                   | 10.4.10.1 Burst-Mode Overview                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                      |

|            |                                                               |                                                                                                                                           | 10.4.10.2 Processor Pre-emption, Termination, or                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                      |

|            |                                                               |                                                                                                                                           | Cancellation of a Burst-Mode Access                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                      |

|            |                                                               |                                                                                                                                           | 10.4.10.3 Slave Cancellation of a Burst-Mode Access                                                                                                                                                                                                                                                                                                                                                                                   | 10-17                                                                                                                                                                |

|            |                                                               |                                                                                                                                           | 10.4.10.4 Using ERLYA for Interleaved Memory Systems .                                                                                                                                                                                                                                                                                                                                                                                | 10-17                                                                                                                                                                |

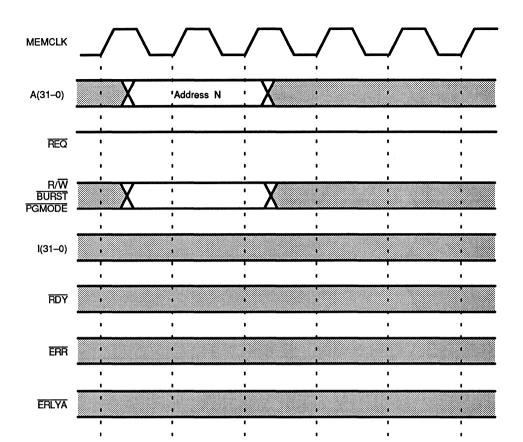

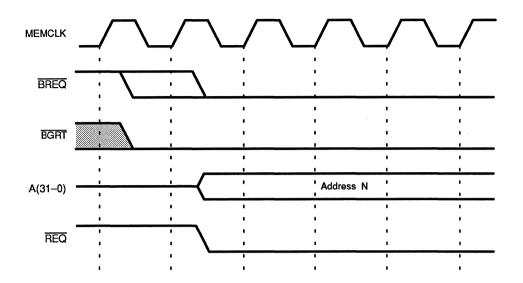

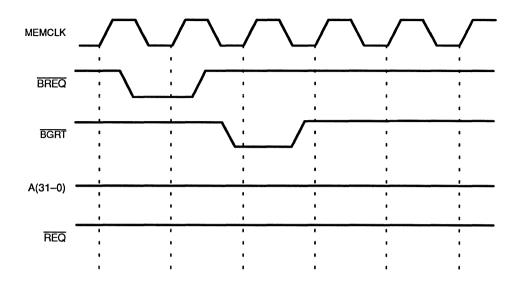

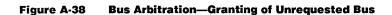

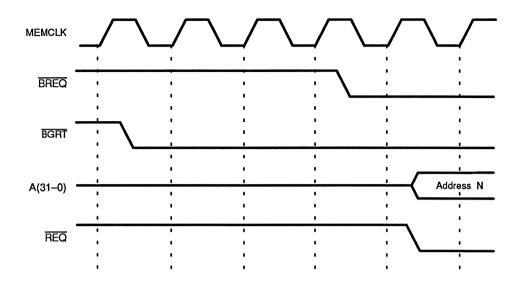

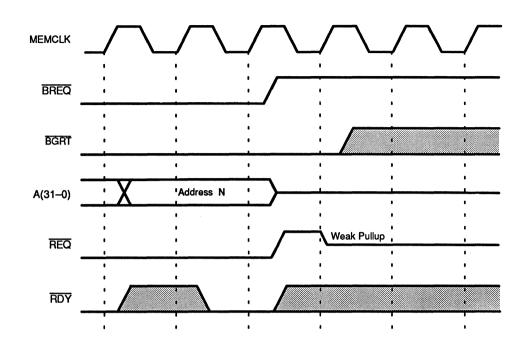

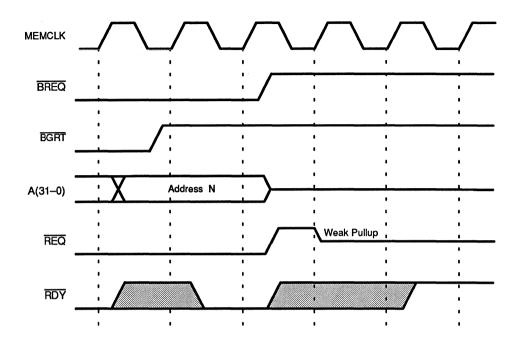

|            |                                                               | 10.4.11                                                                                                                                   | Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                           | 10-18                                                                                                                                                                |

|            | 405                                                           | Due Ohe                                                                                                                                   | 10.4.11.1 Using The Processor as an Arbiter                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

|            |                                                               |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

|            |                                                               |                                                                                                                                           | cessing and the LOCK Output                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

|            | 10.7                                                          |                                                                                                                                           | Slave Checking                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

|            |                                                               | 10.7.1<br>10.7.2                                                                                                                          | Master/Slave Operation<br>Preventing Spurious Errors                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

|            |                                                               | 10.7.2                                                                                                                                    | Switching Master and Slave Processors                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

| <b>.</b>   |                                                               |                                                                                                                                           | ·                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                      |

| Chapter 11 |                                                               |                                                                                                                                           | nd Testing                                                                                                                                                                                                                                                                                                                                                                                                                            | . 11-1                                                                                                                                                               |

|            | 11.1                                                          |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

|            |                                                               |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11-1                                                                                                                                                                 |

|            | 11.2                                                          | Instructio                                                                                                                                | on Breakpoints                                                                                                                                                                                                                                                                                                                                                                                                                        | 11-1<br>11-2                                                                                                                                                         |

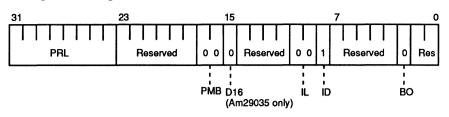

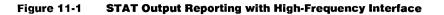

|            | 11.3                                                          | Instruction<br>Processo                                                                                                                   | on Breakpoints                                                                                                                                                                                                                                                                                                                                                                                                                        | 11-1<br>11-2<br>11-2                                                                                                                                                 |

|            | 11.3<br>11.4                                                  | Instruction<br>Processon<br>CPU Cor                                                                                                       | on Breakpoints                                                                                                                                                                                                                                                                                                                                                                                                                        | 11-1<br>11-2<br>11-2<br>11-4                                                                                                                                         |

|            | 11.3<br>11.4                                                  | Instruction<br>Processon<br>CPU Corr<br>Impleme                                                                                           | on Breakpoints                                                                                                                                                                                                                                                                                                                                                                                                                        | 11-1<br>11-2<br>11-2<br>11-4<br>11-5                                                                                                                                 |

|            | 11.3<br>11.4                                                  | Instruction<br>Processon<br>CPU Cont<br>Impleme<br>11.5.1                                                                                 | on Breakpoints<br>or Status Outputs<br>ntrol Inputs<br>nting a Hardware-Development System<br>Halt Mode                                                                                                                                                                                                                                                                                                                               | 11-1<br>11-2<br>11-2<br>11-4<br>11-5<br>11-5                                                                                                                         |

|            | 11.3<br>11.4                                                  | Instruction<br>Processon<br>CPU Cont<br>Impleme<br>11.5.1<br>11.5.2                                                                       | on Breakpoints<br>or Status Outputs<br>ntrol Inputs<br>nting a Hardware-Development System<br>Halt Mode<br>Step Mode                                                                                                                                                                                                                                                                                                                  | 11-1<br>11-2<br>11-2<br>11-4<br>11-5<br>11-5<br>11-5                                                                                                                 |

|            | 11.3<br>11.4                                                  | Instruction<br>Processon<br>CPU Cont<br>Implement<br>11.5.1<br>11.5.2<br>11.5.3                                                           | on Breakpoints<br>or Status Outputs<br>ntrol Inputs<br>nting a Hardware-Development System<br>Halt Mode<br>Step Mode<br>Load Test Instruction Mode                                                                                                                                                                                                                                                                                    | 11-1<br>11-2<br>11-2<br>11-4<br>11-5<br>11-5<br>11-5<br>11-6                                                                                                         |

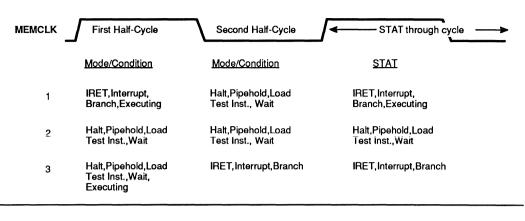

|            | 11.3<br>11.4<br>11.5                                          | Instruction<br>Processon<br>CPU Cond<br>Impleme<br>11.5.1<br>11.5.2<br>11.5.3<br>11.5.4                                                   | on Breakpoints<br>or Status Outputs<br>ntrol Inputs<br>nting a Hardware-Development System<br>Halt Mode<br>Step Mode<br>Load Test Instruction Mode<br>Summary of Development System Operation                                                                                                                                                                                                                                         | 11-1<br>11-2<br>11-2<br>11-4<br>11-5<br>11-5<br>11-5<br>11-6<br>11-9                                                                                                 |

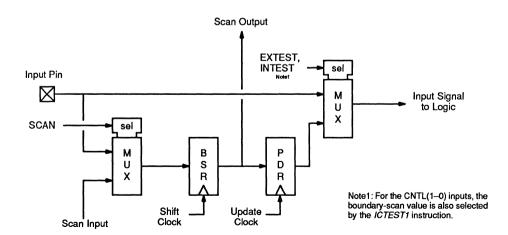

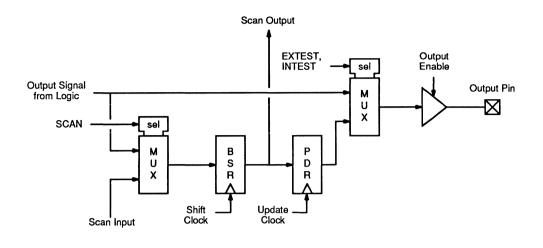

|            | <ul><li>11.3</li><li>11.4</li><li>11.5</li><li>11.6</li></ul> | Instruction<br>Processon<br>CPU Cont<br>Implement<br>11.5.1<br>11.5.2<br>11.5.3<br>11.5.4<br>In-Circuit                                   | on Breakpoints<br>or Status Outputs<br>ntrol Inputs<br>nting a Hardware-Development System<br>Halt Mode<br>Step Mode<br>Load Test Instruction Mode<br>Summary of Development System Operation                                                                                                                                                                                                                                         | 11-1<br>11-2<br>11-2<br>11-4<br>11-5<br>11-5<br>11-5<br>11-6<br>11-9                                                                                                 |

|            | <ul><li>11.3</li><li>11.4</li><li>11.5</li><li>11.6</li></ul> | Instruction<br>Processon<br>CPU Cont<br>Implement<br>11.5.1<br>11.5.2<br>11.5.3<br>11.5.4<br>In-Circuit<br>Test Acco                      | on Breakpoints<br>or Status Outputs<br>ntrol Inputs<br>Halt Mode<br>Step Mode<br>Load Test Instruction Mode<br>Summary of Development System Operation<br>t Testing                                                                                                                                                                                                                                                                   | 11-1<br>11-2<br>11-4<br>11-5<br>11-5<br>11-5<br>11-6<br>11-9<br>11-9<br>11-9                                                                                         |

|            | <ul><li>11.3</li><li>11.4</li><li>11.5</li><li>11.6</li></ul> | Instruction<br>Processon<br>CPU Cont<br>Implement<br>11.5.1<br>11.5.2<br>11.5.3<br>11.5.4<br>In-Circuit                                   | on Breakpoints<br>or Status Outputs<br>introl Inputs<br>Halt Mode<br>Step Mode<br>Load Test Instruction Mode<br>Summary of Development System Operation<br>t Testing<br>ess Port<br>Boundary Scan Cells                                                                                                                                                                                                                               | 11-1<br>11-2<br>11-2<br>11-4<br>11-5<br>11-5<br>11-5<br>11-6<br>11-9                                                                                                 |