~~~~~~~~~~~~~~~~~~~~~~~~ алалалалалалалалалалалалал ~~~~~~~~~~~

# **Advanced Micro Devices**

# Linear and Interface Data Book

Copyright © 1979 by Advanced Micro Devices, Inc.

Advanced Micro Devices cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in an Advanced Micro Devices' product.

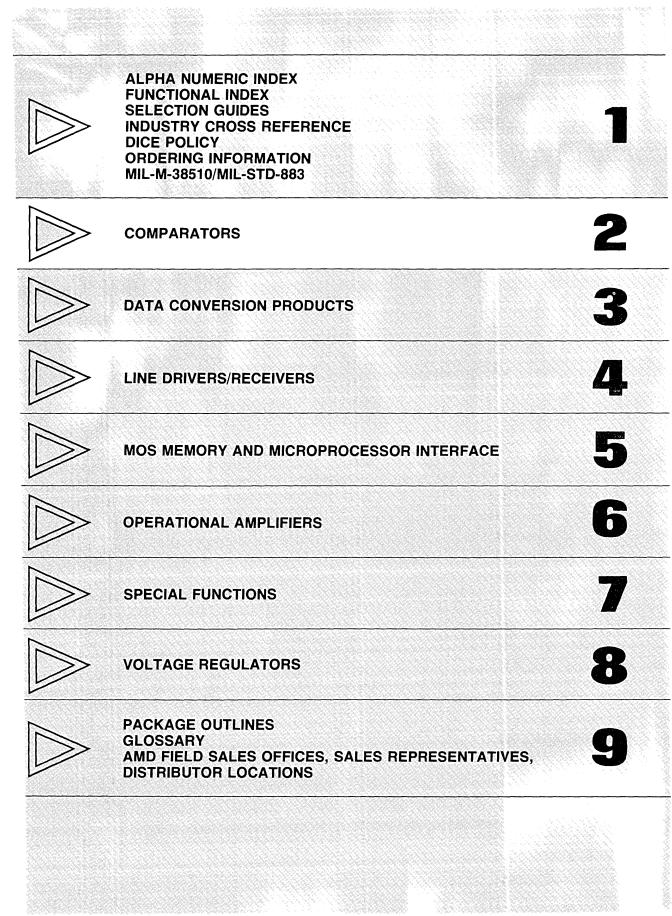

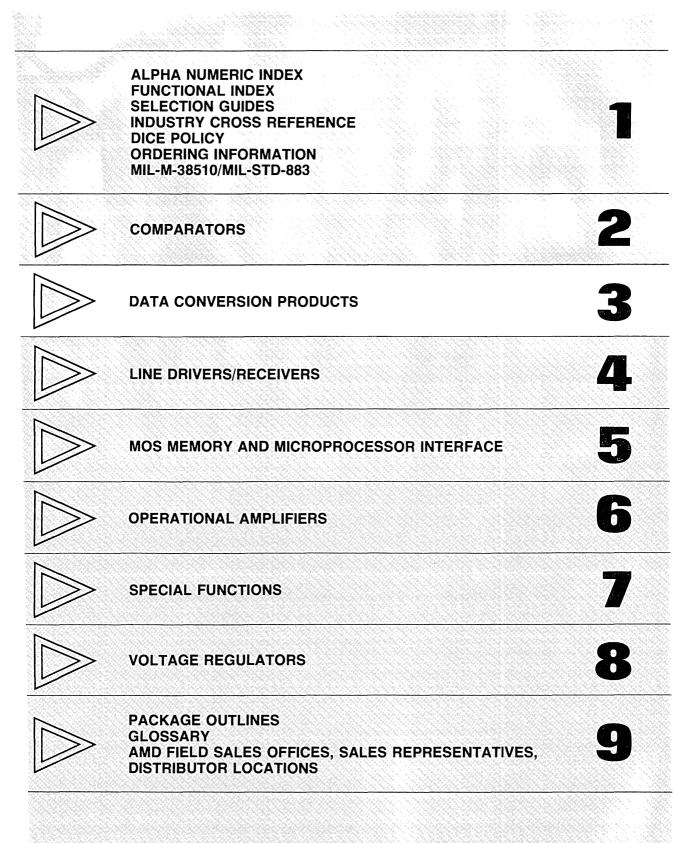

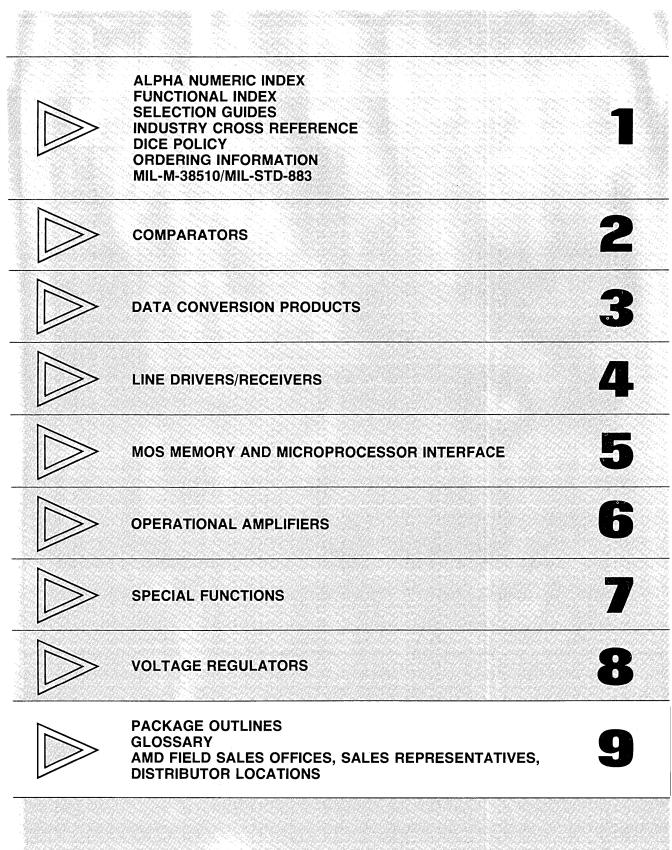

ALPHA NUMERIC INDEX FUNCTIONAL INDEX SELECTION GUIDES INDUSTRY CROSS REFERENCE DICE POLICY ORDERING INFORMATION MIL-M-38510/MIL-STD-883

LINE DRIVERS/RECEIVERS

MOS MEMORY AND MICROPROCESSOR INTERFACE

**OPERATIONAL AMPLIFIERS**

SPECIAL FUNCTIONS

VOLTAGE REGULATORS

2

3

5

5

PACKAGE OUTLINES GLOSSARY AMD FIELD SALES OFFICES, SALES REPRESENTATIVES, DISTRIBUTOR LOCATIONS

# Section I

| Numeric Index            |      |

|--------------------------|------|

| Functional Index         | 1-6  |

| Selection Guides         | 1-10 |

| Industry Cross-Reference | 1-14 |

| Dice Policy              | 1-22 |

| Ordering Information     | 1-23 |

| MIL-M-38510/MIL-STD-883  | 1-26 |

# NUMERIC INDEX

1

| Product  | Description                                        | Page |

|----------|----------------------------------------------------|------|

| Am0026   | 5MHz Two-Phase MOS Clock Driver                    | 5-1  |

| Am0056   | 5MHz Two-Phase MOS Clock Driver                    |      |

| AmDAC-08 | 8-Bit High-Speed Multiplying D/A Converter         | 3-1  |

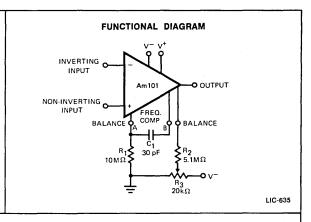

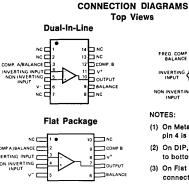

| Am101    | Operational Amplifier                              | 6-1  |

| Am101A   | Operational Amplifier                              |      |

| Am102    | Voltage Follower                                   |      |

| Am105    | Voltage Regulator                                  | 8-1  |

| Am106    | Voltage Comparator/Buffer                          |      |

| Am107    | Frequency Compensated Operational Amplifier        |      |

| Am108    | Operational Amplifier                              |      |

| Am108A   | Operational Amplifier                              |      |

| Am110    | Voltage Follower                                   |      |

| Am111    | Precision Voltage Comparator                       |      |

| Am112    | Compensated High-Performance Operational Amplifier |      |

| Am118    | High-Speed Operational Amplifier                   |      |

| Am119    | Dual Voltage Comparator                            |      |

| Am124    | Quad Operational Amplifier                         |      |

| Am124A   | Quad Operational Amplifier                         |      |

| Am139    | Low Offset Voltage Quad Comparator                 |      |

| Am139A   | Low Offset Voltage Quad Comparator                 |      |

| Am1408   | 8-Bit Multiplying D/A Converter                    |      |

| SSS1408A | 8-Bit Multiplying D/A Converter                    |      |

| Am1458   | Dual Frequency Compensated Operational Amplifier   |      |

| Am148    | Quad 741 Operational Amplifier                     |      |

| Am1488   | Quad RS-232C Line Driver                           |      |

| Am1489   | Quad RS-232C Line Receiver                         |      |

| Am1489A  | Quad RS-232C Line Receiver                         | 4-4  |

| Am149    | Quad 741 Operational Amplifier                     |      |

| Am1500   | Dual Precision Voltage Comparator                  |      |

| Am1501   | Dual Operational Amplifier                         |      |

| Am1508   | 8-Bit Multiplying D/A Converter                    |      |

| SSS1508A | 8-Bit Multiplying D/A Converter                    |      |

| LF155    | JFET Input Operational Amplifier                   |      |

| LF155A   | JFET Input Operational Amplifier                   |      |

| Am1558   | Dual Frequency Compensated Operational Amplifier   |      |

| LF156    | JFET Input Operational Amplifier                   | 6-43 |

| LF156A   | JFET Input Operational Amplifier                   | 6-43 |

| LF157    | JFET Input Operational Amplifier                   | 6-43 |

| LF157A   | JFET Input Operational Amplifier                   |      |

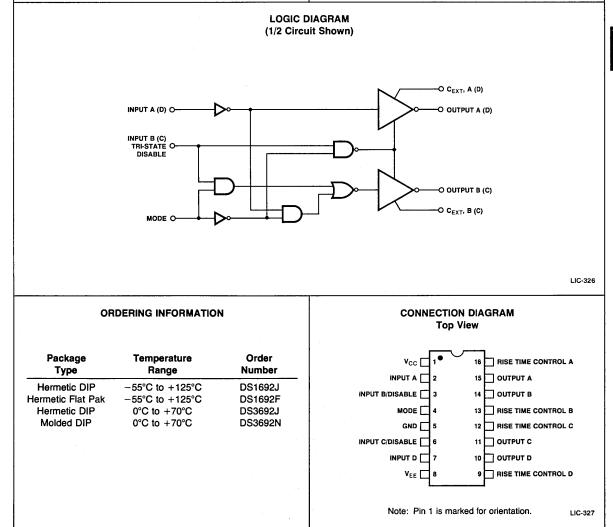

| Am1692   | Three-State Differential Line Drivers              | 4-8  |

| LF198    | Monolithic Sample and Hold Circuits                | 3-7  |

| Am201    | Operational Amplifier                              | 6-1  |

| Am201A   | Operational Amplifier                              | 6-5  |

| Am202    | Voltage Follower                                   |      |

| Am205    | Voltage Regulator                                  | 8-1  |

| Am206    | Voltage Comparator/Buffer                          | 2-1  |

| Am207    | Frequency Compensated Operational Amplifier        | 6-14 |

| Am208    | Operational Amplifier                              |      |

| Am208A   | Operational Amplifier                              |      |

| Am210    | Voltage Follower                                   |      |

| LH2101A  | Dual Operational Amplifier                         |      |

| Product   | Description                                                 | Page   |

|-----------|-------------------------------------------------------------|--------|

| Am211     | Precision Voltage Comparator                                | 2-5    |

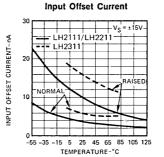

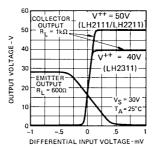

| LH2111    | Dual Precision Voltage Comparator                           | . 2-35 |

| Am212     | Compensated, High-Performance Operational Amplifier         | . 6-26 |

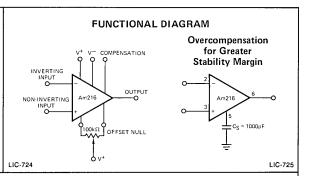

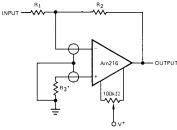

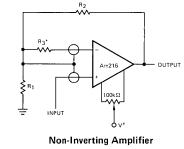

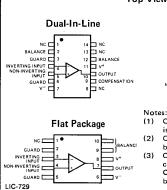

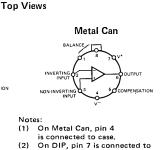

| Am216     | Compensated, High-Performance Operational Amplifier         | . 6-51 |

| Am216A    | Compensated, High Performance Operational Amplifier         | . 6-51 |

| Am218     | High-Speed Operational Amplifier                            | . 6-30 |

| Am219     | Dual Voltage Comparator                                     |        |

| LH2201A   | Dual Operational Amplifier                                  |        |

| LH2211    | Dual Precision Voltage Comparator                           |        |

| Am224     | Quad Operational Amplifier                                  |        |

| Am224A    | Quad Operational Amplifier                                  | . 6-36 |

| LH2301A   | Dual Operational Amplifier                                  |        |

| LH2311    | Dual Precision Voltage Comparator                           | 2-35   |

| Am239     | Low Offset Voltage Quad Comparator                          |        |

| Am239A    | Low Offset Voltage Quad Comparator                          | 2-13   |

| Am248     | Quad 741 Operational Amplifier                              |        |

| Am249     | Quad 741 Operational Amplifier                              |        |

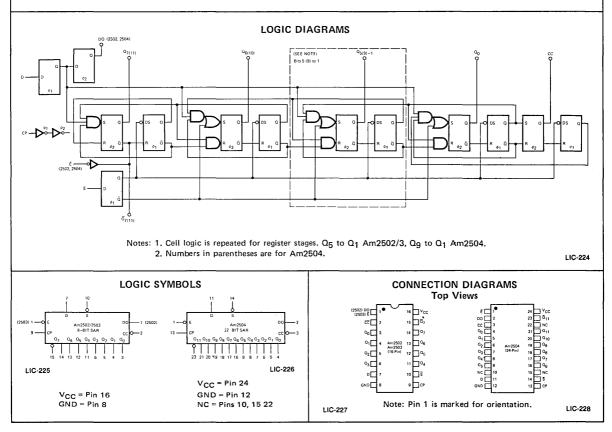

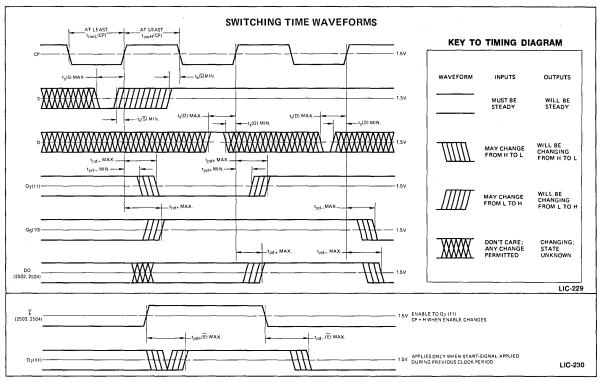

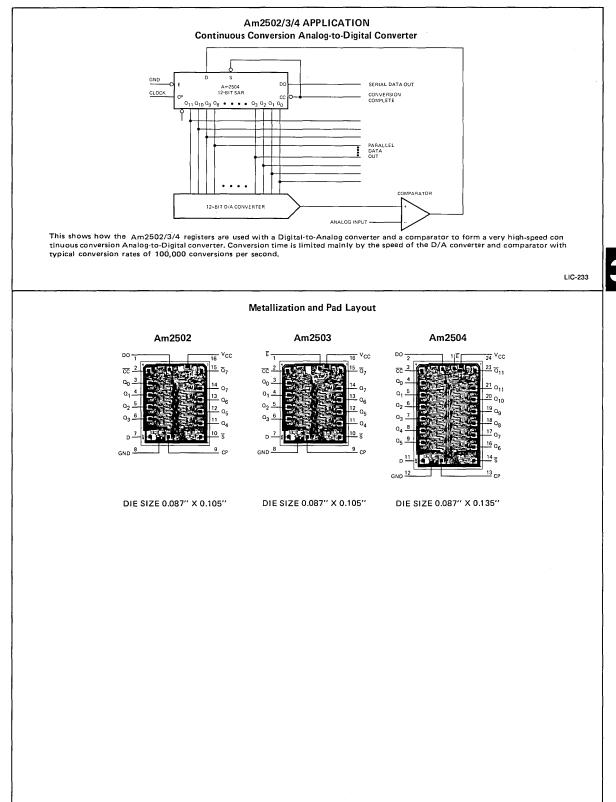

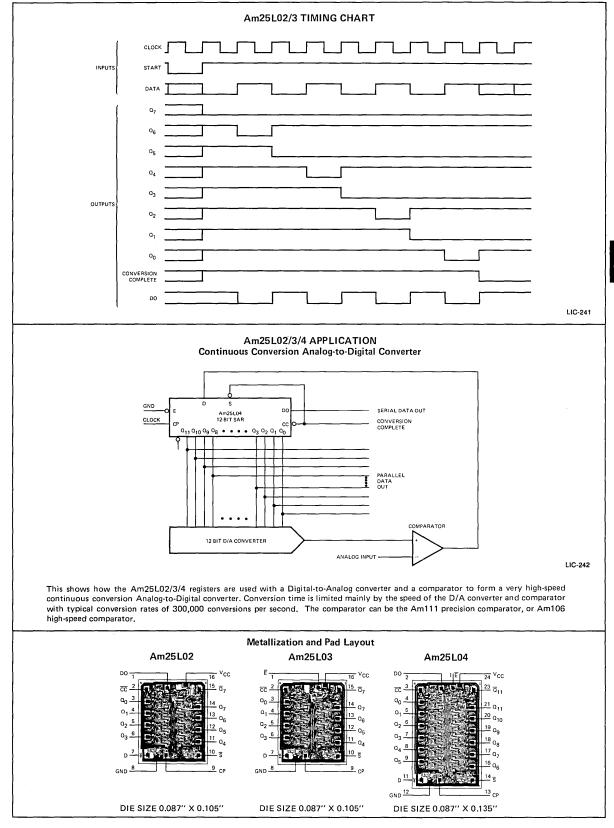

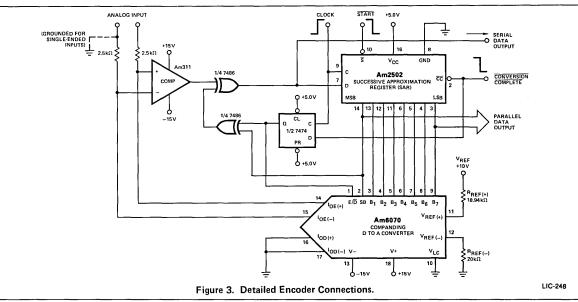

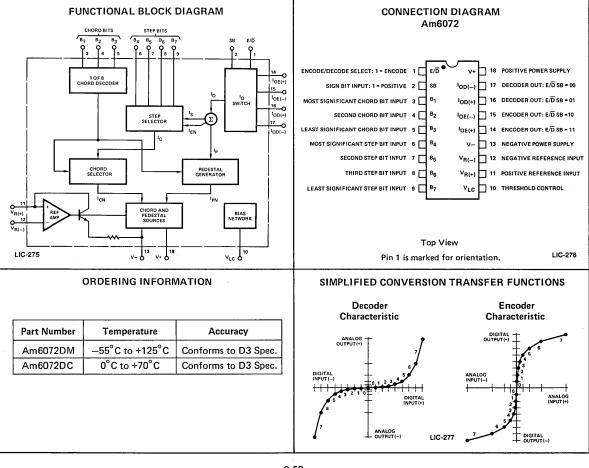

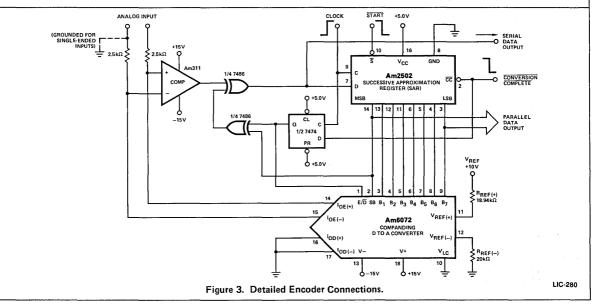

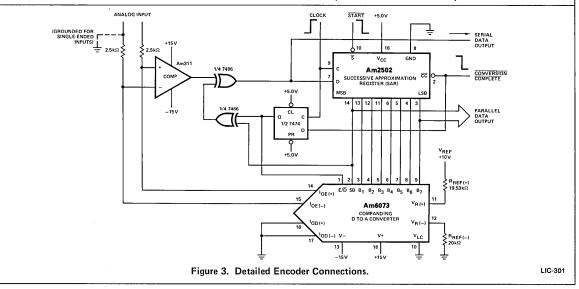

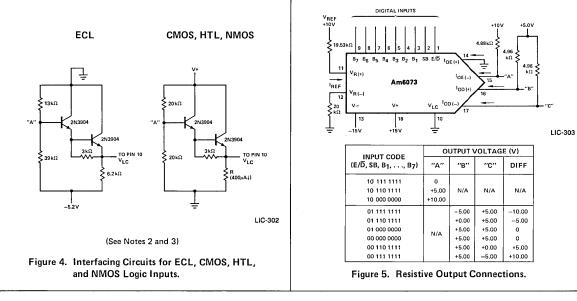

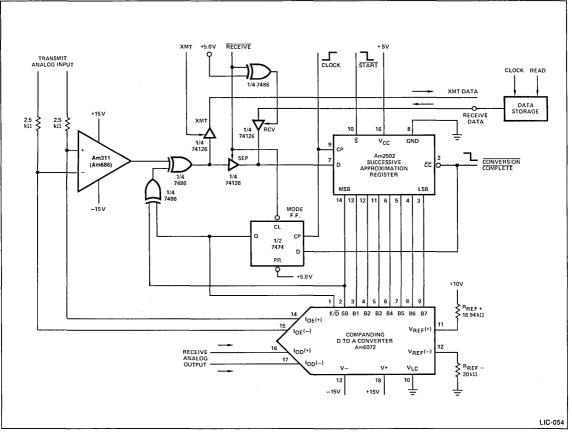

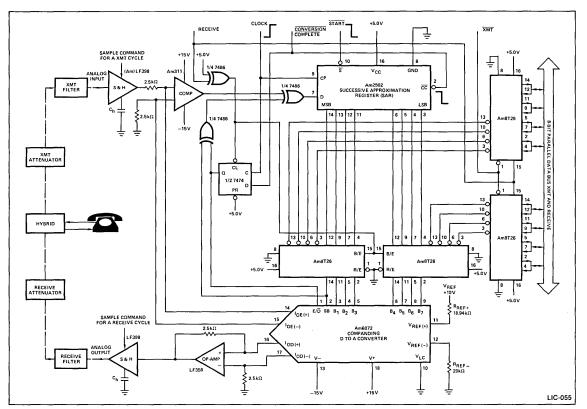

| Am2502    | 8-Bit/12-Bit Successive Approximation Registers             | 3-18   |

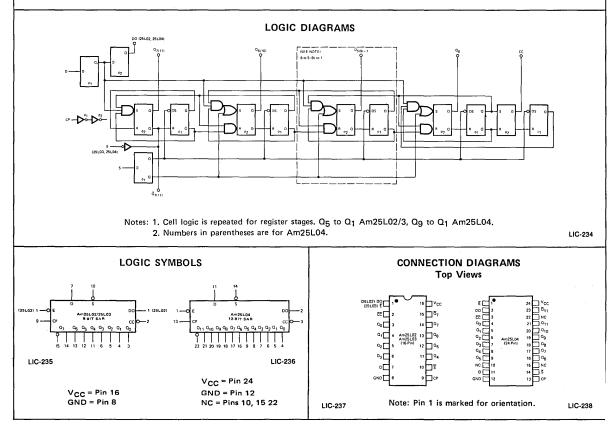

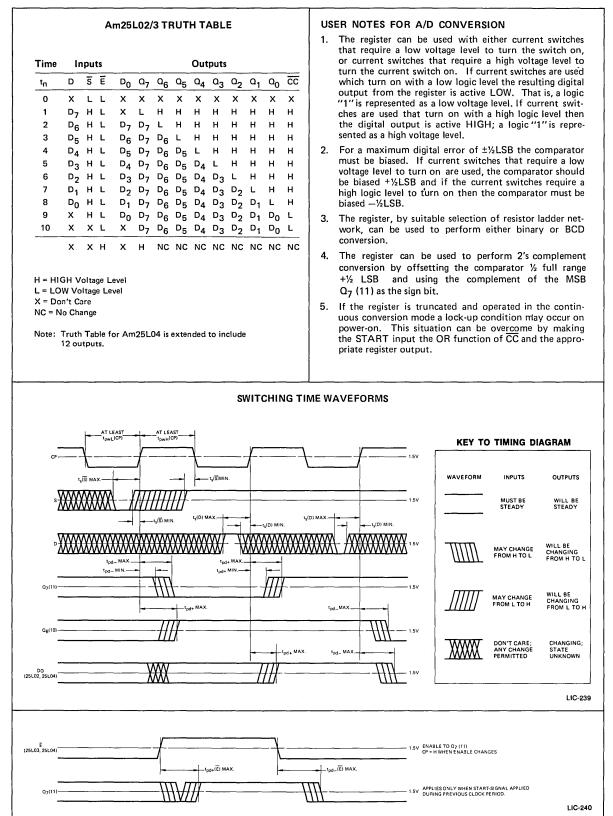

| Am25L02   | Low-Power, 8-Bit/12-Bit Successive Approximation Registers  | 3-24   |

| Am2503    | 8-Bit/12-Bit Successive Approximation Registers             | 3-18   |

| Am25L03   | Low-Power, 8-Bit/12-Bit Successive Approximation Registers  | 3-24   |

| Am2504    | 8-Bit/12-Bit Successive Approximation Registers             | 3-18   |

| Am25L04   | Low-Power, 8-Bit/12-Bit Successive Approximation Registers  | 3-24   |

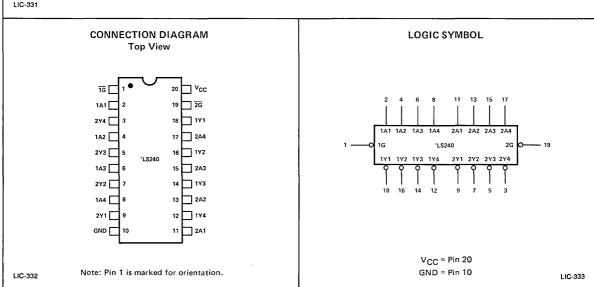

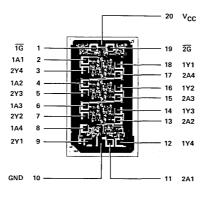

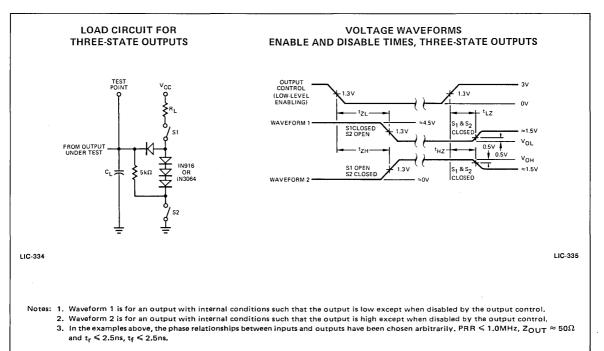

| Am25LS240 | Octal Buffer; Inverting, Three-State                        | . 4-13 |

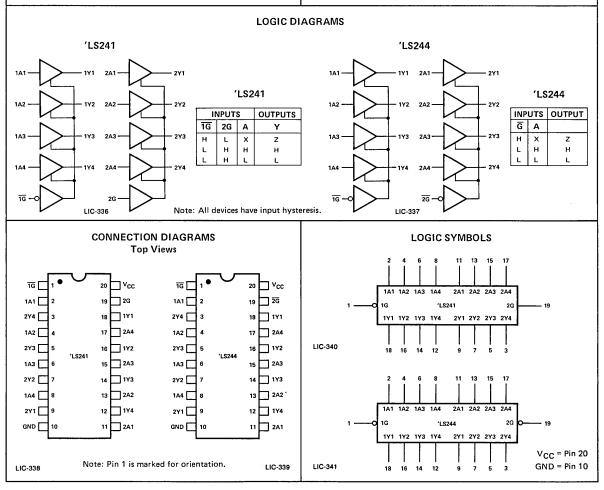

| Am25LS241 | Octal Buffer; Non-Inverting, Three-State                    | 4-17   |

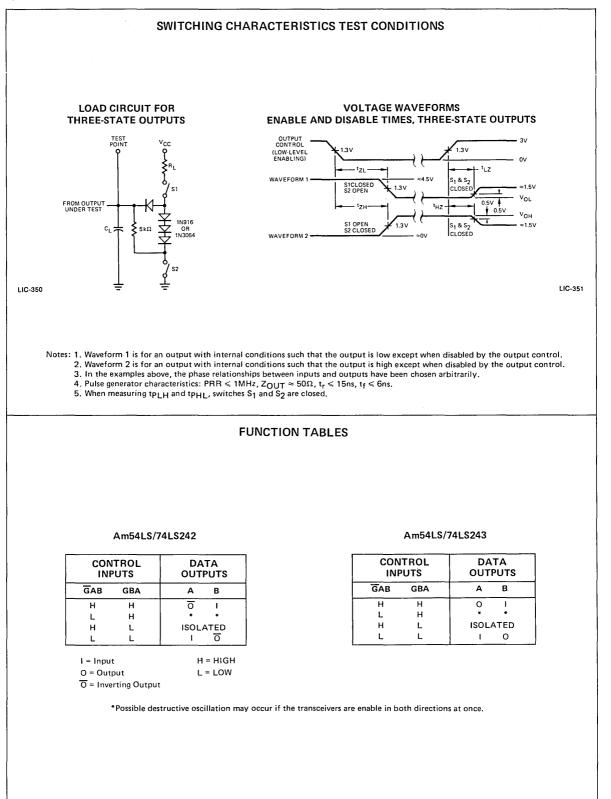

| Am25LS242 | Quad Three-State Transceiver                                |        |

| Am25LS243 | Quad Three-State Transceiver                                |        |

| Am25LS244 | Octal Buffer Non-Inverting, Three-State                     |        |

| LF255     | JFET Input Operational Amplifier                            |        |

| LF255A    | JFET Input Operational Amplifier                            |        |

| LF256     | JFET Input Operational Amplifier                            |        |

| LF256A    | JFET Input Operational Amplifier                            |        |

| LF257     | JFET Input Operational Amplifier                            |        |

| LF257A    | JFET Input Operational Amplifier                            |        |

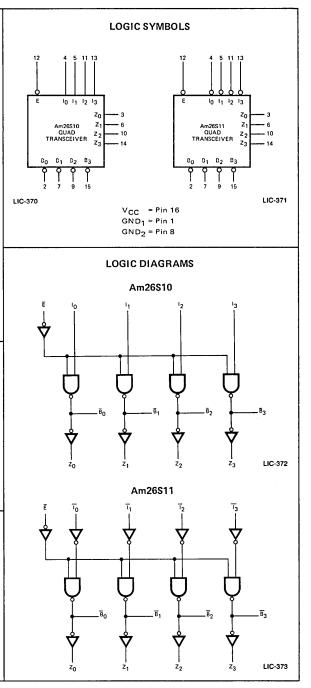

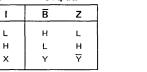

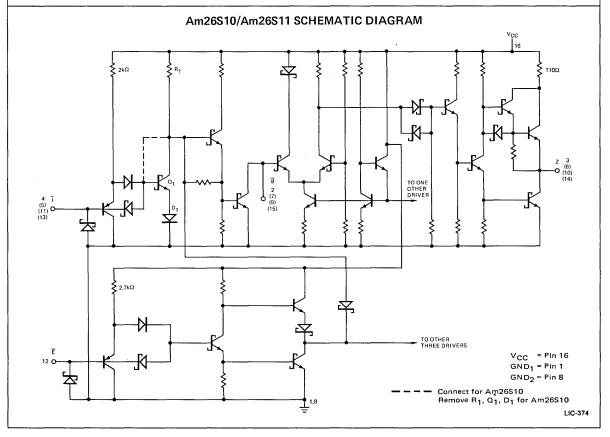

| Am26S10   | Quad Bus Transceiver                                        |        |

| Am26S11   | Quad Bus Transceiver                                        |        |

| Am26S12   | Quad Bus Transceiver                                        |        |

| Am26S12A  | Quad Bus Transceiver                                        |        |

| Am2614    | Quad Single-Ended Line Driver                               |        |

| Am2615    | Dual Line Receiver                                          |        |

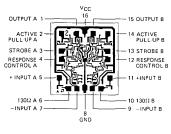

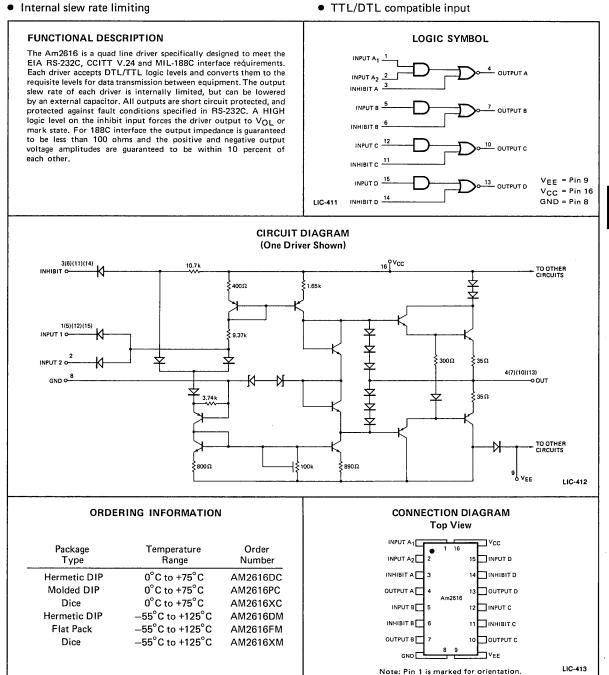

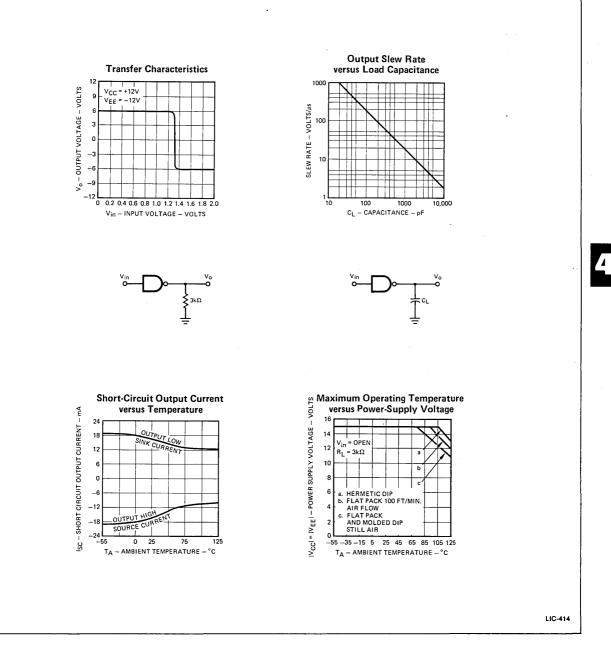

| Am2616    | Quad MIL-188C and RS-232C Line Driver                       |        |

| Am2617    | Quad RS-232C Line Receiver                                  |        |

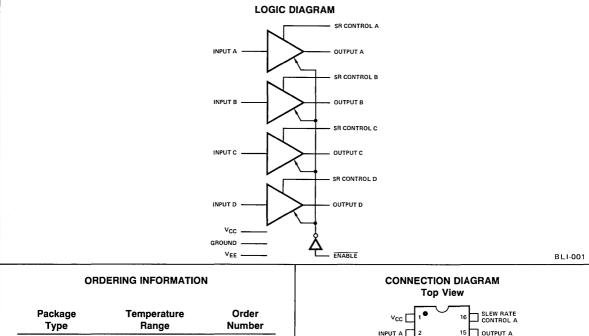

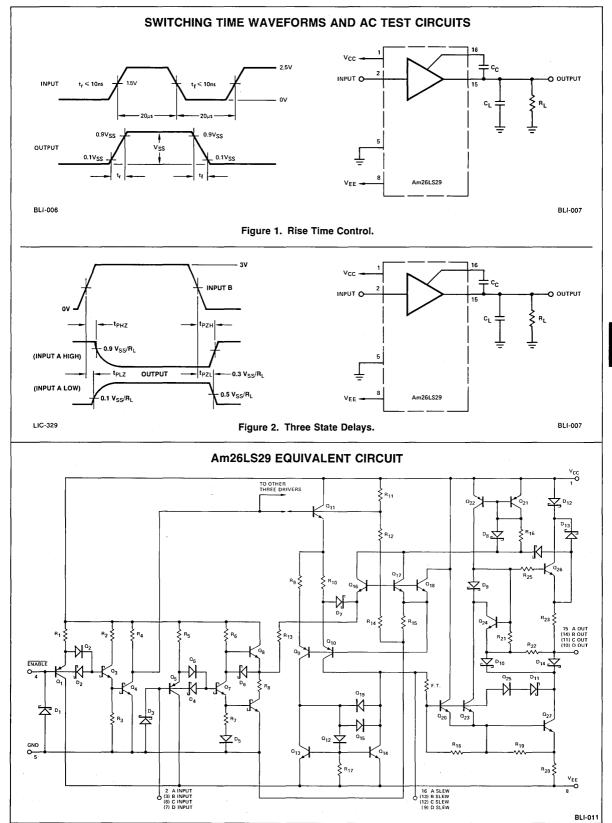

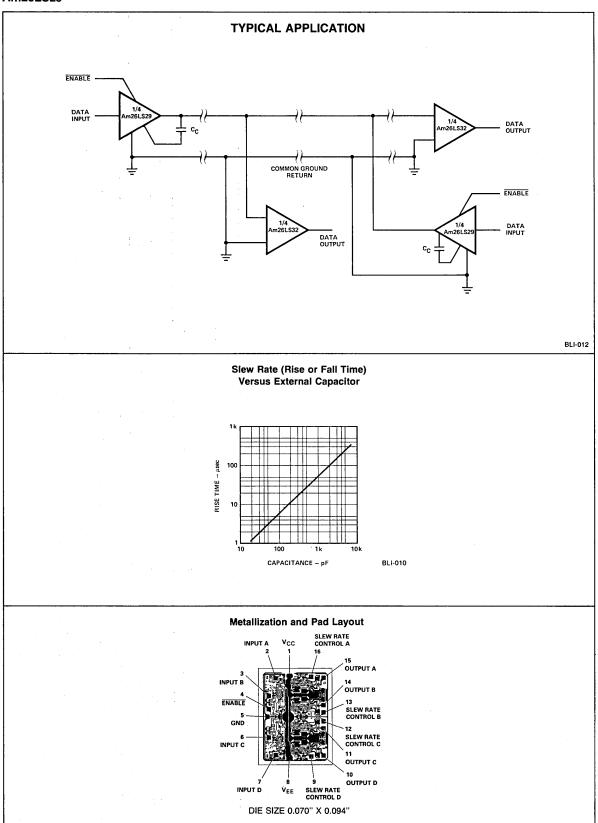

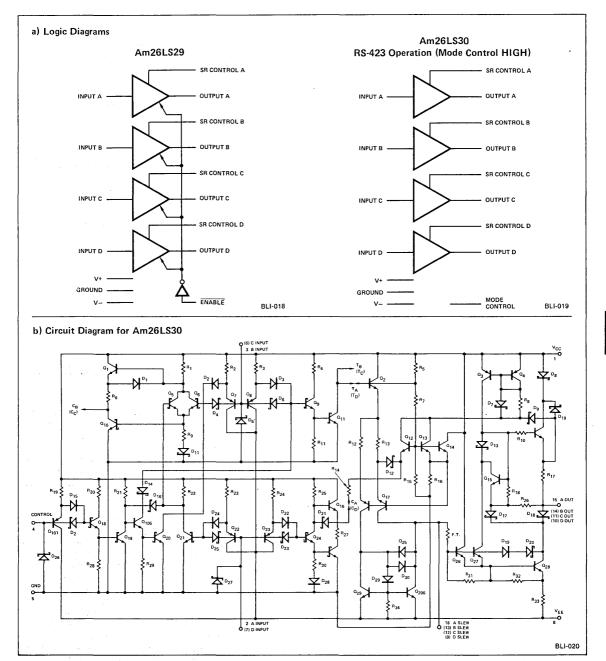

| Am26LS29  | Quad Three-State Single Ended RS-423 Line Driver            | 4-26   |

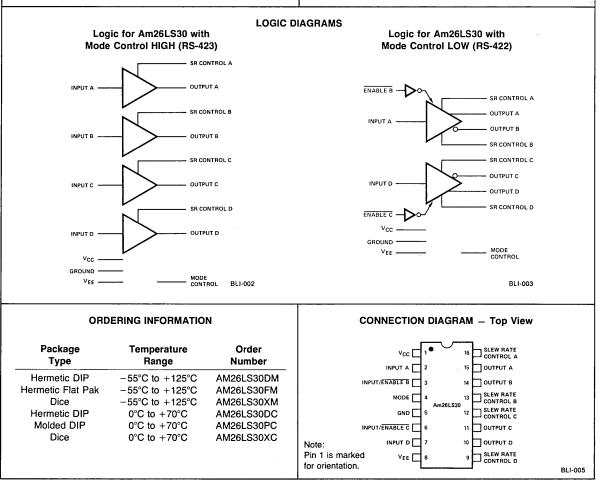

| Am26LS30  | Dual Differential RS-422 Party Line/Quad Single Ended       |        |

|           | RS-423 Line Driver                                          |        |

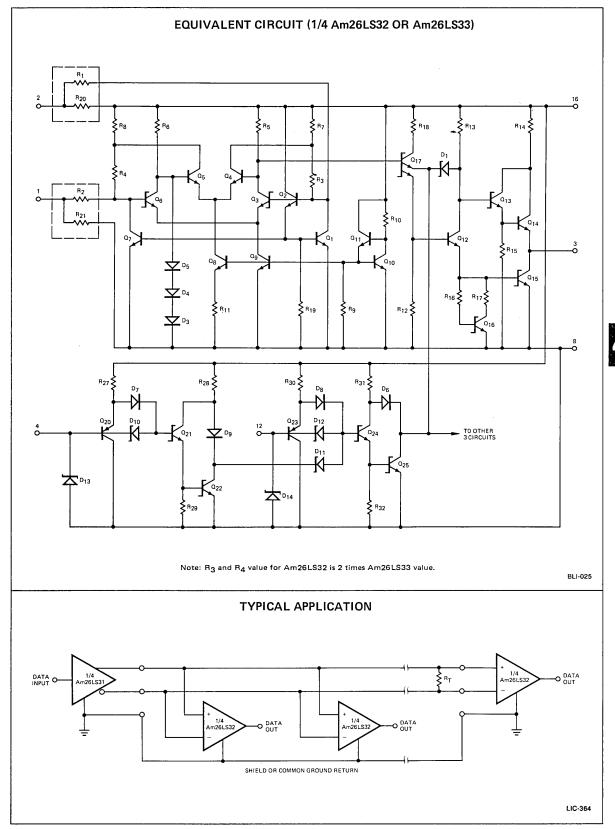

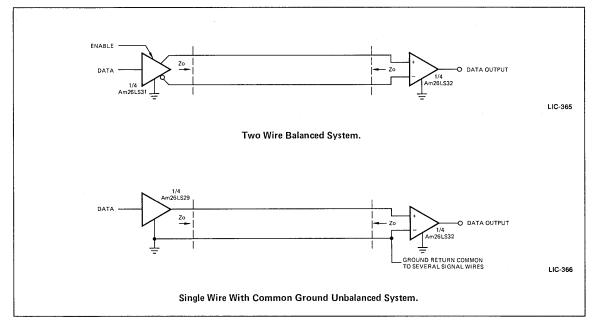

| Am26LS31  | Quad RS-422 High Speed Differential Line Driver             |        |

| Am26LS32  | Quad RS-422 and RS-423 Differential Line Receiver           |        |

| Am26LS33  | Quad Differential Line Receiver                             |        |

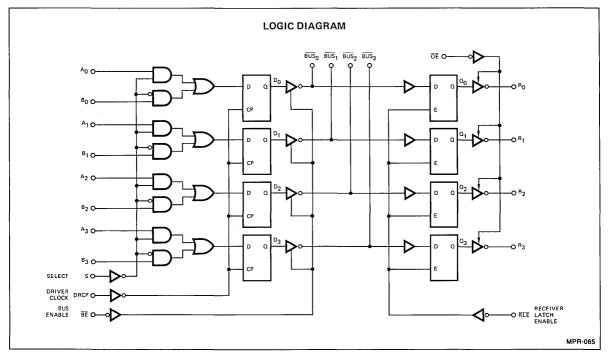

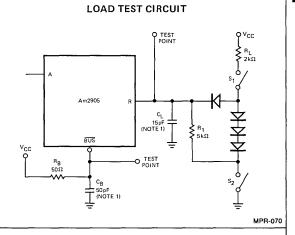

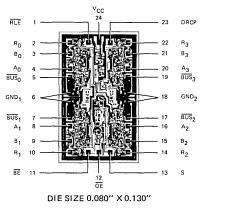

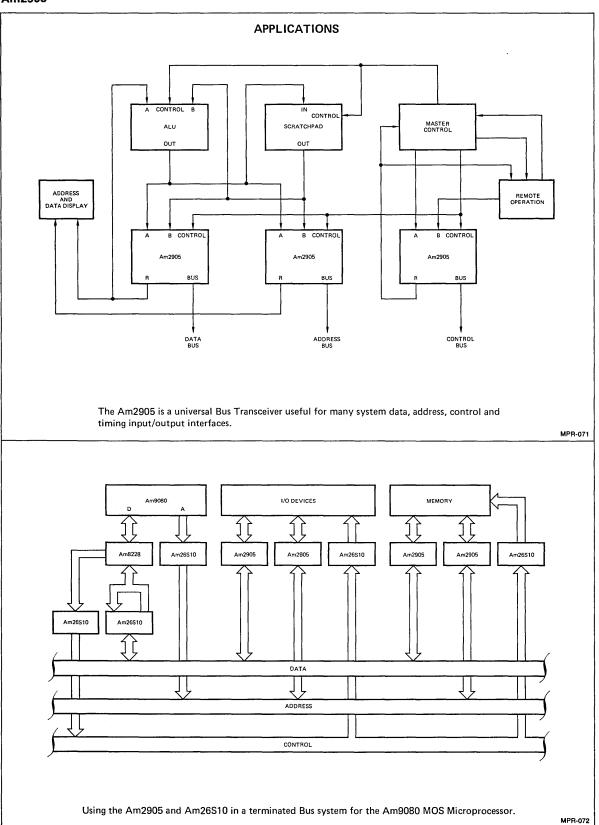

| Am2905    | Quad Two-Input OC Bus Transceiver with Three-State Receiver |        |

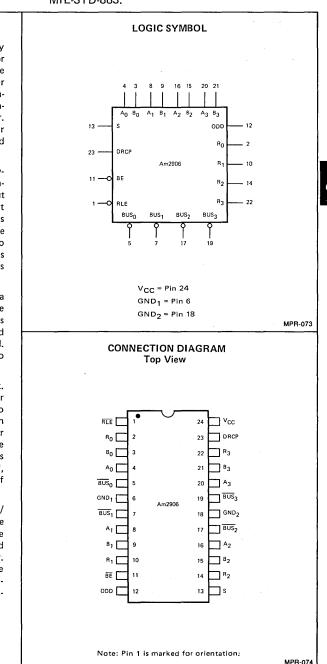

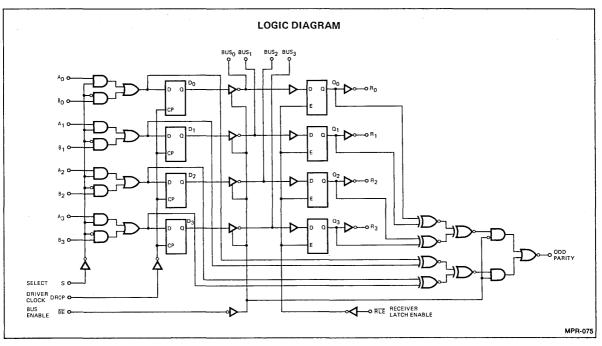

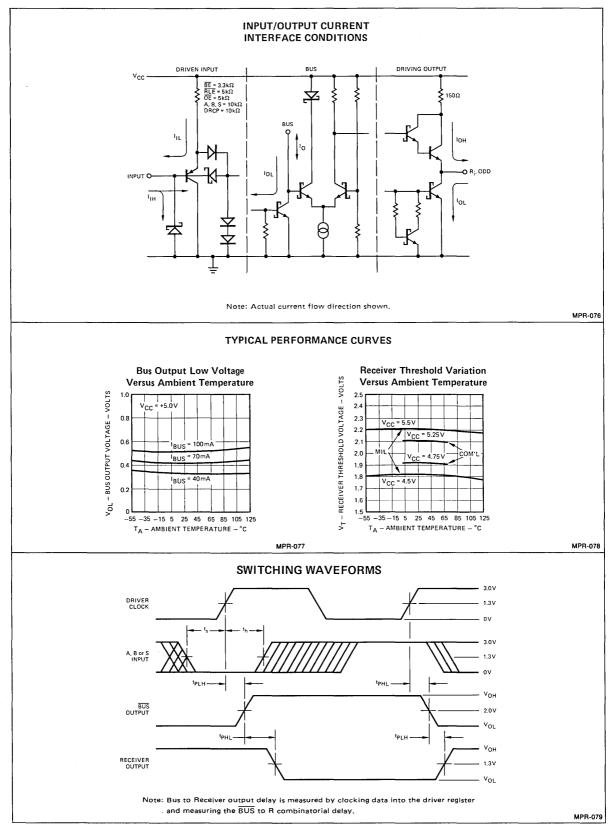

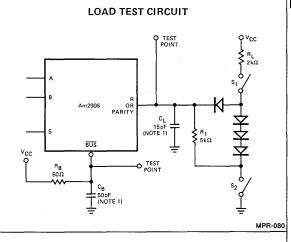

| Am2906    | Quad Two-Input OC Bus Transceiver with Parity               | 4-92   |

| Product        | Description                                                     | Page  |

|----------------|-----------------------------------------------------------------|-------|

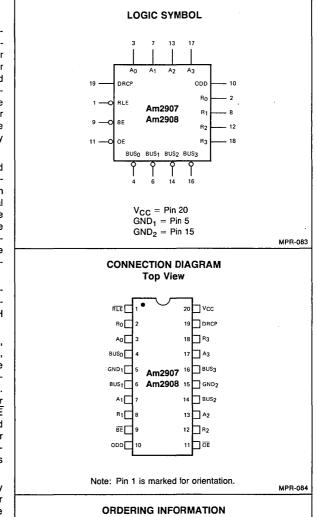

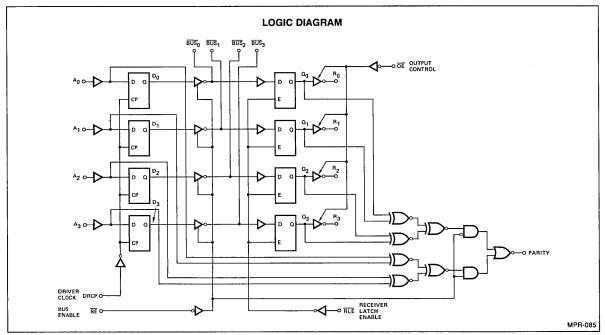

| Am2907         | Quad Bus Transceiver with Interface Logic                       | 4-98  |

| Am2908         | Quad Bus Transceiver with Interface Logic                       | 4-98  |

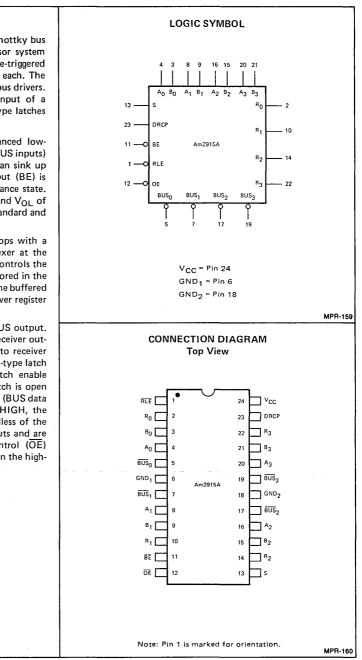

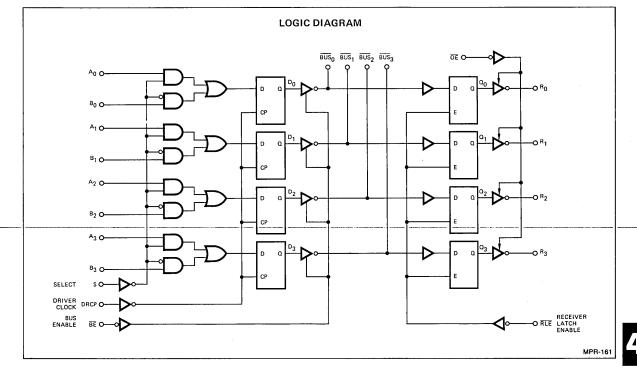

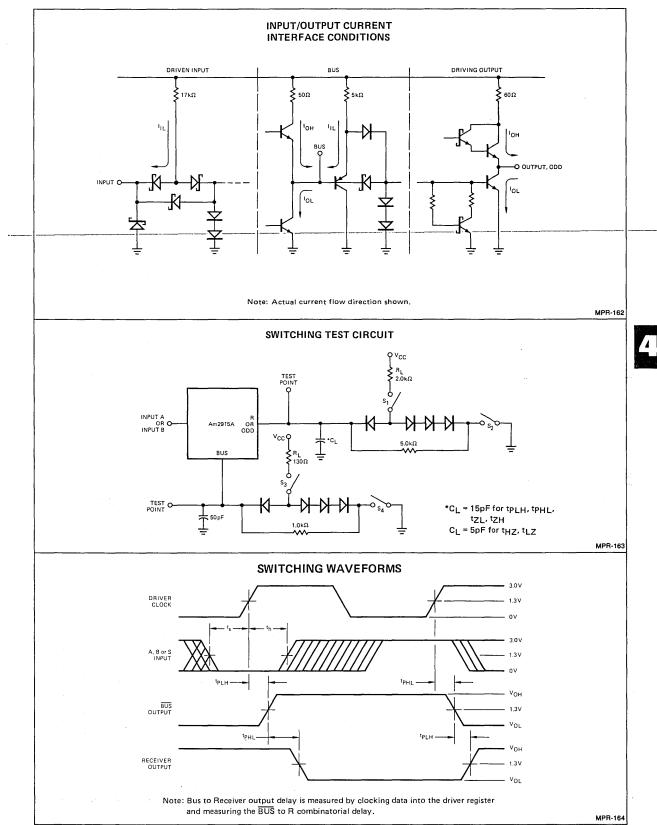

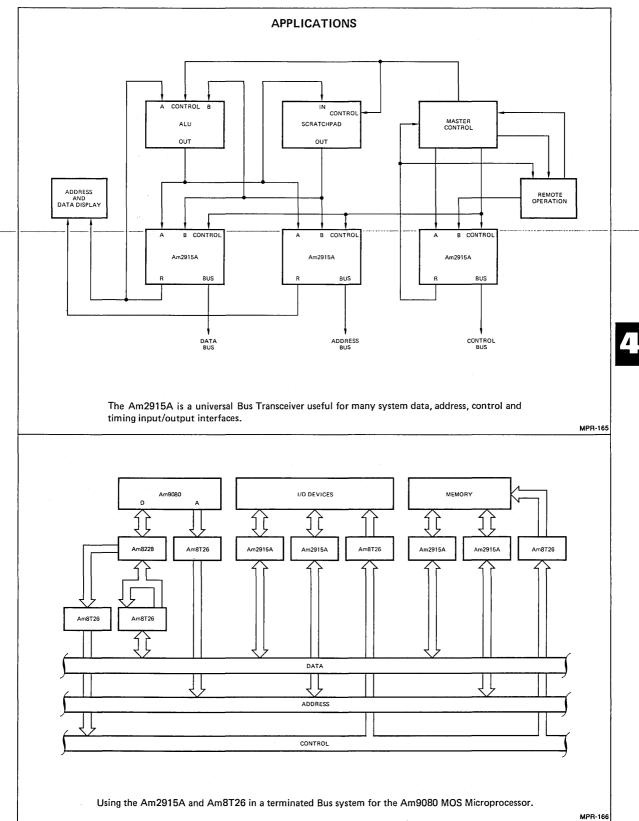

| Am2915A        | Quad Three-State Bus Transceiver with Interface Logic           | 4-107 |

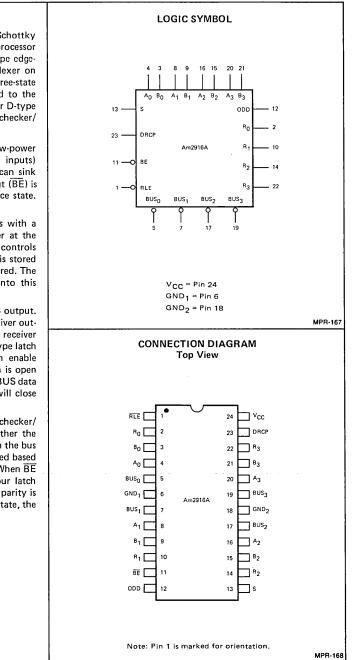

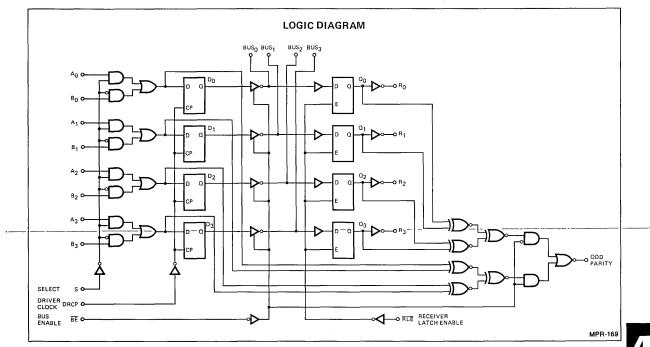

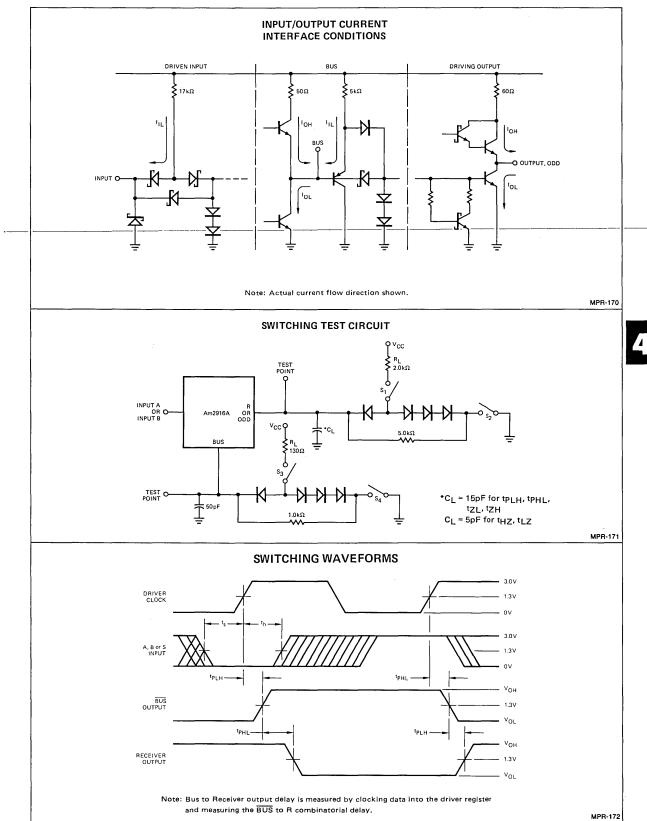

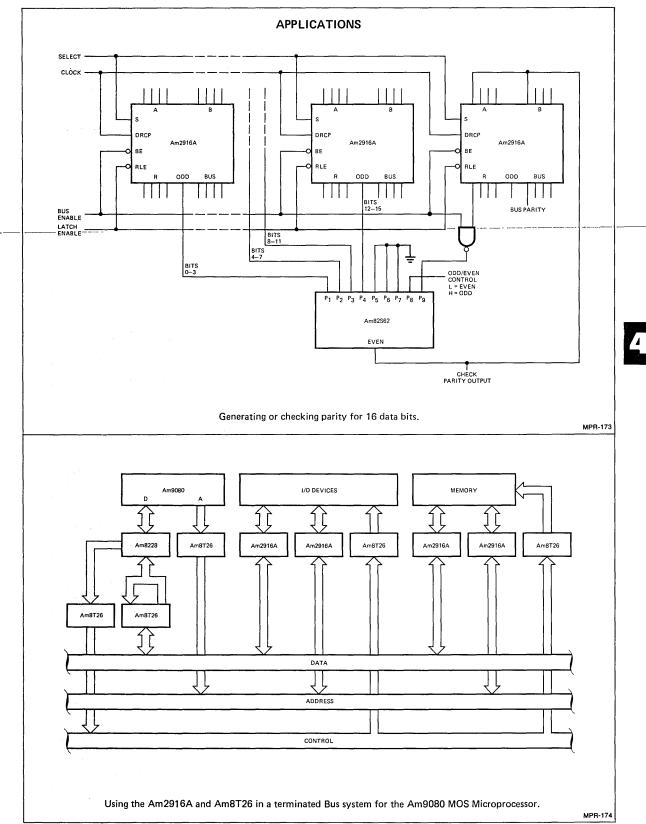

| Am2916A        | Quad Three-State Bus Transceiver with Interface Logic           | 4-113 |

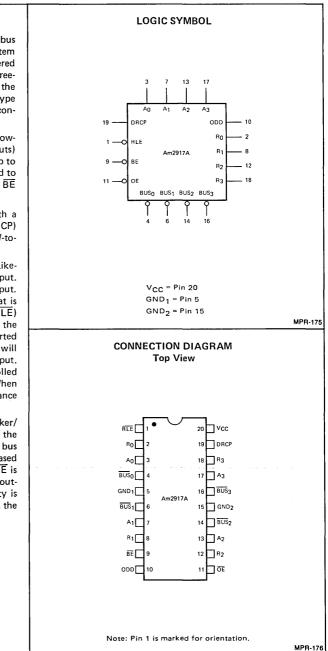

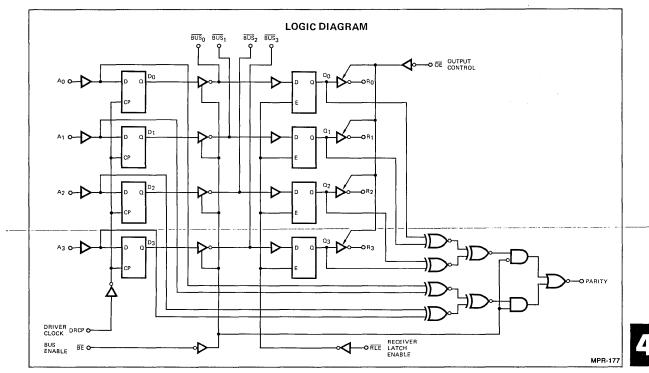

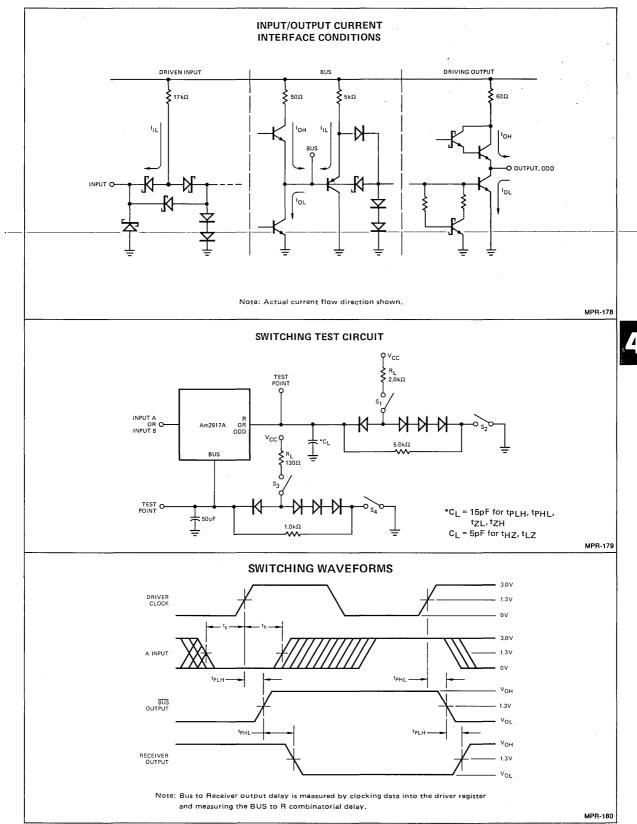

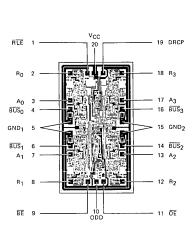

| Am2917A        | Quad Three-State Bus Transceiver with Interface Logic           | 4-119 |

| LF298          | Monolithic Sample and Hold Circuits                             |       |

| Am301          | Operational Amplifier                                           | 6-1   |

| Am301A         | Operational Amplifier                                           |       |

| Am302          | Voltage Follower                                                |       |

| Am305          | Voltage Regulator                                               | 8-1   |

| Am305A         | Voltage Regulator                                               | 8-1   |

| Am306          | Voltage Comparator/Buffer                                       |       |

| Am307          | Frequency Compensated Operational Amplifier                     |       |

| Am308          | Operational Amplifier                                           |       |

| Am308A         | Operational Amplifier                                           |       |

| Am310          | Voltage Follower                                                |       |

| Am311          | Precision Voltage Comparator                                    |       |

| Am312          | Compensated, High-Performance Operational Amplifier             |       |

| Am316          | Compensated, High-Performance Operational Amplifier             |       |

| Am316A         | Compensated, High-Performance Operational Amplifier             |       |

| Am318          | High-Speed Operational Amplifier                                |       |

| Am319          | Dual Voltage Comparator                                         |       |

| Am3212         | 8-Bit Input/Output Port                                         |       |

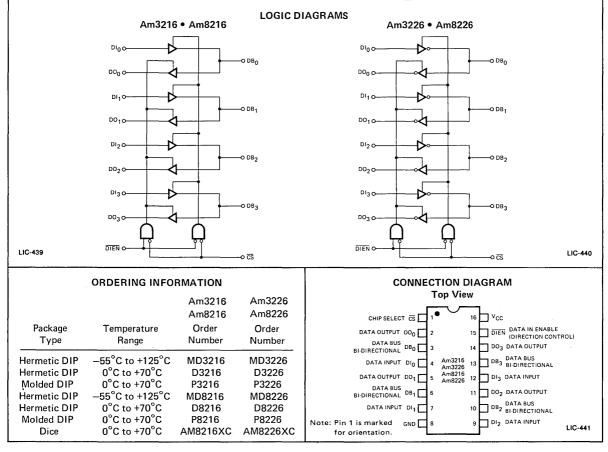

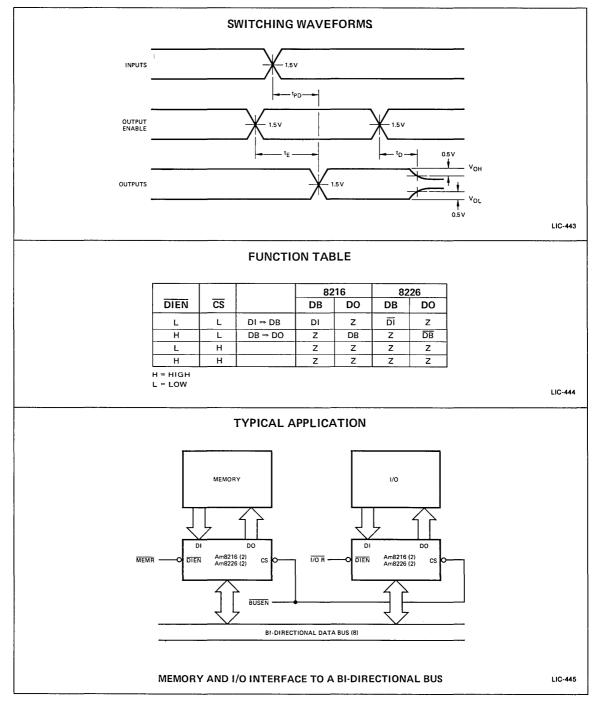

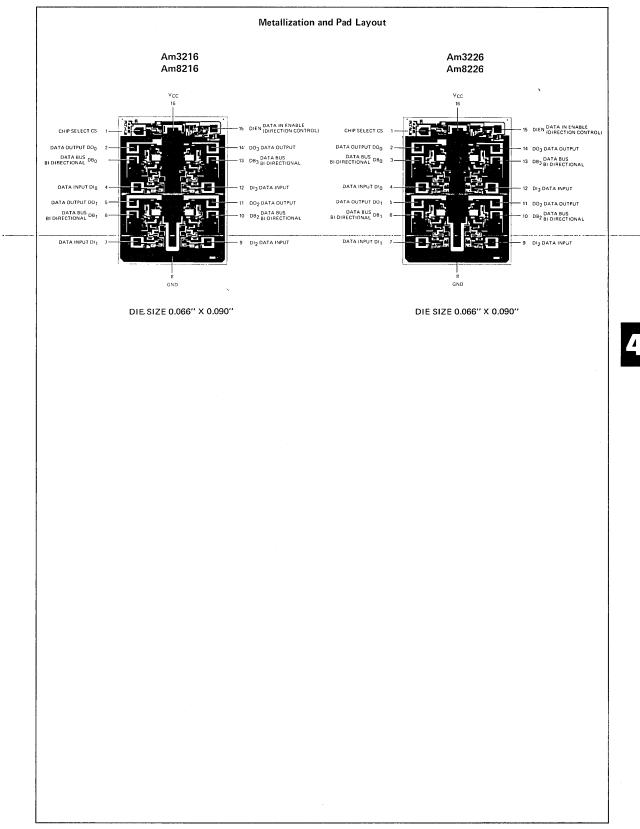

| Am3216         | 4-Bit Parallel Bidirectional Bus Driver                         |       |

| Am3226         | 4-Bit Parallel Bidirectional Bus Driver                         |       |

| Am324          | Quad Operational Amplifier                                      |       |

| Am324A         | Quad Operational Amplifier                                      |       |

| Am339          | Low Offset Voltage Quad Comparator                              |       |

| Am339A         | Low Offset Voltage Quad Comparator                              |       |

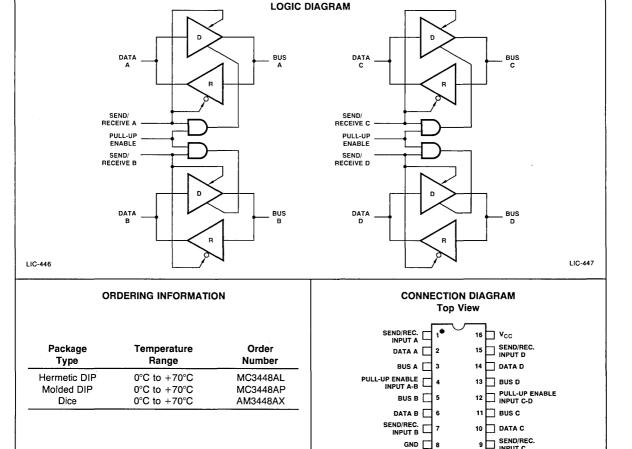

| Am3448A        | IEEE-488 Quad Bidirectional Transceiver                         |       |

| Am348          | Quad 741 Operational Amplifier                                  |       |

| Am349          | Quad 741 Operational Amplifier                                  |       |

| LF355          | JFET Input Operational Amplifier                                |       |

| LF355A         | JFET Input Operational Amplifier                                |       |

| LF356          | JFET Input Operational Amplifier                                |       |

| LF356A         | JFET Input Operational Amplifier                                |       |

| LF357          | JFET Input Operational Amplifier                                |       |

| LF357A         | JFET Input Operational Amplifier                                |       |

| Am3692         | Three-State Differential Line Drivers                           |       |

| L <b>F</b> 398 | Monolithic Sample and Hold Circuits                             |       |

| Am54LS240      | Octal Buffer; Inverting, Three-State                            |       |

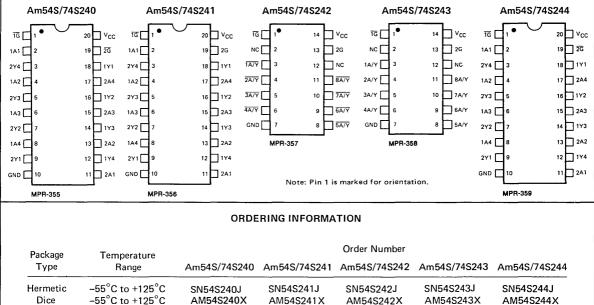

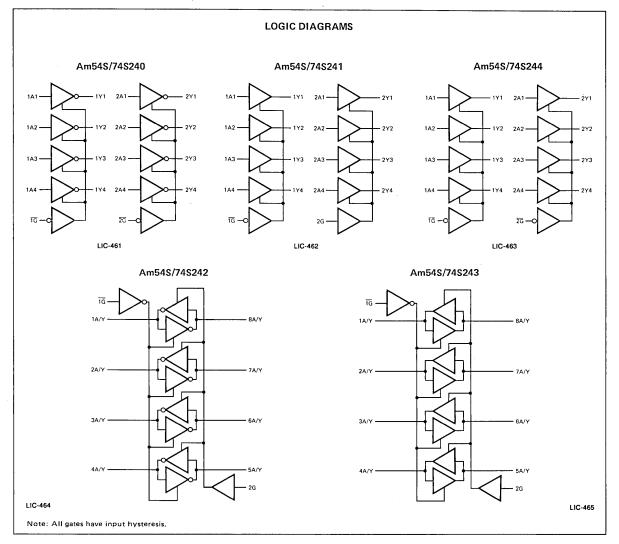

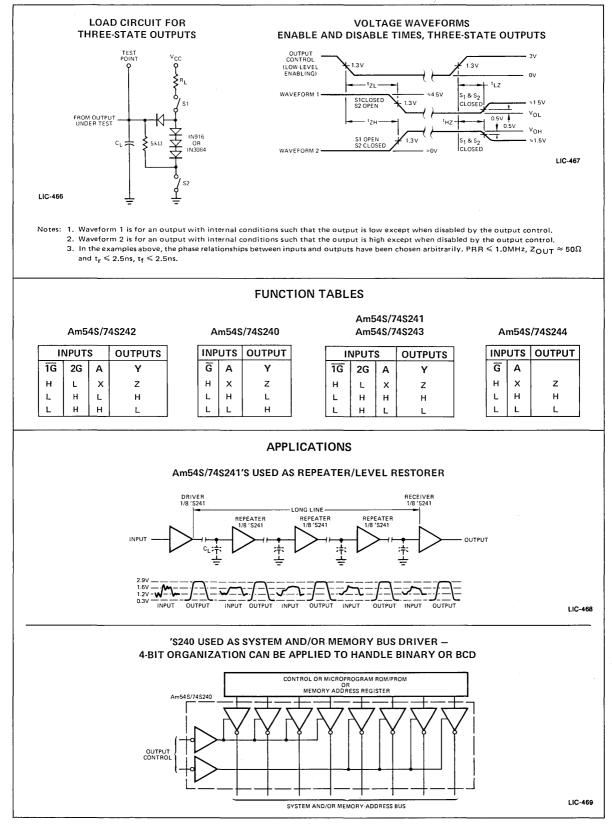

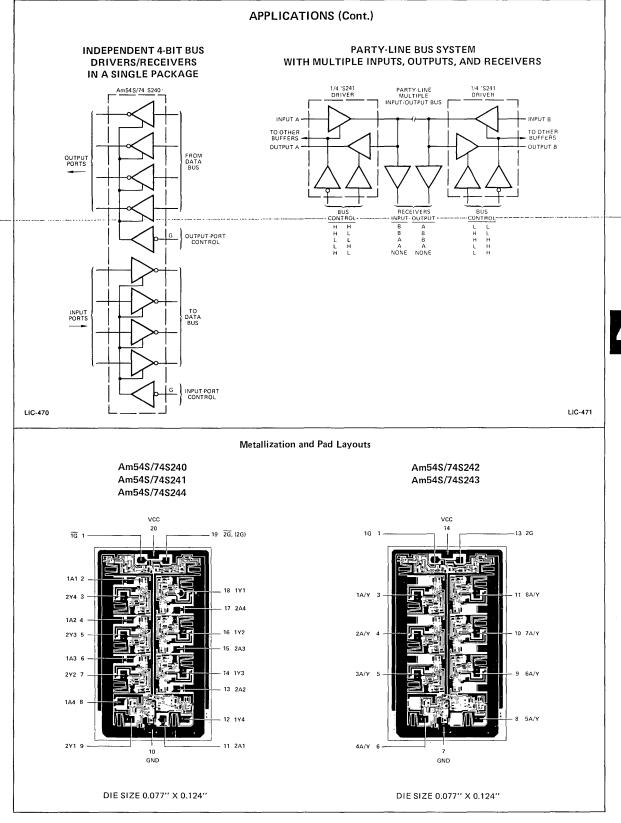

| Am54S240       | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs |       |

| Am54LS241      | Octal Buffer; Non-Inverting, Three-State                        |       |

| Am54S241       | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs |       |

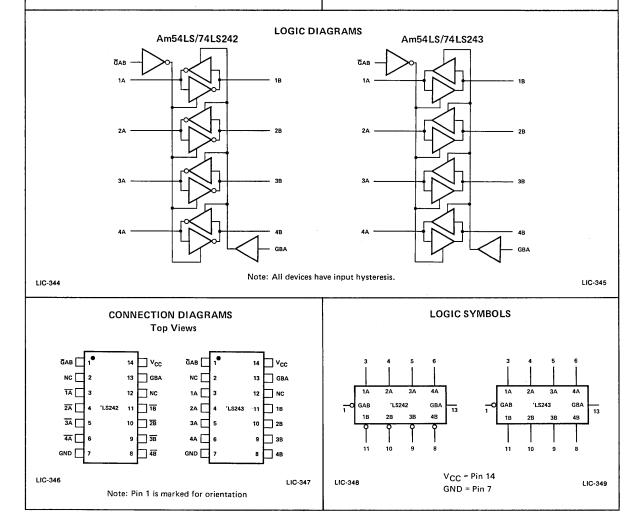

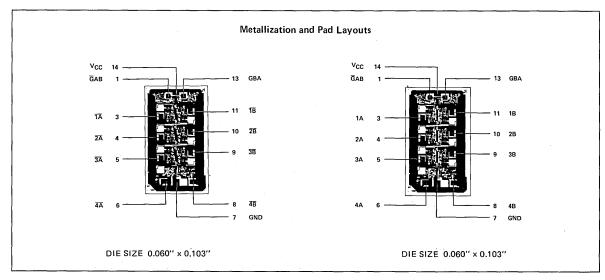

| Am54LS242      | Quad Three-State Bus Transceiver                                |       |

| Am54S242       | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs |       |

| Am54LS243      | Quad Three-State Bus Transceiver                                |       |

| Am54S243       | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs |       |

| Am54LS244      | Octal Buffer, Non-Inverting, Three-State                        |       |

| Am54S244       | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs |       |

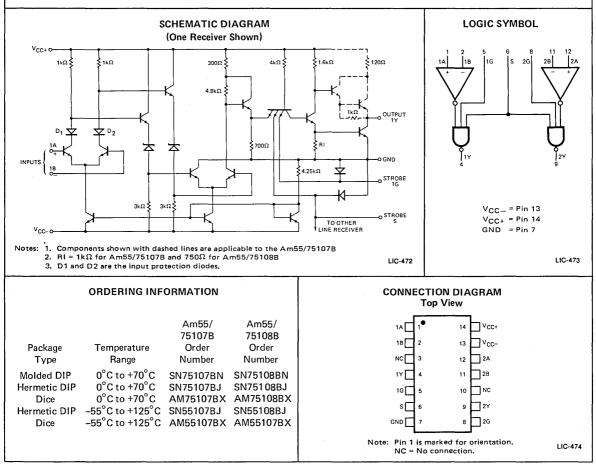

| Am55107B       | Dual Line Receiver                                              |       |

1

| Product   | Description                                                     | Page  |

|-----------|-----------------------------------------------------------------|-------|

| Am55108B  | Dual Line Receiver                                              | 4-147 |

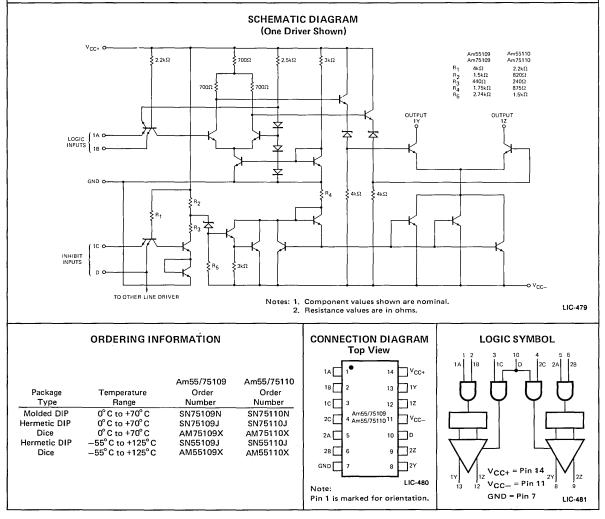

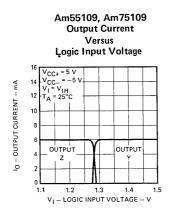

| Am55109   | Dual Line Receiver                                              |       |

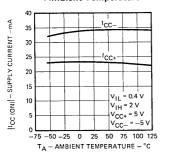

| Am55110   | Dual Line Driver                                                | 4-153 |

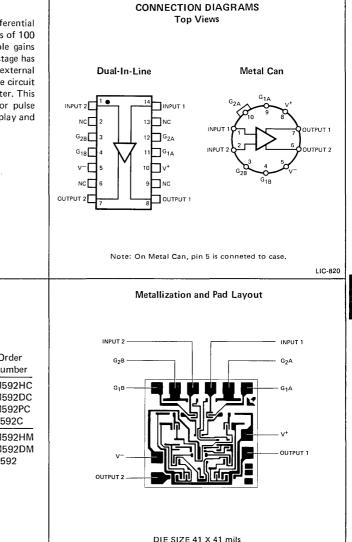

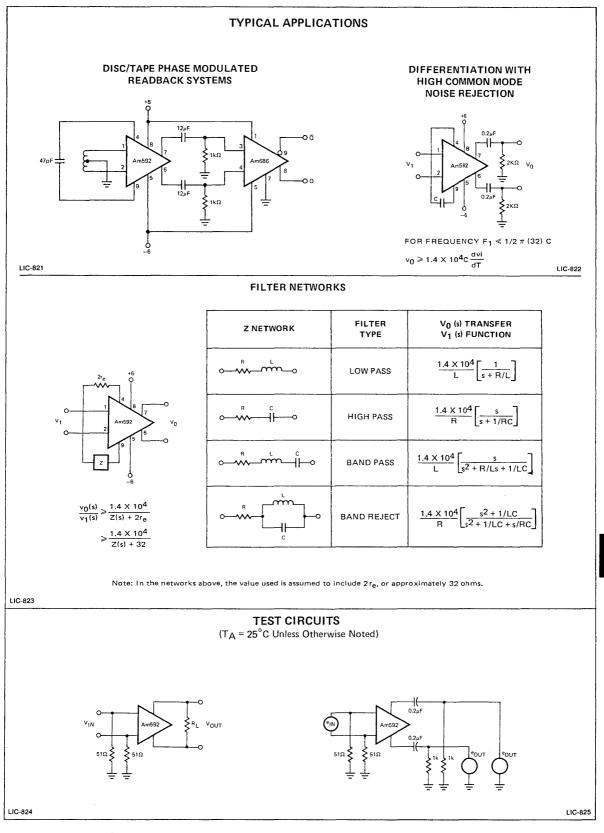

| Am592     | Differential Video Amplifier                                    | . 7-1 |

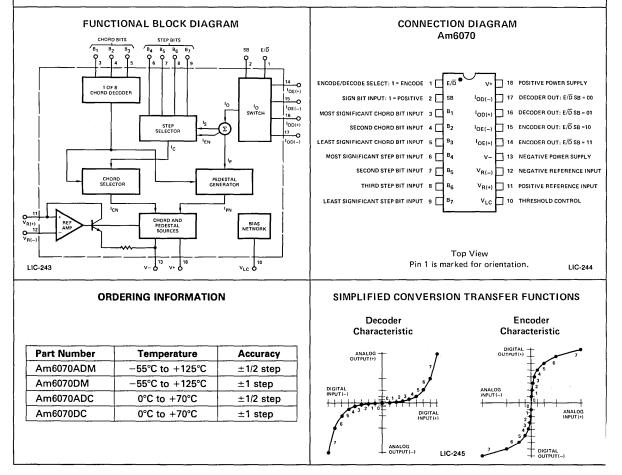

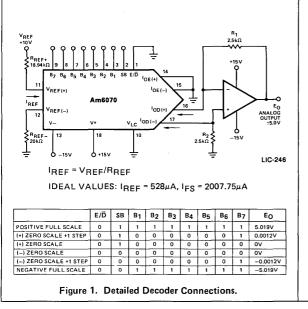

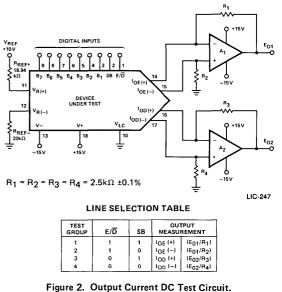

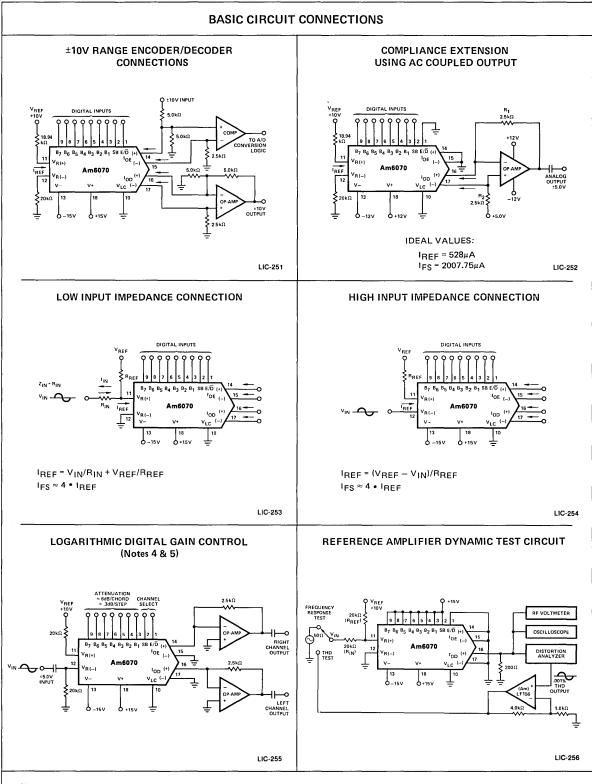

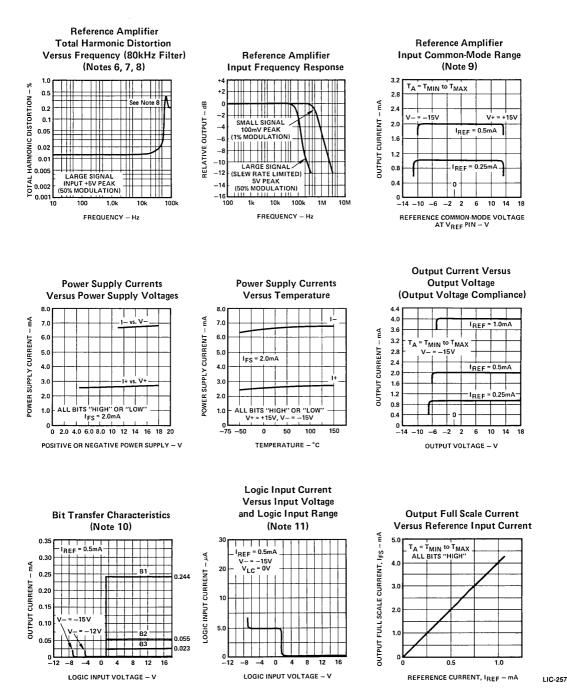

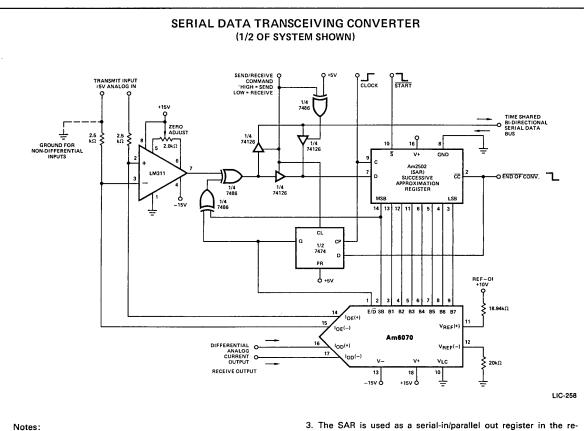

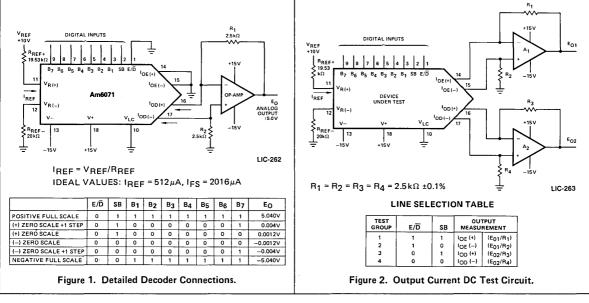

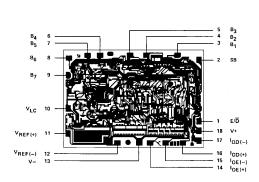

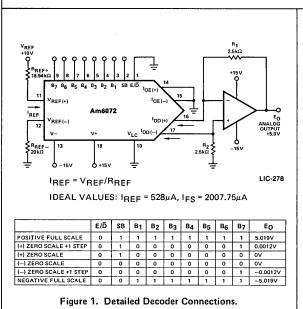

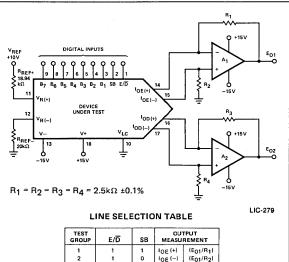

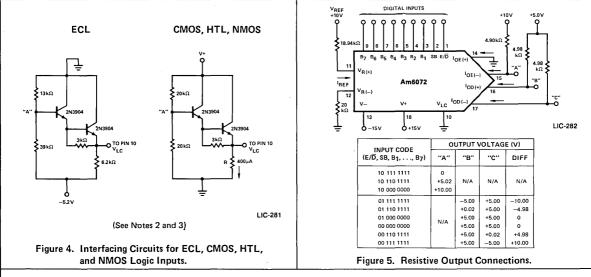

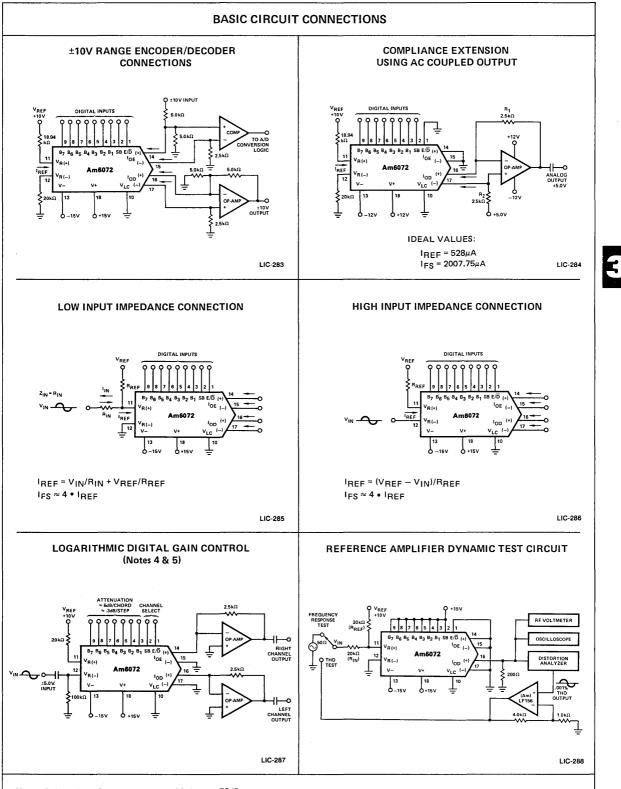

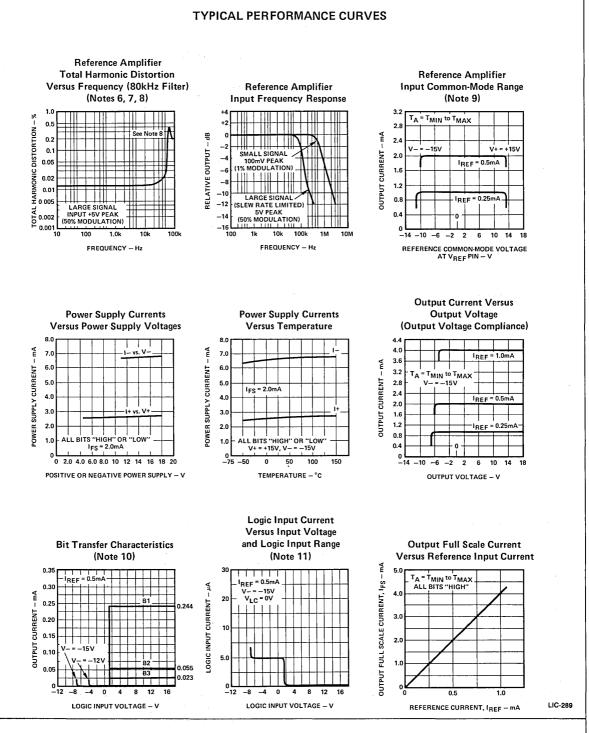

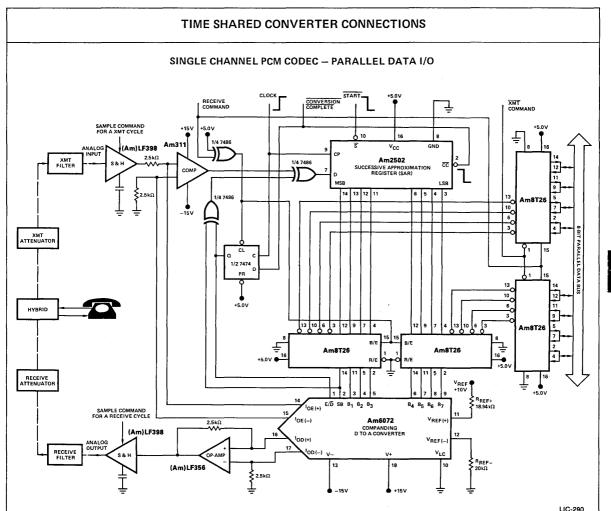

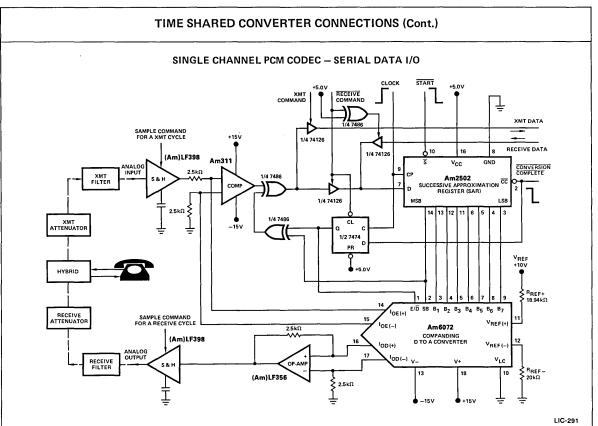

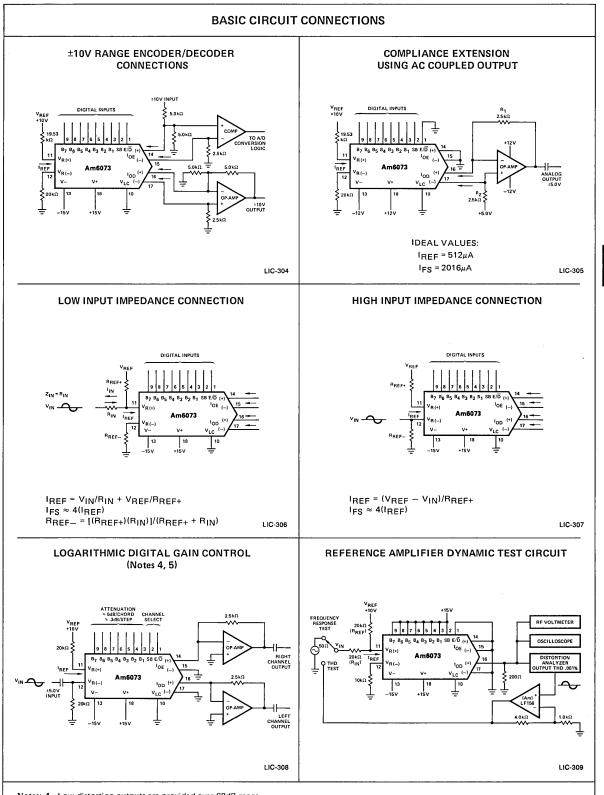

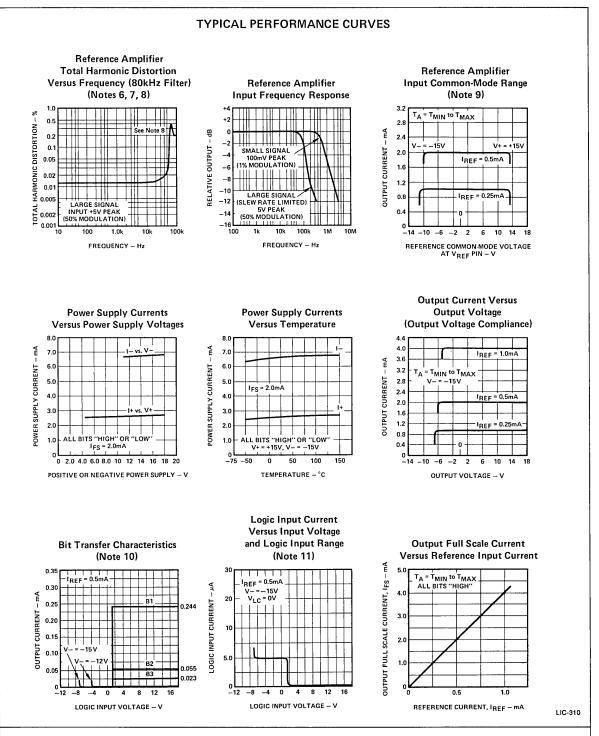

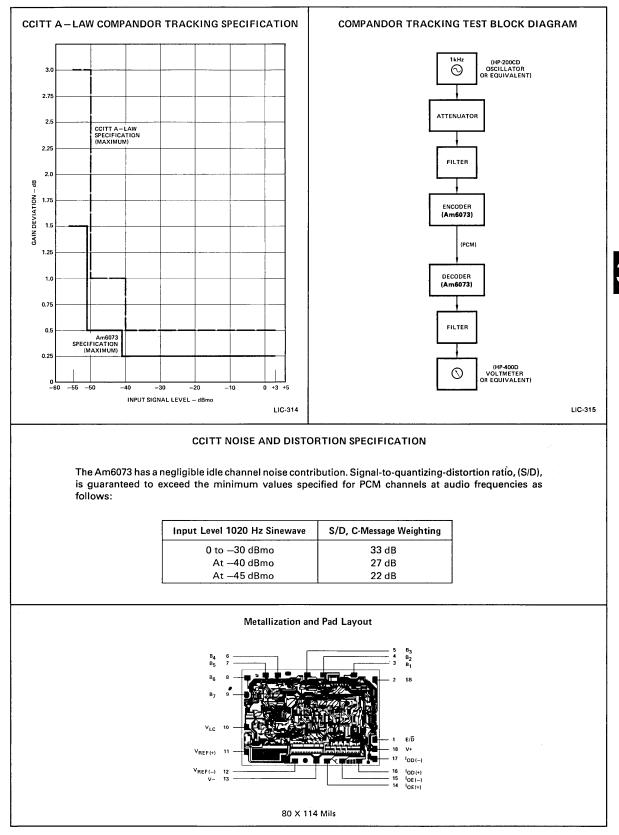

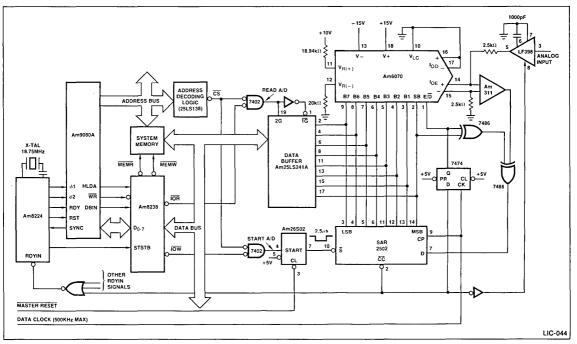

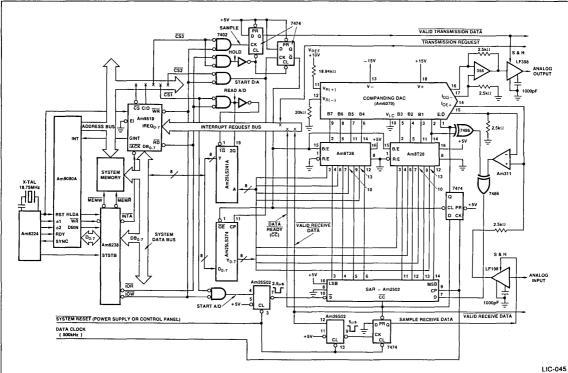

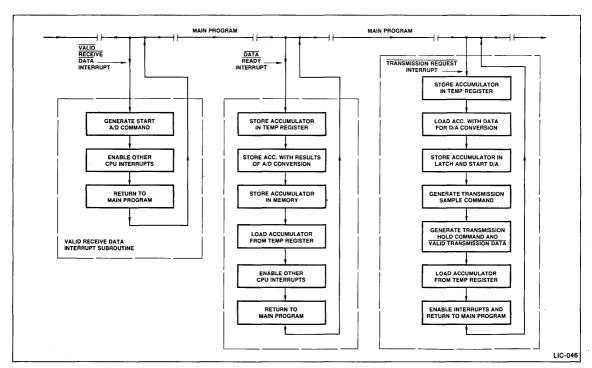

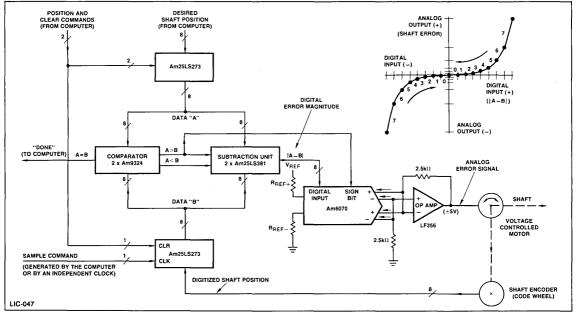

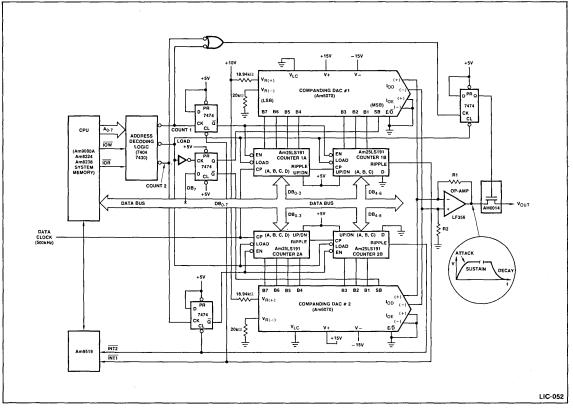

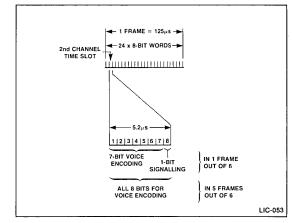

| Am6070    | Companding D-to-A Converter for Control Systems                 | 3-28  |

| Am6071    | Companding D-to-A Converter for Control Systems                 |       |

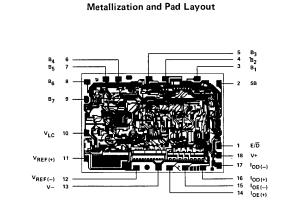

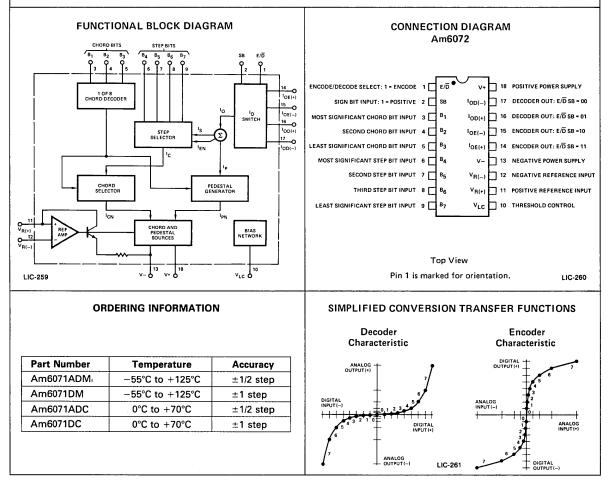

| Am6072    | Companding D-to-A Converter for PCM Communication Systems       |       |

| Am6073    | Companding D-to-A Converter for PCM Communication Systems       |       |

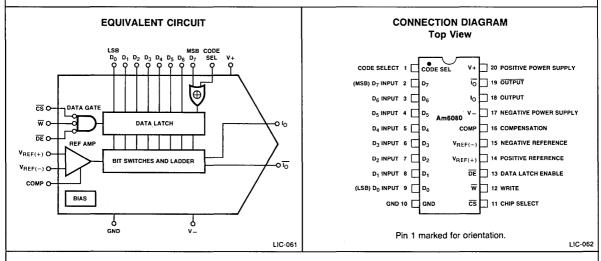

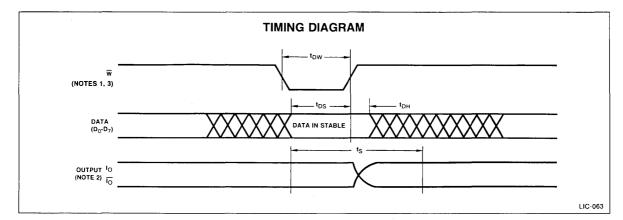

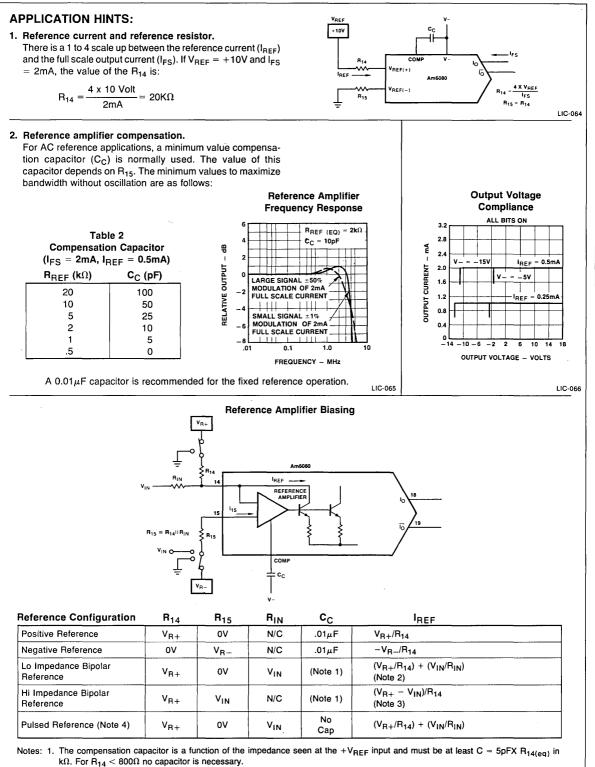

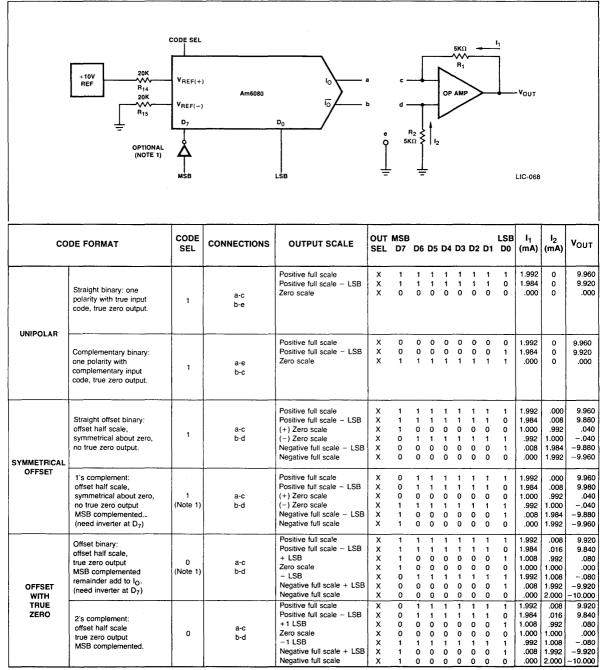

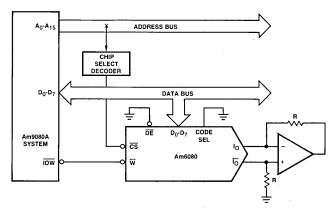

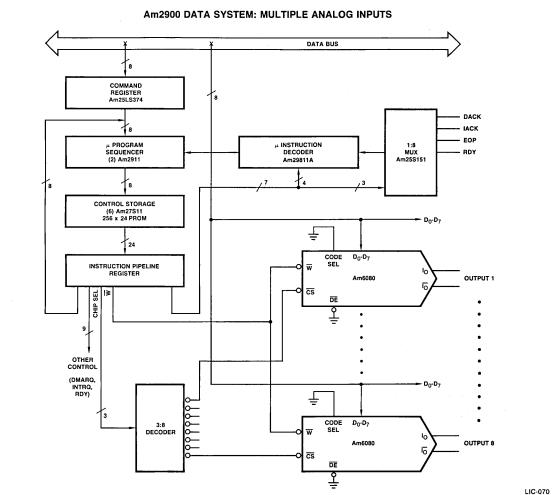

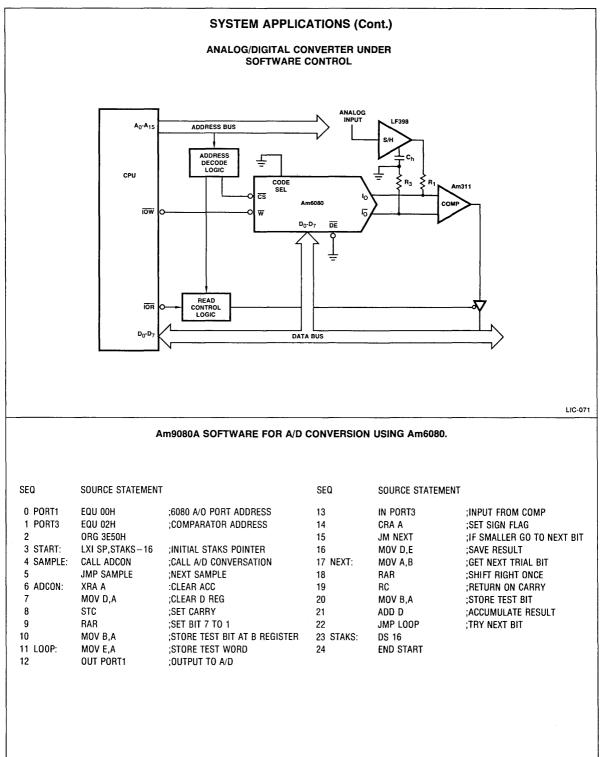

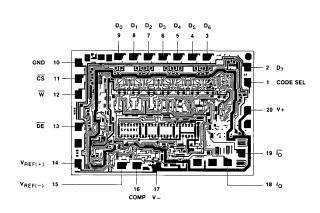

| Am6080    | Microprocessor System Compatible 8-Bit High-Speed               |       |

|           | Multiplying D/A Converter                                       | 3-76  |

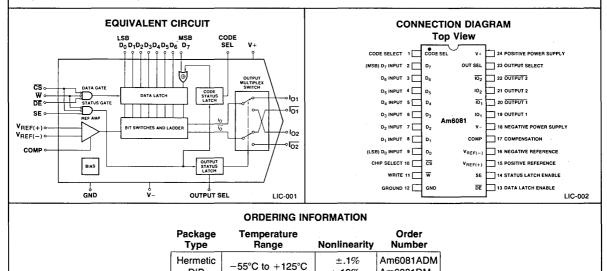

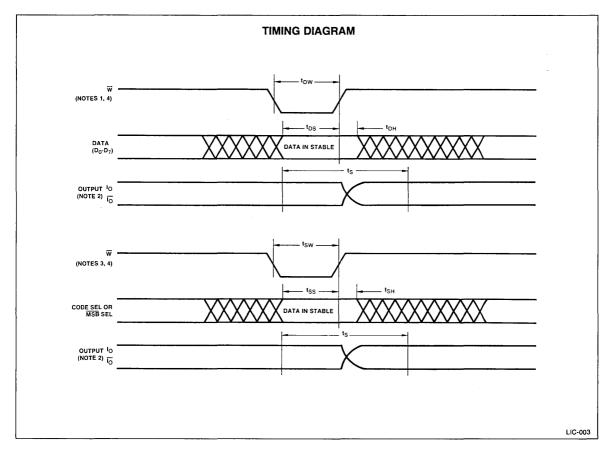

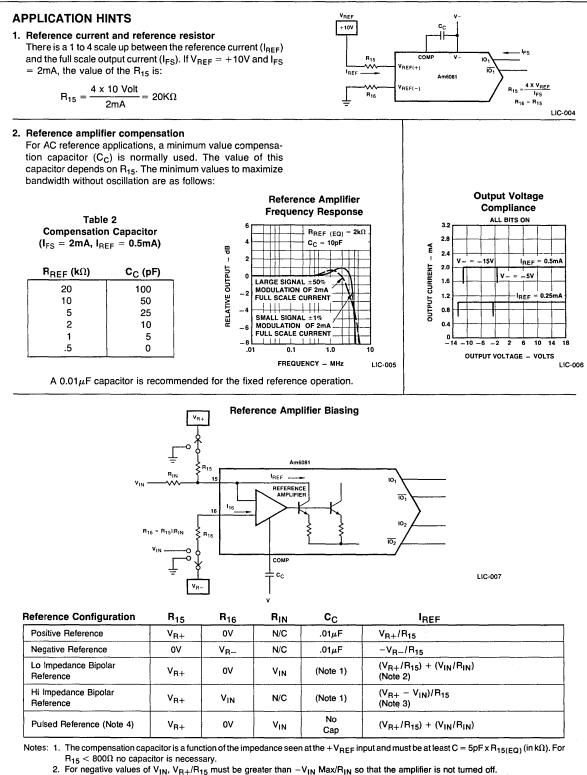

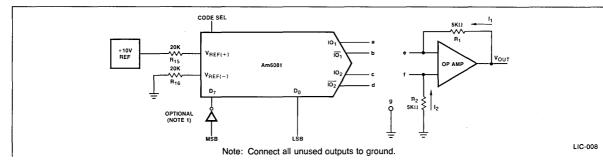

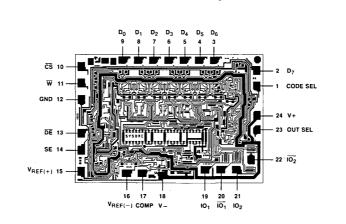

| Am6081    | Microprocessor System Compatible 8-Bit High-Speed               |       |

|           | Multiplying D/A Converter                                       | 3-84  |

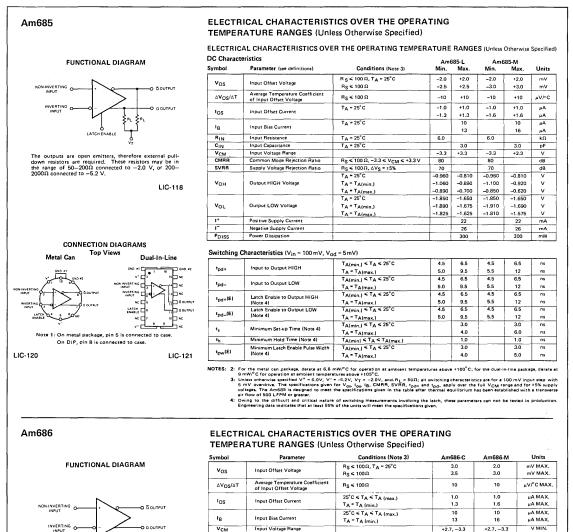

| Am685     | Voltage Comparator                                              |       |

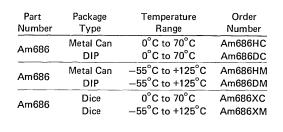

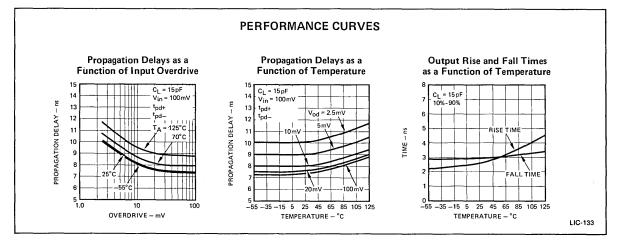

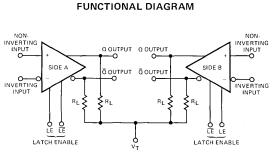

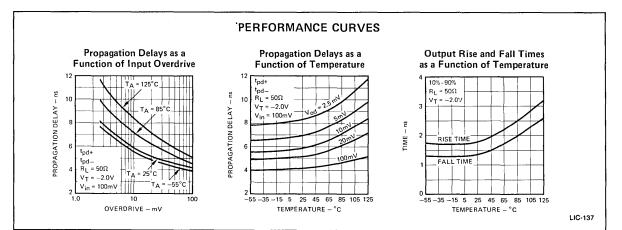

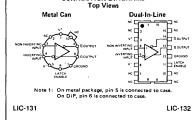

| Am686     | Voltage Comparator                                              | 2-27  |

| Am687     | Dual Voltage Comparator                                         |       |

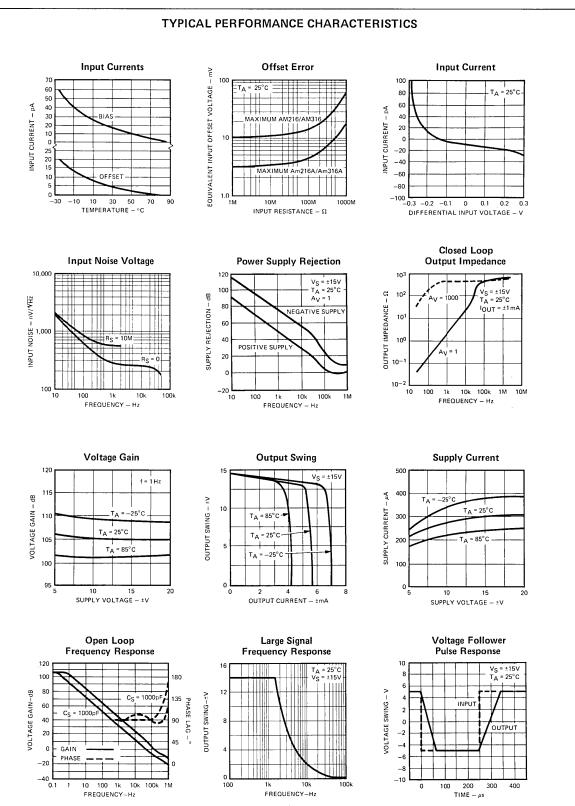

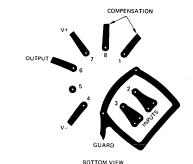

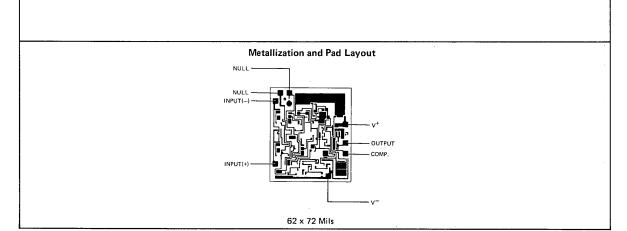

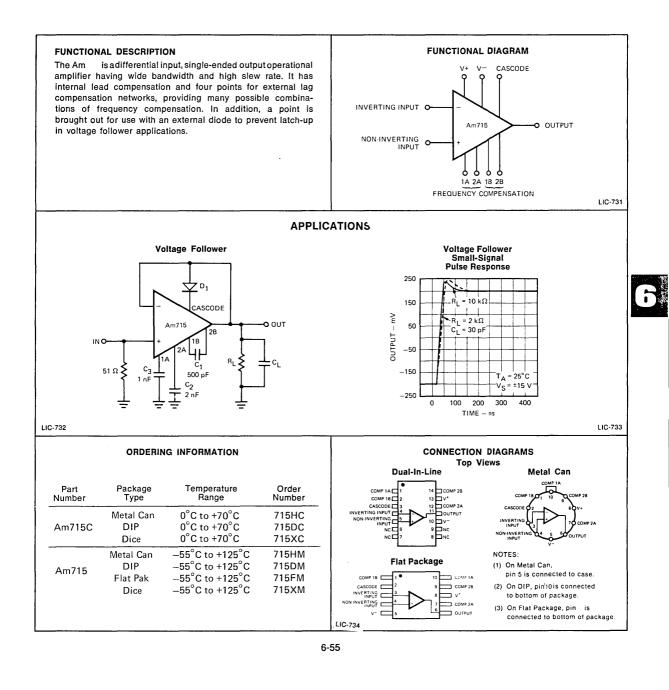

| Am715     | High-Speed Operational Amplifier                                | 6-55  |

| Am715C    | High-Speed Operational Amplifier                                |       |

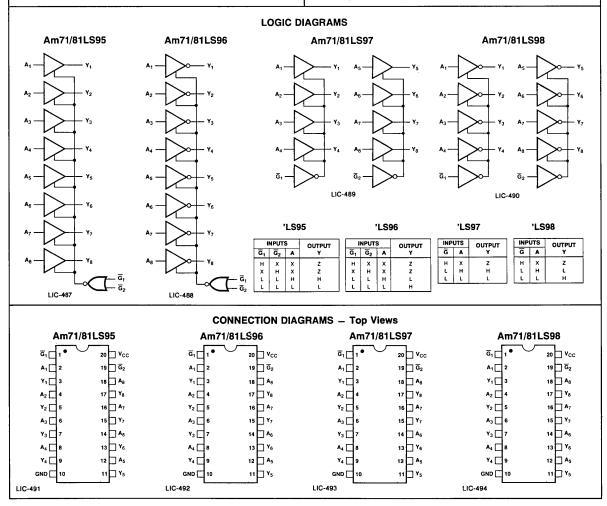

| Am71LS95  | Three-State Octal Buffers                                       |       |

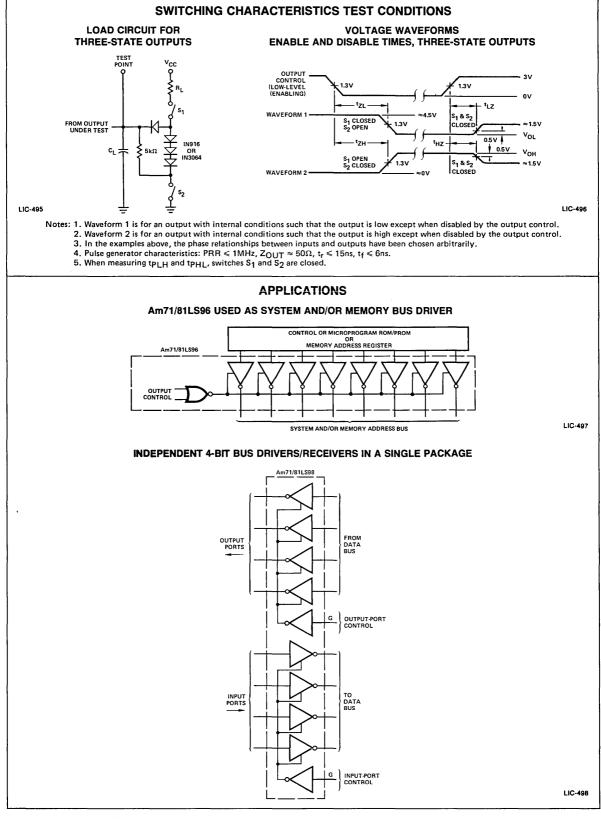

| Am71LS96  | Three-State Octal Buffers                                       | 4-159 |

| Am71LS97  | Three-State Octal Buffers                                       | 4-159 |

| Am71LS98  | Three-State Octal Buffers                                       | 4-159 |

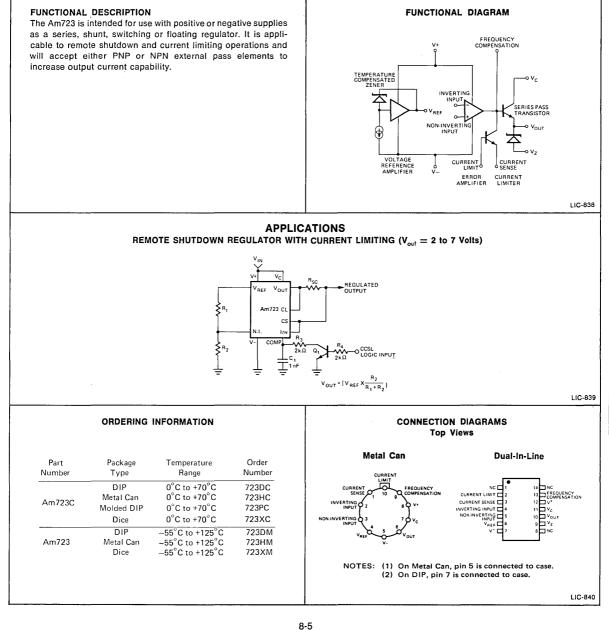

| Am723     | Voltage Regulator                                               | 8-5   |

| Am723C    | Voltage Regulator                                               | 8-5   |

| Am725     | Instrumentation Operational Amplifier                           |       |

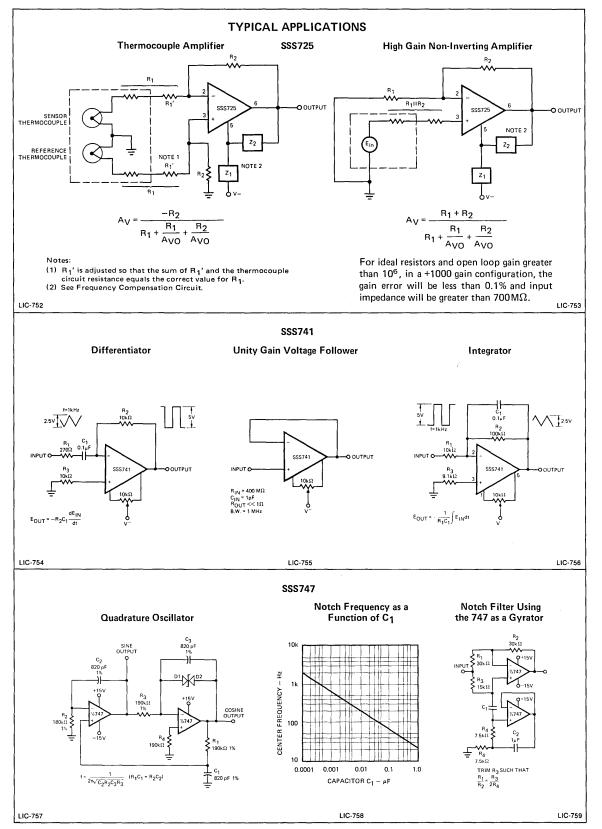

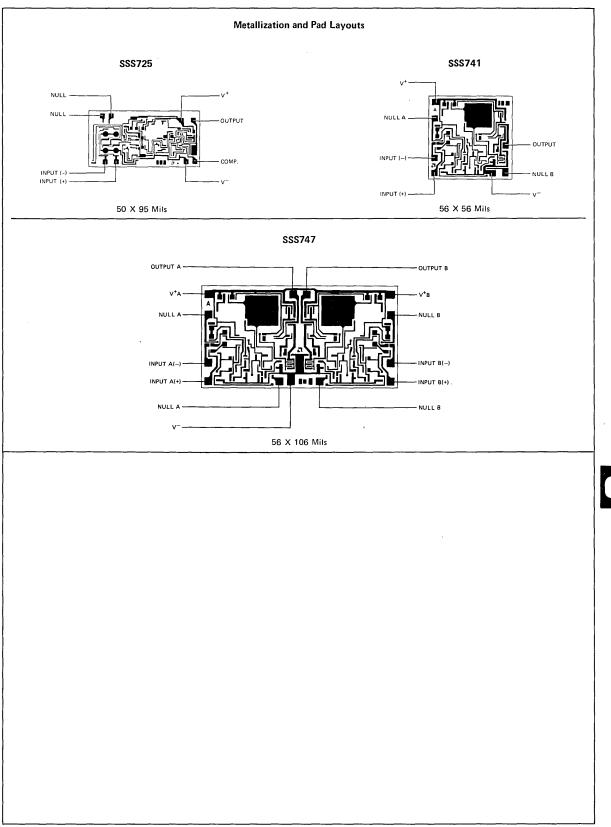

| SSS725    | High-Performance Operational Amplifier                          | 6-64  |

| Am725C    | Instrumentation Operational Amplifier                           | 6-59  |

| Am7303B   | Octal Three-State Inverting Bidirectional Transceiver           |       |

| Am7304B   | Octal Three-State Bidirectional Transceiver                     |       |

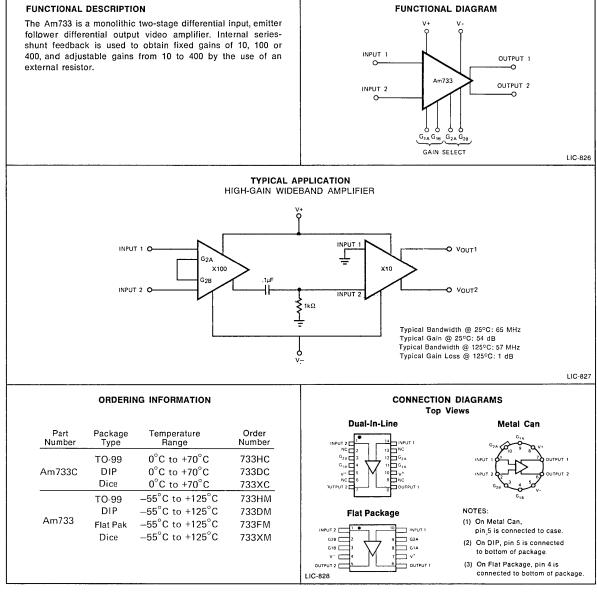

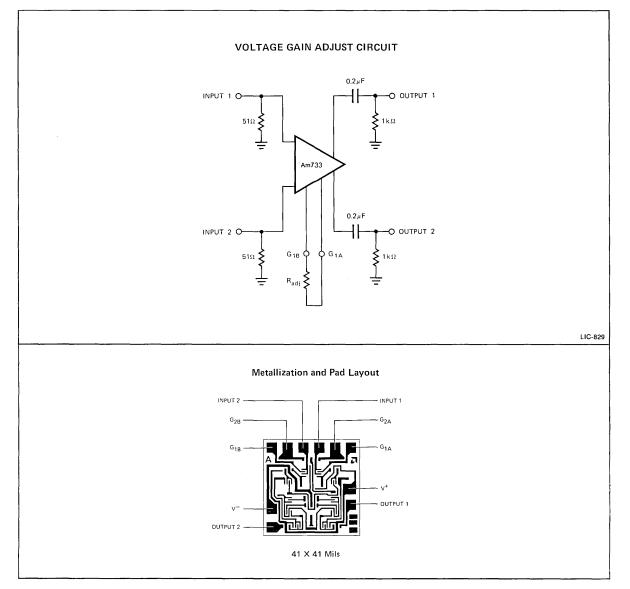

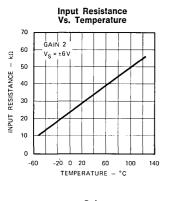

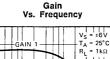

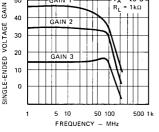

| Am733     | Differential Video Amplifier                                    | 7-4   |

| Am733C    | Differential Video Amplifier                                    | 7-4   |

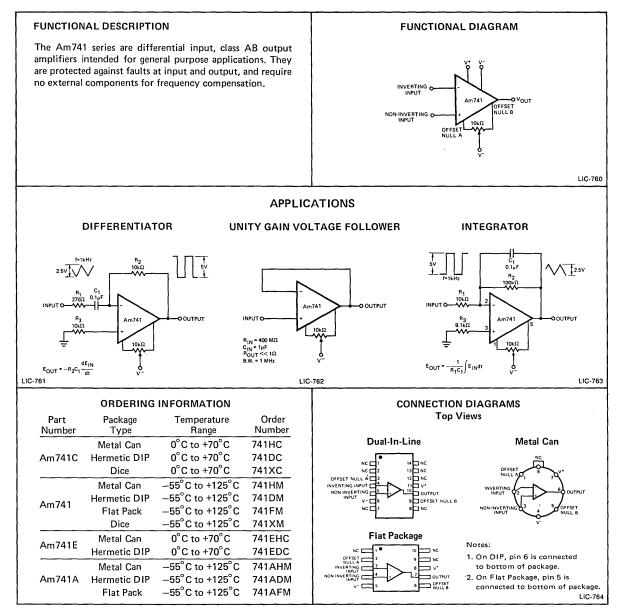

| Am741     | Frequency-Compensated Operational Amplifier                     | 6-70  |

| SSS741    | Frequency-Compensated Operational Amplifier                     | 6-64  |

| Am741A    | Frequency-Compensated Operational Amplifier                     | 6-70  |

| Am74LS240 | Octal Buffer; Inverting, Three-State                            | 4-13  |

| Am74S240  | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs | 4-142 |

| Am74LS241 | Octal Buffer; Non-Inverting, Three-State                        | 4-17  |

| Am74S241  | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs | 4-142 |

| Am74LS242 | Quad Three-State Bus Transceiver                                | 4-21  |

| Am74S242  | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs | 4-142 |

| Am74LS243 | Quad Three-State Bus Transceiver                                | 4-21  |

| Am74S243  | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs | 4-142 |

| Am74LS244 | Octal Buffer, Non-Inverting, Three-State                        | 4-17  |

| Am74S244  | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs |       |

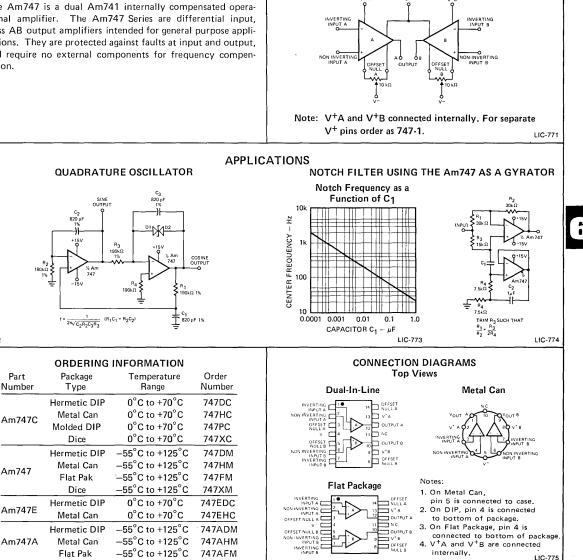

| Am747     | Dual Frequency-Compensated Operational Amplifier                | 6-77  |

| SSS747    | Dual Frequency-Compensated Operational Amplifier                | 6-64  |

| Am747A    | Dual Frequency-Compensated Operational Amplifier                |       |

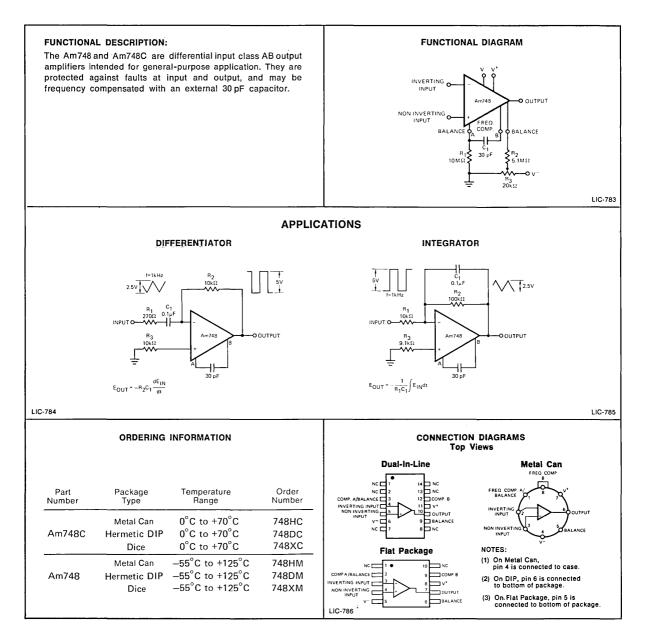

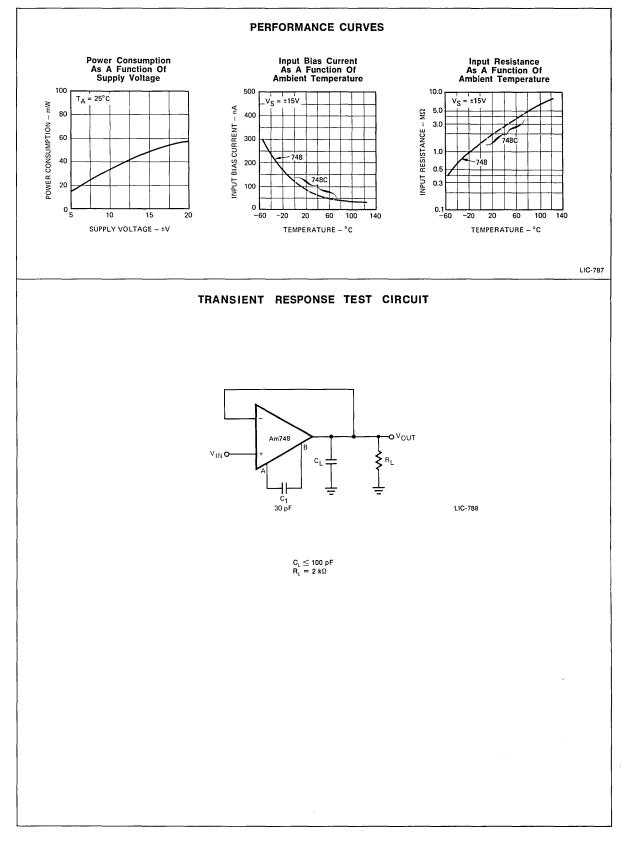

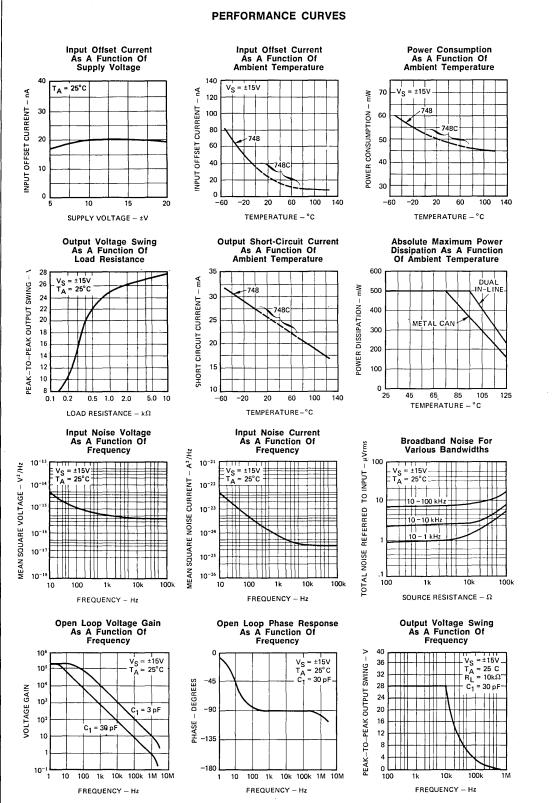

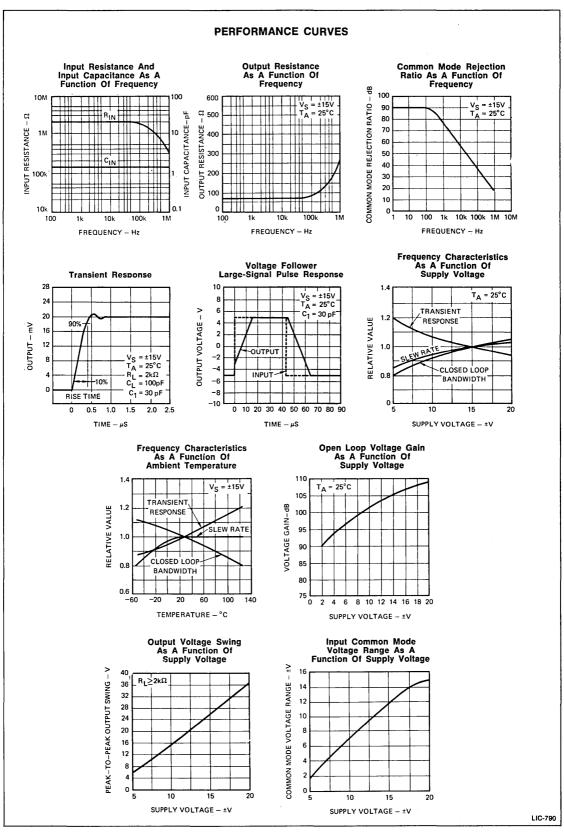

| Am748     | Operational Amplifier                                           | 6-84  |

| Am748C    | Operational Amplifier                                           | 6-84  |

| Am75107B  | Dual Line Receiver                                              | 4-147 |

| Am75108B  | Dual Line Receiver                                              | 4-147 |

| Am75109   | Dual Line Receiver                                              | 4-153 |

| Product  | Description                                           | Page  |

|----------|-------------------------------------------------------|-------|

| Am75110  | Dual Line Driver                                      | 4-153 |

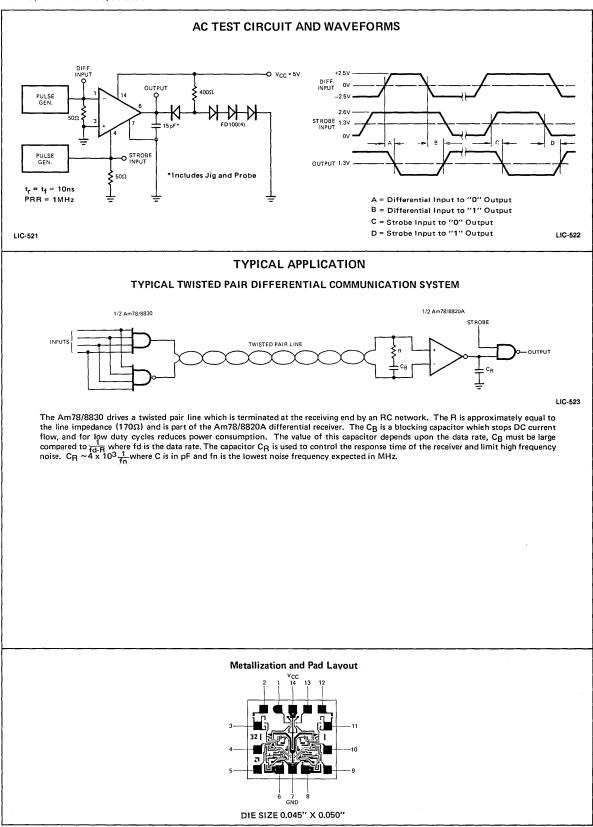

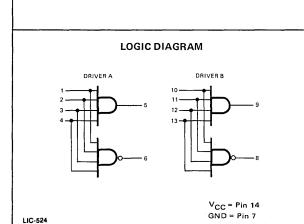

| Am7820   | Dual Differential Line Receiver                       | 4-173 |

| Am7820A  | Dual Differential Line Receiver                       | 4-173 |

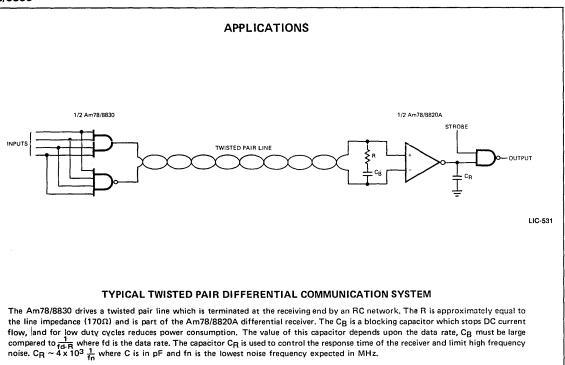

| Am7830   | Dual Differential Line Driver                         | 4-178 |

| Am7831   | Three-State Line Driver                               | 4-182 |

| Am7832   | Three-State Line Driver                               | 4-182 |

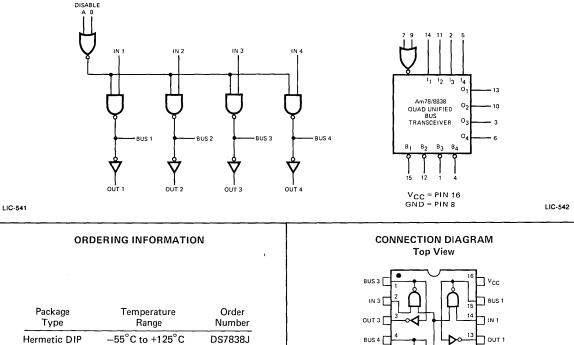

| Am7838   | Quad Unified Bus Transceiver                          | 4-188 |

| Am81LS95 | Three-State Octal Buffers                             | 4-159 |

| Am81LS96 | Three-State Octal Buffers                             | 4-159 |

| Am81LS97 | Three-State Octal Buffers                             | 4-159 |

| Am81LS98 | Three-State Octal Buffers                             | 4-159 |

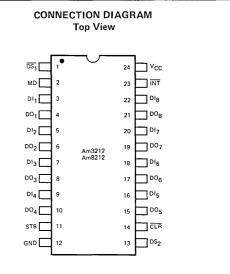

| Am8212   | 8-Bit Input-Output Port                               | 4-125 |

| Am8216   | 4-Bit Parallel Bidirectional Bus Driver               | 4-132 |

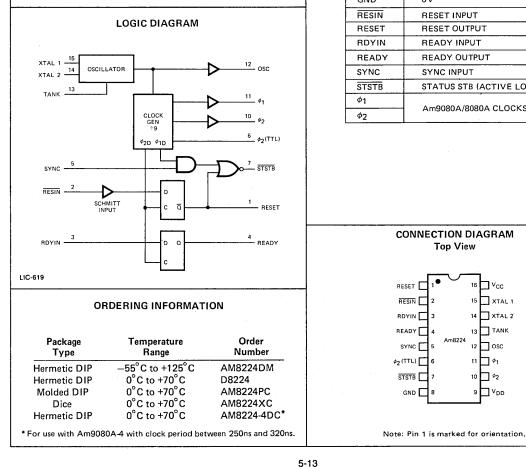

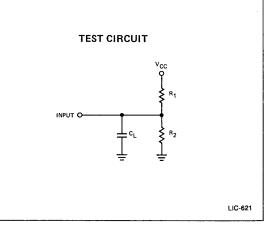

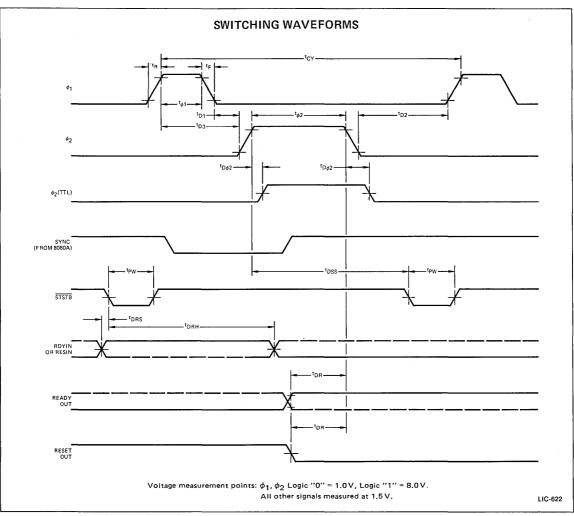

| Am8224   | Clock Generator and Driver                            | 5-13  |

| Am8226   | 4-Bit Parallel Bidirectional Bus                      | 4-132 |

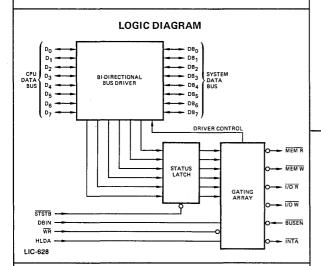

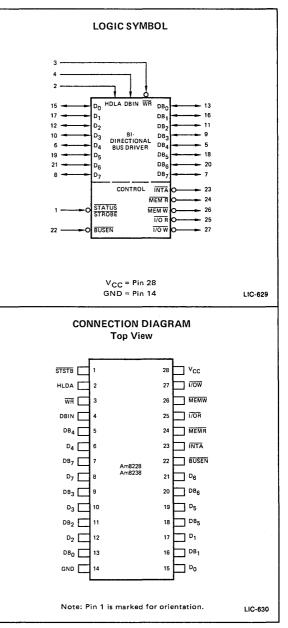

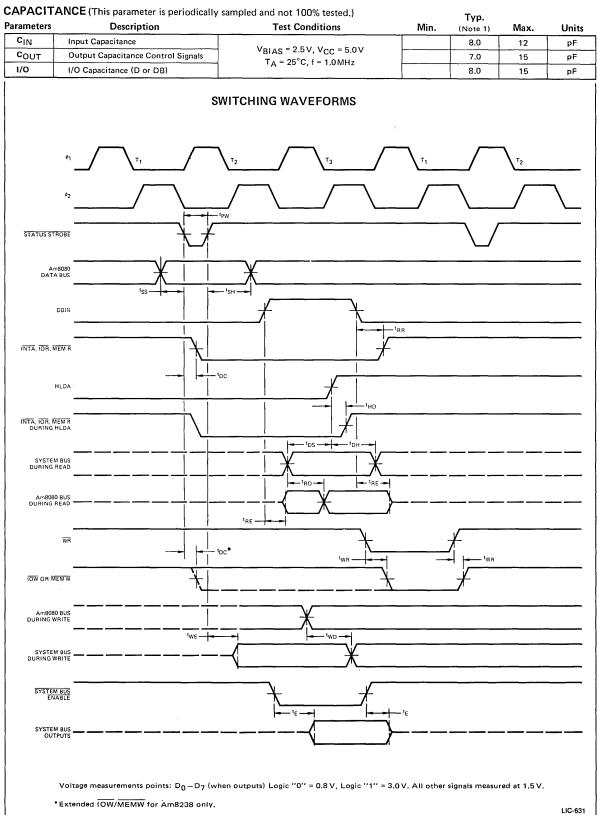

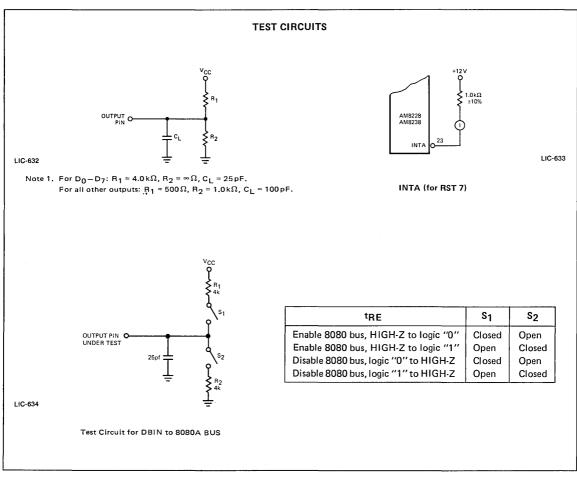

| Am8228   | System Controller and Bus Driver                      |       |

| Am8238   | System Controller and Bus Driver                      |       |

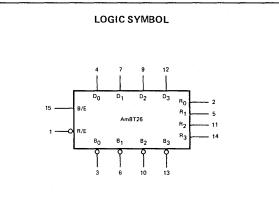

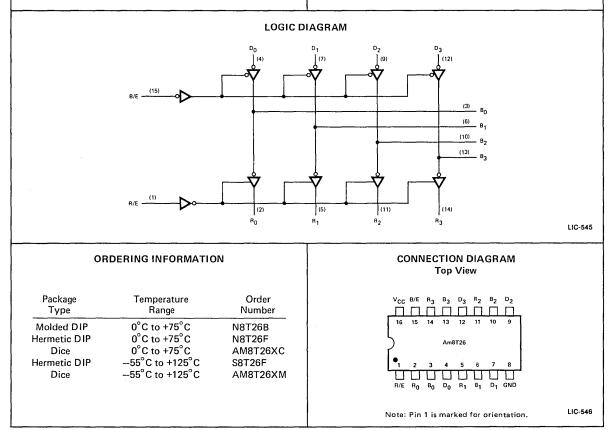

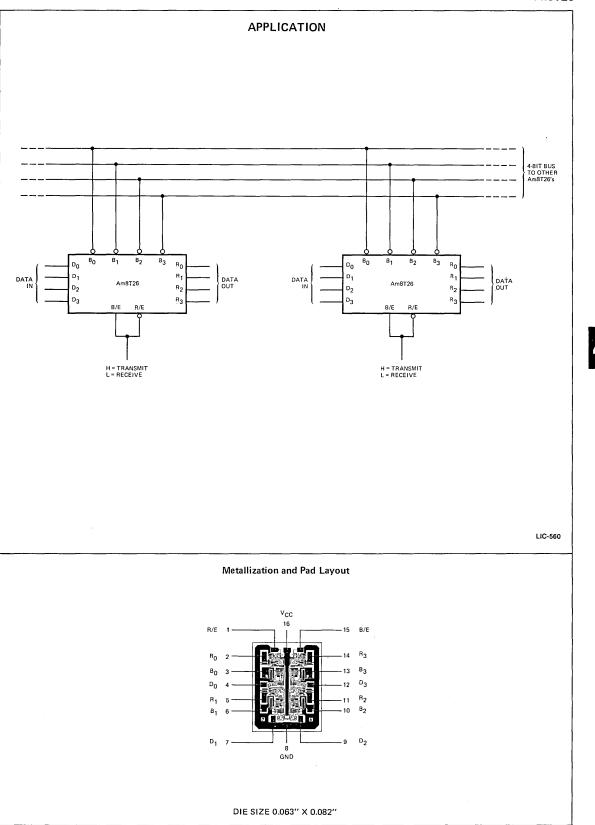

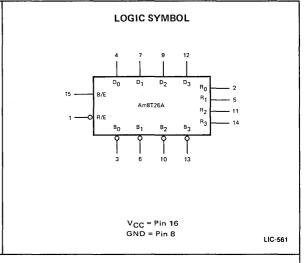

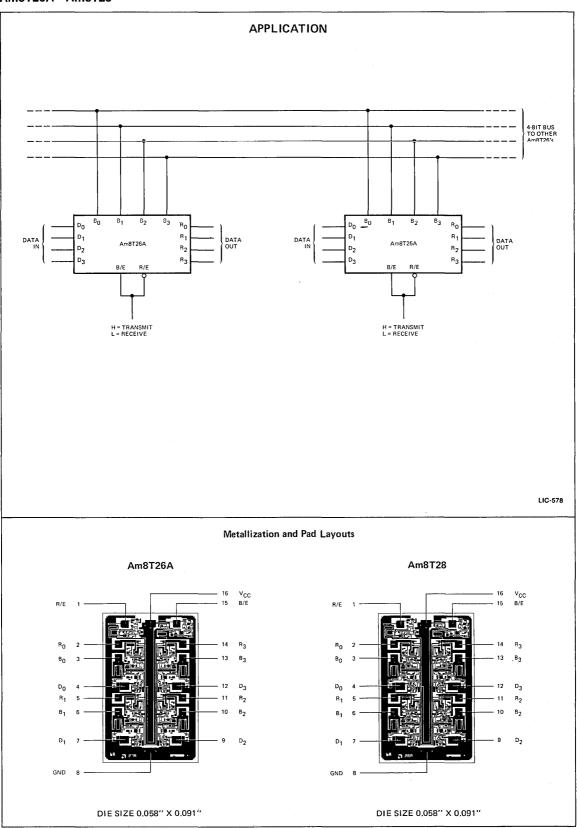

| Am8T26   | Schottky Three-State Quad Bus Driver/Receiver         | 4-190 |

| Am8T26A  | Schottky Three-State Quad Bus Driver/Receiver         | 4-195 |

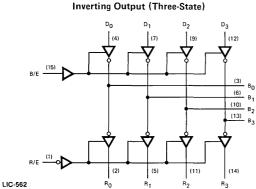

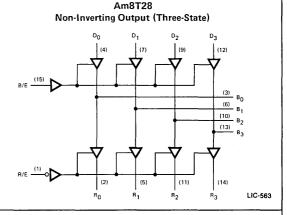

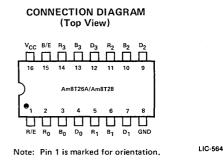

| Am8T28   | Schottky Three-State Quad Bus Driver/Receiver         |       |

| Am8303B  | Octal Three-State Inverting Bidirectional Transceiver |       |

| Am8304B  | Octal Three-State Bidirectional Transceiver           | 4-168 |

| Am8820   | Dual Differential Line Receiver                       | 4-173 |

| Am8820A  | Dual Differential Line Receiver                       | 4-173 |

| Am8830   | Dual Differential Line Driver                         |       |

| Am8831   | Three-State Line Driver                               | 4-182 |

| Am8832   | Three-State Line Driver                               |       |

| Am8838   | Quad Unified Bus Transceiver                          | 4-188 |

| Am9614   | Differential Line Driver                              |       |

| Am9615   | Dual Differential Line Receiver                       |       |

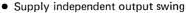

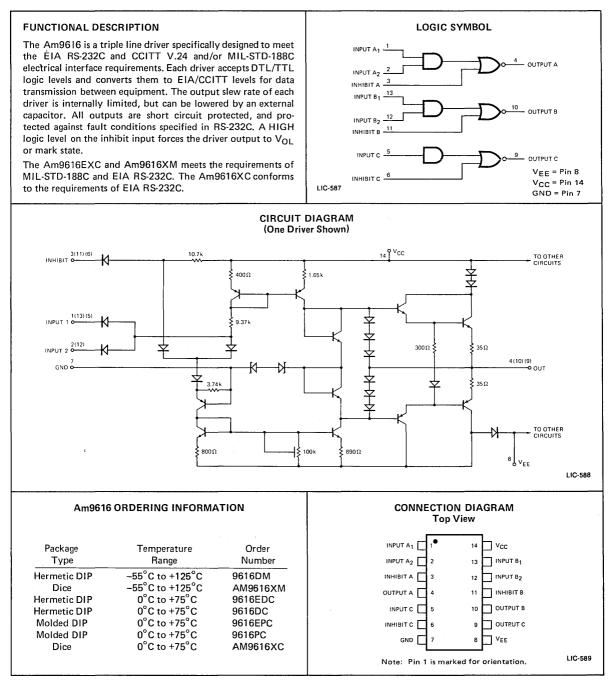

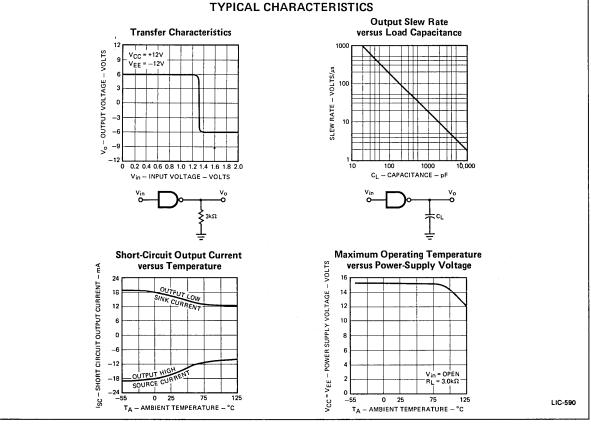

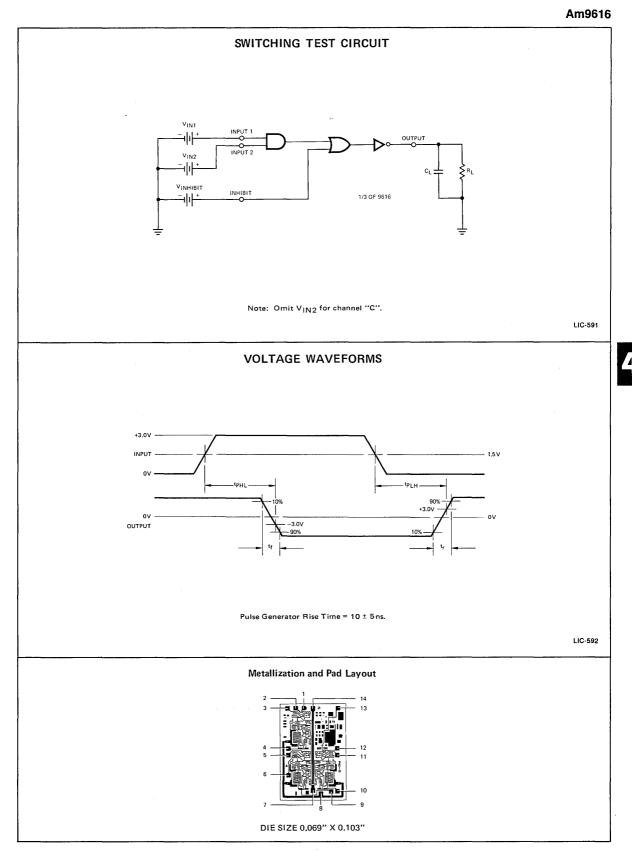

| Am9616   | Triple EIA RS-232C/MIL-STD-188C Line Driver           | 4-205 |

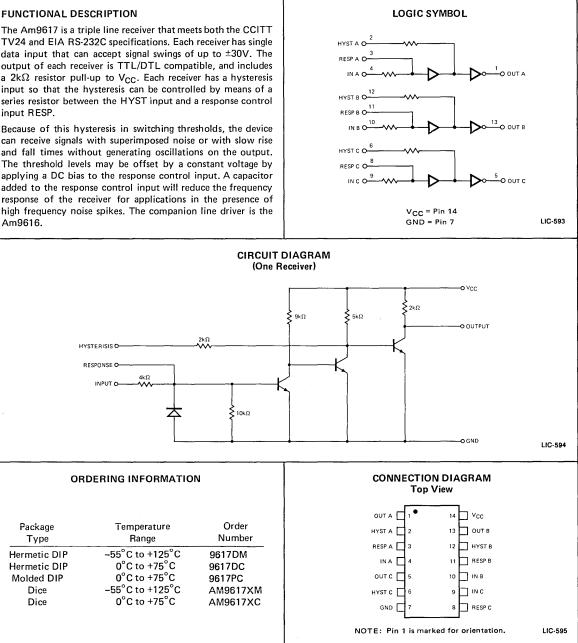

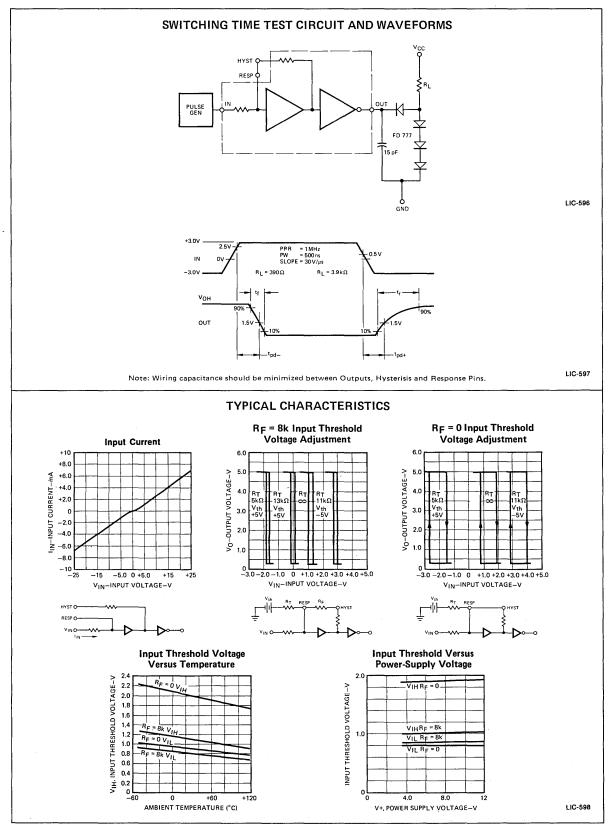

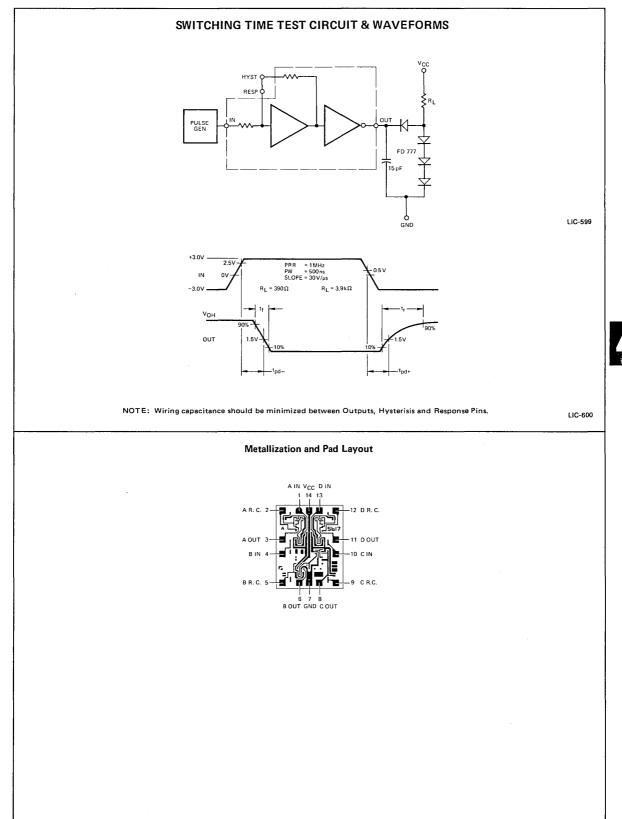

| Am9617   | RS-232C Line Receiver                                 | 4-209 |

# FUNCTIONAL INDEX

# Section 1

| Numeric Index            |      |

|--------------------------|------|

| Functional Index         |      |

| Selection Guides         | 1-10 |

| Industry Cross-Reference | 1-14 |

| Dice Policy              | 1-22 |

| Ordering Information     | 1-23 |

| MIL-M-38510/MIL-STD-883  | 1-26 |

# Comparators – Section II

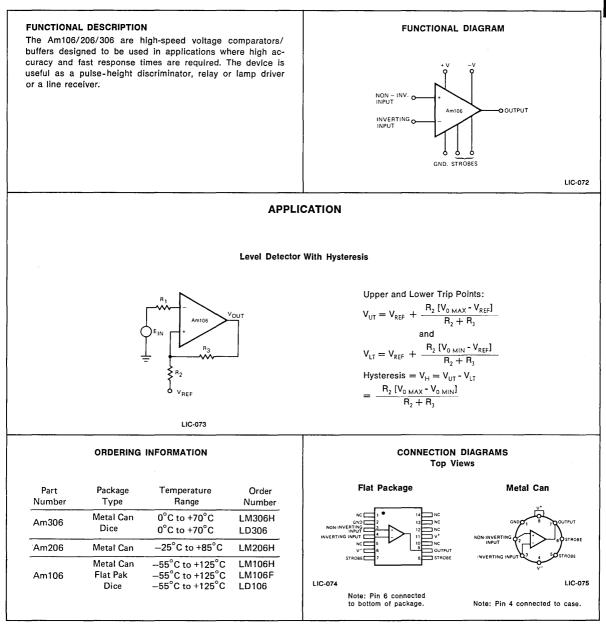

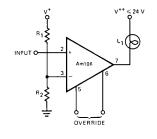

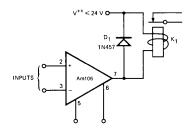

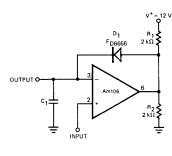

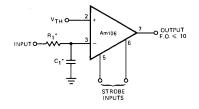

| Am106/206/306    | Voltage Comparator/Buffer          | 2-1  |

|------------------|------------------------------------|------|

| Am111/211/311    | Precision Voltage Comparator       |      |

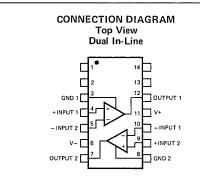

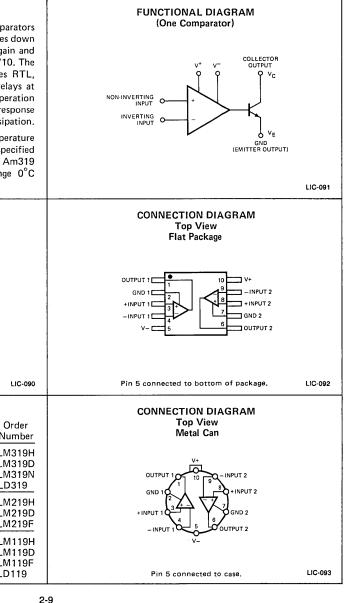

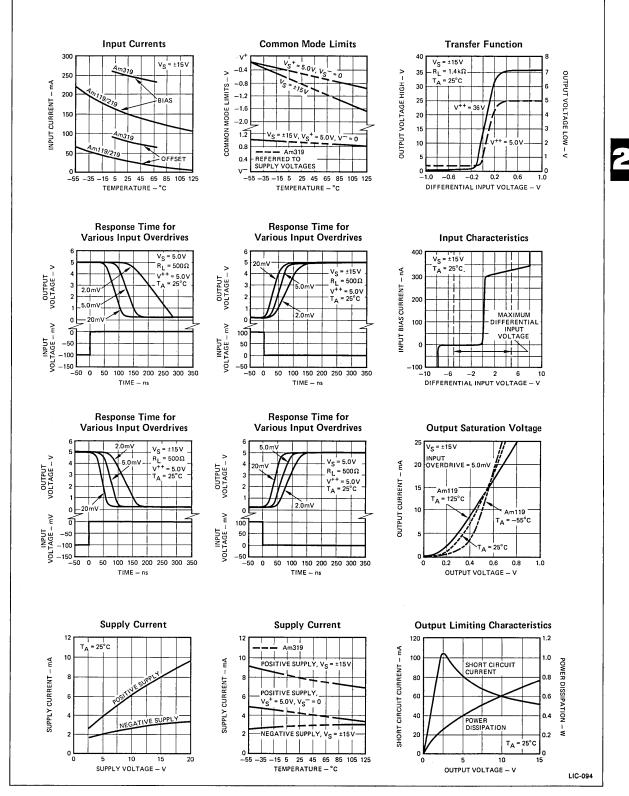

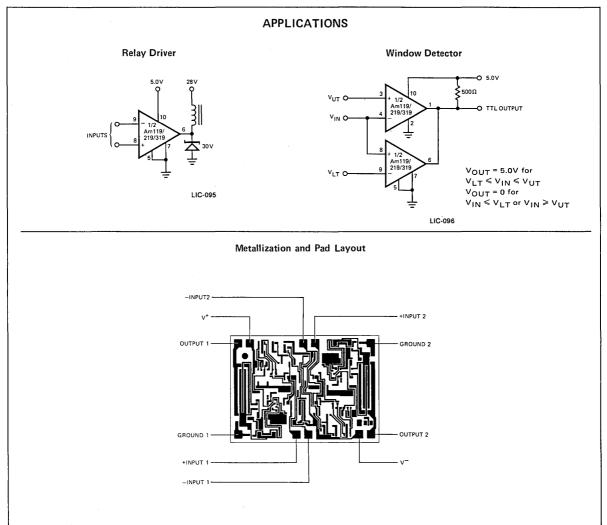

| Am119/219/319    | Dual Voltage Comparator            | 2-9  |

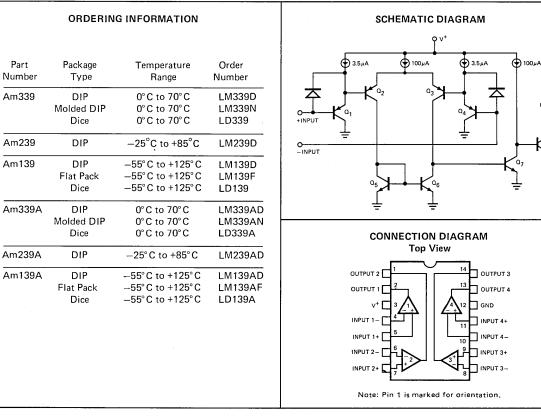

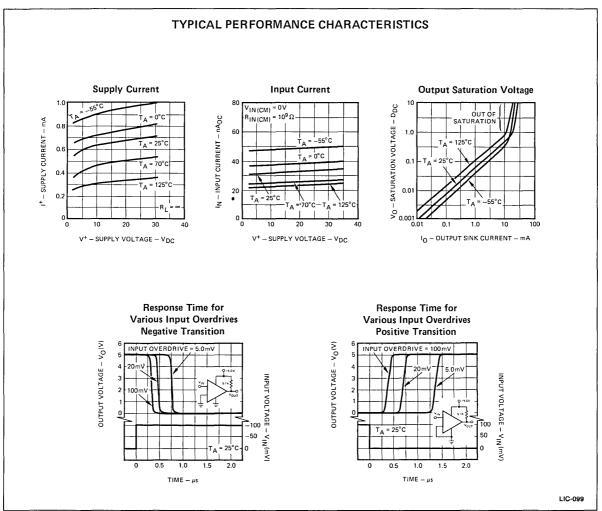

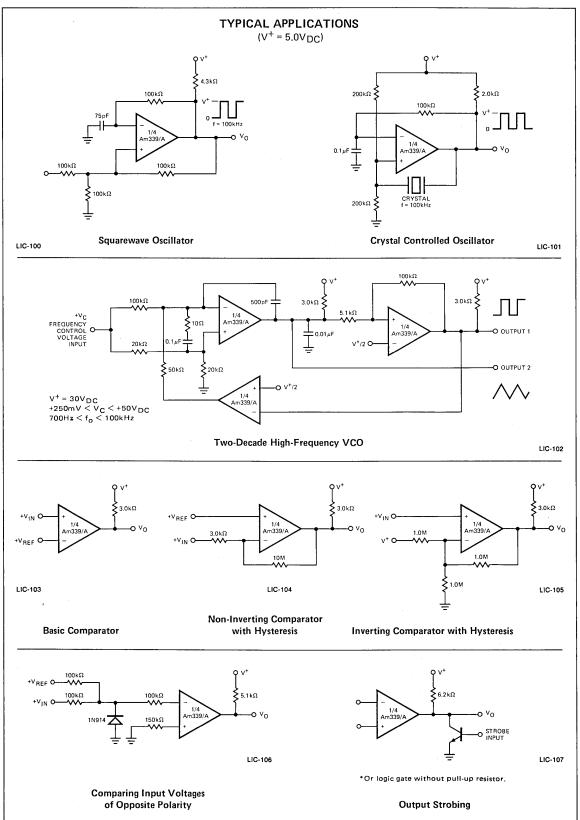

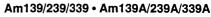

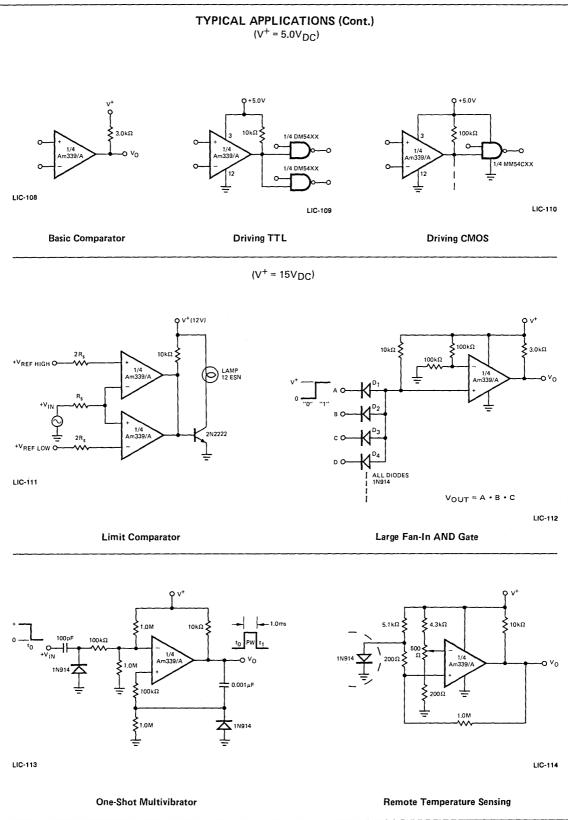

| Am139/239/339    | Low Offset Voltage Quad Comparator | 2-13 |

| Am139A/239A/339A | Low Offset Voltage Quad Comparator | 2-13 |

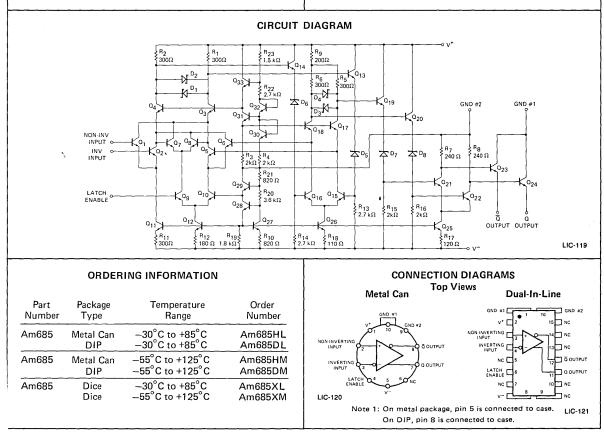

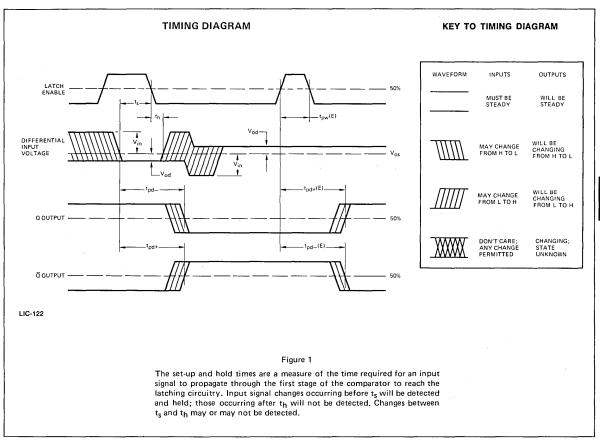

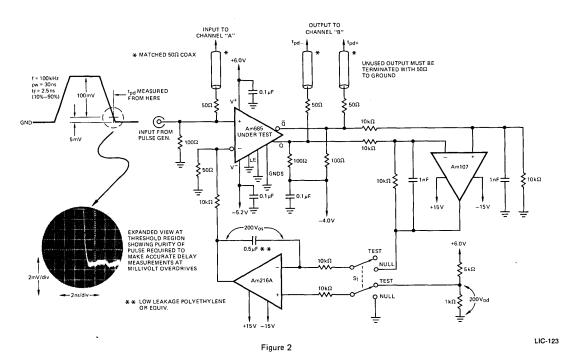

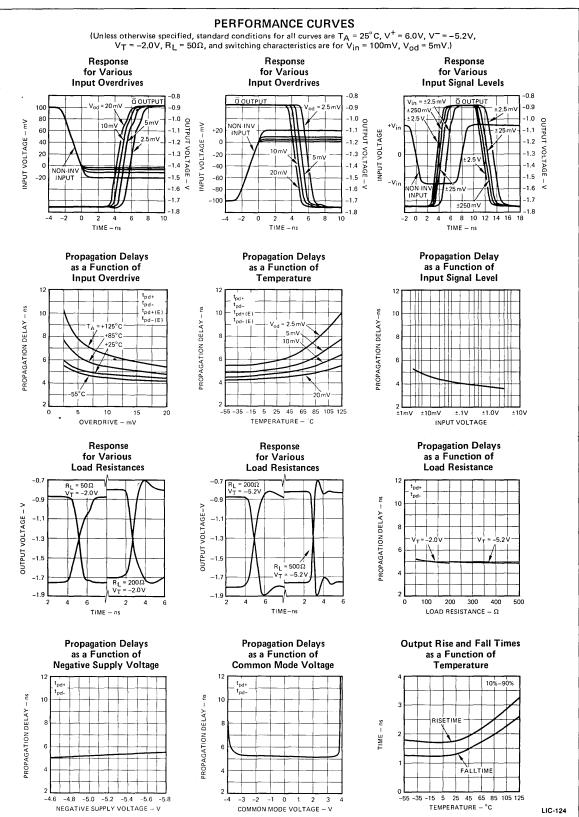

| Am685            | Voltage Comparator                 | 2-19 |

| Am686            | Voltage Comparator                 | 2-27 |

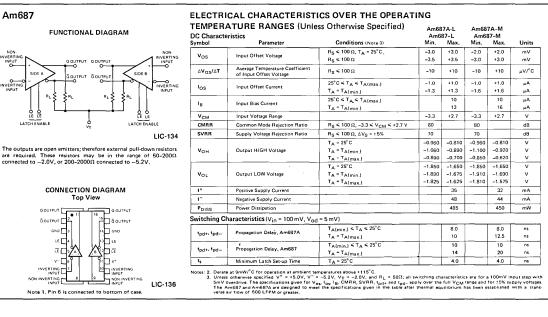

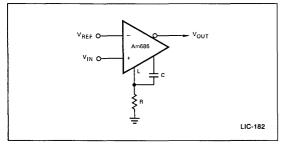

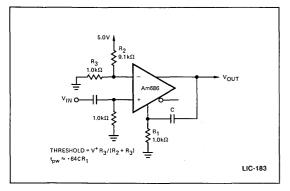

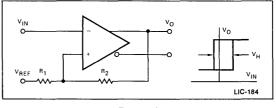

| Am687/687A       | Dual Voltage Comparator            | 2-29 |

| Am1500           | Dual Precision Voltage Comparator  | 2-31 |

| LH2111/2211/2311 | Dual Precision Voltage Comparator  | 2-35 |

# **Application Notes**

| A New High-Speed Comparator – The Am685                   | 2-39 |

|-----------------------------------------------------------|------|

| Am685/Am686/Am687 – Designing with High-Speed Comparators | 2-48 |

# Data Conversion Products – Section III

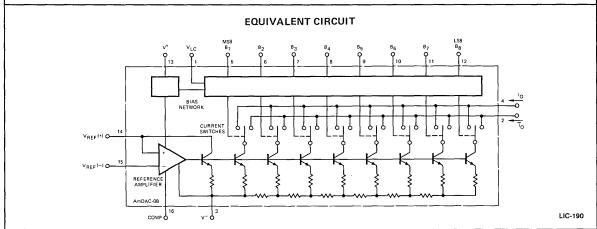

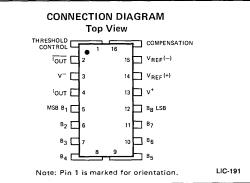

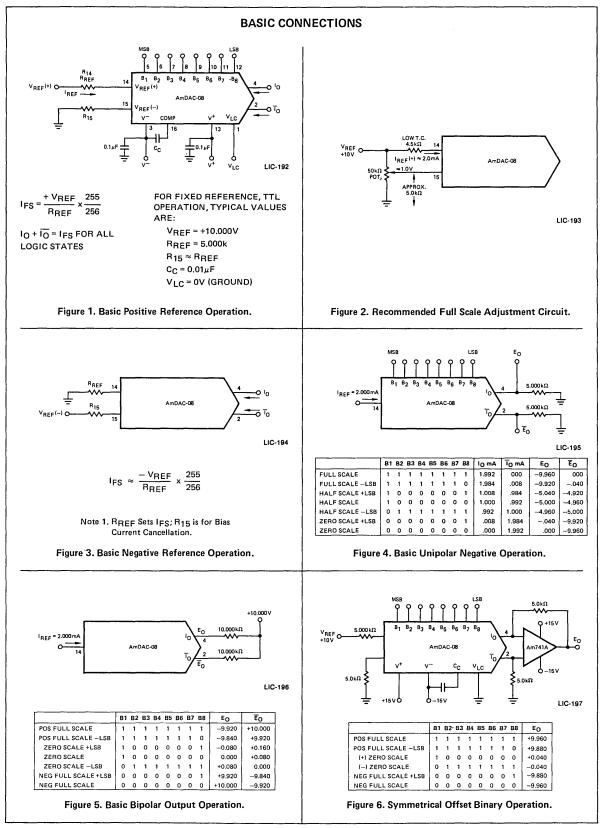

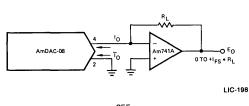

| AmDAC-08              | 8-Bit High-Speed Multiplying D/A Converter                    | 3-1  |

|-----------------------|---------------------------------------------------------------|------|

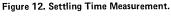

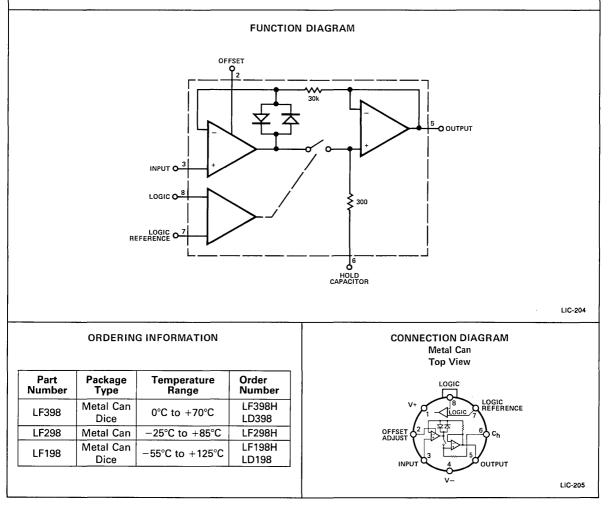

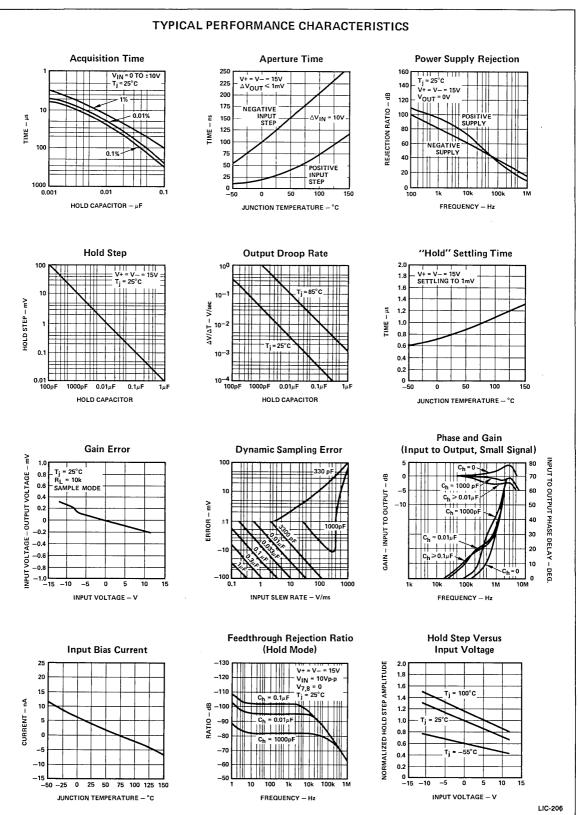

| LF198                 | Monolithic Sample and Hold Circuits                           |      |

| LF298                 | Monolithic Sample and Hold Circuits                           | 3-7  |

| LF398                 | Monolithic Sample and Hold Circuits                           | 3-7  |

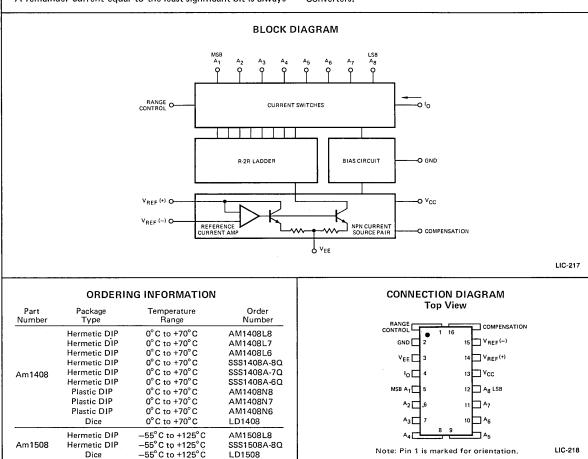

| Am1508/1408           | 8-Bit Multiplying D/A Converter                               | 3-14 |

| SSS1508A/1408A        | 8-Bit Multiplying D/A Converter                               |      |

| Am2502                | 8-Bit/12-Bit Successive Approximation Registers               | 3-18 |

| Am2503                | 8-Bit/12-Bit Successive Approximation Registers               | 3-18 |

| Am2504                | 8-Bit/12-Bit Successive Approximation Registers               | 3-18 |

| Am25L02               | Low Power, 8-Bit/12-Bit Successive Approximation Registers    | 3-24 |

| Am25L03               | Low Power, 8-Bit/12-Bit Successive Approximation Registers    | 3-24 |

| Am25L04               | Low Power, 8-Bit/12-Bit Successive Approximation Registers    | 3-24 |

| Am6070                | Companding D-to-A Converter for Control Systems               | 3-28 |

| Am6071                | Companding D-to-A Converter for Control Systems               | 3-40 |

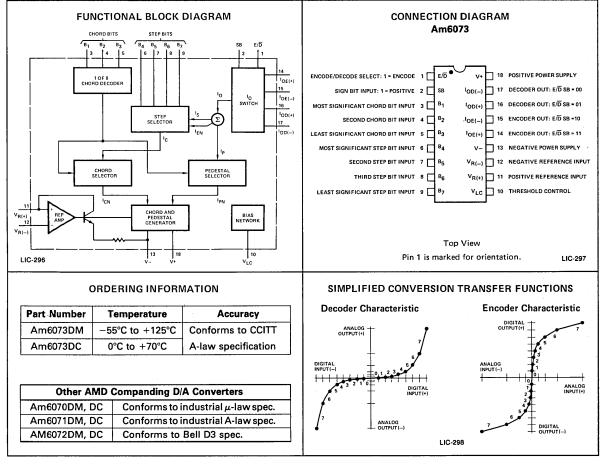

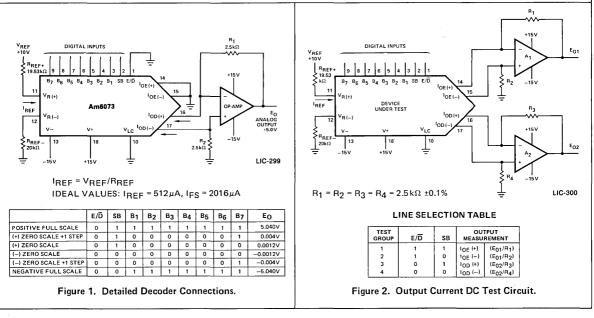

| Am6072                | Companding D-to-A Converter for PCM Communication Systems     | 3-52 |

| Am6073                | Companding D-to-A Converter for PCM Communication Systems     | 3-64 |

| Am6080                | Microprocessor System Compatible 8-Bit High-Speed Multiplying |      |

|                       | D/A Converter                                                 | 3-76 |

| Am6081                | Microprocessor System Compatible 8-Bit High-Speed Multiplying |      |

|                       | D/A Converter                                                 | 3-84 |

| Application Notes     |                                                               |      |

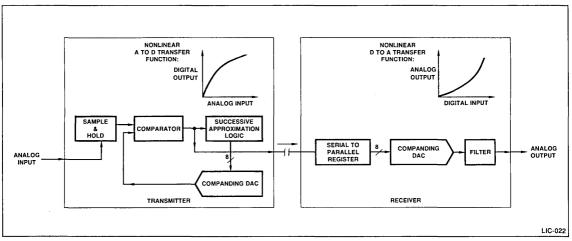

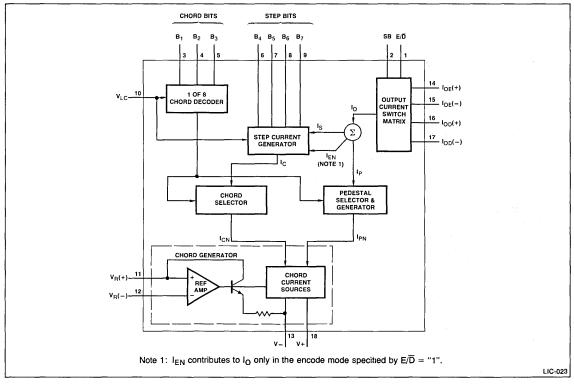

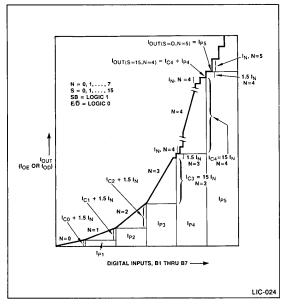

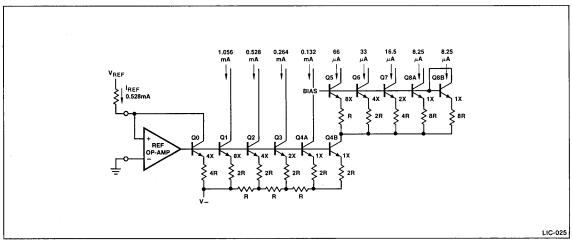

| Companding DAC        | · · · · · · · · · · · · · · · · · · ·                         | 3-96 |

| Line Drivers/Receiver | rs – Section IV                                               |      |

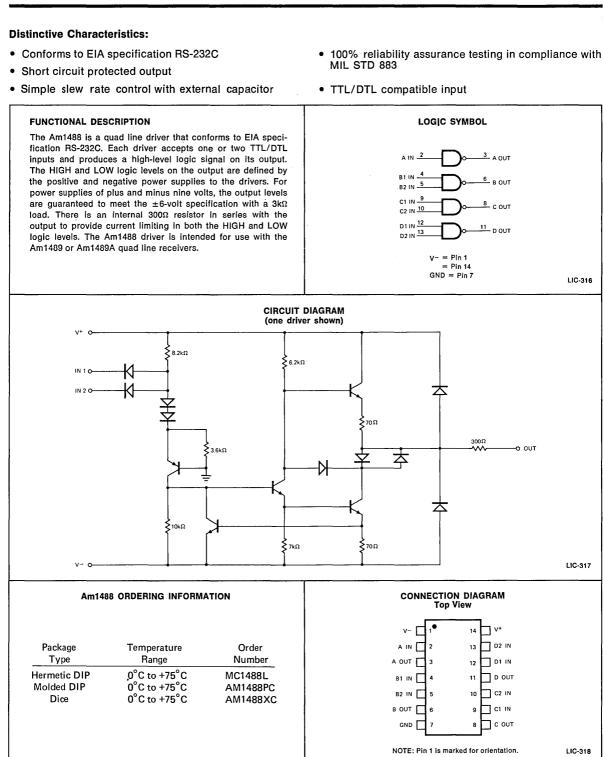

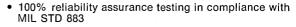

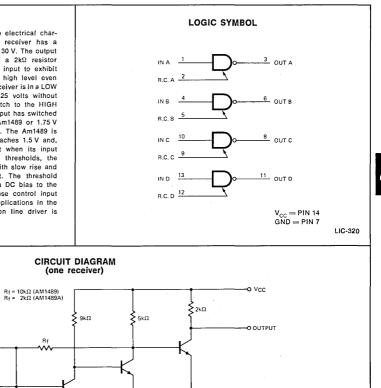

| Am1488                | Quad RS-232C Line Driver                                      | 4-1  |

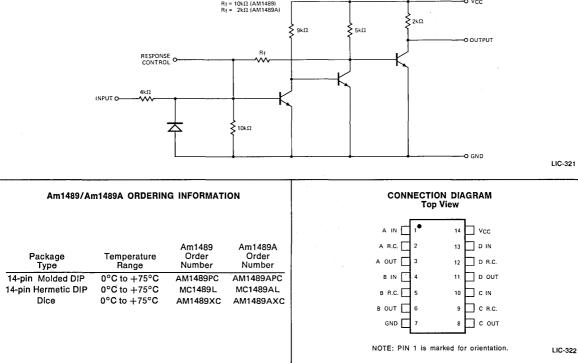

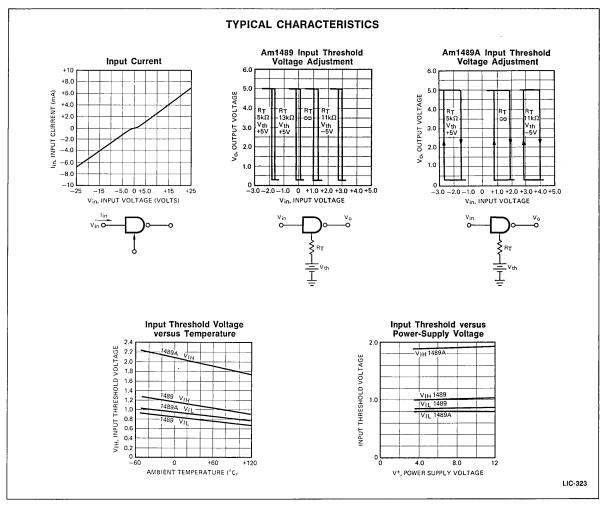

| Am1489                | Quad RS-232C Line Receiver                                    | 4-4  |

| Am1489A               | Quad RS-232C Line Receiver                                    | 4-4  |

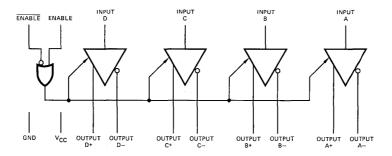

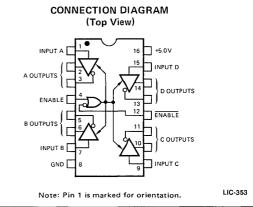

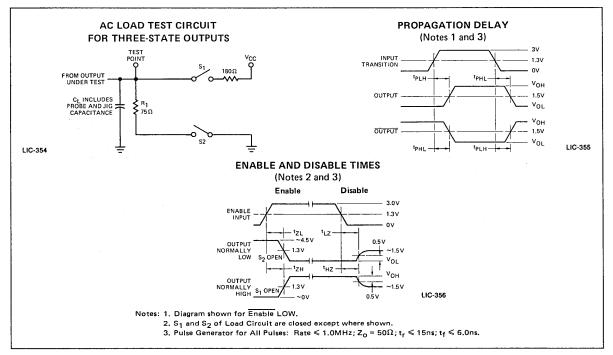

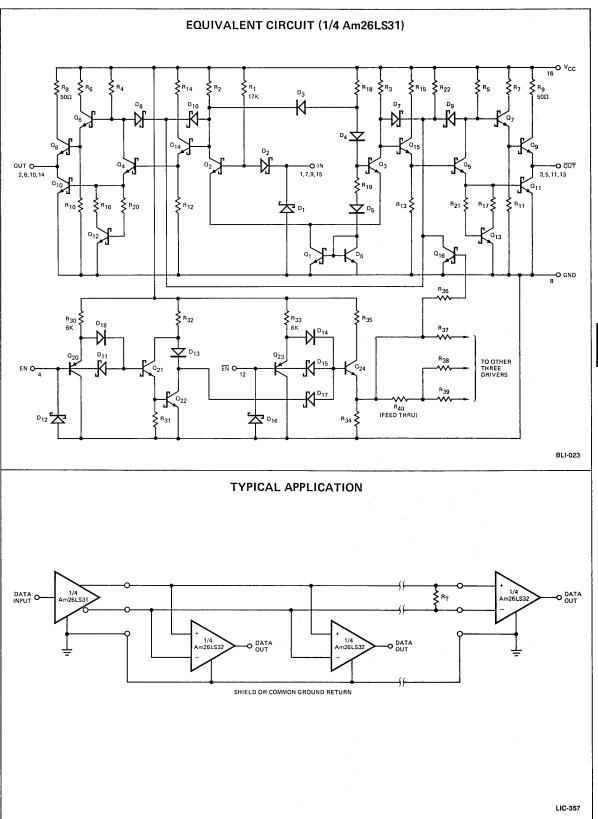

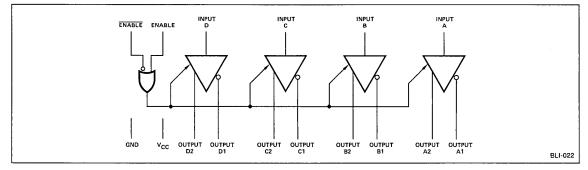

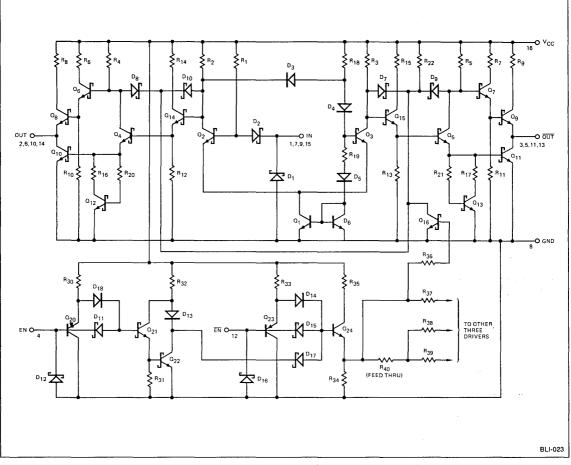

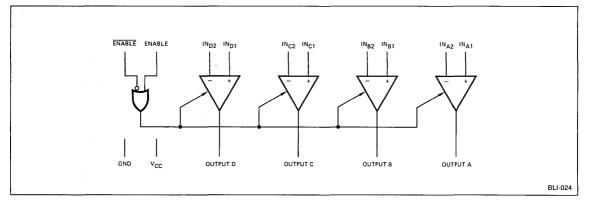

| Am1692/3692           | Three-State Differential Line Drivers                         | 4-8  |

# **FUNCTIONAL INDEX (Cont.)**

# Line Drivers/Receivers – Section IV (Cont.)

| Am25LS240      | Octal Buffer; Inverting, Three-State                        | 4-13  |

|----------------|-------------------------------------------------------------|-------|

| Am25LS241      | Octal Buffer; Non-Inverting, Three-State                    | 4-17  |

| Am25LS242      | Quad Three-State Bus Transceiver                            | 4-21  |

| Am25LS243      | Quad Three-State Bus Transceiver                            | 4-21  |

| Am25LS244      | Octal Buffer, Non-Inverting, Three-State                    | 4-17  |

| Am26LS29       | Quad Three-State Single-Ended RS-423 Line Driver            |       |

| Am26LS30       | Dual Differential RS-422 Party Line/Quad Single-Ended       |       |

|                | RS-423 Line Driver                                          | 4-30  |

| Am26LS31       | Quad RS-422 High-Speed Differential Line Driver             |       |

| Am26LS32       | Quad RS-422 and RS-423 Differential Line Receiver           |       |

| Am26LS33       | Quad Differential Line Receiver                             |       |

| Am26S10        | Quad Bus Transceiver                                        |       |

| Am26S11        | Quad Bus Transceiver                                        |       |

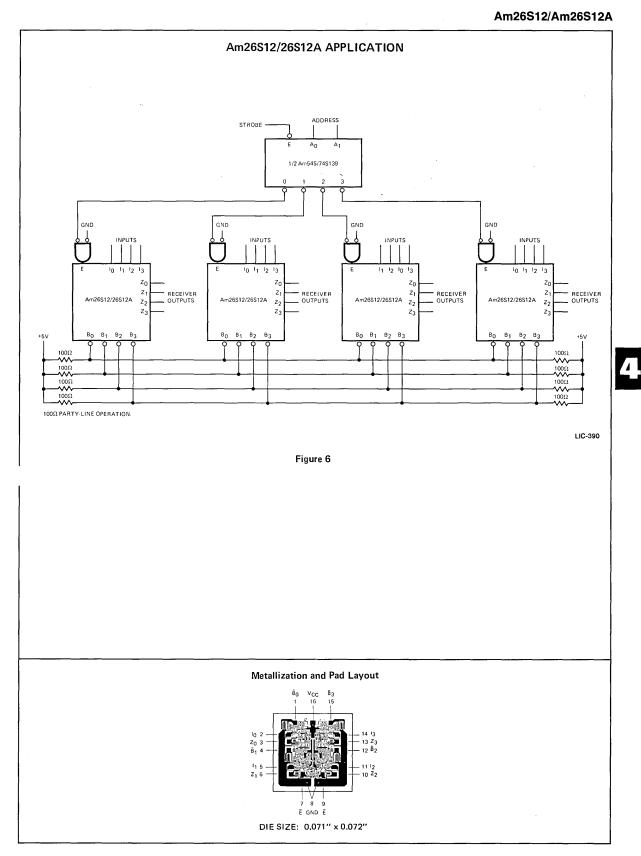

| Am26S12        | Quad Bus Transceiver                                        | 4-62  |

| Am26S12A       | Quad Bus Transceiver                                        |       |

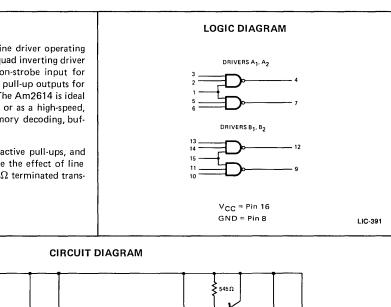

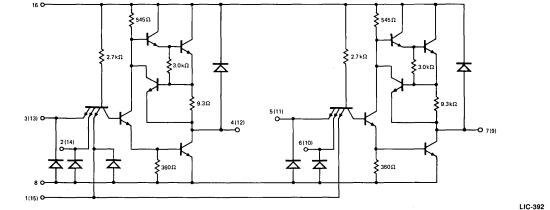

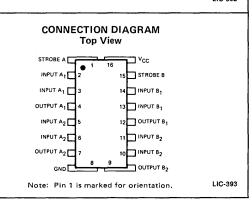

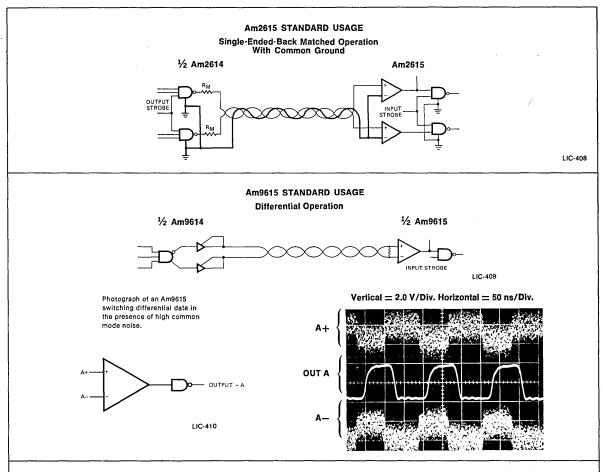

| Am2614         | Quad Single-Ended Line Driver                               |       |

| Am2615         | Dual Differential Line Receiver                             |       |

| Am2616         | Quad MIL-188C and RS-232C Line Driver                       |       |

| Am2617         | Quad RS-232C Line Receiver                                  |       |

| Am2905         | Quad Two-Input OC Bus Transceiver with Three-State Receiver |       |

| Am2906         | Quad Two-Input OC Bus Transceiver with Parity               |       |

| Am2907         | Quad Bus Transceiver with Interface Logic                   |       |

| Am2908         | Quad Bus Transceiver with Interface Logic                   |       |

| Am2915A        | Quad Three-State Bus Transceiver with Interface Logic       |       |

| Am2916A        | Quad Three-State Bus Transceiver with Interface Logic       |       |

| Am2917A        | Quad Three-State Bus Transceiver with Interface Logic       |       |

| Am3212         | 8-Bit Input/Output Port                                     |       |

| Am3216         | 4-Bit Parallel Bidirectional Bus Driver                     |       |

| Am3226         | 4-Bit Parallel Bidirectional Bus Driver                     |       |

| Am3448A        | IEEE-488 Quad Bidirectional Transceiver                     |       |

| Am54LS/74LS240 | Octal Buffer; Inverting, Three-State                        |       |

| Am54LS/74LS241 | Octal Buffer; Non-Inverting, Three-State                    |       |

| Am54LS/74LS242 | Quad Three-State Bus Transceiver                            |       |

|                | Quad Three-State Bus Transceiver                            |       |

| Am54LS/74LS244 | Octal Buffer; Non-Inverting, Three-State                    |       |

| Am54S/74S240   | Octal Buffer/Line Driver/Line Receiver                      |       |

|                | with Three-State Outputs                                    | 4-142 |

| Am54S/74S241   | Octal Buffer/Line Driver/Line Receiver                      |       |

|                | with Three-State Outputs                                    | 4-142 |

| Am54S/74S242   | Octal Buffer/Line Driver/Line Receiver                      |       |

|                |                                                             | 4-142 |

| Am54S/74S243   | Octal Buffer/Line Driver/Line Receiver                      | –     |

|                | with Three-State Outputs                                    | 4-142 |

| Am54S/74S244   | Octal Buffer/Line Driver/Line Receiver                      |       |

|                | with Three-State Outputs                                    | 4-142 |

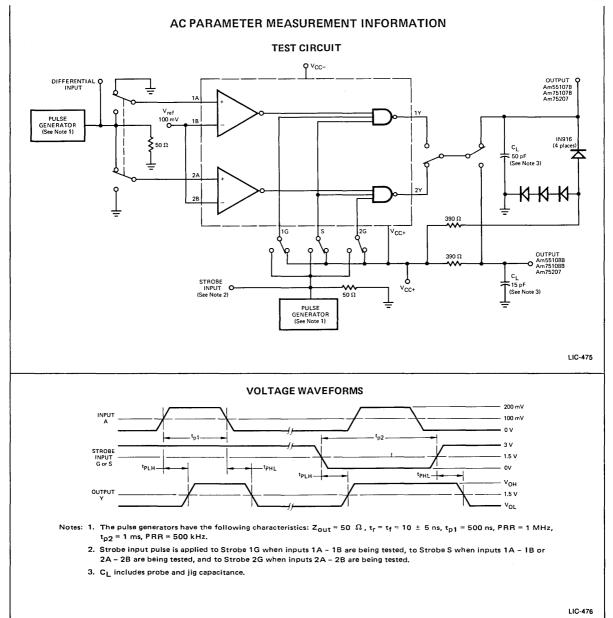

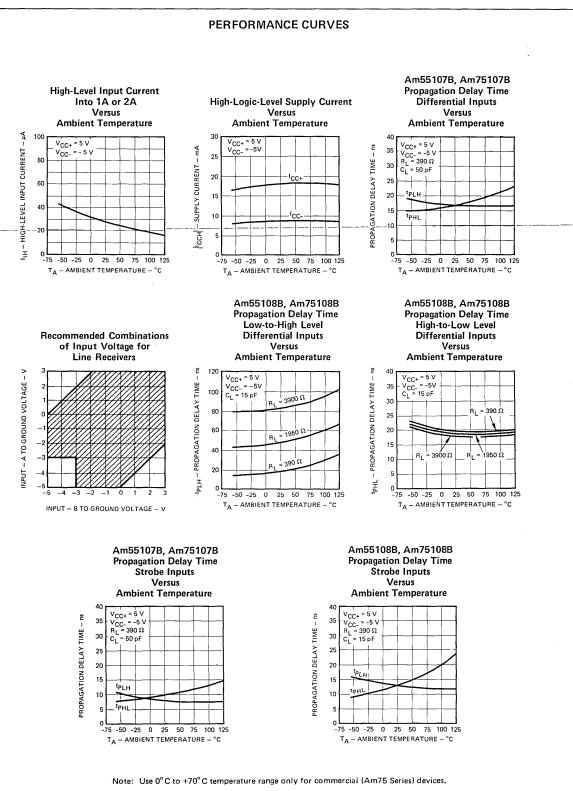

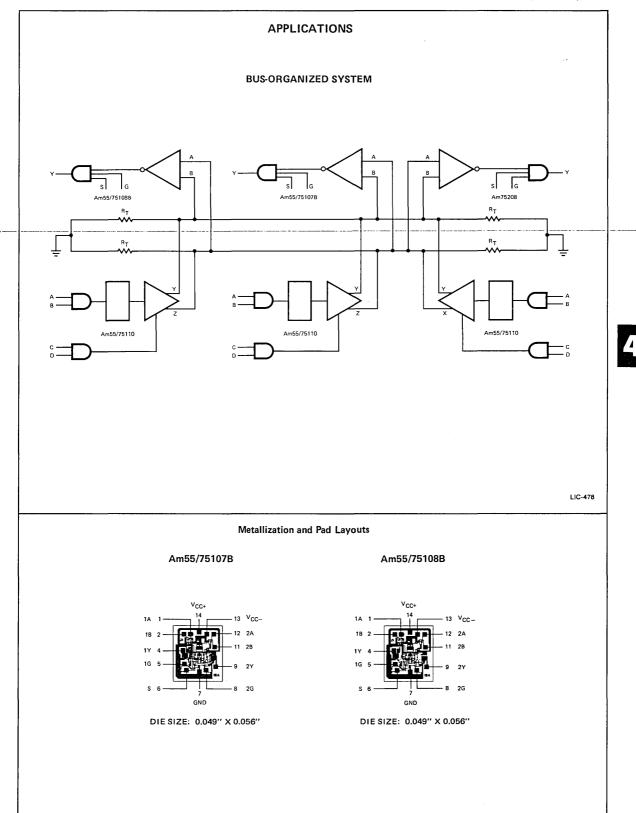

| Am55/75107B    | Dual Line Receiver                                          |       |

| Am55/75108B    | Dual Line Receiver                                          | 4-147 |

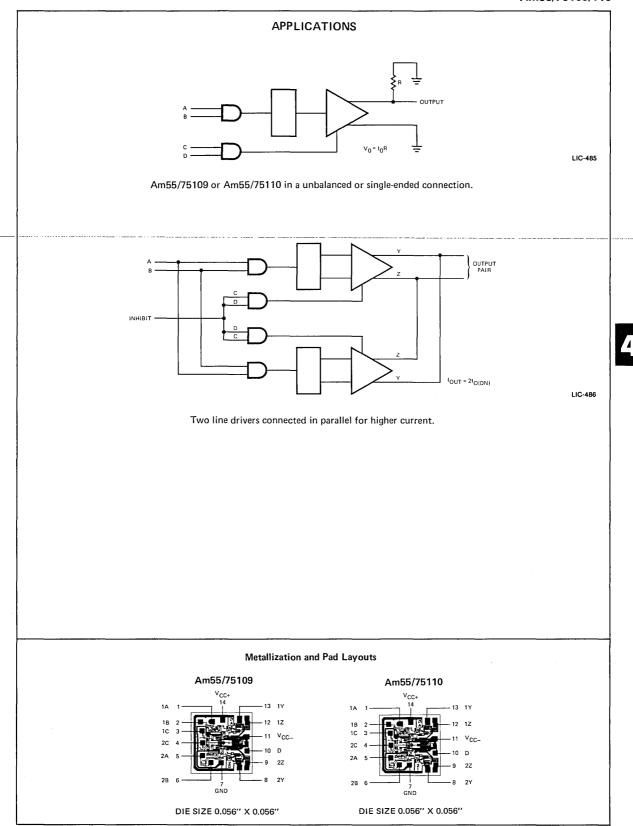

| Am55/75109     | Dual Line Driver                                            | 4-153 |

| Am55/75110     | Dual Line Driver                                            |       |

| Am71LS/81LS95  | Three-State Octal Buffers                                   |       |

| Am71LS/81LS96  | Three-State Octal Buffers                                   | 4-159 |

| Am71LS/81LS97  | Three-State Octal Buffers                                   | 4-159 |

| Am71LS/81LS98  | Three-State Octal Buffers                                   |       |

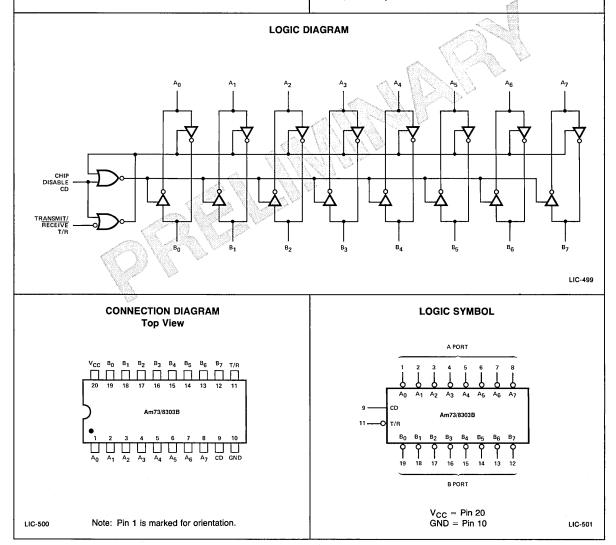

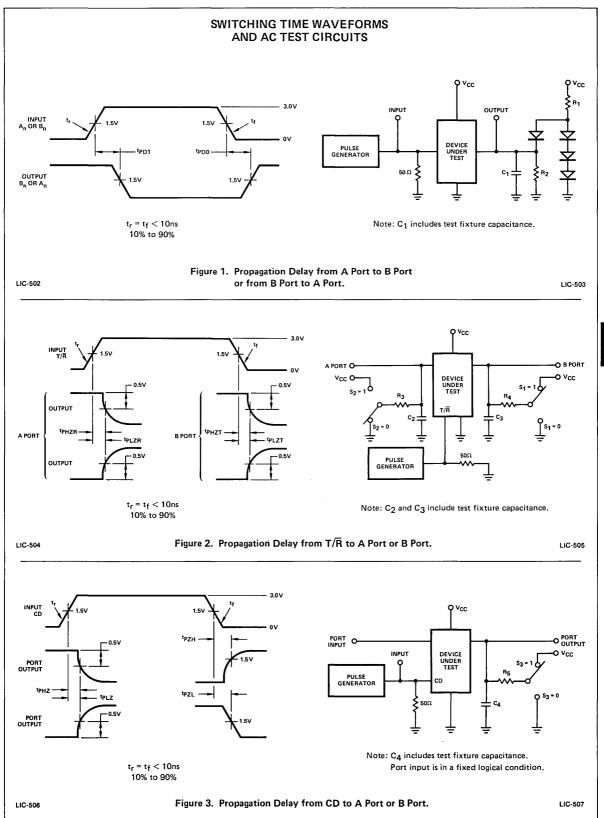

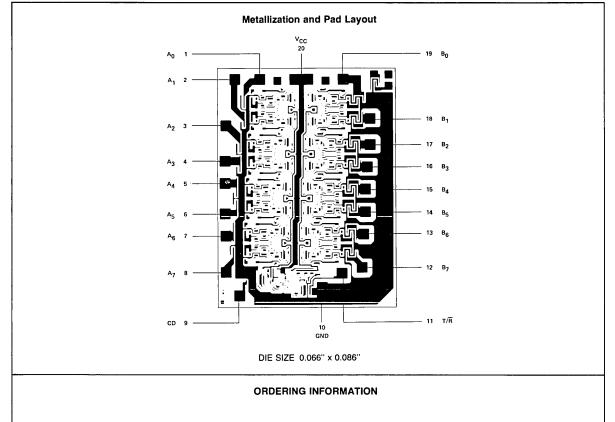

| Am73/8303B     | Octal Three-State Inverting Bidirectional Transceiver       | 4-163 |

# **FUNCTIONAL INDEX (Cont.)**

# Line Drivers/Receivers - Section IV (Cont.)

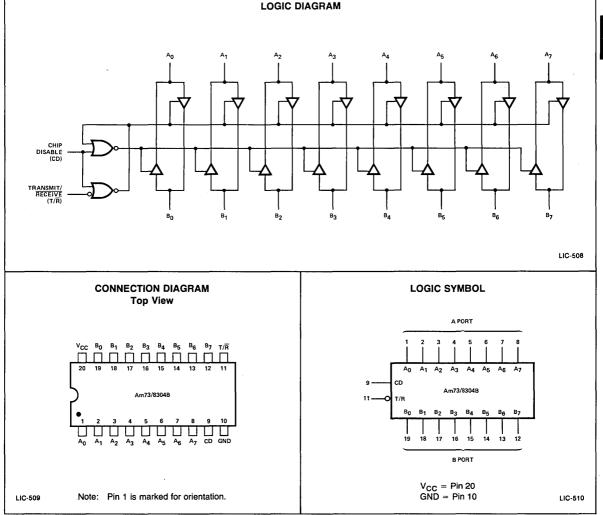

| Am73/8304B | Octal Three-State Bidirectional Transceiver   |

|------------|-----------------------------------------------|

| Am78/8820  | Dual Differential Line Receiver               |

| Am78/8820A | Dual Differential Line Receiver               |

| Am78/8830  | Dual Differential Line Driver                 |

|            |                                               |

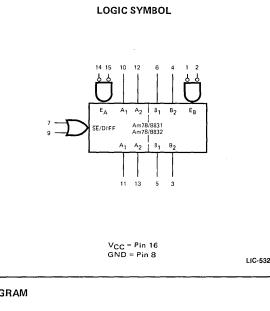

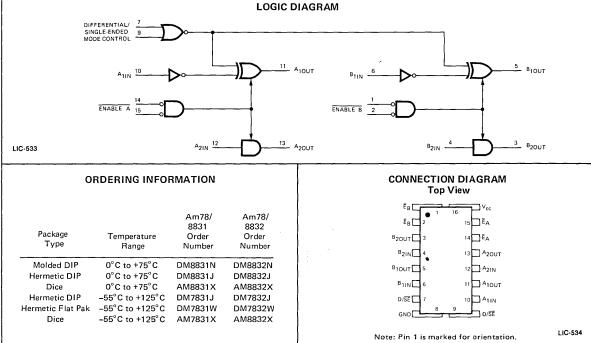

| Am78/8831  | Three-State Line Driver 4-182                 |

| Am78/8832  | Three-State Line Driver 4-182                 |

| Am78/8838  | Quad Unified Bus Transceiver 4-188            |

| Am8T26     | Schottky Three-State Quad Bus Driver/Receiver |

| Am8T26A    | Schottky Three-State Quad Bus Driver/Receiver |

| Am8T28     | Schottky Three-State Quad Bus Driver/Receiver |

| Am8212     | 8-Bit Input/Output Port 4-125                 |

| Am8216     | 4-Bit Parallel Bidirectional Bus Driver       |

| Am8226     | 4-Bit Parallel Bidirectional Bus Driver       |

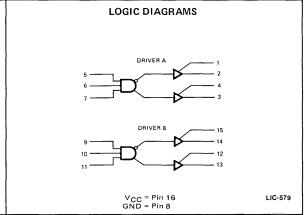

| Am9614     | Differential Line Driver 4-200                |

| Am9615     | Dual Differential Line Receiver 4-72          |

| Am9616     | Triple EIA RS-232C/MIL-STD-188C Line Driver   |

| Am9617     | RS-232C Line Receiver 4-209                   |

|            |                                               |

# **Application Notes**

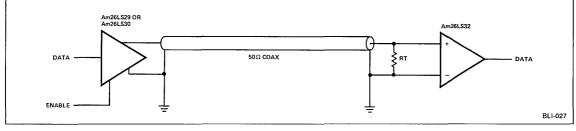

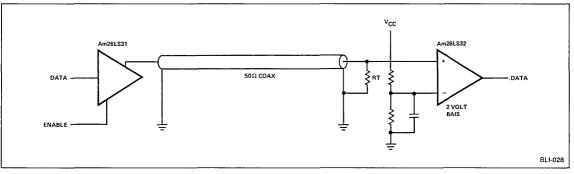

| Use of the Am26LS29, 30, 31 and 32 Quad Driver/Receiver |      |

|---------------------------------------------------------|------|

| Family in EIA-422 and 423 Applications                  | 4-45 |

# MOS Memory and Microprocessor Interface - Section V

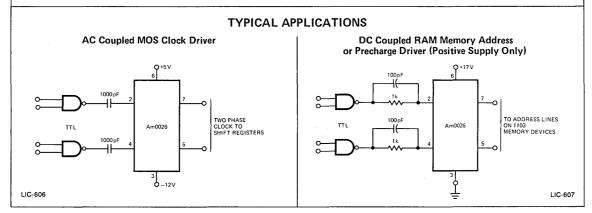

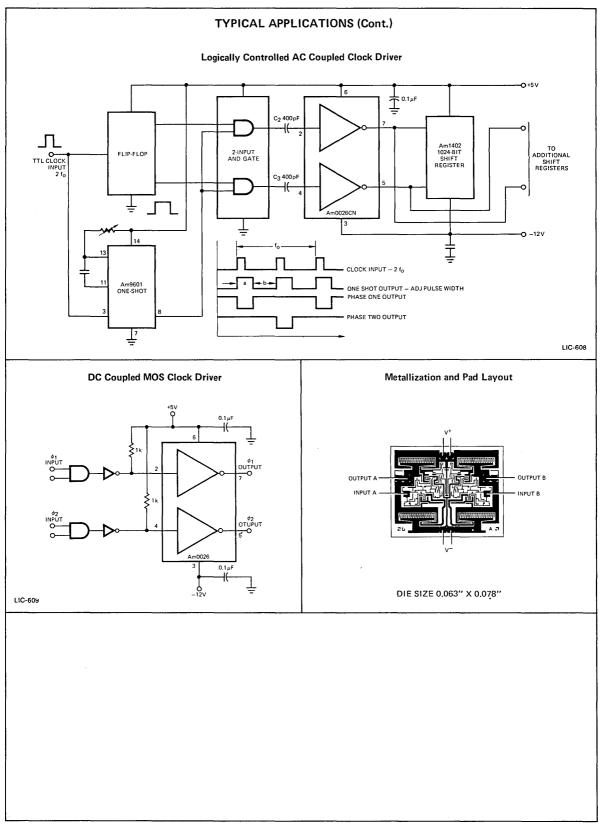

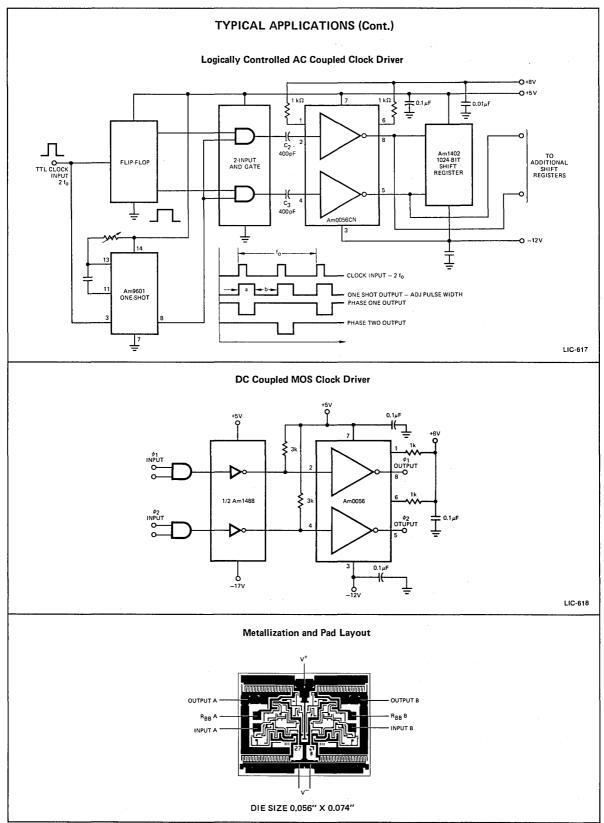

| Am0026/0026C | 5MHz Two-Phase MOS Clock Driver  | 5-1  |

|--------------|----------------------------------|------|

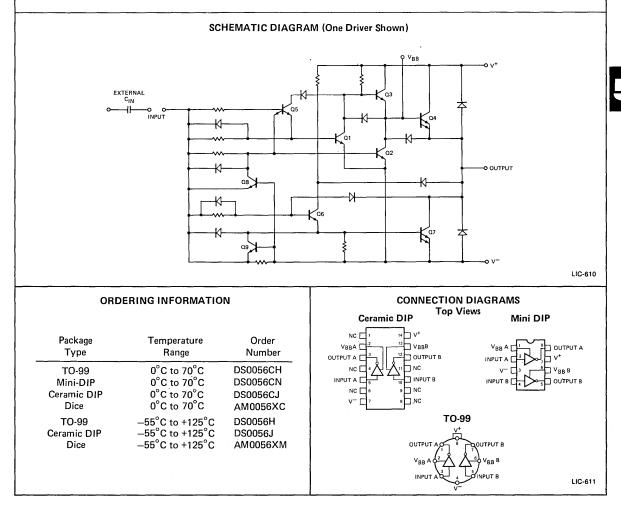

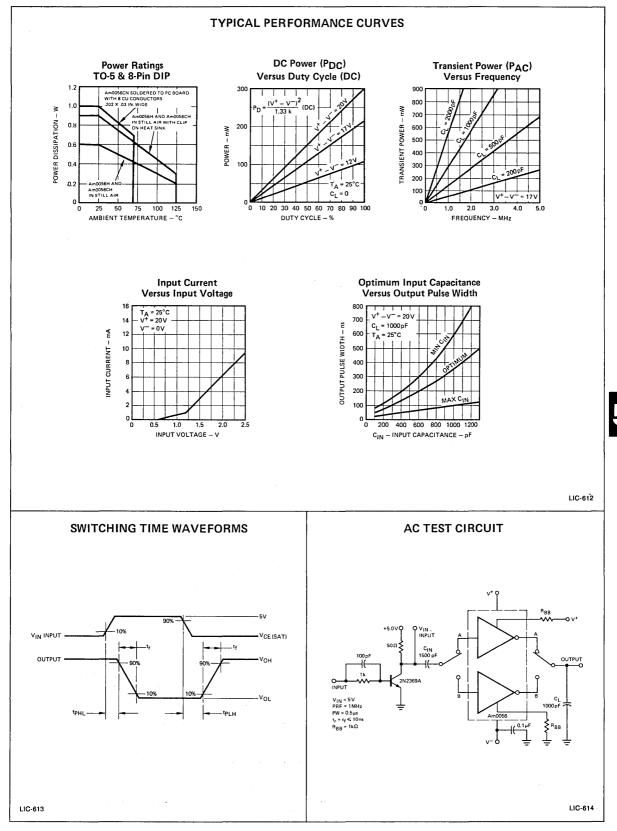

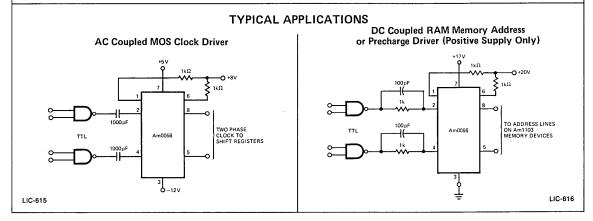

| Am0056/0056C | 5MHz Two-Phase MOS Clock Driver  | 5-7  |

| Am8224       | Clock Generator and Driver       | 5-13 |

| Am8228       | System Controller and Bus Driver | 5-20 |

| Am8238       | System Controller and Bus Driver | 5-20 |

# **Operational Amplifiers – Section VI**

| Am101/201/301    | Operational Amplifier                               | 6-1  |

|------------------|-----------------------------------------------------|------|

| Am101A/201A/301A | Operational Amplifier                               | 6-5  |

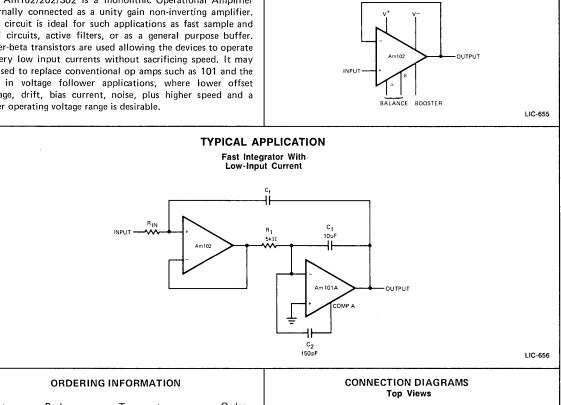

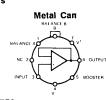

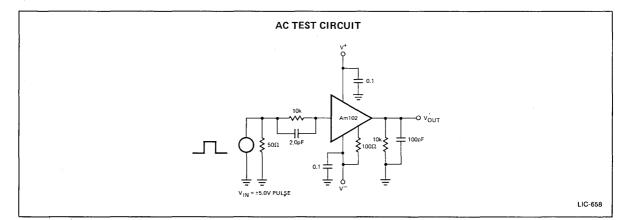

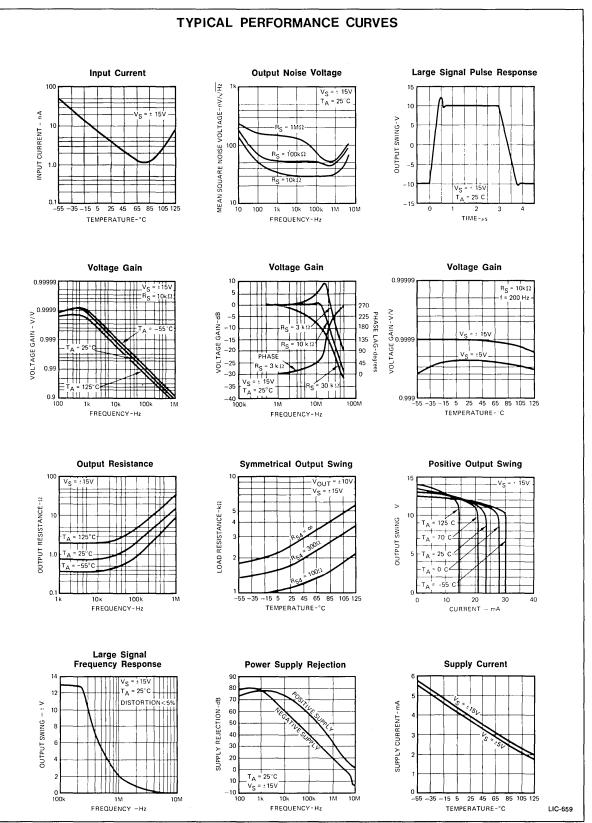

| Am102/202/302    | Voltage Follower                                    | 6-10 |

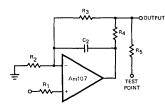

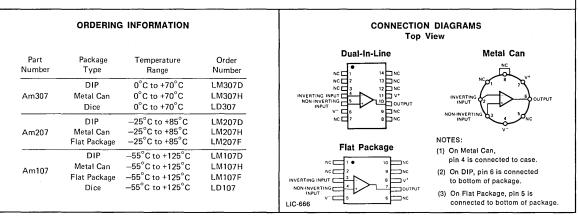

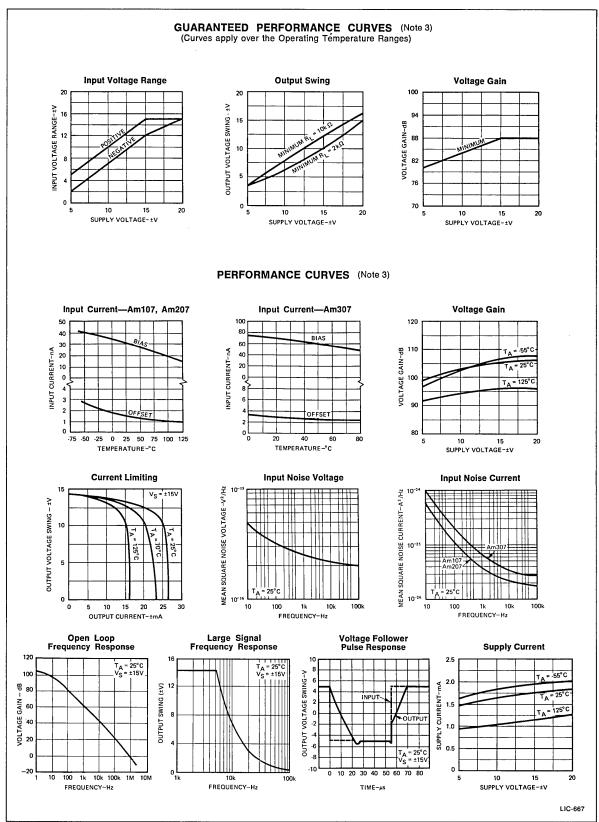

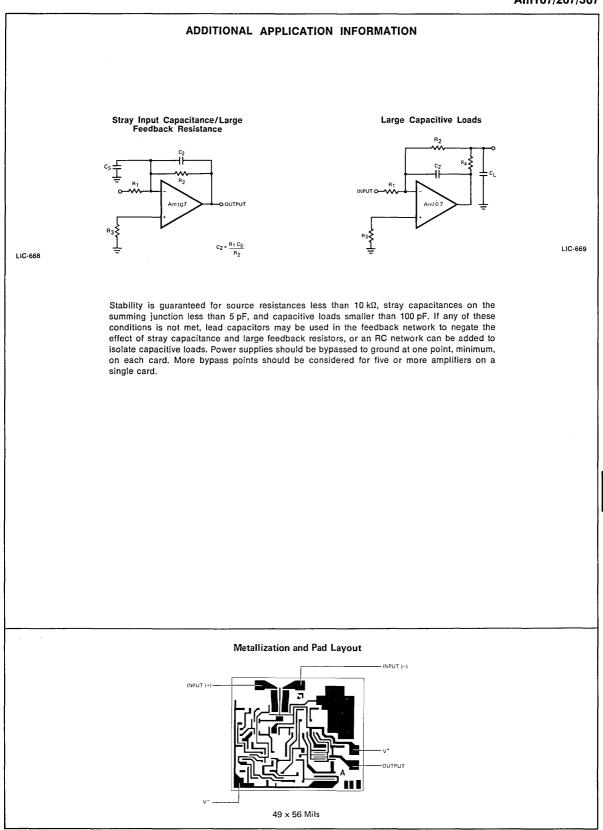

| Am107/207/307    | Frequency Compensated Operational Amplifier         | 6-14 |

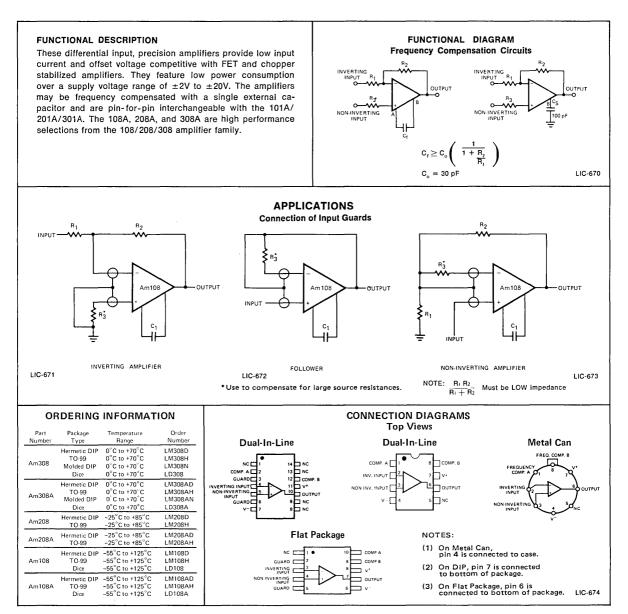

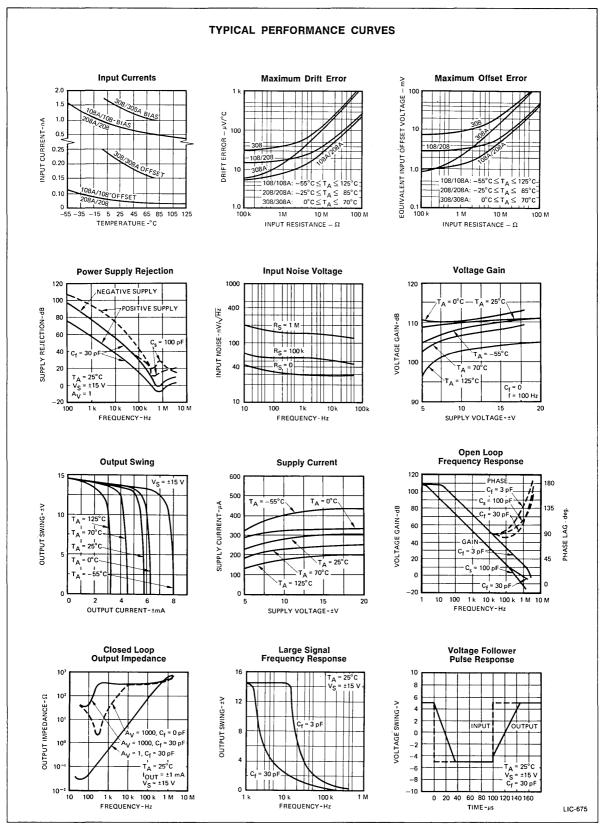

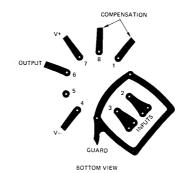

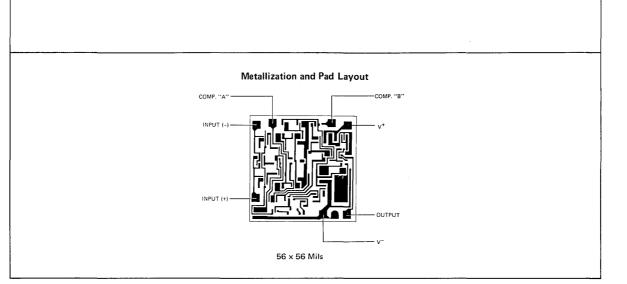

| Am108/208/308    | Operational Amplifier                               | 6-18 |

| Am108A/208A/308A | Operational Amplifier                               | 6-18 |

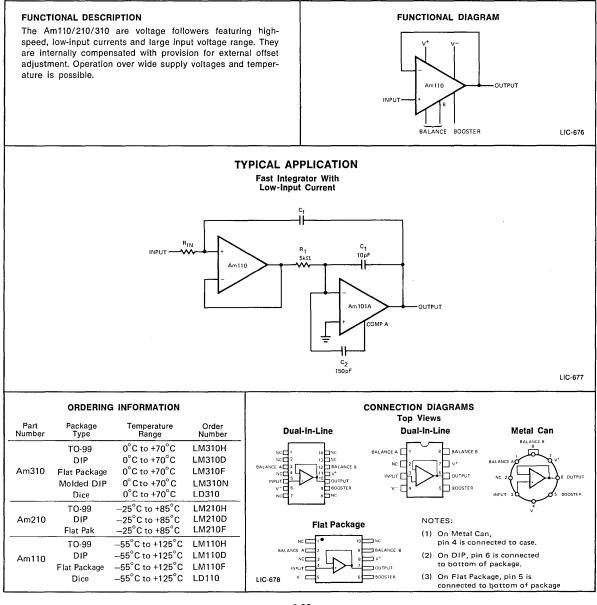

| Am110/210/310    | Voltage Follower                                    | 6-22 |

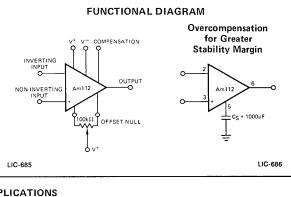

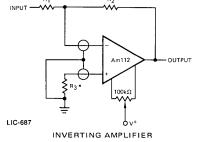

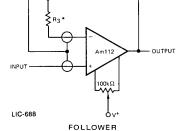

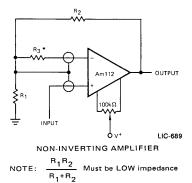

| Am112/212/312    | Compensated, High-Performance Operational Amplifier | 6-26 |

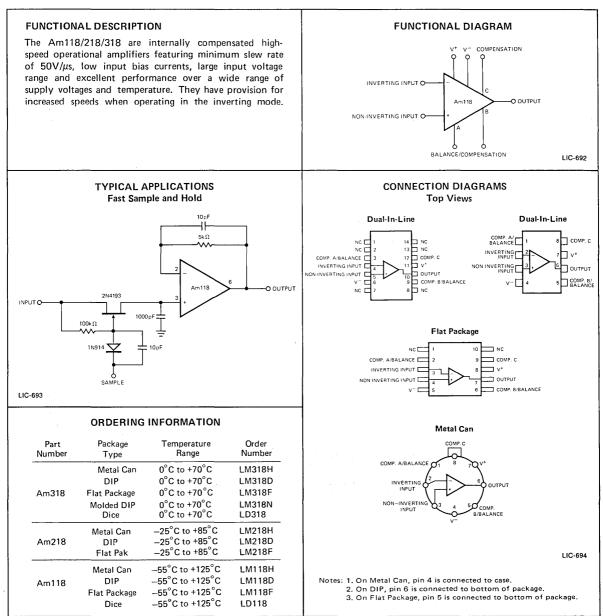

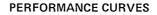

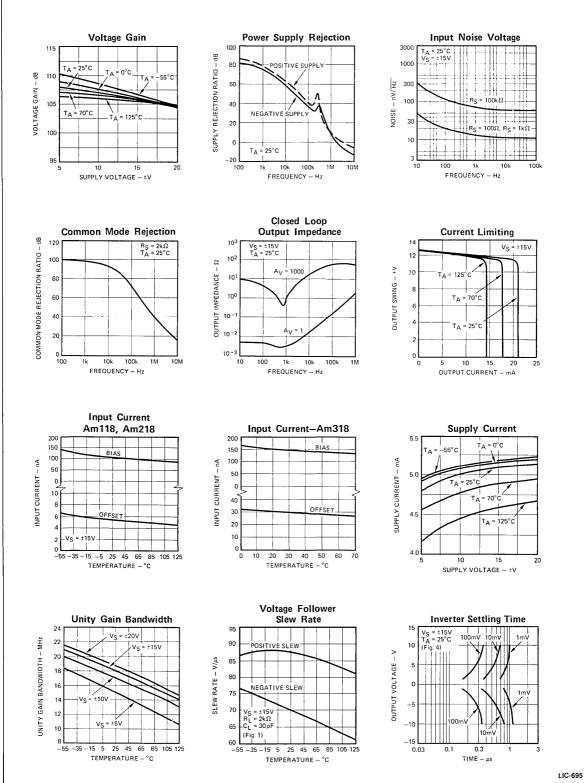

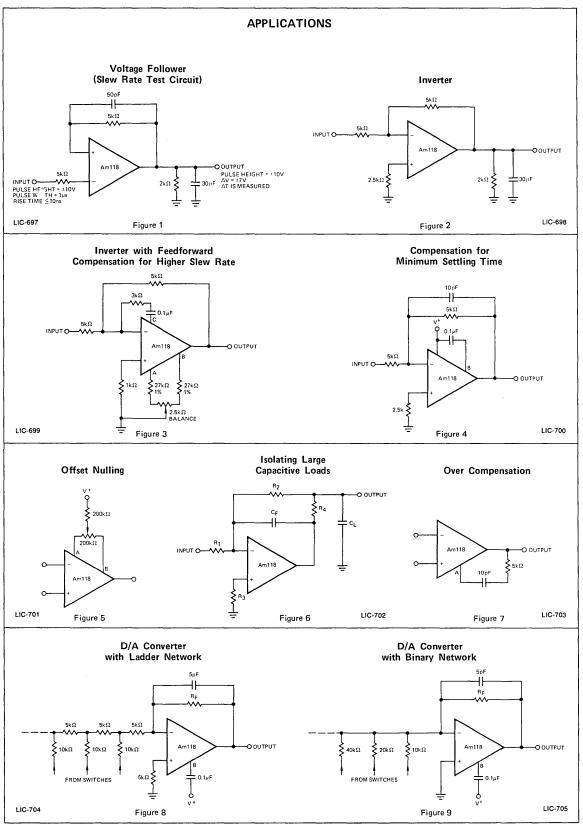

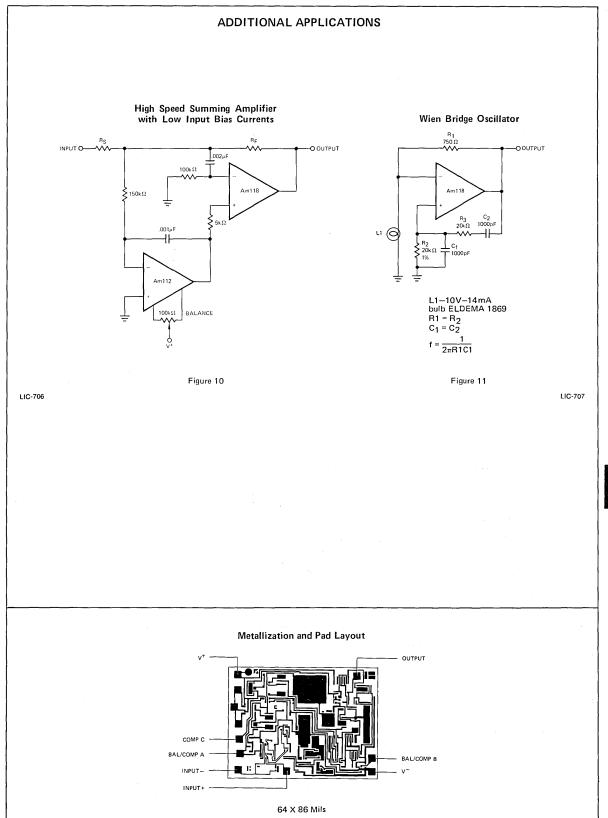

| Am118/218/318    | High-Speed Operational Amplifier                    | 6-30 |

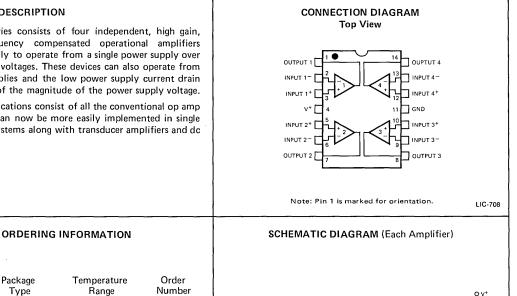

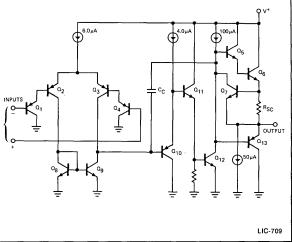

| Am124/224/324    | Quad Operational Amplifier                          | 6-36 |

| Am124A/224A/324A | Quad Operational Amplifier                          | 6-36 |

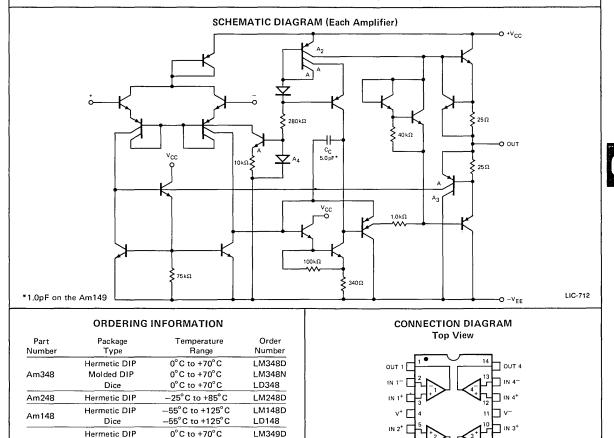

| Am148/248/348    | Quad 741 Operational Amplifier                      | 6-41 |

| Am149/249/349    | Quad 741 Operational Amplifier                      | 6-41 |

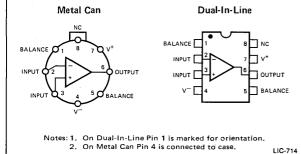

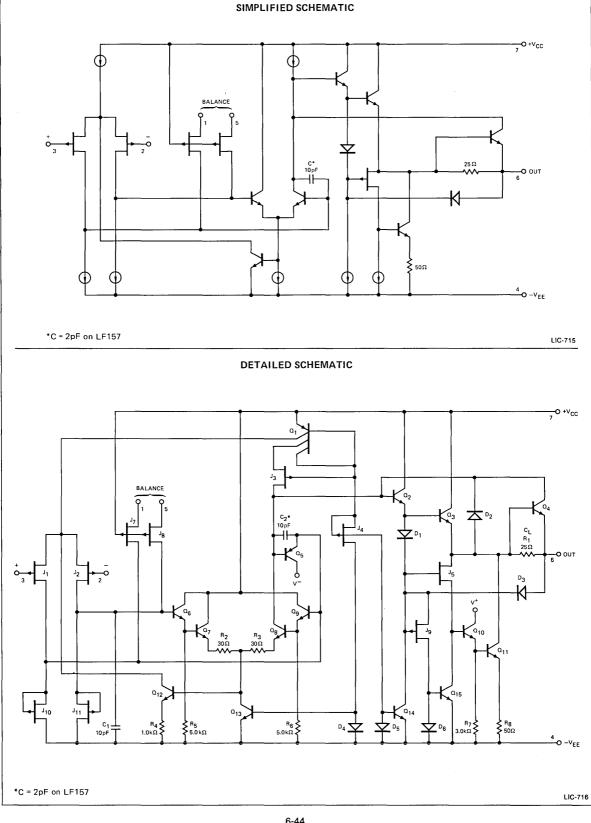

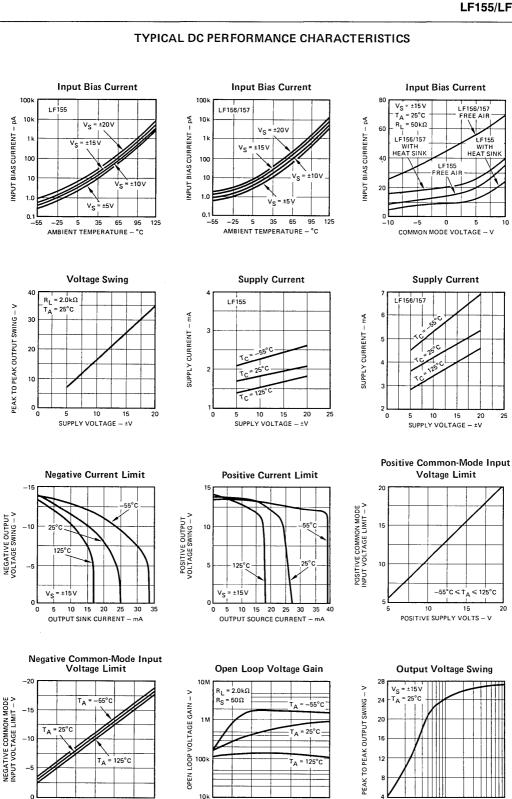

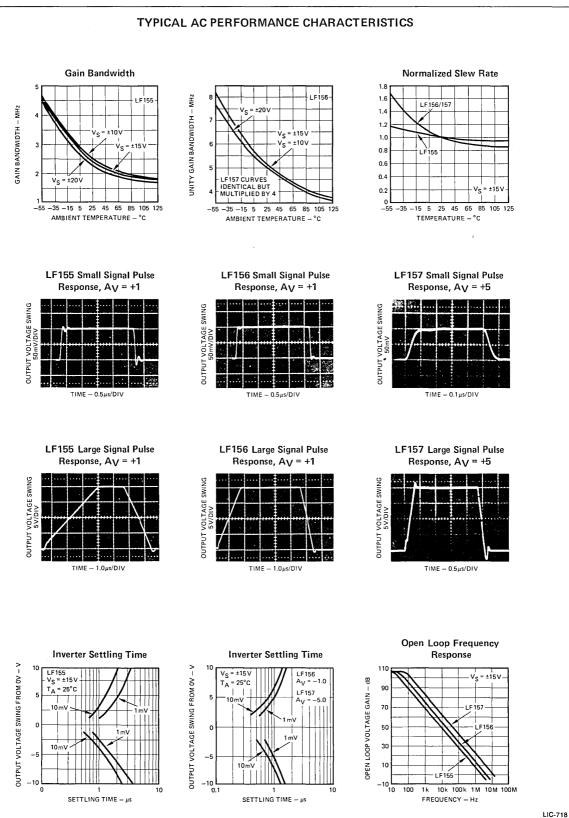

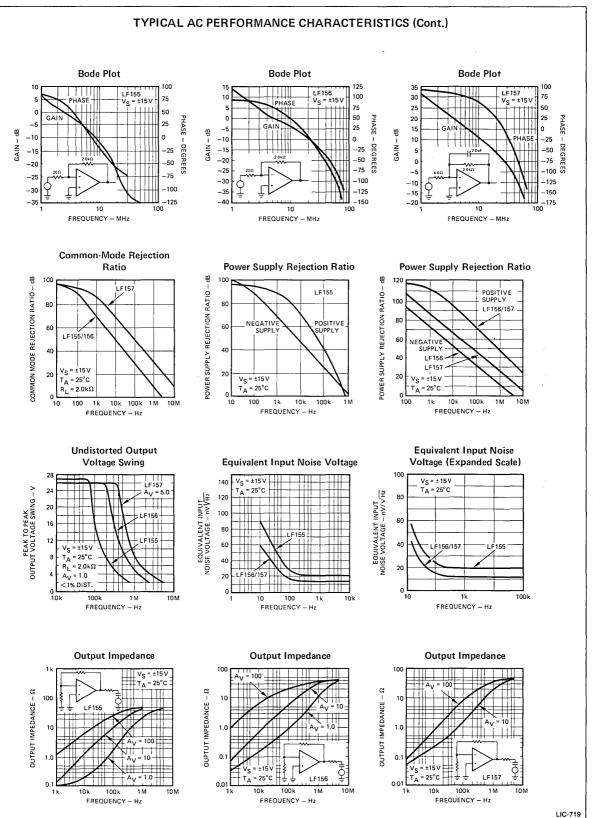

| LF155/255/355    | Monolithic JFET Input Operational Amplifier         | 6-43 |

| LF155A/255A/355A | Monolithic JFET Input Operational Amplifier         | 6-43 |

| LF156/256/356    | Monolithic JFET Input Operational Amplifier         | 6-43 |

| LF156A/256A/356A | Monolithic JFET Input Operational Amplifier         | 6-43 |

| LF157/257/357    | Monolithic JFET Input Operational Amplifier         | 6-43 |

| LF157A/257A/357A | Monolithic JFET Input Operational Amplifier         | 6-43 |

| Am216/316        | Compensated, High-Performance Operational Amplifier | 6-51 |

| Am216A/316A      | Compensated, High-Performance Operational Amplifier | 6-51 |

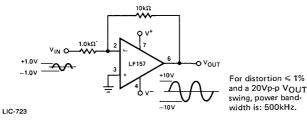

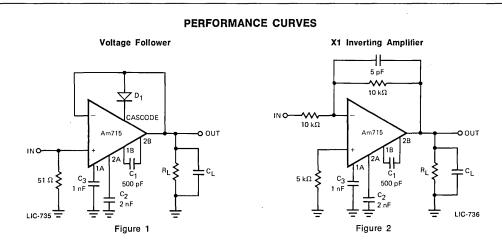

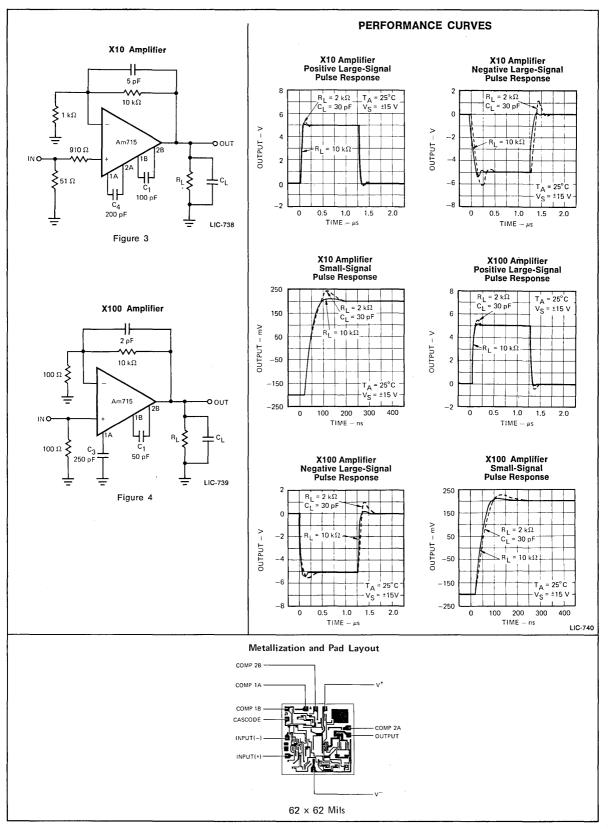

| Am715/715C       | High-Speed Operational Amplifier                    | 6-55 |

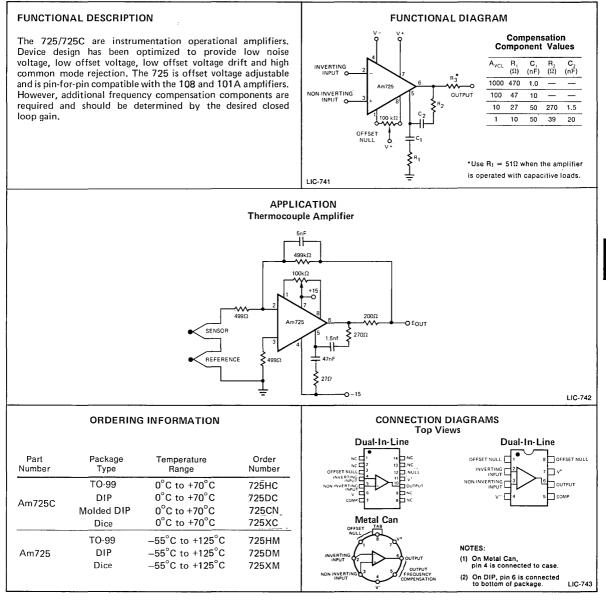

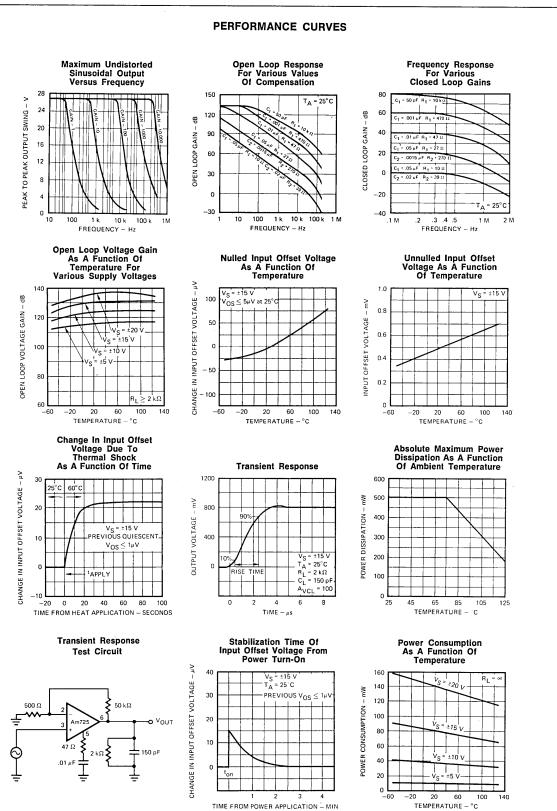

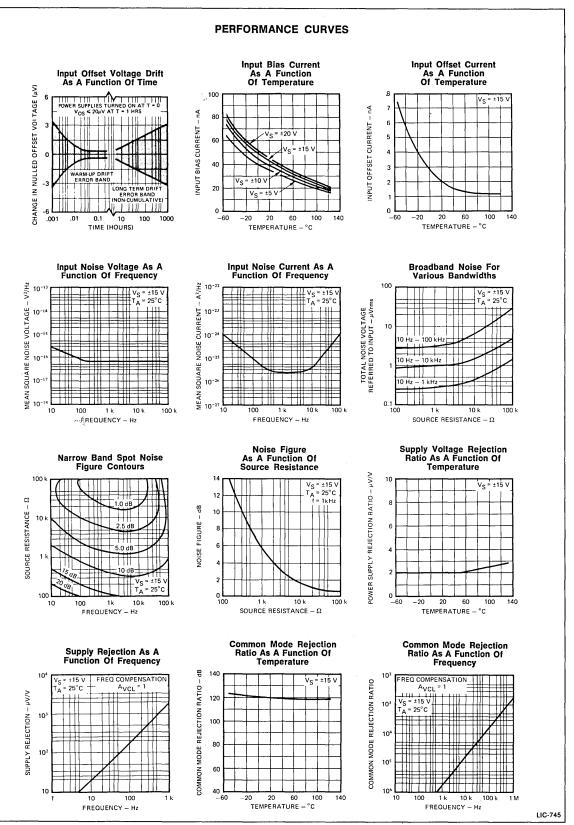

| Am725/725C       | Instrumentation Operational Amplifier               | 6-59 |

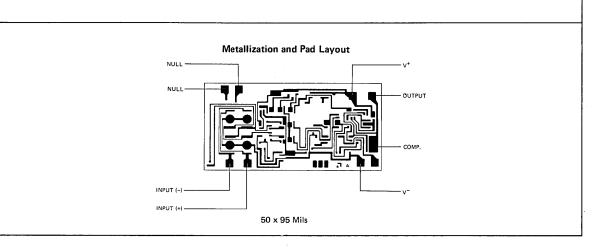

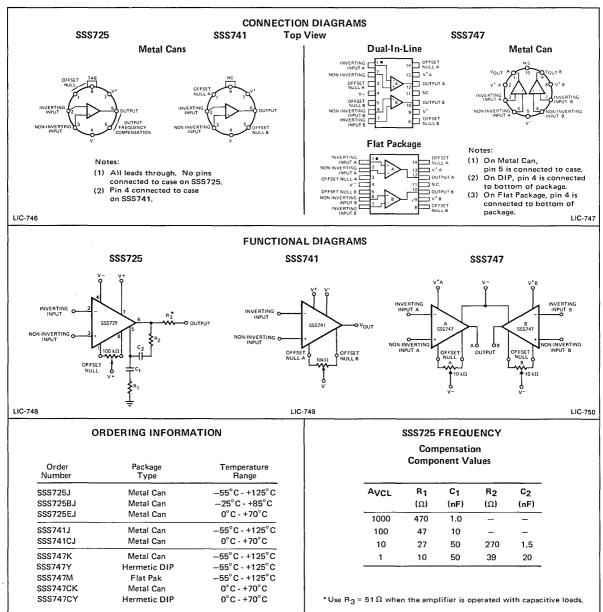

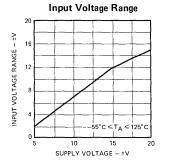

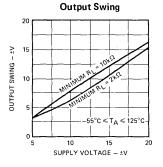

| SSS725/725B/725E | High-Performance Operational Amplifier              | 6-64 |

|                  |                                                     |      |

# FUNCTIONAL INDEX (Cont.)

# **Operational Amplifiers – Section VI (Cont.)**

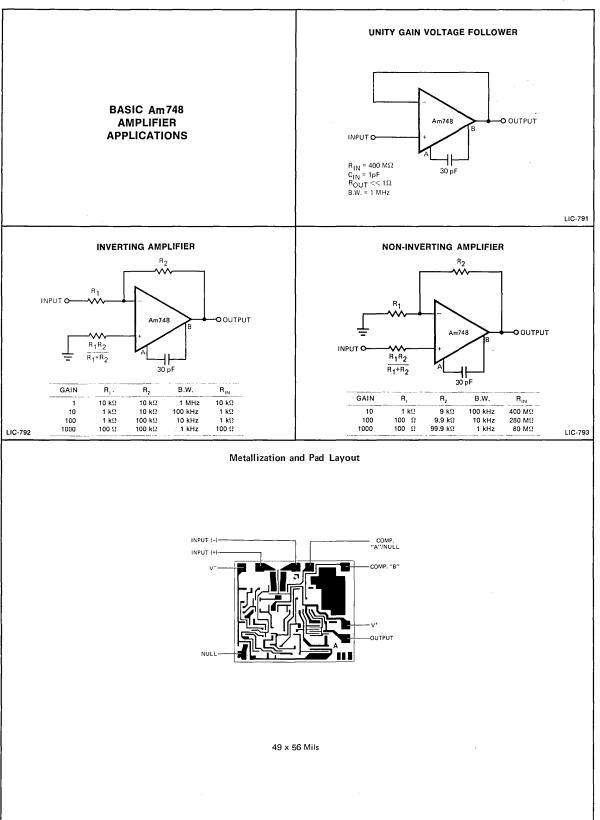

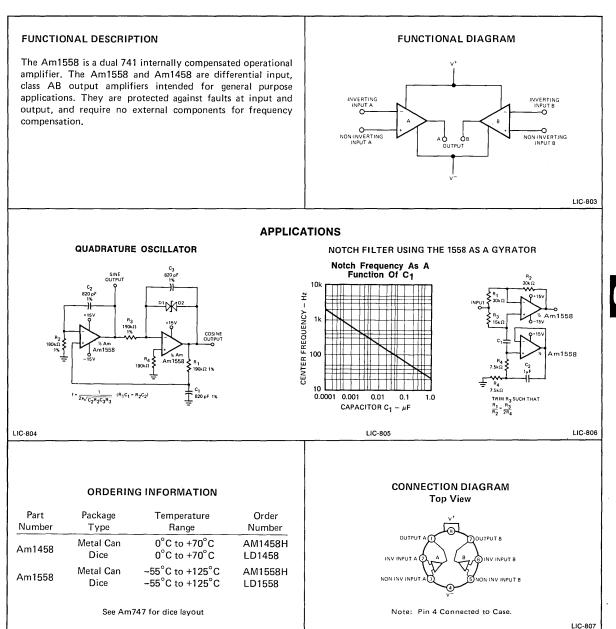

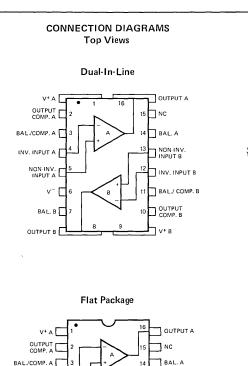

| Am741/741A/741C/741E<br>SSS741/741C<br>Am747/747A/747C/747E<br>SSS747/747C<br>Am748/748C<br>Am1501<br>Am1558/1458<br>LH2101A/LH2201A/<br>LH2301A | High-Performance Operational Amplifier         Dual Frequency-Compensated Operational Amplifier         Dual 741 Operational Amplifier | 6-70<br>6-64<br>6-77<br>6-64<br>6-84<br>6-90<br>6-95<br>6-99 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Special Functions – S                                                                                                                            | Section VII                                                                                                                            |                                                              |

| Am592<br>Am733/733C                                                                                                                              | Differential Video Amplifier<br>Differential Video Amplifier                                                                           |                                                              |

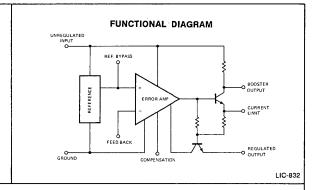

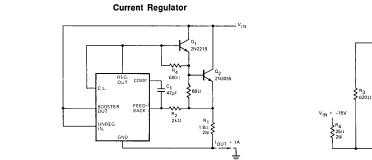

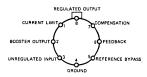

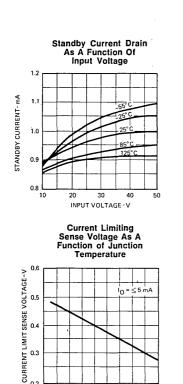

| Voltage Regulators -                                                                                                                             | Section VIII                                                                                                                           |                                                              |

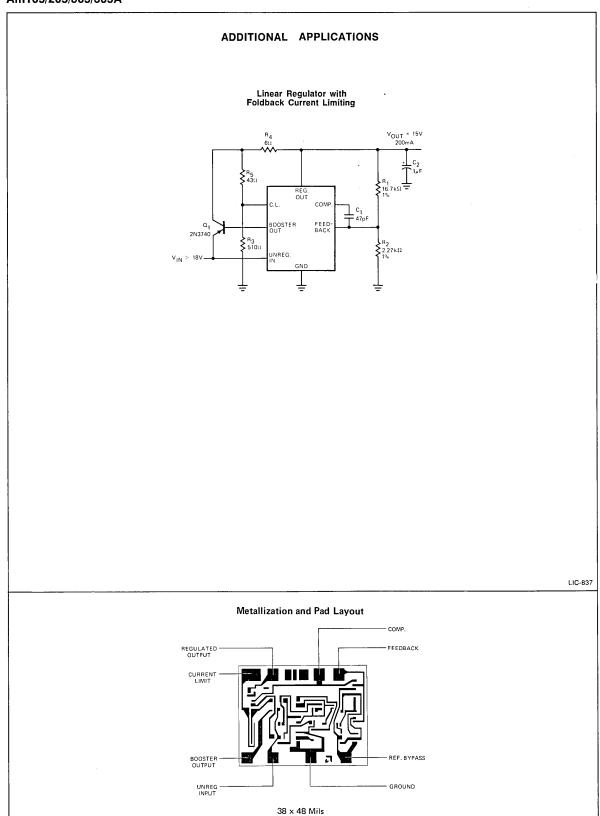

| Am105/205/305/305A<br>Am723/723C                                                                                                                 | Voltage Regulator                                                                                                                      |                                                              |

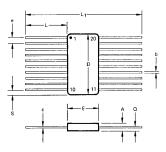

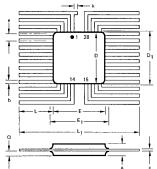

| Section IX                                                                                                                                       |                                                                                                                                        |                                                              |

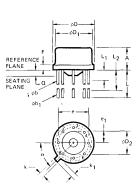

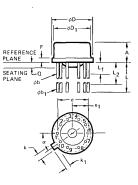

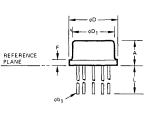

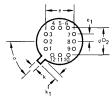

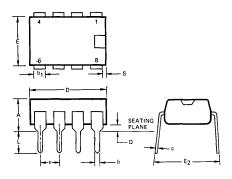

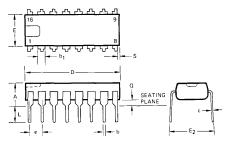

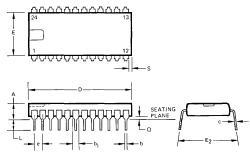

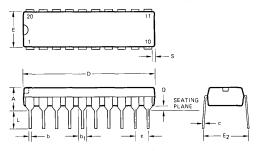

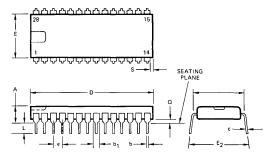

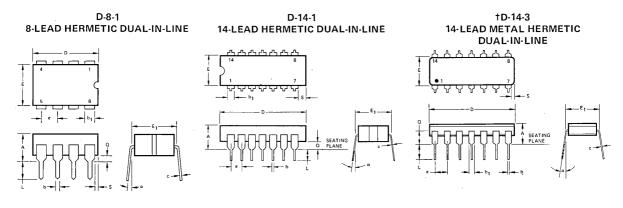

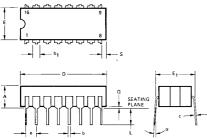

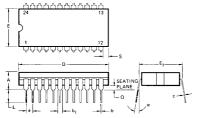

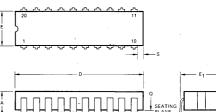

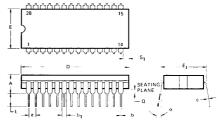

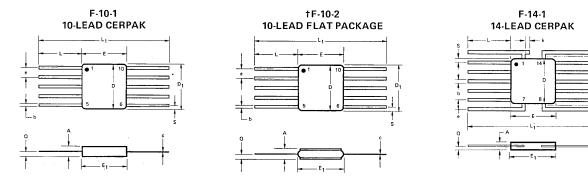

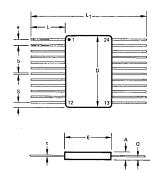

| Package Outlines                                                                                                                                 | · · · · · · · · · · · · · · · · · · ·                                                                                                  | 9-1<br>9-5                                                   |

# SELECTION GUIDE

### **OPERATIONAL AMPLIFIERS**

|                                         | UNCOMPENSATED<br>Page No. |                                                                        |  |  |

|-----------------------------------------|---------------------------|------------------------------------------------------------------------|--|--|

| LM101                                   | 6-1                       | General Purpose, 500nA IB, 5mV Vos                                     |  |  |

| LM748                                   | 6-84                      | General Purpose, 500nA IB, 5mV Vos                                     |  |  |

| LM101A                                  | 6-5                       | Improved General Purpose, 75nA I <sub>B</sub> ,                        |  |  |

|                                         | 0-5                       | 2mV Vos                                                                |  |  |

| AM1501                                  | 0.00                      |                                                                        |  |  |

| ANTSOT                                  | 6-90                      | Dual Improved General Purpose, 75nA                                    |  |  |

|                                         |                           | IB, 2mV Vos                                                            |  |  |

| LH2101A                                 | 6-99                      | Dual Improved General Purpose, 75nA                                    |  |  |

|                                         | }                         | IB, 2mV Vos                                                            |  |  |

| 725                                     | 6-59                      | Instrumentation, 100nA IB, 1mV Vos,                                    |  |  |

|                                         |                           | 5.0V/°C TCVIO                                                          |  |  |

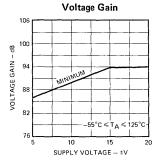

| SSS725                                  | 6-64                      | Improved Instrumentation, 80nA IB,                                     |  |  |

|                                         | 1.1                       | .5mV Vos, 1.0V/°C TCVIO                                                |  |  |

| LM108                                   | 6-18                      | Low Input Current Precision, 2nA IB,                                   |  |  |

|                                         | [ ·                       | 2mV Vos, 0.2nA IOS                                                     |  |  |

| LM108A                                  | 6-18                      | Low Input Current and Offset Voltage                                   |  |  |

|                                         | }                         | Precision, 2nA IB, 0.5mV Vos, 0.2nA                                    |  |  |

|                                         |                           | IOS, 5µV/°C TCVIO                                                      |  |  |

| 715                                     | 6-55                      | High Speed, 15V/µsec slew rate, 750nA                                  |  |  |

|                                         | { .                       | IB, 5mV Vos                                                            |  |  |

| INTERMA                                 |                           | OMPENSATED                                                             |  |  |

| 741                                     | 6-70                      | General Purpose, 500nA IB, 5mV Vos                                     |  |  |

| 741A,E                                  | 6-70                      | Improved General Purpose, 80nA I <sub>B</sub> ,                        |  |  |

| ( , , , , , , , , , , , , , , , , , , , | 0-70                      | $3mV$ Vos, $30nA$ $I_{OS}$ , $50\mu V/VPSRR$                           |  |  |

| SSS741                                  | 6.64                      |                                                                        |  |  |

| 747                                     | 6-64<br>6-77              | High Performance, 50nA IB, 2mV Vos                                     |  |  |

| /4/                                     | 6-77                      | Dual General Purpose, 500nA I <sub>B</sub> , 5mV                       |  |  |

| 747A,E                                  | 6-77                      | Vos                                                                    |  |  |

| 147A,E                                  | 6-77                      | Dual Improved General Purpose, 80nA                                    |  |  |

| 666747                                  | 0.04                      | I <sub>B</sub> , 3mV Vos, 30nA I <sub>OS</sub> , 50µV/VPSRR            |  |  |

| SSS747                                  | 6-64                      | Dual High Performance, 50nA IB, 2mV<br>Vos                             |  |  |

| AM1558                                  | C OF                      |                                                                        |  |  |

| AWI1556                                 | 6-95                      | Dual General Purpose, 500nA I <sub>B</sub> , 5mV                       |  |  |

| LM124                                   | 6-36                      | Vos                                                                    |  |  |

| LM124                                   |                           | Quad General Purpose, 150nA 1 <sub>B</sub> , 5mV                       |  |  |

| LIMI 24A                                | 6-36                      | Vos, Single or Dual Supply, 3 to 30V,                                  |  |  |

| LM148                                   | 6.41                      | 1mW/op amp at +5V                                                      |  |  |

| LM148                                   | 6-41                      | Quad 741, 500nA IB, 5mV Vos                                            |  |  |

| LW149                                   | 6-41                      | Quad Decompensated, 500nA I <sub>B</sub> , 5mV                         |  |  |

|                                         |                           | Vos AV(min.) = 5                                                       |  |  |

| LM107                                   | 6-14                      | Improved General Purpose, 75nA IB,                                     |  |  |

| 1 1 1 1 1 1 1 1                         | 0.00                      | 2mV Vos                                                                |  |  |

| LM112                                   | 6-26                      | Low Input Current Precision, 2nA IB,                                   |  |  |

| 1                                       | 0.51                      | 2mV Vos                                                                |  |  |

| LM216                                   | 6-51                      | Very Low Input Current Precision,                                      |  |  |

|                                         |                           | 150pA I <sub>B</sub> , 10mV Vos                                        |  |  |

| LM216A                                  | 6-51                      | Very Low Input Current Precision, 50pA                                 |  |  |

|                                         |                           | IB, 3mV Vos                                                            |  |  |

| LM118                                   | 6-30                      | High Speed, 50V/µsec slew rate, 4mV                                    |  |  |

|                                         | 1                         | Vos, 250nA I <sub>B</sub>                                              |  |  |

| LF155                                   | 6-43                      | FET Input General Purpose, 5mV Vos,                                    |  |  |

|                                         |                           | 20pA I <sub>OS</sub> , 100pA I <sub>B</sub>                            |  |  |

| LF155A                                  | 6-43                      | FET Input General Purpose, 2mV Vos,                                    |  |  |

| 1                                       | ł                         | 5μV/°C TC V <sub>10</sub> , 10pA I <sub>OS</sub> , 50pA I <sub>B</sub> |  |  |

| LF156                                   | 6-43                      | FET Input Wideband, 5mV Vos, 20pA                                      |  |  |

|                                         | {                         | I <sub>OS</sub> , 100pA I <sub>B</sub> , 7.5V/µsec SR                  |  |  |

| LF156A                                  | 6-43                      | FET Input Wideband, $2mV Vos$ , $5\mu V/^{\circ}C$                     |  |  |

| 1                                       | ł                         | TC V <sub>10</sub> , 10pA I <sub>OS</sub> , 50pA I <sub>B</sub> , 10V/ |  |  |

|                                         |                           | μsec SR                                                                |  |  |

| LF157                                   | 6-43                      | FET Input Wideband Decompensated,                                      |  |  |

|                                         |                           | 5mV Vos, 20pA I <sub>OS</sub> , 100pA I <sub>B</sub> , 30V/            |  |  |

| 1                                       | 1                         | $\mu$ sec SR (A <sub>V</sub> = 5)                                      |  |  |

| LF157A                                  | 6-43                      | FET Input Wideband Decompensated,                                      |  |  |

| 1                                       | 1                         | 2mV Vos, 5µV/°C TC V10, 10pA 105,                                      |  |  |

|                                         | 1                         | $50pA I_B, 40V/\mu sec SR (A_V = 5)$                                   |  |  |

| L                                       | L                         | L                                                                      |  |  |

### VOLTAGE FOLLOWERS Page No.

| LM102 | 6-10 | Low Input Current, High Speed, 10nA IB, 5mV Vos, 20V/ $\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

|-------|------|----------------------------------------------------------------------------------------------------------------------------------|

| LM110 | 6-22 | Improved Low Input Current, High Speed, 3nA IB, 4mV Vos, 20V/µsec slew rate, $10^{10}\Omega$ Rin                                 |

# **VOLTAGE COMPARATORS**

Page No.

|   | LM111  | 2-5  | General Purpose, 100nA IB, 3mV Vos,              |

|---|--------|------|--------------------------------------------------|

|   |        |      | 250ns Response Time, 50V and 50mA                |

|   | i .    |      | Output                                           |

|   | LH2111 | 2-35 | Dual General Purpose, 100nA IB, 3mV              |

|   |        |      | Vos, 250ns Response Time, 50V and                |

|   |        |      | 50mA Output                                      |

|   | AM1500 | 2-31 | Dual General Purpose, 100nA 1 <sub>B</sub> , 3mV |

|   |        |      | Vos, 250ns Response Time, 50V and                |

|   |        |      | 50mA Output                                      |

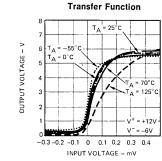

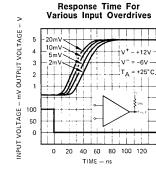

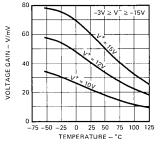

|   | LM106  | 2-1  | High Speed, 20µA I <sub>B</sub> , 2mV Vos, 40ns  |

|   |        |      | Response Time, 24V and 100mA Output              |

|   | LM119  | 2-9  | Dual General Purpose, 500nA IB, 4mV              |

|   |        |      | Vos, 80ns Response Time, 35V and 25mA            |

|   |        |      | Output, +5 or +15V Supply                        |

|   | LM139  | 2-13 | Quad General Purpose, 100nA IB, 2mV              |

|   | LM139A | 2-13 | Vos, Single or Dual Supply 2 to 36V,             |

|   |        |      | 1mW/comp. at +5V                                 |

|   | AM685  | 2-19 | Very Fast ECL Output, 10µA I <sub>B</sub> , 2mV  |

|   |        |      | Vos, 6.5ns Response Time                         |

| Ì | AM686  | 2-27 | Very Fast TTL Output, 10µA I <sub>B</sub> , 2mV  |

|   |        |      | Vos, 12ns Response Time                          |

|   | AM687  | 2-29 | Dual Very Fast ECL Output, 10µA I <sub>B</sub> , |

|   |        |      | 2mV Vos, 6.5ns Response Time                     |

# VOLTAGE REGULATORS

Page No.

| 723   | 8-5 | General Purpose, 2-37V Output, 0.15%   |

|-------|-----|----------------------------------------|

|       |     | load reg., 50V input, 150mA Output     |

| LM105 | 8-1 | General Purpose, 4.5-40V Output, 0.05% |

|       |     | load reg., 50V input, 12mA Output      |

### DATA CONVERSION PRODUCTS Page No.

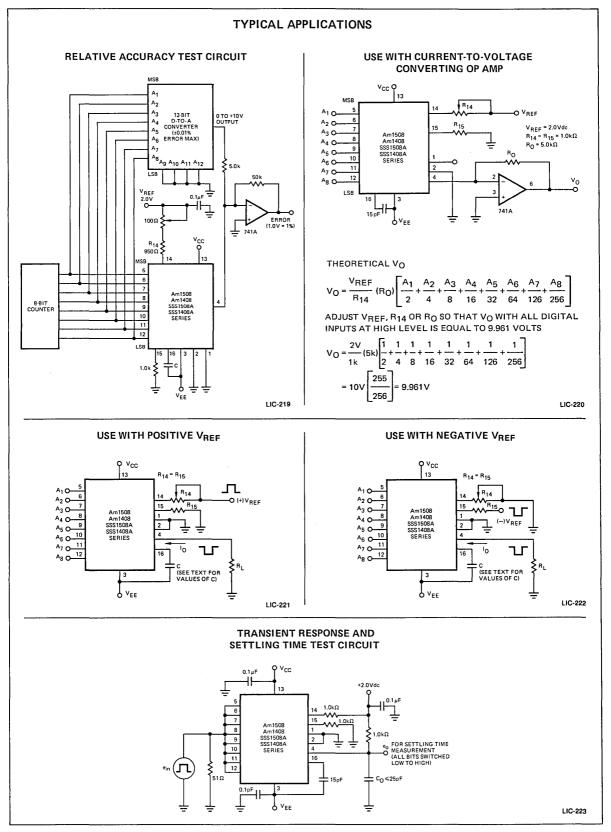

| AM1508   | 3-14 | 8-Bit Multiplying D-to-A Converter, Ac-<br>curacy 0.19%, Settling Time 300nsec typ. |

|----------|------|-------------------------------------------------------------------------------------|

| SSS1508A | 3-14 | 8-Bit Multiplying D-to-A Converter, Ac-                                             |

|          |      | curacy 0.1%, Settling Time 135nsec                                                  |

| DAC-08   | 3-1  | 8-Bit High-Speed Multiplying D/A Converter                                          |

| AM6070   | 3-28 | Companding D-to-A Converter for Control                                             |

|          | 1    | Systems                                                                             |

| AM6071   | 3-40 | Companding D-to-A Converter for Control                                             |

|          | ļ    | Systems                                                                             |

| AM6072   | 3-52 | Companding D-to-A Converter for PCM                                                 |

| 1        |      | Communication Systems                                                               |

| AM6073   | 3-64 | Companding D-to-A Converter for PCM                                                 |

|          | ļ    | Communication Systems                                                               |

| AM6080   | 3-76 | Microprocessor System Compatible 8-Bit                                              |

| · ·      |      | High-Speed Multiplying D/A Converter                                                |

| AM6081   | 3-84 | Microprocessor System Compatible 8-Bit                                              |

|          |      | High-Speed Multiplying D/A Converter                                                |

| LF198,   | 3-7  | Monolithic Sample and Hold Circuits                                                 |

| 298, 398 |      |                                                                                     |

| AM2502,  | 3-18 | 8-Bit/12-Bit Successive Approximation                                               |

| 03, 04   |      | Registers                                                                           |

| 1        |      |                                                                                     |

# **SELECTION GUIDE (Cont.)**

# LINE DRIVERS

| DUAL DIF                                   | ERENTIAL                                                                                                 | Use With            |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------|--|

| 75109                                      | Open collector differential outputs<br>typical current 6mA, inhibit controls                             | 75107B<br>75108B    |  |

| 75110                                      | 12mA output current version of<br>Am75109                                                                | 75107B<br>75108B    |  |

| 8830                                       | Designed for single 5.0V supply<br>operation                                                             | 7820 or<br>7820A    |  |

| 8831                                       | Dual differential device which may also<br>be used as a quad single-ended driver.<br>Three-state output. | 9615 or<br>2615     |  |

| 8832                                       | Similar to 8831 but no V <sub>CC</sub> clamp<br>diodes                                                   | 9615 or<br>2615     |  |

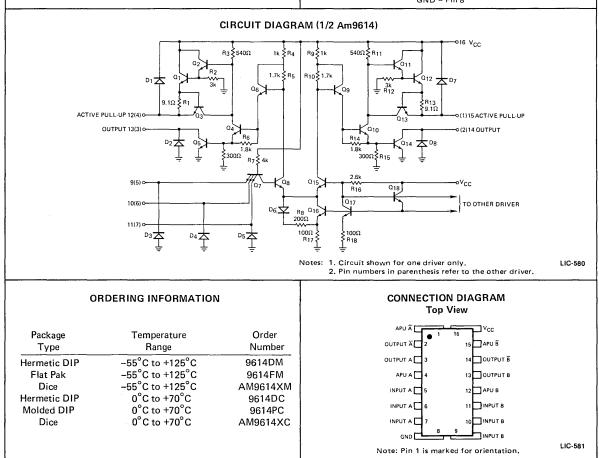

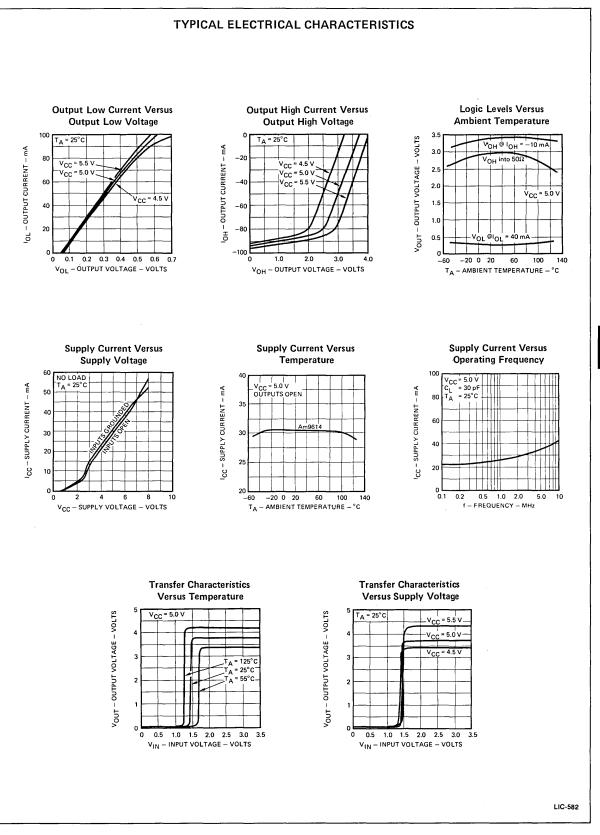

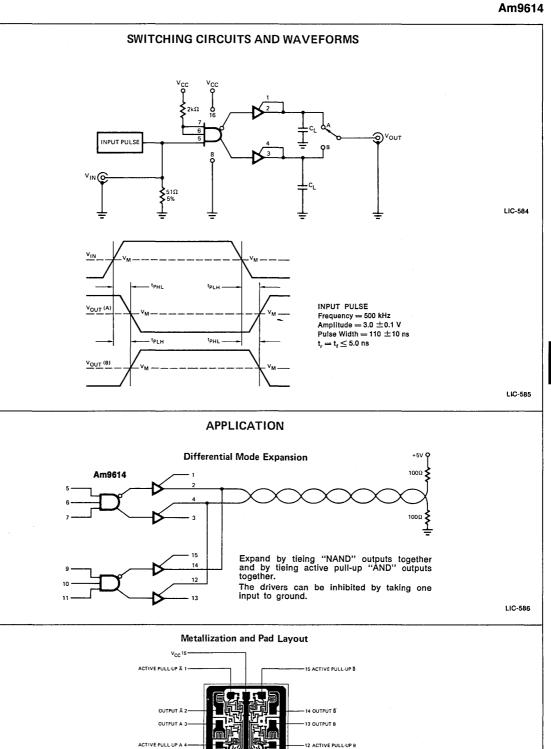

| 9614                                       | 5 volt supply driver with complementary<br>outputs                                                       | 9615                |  |

| 9621                                       | 200mA transient capability with $130\Omega$ back matching resistor                                       | 9620                |  |

| DIFFEREN<br>FEDERAL                        | TIAL EIA RS-422,<br>STD 1020                                                                             |                     |  |

| 26LS31                                     | Quad, high-speed, low output skew                                                                        | 26LS32 or           |  |

| 26LS30                                     | Dual, high output CMR                                                                                    | 26LS33              |  |

| SINGLE EN                                  | NDED                                                                                                     |                     |  |

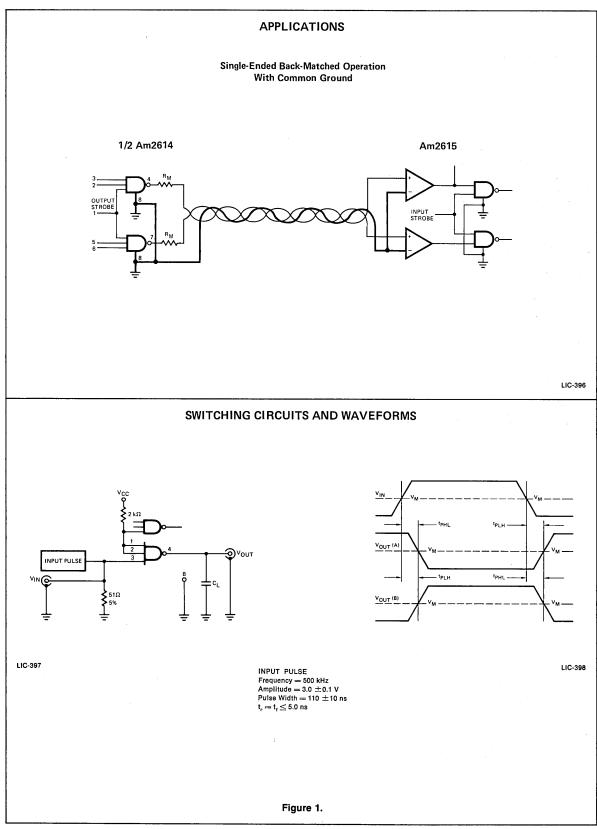

| 2614                                       | High-speed quad driver for multi-channel,<br>common ground operation.                                    | 2615                |  |

| SINGLE EN                                  | IDED, EIA RS-232-C                                                                                       |                     |  |

| 1488                                       | Quad EIA RS-232C driver (14 pins)                                                                        | 1489/<br>1489A      |  |

| 2616                                       | Quad 16-pin driver for EIA RS-232C,<br>CCITT V.24 and MIL-188C interface                                 | 2617                |  |

| 9616                                       | Triple EIA RS-232C driver (14 pins)                                                                      | 9617                |  |

| SINGLE ENDED, EIA RS-423, FEDERAL STD 1030 |                                                                                                          |                     |  |

| 26LS29<br>26LS30                           | Quad, three-state<br>Quad, mode control                                                                  | 26LS32 or<br>26LS33 |  |

# **BUS BUFFERS/DRIVERS**

|         |                                                                                     | t <sub>pd</sub><br>(TYP) | I <sub>OL</sub><br>(MAX) |

|---------|-------------------------------------------------------------------------------------|--------------------------|--------------------------|

| 25LS240 | Inverting octal buffer/driver with three-                                           | 10                       | 48                       |

| 74LS240 | state output                                                                        | 10                       | 24                       |

| 74S240  |                                                                                     | 4.5                      | 68                       |

| 81LS96  |                                                                                     | 9.0                      | 16                       |

| 25LS241 | Non-inverting octal buffer/driver with                                              | 12                       | 48                       |

| 74LS241 | three-state output                                                                  | 12                       | 24                       |

| 74S241  |                                                                                     | 6.0                      | 68                       |

| 81LS95  |                                                                                     | 12                       | 16                       |

| 25LS242 | Inverting buffer/driver with two quad                                               | 10                       | 48                       |

| 74LS242 | data paths connected input-to-output                                                | 10                       | 24                       |

| †74S242 |                                                                                     | 4.5                      | 68                       |

| 25LS243 | Non-inverting buffer/driver with two                                                | 12                       | 48                       |

| 74LS243 | quad data paths connected input-to-                                                 | 12                       | 24                       |

| †74S243 | output                                                                              | 6.0                      | 68                       |

| 25LS244 | Non-inverting octal buffer/driver with                                              | 12                       | 48                       |

| 74LS244 | three-state output and two inverting                                                | 12                       | 24                       |

| 74S244  | enables                                                                             | 6.0                      | 68                       |

| 81LS97  |                                                                                     | 12                       | 16                       |

| 81LS98  | Inverting octal buffer/driver with three-<br>state output and two inverting enables | 9.0                      | 16                       |

Ē

----

-

†In development

# LINE RECEIVERS

| DUAL DIF                                      | Use With                                                                                             |                   |  |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------|--|

| 3603                                          | Receiver with differential input to detect signals > 25mV. Three-state outputs.                      | 75110             |  |

| 75107B                                        | Totem-pole TTL output version of<br>Am363                                                            | 75109 or<br>75110 |  |

| 75108B                                        | Open collector TTL output version of<br>Am363                                                        | 75109 or<br>75110 |  |

| 8820                                          | Designed for ±15V common mode<br>using 5.0V supply                                                   | 8830              |  |

| 8820A                                         | Higher speed, tighter spec 8820                                                                      | 8830              |  |

| 9615                                          | ±15 volt common mode, 5 volt supply receivers with uncommitted collector and active pull-up controls | 9614              |  |

| 9620                                          | ±15 volt common mode receiver with<br>direct and attenuated inputs                                   | 9621              |  |

| QUAD DIF                                      | FERENTIAL                                                                                            |                   |  |

| 26LS33                                        | ±15 volt common mode, 5 volt supply, three-state output                                              | 26LS31            |  |

| QUAD DIF                                      | FERENTIAL EIA RS-422,<br>STD 1020                                                                    |                   |  |

| 26LS32                                        | ±7 volt common mode, 5 volt supply, three-state output                                               | 26LS31            |  |

| SINGLE EN                                     | NDED                                                                                                 |                   |  |

| 2615                                          | Receiver for 3 volt single-ended TTL level data                                                      | 2614              |  |

| SINGLE EN                                     | NDED, EIA RS-232-C                                                                                   |                   |  |

| 1489                                          | Quad EIA RS-232C receiver with input<br>threshold hysteresis                                         | 1488              |  |

| 1489A                                         | Higher threshold version of Am1489                                                                   | 1488              |  |

| 2617                                          | Quad EIA RS-232 receiver specified<br>over military temperature range (same<br>pinout as Am1489A)    | 2616              |  |

| 9617                                          | Triple EIA RS-232 receiver with<br>adjustable hysteresis                                             | 9616              |  |

| SINGLE ENDED, EIA RS-423,<br>FEDERAL STD 1030 |                                                                                                      |                   |  |

| 26LS32                                        | ±7 volt common mode, 5 volt supply,<br>three-state output                                            | 26LS29<br>26LS30  |  |

# **SELECTION GUIDE (Cont.)**

# SPECIAL FUNCTIONS

| 1 | TIMERS |                                    |

|---|--------|------------------------------------|

| ļ | 555    | Single, Precision oscillator/timer |

|   | 556    | Dual version 555                   |

# MOS MEMORY

| DRIVERS   | DRIVERS                                                       |  |  |  |  |  |

|-----------|---------------------------------------------------------------|--|--|--|--|--|

| 0026      | Dual 5MHz Two-Phase MOS clock driver                          |  |  |  |  |  |

| 0056      | 0026 with added V <sub>BB</sub> terminal                      |  |  |  |  |  |

| SENSE AMP | LIFIERS                                                       |  |  |  |  |  |

| 3604      | Differential input for signals > 10mV, Three-state<br>outputs |  |  |  |  |  |

| 75207     | 75207 Totem-pole TTL output 3604                              |  |  |  |  |  |

| 75208     | Open-collector 3604                                           |  |  |  |  |  |

# **MOS-MICROPROCESSOR INTERFACE CIRCUITS**

| 8080A/9080A |                                                            |

|-------------|------------------------------------------------------------|

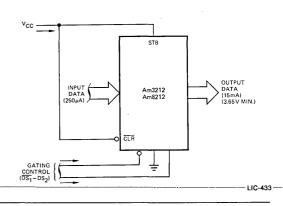

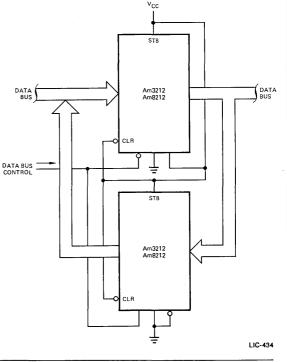

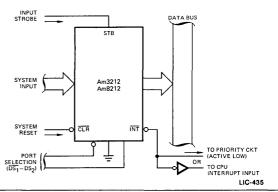

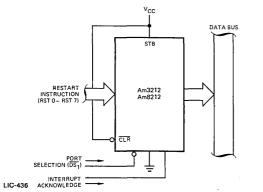

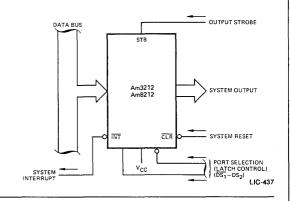

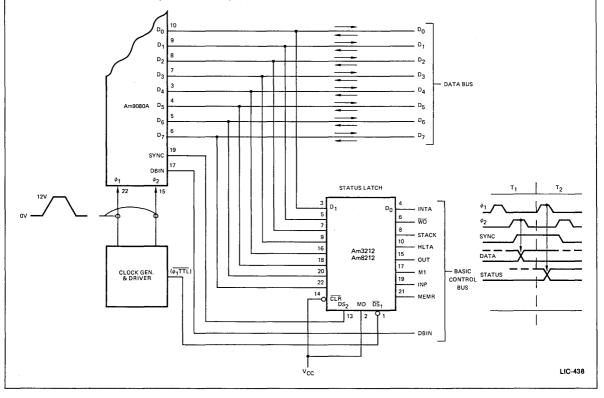

| 8212        | 8-Bit input/output port, with storage                      |

| 8216        | 4-Bit parallel bidirectional bus driver                    |

| 8224        | Clock generator and driver                                 |

| 8226        | Inverting version 8216                                     |

| 8228        | System controller and bus driver                           |

| 8238        | System controller and bus driver with extended<br>IOW/MEMW |

| 8303B       | Two 8226's in one 20 pin package                           |

| 8304B       | Two 8216's in one 20 pin package                           |

# **BUS TRANSCEIVERS**

| Device    | Output        | Function                                   | Hysteresis | Sp <del>ee</del> d<br>(Note 1) | Comments                                        |

|-----------|---------------|--------------------------------------------|------------|--------------------------------|-------------------------------------------------|

| QUAD      | <u> </u>      |                                            |            |                                |                                                 |

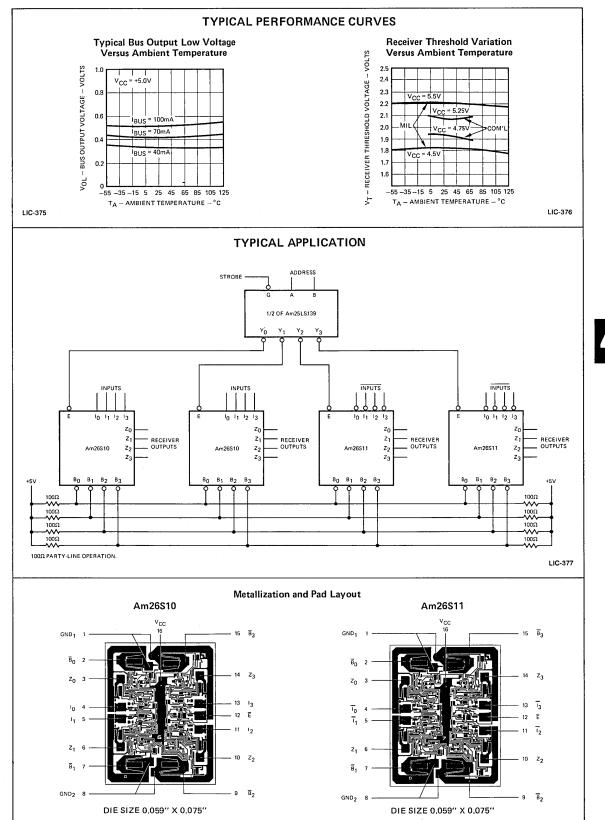

| Am26S10   | 100mA-O.C.    | Inverting                                  | No         | 20ns                           | SN55/75138 pin out                              |

| Am26S11   | 100mA-O.C.    | Non-Inverting to bus;<br>Inverting off bus | No         | 22ns                           | Same as Am26S10 except non-inverting to bus     |

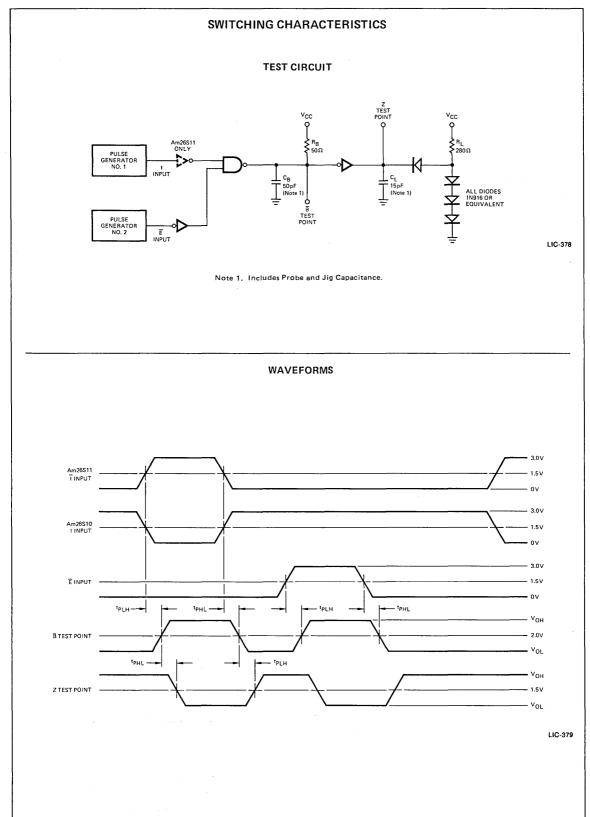

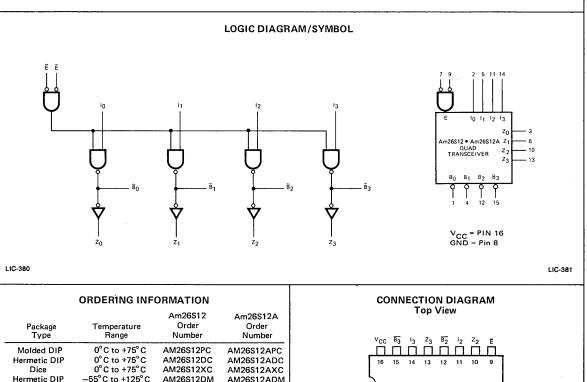

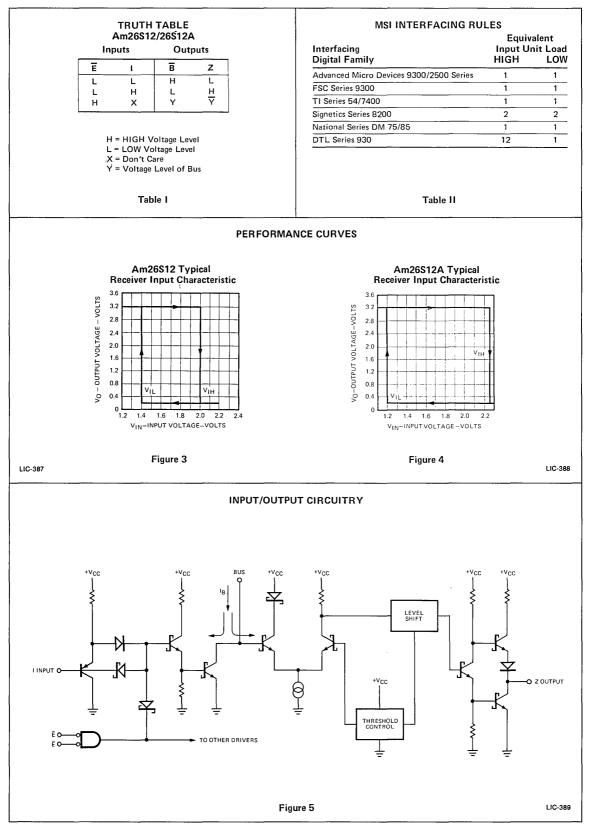

| Am26S12   | 100mA-O.C.    | Inverting                                  | Yes-0.6V   | 32ns                           | Same pin out as DS78/8838 and 8T38              |

| Am26S12A  | 100mA-O.C.    | Inverting                                  | Yes-1.05V  | 32ns                           | Wider threshold Am26S12                         |

| Am2905    | 100mA-O.C.    | Inverting                                  | No         | 31ns<br>(Note 2)               | Has 2-input multiplexer                         |

| Am2906    | 100mA-O.C.    | Inverting                                  | No         | 31ns<br>(Note 2)               | Has 2-input multiplexer and parity              |

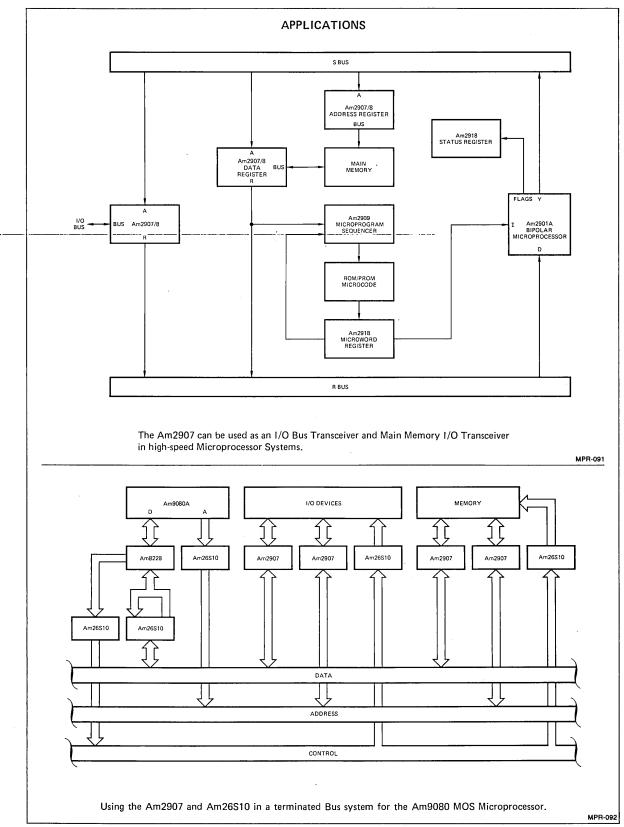

| Am2907    | 100mA-O.C.    | Inverting                                  | No         | 31ns<br>(Note 2)               | Includes parity, 2.0V receiver V <sub>TH</sub>  |

| Am2908    | 100mA-O.C.    | Inverting                                  | No         | 31ns<br>(Note 2)               | Includes parity, 1.5V receiver V <sub>TH</sub>  |

| Am2915A   | 48mA/3-St.    | Inverting                                  | No         | 31ns<br>(Note 2)               | Has 2-input multiplexer                         |

| Am2916A   | 48mA/3-St.    | Inverting                                  | No         | 31ns<br>(Note 2)               | Has 2-input multiplexer and parity              |

| Am2917A   | 48mA/3-St.    | Inverting                                  | No         | 31ns<br>(Note 2)               | Includes parity                                 |

| Am3216    | 50mA/3-St.    | Non-Inverting                              | No         | 34ns                           | Same as 8216 except different A.C. loading spec |

| Am3226    | 50mA/3-St.    | Inverting                                  | No         | 30ns                           | Same as 8216 except different A.C. loading spec |

| Am3448A   | 48mA/3-StO.C. | Non-Inverting                              | Yes        | 32ns                           | IEEE 488 compatible                             |

| Am78/8838 | 50mA-O.C.     | Inverting                                  | No         | 38ns                           | Same pin out and function as Am26S12A and 8T38  |

| Am8T26A   | 48mA/3-St.    | Inverting                                  | No         | 19ns                           | V <sub>OH</sub> MOS compatible                  |

| Am8T28    | 48mA/3-St.    | Non-Inverting                              | No         | 25ns                           | V <sub>OH</sub> MOS compatible                  |

| Am8216    | 50mA/3-St.    | Non-Inverting                              | No         | 34ns                           | Similar to 8T28                                 |

| Am8226    | 50mA/3-St.    | Non-Inverting                              | No         | 30ns                           | Similar to 8T26A                                |

| OCTAL     |               | ······                                     |            |                                |                                                 |

| Am8303B   | 48mA/3-St.    | Inverting                                  | No         | 14ns                           | Same as two 8226's in one 20 pin package        |

| Am8304B   | 48mA/3-St.    | Non-Inverting                              | No         | 24ns                           | Same as two 8216's in one 20 pin package        |

Notes: 1. Typical delay at 28°C for input to bus plus receiver to output.

2. Bus enable to bus plus bus to receiver output. All parts include register or driver plus receiver with latch.

# **SELECTION GUIDE (Cont.)**

### MONOSTABLES (ONE SHOTS)

| Device No. | Description                                                                                                                               | Dual | Retrig-<br>gerable | Reset<br>Table | Initial<br>Accuracy<br>% | Min.<br>Output<br>t <sub>pw</sub> (ns) | Variati | Width<br>on (%)<br>. V <sub>CC</sub> | Power<br>Dissipation<br>(mW typ.) | No.<br>Package<br>Leads |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|----------------|--------------------------|----------------------------------------|---------|--------------------------------------|-----------------------------------|-------------------------|

| Am2600     | $t_{pw} = 55$ ns to $\infty$ , with guaranteed $< 1\%$ change over temperature range                                                      | x    | ×                  | x              | ±10                      | 45                                     | ±0.5    | ±1.5                                 | 95                                | 14                      |

| Am2602     | $t_{pw} = 55ns$ to $\infty$ , with guaranteed < 1% change over temperature range                                                          | x    | x                  | х              | ±10                      | 45                                     | ±0.5    | ±1.5                                 | 175                               | 16                      |

| Am26L02    | Low-Power version 2602, $t_{pw} = 100$ ns to $\infty$                                                                                     | x    | ×                  | х              | ±10                      | 110                                    | ±0.3    | ±1.0                                 | 50                                | 16                      |

| Am26L123   | Low-Power version 26123, $t_{pw} = 120$ ns to $\infty$                                                                                    | x    | ×                  | х              | ±10                      | 120                                    | ±0.3    | ±1.0                                 | 60                                | 16                      |

| Am26S02    | High speed Schottky version 2602, $t_{pw} = 28ns$ to $\infty$                                                                             | x    | x                  | x              | ±5.0                     | 33                                     | ±0.4    | ±1.5                                 | 240                               | 16                      |

| Am26123    | $t_{pw} = 45ns$ to $\infty$ , with guaranteed $< 1\%$<br>change over temperature range. Output<br>stability latch improves noise immunity | x    | x                  | x              | ±10                      | 45                                     | ±0.5    | ±0.5                                 | 230                               | 16                      |

| Am54/74123 | Same as 26123, except no output latch, no $\Delta t_{pw}$ guarantee                                                                       | x    | ×                  | х              | ±10                      | 45                                     | ±2.7    | ±1.0                                 | 230                               | 16                      |

| Am54/74221 | Schmitt-trigger input                                                                                                                     | х    |                    | х              | ±7.0                     | 30                                     | ±0.3    | ±0.3                                 | 130                               | 16                      |

| Am9600     | Same as 2600, except no $\Delta t_{pw}$ guarantee                                                                                         |      | x                  | х              | ±10                      | 50                                     | ±1.5    | ±1.5                                 | 95                                | 14                      |

| Am9601     | Non-resettable version of 9600, $t_{pw} = 55$ ns to $\infty$                                                                              |      | x                  |                | ±10                      | 45                                     | ±2.7    | ±1.0                                 | 95                                | 14                      |

| Am9602     | Same as 2602, except $t_{pw} = 60ns$ to $\infty$ , no $\Delta t_{pw}$ guarantee                                                           | x    | ×                  | x              | ±10                      | 50                                     | ±1.5    | ±1.5                                 | 175                               | 16                      |

| Am96L02    | Same as 26L02, except $t_{pw}$ guaranteed <1.6% change over temperature range                                                             | x    | ×                  | x              | ±10                      | 110                                    | ±0.3    | ±0.5                                 | 50                                | 16                      |

# INDUSTRY CROSS REFERENCE

|                     | AMD*                                        | Fairchild   | Intel | Motorola       | National       | Signetics | Texas<br>Instruments |  |

|---------------------|---------------------------------------------|-------------|-------|----------------|----------------|-----------|----------------------|--|