ההההההההההההההההההה הההההההההההההההההההה הההההההההההההההההההההה הההההההההההההההההההה הההההההההההההההההההה הההההההההההההההההההה

# **Advanced Micro Devices**

# The Designers' Guide

Copyright © 1979 by Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The company assumes no responsibility for the use of any circuits described herein.

# The Designers' Choice

Advanced Micro Devices, the newest giant among the major semiconductor manufacturers, offers a product portfolio numbering over 600 complex, monolithic, integrated circuits with emphasis on microprocessors, memories and their related peripheral circuits.

Included herein are selected data sheets and application notes on several recently introduced key AMD<sup>®</sup> circuits. And, a full set of various indexes and cross reference charts.

Advanced Micro Devices, the Designers' Choice, the company with the commitment – A Commitment to Excellence – where all devices are manufactured in compliance with MIL-STD-883, MIL-M-38510 and MIL-Q-9858.

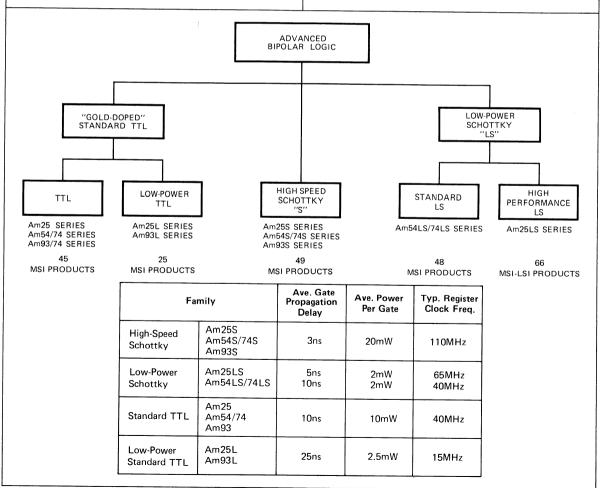

# **TABLE OF CONTENTS**

| PRODUCT GUIDES AND CROSS REFERENCES:                                       |     |

|----------------------------------------------------------------------------|-----|

| Interface Circuits                                                         |     |

| Linear Circuits                                                            |     |

| Bipolar Logic Circuits                                                     |     |

| Functional Selector Guide 1                                                |     |

| AMD® Selection Guide                                                       | -33 |

| MICROPROCESSORS:                                                           |     |

| Am2903                                                                     | 2 1 |

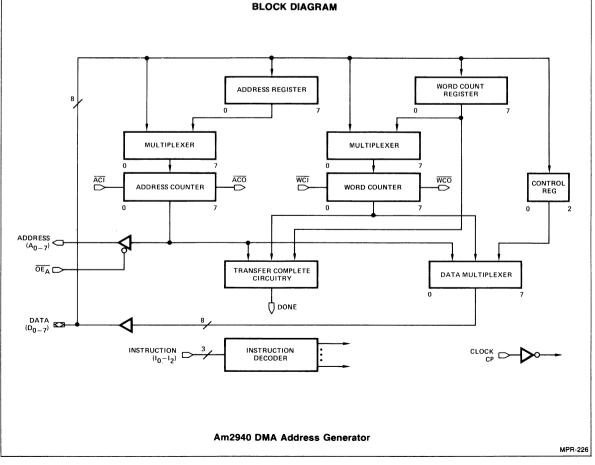

| Am2940                                                                     |     |

| Am2942                                                                     |     |

| Am8085A                                                                    |     |

|                                                                            | 47  |

| MEMORIES:                                                                  |     |

| Am9708/Am2708                                                              | -   |

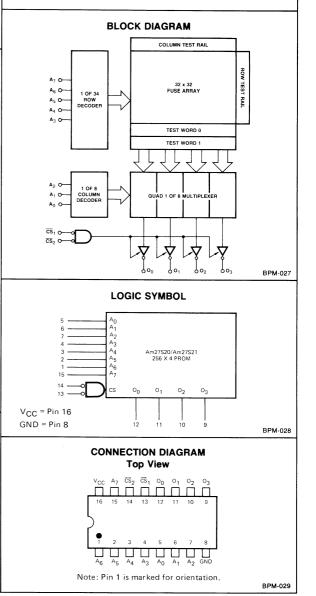

| Am27S18 • Am27S19                                                          |     |

| Am27S20 • Am27S21                                                          |     |

| Am27S12 • Am27S13                                                          |     |

| Am27S15                                                                    |     |

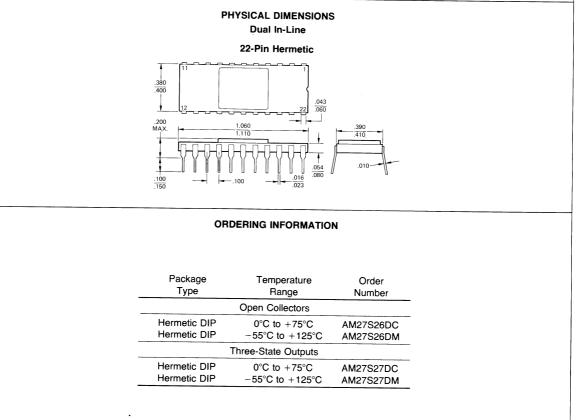

| Am27S26 • Am27S27                                                          |     |

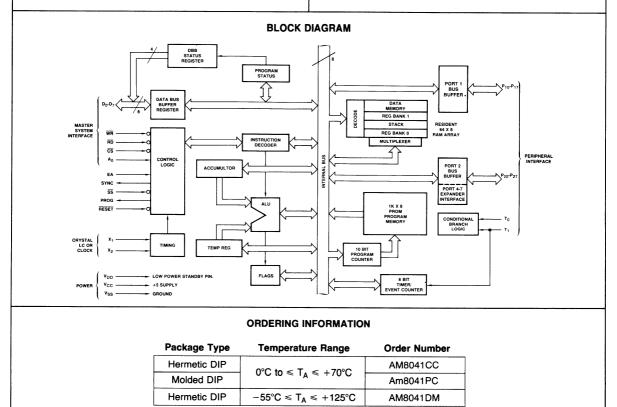

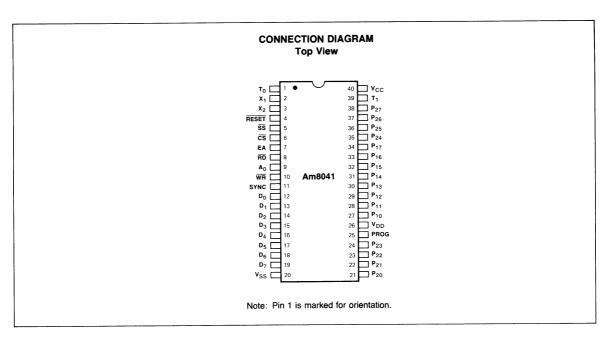

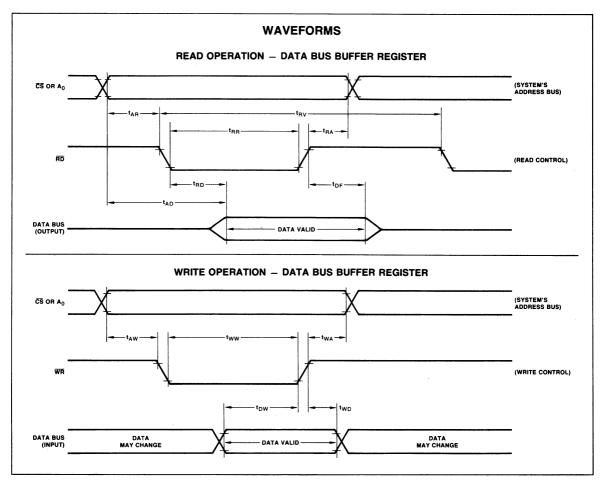

| Am8041                                                                     |     |

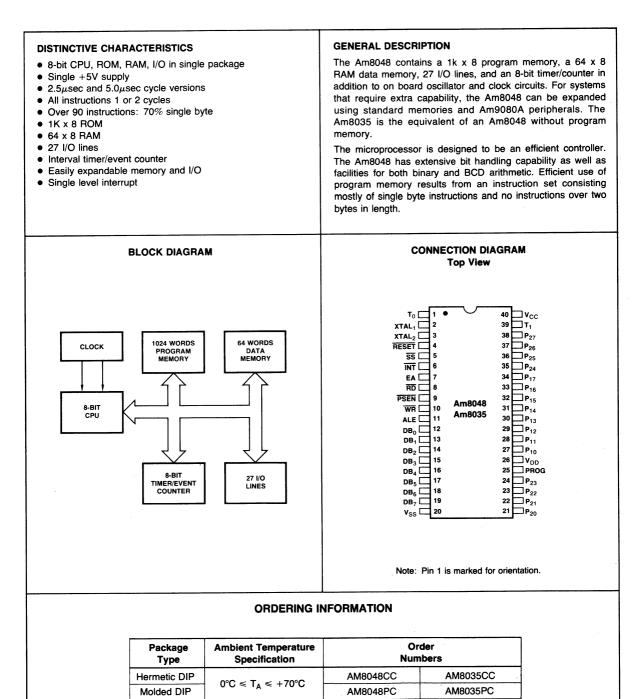

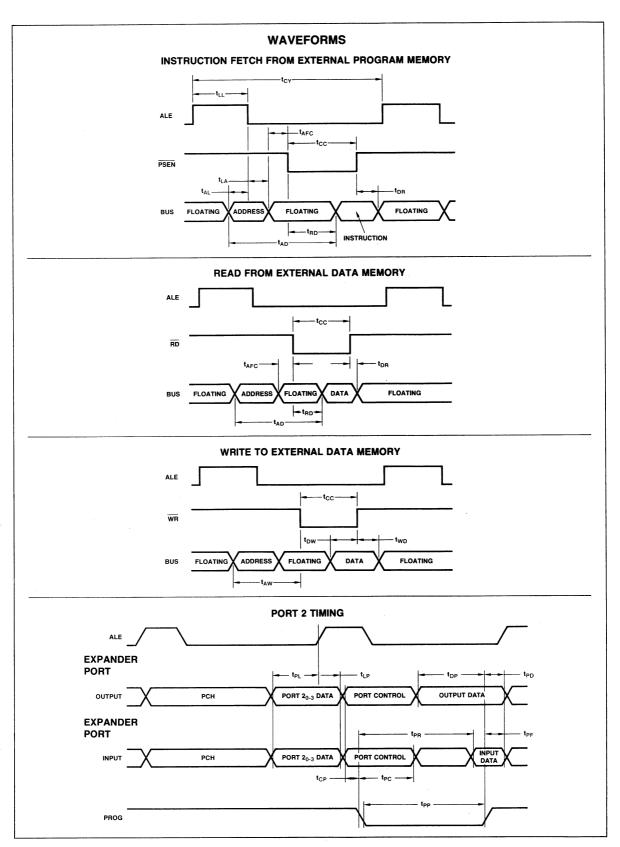

| Am8048/8035                                                                |     |

| Am8253                                                                     |     |

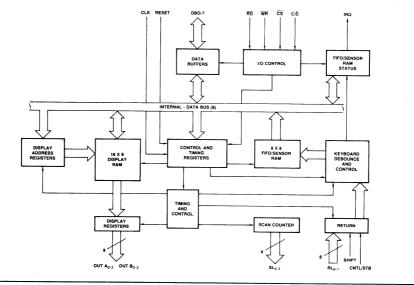

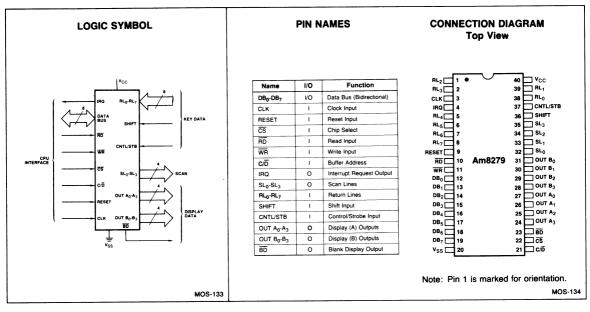

| Am8279/Am8279-5                                                            |     |

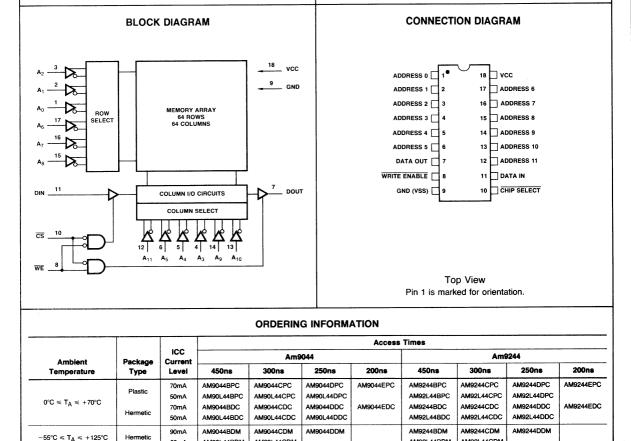

| Am9044 • Am9244                                                            |     |

| Am9114 • Am9124                                                            |     |

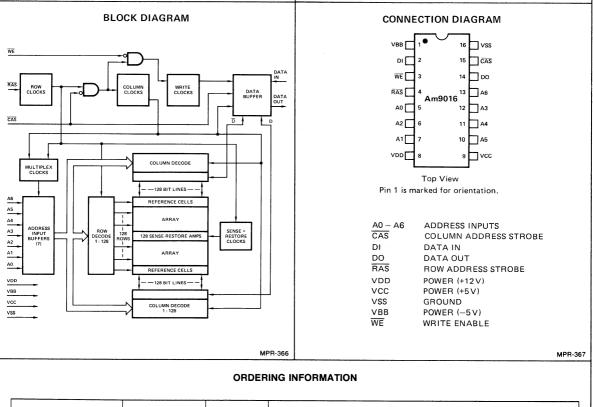

| Am9016                                                                     |     |

| Am9218/8316E                                                               |     |

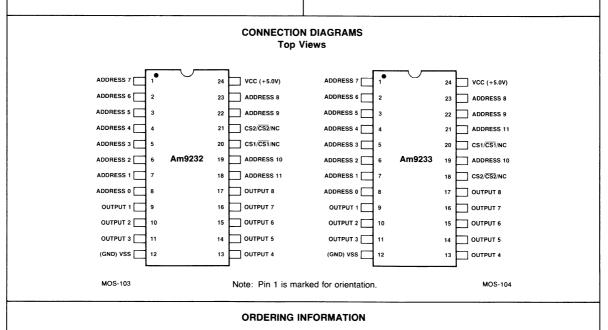

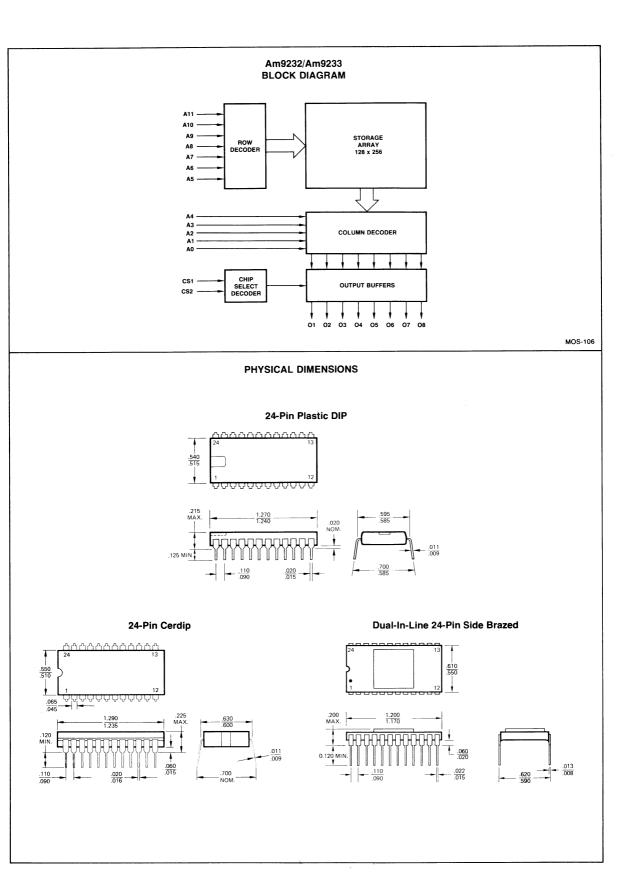

| Am9232 • Am9233                                                            | -75 |

| SUPPORT AND PERIPHERAL CIRCUITS:                                           |     |

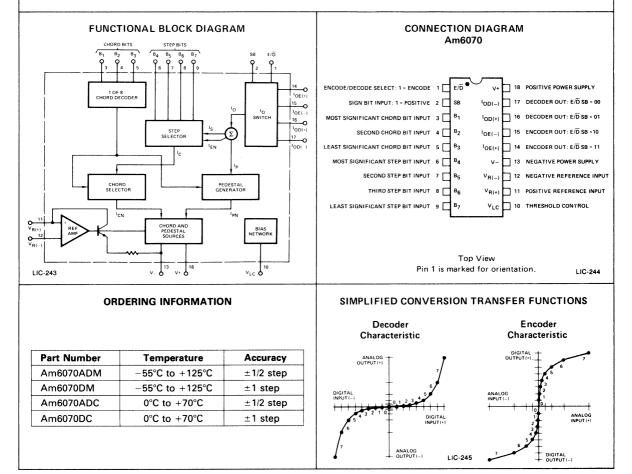

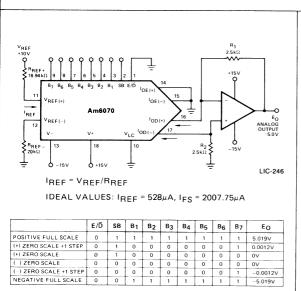

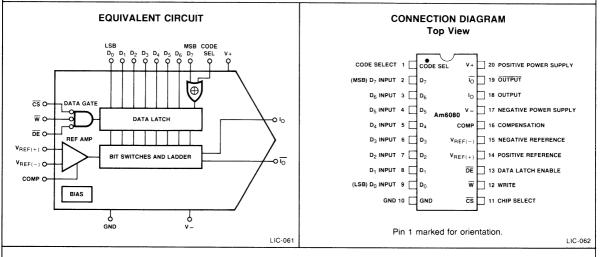

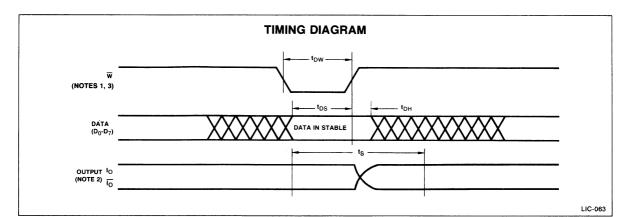

| Am6070                                                                     | 4-1 |

| Am6080                                                                     |     |

| Am6081                                                                     |     |

| Am9511                                                                     |     |

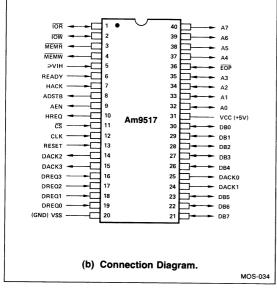

| Am9517                                                                     |     |

| Am9519                                                                     | -59 |

|                                                                            |     |

| APPLICATIONS:                                                              |     |

| Algorithm Details for the Am9511 Arithmetic Processing Unit                |     |

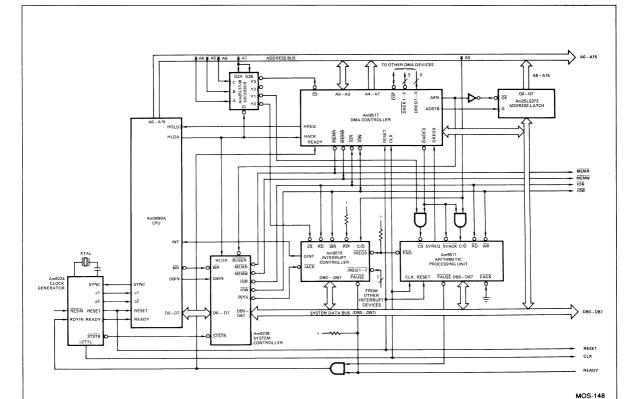

| The Am9517 Multimode Direct Memory Access Controller                       |     |

| Designing Interrupt Systems with the Am9519 Universal Interrupt Controller | -43 |

# PRODUCT ASSURANCE MIL-M-38510 • MIL-STD-883

The product assurance program at Advanced Micro Devices defines manufacturing flow, establishes standards and controls, and confirms the product quality at critical points. Standardization under this program assures that all products meet military and government agency specifications for reliable ground applications. Further screening for users desiring flight hardware and other higher reliability classes is simplified because starting product meets all initial requirements for high-reliability parts.

The quality standards and screening methods of this program are equally valuable for commercial parts where equipment must perform reliably with minimum field service.

Two military documents provide the foundation for this program. They are:

MIL-M-38510 – General Specification for Microcircuits MIL-STD-883 – Test Methods and Procedures for Microelectronics

**MIL-M-38510** describes design, processing and assembly workmanship guidelines for military and space-grade integrated circuits. All circuits manufactured by Advanced Micro Devices for full temperature range (-55°C to +125°C) operation meet these quality requirements of MIL-M-38510.

MIL-STD-883 defines detail testing and inspection methods for integrated circuits. Three of the methods are quality and processing standards directly related to product assurance:

**Test Method 2010** defines the visual inspection of integrated circuits before sealing. By confirming fabrication and assembly quality, inspection to this standard assures the user of reliable circuits in long-term field applications. Standard inspection at Advanced Micro Devices includes all the requirements of the latest revision of Method 2010, condition B.

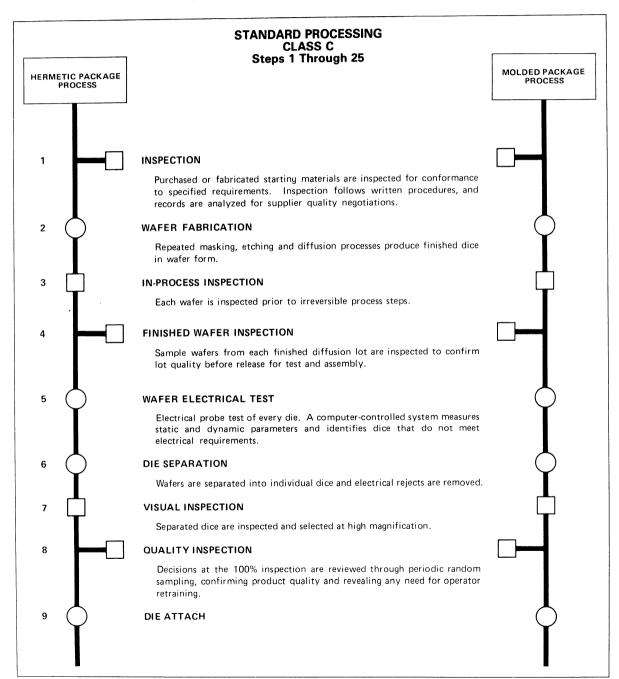

Test Method 5004 defines three reliability classes of parts. All must receive certain basic inspection, preconditioning and screening stresses. The classes are:

$\label{eq:class} \textbf{C} - \textbf{U} \textbf{sed where replacement can be readily accomplished. Screening steps are given in the AMD processing flow chart.$

**Class B** – Used where maintenance is difficult or expensive and where reliability is vital. Devices are upgraded from Class C to Class B by 160-hour burn-in at  $125^{\circ}$ C followed by more extensive electrical measurements. All other screening requirements are the same.

**Class S** – Used where replacement is extremely difficult and reliability is imperative. Class S screening selects extra reliability parts by expanded visual and X-ray inspection, further burn-in, and tighter sampling inspection.

All hermetically sealed integrated circuits (military and commercial) manufactured by Advanced Micro Devices are screened to MIL-STD-883, Class C. Molded integrated circuits receive Class C screening except that centrifuge and hermeticity steps are omitted.

Optional extended processing to MIL-STD-883, Class B is available for all AMD integrated circuits. Parts procured to this screening are marked with a "-B" following the standard part number, except that linear 100, 200 or 300 series are suffixed "/883B".

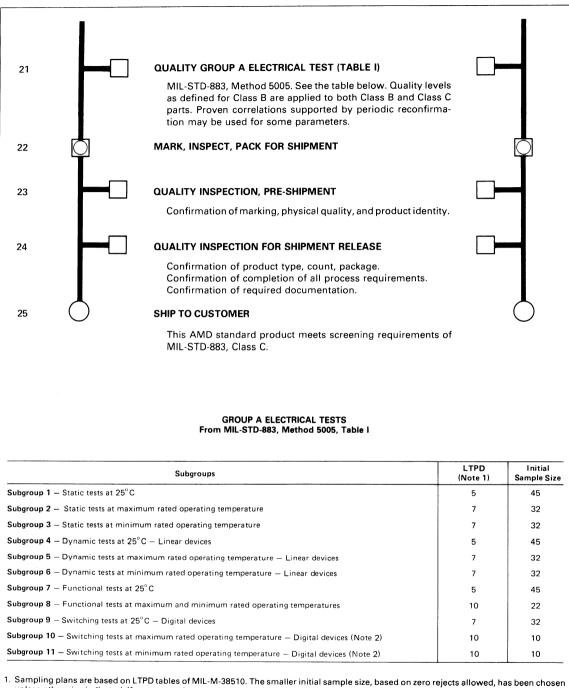

**Test Method 5005** defines qualification and quality conformance procedures. Subgroups, tests and quality levels are given for Group A (electrical), Group B (mechanical quality related to the user's assembly environment), Group C (die related tests) and Group D (package related tests). Group A tests are always performed; Group B, C and D may be specified by the user.

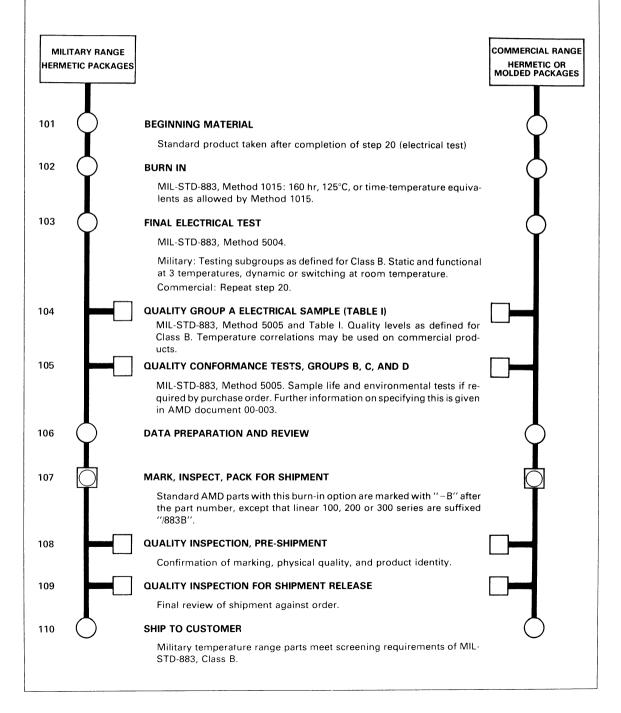

#### MANUFACTURING, SCREENING AND INSPECTION FOR INTEGRATED CIRCUITS

All integrated circuits are screened to MIL-STD-883, Method 5004, Class C; quality conformance inspection where required is performed to Class B quality levels on either Class B or Class C product.

All full-temperature-range ( $-55^{\circ}$ C to  $+125^{\circ}$ C) circuits are manufactured to the workmanship requirements of MIL-M-38510.

The flow chart identifies processing steps as they relate to MIL-STD-883 and MIL-M-38510.

#### QUALITY INSPECTION

Strength of die attachment, position of die and visual quality of eutectic wetting are confirmed periodically by inspecting random samples and push-testing the attached dice.

#### WIRE BOND

Hermetic: Aluminum wires, ultrasonic bonding. Molded: Gold wires, thermocompression bonding.

#### QUALITY INSPECTION

Weld strength, bond size and position, wire dress and general workmanship are confirmed periodically by comparing random samples with assembly instructions and quality standards. Bond strength is plotted on statistical control charts, providing early warning of process drifts.

#### INTERNAL VISUAL INSPECTION

Assembled but unsealed units are individually inspected at low and high power.

#### QUALITY STANDARDS:

All devices – MIL-STD-883, Method 2010, Condition B (latest revision). Full temperature devices – MIL-M-38510, Para. 3.7 for workmanship (rebonding limits).

#### QUALITY INSPECTION

Decisions at the 100% inspection are reviewed through periodic random sampling, providing confirmation of product quality and revealing any need for operator retraining.

#### FINAL SEAL

(Hermetic devices)

#### ENCAPSULATE

(Molded Devices)

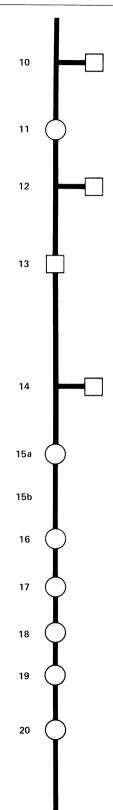

#### HIGH TEMPERATURE STORAGE

MIL-STD-883, Method 1008, Cond. C: 150°C, 24 hr

#### TEMPERATURE CYCLE

MIL-STD-883, Method 1010, Cond. C: -65°C, +150°C, 10 cycles

#### CENTRIFUGE

MIL-STD-883, Method 2001, Cond. E: 30,000 G

#### SEAL (HERMETICITY) TEST

MIL-STD-883, Method 1014, Cond. A or B: Fine Leak MIL-STD-883, Method 1014, Cond. C2: Gross Leak

#### ELECTRICAL TEST

MIL-STD-883, Method 5004, Para. 3.1.12: Static, dynamic, functional tests at  $25^{\circ}$ C or in certain products at the most critical extreme temperature to assure accuracy of device selection.

unless otherwise indicated. If necessary, the sample size will be increased once to the quantity corresponding to an acceptance number of 2. The minimum reject number in all cases is 3.

2. These subgroups are usually performed during initial device characterization only.

#### OPTIONAL EXTENDED PROCESSING CLASS B Steps 101 Through 110

Advanced Micro Devices offers several extended processing options to meet customer high-reliability requirements. These are defined in AMD document 00-003. The flow chart below outlines Option B, a 160-hr burn in. Military temperature range devices processed to this flow (in the left column) meet the screening requirements of MIL-STD-883, Class B.

### **OTHER OPTIONS**

Document 00-003, "Extended Processing Options", further defines Option B as well as other screening or sampling options available or special order. Available options are listed here for reference.

| Option | Description                                                                          | Effect                                                                                                                                                                                                            |

|--------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A      | Modified Class A screen<br>(Similar to Class S screening)                            | Provides space-grade product, fol-<br>lowing most Class S requirements<br>of MIL-STD-883, Method 5004.                                                                                                            |

| В      | 160-hr operating burn in                                                             | Upgrades a part from Class C to Class B.                                                                                                                                                                          |

| ×      | Radiographic inspection (X-ray)                                                      | Related to Option A. Provides<br>limited internal inspection of<br>sealed parts.                                                                                                                                  |

| S      | Scanning Electron Microscope<br>(SEM) metal inspection                               | Sample inspection of metal<br>coverage of die.                                                                                                                                                                    |

| V      | Preseal visual inspection to<br>MIL-STD-883, Method 2010,<br>Cond. A                 | More stringent visual inspection<br>of assemblies and die surfaces<br>prior to seal.                                                                                                                              |

| P      | Particle impact noise (PIN)<br>screen with ultrasonic detection.                     | Detects loose particles of<br>approximately 0.5 mil size or larger,<br>which could affect reliability in<br>zero-G or high vibration applications.                                                                |

| Q      | Quality conformance inspection<br>(Group B, C and D life and<br>environmental tests) | Samples from the lot are stressed<br>and tested per Method 5005.<br>The customer's order must state<br>which groups are required.<br>Group B destroys 16 devices;<br>Group C, 92 devices; Group D,<br>60 devices. |

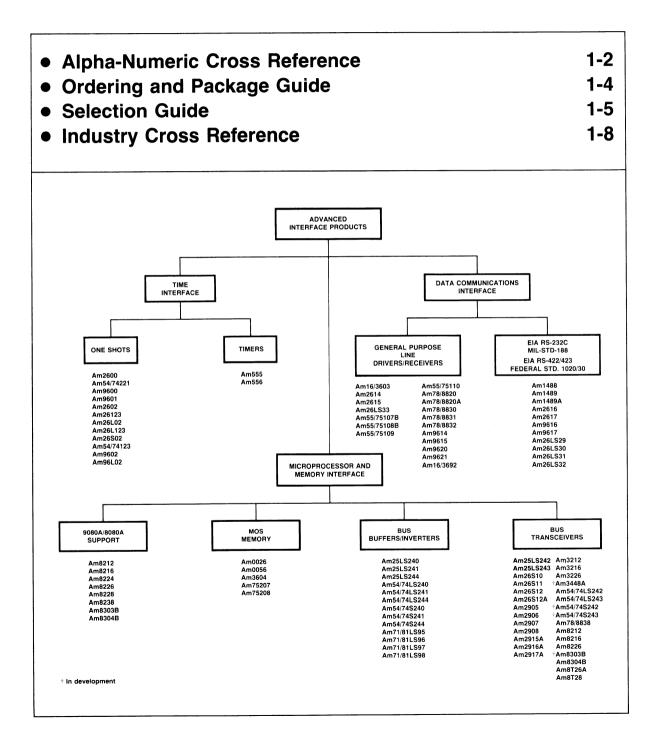

# Product Guides and Cross References

# **Interface Circuits**

### ALPHA NUMERIC CROSS REFERENCE

This list includes devices which can be replaced directly by an Advanced Micro Devices product. In some cases an alternate source vendor may not choose to use the same part number as the original manufacturer. To minimize the number of marking options we recommend ordering the device by the original source designation, as noted in this list.

| DEVICE                      | DESCRIPTION                            | ORDER #   | DEVICE             | DESCRIPTION                      | ORDER #             |

|-----------------------------|----------------------------------------|-----------|--------------------|----------------------------------|---------------------|

| Am25LS240                   | Octal Inverting Buffer/Driver          | AM25LS240 | DS1691             | EIA RS-422/423 Line Driver       | AM26LS30            |

| Am25LS241                   | Octal Non-Inverting Buffer/Driver      | AM25LS241 | DS1692             | Dual Differential Driver         | DS1692              |

| Am25LS242                   | Quad Inverting Transceiver             | AM25LS242 | DS3603             | Dual Differential Line Receiver  | DS3603              |

| Am25LS243                   | Quad Non-Inverting Transceiver         | AM25LS243 | DS3604             | Dual MOS Sense Amp               | DS3604              |

| Am25LS244                   | Octal Non-Inverting Buffer/Driver      | AM25LS244 | DS3691             | EIA RS-422/423 Line Driver       | AM26LS30            |

| Am2600                      | One-Shot                               | AM2600    | DS3692             | Dual Differential Driver         | DS3692              |

| Am2602                      | Dual One-Shot                          | AM2602    | DS55107            | Dual Differential Line Receiver  | SN55107B            |

| Am2614                      | Quad Line Driver                       | AM2614    | DS55108            | Dual Differential Line Receiver  | SN55108B            |

| Am2615                      | Dual Line Receiver                     | AM2615    | DS55109            | Dual Differential Line Driver    | SN55109             |

| Am2616                      | EIA/MIL 188C Quad Line Driver          | AM2616    | DS55110            | Dual Differential Line Driver    | SN55110             |

| Am2617                      | EIA Quad Line Receiver                 | AM2617    | DS75107            | Dual Differential Line Receiver  | SN75107B            |

| Am26123                     | Dual One-Shot                          | AM26123   | DS75108            | Dual Differential Line Receiver  | SN55108B            |

| Am26L02                     | Low-Power, Dual One-Shot               | AM26L02   | DS75109            | Dual Differential Line Driver    | SN75109             |

| Am26L123                    | Low-Power, Dual One-Shot               | AM26L123  | DS75110            | Dual Differential Line Driver    | SN75110             |

| Am26LS29                    | Quad EIA RS-423 Line Driver            | AM26LS29  | DS7820             | Dual Differential Line Receiver  | DM7820              |

| Am26LS30                    | EIA RS-422/423 Line Driver             | AM26LS30  | DS7820A            | Dual Differential Line Receiver  | DM7820A             |

| Am26LS31                    | Quad Differential Line Driver          | AM26LS31  | DS7831             | Three-State Line Driver          | DM7831              |

| Am26LS32                    | Quad Line Receiver EIA RS-422/423      | AM26LS32  | DS7832             | Three-State Line Driver          | DM7832              |

| Am26LS33                    | Quad Line Receiver                     | AM26LS33  | DS7838             | Unified Quad Bus Transceiver     | DS7838              |

| Am26S02                     | Dual One-Shot                          | AM26S02   | DS8820             | Dual Differential Line Receiver  | DM8820              |

| Am26S10                     | Quad Inverting Bus Transceiver         | AM26S10   | DS8820A            | Dual Differential Line Receiver  | DM8820A             |

| Am26S11                     | Quad Non-Inverting Bus Transceiver     | AM26S11   | DS8830             | Dual Differential Line Receiver  | DM8830              |

| Am26S12                     | Quad Bus Transceiver (Hysteresis)      | AM26S12   | DS8831             | Three-State Line Driver          | DM8831              |

| Am26S12A                    | Quad Bus Transceiver (Hysteresis)      | AM26S12A  | DS8832             | Three-State Line Driver          | DM8832              |

| Am2905                      | Quad LSI Bus Transceiver – O.C.        | AM2905    | DS8838             | Unified Quad Bus Transceiver     | DS8838              |

| Am2906                      | Quad LSI Bus Transceiver – O.C.        | AM2906    | LM163              | Dual Differential Line Receiver  | DS1603              |

| Am2907                      | Quad LSI Bus Transceiver – O.C.        | AM2907    | LM363              | Dual Differential Line Receiver  | DS3603              |

| Am2908                      | Quad LSI Bus Transceiver – O.C.        | AM2908    | LM363A             | Dual MOS Sense Amp/Line Receiver | DS3604              |

| Am2915A                     | Quad LSI Bus Transceiver – Three-State | AM2915A   | LM555              | Precision Timer                  | SE555               |

| Am2916A                     | Quad LSI Bus Transceiver – Three-State | AM2916A   | LM555C             | Precision Timer                  | NE555               |

| Am2917A                     | Quad LSI Bus Transceiver – Three-State | AM2917A   | LM556              | Dual Precision Timer             | SE556               |

| DP7303B                     | Octal Inverting Transceiver            | DP7303B   | LM556C             | Dual Precision Timer             | NE556               |

| DP7304B                     | Octal Bidirectional Transceiver        | DP7304B   | LM1488             | Quad EIA Line Driver             | MC1488              |

| Am8212                      | 8-Bit I/O Port for 9080A/8080A         | AM8212    | LM1489             | Quad EIA Line Receiver           | MC1489              |

| Am8216                      | Quad Bus Driver for 9080A/8080A        | AM8216    | LM1489A            | Quad EIA Line Receiver           | MC1489A             |

| Am8224                      | Clock Generator for 9080A/8080A        | AM8224    | LM55107            | Dual Differential Line Receiver  | SN55107B            |

| Am8226                      | Quad Bus Inverter for 9080A/8080A      | AM8226    | LM55108            | Dual Differential Line Receiver  | SN55108             |

| Am8228                      | System Controller for 9080A/8080A      | AM8228    | LM55109            | Dual Differential Line Driver    | SN55109             |

| Am8238                      | System Controller for 9080A/8080A      | AM8238    | LM55110            | Dual Differential Line Driver    | SN55110             |

| DM54123                     | Dual One-Shot                          | SN54123   | LM75107            | Dual Differential Line Receiver  | SN75107B            |

| DM71LS95                    | Octal Non-Inverting Buffer/Driver      | DM71LS95  | LM75108            | Dual Differential Line Receiver  | LM75108B            |

| DM71LS96                    | Octal Inverting Buffer/Driver          | DM71LS96  | LM75109            | Dual Differential Line Driver    | SN75109             |

| DM71LS97                    | Octal Non-Inverting Buffer/Driver      | DM71LS97  | LM75110            | Dual Differential Line Driver    | SN75110             |

| DM71LS98                    | Octal Inverting Buffer/Driver          | DM71LS98  | LM7520             | Dual Sense Amp; ±4mV Threshold   | SN7520              |

| DM74123                     | Dual One-Shot                          | SN74123   | LM7521             | Dual Sense Amp; ±7mV Threshold   | SN7521              |

| DM7820                      | Dual Differential Line Receiver        | DM7820    | LM7524             | Dual Sense Amp; ±4mV Threshold   | SN7524              |

| DM7820A                     | Dual Differential Line Receiver        | DM7820A   | LM7525             | Dual Sense Amp; ±7mV Threshold   | SN7525              |

| DM7830                      | Dual Differential Line Receiver        | DM7830    | LM75325            | Core Memory Driver               | SN75325             |

| DM7831                      | Three-State Line Driver                | DM7831    | MC1455             | Precision Timer                  | NE555               |

| DM7832                      | Three-State Line Driver                | DM7832    | MC1488             | Quad EIA Line Driver             | MC1488              |

| DM81LS95                    | Octal Non-Inverting Buffer/Driver      | DM81LS95  | MC1489             | Quad EIA Line Receiver           | MC1489              |

| DM81LS96                    | Octal Inverting Buffer/Driver          | DM81LS96  | MC1489A            | Quad EIA Line Receiver           | MC1489A             |

| DM81LS97                    | Octal Non-Inverting Buffer/Driver      | DM81LS97  | MC1555             | Precision Timer                  | SE555               |

| DM81LS98                    | Octal Inverting Buffer/Driver          | DM81LS98  | †MC3448A           | IEEE-488 Quad Transceiver        | MC3448A             |

| DM8601                      | One-Shot                               | 9601*C    | MC3456             | Dual Precision Timer             | NE556               |

| DM8602                      | Dual One-Shot                          | 9602*C    | MC3556             | Dual Precision Timer             | SE556               |

| DM8820                      | Dual Differential Line Receiver        | DM8820    | MC8601             | One-Shot                         | 9601*C              |

| DM8820A                     | Dual Differential Line Receiver        | DM8820A   | MC8602             | Dual One-Shot                    | 9602*C              |

| DM8830                      | Dual Differential Line Driver          | DM8830    | MC9601             | One-Shot                         | 9601*M              |

| DM8831                      | Three-State Line Driver                | DM8831    | MC9602             | Dual One-Shot                    | 9602*M              |

| DM8832                      | Three-State Line Driver                | DM8832    | MC55107            | Dual Differential Line Receiver  | SN55107B            |

| DM9601                      | One-Shot                               | 9601*M    | MC55108            | Dual Differential Line Receiver  | SN55108B            |

| DM9602                      | Dual One-Shot                          | 9602*M    | MC55108            | Dual Differential Line Driver    | SN551088            |

| DP8303B                     | Octal Inverting Transceiver            | DP8303B   | MC55110            | Dual Differential Line Driver    |                     |

| DP8304B                     | Octal Bidirectional Transceiver        | DP8304B   | MC75107            | Dual Differential Line Briver    | SN55110<br>SN75107B |

| DS0026                      | Two Phase MOS Clock Driver             | MH0026    |                    | Dual Differential Line Receiver  |                     |

| DS0026C                     | Two Phase MOS Clock Driver             | MH0026C   | MC75108<br>MC75109 | Dual Differential Line Receiver  | SN75108B            |

|                             | Two Phase MOS Clock Driver             | DS0056    |                    |                                  | SN75109             |

|                             | HASE MODE CIUCK DIVE                   |           | MC75110            | Dual Differential Line Driver    | SN75110             |

| DS0056                      | Two Phase MOS Clock Driver             | DEGOREC   |                    |                                  |                     |

| DS0056<br>DS0056C           | Two Phase MOS Clock Driver             | DS0056C   | MH0026             | Two-Phase MOS Clock Driver       | MH0026              |

| DS0056<br>DS0056C<br>DS1488 | Quad EIA Line Driver                   | MC1488    | MH0026C            | Two-Phase MOS Clock Driver       | MH0026C             |

| DS0056<br>DS0056C           |                                        |           |                    |                                  |                     |

# ALPHA NUMERIC CROSS REFERENCE (Cont.)

| DEVICE    | DESCRIPTION                       | ORDER #   | DEVICE    | DESCRIPTION                        | ORDER #   |

|-----------|-----------------------------------|-----------|-----------|------------------------------------|-----------|

| N8T26     | Quad Three-State Bus Transceiver  | N8T26     | SN74S241  | Octal Non-Inverting Buffer/Driver  | SN74S241  |

| N8T26A    | Quad Three-State Bus Transceiver  | N8T26A    | †SN74S242 | Quad Inverting Transceiver         | †SN74S242 |

| N8T28     | Quad Three-State Bus Transceiver  | N8T28     | †SN74S243 | Quad Non-Inverting Transceiver     | †SN74S243 |

| NE555     | Precision Timer                   | NE555     | SN74S244  | Octal Inverting Buffer/Driver      | SN74S244  |

| NE556     | Dual Precision Timer              | NE556     | SN75107A  | Dual Differential Line Receiver    | SN75107B  |

| S8T22     | One-Shot                          | 9601*M    | SN75107B  | Dual Differential Line Receiver    | SN75107B  |

| S8T26     | Quad Three-State Bus Transceiver  | S8T26     | SN75108A  | Dual Differential Line Receiver    | SN75108B  |

| S8T26A    | Quad Three-State Bus Transceiver  | S8T26A    | SN75108B  | Dual Differential Line Receiver    | SN75108B  |

| S8T28     | Quad Three-State Bus Transceiver  | S8T28     | SN75109   | Dual Differential Line Driver      | SN75109   |

| SE555     | Precision Timer                   | SE555     | SN75110   | Dual Differential Line Driver      | SN75110   |

| SE556     | Dual Precision Timer              | SE556     | SN74114   | Dual Line Driver                   | 9614*C    |

| SN52555   | Precision Timer                   | SE555     | SN75115   | Dual Differential Line Receiver    | 9615*C    |

| SN54123   | Dual One-Shot                     | SN54123   | SN75182   | Dual Differential Line Receiver    | DM8820A   |

| SN54221   | Dual One-Shot                     | SN54221   | SN75183   | Dual Differential Line Receiver    | DM8830    |

| SN54S240  | Octal Inverting Buffer/Driver     | †SN54S240 | SN75188   | Quad EIA Line Driver               | MC1488    |

| SN54S241  | Octal Non-Inverting Buffer/Driver | †SN54S241 | SN75189   | Quad EIA Line Receiver             | MC1489    |

| SN54S242  | Octal Inverting Buffer/Driver     | †SN54S242 | SN75189A  | Quad EIA Line Receiver             | MC1489A   |

| SN54S243  | Octal Non-Inverting Buffer/Driver | †SN54S243 | SN75207   | Dual MOS Sense Amp/Line Receiver   | SN75207   |

| SN54S244  | Octal Inverting Buffer/Driver     | †SN54S244 | SN75208   | Dual MOS Sense Amp/Line Receiver   | SN75208   |

| SN55107A  | Dual Differential Line Receiver   | SN55107B  | SN75369   | Two-Phase MOS Clock Driver         | MH0026    |

| SN55107B  | Dual Differential Line Receiver   | SN55107B  | 3212      | 8-Bit I/O Port                     | 3212      |

| SN55108A  | Dual Differential Line Receiver   | SN55108B  | 3216      | Non-Inverting Quad Bus Transceiver | 3216      |

| SN55108B  | Dual Differential Line Receiver   | SN55108B  | 3226      | Inverting Quad Bus Transceiver     | 3226      |

| SN55109   | Dual Differential Line Driver     | SN55109   | 8212      | 8-Bit I/O Port for 9080A/8080A     | AM8212/82 |

| SN55110   | Dual Differential Line Driver     | SN55110   | 8216      | Non-Inverting Quad Bus Transceiver | 8216      |

| SN55114   | Dual Differential Line Driver     | 9614*M    | 8224      | Clock Generator for 9080A/8080A    | 8224      |

| SN55115   | Dual Differential Line Receiver   | 9615*M    | 8226      | Inverting Quad Bus Transceiver     | 8226      |

| SN55182   | Dual Differential Line Receiver   | DM7820A   | 8228      | System Controller for 9080A/8080A  | AM8228/82 |

| SN55183   | Dual Differential Line Receiver   | DM7830    | 8238      | System Controller for 9080A/8080A  | AM8238/82 |

| SN55369   | Two-Phase MOS Clock Driver        | MH0026    | 9600      | One-Shot                           | 9600      |

| SN72555   | Precision Timer                   | SN72555   | 9601      | One-Shot                           | 9601      |

| SN74123   | Dual One-Shot                     | SN74123   | 9602      | Dual One-Shot                      | 9602      |

| SN74221   | Dual One-Shot                     | SN74221   | 96L02     | Low-Power, Dual One-Shot           | 96L02     |

| SN74LS424 | Clock Generator for 9080A/8080A   | Am8224    | 9614      | Dual Line Driver                   | 9614      |

| SN74LS240 | Octal Inverting Buffer/Driver     | SN74LS240 | 9615      | Dual Differential Line Receiver    | 9615      |

| SN74LS241 | Octal Non-Inverting Buffer/Driver | SN74LS241 | 9616      | Triple EIA Line Driver             | 9616      |

| SN74LS242 | Quad Inverting Transceiver        | SN74LS242 | 9617      | Triple EIA Line Receiver           | 9617      |

| SN74LS243 | Quad Non-Inverting Transceiver    | SN74LS243 | 9620      | Dual Differential Line Receiver    | 9620      |

| SN74LS244 | Octal Non-Inverting Buffer/Driver | SN74LS244 | 9621      | Dual Differential Line Driver      | 9621      |

| SN74S240  | Octal Inverting Buffer/Driver     | SN74S240  |           |                                    |           |

†To be announced. \* is the package designator position.

# **SELECTION GUIDE (Cont.)**

### LINE DRIVERS

| DUAL DIF  | FERENTIAL                                                                                                | Use With         |

|-----------|----------------------------------------------------------------------------------------------------------|------------------|

| 75109     | Open collector differential outputs                                                                      | 75107B           |

|           | typical current 6mA, inhibit controls                                                                    | 75108B           |

| 75110     | 12mA output current version of<br>Am75109                                                                | 75107B<br>75108B |

| 8830      | Designed for single 5.0V supply<br>operation                                                             | 7820 or<br>7820A |

| 8831      | Dual differential device which may also<br>be used as a quad single-ended driver.<br>Three-state output. | 9615 or<br>2615  |

| 8832      | Similar to 8831 but no V <sub>CC</sub> clamp<br>diodes                                                   | 9615 or<br>2615  |

| 9614      | 5 volt supply driver with complementary<br>outputs                                                       | 9615             |

| 9621      | 200mA transient capability with $130\Omega$ back matching resistor                                       | 9620             |

| DIFFEREN  | TIAL EIA RS-422,                                                                                         |                  |

| FEDERAL   | STD 1020                                                                                                 |                  |

| 26LS31    | Quad, high-speed, low output skew                                                                        | 26LS32 or        |

| 26LS30    | Dual, high output CMR                                                                                    | 26LS33           |

| SINGLE E  | NDED                                                                                                     |                  |

| 2614      | High-speed quad driver for multi-channel, common ground operation.                                       | 2615             |

| SINGLE EN | IDED, EIA RS-232-C                                                                                       |                  |

| 1488      | Quad EIA RS-232C driver (14 pins)                                                                        | 1489/<br>1489A   |

| 2616      | Quad 16-pin driver for EIA RS-232C,<br>CCITT V.24 and MIL-188C interface                                 | 2617             |

| 9616      | Triple EIA RS-232C driver (14 pins)                                                                      | 9617             |

| SINGLE EN | NDED, EIA RS-423, FEDERAL STD 103                                                                        | 0                |

| 26LS29    | Quad, three-state                                                                                        | 26LS32 or        |

| 26LS30    | Quad, mode control                                                                                       | 26LS33           |

#### **BUS BUFFERS/DRIVERS**

|         |                                                                                     | t <sub>pd</sub><br>(TYP) | I <sub>OL</sub><br>(MAX) |

|---------|-------------------------------------------------------------------------------------|--------------------------|--------------------------|

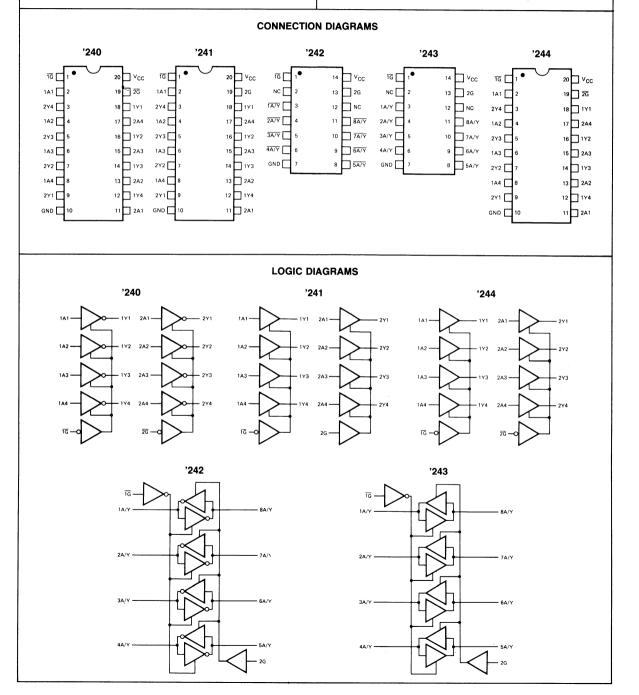

| 25LS240 | Inverting octal buffer/driver with three-                                           | 10                       | 48                       |

| 74LS240 | state output                                                                        | 10                       | 24                       |

| 74S240  |                                                                                     | 4.5                      | 68                       |

| 81LS96  |                                                                                     | 9.0                      | 16                       |

| 25LS241 | Non-inverting octal buffer/driver with                                              | 12                       | 48                       |

| 74LS241 | three-state output                                                                  | 12                       | 24                       |

| 74S241  |                                                                                     | 6.0                      | 68                       |

| 81LS95  |                                                                                     | 12                       | 16                       |

| 25LS242 | Inverting buffer/driver with two quad                                               | 10                       | 48                       |

| 74LS242 | data paths connected input-to-output                                                | 10                       | 24                       |

| †74S242 |                                                                                     | 4.5                      | 68                       |

| 25LS243 | Non-inverting buffer/driver with two                                                | 12                       | 48                       |

| 74LS243 | quad data paths connected input-to-                                                 | 12                       | 24                       |

| †74S243 | output                                                                              | 6.0                      | 68                       |

| 25LS244 | Non-inverting octal buffer/driver with                                              | 12                       | 48                       |

| 74LS244 | three-state output and two inverting                                                | 12                       | 24                       |

| 74S244  | enables                                                                             | 6.0                      | 68                       |

| 81LS97  |                                                                                     | 12                       | 16                       |

| 81LS98  | Inverting octal buffer/driver with three-<br>state output and two inverting enables | 9.0                      | 16                       |

†In development

### LINE RECEIVERS

| DUAL DIF          | FERENTIAL                                                                                                  | Use With          |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|

| 3603              | Receiver with differential input to detect signals > 25mV. Three-state outputs.                            | 75110             |  |  |  |

| 75107B            | Totem-pole TTL output version of<br>Am363                                                                  | 75109 or<br>75110 |  |  |  |

| 75108B            | Open collector TTL output version of<br>Am363                                                              | 75109 or<br>75110 |  |  |  |

| 8820              | Designed for ±15V common mode using 5.0V supply                                                            | 8830              |  |  |  |

| 8820A             | Higher speed, tighter spec 8820                                                                            | 8830              |  |  |  |

| 9615              | ±15 volt common mode, 5 volt supply<br>receivers with uncommitted collector<br>and active pull-up controls | 9614              |  |  |  |

| 9620              | ±15 volt common mode receiver with<br>direct and attenuated inputs                                         | 9621              |  |  |  |

| QUAD DIF          | FERENTIAL                                                                                                  |                   |  |  |  |

| 26LS33            | $\pm$ 15 volt common mode, 5 volt supply, three-state output                                               | 26LS31            |  |  |  |

| FEDERAL<br>26LS32 | FERENTIAL EIA RS-422,<br>STD 1020<br>±7 volt common mode, 5 volt supply,<br>three-state output             | 26LS31            |  |  |  |

| SINGLE E          | L'                                                                                                         | 1                 |  |  |  |

| 2615              | Receiver for 3 volt single-ended TTL level data                                                            | 2614              |  |  |  |

| SINGLE EN         | NDED, EIA RS-232-C                                                                                         |                   |  |  |  |

| 1489              | Quad EIA RS-232C receiver with input<br>threshold hysteresis                                               | 1488              |  |  |  |

| 1489A             | Higher threshold version of Am1489                                                                         | 1488              |  |  |  |

| 2617              | Quad EIA RS-232 receiver specified<br>over military temperature range (same<br>pinout as Am1489A)          | 2616              |  |  |  |

| 9617              | Triple EIA RS-232 receiver with<br>adjustable hysteresis                                                   | 9616              |  |  |  |

| SINGLE EN         | NDED, EIA RS-423,<br>STD 1030                                                                              |                   |  |  |  |

| 26LS32            | $\pm7$ volt common mode, 5 volt supply, three-state output                                                 | 26LS29<br>26LS30  |  |  |  |

# **SELECTION GUIDE (Cont.)**

### SPECIAL FUNCTIONS

| TIMERS |   |         |

|--------|---|---------|

| 555    | I | Single, |

| 556    |   | Dual ve |

Single, Precision oscillator/timer Dual version 555

# MOS MEMORY

| DRIVERS   |                                                            |

|-----------|------------------------------------------------------------|

| 0026      | Dual 5MHz Two-Phase MOS clock driver                       |

| 0056      | 0026 with added V <sub>BB</sub> terminal                   |

| SENSE AMP | LIFIERS                                                    |

| 3604      | Differential input for signals > 10mV, Three-state outputs |

| 75207     | Totem-pole TTL output 3604                                 |

| 75208     | Open-collector 3604                                        |

#### **MOS-MICROPROCESSOR INTERFACE CIRCUITS**

| 8080A/9080A |                                                            |

|-------------|------------------------------------------------------------|

| 8212        | 8-Bit input/output port, with storage                      |

| 8216        | 4-Bit parallel bidirectional bus driver                    |

| 8224        | Clock generator and driver                                 |

| 8226        | Inverting version 8216                                     |

| 8228        | System controller and bus driver                           |

| 8238        | System controller and bus driver with extended<br>IOW/MEMW |

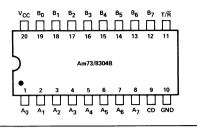

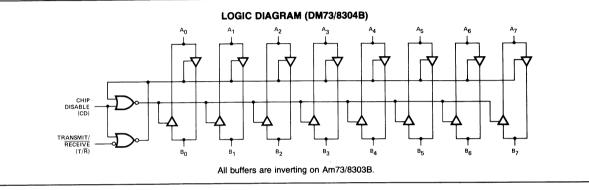

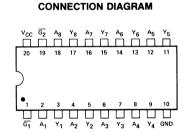

| 8303B       | Two 8226's in one 20 pin package                           |

| 8304B       | Two 8216's in one 20 pin package                           |

### **BUS TRANSCEIVERS**

| Device    | Output        | Function                                   | Hysteresis | Speed<br>(Note 1) | Comments                                        |

|-----------|---------------|--------------------------------------------|------------|-------------------|-------------------------------------------------|

| QUAD      |               |                                            |            |                   |                                                 |

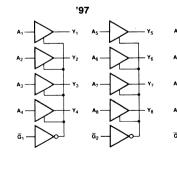

| Am26S10   | 100mA-O.C.    | Inverting                                  | No         | 20ns              | SN55/75138 pin out                              |

| Am26S11   | 100mA-O.C.    | Non-Inverting to bus;<br>Inverting off bus | No         | 22ns              | Same as Am26S10 except non-inverting to bus     |

| Am26S12   | 100mA-O.C.    | Inverting                                  | Yes-0.6V   | 32ns              | Same pin out as DS78/8838 and 8T38              |

| Am26S12A  | 100mA-O.C.    | Inverting                                  | Yes-1.05V  | 32ns              | Wider threshold Am26S12                         |

| Am2905    | 100mA-O.C.    | Inverting                                  | No         | 31ns<br>(Note 2)  | Has 2-input multiplexer                         |

| Am2906    | 100mA-O.C.    | Inverting                                  | No         | 31ns<br>(Note 2)  | Has 2-input multiplexer and parity              |

| Am2907    | 100mA-O.C.    | Inverting                                  | No         | 31ns<br>(Note 2)  | Includes parity, 2.0V receiver V <sub>TH</sub>  |

| Am2908    | 100mA-O.C.    | Inverting                                  | No         | 31ns<br>(Note 2)  | Includes parity, 1.5V receiver V <sub>TH</sub>  |

| Am2915A   | 48mA/3-St.    | Inverting                                  | No         | 31ns<br>(Note 2)  | Has 2-input multiplexer                         |

| Am2916A   | 48mA/3-St.    | Inverting                                  | No         | 31ns<br>(Note 2)  | Has 2-input multiplexer and parity              |

| Am2917A   | 48mA/3-St.    | Inverting                                  | No         | 31ns<br>(Note 2)  | Includes parity                                 |

| Am3216    | 50mA/3-St.    | Non-Inverting                              | No         | 34ns              | Same as 8216 except different A.C. loading spec |

| Am3226    | 50mA/3-St.    | Inverting                                  | No         | 30ns              | Same as 8216 except different A.C. loading spec |

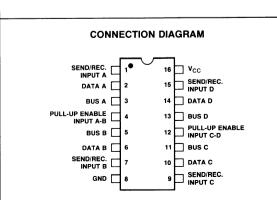

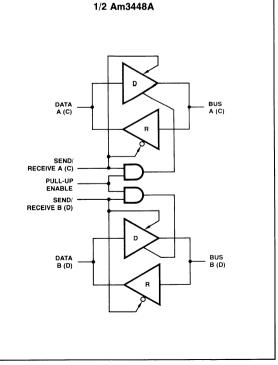

| Am3448A   | 48mA/3-StO.C. | Non-Inverting                              | Yes        | 32ns              | IEEE 488 compatible                             |

| Am78/8838 | 50mA-O.C.     | Inverting                                  | No         | 38ns              | Same pin out and function as Am26S12A and 8T38  |

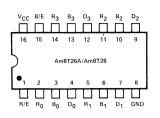

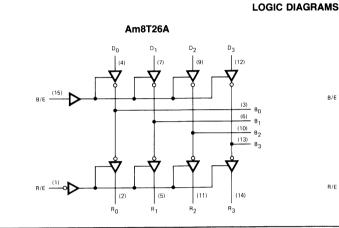

| Am8T26A   | 48mA/3-St.    | Inverting                                  | No         | 19ns              | V <sub>OH</sub> MOS compatible                  |

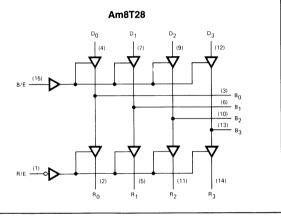

| Am8T28    | 48mA/3-St.    | Non-Inverting                              | No         | 25ns              | V <sub>OH</sub> MOS compatible                  |

| Am8216    | 50mA/3-St.    | Non-Inverting                              | No         | 34ns              | Similar to 8T28                                 |

| Am8226    | 50mA/3-St.    | Non-Inverting                              | No         | 30ns              | Similar to 8T26A                                |

| OCTAL     | •             |                                            |            |                   |                                                 |

| Am8303B   | 48mA/3-St.    | Inverting                                  | No         | 14ns              | Same as two 8226's in one 20 pin package        |

| Am8304B   | 48mA/3-St.    | Non-Inverting                              | No         | 24ns              | Same as two 8216's in one 20 pin package        |

Notes: 1. Typical delay at 28°C for input to bus plus receiver to output.

2. Bus enable to bus plus bus to receiver output. All parts include register or driver plus receiver with latch.

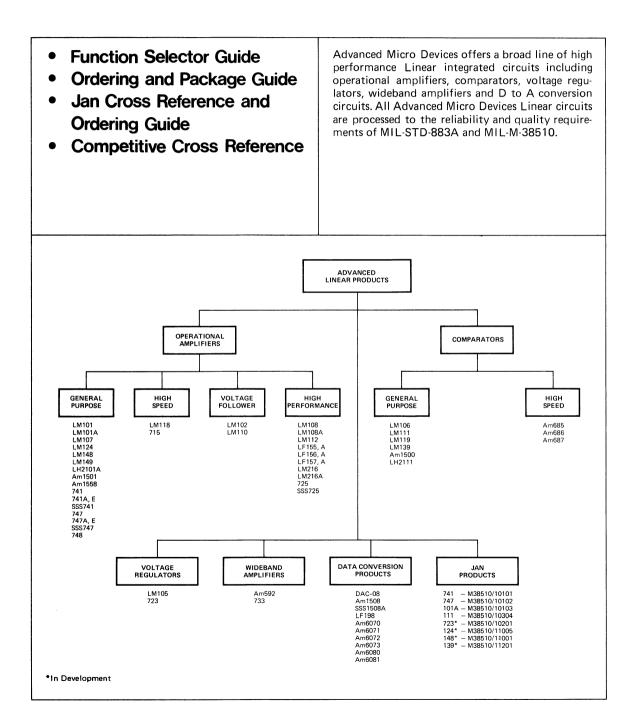

# **Linear Circuits**

### FUNCTION SELECTOR GUIDE

| Туре                           | Description                           | Features                                                                                      | Product         |

|--------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------|-----------------|

| Uncompensated Op Amps          | General Purpose                       | 500nA IB, 5mV Vos                                                                             | LM101           |

|                                | General Purpose                       | 500nA IB, 5mV Vos                                                                             | LM748           |

|                                | Improved General Purpose              | 75nA I <sub>B</sub> , 2mV Vos                                                                 | LM101A          |

|                                |                                       |                                                                                               | AM1501          |

|                                | Dual Improved General Purpose         | 75nA IB, 2mV Vos                                                                              |                 |

|                                | Dual Improved General Purpose         | 75nA I <sub>B</sub> , 2mV Vos                                                                 | LH2101A         |

|                                | Instrumentation                       | 100nA I <sub>B</sub> , 1mV Vos, 0.5µV/°C TCVIO                                                | 725             |

|                                | Improved Instrumentation              | 70nA IB, 0.1mV Vos, 0.1µV/°C TCVIO                                                            | SSS725          |

|                                | Low Input Current Precision           | 2nA IB, 2mV Vos, 0.2nA IOS                                                                    | LM108           |

|                                | Low Input Current and Offset          | 2nA IB, 0.5mV Vos, 0.2nA IOS, 5µV/°C TCVIO                                                    | LM108A          |

|                                | Voltage Precision                     | <b>b</b> , , , , , , , , , , , , , , , , , , ,                                                |                 |

|                                | High Speed                            | 15V/µsec slew rate, 750nA 1 <sub>B</sub> , 5mV Vos                                            | 715             |

| Internally Compensated Op Amps | General Purpose                       | 500nA IB, 5mV Vos                                                                             | 741             |

|                                | Improved General Purpose              | 80nA IB, 3mV Vos, 30nA IOS, 50µV/V PSRR                                                       | 741A, E         |

|                                | High Performance                      | 50nA IB, 2mV Vos                                                                              | SSS741          |

|                                | Dual General Purpose                  | 500nA IB, 5mV Vos                                                                             |                 |

|                                | · · · · · · · · · · · · · · · · · · · |                                                                                               | 747             |

|                                | Dual Improved Generai Purpose         | 80nA I <sub>B</sub> , 3mV Vos, 30nA I <sub>OS</sub> , 50µV/V PSRR                             | 747A, E         |

|                                | Dual High Performance                 | 50nA IB, 2mV Vos                                                                              | SSS747          |

|                                | Dual General Purpose                  | 500nA IB, 5mV Vos                                                                             | AM1558          |

|                                | Quad General Purpose                  | 150nA IB, 5mV Vos, Single or Dual Supply, 3 to 30V,                                           | LM124           |

|                                | Quad 741                              | 1mW/op amp at +5V<br>500nA I <sub>B</sub> , 5mV Vos                                           | LM124A<br>LM148 |

|                                | 1                                     |                                                                                               |                 |

|                                | Quad Decompensated                    | 500nA IB, 5mV Vos AV (min.) = 5                                                               | LM149           |

|                                | Improved General Purpose              | 75nA IB, 2mV Vos                                                                              | LM107           |

|                                | Low Input Current Precision           | 2nA I <sub>B</sub> , 2mV Vos                                                                  | LM112           |

|                                | Very Low Input Current<br>Precision   | 150pA IB, 10mV Vos                                                                            | LM216           |

|                                | Very Low Input Current<br>Precision   | 50pA I <sub>B</sub> , 3mV Vos                                                                 | LM216A          |

|                                | High Speed                            |                                                                                               |                 |

|                                | 5 -1                                  | 50V/µsec slew rate, 4mV Vos, 250nA IB                                                         | LM118           |

|                                | FET Input General Purpose             | 5mV Vos, 20pA I <sub>OS</sub> , 100pA I <sub>B</sub>                                          | LF155           |

|                                | FET Input General Purpose             | 2mV Vos, 5µV/°C TC V <sub>10</sub> , 10pA I <sub>OS</sub> , 50pA I <sub>B</sub>               | LF155A          |

|                                | FET Input Wide Band                   | 5mV Vos, 20pA IOS, 100pA IB, 7.5V/µsec SR                                                     | LF156           |

|                                | FET Input Wide Band                   | $2$ mV Vos, $5\mu$ V/°C TC V <sub>10</sub> , 10pA I <sub>OS</sub> , 50pA I <sub>B</sub> ,     | LF156A          |

|                                | TET input wide band                   | 10V/#sec SR                                                                                   | LEISOA          |

|                                | FET Input Wideband<br>Decompensated   | 5mV Vos, 20pA I <sub>OS</sub> , 100pA I <sub>B</sub> , 30V/ $\mu$ sec SR (A <sub>V</sub> = 5) | LF157           |

|                                | Fet Input Wide Band                   | 2mV Vos, 5µV/°C TC V <sub>10</sub> , 10pA I <sub>OS</sub> , 50pA I <sub>B</sub> ,             | LF157A          |

|                                | Decompensated                         | $40V/\mu sec SR (A_V = 5)$                                                                    |                 |

| Voltage Followers              | Low Input Current, High Speed         | 10nA I <sub>B</sub> , 5mV Vos, 20V/ $\mu$ sec slew rate, 10 <sup>10</sup> $\Omega$ Rin        | LM102           |

|                                | Improved Low Input Current            | $3nAI_{B}$ , 4mV Vos, 20V/µsec slew rate, 10 <sup>10</sup> $\Omega$ Rin                       | LM110           |

|                                | High Speed                            |                                                                                               | 2               |

| Voltage Comparators            | General Purpose                       | 100nA IB, 3mV Vos, 250ns Response Time,                                                       | LM111           |

|                                | Dual General Purpose                  | 50V and 50mA Output<br>100nA I <sub>B</sub> , 3mV Vos, 250ns Response Time,                   | LH2111          |

|                                |                                       | 50V and 50mA Output                                                                           |                 |

|                                | Dual General Purpose                  | 100nA I <sub>B</sub> , 3mV Vos, 250ns Response Time,<br>50V and 50mA Output                   | AM1500          |

|                                | High Speed                            | 20µA I <sub>B</sub> , 2mV Vos, 40ns Response Time,<br>24V and 100mA Output                    | LM106           |

|                                | Dual General Purpose                  | 500nA IB, 4mV Vos, 80ns Response Time,                                                        | LM119           |

|                                | Quad General Purpose                  | 35V and 25mA Output, +5 or +15V Supply<br>100nA IB, 2mV Vos, Single or Dual Supply 2 to 36V,  | LM139           |

|                                |                                       | 1mW/comp. at +5V                                                                              | LM139A          |

|                                | Very Fast ECL Output                  | 10µA IB, 2mV Vos, 6.5ns Response Time                                                         | AM685           |

|                                | Very Fast TTL Output                  | 10µA IB, 2mV Vos, 12ns Response Time                                                          | AM686           |

|                                | Dual Very Fast ECL Output             | 10µA IB, 2mV Vos, 6.5ns Response Time                                                         | AM687           |

| Voltage Regulators             | General Purpose                       | 2-37V Output, 0.15% load reg., 50V input, 150mA Output                                        | 723             |

|                                | General Purpose                       | 4.5-40V Output, 0.05% load reg., 50V input, 12mA Output                                       | LM105           |

| D to A Converter Products      | 8-Bit Multiplying D-to-A Converter    | Accuracy 0.19%, Settling Time 300nsec typ.                                                    | AM1508          |

|                                | 8-Bit Multiplying D-to-A Converter    | Accuracy 0.1%, Settling Time 135nsec                                                          | SSS1508A        |

|                                |                                       |                                                                                               | DAC-08          |

|                                | FET Input Sample and Hold             | Gain Error .005%, Acquisition Time                                                            | 040-08          |

|                                |                                       | 10µsec Z <sub>IN</sub> 10 <sup>10</sup> Ohm                                                   | LF198           |

|                                | Companding D to A Converters          | 12 bit Dynamic Range, A-law or μlaw                                                           | AM6070/1/       |

|                                | Bus Compatible D to A Converters      | 12 bit Dynamic Hange, A-law or µlaw<br>.1% Accuracy, Compatible with any Microprocessor       | AM6080/81       |

| Wideband Amplifiers            | Differential Input and Output         | 40-120MHz B.W., 100-400 Voltage Gain                                                          | 700             |

| macoana Ampimers               | Differential Input and Output         |                                                                                               | 733             |

|                                | Differential Input and Output         | 40-120MHz B.W., 100-400 Voltage Gain                                                          | AM592           |

DICE – All Advanced Micro Devices Linear products are available as electrically tested and optically inspected dice for assemblers of hybrid circuits. Dice are processed to MIL-STD-883A level B and packaged in waffle packs. Gold backing is not available.

# ADVANCED LINEAR – ORDERING AND PACKAGE GUIDE

| DEVICE          |                    | ORDER 1<br>0°C to        |                   |                    | ORDER NUMBER<br>-55°C to +125°C |                         |                      |                    |  |

|-----------------|--------------------|--------------------------|-------------------|--------------------|---------------------------------|-------------------------|----------------------|--------------------|--|

| NUMBER          | Metal<br>Can       | Hermetic<br>DIP          | Molded<br>DIP     | Dice               | Metal<br>Can                    | Hermetic                |                      |                    |  |

| LM101           | LM301H             | LM301D                   | LM301N            | LD301              | LM101H                          | LM101D                  | Elat Pack            | LD101              |  |

| LM101A          | LM301AH            | LM301AD                  | LM201N<br>LM301AN | LD301A             | LM201H<br>LM101AH               | LM201D<br>LM101AD       | LM201F               |                    |  |

| LM102           | LM302H             |                          | LM201AN           |                    | LM201AH                         | LM101AD                 | LM101AF<br>LM201AF   | LD101A             |  |

|                 | LWISUZH            | LM302D                   |                   | LD302              | LM102H<br>LM202H                | LM102D<br>LM202D        | LM102F<br>LM202F     | LD102              |  |

| LM105           | LM305H             |                          |                   | LD305              | LM105H                          | Emedeo                  | EW202F               | LD105              |  |

| LM106           | LM305AH<br>LM306H  | LM306D                   |                   | LD306              | LM205H<br>LM106H                |                         |                      |                    |  |

| *<br>LM107      | LM307H             | LM307D                   |                   |                    | LM206H                          |                         | LM106F<br>LM206F     | LD106              |  |

| *               | Eliido             | EW307D                   |                   | LD307              | LM107H<br>LM207H                | LM107D<br>LM207D        | LM107F<br>LM207F     | LD107              |  |

| LM108           | LM308H             | LM308D                   | LM308N            | LD308              | LM108H                          | LM108D                  | LM108F               | LD108              |  |

| LM108A          | LM308AH            | LM308AD                  | LM308AN           | LD308A             | LM208H<br>LM108AH               | LM208D<br>LM108AD       | LM208F<br>LM108AF    | LD108A             |  |

| LM110           | LM310H             | LM310D                   | LM310N            | LD310              | LM208AH<br>LM110H               | LM208AD<br>LM110D       | LM208A F             |                    |  |

| •               |                    |                          |                   | 20010              | LM210H                          | LM110D                  | LM110F<br>LM210F     | LD110              |  |

| LM111 *         | LM311H             | LM311D                   | LM311N            | LD311              | LM111H                          | LM111D                  | LM111F               | LD111              |  |

| LM112           | LM312H             | LM312D                   |                   | LD312              | LM211H<br>LM112H                | LM211D<br>LM112D        | LM211F<br>LM112F     | LD112              |  |

| LM118           | LM318H             | LM318D                   | LM318N            | 10040              | LM212H                          | LM212D                  | LM212F               |                    |  |

| •               |                    |                          |                   | LD318              | LM118H<br>LM218H                | LM118D<br>LM218D        | LM118F<br>LM218F     | LD118              |  |

| LM119           | LM319H             | LM319D                   | LM319N            | LD319              | LM119H<br>LM219H                | LM119D<br>LM219D        | LM119F               | LD119              |  |

| LM124           |                    | LM324D                   | LM324N            | LD324              | LW2191                          | LM124D                  | LM219F<br>LM124F     | LD124              |  |

| LM124A          |                    | LM324AD                  | LM324AN           | LD324A             |                                 | LM224D<br>LM124AD       | LM224F<br>LM124AF    | LD124A             |  |

| LM139           |                    | LM339D                   | LM339N            | 10000              |                                 | LM224AD                 | LM224AF              |                    |  |

| *<br>LM139A     |                    |                          |                   | LD339              |                                 | LM139D<br>LM239D        | LM139F<br>LM239F     | LD139              |  |

| •               |                    | LM339AD                  | LM339AN           | LD339A             |                                 | LM139AD<br>LM239AD      | LM139AF<br>LM239AF   | LD139A             |  |

| LM148           |                    | LM348D                   | LM348N            | LD348              |                                 | LM148D<br>LM248D        | EM235/41             | LD148              |  |

| LM149           |                    | LM349D                   | LM349N            | LD349              |                                 | LM149D                  |                      | LD149              |  |

| LF155           | LF355H             |                          | LF355N            | LD355              | LF155H                          | LM249D                  |                      | LD155              |  |

| LF155A          | LF355AH            |                          |                   | LD355A             | LF255H<br>LF155AH               |                         |                      |                    |  |

| LF156           | LF356H             |                          | LF356N            | LD356              | LF156H                          |                         |                      | LD155A             |  |

| •<br>LF156A     | LF356AH            |                          | 2,000,1           |                    | LF256H                          |                         |                      | LD156              |  |

| LF157           | LF357H             |                          |                   | LD356A             | LF156AH                         |                         |                      | LD156A             |  |

| •               |                    |                          | LF357N            | LD357              | LF157H<br>LF257H                |                         |                      | LD157              |  |

| LF157A          | LF357AH            |                          |                   | LD357A             | LF157AH                         |                         |                      | LD157A             |  |

| LF198           | LF398H             |                          |                   | LD398              | LF198H<br>LF298H                |                         |                      | LD198              |  |

| LM216           | LM316H             | LM316D                   |                   | LD316              |                                 |                         |                      |                    |  |

| LM216A          | LM316AH            | LM316AD                  |                   | LD316A             | LM216H                          | LM216D                  | LM216F               | LD216              |  |

| AM592           | AM592HC            | AM592DC                  | AM592PC           | AM592XC            | LM216AH<br>AM592HM              | LM216AD<br>AM592DM      | LM216A F             | LD216A<br>AM592XM  |  |

| AM685*<br>AM686 | AM685HL<br>AM686HC | AM685DL                  |                   | AM685XL            | AM685HM                         | AM685DM                 |                      | AM685 XM           |  |

| AM687*          | AWOODTC            | AM686DC<br>AM687DL       |                   | AM686XC<br>AM687XL | AM686HM                         | AM686DM<br>AM687DM      |                      | AM686XM<br>AM687XM |  |

| 715             | 715HC              | 715DC                    |                   | 715XC              | 715HM                           | 715DM                   |                      | 715XM              |  |

| 723<br>725      | 723HC<br>725HC     | 723DC<br>725DC           | 723PC<br>725CN    | 723XC<br>725XC     | 723HM<br>725HM                  | 723DM<br>725DM          |                      | 723 X M            |  |

| SSS725<br>733   | SSS725CJ           | SSS725CP                 | 120011            |                    | SSS725J                         | SSS725P                 |                      | 725XM              |  |

| 733             | 733HC<br>741HC     | 733DC<br>741DC           |                   | 733XC<br>741XC     | 733HM<br>741HM                  | 733DM<br>741DM          | 733FM<br>741FM       | 733XM              |  |

| 741A            | 741EHC             | 741EDC                   |                   |                    | 741AHM                          | 741ADM                  | 741AFM               | 741 XM             |  |

| SSS741<br>747   | SSS741CJ<br>747HC  | 747DC                    | 747PC             | 747 XC             | SSS741J<br>747HM                |                         |                      |                    |  |

| 747A<br>SSS747  | 747EHC             | 747EDC                   |                   | 141/10             | 747AHM                          | 747DM<br>747ADM         | 747EM<br>747AEM      | 747XM              |  |

| SSS /4 /<br>748 | SSS747CK<br>748HC  | SSS747CP<br>748DC        | 748PC             | 748XC              | SSS747K<br>748HM                | SSS 74 7P<br>748DM      | SSS747M<br>748FM     | 748XM              |  |

| AM1500          |                    | AM1500DC                 |                   |                    |                                 | AM1500DM                | AM1500FM             | 70/11              |  |

| AM1501          |                    | AM1501DC                 |                   |                    |                                 | AM1500DL<br>AM1501DM    | AM1500FL<br>AM1501FM |                    |  |

| AM1508          |                    | AM1408L8                 |                   |                    |                                 | AM1501DL                | AM1501FL             |                    |  |

| -               |                    | AM1408L7                 |                   |                    |                                 | AM1508L8                |                      |                    |  |

| AM1558          | AM1458H            | AM1408L6                 |                   |                    |                                 |                         |                      |                    |  |

| LH2101A         |                    | LH2301AD                 |                   |                    | AM1558H                         | LH2101AD                | LH2101AF             |                    |  |

|                 |                    |                          |                   |                    |                                 | LH2201AD                | LH2201AF             |                    |  |

| LH2111          |                    | LH2311D                  |                   |                    |                                 | LH2111D<br>LH2211D      | LH2111F<br>LH2211F   |                    |  |

| DAC-08          |                    | AMDAC-08EQ<br>AMDAC-08CQ |                   |                    |                                 | AMDAC-08AQ<br>AMDAC-08Q |                      |                    |  |

| AM6070/1/2/3    |                    | AM6070DC                 | AM6070PC          | 6070XC             | 1                               | AM6070DM                |                      |                    |  |

\*Indicates -25°C to +85°C Operating Temperature Range.

For MIL-STD-883A Class B processing order as follows: For all LM100 and LM2100 series devices add/883B suffix. Example: LM101AH/883B, LH2111D/883B

For other devices add B suffix. Example: 741HMB, AM687DMB, AM1500DMB

#### ADVANCED LINEAR PROCESSING

Every AMD Linear integrated circuit is manufactured to the full requirements of MIL-STD-883A level C or better. AMD has been rigorously inspected by NASA and DESC and has received full line certification by both to supply high reliability Linear circuits on NASA and JAN programs.

During a period when the industry is continually looking for ways to decrease cost through production efficiency as well as process simplification, AMD has maintained the highest integrity and in many instances developed more sophisticated and costly processes to enhance device performance and reliability. The following special processing is representative of the importance AMD places on maintaining product reliability.

#### AMD Wafer Processing

- Controlled oxide step profile for superior metal coverage.

- Wafer lots regularly SEM inspected on in-house SEM.

- Proprietary passivation process prevents MOS channeling and inherently provides extra radiation hardness.

#### THE FUTURE - LINEAR LSI

Linear processing is advancing dramatically and AMD is at the forefront of this technology expansion with the processes already developed for the next generation linear circuits. The standard high voltage process has been advanced in two directions, both employing ion implantation as a key and incorporating FET's together with bipolar devices monolithically. One process is being used to build a series of operational amplifiers using J-FET input transistors; the other is an advanced MOSFET compatible bipolar process which will be used in a new generation of data and speech communications circuits.

Three years ago the analog group at AMD developed the Am685, 686 and 687 that were billed as the world's fastest ECL, TTL and DUAL ECL comparators. Their claim has been unchallenged by anyone. The process that was developed for these products employed thin epitaxial layers, shallow junctions and advanced barrier layer metallization

#### AMD Electrical Testing

- All devices, in all packages, 100% tested at room, high and low temperatures.

- All devices tested for AC parameters.

- All internally compensated devices undergo capacitor stress testing to eliminate marginal units.

- When required by application many devices are tested at 150°C to simulate die temperatures reached under continuous operation.

#### AMD-JAN LINEAR PRODUCT GUIDE

The following Linear devices are available as fully qualified JM38510 parts:

| Device Type | Slash Sheet Number |

|-------------|--------------------|

| 741         | JM38510/10101BGC   |

|             | JM38510/10101BGA   |

| 747         | JM38510/10102BCA   |

|             | JM38510/10102BCB   |

|             | JM38510/10102BIC*  |

| 101A        | JM38510/10103BGC   |

|             | JM38510/10103BGA   |

| 111         | JM38510/10304BGC   |

| 723         | JM38510/10201*     |

| 139         | JM38510/11201*     |

| 124         | JM38510/11005*     |

| 148         | JM38510/11001*     |

\* Qualification in progress.

and allowed the integration of 1GHz transistors and fast Schottky diode clamps.