# Advanced Micro Devices

# The Am2960 Series Dynamic Memory Support Handbook

The International Standard of Quality guarantees these electrical AQLs on all parameters over the operating temperature range: 0.1% on MOS RAMs & ROMs; 0.2% on Bipolar Logic & Interface; 0.3% on Linear, LSI Logic & other memories.

© 1981 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The company assumes no responsibility for the use of any circuits described herein.

> 901 Thompson Place, P.O. Box 453, Sunnyvale, California 94086 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

> > Printed in U.S.A. 2/81 MPR-502

# Am2900 FAMILY DYNAMIC MEMORY SUPPORT

## TABLE OF CONTENTS

| 1                                                    |

|------------------------------------------------------|

| 16-Bit Error Detection and Correction (EDC) Unit     |

| Am2960 Boosts Memory Reliability                     |

| EDC Data Bus Buffer (Inv. to Bus)                    |

| EDC Data Bus Buffer (Non-Inv. to Bus)                |

| Dynamic Memory Controller                            |

| RAM Drivers (Inv.)                                   |

| RAM Drivers (Non-Inv.)                               |

| Dynamic Memory Drivers Improve Memory Performance71  |

| Dynamic Memory Timing, Refresh and EDC Controller 79 |

| Extended Operating Temperature Range                 |

| 16,384 x 1 Dynamic R/W Random Access Memory 80       |

| 16,384 x 1 Dynamic R/W Random Access Memory 90       |

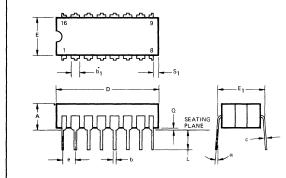

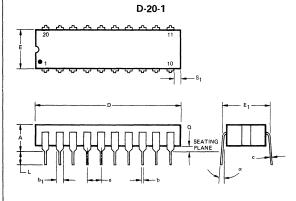

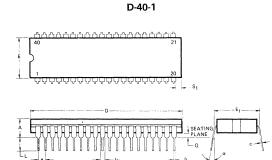

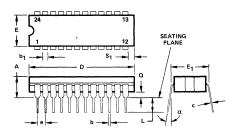

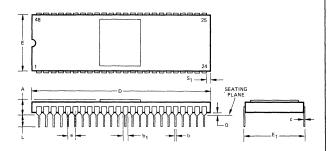

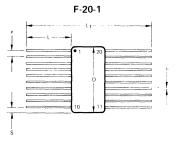

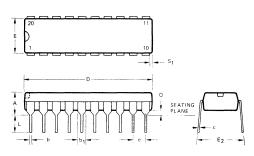

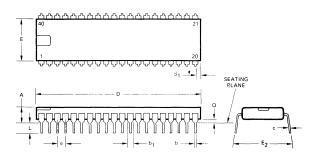

| Package Outlines A-1                                 |

| Sales Office Listing B-1                             |

|                                                      |

# The Am2960 Family **Dynamic Memory Support Products**

Advanced Micro Devices has developed a set of bipolar high-performance memory-support products to maximize the speed and reliability of MOS dynamic RAM systems. This family is designed to provide, in the minimum package count, all the logic, interface and control functions required in the address and data paths of memory systems based on 16K and 64K devices.

These TTL-compatible products are specified for use in equipment based on either bipolar or MOS CPUs. The Am2960 Series serves bipolar microprocessors such as the Am2901, Am29203, etc., while the AmZ8160 Series serves MOS microprocessors, such as the 16-bit AmZ8000.

# **Key System Level Features**

## **Maximum Memory Performance**

- Schottky performance with matched TPD paths and skew limit guarantees.

- Optimized interface devices for maximum speed.

- Hamming code EDC with internal ECL circuitry for maximum speed combined with maximum memory reliability.

#### Lowest Package Count Plus Maximum Flexibility

- LSI DMC Controller is designed for up to 64K RAMs.

- EDC is 16-bit expandable slice with byte I/O controls.

- Flexible interface for speed or minimum parts count.

#### **Operation in Any Timing Environment**

- Synchronous Clock Timing (AmZ8000 systems).

- Delay-line timing for maximum performance.

#### **Operation with Any RAM Refresh Mode**

128 of 256 Line Refresh

## **All Refresh Modes**

Burst Refresh

- Hidden (transparent) Refresh

- Cucle Steal Refresh

# Am2960 Family Product Summary

• Byte-op controls

#### Am2960 • AmZ8160 Error Detection and Correction (EDC)

- High-speed 16-bit slice expandable to 64 bits

- Single-bit correction/double-bit detection

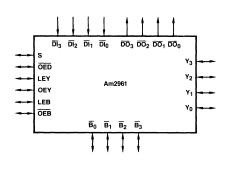

# Am2961/62 • AmZ8161/62 EDC Data Bus Buffer

- EDC interface between RAM, EDC and data bus

- 24mA bus drive with three-state control

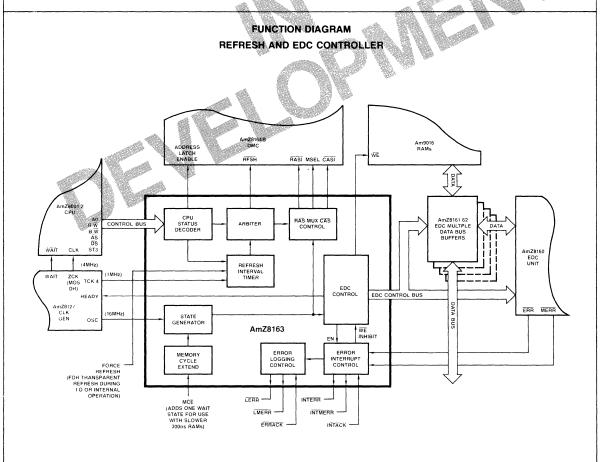

# AmZ8163 EDC and Refresh Control for AmZ8000 Systems

- RAS/MUX/CAS timing control for AmZ8164

- EDC control for word or byte read and write

- Memory/refresh request arbitration

Initialization and diagnostics built-in

• Refresh timer and control independent of CPU

Separated RAM I/O with undershoot protection

• Bus latches for byte-op or multiplexed buses

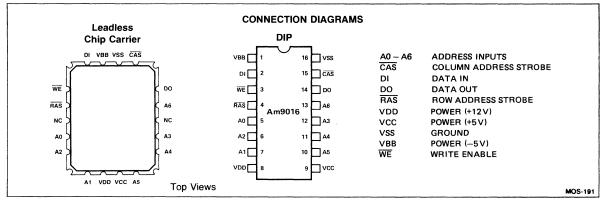

# Am2964 • AmZ8164 Dynamic Memory Control (DMC)

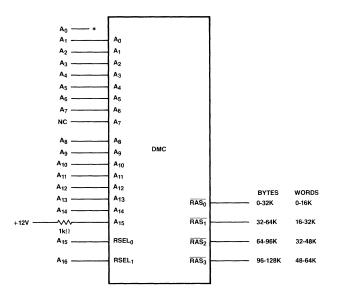

- 16-bit address for up to 64K RAMs

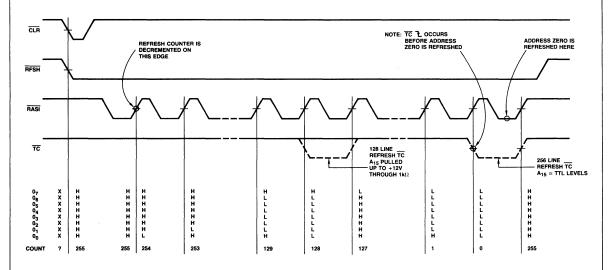

- Refresh Counter for 128- or 256-line refresh

## Am2965/66 • AmZ8165/66 Octal Dynamic RAM Drivers

- -0.5V maximum undershoot

- V<sub>OH</sub>/I<sub>OH</sub> specs for MOS with no external resistors

- 3-port 8-bit Schottky speed address MUX

- RAS and CAS paths on-chip for minimum skew

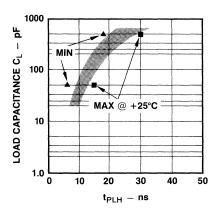

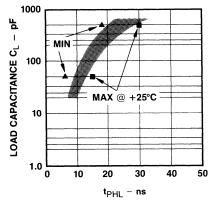

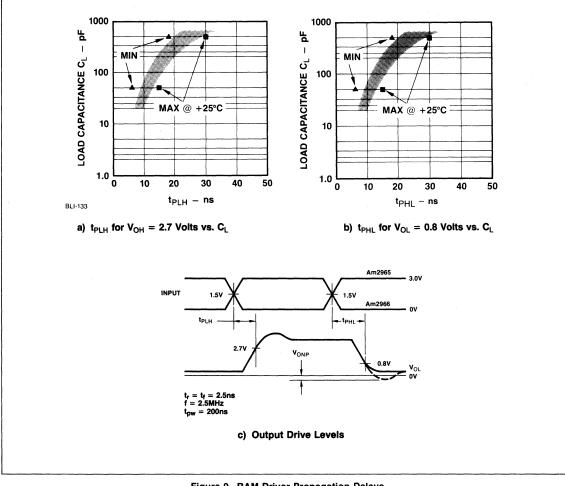

- tpi.H/tpHI min and max specs for 50pF and 500pF

- Pin-compatible with 'S240/244

# System Overview

By John R. Mick

As larger and larger dynamic RAMs are used with microprocessors, minicomputers and even larger computer systems, the design engineer becomes increasingly concerned about the reliability of his memory system. As the RAM size increases, the error rate caused by alpha particles increases significantly. It is essential therefore that all new memory designs using higher density dynamic RAMs (and perhaps even larger static RAMs) use error detection and correction (EDC) to improve memory system reliability. Current estimates are that the reliability can be increased by a factor of 60 or more if a suitable error detection and correction scheme is employed.

Advanced Micro Devices is introducing a new set of LSI devices that allows the designer to implement error detection and correction in a cost effective fashion. In addition, EDC can slash field maintenance costs and allow systems to run longer uninterrupted due to soft or hard memory errors. If desired, memory errors can be logged for future use in determining marginal RAM chips by running memory diagnostics routines.

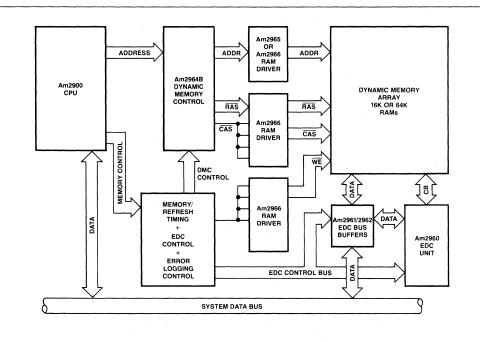

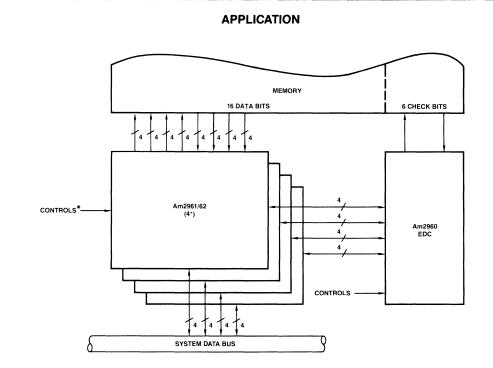

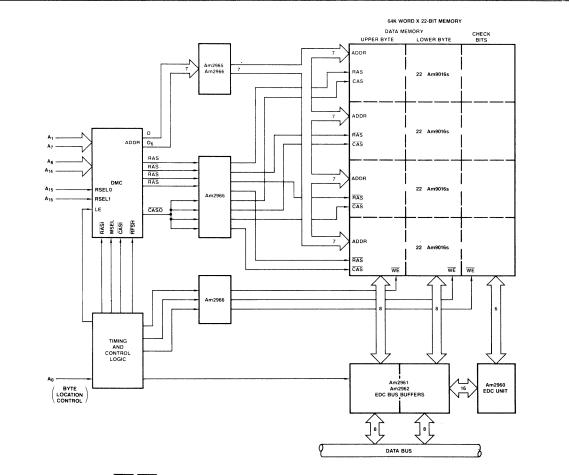

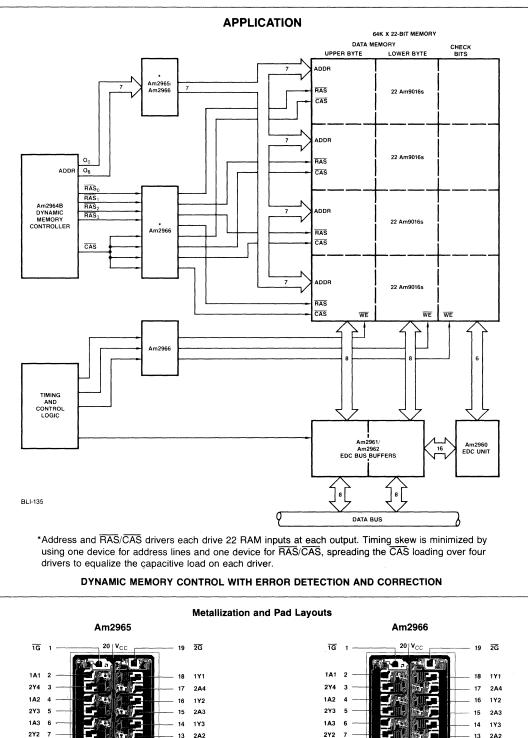

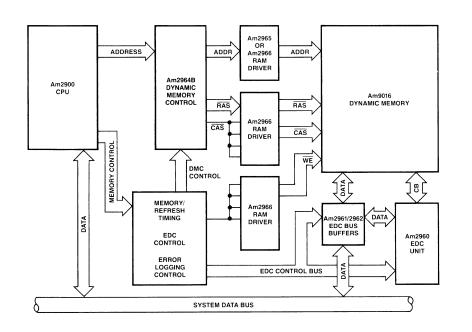

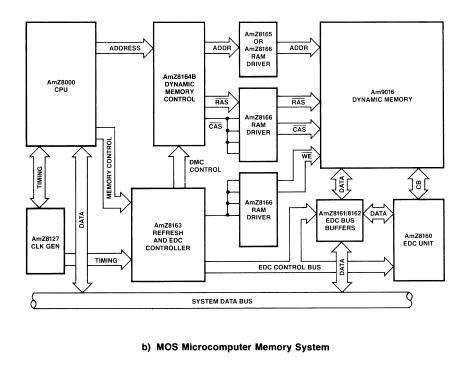

The Advanced Micro Devices Am2960 Memory Support family of products includes the Am2960 Error Detection and Correction Unit, the Am2961/2962 EDC Bus Buffers, the Am2964B Dynamic Memory Controller and the Am2965/2966 Dynamic RAM Drivers. The system interconnection of these devices is shown in Figure 1 where a typical Am2900 microcomputer memory system is configured. As shown in this diagram, the memory support subsystem interfaces to the System Data Bus, Address Bus, and control signals.

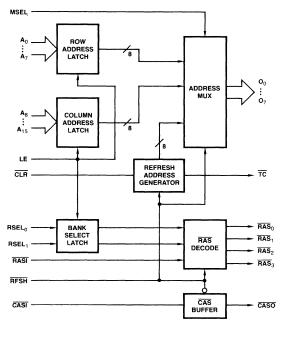

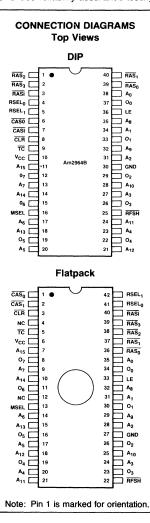

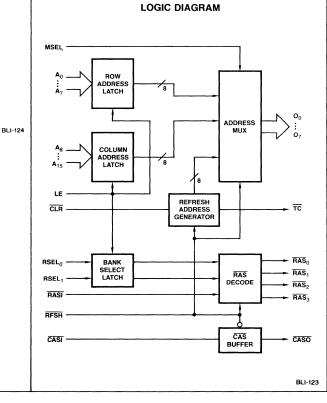

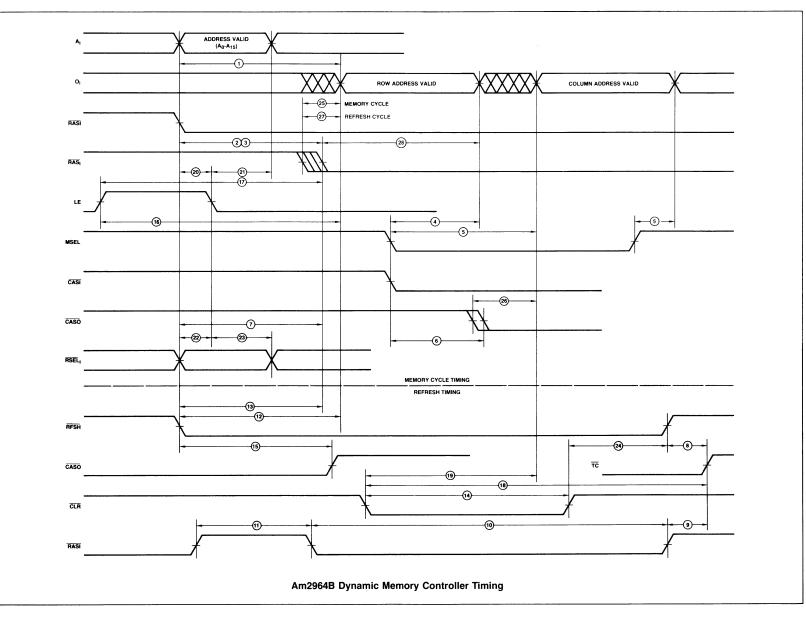

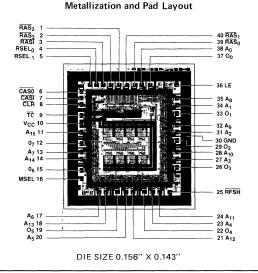

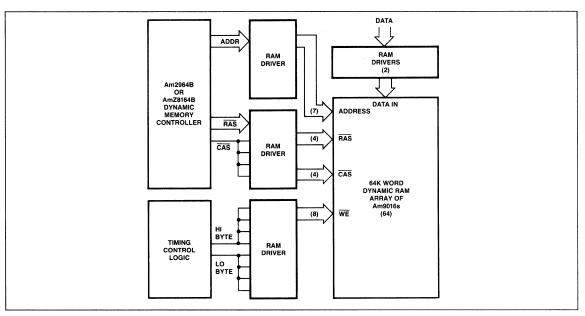

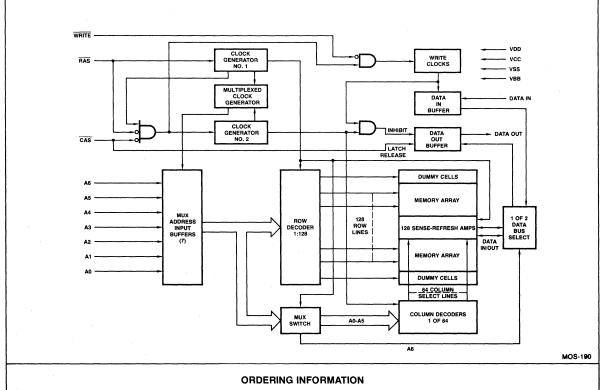

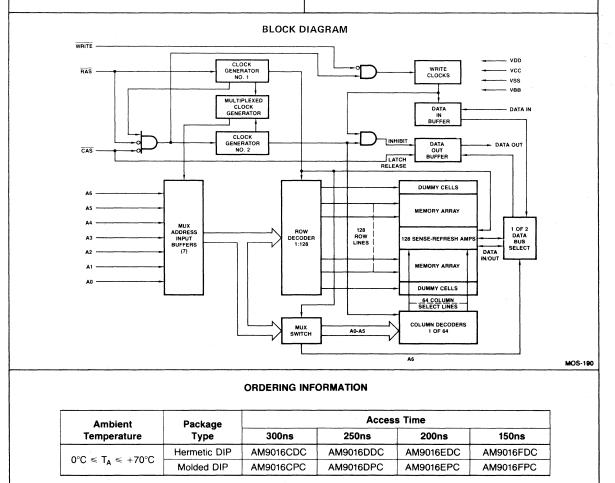

The Am2964B Dynamic Memory Controller is used to provide all address handling, as well as RAS and CAS decoding and control. A block diagram of the Am2964B dynamic memory controller is shown in Figure 2. The device contains 18 input latches for capturing an 18-bit address for memory control. The two highest order addresses are decoded in the Am2964B to select one of four banks of RAM by selecting one of the four RAS outputs.

The Am2964B is designed to operate with either 16K Dynamic RAMs or 64K Dynamic RAMs. Thus, the designer either uses 14 of the multiplexer address inputs and 7 of the address outputs or all 16 of the multiplexer address inputs and all 8 of the address outputs as needed by the memory. In the case of 16K dynamic RAMs, 7 address inputs are provided to the RAM during the RAS LOW signal and then the 8-bit multiplexer is switched so that 7 upper address bits are provided to the RAM for the  $\overline{CAS}$  LOW part of the cycle. The Am2964B Dynamic Memory Controller contains an 8-bit refresh counter that is used to supply the refresh address to the dynamic memory during the refresh mode. A  $\overline{CAS}$  buffer is included in the dynamic memory controller so that the  $\overline{CAS}$  output can be inhibited during refresh.

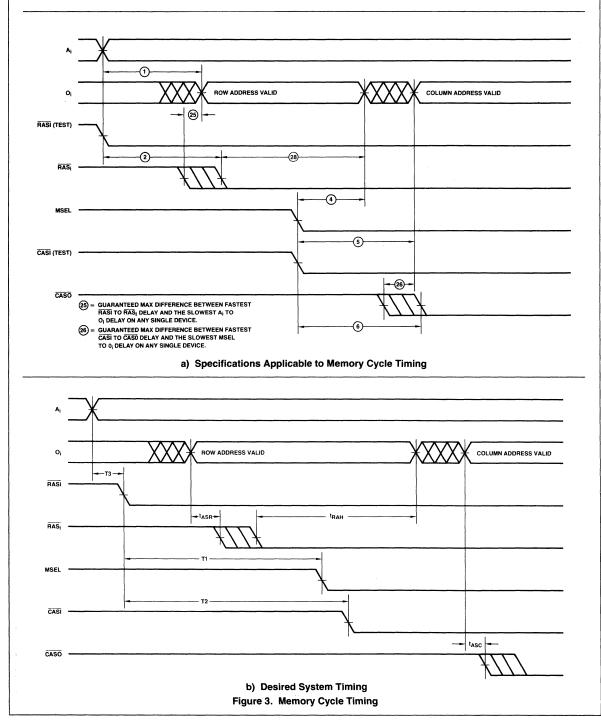

Figure 1. Am2900 High Performance Computer Memory

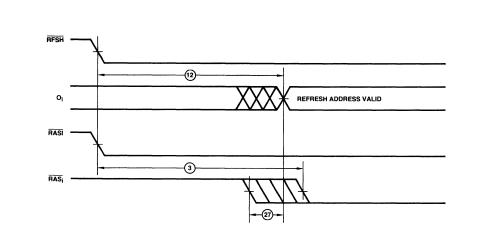

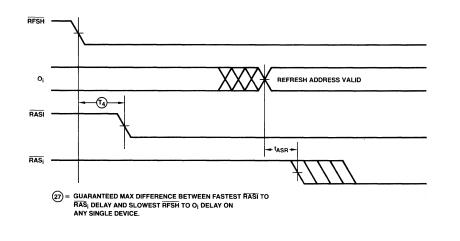

Normal operation of the Dynamic Memory Controller is to provide the address, close the input address latches and kick off a normal memory cycle. This is accomplished by bringing the RASI input LOW which will cause one of the RAS outputs to go LOW. After the required memory timing, the MSEL input will be used to switch the multiplexer to the other address latch. Then, the CASI input will be driven LOW causing the CASO output to go LOW and execute the CAS part of the memory cycle. The refresh cycle is executed by driving the RFSH input LOW which causes the multiplexer to select the refresh counter to its address outputs. Then, the RASI input is driven LOW which causes all four RAS outputs to go LOW. This will simultaneously refresh all four banks of dynamic RAMs controlled by the Am2964B Dynamic Memory Controller. When either the RFSH or RASI input is brought HIGH, the refresh counter is advanced so it will be ready for the next refresh cycle.

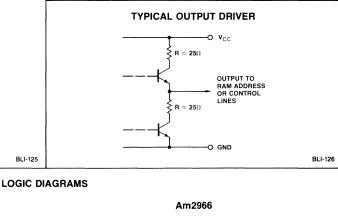

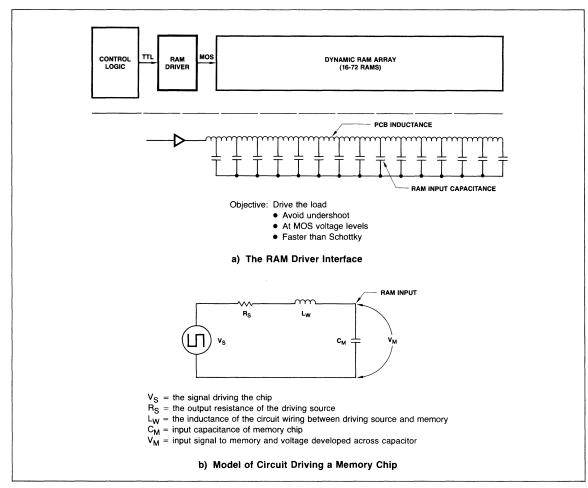

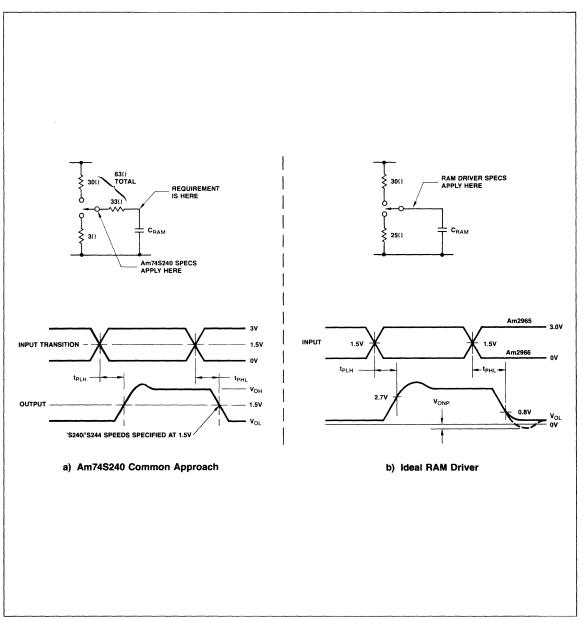

As can be seen in Figure 1, Dynamic RAM Drivers can be used in large memory systems to buffer the Address, RAS, CAS and WRITE ENABLE signals to the RAMs. The Am2965 and Am2966 are pin compatible devices with the Am74S240 and Am74S244. These RAM drivers are specifically designed for driving dynamic RAMs and feature high capacitance drive, guaranteed maximum undershoot of less than -0.5 volts and high V<sub>OH</sub> of greater than V<sub>CC</sub> -1.15 volts. The Am2965 is inverting and the Am2966 is noninverting. The devices feature symmetrical rise and fall times and have guaranteed minimum and maximum t<sub>PD</sub> specifications at both 50pF and 500pF loads. loads.

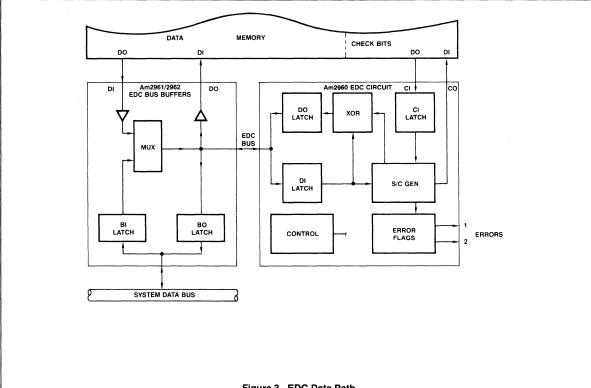

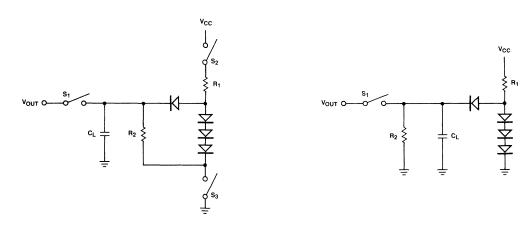

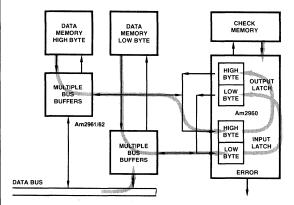

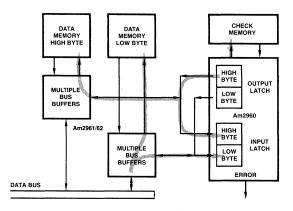

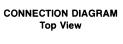

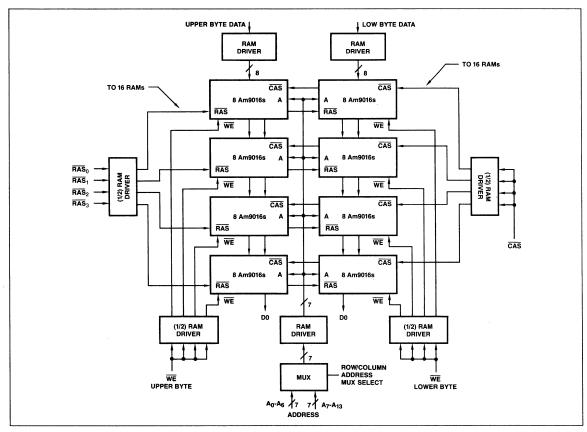

Data interface between the dynamic memories, the Am2960 EDC chip and the system data bus is accomplished by means of the Am2961/2962 bus buffers. Figure 3 depicts the ar-

chitecture of these devices along with a simplified block diagram of the Am2960. The Am2961 is inverting between the system data bus and the EDC bus while the Am2962 is noninverting between the system data bus and the EDC bus. As shown in Figure 3, the Am2961 and Am2962 contain two internal latches, a multiplexer, and a RAM driver output buffer.

These devices feature 4-bit wide data paths to and from the RAM, to the EDC, and to the system data bus. The bus-input (BI) latch is used predominantly in byte WRITE operations so that an incoming byte from the system data bus can be stored while the memory is being read and any necessary correction is made in the bytes not being changed. The bus-output (BO) latch in the bus buffer is used predominantly for storing the output data if the processor is in the single step mode. In the single step mode it is necessary to hold the output data on the system data bus but the memory must be released for refresh.

The Am2960 Error Detection and Correction Unit contains all the logic necessary to generate check bits on a 16-bit data field according to a modified Hamming code and to correct the data word when check bits are supplied. Operating on the data read from memory, the Am2960 will correct any single bit error and will detect all double and some triple bit errors. For 16-bit words, 6 check bits are used. The Am2960 is expandable to operate on 32-bit words (7 check bits) and 64-bit words (8 check bits). In all configurations, the device makes the error syndrome bits available on separate outputs for data logging.

The Am2960 also features two diagnostic modes in which diagnostic data can be forced into portions of the device to simplify device testing and to execute system diagnostic functions.

Figure 3. EDC Data Path

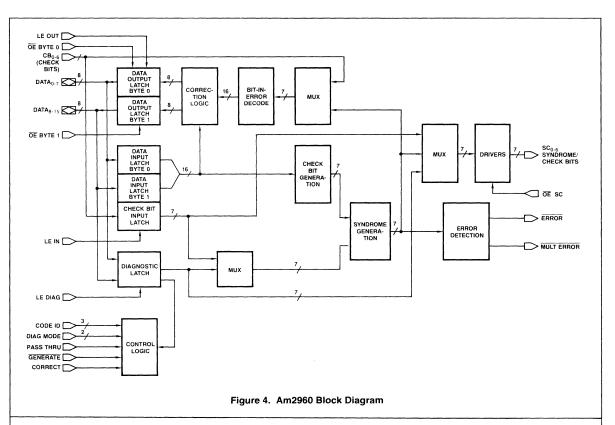

As shown in the Figure 4 Am2960 block diagram, the device consists of the following:

- · Data Input Latch

- Check Bit Input Latch

- Check Bit Generation Logic

- Syndrome Generation Logic

- · Error Detection Logic

- Error Correction Logic

- Data Output Latch

- Diagnostic Latch

- Control Latch

16 bits of data are loaded into the Data Input Latch from the bidirectional Data lines under control of the Latch Enable input. Depending on the control mode the input data is either used for check bit generation or error detection/correction.

Seven check bits are loaded into the Check Bit Input Latch under control of LE IN. Check bits are used in the Error Detection and Error Correction modes.

The Check Bit Generation Logic generates the appropriate check bits for the 16 bits of data in the Data Input Latch. The check bits are generated according to a modified Hamming code.

In both Error Detection and Error Correction modes, the Syndrome Generation Logic block compares the check bits read from memory against a newly generated set of check bits produced for the data read in from memory. If both sets of check bits match, then there are no errors. If there is a mismatch, then one or more of the data or check bits is in error. The syndrome bits are produced by an exclusive-OR of the two sets of check bits. If the two sets of check bits are identical (meaning there are no errors) the syndrome bits will be all zeroes. If the syndromes are non-zero, the syndrome bits can be decoded to determine the number of errors and the bit-in-error (single error).

The Error Detection Logic decodes the syndrome bits generated by the Syndrome Generation Logic. If there are no errors in either the input data or check bits, the ERROR and MULTI ERROR outputs remain HIGH. If one or more errors are detected, ERROR goes LOW. If two or more errors are detected, both ERROR and MULTI ERROR go LOW.

For single errors, the Error Correction Logic complements (corrects) the single data bit in error. This corrected data is loadable into the Data Output Latch, which can then be read onto the bidirectional data lines. If the single error is one of the check bits, the correction logic does not place corrected bits on the syndrome/check bit outputs. If the corrected check bits are needed the EDC must be switched to Generate Mode.

The Data Output Latch is used for storing the result of an error correction operation. The latch is loaded from the correction logic under control of the Data Output Latch Enable, LE OUT. The Data Output Latch may also be loaded directly from the Data Input Latch under control of the PASS THRU control input. The Data Output Latch is split into two 8-bit (byte) latches which may be enabled independently for reading onto the bidirectional data lines.

The Diagnostic Latch is a 16-bit latch loadable from the bidirectional data lines under control of the Diagnostic Latch Enable, LE DIAG. The Diagnostic Latch contains check bit information in one byte and control information in the other byte. The Diagnostic Latch is used for driving the device when in Internal Control Mode, or for supplying check bits when in one of the Diagnostic Modes.

The control logic determines the specific mode the device operates in. Normally the control logic is driven by external control inputs. However, in Internal Control Mode, the control signals are instead read from the Diagnostic Latch.

As can be seen, the Am2960 Family can be used to significantly improve the MTTF (Mean Time to Failure) of memory systems. By boosting memory reliability, two competitive advantages are gained. First, the system can run uninterrupted with either single soft errors or the loss of one memory chip. Second, field maintenance costs can be reduced in that service can be scheduled on a regular basis and faulty memory components can be replaced by reviewing logged errors.

The demand for reliable system performance is increasing steadily. Reliability is a must for applications in aerospace, medical, banking, process control and on-line systems. Applications such as word processors, small business systems and telecommunications also need memory reliability, as their users do not have the technical staff to handle system failures and are willing to pay for the convenience of smooth, error free operation. The Am2960 Family is the solution in these systems.

# Am2960 Fast Error Detection and Correction for Memories

# Corrects All Single-Bit Errors

Corrects all single bit errors. Detects all double and some triple bit errors.

# Expandable

One Am2960 provides Error Detection and Correction for 16-bits. Two Am2960s handle 32 bits; four Am2960s handle 64 bits.

# Fast

Worst case 32 nanoseconds for error detect and 65 nanoseconds for error correct (16 bits).

# **Latches Built-In**

Check Bit, Data, and Diagnostic latches are built-in to save MSI.

# Flexible

Can be used with Am2900-based designs, the AmZ8000 or other processors.

# **Diagnostics Built-In**

Logic on-chip for device test and softwarecontrolled diagnostics.

# Increases Memory Reliability

And can significantly reduce field maintenance costs.

# A Must for 64K RAMs

Alpha error rates are several times higher for 64K RAMs than 16Ks.

Also available as the AmZ8160 for AmZ8000 Systems

# Am2960 EDC

#### **Cascadable 16-Bit Error Detection and Correction Unit**

#### DISTINCTIVE CHARACTERISTICS

#### Boosts Memory Reliability

Corrects all single-bit errors. Detects all double and some triple-bit errors. Reliability of dynamic RAM systems is increased more than 60-fold.

#### Very High Speed

Perfect for MOS microprocessor, minicomputer, and mainframe systems.

- Data in to error detect: 32ns worst case.

- Data in to corrected data out: 65ns worst case.

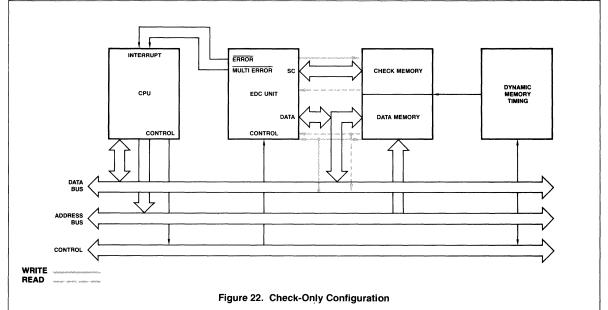

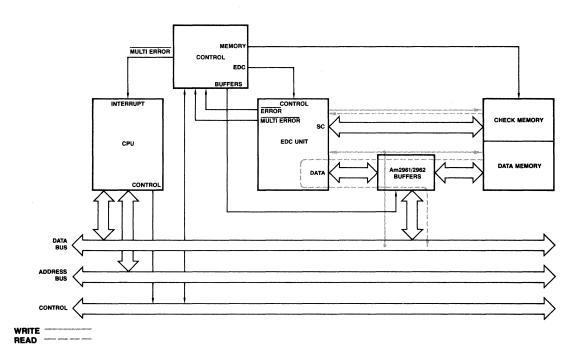

High performance systems can use the Am2960 EDC in check-only mode to avoid memory system slowdown.

Replaces 25 to 50 MSI chips

All necessary features are built-in to the Am2960 EDC, including diagnostics, data in, data out, and check bit latches.

Handles Data Words From 8 to 64 Bits The Am2960 EDC cascades: 1 EDC for 8 or 16 bits, 2 for 32 bits, 4 for 64 bits.

#### Easy Byte Operations

Separate byte enables on the data out latch simplify the steps and cuts the time required for byte writes.

• Diagnostics Built-In The processor may completely exercise the EDC under

software control to check for proper operation of the EDC.

#### TABLE OF CONTENTS

| FUNCTIONAL DESCRIPTION                     |

|--------------------------------------------|

| Block Diagram8                             |

| Architecture                               |

| Pin Definitions                            |

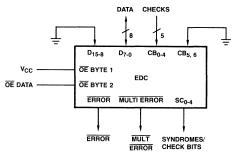

| 16-Bit Configuration                       |

| 32-Bit Configuration                       |

| 64-Bit Configuration                       |

| ELECTRICAL SPECIFICATIONS                  |

| APPLICATIONS                               |

| Byte Write                                 |

| Diagnostics                                |

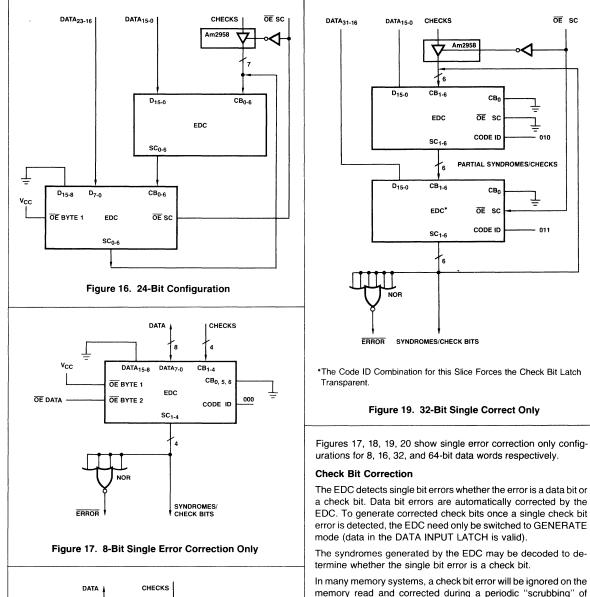

| Eight-Bit Data Word                        |

| Other Word Widths                          |

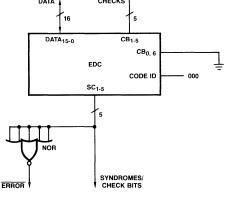

| Single Error Correction Only               |

| Check Bit Correction                       |

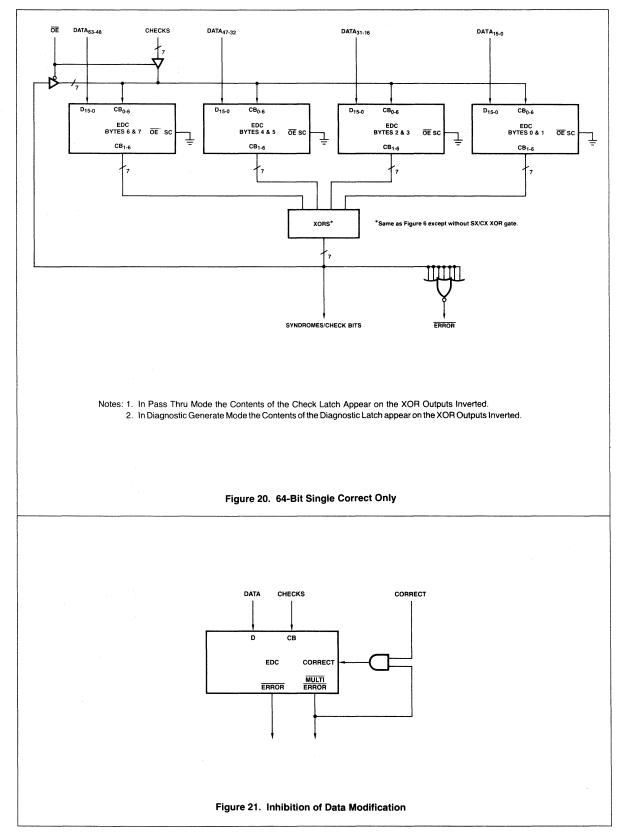

| Multiple Errors                            |

| SYSTEM DESIGN CONSIDERATIONS               |

| High Performance Parallel Operation        |

| EDC in the Data Path                       |

| Scrubbing Avoids Memory Errors             |

| Correction of Double Bit Errors            |

| Error Logging and Preventative Maintenance |

| Reducing Check Bit Overhead                |

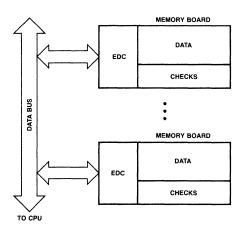

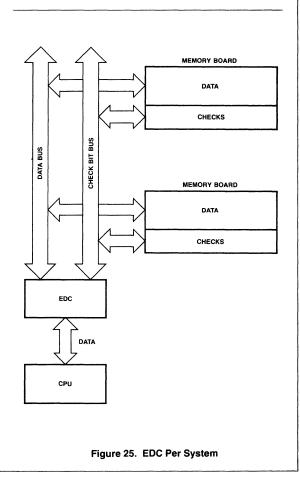

| EDC Per Board vs. EDC Per System           |

| FUNCTIONAL EQUATIONS                       |

| Am2960 BOOSTS MEMORY RELIABILITY           |

|                                            |

#### **GENERAL DESCRIPTION**

The Am2960 Error Detection and Correction Unit (EDC) contains the logic necessary to generate check bits on a 16-bit data field according to a modified Hamming Code, and to correct the data word when check bits are supplied. Operating on data read from memory, the Am2960 will correct any single bit error and will detect all double and some triple bit errors. For 16-bit words, 6 check bits are used. The Am2960 is expandable to operate on 32-bit words (7 check bits) and 64-bit words (8 check bits). In all configurations, the device makes the error syndrome available on separate outputs for data logging.

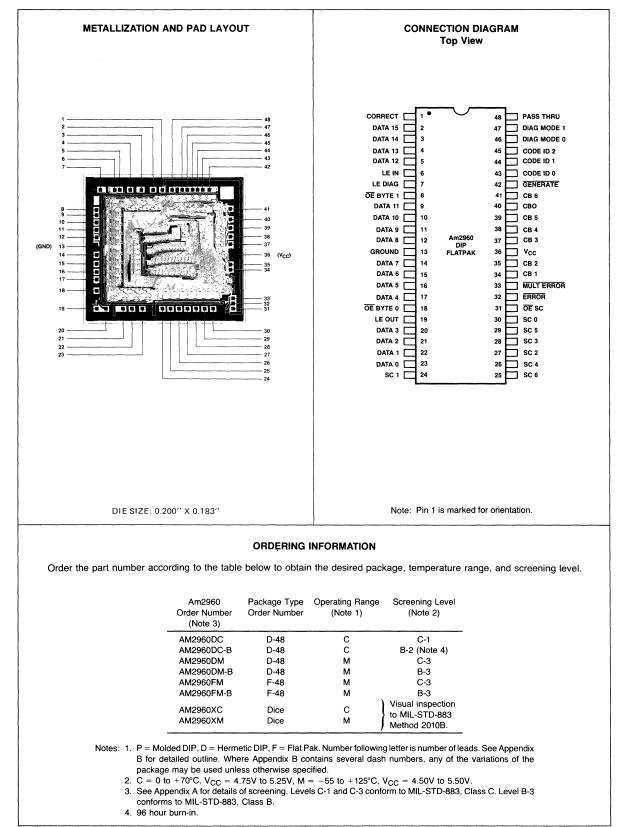

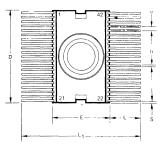

The Am2960 also features two diagnostic modes, in which diagnostic data can be forced into portions of the chip to simplify device testing and to execute system diagnostic functions. The product is supplied in a 48 lead hermetic DIP package.

BLOCK DIAGRAM

Am2960

80

#### **EDC Architecture**

The EDC Unit is a powerful 16-bit cascadable slice used for check bit generation, error detection, error correction and diagnostics.

As shown in the block diagram, the device consists of the following:

- Data Input Latch

- Check Bit Input Latch

- Check Bit Generation Logic

- Syndrome Generation Logic

- Error Detection Logic

- Error Correction Logic

- Data Output Latch

- Diagnostic Latch

- Control Logic

#### **Data Input Latch**

16 bits of data are loaded from the bidirectional DATA lines under control of the Latch Enable input, LE IN. Depending on the control mode the input data is either used for check bit generation or error detection/correction.

#### **Check Bit Input Latch**

Seven check bits are loaded under control of LE IN. Check bits are used in the Error Detection and Error Correction modes.

#### **Check Bit Generation Logic**

This block generates the appropriate check bits for the 16 bits of data in the Data Input Latch. The check bits are generated according to a modified Hamming code.

#### Syndrome Generation Logic

In both Error Detection and Error Correction modes, this logic block compares the check bits read from memory against a newly generated set of check bits produced for the data read in from memory. If both sets of check bits match, then there are no errors. If there is a mismatch, then one or more of the data or check bits is in error.

The syndrome bits are produced by an exclusive-OR of the two sets of check bits. If the two sets of check bits are identical

(meaning there are no errors) the syndrome bits will be all zeroes. If there are errors, the syndrome bits can be decoded to determine the number of errors and the bit-in-error.

#### Error Detection Logic

This section decodes the syndrome bits generated by the Syndrome Generation Logic. If there are no errors in either the input data or check bits, the ERROR and MULT ERROR outputs remain HIGH. If one or more errors are detected, ERROR goes LOW. If two or more errors are detected, both ERROR and MULT ERROR go LOW.

#### **Error Correction Logic**

For single errors, the Error Correction Logic complements (corrects) the single data bit in error. This corrected data is loadable into the Data Output Latch, which can then be read onto the bidirectional data lines. If the single error is one of the check bits, the correction logic does not place corrected check bits on the syndrome/check bit outputs. If the corrected check bits are needed the EDC must be switched to Generate Mode.

#### Data Output Latch

The Data Output Latch is used for storing the result of an error correction operation. The latch is loaded from the correction logic under control of the Data Output Latch Enable, LE OUT. The Data Output Latch may also be loaded directly from the Data Input Latch under control of the PASS THRU control input.

The Data Output Latch is split into two 8-bit (byte) latches which may be enabled independently for reading onto the bidirectional data lines.

#### **Diagnostic Latch**

This is a 16-bit latch loadable from the bidirectional data lines under control of the Diagnostic Latch Enable, LE DIAG. The Diagnostic Latch contains check bit information in one byte and control information in the other byte. The Diagnostic Latch is used for driving the device when in Internal Control Mode, or for supplying check bits when in one of the Diagnostic Modes.

#### **Control Logic**

The control logic determines the specific mode the device operates in. Normally the control logic is driven by external control inputs. However, in Internal Control Mode, the control signals are instead read from the Diagnostic Latch.

#### PIN DEFINITIONS

- DATA<sub>0-15</sub> 16 bidirectional data lines. They provide input to the Data Input Latch and Diagnostic Latch, and receive output from the Data Output Latch. DATA<sub>0</sub> is the least significant bit; DATA<sub>15</sub> the most significant.

- CB<sub>0-6</sub> Seven Check Bit input lines. The check bit lines are used to input check bits for error detection. Also used to input syndrome bits for error correction in 32 and 64-bit configurations.

- LE IN Latch Enable Data Input Latch. Controls latching of the input data. When HIGH the Data Input Latch and Check Bit Input Latch follow the input data and input check bits. When LOW, the Data Input Latch and Check Bit Input Latch are latched to their previous state.

- GENERATE Generate Check Bits input. When this input is LOW the EDC is in the Check Bit Generate Mode. When HIGH the EDC is in the Detect Mode or Correct Mode.

In the Generate Mode the circuit generates the check bits or partial check bits specific to the data in the Data Input Latch. The generated check bits are placed on the SC outputs.

In the Detect or Correct Modes the EDC detects single and multiple errors, and generates syndrome bits based upon the contents of the Data Input Latch and Check Bit Input Latch. In Correct Mode, single-bit errors are also automatically corrected – corrected data is placed at the inputs of the Data Output Latch. The syndrome result is placed on the SC outputs and indicates in a coded form the number of errors and the bit-in-error.

- SC<sub>0-6</sub> Syndrome/Check Bit outputs. These seven lines hold the check/partial-check bits when the EDC is in Generate Mode, and will hold the syndrome/ partial syndrome bits when the device is in Detect or Correct Modes. These are 3-state outputs.

- **OE SC** Output Enable Syndrome/Check Bits. When LOW, the 3-state output lines SC<sub>0-6</sub> are enabled. When HIGH, the SC outputs are in the high impedance state.

- ERROR Error Detected output. When the EDC is in Detect or Correct Mode, this output will go LOW if one or more syndrome bits are asserted, meaning there are one or more bit errors in the data or check bits. If no syndrome bits are asserted, there are no errors detected and the output will be HIGH. In Generate Mode, ERROR is forced HIGH. (In a 64-bit configuration, ERROR must be externally implemented.)

- **MULT ERROR** Multiple Errors Detected output. When the EDC is in Detect or Correct Mode, this output if LOW indicates that there are two or more bit errors that have been detected. If HIGH this indicates that either one or no errors have been detected. In

Generate mode, MULT ERROR is forced HIGH. (In a 64-bit configuration, MULT ERROR must be externally implemented.)

- **CORRECT** Correct input. When HIGH this signal allows the correction network to correct any single-bit error in the Data Input Latch (by complementing the bit-in-error) before putting it onto the Data Output Latch. When LOW the EDC will drive data directly from the Data Input Latch to the Data Output Latch without correction.

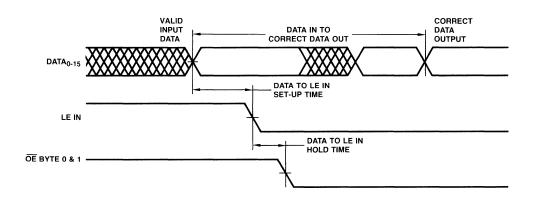

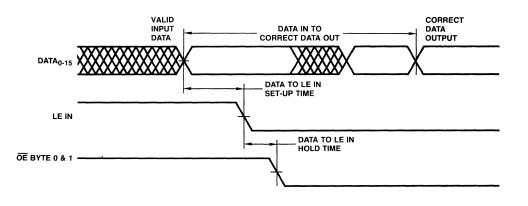

- LE OUT Latch Enable Data Output Latch. Controls the latching of the Data Output Latch. When LOW the Data Output Latch is latched to its previous state. When HIGH the Data Output Latch follows the output of the Data Input Latch as modified by the correction logic network. In Correct Mode, singlebit errors are corrected by the network before loading into the Data Output Latch. In Detect Mode, the contents of the Data Input Latch are passed through the correction network unchanged into the Data Output Latch. The inputs to the Data Output Latch are unspecified if the EDC is in Generate Mode.

- **OE BYTE 0**, Output Enable Bytes 0 and 1, Data Output

- **OE** BYTE 1 Latch. These lines control the 3-state outputs for each of the two bytes of the Data Output Latch. When LOW these lines enable the Data Output Latch and when HIGH these lines force the Data Output Latch into the high impedance state. The two enable lines can be separately activated to enable only one byte of the Data Output Latch at a time.

- DIAG Diagnostic Mode Select. These two lines control MODE<sub>0-1</sub> the initialization and diagnostic operation of the EDC.

- **CODE ID**<sub>0-2</sub> Code Identification inputs. These three bits identify the size of the total data word to be processed and which 16-bit slice of larger data words a particular EDC is processing. The three allowable data word sizes are 16, 32 and 64 bits and their respective modified Hamming codes are designated 16/22, 32/39 and 64/72. Special CODE ID input 001 (ID<sub>2</sub>, ID<sub>1</sub>, ID<sub>0</sub>) is also used to instruct the EDC that the signals CODE ID<sub>0-2</sub>, DIAG MODE<sub>0-1</sub>, CORRECT and PASS THRU are to be taken from the Diagnostic Latch, rather than from the input control lines.

- LE DIAG Latch Enable Diagnostic Latch. When HIGH the Diagnostic Latch follows the 16-bit data on the input lines. When LOW the outputs of the Diagnostic Latch are latched to their previous states. The Diagnostic Latch holds diagnostic check bits, and internal control signals for CODE ID<sub>0-2</sub>, DIAG MODE<sub>0-1</sub>, CORRECT and PASS THRU.

#### FUNCTIONAL DESCRIPTION

The EDC contains the logic necessary to generate check bits on a 16-bit data field according to a modified Hamming code. Operating on data read from memory, the EDC will correct any single-bit error, and will detect all double and some triple-bit errors. The Am2960 may be configured to operate on 16-bit data words (with 6 check bits), 32-bit data words (with 7 check bits) and 64-bit data words (with 8 check bits). In fact the EDC can be configured to work on data words from 8 to 64 bits. In all configurations, the device makes the error syndrome bits available on separate outputs for error data logging.

#### Code and Byte Specification

The EDC may be configured in several different ways and operates differently in each configuration. It is necessary to indicate to the device what size data word is involved and which bytes of the data word it is processing. This is done with input lines CODE  $ID_{0-2}$ , as shown in Table I. The three modified Hamming codes referred to in Table I are:

- 16/22 16 data bits

- 6 check bits

- 22 bits in total.

- 32/39 code 32 data bits

- 7 check bits

- 39 bits in total.

- 64/72 code 64 data bits

- 8 check bits

- 72 bits in total.

CODE ID input 001  $(ID_2, ID_1, !D_0)$  is a special code used to operate the device in Internal Control Mode (described later in this section).

#### **Control Mode Selection**

The device control lines are GENERATE, CORRECT, PASS THRU, DIAG MODE<sub>0-1</sub> and CODE ID<sub>0-2</sub>. Table III indicates the operating modes selected by various combinations of the control line inputs.

#### Diagnostics

Table II shows specifically how DIAG MODE<sub>0-1</sub> select between normal operation, initialization and one of two diagnostic modes.

The Diagnostic Modes allow the user to operate the EDC under software control in order to verify proper functioning of the device.

#### Check and Syndrome Bit Labeling

The check bits generated in the EDC are designated as follows:

- 16-bit configuration CX C0, C1, C2, C4, C8;

- 32-bit configuration CX, C0, C1, C2, C4, C8, C16;

- 64-bit configuration CX, C0, C1, C2, C4, C8, C16, C32.

Syndrome bits are similarly labeled SX through S32. There are only 6 syndrome bits in the 16-bit configuration, 7 for 32 bits and 8 syndrome bits in the 64-bit configuration.

#### Initialize Mode

The inputs of the Data Output Latch are forced to zeroes. The check bit outputs (SC) are generated to correspond to the all-zero data. ERROR and MULT ERROR are forced HIGH in the Initialize Mode.

Initialize Mode is useful after power up when RAM contents are random. The EDC may be placed in initialize mode and its' outputs written in to all memory locations by the processor.

#### TABLE I. HAMMING CODE AND SLICE IDENTIFICATION.

| CODE<br>ID <sub>2</sub> | CODE<br>ID <sub>1</sub> | CODE<br>ID <sub>0</sub> | Hamming Code and Slice Selected |

|-------------------------|-------------------------|-------------------------|---------------------------------|

| 0                       | 0                       | 0                       | Code 16/22                      |

| 0                       | 0                       | 1                       | Internal Control Mode           |

| 0                       | 1                       | 0                       | Code 32/39, Bytes 0 and 1       |

| 0                       | 1                       | 1                       | Code 32/39, Bytes 2 and 3       |

| 1                       | 0                       | 0                       | Code 64/72, Bytes 0 and 1       |

| 1                       | 0                       | 1                       | Code 64/72, Bytes 2 and 3       |

| 1                       | 1                       | 0                       | Code 64/72, Bytes 4 and 5       |

| 1                       | 1                       | 1                       | Code 64/72, Bytes 6 and 7       |

#### TABLE II. DIAGNOSTIC MODE CONTROL.

| DIAG<br>MODE <sub>1</sub> | DIAG<br>MODE <sub>0</sub> | Diagnostic Mode Selected                                                                                                                                                                                                                |

|---------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                         | 0                         | Non-diagnostic mode. The EDC functions normally in all modes.                                                                                                                                                                           |

| 0                         | 1                         | <b>Diagnostic Generate.</b> The contents of the Diagnostic Latch are substi-<br>tuted for the normally generated check bits when in the Generate Mode.<br>The EDC functions normally in the Detect or Correct modes.                    |

| 1                         | 0                         | <b>Diagnostic Detect/Correct.</b> In the Detect or Correct Mode, the contents of the Diagnostic Latch are substituted for the check bits normally read from the Check Bit Input Latch. The EDC functions normally in the Generate Mode. |

| 1                         | 1                         | <b>Initialize.</b> The outputs of the Data Input Latch are forced to zeroes (and latched upon removal of the Initialize Mode) and the check bits generated correspond to the all-zero data.                                             |

#### HAMMING CODE SELECTION

The Am2960 EDC uses a modified Hamming Code that allows 1) the EDC to be cascaded, 2) all double errors to be detected, 3) the gross error conditions of all 0s or 1s to be detected.

The error correction code can be selected independent of the processor with the exception of diagnostics software.

Diagnostic software run by a processor to checkout the EDC system must know specifically which code is being used. This is only a problem when the EDC replaces an existing MSI im-

plementation on an existing computer. In this case, the computer's software must first determine which of two codes (the old one used by the MSI implementation or the new one used by the EDC) is used by the computer's memory system.

This is easily determined by writing a test data word into memory and then examining whether the generated check bits are typical of the old or the new code. From then on the software runs only the diagnostic appropriate for the code used on that particular computer's memory system.

| Operating              | Diagnosti       | c Mode**        | GEN                             | ERATE                  |

|------------------------|-----------------|-----------------|---------------------------------|------------------------|

| Mode                   | DM <sub>1</sub> | DM <sub>0</sub> | 0                               | 1                      |

| Normal                 | 0               | 0               | Generate                        | Correct*               |

| Diagnostic<br>Generate | 0               | 1               | Diagnostic<br>Generate          | Correct*               |

| Diagnostic<br>Correct  | 1               | 0               | Generate                        | Diagnostic<br>Correct* |

| Initialize             | 1               | 1               | Initialize                      | Initialize             |

| Pass Thru              |                 |                 | asserted the C<br>e Pass Thru I |                        |

## TABLE III. Am2960 OPERATING MODES

\*Correct if the CORRECT Input is HIGH, Detect if the CORRECT Input is LOW.

\*\*In Code  $ID_{2-0}$  001 ( $ID_2$ ,  $ID_1$ ,  $ID_0$ )  $DM_1$  and  $DM_0$  are taken from the Diagnostic Latch.

#### FUNCTIONAL DESCRIPTION – 16-BIT DATA WORD CONFIGURATION

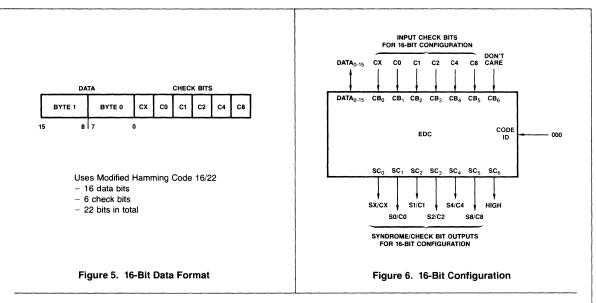

The 16-bit format consists of 16 data bits, 6 check bits and is referred to as 16/22 code (see Figure 5.)

The 16-bit configuration is shown in Figure 6.

#### Generate Mode

In this mode check bits will be generated that correspond to the contents of the Data Input Latch. The check bits generated are placed on the outputs  $SC_{0-5}$  (SC<sub>6</sub> is a logical one, or high).

Check bits are generated according to a modified Hamming code. Details of the code for check bit generation are contained in Table IV. Each check bit is generated as either an XOR or XNOR of eight of the 16 data bits as indicated in the table. The XOR function results in an even parity check bit, the XNOR is an odd parity check bit.

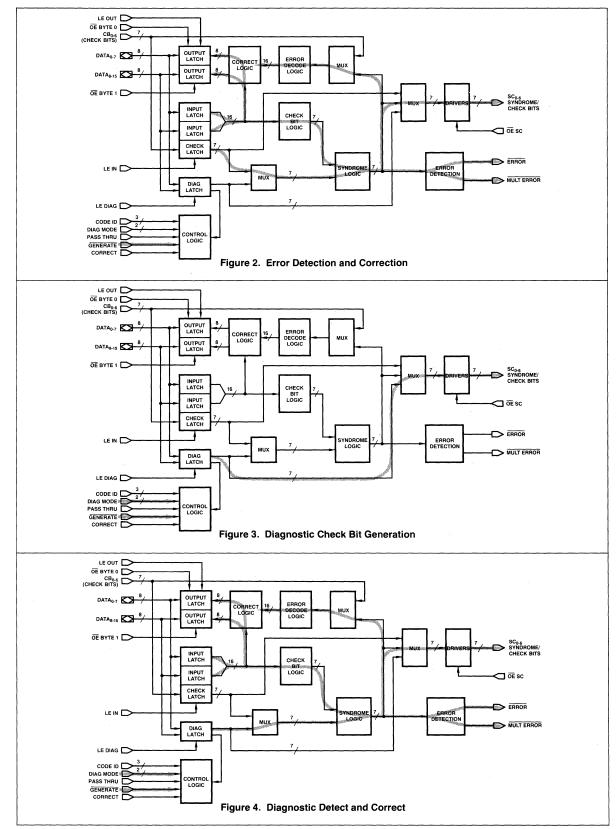

Figure 1 shows the data flow in the Generate Mode.

#### **Detect Mode**

In this mode the device examines the contents of the Data Input Latch against the Check Bit Input Latch, and will detect all single-bit errors, all double-bit errors and some triple-bit errors. If one or more errors are detected, <u>ERROR</u> goes LOW. If two or more errors are detected, <u>MULT</u> ERROR goes LOW. Both error indicators are HIGH if there are no errors.

Also available on device outputs  $SC_{0-5}$  are the syndrome bits generated by the error detection step. The syndrome bits may be decoded to determine if a bit error was detected and, for single-bit errors, which of the data or check bits is in error. Table V gives the chart for decoding the syndrome bits generated by the 16-bit configuration (as an example, if the syndrome bits SX/S0/S1/S2/S4/S8 were 101001 this would be decoded to indicate that there is a single-bit error at data bit 9). If no error is detected the syndrome bits will all be zeroes.

In Detect Mode, the contents of the Data Input Latch are driven directly to the inputs of the Data Output Latch without correction.

#### **Correct Mode**

In this mode, the EDC functions the same as in Detect Mode except that the correction network is allowed to correct (complement) any single-bit error of the Data Input Latch before putting it. onto the inputs of the Data Output Latch. (see Figure 2.) If multiple errors are detected, the output of the correction network is unspecified. If the single-bit error is a check bit there is no automatic correction. If check bit correction is desired, this can be done by placing the device in Generate Mode to produce a correct check bit sequence for the data in the Data Input Latch.

#### Pass Thru Mode

In this mode, the unmodified contents of the Data Input Latch are placed on the inputs of the Data Output Latch and the contents of the Check Bit Input Latch are placed on outputs  $SC_{0-5}$ . ERROR and MULT ERROR are forced HIGH in this mode.

#### **Diagnostic Latch**

The Diagnostic Latch serves both for diagnostic uses and internal control uses. It is loaded from the DATA lines under the control of LE DIAG. Table VI shows the loading definitions for the DATA lines.

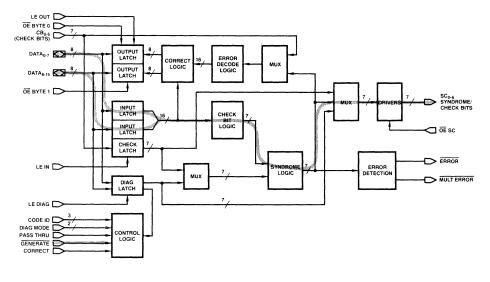

#### Diagnostic Generate Diagnostic Detect Diagnostic Correct

These are special diagnostic modes selected by DIAG  $\text{MODE}_{0-1}$  where either normal check bit inputs or outputs are substituted for by check bits loaded into the Diagnostic Latch. See Table III for details. Figures 3 and 4 illustrate the flow of data during the two diagnostic modes.

#### Internal Control Mode

This mode is selected by CODE ID<sub>0-2</sub> input 001 (ID<sub>2</sub>, ID<sub>1</sub>, ID<sub>0</sub>).

When in Internal Control Mode, the EDC takes the CODE  $\rm ID_{0-2}, DIAG\ MODE_{0-1},\ CORRECT$  and PASS THRU control signals from the internal Diagnostic Latch rather than from the external input lines.

Table VI gives the format for loading the Diagnostic Latch.

#### Figure 1. Check Bit Generation

#### Am2960

#### TABLE IV. 16-BIT MODIFIED HAMMING CODE - CHECK BIT ENCODE CHART.

| Generated<br>Check |            |   |   |   |   |   |   |   |   | ipati<br>Bits |   |    |    |    |    |    |    |

|--------------------|------------|---|---|---|---|---|---|---|---|---------------|---|----|----|----|----|----|----|

| Bits               | Parity     | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8             | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| CX                 | Even (XOR) |   | х | х | Х |   | х |   |   | X             | х |    | х  |    |    | х  |    |

| C0                 | Even (XOR) | X | х | х |   | X |   | Х |   | х             |   | х  |    | x  |    |    |    |

| C1                 | Odd (XNOR) | x |   |   | х | x |   |   | х |               | х | х  |    |    | х  |    | х  |

| C2                 | Odd (XNOR) | x | х |   |   |   | х | Х | х |               |   |    | х  | х  | Х  |    |    |

| C4                 | Even (XOR) |   |   | Х | Х | X | Х | Х | Х |               |   |    |    |    |    | х  | х  |

| C8                 | Even (XOR) |   |   |   |   |   |   |   |   | х             | х | х  | х  | x  | х  | х  | х  |

The check bit is generated as either an XOR or XNOR of the eight data bits noted by an "X" in the table.

1 1 1

м т Т м

т

М

|    |              | ſ  | ABLI           |             | SYND<br>TO B |             |             |       | DE     |       |   |

|----|--------------|----|----------------|-------------|--------------|-------------|-------------|-------|--------|-------|---|

| Sy | ndro<br>Bits | me | S8<br>S4<br>S2 | 0<br>0<br>0 | 1<br>0<br>0  | 0<br>1<br>0 | 1<br>1<br>0 | 0 0 1 | 1<br>0 | 0 1 1 | - |

| SX | S0           | S1 | UZ             | Ū           |              |             |             | 1     | '      | 1     |   |

| 0  | 0            | 0  |                | *           | C8           | C4          | Т           | C2    | Т      | т     |   |

| 0  | 0            | 1  |                | C1          | т            | Т           | 15          | т     | 13     | 7     |   |

| 0  | 1            | 0  |                | CO          | т            | т           | м           | Т     | 12     | 6     |   |

| 0  | 1            | 1  |                | Т           | 10           | 4           | Т           | 0     | т      | т     |   |

т

1 т т

т

11 5

м

М Т

14

М

т

#### TADLEN SYNDROME DECODE

#### TABLE VI. DIAGNOSTIC LATCH LOADING -16-BIT FORMAT.

| Data Bit | Internal Function      |  |  |  |  |  |  |

|----------|------------------------|--|--|--|--|--|--|

| 0        | Diagnostic Check Bit X |  |  |  |  |  |  |

| 1        | Diagnostic Check Bit 0 |  |  |  |  |  |  |

| 2        | Diagnostic Check Bit 1 |  |  |  |  |  |  |

| 3        | Diagnostic Check Bit 2 |  |  |  |  |  |  |

| 4        | Diagnostic Check Bit 4 |  |  |  |  |  |  |

| 5        | Diagnostic Check Bit 8 |  |  |  |  |  |  |

| 6, 7     | Don't Care             |  |  |  |  |  |  |

| 8        | CODE ID 0              |  |  |  |  |  |  |

| 9        | CODE ID 1              |  |  |  |  |  |  |

| 10       | CODE ID 2              |  |  |  |  |  |  |

| 11       | DIAG MODE 0            |  |  |  |  |  |  |

| 12       | DIAG MODE 1            |  |  |  |  |  |  |

| 13       | CORRECT                |  |  |  |  |  |  |

| 14       | PASS THRU              |  |  |  |  |  |  |

| 15       | Don't Care             |  |  |  |  |  |  |

\* - no errors detected

0

1

0 0

1

S

1 1 0 1

1 1

1

Number - the location of the single bit-in-error

сх т т

Т 9 3 т М т т М

т 8 2 т

М т

T - two errors detected

M - three or more errors detected

#### FUNCTIONAL DESCRIPTION -32-BIT DATA WORD CONFIGURATION

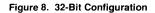

The 32-bit format consists of 32 data bits, 7 check bits and is referred to as 32/39 code (see Figure 7).

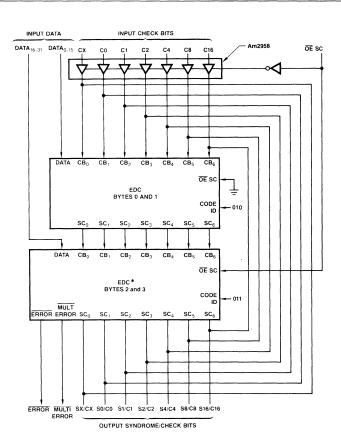

The 32-bit configuration is shown in Figure 8.

The upper EDC (Slice 0/1) handles the least significant bytes 0 and 1 - the external DATA lines 0 to 15 are connected to the same numbered inputs of the upper device. The lower EDC (Slice 2/3) handles the most significant bytes 2 and 3 - the external DATA lines for bits 16 to 31 are connected to inputs DATA<sub>0</sub> through DATA<sub>15</sub> respectively.

The valid syndrome and check bit outputs are those of Slice 2/3 as shown in the diagram. In Correct Mode these must be read into Slice 0/1 via the CB inputs and are selected by the MUX as inputs to the bit-in-error decoder (see block diagram), thus requiring external buffering and output enabling of the check bit lines as shown. The OE SC signal can be used to control enabling of check bit inputs - when syndrome outputs are enabled, the external check bit inputs will be disabled.

The valid ERROR and MULT ERROR outputs are those of the Slice 2/3. The ERROR and MULT ERROR outputs of Slice 0/1 are unspecified. All of the latch enables and control signals must be input to both of the devices.

#### **Generate Mode**

In this mode check bits will be generated that correspond to the contents of the Data Input Latch. The check bits generated are placed on the outputs SC<sub>0-6</sub> of Slice 2/3.

Check bits are generated according to a modified Hamming code. Details of the code for check bit generation are contained in Table X. Check bits are generated as either an XOR or XNOR of 16 of the 32 data bits as indicated in the table. The XOR function results in an even parity check bit, the XNOR in an odd parity check bit.

#### **Detect Mode**

In this mode the device examines the contents of the Data Input Latch against the Check Bit Input Latch, and will detect all single-bit errors, all double-bit errors and some triple-bit errors. If one or more errors are detected, ERROR goes LOW. If two or more errors are detected, MULT ERROR goes LOW. Both error indicators are HIGH if there are no errors. The valid ERROR and MULT ERROR signals are those of Slice 2/3 - those of Slice 0/1 are undefined.

Also available on Slice 2/3 outputs SC<sub>0-6</sub> are the syndrome bits generated by the error detection step. The syndrome bits may be decoded to determine if a bit error was detected and, for single-bit errors, which of the data or check bits is in error. Table VII gives the chart for decoding the syndrome bits generated for the 32-bit configuration (as an example, if the syndrome bits SX/S0/S1/S2/S4/S8/S16 were 0010011 this would be decoded to indicate that there is a single-bit error at data bit 25). If no error is detected the syndrome bits will be all zeroes.

In Detect Mode, the contents of the Data Input Latch are driven directly to the inputs of the Data Output Latch without corrections.

#### **Correct Mode**

In this mode, the EDC functions the same as in Detect Mode except that the correction network is allowed to correct (complement) any single-bit error of the Data Input Latch before putting it onto the inputs of the Data Output Latch. If multiple errors are detected, the output of the correction network is unspecified. If the single-bit error is a check bit there is no automatic correction - if desired this would be done by placing the device in Generate Mode to produce a correct check bit sequence for the data in the Data Input Latch.

For data correction, both Slices 0/1 and 2/3 require access to the syndrome bits on Slice 2/3's outputs SC0-6. Slice 2/3 has access to these syndrome bits through internal data paths, but for Slice 0/1 they must be read through the inputs CB<sub>0-6</sub>. The device connections for this are shown in Figure 8. When in Correct Mode the SC outputs must be enabled so that they are available for reading in through the CB inputs.

#### Pass Thru Mode

In this mode, the unmodified contents of the Data Input Latch are placed on the inputs of the Data Output Latch and the contents of the Check Bit Input Latch are placed on outputs SC<sub>0-6</sub> of Slice 2/3. ERROR and MULT ERROR are forced HIGH in this mode.

#### TABLE VII. SYNDROME DECODE TO BIT-IN-ERROR.

|    | Synd<br>Bi | rome<br>its | )   | S16<br>Ş8<br>S4 | 0<br>0<br>0 | 1<br>0<br>0 | 0<br>1<br>0 | 1<br>1<br>0 | 0<br>0<br>1 | 1<br>0<br>1 | 0<br>1<br>1 | 1 1 1 |

|----|------------|-------------|-----|-----------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------|

| SX | S0         | S1          | S2  | -               | -           |             |             |             |             | ·           |             |       |

| 0  | 0          | 0           | 0   |                 | ¥           | C16         | C8          | Т           | C4          | Т           | т           | 30    |

| 0  | 0          | 0           | 1   |                 | C2          | Т           | т           | 27          | Т           | 5           | м           | Т     |

| 0  | 0          | 1           | 0   |                 | C1          | Т           | Т           | 25          | Т           | 3           | 15          | Т     |

| 0  | 0          | 1           | 1   |                 | Т           | М           | 13          | т           | 23          | Т           | т           | м     |

| 0  | 1          | 0           | 0   |                 | CO          | Т           | Т           | 24          | Т           | 2           | М           | Т     |

| 0  | 1          | 0           | • 1 |                 | Т           | 1           | 12          | Т           | 22          | T           | Т           | м     |

| 0  | 1          | 1           | 0   |                 | т           | м           | 10          | Т           | 20          | Т           | Т           | м     |

| 0  | 1          | 1           | 1   |                 | 16          | Т           | Т           | М           | Т           | м           | м           | Т     |

| 1  | 0          | 0           | 0   |                 | сх          | Т           | Т           | м           | Т           | М           | 14          | Т     |

| 1  | 0          | 0           | 1   |                 | т           | м           | 11          | т           | 21          | Т           | Т           | м     |

| 1  | 0          | 1           | 0   |                 | Т           | м           | 9           | Т           | 19          | т           | Т           | 31    |

| 1  | 0          | 1           | 1   |                 | м           | Т           | т           | 29          | Т           | 7           | м           | т     |

| 1  | 1          | 0           | 0   |                 | т           | М           | 8           | Т           | 18          | т           | Т           | м     |

| 1, | 1          | 0           | 1   |                 | 17          | Т           | Т           | 28          | Т           | 6           | м           | Т     |

| 1  | 1          | 1           | 0   |                 | м           | Т           | Т           | 26          | т           | 4           | м           | Т     |

| 1  | 1          | 1           | 1   |                 | Т           | 0           | м           | Т           | м           | Т           | Т           | м     |

\* - no errors detected

Numbers - number of the single bit-in-error

T - two errors detected

M – three or more errors detected

Uses Modified Hamming Code 32/39 - 32 data bits – 7 check bits

- 39 bits in total

|   |        | CHECK BITS |        |        |    |    |    |    |    |    |     |

|---|--------|------------|--------|--------|----|----|----|----|----|----|-----|

|   | BYTE 3 | BYTE 2     | BYTE 1 | BYTE 0 | сх | CO | C1 | C2 | C4 | C8 | C16 |

| 3 | 1 24   | 23 16      | 15 8   | 7      | D  |    |    |    |    |    |     |

Figure 7. 32-Bit Data Format

MPR-732

#### Am2960

\*Check Bit Latch is Forced Transparent in this Code ID Combination for this Slice.

#### TABLE VIII. KEY AC CALCULATIONS FOR THE 32-BIT CONFIGURATION

| Propa   | 32-Bit<br>agation Delay   | Component Delay from Am2960<br>AC Specifications, Table C             |

|---------|---------------------------|-----------------------------------------------------------------------|

| From    | То                        |                                                                       |

| DATA    | Check Bits<br>Out         | (DATA to SC) + (CB to SC, CODE ID 011)                                |

| DATA In | Corrected<br>DATA Out     | (DATA to SC) + (CB to SC, CODE ID 011) +<br>(CB to DATA, CODE ID 010) |

| DATA    | Syndromes<br>Out          | (DATA to SC) + (CB to SC, CODE ID 011)                                |

| DATA    | ERROR for<br>32 Bits      | (DATA to SC) + (CB to ERROR,<br>CODE ID 011)                          |

| DATA    | MULT ERROR<br>for 32 Bits | (DATA to SC) + (CB to MULT ERROR,<br>CODE ID 011)                     |

|     | 32-      | BIT FORMAT.             |

|-----|----------|-------------------------|

| · [ | Data Bit | Internal Function       |

|     | 0        | Diagnostic Check Bit X  |

|     | . 1      | Diagnostic Check Bit 0  |

|     | .2       | Diagnostic Check Bit 1  |

|     | 3        | Diagnostic Check Bit 2  |

|     | 4        | Diagnostic Check Bit 4  |

|     | 5        | Diagnostic Check Bit 8  |

|     | 6        | Diagnostic Check Bit 16 |

|     | 7        | Don't Care              |

|     | 8        | Slice 0/1 - CODE ID 0   |

|     | 9        | Slice 0/1 - CODE ID 1   |

|     | 10       | Slice 0/1 - CODE ID 2   |

|     | 11       | Slice 0/1 - DIAG MODE 0 |

|     | 12       | Slice 0/1 - DIAG MODE 1 |

|     | 13       | Slice 0/1 - CORRECT     |

|     | 14       | Slice 0/1 - PASS THRU   |

|     | 15       | Don't Care              |

|     | 16-23    | Don't Care              |

|     | 24       | Slice 2/3 - CODE ID 0   |

|     | 25       | Slice 2/3 - CODE ID 1   |

|     | 26       | Slice 2/3 - CODE ID 2   |

|     | 27       | Slice 2/3 - DIAG MODE ( |

| ×.  | 28       | Slice 2/3 - DIAG MODE   |

| 5   | 29       | Slice 2/3 - CORRECT     |

| -   | 30       | Slice 2/3 - PASS THRU   |

| -   | 31       | Don't Care              |

# TABLE IX. DIAGNOSTIC LATCH LOADING -32-BIT FORMAT.

#### TABLE X. 32-BIT MODIFIED HAMMING CODE - CHECK BIT ENCODE CHART.

| Generated<br>Check |            | Participating Data Bits |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

|--------------------|------------|-------------------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| Bits               | Parity     | 0                       | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| СХ                 | Even (XOR) | X                       |   |   |   | X |   | Х | х | Х | х |    | х  |    |    | X  |    |

| CO                 | Even (XOR) | X                       | x | X |   | х |   | Х |   | Х |   | х  | ., | X  |    |    |    |

| C1                 | Odd (XNOR) | X                       |   |   | х | X |   |   | Х |   | х | х  |    |    | х  |    | х  |

| C2                 | Odd (XNOR) | х                       | х |   |   |   | х | х | х |   |   |    | х  | Х  | х  |    |    |

| C4                 | Even (XOR) |                         |   | X | х | X | х | Х | х | 1 |   |    |    |    |    | х  | х  |

| C8                 | Even (XOR) |                         |   |   |   |   |   |   |   | X | х | х  | х  | X  | х  | х  | X  |

| C16                | Even (XOR) | X                       | х | Х | х | X | Х | Х | х |   |   |    |    |    |    |    |    |

| Generated<br>Check |            | Participating Data Bits |    |    |    |       |    |    |    |    |    |    |    |    |    |    |    |

|--------------------|------------|-------------------------|----|----|----|-------|----|----|----|----|----|----|----|----|----|----|----|

| Bits               | Parity     | 16                      | 17 | 18 | 19 | 20    | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| СХ                 | Even (XOR) |                         | х  | х  | х  |       | х  |    |    |    |    | х  |    | X  | Х  |    | х  |

| C0                 | Even (XOR) | X                       | Х  | X  |    | х     |    | Х  |    | X  |    | х  |    | X  |    |    |    |

| C1                 | Odd (XNOR) | X                       |    |    | х  | X     |    |    | х  |    | Х  | х  |    |    | Х  |    | х  |

| C2                 | Odd (XNOR) | X                       | Х  |    |    |       | х  | х  | х  |    |    |    | х  | X  | х  |    |    |

| C4                 | Even (XOR) |                         |    | х  | Х  | • X * | х  | X  | Х  |    |    |    |    |    |    | х  | х  |

| C8                 | Even (XOR) |                         |    |    |    |       |    |    |    | X  | х  | х  | х  | x  | х  | х  | х  |

| C16                | Even (XOR) |                         |    |    |    |       |    |    |    | x  | х  | х  | х  | X  | х  | х  | х  |

The check bit is generated as either an XOR or XNOR of the sixteen data bits noted by an "X" in the table.

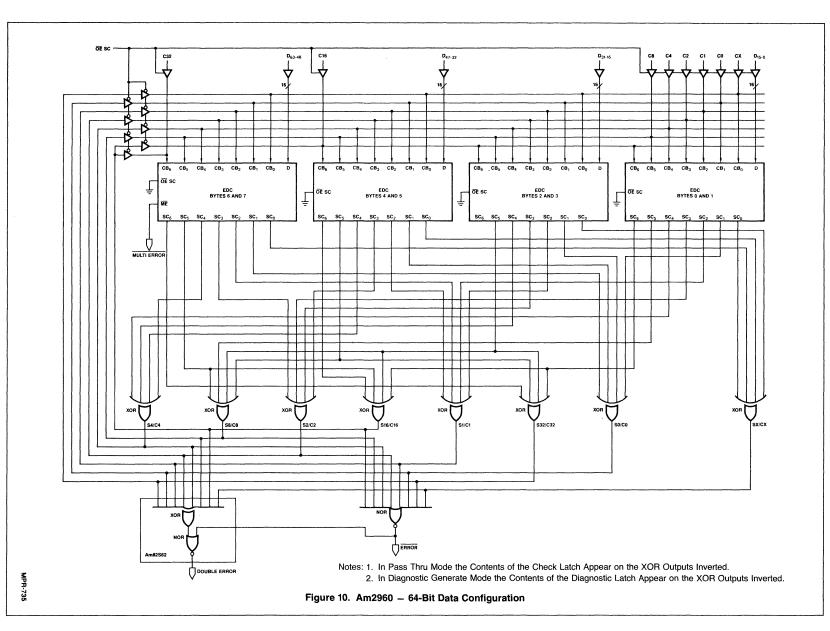

#### FUNCTIONAL DESCRIPTION --64-BIT DATA WORD CONFIGURATION

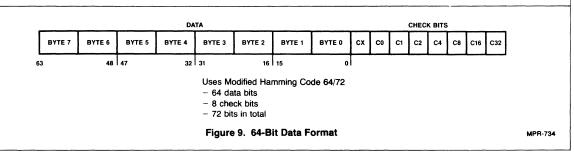

The 64-bit format consists of 64 data bits, 8 check bits and is referred to as 64/72 code (see Figure 9.).

The configuration to process 64-bit format is shown in Figure 6. In this configuration a portion of the syndrome generation and error detection is implemented externally of the EDCs in MSI. For error correction the syndrome bits generated must be read back into all four EDCs through the CB inputs. This necessitates the check bit buffering shown in the connection diagram of Figure 10. The  $\overline{OE}$  SC signal can control the check bit enabling – when syndrome bit outputs are enabled the external check bit lines will be disabled so that the syndrome bits may be read onto the CB inputs.

The error detection signals for the 64-bit configuration differ from the 16 and 32-bit configurations. The ERROR signal functions the same: it is LOW if one or more errors are detected, and HIGH if no errors are detected. The DOUBLE ERROR signal is HIGH if and only if a double-bit error is detected – it is LOW otherwise. All of the MULT ERROR outputs of the four devices are valid. MULT ERROR is LOW for all three ERROR cases and some DOUBLE ERROR combinations. (See TOME definition in Functional Equations section.) It is HIGH if either zero or one errors are detected.

This is a different meaning for MULT ERROR than in other configurations.

#### Generate Mode

In this mode check bits will be generated that correspond to the contents of the Data Input Latch. The check bits generated appear at the outputs of the XOR gates as indicated in Figure 10.

Check bits are generated according to a modified Hamming code. Details of the code for check bit generation are contained in Table XII. Check bits are generated as either an XOR or XNOR of 32 of the 64 bits as indicated in the table. The XOR function results in an even parity check bit, the XNOR in an odd parity check bit.

#### Detect Mode

In this mode the device examines the contents of the Data Input Latch against the Check Bit Input Latch, and will detect all single-bit errors, all double-bit errors and some triple-bit errors. If one or more errors are detected, ERROR goes LOW. If exactly two errors are detected, DUBLE ERROR goes HIGH. If three or more errors are detected, MULT ERROR goes LOW – the MULT ERROR output of any of the four EDCs may be used.

Available as XOR gate outputs are the generated syndrome bits (see Figure 10). The syndrome bits may be decoded to determine if a bit error was detected and, for single-bit errors, which of the data or check bits is in error. Table XIII gives the chart for encoding the syndrome bits generated for the 64-bit configuration (as an example, if the syndrome bits SX/S1/S2/S4/S8/ S16/S32 were 00100101 this would be decoded to indicate that there is a single-bit error at data bit 41). If no error is detected the syndrome bits will all be zeroes.

In Detect Mode the contents of the Data Input Latch are driven directly to the inputs of the Data Output Latch without corrections.

#### **Correct Mode**

In this mode, the EDC functions the same as in Detect Mode except that the correction network is allowed to correct (complement) any single-bit error of the Data Input Latch before putting it onto the inputs of the Data Output Latch. If multiple errors are detected, the output of the correction network is unspecified. If the single bit error is a check bit there is no automatic correction. Check bit correction can be done by placing the device in generate mode to produce a correct check bit sequence for the data in the Data Input Latch.

To perform the correction step, all four slices require access to the syndrome bits which are generated externally of the devices. This access is provided by reading the syndrome bits in through the CB inputs where they are selected as inputs to the bit-inerror decoder by the multiplexer (see block diagram). The device connections for this are shown in Figure 10. When in Correct Mode the SC outputs must be enabled so that the syndrome bits are available at the CB inputs.

#### Pass Thru Mode

In this mode, the unmodified contents of the Data Input Latch are placed on the inputs of the Data Output Latch, and the contents of the Check Bit Input Latch are passed through the external XOR network and appear inverted at the XOR gate outputs labeled CX to C32 (see Figure 10).

#### **Diagnostic Latch**

The Diagnostic Latch serves both for diagnostic uses and internal control uses. It is loaded from the DATA lines under the control of LE DIAG. Table XIV shows the loading definitions for the DATA lines.

#### Diagnostic Generate Diagnostic Detect Diagnostic Correct

These are special diagnostic modes selected by DIAG MODE\_{0-1} where either normal check bit inputs or outputs are substituted for by check bits from the Diagnostic Latch. See Table II for details.

#### Internal Control Mode

This mode is selected by CODE ID<sub>0-2</sub>, input 001 (ID<sub>2</sub>, ID<sub>1</sub>, ID<sub>0</sub>).

When in Internal Control Mode the EDC takes the CODE  $ID_{0-2}$ , DIAG MODE<sub>0-1</sub>, CORRECT and PASS THRU signals from the internal Diagnostic Latch rather than from the external control lines. Table XIV gives format for loading the Diagnostic Latch.

20

# TABLE XI. KEY AC CALCULATIONS FOR THE 64-BIT CONFIGURATION

|         | 64-Bit<br>Propagation Delay | Component Delays from Am2960<br>AC Specifications, Table C (plus MSI)            |

|---------|-----------------------------|----------------------------------------------------------------------------------|

| From    | То                          | Ao opecifications, rable o (plus hiol)                                           |

| DATA    | Check Bits Out              | (DATA to SC) + (XOR Delay)                                                       |

| DATA In | Corrected DATA Out          | (DATA to SC) + (XOR Delay) + (Buffer Delay) + (CB to DATA, CODE ID 1xx)          |

| DATA    | Syndromes                   | (DATA to SC) + (XOR Delay)                                                       |

| DATA    | ERROR for 64 Bits           | (DATA to SC) + (XOR Delay) + (NOR Delay)                                         |

| DATA    | MULT ERROR for 64 Bits      | (DATA to SC) + (XOR Delay) + (Buffer Delay) +<br>(CB to MULT ERROR, CODE ID 1xx) |

| DATA    | DOUBLE ERROR for 64 Bits    | (DATA to SC) + (XOR Delay) + (XOR/NOR Delay)                                     |

#### TABLE XII. 64-BIT MODIFIED HAMMING CODE - CHECK BIT ENCODE

| Generated<br>Check |                          | Participating Data Bits |        |        |        |        |        |        |        |        |   |    |    |    |        |        |        |

|--------------------|--------------------------|-------------------------|--------|--------|--------|--------|--------|--------|--------|--------|---|----|----|----|--------|--------|--------|

| Bits               | Parity                   | 0                       | 1      | 2      | 3      | 4      | 5      | 6      | 7      | 8      | 9 | 10 | 11 | 12 | 13     | 14     | 15     |

| CX<br>C0           | Even (XOR)<br>Even (XOR) | x                       | x<br>x | x<br>x | x      | x      | X      | x      |        | X<br>X | х | x  | х  | x  |        | x      |        |

| C1<br>C2           | Odd (XNOR)<br>Odd (XNOR) | x<br>x                  | x      |        | х      | x      | x      | x      | X<br>X |        | х | x  | x  | x  | x<br>x |        | х      |

| C4<br>C8           | Even (XOR)<br>Even (XOR) |                         |        | x      | X      | x      | х      | х      | х      | x      | х | ×  | x  | x  | x      | x<br>x | X<br>X |

| C16<br>C32         | Even (XOR)<br>Even (XOR) | x<br>x                  | x<br>x | x<br>x | X<br>X | X<br>X | x<br>x | X<br>X | X<br>X |        |   |    |    |    |        |        |        |

| Generated<br>Check |                          | Participating Data Bits |        |        |    |    |    |    |        |        |        |        |        |        |        |        |        |

|--------------------|--------------------------|-------------------------|--------|--------|----|----|----|----|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Bits               | Parity                   | 16                      | 17     | 18     | 19 | 20 | 21 | 22 | 23     | 24     | 25     | 26     | 27     | 28     | 29     | 30     | 31     |

| CX<br>C0           | Even (XOR)<br>Even (XOR) | x                       | x<br>x | x<br>x | x  | x  | х  | x  |        | X<br>X | х      | х      | х      | x      |        | х      |        |

| C1<br>C2           | Odd (XNOR)<br>Odd (XNOR) | x<br>x                  | x      |        | x  | x  | x  | x  | X<br>X |        | х      | x      | x      | x      | x<br>x |        | х      |

| C4<br>C8           | Even (XOR)<br>Even (XOR) |                         |        | x      | x  | x  | х  | х  | х      | x      | x      | x      | x      | x      | x      | x<br>x | X<br>X |

| C16<br>C32         | Even (XOR)<br>Even (XOR) |                         |        |        |    |    |    |    |        | X<br>X |

| Generated<br>Check |                          | Participating Data Bits |    |    |    |        |    |        |        |    |    |        |    |        |        |        |        |

|--------------------|--------------------------|-------------------------|----|----|----|--------|----|--------|--------|----|----|--------|----|--------|--------|--------|--------|

| Bits               | Parity                   | 32                      | 33 | 34 | 35 | 36     | 37 | 38     | 39     | 40 | 41 | 42     | 43 | 44     | 45     | 46     | 47     |

| CX<br>C0           | Even (XOR)<br>Even (XOR) | X<br>X                  | x  | x  |    | X<br>X |    | x<br>x | х      | x  |    | x<br>x |    | X<br>X | х      |        | х      |

| C1<br>C2           | Odd (XNOR)<br>Odd (XNOR) | x<br>x                  | x  |    | х  | ×      | x  | x      | X<br>X |    | х  | х      | x  | x      | X<br>X |        | х      |

| C4<br>C8           | Even (XOR)<br>Even (XOR) |                         |    | X  | х  | ×      | Х  | х      | х      | x  | x  | x      | x  | x      | x      | x<br>x | x<br>x |

| C16<br>C32         | Even (XOR)<br>Even (XOR) | ×                       | x  | X  | x  | ×      | х  | х      | х      | x  | x  | x      | x  | x      | x      | x      | x      |

| Generated<br>Check |                          |        |    |    |    |        | Pa | rtici  | patir  | ng D | ata I | Bits   |    |        |        |        |        |

|--------------------|--------------------------|--------|----|----|----|--------|----|--------|--------|------|-------|--------|----|--------|--------|--------|--------|

| Bits               | Parity                   | 48     | 49 | 50 | 51 | 52     | 53 | 54     | 55     | 56   | 57    | 58     | 59 | 60     | 61     | 62     | 63     |

| CX<br>C0           | Even (XOR)<br>Even (XOR) | X<br>X | x  | x  |    | x<br>x |    | x<br>x | х      | x    |       | x<br>x |    | X<br>X | x      |        | x      |

| C1<br>C2           | Odd (XNOR)<br>Odd (XNOR) | X<br>X | x  |    | х  | ×      | x  | x      | x<br>x |      | x     | x      | x  | x      | X<br>X |        | x      |

| C4<br>C8           | Even (XOR)<br>Even (XOR) |        |    | x  | X  | ×      | х  | х      | x      | x    | x     | x      | x  | x      | x      | x<br>x | X<br>X |

| C16<br>C32         | Even (XOR)<br>Even (XOR) | x      | x  | x  | x  | x      | x  | x      | x      | x    | х     | x      | x  | x      | x      | x      | x      |

The check bit is generated as either an XOR or XNOR of the 32 data bits noted by an "X" in the table.

|    | Synd<br>Bi | rome<br>its | •  | S32<br>S16<br>S8 | 0<br>0<br>0 | 1<br>0<br>0 | 0<br>1<br>0 | 1<br>1<br>0 | 0<br>0<br>1 | 1<br>0<br>1 | 0<br>1<br>1 | 1<br>1<br>1 | 0<br>0<br>0 | 1<br>0<br>0 | 0<br>1<br>0 | 1<br>1<br>0 | 0<br>0<br>1 | 1<br>0<br>1 | 0<br>1<br>1 | 1<br>1<br>1 |

|----|------------|-------------|----|------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| sx | S0         | S1          | S2 | S4               | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

| 0  | 0          | 0           | 0  |                  | *           | C32         | C16         | т           | C8          | т           | т           | М           | C4          | т           | т           | м           | т           | 46          | 62          | т           |

| 0  | 0          | 0           | 1  |                  | C2          | Т           | т           | М           | т           | 43          | 59          | т           | т           | 53          | 37          | Т           | м           | Т           | Т           | м           |

| 0  | 0          | 1           | 0  |                  | Cì          | т           | Т           | м           | т           | 41          | 57          | Т           | Т           | 51          | 35          | т           | 15          | т           | Т           | 31          |

| 0  | 0          | 1           | 1  |                  | Т           | м           | м           | Т           | 13          | Т           | Т           | 29          | 23          | Т           | Т           | 7           | Т           | м           | м           | Т           |

| 0  | 1          | 0           | 0  |                  | C0          | т           | Т           | М           | Т           | 40          | 56          | т           | т           | 50          | 34          | т           | м           | т           | Т           | м           |

| 0  | 1          | 0           | 1  |                  | Т           | 49          | 33          | Т           | 12          | Т           | Т           | 28          | 22          | Т           | Т           | 6           | Т           | м           | м           | Т           |

| 0  | 1          | 1           | 0  |                  | Т           | м           | м           | Т           | 10          | Т           | Т           | 26          | 20          | Т           | Т           | 4           | т           | м           | м           | т           |

| 0  | 1          | 1           | 1  |                  | 16          | т           | Т           | 0           | т           | м           | М           | т           | Т           | М           | м           | т           | м           | т           | Т           | м           |

| 1  | 0          | 0           | 0  |                  | СХ          | т           | Т           | М           | т           | м           | М           | Ť           | Т           | м           | м           | т           | 14          | Т           | Т           | 30          |

| 1  | 0          | 0           | 1  |                  | Т           | м           | м           | Т           | 11          | Т           | Т           | 27          | 21          | Т           | Т           | 5           | Т           | м           | м           | т           |

| 1  | 0          | 1           | 0  |                  | Т           | М           | м           | Т           | 9           | Т           | Т           | 25          | 19          | Т           | Т           | 3           | Т           | 47          | 63          | Т           |

| 1  | 0          | 1           | 1  |                  | М           | Т           | Т           | М           | Т           | 45          | 61          | т           | т           | 55          | 39          | т           | м           | т           | Т           | м           |

| 1  | 1          | 0           | 0  |                  | Т           | М           | м           | Т           | 8           | Т           | Т           | 24          | 18          | т           | Т           | 2           | т           | м           | м           | т           |

| 1  | 1          | 0           | 1  |                  | 17          | Т           | Т           | 1           | т           | 44          | 60          | Т           | Т           | 54          | 38          | Т           | м           | т           | Т           | м           |

| 1  | 1          | 1           | 0  |                  | М           | т           | т           | м           | т           | 42          | 5 <b>8</b>  | т           | Т           | 52          | 36          | т           | м           | т           | Т           | м           |

| 1  | 1          | 1           | 1  |                  | Т           | 48          | 32          | т           | м           | т           | т           | м           | м           | т           | Т           | м           | т           | м           | м           | т           |

#### TABLE XIII. SYNDROME DECODE TO BIT-IN-ERROR.

\* - no errors detected

T - two errors detected

Number – the number of the single bit-in-error M – more than two errors detected

TABLE XIV. DIAGNOSTIC LATCH LOADING - 64-BIT FORMAT.

| Data Bit | Internal Function       |

|----------|-------------------------|

| 0        | Diagnostic Check Bit X  |

| 1        | Diagnostic Check Bit 0  |

| 2        | Diagnostic Check Bit 1  |

| 3        | Diagnostic Check Bit 2  |

| 4        | Diagnostic Check Bit 4  |

| 5        | Diagnostic Check Bit 8  |

| 6, 7     | Don't Care              |

| 8        | Slice 0/1 - CODE ID 0   |

| 9        | Slice 0/1 - CODE ID 1   |

| 10       | Slice 0/1 - CODE ID 2   |

| 11       | Slice 0/1 - DIAG MODE 0 |

| 12       | Slice 0/1 - DIAG MODE 1 |

| 13       | Slice 0/1 - CORRECT     |

| 14       | Slice 0/1 - PASS THRU   |

| 15       | Don't Care              |

| 16-23    | Don't Care              |

| 24       | Slice 2/3 - CODE ID 0   |

| 25       | Slice 2/3 - CODE ID 1   |

| 26       | Slice 2/3 - CODE ID 2   |

| 27       | Slice 2/3 - DIAG MODE 0 |

| 28       | Slice 2/3 - DIAG MODE 1 |

| 29       | Slice 2/3 - CORRECT     |

| 30       | Slice 2/3 - PASS THRU   |

| Data Bit | Internal Function       |

|----------|-------------------------|

| 31       | Don't Care              |

| 32-37    | Don't Care              |

| 38       | Diagnostic Check Bit 16 |

| 39       | Don't Care              |

| 40       | Slice 4/5 - CODE ID 0   |

| 41       | Slice 4/5 - CODE ID 1   |

| 42       | Slice 4/5 - CODE ID 2   |

| 43       | Slice 4/5 - DIAG MODE 0 |

| 44       | Slice 4/5 - DIAG MODE 1 |

| 45       | Slice 4/5 - CORRECT     |

| 46       | Slice 4/5 - PASS THRU   |

| 47       | Don't Care              |

| 48-54    | Don't Care              |

| 55       | Diagnostic Check Bit 32 |

| 56       | Slice 6/7 - CODE ID 0   |

| 57       | Slice 6/7 - CODE ID 1   |

| 58       | Slice 6/7 - CODE ID 2   |

| 59       | Slice 6/7 - DIAG MODE 0 |

| 60       | Slice 6/7 - DIAG MODE 1 |

| 61       | Slice 6/7 - CORRECT     |

| 62       | Slice 6/7 - PASS THRU   |

| 63       | Don't Care              |

#### Am2960

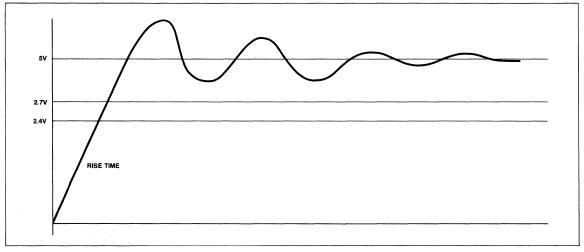

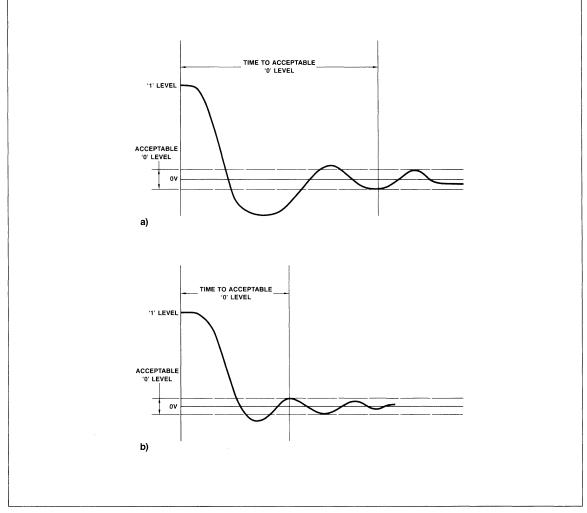

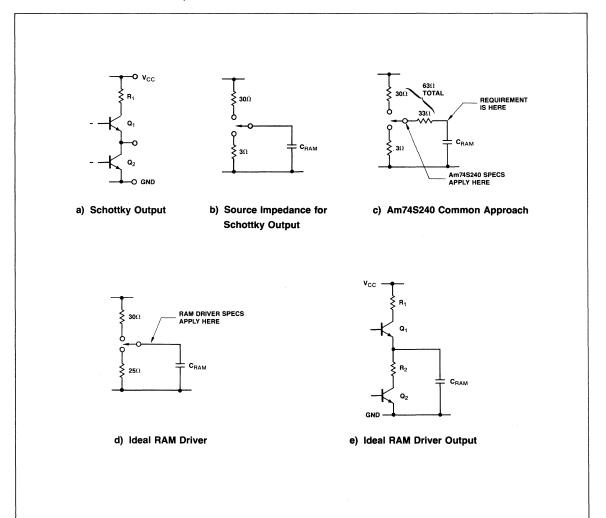

#### MAXIMUM RATINGS (above which the useful life may be impaired)