## ExpressROM<sup>™</sup>Memory

1989 Data Book

Advanced Micro Devices

**Advanced Micro Devices**

## ExpressROM<sup>™</sup> Memory

## 1989 Databook

#### © 1989 Advanced Micro Devices

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warranties of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry embodied in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088 (408) 732–2400 TWX: 910–339–9280 TELEX: 34–6306

ExpressROM is a trademark of Advanced Micro Devices, Inc.

For over ten years Advanced Micro Devices has been an industry leader in EPROM technology. We were the first to introduce the 512K EPROM and the 1 Megabit EPROM, we offer the most complete selection of high speed (<100ns) CMOS EPROMs, and we are the first company to convert our entire commercial product line to advanced CMOS technology. Now, in order to help our customers get more bytes-for-the-buck, AMD has created a new concept — ExpressROM memories. These waferprogrammed EPROMs offer users a low cost alternative for EPROMs without the long time-to-market associated with ROMs.

If you're looking for EPROM cost savings and your codes aren't changing, consider ExpressROM devices, the ROMs without the wait.

Walid Magribi Product Line Director Non-Volatile Memory Division

ih Joste

Rich Forte Division Vice President Non-Volatile Memory Division

## TABLE OF CONTENTS

| Introduction to ExpressROM Memory | 1-1 |

|-----------------------------------|-----|

| Am27X64                           | 2-1 |

| Am27X128                          | 3-1 |

| Am27X256                          | 4-1 |

| Am27X512                          | 5-1 |

| Am27X010                          | 6-1 |

| Am27X1024                         | 7-1 |

## Introduction to ExpressROM Memory

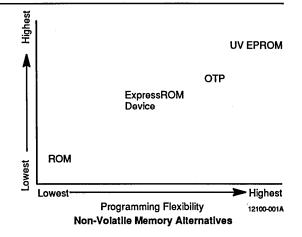

ExpressROM memories are an exciting new product family created by Advanced Micro Devices to offer the system manufacturer a cost savings over standard EPROMs while eliminating many of the disadvantages associated with traditional ROMs. These new memory products provide a lower cost alternative for volume production with stable codes.

ExpressROM devices are delivered pre-programmed in a low cost plastic package and are 100% compatible with the EPROMs they replace. They address two critical needs of system manufacturers which are vital in today's marketplace: reduced cost and time-to-market. Typically ExpressROM devices become cost-effective at volumes of 5000 units and offer leadtimes as short as 3-4 weeks.

ExpressROM wafers are manufactured with the same process as standard AMD EPROMs with one important exception. Since the devices will be pre-programmed with a single code they do not need the transparent topside passivation used on OTP (One Time Programmable) EPROMs. Instead the wafers are coated with a cost-effective nitride topside. This passivation is acknowledged industry-wide as the highest quality protection for plastic encapsulated CMOS devices not requiring UV erasure. Since a standard EPROM die is used, you are assured that the ExpressROM family is identical in architecture, density, and pinout to both AMD's current and future generations of high performance CMOS EPROMs.

Prior to receipt of a custom code ExpressROM wafers are inventoried untested and unprogrammed. Upon verification of your code the wafers are sorted, packaged and tested. Since your ExpressROM devices are programmed at wafer sort, every device can be rigorously tested with your code under both AC and DC operating conditions prior to shipment. Also, because ExpressROM memories are shipped board-ready with factory guaranteed quality your ship-to-stock or Just-In-Time programs can be easily implemented. At Advanced Micro Devices, we ship them the way you want them — ready for your system. And, there are none of the delays, costs or risks normally associated with custom ROM masks and wafer production.

|                                | UV EPROM                 | OTP                      | ExpressROM<br>Device          | ROM                                |

|--------------------------------|--------------------------|--------------------------|-------------------------------|------------------------------------|

| Leadtime                       | Manufactures<br>Leadtime | Manufactures<br>Leadtime | 4 Weeks                       | 8 - 12 Weeks                       |

| Set-up Charge                  | No                       | No                       | No                            | Yes                                |

| Minimum Quantity               | 0                        | 0                        | 5K to 10K                     | 25K                                |

| Fully Tested<br>Custom Pattern | No                       | No                       | Yes                           | Yes                                |

| User Programming<br>Required   | Yes                      | Yes                      | No                            | No                                 |

| Auto Insertion                 | No                       | Yes                      | Yes                           | Yes                                |

| Flexibility                    | Total                    | Can Not<br>Reprogram     | Fixed 4 Weeks<br>Prior To Use | Fixed 8 - 12 Weeks<br>Prior to Use |

#### **Non-Volatile Memory Alternatives**

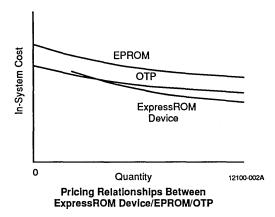

Plastic packaging inherently provides a cost savings over standard EPROMs packaged in expensive windowed ceramic DIPs. Due to simplified test requirements, ExpressROM devices can even cost less than unprogrammed OTP EPROMs. However component price is only a small part of your true in-system cost. ExpressROM devices allow you to eliminate or reduce costs in several other areas: programming, testing and production. Since ExpressROM memories are delivered with your code, you will reap savings by eliminating programming costs and associated yield losses. Incoming inspection may often be eliminated since your ExpressROM devices have been thoroughly tested and are guaranteed to operate to full specifications with your code! Additional in-house cost savings can be attained by using automatic insertion equipment in lieu of manual placement into sockets.

ExpressROM devices were designed to provide a low cost alternative for EPROM users without the liabilities of other non-volatile memory alternatives. Although ROMs have a lower component cost, they are economically feasible only at high volume and have the risks of long leadtimes and limited manufacturing flexibility. While OTP EPROMs offer the systems manufacturer the ability to respond to varying codes during production, they force the user to incur additional and sometimes hidden costs.

Our mission at AMD is to deliver you the service and products you demand to build the cost competitive systems that are needed to win in your markets. The ExpressROM memory provides this opportunity. As one of the world's five largest IC manufacturers and the first to market with a 1 megabit EPROM, we appreciate the value of efficient manufacturing. Compressing time-tomarket cycles, improving yields and providing high levels of quality are invaluable strategies for today's manufacturer. At Advanced Micro Devices we are proud to offer another tool to give our customers this strategic advantage, the ExpressROM memory: the ROM without the wait!

#### **ORDERING ExpressROM DEVICES**

The following are guidelines for ordering an ExpressROM device. For more information, contact your local AMD sales representative.

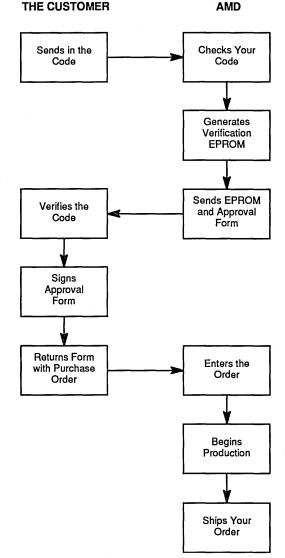

#### 1) SEND IN THE CODE

Please send your sales representative two EPROMs containing identical copies of the code. To minimize the verification turnaround process, use EPROMs with JEDEC-approved pinouts identical in architecture and density as the ExpressROM device being ordered.

#### 2) AMD CHECKS THE CODE

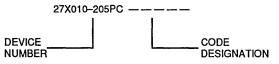

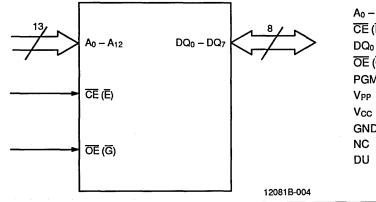

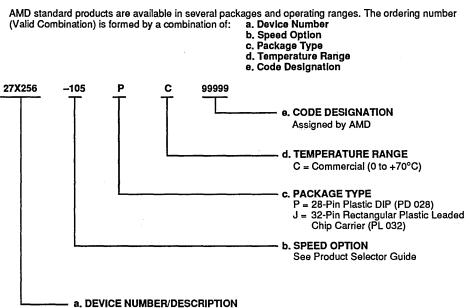

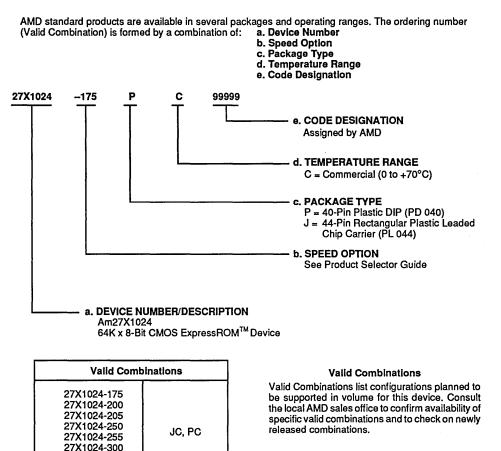

We check that both EPROMs contain the same code to make certain there was not a mix-up in shipping your codes to the factory as well as ensuring that the integrity of your code has been preserved. After confirming this, a unique 5-digit code designation is assigned. The ordering part number is formed by adding the 5-digit code designation as a suffix to the ExpressROM device number. See below:

#### 3) AMD GENERATES A VERIFICATION EPROM After the check is completed, we duplicate the code and return it to you for verification.

#### 4) CONFIRM THE CODE

The verification EPROM and the code approval form should be back in your hands for final approval before production within 3 days. Sign the approval form and return it to AMD.

#### 5) THE ORDER IS ENTERED

Upon receipt of the authorized code approval form and a purchase order, the order is entered and production is initiated. Delivery is scheduled per the negotiated leadtime.

#### **TERMS AND CONDITIONS**

You should be aware of the following guidelines when order ExpressROM devices. Please note that the exact terms and conditions can be found on the code approval form available from your local sales representative.

- 1) AMD will maintain customer code confidentiality.

- 2) AMD will absorb all initial set-up cost.

- 3) All orders are subject to minimum quantities.

- AMD requires 8 weeks notification for code changes. The customer is liable for all work-in-process.

- No schedule chages may be made within 30 days of current schedule date. Otherwise any line item may be rescheduled ±30 days from the original schedule date.

- 6) The customer will accept shipments of line items  $\pm 5$ .

#### Final

## Am27X64

## 8,192 x 8-Bit CMOS ExpressROM<sup>™</sup> Device

## DISTINCTIVE CHARACTERISTICS

#### OTP EPROM alternative:

- Factory programmed

- Fully tested and guaranteed

- Low cost

- Mask ROM alternative

- Shorter leadtime

- Lower volume per code

- Compatible with JEDEC-approved EPROM pinout

#### **GENERAL DESCRIPTION**

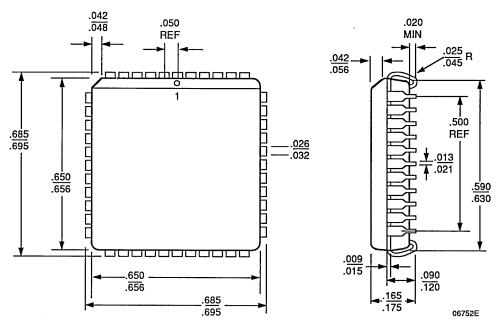

The Am27X64 is a wafer-level programmed EPROM with a standard topside for plastic packaging. It is organized as 8,192 by 8 bits and is available in plastic DIP as well as plastic leaded chip carrier (PLCC) packages. ExpressROM<sup>™</sup> devices provide a board-ready memory solution for medium to high volume codes with short leadtimes. This offers manufacturers a cost-effective and flexible alternative to OTP EPROMs and mask programmed ROMs. High performance CMOS technology

– Fast access time — 100 ns

- Low power dissipation

100 μA maximum standby current

- Available in plastic DIP and plastic leaded chip carrier

Access times as fast as 100 ns allow operation with high-performance microprocessors with reduced WAIT states. The Am27X64 offers separate Output Enable  $(\overline{OE})$  and Chip Enable  $(\overline{CE})$  controls, thus eliminating bus contention in a multiple bus microprocessor system.

AMD's CMOS process technology provides high speed, low power, and high noise immunity. Typical power consumption is only 100 mW in active mode, and 250  $\mu$ W in standby mode.

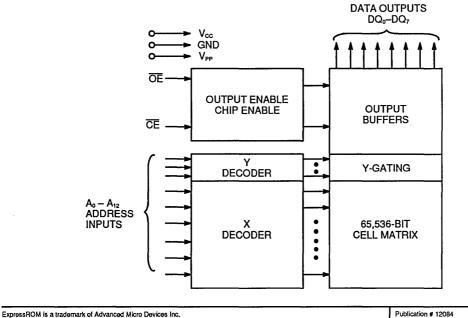

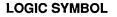

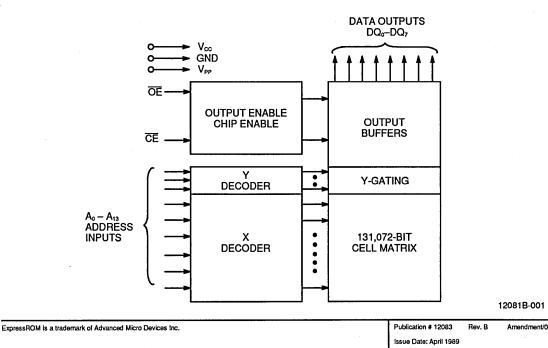

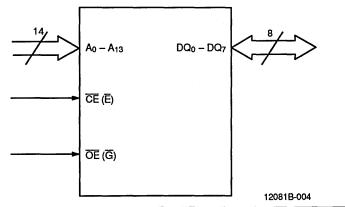

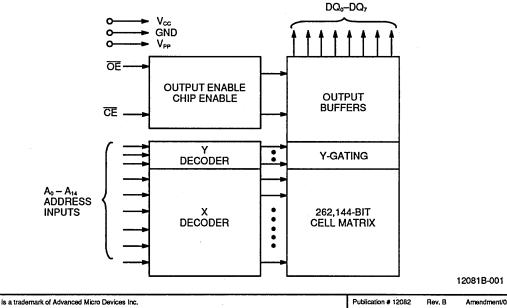

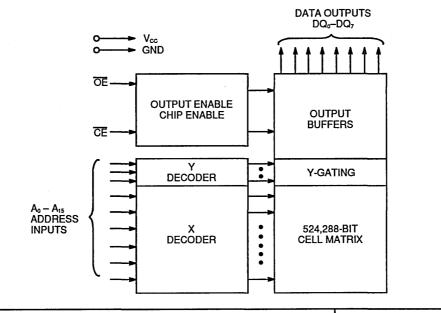

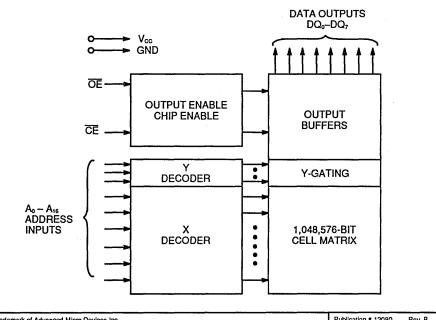

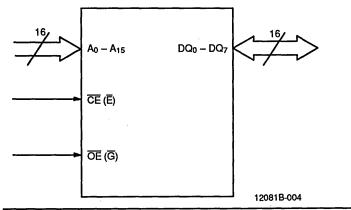

#### **BLOCK DIAGRAM**

Advanced Micro Devices

| Family Part No.                        | Am27X64 |      |     |      |      |      |

|----------------------------------------|---------|------|-----|------|------|------|

| Ordering part No:<br>±5% VCC Tolerance | -105    | -125 | 155 | -205 | -255 | 305  |

| ±10% VCC Tolerance                     | —       | -120 | 150 | -200 | 250  | -300 |

| Max Access Time (ns)                   | 100     | 120  | 150 | 200  | 250  | 300  |

| CE (E) Access (ns)                     | 100     | 120  | 150 | 200  | 250  | 300  |

| OE (G) Access (ns)                     | 40      | 50   | 65  | 75   | 100  | 120  |

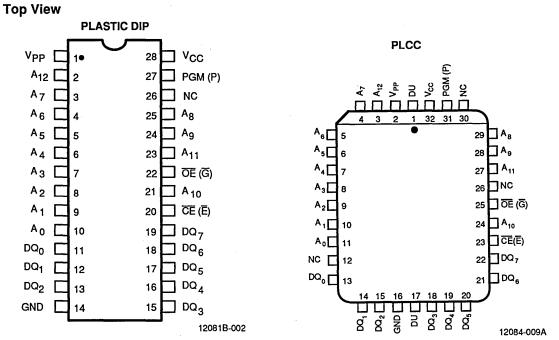

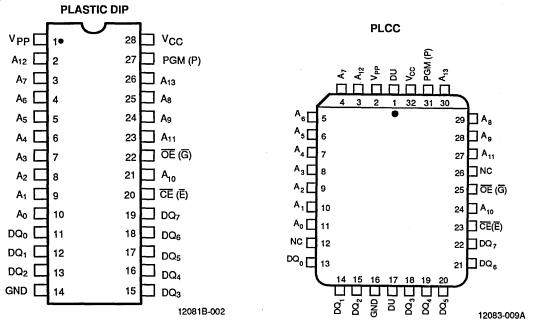

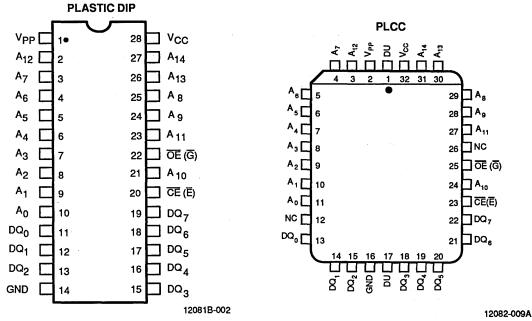

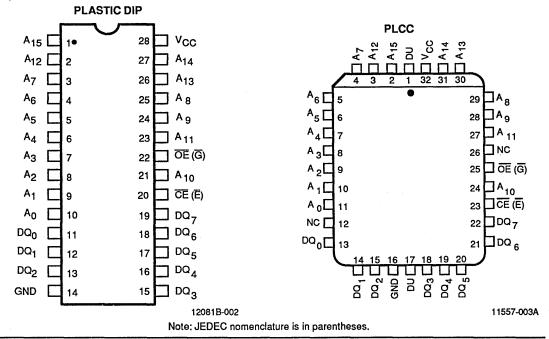

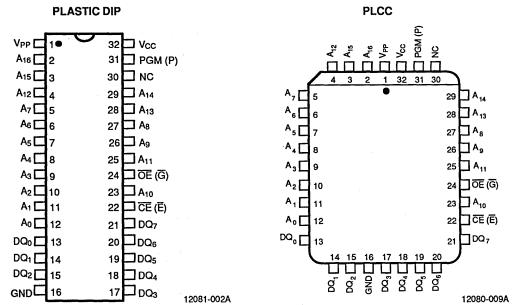

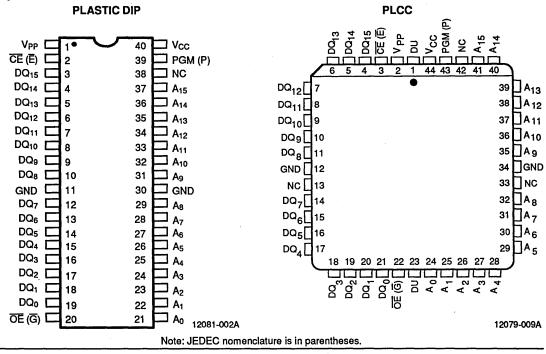

### **CONNECTION DIAGRAMS**

Note: JEDEC nomenclature is in parentheses.

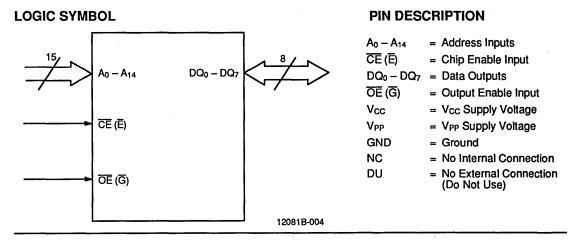

#### **PIN DESCRIPTION**

| A0 - A12  | = Address Inputs                                            |

|-----------|-------------------------------------------------------------|

| CE (E)    | <ul> <li>Chip Enable Input</li> </ul>                       |

| DQ0 – DQ7 | = Data Outputs                                              |

| OE (G)    | <ul> <li>Output Enable Input</li> </ul>                     |

| PGM (P)   | = Enable Input                                              |

| Vpp       | <ul> <li>VPP Supply Voltage</li> </ul>                      |

| Vcc       | = V <sub>CC</sub> Supply Voltage                            |

| GND       | = Ground                                                    |

| NC        | = No Internal Connection                                    |

| DU        | <ul> <li>No External Connection<br/>(Do Not Use)</li> </ul> |

|           |                                                             |

Am27X64

# ORDERING INFORMATION Standard Products

# FUNCTIONAL DESCRIPTION Read Mode

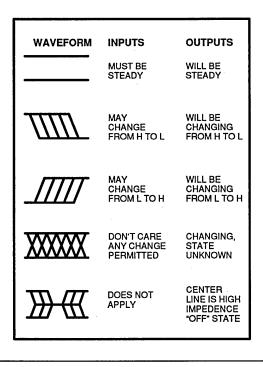

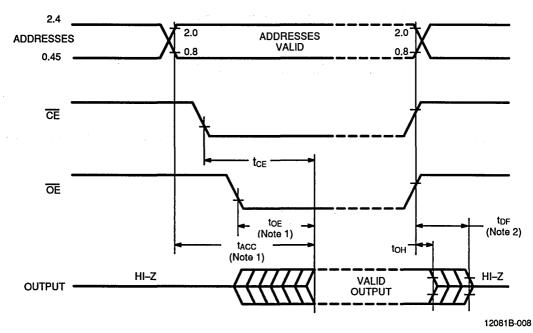

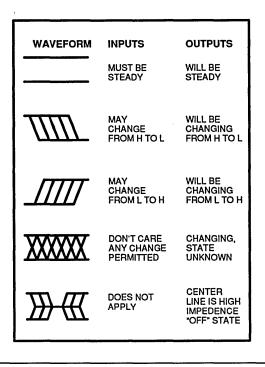

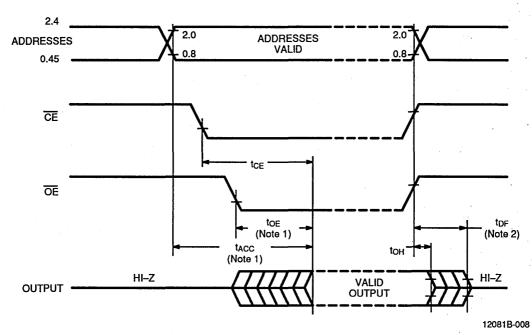

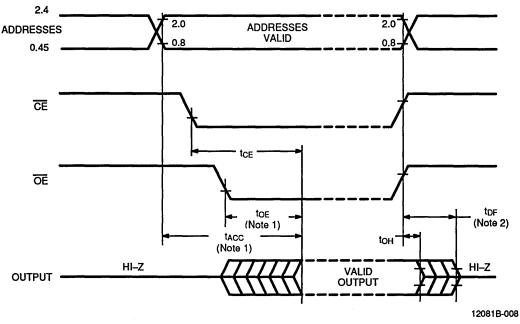

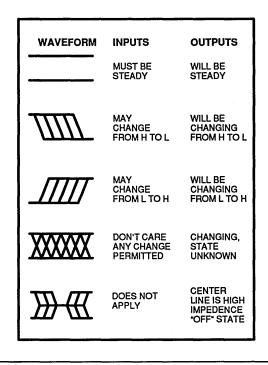

The Am27X64 has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip Enable ( $\overline{CE}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{OE}$ ) is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that addresses are stable, address access time (t<sub>ACC</sub>) is equal to the delay from  $\overline{CE}$  to output (t<sub>CE</sub>). Data is available at the outputs to<sub>E</sub> after the falling edge of  $\overline{OE}$ , assuming that  $\overline{CE}$  has been LOW and addresses have been stable for at least t<sub>ACC</sub> – t<sub>OE</sub>.

#### **Standby Mode**

The Am27X64 has a CMOS standby mode which reduces the maximum V<sub>CC</sub> current to 100  $\mu$ A. It is placed in CMOS-standby when  $\overline{CE}$  is at V<sub>CC</sub>  $\pm$  0.3 V. The Am27X64 also has a TTL-standby mode which reduces the maximum V<sub>CC</sub> current to 1.0 mA. It is placed in TTL-standby when  $\overline{CE}$  is at V<sub>IH</sub>. When in standby mode, the outputs are in a high-impedance state, independent of the  $\overline{OE}$  input.

## **Output OR-Tieing**

To accommodate multiple memory connections, a twoline control function is provided to allow for:

- 1. Low memory power dissipation, and

- 2. Assurance that output bus contention will not occur.

It is recommended that  $\overline{CE}$  be decoded and used as the primary device-selecting function, while  $\overline{OE}$  be made a common connection to all devices in the array and connected to the READ line from the system control bus. This assures that all deselected memory devices are in their low-power standby mode and that the output pins

are only active when data is desired from a particular memory device.

### **System Applications**

During the switch between active and standby conditions, transient current peaks are produced on the rising and falling edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitance loading of the device. At a minimum, a 0.1  $\mu$ F ceramic capacitor (high frequency, low inherent inductance) should be used on each device between V<sub>CC</sub> and GND to minimize transient effects. In addition, to overcome the voltage drop caused by the inductive effects of the printed circuit board traces on ExpressROM<sup>TM</sup> device arrays, a 4.7- $\mu$ F bulk electrolytic capacitor should be used between V<sub>CC</sub> and GND for each eight devices. The location of the capacitor should be array.

| Mode Select Table |                    |     |     |     |         |

|-------------------|--------------------|-----|-----|-----|---------|

| Pins<br>Mode      | CE                 | ŌĒ  | PGM | Vpp | Outputs |

| Read              | VIL                | VIL | х   | Vcc | Dout    |

| Output<br>Disable | VIL                | VIH | x   | Vcc | High Z  |

| Standby<br>(TTL)  | ViH                | х   | x   | Vcc | High Z  |

| Standby<br>(CMOS) | $V_{CC} \pm 0.3 V$ | х   | х   | Vcc | High Z  |

Note: X can be either VIL or VIH

## ABSOLUTE MAXIMUM RATINGS

| Storage Temperature                                 | -65 to 125°C                   |

|-----------------------------------------------------|--------------------------------|

| Ambient Temperature<br>with Power Applied           | –55 to +125°C                  |

| Voltage with Respect to Ground:                     |                                |

| All pins except V <sub>CC</sub> and V <sub>PP</sub> | -0.6 to V <sub>CC</sub> +0.5 V |

| V <sub>CC</sub> and V <sub>PP</sub>                 | –0.6 to 7.0 V                  |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure of the device to absolute maximum rating conditions for extended periods may affect device reliability.

#### Note:

Minimum DC voltage on input or output is -0.5 V. During transitions, the inputs may undershoot GND to -2.0 V for periods of up to 20 ns. Maximum DC voltage on input and output is V<sub>CC</sub>+0.5 V which may overshoot to V<sub>CC</sub>+2.0 V for periods up to 20 ns.

### **OPERATING RANGES**

| Commercial (C) Devices<br>Case Temperature (T)   | 0 to +70°C       |

|--------------------------------------------------|------------------|

| Supply Read Voltages:                            | Y                |

| Vcc /Vpp for Am27X64–XX5                         | +4.75 to +5.25 V |

| V <sub>CC</sub> /V <sub>PP</sub> for Am27X64–XX0 | +4.50 to +5.50 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over operating range unless otherwise specified (Notes 3, 4, 6 and 8)

| -                   |                                         |                                                                                   |                       |                       |      |

|---------------------|-----------------------------------------|-----------------------------------------------------------------------------------|-----------------------|-----------------------|------|

| Parameter<br>Symbol | Parameter<br>Description                | Test Conditions                                                                   | Min.                  | Max.                  | Unit |

| Vон                 | Output HIGH Voltage                     | I <sub>OH</sub> = - 400 μA                                                        | 2.4                   |                       | v    |

| Vol                 | Output LOW Voltage                      | l <sub>OL</sub> = 2.1 mA                                                          |                       | 0.45                  | v    |

| VIH                 | Input HIGH Voltage                      |                                                                                   | 2.0                   | Vcc + 0.5             | v    |

| ViL                 | Input LOW Voltage                       |                                                                                   | - 0.3                 | +0.8                  | v    |

| lu                  | Input Load Current                      | $V_{IN} = 0 V to V_{CC}$                                                          |                       | 1.0                   | μA   |

| llo                 | Output Leakage Current                  | V <sub>OUT</sub> = 0 V to V <sub>CCPP</sub>                                       |                       | 10                    | μΑ   |

| lcc1                | V <sub>CC</sub> Active Current (Note 4) | CE = V <sub>IL</sub> ,<br>f = 5 MHz,<br>l <sub>OUT</sub> = 0 mA<br>(Open Outputs) |                       | 30                    | mA   |

| Icc2                | Vcc Standby Current                     | <del>CE</del> = V <sub>IH</sub>                                                   |                       | 1                     | mA   |

| lpp                 | Vcc Supply Current (Note 7)             | $\overline{CE} = \overline{OE} = V_{IL}, V_{PP} = V_{CC}$                         |                       | 100                   | μA   |

| CMOS Inpu           | uts                                     |                                                                                   |                       |                       |      |

| Parameter<br>Symbol | Parameter<br>Description                | Test Conditions                                                                   | Min.                  | Max.                  | Unit |

| Voh                 | Output HIGH Voltage                     | I <sub>OH</sub> = – 400 μA                                                        | 2.4                   |                       | V    |

| Vol                 | Output LOW Voltage                      | l <sub>OL</sub> = 2.1 mA                                                          |                       | 0.45                  | v    |

| VIH                 | Input HIGH Voltage                      |                                                                                   | V <sub>CC</sub> – 0.3 | V <sub>cc</sub> + 0.3 | v    |

| VIL                 | Input LOW Voltage                       |                                                                                   | - 0.3                 | +0.8                  | v    |

| lLt                 | Input Load Current                      | V <sub>IN</sub> = 0 V to V <sub>CC</sub>                                          |                       | 1.0                   | μΑ   |

| ILO                 | Output Leakage Current                  | V <sub>OUT</sub> = 0 V to V <sub>CC</sub>                                         |                       | 10                    | μΑ   |

| Icc1                | V <sub>CC</sub> Active Current (Note 4) | CE = V <sub>IL,</sub><br>f = 5 MHz,<br>l <sub>OUT</sub> = 0 mA<br>(Open Outputs)  |                       | 30                    | mA   |

| Icc2                | Vcc Standby Current                     | $\overline{CE} = V_{CC} \pm 0.3$                                                  |                       | 100                   | μA   |

| <br>Ірр             | Vcc Supply Current (Note 7)             | $\overline{CE} = \overline{OE} = V_{IL}, V_{PP} = V_{CC}$                         |                       | 100                   | μA   |

## CAPACITANCE (Notes 1, 2 and 5)

| Parameter<br>Symbol | Parameter<br>Description | Test Conditions        | Тур. | Max. | Unit |

|---------------------|--------------------------|------------------------|------|------|------|

| C <sub>IN1</sub>    | Input Capacitance        | V <sub>IN</sub> = 0 V  | 8    | 12   | pF   |

| C <sub>IN2</sub>    | OE Input Capacitance     | V <sub>IN</sub> = 0 V  | 12   | 20   | pF   |

| CIN3                | CE Input Capacitance     | V <sub>IN</sub> = 0 V  | 9    | 12   | pF   |

| Солт                | Output Capacitance       | V <sub>OUT</sub> = 0 V | 8    | 12   | pF   |

Notes:

- 1. Typical values are for nominal supply voltages.

- 2. This parameter is only sampled and not 100% tested.

- 3. Caution: The Am27X64 must not be removed from, or inserted into, a socket or board when VPP or VCC is applied.

- 4. I<sub>CC1</sub> is tested with  $\overline{OE} = V_{IH}$  to simulate open outputs.

- 5. T<sub>A</sub> = 25°C, f = 1 MHz.

- Minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for periods less than 20 ns. Maximum DC voltage on output pins is V<sub>CC</sub> + 0.5 V which may overshoot to V<sub>CC</sub> + 2.0 V for periods less than 20 ns.

- 7. Maximum active power usage is the sum of Icc and Ipp.

- 8. V<sub>cc</sub> must be applied simultaneously or before V<sub>PP</sub>, and removed simultaneously or after V<sub>PP</sub>.

## SWITCHING CHARACTERISTICS over operating ranges unless otherwise specified (Notes 1, 3 and 4)

| Parame<br>JEDEC    | ter Symbol<br>Standard | Parameter<br>Description                                   | Test<br>Conditions                       |      | -105 | -120<br>-125 |     |     |     | 300<br>305 | Unit |

|--------------------|------------------------|------------------------------------------------------------|------------------------------------------|------|------|--------------|-----|-----|-----|------------|------|

| tavov              | tacc                   | Address to                                                 | $\overline{CE} = \overline{OE} = V_{IL}$ | Min. | 100  | 100          | 150 | 000 | 050 | 200        | ns   |

|                    |                        | Output Delay                                               | <u></u>                                  | Max. | 100  | 120          | 150 | 200 | 250 | 300        | ns   |

| t <sub>el</sub> qv | tce                    | Chip Enable to                                             | $\overline{OE} = V_{IL}$                 | Min. |      |              |     |     |     |            | ns   |

|                    |                        | Output Delay                                               |                                          | Max. | 100  | 120          | 150 | 200 | 250 | 300        | ns   |

| tglav              | toe                    | Output Enable to                                           | $\overline{CE} = V_{IL}$                 | Min. |      |              |     |     |     |            | ns   |

|                    |                        | Output Delay                                               |                                          | Max. | 40   | 50           | 65  | 75  | 100 | 120        | ns   |

| t <sub>EHQZ</sub>  | tDF                    | Output Enable                                              |                                          | Min. |      |              |     |     |     |            | ns   |

| tgнaz              |                        | HIGH to Output<br>Float (Note 1)                           |                                          | Max. | 30   | 35           | 50  | 55  | 60  | 75         | ns   |

| taxax              | toн                    | Output Hold                                                |                                          | Min. | 0    | 0            | 0   | 0   | 0   | 0          | ns   |

|                    |                        | from Addresses,<br>CE or OE<br>whichever<br>occurred first |                                          | Max. |      |              |     |     |     |            | ns   |

#### Notes:

- 1. V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub>, and removed simultaneously or after V<sub>PP</sub>.

- 2. This parameter is only sampled and not 100% tested.

- 3. Caution: The Am27X64 must not be removed from, or inserted into, a socket or board when Vpp or Vcc is applied.

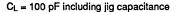

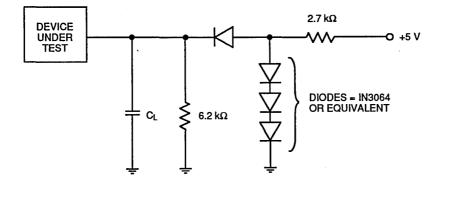

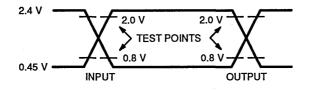

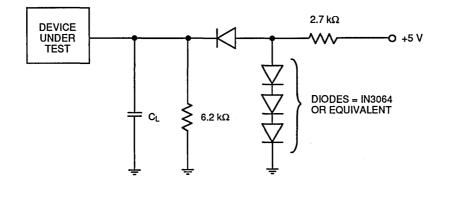

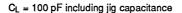

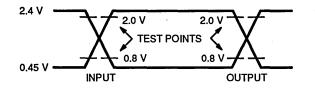

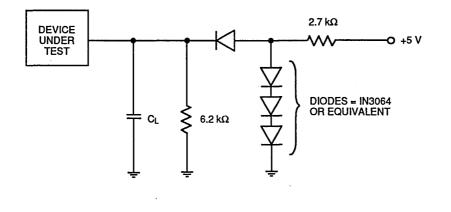

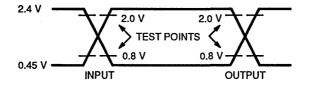

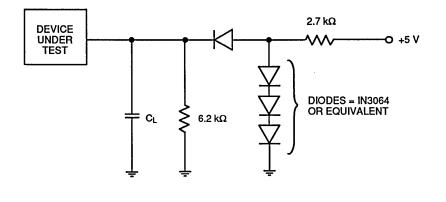

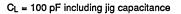

- 4. Output Load: 1 TTL gate and CL = 100 pF, Input Rise and Fall Times: 20 ns, Input Pulse Levels: 0.45 to 2.4 V,

Timing Measurement Reference Level - Inputs: 0.8 V and 2 V

Outputs: 0.8 V and 2 V

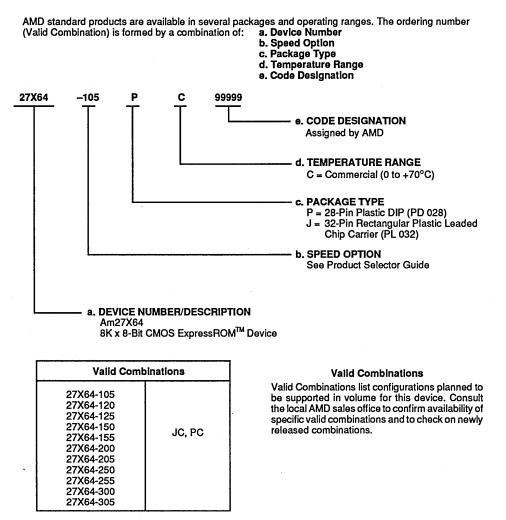

#### SWITCHING TEST CIRCUIT

12081B-005

#### SWITCHING TEST WAVEFORM

12081B-006

AC Testing: Inputs are driven at 2.4 V for a logic "1" and 0.45 V for a logic "0". Input pulse rise and fall times are ≤ 20ns.

#### **KEY TO SWITCHING WAVEFORMS**

KS000010

#### SWITCHING WAVEFORMS

Note:

1.  $\overline{OE}$  may be delayed up to t<sub>ACC</sub>-t<sub>OE</sub> after the falling edge of  $\overline{CE}$  without impact on t<sub>ACC</sub>. 2. t<sub>DF</sub> is specified from  $\overline{OE}$  or  $\overline{CE}$ , whichever occurs first.

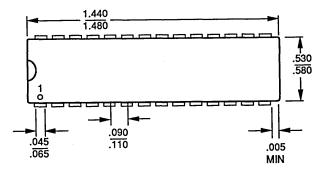

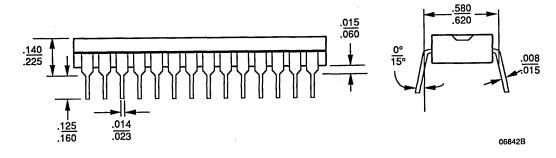

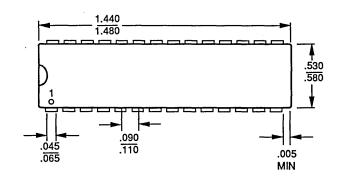

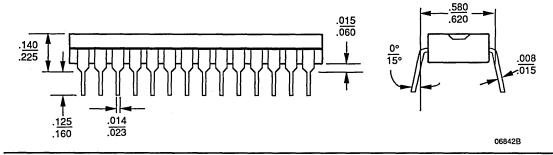

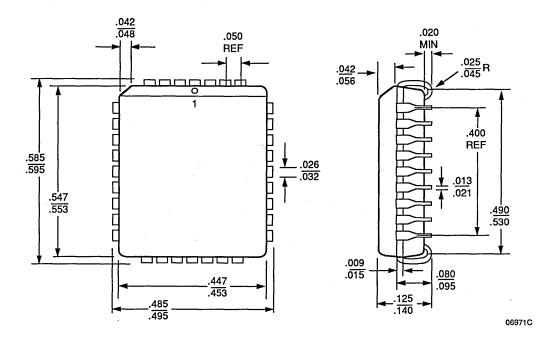

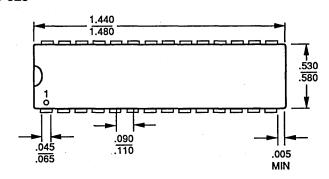

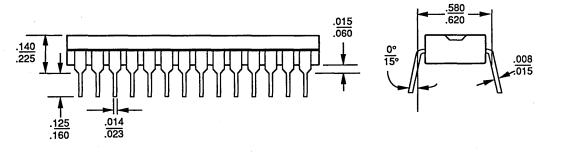

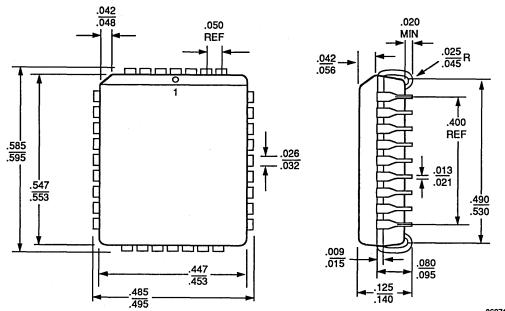

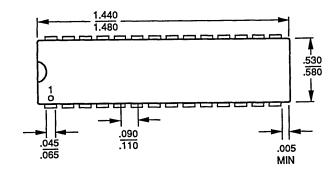

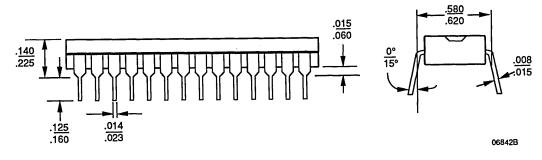

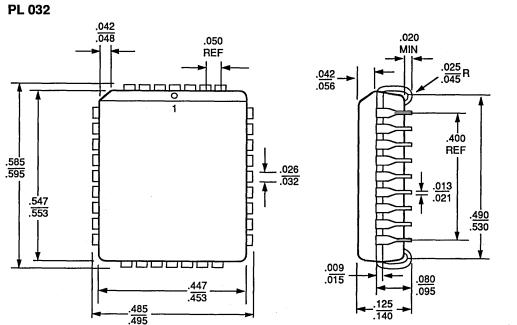

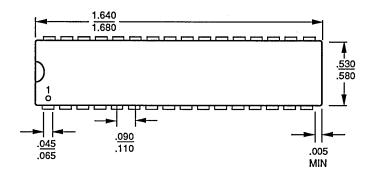

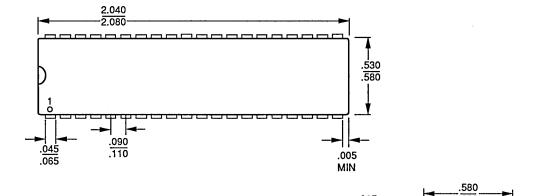

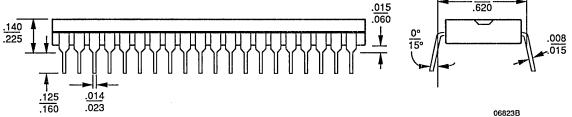

### PHYSICAL DIMENSIONS PD 028

2–10

## Am27X128

## 16,384 x 8-Bit ExpressROM<sup>™</sup> Device

#### DISTINCTIVE CHARACTERISTICS

#### OTP EPROM alternative:

- Factory programmed

- Fully tested and guaranteed

- Low cost

- Mask ROM alternative

- Shorter leadtime

- Lower volume per code

- Compatible with JEDEC-approved EPROM pinout

#### **GENERAL DESCRIPTION**

The Am27X128 is a wafer-level programmed EPROM with a standard topside for plastic packaging. It is organized as 16,384 by 8 bits and is available in plastic DIP as well as plastic leaded chip carrier (PLCC) packages. ExpressROM<sup>™</sup> devices provide a board-ready memory solution for medium to high volume codes with short leadtimes. This offers manufacturers a cost-effective and flexible alternative to OTP EPROMs and mask programmed ROMs. Access times as fast as 100 ns allow operation with high-performance microprocessors with reduced WAIT states. The Am27X128 offers separate Output Enable  $(\overline{OE})$  and Chip Enable  $(\overline{CE})$  controls, thus eliminating bus contention in a multiple bus microprocessor system.

AMD's CMOS process technology provides high speed, low power, and high noise immunity. Typical power consumption is only 100 mW in active mode, and 250  $\mu$ W in standby mode.

#### **BLOCK DIAGRAM**

Advanced Micro Devices

- High performance CMOS technology

Fast access time 100 ns

- Low power dissipation

100 μA maximum standby current

- Available in plastic DIP and plastic leaded chip carrier

2000 - Levy -

### PRODUCT SELECTOR GUIDE

| Family Part No.                        | Am27X128 |      |      |      |      |      |

|----------------------------------------|----------|------|------|------|------|------|

| Ordering part No:<br>±5% VCC Tolerance | -105     | -125 | -155 | -205 | -255 | -305 |

| ±10% VCC Tolerance                     |          | -120 | 150  | -200 | -250 | -300 |

| Max Access Time (ns)                   | 100      | 120  | 150  | 200  | 250  | 300  |

| CE (E) Access (ns)                     | 100      | 120  | 150  | 200  | 250  | 300  |

| OE (G) Access (ns)                     | 40       | 50   | 65   | 75   | 100  | 120  |

#### **CONNECTION DIAGRAMS**

#### **Top View**

Note: JEDEC nomenclature is in parentheses.

### LOGIC SYMBOL

### **PIN DESCRIPTION**

| A0 - A13  | <ul> <li>Address inputs</li> </ul>                          |

|-----------|-------------------------------------------------------------|

| CE (E)    | <ul> <li>Chip Enable Input</li> </ul>                       |

| DQ0 - DQ7 | <ul> <li>Data Outputs</li> </ul>                            |

| OE (G)    | = Output Enable Input                                       |

| PGM (P)   | <ul> <li>Enable Input</li> </ul>                            |

| Vpp       | = V <sub>PP</sub> Supply Voltage                            |

| Vcc       | = V <sub>CC</sub> Supply Voltage                            |

| GND       | = Ground                                                    |

| NC        | = No Internal Connection                                    |

| DU        | <ul> <li>No External Connection<br/>(Do Not Use)</li> </ul> |

|           |                                                             |

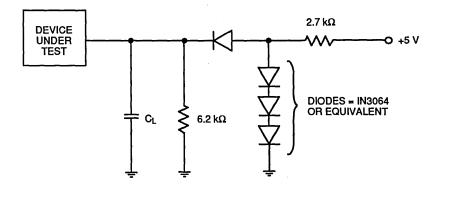

## **ORDERING INFORMATION Standard Products**

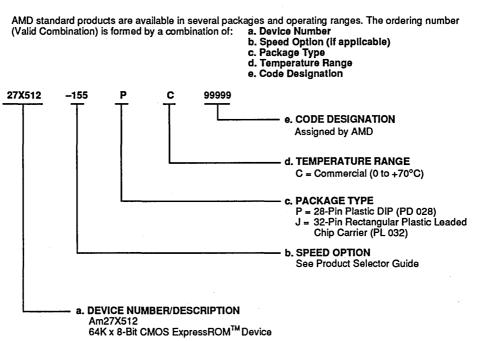

AMD standard products are available in several packages and operating ranges. The ordering number (Valid Combination) is formed by a combination of: a. Device Number b. Speed Option c. Package Type d. Temperature Range e. Code Designation 27X128 -105 P С 99999 e. CODE DESIGNATION Assigned by AMD d. TEMPERATURE RANGE C = Commercial (0 to +70°C) c. PACKAGE TYPE P = 28-Pin Plastic DIP (PD 028) J = 32-Pin Rectangular Plastic Leaded Chip Carrier (PL 032) **b. SPEED OPTION** See Product Selector Guide a. DEVICE NUMBER/DESCRIPTION Am27X128

16K x 8-Bit CMOS ExpressROM<sup>™</sup> Device

| Valid Comb                                                                                                                                                           | vinations |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 27X128-105<br>27X128-120<br>27X128-125<br>27X128-155<br>27X128-155<br>27X128-200<br>27X128-205<br>27X128-250<br>27X128-255<br>27X128-255<br>27X128-300<br>27X128-305 | JC, PC    |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

# FUNCTIONAL DESCRIPTION Read Mode

The Am27X128 has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip Enable ( $\overline{CE}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{OE}$ ) is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that addresses are stable, address access time (t<sub>ACC</sub>) is equal to the delay from  $\overline{CE}$  to output (t<sub>CE</sub>). Data is available at the outputs to<sub>E</sub> after the falling edge of  $\overline{OE}$ , assuming that  $\overline{CE}$  has been LOW and addresses have been stable for at least t<sub>ACC</sub> – to<sub>E</sub>.

## Standby Mode

The Am27X128 has a CMOS standby mode which reduces the maximum  $V_{CC}$  current to  $100 \,\mu$ A. It is placed in CMOS-standby when  $\overrightarrow{CE}$  is at  $V_{CC} \pm 0.3$  V. The Am27X128 also has a TTL-standby mode which reduces the maximum  $V_{CC}$  current to 1.0 mA. It is placed in TTL-standby when  $\overrightarrow{CE}$  is at  $V_{IH}$ . When in standby mode, the outputs are in a high-impedance state, independent of the  $\overrightarrow{OE}$  input.

## **Output OR-Tieing**

To accommodate multiple memory connections, a twoline control function is provided to allow for:

- 1. Low memory power dissipation, and

- 2. Assurance that output bus contention will not occur.

It is recommended that  $\overline{CE}$  be decoded and used as the primary device-selecting function, while  $\overline{OE}$  be made a common connection to all devices in the array and connected to the READ line from the system control bus. This assures that all deselected memory devices are in their low-power standby mode and that the output pins

are only active when data is desired from a particular memory device.

## System Applications

During the switch between active and standby conditions, transient current peaks are produced on the rising and falling edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitance loading of the device. At a minimum, a 0.1  $\mu$ F ceramic capacitor (high frequency, low inherent inductance) should be used on each device between V<sub>CC</sub> and GND to minimize transient effects. In addition, to overcome the voltage drop caused by the inductive effects of the printed circuit board traces on ExpressROM<sup>TM</sup> device arrays, a 4.7- $\mu$ F bulk electrolytic capacitor should be used between V<sub>CC</sub> and GND for each eight devices. The location of the capacitor should be close to where the power supply is connected to the array.

| Mode Select Table |                         |     |     |     |         |  |

|-------------------|-------------------------|-----|-----|-----|---------|--|

| Pins              |                         |     |     |     |         |  |

| Mode              | CE                      | ŌĒ  | PGM | Vpp | Outputs |  |

| Read              | VIL                     | VIL | х   | Vcc | Dout    |  |

| Output<br>Disable | VIL                     | VIH | x   | Vcc | High Z  |  |

| Standby<br>(TTL)  | ViH                     | х   | x   | Vcc | High Z  |  |

| Standby<br>(CMOS) | V <sub>CC</sub> ± 0.3 V | х   | x   | Vcc | High Z  |  |

Note: X can be either VIL or VIH

### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature                       | -65 to 125°C                   |

|-------------------------------------------|--------------------------------|

| Ambient Temperature<br>with Power Applied | –55 to +125°C                  |

| Voltage with Respect to Ground:           |                                |

| All pins except $V_{CC}$ and $V_{PP}$     | -0.6 to V <sub>CC</sub> +0.5 V |

| V <sub>CC</sub> and V <sub>PP</sub>       | –0.6 to 7.0 V                  |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure of the device to absolute maximum rating conditions for extended periods may affect device reliability.

#### Note:

Minimum DC voltage on input or output is -0.5 V. During transitions, the inputs may undershoot GND to -2.0 V for periods of up to 20 ns. Maximum DC voltage on input and output is V<sub>CC</sub> +0.5 V which may overshoot to V<sub>CC</sub> +2.0 V for periods up to 20 ns.

#### **OPERATING RANGES**

| Commercial (C) Devices<br>Case Temperature (T)    | 0 to +70°C       |

|---------------------------------------------------|------------------|

| Supply Read Voltages:                             |                  |

| V <sub>CC</sub> /V <sub>PP</sub> for Am27X128–XX5 | +4.75 to +5.25 V |

| V <sub>CC</sub> /V <sub>PP</sub> for Am27X128–XX0 | +4.50 to +5.50 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

## DC CHARACTERISTICS over operating range unless otherwise specified (Notes 3, 4, 6 and 8)

| Parameter           | Parameter                               | Test Conditions                                                                  | Min.                  | Max.      | Unit |

|---------------------|-----------------------------------------|----------------------------------------------------------------------------------|-----------------------|-----------|------|

| Symbol              | Description                             |                                                                                  |                       |           |      |

| V <sub>OH</sub>     | Output HIGH Voltage                     | I <sub>OH</sub> =  – 400 µA                                                      | 2.4                   |           | v    |

| Vol                 | Output LOW Voltage                      | l <sub>OL</sub> = 2.1 mA                                                         |                       | 0.45      | ν    |

| ViH                 | Input HIGH Voltage                      |                                                                                  | 2.0                   | Vcc + 0.5 | v    |

| VIL                 | Input LOW Voltage                       |                                                                                  | - 0.3                 | +0.8      | v    |

| lu                  | Input Load Current                      | $V_{IN} = 0 V to V_{CC}$                                                         |                       | 1.0       | μA   |

| lιo                 | Output Leakage Current                  | V <sub>OUT</sub> = 0 V to V <sub>CCPP</sub>                                      |                       | 10        | μA   |

| Icc1                | V <sub>CC</sub> Active Current (Note 4) | $\overline{CE} = V_{IL}$ ,f = 5 MHz, $l_{OUT} = 0$ mA(Open Outputs)              |                       | 30        | mA   |

| Icc2                | Vcc Standby Current                     | <del>CE</del> = V <sub>IH</sub>                                                  |                       | 1         | mA   |

| lpp                 | Vcc Supply Current (Note 7)             | $\overline{CE} = \overline{OE} = V_{1L}, V_{PP} = V_{CC}$                        |                       | 100       | μA   |

| CMOS Inpu           | uts                                     |                                                                                  |                       |           |      |

| Parameter<br>Symbol | Parameter<br>Description                | Test Conditions                                                                  | Min.                  | Max.      | Unit |

| Vон                 | Output HIGH Voltage                     | l <sub>OH</sub> = – 400 μA                                                       | 2.4                   |           | v    |

| Vol                 | Output LOW Voltage                      | l <sub>OL</sub> = 2.1 mA                                                         |                       | 0.45      | v    |

| ViH                 | Input HIGH Voltage                      |                                                                                  | V <sub>cc</sub> – 0.3 | Vcc+0.3   | v    |

| VIL                 | Input LOW Voltage                       |                                                                                  | - 0.3                 | +0.8      | v    |

| lu                  | Input Load Current                      | $V_{IN} = 0 V$ to $V_{CC}$                                                       |                       | 1.0       | μA   |

| llo                 | Output Leakage Current                  | V <sub>OUT</sub> = 0 V to V <sub>CC</sub>                                        |                       | 10        | μA   |

| Icc1                | V <sub>CC</sub> Active Current (Note 4) | CE = V <sub>IL,</sub><br>f = 5 MHz,<br>l <sub>OUT</sub> = 0 mA<br>(Open Outputs) |                       | 30        | mA   |

| ICC2                | Vcc Standby Current                     | $\overline{CE} = V_{CC} \pm 0.3$                                                 |                       | 100       | μA   |

| lpp                 | Vcc Supply Current (Note 7)             | $\overline{CE} = \overline{OE} = V_{IL}, V_{PP} = V_{CC}$                        |                       | 100       | μA   |

## CAPACITANCE (Notes 1, 2 and 5)

| Parameter<br>Symbol | Parameter<br>Description | Test Conditions       | Тур. | Max. | Unit |

|---------------------|--------------------------|-----------------------|------|------|------|

| CIN1                | Input Capacitance        | V <sub>IN</sub> = 0 V | 8    | 12   | pF   |

| C <sub>IN2</sub>    | OE Input Capacitance     | V <sub>IN</sub> = 0 V | 12   | 20   | pF   |

| CIN3                | CE Input Capacitance     | V <sub>IN</sub> = 0 V | 9    | 12   | pF   |

| Солт                | Output Capacitance       | Vour = 0 V            | 8    | 12   | pF   |

#### Notes:

- 1. Typical values are for nominal supply voltages.

- 2. This parameter is only sampled and not 100% tested.

- 3. Caution: The Am27X128 must not be removed from, or inserted into, a socket or board when VPP or VCC is applied.

- 4.  $I_{CC1}$  is tested with  $\overline{OE} = V_{IH}$  to simulate open outputs.

- 5. T<sub>A</sub> = 25°C, f = 1 MHz.

- Minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for periods less than 20 ns.

Maximum DC voltage on output pins is V<sub>CC</sub> + 0.5 V which may overshoot to V<sub>CC</sub> + 2.0 V for periods less than 20 ns.

- 7. Maximum active power usage is the sum of Icc and Ipp.

- 8. Vcc must be applied simultaneously or before Vpp, and removed simultaneously or after Vpp.

## SWITCHING CHARACTERISTICS over operating ranges unless otherwise specified (Notes 1, 3 and 4)

| Parame         | ter Symbol<br>Standard | Parameter<br>Description                                                  | Test<br>Conditions                       |              | -105 | 120<br>125 | -150<br>-155 |     |     | 300<br>305 |          |

|----------------|------------------------|---------------------------------------------------------------------------|------------------------------------------|--------------|------|------------|--------------|-----|-----|------------|----------|

| tavav          | tacc                   | Address to<br>Output Delay                                                | $\overline{CE} = \overline{OE} = V_{1L}$ | Min.<br>Max. | 100  | 120        | 150          | 200 | 250 | 300        | ns<br>ns |

| <b>t</b> ELQV  | tce                    | Chip Enable to<br>Output Delay                                            | OE = VIL                                 | Min.<br>Max. | 100  | 120        | 150          | 200 | 250 | 300        | ns       |

| tglav          | toe                    | Output Enable to<br>Output Delay                                          | CE = VIL                                 | Min.<br>Max. | 40   | 50         | 65           | 75  | 100 | 120        | ns<br>ns |

| tehaz<br>tghaz | tDF                    | Output Enable<br>HIGH to Output<br>Float (Note 1)                         |                                          | Min.<br>Max. | 30   | 35         | 50           | 55  | 60  | 75         | ns<br>ns |

| ταχοχ          | tон                    | Output Hold<br>from Addresses,<br>CE or OE<br>whichever<br>occurred first |                                          | Min.<br>Max. | 0    | 0          | 0            | 0   | 0   | 0          | ns<br>ns |

#### Notes:

- 1. Vcc must be applied simultaneously or before VPP, and removed simultaneously or after VPP.

- 2. This parameter is only sampled and not 100% tested.

- 3. Caution: The Am27X128 must not be removed from, or inserted into, a socket or board when Vpp or V<sub>CC</sub> is applied.

- 4. Output Load: 1 TTL gate and CL = 100 pF, Input Rise and Fall Times: 20 ns, Input Pulse Levels: 0.45 to 2.4 V,

Timing Measurement Reference Level — Inputs: 0.8 V and 2 V Outputs: 0.8 V and 2 V

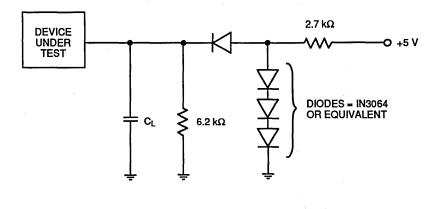

## SWITCHING TEST CIRCUIT

12081B-005

### SWITCHING TEST WAVEFORM

12081B-006

AC Testing: Inputs are driven at 2.4 V for a logic "1" and 0.45 V for a logic "0". Input pulse rise and fall times are ≤ 20ns.

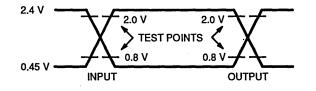

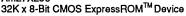

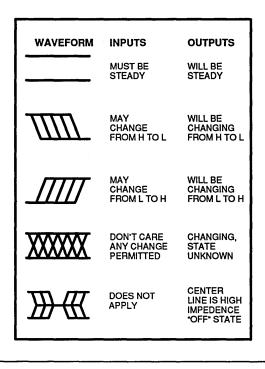

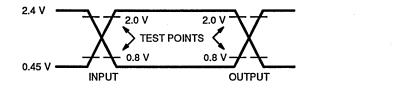

## **KEY TO SWITCHING WAVEFORMS**

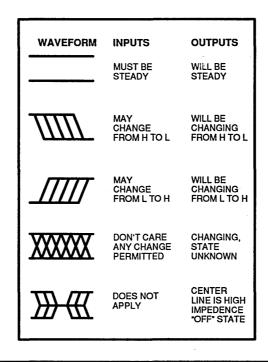

| WAVEFORM | INPUTS                                | OUTPUTS                                            |

|----------|---------------------------------------|----------------------------------------------------|

|          | MUST BE<br>STEADY                     | WILL BE<br>STEADY                                  |

|          | MAY<br>CHANGE<br>FROM H TO L          | WILL BE<br>CHANGING<br>FROM H TO L                 |

|          | MAY<br>CHANGE<br>FROM L TO H          | WILL BE<br>CHANGING<br>FROM L TO H                 |

| XXXXXX   | DON'T CARE<br>ANY CHANGE<br>PERMITTED | CHANGING,<br>STATE<br>UNKNOWN                      |

| ≫₩       | DOES NOT<br>APPLY                     | CENTER<br>LINE IS HIGH<br>IMPEDENCE<br>"OFF" STATE |

SWITCHING WAVEFORMS

Note:

1.  $\overline{OE}$  may be delayed up to  $t_{ACC}$ - $t_{OE}$  after the falling edge of  $\overline{CE}$  without impact on  $t_{ACC}$ . 2.  $t_{DF}$  is specified from  $\overline{OE}$  or  $\overline{CE}$ , whichever occurs first. KS000010

## PHYSICAL DIMENSIONS PD 028

ExpressROM is a trademark of Advanced Micro Devices Inc.

#### Final

# Am27X256

## 32,768 x 8-Bit CMOS ExpressROM<sup>™</sup> Device

### **DISTINCTIVE CHARACTERISTICS**

- OTP EPROM alternative:

- Factory programmed

- Fully tested and guaranteed

- Low cost

- Mask ROM alternative

- Shorter leadtime

- Lower volume per code

- Compatible with JEDEC-approved EPROM pinout

- High performance CMOS technology - Fast access time - 100 ns

- Low power dissipation

- 100 µA maximum standby current

- Available in plastic DIP and plastic leaded chip carrier

**GENERAL DESCRIPTION** The Am27X256 is a wafer-level programmed EPROM

with a standard topside for plastic packaging. It is organized as 32,768 by 8 bits and is available in plastic DIP as well as plastic leaded chip carrier (PLCC) packages. ExpressROM<sup>™</sup> devices provide a board-ready memory solution for medium to high volume codes with short leadtimes. This offers manufacturers a cost-effective and flexible alternative to OTP EPROMs and mask programmed ROMs.

Access times as fast as 100 ns allow operation with high-performance microprocessors with reduced WAIT states. The Am27X256 offers separate Output Enable  $(\overline{OE})$  and Chip Enable  $(\overline{CE})$  controls, thus eliminating bus contention in a multiple bus microprocessor system.

AMD's CMOS process technology provides high speed, low power, and high noise immunity. Typical power consumption is only 100 mW in active mode, and 250 µW in standby mode.

Issue Date: April 1989

DATA OUTPUTS

## **BLOCK DIAGRAM**

Advanced Micro **Devices**

#### PRODUCT SELECTOR GUIDE

| Family Part No.                        | Am27X256 |      |      |      |      |      |      |

|----------------------------------------|----------|------|------|------|------|------|------|

| Ordering part No:<br>±5% VCC Tolerance | -105     | -125 | 155  | -175 | -205 | -255 | -305 |

| ±10% VCC Tolerance                     |          | -120 | -150 | -170 | -200 | -250 | -300 |

| Max Access Time (ns)                   | 100      | 120  | 150  | 170  | 200  | 250  | 300  |

| CE (E) Access (ns)                     | 100      | 120  | 150  | 170  | 200  | 250  | 300  |

| OE (G) Access (ns)                     | 40       | 50   | 65   | 70   | 75   | 100  | 120  |

#### **CONNECTION DIAGRAMS**

Note: JEDEC nomenclature is in parentheses.

Am27X256

## ORDERING INFORMATION Standard Products

Am27X256

| Valid Comb                                                                                                                                                                                       | oinations |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 27X256-105<br>27X256-120<br>27X256-125<br>27X256-155<br>27X256-155<br>27X256-170<br>27X256-175<br>27X256-200<br>27X256-200<br>27X256-205<br>27X256-250<br>27X256-250<br>27X256-300<br>27X256-305 | JC, PC    |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

### FUNCTIONAL DESCRIPTION Read Mode

The Am27X256 has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip Enable ( $\overline{CE}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{OE}$ ) is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that addresses are stable, address access time (t<sub>ACC</sub>) is equal to the delay from  $\overline{CE}$  to output (t<sub>CE</sub>). Data is available at the outputs to<sub>E</sub> after the falling edge of  $\overline{OE}$ , assuming that  $\overline{CE}$  has been LOW and addresses have been stable for at least t<sub>ACC</sub> – t<sub>OE</sub>.

### Standby Mode

The Am27X256 has a CMOS standby mode which reduces the maximum  $V_{CC}$  current to  $100 \,\mu$ A. It is placed in CMOS-standby when  $\overline{CE}$  is at  $V_{CC} \pm 0.3$  V. The Am27X256 also has a TTL-standby mode which reduces the maximum  $V_{CC}$  current to 1.0 mA. It is placed in TTL-standby when  $\overline{CE}$  is at  $V_{IH}$ . When in standby mode, the outputs are in a high-impedance state, independent of the  $\overline{OE}$  input.

## **Output OR-Tieing**

To accommodate multiple memory connections, a twoline control function is provided to allow for:

- 1. Low memory power dissipation, and

- 2. Assurance that output bus contention will not occur.

It is recommended that  $\overrightarrow{CE}$  be decoded and used as the primary device-selecting function, while  $\overrightarrow{OE}$  be made a common connection to all devices in the array and connected to the READ line from the system control bus. This assures that all deselected memory devices are in their low-power standby mode and that the output pins

are only active when data is desired from a particular memory device.

## System Applications

During the switch between active and standby conditions, transient current peaks are produced on the rising and falling edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitance loading of the device. At a minimum, a 0.1  $\mu$ F ceramic capacitor (high frequency, low inherent inductance) should be used on each device between V<sub>CC</sub> and GND to minimize transient effects. In addition, to overcome the voltage drop caused by the inductive effects of the printed circuit board traces on ExpressROM<sup>TM</sup> device arrays, a 4.7- $\mu$ F bulk electrolytic capacitor should be used between V<sub>CC</sub> and GND for each eight devices. The location of the capacitor should be close to where the power supply is connected to the array.

| Mode Select Table |             |     |     |         |  |  |

|-------------------|-------------|-----|-----|---------|--|--|

| Pins              |             |     |     |         |  |  |

| Mode              | ĈĒ          | ŌĒ  | Vpp | Outputs |  |  |

| Read              | VIL         | ViL | Vcc | Dout    |  |  |

| Output<br>Disable | VIL         | ViH | Vcc | High Z  |  |  |

| Standby<br>(TTL)  | VIH         | x   | Vcc | High Z  |  |  |

| Standby<br>(CMOS) | Vcc ± 0.3 V | х   | Vcc | High Z  |  |  |

Note: X can be either VIL or VIH

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature                                                                    | –65 to 125°C                   |

|----------------------------------------------------------------------------------------|--------------------------------|

| Ambient Temperature<br>with Power Applied                                              | –55 to +125°C                  |

| Voltage with Respect to Ground:<br>All pins except V <sub>CC</sub> and V <sub>PP</sub> | -0.6 to V <sub>CC</sub> +0.5 V |

| Vcc and VPP                                                                            | –0.6 to 7.0 V                  |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure of the device to absolute maximum rating conditions for extended periods may affect device reliability.

#### Note:

Minimum DC voltage on input or output is -0.5 V. During transitions, the inputs may undershoot GND to -2.0 V for periods of up to 20 ns. Maximum DC voltage on input and output is V<sub>CC</sub>+0.5 V which may overshoot to V<sub>CC</sub>+2.0 V for periods up to 20 ns.

#### **OPERATING RANGES**

| Commercial (C) Devices<br>Case Temperature (T) | 0 to +70°C | ; |

|------------------------------------------------|------------|---|

| Supply Read Voltages:                          |            |   |

V<sub>CC</sub> /V<sub>PP</sub> for Am27X256–XX5 +4.75 to +5.25 V V<sub>CC</sub> /V<sub>PP</sub> for Am27X256–XX0 +4.50 to +5.50 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over operating range unless otherwise specified (Notes 3, 4, 6 and 8)

| Parameter<br>Symbol | Parameter<br>Description                | Test Conditions                                                                                  | Min.                  | Max.                  | Unit<br>V |  |

|---------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------|--|

| Vон                 | Output HIGH Voltage                     | l <sub>OH</sub> = – 400 µA                                                                       | 2.4                   |                       |           |  |

| Vol                 | Output LOW Voltage                      | l <sub>OL</sub> = 2.1 mA                                                                         |                       | 0.45                  | V         |  |

| ViH                 | Input HIGH Voltage                      | ······································                                                           | 2.0                   | V <sub>CC</sub> + 0.5 | v         |  |

| VIL                 | Input LOW Voltage                       |                                                                                                  | - 0.3                 | +0.8                  | v         |  |

| lu                  | Input Load Current                      | V <sub>IN</sub> = 0 V to V <sub>CC</sub>                                                         |                       | 1.0                   | μA        |  |

| llo                 | Output Leakage Current                  | V <sub>OUT</sub> = 0 V to V <sub>CC</sub>                                                        |                       | 10                    | μA        |  |

| ICC1                | V <sub>CC</sub> Active Current (Note 4) | CE = V <sub>IL</sub> ,<br>f = 5 MHz,<br>lout = 0 mA<br>(Open Outputs)                            |                       | 30                    | mA        |  |

| Icc2                | Vcc Standby Current                     | CE = VIH                                                                                         |                       | 1                     | mA        |  |

| IPP                 | VPP Supply Current (Note 7)             | $\overline{CE} = \overline{OE} = V_{IL}, V_{PP} = V_{CC}$                                        |                       | 100                   | μA        |  |

| CMOS Inpu           | uts                                     |                                                                                                  |                       |                       | L         |  |

| Parameter<br>Symbol | Parameter<br>Description                | Test Conditions                                                                                  | Min.                  | Max.                  | Unit      |  |

| VOH                 | Output HIGH Voltage                     | l <sub>он</sub> = – 400 µА                                                                       | 2.4                   |                       | v         |  |

| VoL                 | Output LOW Voltage                      | l <sub>OL</sub> = 2.1 mA                                                                         |                       | 0.45                  | v         |  |

| VIH                 | Input HIGH Voltage                      |                                                                                                  | V <sub>CC</sub> – 0.3 | V <sub>CC</sub> + 0.3 | v         |  |

| VIL                 | Input LOW Voltage                       |                                                                                                  | - 0.3                 | +0.8                  | v         |  |

| lu                  | Input Load Current                      | V <sub>IN</sub> = 0 V to V <sub>CC</sub>                                                         |                       | 1.0                   | μΑ        |  |

| ILO                 | Output Leakage Current                  | V <sub>OUT</sub> = 0 V to V <sub>CC</sub>                                                        |                       | 10                    | μA        |  |

| Icc1                | V <sub>CC</sub> Active Current (Note 4) | CE         VIL,           f = 5 MHz,         Iout = 0 mA           (Open Outputs)         Iouts) |                       | 25                    | mA        |  |

| Icc2                | V <sub>CC</sub> Standby Current         | $\overline{CE} = V_{CC} \pm 0.3$                                                                 |                       | 100                   | μΑ        |  |

| Ірр                 | VPP Supply Current (Note 7)             | $\overline{CE} = \overline{OE} = V_{IL}, V_{PP} = V_{CC}$                                        |                       | 100                   | μA        |  |

### CAPACITANCE (Notes 1, 2 and 5)

| Parameter<br>Symbol | Parameter<br>Description | Test Conditions        | Тур. | Max. | Unit |

|---------------------|--------------------------|------------------------|------|------|------|

| C <sub>IN1</sub>    | Input Capacitance        | V <sub>IN</sub> = 0 V  | 8    | 12   | pF   |

| C <sub>IN2</sub>    | OE Input Capacitance     | V <sub>IN</sub> = 0 V  | 12   | 20   | pF   |

| Сілз                | CE Input Capacitance     | V <sub>IN</sub> = 0 V  | 9    | 12   | pF   |

| Соит                | Output Capacitance       | V <sub>OUT</sub> = 0 V | 8    | 12   | pF   |

#### Notes:

- 1. Typical values are for nominal supply voltages.

- 2. This parameter is only sampled and not 100% tested.

- 3. Caution: The Am27X256 must not be removed from, or inserted into, a socket or board when VPP or VCC is applied.

- 4. ICC1 is tested with  $\overline{OE} = V_{IH}$  to simulate open outputs.

- 5. T<sub>A</sub> = 25°C, f = 1 MHz.

- Minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for periods less than 20 ns.

Maximum DC voltage on output pins is V<sub>CC</sub> + 0.5 V which may overshoot to V<sub>CC</sub> + 2.0 V for periods less than 20 ns.

- 7. Maximum active power usage is the sum of Icc and Ipp.

- 8. VCC must be applied simultaneously or before VPP, and removed simultaneously or after VPP.

## SWITCHING CHARACTERISTICS over operating ranges unless otherwise specified (Notes 1, 3 and 4)

| Parame<br>JEDEC                         | ter Symbol<br>Standard | Parameter<br>Description                                                  | Test<br>Conditions           |              | -105 | -120<br>-125 |     | -170<br>-175 | -200<br>-205 |     | 300<br>305 | Unit     |

|-----------------------------------------|------------------------|---------------------------------------------------------------------------|------------------------------|--------------|------|--------------|-----|--------------|--------------|-----|------------|----------|

| tavov                                   | tacc                   | Address to<br>Output Delay                                                | CE = OE<br>= V <sub>IL</sub> | Min.<br>Max. | 100  | 120          | 150 | 170          | 200          | 250 | 300        | ns<br>ns |

| <b>t</b> ELQV                           | tce                    | Chip Enable to<br>Output Delay                                            | $\overline{OE} = V_{IL}$     | Min.<br>Max. | 100  | 120          | 150 | 170          | 200          | 250 | 300        | ns<br>ns |

| tglav                                   | toe                    | Output Enable to<br>Output Delay                                          | CE = VIL                     | Min.<br>Max. | 40   | 50           | 65  | 70           | 75           | 100 | 120        | ns<br>ns |

| t <sub>ehoz,</sub><br>t <sub>ghoz</sub> | tor                    | Output Enable<br>HIGH to Output<br>Float (Note 1)                         |                              | Min.<br>Max. | 30   | 35           | 50  | 50           | 55           | 60  | 75         | ns<br>ns |

| taxox                                   | tон                    | Output Hold<br>from Addresses,<br>CE or OE<br>whichever<br>occurred first |                              | Min.<br>Max. | 0    | 0            | 0   | 0            | 0            | 0   | 0          | ns<br>ns |

#### Notes:

- 1. Vcc must be applied simultaneously or before VPP, and removed simultaneously or after VPP.

- 2. This parameter is only sampled and not 100% tested.

- 3. Caution: The Am27X256 must not be removed from, or inserted into, a socket or board when Vpp or V<sub>CC</sub> is applied.

- 4. Output Load: 1 TTL gate and C<sub>L</sub> = 100 pF, Input Rise and Fall Times: 20 ns, Input Pulse Levels: 0.45 to 2.4 V, Timing Measurement Reference Level — Inputs: 0.8 V and 2 V

Outputs: 0.8 V and 2 V

#### **KEY TO SWITCHING WAVEFORMS**

KS000010

#### SWITCHING WAVEFORMS

Note:

1. OE may be delayed up to tACC-tOE after the falling edge of CE without impact on tACC.

2. tDF is specified from OE or CE, whichever occurs first.

### SWITCHING TEST CIRCUIT

12081B-005

## SWITCHING TEST WAVEFORM

12081B-006

AC Testing: Inputs are driven at 2.4 V for a logic "1" and 0.45 V for a logic "0". Input pulse rise and fall times are ≤ 20ns.

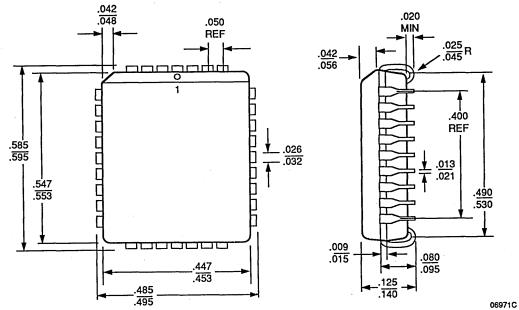

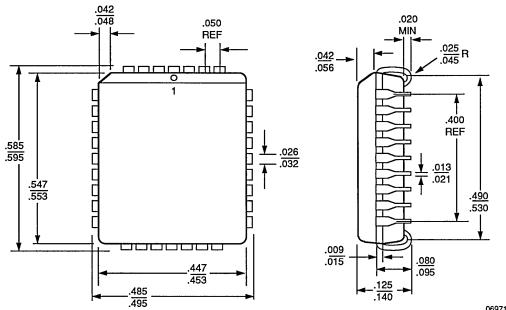

### PHYSICAL DIMENSIONS PD 028

06971C

4-10

# Am27X512

# 65,536 x 8-Bit CMOS ExpressROM<sup>™</sup> Device

#### **DISTINCTIVE CHARACTERISTICS**

- OTP EPROM alternative:

- Factory programmed

- Fully tested and guaranteed

- Low cost

- Mask ROM alternative

- Shorter leadtime

- Lower volume per code

- Compatible with JEDEC-approved EPROM pinout

# High performance CMOS technology – Fast access time — 150 ns

- Low power dissipation

100 µA maximum standby current

- Available in plastic DIP and plastic leaded chip carrier

Advanced Micro

Devices

### **GENERAL DESCRIPTION**

The Am27X512 is a wafer-level programmed EPROM with a standard topside for plastic packaging. It is organized as 65,536 by 8 bits and is available in plastic DIP as well as plastic leaded chip carrier (PLCC) packages. ExpressROM<sup>™</sup> devices provide a board-ready memory solution for medium to high volume codes with short leadtimes. This offers manufacturers a cost-effective and flexible alternative to OTP EPROMs and mask programmed ROMs.

Access times as fast as 150 ns allow operation with

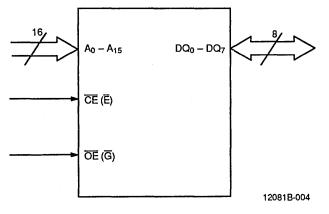

#### **BLOCK DIAGRAM**

high-performance microprocessors with reduced WAIT states. The Am27X512 offers separate Output Enable  $(\overline{OE})$  and Chip Enable  $(\overline{CE})$  controls, thus eliminating bus contention in a multiple bus microprocessor system.

AMD's CMOS process technology provides high speed, low power, and high noise immunity. Typical power consumption is only 100 mW in active mode, and 250  $\mu W$  in standby mode.

ExpressROM is a trademark of Advanced Micro Devices Inc.

12081B-001

### **PRODUCT SELECTOR GUIDE**

| Family Part No.                        | Am27X512 |      |      |      |      |

|----------------------------------------|----------|------|------|------|------|

| Ordering part No:<br>±5% VCC Tolerance | -155     | -175 | -205 | -255 | 305  |

| ±10% VCC Tolerance                     | -        | -170 | -200 | -250 | -300 |

| Max Access Time (ns)                   | 150      | 170  | 200  | 250  | 300  |

| CE (E) Access (ns)                     | 150      | 170  | 200  | 250  | 300  |

| OE (G) Access (ns)                     | 50       | 50   | 75   | 100  | 100  |

#### **CONNECTION DIAGRAMS**

#### **Top View**

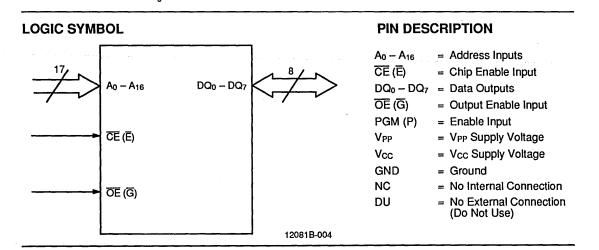

# LOGIC SYMBOL

#### **PIN DESCRIPTION**

| A0 - A15                          | = | Address Inputs                         |

|-----------------------------------|---|----------------------------------------|

| CE (E)                            | = | Chip Enable Input                      |

| DQ <sub>0</sub> – DQ <sub>7</sub> | = | Data Outputs                           |

| OE (G)                            | = | Output Enable Input                    |

| V <sub>CC</sub>                   | 1 | Vcc Supply Voltage                     |

| GND                               | = | Ground                                 |

| NC                                | = | No Internal Connection                 |

| DU                                | H | No External Connection<br>(Do Not Use) |

|                                   |   |                                        |

|                                   |   |                                        |

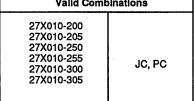

### ORDERING INFORMATION Standard Products

| Valid Comb                                                                                                                 | inations |

|----------------------------------------------------------------------------------------------------------------------------|----------|

| 27X512-155<br>27X512-170<br>27X512-175<br>27X512-200<br>27X512-205<br>27X512-250<br>27X512-255<br>27X512-300<br>27X512-305 | JC, PC   |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

#### FUNCTIONAL DESCRIPTION Read Mode

The Am27X512 has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip Enable ( $\overline{CE}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{OE}$ ) is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that addresses are stable, address access time (t<sub>ACC</sub>) is equal to the delay from  $\overline{CE}$  to output (t<sub>CE</sub>). Data is available at the outputs to<sub>E</sub> after the falling edge of  $\overline{OE}$ , assuming that  $\overline{CE}$  has been LOW and addresses have been stable for at least t<sub>ACC</sub> – t<sub>OE</sub>.

#### **Standby Mode**

The Am27X512 has a CMOS standby mode which reduces the maximum  $V_{CC}$  current to  $100 \,\mu$ A. It is placed in CMOS-standby when  $\overrightarrow{CE}$  is at  $V_{CC} \pm 0.3$  V. The Am27X512 also has a TTL-standby mode which reduces the maximum  $V_{CC}$  current to 1.0 mA. It is placed in TTL-standby when  $\overrightarrow{CE}$  is at  $V_{IH}$ . When in standby mode, the outputs are in a high-impedance state, independent of the  $\overrightarrow{OE}$  input.

#### **Output OR-Tieing**

5-4

To accommodate multiple memory connections, a twoline control function is provided to allow for:

1.Low memory power dissipation, and

2. Assurance that output bus contention will not occur.

It is recommended that  $\overline{CE}$  be decoded and used as the primary device-selecting function, while  $\overline{OE}$  be made a common connection to all devices in the array and connected to the READ line from the system control bus.

This assures that all deselected memory devices are in their low-power standby mode and that the output pins are only active when data is desired from a particular memory device.

#### System Applications

During the switch between active and standby conditions, transient current peaks are produced on the rising and falling edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitance loading of the device. At a minimum, a 0.1  $\mu$ F ceramic capacitor (high frequency, low inherent inductance) should be used on each device between V<sub>CC</sub> and GND to minimize transient effects. In addition, to overcome the voltage drop caused by the inductive effects of the printed circuit board traces on ExpressROM<sup>TM</sup> device arrays, a 4.7- $\mu$ F bulk electrolytic capacitor should be used between V<sub>CC</sub> and GND for each eight devices. The location of the capacitor should be array.

| Mode Select Table |                    |     |         |  |  |  |

|-------------------|--------------------|-----|---------|--|--|--|

| Pins              |                    |     |         |  |  |  |

| Mode              | CE                 | ŌĒ  | Outputs |  |  |  |

| Read              | VIL                | VıL | Dout    |  |  |  |

| Output Disable    | VIL                | VIH | High Z  |  |  |  |

| Standby (TTL)     | ViH                | х   | High Z  |  |  |  |

| Standby (CMOS)    | $V_{CC} \pm 0.3 V$ | х   | High Z  |  |  |  |

Note: X can be either VIL or VIH

### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature                       | -65 to 125°C       |

|-------------------------------------------|--------------------|

| Ambient Temperature<br>with Power Applied | –55 to +125°C      |

| Voltage with Respect to Ground:           |                    |

| All pins except V <sub>CC</sub>           | -0.6 to Vcc +0.5 V |

| Vcc                                       | -0.6 to 7.0 V      |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure of the device to absolute maximum rating conditions for extended periods may affect device reliability.

**Note:** Minimum DC voltage on input or output is -0.5 V. During transitions, the inputs may undershoot GND to -2.0 V for periods of up to 20 ns. Maximum DC voltage on input and output is V<sub>CC</sub> +0.5 V which may overshoot to V<sub>CC</sub> +2.0 V for periods up to 20 ns.

#### **OPERATING RANGES**

| Commercial (C) Devices<br>Case Temperature (T) | 0 to +70°C |

|------------------------------------------------|------------|

| Cumply Dead Vellegees                          |            |

#### Supply Read Voltages:

V<sub>cc</sub> for Am27X512–XX5 +4.7 V<sub>cc</sub> for Am27X512–XX0 +4.5

+4.75 to +5.25 V +4.50 to +5.50 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over operating range unless otherwise specified (Notes 3, 4, and 6)

| TTL and N           | MOS Inputs                                                                               |                                                                                |                       |           |      |

|---------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------|-----------|------|

| Parameter<br>Symbol | Parameter<br>Description                                                                 | Test Conditions                                                                | Min.                  | Max.      | Unit |

| V <sub>OH</sub>     | Output HIGH Voltage                                                                      | I <sub>OH</sub> = - 400 μA                                                     | 2.4                   |           | v    |

| VoL                 | Output LOW Voltage                                                                       | I <sub>OL</sub> = 2.1 mA                                                       |                       | 0.45      | v    |

| ViH                 | Input HIGH Voltage                                                                       |                                                                                | 2.0                   | Vcc + 0.5 | v    |

| VIL                 | Input LOW Voltage                                                                        |                                                                                | -0.3                  | +0.8      | v    |

| lu                  | Input Load Current                                                                       | $V_{IN} = 0 V to V_{CC}$                                                       |                       | 1.0       | μA   |

| ILO                 | Output Leakage Current                                                                   | $V_{OUT} = 0 V to V_{CC}$                                                      |                       | 10        | μA   |