# Advanced Micro Devices Multiple Bus Exchange

1991 Handbook/Data Book

© 1990 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

#### Trademarks

Am29000 is a trademark of Advanced Micro Devices, Inc. MACH is a trademark of Advanced Micro Devices, Inc. OrCAD is registered trademark of OrCAD Systems Corporation OrCAD/SDT is a trademark of OrCAD Systems Corporation PAL is a registered trademark of Advanced Micro Devices, Inc. PC-AT is a registered trademark of IBM Corporation SmartModel is a registered trademark of Logic Automation , Inc. SmartModel Windows is a trademark of Logic Automation, Inc. TAXI and TAXIchip are trademarks of Advanced Micro Devices, Inc. VMEbus is a trademark of Motorola, Inc. As part of AMD's continued commitment to provide high-performance, innovative bus interface products, we have developed the Multiple Bus Exchange Family. Each MBE device efficiently implements a high-speed digital cross-point switch with high output drive on all ports. These devices provide a level of flexibility and integration superior to alternative inter-bus solutions. We encourage you to evaluate these products for your multiple bus and multiprocessing communication requirements.

Fuel JRoeden

Fred J. Roeder Vice President Standard Products Division Advanced Micro Devices, Inc.

#### PREFACE

An innovative designer of high-performance bus interface devices, AMD offers an integrated solution for sophisticated multiple bus and multiprocessing designs-the Multiple Bus Exchange family:

| Am29C982  | 4-bit x 4-port Multiple Bus Exchange                        |

|-----------|-------------------------------------------------------------|

| Am29C983A | 9-bit x 4-port Multiple Bus Exchange with input/out latches |

| Am29C985  | 9-bit x 4-port Multiple Bus Exchange with                   |

|           | Parity Generate/Check                                       |

This Handbook/Data Book provides descriptions of AMD's Multiple Bus Exchange devices, including specifications, and gives examples of how to design multiple bus and multiprocessing systems, using these high-speed CMOS bus interface devices.

- Chapter 1 gives an overview of the Multiple Bus Exchange family.

- Chapter 2 presents application notes and an article reprint describing different multiple bus and multiprocessing communication designs using the MBE devices. The applications are divided into three functional areas:

- funnelina

- interleaving

- data routing

- Chapter 3 reviews output edge-rate control design methodology used to minimize ground bounce.

- Chapter 4 provides general information on AMD's design and testing methodologies.

- Chapter 5 contains the MBE data sheets as listed in the table of contents.

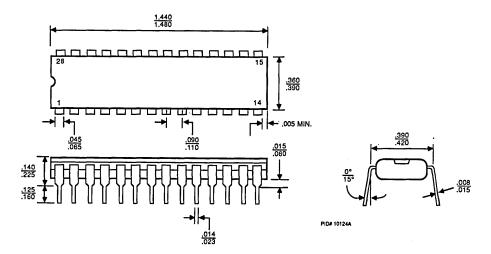

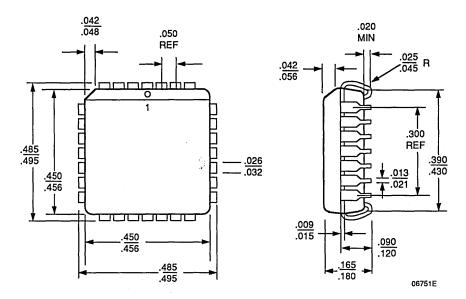

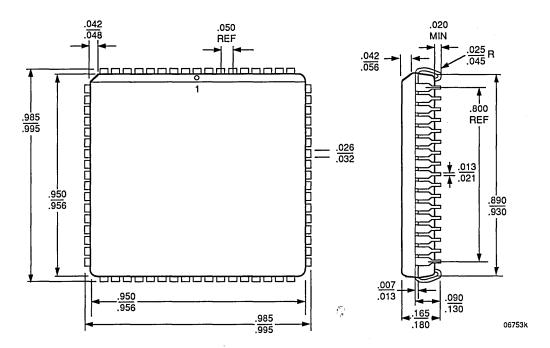

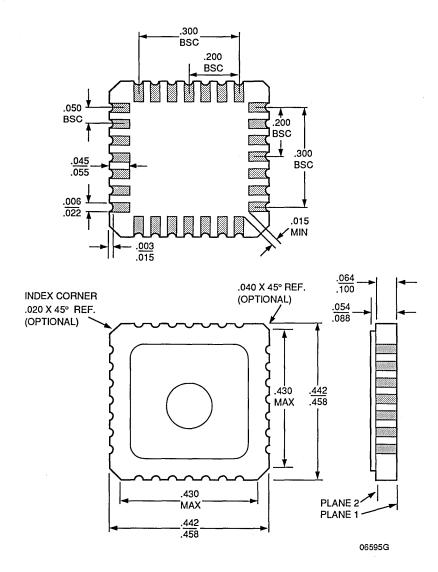

- Chapter 6 shows packaging and physical dimensions.

- Appendix A is a brief discussion of the electronic design automation tools from OrCAD Systems Corporation.

- Appendix B is a brief discussion of the behavioral simulation models from Logic Automation, Inc.

- Appendix C provides device packaging and process data, useful for qualification purposes.

## **TABLE OF CONTENTS**

| Chapter 1  | Multiple Bus Exchange Overview                                    | 1-1 |

|------------|-------------------------------------------------------------------|-----|

| Chapter 2  | Applications and Article Reprint                                  | 2–1 |

| Chapter 3  | Design Methodology                                                | 3–1 |

| Chapter 4  | General Product Information                                       | 4–1 |

| Chapter 5  | Product Specifications                                            | 5-1 |

| Chapter 6  | Physical Dimensions                                               | 6–1 |

| Appendix A | Electronic Design Automation Tools from OrCAD Systems Corporation | A–1 |

| Appendix B | Behavioral Simulation Models from Logic Automation, Inc           | B-1 |

| Appendix C | Device Process and Package Information                            | C-1 |

Л

.

# コ

## **CHAPTER 1** Multiple Bus Exchange Overview

| MBE Family Overview<br>Am29C982<br>Am29C983/Am29C983A<br>Am29C985                                                  | 1–3 |

|--------------------------------------------------------------------------------------------------------------------|-----|

| MBE Family Features<br>High-Drive, Low Ground Bounce Outputs<br>Glitch-Free Power-Up/Down<br>Matched Port Decoding | 1–4 |

| The Multiple Bus Exchange—An Integrated Solution                                                                   | 1–4 |

### **Multiple Bus Exchange Overview**

#### **MULTIPLE BUS EXCHANGE**

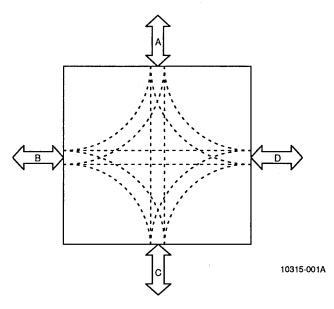

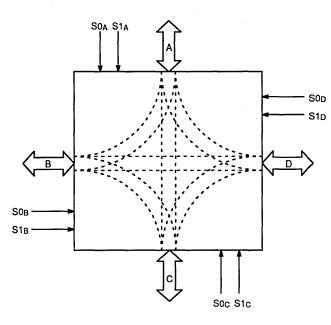

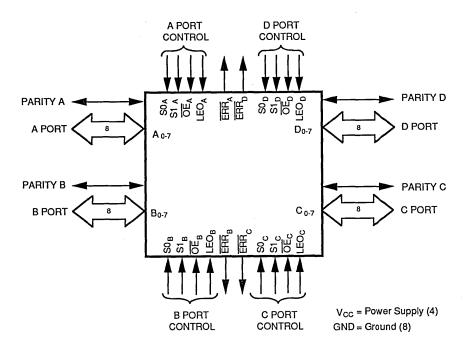

Multiple Bus Exchange (MBE) devices are general purpose, digital crosspoint switches that provide both efficient interbus communication and high bus drive capability. A crosspoint switch provides multi-directional communication between 4 ports, such that any port can, with no restrictions, send data to, or receive data from, any other port. This allows data to be broadcast to all other ports, to be funneled from multiple ports to one port, or for data to be concurrently sent between two sets of ports. In addition, any port which is an input, may simultaneously be an output; i.e., a port may write to itself.

Applications for this flexible architecture include parallel and array processing, memorysystem interfaces, fault-tolerant environments, and other digital systems that require management of the flow and routing of data between buses.

#### **MBE FAMILY OVERVIEW**

Three MBE architectures are presently available—the Am29C982, Am29C983/983A, and the Am29C985.

#### Am29C982

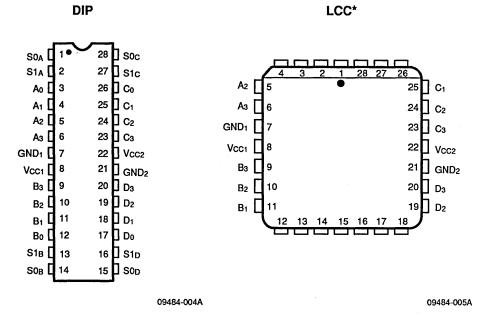

The Am29C982 is a 4-port, 4-bit/port device with no internal storage. The '982 offers a small (28-pin PLCC), low-cost solution for nibble-divisible applications that require data routing.

Figure 1-1. Multiple Bus Exchange— Digital Crosspoint Switch

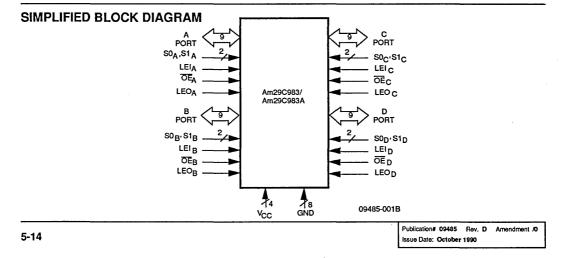

#### Am29C983/Am29C983A

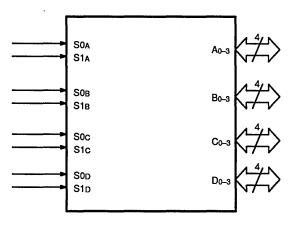

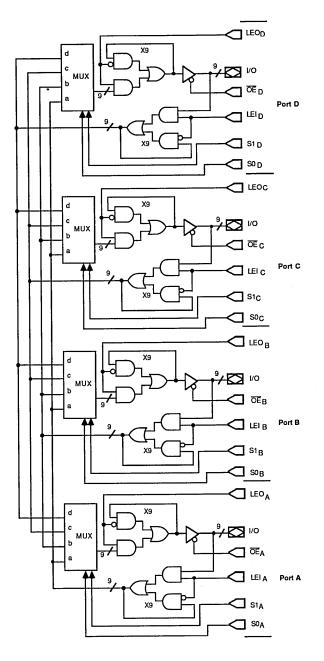

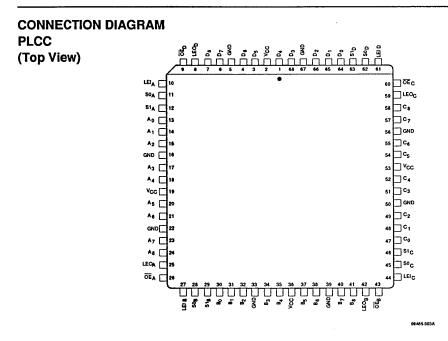

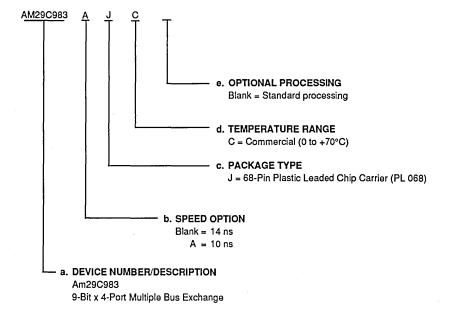

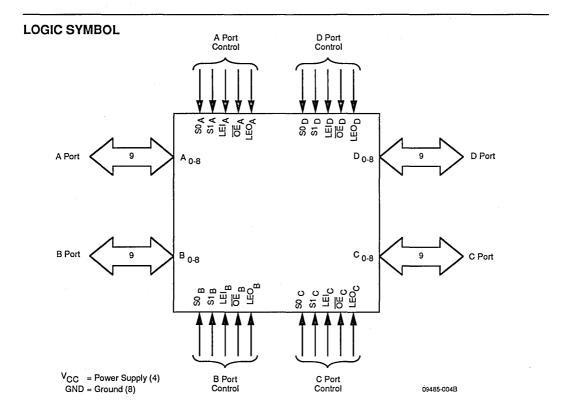

The Am29C983 is a wider (9-bit), faster (Am29C983A) version of the four-port crosspoint switch. Each I/O port has an input latch and an output latch; thus, data can be latched before and after the switching matrix. All input and output latches are independently controlled by active-HIGH Latch Enable inputs. The integration of these flexible storage and enable features into the bus switch saves board space and improves performance over discrete-based data routing solutions.

The 9-bit port width is an additional boon to the system designer, transmitting a data byte and its (system supplied) parity bit without having to break the byte across multiple devices. The ability to route entire parity protected bytes in one package saves board space and reduces skew problems.

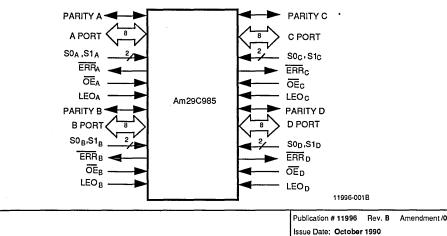

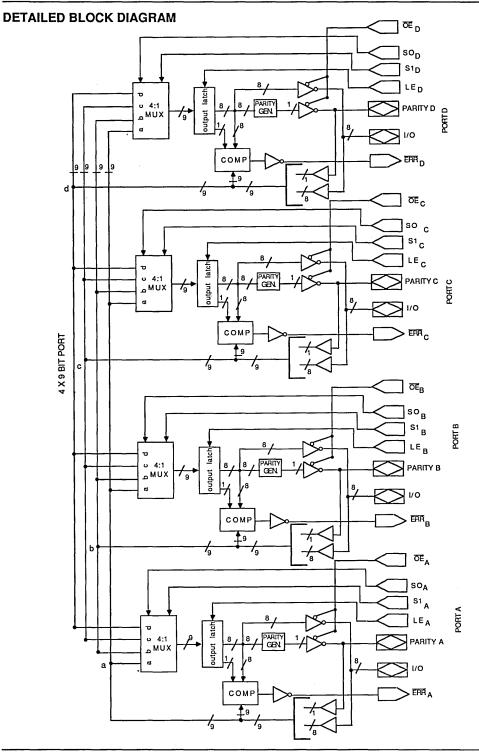

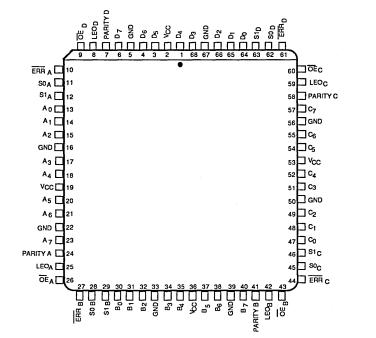

#### Am29C985

For those systems which require parity generation and checking, AMD integrates this generation and check capability into a 4-port, 9-bit/port crosspoint switch.

The Am29C985 incorporates parity check and generation capabilities on all four output ports. Each output port is capable of generating odd parity on byte-wide input data. Accordingly, parity check is accomplished at each output on the incoming 9-bit data + parity word. Data integrity is further ensured by a proprietary comparison scheme that compares the state of the bus with the data driven onto it. Stuck-at faults and system interconnect problems, which would escape a simple internal parity check, are also detected.

Each I/O port has an output latch to capture outgoing data. All output latches are independently controlled by active-HIGH Output Latch Enable inputs.

#### **MBE FAMILY FEATURES**

#### **High-Drive, Low Ground Bounce Outputs**

Every MBE device has 48-mA loc outputs for high capacitance bus driving. AMD's proprietary output edge-rate control minimizes ground bounce and reduces the severity of crosstalk (See Application Note, chapter 3). The MBE not only routes and stores data, but can also drive heavily loaded system buses too. Ample power and ground pins are included to further reduce noise and ground bounce.

#### **Glitch-Free Power-Up/Down**

Every MBE device has a power up/down circuit for maintaining a high-impedance state on the bus during power supply sequencing. Each MBE output structure uses n-channel pull-up transistors that withstand an external bus voltage when supply voltage is off. These features guarantee glitch-free operation, an important concern for large systems with separately powered sub-units. For additional power-up/down information, see Chapter 4.

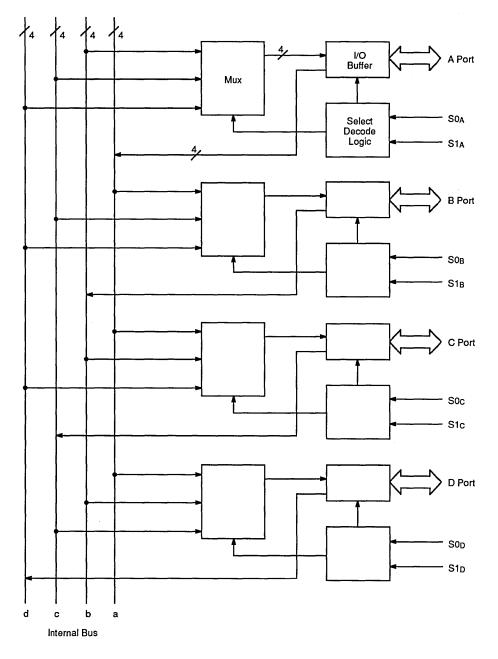

#### **Matched Port Decoding**

The MBE has matched port decoding. Each port uses a common coding rule, with a 2-bit port-select code determining the source of data for output. This scheme simplifies external decode logic because all four ports are controlled in an identical manner. This avoids decoding delays and permits independent operation of the routing at each port. As a result, multiple MBEs can be cascaded to effectively construct wider-bus (16-, 32-,...-bit) interface structures.

# THE MULTIPLE BUS EXCHANGE—AN INTEGRATED SOLUTION

The MBE provides an integrated interface solution which logically replaces a large number of latches, multiplexers and buffers. This highly integrated solution provides two main advantages: design simplicity and real-estate savings.

#### **Design Simplicity**

The advantage of design simplicity is most apparent during the timing and logic control design phases. Since fewer devices are now required in the bus interface design, fewer delays and skews must be factored into the timing equations. Likewise, since the MBE not only integrates multiple components, but also has matched-port decoding, the logic necessary to control the interface device is much less complex. Fewer devices and matched-port decoding result in a simpler timing controller.

#### **Real-Estate Savings**

One does not have to look far to realize the importance of real-estate savings. Each computer generation has not only become quite a bit more powerful than its predecessor, but also quite a bit smaller! This decrease in space not only satisfies the end-customer's desire for a compact solution, but also represents significant cost savings for the manufacturer.

Each integrated circuit used on a board costs a certain amount of money to install, house, power and cool, regardless of what it is or what it does. If one adds up the cost of all the physical hardware (cabinets, boards, power supplies, fans, etc.) which support the integrated circuits in the system, minus the cost of the circuits themselves, but including the assembly cost of mounting them onto the board, and divides this cost by the total number of integrated circuits, one would get some sort of "overhead factor"—the cost of having one integrated circuit.

It may seem arbitrary to allocate a specific charge per integrated circuit without regard to the circuit's function; however, any human or automated handling costs are probably similar for any size package. Additionally, since packages cannot touch one another on a circuit board without shorting each other out, a border must be allocated around each package. The corresponding "footprint" around the package tends to decrease the relative difference in board space consumed by smaller and larger packaged parts. Thus, the additional space required for a smaller package footprint increases at a higher percentage than that of a larger package. This also means that being capable of removing any package, large or small, from the design can drastically reduce the overall real-estate and cost requirements.

The following tables demonstrate average real-estate savings of the 68-pin PLCC Am29C983A versus 20-pin PDIP or SOIC octal buffers and latches and 24-pin PDIP or SOIC octal transceiver/registers. Modern component mounting technologies require a minimum of 100 mils (0.1") between the ends and sides of each device.

The minimum area of each component footprint, as shown in Table 1–1, is calculated by adding 0.1" to both the length and width of the device features. The device feature measurements are representative of the package length and pin width of 74F245 buffers, 74F373 latches and 74F646 transceiver/registers.

The real-estate requirements for a typical 8-bit multiple bus interface design with storage, comparing one Am29C983A with four latches and two buffers, is shown in Table 1–2. The real-estate requirements for a typical 32-bit interface design, comparing four Am29C983As with eight buffers and eight transceiver/registers, is shown in Table 1–3. These comparisons are based on systems which do not use parity. The real-estate savings resulting from using Am29C983As is drastically higher in data + parity designs, as demonstrated in tables 1–4 and 1–5.

|             | Package |       | Footprint |       | Area               |  |

|-------------|---------|-------|-----------|-------|--------------------|--|

| Туре        | Length  | Width | Length    | Width | (in <sup>2</sup> ) |  |

| 20-Pin PDIP | 1.057   | 0.322 | 1.157     | 0.422 | 0.488              |  |

| 20-Pin SOIC | 0.512   | 0.419 | 0.612     | 0.519 | 0.318              |  |

| 24-Pin PDIP | 1.280   | 0.322 | 1.380     | 0.422 | 0.582              |  |

| 24-Pin SOIC | 0.614   | 0.419 | 0.714     | 0.519 | 0.371              |  |

| 68-Pin PLCC | 0.995   | 0.995 | 1.095     | 1.095 | 1.199              |  |

Table 1–1. Calculated Component Footprints, in Inches

| Design       | Pkg  | Units | Area/Unit | Total Area    |

|--------------|------|-------|-----------|---------------|

| Buffer/Latch | PDIP | 6     | 0.488     | 2.928         |

|              | SOIC | 6     | 0.318     | 1. <u>908</u> |

| Am29C983A    | PLCC | 1     | 1.199     | 1.199         |

Table 1–3. Typical 32-bit footprint comparison, in Square inches

| Design                | Pkg          | Units  | Area/Unit      | Total Area                       |

|-----------------------|--------------|--------|----------------|----------------------------------|

| Buffer<br>Xceiver/Reg | PDIP<br>PDIP | 8<br>8 | 0.488<br>0.582 | 3.904<br><u>+ 4.656</u><br>8.560 |

| Buffer<br>Xceiver/Reg | SOIC<br>SOIC | 8<br>8 | 0.318<br>0.371 | 2.544<br>+ 2.968<br>5.512        |

| Am29C983A             | PLCC         | 4      | 1.199          | 4.796                            |

Table 1-4. Typical 8-bit Data + Parity Footprint Comparison, in Square Inches

| Design       | Pkg  | Units | Area/Unit | Total Area |

|--------------|------|-------|-----------|------------|

| Buffer/Latch | PDIP | 8     | 0.488     | 3.904      |

|              | SOIC | 8     | 0.318     | 2.544      |

| Am29C983A    | PLCC | 1     | 1.199     | 1.199      |

| Design      | Pkg  | Units | Area/Unit | Total Area |

|-------------|------|-------|-----------|------------|

| Buffer      | PDIP | 10    | 0.488     | 4.880      |

| Xceiver/Reg | PDIP | 10    | 0.582     | + 5.820    |

|             |      |       |           | 10.700     |

| Buffer      | SOIC | 10    | 0.318     | 3.180      |

| Xceiver/Reg | SOIC | 10    | 0.371     | + 3.710    |

|             |      |       |           | 6.890      |

| Am29C983A   | PLCC | 4     | 1.199     | 4.796      |

# Л

## **CHAPTER 2** Applications and Article Reprint

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Funneling Applications<br>Maintaining Software Compatibility with Established Bus Standards<br>Dynamic Bus Sizing with the 80386 Microprocessor<br>Expanding the Apparent Width of Various Devices and Systems<br>Expansion of a ROM-Based Finite-State Machine<br>Expansion of FIFOs<br>Expansion of FIFOs<br>Expansion of Peripheral Ports<br>Adaptation of Peripheral Ports<br>Bus Expansion for Graphics — Controlling 24-bit<br>Planes with an 8-bit Bus | 2–3  |

| Interleaving Applications                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2–9  |

| Data Routing Applications<br>Microprocessor-Memory Interface                                                                                                                                                                                                                                                                                                                                                                                                  | 2–14 |

| Article Reprint                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2–24 |

#### INTRODUCTION

This chapter includes application notes and an article reprint utilizing the Multiple Bus Exchange in various system solutions. The applications are categorized into three general purpose functional groups—funneling, interleaving and data routing.

Diverse applications have been included in each functional group so that the user may understand the broad application base which the MBE serves. Each application is written as general as possible so that the user may tailor his implementation as required.

The article reprint, which was originally printed in Electronic Design, discusses the advantages a silicon digital crosspoint switch in silicon offers to interbus communications.

### **Applications and Article Reprint**

#### **FUNNELING APPLICATIONS**

Many applications require data communications between subsystems of differing buswidths. In these applications, the processor or controller uses byte-word compression and expansion techniques to communicate between the varying bus-widths. This communication between larger and smaller bus sizes is generically called "funneling."

For example, if a 32-bit processor communicates with an 8-bit peripheral, the data must be "funneled" from 32-bits to 8-bits. When byte-word expansion techniques are used, such that an 8-bit peripheral is communicating to a 32-bit processor, the technique is often called "bus expansion."

Another funneling application occurs when a microprocessor communicates to buses of differing widths. For example, a 32-bit processor may have 8-, 16- or 32-bit peripherals. In this application, the processor uses byte-word compression and expansion and then latches the bytes into 8-,16- or 32-bit words, respectively. These words are then communicated to the peripheral device. This intelligent funneling application is often called "dynamic bus sizing."

## Maintaining Software Compatibility with Established Bus Standards

Bus standards have traditionally not kept pace with the microprocessors that they are supposed to serve. While microprocessors have evolved from 8-bit to 16-bit, and now 32-bit data buses, the most popular buses (in terms of sales volume and installed base) are either 8-bit (PC, PC-XT) or 16-bit (PC-AT<sup>®</sup>). This mismatch in bus width places an additional constraint on the hardware designer, that of providing downward compatibility with an installed base of peripheral cards and software, while improving system performance and reducing cost.

Some aspects of the compatibility issue, such as the assignment of memory and peripheral addresses, pose no real design problems. However, ensuring that peripherals behave properly when the source of data is wider than the bus to which it is connected requires a basic understanding of the system code.

For example, the iAPX8088 is a processor with 16-bit internal data paths, but only an 8-bit external data bus. Data is funneled from the external 8-bit to the internal 16-bit data bus. For instruction fetches, code is read a byte at a time and assembled into words internally. Similarly, word-data accesses are converted into two byte-Read operations or two byte-Write operations. It is possible to write iAPX8088 code that performs two byte-writes to a peripheral by using a one-word Write instruction.

Unfortunately, this code is hardware dependent. When using a 16-bit processor, executing a word Write on a 16-bit bus, all 16 bits are transferred at once. However, if the peripheral is an 8-bit device, only the lower byte is read; the upper byte is lost and the peripheral is programmed incorrectly.

To successfully design systems using differing bus-widths, instructions dependent on bus width must not be used. Byte-wide peripherals require byte-oriented instructions to ensure proper operation. Unfortunately, constraining the system to use only byte operations increases code size and slows the system down. Wider data buses and microprocessors are used to increase bus bandwidth and improve system performance. Forcing data transfers to always be byte wide is like using only one lane of a four-lane highway—it's slow and doesn't make much sense.

The only real choice for system designers who wish to maintain compatibility with old software is to incorporate extra hardware which emulates byte Reads and Writes. For example, the IBM PC-AT supports several types of bus access, including word Read or Write to byte memory or to byte I/O. Two bus signals, MEM16 and IOCS16, inform the microprocessor of the data size of the memory or peripheral being accessed. These signals are generated by any word-wide device, but not by any byte-wide devices. If a word access is performed by a 16-bit microprocessor and either MEM16 or IOCS16 is valid, both the high and low bytes of the word are read or written simultaneously. If MEM16 or IOCS16 is not valid, two actions must be taken, depending on the type of access.

For word Write operations, data is valid on the microprocessor data pins for the duration of the access. The microprocessor starts the Write operation on the lower byte, but does not complete it. Instead, the microprocessor is placed in a Wait state and the Write operation to the lower byte is completed by external hardware. The address is then incremented by one, and the high-order data byte is then routed (funneled) to the low-order byte position. A Write strobe is performed, writing the second byte of data, and the microprocessor is then released from the Wait state.

Word Read accesses from an 8-bit device are performed in a similar manner. In this case, the microprocessor is held in the Wait state until a word has been assembled from two byte-Reads. A latch holds the low-order byte until the high-order byte is accessed. Both bytes are then read simultaneously by the microprocessor.

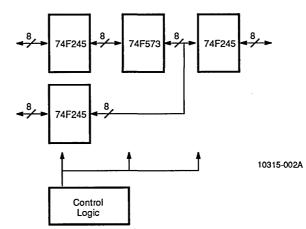

The external hardware required to perform this byte/word funneling without an MBE consists of three bidirectional buffers and a latch, plus some control logic, as shown in Figure 2–1. The control logic can be implemented in a PAL device, but implementing the bidirectional buffers with discrete logic presents some problems. Board space, the cumulative propagation delay of two or more bidirectional buffers in series, and the need for low noise, high drive capability weigh heavily against using discrete devices in funneling applications.

Figure 2-1. 8/16-bit Bus Funnel Using 3 Bidirectional Buffers and a Latch

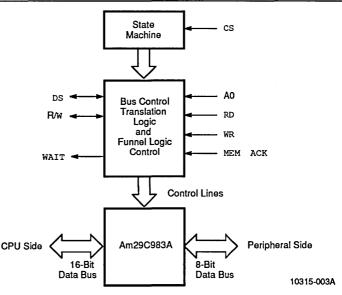

These problems are solved by using the Am29C983 MBE device, as shown in the completed circuit in Figure 2–2. The four 9-bit I/O ports can be configured as either inputs or outputs. Both input and output latches are available on all ports. The 9-bit data path supports the transmission of byte-wide parity through the system, while the non-blocking crosspoint switch can connect any input port to any output port or ports. Maximum propagation delay from any port to any other port or ports is 14 ns worst case with a 50-pF load. The Am29C983A improves the port-to-port delay to 10 ns worst case. Both parts are specified with an loL of 48 mA.

2-4

Figure 2–2. 8/16-bit Bus Funnel Using Am29C983A with Control Logic

As shown in the figure, the MBE connects directly onto the microprocessor data pins with two ports, and onto the system backplane (PC-XT bus, in this case) with one of the other two ports. Two PAL<sup>®</sup> devices are used, one to control MBE data paths, and one to generate Read and Write strobes and increment the address for the byte-oriented device.

#### Dynamic Bus Sizing with the 80386 Microprocessor

As shown in the previous application, newer system designs are continually increasing data bus-widths. However, many peripheral devices do not require, or have not yet designed-in, these wider data buses. In most cases, the 32-bit microprocessor is forced to run with the smaller 8- or 16-bit bus. The capability of a microprocessor to fetch 8-, 16- and 32-bit words from an 8-bit bus is called *dynamic bus sizing*. The 68020 and 68030 microprocessors support this mode of operation; however, many other microprocessors do not. For example, the 80386 microprocessor can handle a 16-bit bus, but cannot operate in an 8-bit environment.

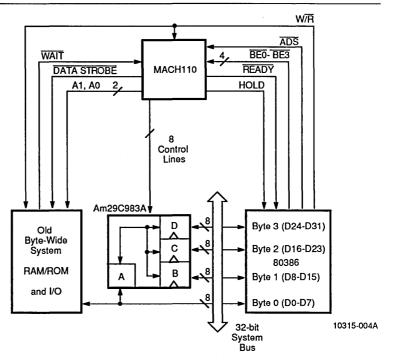

Full byte-level dynamic bus sizing can be added to an 80386 microprocessor by using one MACH<sup>™</sup> device and one Am29C983A MBE, as shown in Figure 2–3. The function of the Am29C983A in this application is made clear by analyzing the conversion of a 32-bit Read or Write cycle to byte accesses on the system bus.

In the case of a 32-bit Read, data must be expanded from 8 bits up to 32 bits. This expansion is done by translating the single 32-bit Read request from the 80386 into four single-byte accesses. Three of the four bytes are input through port A and are latched in ports D, C and B, respectively. On the fourth byte access, the three stored bytes, plus the fourth byte, are presented to the 80386 simultaneously. The MACH110 handles all control signals from the 80386 and controls the Latch Enables and Port Select lines on the MBE.

To transfer 32-bit Writes to the 8-bit bus, data must be funneled down so that a single 32-bit Write is translated into four byte-level transactions. When the 80386 writes the 32-bit data, the lowest-order byte is written directly to the memory or peripheral, while the other three bytes are latched in ports B, C and D. The MACH110 then sends a /Ready signal to the 80386 to indicate completion of the Write cycle, along with the Hold signal to keep the 80386 off the bus until the other three bytes are sent, from their respective latches, to the 8-bit memory or peripheral.

Figure 2–3. 8/32-bit Dynamic Bus Sizing

# Expanding the Apparent Width of Various Devices and Systems

Another type of funneling application trades width for depth by using the MBE to expand the width of a data stream. The idea here is to use the MBE to create a "virtual device" that is much wider than the real device on which it is based. This is done by interleaving addresses and running the real device at a multiple of the system clock, which is equal to the expansion factor. Some examples of this technique follow.

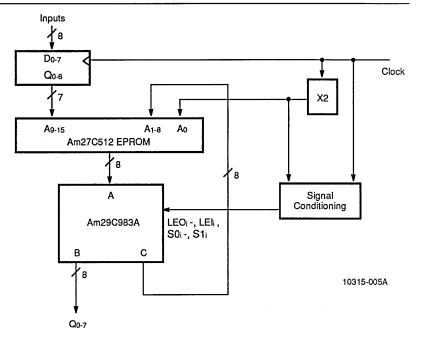

#### **Expansion of a ROM-Based Finite-State Machine**

A finite state machine (FSM) can be built using an EPROM, as shown in Figure 2–4. The number of user-available outputs in this direct implementation of an FSM is limited by the need to use some of the EPROM outputs for next-state information. One solution to this limitation would be to use more EPROMs in parallel, with their address lines connected. Another, more cost effective solution, uses an MBE to double the number of outputs. Since the wide word is stored as a series of contiguous locations in the narrower EPROM, the system clock must be increased by the expansion factor to maintain overall system performance. For this example, where the apparent width is doubled, the EPROM must be accessed twice as often as usual to maintain the same system speed as the unexpanded EPROM. Proper ordering of two EPROM words into one wide word is easily done with an ordinary flip-flop, alternating between odd and even addresses. In the general case, ordering of n contiguous EPROM words into a single wide word requires a modulo-n counter.

Figure 2-4. Expansion of a ROM-Based Finite-State Machine

#### **Expansion of FIFOs**

The same arguments that apply to expanding finite state-machine word width apply to FIFOs as well. A variation of the basic architecture uses two FIFOs and two MBEs to create a wide bidirectional FIFO module.

#### **Expansion of Peripheral Ports**

The MBE makes an ideal port expander for many microcontroller applications. With the overhead of just a few control pins, the MBE expands the port from one byte to three. Each expanded byte can be an input or output. The separate input and output latches at each port can add a layer of buffering in both directions between the microcontroller and real-world I/O if desired.

#### **Adaptation of Peripheral Ports**

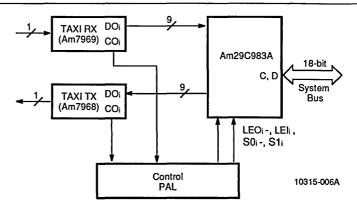

The MBE provides a convenient interface between multiple 8-bit peripherals and buses of various widths. A good example of the power of this type of connectivity is an 80386 to TAXIchip<sup>TM</sup> device interface. The TAXIchip set consists of a byte-wide parallel-to-serial converter with multiplying phase locked loop (TAXI<sup>TM</sup> TX) and a companion serial-to-parallel converter with tracking phase locked loop (TAXI<sup>TM</sup> TX). The TAXI TX and RX comprise a simple point-to-point serial link which looks to the user like a 10-MByte/s parallel transfer. Since the 80386 can handle 16-bit transfers, the MBE provides a single-chip data-path interface between the microprocessor and the TAXI TX and RX. The separate input and output latches at each port buffer incoming and outgoing bytes.

Figure 2–5. TAXI System Interface - 9/18-bit Bus Expansion

## Bus Expansion for Graphics – Controlling 24-Bit Planes with an 8-Bit Bus

Display memory for graphics applications is arranged as a bit map, where each picture element (pixel) on the screen corresponds to a particular location in memory. A bit map of  $m \times n \times 1$  memory locations is referred to as a plane of memory. A single memory plane can indicate if a pixel is on or off. Adding memory planes increases the number of attributes of any particular pixel, such as gray scale, or a pixel blink attribute.

Monochrome images are adequately represented by 256 levels of gray, or 8 bits per pixel. Palette based color graphic systems, which display only 256 selected colors at a time, also require only 8 bits per pixel. True color graphic systems represent the next step up in the display of realistic images. There are no restrictions on the number of simultaneously displayable colors; thus, requiring 8 bits per pixel for each of the primary colors, red green and blue, for a total of 24 bits per pixel. The MBE can provide an easy upgrade path from monochrome or palette based color to true color display by allowing the original 8-bit data bus to support 24 planes of display memory.

The basic system architecture is just a simple bus funnel, transforming an 8-bit graphics processor data bus to the 24-bit width of the bit map. Many variations of this architecture are possible, including modifications for stripe, matrix, and packed-pixel organized bit maps.

Figure 2–6. Graphics Display – 8/24-bit Bus Expansion

#### INTERLEAVING APPLICATIONS

Interleaving is similar to funneling, in that byte-word compression is used to subdivide a wide word into a multitude of smaller words. However, the accessing of these smaller words is done independently. Further, different operations are performed on the smaller words simultaneously.

An additional method of interleaving is to transfer sequential words to two parallel systems, such as memory. This architecture allows the odd and even words to be simultaneously transferred to memory. During memory accesses, the overhead of odd and even word accesses can be overlapped; thus, substantially reducing the average transfer time in comparison to standard sequential accesses.

#### 2-Way Interleaved Memory System

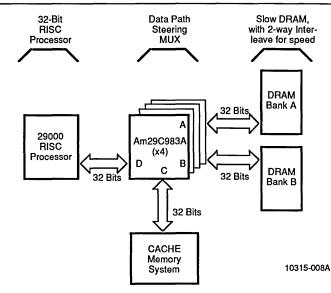

In a 2-way interleaved memory system the DRAMs are arranged into two physically separate memories - odd addresses in one and even addresses in the other. Because they are physically separate memories, both banks are accessed in parallel, starting the read of the next word while the previous word is being processed (see Figure 2–7).

Many microproprocessors require high speed cache, in addition to interleaved main memory, to avoid wait states and maintain high performance. The MBE is ideally suited to this application, providing the odd-even data path switching for bank interleaving, as well as a port for cache accesses. Additional performance is gained by using the MBE's internal latches for posted or deferred writes. In posted writes, the processor completes a write cycle with no wait states to what it thinks is the DRAM main memory. In reality, the data is written to the Am29C983A, which then completes the slow write to DRAM. The latches and data routing capability of the MBE allow the processor to run out of cache concurrently with writing data back to DRAM.

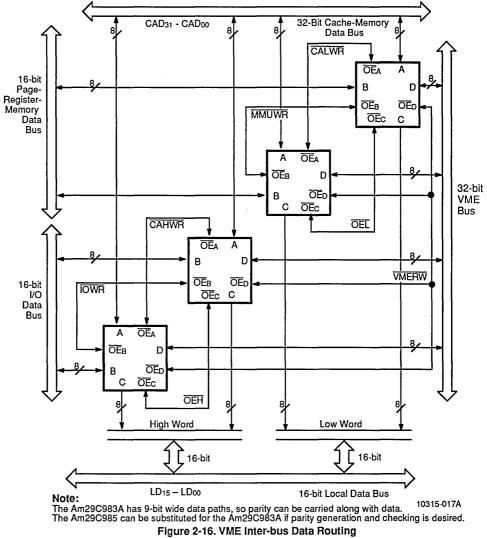

The Am29C983A has 9-bit wide data paths, so parity can be carried along with data. The Am29C985 can be substituted for the Am29C983A if parity generation and checking is desired.

Figure 2–7. 2-Way Interleaved Memory System with Cache

#### Interleaved Data/Instruction Memory (RISC Memory System)

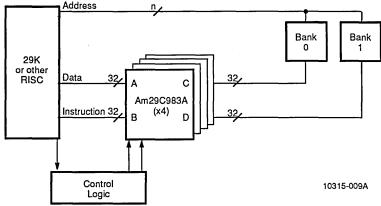

The key feature to the Harvard Architecture, on which the Am29000<sup>TM</sup> device and many other RISC microprocessors are based, is the utilization of separate data and instruction buses. Since parallel data and instruction routing is desired, the system designer will also prefer or require separate memory banks. However, some circumstances will require the data bus to have access to either memory bank. The Am29C983A enables such an access to occur with minimal logical overhead.

Figure 2–8 demonstrates the Am29C983A providing the data flow path between the Am29000 or other Harvard Architecture processor and interleaved data and instruction memory banks. Posted-write operations can be performed by latching in the data then sending a /Ready signal to the processor. The processor can then proceed to its next operation without waiting for the write cycle to be completed.

The MBE also allows access to the Instruction Bus via the Data Bus. This is desirable on systems which have the instruction code stored in volatile memory, as the code may need to be loaded into the data memory at power-up.

The Am29C983A has 9-bit wide data paths, so parity can be carried along with data. The Am29C985 can be substituted for the Am29C983A if parity generation and checking is desired.

#### Figure 2–8. Interleaved Data/Instruction Memory (RISC Memory System)

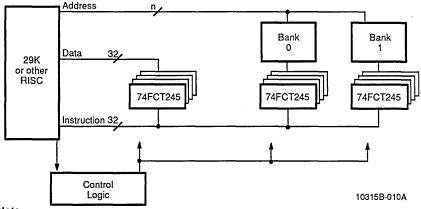

Bank interleaving can also be performed by using buffers, as demonstrated in Figure 2–9. The buffer design adds additional delay while data propagates through the buffers connecting the Data and Instruction buses. This forces the user to add one wait state to all data accesses, as invariably, the speed of the memory is chosen to match the instruction path and not the data path. Posted-write operations cannot be performed with this application; therefore, system performance will be limited.

Note:

This application cannot perform posted-write operations.

Figure 2–9. Interleaved Data/Instruction Memory using 7ns Buffers (RISC Memory System)

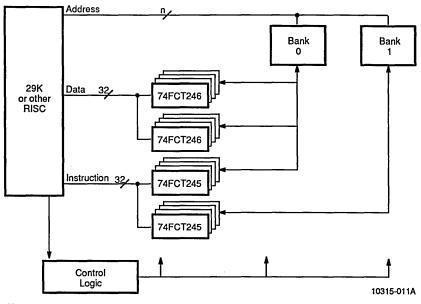

If posted-write operations are required, one could use buffers and transceiver/registers to complete the design, as shown if Figure 2–10. The data path will now incorporate 11 ns transceiver/registers in order to latch the data to be written to memory. Once again, a /Ready signal will inform the processor that it can proceed to its next operation. The propagation delay of accessing the Instruction bus via the Data bus will now climb to 18ns. Additional board space will be lost due to the 16 discrete devices and additional logic control requirements.

This application requires 19 ns delay time (Buffer + Transceiver/Register) to access the instruction via the data bus.

#### Figure 2–10. Interleaved Data/Instruction Memory using 7ns Buffers and 9ns Transceiver/Registers (RISC Memory System)

Tables 2–1 thru 2–6 calculate the memory access times allotted for the Am29C983A, 7 ns buffer and 7 ns buffer with 11 ns transceiver/register designs. This data is duplicated for 7.5 ns and 5 ns PAL control logic. The Am29C983A propagation delay (11 ns) is calculated from Select In to Port. Two buffer propagation delays (14 ns total) must be used in the buffer application in order not to add an extra wait state on data accesses. Only the transceiver/register propagation delay (11 ns) is used for the third design because data access times are being measured. Note that the buffer with transceiver/register design will require an additional 7 nanoseconds when accessing the Instruction bus via the Data bus.

All accesses are based on the following equation:

$t_{acc} = 2t_{cyc} - t_{add} - t_{pd} - t_{su}$

| where | tacc | = Allotted memory access time                |

|-------|------|----------------------------------------------|

|       | tcyc | = Processor cycle time                       |

|       | tadd | = Address valid delay (PAL tco)              |

|       | tpd  | <ul> <li>Buffer propagation delay</li> </ul> |

|       | tsu  | = Am29000 Processor Data/Instr setup         |

#### Table 2–1. Am29C983As and 7.5ns PALs

| Parameter | 33MHz | 25MHz | 20MHz | 16MHz |

|-----------|-------|-------|-------|-------|

| tcyc      | 30    | 40    | 50    | 62.5  |

| tadd      | 6.5   | 6.5   | 6.5   | 6.5   |

| tpd       | 11    | 11    | 11    | 11    |

| tsu       | 4     | 6     | 8     | 8     |

| tacc      | 38.5  | 56.5  | 74.5  | 99.5  |

| Table 2–2. | 7 ns Buf | fers and ' | 7.5 ns | PALS |

|------------|----------|------------|--------|------|

|------------|----------|------------|--------|------|

| Parameter | 33MHz | 25MHz | 20MHz | 16MHz |

|-----------|-------|-------|-------|-------|

| tcyc      | 30    | 40    | 50    | 62.5  |

| tadd      | 6.5   | 6.5   | 6.5   | 6.5   |

| tpd       | 14    | 14    | 14    | 14    |

| tsu       | 4     | 6     | 8     | 8     |

| tacc      | 35.5  | 53.5  | 71.5  | 96.5  |

| Parameter        | 33MHz | 25MHz | 20MHz | 16MHz |

|------------------|-------|-------|-------|-------|

| t <sub>cyc</sub> | 30    | 40    | 50    | 62.5  |

| tadd             | 6.5   | 6.5   | 6.5   | 6.5   |

| tpd              | 11    | 11    | 11    | 11    |

| tsu              | 4     | 6     | 8     | 8     |

| tacc             | 38.5  | 56.5  | 74.5  | 99.5  |

Table 2-4. Am29C983As and 5 ns PALs

| Parameter | 33MHz | 25MHz | 20MHz | 16MHz |

|-----------|-------|-------|-------|-------|

| tcyc      | 30    | 40    | 50    | 62.5  |

| tadd      | 4     | 4     | 4     | 4     |

| tpd       | 11    | 11    | 11    | 11    |

| tsu       | 4     | 6     | 8     | 8     |

| tacc      | 41    | 59    | 77    | 102   |

#### Table 2–5. 7 ns Buffers and 5ns PALs

| Parameter | 33MHz | 25MHz | 20MHz | 16MHz |

|-----------|-------|-------|-------|-------|

| tcyc      | 30    | 40    | 50    | 62.5  |

| tadd      | 4     | 4     | 4     | 4     |

| tpd       | 14    | 14    | 14    | 14    |

| tsu       | 4     | 6     | 8     | 8     |

| tacc      | 38    | 56    | 74    | 99    |

|                  | •     |       | -     |       |

|------------------|-------|-------|-------|-------|

| Parameter        | 33MHz | 25MHz | 20MHz | 16MHz |

| t <sub>cyc</sub> | 30    | 40    | 50    | 62.5  |

| tadd             | 4     | 4     | 4     | 4     |

| tpd              | 11    | 11    | 11    | 11    |

| tsu              | 4     | 6     | 8     | 8     |

| tacc             | 41    | 59    | 77    | 102   |

#### DATA ROUTING APPLICATIONS

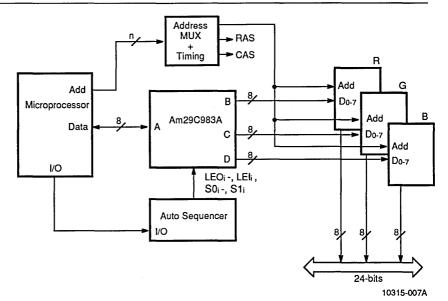

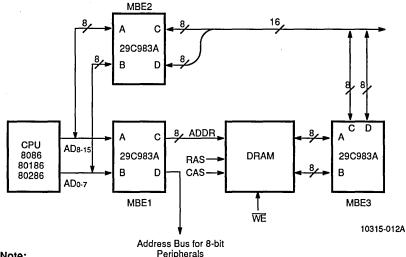

This application illustrates the use of matched port decoding and Input/Output latches of the Am29C983A Multiple Bus Exchange in a simple yet powerful microprocessor-to-DRAM interface (see Figure 2-11).

MBE1 is used as an address latch to capture the 16-bit address into the A and B port input latches from the multiplexed address/data bus. It multiplexes upper and lower bytes of the address to directly drive the DRAM array. MBE2 is configured as an 18-bit wide bidirectional latch to drive the Am29C983A (MBE3) configured as another bidirectional latch for isolation from data bus activity.

#### Note:

The Am29C983A has 9-bit wide data paths, so parity can be carried along with data. The Am29C985 can be substituted for the Am29C983A if parity generation and checking is desired.

Figure 2–11. Microprocessor-Memory Interface

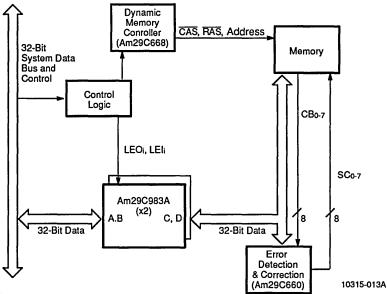

#### Microprocessor-Memory with EDC Interface

As memory size and density increase, protecting your memory from soft errors becomes more and more important. Error Detection and Correction (EDC) circuitry can correct random single-bit soft errors and detect all double-bit and some triple-bit errors. When a word is accessed from memory, it is checked for errors and if an error is found, the corrected data is written back to memory as well as to the data bus. Memory "scrubbing," which is the detection and correction of single-bit errors during normal refresh cycles, allows the system to maintain memory integrity without interrupting the microprocessor.

One complication associated with Error Detection and Correction is the increased data routing necessary to communicate between the microprocessor, dynamic memory controller, EDC and memory. This function can be simplified by using the Am29C983A to latch and drive data between the devices.

During write sequences, data is latched into the Am29C983As then driven to the EDC and memory. The EDC then generates checkbits and sends them directly to memory.

During a memory read, data is sent to the EDC and MBE simultaneously. The MBE routes the data to the system bus. If an error occurs, a Read/Modify/Write cycle is enacted. The EDC detects the error and sends an error message to the control logic. The EDC corrects the data, which is then rerouted to the system bus via the MBE. The control logic delays sending the READY signal to the microprocessor until the corrected data has been sent.

During memory scrub routines, the EDC performs a Read/Modify/Write cycle and writes directly to the memory.

#### Note:

The Am29C983A has 9-bit wide data paths, so parity can be carried along with data. The Am29C985 can be substituted for the Am29C983A if parity generation and checking is desired.

#### Figure 2–12. Microprocessor-Memory with EDC Interface

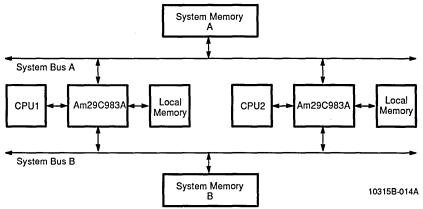

#### Multiprocessing

The logical cross-point interconnect provided by the Am29C983A is ideal for many types of multiprocessor systems. The ability of any port to drive any other port or combination of ports permits the simultaneous updating of both system (global) and cache (local) memories. Alternatively, data from one system bus can be driven onto the other system bus while the CPU communicates with its local memory. Since the Multiple Bus Exchange cascades directly bit-wise, data paths of any width are easily accommodated, with no performance degradation, by merely tying corresponding port-select pins together. The 48-mA drive (loc) capability permits driving the system buses directly, saving board area and reducing system cost.

#### Note:

The Am29C983A has 9-bit wide data paths, so parity can be carried along with data. The Am29C985 can be substituted for the Am29C983A if parity generation and checking is desired.

#### Figure 2–13. Multiprocessing Application

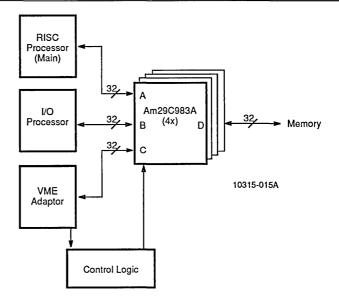

Many applications have evolved to the point that multiprocessing has become the status quo. Workstation motherboard designs, as in Figure 2–14, are one such example. This application divides the processing workload across three microprocessors. The RISC processor operates as the central processing unit, the I/O processor manipulates and distributes data to and from the peripherals and the VME Adaptor controller manages all data distributed to and from the network.

The Am29C983A has 9-bit wide data paths, so parity can be carried along with data. The Am29C985 can be substituted for the Am29C983A if parity generation and checking is desired.

#### Figure 2–14. Workstation Design Using Multiple Processors

#### **Byte Data Swapping**

The Am29C982 can be used to shuffle, swap, or align data paths for a variety of computational and interface applications. For example, upper and lower bytes can be swapped, bidirectionally, to interface systems with different data format requirements. Bidirectional bit-order reversal is easily handled by wiring up the bits in proper order.

Computational applications include FFTs and other forms of array processing. The 14-ns maximum port-to-port propagation delay allows stacking of parts to achieve more complex forms of interconnect at reasonable performance levels. The port-to-port and control-to-port delays are closely matched, further easing the task of dynamic datapath switching.

#### **VME System Interface**

The VMEbus<sup>TM</sup> was developed by Motorola, in association with other companies, to provide an open architecture. The VMEbus offers 8-, 16-, or 32-bit data and 16-, 24-, or 32-bit addressing and a 40 MByte/s bandwidth. Numerous products are offered for use with the VMEbus, including almost all processors, memories and memory boards, controllers, error-detection and correction circuits, and other support products.

The following application connects a 32-bit VME data bus to other 32- and 16-bit buses.

In this application, four Am29C983As provide data routing between the 32-bit VME Data Bus, the 32-bit Cache-Memory Data Bus, the 16-bit I/O Data Bus, the 16-bit Page-Register-Memory Data Bus and the 16-bit Local Data Bus.

The MBEs' input and output latches support the VME address pipeline mode. The Am29C983As' 48mA drive and voltage clamps allow direct drive of the VME and interconnected data buses. The MBEs also provide data funneling capabilities necessary for transferring 32-bit data to the 16-bit Local Data Bus.

#### **Networking Applications**

#### Non-Blocking Digital PBX or Matrix Switching Applications

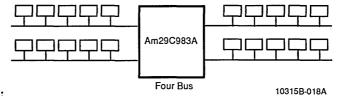

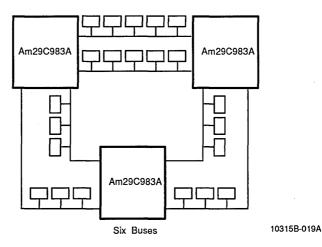

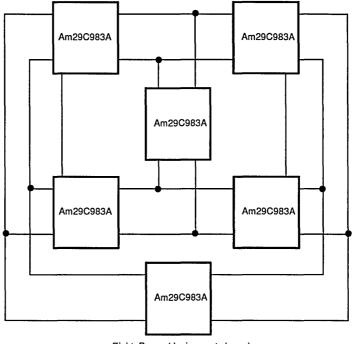

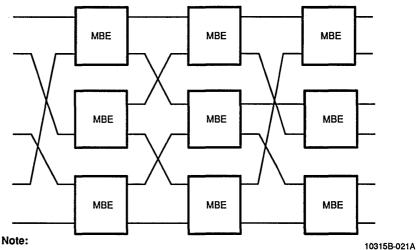

Figures 2-17, 2-18 and 2-19 demonstrate 4-, 6- and 8-bus matrix switching techniques useful in non-blocking PBX or other network applications. This architecture greatly simplifies the PBX design by not only integrating the latches and buffers at each crosspoint switch function, but also by reducing overall control logic requirements.

#### Note:

Note:

The Am29C983A has 9-bit wide data paths, so parity can be carried along with data. The Am29C985 can be substituted for the Am29C983A if parity generation and checking

Figure 2–17. Four-Bus Non-Blocking Digital PBX or Matrix Switch

The Am29C983A has 9-bit wide data paths, so parity can be carried along with data. The Am29C985 can be substituted for the Am29C983A if parity generation and checking is desired.

Figure 2–18. Six-Bus Non-Blocking Digital PBX or Matrix Switch

is desired.

Eight Buses (devices not shown)

10315B-020A

#### Note:

The Am29C983A has 9-bit wide data paths, so parity can be carried along with data. The Am29C985 can be substituted for the Am29C983A if parity generation and checking is desired.

Figure 2–19. 8-Bus Non-Blocking Digital PBX or Matrix Switch

#### **Bidirectional Wideband Network Switching Applications**

Figure 2–20 presents a bidirectional wideband network switching application in which the six 9-bit input channels can communicate with any of six output channels, or any one of six input channels can broadcast to from one to all six output channels, or any combination of the above using both selective channel and broadcast communication techniques.

The Am29C983A has 9-bit wide data paths, so parity can be carried along with data. Figure 2–20. Bidirectional Switching Network

#### **Packet Switching Ring Network Node**

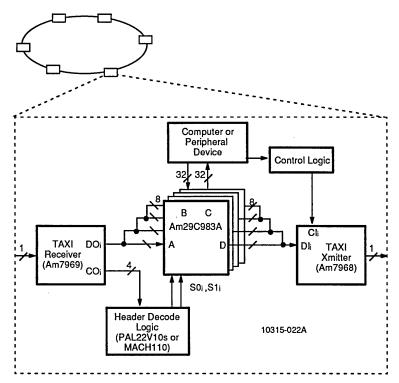

A packet switching ring network allows data to be shared among any computer or peripheral connected to the network. The ring network sends serial data in "packets" which consist of header information and data. The header information informs each node whether it should receive the data or allow the data to pass to the next node.

One can design a high-speed ring network by implementing AMD's TAXI chipset, the Am29C983A MBEs and header decode logic (see Figure 2–21). The TAXI chipset performs high-speed (125-175 MHz) node-to-node transfers, the Header Decode Logic controls the Am29C983A data paths, and the MBE is used as the network node switch and driver.

Data packets designated for the node are routed from Port A to Port C. Empty packets loaded at the node for other nodal destinations are routed from Port B to Port D. Information not intended for this node is passed through from Port A to Port D.

The header information is decoded by a state machine and is then address matched to the node address. If no match occurs, the data is passed onto the next node. The state machine can be implemented with AmPAL22V10s, or one high density MACH110. The addresses can be easily compared by using a content addressable memory, such as the Am99C10.

#### Note:

The Am29C983A has 9-bit wide data paths, so parity can be carried along with data. The Am29C985 can be substituted for the Am29C983A if parity generation and checking is desired.

#### Figure 2–21. Packet Switching Ring Network Node

#### **Ethernet Bridge**

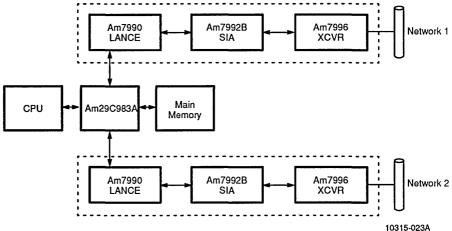

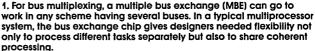

In this communications application, the Am29C983A serves as the link between two networks, accommodating simultaneous bidirectional data transfers: network to network, network to buffer memory, CPU to network, or CPU to buffer memory. The true logical crosspoint interconnect permits any two operations to occur simultaneously, or permits the broadcast of data from any one port to any or all of the other three ports.

Figure 2–22. Ethernet Bridge Application

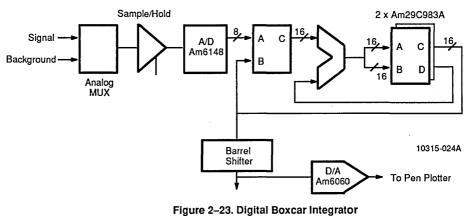

#### **Digital Boxcar Integrator**

This application illustrates use of the Am29C983A Multiple Bus Exchange (MBE) in a digital "boxcar" integrator. The integrator uses repetitive sampling and a background subtraction scheme to obtain accurate readings of periodic signals in the presence of noise (see Figure 2–23).

The Am29C983A MBEs are used to route and store a running sum of digitized data, signal as well as background. B port input latches can be used for signal, and A port input latches for background. Successive summation is performed by routing A port or latch data to the D port. Background subtraction is performed by connecting the A port to the C port, and the B port to the D port, and routing C port data to the ALU via the 2-to-1 multiplexer. The result is then routed via the C port of the Am29C983A MBE to the barrel shifter for integer division to convert running sums to averages. The output of the barrel shifter can be used to drive an output device, such as a pen plotter, after D/A conversion.

## DESIGN INNOVATION

# Multiple-bus exchange ICs speed interbus communications

Two chips replace 28 discrete components to build a four-port crosspoint switch, 4 or 9 bits wide, for transferring data between four buses.

#### NICOLAS MOKHOFF

To link various system elements, traditional interface devices typically deal only with such circuit parameters as volts, milliamps, and nanoseconds. But this scenario overlooks managing interconnections efficiently. Now that picture has changed: With a couple of crosspoint IC switches, a system designer can dynamically manage the interconnection of system elements in multiprocessor, shared-resource, and computational applications.

The Am29C982 and Am29C983 multiple bus exchange (MBE) ICs replace 14 and 28 discrete devices, respectively. Each constructs a four-port crosspoint switch 4 or 9 bits wide. The switching function is a logical one instead of a direct physical connection between input and output ports. The two ICs can be applied to any bus-based digital system to switch data between up to four buses.

Most current digital systems are organized by bus, with data shuttling between sources and sinks over a common data highway. Such systems, though managing connectors and the number of wires efficiently, still are time-division multiplexed under strict rules. Such rules govern bus arbitration to determine which data source wins the right to talk and the length of time that source may occupy the bus. As long as one source transmits data over the bus, no others can. Because only one transfer can take place at time, interconnection efficiency comes at the expense of throughput.

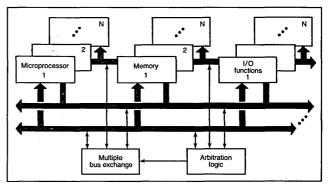

For its part, throughput can be improved by adding more buses to allow more than one transfer to occur at one time. Without communication between buses, however, the result is essentially separate processing of different tasks, rather than coherent shared processing of one overall task. To achieve coherency, the task of the multiple bus exchange chips is to tie all buses together (Fig. 1).

One way to improve coherency is to rely on discrete components such as several bus interface devices and the required SSI/MSI glue logic. The number of discrete elements depends upon the number of buses to be switched, the number of ports, and the width of each port. This solution, though, consumes much board space and hampers throughput.

Or designers can opt for a custom gate array, which is costly and detracts from flexibility. On top of this, a typical gate-array scheme cannot drive high-capacitance loads.

"The Am29C982 and the Am29C983 offer a superior alternative to the discrete as well as gate array implementations of a bus multiplexing scheme," says Roy Sellinger, manager of directorate marketing. "By using AMD's state-ofthe-art CMOS technology and a clever bus-selection coding scheme, the discrete functional blocks are integrated to offer a flexible and highspeed solution at very low standby power dissipation for a board spacesaving of up to 80%."

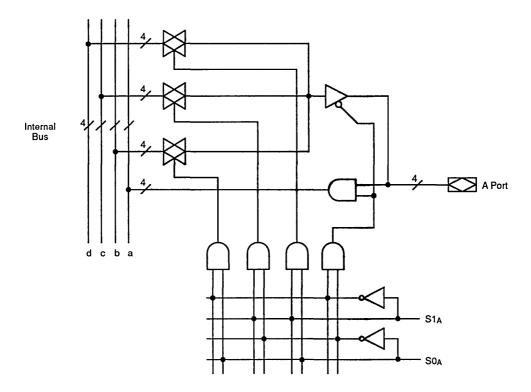

The ICs share a similar structure. The input for each port (either 4 or 9

bits wide) is buffered and distributed along an internal bus to multiplexers at each of the other ports on the Am29C982 or at all the ports on the Am29C983. Port selection is independent for each port.

A common coding rule for all ports specifies that the 2-bit port select code asserted at each port must always refer to the source of data. This independent matched-port selection simplifies using the buses and avoids the decoding delays inherent in a centralized, encoded port-selection scheme.

On one hand, if the D port has 00 asserted, then the source data is the "A" port. On the other hand, if the A port has 00 asserted, then the A port is the source of data. For the Am29C982, a port selecting itself means that the port is an input and that the drivers are internally gated to a high-impedance state.

For the Am29C983, the Output Enable signal for each port is brought out to the user so that a port may select itself and store data in the port's output latch, for later transmission back out on the same bus. This readback facility is useful for diagnostics, in which a bus connected to one port can send data to any or all of the other ports and read back from its own port the data that was sent.

The two CMOS devices can drive 48 mA and exhibit typical propagation delays of 9 ns from port to port and 10 ns from control to port. Bus Disable times are shorter than Bus Enable times to avoid contention and minimize system noise. The Am29C982 chip has two power and two ground pins to support a maximum of 12 outputs switching simultaneously from the 16 inputs available. In comparison, the Am29C983 IC has four power and eight ground pins, resulting in one power and two ground pins per port. The drivers in both devices use AMD's proprietary edge-rate control circuitry to minimize the effects of ground balance.

#### MANY APPLICATIONS

The logical crosspoint interconnection supplied by the multiple bus exchange chip fits many multiprocessor configurations. In one such system either of the two chips serves

In a typical communication task, the multiple bus exchange links two Ethernets, for example. With the bus exchange's true logical crosspoint interconnection, two operations can occur simultaneously, or data can be broadcast from any one port to any or all of the other three ports.

to update simultaneously both system (global) and cache (local) memories.

Or data from one system bus can be driven onto the other system bus while the CPU communicates with the local memory. Because multiple bus exchange chips can be cascaded directly in terms of bits, data paths of any width are easily accommodated without sacrificing performance by simply tying the corresponding port select pins together. The 48-mA output capability allows driving the system buses directly, saving board area and reducing system cost.

In a multiprocessing system with multiple access memories, for instance, two Am29C983s can latch up to three sources of addresses while also performing the address multiplexing necessary for row address and column address selection. On the data side, the two chips can deliver bidirectional multiplexing between dynamic RAM memory and any or all of the available processor buses.

In a communication task, the multiple bus exchange chip links two networks, accommodating simultaneous bidirectional data transfers in one of many configurations: network-to-network, network-to-buffer memory, CPU-tonetwork, or CPU-to-buffer memory (*Fig. 2*). The true logical crosspoint interconnection allows any two operations to occur simultaneously; or data can be broadcast from any one port to any or all the other three ports.

The chip can also help shuffle, swap, or align data paths for various interface and computational applications. For example, upper and lower bytes can be swapped bidirectionally to link systems with different data format requirements. Bidirectional bit-order reversal is easily handled by wiring up the bits in broper order.

Some computational applications that can be handled by the multiple

bus exchange include fast Fourier transforms (FFTs) and other forms of array processing that require dynamic switching of data paths. With the 14-ns port-to-port propagation delay, parts can be stacked for more complex interconnections while maintaining reasonable system performance.

Although originally intended to take on multiprocessor applications, the multiple bus exchange chip can also stand in for more conventional interface parts. For example, by hard-wiring the Port Select pins so that each port receives data from the complement of that port (A-D, D-A, B-C, and C-B) and connecting A and B as well as C and D Output Enables, the Am29C983 functions as an 18-bit-wide bus transceiver.

And by using the output Latch Enable pins, the chip works as an 18-bit-wide bidirectional register. As a result, two chips, occupying 2 in.<sup>2</sup> of board space, along with just two inverters, constitute a 36-bit-wide bidirectional register that can drive a bus and meet the data-path requirements of 32-bit buses with byte parity.

# Д

### CHAPTER 3 Design Methodology

| Introduction                                                   | 3–2 |

|----------------------------------------------------------------|-----|

| Minimization of Ground Bounce Through Output Edge-Rate Control | 3–3 |

### INTRODUCTION

This chapter includes an application note describing AMD's proprietary output structure which minimizes ground-bounce by controlling output edge-rates. The application note assesses ideal drivers and recommends real world solutions to reduce ground bounce and system noise. All members of the Multiple Bus Exchange Family incorporate these system friendly output structures.

### Minimization of Ground Bounce Through Output Edge-Rate Control

The development of fast, high-current integrated circuits has brought about a phenomenon known as ground bounce. This is especially noticeable in bus-driving applications, where individual devices can have multiple outputs switching very high currents simultaneously.

There are three symptoms associated with the phenomenon:

- Outputs switching from HIGH-to-LOW exhibit excessive ringing, which may cause multiple transitions at inputs connected to that output.

- The ringing also appears at non-switching outputs which are in the LOW state. This may also cause unwanted transitions at inputs connected to those outputs.

- If the device contains storage elements, the ringing may corrupt the data stored in these elements.

Ground bounce is associated with parasitic inductance and resistance in the power-supply connections. These parasitic effects exist within all integrated circuits and may not totally be eliminated. Poor board design will also contribute to the problem. The following discussion covers the cause of ground bounce in CMOS circuits, and describes AMD's output-driver circuit design that minimizes the problem. Accompanying photographs show an example of the driver in operation.

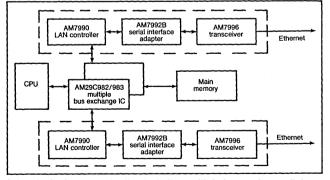

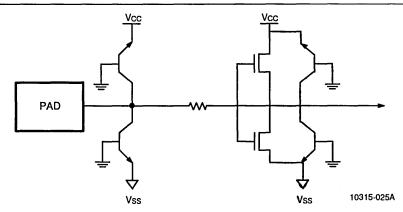

### THE IDEAL DRIVER

Figure 1 shows an ideal totem-pole output driver. The two transistors are switched on alternately, the upper one for a logic '1', and the lower one for a logic '0'. Apart from a brief period of overlap during switching, the two transistors are never on together. For the high-impedance state of 3-state outputs, both transistors are turned off. The load connected to the totem-pole output is adequately modeled as a parallel R-C circuit.

Figure 1. Ideal Driver

While this is an ideal driver, it is not constructed with ideal transistors. Each transistor has a finite impedance when in the 'on' state. This impedance manifests itself in three ways; it affects the slew rate of the output, the dc level of the output, and it limits the short-circuit current.

Before a transition, the load capacitor is charged according to the current output state ('0' or '1'). When the output transistors switch, they charge or discharge the load capacitor, and their impedance is part of the R-C time constant, which determines the slew rate of the output. In this respect, lower impedance is better. With a lower impedance, the load capacitance can be charged or discharged to the required output level faster, thus permitting higher operating speeds.

When the output voltage has stabilized at the desired logic level, the dc current flowing through the transistor impedance creates a residual voltage across the transistor (I-R drop). The output voltage specifications require that this residual voltage be kept below maximum values ( $V_{cl}$ ). Again, a lower impedance is better, allowing higher output currents at any given  $V_{cl}$ .

However, even in the ideal case, the impedances should not be arbitrarily small, since they also control short-circuit current. If an output is inadvertently connected to one of the power supplies, or to a second output in a different state, these impedances will limit the power dissipation in the device and prevent potential destruction.

It would appear that the optimum design would be to make the impedance just large enough to protect the device under short-circuit conditions, while maximizing slew-rate and drive capability. This assumes that die area is not a consideration, since low impedance transistors are physically large. However, in the real world, parasitic effects cause this choice to lead to far from optimum results.

### THE REAL WORLD

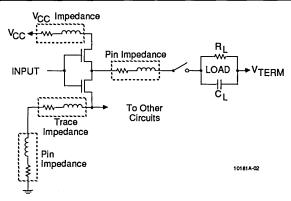

The practical problems that arise concern parasitic effects in the connections to the transistors. Between the output of the driver and the load, there is a small bond wire and a trace from the package bonding pad to the external pin. These connections are both resistive and inductive.

A similar parasitic impedance is also found in the ground pin of the device. Additionally, it is not possible to locate all outputs physically close to the ground connection on the die. The deposited metal trace that connects the output driver to the ground pad also contributes parasitic resistance and inductance.

In the circuit of Figure 2, only effects in the ground connections are shown. Similar parasitics must exist in the  $V_{cc}$  connections but, since requirements for  $V_{OH}$  are less demanding, higher-impedance pull-up transistors can be used. This reduces the effect of the parasitic impedance. Experience has shown the problem to be associated with the HIGH-to-LOW transition and outputs in the LOW state, hence the name ground bounce.

Before a HIGH-to-LOW transition, the load capacitor is charged to the HIGH state. During the transition, the pull-up transistor turns 'off' and the pull-down transistor turns 'on' to discharge the load capacitor. The very low impedance of the pull-down transistor causes the parasitic impedances to interact with the load to form a step-excited L-C-R network. This results in ringing on the output.

While the output might quickly reach  $V_{OL}$ , it will not remain there due to the ringing. The output may not be considered a LOW until the output has stabilized to the point that it remains below  $V_{OL}$ . During the ringing, the output could exceed the actual threshold (as opposed to  $V_{IH}$ , the guaranteed input HIGH level) of an input to which it is connected, causing multiple transitions.

Other outputs in the same device may also be affected because the output voltages are referred to the internal device ground. The ringing causes this internal ground to move away from external ground. The other LOW outputs are connected to the internal ground through a low-impedance transistor, and movement in this ground will

therefore be reflected at these outputs. Again, this may lead to erroneous transitions in devices connected to these outputs. In addition, the movement of the internal ground may corrupt data stored in the registers.

At this point it is worth noting a different effect also caused by parasitic impedances in the power connections. In accordance with industry practice, the output delays of AMD parts are measured with only one output switching. When more than one output switches, the impedance in the common power-supply connections reduces the current available to each output, thus increasing the delay. This effect occurs in any integrated circuit.

### THE SOLUTION

The effects of the load capacitance and the interconnection parasitics are inescapable, although the latter may be minimized by good chip design. The solution must lie in modifying the pull-down transistor.

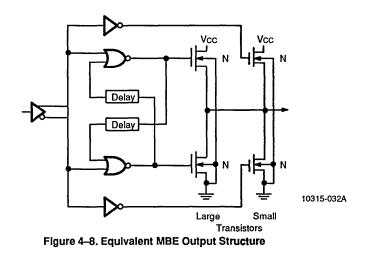

The AMD solution structures the pull-down transistor so it limits the initial current minimizing the transient; then, after a delay, its strength increases to provide sufficient current to maintain the LOW logic level. This is achieved by using two transistors contained in parallel output buffers. These buffers are designed to have different drive capabilities. One has small transistors with low drive which is used to initiate the transition without causing the shock excitation. After a short delay, a second larger driver turns on. This driver completes the transition, and is capable of sinking the necessary dc current to maintain  $V_{OL}$ . Additionally, a similar parallel structure is used in the pull-up circuit to moderate the LOW-to-HIGH transition.

While introducing delay into a high-speed circuit may appear counter productive, that is not the case. The primary objective must be to achieve a stable output

Figure 2. Real Driver and Parasitics

voltage level less than  $V_{\mu}$  as quickly as possible. The non-controlled output signal may reach  $V_{\mu}$  sooner, but it will not remain there until the ringing has subsided. This may require more time than the specified output delay, and a good design must allow for this. The modified AMD output will provide a stable, usable voltage level in less time in spite of the added delay.

A secondary effect of limiting the current during transition is that the slew rate is controlled by the driver rather than power-supply parasitics. This generally leads to less delay variations (skew) caused by a different number of switching outputs.

### TEST RESULTS

The output driver described above has been incorporated into the Am29C982 4-bit x 4-port Multiple Bus Exchange. This product was mounted in a test jig and its output characteristics photographed. For comparison, a similar test jig was used to test an Am29C821 10-bit register, with traditional 24 mA totem-pole outputs, and a competitive 48 mA output version.

The jigs were designed to eliminate, as far as possible, electrical effects due to the mounting and probing so that intrinsic characteristics of the IC could be observed. It should be noted that the layout and dc loading found on a carefully designed pc board could lower the current transient and its effects. In that respect the following results should be considered worst case.

The test jigs were constructed of double-sided copperclad board. The two copper planes were used for V<sub>cc</sub> and GND. Holes were drilled to accept the ICs, and only sufficient copper was cut away to allow clearance of active pins. The ICs were soldered directly into this board. Decoupling was provided by a tantalum capacitor, and a .01  $\mu$ F ceramic capacitor mounted close to the V<sub>cc</sub> pin.

Each output was loaded with 47 pF to GND. The leads of this capacitor were cropped short, and the capacitor was soldered directly to the IC pin and the ground plane. Outputs to be observed were connected to SMB sockets through 453  $\Omega$  resistors. Each series resistor, together with a 50  $\Omega$  oscilloscope input impedance, creates a standard 500  $\Omega$  load. The leads of each resistor were cropped short and soldered directly to the IC pin and the socket. The socket body was soldered to the ground plane.

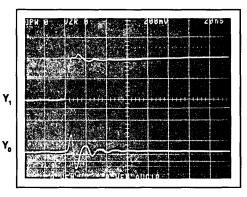

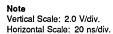

These SMB sockets were connected by coax to the 50  $\Omega$  oscilloscope input (Tektronix 7854 with 7S14 sampling input plug-in). The series resistance creates an attenuation of 10:1. The vertical scale is 2 V/div, and the horizontal scale is 20 ns/div.

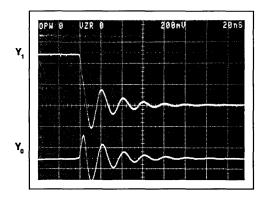

On the Am29C821, input  $D_0$  was grounded to provide a "quiet" output  $Y_0$ .  $Y_0$  was chosen, because it is farthest from the ground pin, and therefore, most susceptible to noise in the supply. Inputs  $D_{1,9}$  were all connected to output  $Y_0$  through a single inverter. The device was then clocked, such that the nine outputs  $(Y_{1,9})$  toggled simultaneously.

Photograph 1 shows the outputs  $Y_0$  and  $Y_1$  during a HIGH-to-LOW transition. The quiet output  $(Y_0)$  "bounces" approximately 2.2 V. The maximum positive ringing in  $Y_1$  is approximately 1.5 V. Observation of the transition on the  $Y_0$  output, which is closer to the GND pin, revealed slightly less ringing.

It should be noted that the capacitive loading of the quiet output reduces the initial transient slope and slightly reduces the positive excursion. Since an actual application will present capacitive loading, this test is representative. Without the capacitor, the positive excursion was approximately 0.2 V greater.

Photo 1. Am29C821

Note Vertical Scale: 2.0 V/div. Horizontal Scale: 20 ns/div. Photograph 2 shows the same outputs during a LOW-to-HIGH transition. Here the effect is much less; the excursion of  $Y_0$  is approximately 0.9 V. In this case,  $Y_0$ , which is farther from  $V_{cc}$ , exhibited slightly more ringing.

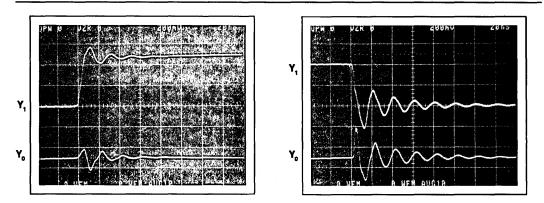

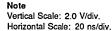

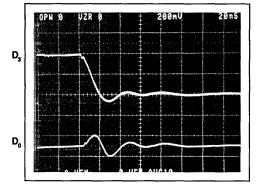

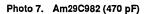

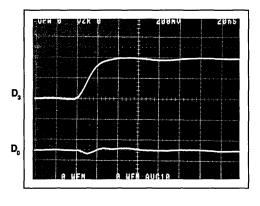

The same tests were performed on a competitor's version of the Am29C821. The results are shown in photographs 3 and 4. As expected, the 48 mA outputs of this part create considerably more noise than the 24 mA outputs of the AMD part.

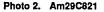

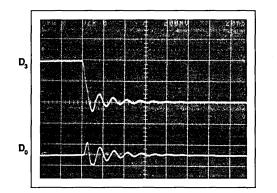

To test the Am29C982 Multiple Bus Exchange, the A-port was configured as an input that was directed to the B-, Cand D-Ports which were outputs.  $A_0$  was grounded, and a square wave was applied to  $A_{1,3}$ . This again gave nine switching outputs and three quiet outputs.

The outputs on  $D_0$  and  $D_3$  are shown in photographs 5 and 6 for HIGH-to-LOW and LOW-to-HIGH transitions respectively. The effect of the modified output driver is quite clear. Both ringing and ground bounce have been reduced dramatically. The maximum ground bounce during the negative transition is approximately 1.1 V, while the positive ringing is limited to approximately 0.8 V. When compared to Am29C800, this represents a 50% reduction in noise, while increasing the output current from 24 mA to 48 mA.

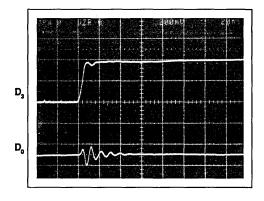

The tests on the Am29C982 were repeated with the load capacitors increased to 470 pF. The results are shown in photographs 7 and 8. The amplitude of the ringing and ground bounce are the same or less than with the 47 pF load. The ringing frequency is predictably lower due to the larger capacitor.

The improved output structure is also used in the Am29C983 9-Bit x 4-Port Multiple Bus Exchange. A more comprehensive analysis of this output transition control technique, including results from additional package options and the AM29C983, are being prepared for future release.

Photo 4. Competitor's C821

While these tests were performed on individual, randomly selected parts, and cannot therefore be considered definitive, they do indicate the effectiveness of the new output structure. It is AMD's intent to incorporate outputs with this improved current characteristic into future bus interface devices.

### **GOOD DESIGN PRACTICE**

Ground bounce cannot be eliminated through good design practice alone. However, the situation can be aggravated considerably by failure to follow good practices. The following guidelines are suggested:

Ensure good power supply connection. Power supply planes are essential, and wire wrap should be avoided. Provide good wide-band decoupling. The ringing occurs at very high frequency, in the gigahertz region. Therefore, a comprehensive decoupling scheme should be designed, including chip capacitors very close to the high-drive devices.

In general, the layout rules followed should be similar to those for ECL. Branching traces should not be used for signals that are to be routed to more than one input. Traces should pass from one input to the next without Ys or Ts. If possible, the traces should have controlled impedance, and should be terminated.

Photo 5. Am29C982

Photo 6. Am29C982

Photo 8. Am29C982 (470 pF)

# ת

### **CHAPTER 4** General Product Information

| Introduction                                                                                                                                                                             | 4–2 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Test Philosophy and Methods<br>ATE Loads<br>Threshold Testing<br>AC Testing<br>Output Short Circuit Current Testing                                                                      | 4–3 |

| Typical Capacitance Values                                                                                                                                                               | 4–4 |

| Device Gate Count                                                                                                                                                                        | 4–4 |

| Package Information                                                                                                                                                                      | 4–4 |

| Die Dimensions                                                                                                                                                                           | 4–4 |

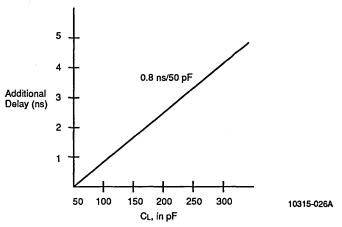

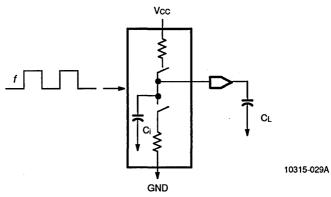

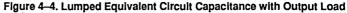

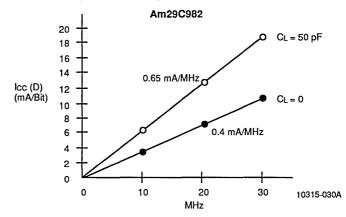

| Typical Switching Speeds vs. Load Capacitance                                                                                                                                            | 44  |