# **Telecommunication Products**

Data Book 1992/1993

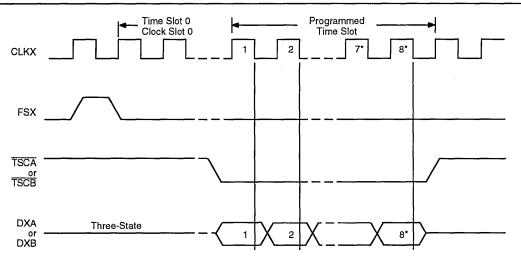

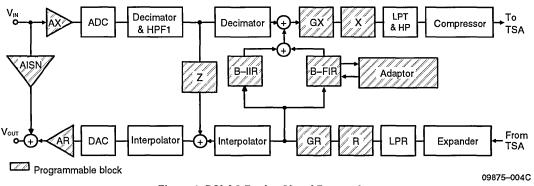

Advanced Micro Devices

AMD's Marketing Communications Department specifies environmentally sound agricultural inks and recycled papers, making this book highly recyclable.

# Telecommunication Products Data Book

1992/1993

© 1992 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD® assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

#### Trademarks

AMD and WORLD-CHIP are registered trademarks of Advanced Micro Devices, Inc. AmSLAC, AmSLAC2, DSLAC, SLAC, Digital Subscriber Controller, Am29000, Am386 are trademarks of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# TELECOMMUNICATION PRODUCTS DATA BOOK 1992/1993 TABLE OF CONTENTS

| Introduction to Telecommunication Produ                                                                          | cts iv                                                      |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Chapter 1                                                                                                        | SLIC PRODUCTS                                               |

| Introduction to SLIC Products Product Selector Guide                                                             | 1-1<br>1-3<br>                                              |

| General Description<br>Am7942 Data Sheet<br>Am7943(A) Data Sheet                                                 | 1-17<br>1-18<br>1-18<br>1-19<br>1-35<br>1-50                |

| General Description<br>Am79530/Am79531/Am79534/Am79535<br>Am79571/Am79573/Am79574 Data Shee<br>Am7958 Data Sheet | 1-55<br>Data Sheet                                          |

| General Description<br>Am79M531/Am79M535 Data Sheet<br>Am79M570/Am79M574 Data Sheet<br>Am79HM53 Data Sheet       | 1-113<br>1-114<br>1-115<br>1-131<br>1-131<br>1-147<br>1-161 |

| SLIC Extended Temperature and Package                                                                            | ing Considerations 1-167                                    |

# Chapter 2

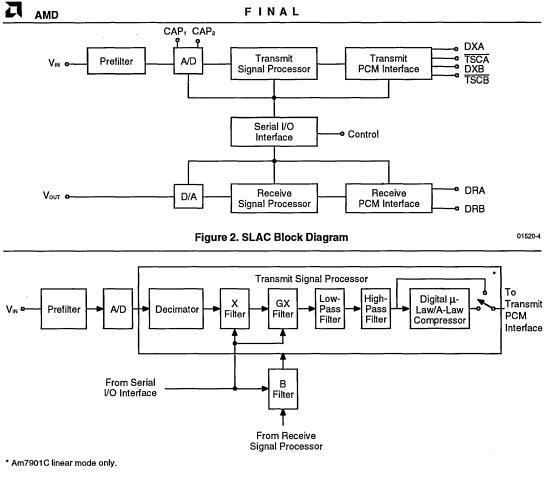

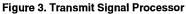

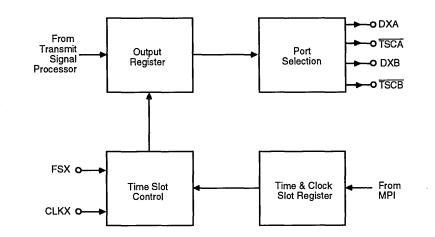

# SLAC/DSLAC PRODUCTS

| Introduction to SLAC/DSLAC Products   | 2-3   |

|---------------------------------------|-------|

| Am7901B/C Data Sheet                  | 2-5   |

| Am7905A Data Sheet                    | 2-37  |

| Am79C02/3(A) Data Sheet               | 2-69  |

| Am79C04(A) Data Sheet                 | 2-113 |

| DSLAC Extended Temperature Supplement | 2-153 |

# Chapter 3

# **ISDN PRODUCTS**

| Introduction to ISDN Products |

|-------------------------------|

| Am79C30A Data Sheet           |

| Am7938 Data Sheet             |

# Chapter 4

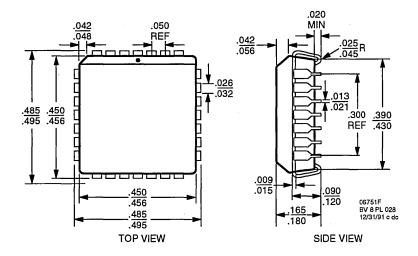

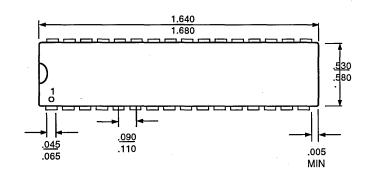

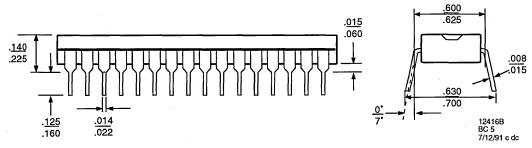

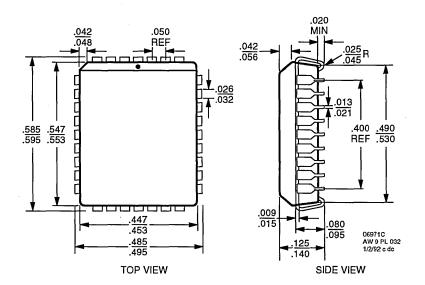

# PHYSICAL DIMENSIONS

| vsical Dimensions |

|-------------------|

|-------------------|

# INTRODUCTION TO TELECOMMUNICATION PRODUCTS

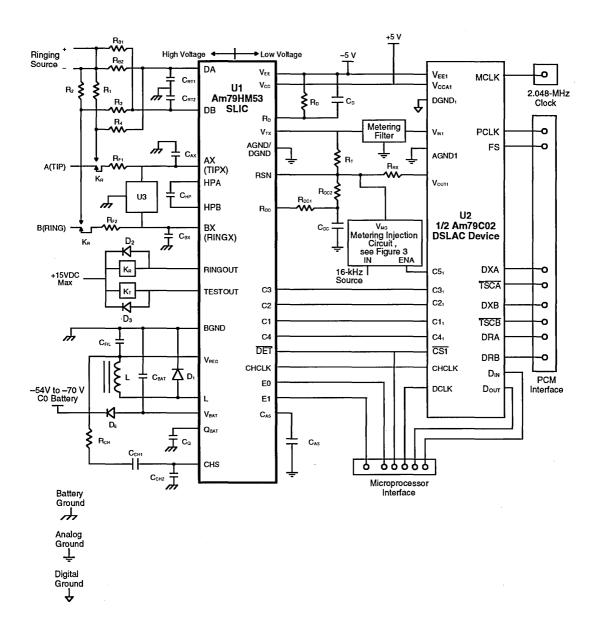

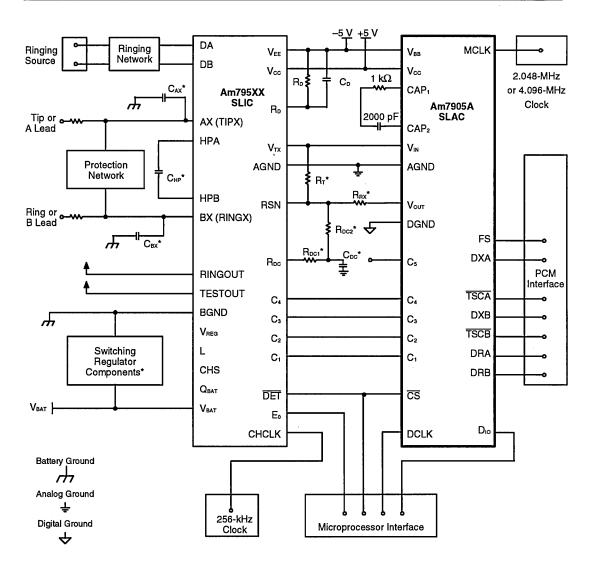

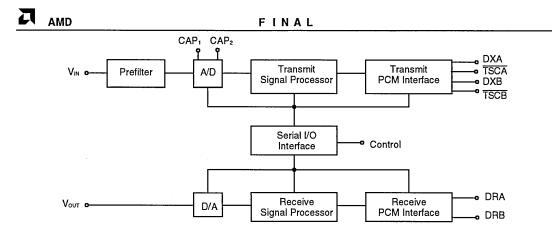

Advanced Micro Devices supplies system solutions for your telecommunications applications. AMD provides customers with the most advanced integrated circuits, together with the software and development tools necessary for keeping pace with the ongoing revolution in telecommunications. AMD telecommunication products support applications ranging from switches for the analog telephone network to terminals for the Integrated Services Digital Network (ISDN).

# **Analog Subscriber Solutions**

AMD has established a leadership position in the telephone switching equipment marketplace with the Subscriber Line Interface Circuit (SLIC) and Subscriber Line Audio-Processing Circuit (SLAC™ and DSLAC™) products. These components are used in telephone Central Office Exchanges and PBXs around the world and are used in some of the most sophisticated Central Office Exchanges available today.

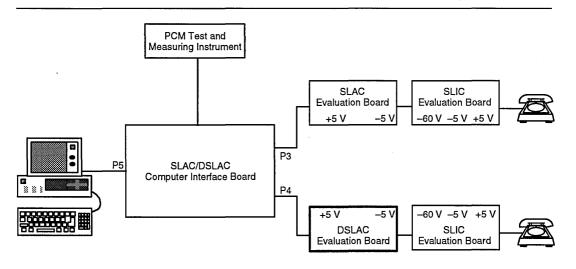

AMD's many evaluation boards, software packages, kits, and extensive documentation allow quick evaluation of the SLIC/SLAC and DSLAC circuit's performance and features, and fast time-to-market for linecard applications.

# **ISDN Solutions**

ISDN is the standard for the conversion of the world telephone network to an integrated, public digital network for both voice and data. ISDN technology is being implemented and tested in many parts of the world, and its use will accelerate as the speed and cost advantages of digital communications become readily apparent. The ISDN network will provide a multitude of new services through simultaneous transmission and reception of voice, data, and video over a common network.

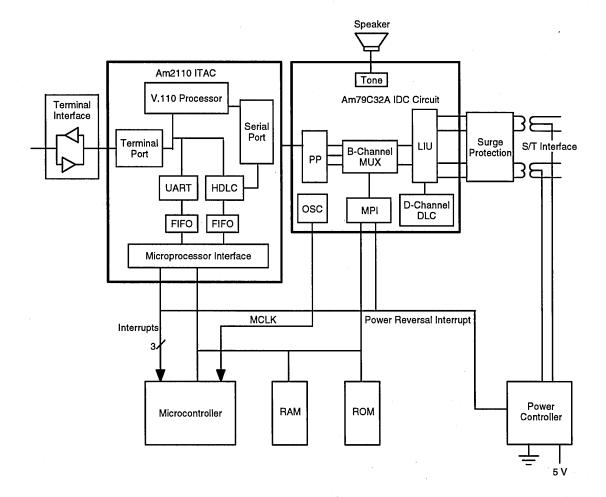

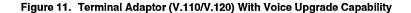

AMD's Am79C30A Digital Subscriber Controller™ ISDN circuit provides maximum functional integration consistent with international standards. It is the world's first ISDN terminal circuit that can be used to build ISDN telephones and terminals that conform to CCITT power specifications. This circuit, combined with EPROM, SRAM, a microcontroller, and a power controller, are all that is needed for a basic CCITT power-compliant telephone or terminal. AMD's ISDN development boards and support software guide the user through each step of the ISDN product development process, significantly reducing time-to-market.

# AMD's Complete Offering

The telecommunication function is just one of the areas where AMD can aid design efforts. AMD is also a leading supplier of programmable logic devices, high-performance memories, the CISC and RISC processors, and related peripherals.

AMD has developed more solutions than anyone else for getting applications to market faster with programmable logic. AMD offers the broadest, best-supplied line of programmable logic devices in the industry.

AMD's total system solution for managing high-performance dynamic memories offers flexibility, integration, and performance with the industries fastest 32- and 16-bit error detection and correction circuits and the most flexible DRAM controllers and drivers. AMD is a pioneer in the field of specialty memory devices with an extensive line of bipolar and CMOS FIFOs. AMD also supplies a broad range of EPROM and SRAM products.

AMD's Embedded Processor Division supplies 8- and 16-bit microcontrollers as well as bit block and field programmable controllers. This group also manufacturers the high-performance Am29000™ Family of 32-bit RISC processors. AMD also offers a line of iAPX microprocessors and related peripherals from the 8088 to the high-performance Am386™ microprocessor.

# Chapter 1

**SLIC Products**

# CHAPTER 1 SLIC Products

| SLIC Products                                          |

|--------------------------------------------------------|

| Introduction to SLIC Products                          |

| Product Selector Guide 1-5                             |

| SLIC Family Functional Description 1-7                 |

| PBX SLICs 1-17                                         |

| General Description                                    |

| Am7942 Data Sheet                                      |

| Am7943(A) Data Sheet                                   |

| Application Notes                                      |

| Central Office SLICs                                   |

| General Description                                    |

| Am79530/Am79531/Am79534/Am79535 Data Sheet             |

| Am79571/Am79573/Am79574 Data Sheet 1-75                |

| Am7958 Data Sheet                                      |

| Application Notes                                      |

| Central Office Metering SLICs 1-113                    |

| General Description                                    |

| Am79M531/Am79M535 Data Sheet 1-115                     |

| Am79M570/Am79M574 Data Sheet 1-131                     |

| Am79HM53 Data Sheet                                    |

| Application Notes                                      |

| SLIC Extended Temperature and Packaging Considerations |

# INTRODUCTION TO SLIC PRODUCTS

AMD's Subscriber Line Interface Circuit (SLIC) products perform the telephone line interface functions required by most types of telephone switching and transmission equipment. In addition to supporting the BORSCHT functions (Battery Feed, Overvoltage protection, Ringing, Supervision, Coding, Hybrid and Test), the AMD SLIC Family offers such features as current limiting, on-hook transmission, polarity reversal, tip-open mode for ground start signaling, ground-key detection, and ground-key filtering.

SLICs optimize linecard costs by minimizing the number of components needed per line, by minimizing the board space requirements, and by supporting automated manufacturing techniques not supported by alternative technologies.

#### SLIC Types

AMD's SLIC products are designed to address a number of different applications including:

- · Central Office Switches,

- Private Branch Exchanges (PBXs) and Key Systems,

- Digital Loop Carriers (DLCs), Multiplexers, Channel Banks, and Fiber-In-The-Loop (FITL) equipment.

SLICs intended primarily for Central Office applications are offered and comply with the most stringent standards set by the CCITT, Bellcore, and/or British Telecom. Central Office SLICs also incorporate a self-adjusting switching regulator to reduce power consumption to a minimum and enhance system reliability. Constant current feed SLICs, constant voltage feed SLICs, and versions of each SLIC that supports metering are offered in a variety of configurations and package types.

AMD also offers SLICs optimized for other switching applications such as PBXs. These SLICs are specified and tested to meet the requirements of both the EIA/TIA-464-A and ETSI TE10–02 PBX standards. They have a wider battery operating range than the Central Office SLICs and will operate with either 24- or 48-V batteries. Also, the switching regulator function is either not offered or is optional, saving the cost of a few external components in applications where power control into short loops is unnecessary.

Both Central Office and PBX SLICs support on-hook transmission and offer extended temperature performance, making either type ideal for Digital Loop Carrier and Multiplexer applications. SLICs from both Central Office and PBX families are offered that comply with Bellcore's TR-TSY-000057 Specification for DLCs, and TR-909 for FITL.

Performance grades are offered for all AMD SLICs that support the various idle channel noise and longitudinal balance specifications worldwide.

#### **SLIC Functions**

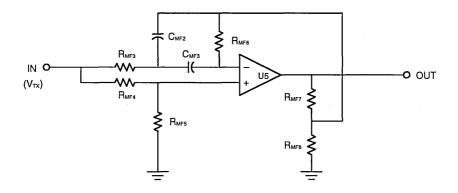

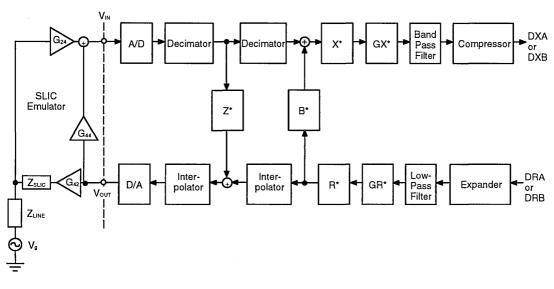

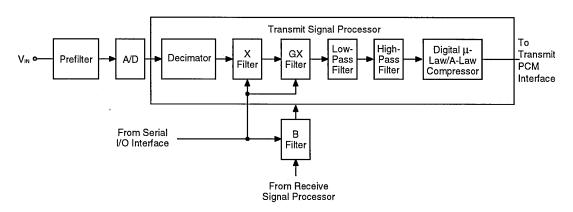

The signal transmission functions of all AMD SLICs include both two-to-four wire and four-to-two wire conversion. The two-wire termination impedance is programmed with a single external impedance. The companion AMD SLAC or DSLAC IC (Single- or Dual-Channel Subscriber Line Audio-Processing Circuit) has a digital balancing filter that provides the trans-hybrid loss function. If the DSLAC device is not used, most codec/filters provide an uncommitted op amp for this purpose.

The SLIC's battery feed architecture makes the DC feed characteristics programmable by external resistors. Furthermore, these characteristics are independent of battery variations. AMD's PBX SLICs can operate from below 24 V to above 48 V, while the Central Office SLICs are optimized for 48-V operation.

A polarity reversal function is provided on most SLICs which transposes the voltage applied to the A(TIP) and B(RING) leads with a controlled transition time. All transmission functions continue normally following the transition. A disable mode is also provided, limiting loop current and cutting power dissipation while allowing the full complement of supervisory functions to be utilized.

The supervisory functions of off-hook detection and ring-trip detection are read through a single, TTL-compatible output. To eliminate noise-induced errors, the off-hook signal may be filtered before being detected. Off-hook detection has a threshold that is set by the value of an external resistor. Additional supervisory controls put the A lead into an open circuit (high impedance) state suitable for application in ground-start systems. Similarly, both the A and B leads may be open circuited to clear relays, recover from line faults, or turn off out-of-service lines. Two relay drivers support ring and test relay functions, or can be used for other functions such as a message-waiting lamp.

The SLIC's user-programmable states are controlled by a TTL-compatible code. The control inputs are designed to easily interface to popular single-chip microcontrollers, such as the industry standard 8051, or to latched outputs from a SLAC or DSLAC device.

# PRODUCT SELECTOR GUIDE

The following selector chart shows the most commonly used AMD SLIC types offered at the time of publication. SLIC part numbers are shown at the top of the chart and are referenced to the principal SLIC characteristics and features on the left. Use this selection chart to identify a SLIC that meets the general needs of a specific application, then turn to the appropriate data sheet for detailed information. If there is no SLIC that meets these specific requirements, contact the local AMD sales office or the AMD Communication Products Division for information on new SLIC product offerings or other assistance.

# **Bond-Out Options**

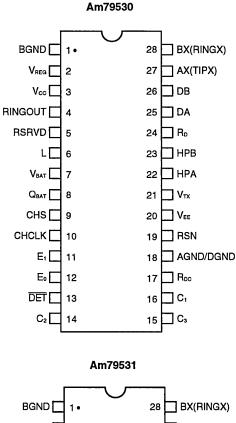

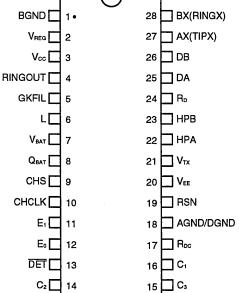

Some of the Central Office SLICs are offered in a number of different bond-out options. These SLICs are the Am7953n, Am7957n, Am79M53n, and Am79M57n, where the n is a number indicating the bond-out option used. Generally, the bond-out options are as follows.

n=0 indicates that both E0 and E1 functions are present, with one relay driver and no ground-key filter.

n=1 indicates that both E0 and E1 functions are present, with a ground-key filter and one relay driver.

n=2 indicates that the E1 function only is present, with two relay drivers.

n=3 indicates that the E0 function only is present, with two relay drivers.

n=4 indicates that both E0 and E1 functions are present, with two relay drivers (32-pin PLCC package).

n = 5 indicates that both E0 and E1 functions are present, with a ground-key filter pin and one relay driver (32-pin PLCC package).

All these SLIC versions are potentially available, but not all are presently in production. Versions that are in volume production are indicated in the chart. If a specific bond-out configuration is not indicated to be in production, please contact AMD's Communication Products Division or the local AMD Sales Office.

# **Performance Grades**

Each of the devices shown on the selector chart is offered in standard, -1, and -2 performance grades. Enhanced performance is specified in the following areas:

- Analog output DC offset

- Longitudinal balance

- · Gain flatness and tracking

- Idle channel noise

- Power supply rejection ratio

- Power dissipation

The -2 performance grade has the same performance as the -1 grade except where noted. See the individual product's data sheet for more information. The -2 performance grade SLICs have also been characterized for extended temperature performance. See the SLIC Extended Temperature Supplement for information on industrial temperature range (-40°C to +85°C) specifications.

# Selector Chart

# Possible SLIC Products

|                          |    | Am7 | 953n |    | A | n795 | 7n | Am7958  | Am79 | 9M53n | Am79 | M57n | Am79HM53 | Am7942 Am7943 |         |

|--------------------------|----|-----|------|----|---|------|----|---------|------|-------|------|------|----------|---------------|---------|

|                          | n= |     |      | n= |   |      | 1  | n=      |      | n=    |      | 1    |          |               |         |

|                          | 0  | 1   | 4    | 5  | 1 | 3    | 4  |         | 1    | 5     | 0    | 4    |          |               |         |

| Functions                |    |     |      |    |   |      |    |         |      |       |      |      |          |               |         |

| Constant Current Feed    | •  | ٠   | •    | •  |   |      |    |         | •    | •     |      |      | •        | •             | •       |

| Constant Resistance Feed |    |     |      |    | • | •    | •  | •       |      |       | •    | •    |          |               |         |

| 2.2-V Metering           |    |     |      |    |   |      |    |         | •    | •     | •    | •    |          |               |         |

| 5-V Metering             |    |     |      |    |   |      |    |         |      |       |      |      | •        |               |         |

| Switching Regulator      | •  | •   | •    | •  | • | •    | •  | •       | •    | •     | •    | •    | •        | Option        |         |

| DET Enable Bit, E0       | •  | •   | •    | •  | • | •    | •  | •       | •    | •     | •    | •    | •        |               | JC only |

| GND Key Select Bit, E1   | •  | •   | •    | •  | • |      | •  | •       | ٠    | •     | •    | •    | •        | •             | JC only |

| GND Key Filter Pin       | 1  | •   |      | •  | • |      |    |         | •    | •     |      |      |          | •             |         |

| Ring Relay Driver        | •  | •   | •    | •  | • | •    | •  | •       | ٠    | •     | •    | •    | •        | •             | •       |

| Test Relay Driver        |    |     | •    |    |   | •    | •  | JC only |      |       |      | •    | JC only  | JC only       |         |

| Packaging                |    |     |      |    |   |      |    |         |      |       |      |      |          |               |         |

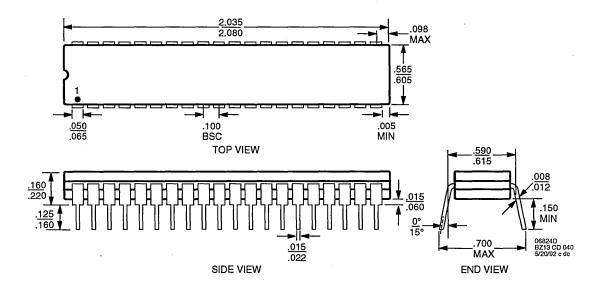

| 28-pin DIP               | •  | •   |      |    | • | •    |    | •       | •    |       | •    |      | •        | •             |         |

| 22-pin DIP               |    |     |      |    |   |      |    |         |      |       |      |      |          |               | •       |

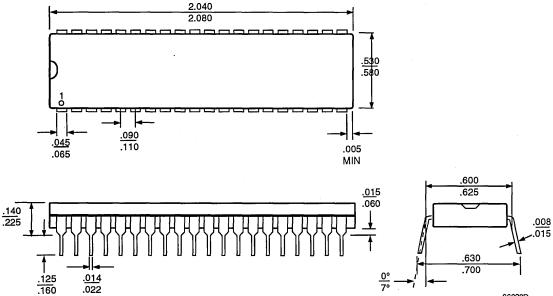

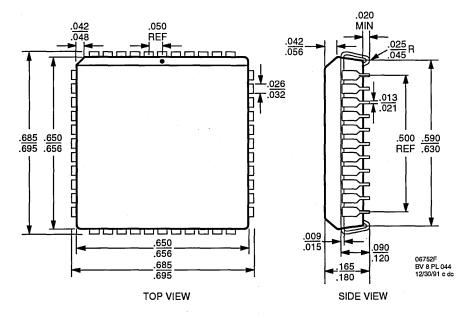

| 32-pin PLCC              |    |     | •    | •  |   |      | •  | •       |      | •     |      | •    | •        | •             | •       |

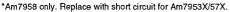

# SLIC FAMILY FUNCTIONAL DESCRIPTION

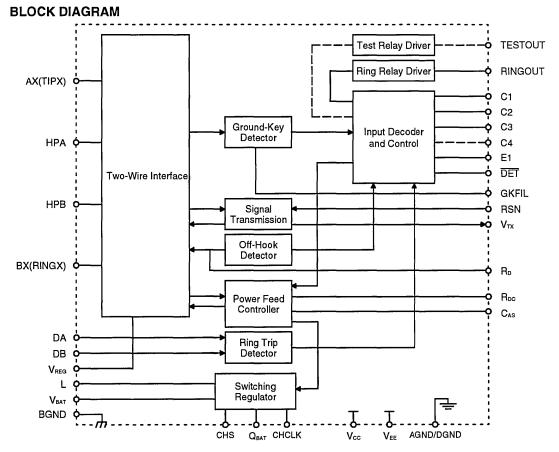

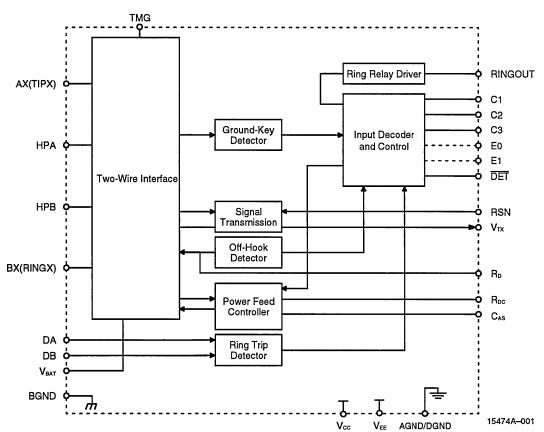

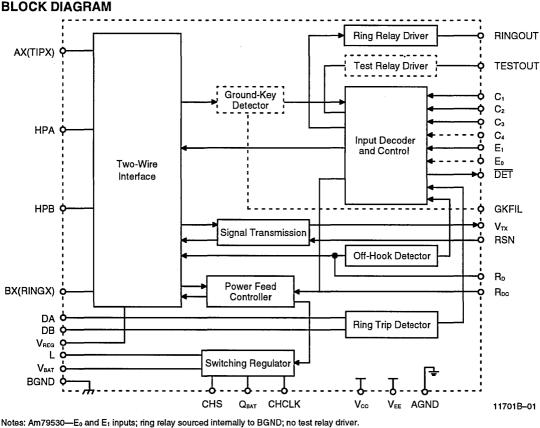

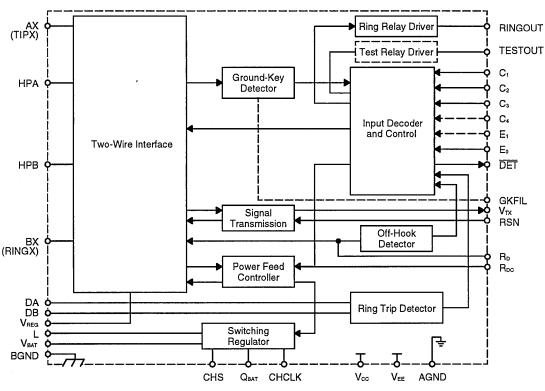

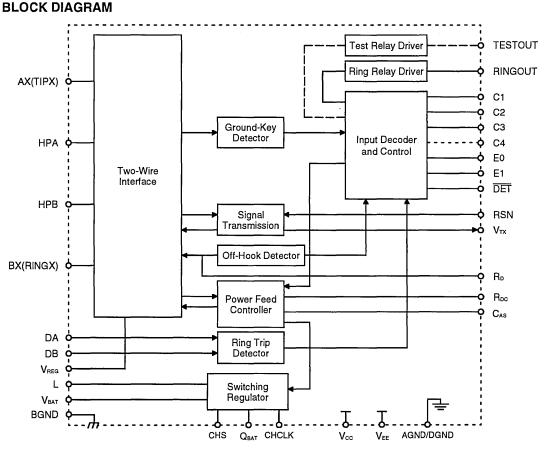

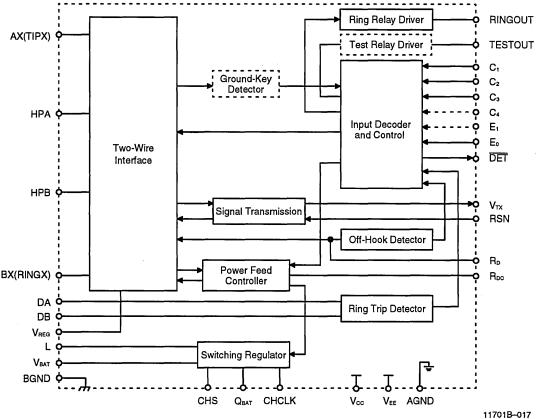

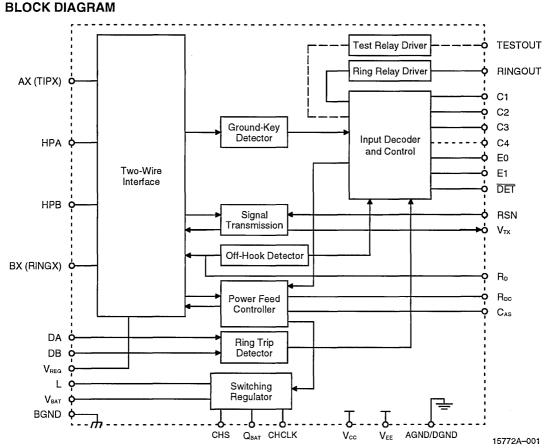

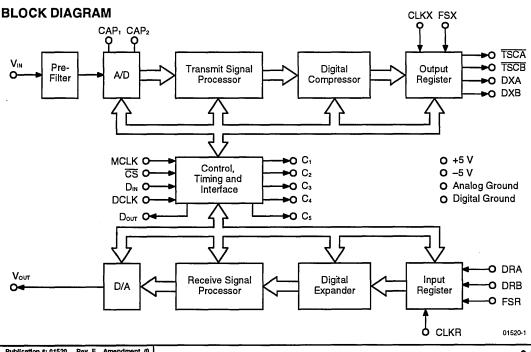

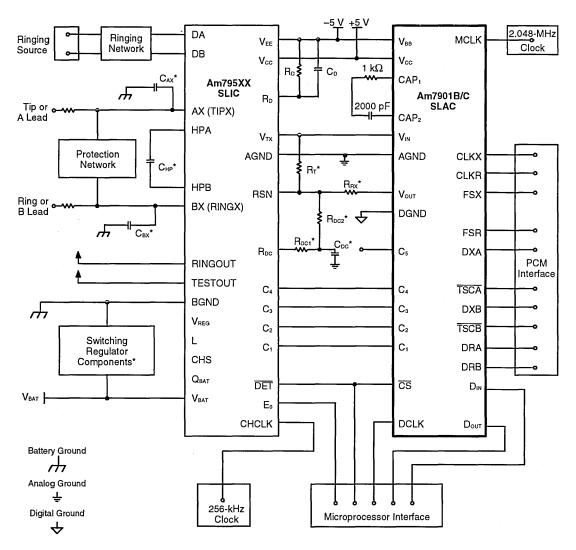

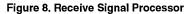

The internal operation of the AMD Family of Subscriber Line Interface Circuits is summarized in the Block Diagram in each of the SLIC Family data sheets. The following sections describe in detail the operation of each block in these diagrams.

#### **Two-Wire Interface**

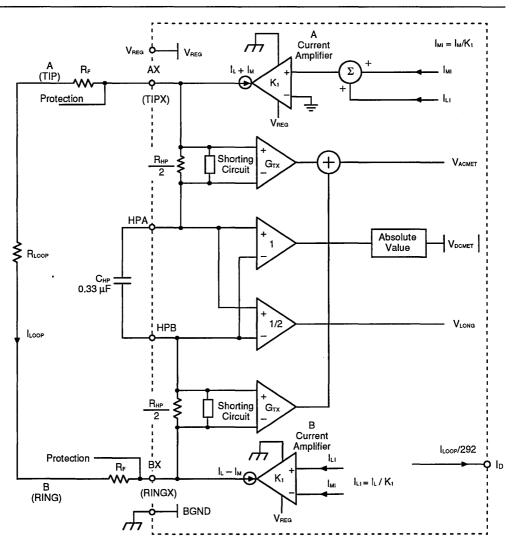

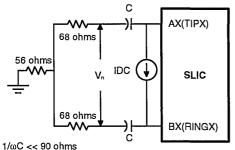

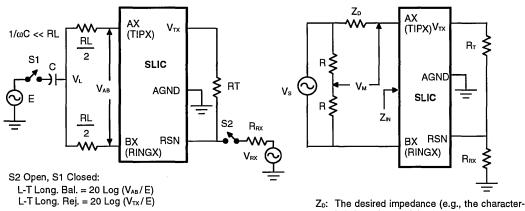

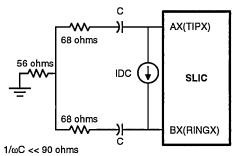

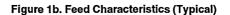

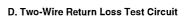

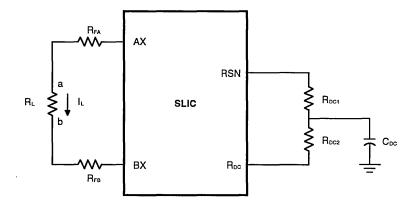

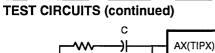

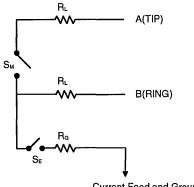

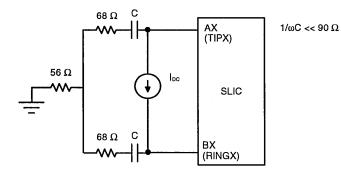

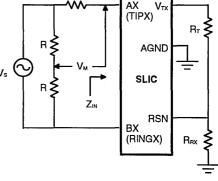

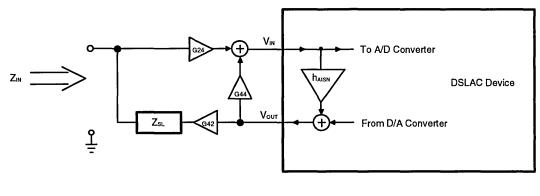

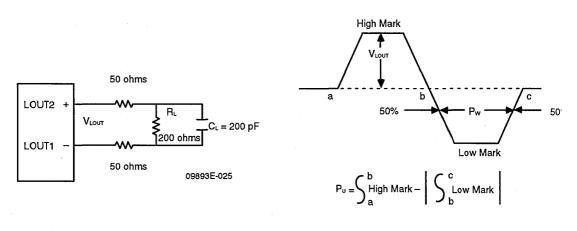

The function of the two-wire interface is to provide DC current and to send voice signals to a telephone apparatus connected to the central office with a two-wire line. The two-wire interface also receives the returning voice signals from the telephone transmitter. The two-wire interface (see Figure 1) consists of two current mode line-driver amplifiers, line-voltage sensing circuits with AC/DC pass separation, and a loop-current sensing circuit.

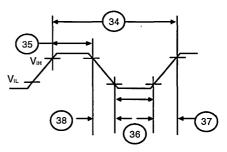

The current mode amplifiers driving the AX(TIPX) and BX(RINGX) pins are controlled by two input signals,  $I_{L1}$  and  $I_{M1}$ .  $I_{L1}$  controls the longitudinal (common mode) current, and  $I_{M1}$  controls the metallic (transverse) current.

Figure 1. Two-Wire Interface

11701A-03

The two-wire currents are:

$I_{AX} = K_1(I_{L1} + I_{M1})$  and  $I_{BX} = K_1(I_{L1} - I_{M1})$

Where:  $K_1$  is the internal current mode amplifier gain.

I<sub>MI</sub> is equal to the current into the Receive Summing Node (RSN), which is the terminating point for the external networks controlling two-wire impedance, receive gain, battery feed, and metering gain (in metering versions). These networks are described in detail later. I<sub>u</sub> controls the longitudinal line voltage to obtain the optimum common mode DC operating point for the current mode amplifiers.

The voltage sense signal ( $V_{ACMET}$ ) that goes to the signal transmission block is the AC metallic component of the AX and BX voltages.

Two voltage sense signals ( $|V_{\text{DCMET}}|$  and  $V_{\text{LONG}}$ ) go to the power feed controller block.  $V_{\text{DCMET}}$  is the DC metallic component of the AX and BX voltages.  $V_{\text{LONG}}$  is the longitudinal component of the AX and BX voltages.

An external capacitor ( $C_{HP}$ ), connected between HPA and HPB, separates the AC and DC components of the metallic voltage. Since the time constant would be too long during polarity reversal or pulse dialing, the twowire interface has a shorting circuit that decreases the time constant during these events.

The loop-current sensing circuit produces a current ( $I_{\text{D}}$ ) that is proportional to the magnitude of the loop current and is output to the  $R_{\text{D}}$  pin. An external resistor and filter capacitor connected from  $R_{\text{D}}$  to  $V_{\text{EE}}$  converts this current to a filtered voltage for use by the off-hook detector.

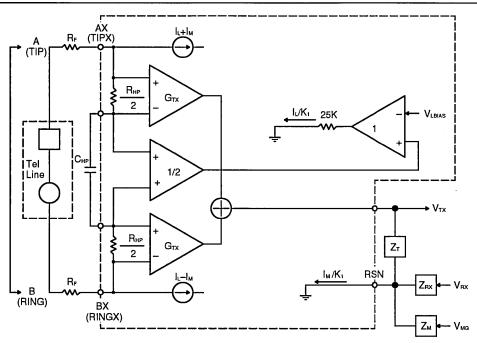

#### Signal Transmission

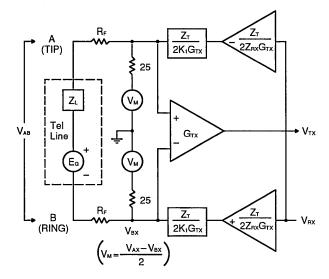

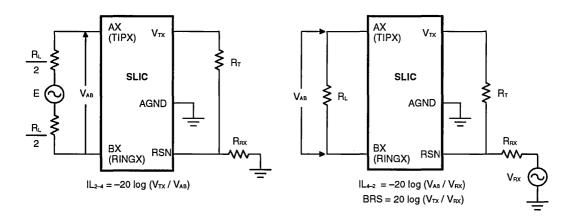

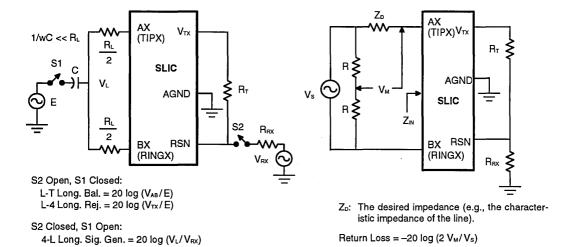

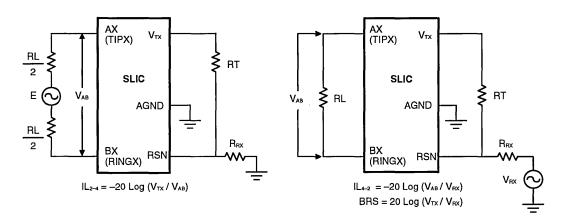

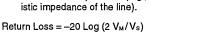

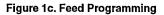

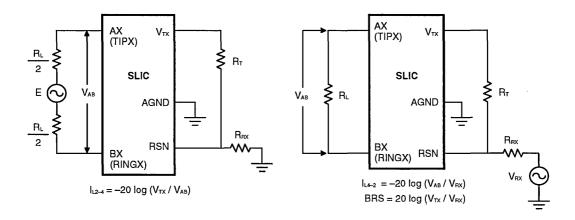

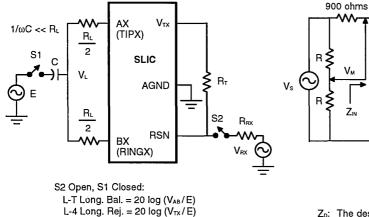

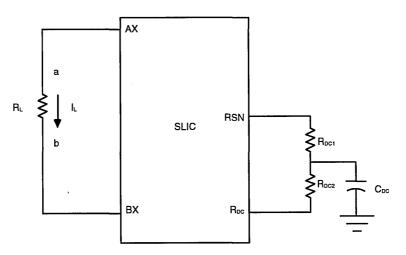

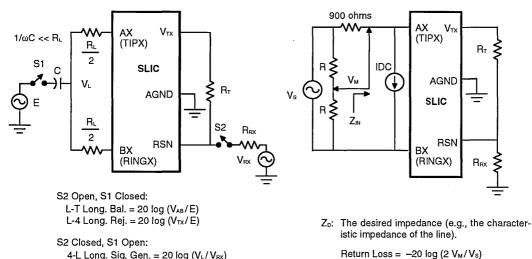

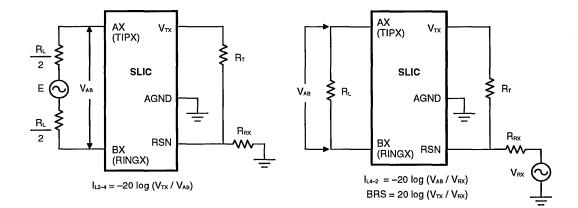

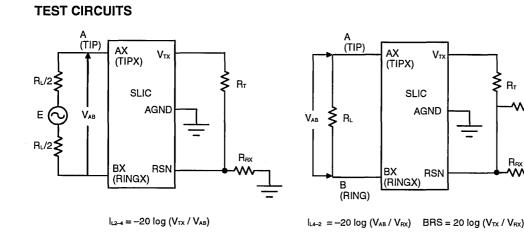

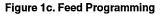

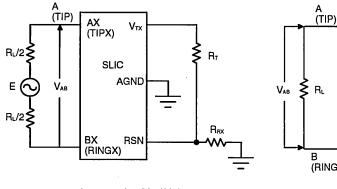

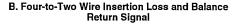

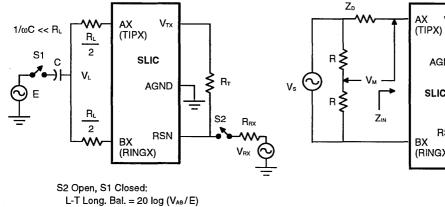

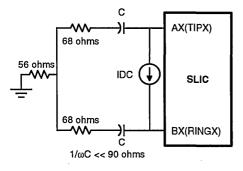

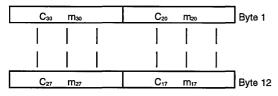

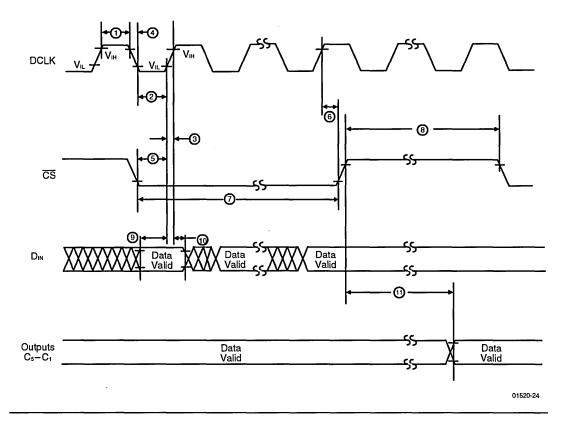

Figures 2a and 2b provide more detail of the SLIC transmission path. This path is split between the signal transmission block and the two-wire interface block.

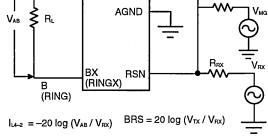

The AC line voltage is sensed by differential amplifiers between the AX and HPA leads, and between the HPB and BX leads. The outputs of these amplifiers are equal to the AC metallic components of the line voltages. These voltages are summed and buffered by the op amp  $G_{Tx}$ . For non-metering versions,  $G_{Tx}$  is set to a gain of 1.0. For metering SLICs,  $G_{Tx}$  is set to a gain of either 0.51 (2.2 VRMS metering versions) or 0.282 (5.1 VRMS versions) to avoid overload during metering signal transmission. Longitudinal voltages are rejected by the differential amplifiers and do not affect  $V_{Tx}$ .

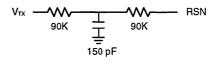

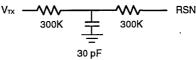

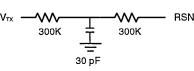

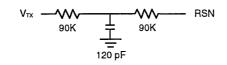

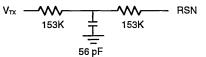

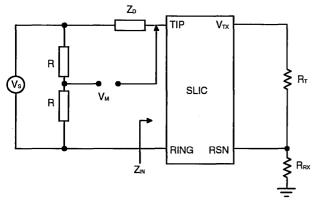

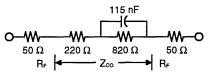

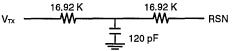

The balance return signal on V<sub>Tx</sub> exhibits 180° phase shift with respect to V<sub>FX</sub>. This allows the SLIC's two-wire AC input impedance to be programmed by means of an external impedance that is connected between RSN and V<sub>Tx</sub> (see Figures 2a and 2b). This impedance may be a complex R-C network and should be K<sub>1</sub> times the desired two-wire input impedance minus K<sub>1</sub> times the fuse resistors. This means resistors become K<sub>1</sub> times smaller. Note that any external stray capacitance between V<sub>Tx</sub> and RSN must be included in Z<sub>T</sub> when precise computations for output impedance, gain, trans-hybrid loss, or return loss are being made.

$Z_{T} = K_{1} \operatorname{G}_{Tx} \left( Z_{2WIN} - 2R_{F} \right)$

Where: Z<sub>2WIN</sub> = desired two-wire impedance

The four-wire output is found on the  $V_{Tx}$  terminal, and the four-wire input terminal is  $V_{Rx}$  (see Figure 2b). Both these ports are referenced to analog ground (AGND).

Because the fuse resistors are outside the feedback loops, they influence the effective gains. These gains are as follows:

$$G_{42L} = \frac{V_{AB}}{V_{RX}} [E_{\alpha} = 0] = -\frac{Z_L}{Z_{RX}} \frac{K_1 Z_T}{Z_T + K_1 G_{TX} (Z_L + 2_{RF})}$$

$$G_{24} = \frac{V_{TX}}{V_{AB}} [V_{RX} = 0] = \frac{\frac{Z_T}{K_1}}{2R_F + \frac{Z_T}{K_1 G_{TX}}}$$

$$G_{44L} = \frac{V_{TX}}{V_{RX}} [E_{G} = 0] = -\frac{Z_{T}}{Z_{RX}} \frac{(Z_{L} + 2R_{F})}{Z_{L} + 2_{RF} + \frac{Z_{T}}{K_{I}G_{TX}}}$$

AMD 🎵

2a. Detailed Model

2b. Simplified Model (AC Only for Conceptual Purposes)

11701A-04

Figure 2. SLIC Transmission Model

The dynamic performances of  $K_1$  (the current amplifier gain) and  $G_{Tx}$  (the transmit voltage amplifier gain) are modeled by the following S-domain transfer functions:

$$\begin{split} K_1(S) &= |K_1| \quad \frac{1}{1 + 1.15 \cdot 10^{-8} \cdot [36 + Z_{AB}(S)] \cdot S} \\ G_{TX}(S) &= \frac{|G_{TX}|}{1 + \frac{1}{424 \cdot 10^3 \, C_{HP} \, S}} \quad \cdot \quad \frac{1}{1 + 4.5 \cdot 10^{-7} S} \end{split}$$

Where:  $|K_1|$  = Current amplifier DC gain  $Z_{AB}$  = Load between the AX and BX pins  $|G_{TX}|$  = Two- to four-wire transmit path

midband gain

These functions are useful for the prediction of system return loss and echo cancellation performance. The value of K<sub>1</sub> is typically 1000 for the Am795XX/Am79M5XX versions. K<sub>1</sub> is 200 for the Am7942, Am7943, and Am7958. G<sub>TX</sub> is 1.0 for non-metering SLICs, 0.51 for metering versions, (Am79M53X/M57X) and .282 for the Am79HM53. C<sub>HP</sub> sets the low frequency limit of the voice band response. A C<sub>HP</sub> value of 0.33 µF should optimize voice-band and DC-loop performance in many applications.

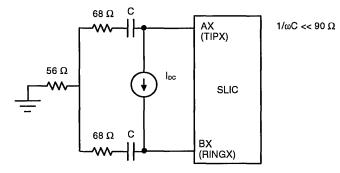

The transmission circuit also contains a longitudinal feedback circuit to shunt longitudinal signals to a DC bias voltage (VL<sub>BIAS</sub>) which comes from the power feed controller. Longitudinally, the SLIC typically appears as 25-ohm resistors from AX and BX to VL<sub>BIAS</sub>. The longitudinal feedback does not affect metallic signals.

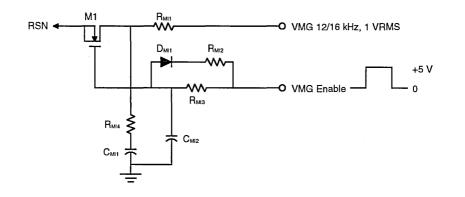

In metering versions of the SLIC, metering signals are injected by adding an additional current into summing point RSN through an external impedance,  $Z_{M}$ .

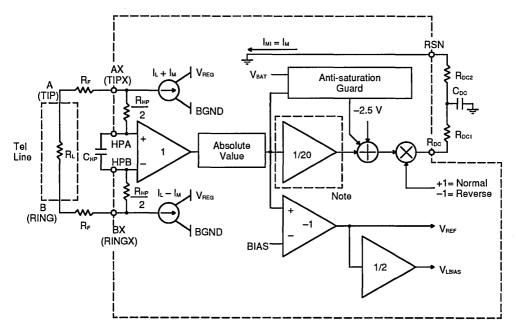

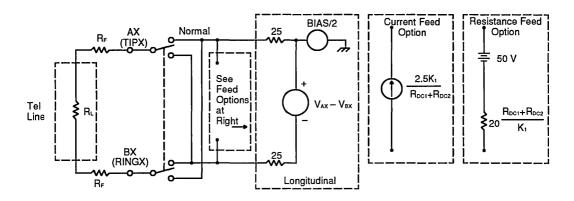

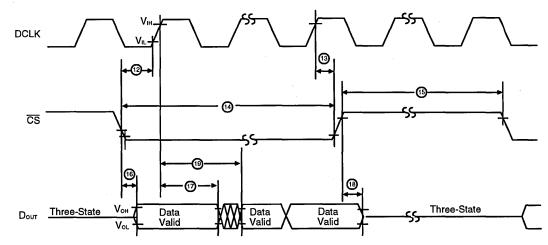

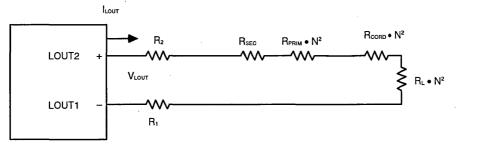

# **Power Feed Controller**

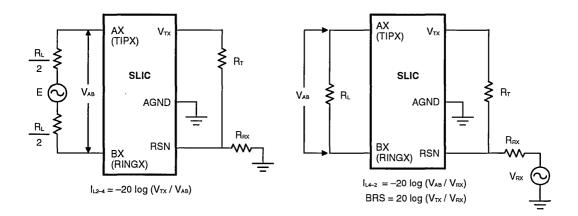

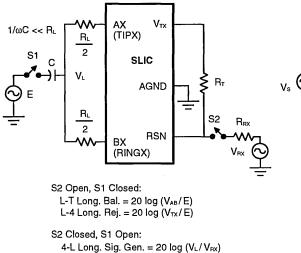

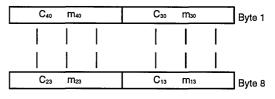

The power feed controller has three sections: (1) the battery feed circuit; (2) the polarity reversal circuit; and (3) the bias circuit. These are shown in Figures 3a and 3b. The detailed model is shown in Figure 3a and the simplified model in Figure 3b.

The battery feed circuit regulates the amount of DC current and voltage supplied to the telephone over a wide range of loop resistance. The polarity reversal circuit gives the SLIC the capability to reverse the loop current for pay telephone coin return and other applications. The bias circuit provides a reference voltage, which is offset from the subscriber line voltage. The reference voltage controls the switched mode regulator (described later), which minimizes SLIC power consumption by providing the minimum supply voltage needed by the line drivers for proper operation.

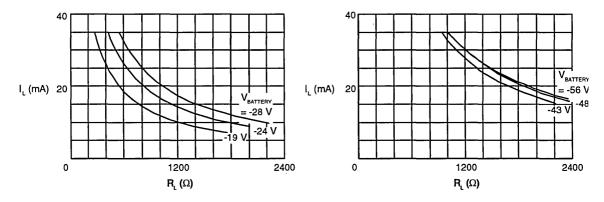

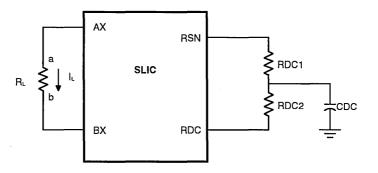

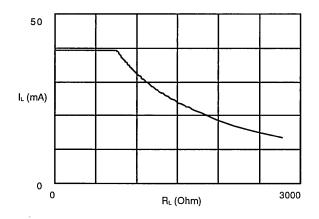

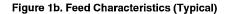

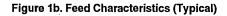

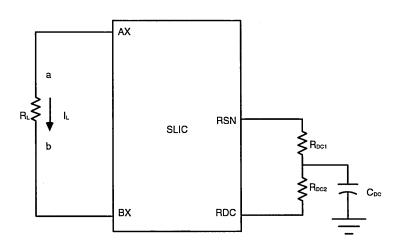

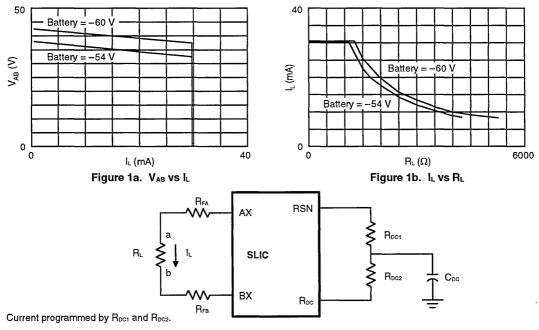

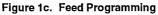

$V_{\text{DCMET}}$  is the DC component of the voltage between AX and BX. When  $C_{\text{HP}}$  is 0.33  $\mu$ F, the low pass filter formed by  $R_{\text{HP}}$  and  $C_{\text{HP}}$  attenuates frequencies above 1.2 Hz. The loop current is equal to K<sub>1</sub> times the current into the Receive Summing Node (RSN), which is equal to the voltage on  $R_{\text{DC}}$  divided by  $R_{\text{DC1}} + R_{\text{DC2}}$ . The values of the programming resistors,  $R_{\text{DC1}}$  and  $R_{\text{DC2}}$ , should be kept somewhat equal in order to minimize the size of  $C_{\text{DC}}$ .

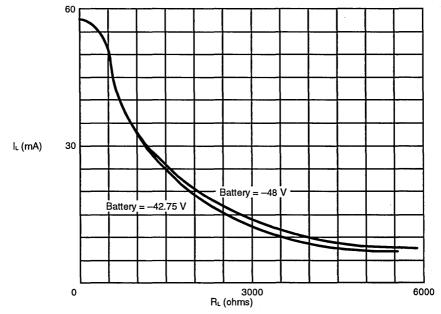

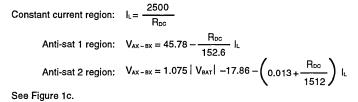

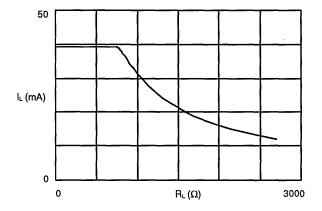

In constant current feed versions, the battery feed circuit produces a voltage at the  $R_{\text{pc}}$  pin whose magnitude is equal to 2.5 V, and whose sign depends on the feed polarity desired (minus for normal polarity and plus for reverse polarity). The net result is that the SLIC appears to have a constant current feed with the feed current given by the following equation:

$$I_{FEED} = \frac{2.5K_1}{R_{DC2} + R_{DC2}}$$

For example, if  $K_1$  is 1000 and a loop current of 40 mA is desired:

$$R_{DC1} + R_{DC2} = \frac{2.5 \cdot 1000}{40} = 62.5K$$

In this example, values of  $R_{\mbox{\tiny DC1}}$  and  $R_{\mbox{\tiny DC2}}$  of 31.25K could be used.

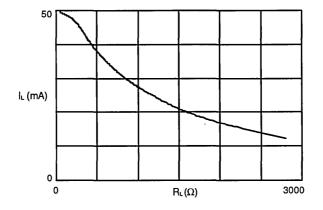

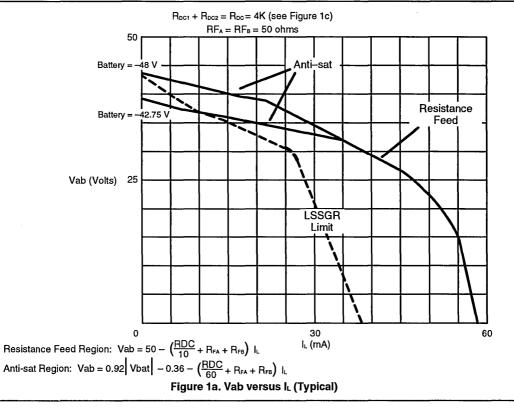

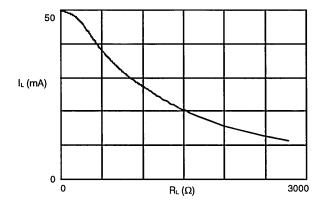

For resistance feed versions, the battery feed produces a voltage at the R<sub>DC</sub> pin whose magnitude is equal to  $(50 - |V_{DCMET}|)/20$ , and whose sign depends on the feed polarity desired (minus for normal polarity and plus for reverse polarity). The net result is that the SLIC appears to have an apparent open circuit voltage of 50 V and a feed resistance, R<sub>FEED</sub>, equal to  $20(R_{DC1} + R_{DC2})/K_1$ ; thus, the feed resistance is programmable, but the apparent open circuit voltage is not. Including the fuse resistors R<sub>F</sub>, the total feed resistance is then:

$$R_{\text{FEED}} = 2R_{\text{F}} + \frac{20(R_{\text{DC1}} + R_{\text{DC2}})}{K_1}$$

For example, if  $K_1 = 1000$ , and a feed resistance of 840 ohms is desired using 20-ohm fuse resistors:

$$R_{DC1} + R_{DC2} = \frac{1000(840 - 2 \cdot 20)}{20} = 40K$$

In this example, values of  $R_{\mbox{\tiny DC1}}$  and  $R_{\mbox{\tiny DC2}}$  of 20K could be used.

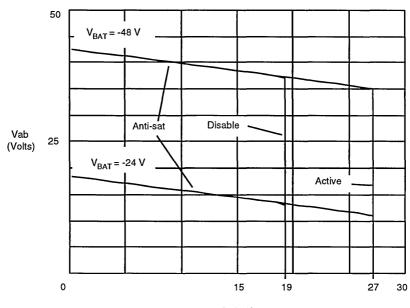

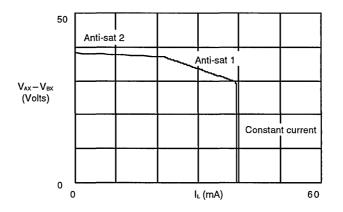

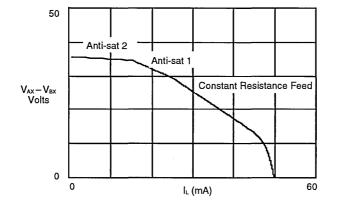

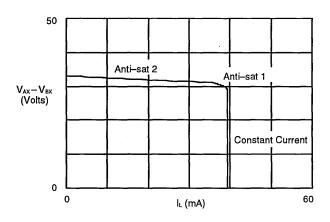

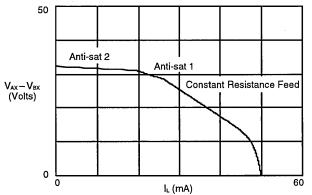

All versions of the SLIC have an anti-saturation guard that prevents the output amplifiers from saturating under high line voltage conditions which, in turn, prevents clipping. When the  $V_{Ax}$  to  $V_{Bx}$  voltage reaches a threshold of approximately 30 V (exact voltage depends on SLIC version), the SLIC goes into the Anti-sat 1 region of operation.

Note: The 1/20 operational amplifier is only present in constant resistance feed versions of the SLIC.

#### **3a. Detailed Model**

3b. Simplified Model

11701A-05

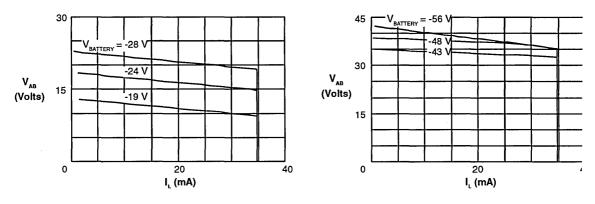

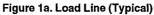

In this region, the feed synthesis loop gain is greatly increased, thereby reducing the output resistance to a much lower value. The output voltage then rises at a slower rate with increasing loop resistance, thereby keeping the amplifier out of saturation. All transmission specifications are met in the Anti-sat 1 region. If the line voltage increases further to greater than approximately 15 V (exact voltage depends on SLIC version) below VBAT, the SLIC goes into the Anti-sat 2 region where the loop gain is again increased and the output resistance further decreased. In this region, the voltage rises very slowly, with increasing loop resistance, and the DC feed of the SLIC looks almost like a constant voltage source. The transmission specifications in the Anti-sat 2 region will be somewhat degraded. Load lines and equations describing all regions of operation are provided in each device data sheet.

To obtain polarity reversal, the input decoder and control circuit send a signal that reverses the sign of the voltage on the R<sub>DC</sub> pin. During reversal, sense resistors R<sub>HP</sub> are drastically reduced in value to reduce the time constant formed by R<sub>HP</sub> and C<sub>HP</sub>. This allows the polarity reversal time to be controlled only by C<sub>DC</sub> and the parallel combination of R<sub>DC1</sub> and R<sub>DC2</sub>. A typical polarity transition time is 1.5 ms. In the previous example for a resistance feed version SLIC, R<sub>DC1</sub> and R<sub>DC2</sub> were computed to be 20K. The value of C<sub>DC</sub> should then be 0.15  $\mu$ F.

The V<sub>REF</sub> output of this block is fed to the switching regulator (see next section) which adjusts V<sub>REG</sub>, the voltage supplying the line output amplifiers, until it is equal to twice V<sub>LBIAS</sub>. Additional BIAS is added to provide enough "headroom" for the amplifiers to always operate in the linear region. In summary, the equations for these voltages are:

$V_{REG} = V_{REF} = -(|V_{DCMET}| + BIAS)$  $V_{LBIAS} = V_{REF}/2$

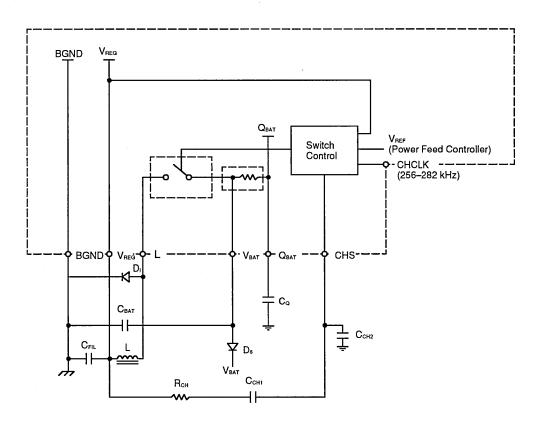

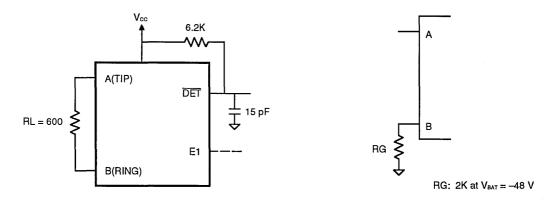

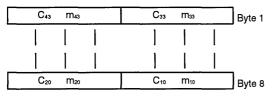

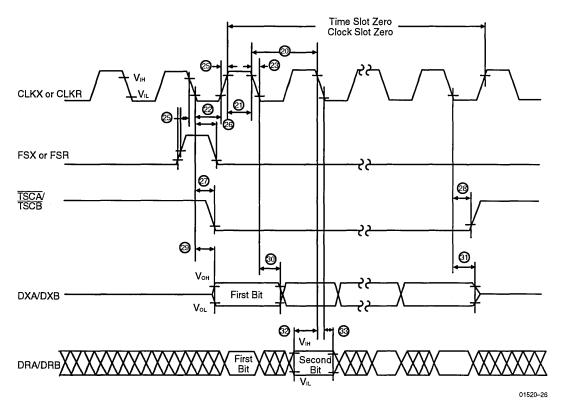

# Switching Regulator

The switching regulator supplies the operating voltage,  $V_{\text{REG}}$ , to the two-wire interface (see Figure 4). This circuit adjusts  $V_{\text{REG}}$  to the minimum voltage necessary

to power the output amplifiers. In this manner, the power consumption is held to a minimum. This is particularly important for short loops where there is a potential for high loop currents.

A 256- to 282-kHz clock is required at input CHCLK to operate the switching regulator. The switch control tells the switch to disconnect the L pin from  $V_{BAT}$  at the beginning of each CHCLK cycle, and connect it for a time that depends upon the difference between  $V_{REF}$  and  $V_{REG}$ . During this time, the current through the inductor decreases. A comparator senses when  $V_{REG}$  falls below  $V_{REF}$  and the inductor is again switched to  $V_{BAT}$ . The result is that the average value of  $V_{REG}$  is always held equal to the value of  $V_{REF}$ . The filter capacitor,  $C_{FIL}$ , between  $V_{REG}$  and BGND smooths out the ripple caused by the inductor switching action.

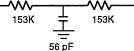

The regulator is a high-gain feedback circuit, and therefore requires the stabilization network formed by  $R_{CH1}$ ,  $C_{CH1}$ , and  $C_{CH2}$  between  $V_{RE9}$  and CHS.

The design and layout of the external switching regulator circuitry are very important. Fast switching currents can occur in the catch diode,  $D_1$ , and in the  $V_{BAT}$  filter capacitor,  $C_{BAT}$ . These must be low inductance components with short leads. Capacitor  $C_{FIL}$  must have low effective series resistance at high frequencies. A stable, voltage insensitive capacitor, such as a metallized polyester type, should be used.

The connections from the diode to the L pin, from  $C_{BAT}$  to the V<sub>BAT</sub> pin, and from the diode to C<sub>BAT</sub> must all be short, low-inductance connections. The L pin is subject to very fast voltage transients as the switch turns on and off, so all of the connections to this pin must be isolated from sensitive signals by means of traces connected to BGND. All of the external components in the regulator circuit except C<sub>CH1</sub> must have voltage ratings in excess of 70 V. C<sub>CH1</sub> can have a voltage rating of 10 V or more. In addition, the diode must have a reverse recovery time of less than 4 ns. All of the SLICs in a system should be synchronized to a common clock to prevent intermodulation products and crosstalk in the voice band.

11701A--06

# Figure 4. SLIC Switching Regulator

# Input Decoder and Control

The input decoder and control block provide a means for a microprocessor or SLAC IC to control such system functions as line activate/disable, ringing, and polarity reversal.

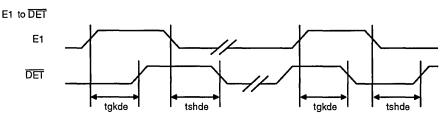

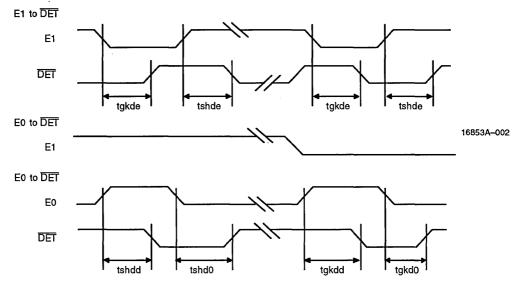

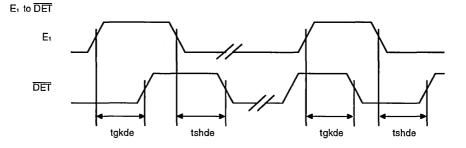

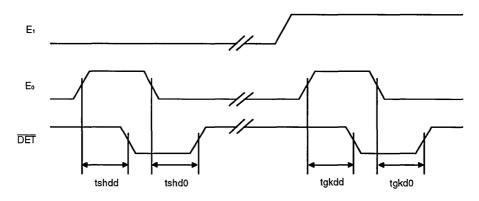

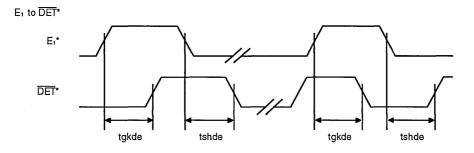

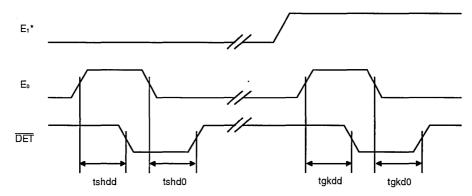

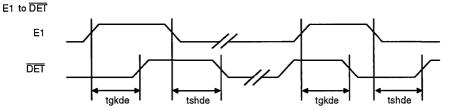

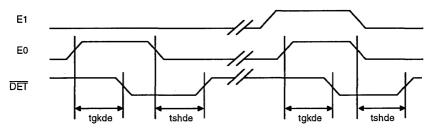

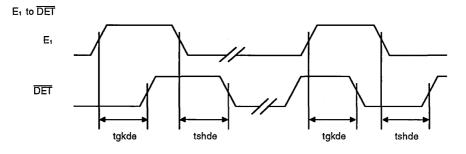

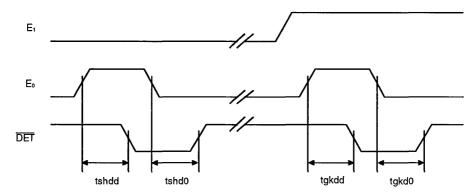

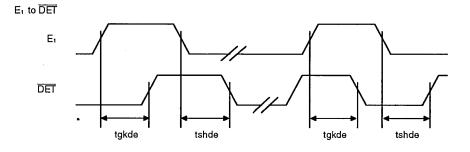

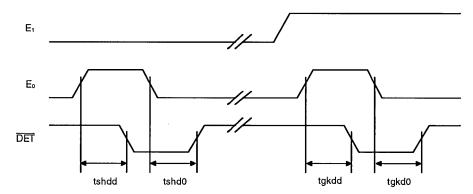

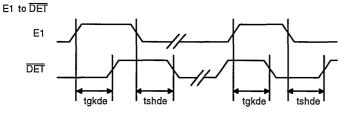

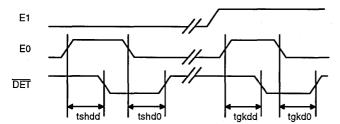

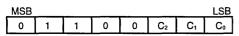

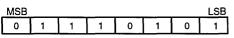

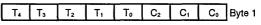

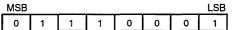

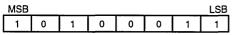

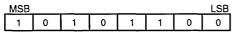

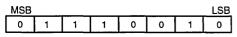

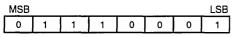

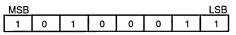

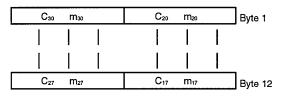

The input decoder and control block has TTL-compatible inputs, and sets the operating states of the SLIC.  $C_1$ ,  $C_2$ , and  $C_3$  inputs are common to all versions and can select seven operating states.  $C_4$  is a dedicated input used as a test relay command in versions with a test relay driver.  $E_0$  and  $E_1$  control the function of the DET output. Table 1 summarizes the SLIC control logic.

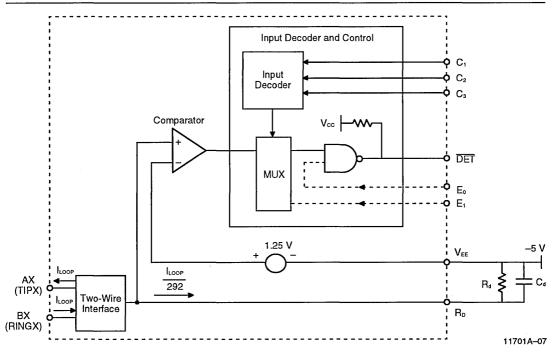

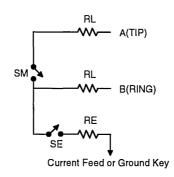

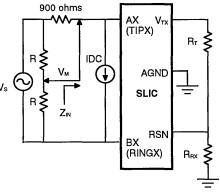

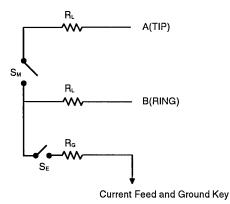

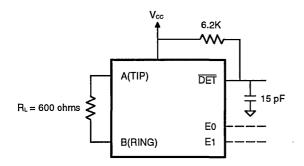

#### **Off-Hook Detector**

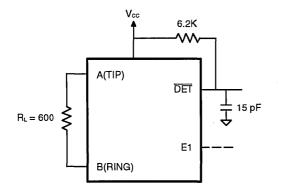

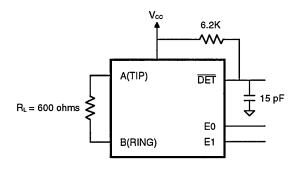

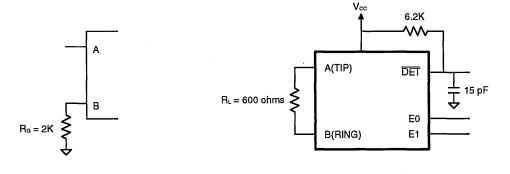

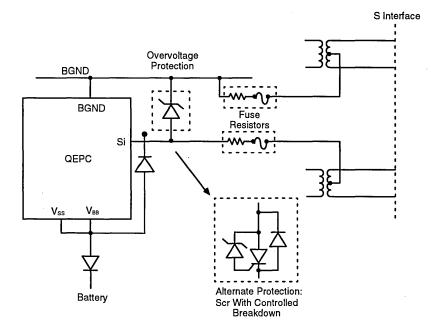

The first and most important loop monitoring function is off-hook detection. The block diagram of this detector is shown in Figure 5.

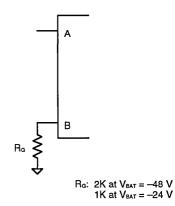

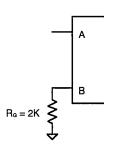

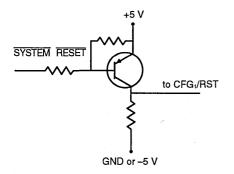

The two-wire interface produces a current equal in magnitude to the loop current divided by 292, and sends it out on the R<sub>0</sub> pin. An external resistor and capacitor (R<sub>4</sub> and C<sub>4</sub>) connects the R<sub>0</sub> pin to V<sub>EE</sub> (–5 V). The value of the voltage across resistor R<sub>4</sub> is the current leaving the R<sub>0</sub> pin times the value of R<sub>4</sub>. The off-hook detector outputs a logic Low to the DET pin when this voltage rises above a threshold of 1.25 V.

The value of  $R_d$  required for a desired off-hook line current threshold is then:

The value of  $C_d$  for a typical on-hook to off-hook time constant of 0.5 ms should satisfy the relation:

$R_d C_d = 0.5 ms$

|    |             |                                 | Table 1. SLIC Decodi                                                                                                                                                                  | ing                                                                                                                |                                                                                                                                                                                                                                        |  |  |  |  |

|----|-------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|    |             |                                 |                                                                                                                                                                                       | DET Output                                                                                                         |                                                                                                                                                                                                                                        |  |  |  |  |

| C3 | C,₂         | C1                              | Two-Wire Status                                                                                                                                                                       | E0 = 1<br>E1 = 0                                                                                                   | E0 = 1<br>E1 = 1                                                                                                                                                                                                                       |  |  |  |  |

| 0  | 0           | 0                               | Open Circuit                                                                                                                                                                          | Ring Trip                                                                                                          | Ring Trip                                                                                                                                                                                                                              |  |  |  |  |

| 0  | 0           | 1                               | Ringing                                                                                                                                                                               | Ring Trip                                                                                                          | Ring Trip                                                                                                                                                                                                                              |  |  |  |  |

| 0  | 1           | 0                               | Active                                                                                                                                                                                | Loop Det.                                                                                                          | Ground Key                                                                                                                                                                                                                             |  |  |  |  |

| 0  | 1           | 1                               | Disable                                                                                                                                                                               | Loop Det.                                                                                                          | Ground Key                                                                                                                                                                                                                             |  |  |  |  |

| 1  | 0           | 0                               | Tip Open                                                                                                                                                                              | Loop Det.                                                                                                          |                                                                                                                                                                                                                                        |  |  |  |  |

| 1  | 0           | 1                               | Reserved                                                                                                                                                                              | Loop Det.                                                                                                          |                                                                                                                                                                                                                                        |  |  |  |  |

| 1  | 1           | 0                               | Active Polarity Reversal                                                                                                                                                              | Loop Det.                                                                                                          | Ground Key                                                                                                                                                                                                                             |  |  |  |  |

| 1  | 1           | 1                               | Disable Polarity Reversal                                                                                                                                                             | Loop Det.                                                                                                          | Ground Key                                                                                                                                                                                                                             |  |  |  |  |

|    | 0<br>0<br>0 | 0 0<br>0 0<br>0 1<br>0 1<br>1 0 | 0         0         0           0         0         1           0         1         0           0         1         1           1         0         0           1         0         1 | C3C2C1Two-Wire Status000Open Circuit001Ringing010Active011Disable100Tip Open101Reserved110Active Polarity Reversal | $C_3$ $C_2$ $C_1$ Two-Wire Status $E0 = 1$<br>$E1 = 0$ 000Open CircuitRing Trip001RingingRing Trip010ActiveLoop Det.011DisableLoop Det.100Tip OpenLoop Det.101ReservedLoop Det.11ReservedLoop Det.110Active Polarity ReversalLoop Det. |  |  |  |  |

**Open Circuit:** When the SLIC is in the Open Circuit state, both the AX(TIPX) and BX(RINGX) power amplifiers are switched off and present high impedance to the line. The Open Circuit state has the lowest power dissipation. Loop detectors are inoperative in this state. This function is useful for allowing line-powered relays to collapse, denying power to out-of-service lines, as well as allowing clearing of line faults.

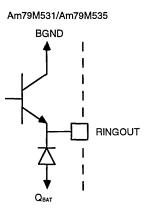

**Ringing:** When the SLIC is in the Ringing state, the ring relay driver (RINGOUT) is activated, and the Ring Trip Detector is readable at DET. Also, the AX(TIPX) and BX(RINGX) are both open circuit. While the SLIC is in the ringing state, signal transmission is inhibited.

Active: In states where normal, Active operation is indicated, the standard battery convention applies; AX(TIPX) is near ground and sources current. BX(RINGX) is near  $V_{\text{BAT}}$  and sinks current. During active mode operation, all signal transmission and loop supervision functions operate, and the offhook detector or ground-key detector is gated to  $\overline{\text{DET}}$ .

**Disable**: The Disable operating state is the SLIC's low-power mode in which the battery feed circuit limits the DC loop current to typically 0.5 (value depends on SLIC version) times the

active-mode short circuit current limit. In this state, the offhook detector works normally.

**Tip Open:** When the SLIC is in the Tip Open state, the AX(TIPX) power amplifier is switched off so that it presents a high impedance to the line. This mode is provided to facilitate ground start signaling.

Active Polarity Reversal: When the SLIC is in Active Polarity Reversal state, the normal battery feed convention is reversed, with BX(RINGX) approaching ground and sourcing current, while AX(TIPX) approaches battery and sinks current. While AX(TIPX) and BX(RINGX) are in transition, the off-hook function is meaningless because the loop current must pass through zero.

**Disable Polarity Reversal:** This state is similar to the Disable state, except that the feed is reversed.

Figure 5. Signaling Off-Hook Detection

# **Ringing Circuit**

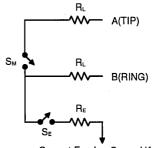

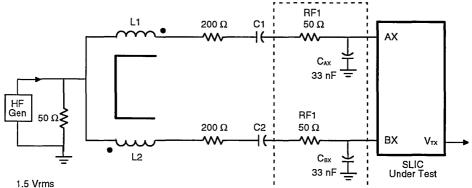

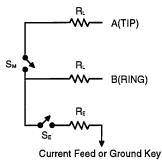

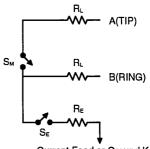

A generalized ringing circuit is shown in Figure 6. In common applications, the circuit can be simplified as shown later. During ringing, the ring relay driver is activated and the AX(TIPX) and BX(RINGX) leads are placed in the open circuit state. The ring feed source is connected by the ring relay to the line, through ring feed resistors  $R_1$  and  $R_2$ .

The bridging resistors  $R_{B1}$ ,  $R_{B2}$ ,  $R_{3}$ , and  $R_{4}$ , and filter capacitors  $C_{RT1}$  and  $C_{RT2}$ , produce a DC voltage sign reversal between DA and DB when an off-hook occurs.

If  $R_{\text{LMAX}}$  is the maximum line resistance that is to be detected as an off-hook, the bridging resistors should be chosen such that:

$$\frac{R_{B1}}{R_3} = \frac{R_{B2}}{R_4} = \frac{(R_{LMAX} + R_{FEED})}{R_{LMAX}}$$

Where:  $R_{FEED} = R_1 + R_2$

The capacitors reduce the effective amplitude of the ringing signal by a factor of  $1/|1+j2\pi f_r t|$ .

where:

$$t = \frac{R_3 R_{B1} C_{RT1}}{R_3 + R_{B1}} + \frac{R_4 R_{B2} C_{RT2}}{R_4 + R_{B2}}$$

For  $f_r$ =20 Hz ringing,  $C_{RT}$  should be chosen to give a value of t=50 ms. This will reduce the ringing by a factor 6.4 and allow detection within 2 ringing cycles.

For balanced ringing, the ringing voltage splits between the ground and battery sides. The resistors should be balanced, (i.e.,  $R_{1=}R_2$ ,  $R_{B1} = R_{B2}$ , and  $R_3 = R_4$ ). A single capacitor of half the value between DA and DB can replace the capacitors  $C_{RT1}$  and  $C_{RT2}$ .

For unbalanced ringing on the ground side, use equal networks with  $R_1 = R_2$ ,  $R_{B1} = R_{B2}$ ,  $R_3 = R_4$ , and  $C_{RT1} = C_{RT2}$ .

For unbalanced ringing on the battery side, the following simplification can be made. The positive side of the ringing supply is grounded and R<sub>1</sub> is replaced by a short circuit. In this case, the R<sub>4</sub>, R<sub>82</sub>, and C<sub>RT2</sub> network can be combined with other channels into a ringer threshold, because the voltage on the DA pin is independent of line conditions.

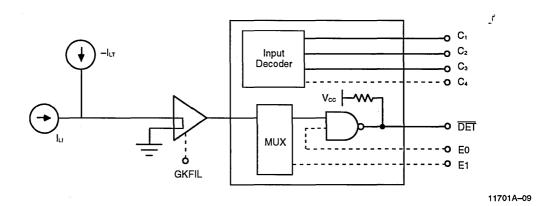

#### **Ground-Key Detector**

The Ground-Key Detector (for ground-key versions, see Figure 7) compares the longitudinal control current ( $I_L$ ) to an internally generated threshold current,  $I_{LT}$ . The current flowing in the earth loop will be proportional to the longitudinal control current. When the current in the earth loop exceeds the threshold value and  $E_1$  is High, the ground-key signal forces the DET output Low.

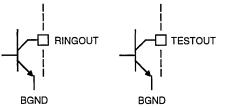

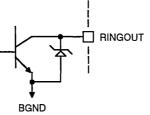

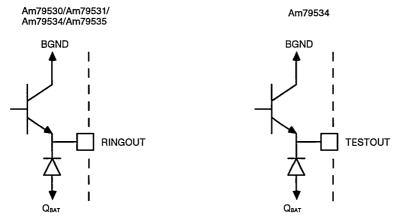

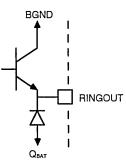

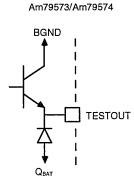

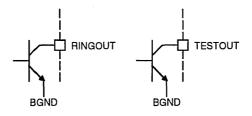

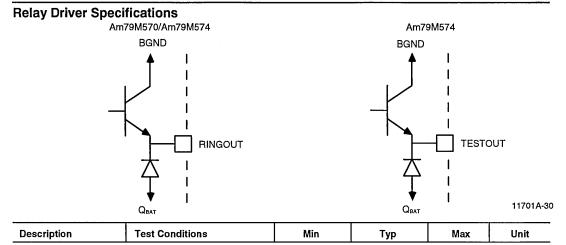

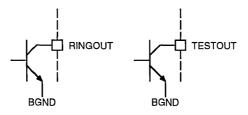

# **Ring Relay Driver**

A ring relay driver is provided in all versions. The normal functioning driver is an internal transistor, with the collector sourced to BGND and the emitter as the driver output. Some versions may have the collector brought out to a separate pin.

# **Test Relay Driver**

A test relay driver is provided only on dual relay driver versions, and has specifications identical to the ring relay driver. In these versions, the test relay driver is activated by logic 0 at input pin  $C_4$ .

Figure 6. Ringing Circuit

11701A-08

# **PBX SLICs**

# PBX SLIC General Description

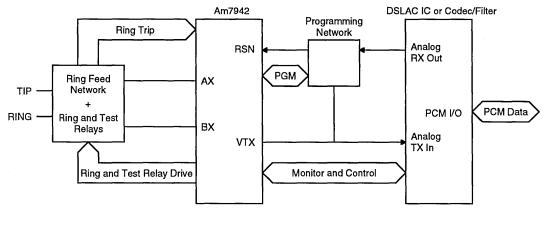

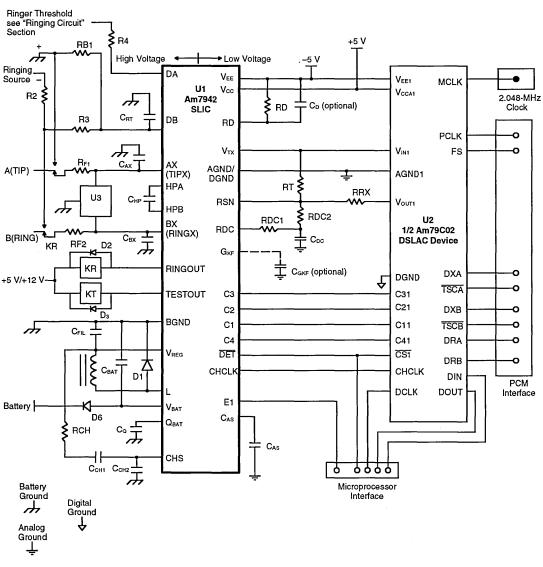

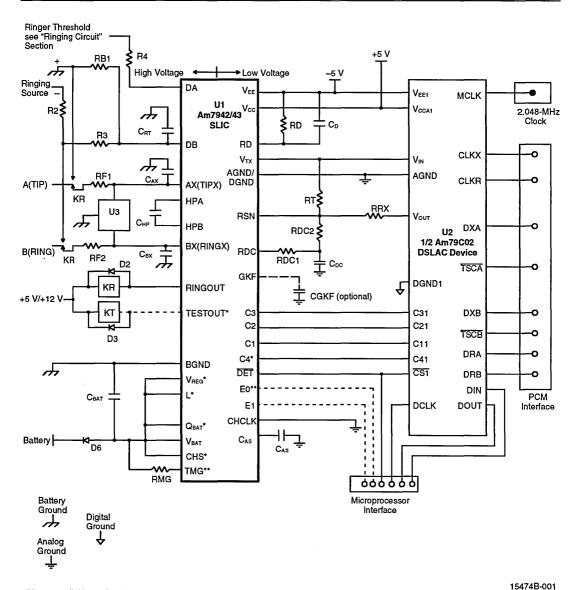

AMD's PBX SLICs are the Am7942 and Am7943(A). Both are compliant to EIA/TIA-464-A and ETSI-TE10-02 PBX standards, and will operate over a wide range of battery voltages.

The Am7942 incorporates a switching regulator function, similar to that offered on the Central Office SLICs, and is ideal for large PBXs intended for campus environments or other applications where loop length is expected to vary a great deal. In applications such as this, the switching regulator automatically adjusts the voltage applied to the SLIC's amplifiers to the minimum required to achieve the specified loop current, thus minimizing the system's power consumption. In cases where power consumption is not an issue, such as many 24-V battery applications, the switcher can be bypassed, eliminating the need for a few external components and lowering system cost. The Am7942 is tested under both 24- and 48-V battery conditions.

The Am7943(A) also incorporates power management circuitry, but in this case, power is dissipated in an external resistor. This approach, while not minimizing system power dissipation, lowers system cost by eliminating some external component requirements, and maintains device reliability, even at higher battery voltages.

Two versions of the Am7943(A) are offered: the standard Am7943 and the Am7943A. The primary difference between the two versions is the way the devices are tested. The standard version is tested with a 24-V battery and a 600-ohm load to ensure compliance to most PBX requirements. Polarity reversal and other functions not typically required by PBXs are not offered on the standard version. The "A" version of the Am7943 is specified and tested for compliance to Bellcore's TR-TSY-000057 standard required by Digital Loop Carriers (DLCs) and other types of switching equipment. The Am7943A is tested with a 48-V battery and a 900-ohm load.

Both the Am7942 and Am7943 support on-hook transmission and offer extended temperature performance, making either type suitable for Digital Loop Carriers and other applications. The signal transmission functions of all AMD SLICs include both two-to-four-wire and four-to-two-wire conversion. The two-wire termination impedance is programmable with a single external impedance. The companion AMD SLAC or DSLAC IC (Single-Channel or Dual-Channel Subscriber Line Audio-Processing Circuit) has a digital balancing filter that provides the trans-hybrid loss function. If the DSLAC IC is not used, most codec/filters provide an uncommitted op amp for this purpose.

The SLIC's battery feed architecture makes their DC feed characteristics programmable with external resistors. Furthermore, these characteristics are independent of battery variations.

A polarity reversal function is provided on all SLICs which transposes the normal voltage sense of the A(TIP) and B(RING) leads with a controlled transition time. All transmission functions continue normally following the transition. A disable mode is also provided, limiting loop current and cutting power dissipation while allowing the full complement of supervisory functions to be utilized.

The supervisory functions of off-hook detection and ring trip detection are read through a single, TTL-compatible output. To eliminate noise-induced errors, the off-hook detector signal may be filtered. Off-hook detection has a threshold that is set by the value of an external resistor. Additional supervisory controls put the A lead into an open circuit or high-impedance state suitable for application in ground start systems. Similarly, both the A and B leads may be open circuited to clear relays, recover from line faults, or turn off out-of-service lines. Relay drivers support ring and/or test relay functions, or can be used for other functions such as activating a message waiting lamp.

The SLIC's user-programmable states are controlled by a TTL-compatible code. The control inputs are designed to easily interface to popular single-chip microcontrollers, such as the industry standard 8051, or to latched outputs from a SLAC or DSLAC device.

# PRELIMINARY

# Am7942

# Subscriber Line Interface Circuit

# **DISTINCTIVE CHARACTERISTICS**

- Programmable constant current feed

- Receive current gain = 200

- Programmable loop detect threshold

- Low standby power

- Performs polarity reversal

- Ground-key detector

- Pin for external ground-key noise filter capacitor

- Test relay driver option (PLCC only)

- –19 V to –63 V battery operation

Tip open state for ground start lines

- Meets EIA/TIA-464-A

- On-chip switching regulator for low-power dissipation

- Can be used without switching regulator with 24-V battery

- Two-wire impedance set by single external impedance

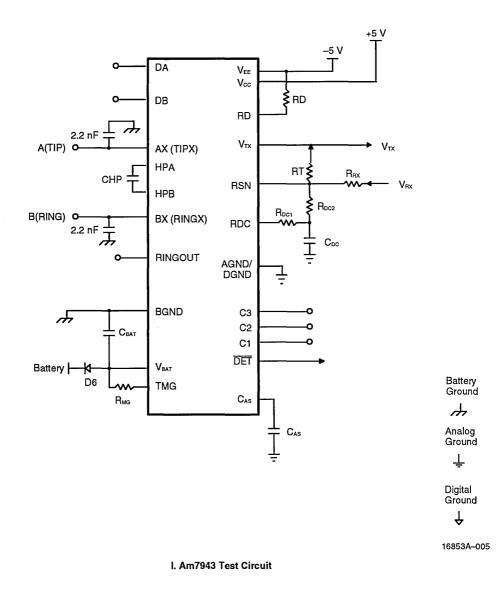

This document contains information on a product under development at Advanced Micro Devices, Inc. The information is intended to help you evaluate this product. AMD reserves the right to change or discontinue work on this proposed product without notice. 15474A-001

#### 1-19

Advanced Micro Devices

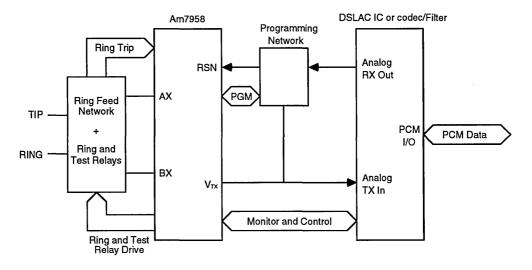

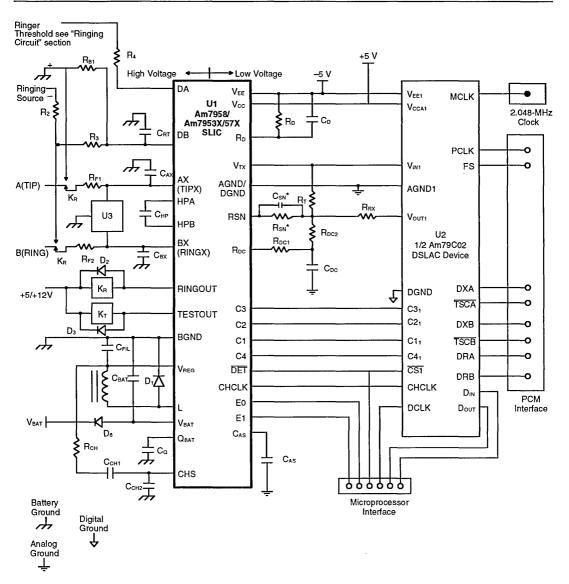

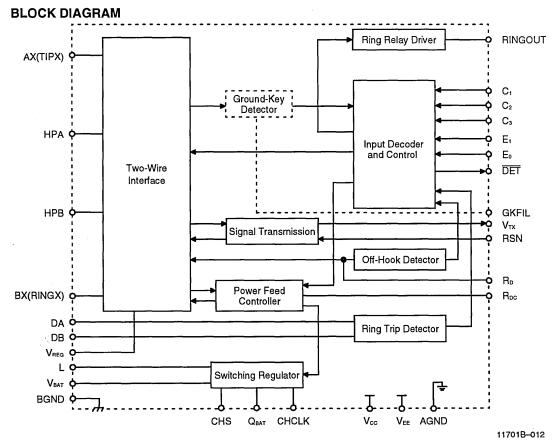

# SYSTEM BLOCK DIAGRAM

**Two-Wire**

Four-Wire

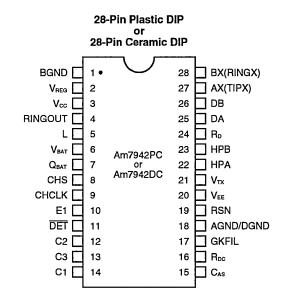

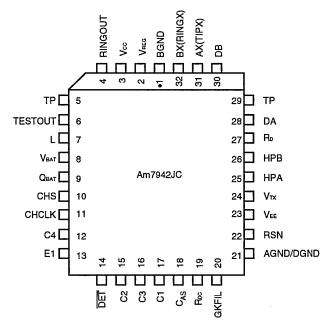

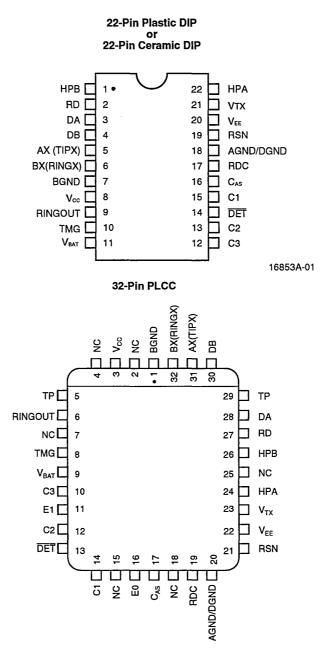

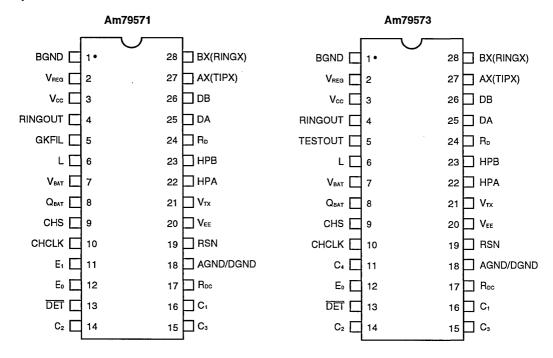

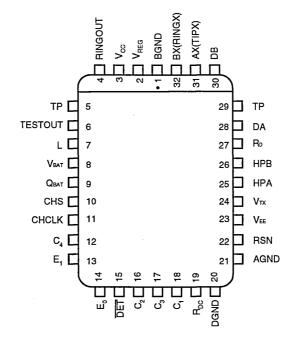

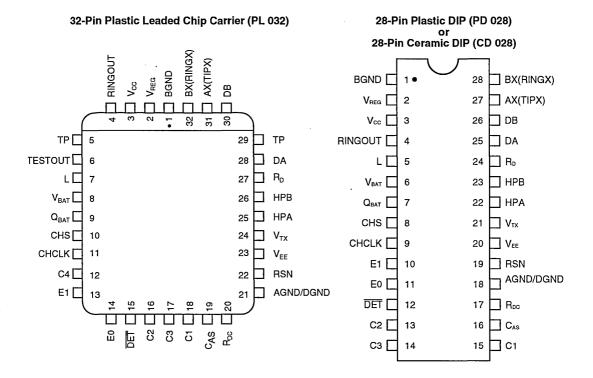

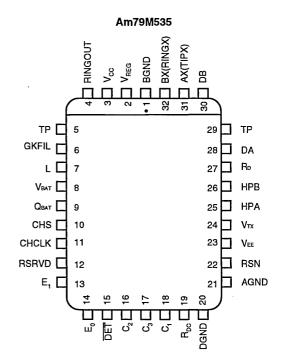

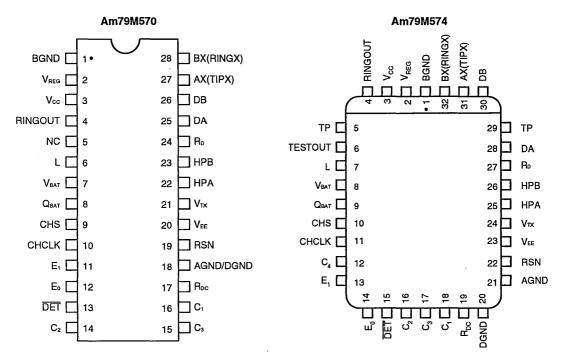

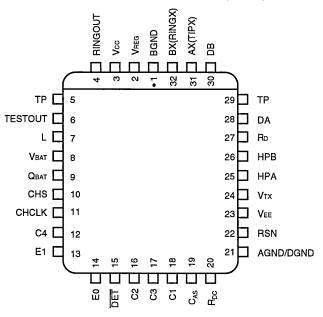

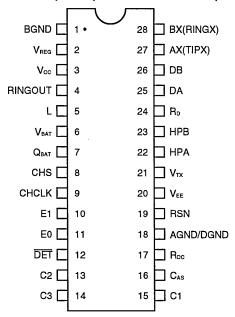

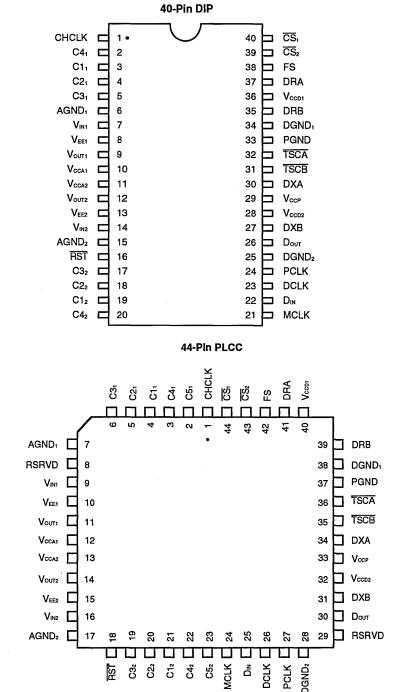

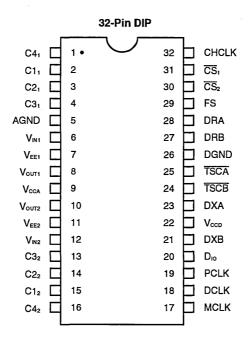

# **CONNECTION DIAGRAMS**

Notes: 1. Pin 1 is marked for orientation. 2. TP is a thermal conduction pin tied to substrate (Q<sub>BAT</sub>).

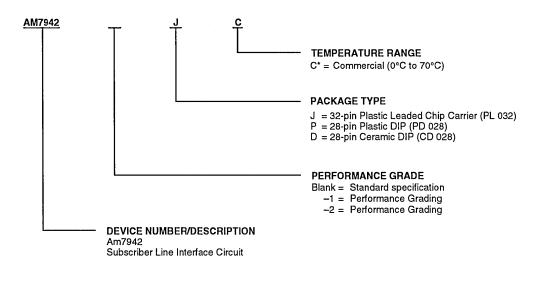

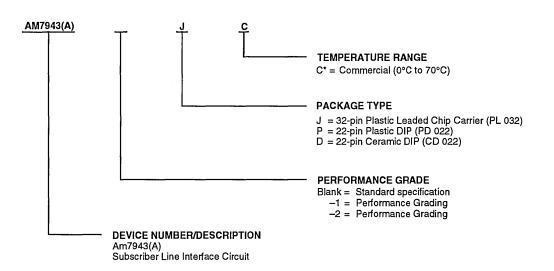

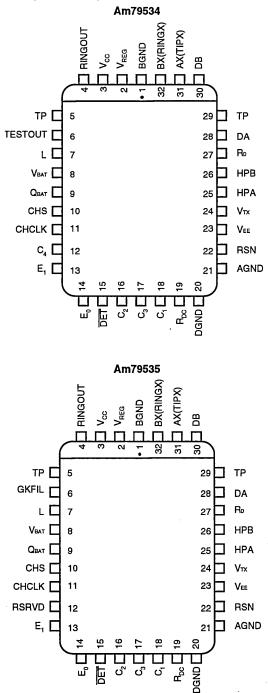

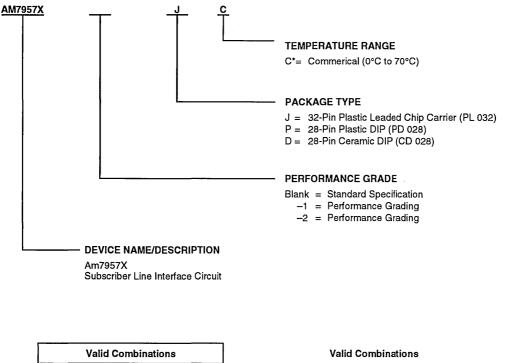

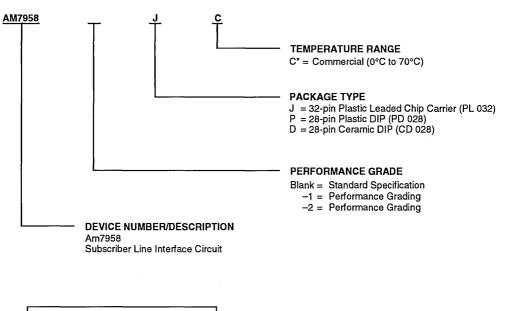

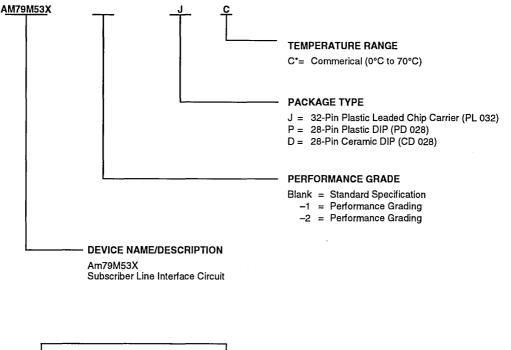

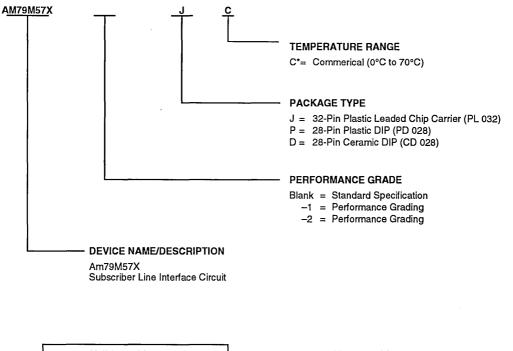

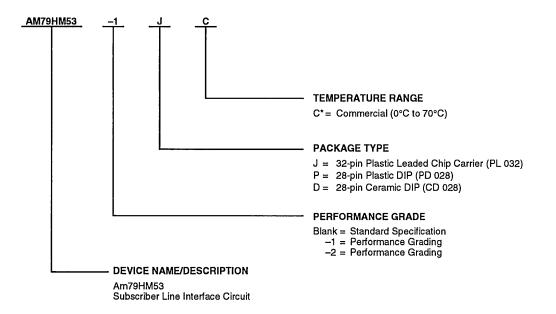

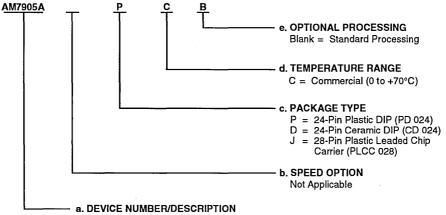

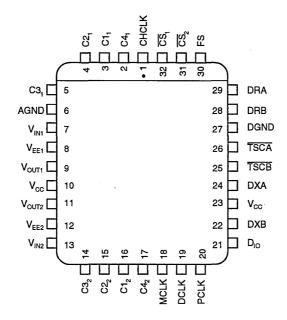

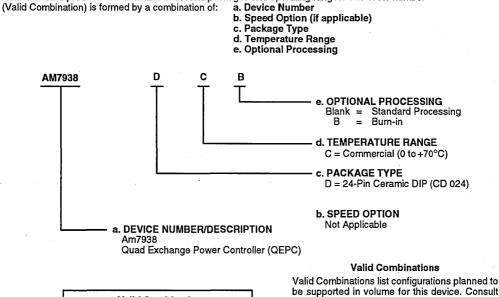

# ORDERING INFORMATION Standard Products

AMD® standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

| Valid Combinations |                  |  |  |  |  |  |

|--------------------|------------------|--|--|--|--|--|

|                    | DC, JC, PC       |  |  |  |  |  |

| AM7942             | –1DC, –1JC, –1PC |  |  |  |  |  |

|                    | –2DC, –2JC, –2PC |  |  |  |  |  |

#### Valid Combinations

Valid Combinations lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD standard military grade products.

\*The performance specifications contained in this data sheet are valid for the commercial temperature range only. See the SLIC Extended Temperature Supplement for information on industrial temperature range (-40°C to +85°C) specifications.

# **PIN DESCRIPTION**

#### AGND/DGND Ground

Analog and Digital ground.

#### AX(TIPX) (Output)

Output of A(TIP) power amplifier.

#### BGND Ground

Battery (power) ground.

BX(RINGX) (Output) Output of B(RING) power amplifier.

#### C3-C1 Decoder (Inputs)

TTL compatible. C3 is MSB and C1 is LSB.

#### CHCLK Chopper Clock (Input)—(see Note 1)

Input to switching regulator (TTL compatible). Frequency = 256 kHz (nominal).

# CHS

#### Chopper Stabilization (Input)—(see Note 1)

Connection for external chopper stabilizing components.

# DA

#### **Ring Trip Negative (Input)**

Negative input to ring trip comparator.

#### DB

# Ring Trip Positive (Input)

Positive input to ring trip comparator.

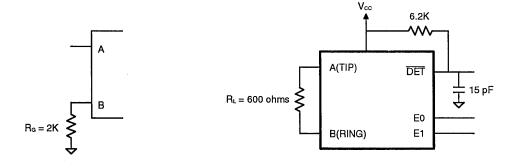

# DET

# Switch Hook Detector (Output)

When enabled, a logic Low indicates the selected detector is tripped. The detector is selected by the logic inputs (C3–C1, E1). The output is open-collector with a builtin 15K pull-up resistor.

# E1

# Ground-Key Enable (Input)

E1 = High connects the ground-key detector to  $\overline{\text{DET}}$ . E1 = Low connects the off-hook or ring trip detector to  $\overline{\text{DET}}$ .

# HPA

A(TIP) side of high-pass filter capacitor.

#### HPB

B(RING) side of high-pass filter capacitor.

#### L

#### Switching Regulator Power Transistor (Output)—(see Note 1)

Connection point for filter inductor and anode of catch diode. This pin will have up to 60 V of pulse waveform on it and must be isolated from sensitive circuits. Extreme care must be taken to keep the diode connections short because of the high currents and high di/dt.

# QBAT

Quiet Battery-(see Note 1)

Filtered battery supply for the signal processing circuits.

# R₀

Threshold modification and filter point for the off-hook detector.

#### RDC

Connection point for the DC feed current programming network. The other end of the network connects to the receiver summing node (RSN). The sign of  $V_{\text{RDC}}$  is minus for normal polarity and plus for reverse polarity.

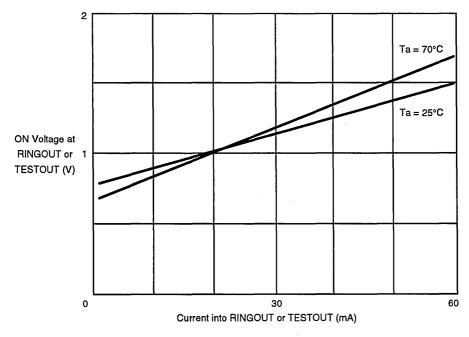

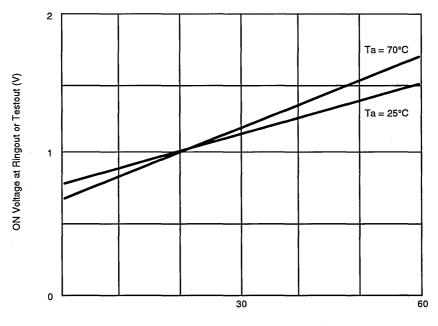

#### RINGOUT

#### **Ring Relay Driver (Output)**

Open collector driver with emitter internally connected to BGND.

#### TESTOUT

#### Test Relay Driver (Output)—(see Note 3)

Open collector driver with emitter internally connected to BGND.

# C4

# Test Relay Driver Command (Input)—(see Note 3)

TTL compatible. A logic Low enables the driver.

# GKFIL

#### (see Notes 2 and 3)

Connection for external ground-key, noise-filter capacitor.

#### RSN

#### **Receive Summing Node (Input)**

The metallic current (both AC and DC) between A(TIP) and B(RING) is equal to 200 times the current into this pin. The networks which program receive gain, two-wire impedance, and feed resistance all connect to this node.

chopper stabilization.

|    | - |   |   |   |   |   | - |   |

|----|---|---|---|---|---|---|---|---|

| PR | E | L | L | M | N | А | к | Y |

| it Audio (Output)                                                                                                                                                              |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| This output is a unity gain version of the AX(TIPX) and<br>BX(RINGX) metallic voltage. The other end of the two-<br>wire input impedance programming network connects<br>here. |  |  |  |  |  |

| ce Filter Capacitor                                                                                                                                                            |  |  |  |  |  |

| itor should be connected to this pin to filter anti-saturation reference voltage.                                                                                              |  |  |  |  |  |

|                                                                                                                                                                                |  |  |  |  |  |

- Notes: 1. All pins, except CHCLK, connect to V<sub>BAT</sub> when using SLIC without a switching regulator. CHCLK is connected to AGND/DGND.

- 2. To prevent noise pickup by the detection circuits when using ground-key mode (E1 = logical 1), a 3300-pF minimum bypass capacitor is recommended between the GKFIL pin and ground.

- 3. Not available on standard 28-pin DIP package.

# ABSOLUTE MAXIMUM RATINGS

| Storage Temperature55°C to +150°C                                                                                      |

|------------------------------------------------------------------------------------------------------------------------|

| $V_{cc}$ with respect to AGND/DGND $\ .\ .\ -0.4$ V to +7.0 V                                                          |

| $V_{\mbox{\tiny EE}}$ with respect to AGND/DGND $\ .\ .\ +0.4$ V to $-7.0$ V                                           |

| $V_{\mbox{\tiny BAT}}$ with respect to AGND/DGND $\ldots$ +0.4 V to -70 V                                              |

| Note: Rise time of $V_{\text{BAT}}$ (dv/dt) must be limited to 27 V/µs or less when $Q_{\text{BAT}}$ bypass = 0.33 µF. |

| BGND with respect to                                                                                                   |

| AGND/DGND +1.0 V to -3.0 V                                                                                             |

| AX(TIPX) or BX(RINGX) to BGND:                                                                                         |

| Continuous70 V to +1.0 V                                                                                               |

| 10 ms (F = 0.1 Hz)70 V to +5.0 V                                                                                       |

| 1 μs (F = 0.1 Hz) –90 V to +10 V                                                                                       |

| 250 ns (F = 0.1 Hz)120 V to +15 V                                                                                      |

| Current from AX(TIP) or BX(RING) ±150 mA                                                                               |

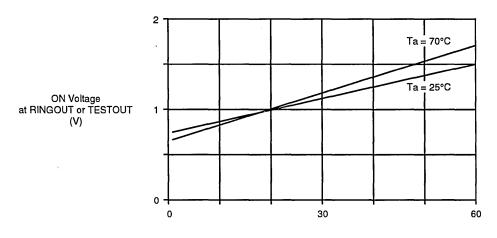

| Voltage on RINGOUT BGND to 70 V above $Q_{\text{BAT}}$                                                                 |

| Voltage on TESTOUT BGND to 70 V above $Q_{\mbox{\tiny BAT}}$                                                           |

| Current through Relay Drivers 60 mA                                                                                    |

| Voltage on Ring Trip Inputs                                                                                            |

| (DA and DB) V $_{\mbox{\tiny BAT}}$ to 0 V                                                                             |

| Current into Ring Trip Inputs $\pm 10 \text{ mA}$                                                                      |

| Peak Current into Regulator                                                                                            |

| Switch (L pin) 150 mA                                                                                                  |

| Switcher Transient Peak Off                                                                                            |

| Voltage on L pin                                                                                                       |

| C4-C1, E1, CHCLK to                                                                                                    |

| AGND/DGND                                                                                                              |

| Maximum Power Dissipation, $T_A$ (see note) $\hdots$ 70°C                                                              |

| In 28-pin ceramic DIP package                                                                                          |

| In 28-pin plastic DIP package                                                                                          |

| In 32-pin PLCC package 1.74 W                                                                                          |

| Note: Thermal limiting circuitry on chip will shut down the                                                            |

Note: Thermal limiting circuitry on chip will shut down the circuit at a junction temperature of about 165°C. The device should never see this temperature and operation above 145°C junction temperature may degrade device reliability. See SLIC Packaging Considerations section for more information.

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may effect device reliability.

#### **OPERATING RANGES**

#### Commercial (C) Devices

| Ambient Temperature 0°C to +70°C                  |

|---------------------------------------------------|

| $V_{cc}$ $\ldots$                                 |

| $V_{\mbox{\tiny EE}}$ $\ldots$                    |

| $V_{\scriptscriptstyle BAT}$                      |

| AGND/DGND 0 V                                     |

| BGND with respect to                              |

| AGND/DGND                                         |

| Load Resistance on $V_{Tx}$ to Ground 10 Kohm Min |

\*Can be used without switching regulator components in this range of battery voltages provided maximum power dissipation specifications are not exceeded.

"-2" performance grade SLICs are functional from -40°C to +85°C. See the SLIC Extended Temperature Supplement for information on industrial temperature range (-40°C to +85°C) specifications.

Operating ranges define those limits between which the functionality of the device is guaranteed.

# **ELECTRICAL CHARACTERISTICS (see Note 1)**

| ······································     |                                      |              |            | P                 | relimina | у                 | T         |

|--------------------------------------------|--------------------------------------|--------------|------------|-------------------|----------|-------------------|-----------|

| Description                                | Test Conditions                      | Notes        | P.G.*      | Min               | Тур      | Max               | Unit      |

| Analog (V <sub>Tx</sub> ) Output Impedance |                                      | 5            |            | 3                 |          | ohm               |           |

| Analog ( $V_{Tx}$ ) Output Offset          |                                      |              | -1<br>-2   | -35<br>-35<br>-30 |          | +35<br>+35<br>+30 | mV        |

| Analog (RSN) Input Impedance               | 300 Hz to 3.4 kHz                    |              |            |                   | 1        | 20                | ohm       |

| Longitudinal Impedance at AX or BX         |                                      |              |            |                   |          | 35                | ohm       |

| Overload Level                             | four-wire<br>two-wire                | 2            |            | -2.5              |          | +2.5              | Vpk       |

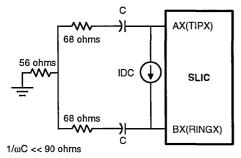

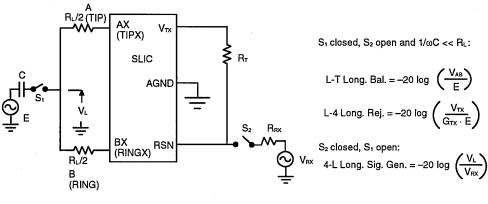

| Transmission Performance, two-wire i       | mpedance (see Test Circu             | rit D)       |            |                   |          |                   |           |

| Two-Wire Return Loss                       | 300 Hz to 3400 Hz                    | 5, 10        |            | 26                |          |                   | dB        |

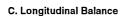

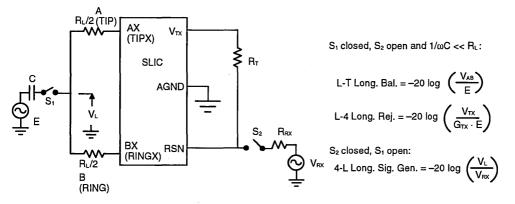

| Longitudinal Balance (two-wire and fo      | ur-wire, see Test Circuit C          | ;); R⊾ = 600 | ohms       |                   |          |                   |           |

|                                            | 200 Hz to 1 kHz<br>Normal Polarity   |              | -1<br>-2   | 52<br>63<br>63    |          |                   | dB        |

|                                            | 200 Hz to 1 kHz<br>Reverse Polarity  |              | 1<br>2     | 52<br>54<br>54    |          |                   | dB        |

| Longitudinal to Metallic L-T, L-4          | 1 kHz to 3.4 kHz<br>Normal Polarity  |              | 1<br>2     | 52<br>58<br>58    |          |                   | dB        |

|                                            | 1 kHz to 3.4 kHz<br>Reverse Polarity |              | -1<br>-2   | 52<br>54<br>54    |          |                   | dB        |

| Longitudinal Signal Generation 4-L         | 300 Hz to 800 Hz<br>Reverse Polarity |              | -1<br>-2   | 40<br>40<br>42    |          |                   | dB        |

| Longitudinal Current Capability per Wire   | Active State<br>Disable State        |              | all<br>all |                   | 28<br>18 |                   | mA<br>RMS |

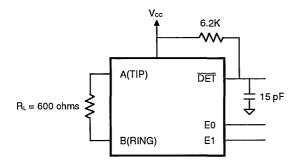

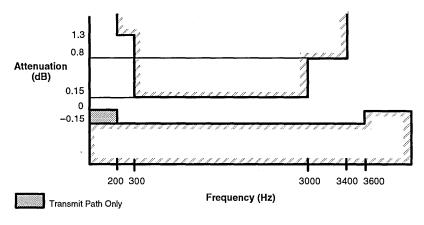

Insertion Loss (two-wire to four-wire and four-wire to two-wire, see Test Circuits A and B) Battery = -48 V,  $R_{LDC} = R_{LAC} = 600$  ohms; Battery = -24 V,  $R_{LDC} = 300$  ohms,  $R_{LAC} = 600$  ohms

|                          |                   |     |    | -0.15 | +0.15     |    |

|--------------------------|-------------------|-----|----|-------|-----------|----|

| Gain Accuracy            | 0 dBm, 1 kHz      |     | -1 | -0.15 | +0.15     | dB |

|                          |                   |     |    |       |           |    |

|                          |                   |     |    | -0.15 | +0.15     |    |

| Variation with Frequency |                   |     | -1 | -0.15 | +0.15     | dB |

| Variation with Frequency |                   |     | -2 | -0.10 | <br>+0.10 |    |

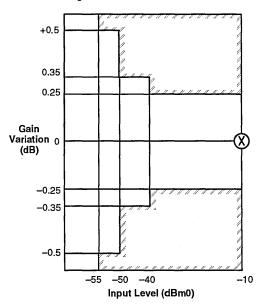

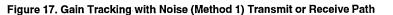

| Osia Tradina             | +7 dBm to –55 dBm | 5   |    | 0.10  | .0.10     | dB |

| Gain Tracking            | Reference: –0 dBm | ) ° |    | -0.10 | +0.10     |    |

\*P.G. = Performance Grade

# PRELIMINARY

AMD

# ELECTRICAL CHARACTERISTICS (continued) Т

|                                                                                          | 1              |                                        |             |          | P                                                                                                                                                                                                                                         | relimina                                              | <u>y</u>                |      |

|------------------------------------------------------------------------------------------|----------------|----------------------------------------|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------|------|

| Description                                                                              |                | Test Conditions                        | Notes       | P.G.     | Min                                                                                                                                                                                                                                       | Тур                                                   | Max                     | Unit |

| Balance Return Signal (fo<br>Battery = -48 V, RLDC = RLA                                 |                |                                        |             | lac = 60 | 0 ohms                                                                                                                                                                                                                                    |                                                       |                         |      |

| Gain Accuracy                                                                            |                | 0 dBm, 1 kHz                           |             | -1<br>-2 | -0.15<br>-0.15<br>-0.10                                                                                                                                                                                                                   |                                                       | +0.15<br>+0.15<br>+0.10 | dB   |

| Variation with Frequency                                                                 |                | 300 Hz to 3400 Hz<br>Relative to 1 kHz | 3           |          | -0.10                                                                                                                                                                                                                                     |                                                       | +0.10                   | dB   |

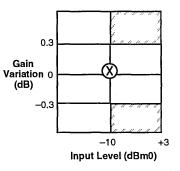

| Gain Tracking                                                                            |                | +3 dBm to -55 dBm<br>Reference: 0 dBm  | 5           |          | -0.10                                                                                                                                                                                                                                     |                                                       | +0.10                   | dB   |

| Group Delay                                                                              |                | f = 1 kHz                              | 5, 12       |          |                                                                                                                                                                                                                                           | 5.3                                                   |                         | μs   |

| Total Harmonic Distortion<br>Battery = $-48 \text{ V}, \text{ R}_{LDC} = \text{ R}_{LA}$ |                | our-wire or four-wire to t             | wo-wire, se | e Test   | Circuits A                                                                                                                                                                                                                                | A and B)                                              |                         |      |

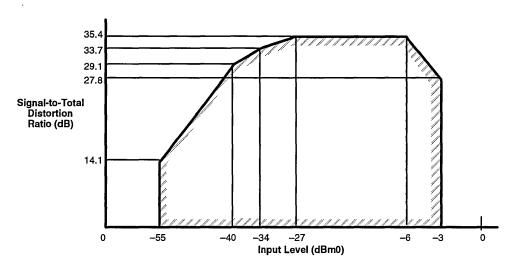

| Harmonic Distortion<br>300 Hz to 3400 Hz                                                 |                | 0 dBm<br>+7 dBm                        |             |          |                                                                                                                                                                                                                                           | 64<br>55                                              | 50<br>40                | dB   |

| ldle Channel Noise<br>Battery = −48 V, Rւ⊳c = Rւ₄                                        | .c = 600 ohms; | Battery = –24 V, R⊥Dc = 3              | 00 ohms, R  | lac = 60 | 0 ohms                                                                                                                                                                                                                                    |                                                       |                         |      |

| C-Message Weighted Noise                                                                 |                | two-wire<br>four-wire                  | - 5         |          |                                                                                                                                                                                                                                           | +7<br>+7                                              | +10<br>+10              | dBrn |

| Psophometric Weighted Noise                                                              |                | two-wire<br>four-wire                  | _           |          |                                                                                                                                                                                                                                           | 83<br>83                                              | -80                     | dBm  |

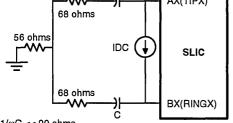

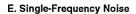

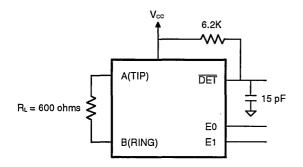

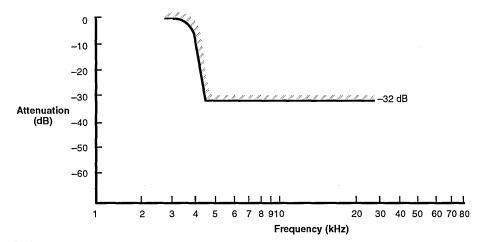

| Single Frequency Out-of-Band Noise (                                                     |                |                                        | <b>I</b>    | I        | L                                                                                                                                                                                                                                         |                                                       |                         | I    |

|                                                                                          | 4 kHz to 9 kH  |                                        | 5           | <u> </u> |                                                                                                                                                                                                                                           | 76                                                    |                         |      |

| Metallic                                                                                 | 9 kHz to 1 M   | Hz                                     | 4, 5, 8     |          |                                                                                                                                                                                                                                           | -76                                                   |                         | dBm  |

|                                                                                          | 256 kHz and    | harmonics*                             | 4,5         |          |                                                                                                                                                                                                                                           | -63                                                   |                         | 1    |

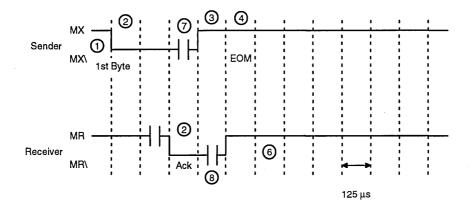

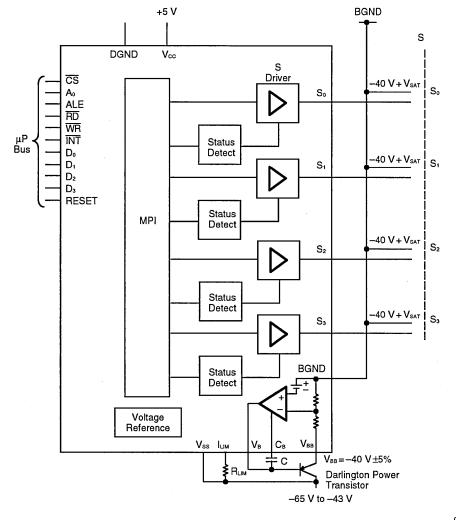

|                                                                                          | 1 kHz to 15 k  | Hz                                     | 5           |          |                                                                                                                                                                                                                                           | -70                                                   |                         |      |