### MACH<sup>®</sup> 1, 2, 3, and 4 Family Data Book

High Density EE CMOS Programmable Logic 1995 Advanced Micro Devices

AMD's Marketing Communications Department specifies environmentally sound agricultural inks and recycled papers, making this book highly recyclable.

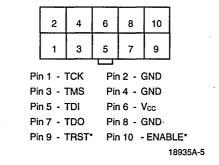

## MACH<sup>®</sup> 1, 2, 3, and 4 Data Book and Design Guide

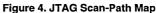

1995

ADVANCED MICRODEVICES

Л

#### © 1995 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD\* assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

#### Trademarks

AMD, the AMD logo, MACH, MACHXL, PAL, PALASM and MACHPRO are registered trademarks of Advanced Micro Devices, Inc. 29K, Am29200, Am29240, Am29245, Am29243, and LabPro are trademarks of Advanced Micro Devices, Inc. FusionPLD is a service mark of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies. Cover plane image courtesy of NASA. First introduced in the Fall of 1990, MACH (Macro Array CMOS High-density) devices have set the industry standard for high-speed, predictable worst-case pin-to-pin delays for devices ranging from 900 to 3,600 PLD gates. For the first time, higher-density electrically-erasable (EE) CMOS PAL®-like devices with truly predictable speeds were widely available. The MACH family's already-familiar architecture aided its rapid acceptance. Today, the MACH family has been designed into thousands of systems around the world and several million MACH devices have been shipped.

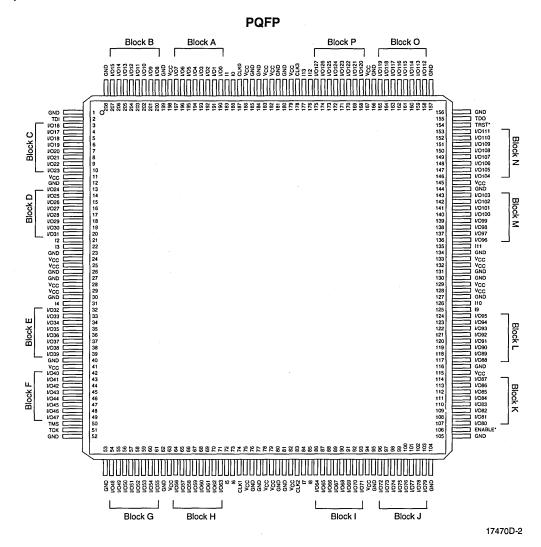

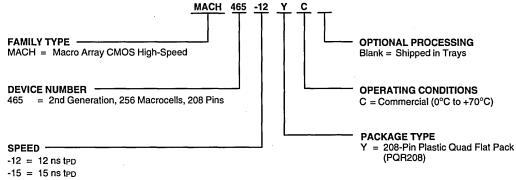

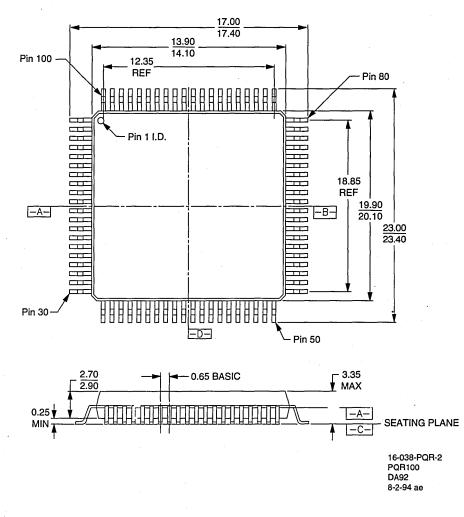

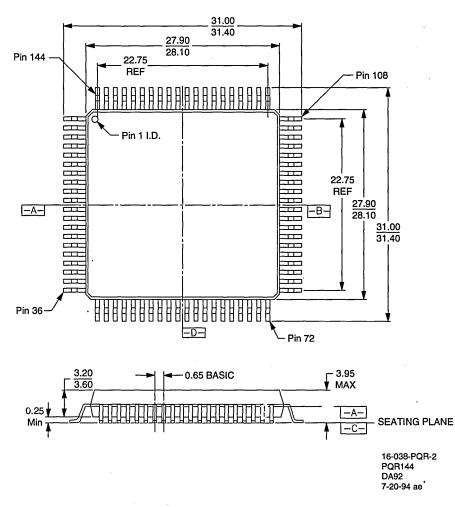

Based on customer feedback on the MACH 1 and 2 family, Advanced Micro Devices (AMD) created the MACH 3 and 4 family. Like the first generation MACH 1 and 2 devices, the newer MACH 3 and 4 devices offer the same, truly predictable pin-to-pin delays, but with greater density, flexibility and higher pin-count packages. The MACH 3 and 4 family feature synchronous and asynchronous operation, 5-volt on-board programming and JTAG in packages greater than 84 pins, densities from 3,500 to 10,000 PLD gates, and 84 to 208 pins in PLCC and PQFP packages.

However, the evolution of the MACH family did not stop here. As a growing number of customer designs migrated from PAL to MACH devices, they required solutions offering even higher density, greater flexibility and higher value. Through leading-edge process technology and design innovation, AMD introduced Performance Plus devices, enhanced versions of popular MACH 1 and 2 devices. The Performance Plus devices build upon the same densities and solid benefits of the original MACH 1 and 2 family, adding improved routing, power management, Bus-Friendly I/Os, and PCI compliance.

An early pioneer and leader in the programmable logic world, AMD invented the industry-standard PAL devices and 22V10. AMD continued that tradition with the MACH family. Enabled by advanced process technology, which began with bipolar and today is state-of-the-art EE CMOS, AMD is committed to innovation in programmable logic. At AMD, we believe: "If it's a good idea. If it makes a difference to our customers. Run with it." The result: designers leverage the rapid design with and advanced features of MACH devices to speed their own value-added products to market.

Cheir Herry/

Chris Henry Director of Marketing Programmable Logic

#### INTRODUCTION

This book is a guide to the MACH 1, 2, 3, and 4 families of programmable logic from Advanced Micro Devices. These devices provide programmable logic capabilities from 900 PLD gates to 10,000 PLD gates. Included in this book is an overview of and data sheets for the MACH 1, 2, 3, and 4 family members.

The overview covers details affecting the entire MACH 1 and 2, and MACH 3 and 4 device families including a brief discussion of design software used in configuring the devices. Because of the common architecture, understanding the whole family yields knowledge about much of the individual members.

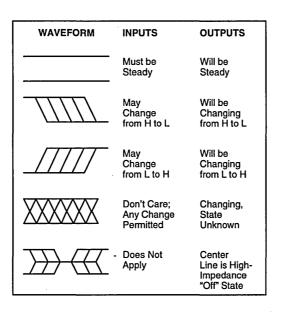

The data sheets discuss items that are specific to each device. They contain the basic DC and switching specifications. Other general specifications, such as switching waveforms and endurance information, follow the data sheets since they are consistent for all devices.

Rounding out this book are application notes. The application notes range in topic from the general methodology of designing with MACH devices, to the theory and use of advanced MACH features such as on-board programming and test via JTAG pins, to specific MACH design examples.

### **TABLE OF CONTENTS**

| Â | • |   |

|---|---|---|

|   | 7 | ◄ |

| Chapter 1 | MACH 1 and 2 Device Families Description                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-3                                                                                                   |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|           | Synchronous MACH 1 and 2 Devices                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-7                                                                                                   |

|           | MACH 1 Family<br>MACH110-12/15/20<br>MACH111-5/7/10/12/15/20<br>MACH120-12/15/20<br>MACH130-15/20<br>MACH131-7/10/12/15/20                                                                                                                                                                                                                                                                                                                                | 1-13<br>1-27<br>1-43<br>1-59<br>1-73                                                                  |

|           | MACH 2 Family         MACH210-7/12/15/20         MACHLV210-10/12/15/20         MACH211-7/12/15/20         MACH220-10/12/15/20         MACH220-10/12/15/20         MACH221-7/10/12/15/20         MACH230-10/15/20         MACH231-7/10/12/15/20                                                                                                                                                                                                            |                                                                                                       |

| Chapter 2 | MACH 3 and 4 Device Families                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-3<br>2-19<br>2-33<br>2-55<br>2-75                                                                   |

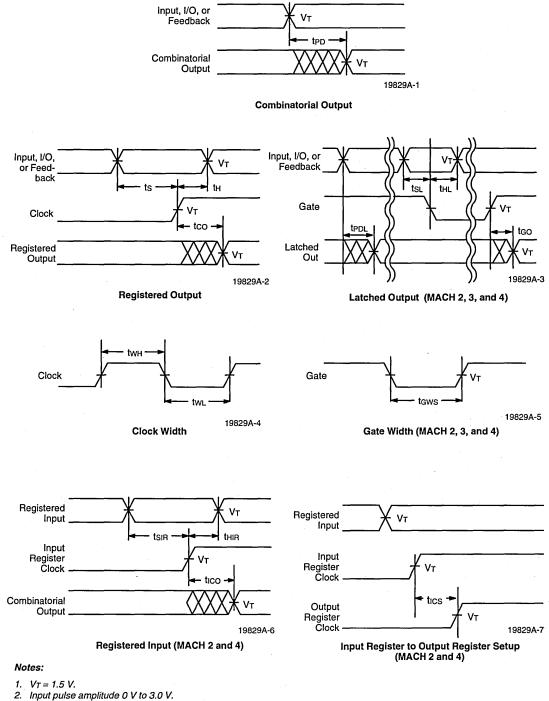

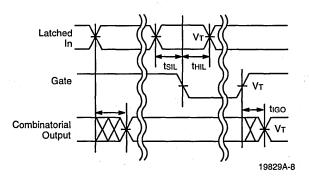

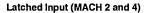

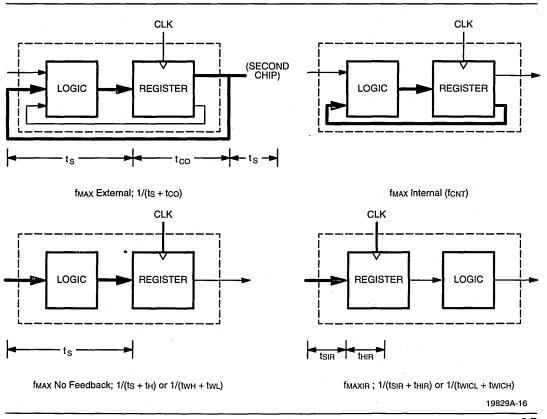

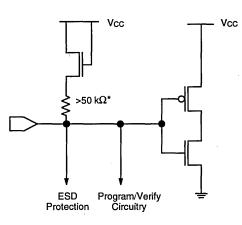

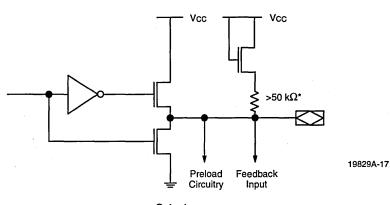

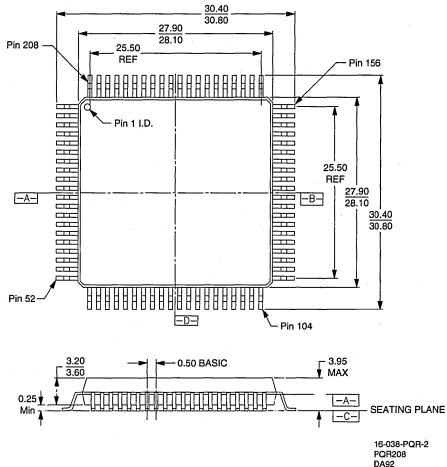

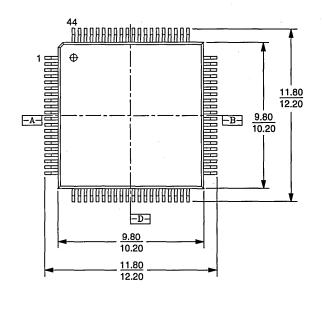

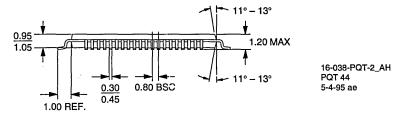

| Chapter 3 | General Information         Switching Waveforms         Key to Switching Waveforms         Switching Test Circuit         fMax Parameters         Endurance Characteristics         Input/Output Equivalent Schematics         Power-Up Reset         Using Preload and Observability         Development Systems         Approved Programmers         Programmer Socket Adapter         Design Tool Support for MACH Devices         Physical Dimensions | 3-1<br>3-3<br>3-6<br>3-6<br>3-7<br>3-8<br>3-8<br>3-10<br>3-11<br>3-12<br>3-14<br>3-15<br>3-17<br>3-25 |

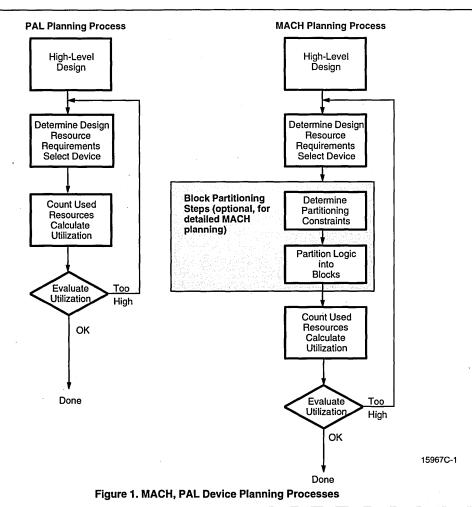

| Chapter 4 | Application NotesMACH Device Design Planning GuideEvolution of Bus-Friendly Inputs and I/OsPCI Bus Interface Using AMD PLDsIntroduction to JTAG and Five-VoltProgramming with MACH 3 and 4 DevicesAdvanced In-Circuit ProgrammingGuidelines for MACH 3 and 4 Devices                                                                                                                                                                                      | 4-3<br>4-17<br>4-25<br>4-61<br>4-67                                                                   |

CHAPTER

### MACH 1 AND 2 DEVICE FAMILIES DESCRIPTION

#

| Synchronous MACH 1 and 2 Devices                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MACH 1 Family                                                                                                                                                                                                                                                                                           |

| MACH110-12/15/20       1-1         MACH111-5/7/10/12/15/20       1-2         MACH120-12/15/20       1-4         MACH130-15/20       1-5         MACH131-7/10/12/15/20       1-7                                                                                                                         |

| MACH 2 Family       1-8         MACH210-7/12/15/20       1-12         MACHLV210-10/12/15/20       1-12         MACH215-12/15/20       1-14         MACH220-10/12/15/20       1-16         MACH221-7/10/12/15/20       1-18         MACH221-7/10/12/15/20       1-20         MACH230-10/15/20       1-21 |

4

ſ

### MACH 1 and 2 Device Families

High-Density EE CMOS Programmable Logic

#### DISTINCTIVE CHARACTERISTICS

- High-performance, high-density, electrically-erasable CMOS PLD families

- 900 to 3600 PLD gates

- 44 to 84 pins in cost-effective PLCC and TQFP packages

- 32 to 128 macrocells

- State-of-the art EE CMOS provides predictable design-independent high speeds

- Commercial 7/10/12/15/20-ns tpp. 133/100/76.9/66.6/50-MHz form

- Industrial 12/14/18/24, 80/61.5/53/38-MHz fcnt

- Synchronous and asynchronous devices

- PAL blocks connected by switch matrix

- Provides optimized global connectivity

- Switch matrix integrates blocks into uniform device

- Configurable macrocells

- Programmable polarity

- Registered or combinatorial

#### PRODUCT SELECTOR CLIDE

- Internal and I/O feedback

- D-type or T-type flip-flops

- Choice of clocks for each flip-flop

- Input registers for MACH 2 family

- Performance Plus devices such as the MACH111, MACH131, MACH211, MACH221, and MACH231 have a programmable power-down mode resulting in power savings of up to 75%

- The MACH111, MACH211, and MACH231 have improved routing over the MACH110, MACH210, and MACH230

- Extensive third-party software and programmer support through FusionPLD<sup>SM</sup> partners

- Schematic capture and text entry

- Compilation and JEDEC file generation

- Design simulation

- Logic and timing models

- Standard PLD programmers

- Each MACH product has a factory programming option available for high-volume applications

| Device      | Pins       | Macrocells | PLD Gates | Max<br>Inputs | Max<br>Outputs | Max<br>Flip-Flops | Speed<br>(ns)     |

|-------------|------------|------------|-----------|---------------|----------------|-------------------|-------------------|

| MACH 1 Fami | ly         |            |           | <u></u>       | •              |                   | •                 |

| MACH110     | 44         | 32         | 900       | 38            | 32             | 32                | 12, 15, 20        |

| MACH111     | 44         | 32         | 900       | 38            | 32             | 32                | 7, 10, 12, 15, 20 |

| MACH120     | 68         | 48         | 1200      | 56            | 48             | 48                | 12, 15, 20        |

| MACH130     | 84         | 64         | 1800      | 70            | 64             | 64                | 15, 20            |

| MACH131     | 84         | 64         | 1800      | 70            | 64             | 64                | 7, 10, 12, 15, 20 |

| MACH 2 Fami | ly         |            |           |               |                |                   |                   |

| MACH210     | 44         | 64         | 1800      | 38            | 32             | 64                | 7, 10, 12, 15, 20 |

| MACH211     | 44         | 64         | 1800      | 38            | 32             | 64                | 7, 10, 12, 15, 20 |

| MACH220     | _68        | 96         | 2400      | 56            | 48             | 96                | 12, 15, 20        |

| MACH221     | 68         | 96         | 2400      | 56            | 48             | 96                | 7, 10, 12, 15, 20 |

| MACH230     | 84         | 128        | 3600      | 70            | 64             | 128               | 15, 20            |

| MACH231     | 84         | 128        | 3600      | 70            | 64             | 128               | 7, 10, 12, 15, 20 |

| Asynchronou | s MACH Dev | /ice       |           |               |                | <u> </u>          | ······            |

| MACH215     | 44         | 64         | 1500      | 38            | 32             | 64                | 12, 15, 20        |

#### **GENERAL DESCRIPTION**

The MACH (Macro Array CMOS High-density) family provides a new way to implement large logic designs in a programmable logic device. AMD has combined an innovative architecture with advanced electrically-

Publication# 14051 Rev. | Amendment/0 Issue Date: May 1995

erasable CMOS technology to offer a device with several times the logic capability of the industry's most popular existing PAL device solutions at comparable speed and cost.

Advanced Micro Devices

###

Their unique architecture makes these devices ideal for replacing large amounts of TTL, PAL-device, glue, and gate-array logic. They are the first devices to provide such increased functionality with completely predictable, deterministic speed.

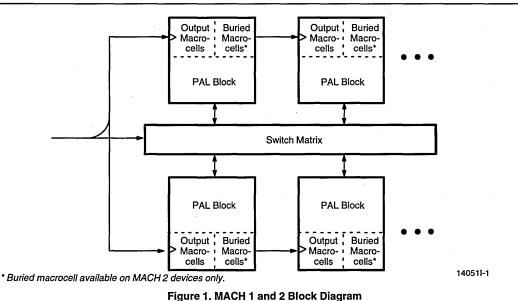

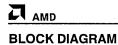

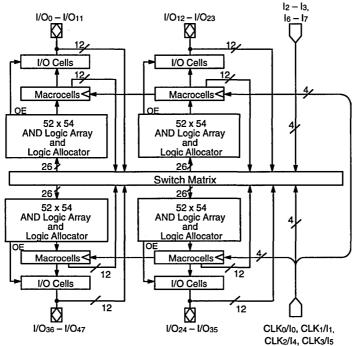

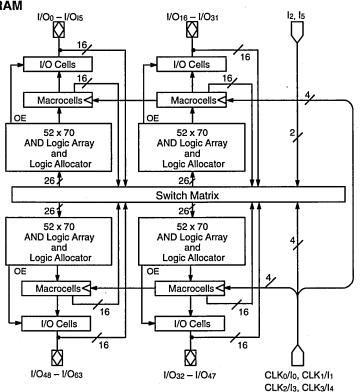

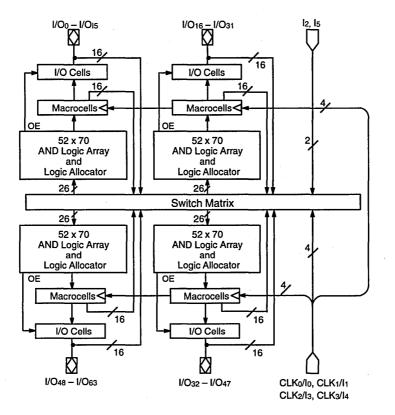

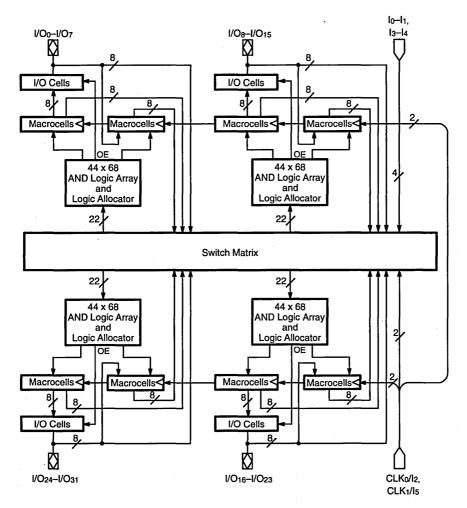

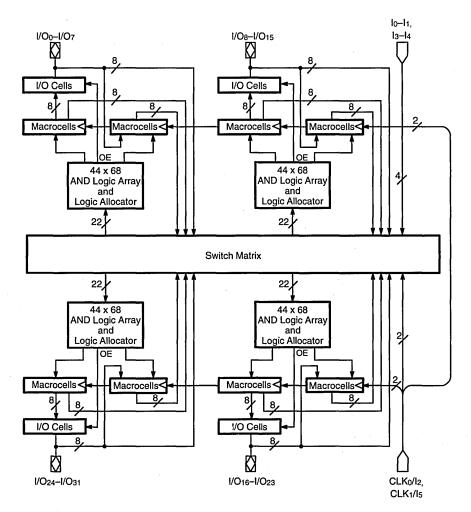

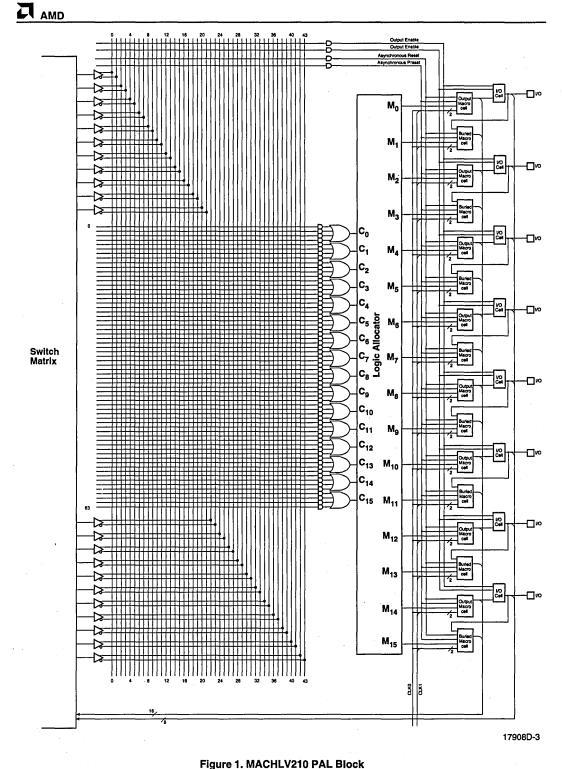

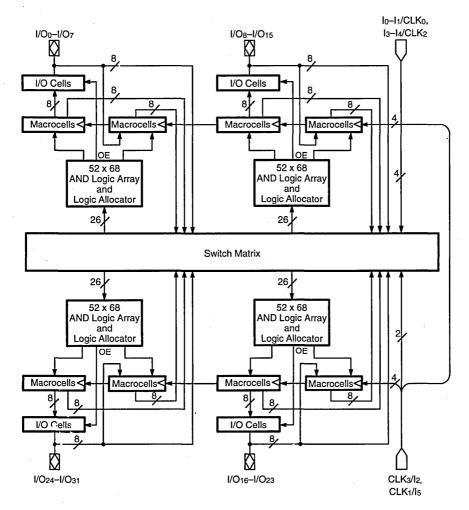

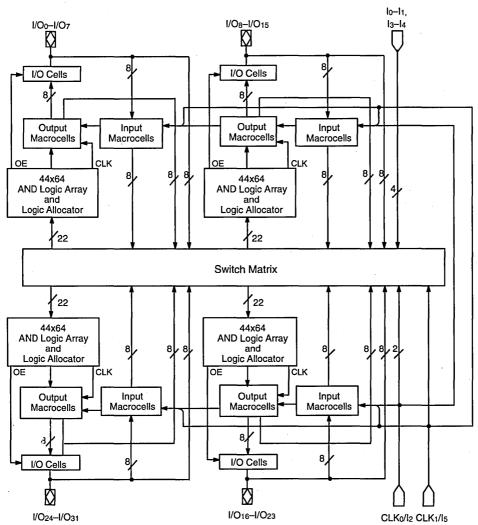

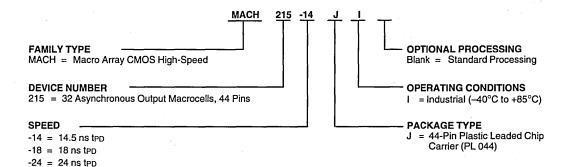

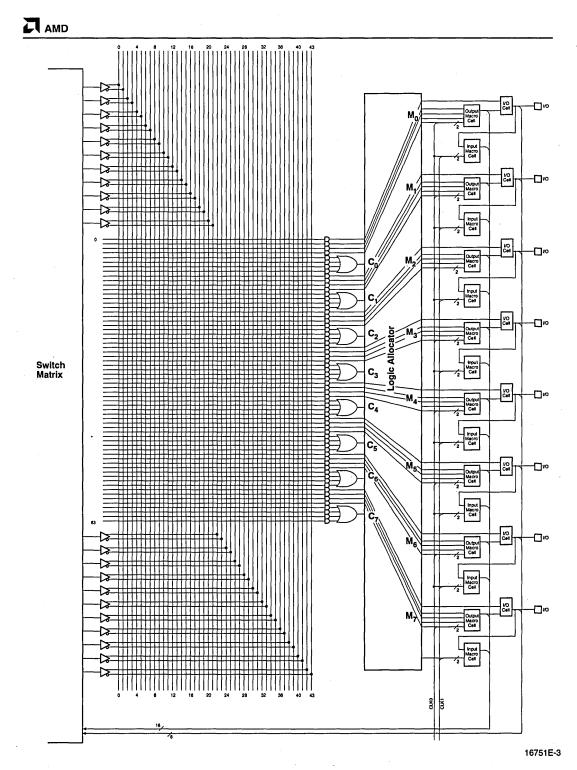

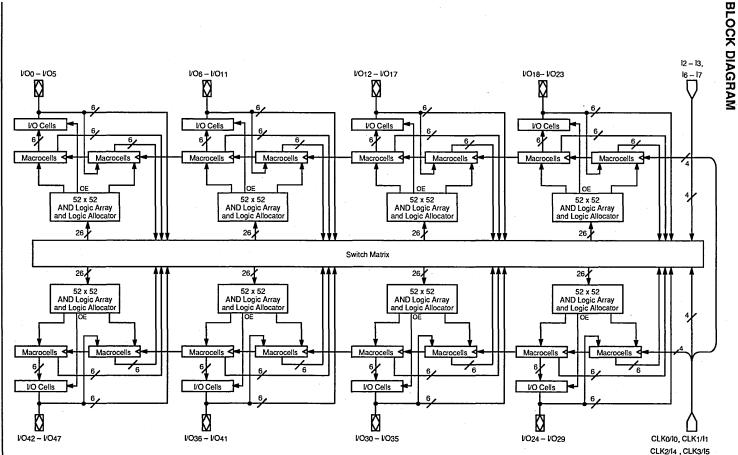

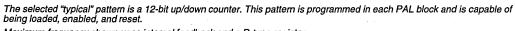

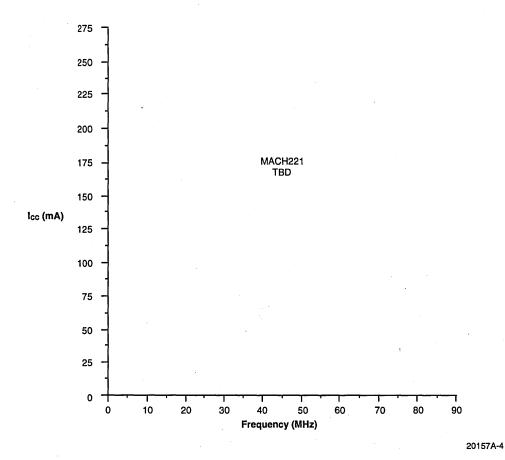

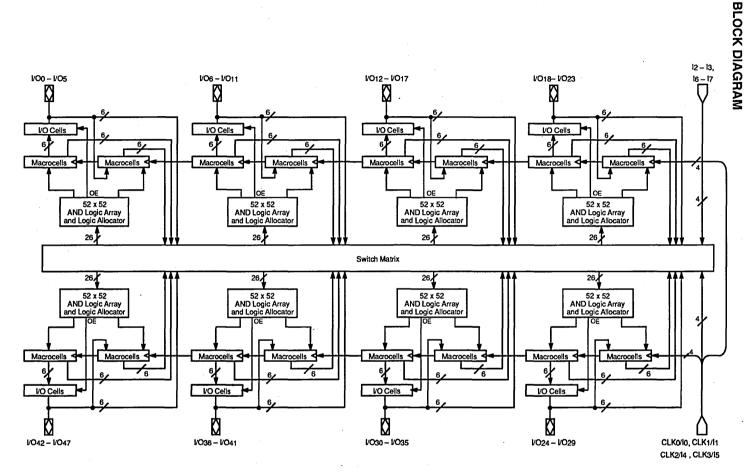

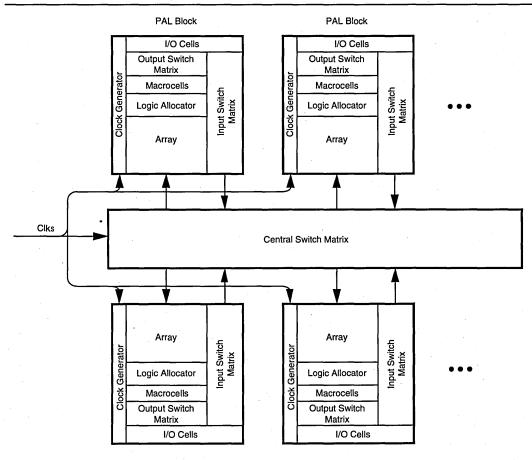

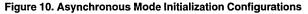

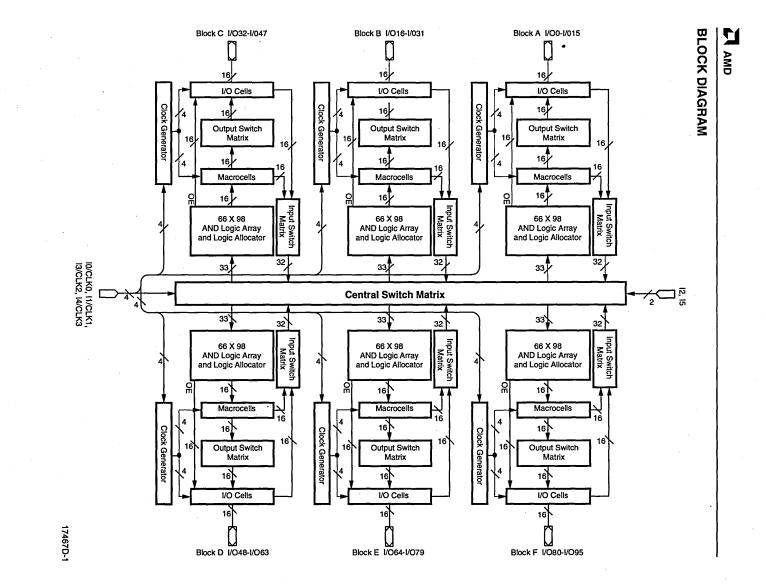

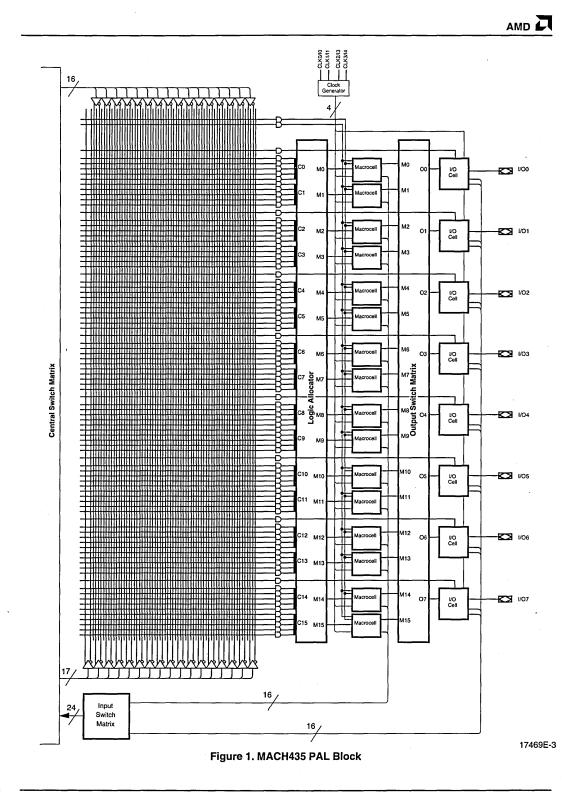

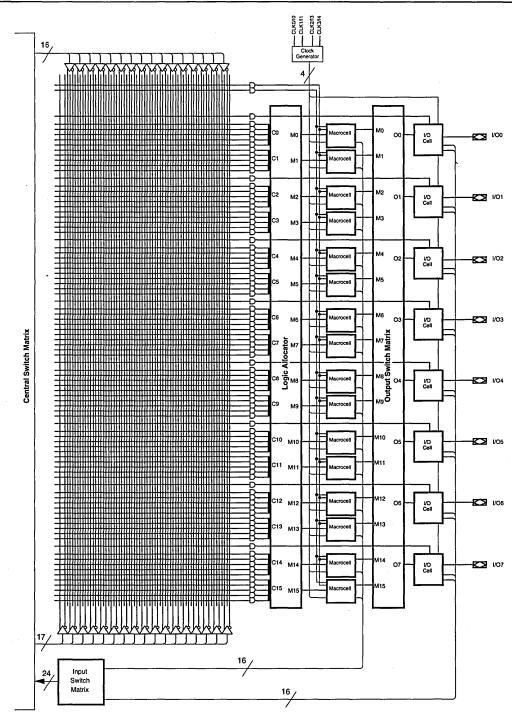

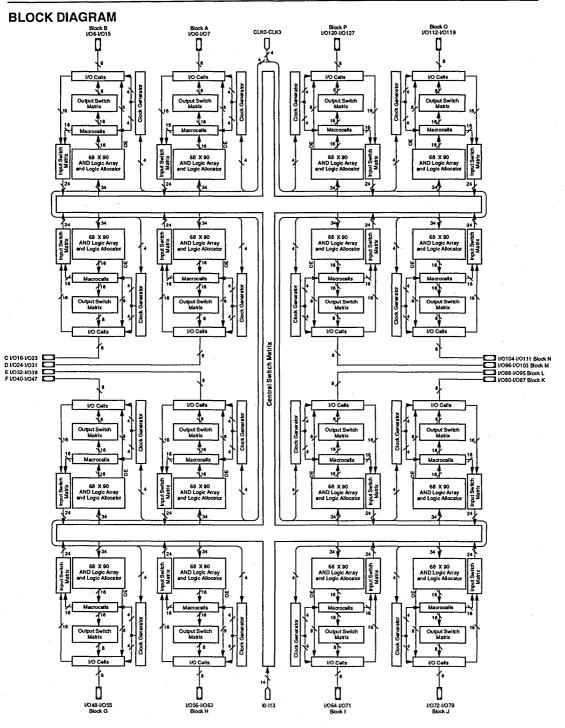

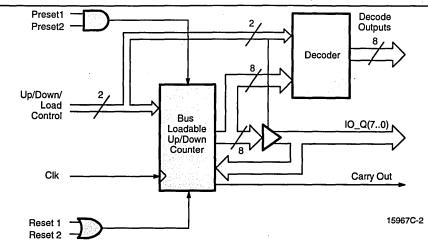

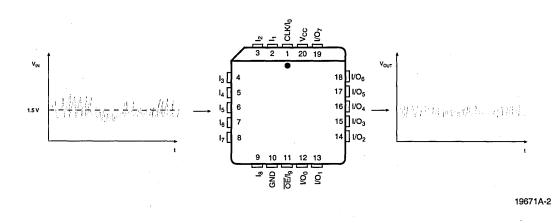

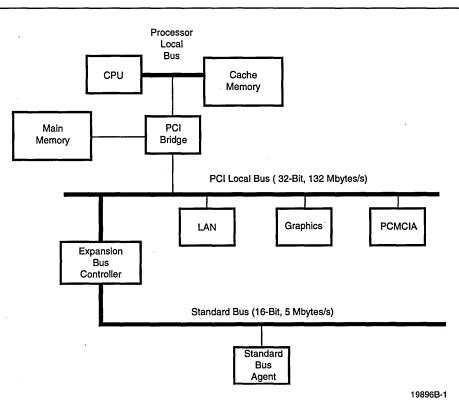

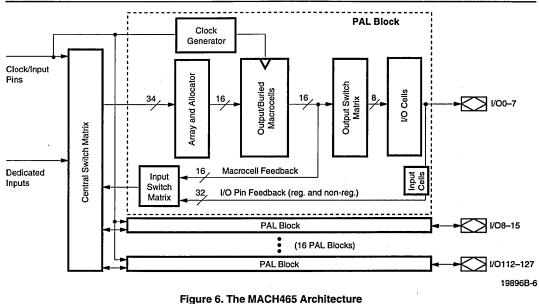

The MACH devices consist of PAL blocks interconnected by a programmable switch matrix (Figure 1). Designs that consist of several interconnected functional modules can be efficiently implemented by placing the modules into PAL blocks. Designs that are not as modular can also be readily implemented since the switch matrix provides a high level of connectivity between PAL blocks. The internal arrangement of resources is managed automatically by the design software, so that the designer does not have to be concerned with the logic implementation details.

The MACH family consists of the MACH 1 and MACH 2 series of synchronous devices and the MACH215, an asynchronous device. The MACH 1 and 2 series are ideal for synchronous subsystems like memory control-

lers and peripheral controllers. The MACH215 is appropriate for applications having asynchronous inputs and for collecting random glue logic.

AMD's FusionPLD program allows MACH device designs to be implemented using a wide variety of popular industry-standard design tools. By working closely with the FusionPLD partners, AMD certifies that the tools provide timely, accurate, quality support. This ensures that a designer does not have to buy a complete new set of tools for each new device, but rather can use the tools with which he or she is already familiar. The MACH devices can be programmed on conventional PAL device programmers with appropriate personality and socket adapter modules.

MACH devices are manufactured using AMD's state-ofthe-art advanced CMOS electrically-erasable process for high performance and logic density. CMOS EE technology provides 100% testability, reducing both prototype development costs and production costs.

#### Design Methodology

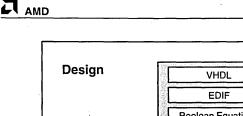

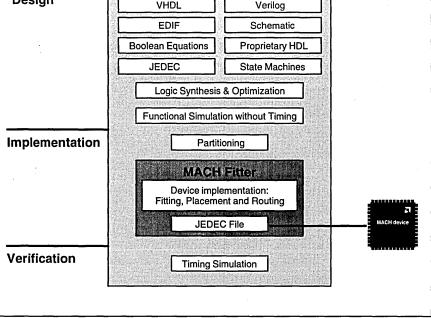

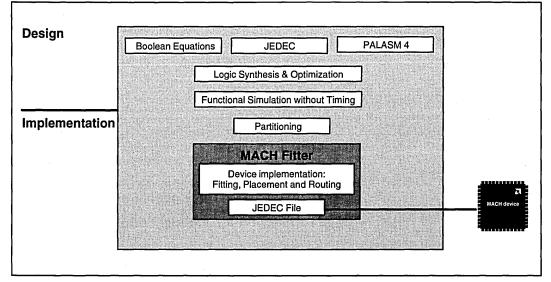

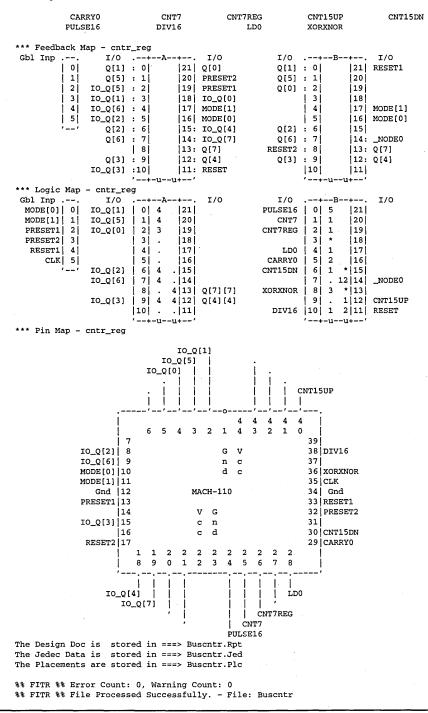

Design tools for MACH devices are widely available both from AMD and from third-party software vendors. AMD supplies MACHXL® software as a low-cost baseline tool set and works with tools vendors to ensure broad MACH device support. This allows designers to do MACH device designs using the same tools that they would use to do PAL device designs, whether MACHXL software or any of the other popular PLD device design packages.

Design entry is the same as that used for PAL devices. The basic logic processing steps are the same steps that are needed to process and minimize logic for any PAL device. Simulation is available for verifying the correct behavior of the device. Functional (unit-delay) simulation of MACH devices is supported in all approved software packages, and other options for simulating the timing and board-level behavior of the MACH devices are available. The end result is a JEDEC file that can be downloaded to a programmer for device configuration.

MACH device design methodology differs somewhat from that of a PAL device due to the automatic design fitting procedure that the software performs. Designs written by logic designers—whether by schematic capture, state machine equations, or Boolean equations—are partitioned and placed into the PAL blocks of the MACH device. While this procedure is handled automatically by the software, the software can also accept manual direction based upon the user's working knowledge of the design. MACH device connectivity is 100% with the exception of the MACH230. This facilitates automatic place and route.

AMD recommends allowing the software to decide the best fit and pin placement automatically for the first design iteration to provide the best chance of fitting. With this approach, large designs can be implemented incrementally, starting with low device utilization and building up by adding logic until the device is full. This generally means that designs are done without any specific pinout assignments, with the final pinout decided by the software. While it is possible to pre-place signals, it is not recommended in most cases. If done carefully, pre-placement can help the software fit difficult designs; if not done carefully, it may make it harder for the design to fit.

The design is partitioned and placed into the MACH device by the software so as not to affect the

performance of the design. With designs that do not fit, it is possible to make some performance tradeoffs to aid in fitting (for example, by optimizing the flip-flop type or passing through the device more than once), while any additional delays are entirely predictable, tradeoffs must be specifically requested.

Once an initial design fits, there may be subsequent changes to the design. This is important if board layout has already started based on the original pinout. Design changes make it necessary to refit the design, which may result in a different pinout. Some design changes may not make it possible to refit the design, regardless of the pinout. The stability of the design and the expected extent of any changes should therefore be considered before committing the design to layout. Hints on designing for change can be found in the *MACH Device Design Planning Guide* near the end of this book.

### Synchronous MACH 1 and 2 Devices

Advanced Micro Devices

#### SYNCHRONOUS MACH DEVICES

The MACH 1 and MACH 2 families of synchronous devices each consist of several members. The items that differentiate the members of the family are the number of pins, the number of macrocells, the amount of interconnect, and the number of clocks. The MACH 1 family has output macrocells; the MACH 2 family has output and buried macrocells. In all other respects, the two families are the same.

This provides a convenient way of migrating designs up or down with little difficulty. Because there is a choice of I/O-pin-to-macrocell ratio, the designer can choose a device that suits both internal logic needs and I/O needs.

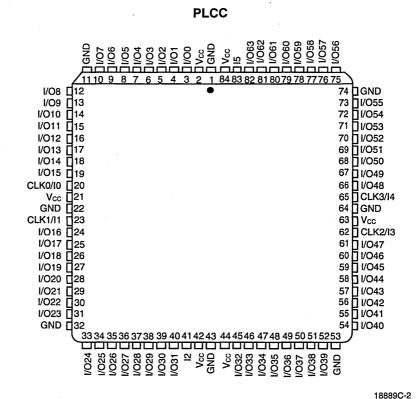

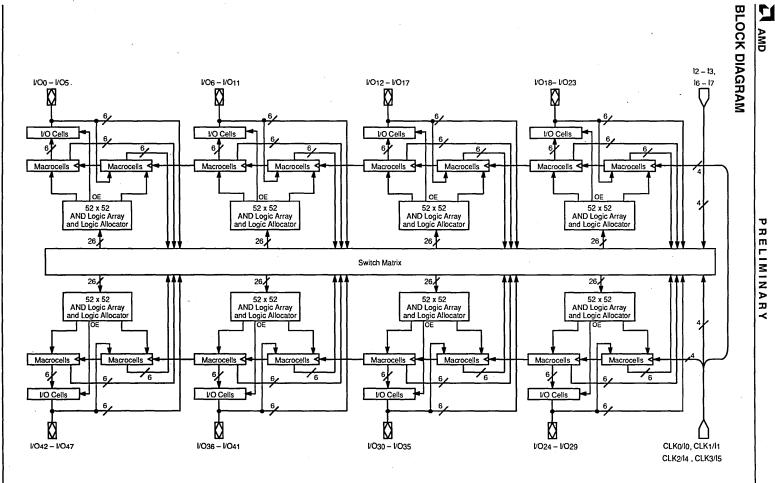

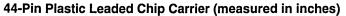

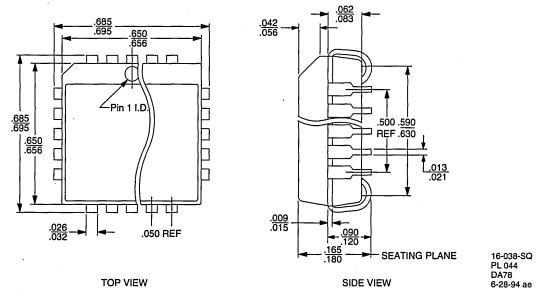

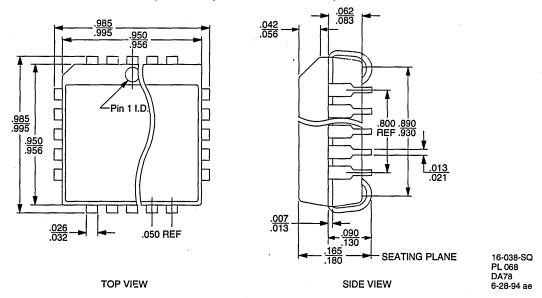

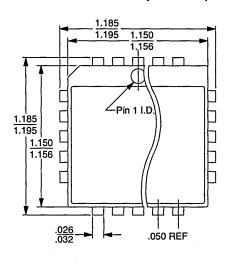

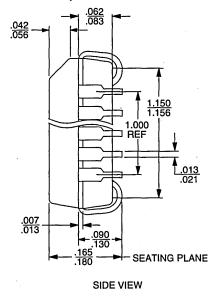

The devices range in pin count from 44 to 84, and in number of macrocells from 32 to 128. All devices are provided in cost-effective PLCC packages; some are available in TQFP packages.

#### **Functional Description**

The fundamental architecture of the MACH devices consists of multiple, optimized PAL blocks interconnected by a switch matrix. The switch matrix allows communication between PAL blocks, and routes inputs to the PAL blocks. Together, the PAL blocks and switch matrix allow the logic designer to create large designs in a single device instead of multiple devices.

Most pins are I/O pinc that can be used as inputs, outputs, or bidirectional pins. There are some dedicated input pins, but all macrocells have internal feedback, allowing the pin to be used as an input if the macrocell signal is not needed externally.

The key to being able to make effective use of these devices lies in the interconnect schemes. Because of the programmable interconnections, the product-term arrays have been decoupled from the switch matrix, the macrocells, and the I/O pins. This provides the needed flexibility to place and route designs efficiently.

In a MACH device, all signals incur the same delays, regardless of routing. Performance is design-independent, and is therefore known before the design is begun.

#### The PAL Blocks

The PAL blocks can be viewed as independent PAL devices on the chip. This provides for logic functions that need the complete interconnect that a PAL device

provides. PAL blocks communicate with each other only through the switch matrix.

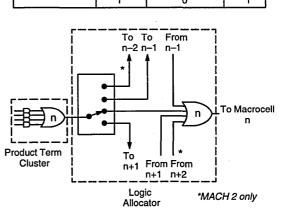

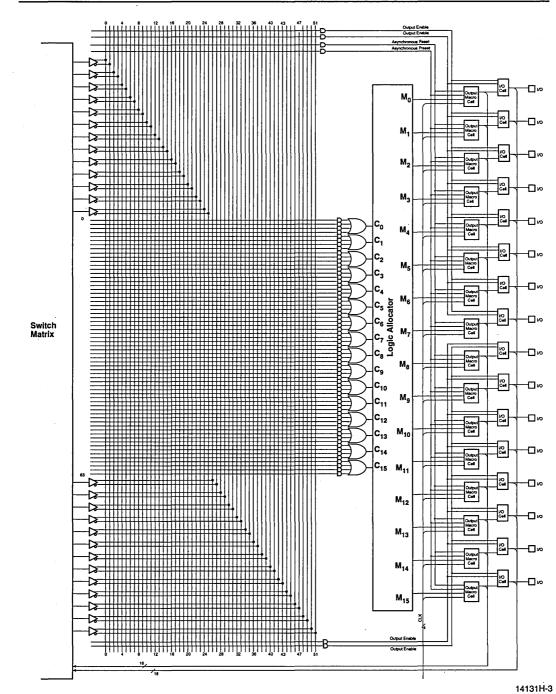

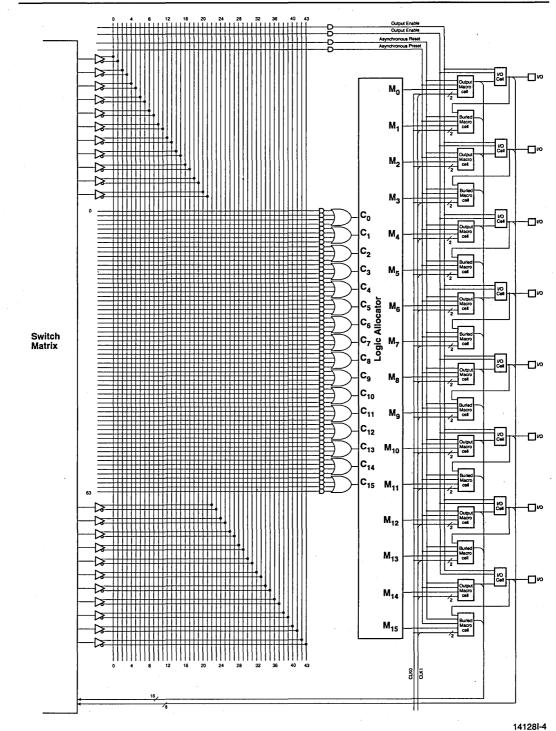

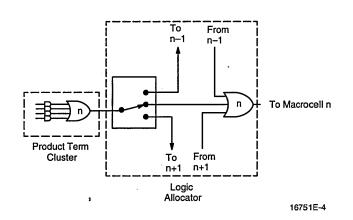

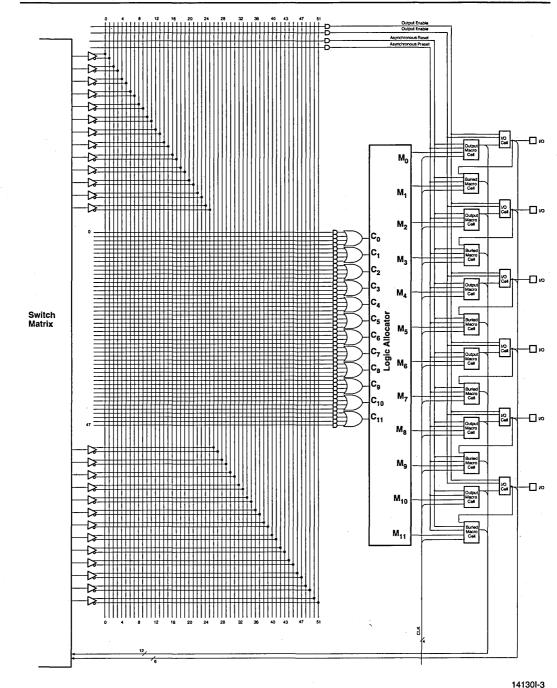

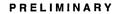

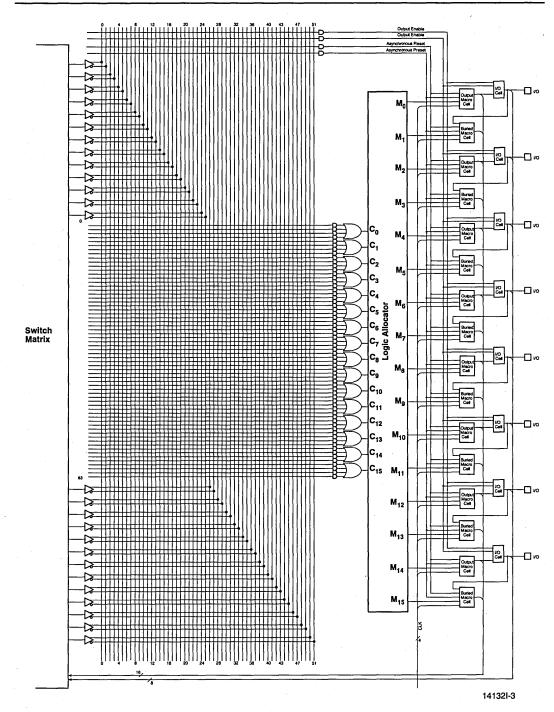

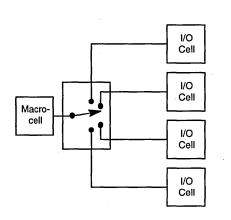

Each PAL block consists of a product-term array, a logic allocator, macrocells, and I/O cells. The product-term array generates the basic logic, although the number of product terms per macrocell is variable. The logic allocator distributes the product terms to the macrocells as required by the design. The macrocell configures the signal, and the I/O cell delivers the final signal to the output pin.

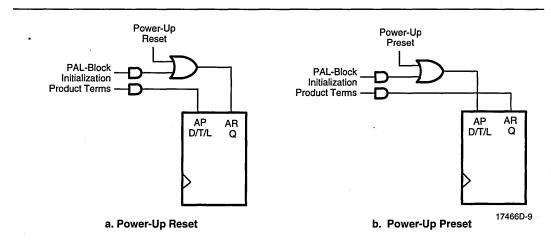

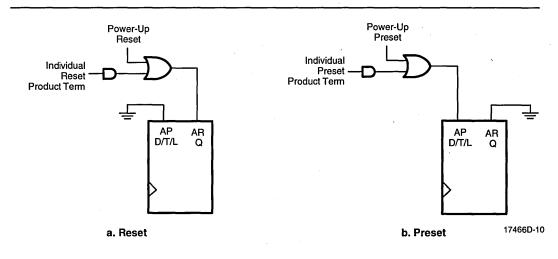

Each PAL block additionally contains an asynchronous reset product term and an asynchronous preset product term. This allows the flip-flops within a single PAL block to be initialized as a bank. There are also several three-state product terms that provide three-state control to the I/O cells.

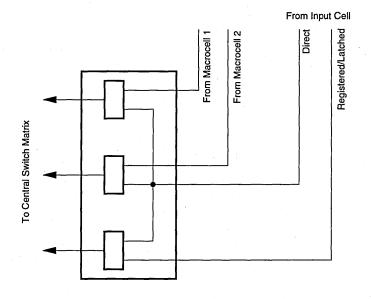

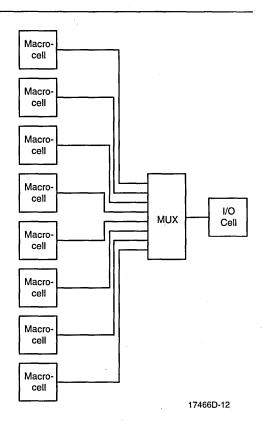

#### The Switch Matrix

The switch matrix takes all dedicated inputs and signals from the input switch matrices and routes them as needed to the PAL blocks. Feedback signals that only return to the same PAL block still must go through the switch matrix. This mechanism ensures that PAL blocks in MACH devices communicate with each other with consistent, predictable delays.

The switch matrix makes a MACH device more than just several PAL devices on a single chip. It allows the designer to think of the device not as a collection of blocks, but as a single programmable device; the software partitions the design into PAL blocks through the central switch matrix so that the designer does not have to be concerned with the internal architecture of the device.

#### The Product-Term Array

The product-term array consists of a number of product terms that form the basis of the logic being implemented. The inputs to the AND gates come from the switch matrix (Table 1), and are provided in both true and complement forms for efficient logic implementation.

Because the number of product terms available for a given function is not fixed, the full sum of products is not realized in the array. The product terms drive the logic allocator, which allocates the appropriate number of product terms to generate the function.

### 🗖 AMD

Table 1. PAL Block Inputs

| Device  | Number of Inputs to PAL Block |

|---------|-------------------------------|

| MACH110 | 22                            |

| MACH111 | 26                            |

| MACH120 | 26                            |

| MACH130 | 26                            |

| MACH131 | 26                            |

| MACH210 | 22                            |

| MACH211 | 26                            |

| MACH220 | 26                            |

| MACH221 | 26                            |

| MACH230 | 26                            |

| MACH231 | 32                            |

#### **The Logic Allocator**

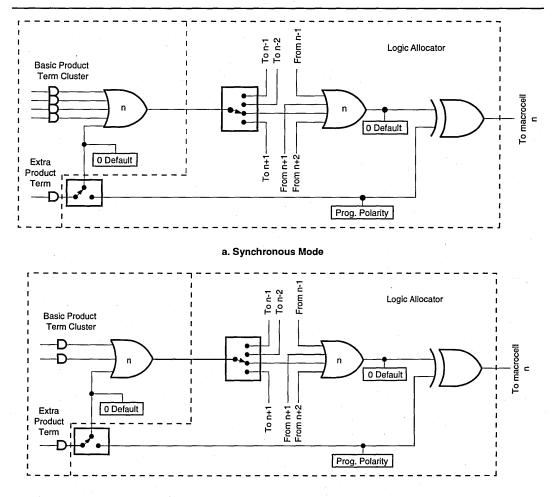

The logic allocator (Figure 2) is a block within which different product terms are allocated to the appropriate macrocells in groups of four product terms called "product term clusters". The availability and distribution of product term clusters is automatically considered by the software as it places and routes functions within the PAL block. The size of the product term clusters has been designed to provide high utilization of product terms. Complex functions using many product terms are possible. When few product terms are used, there will be a minimal number of unused–or wasted–product terms left over.

The product term clusters do not "wrap" around the logic block. This means that the macrocells at the ends of the block have fewer product terms available. Refer to the individual device data sheets for details.

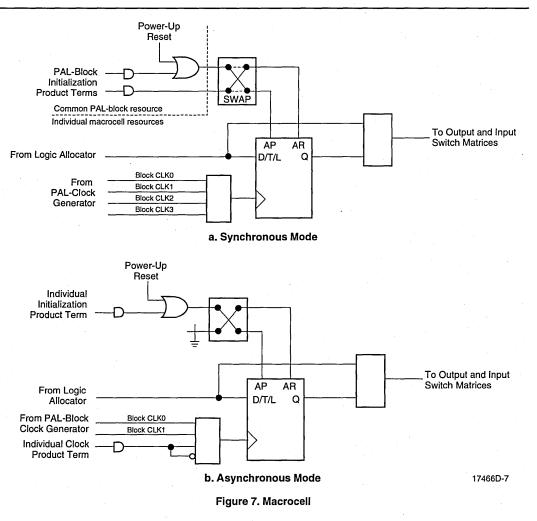

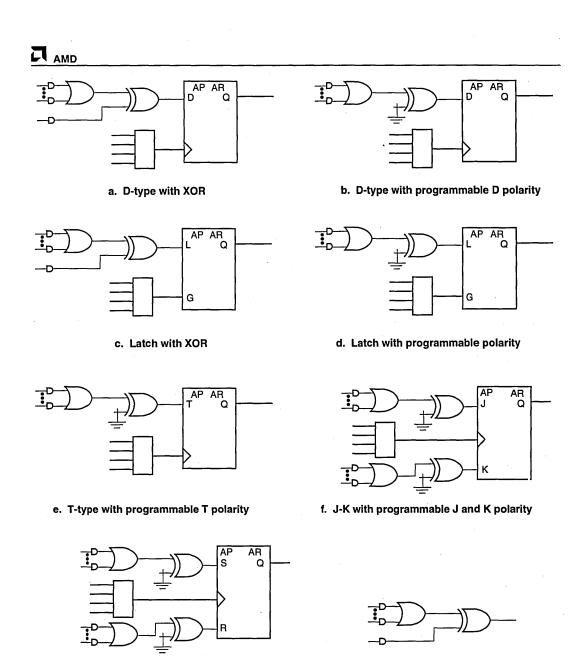

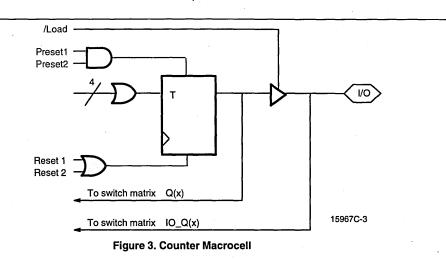

#### **The Macrocell**

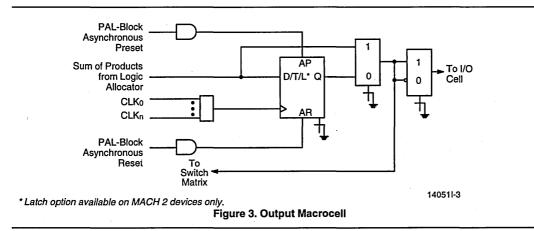

There are two fundamental types of macrocell: the output macrocell and the buried macrocell. The buried macrocell is only found in MACH 2 devices. The use of buried macrocells effectively doubles the number of macrocells available without increasing the pin count.

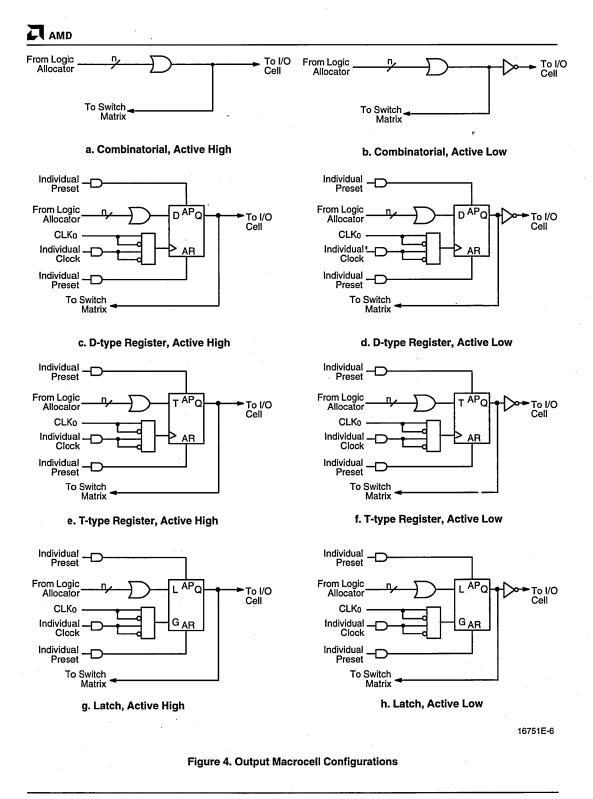

Both macrocell types can generate registered or combinatorial outputs. For the MACH 2 series, a transparent-low latched configuration is provided. If used, the register can be configured as a T-type or a D-type flip-flop. Register and latch functionality is defined in Table 2. Programmable polarity (for output macrocells) and the T-type flip-flop both give the software a way to minimize the number of product terms needed. These choices can be made automatically by the software when it fits the design into the device.

**Table 2. Register/Latch Operation**

|               | •   |          |    |

|---------------|-----|----------|----|

| Configuration | D/T | CLK/LE   | Q+ |

| D-Register    | x   | 0, 1, ↓  | Q  |

|               | 0   | ↑ (      | 0  |

|               | 1   | ↑        | 1  |

| T-Register    | Х   | 0,1,↓    | Q  |

|               | 0   | ↑ (      | Q  |

|               | 1   | <b>↑</b> | ā  |

| Latch         | X   | 1        | Q  |

|               | 0   | 0        | 0  |

|               | 1   | 0        | 1  |

Synchronous MACH Devices

1-9

###

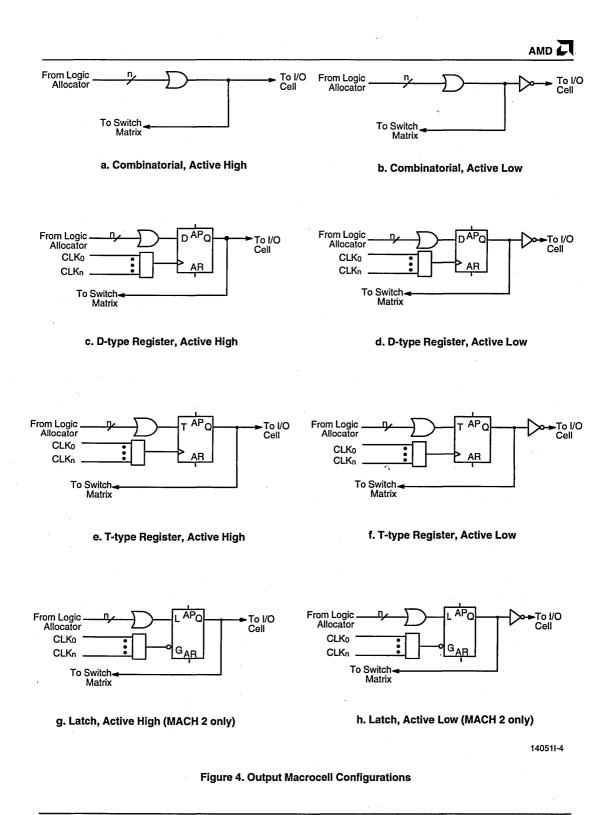

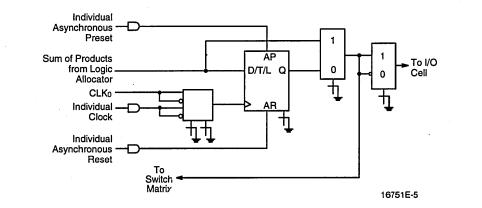

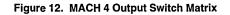

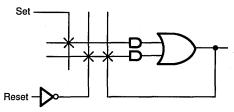

The output macrocell (Figure 3) sends its output back to the switch matrix, via internal feedback, and to the I/O cell. The feedback is always available regardless of the configuration of the I/O cell. This allows for buried combinatorial or registered functions, freeing up the I/O pins for use as inputs if not needed as outputs. The basic output macrocell configurations are shown in Figure 4.

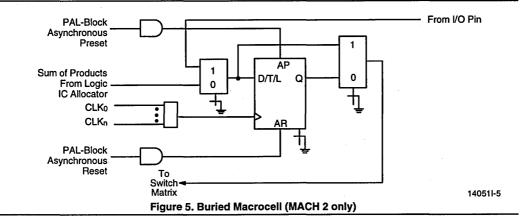

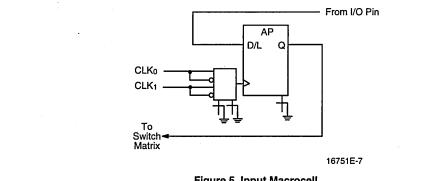

The buried macrocell (Figure 5) does not send its output to an I/O cell. The output of a buried macrocell is provided only as an internal feedback signal which feeds the switch matrix. This allows the designer to generate additional logic without requiring additional pins.

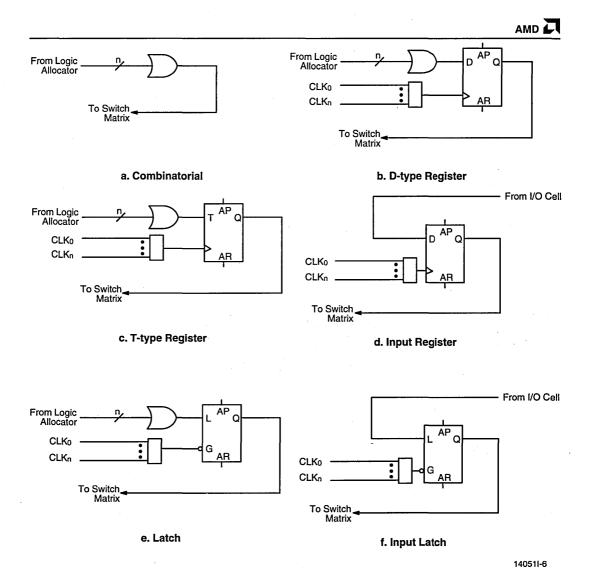

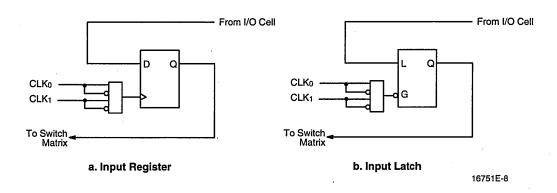

In addition to the capabilities of the output macrocell, the buried macrocell allows the use of registered or latched inputs. The input register is a D-type flip-flop; the input latch is a transparent-low D-type latch. Once configured as a registered or latched input, the buried macrocell cannot generate logic from the product-term array. The basic buried macrocell configurations are shown in Figure 6.

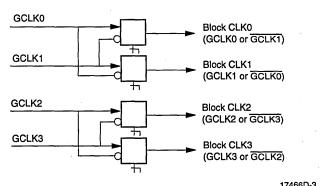

The flip-flops in either macrocell type can be clocked by one of several clock pins (Table 3). Registers are clocked on the rising edge of the clock input. Latches hold their data when the gate input is HIGH. Clock pins are also available as inputs, although care must be taken when a signal acts as both clock and input to the same device.

Table 3. Macrocell Clocks

| Device  | Number of Clocks Available |

|---------|----------------------------|

| MACH110 | 2                          |

| MACH111 | 4                          |

| MACH120 | 4                          |

| MACH130 | 4                          |

| MACH131 | 4                          |

| MACH210 | 2                          |

| MACH211 | 4                          |

| MACH220 | 4                          |

| MACH221 | . 4                        |

| MACH230 | 4                          |

| MACH231 | 4                          |

All flip-flops have asynchronous reset and preset. This is controlled by the common product terms that control all flip-flops within a PAL block. For a single PAL block, all flip-flops, whether in an output or a buried macrocell, are initialized together. The initialization functionality of the flip-flops is illustrated in Table 4.

| Configuration | AR | AP | CLK/LE | Q+          |

|---------------|----|----|--------|-------------|

| Register      | 0  | 0  | x      | See Table 2 |

|               | 0  | 1  | X      | 1           |

|               | 1  | 0  | X      | 0           |

|               | 1  | 1  | X      | 0           |

| Latch         | 0  | 0  | x      | See Table 2 |

|               | 0  | 1  | 0      | Illegal     |

|               | 0  | 1  | 1      | 1           |

|               | 1  | 0  | 0      | Illegal     |

|               | 1  | 0  | 1      | 0           |

|               | 1  | 1  | 0      | lilegal     |

|               | 1  | 1  | 1      | 0           |

**Table 4. Asynchronous Reset/Preset Operation**

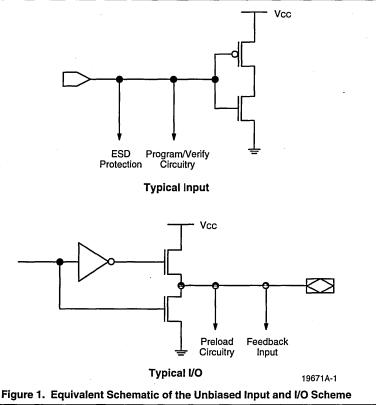

#### The I/O Cell

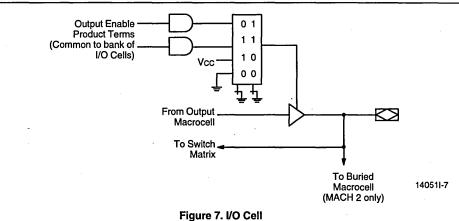

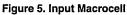

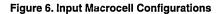

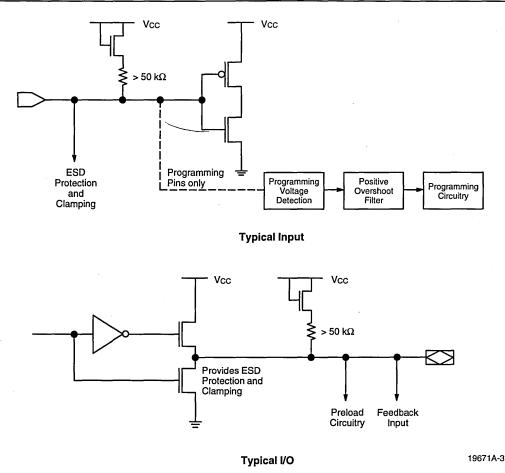

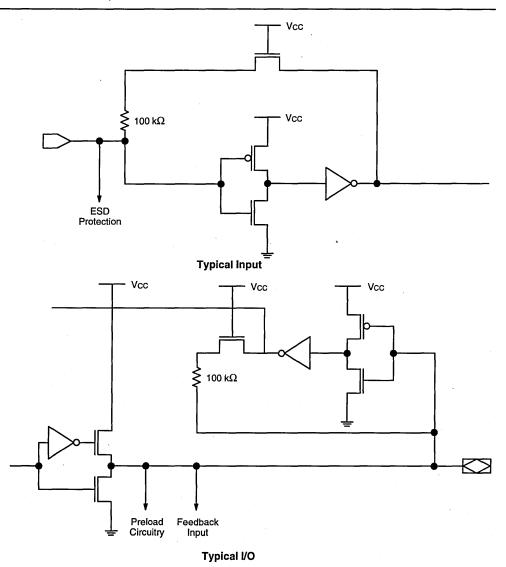

The I/O cell (Figure 7) provides a three-state output buffer. The three-state buffer can be left permanently enabled, for use only as an output; permanently disabled, for use as an input; or it can be controlled by one of two product terms, for bidirectional signals and bus connections. The two product terms provided are common to a bank of I/O cells.

#### Figure 6. Buried Macrocell Configurations (MACH 2 only)

#### **Register Preload**

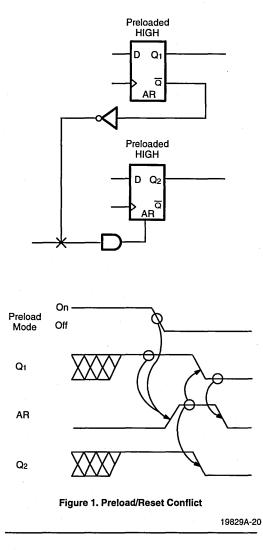

All registers on the MACH devices can be preloaded from the I/O pins to facilitate functional testing of complex state machine designs. This feature allows direct loading of arbitrary states, making it unnecessary to cycle through long test vector sequences to reach a desired state. In addition, transitions from illegal states can be verified by loading illegal states and observing proper recovery.

#### Observability

In addition to the control offered by preload, testing requires observability of the internal state of the device following a sequence of vectors. The MACH devices offer an observability feature that allows the user to send hidden buried register values to observable output pins.

For macrocells that are configured as combinatorial, the observability function suppresses the selection of the combinatorial output by forcing the macrocell output multiplexer into registered output mode. The observability function allows observation of the associated registers by overriding the output enable control and enabling the output buffer.

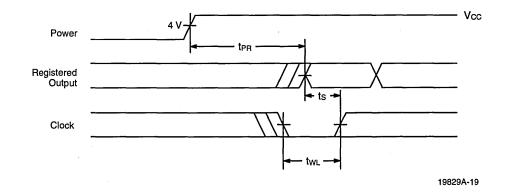

#### **Power-up Reset**

All flip-flops power-up to a logic LOW for predictable system initialization. The actual values of the outputs of the MACH devices will depend on the configuration of the macrocell. The Vcc rise must be monotonic and the reset delay time is  $10 \,\mu$ s maximum.

#### **Security Bit**

A security bit is provided on the MACH devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, this bit defeats readback of the programmed pattern by a device programmer, securing proprietary designs from

competitors. Programming and verification are also defeated by the security bit, but test vectors containing preload can be used independently of the security bit. The bit can only be erased in conjunction with the array during an erase cycle.

#### **Programming and Erasing**

The MACH devices can be programmed on standard logic programmers. They may also be erased to reprogram a previously configured device with a new program. Erasure is automatically performed by the programming hardware. No special erase operation is required.

#### **Quality and Testability**

The MACH devices offer a very high level of built-in quality. The fact that the device is erasable allows direct verification of all AC and DC parameters. In addition, this verifies complete programmability and functionality of the device to provide the highest programming yields and post-programming functional yields in the industry.

#### Technology

The MACH devices are fabricated with AMD's advanced electrically-erasable floating-gate  $0.8 + \mu m$ ,  $0.65 + \mu m$ , and  $0.50 + \mu m$  CMOS technology. This provides the devices with performance and power consumption that are unmatched in the industry. The floating gate cells rely on Fowler-Nordheim tunneling to charge the gate, and have long proven their endurance and reliability. 20-year data retention is provided over operating conditions when devices are programmed on approved programmers.

The substrate of these devices is grounded, providing for a more efficient circuit. In addition, this provides substrate clamp diodes at all inputs, making them more immune to noisy input signals. COM'L: -12/15/20

IND: -14/18/24

### MACH110-12/15/20

High-Density EE CMOS Programmable Logic

#### **DISTINCTIVE CHARACTERISTICS**

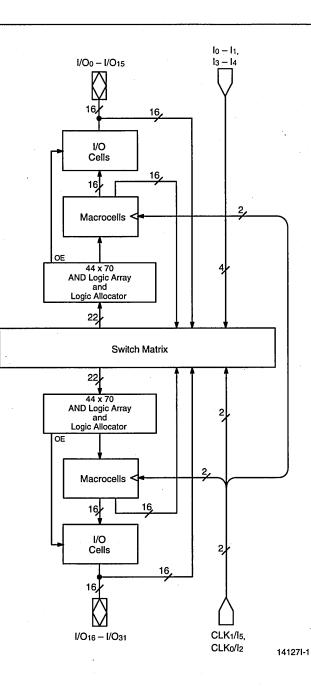

- 🔳 44 Pins

- 32 Macrocells

- 12 ns tPD Commercial 14 ns tPD Industrial

- 77 MHz fcnt

- 38 Inputs

#### **GENERAL DESCRIPTION**

The MACH110 is a member of AMD's high-performance EE CMOS MACH 1 family. This device has approximately three times the logic macrocell capability of the popular PAL22V10 without loss of speed.

The MACH110 consists of two PAL blocks interconnected by a programmable switch matrix. The two PAL blocks are essentially "PAL22V16" structures complete with product-term arrays and programmable macrocells. The switch matrix connects the PAL blocks to each other and to all input pins, providing a high degree of connectivity between the fully-connected PAL blocks. This allows designs to be placed and routed efficiently. 32 Outputs

- 32 Flip-flops; 2 clock choices

- 2 "PAL22V16" Blocks

- Pin-compatible with MACH111, MACH210, MACH211, MACH215

The MACH110 macrocell provides either registered or combinatorial outputs with programmable polarity. If a registered configuration is chosen, the register can be configured as D-type or T-type to help reduce the number of product terms. The register type decision can be made by the designer or by the software. All macrocells can be connected to an I/O cell. If a buried macrocell is desired, the internal feedback path from the macrocell can be used, which frees up the I/O pin for use as an input.

.

Advanced Micro

Devices

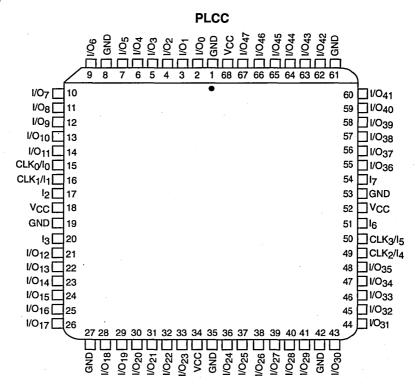

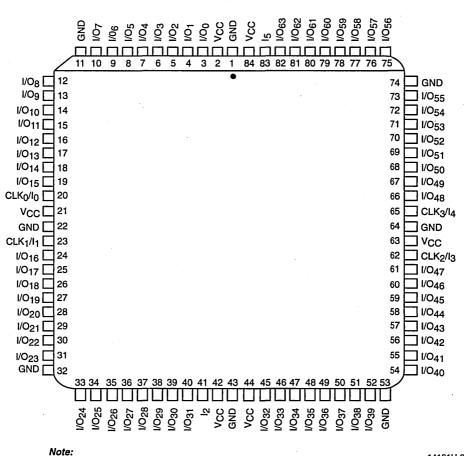

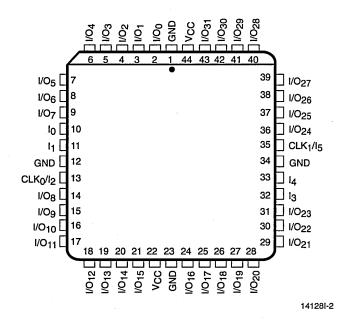

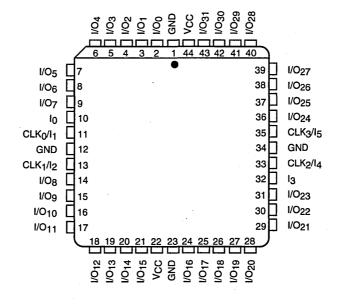

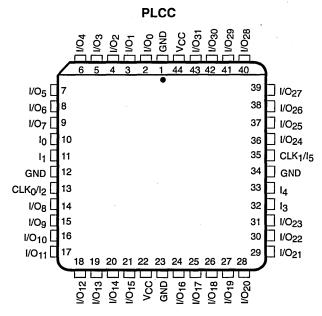

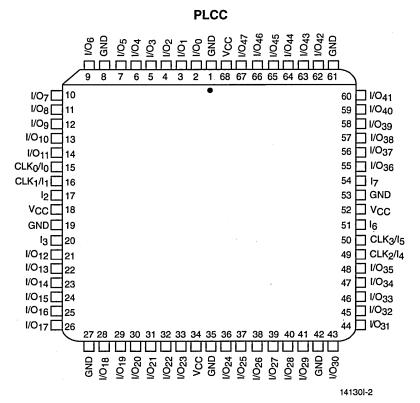

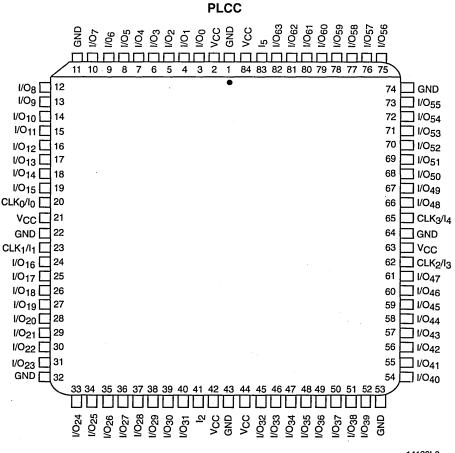

CONNECTION DIAGRAM Top View

PLCC

Note:

#### Pin-compatible with MACH111, MACH210, MACH211, and MACH215.

#### **PIN DESIGNATIONS**

CLK/I = Clock or Input

. 1

- GND = Ground

- I = Input

- I/O = Input/Output

- Vcc = Supply Voltage

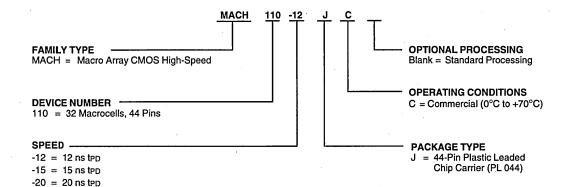

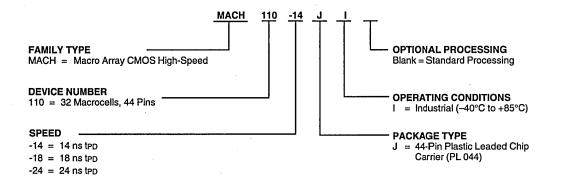

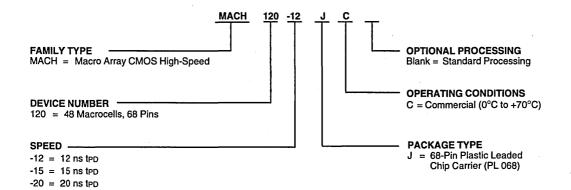

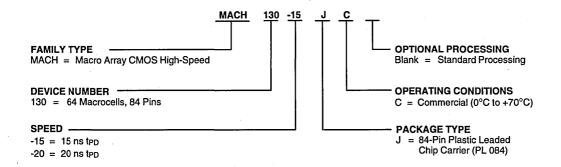

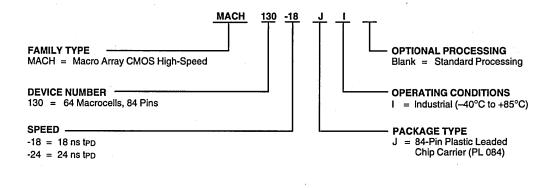

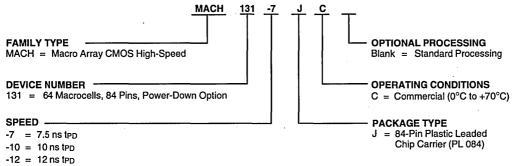

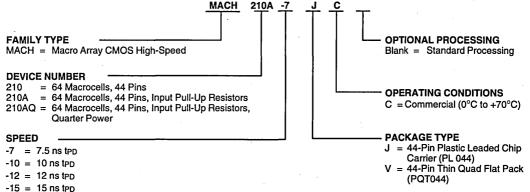

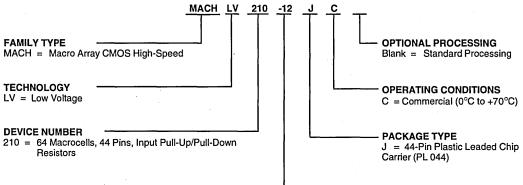

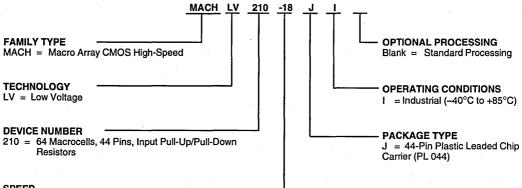

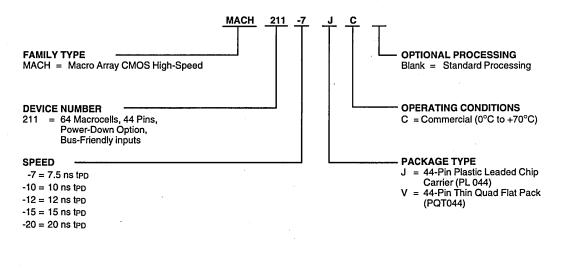

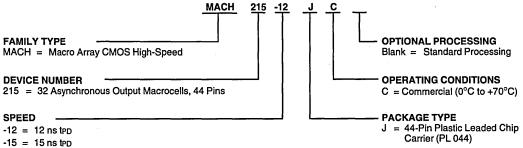

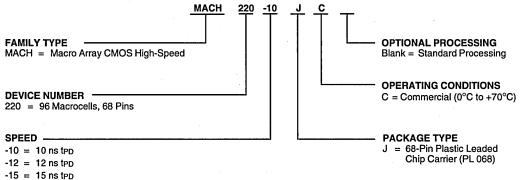

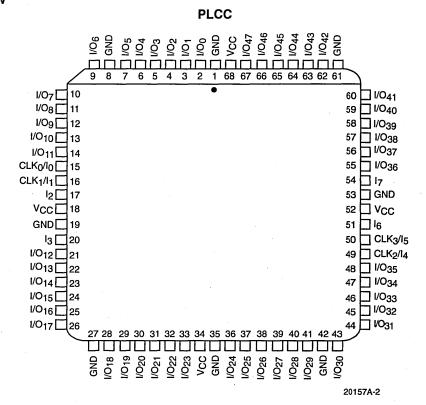

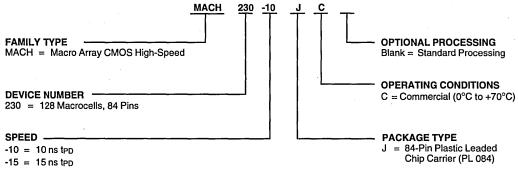

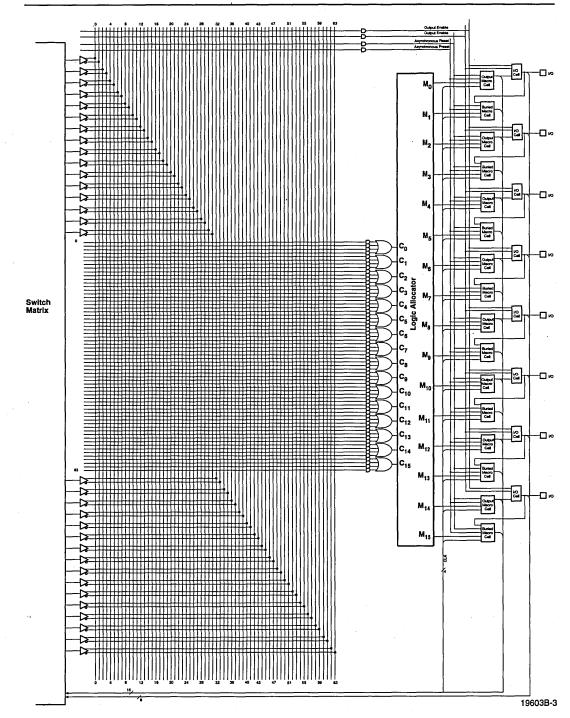

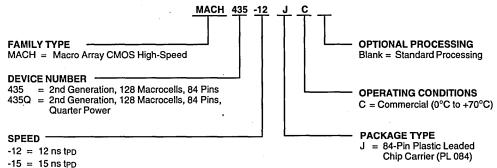

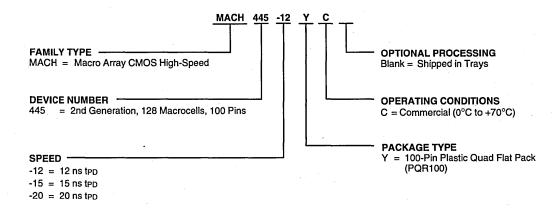

#### ORDERING INFORMATION

#### **Commercial Products**

AMD programmable logic products for commercial applications are available with several ordering options. The order number (Valid Combination) is formed by a combination of:

Valid Combinations MACH110-12 MACH110-15 JC MACH110-20

#### Valid Combinations

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

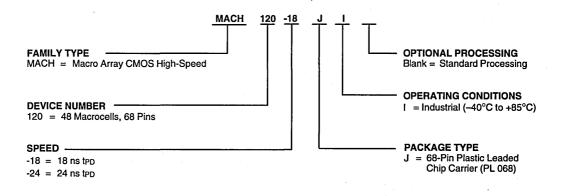

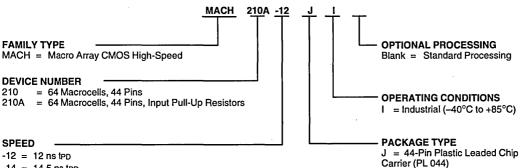

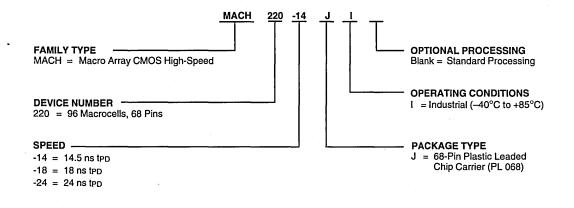

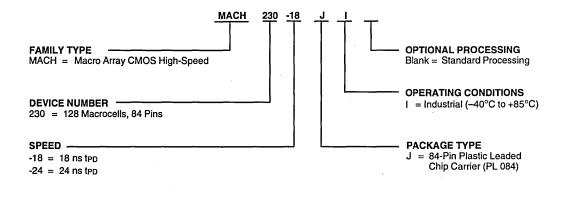

#### **ORDERING INFORMATION**

#### **Industrial Products**

AMD programmable logic products for Industrial applications are available with several ordering options. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |      |  |

|--------------------|------|--|

| MACH110-14         |      |  |

| MACH110-18         | JI . |  |

| MACH110-24         |      |  |

Ċ.

#### Valid Combinations

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

#### FUNCTIONAL DESCRIPTION

The MACH110 consists of two PAL blocks connected by a switch matrix. There are 32 I/O pins and 6 dedicated input pins feeding the switch matrix. These signals are distributed to the two PAL blocks for efficient design implementation. There are two clock pins that can also be used as dedicated inputs.

#### The PAL Blocks

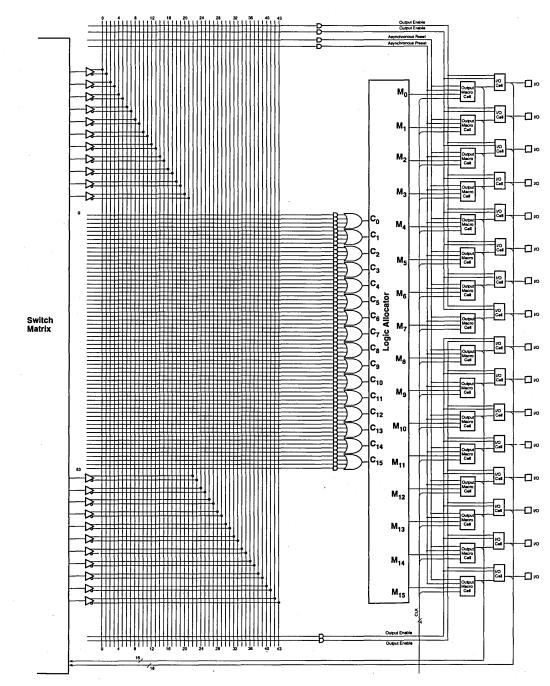

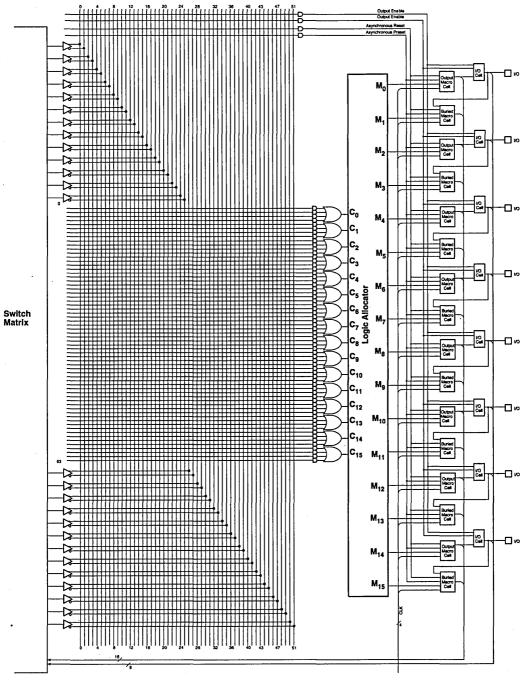

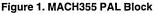

Each PAL block in the MACH110 (Figure 1) contains a 64-product-term logic array, a logic allocator, 16 macrocells and 16 I/O cells. The switch matrix feeds each PAL block with 22 inputs. This makes the PAL block look effectively like an independent "PAL22V16".

There are four additional output enable product terms in each PAL block. For purposes of output enable, the 16 I/O cells are divided into 2 banks of 8 macrocells. Each bank is allocated two of the output enable product terms.

An asynchronous reset product term and an asynchronous preset product term are provided for flip-flop initialization. All flip-flops within the PAL block are initialized together.

#### The Switch Matrix

The MACH110 switch matrix is fed by the inputs and feedback signals from the PAL blocks. Each PAL block provides 16 internal feedback signals and 16 I/O feedback signals. The switch matrix distributes these signals back to the PAL blocks in an efficient manner that also provides for high performance. The design software automatically configures the switch matrix when fitting a design into the device.

#### The Product-Term Array

The MACH110 product-term array consists of 64 product terms for logic use, and 6 special-purpose product terms. Four of the special-purpose product terms provide programmable output enable, one provides asynchronous reset, and one provides a synchronous preset. Two of the output enable product terms are used for the first eight I/O cells; the other two control the last eight macrocells.

#### The Logic Allocator

The logic allocator in the MACH110 takes the 64 logic product terms and allocates them to the 16 macrocells as needed. Each macrocell can be driven by up to 12 product terms. The design software automatically configures the logic allocator when fitting the design into the device.

Table 1 illustrates which product term clusters are available to each macrocell within a PAL block. Refer to Figure 1 for cluster and macrocell numbers.

| Output Macroceli | Available<br>Clusters                             |

|------------------|---------------------------------------------------|

| Mo               | C <sub>0</sub> , C <sub>1</sub>                   |

| M1               | C <sub>0</sub> , C <sub>1</sub> , C <sub>2</sub>  |

| M2               | C1, C2, C3                                        |

| M3               | C <sub>2</sub> , C <sub>3</sub> , C <sub>4</sub>  |

| M4               | C3, C4, C5                                        |

| M5               | C4, C5, C6                                        |

| M <sub>6</sub>   | C5, C6, C7                                        |

| M7               | C6, C7                                            |

| M8               | C8, C9                                            |

| M9               | C <sub>8</sub> , C <sub>9</sub> , C <sub>10</sub> |

| M10              | C9, C10, C11                                      |

| M11              | C10, C11, C12                                     |

| M12              | C11, C12, C13                                     |

| M13              | C12, C13, C14                                     |

| M14              | C13, C14, C15                                     |

| M15              | C14, C15                                          |

#### Table 1. Logic Allocation

#### The Macrocell

The MACH110 macrocells can be configured as either registered or combinatorial, with programmable polarity. The macrocell provides internal feedback whether configured as registered or combinatorial. The flip-flops can be configured as D-type or T-type, allowing for product-term optimization.

The flip-flops can individually select one of two clock pins, which are also available as data inputs. The registers are clocked on the LOW-to-HIGH transition of the clock signal. The flip-flops can also be asynchronously initialized with the common asynchronous reset and preset product terms.

#### The I/O Cell

The I/O cell in the MACH110 consists of a three-state output buffer. The three-state buffer can be configured in one of three ways: always enabled, always disabled, or controlled by a product term. If product term control is chosen, one of two product terms may be used to provide the control. The two product terms that are available are common to eight I/O cells. Within each PAL block, two product terms are available for selection by the first eight three-state outputs; two other product terms are available for selection by the last eight three-state outputs.

These choices make it possible to use the macrocell as an output, an input, a bidirectional pin, or a three-state output for use in driving a bus.

141271-3

MACH110-12/15/20

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                                               |

|-------------------------------------------------------------------|

| Ambient Temperature<br>With Power Applied                         |

| Supply Voltage with                                               |

| Respect to Ground                                                 |

| DC Input Voltage0.5 V to Vcc + 0.5 V                              |

| DC Output or I/O                                                  |

| Pin Voltage                                                       |

| Static Discharge Voltage 2001 V                                   |

| Latchup Current                                                   |

| $(T_A = 0^{\circ}C \text{ to } 70^{\circ}C) \dots 200 \text{ mA}$ |

|                                                                   |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

### **OPERATING RANGES**

#### **Commercial (C) Devices**

| Ambient Temperature (TA)   |                 |

|----------------------------|-----------------|

| Operating in Free Air      | . 0°C to +70°C  |

| Supply Voltage (Vcc)       |                 |

| with Respect to Ground +4. | 75 V to +5.25 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                                                   | Min | Тур | Max  | Unit |

|---------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Vон                 | Output HIGH Voltage                      | $I_{OH} = -3.2 \text{ mA}, V_{CC} = Min$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$                                                  | 2.4 |     |      | v    |

| Vol                 | Output LOW Voltage                       | $I_{OL} = 16 \text{ mA}, V_{CC} = Min$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$                                                    |     |     | 0.5  | v    |

| Viн                 | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 1)                                                                  | 2.0 |     |      | ° V  |

| VIL                 | Input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 1)                                                                   |     |     | 0.8  | v    |

| lн                  | Input HIGH Current                       | V <sub>IN</sub> = 5.25 V, V <sub>CC</sub> = Max (Note 2)                                                                          |     | ·   | 10   | μA   |

| lı.                 | Input LOW Current                        | VIN = 0 V, Vcc = Max (Note 2)                                                                                                     |     |     | -10  | μA   |

| lozh                | Off-State Output Leakage<br>Current HIGH | Vour = 5.25 V, Vcc = Max<br>VIN = VIH or VIL (Note 2)                                                                             |     |     | 10   | μA   |

| lozi.               | Off-State Output Leakage<br>Current LOW  | $\label{eq:Vout} \begin{split} V_{OUT} &= 0 \; V, \; V_{CC} = Max \\ V_{IN} &= V_{IH} \; or \; V_{IL} \; (Note \; 2) \end{split}$ |     |     | 10   | μA   |

| lsc                 | Output Short-Circuit Current             | Vour = 0.5 V, Vcc = Max (Note 3)                                                                                                  | 30  |     | -160 | mA   |

| ļcc                 | Supply Current (Typical)                 | V <sub>CC</sub> = 5 V, T <sub>A</sub> =25°C,<br>f = 25 MHz (Note 4)                                                               |     | 95  |      | mA   |

Notes:

1. These are absolute values with respect to device ground and all overshoots due to system and/or tester noise are included.

2. I/O pin leakage is the worst case of IIL and IOZL (or IIH and IOZH).

3. Not more than one output should be shorted at a time. Duration of the short-circuit should not exceed one second. Vour = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

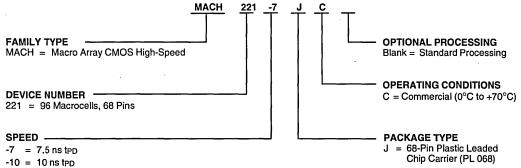

4. Measured with a 16-bit up/down counter program. This pattern is programmed in each PAL block and is capable of being loaded, enabled, and reset.

#### **CAPACITANCE (Note 1)**

| Parameter<br>Symbol | Parameter Description | Test Conditi            | ons                                | Тур | Unit |

|---------------------|-----------------------|-------------------------|------------------------------------|-----|------|

| CIN                 | Input Capacitance     | V <sub>IN</sub> = 2.0 V | Vcc = 5.0 V, T <sub>A</sub> = 25°C | 6   | pF   |

| Солт                | Output Capacitance    | Vout = 2.0 V            | f = 1 MHz                          | 8   | pF   |

#### SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)

| Parameter        |                                                                   |                                                   |                 |        | -1   | 12  | -1   | 5   | -2   | 0   |      |

|------------------|-------------------------------------------------------------------|---------------------------------------------------|-----------------|--------|------|-----|------|-----|------|-----|------|

| Symbol           | Parameter De                                                      | scription                                         |                 |        | Min  | Max | Min  | Max | Min  | Max | Unit |

| tep              | Input, I/O, or Feedback to Combinatorial<br>Output (Note 3)       |                                                   |                 | 12     |      | 15  |      | 20  | ns   |     |      |

| ts               | Setup Time from Input, I/O, or Feedback D-type<br>to Clock T-type |                                                   | 7               |        | 10   |     | 13   |     | ns   |     |      |

| 5                |                                                                   |                                                   | 8               |        | 11   |     | 14   |     | ns   |     |      |

| tн               | Hold Time                                                         |                                                   |                 |        | 0    |     | 0    |     | 0    |     | ns   |

| tco              | Clock to Outpu                                                    | ut (Note 3)                                       |                 |        |      | 8   |      | 10  |      | 12  | ns   |

| twL              | Clock Width                                                       | LOW                                               |                 | 6      |      | 6   |      | 8   |      | ns  |      |

| twн              |                                                                   |                                                   |                 | HIGH   | 6    |     | 6    |     | 8    |     | ns   |

|                  | 1                                                                 |                                                   | < 1/(ts + tco)  | D-type | 66.7 |     | 50   |     | 40   |     | MHz  |

|                  | Maximum                                                           | External Feedback                                 |                 | T-type | 62.5 |     | 47.6 |     | 38.5 |     | MHz  |

| fмах             | Frequency                                                         |                                                   |                 | D-type | 76.9 |     | 66.6 |     | 47.6 |     | MHz  |

|                  | (Note 1)                                                          | Internal Feedback                                 | (ICNT)          | T-type | 71.4 |     | 55.5 |     | 43.5 |     | MHz  |

|                  |                                                                   | No Feedback                                       | 1/(tw∟+twн)     |        | 83.3 |     | 83.3 |     | 62.5 |     | MHz  |

| tar              | Asynchronous                                                      | Reset to Registered                               | Output          |        |      | 16  |      | 20  |      | 25  | ns   |

| tarw             | Asynchronous                                                      | Reset Width (Note 1                               | )               |        | 12   |     | 15   |     | 20   |     | ns   |

| t <sub>ARR</sub> | Asynchronous                                                      | Reset Recovery Tim                                | e (Note 1)      |        | 8    |     | 10   |     | 15   |     | ns   |

| tap              | Asynchronous                                                      | Preset to Registered                              | Output          |        |      | 16  |      | 20  |      | 25  | ns   |

| tapw             | Asynchronous                                                      | Preset Width (Note 1)                             |                 | 12     |      | 15  |      | 20  |      | ns  |      |

| tapr             | Asynchronous                                                      | chronous Preset Recovery Time (Note 1)            |                 | 8      |      | 10  |      | 15  |      | ns  |      |

| tea              | Input, I/O, or F                                                  | Input, I/O, or Feedback to Output Enable (Note 3) |                 |        | 12   |     | 15   |     | 20   | ns  |      |

| ter              | Input, I/O, or F                                                  | eedback to Output D                               | isable (Note 3) |        |      | 12  |      | 15  |      | 20  | ns   |

Notes:

- 1. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

- 2. See Switching Test Circuit, for test conditions.

- 3. Parameters measured with 16 outputs switching.

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature65°C to +150°C                                    |

|----------------------------------------------------------------------|

| Ambient Temperature<br>With Power Applied –55°C to +125°C            |

| Supply Voltage with<br>Respect to Ground                             |

| DC Input Voltage                                                     |

| DC Output or I/O                                                     |

| Pin Voltage                                                          |

| Static Discharge Voltage 2001 V                                      |

| Latchup Current                                                      |

| $(T_A = -40^{\circ}C \text{ to } +85^{\circ}C) \dots 200 \text{ mA}$ |

| Strasses above these listed under Absolute Maximum Patings           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

#### **INDUSTRIAL OPERATING RANGES**

| Ambient Temperature (T <sub>A</sub> )<br>Operating in Free Air | -40°C to +85°C   |

|----------------------------------------------------------------|------------------|

| Supply Voltage (Vcc) with Respect to Ground                    | +4.5 V to +5.5 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                          | Min | Тур | Max  | Unit |

|---------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Vон                 | Output HIGH Voltage                      | $I_{OH} = -3.2 \text{ mA}, V_{CC} = Min$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$                         | 2.4 |     |      | v    |

| V <sub>OL</sub>     | Output LOW Voltage                       | $l_{OL} = 16 \text{ mA}, V_{CC} = Min$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$                           |     |     | 0.5  | v    |

| Vін                 | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 1)                                         | 2.0 |     |      | V    |

| VIL                 | Input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 1)                                          |     |     | 0.8  | v    |

| l <sub>ін</sub>     | Input HIGH Current                       | V <sub>IN</sub> = 5.25 V, V <sub>CC</sub> = Max (Note 2)                                                 |     |     | 10   | μA   |

| 1 <sub>1L</sub>     | Input LOW Current                        | V <sub>IN</sub> = 0 V, V <sub>CC</sub> = Max (Note 2)                                                    |     |     | -10  | μA   |

| Іогн                | Off-State Output Leakage<br>Current HIGH | $V_{OUT} = 5.25 \text{ V}, V_{CC} = \text{Max}$<br>$V_{IN} = V_{IH} \text{ or } V_{IL} \text{ (Note 2)}$ |     |     | 10   | μA   |

| lozi.               | Off-State Output Leakage<br>Current LOW  | $V_{OUT} = 0 V, V_{CC} = Max$<br>$V_{IN} = V_{IH} \text{ or } V_{IL} \text{ (Note 2)}$                   |     |     | -10  | μA   |

| lsc                 | Output Short-Circuit Current             | Vour = 0.5 V, Vcc = Max (Note 3)                                                                         | -30 |     | -160 | mA   |

| lcc                 | Supply Current (Typical)                 | V <sub>cc</sub> = 5 V, T <sub>A</sub> = 25°C, f = 25 MHz (Note 4)                                        |     | 95  |      | mA   |

#### Notes:

1. These are absolute values with respect to device ground and all overshoots due to system and/or tester noise are included.

2. I/O pin leakage is the worst case of IIL and IOZL (or IIH and IOZH).

Not more than one output should be shorted at a time. Duration of the short-circuit should not exceed one second.

V<sub>OUT</sub> = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

Measured with a 16-bit up/down counter pattern. This pattern is programmed in each PAL block and is capable of being loaded, enabled, and reset.

#### **CAPACITANCE (Note 1)**

| Parameter<br>Symbol | Parameter Description | Test Conditio            | ns                                             | Тур | Unit |

|---------------------|-----------------------|--------------------------|------------------------------------------------|-----|------|

| Cin                 | Input Capacitance     | V <sub>IN</sub> = 2.0 V  | V <sub>CC</sub> = 5.0 V, T <sub>A</sub> = 25°C | 6   | pF   |

| COUT                | Output Capacitance    | V <sub>OUT</sub> = 2.0 V | f = 1 MHz                                      | 8   | pF   |

#### SWITCHING CHARACTERISTICS over INDUSTRIAL operating ranges (Note 2)

| Parameter |                                                             |                                            |                             |        |      | 14   | -1   | -18 |      | -24  |      |

|-----------|-------------------------------------------------------------|--------------------------------------------|-----------------------------|--------|------|------|------|-----|------|------|------|

| Symbol    | Parameter De                                                | escription                                 |                             |        | Min  | Max  | Min  | Max | Min  | Max  | Unit |

| tpp       | Input, I/O, or Feedback to Combinatorial<br>Output (Note 3) |                                            |                             | 14.5   |      | 18   |      | 24  | ns   |      |      |

| ts        |                                                             | om Input, I/O, or Feed                     | lback                       | D-type | 8.5  |      | 12   |     | 16   |      | ns   |

| 15        | to Clock T-type                                             |                                            | T-type                      | 10     |      | 13.5 |      | 17  |      | ns   |      |

| tн        | Hold Time                                                   |                                            |                             |        | 0    |      | 0    |     | 0    |      | ns   |

| tco       | Clock to Outpu                                              | ut (Note 3)                                |                             |        |      | 10   |      | 12  |      | 14.5 | ns   |

| twL       | Clock Width                                                 |                                            |                             | LOW    | 7.5  |      | 7.5  |     | 10   |      | ns   |

| twн       |                                                             |                                            | HIGH                        |        | 7.5  |      | 7.5  |     | 10   |      | ns   |

|           | E<br>Maximum —                                              |                                            |                             | D-type | 53.5 |      | 40   |     | 32   |      | MHz  |

|           |                                                             | External Feedback                          | 1/(ts + tco)                | T-type | 50   |      | 38   |     | 30   |      | MHz  |

| fмах      | Frequency                                                   | requency                                   | /f. \                       | D-type | 61.5 |      | 53   |     | 38   |      | MHz  |

|           | (Note 1)                                                    | Internal Feedback (f <sub>CNT</sub> )      |                             | T-type | 57   |      | 44   |     | 34.5 |      | MHz  |

|           |                                                             | No Feedback                                | $1/(t_{WL} + t_{WH})$       |        | 66.5 |      | 66.5 |     | 50   |      | MHz  |

| tar       | Asynchronous                                                | Reset to Registered                        | Output                      |        |      | 19.5 |      | 24  |      | 30   | ns   |

| tarw      | Asynchronous                                                | Reset Width (Note 1                        | )                           |        | 14.5 |      | 18   |     | 24   |      | ns   |

| tarr      | Asynchronous                                                | Reset Recovery Tim                         | e (Note 1)                  |        | 10   |      | 12   |     | 18   |      | ns   |

| tap       | Asynchronous                                                | Preset to Registered                       | Preset to Registered Output |        |      | 19.5 |      | 24  |      | 30   | ns   |

| tapw      | Asynchronous Preset Width (Note 1)                          |                                            | 14.5                        |        | 18   |      | 24   |     | ns   |      |      |

| tapr      | Asynchronous                                                | Asynchronous Preset Recovery Time (Note 1) |                             | 10     |      | 12   |      | 18  |      | ns   |      |

| tEA       | Input, I/O, or F                                            | eedback to Output E                        | nable (Note 3)              |        | 1    | 14.5 |      | 18  |      | 24   | ns   |

| ter       | Input, I/O, or F                                            | eedback to Output Di                       | sable (Note 3)              |        |      | 14.5 |      | 18  | ĺ    | 24   | ns   |

Notes:

1. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

2. See Switching Test Circuit, for test conditions.

3. Parameters measured with 16 outputs switching.

###

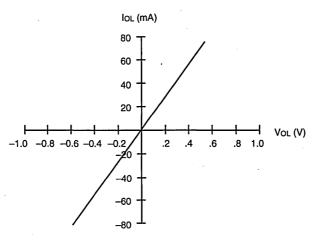

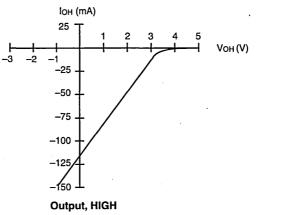

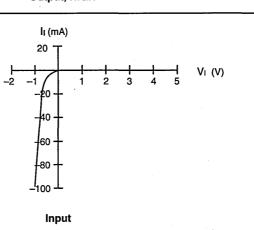

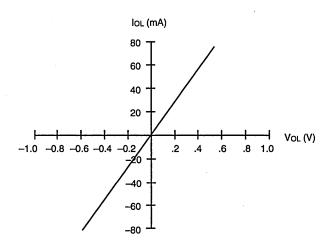

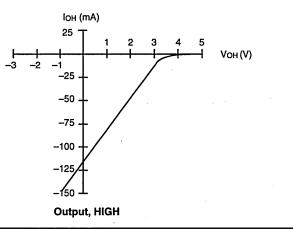

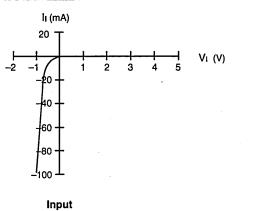

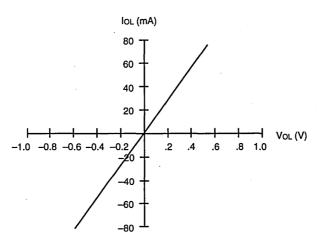

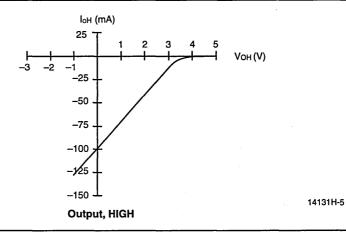

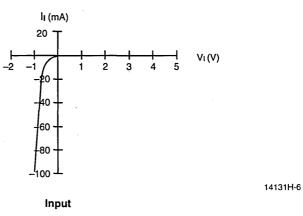

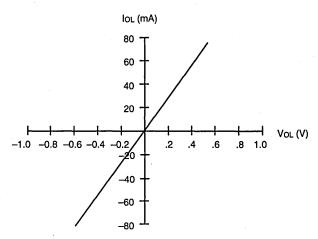

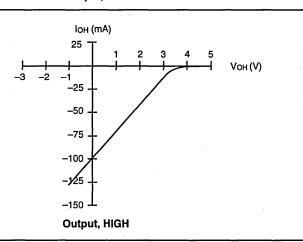

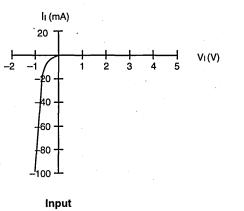

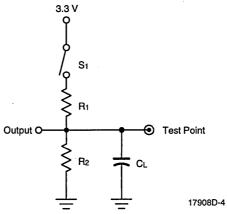

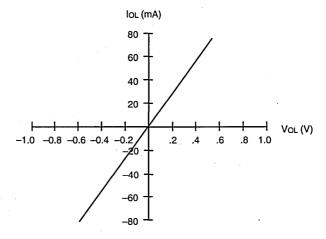

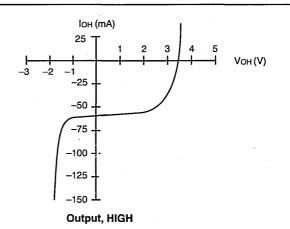

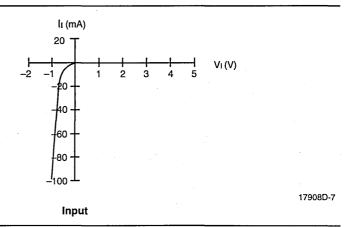

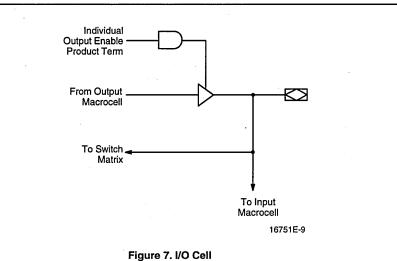

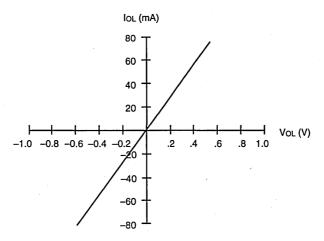

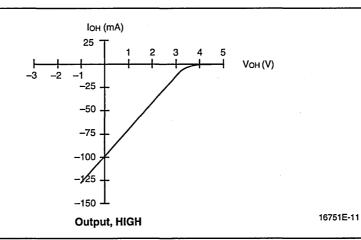

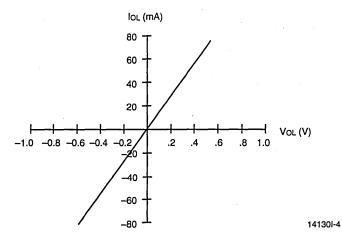

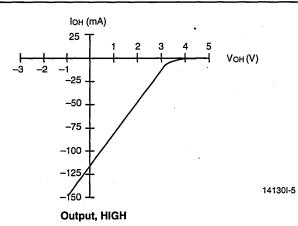

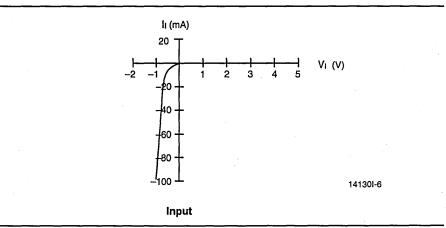

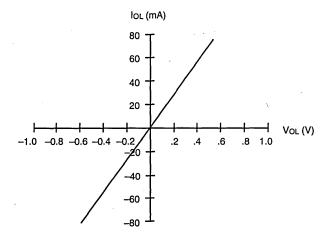

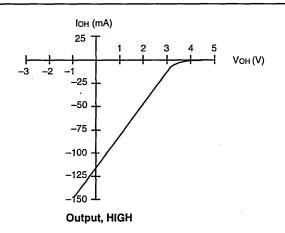

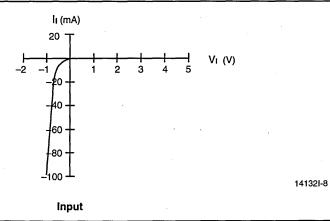

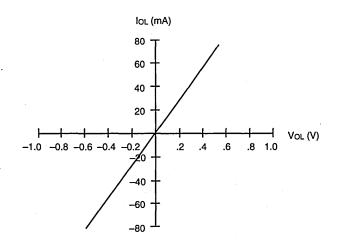

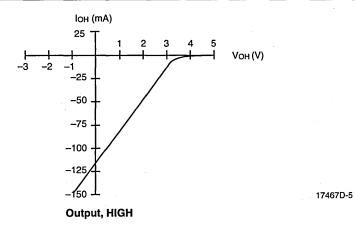

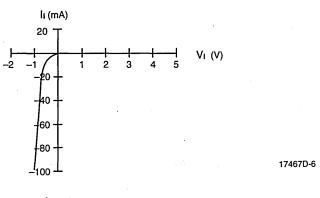

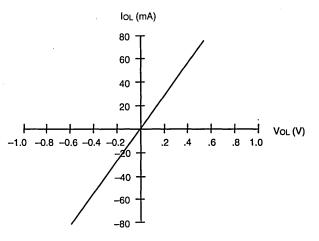

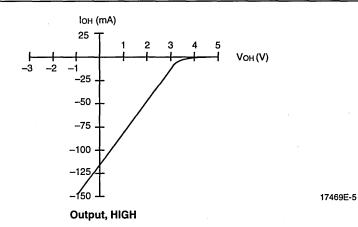

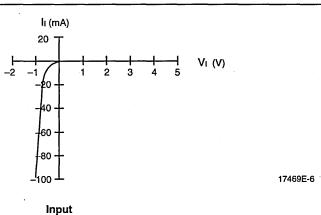

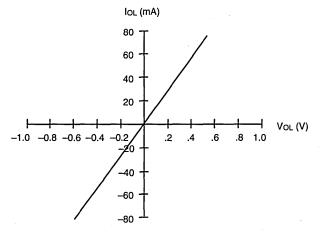

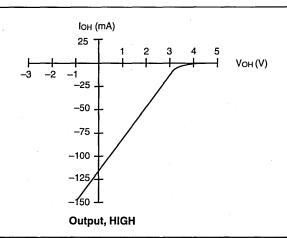

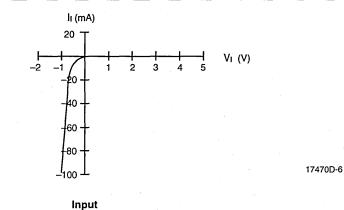

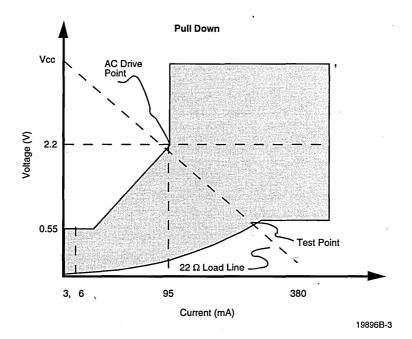

### TYPICAL CURRENT VS. VOLTAGE (I-V) CHARACTERISTICS

$V_{CC}$  = 5.0 V,  $T_{A}~$  = 25°C

141271-4

141271-6

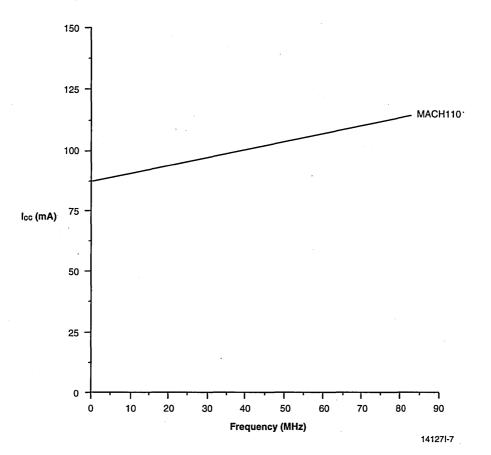

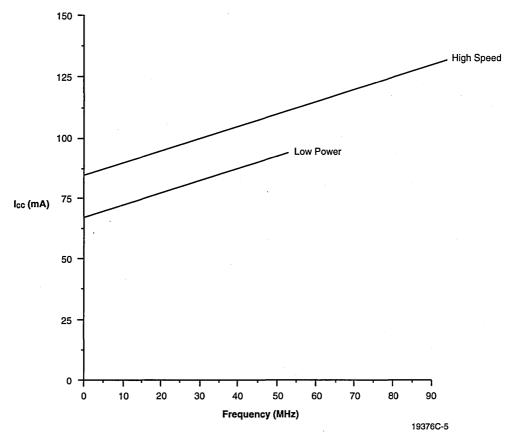

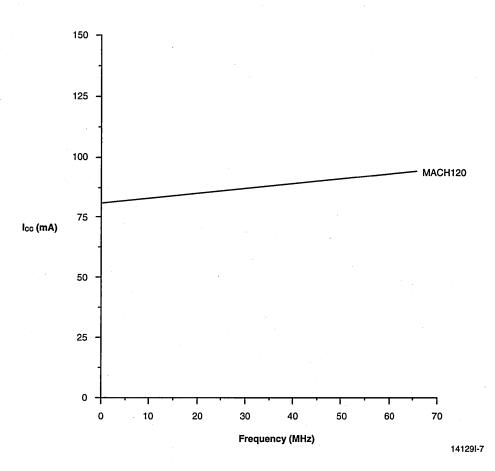

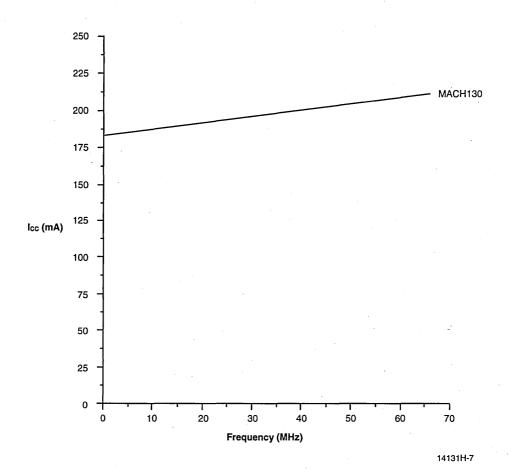

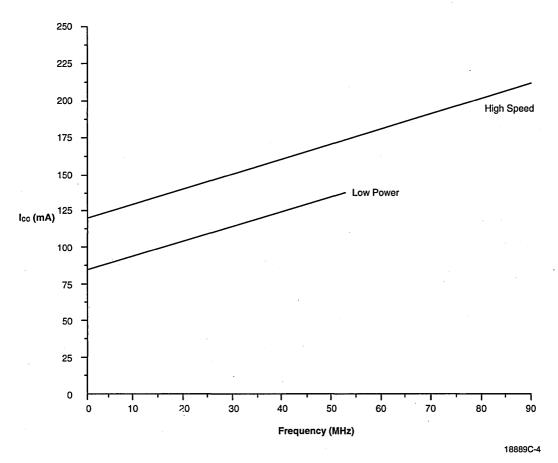

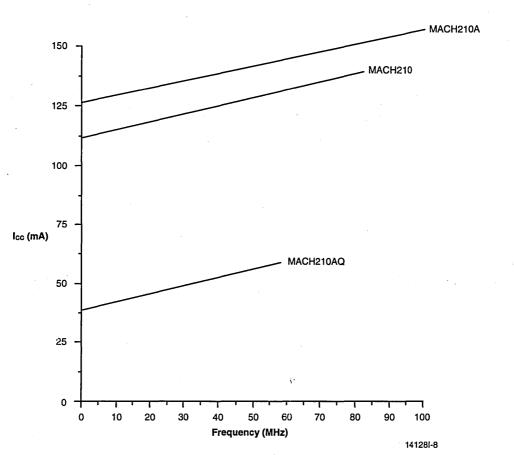

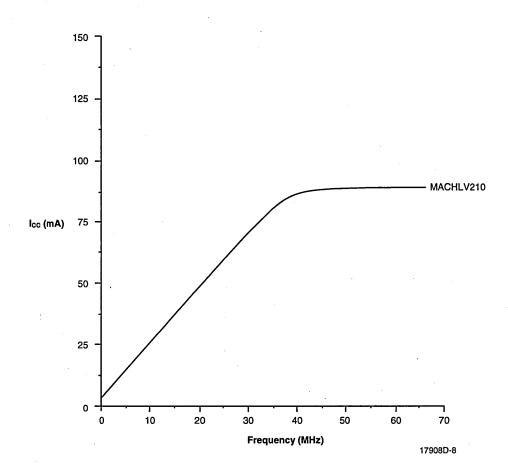

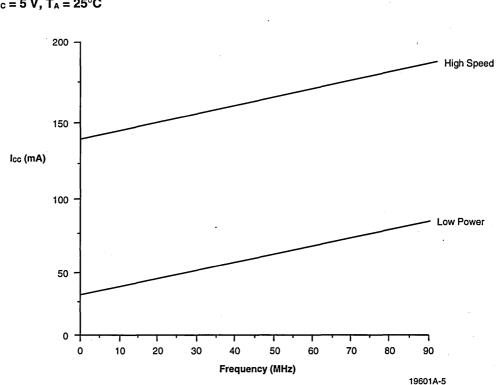

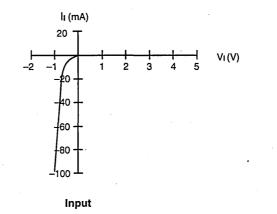

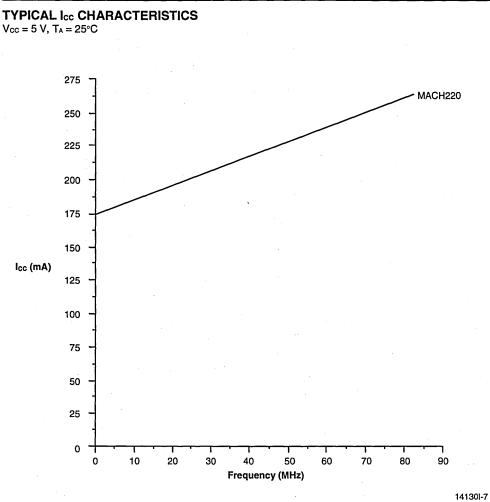

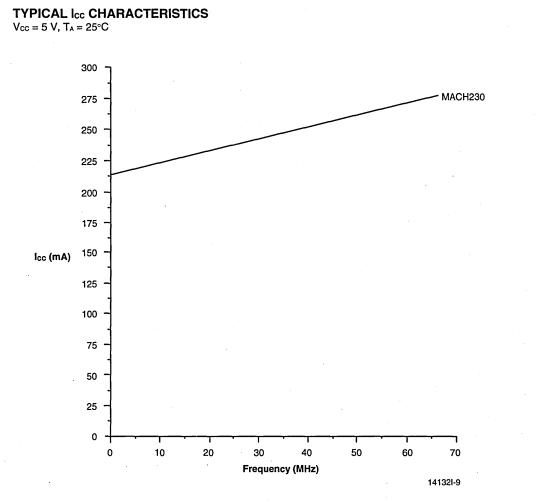

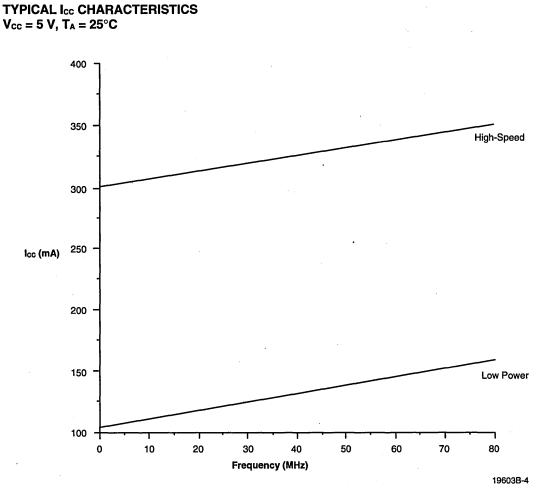

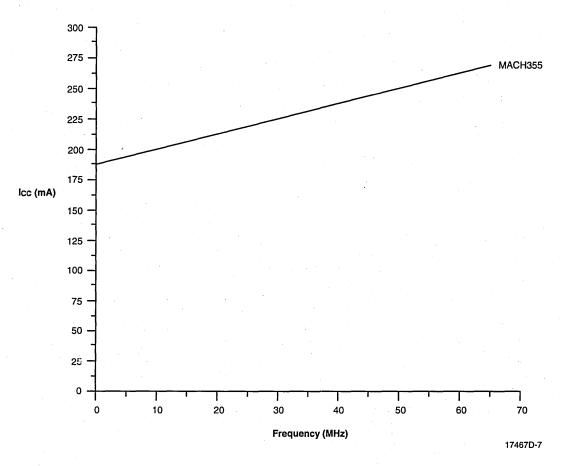

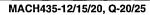

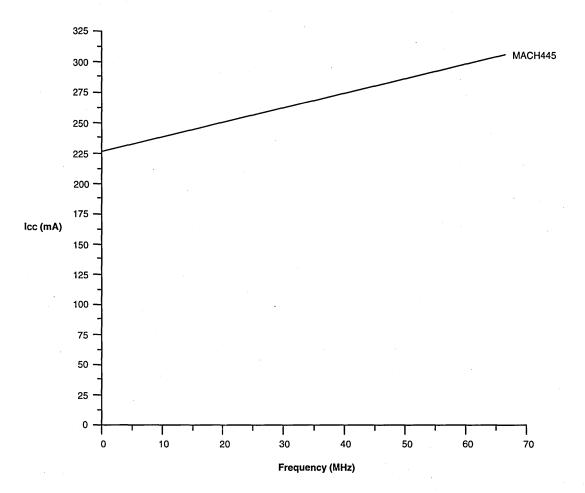

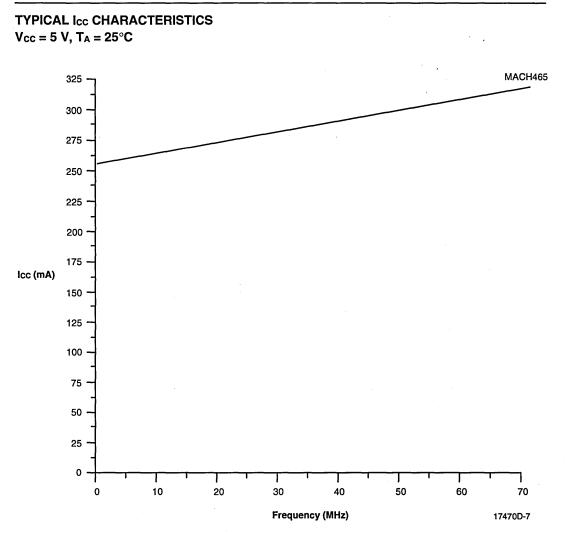

## TYPICAL I<sub>CC</sub> CHARACTERISTICS $V_{CC} = 5 V$ , $T_A = 25^{\circ}C$

The selected "typical" pattern is a 16-bit up/down counter. This pattern is programmed in each PAL block and is capable of being loaded, enabled, and reset.

Maximum frequency shown uses internal feedback and a D-type register.

•

#### **TYPICAL THERMAL CHARACTERISTICS**

Measured at 25°C ambient. These parameters are not tested.

| Parameter<br>Symbol | Parameter Description                                |              | Typ<br>PLCC | Unit |

|---------------------|------------------------------------------------------|--------------|-------------|------|

| θjc                 | Thermal impedance, junction to case                  |              | 14          | •C/W |

| θja                 | Thermal impedance, junction to ambient               |              | 39          | °C/W |

| θjma                | Thermal impedance, junction to ambient with air flow | 200 lfpm air | 33          | °C/W |

|                     | ambient with air flow                                | 400 lfpm air | 30          | °C/W |

|                     |                                                      | 600 lfpm air | 27          | °C/W |

|                     |                                                      | 800 lfpm air | 25          | °C/W |

#### Plastic θjc Considerations

The data listed for plastic  $\theta_{ic}$  are for reference only and are not recommended for use in calculating junction temperatures. The heat-flow paths in plastic-encapsulated devices are complex, making the  $\theta_{ic}$  measurement relative to a specific location on the package surface. Tests indicate this measurement reference point is directly below the die-attach area on the bottom center of the package. Furthermore,  $\theta_{ic}$  tests on packages are performed in a constant-temperature bath, keeping the package surface at a constant temperature. Therefore, the measurements can only be used in a similar environment.

------

### ■ 44 Pins

- 32 Macrocells

- 🔳 5 ns t<sub>PD</sub>

- 📕 167 MHz fçnt

- 38 Bus-Friendly Inputs

- Peripheral Component Interconnect (PCI) compliant

- Programmable power-down mode

- 32 Outputs

- 32 Flip-flops; 4 clock choices

- 2 "PAL26V16" Blocks

- Pin-compatible with MACH110, MACH210, MACH211, MACH215

- Improved routing over the MACH110

#### **GENERAL DESCRIPTION**

The MACH111 is a member of AMD's EE CMOS Performance Plus MACH 1 family. This device has approximately three times the logic macrocell capability of the popular PAL22V10 without loss of speed.

The MACH111 consists of two PAL blocks interconnected by a programmable switch matrix. The two PAL blocks are essentially "PAL26V16" structures complete with product-term arrays and programmable macrocells, which can be programmed as high speed or low power. The switch matrix connects the PAL blocks to each other and to all input pins, providing a high degree of connectivity between the fully-connected PAL blocks. This allows designs to be placed and routed efficiently.

The MACH111 macrocell provides either registered or combinatorial outputs with programmable polarity. If a registered configuration is chosen, the register can be configured as D-type or T-type to help reduce the number of product terms. The register type decision can be made by the designer or by the software. All macrocells can be connected to an I/O cell. If a buried macrocell is desired, the internal feedback path from the macrocell can be used, which frees up the I/O pin for use as an input.

Publication# 19376 Rev. C Amendment/0 Issue Date: May 1995 Advanced Micro Devices

FINAL

**DISTINCTIVE CHARACTERISTICS**

MACH111-5/7/10/12/15/20

**High-Density EE CMOS Programmable Logic**

COM'L: -5/7.5/10/12/15/20

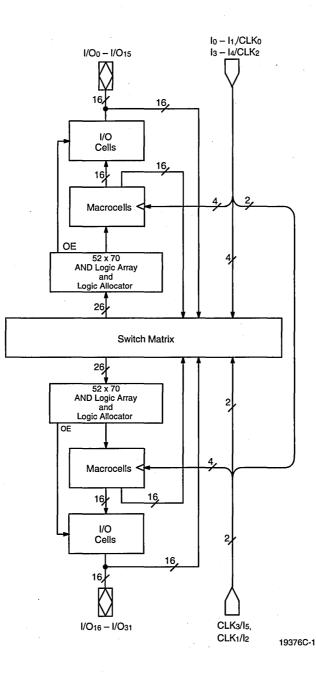

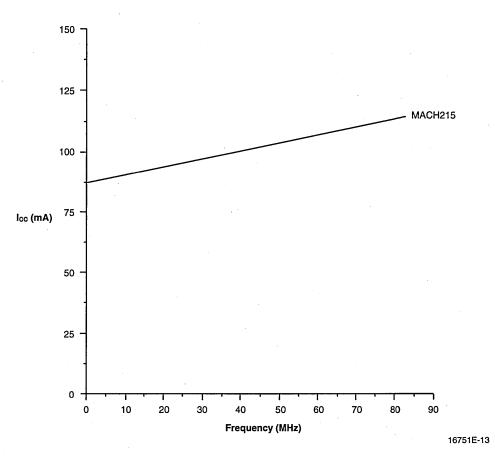

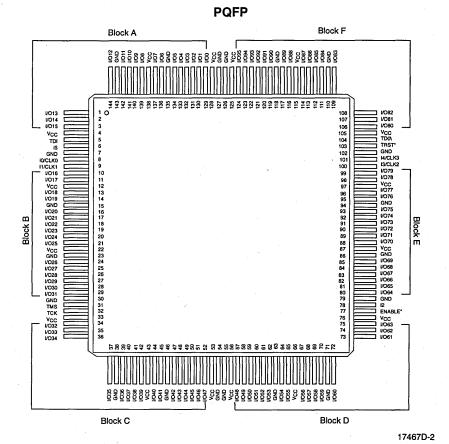

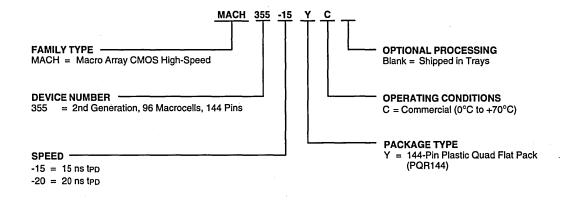

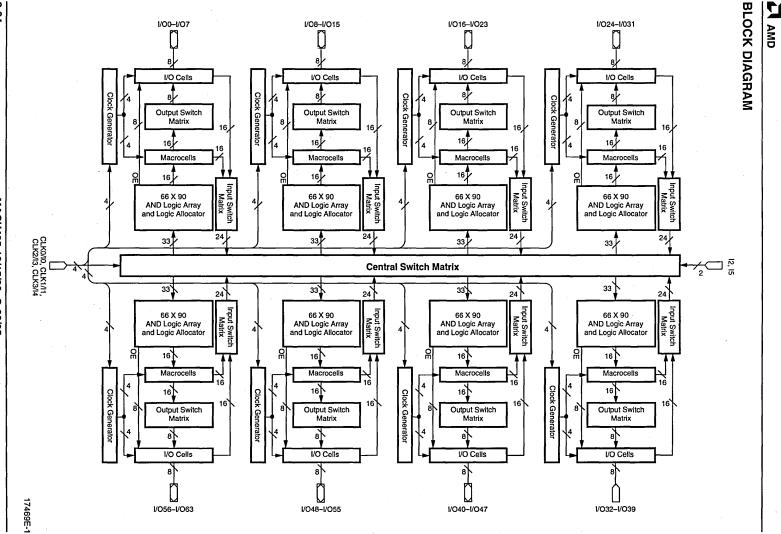

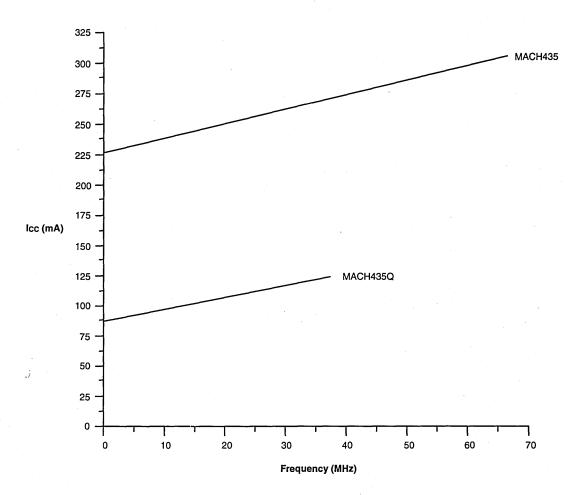

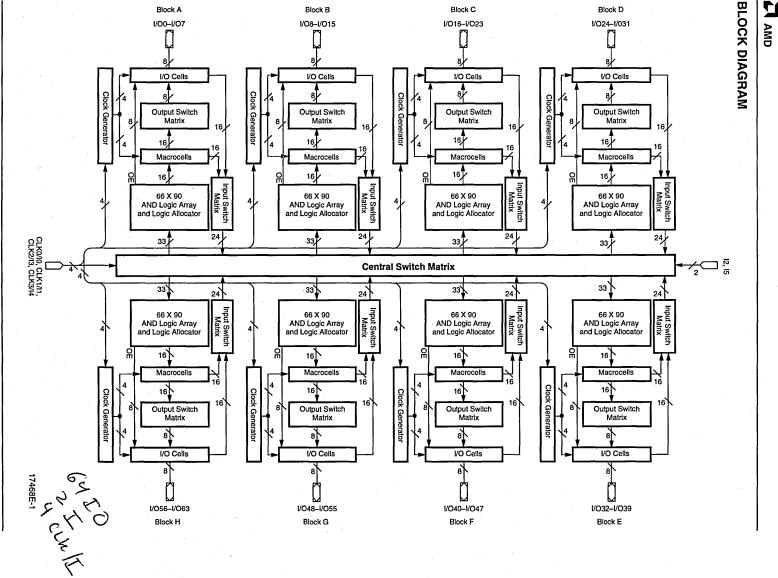

### **BLOCK DIAGRAM**

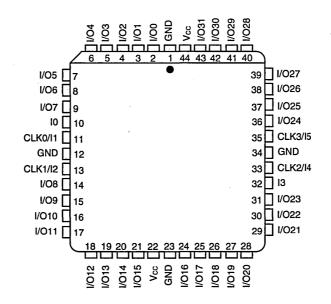

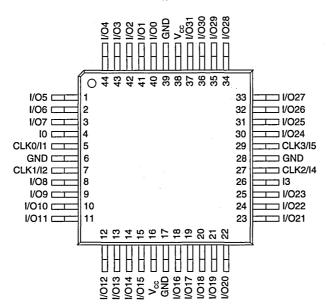

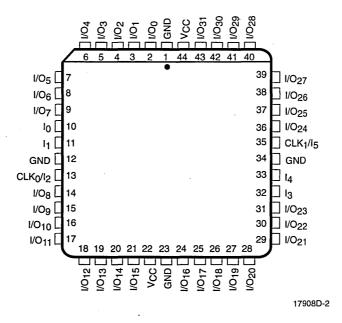

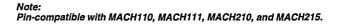

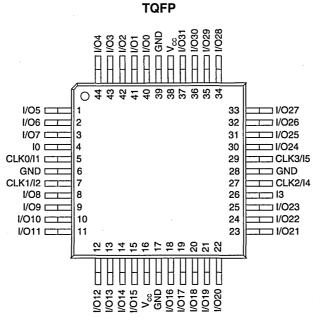

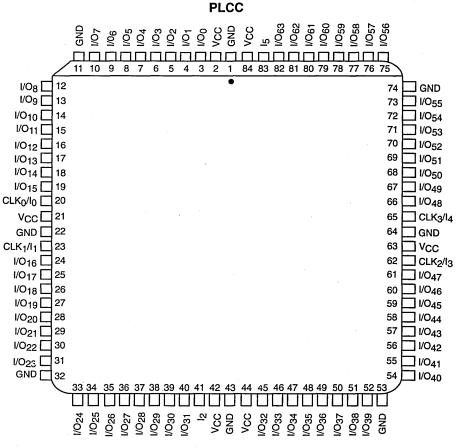

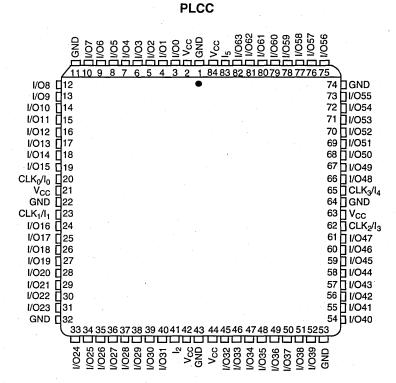

#### **CONNECTION DIAGRAM Top View**

PLCC

# CONNECTION DIAGRAM Top View

TQFP

Pin-compatible with MACH211 and MACH210A.

Note:

19376C-3

### **PIN DESIGNATIONS**

| CLK/I | = | Clock or Input |

|-------|---|----------------|

| GND   | = | Ground         |

| 1     | = | Input          |

| I/O   | = | Input/Output   |

| Vcc   | = | Supply Voltage |

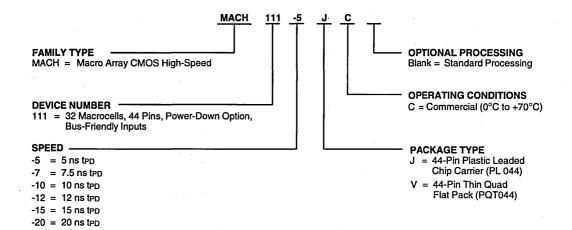

#### **ORDERING INFORMATION**

#### **Commercial Products**

AMD programmable logic products for commercial applications are available with several ordering options. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |     |  |  |

|--------------------|-----|--|--|

| MACH111-5          | JC  |  |  |

| MACH111-7          |     |  |  |

| MACH111-10         | JC. |  |  |

| MACH111-12         |     |  |  |

| MACH111-15         |     |  |  |

| MACH111-20         |     |  |  |

#### **Valid Combinations**

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

#### **FUNCTIONAL DESCRIPTION**

The MACH111 consists of two PAL blocks connected by a switch matrix. There are 32 I/O pins and 6 dedicated input pins feeding the switch matrix. These signals are distributed to the two PAL blocks for efficient design implementation. There are four clock pins that can also be used as dedicated inputs.

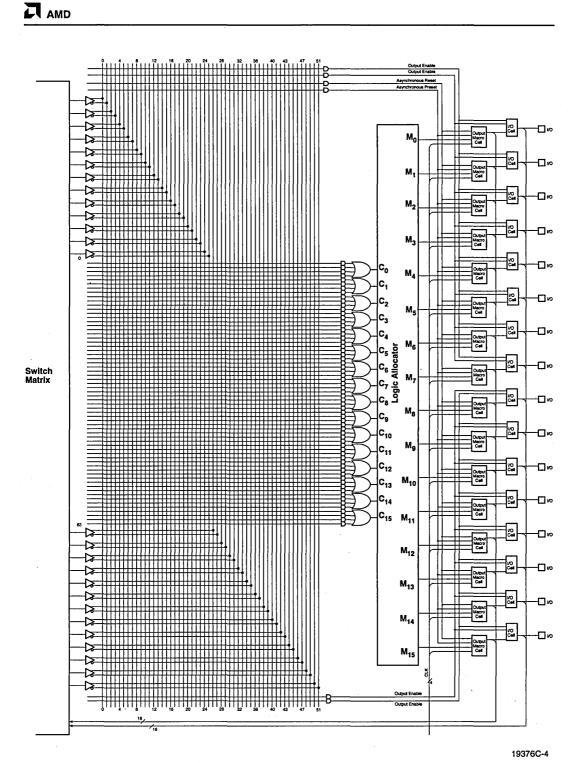

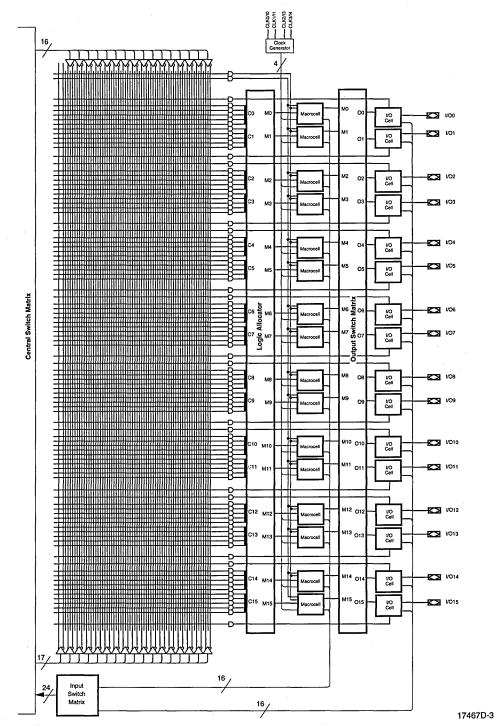

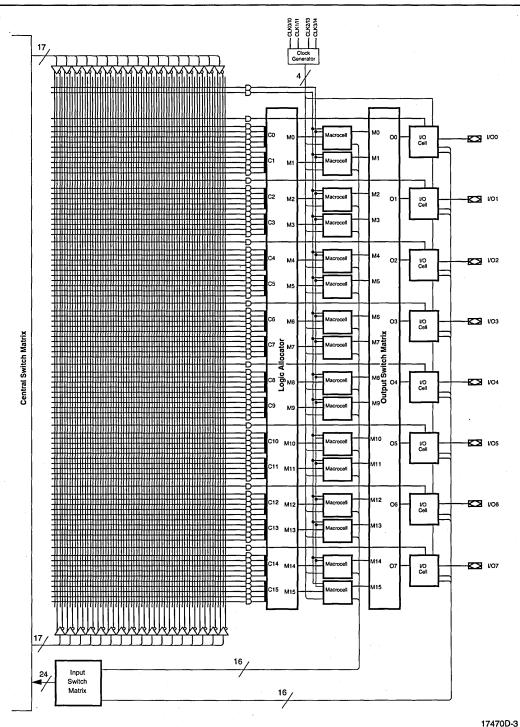

#### The PAL Blocks

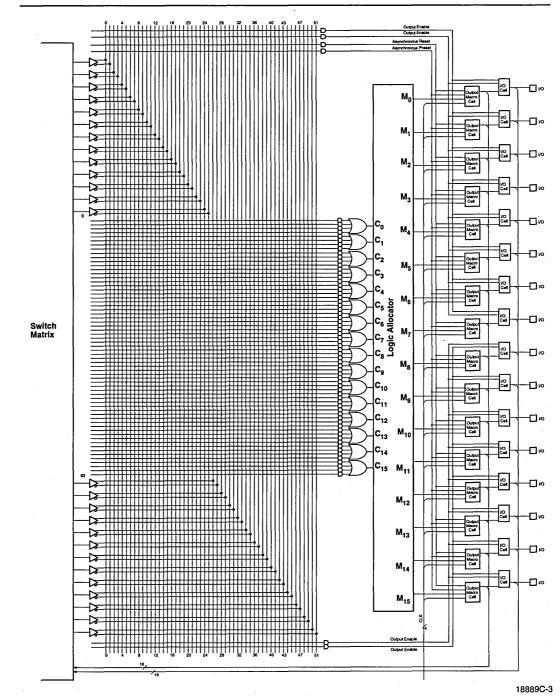

Each PAL block in the MACH111 (Figure 1) contains a 64-product-term logic array, a logic allocator, 16 macrocells and 16 I/O cells. The switch matrix feeds each PAL block with 26 inputs. This makes the PAL block look effectively like an independent "PAL26V16".

There are four additional output enable product terms in each PAL block. For purposes of output enable, the 16 I/O cells are divided into 2 banks of 8 macrocells. Each bank is allocated two of the output enable product terms.

An asynchronous reset product term and an asynchronous preset product term are provided for flip-flop initialization. All flip-flops within the PAL block are initialized together.

#### The Switch Matrix

The MACH111 switch matrix is fed by the inputs and feedback signals from the PAL blocks. Each PAL block provides 16 internal feedback signals and 16 I/O feedback signals. The switch matrix distributes these signals back to the PAL blocks in an efficient manner that also provides for high performance. The design software automatically configures the switch matrix when fitting a design into the device.

#### **The Product-Term Array**

The MACH111 product-term array consists of 64 product terms for logic use, and 6 special-purpose product terms. Four of the special-purpose product terms provide programmable output enable, one provides asynchronous reset, and one provides asynchro-

nous preset. Two of the output enable product terms are used for the first eight I/O cells; the other two control the last eight macrocells.

#### The Logic Allocator

The logic allocator in the MACH111 takes the 64 logic product terms and allocates them to the 16 macrocells as needed. Each macrocell can be driven by up to 12 product terms. The design software automatically configures the logic allocator when fitting the design into the device.

Table 1 illustrates which product term clusters are available to each macrocell within a PAL block. Refer to Figure 1 for cluster and macrocell numbers.

| Output Macrocell | Available Clusters |

|------------------|--------------------|

| Mo               | Co, C1             |

| M1               | C0, C1, C2         |

| M2               | C1, C2, C3         |

| M3               | C2, C3, C4         |

| M4               | C3, C4, C5         |

| M5               | C4, C5, C6         |

| M <sub>6</sub>   | C5, C6, C7         |

| M7               | C6, C7             |

| Ma               | C8, C9             |

| M <sub>9</sub>   | C8, C9, C10        |

| M10              | C9, C10, C11       |

| M11              | C10, C11, C12      |

| M12              | C11, C12, C13      |

| M13              | C12, C13, C14      |

| M14              | C13, C14, C15      |

| M15              | C14, C15           |

Table 1. Logic Allocation

#### The Macrocell

The MACH111 macrocells can be configured as either registered or combinatorial, with programmable polarity. The macrocell provides internal feedback whether configured as registered or combinatorial. The flip-flops can be configured as D-type or T-type, allowing for product-term optimization.

The flip-flops can individually select one of four clock pins, which are also available as data inputs. The registers are clocked on the LOW-to-HIGH transition of the clock signal. The flip-flops can also be asynchronously initialized with the common asynchronous reset and preset product terms.

#### **Power-Down Mode**

The MACH111 features a programmable low-power mode in which individual signal paths can be programmed as low power. These low-power speed paths will be slightly slower than the non-low-power paths. This feature allows speed critical paths to run at maximum frequency while the rest of the paths operate in the low-power mode, resulting in power savings of up to 50%.

#### The I/O Cell

The I/O cell in the MACH111 consists of a three-state output buffer. The three-state buffer can be configured in one of three ways: always enabled, always disabled, or controlled by a product term. If product term control is chosen, one of two product terms may be used to provide the control. The two product terms that are available are common to eight I/O cells. Within each PAL block, two product terms are available for selection by the first eight three-state outputs; two other product terms are available for selection by the last eight three-state outputs.

#### **Bus-Friendly Inputs and I/Os**

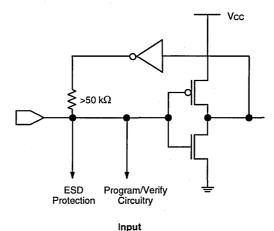

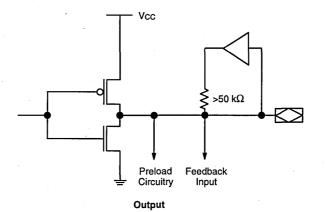

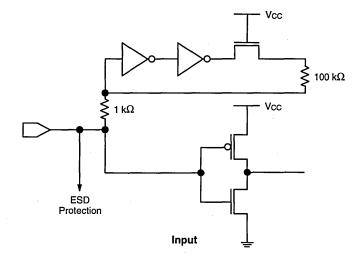

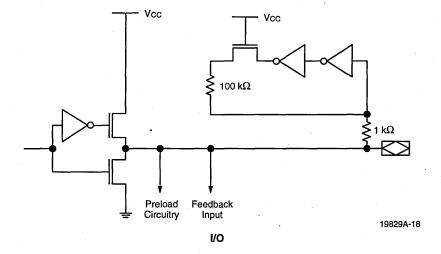

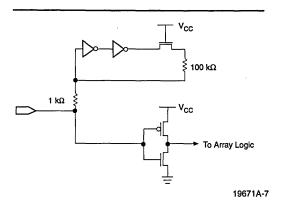

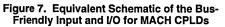

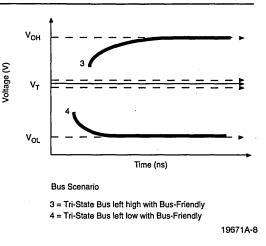

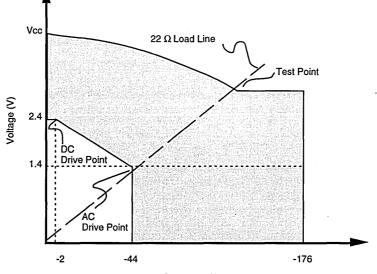

The MACH111 inputs and I/Os include two inverters in series which loop back to the input. This double inversion reinforces the state of the input and pulls the voltage away from the input threshold voltage. Unlike a pull-up, this configuration cannot cause contention on a bus. For an illustration of this configuration, please turn to the input and output equivalent schematics at the end of this data book.

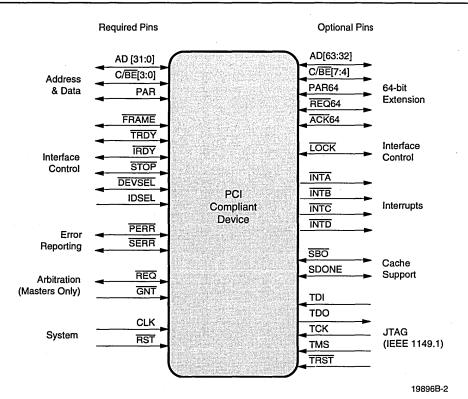

#### **PCI Compliance**

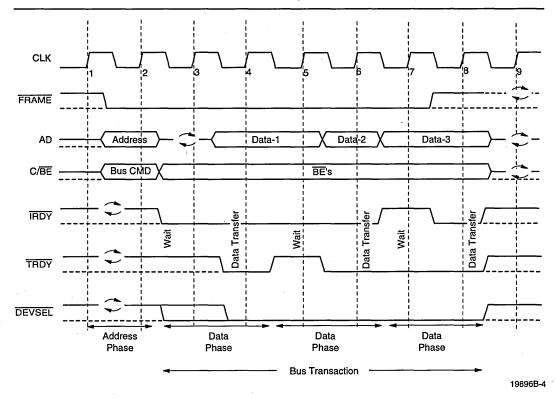

The MACH111-7/10 is fully compliant with the *PCI Local Bus Specification* published by the PCI Special Interest Group. The MACH111-7/10's predictable timing ensures compliance with the PCI AC specifications independent of the design. On the other hand, in CPLD and FPGA architectures without predictable timing, PCI compliance is dependent upon routing and product term distribution.

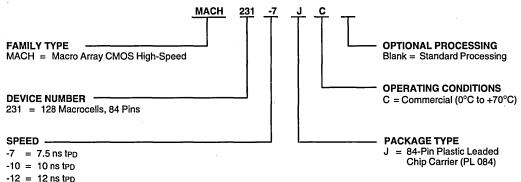

Figure 1. MACH111 PAL Block

#### MACH111-5/7/10/12/15/20

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65°C to +150°C         |

|-------------------------------------------|

| Ambient Temperature<br>With Power Applied |

| Supply Voltage with                       |

| Respect to Ground0.5 V to +7.0 V          |

| DC Input Voltage0.5 V to Vcc + 0.5 V      |

| DC Output or I/O                          |

| Pin Voltage                               |

| Static Discharge Voltage 2001 V           |

| Latchup Current                           |

| (T <sub>A</sub> = 0°C to 70°C)            |

|                                           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

#### **OPERATING RANGES**

| Commercial | (C) Devices |  |

|------------|-------------|--|

|------------|-------------|--|

| Ambient Temperature (T <sub>A</sub> ) |                |

|---------------------------------------|----------------|

| Operating in Free Air                 | 0°C to +70°C   |

| Supply Voltage (Vcc)                  |                |

| with Respect to Ground +4.75          | 5 V to +5.25 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

#### DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

|                     |                                          |                                                                                                                   |     | PRELIMINARY |      |            |

|---------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-------------|------|------------|

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                                   | Min | Тур         | Max  | Unit       |

| Vон                 | Output HIGH Voltage                      | $I_{OH} = -3.2 \text{ mA}, V_{CC} = Min$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$                                  | 2.4 |             |      | v          |