# **PRODUCT OVERVIEW**

The Vadem VG-469 is a compact, highly integrated PC Card controller chip implementing the PC Card Standard along with ExCA<sup>TM</sup> extensions. It is register-compatible to the Intel® 82365SL. Supporting two PC Card sockets, it is uniquely designed for space-limited, cost-sensitive applications where battery life is an important factor. For systems requiring more than two sockets, the VG-469 can be cascaded to support up to four sockets without external logic. With external decoder logic, unlimited cascading is possible. Typical VG-469 applications include small notebook computers, palmtops and other personal information devices.

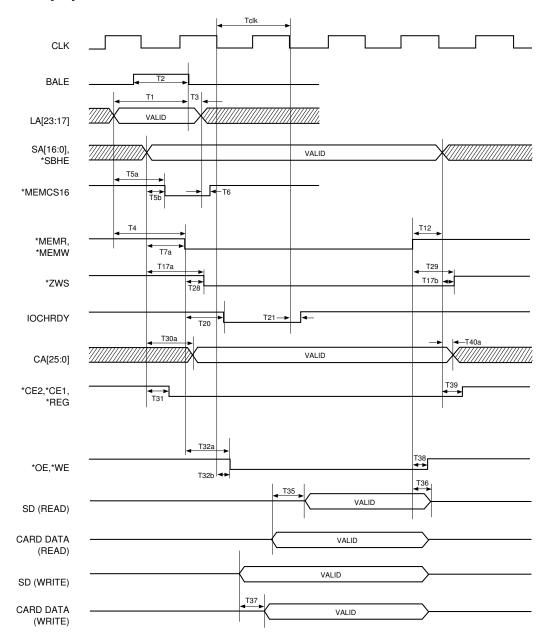

The VG-469 supports the system bus timing of standard ISA and EISA architectures. A programmable configuration mechanism allows the system manufacturer to control many PC Card setup parameters in software or firmware.

The VG-469 supports mixed voltage operation. The internal logic, the ISA bus interface and each of the two PC Card sockets can be independently operated at either 3.3V or 5V.

Power management based on activity monitoring and the VG-469's very low current-draw minimize the demand for battery power.

Jumperless add-in card installation is supported by the VG-469 with the on-chip implementation of the Plug and Play ISA version 1.0a, which lets the software relocate the VG-469 registers from the default at 3E0h/3E1h or 3E2h/3E3h.

# **PRODUCT FEATURES**

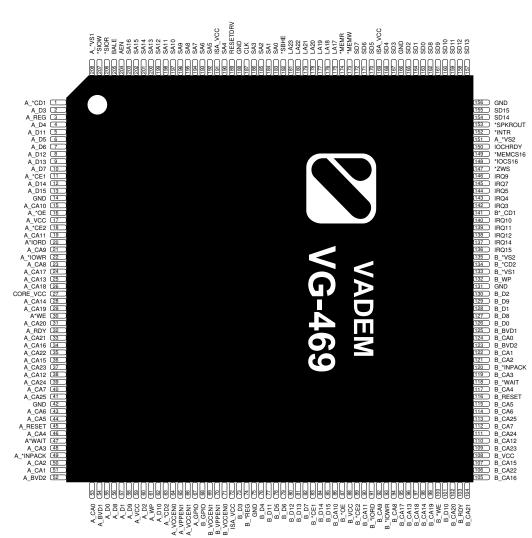

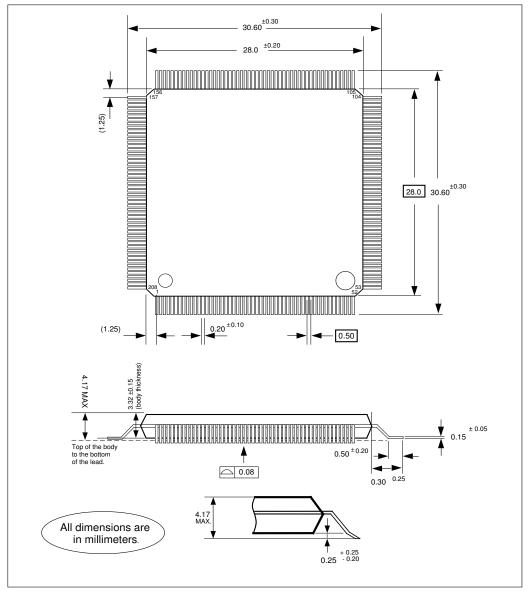

- 208-pin chip provides full ExCA implementation of two PC Card sockets.

- $\Rightarrow$  Complies with PC Card Standard, and backward compatible to PCMCIA 2.1/JEIDA 4.1.

- $\Rightarrow$  Supports both memory cards and I/O cards.

- $\Rightarrow$  Supports PCMCIA-ATA specification.

- $\Rightarrow$  Memory-saving execute-in-place standard (XIP).

- ⇒ Supports overlapping I/O windows across sockets and duplicate I/O cards via \*INPACK signal.

- $\Rightarrow$  Cascadable up to four sockets without "glue," unlimited cascading with external logic.

- Register-compatible with Intel 82365SL.

- Five mappable memory windows and two I/O windows for each socket.

- Internal buffering supports 'hot' insertion and removal of cards.

- Integrated timer supports power management based on activity monitoring.

#### Preface

- Socket activity LED support.

- Plug and Play ISA version 1.0a with EEPROM support.

- $\Rightarrow$  Allows dynamic relocation of VG-469 in the address space to avoid conflict with system resources.

- $\Rightarrow$  Allows use of as many PCMCIA controllers as needed.

- $\Rightarrow$  Simplifies interface to and design of docking stations.

- Mixed voltage operation.

- $\Rightarrow$  Supports 3.3V or 5V ISA bus interface.

- $\Rightarrow$  Supports 3.3V or 5V PCMCIA socket interface.

- $\Rightarrow$  Internal logic operates at either 3.3V or 5V.

- Built-in over-voltage protection logic.

⇒ Prevents damage to low-voltage cards (3.3V and future X.XV).

- Optional buffer directional/enable control for buffered cable driving.

- Support for PC Card DMA operation.

- Includes two GPIO pins.

This chapter provides the pin assignment, signal description, and pin descriptions for the VG-469 PC Card Socket Controller.

#### DEFAULT PIN ASSIGNMENT

# Chapter 1 Introduction

### VADEM VG-469 PC Card Socket Controller

|                                                                                                                                                                           | Signal Description |     |                                           |        |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------------------------------------------|--------|--|--|--|--|

| Pin #                                                                                                                                                                     | Signal Names       | Тур | Characteristics                           | # Pins |  |  |  |  |

| 204                                                                                                                                                                       | AEN                | Ι   | TTL Compatible                            | 1      |  |  |  |  |

| 205                                                                                                                                                                       | BALE               | Ι   | TTL Compatible                            | 1      |  |  |  |  |

| 54, 125                                                                                                                                                                   | BVD1 (*STSCHG/*RI) | Ι   | Schmitt Trigger w/pull-up                 | 2      |  |  |  |  |

| 52, 123                                                                                                                                                                   | BVD2 (*SPKR)       | Ι   | Schmitt Trigger w/pull-up                 | 2      |  |  |  |  |

| 15, 19, 21,<br>23-26, 28,<br>29, 31, 33-<br>41, 43, 44,<br>46, 48, 50,<br>51, 53, 86,<br>90, 92, 94-<br>99, 102,<br>104-107,<br>109-115,<br>117, 119,<br>121, 122,<br>124 | CA[25:0]           | 0   | 2mA Tri-State                             | 52     |  |  |  |  |

| 63, 1, 134,<br>141                                                                                                                                                        | *CD[2:1]           | Ι   | Schmitt Trigger w/pull-up                 | 4      |  |  |  |  |

| 18, 11, 89,<br>83                                                                                                                                                         | *CE[2:1]           | 0   | 2mA Tri-State                             | 4      |  |  |  |  |

| 187                                                                                                                                                                       | CLK                | Ι   | TTL Compatible                            | 1      |  |  |  |  |

| 2, 4-10, 12,<br>13, 55-58,<br>60, 62, 73,<br>76-82, 84,<br>85, 101,<br>126-130                                                                                            | D[15:0]            | I/O | I = TTL Compatible<br>O = 2 mA Tri-state  | 32     |  |  |  |  |

| 14, 42, 75,<br>131, 156,<br>166, 188                                                                                                                                      | GND                |     |                                           | 7      |  |  |  |  |

| 67                                                                                                                                                                        | A_GPIO             | I/O | I = TTL Compatible<br>O = 12 mA Tri-state | 1      |  |  |  |  |

| 68                                                                                                                                                                        | B_GPIO             | I/O | I = TTL Compatible<br>O = 12 mA Tri-state | 1      |  |  |  |  |

| 49, 120                                                                                                                                                                   | *INPACK            | Ι   | TTL Compatible w/pull-up                  | 2      |  |  |  |  |

# Signal Description

| Pin #                              | Signal Names           | Тур | Characteristics                          | # Pins |

|------------------------------------|------------------------|-----|------------------------------------------|--------|

| 152                                | *INTR (E2SK)           | I/O | I = TTL Compatible<br>O = 2 mA Tri-state | 1      |

| 150                                | IOCHRDY                | 0   | 16 mA Tri-State                          | 1      |

| 148                                | *IOCS16                | 0   | 16 mA Tri-State                          | 1      |

| 20, 91                             | *IORD                  | 0   | 2 mA Tri-State                           | 2      |

| 22, 93                             | *IOWR                  | 0   | 2 mA Tri-State                           | 2      |

| 138                                | IRQ12(LED)             | 0   | 12 mA Tri-State                          | 1      |

| 136-137,<br>139,140,146<br>144-142 | IRQ[15, 14, 11:9, 5:3] | 0   | 2 mA Tri-State                           | 8      |

| 145                                | IRQ7(*HDACK)           | I/O | I = TTL Compatible<br>O = 2mA Tri-State  | 1      |

| 181-175                            | LA[23:17]              | Ι   | TTL Compatible                           | 7      |

| 149                                | *MEMCS16               | 0   | 16 mA Tri-State                          | 1      |

| 174                                | *MEMR                  | Ι   | TTL Compatible                           | 1      |

| 173                                | *MEMW                  | Ι   | TTL Compatible                           | 1      |

| 16, 87                             | *OE                    | 0   | 2mA Tri-State                            | 2      |

| 32, 103                            | RDY/*BSY (*IREQ)       | Ι   | Schmitt Trigger w/pull-up                | 2      |

| 3, 74                              | *REG                   | 0   | 2mA Tri-State                            | 2      |

| 45, 116                            | RESET                  | 0   | 2mA Tri-State                            | 2      |

| 189                                | RESETDRV               | Ι   | Schmitt Trigger                          | 1      |

| 202-192,<br>190, 186-<br>183       | SA[16:0]               | Ι   | TTL Compatible                           | 17     |

| 182                                | *SBHE                  | Ι   | TTL Compatible                           | 1      |

| 206                                | *SIOR                  | Ι   | Schmitt Trigger                          | 1      |

| 207                                | *SIOW                  | Ι   | Schmitt Trigger                          | 1      |

# Chapter 1 Introduction

| Pin #                                                     | Signal Names            | Тур | Characteristics                           | # Pins |

|-----------------------------------------------------------|-------------------------|-----|-------------------------------------------|--------|

| 155, 154,<br>157-162,<br>172-170,<br>168, 167,<br>165-163 | SD[15:0]                | I/O | I = TTL Compatible<br>O = 12 mA Tri-state | 16     |

| 153                                                       | *SPKROUT (E2DIO)        | I/O | I = TTL Compatible<br>O = 2 mA Tri-state  | 1      |

| 66, 64, 69,<br>71                                         | VCCEN[1:0]              | I/O | I = TTL Compatible<br>O = 2 mA Tri-state  | 4      |

| 17, 59                                                    | A_VCC                   |     |                                           | 2      |

| 88, 108                                                   | B_VCC                   |     |                                           | 2      |

| 27                                                        | CORE_VCC                |     |                                           | 1      |

| 72, 169, 191                                              | ISA_VCC                 |     |                                           | 3      |

| 65, 70                                                    | VPPEN1                  | 0   | 2 mA Output                               | 2      |

| 151, 135                                                  | *VS2(VPPEN0)            | I/O | I = TTL Compatible<br>O = 12 mA Tri-state | 2      |

| 208                                                       | A_*VS1(*VSENBL)         | I/O | I = TTL Compatible<br>O = 2 mA Tri-state  | 1      |

| 133                                                       | B_*VS1<br>(E2CS/*HDACK) | I/O | I = TTL Compatible<br>O = 2 mA Tri-state  | 1      |

| 47, 118                                                   | *WAIT                   | Ι   | TTL Compatible w/pull-up                  | 2      |

| 30, 100                                                   | *WE/*PRGM               | 0   | 2 mA Tri-State                            | 2      |

| 61, 132                                                   | WP (*IOIS16)            | Ι   | TTL Compatible w/pull-up                  | 2      |

| 147                                                       | *ZWS                    | 0   | 16 mA 5V Tri-State                        | 1      |

| Symbol                | Туре | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AEN                   | Ι    | 204     | System Address Enable. High during DMA cycles, low otherwise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BALE                  | Ι    | 205     | Bus Address Latch Enable. An active high input used to latch LA[23:17] at the beginning of a bus cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

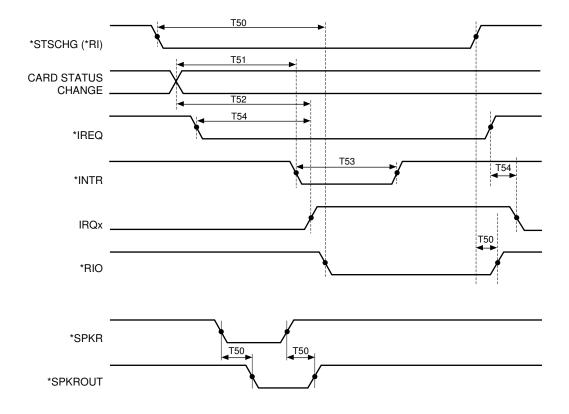

| BVD1<br>(*STSCHG/*RI) | Ι    | 54,125  | If BVD1 is negated by a memory PC Card<br>with a battery, it indicates that the battery is<br>no longer serviceable and data is lost.<br>For I/O PC Cards, this signal is held high<br>when either or both the Signal on Change bit<br>and Changed bit in the Card Status Register<br>on the PC Card are set to zero. When both<br>the bits are one, the signal is held low. The<br>Changed bit is the logical OR of the bits<br>CVBAT1, CVBAT2, CWP, and CBSYRDY<br>in the Pin Replacement Register on the PC<br>Card. Or this pin is connected to Ring<br>Indicate, which is qualified by Ring Indicate<br>Enable to become *RIO. *RIO can be routed<br>to one of the following output pins: A_GPIO,<br>B_GPIO or *INTR. |

| BVD2<br>(*SPKR)       | Ι    | 52,123  | <ul> <li>BVD1 and BVD2 are generated by memory<br/>PC Cards with onboard batteries. These<br/>signals indicate the health of the battery.</li> <li>Both are asserted high when the battery is in<br/>good condition. When BVD2 is negated<br/>while BVD1 is still asserted, the battery<br/>should be replaced, although data integrity<br/>on the memory PC Card is still assured.</li> <li>When the I/O interface is selected, BVD2<br/>may be used to provide a single amplitude<br/>Digital Audio waveform intended to be<br/>passed through to the system's speaker<br/>without signal conditioning. If the PC Card<br/>is the DMA device, this pin can be redefined<br/>as *DREQ input from the card.</li> </ul>     |

### Pin Descriptions

# Chapter 1 Introduction

| Symbol   | Туре | Pin No.                                                                                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CA[25:0] | 0    | 15, 19, 21, 23-26,<br>28, 31, 33-41, 43,<br>44, 46, 48, 50,<br>51, 53, 86, 90,<br>92, 94-99, 102,<br>104-107, 109-<br>115, 117, 119,<br>121, 122, 124 | Card Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| *CD[2:1] | I    | 63, 1, 134, 141                                                                                                                                       | Detects proper card insertion. The signals are<br>connected to ground internally on the PC<br>Card and will be forced low whenever a card<br>is placed in a host socket. Status is available<br>to software through the Interface Status<br>Register.                                                                                                                                                                                                                                                                                                  |

| *CE[2:1] | 0    | 18, 11, 89, 83                                                                                                                                        | Active low card enable signals. *CE1 is used<br>to enable even bytes. *CE2 for odd bytes. A<br>multiplexing scheme based on A0, *CE1,<br>*CE2 allows 8-bit hosts to access all data on<br>Card Data [7:0] if desired.                                                                                                                                                                                                                                                                                                                                  |

| CLK      | Ι    | 187                                                                                                                                                   | System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| D[15:0]  | I/O  | 2, 4-10, 12, 13,<br>55-58, 60, 62, 73,<br>76-82, 84, 85,<br>101, 126-130                                                                              | Card Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A_GPIO   | I/O  | 67                                                                                                                                                    | General purpose input/output. May also be<br>used for one of several purposes.<br>- An active low input indicates that Vpp<br>power line has reached the user specified<br>range.<br>- An input indication a card eject or card<br>insertion pending.<br>- An input source for generating a card status<br>change interrupt.<br>- Power down control input.<br>- Programmable chip select output.<br>- Option A_VPPEN0.<br>- *LED output.<br>- *RIO output.<br>- Host TC (Terminal Count) input in a DMA<br>operation.<br>- Zoom Video Buffer Control. |

| Symbol          | Туре | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B_GPIO          | I/O  | 68      | <ul> <li>General purpose output. May also be used for<br/>one of several purposes.</li> <li>Programmable chip select output.</li> <li>Optional B_VPPEN0.</li> <li>*LED output.</li> <li>*RIO output.</li> <li>HDRQ output in a DMA operation.</li> <li>Resistor strapping input during<br/>RESETDRV to indicate the voltage of the<br/>ISA bus; high for 3.3 volt and low for 5 volt.</li> </ul>                                   |

| *INPACK         | I    | 49,120  | Input Acknowledge. Asserted by some PC<br>Cards during I/O read cycles. This signal is<br>used by the VG-469 to control the enable of<br>its input data buffer between the card and<br>CPU. If the PC Card is the DMA device, this<br>pin can be redefined as *DREQ input from<br>the card.                                                                                                                                        |

| *INTR<br>(E2SK) | I/O  | 152     | Interrupt Request output: Active low output<br>requesting a nonmaskable interrupt to the<br>CPU. Ring Indicator from PC Card can be<br>steered to this pin. If B_*VS1 is strapped low<br>in the extended configuration, this pin<br>becomes the clock output to the external<br>serial EEPROM for supporting Plug and Play<br>ISA. Also, a resistor strapping input during<br>RESETDRV to select the internal register<br>address. |

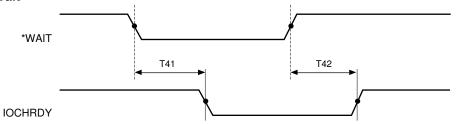

| IOCHRDY         | 0    | 150     | I/O Channel Ready. This active high signal<br>indicates that the current I/O bus cycle has<br>completed. When a PC Card needs to extend<br>a Read or Write cycle, the VG-469 pulls<br>IOCHRDY low. IOCHRDY can be<br>deasserted by either *WAIT, or by<br>programming to add wait states for 16-bit<br>memory and I/O cycles.                                                                                                      |

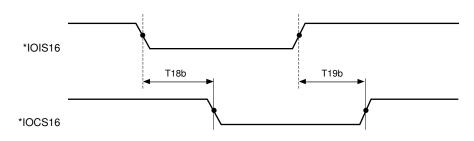

| *IOCS16         | 0    | 148     | This active low I/O 16-bit chip select signal<br>indicates to the host system the current I/O<br>cycle is a 16-bit access. A 16-bit to 8-bit<br>conversion is done if it is inactive.                                                                                                                                                                                                                                              |

# Chapter 1 Introduction

| Symbol          | Туре | Pin No.               | Description                                                                                                                                                                                                          |

|-----------------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *IORD           | 0    | 20, 91                | I/O Read signal is driven active to read data<br>from the PC Card's I/O space. The *REG<br>signal and at least one of the Card Enable<br>signals must also be active for the I/O<br>transfer to take place.          |

| *IOWR           | 0    | 22, 93                | I/O Write signal is driven active to write data<br>to the PC Card's I/O space. The *REG signal<br>and at least one of the Card Enable signals<br>must also be active for the I/O transfer to<br>take place.          |

| IRQ[14, 9, 5:3] | 0    | 137, 146, 144-<br>142 | Interrupt Request signals to the ISA bus.                                                                                                                                                                            |

| IRQ7            | I/O  | 145                   | By default this is IRQ7 to the ISA bus. In<br>external mode when Plug and Play is<br>enabled, this pin can become *HDACK from<br>the DMA controller if bit 7 of the Extended<br>Mode Register-A is written with a 1. |

| IRQ[11:10]      | 0    | 139, 140              | By default these are the Interrupt Request<br>signals to the ISA bus. Alternately, these<br>become the VPPEN0 outputs if bit[1:0] of the<br>Extended Mode Register-A are so<br>programmed.                           |

| IRQ12           | 0    | 138                   | By default this is the Interrupt Request to the<br>ISA bus. It becomes *LED if LED function is<br>enabled and no GPIO is programmed as RIO.                                                                          |

| IRQ15           | 0    | 136                   | By default this is the Interrupt Request to the<br>ISA bus. It becomes *RIO if RIO function is<br>enabled and no GPIO is programmed as RIO.                                                                          |

| LA[23:17]       | Ι    | 181-175               | Local Address bus used to address memory<br>devices on the ISA bus. Together with the<br>system address signals, they address up to<br>16MB on the ISA bus.                                                          |

| *MEMCS16        | 0    | 149                   | This active low 16-bit memory chip select<br>signal indicates to the host system that the<br>current memory cycle is a 16-bit access.                                                                                |

| *MEMR           | Ι    | 174                   | Active low command signal indicates a memory read cycle on the ISA bus.                                                                                                                                              |

| *MEMW           | Ι    | 173                   | Active low command signal indicates a memory write cycle on the ISA bus.                                                                                                                                             |

| Symbol              | Туре | Pin No.                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *OE                 | 0    | 16, 87                   | Active low signal used to gate memory reads from memory cards.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RDY/*BSY<br>(*IREQ) | Ι    | 32,103                   | Memory PC Cards drive Ready / *Busy low<br>to indicate that the memory card circuits are<br>busy processing a previous write command.<br>It is set high when they are ready to accept a<br>new data transfer command.                                                                                                                                                                                                                                                                                             |

|                     |      |                          | For I/O PC Cards, this pin is used as an<br>interrupt request and driven low to indicate<br>to the host that a device on the I/O PC Card<br>requires service by the host software. The<br>signal is held at the inactive level when no<br>interrupt is requested.                                                                                                                                                                                                                                                 |

| *REG                | 0    | 3, 74                    | Select attribute memory. This signal is set<br>inactive (high) for all accesses to common<br>memory of a PC Card. When it is active,<br>access is limited to Attribute Memory when<br>*WE or *OE are active, and to I/O ports<br>when *IORD or *IOWR are active. I/O PC<br>Cards will not respond to *IORD or *IOWR<br>when the *REG signal is inactive. During<br>ISA DMA operations the *REG signal is<br>inactive. If the PC Card is the DMA device,<br>this pin is redefined as DACK output to the<br>socket. |

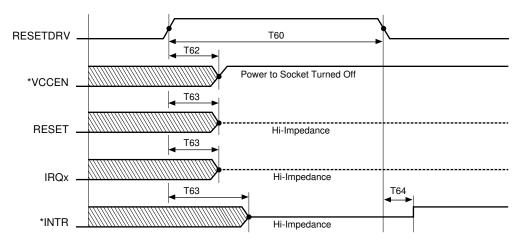

| RESET               | 0    | 45,116                   | Provides a hard reset to a PC Card and clears<br>the Card Configuration Option Register, thus<br>placing card in an unconfigured (memory<br>interface) state.                                                                                                                                                                                                                                                                                                                                                     |

| RESETDRV            | Ι    | 189                      | Active high indicates a main system reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SA[16:0]            | Ι    | 203-192, 190,<br>186-183 | System Address bus used to address memory<br>and I/O devices on the ISA bus. These<br>signals are latched and are valid throughout<br>the bus cycle.                                                                                                                                                                                                                                                                                                                                                              |

| *SBHE               | Ι    | 182                      | System Byte High Enable. When asserted,<br>this active low signal indicates that a data<br>transfer is occurring on the upper byte of the<br>system data bus.                                                                                                                                                                                                                                                                                                                                                     |

# Chapter 1 Introduction

| Symbol              | Туре | Pin No.                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------|------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD[15:0]            | I/O  | 155, 154, 157-<br>162, 172-170,<br>168, 167, 165-<br>163 | System Data Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

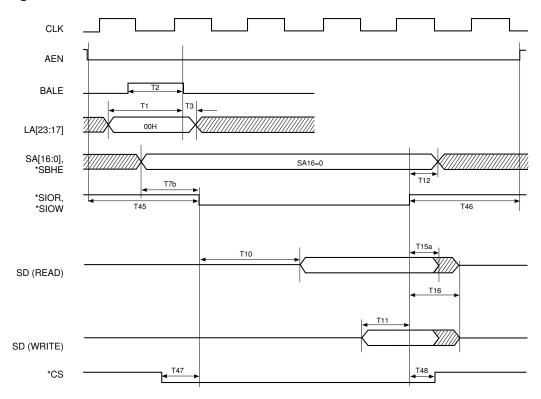

| *SIOR               | Ι    | 206                                                      | Active low command signal indicates an I/O read cycle on the ISA bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| *SIOW               | Ι    | 207                                                      | Active low command signal indicates an I/O write cycle on the ISA bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| *SPKROUT<br>(E2DIO) | I/O  | 153                                                      | Digital audio signal which provides a single<br>amplitude (digital) audio waveform to drive<br>the system's speaker. Passes through *SPKR<br>from an I/O PC Card. This signal must be<br>held high when no audio signal is present.<br>Also, a resistor strapping input during<br>RESETDRV to determine if the chip is<br>operated in extended configuration for cable<br>driving. While in extended configuration, if<br>B_*VS1 is strapped low, this pin becomes<br>the data port to and from the external serial<br>EEPROM for supporting Plug and Play ISA. |

| VCCEN[1:0]          | I/O  | 66, 64, 69, 71                                           | Power Control signals for card Vcc. These<br>are resistor strapped to the level which turns<br>off the Vcc Switch and are input during<br>RESETDRV to determine the polarity of the<br>Vcc Enable functions.                                                                                                                                                                                                                                                                                                                                                    |

| VPPEN1              | 0    | 65, 70                                                   | Power Control signal for card Vpp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Symbol | Туре | Pin No.  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *VS2   | I/O  | 151, 135 | Voltage Sense 2 inputs, which are connected<br>to pin 57 of the PCMCIA sockets. Together<br>with *VS1, these pins determine the<br>operating voltage of the card. In a 5-volt only<br>system where the voltage sensing is not<br>needed, or in a system which provides<br>limited voltage sensing capability (5 volt<br>versus 3.3 volt, but not X.X volt) these pins<br>can be redefined as VPPEN0 outputs if bit<br>[1:0] of the Extended Mode Register are so<br>programmed. In the extended configuration<br>where capable driving is required, these pins<br>become ISA buffer direction controls<br>(HBUFDIR and LBUFDIR) if B_*VS2 is<br>strapped low; or become socket B buffer<br>enable (*BSIGEN) and direction control<br>(DIR) if B_*VS2 is strapped high. |

| A_*VS1 | I/O  | 208      | Voltage Sense 1 input, which is connected to<br>pin 43 of the A socket. It determines the<br>operating voltage of the card along with<br>*VS2. If external voltage sense logic is<br>implemented and bit 2 of the Extended Mode<br>Register is set, this pin becomes *VSENBL<br>output for external buffer enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# Chapter 1 Introduction

| Symbol                  | Туре | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B_*VS1<br>(E2CS/*HDACK) | Ι    | 133     | <ul> <li>Voltage Sense 1 input, which is connected to pin 43 of the B socket. It determines the operating voltage of the card along with *VS2. If the card is a DMA device, and the DMA function is activated this pin becomes *HDACK which is passed through to *REG (redefined as *DACK) in one of three cases: (1) 5 volt only system.</li> <li>(2) The chip is in the basic configuration (*SPKROUT strapped high) and external voltage sense is used.</li> <li>(3) The chip is in the extended configuration (*SPKROUT strapped low) and this pin is strapped high.</li> </ul> |

|                         |      |         | If this pin is strapped low in the extended<br>configuration this pin becomes the chip<br>select for the external serial EEPROM to<br>support the Plug and Play ISA.                                                                                                                                                                                                                                                                                                                                                                                                                |

| *WAIT                   | Ι    | 47, 118 | This signal is driven by the PC Card to delay completion of the memory or I/O cycle in progress.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| *WE/*PRGM               | 0    | 30, 100 | The host uses *WE for gating memory write data, and for memory PC Cards that employ programmable memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Symbol          | Туре | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WP<br>(*IOIS16) | Ι    | 61, 132 | Reflects the status of the Write Protect switch<br>on some memory PC Cards. If the memory<br>PC Card has no write protect switch, the card<br>will connect this line to ground (the card can<br>always be written) or to Vcc (permanently<br>write protected).<br>When the I/O interface is selected, this pin is<br>used for the "I/O is 16-bit Port" function:<br>asserted by the PC Card when the address on<br>the bus corresponds to an address to which<br>the PC Card responds, and the I/O Port<br>which is addressed is capable of 16-bit<br>access. If this signal is not asserted during a<br>16-bit I/O access, the system will generate 8-<br>bit references to the even and odd byte of the<br>16-bit port being accessed. If the 8-bit<br>window size is selected, *IOIS16 is ignored.<br>If the PC Card is the DMA device, this pin<br>can be redefined as *DREQ input from the<br>card. |

| *ZWS            | 0    | 147     | Zero Wait State. An active low output<br>indicates that the PC Card wishes to<br>terminate the present bus cycle without<br>inserting additional wait states. This cycle<br>will not be driven during a 16-bit I/O access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

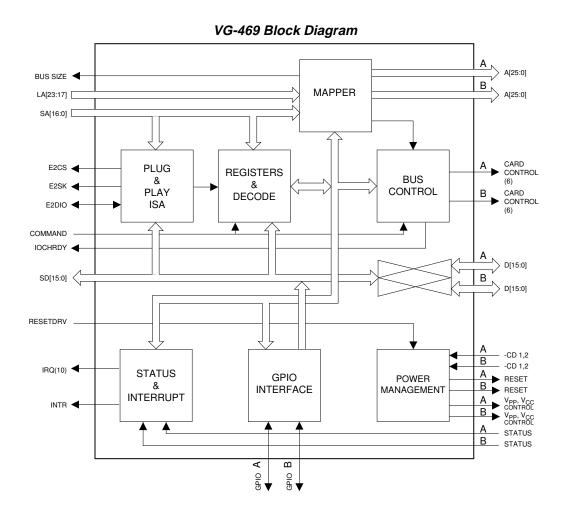

This chapter provides a description of the functional blocks that comprise the VG-469 PC Card Socket Controller. Major functional blocks of the VG-469 include the ISA bus interface, Plug and Play ISA, PC Card socket interface, memory and I/O window mapping, power management support, interrupt handling, configuration, status and control registers and GPIO.

# **ISA INTERFACE**

The VG-469 has built in a standard ISA interface, including 10 IRQs. If DMA capability is needed in the system design, the chip can be configured to provide one set of DMA handshake signals plus Terminal Count. The VG-469 also provides special signals such as \*SPKROUT, \*INTR, \*RIO, and \*LED, the latter two can be brought out through several options.

The ISA interface is selectable to work with either 5V or 3.3V ISA bus. This will be discussed further in section titled 'Mixed Voltage Operation'.

# PCMCIA/JEIDA PC CARD SOCKET INTERFACE

The 68-pin PCMCIA/JEIDA PC Card socket interface consists of 60 signals and 8 power connections. A single VG-469 supports two PC Card sockets directly. Up to four PC Card sockets may be supported by cascading VG-469's. If an external decoder is used, any number of sockets can be supported. Each VG-469 is uniquely selected using pull-up/pull-down resistors

### Control/Status Signal Multiplexers

The VG-469 supports two PC Card types (either memory or I/O) interchangeably. A number of the PC Card signals have different uses based on the PC Card type. The VG-469 incorporates multiplexers to redirect the appropriate signals that are defined differently for memory and I/O PC Cards. These signals are configured correctly based upon the setting of the PC Card type bit in the Interrupt and General Control Register.

### PC Card Status

The status of the PC Card including detection of card insertion or removal, memory write protect status, battery voltage warnings, PC Card power status, and Ready/Busy is accessible through the interface status register. A change in status can cause a card status change interrupt (such as when a PC Card is inserted or removed). The various sources of the interrupt may be enabled separately.

### Mixed Voltage Operation

The VG-469 has four power planes: ISA bus interface, socket A interface, socket B interface, and the internal core, each can be independently connected to 3.3V or 5.0V. The voltage levels for the ISA interface and internal core are fixed at the board level, while those for the socket interface are set after a PC Card is inserted. Two card voltage sense pins: \*VS1 and \*VS2, determine the voltage to be applied according to the following table:

|      | 5.0 Volt Only | 3.3V Capable | X.XV Only | X.X/3.3 Volt Capable |

|------|---------------|--------------|-----------|----------------------|

| *VS1 | Н             | L            | Н         | L                    |

| *VS2 | Н             | Н            | L         | L                    |

X.X volt is a future Vcc level yet to be defined.

In a mixed voltage implementation, the socket is not powered without a card in the socket. After a card is inserted, the system reads the state of the two voltage sense pins and possibly CIS to determine the voltage to be applied to the card. Then it writes to the Power and RESETDRV Control Register, bit 4, which enables the outputs to the voltage switch. To provide the flexibility of interfacing different polarity voltage switches, the voltage enable pins must be resistorstrapped to the level that turns off the switch. The voltage switch supplies power to the socket as well as the VG-469 socket interface.

Since X.X volt is undefined and is not supported by the current generation of voltage switch devices, VG-469 uses the X.X volt combination of VCCEN[1:0] pins to turn off the socket voltage.

The ISA bus voltage level is indicated by a resistor strapping on B\_GPIO. The value of this pin is latched at the falling edge of RESETDRV, and is readable at bit D7 of Card Voltage Select Register.

| B_GPIO Resistor | ISA Bus Voltage |

|-----------------|-----------------|

| Pull-up         | 3.3 volt        |

| Pulldown        | 5 volt          |

Strapping Table for ISA Bus Voltage Indication

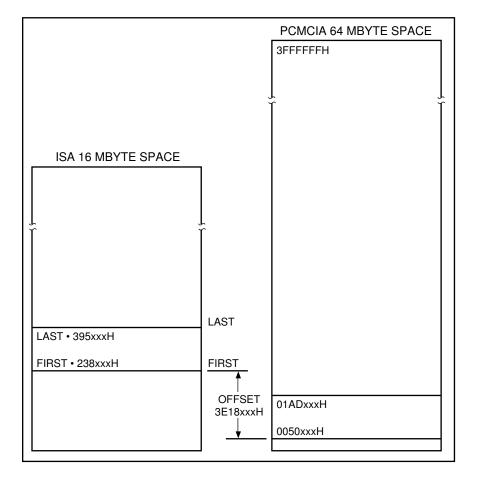

# **MEMORY AND I/O MAPPING**

Multiple PC Cards in a system can conflict if they try to utilize the same system memory and I/O range. The VG-469 allows the operating system to map PC Card memory into up to five separate memory ranges, and PC Card I/O into two separate I/O ranges, thus avoiding system configuration conflicts.

The VG-469 provides memory paging and memory address mapping for both PC Card attribute and common memory and I/O address mapping. The VG-469 includes registers which provide access to the card information structure and card configuration registers within PC Card's attribute memory described by the PCMCIA/JEIDA PC Card Standard.

### PC Card Memory Addressing

The VG-469 provides logic to map portions of the 64MB common memory and/or 64MB attribute memory spaces found on PC Cards into the smaller 16MB system (ISA) address space. These mapping functions allow expansion of the system address space up to the full 64MB PC Card capability.

The VG-469 supports 5 independently enabled and controlled system memory address mapping windows. Each system memory window may map into either the common or attribute memory space of the PC Card and may independently control memory data bus width, system bus wait states, software write protect, and card enable.

Mapping of each system memory window starts and stops on any 4K byte boundary of ISA system memory above 64K. The VG-469 does not allow mapping of a system memory window between 0 and 64K in the system address space. Only I/O address windows are allowed to be mapped into that range. This limitation allows the VG-469 to resolve conflicts when accessing I/O PC Cards that contain memory.

#### **Opening a Window**

To open a window, software sets the system memory start address (Start), system memory stop address (Stop), and PC Card memory offset appropriately. If Start = Stop, the minimum size of

4K bytes is realized. The offset address is set by the software to be equal to the 2's complement of the difference between Start and the start address of the PC Card, and is added to the system address to generate the address for the PC Card.

PC Card memory is accessed only when all of the following conditions are satisfied:

- 1. The system memory address mapping window is enabled.

- 2. The system memory address is greater than or equal to the system memory address mapping start register A[23:12].

- 3. The system memory address is less than or equal to the system memory address mapping stop register A[23:12].

All the system memory address mapping windows can be configured by software to be independently used, or can be used together for special memory mapping requirements, like LIM/EMS or XIP.

Multiple ROM executable images on a single PC Card may be organized by the system memory address mapping windows. These images must be aligned to start on a 4 K byte boundary of the memory PC Card. Software can access these ROM executable images by setting the size of a system memory address mapping window to the size of the executable image (minimum 4 K block), and setting the PC Card memory offset from the system memory start address (Start) to generate the address of the first byte of the executable image on the PC Card.

The PC Card memory offset can be either a positive or negative value. Furthermore, the VG-469 does not check for a window whose size and offset allow it to wrap from the last PC Card address to the first PC Card address. Software must check to prevent address wrapping.

#### Memory Address Mapping

Common/Attribute memory on the PC Card can be accessed through any of the system memory address mapping windows. This is accomplished by selectively setting the "REG Active Bit" in the Card Memory Offset Address Register. When this bit is set to zero, common memory can be accessed; when this bit is set to one, attribute memory can be accessed. The system memory window to common/attribute memory can be mapped from any ISA address above 64K to any PC Card address.

Multiple system memory address mapping windows to separate common/attribute memory address spaces can be opened simultaneously. Each of these windows can be configured to use a different number of wait states, software write protect, and data width.

### Memory Paging

System memory paging is supported in the VG-469 through the use of multiple system memory address mapping windows. When using LIM or XIP, software should assign a window to each page required to support the LIM/XIP function. The software has the responsibility to set up the system memory address mapping windows to be in one contiguous system address space with

each window controlling a single page in the PC Card memory. When changing the page pointer only the PC Card memory offset address value needs to be altered to change the mapping.

#### PC Card I/O Addressing

The ISA system bus is limited to 768 bytes of common I/O address space between I/O addresses 100H and 3FFH. The VG-469 supports system I/O address decode from 0 to 64K. A PC Card can request specific common I/O address locations or it can request a block of I/O space by the size required. When I/O space is requested by size, the system is free to locate the PC Card anywhere in the 64K system I/O address space. The PC Card decodes the \*CE[2:1], \*IORD, and \*IOWR signals to respond to an I/O access.

The VG-469 provides two independently enabled and controlled I/O address windows which are defined by 16-bit addresses to achieve a 1 byte resolution. Each window has independent control of I/O data bus width, zero wait state system bus access, and generation of \*IOCS16.

A PC Card I/O address is accessed only when all of the following conditions are satisfied:

- 1. The I/O address window is enabled.

- 2. The system address is greater than or equal to the I/O address start register A[15:0].

- 3. The system address is less than or equal to the I/O address stop register A[15:0].

- 4. The access is not a DMA transfer. AEN = 0 to access the I/O PC Card.

It is the responsibility of the system software to account for each I/O address range assigned to a particular PC Card. The reservation of a particular I/O address range for each PC Card can reduce card power consumption since only one PC Card is enabled during each I/O access.

The VG-469 can directly map the system I/O address space to the PC Card I/O ports with single byte granularity. Each PC Card is guaranteed a reserved system I/O address space, and an I/O cycle will be generated to the PC Card only within the assigned space.

# PC CARD DMA OPERATION

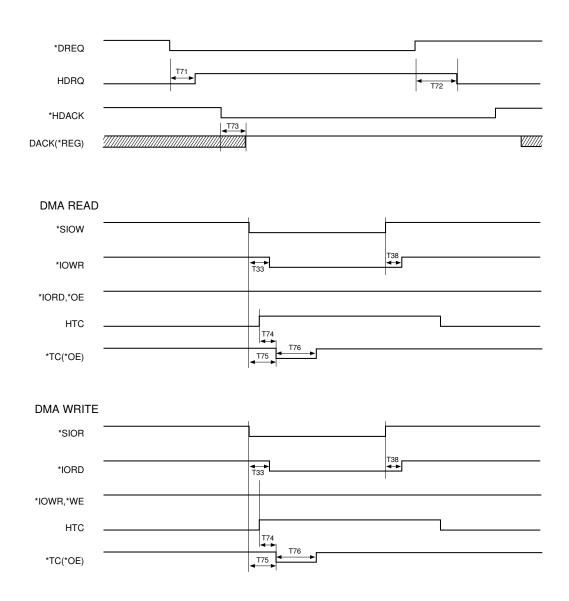

The VG-469 supports using a the socket as an interface to a DMA device. PC Cards that take advantage of this new DMA extension in PC Card Standard are sound card, network card, and floppy drive card.

DMA mode can be used in a 5V-only socket, or a mixed voltage socket where voltage sensing is done using an external buffer. Only one socket at a time should be enabled for DMA transfer because the ISA bus DMA handshake signals are shared between both socket interfaces.

DMA transfers to and from the DMA-capable PC Card may be 8-bit or 16-bit, as specified by bit D4 of the DMA register (index 3Eh/7Eh). External steering logic is needed to direct the DMA signals to the desired channel.

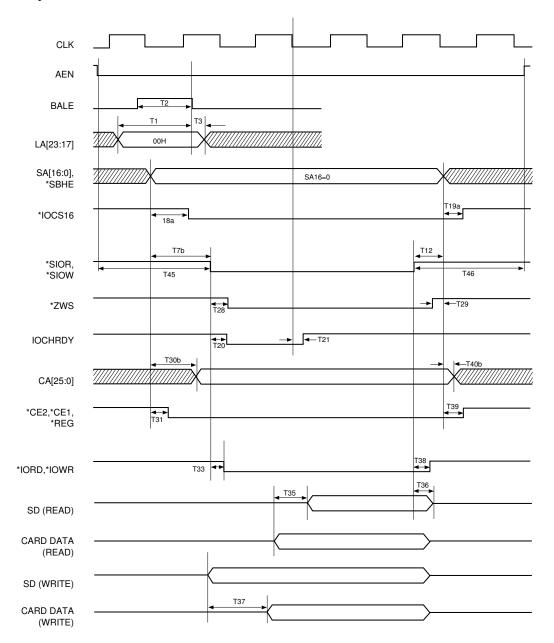

To use the DMA mode, the socket interface must be set to I/O card type (bit D5 of the Interrupt and General Control Register). Setting D0 of the DMA and Programmable Chip Select Configuration Register enables the DMA mode, and other bits in this register define the card \*DREQ steering, DMA data size, and terminal count steering. Once DMA mode is enabled and DMA operation is taking place, several PCMCIA signals are re-defined as DMA interface signals, according to the following table:

| Standard I/O Card Signals | DMA Card Signals | Condition                  |

|---------------------------|------------------|----------------------------|

| *IOIS16                   | *DREQ            | DMA register $D[6:5] = 00$ |

| *SPKR                     | *DREQ            | DMA register $D[6:5] = 01$ |

| *INPACK                   | *DREQ            | DMA register $D[6:5] = 10$ |

| *REG                      | DACK             | During actual DMA cycles   |

| *OE                       | *TC              | During DMA write cycles if |

|                           |                  | DMA register $D[2:1] = 00$ |

| *WE                       | *TC              | During DMA read cycles if  |

|                           |                  | DMA register $D[2:1] = 00$ |

The VG-469 multiplexes the ISA bus DMA handshake signals onto the pins also used for other purposes. The table below specifies these signals:

| VG-469 Signals | ISA Bus DMA Signals | Condition                                                                                       |

|----------------|---------------------|-------------------------------------------------------------------------------------------------|

| B_GPIO         | HDRQ                | DMA register $D0 = 1$                                                                           |

| A_GPIO         | HTC                 | DMA register $D0 = 1$                                                                           |

| B_*VS1         | *HDACK              | DMA register $D0 = 1$ and Plug-and-Play is not enabled                                          |

| IRQ7           | *HDACK              | DMA register D0 = 1, Plug-and-Play is<br>enabled, and D7 of Extended Mode<br>Register A is set. |

When a PC Card and socket are configured for DMA operations, the DACK (\*REG) signal is used to distinguish between a DMA cycle and a normal I/O cycle. The \*REG is negated (high) during the entire DMA bus cycle, as opposed to being active (low) for a normal I/O cycle. It should be noted that DMA acknowledgment is indicated when DACK (\*REG) is high and either \*IORD or \*IOWR is active. DACK (\*REG) may be high before DMA request is issued, therefore a high DACK without an active I/O command does not mean DMA is acknowledged by the system.

Address lines to the PC Card are ignored during DMA operations.

A PC Card requests a DMA transfer by asserting \*DREQ, VG-469 then asserts HDRQ to the core logic. Once receiving an active \*HDACK from the core logic, VG-469 drives DACK high and sets up the internal logic for DMA transfer. An I/O command is then asserted (\*IOWR for DMA read and \*IORD for DMA write). When the DMA transfer is complete and the core logic

asserts terminal count (HTC), VG-469 by default steers \*TC to \*WE for DMA read, or \*OE for DMA write. It is recommended to use the default conditions (bits D[2:1] of the DMA register) in order to be compliant with the PC Card Standard, although other options for terminal count steering are provided. \*TC is asserted for one ISA Bus clock (TCKLK). It will not be asserted beyond the trailing edge of an ISA bus I/O command to avoid being misinterpreted by the PC Card as a common memory access.

# **INTERRUPT HANDLING**

Since multiple PC Cards in a system can conflict if they try to utilize the same interrupt, the VG-469 can be programmed to eliminate this conflict by routing each PC Card interrupt request to a different system interrupt. Based upon four bits in the Interrupt and General Control Register, the interrupt request signal (\*IREQ) from an I/O PC Card will be directed to one of ten interrupt request lines on the system bus.

The VG-469 provides a card status change interrupt which can notify the system of a change in the battery voltage levels, card insertion/removal detection, Ready/\*Busy condition, and status change. It can be directed to one of the ten interrupt request lines on the system bus based upon four bits in the Card Status Change Interrupt Configuration Register. When used with a CPU that supports SMI, it should be configured as the \*INTR signal and connected to the \*EXTSMI input of the CPU.

The ten interrupt request lines can all be configured as edge-triggered to support the standard interrupt from I/O cards and card status change interrupts, or as level mode interrupts to support I/O cards with pulse-mode interrupt requests.

# **POWER MANAGEMENT**

The VG-469 implements power management for each PC Card socket. Programming the Power and RESETDRV control register controls socket power management.

The VG-469 will automatically enter into lower power consumption state when memory windows and I/O windows are disabled, and when sockets become empty. Further, the lowest power consumption level can be achieved by putting the VG-469 into power down mode. This mode is entered by disabling all the I/O, memory windows, output buffers, configuring one of the GPIO as power down control input enabling the power down mode, and driving the GPIO pin to high.

During the power down mode, VG-469's Vcc will still be powered up, and the internal register contents will be maintained. The interrupt (IRQs) can still be generated to the host system from either card status change, or PC Card interrupt requests. \*RIO can still be armed to route either \*RI or Card detect change. \*INTR can still be armed for card status change interrupts but will not be generated until power down mode is exited.

# CONFIGURATION, STATUS AND CONTROL REGISTERS

The VG-469 provides complete control of a PC Card through its registers. Among the functions provided are bit programmable memory write protect for the attribute and common memory, Vcc, and Vpp power control, and interrupt steering. Control of the signal multiplexers for directing the appropriate memory or I/O signals to the socket is also provided, as well as control bits to set memory and I/O data path size. Other registers set the boundaries of the memory and I/O mapping windows. Finally, a number of registers reflect the status of the PC Card.

### Register Addressing

All VG-469 control registers are byte wide and accessed using an indirect indexing scheme. Two I/O addresses are required to access the control registers. The first address is the index register. The second address, which equals to index register address plus 1, points to the data register. Each socket contains a block of 64 indirectly addressed registers. In order to support up to two VG-469's in a system, two sets of selectbale I/O addresses are available. These values are selected by pull-up/pulldown strapping resistor on the \*INTR pin, according to the table. While RESETDRV is true this pin becomes an input, the falling edge of RESETDRV latches the pulled up or down state of the pin, and thereafter the pin resumes its normal function.

The index register and the data register are read/write registers. The VG-469 will not respond to a data register read or write operation or to an index register read operation unless the index register has first been written to with a valid index.

| *INTR Resistor | I/O Address |

|----------------|-------------|

| Pull-up        | 3E0h/3E1h   |

| Pulldown       | 3E2h/3E3h   |

#### Strapping Option Table for Selecting the I/O Address

### External Decoding

The VG-469 can be configured to respond to an external chip select input, allowing an unlimited number of VG-469's to exist in a system. One VG-469 using internal decoding can coexist with an unlimited number using external decoding. The devices which use external decoding may have the same or different strapping resistor configurations, which must be different from the configurations of the device which uses internal decoding.

With external decoding, index register is accessed if ISA address A0 = 0, and data register is accessed if A0 = 1.

# **OPERATING MODES**

VG-469 is very flexible in that it can be configured to provide different functions to meet system's requirement. During power on reset, a number of resistor strapping options determine the operating modes. The two primary configuration strappings are to decide: (1) if the socket is operated at 5 volt only, or it is designed to be switchable between 5 volt and 3.3 volt. (2) if the VG-469 is to be used in a small computer environment, in which it is connected directly to ISA bus and PC Card sockets (Basic Mode); or expandability is the design goal such that Plug-and-Play or cable driving is required (Extended Mode).

For a 5 volt only socket, one VCCEN pin (VCCEN1) is sufficient to select between power on and off. The extra pin from each socket is then strapped in opposite sense: A\_VCCEN0 to VCC, and B\_VCCEN0 to ground, for example. For a mixed voltage socket, both VCCEN1 and VCCEN0 are required to select among 5 volt, 3.3 volt and power off. Since all VCCENs are strapped to the level that would turn off the switch, A\_VCCEN0 and B\_VCCEN0 are strapped to the same level.

| A_VCCEN0 and B_VCCEN0 Resistors | Socket Voltage Support |

|---------------------------------|------------------------|

| Strapped to opposite levels     | 5 volt only            |

| Strapped to the same level      | mixed voltage          |

A mixed voltage socket can have two ways of accessing the voltage sense pins. The first method is to have all the voltage sense pins connected to the VG-469, and are readable through an internal Voltage Sense Register (index 1Fh/5Fh). The other method is to use an external buffer chip as the voltage sense register. When the same indexed register is accessed, A\_\*VS1 becomes Voltage Sense Read Enable which is connected to Output Enable of the external buffer.

A second resistor strapping, which is on the \*SPKROUT pin, is used to differentiate the Basic Mode and Extended Mode:

| *SPKROUT Resistor | Operating Mode |

|-------------------|----------------|

| Pull-up           | Basic Mode     |

| Pulldown          | Extended Mode  |

### Basic Mode

In Basic Mode, VG-469 is connected directly to ISA bus and PC Card sockets. DMA is available for a 5 volt only socket and a mixed voltage socket with external voltage sense, but not available if internal voltage sense is implemented.

### Extended Mode

The VG-469 can be configured to enable the Extended Mode to support buffered cable driving applications. In this configuration two options are available: VG-469 can be located at the drive

bay and is connected through cable to the buffers that drive the ISA bus, or it can be near the ISA bus and drives the socket\_B through cable. When enabled, the definitions of several pins are changed to provide buffer direction controls.

| Pin Definition in                               | Pin Definition for ISA Buffer | Pin Definition for Socket _B   |  |  |

|-------------------------------------------------|-------------------------------|--------------------------------|--|--|

| Basic Mode                                      | with B_*VS2 pulled low        | Buffer with B_*VS2 pulled high |  |  |

| A_*VS2                                          | HBUFDIR <sup>1</sup>          | *BSIGEN                        |  |  |

| B_*VS2                                          | LBUFDIR <sup>1</sup>          | DIR <sup>2</sup>               |  |  |

| B_GPIO                                          | D7BUFDIR <sup>1</sup>         | B_GPIO                         |  |  |

| Notes: 1. Normally low, from ISA bus to VG-469. |                               |                                |  |  |

| 2. Normally high, from VG-469 to socket_B.      |                               |                                |  |  |

In the case of ISA buffer support, if a floppy or hard disk is installed in the socket, the VG-469 can be programmed to avoid contention with a motherboard drive. In this situation VG-469 either tri-states SD7 (with hard disk in the socket) or SD[6:0] (with floppy disk in the socket) when reading the drive address register. If this feature is used in a cable driving configuration, LBUFDIR will control the SD[6:0] and D7BUFDIR will control the SD7 buffer.

In the extended mode, VG-469 can also support both Plug and Play ISA and DMA.Plug and Play ISA requires an external serial EEPROM for configuration storage. The interface signals to the EEPROM are provided by strapping B\_\*VS1 low. The alternate definitions for these pins are shown in the next table:

| Pin Definition in Basic Mode or in Extended<br>Mode with B_*VS1 pulled high | Pin Definition for Plug and Play ISA<br>Support with B_*VS1 pulled low |  |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------|--|

| B_*VS1 (*HDACK)                                                             | E2CS (serial EEPROM chip select)                                       |  |

| *INTR                                                                       | E2SK (serial EEPROM clock input)                                       |  |

| *SPKROUT                                                                    | E2DIO (Serial EEPROM data port)                                        |  |

When Plug and Play is enabled, DMA can still be used if IRQ7 is configured to be \*HDACK. This can be accomplished by setting bit D7 of the Extended Mode Register-A.

# PLUG AND PLAY

VG-469 supports the Plug and Play ISA Specification Version 1.0a to provide automatic configuration capability. This plug and play implementation lets the software relocate the VG-469 registers from the default at 3E0h/3E1h or 3E2h/3E3h. Plug and Play is only available in extended mode.

The major steps of the auto-configuration process are as follows:

- 1. Put all Plug-and-Play devices in configuration mode.

- 2. Isolate one Plug-and-Play device at a time.

- 3. Assign a handle and read the card's resource data structure.

- 4. After the resource requirements and capabilities are determined for all cards, use the handle to assign conflict free resources to each device.

#### **Auto-configuration Ports**

The Plug-and-Play software identifies and configures devices with a set of commands that are executed using three 8-bit I/O ports. These ports are listed below:

| Port Name                                              | Location                            | Туре       |  |

|--------------------------------------------------------|-------------------------------------|------------|--|

| Address                                                | 0279H                               | Write-only |  |

| Write_Data                                             | 0A79H                               | Write-only |  |

| Read_Data                                              | Relocatable in range 0200H to 03FFH | Read-only  |  |

| Note: All three ports use a 12-bit ISA address decode. |                                     |            |  |

The Plug-and-Play Registers are accessed by first writing the address of the desired register to the Address port, followed by a read of data from the Read\_Data port or a write of data to the Write\_Data port. A write to the Address port may be followed by any number of Write\_Data or Read\_Data accesses to the same register location without the need to write to the Address port before each access.