1996/1997 Data Book

# Flash Memory • E<sup>2</sup>PROM • Mixed Signal

# **1996/1997 Data Book**

Printed in U.S.A. ©1996 by Catalyst Semiconductor, Inc. "All Rights Reserved"

#### LIMITED WARRANTY

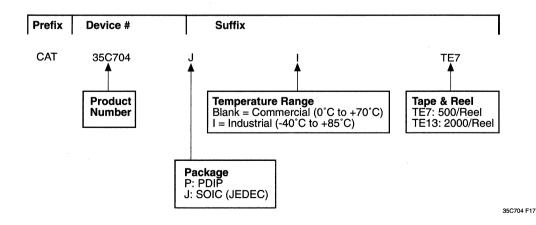

Devices sold by Catalyst Semiconductor, Inc. are covered by the limited warranty and other limited provisions appearing in its Terms of Sale. Catalyst Semiconductor makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent or other intellectual property infringement. Catalyst Semiconductor makes no warranty of merchantability or fitness for any purpose. Catalyst Semiconductor reserves the right to discontinue production and change specifications and prices at any time and without notice.

Catalyst Semiconductor, Inc. assumes no responsibility for the use of any circuitry other than circuitry it embodies in a Catalyst Semiconductor product.

#### LIFE RELATED POLICY DISCLAIMER

Catalyst Semiconductor's products are not authorized for use as critical components in life support devices or systems.

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support

or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the

labelling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

In situations where semiconductor component failure may endanger life, system designers using this product should design the system with appropriate error detection and correction, redundancy and back-up features to prevent such an occurence.

Copyright © 1996 Catalyst Semiconductor, Inc. Catalyst Semiconductor is licensed by Philips Corporation to carry the I<sup>2</sup>C Bus Protocol. Intelligent Programming, Quick-Erase Programming and Quick-Pulse Programming are trademarks of Intel Corporation. Product names used in this publication are for identification purposes only and may be trademarks of their respective companies. Catalyst Semiconductor, Inc. reserves the right to make changes in the device or specifications described herein without notice. Information in this document is subject to change without notice.

# **Table of Contents**

| CAT93C46/56/66/86       1K/2K/4K/16K-Bit       3-1         CAT93C46A/56A/66A/86A       1K/2K/4K/16K-Bit No ORG Pin       3-9         CAT93C57       2K-Bit       3-17         Section 4       SPI Bus Serial E <sup>2</sup> PROMs       3-17         CAT64LC10/20/40       1K/2K/4K-Bit       4-1         Section 5       Secure Access Serial E <sup>2</sup> PROMs       4K-Bit 5V Operating Voltage       5-1         CAT35C704       4K-Bit 3V Operating Voltage       5-15         CAT33C804A       4K-Bit 5V Operating Voltage       5-29         CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       6-1       6-1         CAT22C10       256-Bit       6-1       6-11         Section 7       Flash Memories       6-11       6-11         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1 M-Bit 8-Bit Data Bus       7-15         CAT28F020       2 M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                                 | Section 1    | Product Information                     |                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------|-----------------------------------------|

| Section 2         I*C Bus Serial E*PROMs           CAT24C01/02/04/08/16         1K/2K/4K/8K/16K-Bit         2-1           CAT24WC01/02/04/08/16         1K/2K/4K/8K/16K-Bit Write Protection Pin         2-9           CAT24C32/64         32K/64K-Bit         2-17           CAT24WC32/64         32K/64K-Bit Write Protection Pin         2-25           Section 3         Microwire Bus Serial E*PROMs         3-1           CAT93C46/56/66/86         1K/2K/4K/16K-Bit No ORG Pin         3-9           CAT93C46/56/66/86         1K/2K/4K/16K-Bit No ORG Pin         3-9           CAT93C57         2K-Bit         3-17           Section 5         Secure Access Serial E*PROMs         4-1           Section 5         Secure Access Serial E*PROMs         4-1           Section 5         Secure Access Serial E*PROMs         5-1           CAT33C704         4K-Bit 5V Operating Voltage         5-1           CAT33C704         4K-Bit 3V Operating Voltage         5-29           CAT33C804A         4K-Bit 3V Operating Voltage         5-43           Section 6         NVRAMs         6-1         6-1           CAT22C10         256-Bit         6-1         6-1           CAT22C10         256-Bit         6-1         6-1           CAT22F5                                    | Alpha-Numer  | ric Index                               |                                         |

| CAT24C01/02/04/08/16       1K/2K/4K/8K/16K-Bit       2-1         CAT24WC01/02/04/08/16       1K/2K/4K/8K/16K-Bit Write Protection Pin       2-9         CAT24C32/64       32K/64K-Bit Write Protection Pin       2-17         CAT24WC32/64       32K/64K-Bit Write Protection Pin       2-25         Section 3       Microwire Bus Serial E*PROMs       3-17         CAT93C46/56/66/86       1K/2K/4K/16K-Bit No ORG Pin       3-9         CAT93C46A/56A/66A/86A       1K/2K/4K/16K-Bit       3-17         Section 4       SPI Bus Serial E*PROMs       3-17         Section 5       Secure Access Serial E*PROMs       4-1         Section 5       Secure Access Serial E*PROMs       4-1         Section 5       Secure Access Serial E*PROMs       5-1         CAT35C704       4K-Bit 5V Operating Voltage       5-15         CAT33C704       4K-Bit 5V Operating Voltage       5-29         CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       6-11         CAT24C10       256-Bit       6-11         Section 7       Flash Memories       7-1         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1       M-Bit 8-Bit Data Bus       7-15 <t< td=""><td>Product Feat</td><td>ures</td><td></td></t<>                | Product Feat | ures                                    |                                         |

| CAT24C01/02/04/08/16       1K/2K/4K/8K/16K-Bit       2-1         CAT24WC01/02/04/08/16       1K/2K/4K/8K/16K-Bit Write Protection Pin       2-9         CAT24C32/64       32K/64K-Bit Write Protection Pin       2-17         CAT24WC32/64       32K/64K-Bit Write Protection Pin       2-25         Section 3       Microwire Bus Serial E*PROMs       3-17         CAT93C46/56/66/86       1K/2K/4K/16K-Bit No ORG Pin       3-9         CAT93C46A/56A/66A/86A       1K/2K/4K/16K-Bit       3-17         Section 4       SPI Bus Serial E*PROMs       3-17         Section 5       Secure Access Serial E*PROMs       4-1         Section 5       Secure Access Serial E*PROMs       4-1         Section 5       Secure Access Serial E*PROMs       5-1         CAT35C704       4K-Bit 5V Operating Voltage       5-15         CAT33C704       4K-Bit 5V Operating Voltage       5-29         CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       6-11         CAT24C10       256-Bit       6-11         Section 7       Flash Memories       7-1         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1       M-Bit 8-Bit Data Bus       7-15 <t< td=""><td>Ocetice 0</td><td>120 Due Cariel S2DDOMe</td><td></td></t<> | Ocetice 0    | 120 Due Cariel S2DDOMe                  |                                         |

| CAT24WC01/02/04/08/16.       1K/2K/4K/8K/16K-Bit Write Protection Pin       2-9         CAT24C32/64       32K/64K-Bit       2-17         CAT24WC32/64       32K/64K-Bit Write Protection Pin       2-25         Section 3       Microwire Bus Serial E*PROMs       2-25         Section 3       Microwire Bus Serial E*PROMs       3-1         CAT93C46/56/66/86       1K/2K/4K/16K-Bit       3-1         CAT93C46/A/56A/66A/86A       1K/2K/4K/16K-Bit No ORG Pin       3-9         CAT93C57       2K-Bit       3-17         Section 4       SPI Bus Serial E*PROMs       3-17         Section 5       Secure Access Serial E*PROMs       4-1         CAT35C704       4K-Bit 5V Operating Voltage       5-1         CAT33C704       4K-Bit 3V Operating Voltage       5-15         CAT33C804A       4K-Bit 3V Operating Voltage       5-29         CAT23C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       6-1         CAT22C10       256-Bit       6-1         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1 M-Bit 8-Bit Data Bus       7-15         CAT28F020       2 M-Bit 8-Bit Data Bus       7-29                                                                                                                      |              |                                         | 1K/2K/AK/9K/16K Bit 2.1                 |

| CAT24C32/64       32K/64K-Bit       2-17         CAT24WC32/64       32K/64K-Bit Write Protection Pin       2-25         Section 3       Microwire Bus Serial E²PROMs       3-1         CAT93C46/56/66/86       1K/2K/4K/16K-Bit       3-1         CAT93C46/56/66/86       1K/2K/4K/16K-Bit No ORG Pin       3-9         CAT93C57       2K-Bit       3-17         Section 4       SPI Bus Serial E²PROMs       4-1         Section 5       Secure Access Serial E²PROMs       4-1         Section 5       Secure Access Serial E²PROMs       5-1         CAT33C704       4K-Bit 5V Operating Voltage       5-1         CAT33C704       4K-Bit 3V Operating Voltage       5-29         CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       256-Bit       6-1         CAT22C10       256-Bit       6-1       6-1         CAT24C44       256-Bit       6-1       6-1         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1       M-Bit 8-Bit Data Bus       7-15         CAT28F020       2       M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                              |              |                                         |                                         |

| CAT24WC32/64       32K/64K-Bit Write Protection Pin       2-25         Section 3       Microwire Bus Serial E*PROMs       3-1         CAT93C46/56/66/86       1K/2K/4K/16K-Bit       3-1         CAT93C46A/56A/66A/86A       1K/2K/4K/16K-Bit No ORG Pin       3-9         CAT93C57       2K-Bit       3-17         Section 4       SPI Bus Serial E*PROMs       3-17         Section 5       Secure Access Serial E*PROMs       4-1         Section 5       Secure Access Serial E*PROMs       4-1         CAT33C704       4K-Bit 5V Operating Voltage       5-1         CAT33C704       4K-Bit 3V Operating Voltage       5-15         CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       6-1       6-1         CAT22C10       256-Bit       6-1       6-1         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1 <m-bit 8-bit="" bus<="" data="" td="">       7-15         CAT28F020       2<m-bit 8-bit="" bus<="" data="" td="">       7-29</m-bit></m-bit>                                                                                                                                                                                                                                                          |              |                                         |                                         |

| Section 3         Microwire Bus Serial E <sup>2</sup> PROMs           CAT93C46/56/66/86         1K/2K/4K/16K-Bit           CAT93C46A/56A/66A/86A         1K/2K/4K/16K-Bit No ORG Pin           CAT93C57         2K-Bit           Section 4         SPI Bus Serial E <sup>2</sup> PROMs           CAT64LC10/20/40         1K/2K/4K-Bit           Section 5         Secure Access Serial E <sup>2</sup> PROMs           CAT35C704         4K-Bit 5V Operating Voltage           CAT33C704         4K-Bit 3V Operating Voltage           CAT33C804A         4K-Bit 3V Operating Voltage           CAT24C10         256-Bit           CAT22C10         256-Bit           CAT24C44         256-Bit           CAT24C44         6-1           Section 7         Flash Memories           CAT28F512         512K-Bit 8-Bit Data Bus           CAT28F010         1           M-Bit 8-Bit Data Bus         7-15           CAT28F020         2                                                                                                                                                                                                                                                                                                                                                              |              |                                         |                                         |

| CAT93C46/56/66/86       1K/2K/4K/16K-Bit       3-1         CAT93C46A/56A/66A/86A       1K/2K/4K/16K-Bit No ORG Pin       3-9         CAT93C57       2K-Bit       3-17         Section 4       SPI Bus Serial E <sup>2</sup> PROMs       3-17         CAT64LC10/20/40       1K/2K/4K-Bit       4-1         Section 5       Secure Access Serial E <sup>2</sup> PROMs       4K-Bit 5V Operating Voltage       5-1         CAT35C704       4K-Bit 3V Operating Voltage       5-15       5         CAT33C804A       4K-Bit 5V Operating Voltage       5-29         CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       6-1       6-1         CAT22C10       256-Bit       6-1       6-11         Section 7       Flash Memories       6-11       6-11         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1 M-Bit 8-Bit Data Bus       7-15         CAT28F020       2 M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                         | CA124WC32    | /64                                     | . 32K/64K-Bit Write Protection Pin 2-25 |

| CAT93C46A/56A/66A/86A       1K/2K/4K/16K-Bit No ORG Pin       3-9         CAT93C57       2K-Bit       3-17         Section 4       SPI Bus Serial E <sup>2</sup> PROMs       4         CAT35C704       1K/2K/4K-Bit       4-1         Section 5       Secure Access Serial E <sup>2</sup> PROMs       5-1         CAT35C704       4K-Bit 5V Operating Voltage       5-1         CAT33C704       4K-Bit 3V Operating Voltage       5-29         CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       256-Bit       6-1         CAT22C10       256-Bit       6-11       6-11         Section 7       Flash Memories       512K-Bit 8-Bit Data Bus       7-1         CAT28F512       512K-Bit 8-Bit Data Bus       7-15         CAT28F020       2 M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Section 3    | Microwire Bus Serial E <sup>2</sup> PRO | Ms                                      |

| CAT93C57       2K-Bit       3-17         Section 4       SPI Bus Serial E²PROMs       4-1         CAT64LC10/20/40       1K/2K/4K-Bit       4-1         Section 5       Secure Access Serial E²PROMs       5-1         CAT35C704       4K-Bit 5V Operating Voltage       5-15         CAT33C704       4K-Bit 3V Operating Voltage       5-29         CAT33C804A       4K-Bit 5V Operating Voltage       5-43         Section 6       NVRAMs       4K-Bit 3V Operating Voltage       5-43         Section 7       Flash Memories       6-1       6-1         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1       M-Bit 8-Bit Data Bus       7-15         CAT28F020       2       M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CAT93C46/5   | 6/66/86                                 | . 1K/2K/4K/16K-Bit                      |

| Section 4         SPI Bus Serial E <sup>2</sup> PROMs           CAT64LC10/20/40         1K/2K/4K-Bit         4-1           Section 5         Secure Access Serial E <sup>2</sup> PROMs         5-1           CAT35C704         4K-Bit 5V Operating Voltage         5-15           CAT33C704         4K-Bit 3V Operating Voltage         5-15           CAT35C804A         4K-Bit 5V Operating Voltage         5-29           CAT33C804A         4K-Bit 3V Operating Voltage         5-43           Section 6         NVRAMs         5-43           CAT22C10         256-Bit         6-1           CAT24C44         256-Bit         6-11           Section 7         Flash Memories         7-1           CAT28F512         512K-Bit 8-Bit Data Bus         7-15           CAT28F010         1 M-Bit 8-Bit Data Bus         7-15           CAT28F020         2 M-Bit 8-Bit Data Bus         7-29                                                                                                                                                                                                                                                                                                                                                                                                  | CAT93C46A/   | /56A/66A/86A                            | . 1K/2K/4K/16K-Bit No ORG Pin 3-9       |

| CAT64LC10/20/40       1K/2K/4K-Bit       4-1         Section 5       Secure Access Serial E <sup>2</sup> PROMs       5-1         CAT35C704       4K-Bit 5V Operating Voltage       5-1         CAT33C704       4K-Bit 3V Operating Voltage       5-15         CAT35C804A       4K-Bit 3V Operating Voltage       5-29         CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       5-43         CAT22C10       256-Bit       6-1         CAT24C44       256-Bit       6-1         Section 7       Flash Memories       7-1         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1       M-Bit 8-Bit Data Bus       7-15         CAT28F020       2       M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CAT93C57     |                                         | . 2K-Bit                                |

| CAT64LC10/20/40       1K/2K/4K-Bit       4-1         Section 5       Secure Access Serial E <sup>2</sup> PROMs       5-1         CAT35C704       4K-Bit 5V Operating Voltage       5-1         CAT33C704       4K-Bit 3V Operating Voltage       5-15         CAT35C804A       4K-Bit 3V Operating Voltage       5-29         CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       5-43         CAT22C10       256-Bit       6-1         CAT24C44       256-Bit       6-1         Section 7       Flash Memories       7-1         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1       M-Bit 8-Bit Data Bus       7-15         CAT28F020       2       M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • • •        |                                         |                                         |

| Section 5       Secure Access Serial E²PROMs         CAT35C704       4K-Bit 5V Operating Voltage       5-1         CAT33C704       4K-Bit 3V Operating Voltage       5-15         CAT35C804A       4K-Bit 5V Operating Voltage       5-29         CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       56-Bit       6-1         CAT24C44       256-Bit       6-11         Section 7       Flash Memories       6-11         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1       M-Bit 8-Bit Data Bus       7-15         CAT28F020       2       M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                         |                                         |

| CAT35C704       4K-Bit 5V Operating Voltage       5-1         CAT33C704       4K-Bit 3V Operating Voltage       5-15         CAT35C804A       4K-Bit 5V Operating Voltage       5-29         CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       5-43         CAT22C10       256-Bit       6-1         CAT24C44       256-Bit       6-11         Section 7       Flash Memories       6-11         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1       M-Bit 8-Bit Data Bus       7-15         CAT28F020       2       M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CAI64LC10/2  | 20/40                                   | . 1K/2K/4K-Bit                          |

| CAT33C704       4K-Bit 3V Operating Voltage       5-15         CAT35C804A       4K-Bit 5V Operating Voltage       5-29         CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       5-43         CAT22C10       256-Bit       6-1         CAT24C44       256-Bit       6-11         Section 7       Flash Memories       6-11         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1       M-Bit 8-Bit Data Bus       7-15         CAT28F020       2       M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Section 5    | Secure Access Serial E <sup>2</sup> PRC | DMs                                     |

| CAT35C804A       4K-Bit 5V Operating Voltage       5-29         CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       6-1         CAT22C10       256-Bit       6-1         CAT24C44       256-Bit       6-11         Section 7       Flash Memories       6-11         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1       M-Bit 8-Bit Data Bus       7-15         CAT28F020       2       M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CAT35C704    |                                         | . 4K-Bit 5V Operating Voltage 5-1       |

| CAT33C804A       4K-Bit 3V Operating Voltage       5-43         Section 6       NVRAMs       6-1         CAT22C10       256-Bit       6-1         CAT24C44       256-Bit       6-11         Section 7       Flash Memories       6-11         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1       M-Bit 8-Bit Data Bus       7-15         CAT28F020       2       M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CAT33C704.   |                                         | . 4K-Bit 3V Operating Voltage 5-15      |

| Section 6         NVRAMs           CAT22C10         256-Bit         6-1           CAT24C44         256-Bit         6-11           Section 7         Flash Memories         6-11           CAT28F512         512K-Bit 8-Bit Data Bus         7-1           CAT28F010         1         M-Bit 8-Bit Data Bus         7-15           CAT28F020         2         M-Bit 8-Bit Data Bus         7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CAT35C8044   | ۹                                       | . 4K-Bit 5V Operating Voltage 5-29      |

| CAT22C10       256-Bit       6-1         CAT24C44       256-Bit       6-11         Section 7       Flash Memories       6-11         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1       M-Bit 8-Bit Data Bus       7-15         CAT28F020       2       M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CAT33C804/   | ۹                                       | . 4K-Bit 3V Operating Voltage 5-43      |

| CAT22C10       256-Bit       6-1         CAT24C44       256-Bit       6-11         Section 7       Flash Memories       6-11         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1       M-Bit 8-Bit Data Bus       7-15         CAT28F020       2       M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                         |                                         |

| CAT24C44       256-Bit       6-11         Section 7       Flash Memories         CAT28F512       512K-Bit 8-Bit Data Bus       7-1         CAT28F010       1 M-Bit 8-Bit Data Bus       7-15         CAT28F020       2 M-Bit 8-Bit Data Bus       7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                         | 256 Bit 6 1                             |

| Section 7         Flash Memories           CAT28F512         512K-Bit 8-Bit Data Bus         7-1           CAT28F010         1 M-Bit 8-Bit Data Bus         7-15           CAT28F020         2 M-Bit 8-Bit Data Bus         7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |                                         |                                         |

| CAT28F512                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CAI 24C44    |                                         | . 256-Bit 6-11                          |

| CAT28F010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Section 7    | Flash Memories                          |                                         |

| CAT28F020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CAT28F512    |                                         | . 512K-Bit 8-Bit Data Bus               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CAT28F010 .  |                                         | . 1 M-Bit 8-Bit Data Bus7-15            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CAT28F020 .  |                                         | . 2 M-Bit 8-Bit Data Bus7-29            |

| CAI 28F 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CAT28F102.   |                                         | . 1 M-Bit 16-Bit Data Bus 7-43          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                                         |                                         |

i

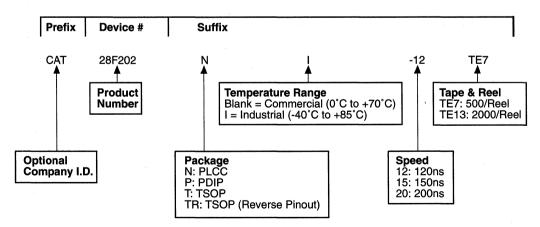

| CAT28F202 | 2 M-Bit 16-Bit Data Bus | . 7-57 |

|-----------|-------------------------|--------|

| CAT28F001 | 1 M-Bit Boot Block      | 7-71   |

| CAT28F002 | 2 M-Bit Boot Block      | 7-73   |

#### Section 8 Parallel E<sup>2</sup>PROMs

| CAT28C16A  | 16K-Bit  | 8-1   |

|------------|----------|-------|

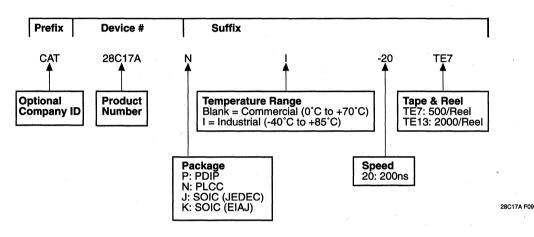

| CAT28C17A  | 16K-Bit  | 8-9   |

| CAT28C64B  | 64K-Bit  | 8-17  |

| CAT28C65B  | 64K-Bit  | 8-29  |

| CAT28C256  | 256K-Bit | 8-41  |

| CAT281 V64 | 64K-Bit  | 0.54  |

|            | 64K-Bit  | 8-5 I |

|            | 64K-Bit  |       |

# Section 9 Mixed Signal Products

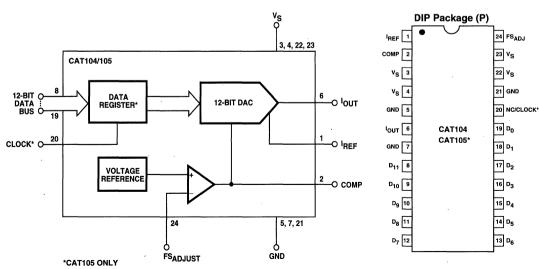

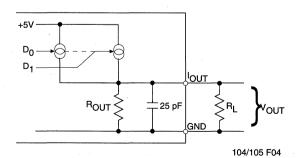

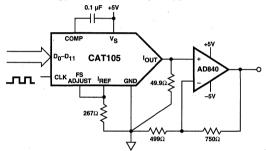

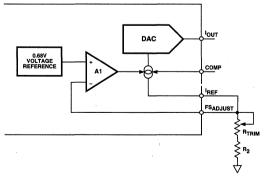

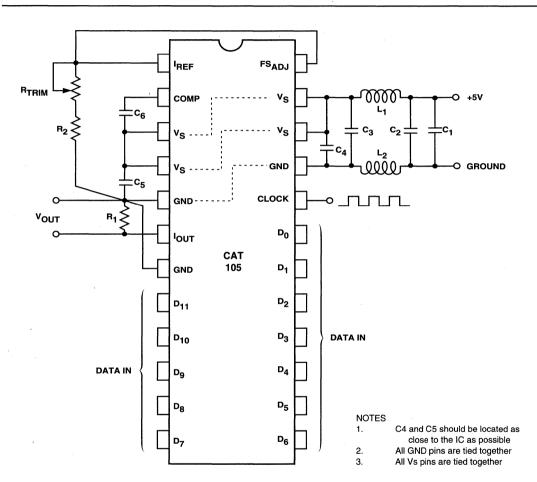

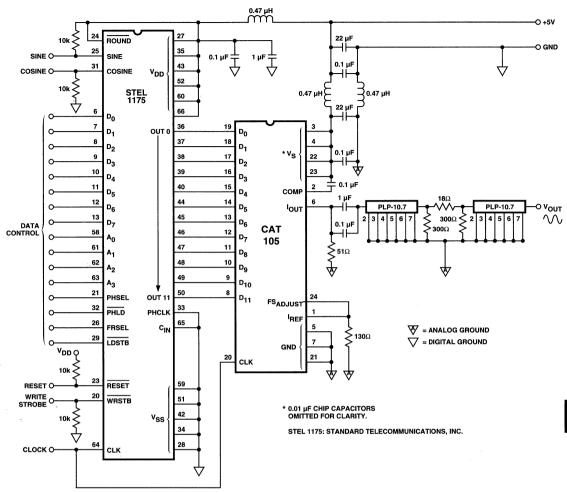

| CAT104/105 | 12 Bit, 25MHz D/A Converter   | 9-1              |

|------------|-------------------------------|------------------|

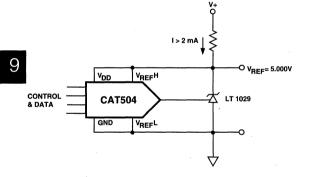

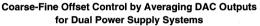

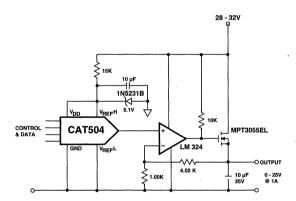

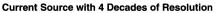

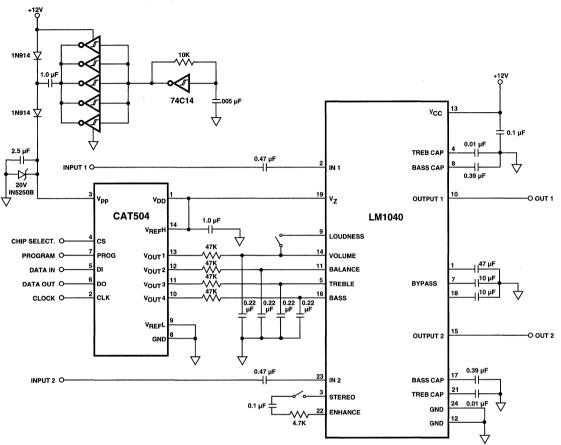

| CAT504     | 8-Bit Quad DACpot9            | €13              |

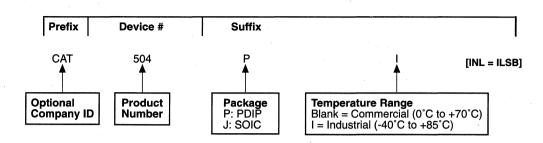

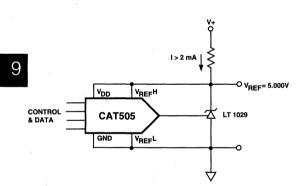

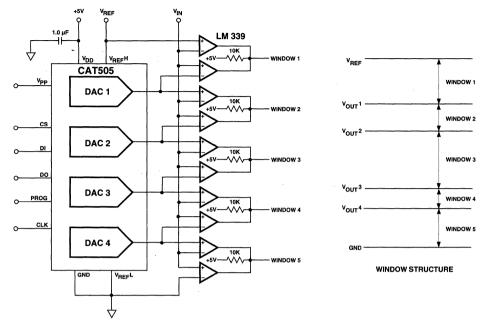

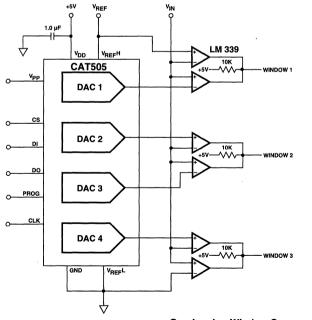

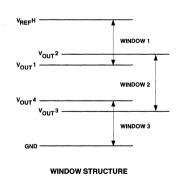

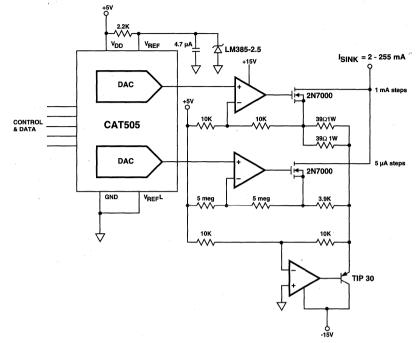

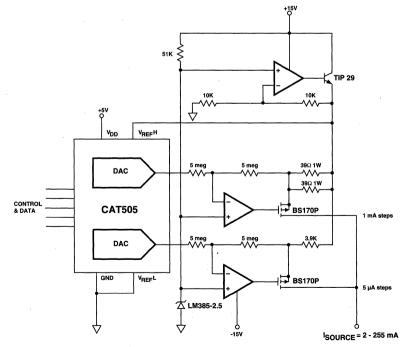

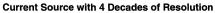

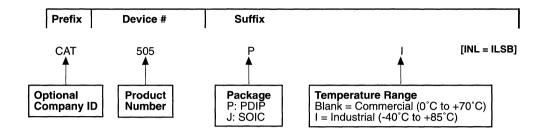

| CAT505     | 8-Bit Quad DACpot9            | )-25             |

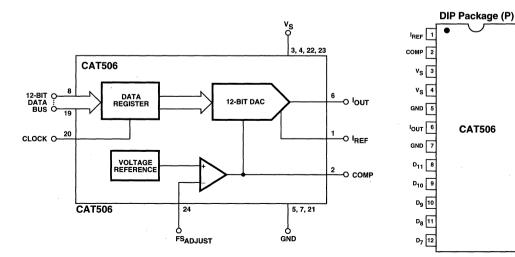

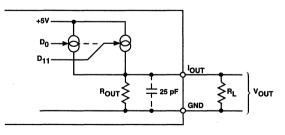

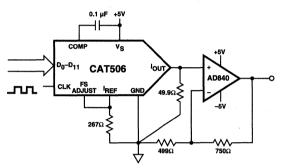

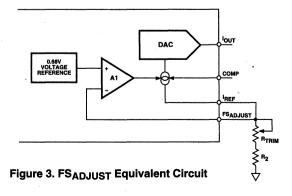

| CAT506     | 12 Bit, 40MHz D/A Converter 9 | <del>)</del> -37 |

## Section 10 Application Notes

| Using Catalyst's Serial E <sup>2</sup> PROMs in Shared Input/Output Configuration | 10-1  |

|-----------------------------------------------------------------------------------|-------|

| I <sup>2</sup> C Interface to 8051 Microcontroller                                | 10-5  |

| CAT64LC10: A User-Friendly Serial E <sup>2</sup> PROM                             |       |

| How to Use Catalyst Secure Access Serial E <sup>2</sup> PROMs                     |       |

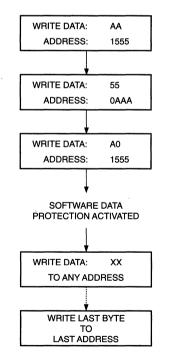

| Catalyst Parallel E <sup>2</sup> PROMs Feature Software Data Protection           |       |

| Programmer Vendors                                                                | 10-27 |

# Section 11 Quality and Reliability

| Catalyst Quality and Reliability                                                        |       |

|-----------------------------------------------------------------------------------------|-------|

| Warranty Procedure                                                                      | 11-7  |

| Reliability Considerations for E <sup>2</sup> PROMs                                     | 11-11 |

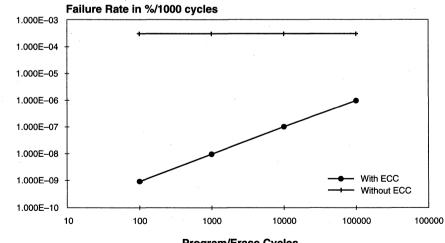

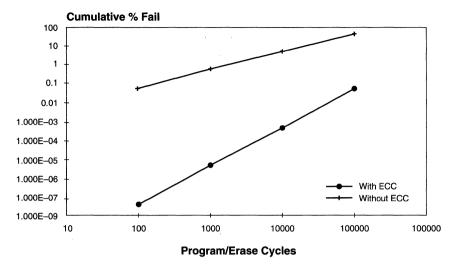

| E <sup>2</sup> PROM Reliability: On-Chip Error Code Correction for E <sup>2</sup> PROMs | 11-13 |

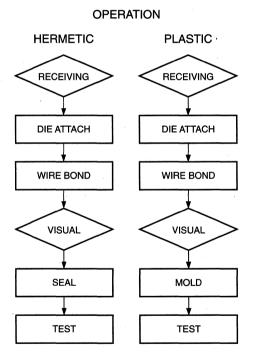

| Procurement Considerations for Reprogrammable Nonvolatile Microcircuit Memories         | 11-17 |

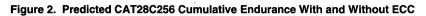

| Full-Featured E <sup>2</sup> PROM Cell Operation                                        | 11-25 |

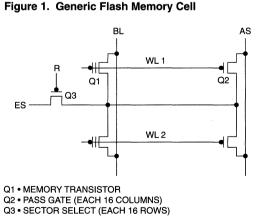

| Flash Memory Cell Operation                                                   | 11-27 |

|-------------------------------------------------------------------------------|-------|

| Failure Rate Prediction                                                       | 11-29 |

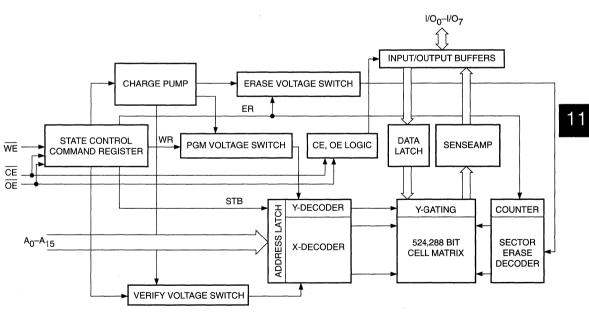

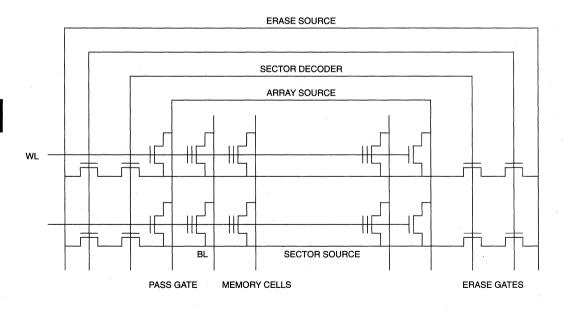

| Single Transistor 5V Flash Technology, with Sector Erase                      | 11-31 |

| Features and Performance of Reprogrammable Nonvolatile Floating Gate Memories | 11-35 |

| Section 12 Die Products                                                       |       |

| Catalyst Die Products                                                         | 12-1  |

| Section 13 General Information                                                |       |

| Product Selector Table                                                        | 13-1  |

| I <sup>2</sup> C Bus Serial E <sup>2</sup> PROMs                              | 13-1  |

| Microwire Bus Serial E <sup>2</sup> PROMs                                     | 13-9  |

| SPI Bus Serial E <sup>2</sup> PROMs                                           | 13-15 |

| Secure Access Serial E <sup>2</sup> PROMs                                     | 13-16 |

| NVRAMs                                                                        | 13-16 |

| Flash Memories                                                                | 13-17 |

| PEROMs (Flash Memories)                                                       | 13-20 |

| Parallel E <sup>2</sup> PROMs                                                 | 13-22 |

| Mixed Signal                                                                  | 13-27 |

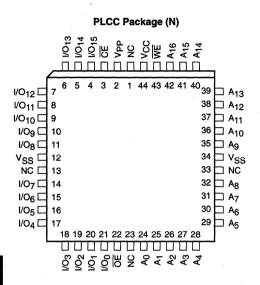

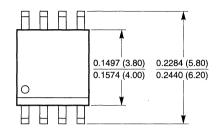

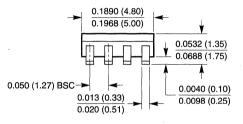

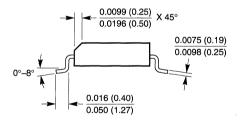

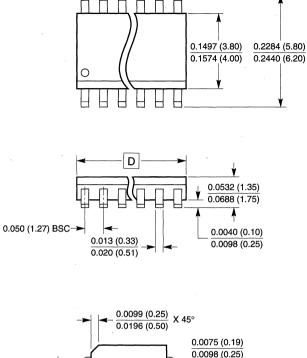

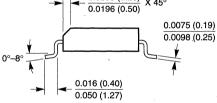

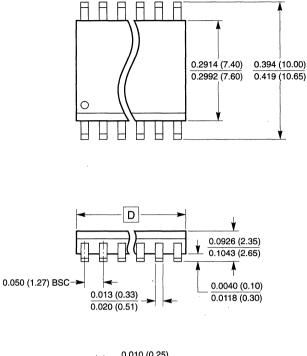

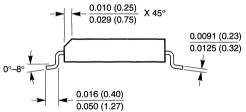

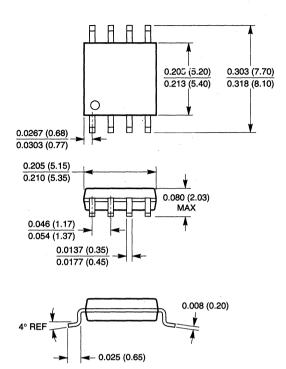

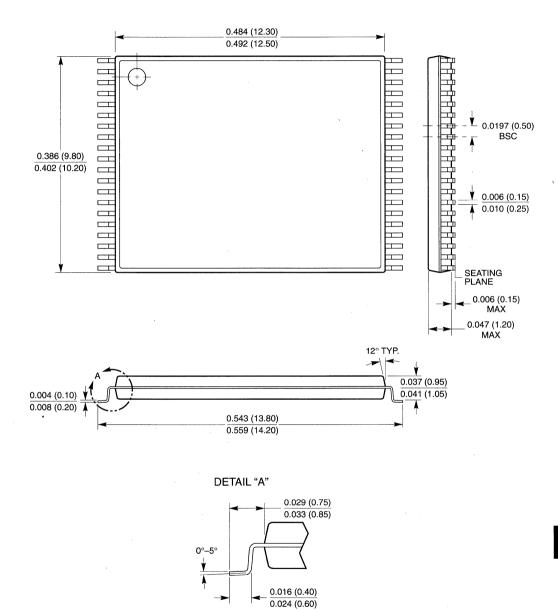

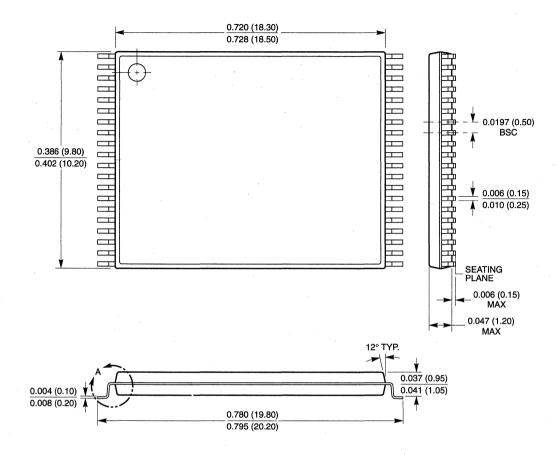

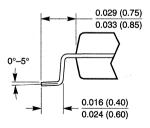

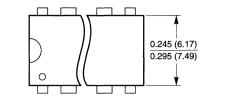

| Packaging Information                                                         | 13-29 |

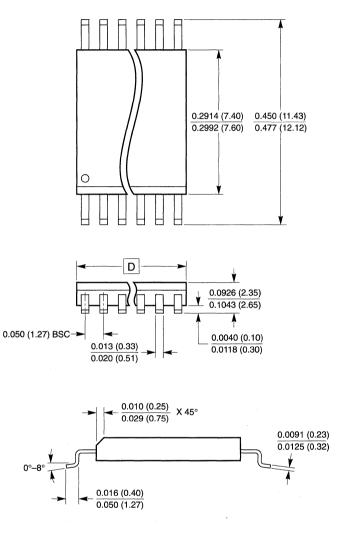

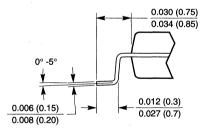

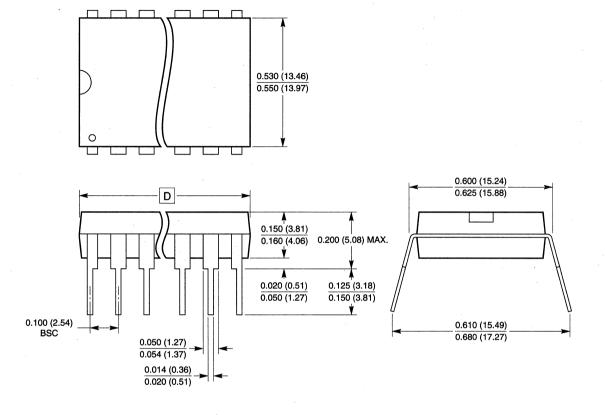

| SOIC                                                                          | 13-29 |

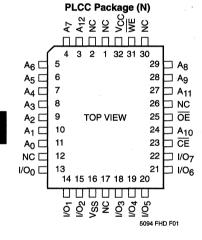

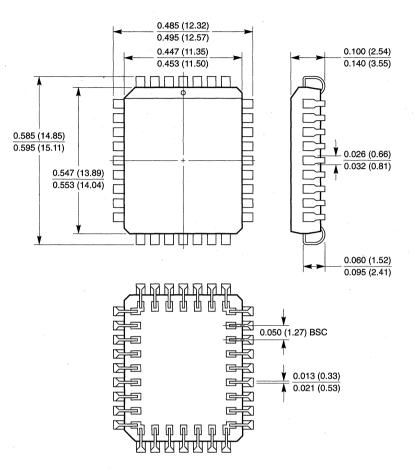

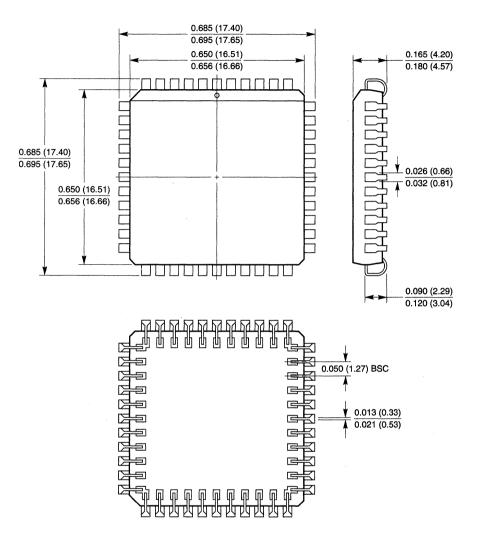

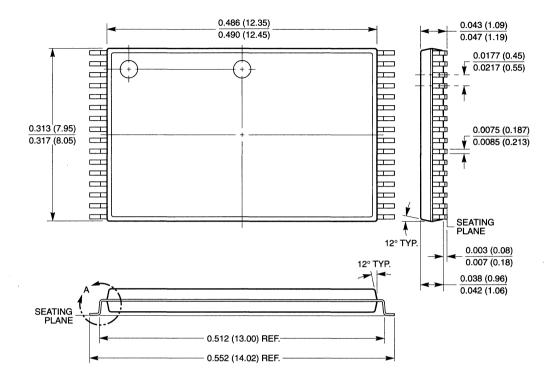

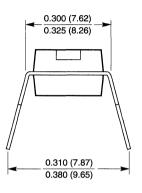

| PLCC                                                                          | 13-34 |

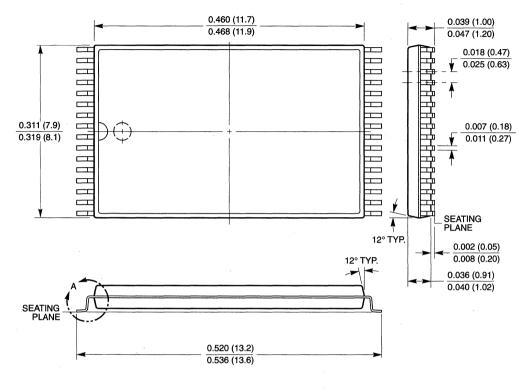

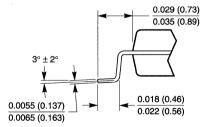

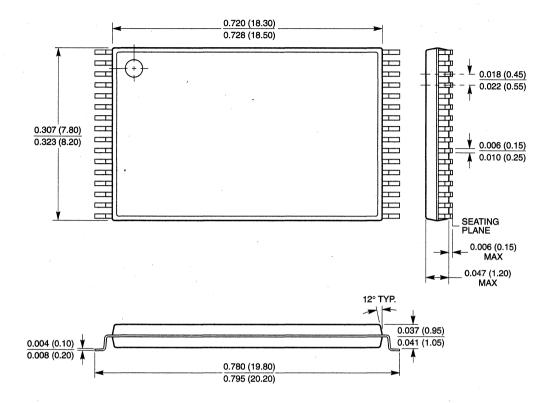

| TSOP                                                                          | 13-36 |

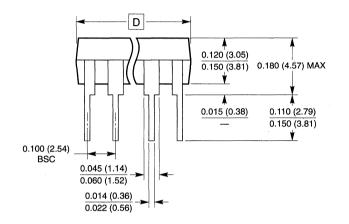

| Plastic DIP                                                                   | 13-41 |

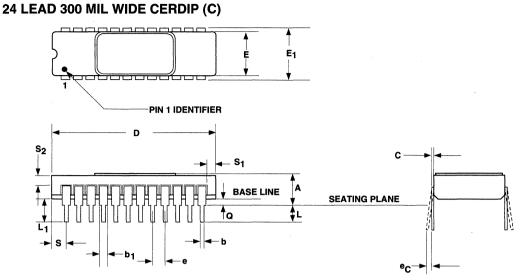

| CerDIP                                                                        | 13-43 |

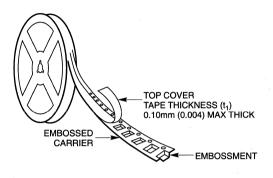

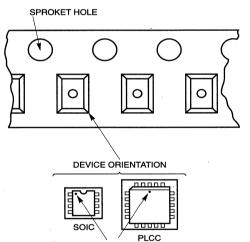

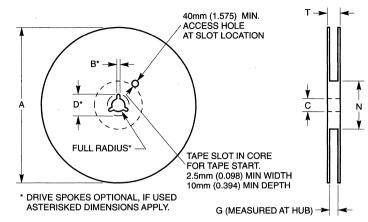

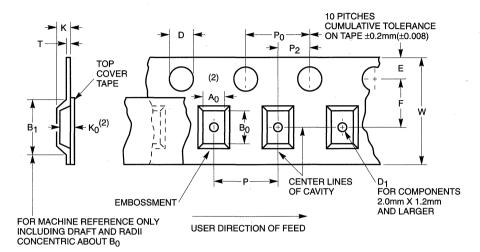

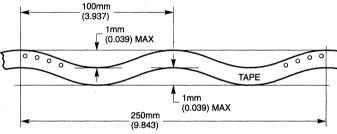

| Tape and Reel                                                                 | 13-44 |

iii

iv

**Product Information** I<sup>2</sup>C Bus Serial E<sup>2</sup>PROMs **Microwire Bus Serial E<sup>2</sup>PROMs SPI Bus Serial E<sup>2</sup>PROMs** Secure Access Serial E<sup>2</sup>PROMs **NVRAMs Flash Memories** Parallel E<sup>2</sup>PROMs **Mixed Signal Products Application Notes Quality and Reliability** Die Products **General Information**

Product Information I<sup>2</sup>C Bus Serial E<sup>2</sup>PROMs Microwire Bus Serial E<sup>2</sup>PROMs **SPI Bus Serial E<sup>2</sup>PROMs** Secure Access Serial E<sup>2</sup>PROMs **NVRAMs Flash Memories** Parallel E<sup>2</sup>PROMs **Mixed Signal Products Application Notes Quality and Reliability Die Products General Information**

1

# Contents

| Section 1   | Product Information |

|-------------|---------------------|

| Alpha-Nume  | eric Index 1-1      |

| Product Fea | tures               |

1

# Alpha-Numeric Index

| Part No.              | Description                                       | Organization                                | Page |

|-----------------------|---------------------------------------------------|---------------------------------------------|------|

| CAT104/105            | . Mixed Signal Products                           | . 12 Bit, 25MHz D/A Converter               | 9-1  |

| CAT22C10              | NVRAM                                             | . 256-Bit                                   | 6-1  |

| CAT24C01/02/04/08/16  | . I <sup>2</sup> C Bus Serial E <sup>2</sup> PROM | . 1K/2K/4K/8K/16K-Bit                       | 2-1  |

| CAT24C32/64           | . I <sup>2</sup> C Bus Serial E <sup>2</sup> PROM | . 32K/64K-Bit                               | 2-17 |

| CAT24C44              | NVRAM                                             | . 256-Bit                                   | 6-11 |

| CAT24WC01/02/04/08/16 | . I <sup>2</sup> C Bus Serial E <sup>2</sup> PROM | . 1K/2K/4K/8K/16K-Bit Write Protection Pin. | 2-9  |

| CAT24WC32/64          | . I <sup>2</sup> C Bus Serial E <sup>2</sup> PROM | . 32K/64K-Bit Write Protection Pin          | 2-25 |

| CAT28C16A             | . Parallel E <sup>2</sup> PROM                    | . 16K-Bit                                   | 8-1  |

| CAT28C17A             | . Parallel E <sup>2</sup> PROM                    | . 16K-Bit                                   | 8-9  |

| CAT28C256             | . Parallel E <sup>2</sup> PROM                    | . 256K-Bit                                  | 8-41 |

| CAT28C64B             | . Parallel E <sup>2</sup> PROM                    | . 64K-Bit                                   | 8-17 |

| CAT28C65B             | . Parallel E <sup>2</sup> PROM                    | . 64K-Bit                                   | 8-29 |

| CAT28F001             | . Flash Memory                                    | . 1 M-Bit Boot Block                        | 7-71 |

| CAT28F002             | . Flash Memory                                    | . 2 M-Bit Boot Block                        | 7-73 |

| CAT28F010             | . Flash Memory                                    | . 1 M-Bit 8-Bit Data Bus                    | 7-15 |

| CAT28F020             | . Flash Memory                                    | . 2 M-Bit 8-Bit Data Bus                    | 7-29 |

| CAT28F102             | . Flash Memory                                    | . 1 M-Bit 16-Bit Data Bus                   | 7-43 |

| CAT28F202             | . Flash Memory                                    | . 2 M-Bit 16-Bit Data Bus                   | 7-57 |

| CAT28F512             | . Flash Memory                                    | . 512K-Bit 8-Bit Data Bus                   | 7-1  |

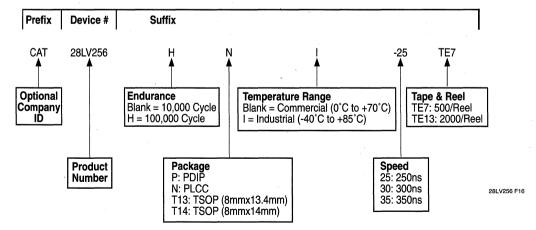

| CAT28LV256            | . Parallel E <sup>2</sup> PROM                    | . 256K-Bit 3.3V Operating Voltage           | 8-71 |

| CAT28LV64             | . Parallel E <sup>2</sup> PROM                    | . 64K-Bit 3.3V Operating Voltage            | 8-51 |

| CAT28LV65             | . Parallel E <sup>2</sup> PROM                    | . 64K-Bit 3.3V Operating Voltage            | 8-61 |

| CAT33C704             | . Secure Access Serial E <sup>2</sup> PROM        | . 4K-Bit 3V Operating Voltage               | 5-15 |

| CAT33C804A            | . Secure Access Serial E <sup>2</sup> PROM        | . 4K-Bit 3V Operating Voltage               | 5-43 |

| CAT35C704             | . Secure Access Serial E <sup>2</sup> PROM        | . 4K-Bit 5V Operating Voltage               | 5-1  |

| CAT35C804A            | . Secure Access Serial E <sup>2</sup> PROM        | . 4K-Bit 5V Operating Voltage               | 5-29 |

| CAT504                | Mixed Signal Products                             | . 8-Bit Quad DAC pot                        | 9-13 |

| CAT505                | Mixed Signal Products                             | . 8-Bit Quad DAC pot                        | 9-25 |

| CAT506                | Mixed Signal Products                             | . 12 Bit, 40MHz D/A Converter               | 9-37 |

|                       |                                                   |                                             |      |

## Alpha-Numeric Index

| Part No.              | Description                               | Organization                | Page   |

|-----------------------|-------------------------------------------|-----------------------------|--------|

| CAT64LC10/20/40       | SPI Bus Serial E <sup>2</sup> PROM        | 1K/2K/4K-Bit                | 4-1    |

| CAT93C46/56/66/86     | Microwire Bus Serial E <sup>2</sup> PROM  | 1K/2K/4K/16K-Bit            | 3-1    |

| CAT93C46A/56A/66A/86A | Microwire Bus Serial E <sup>2</sup> PROM  | 1K/2K/4K/16K-Bit No ORG Pin | 3-9    |

| CAT93C57              | .Microwire Bus Serial E <sup>2</sup> PROM | 2K-Bit                      | . 3-17 |

# **Product Features**

# SERIAL E<sup>2</sup>PROMs

I<sup>2</sup>C Bus (Data Book Section 2)

| Device | Temp.<br>Range | Density<br>(Organization) | ICC<br>(Active/Standby) | Max. Clock<br>Freq. | Lead<br>Count | Pkg<br>Types       | Oprtg<br>Vitg. Range |

|--------|----------------|---------------------------|-------------------------|---------------------|---------------|--------------------|----------------------|

| 24C01  | C, I           | 1Kb<br>(128X8)            | 3mA/0µA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

| 24WC01 | C, I           | 1Kb<br>(128X8)            | 3mA/0μA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

| 24C02  | C, I           | 2Kb<br>(256X8)            | 3mA/0μA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

| 24WC02 | C, I           | 2Kb<br>(256X8)            | 3mA/0μA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

| 24C04  | C, I           | 4Kb<br>(512X8)            | 3mA/0μA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

| 24WC04 | C, I           | 4Kb<br>(512X8)            | 3mA/0µA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

| 24C08  | C, I           | 8Kb<br>(1024X8)           | 3mA/0μA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

| 24WC08 | C, I           | 8Kb<br>(1024X8)           | 3mA/0μA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

| 24C16  | C, I           | 16Kb<br>(2048X8)          | 3mA/0μA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

| 24WC16 | C, I           | 16Kb<br>(2048X8)          | 3mA/0μA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

| 24C32  | C, I           | 32Kb<br>(4096X8)          | 3mA/0μA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

| 24WC32 | C, I           | 32Kb<br>(4096X8)          | 3mA/0μA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

| 24C64  | C, I           | 64Kb<br>(8192X8)          | 3mA/0μA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

| 24WC64 | C, I           | 64Kb<br>(8192X8)          | 3mA/0μA                 | 400kHz              | 8<br>14       | PDIP, SOIC<br>SOIC | 1.8 -6.0V            |

1

#### SERIAL E<sup>2</sup>PROMs Microwire Bus (Data Book Section 3)

| Device | Temp.<br>Range | Density<br>(Organization) | ICC<br>(Active/Standby) | Max. Clock<br>Freq. | Lead<br>Count | Pkg<br>Types | Oprtg<br>Vitg. Range |

|--------|----------------|---------------------------|-------------------------|---------------------|---------------|--------------|----------------------|

| 93C46  | C, I           | 1Kb<br>(64X16/128X8)      | 3mA/50μA                | 1MHZ                | 8             | PDIP, SOIC   | 1.8 - 6.0V           |

| 93C46A | C, I           | 1Kb<br>(64X16)            | 3mA/50μA                | 1MHZ                | . 8           | PDIP, SOIC   | 1.8 - 6.0V           |

| 93C56  | C, I           | 2Kb<br>(128X16/256X8)     | 3mA/50μA                | 1MHZ                | 8             | PDIP, SOIC   | 1.8 - 6.0V           |

| 93C56A | C, I           | 2Kb<br>(128X16)           | 3mA/50μA                | 1MHZ                | 8             | PDIP, SOIC   | 1.8 - 6.0V           |

| 93C66  | C, I           | 4Kb<br>(256X16/512X8)     | 3mA/50μA                | 1MHZ                | 8             | PDIP, SOIC   | 1.8 - 6.0V           |

| 93C66A | C, I           | 4Kb<br>(256X16)           | 3mA/50μA                | 1MHZ                | . 8           | PDIP, SOIC   | 1.8 - 6.0V           |

| 93C86  | C, I           | 16Kb<br>(1024X16/2048X8)  | 3mA/50μA                | 1MHZ                | 8             | PDIP, SOIC   | 1.8 - 6.0V           |

| 93C86A | C, I           | 16Kb<br>(1024X16)         | 3mA/50μA                | 1MHZ                | 8             | PDIP, SOIC   | 1.8 - 6.0V           |

| 93C57  | C, I           | 2Kb<br>(128X16/256X8)     | 3mA/50μA                | 1MHZ                | 8             | PDIP, SOIC   | 1.8 - 6.0V           |

# SERIAL E<sup>2</sup>PROMs

# SPI Bus (Data Book Section 4)

| Device | Temp.<br>Range | Density<br>(Organization) | ICC<br>(Active/Standby) | Max. Clock<br>Freq. | Lead<br>Count | Pkg<br>Types | Oprtg<br>Vitg |

|--------|----------------|---------------------------|-------------------------|---------------------|---------------|--------------|---------------|

| 64LC10 | C, I           | 1Kb<br>(64X16)            | 1mA/0μA                 | 1MHZ                | 8             | PDIP, SOIC   | 2.5-6.0V      |

| 64LC20 | C, I           | 2Kb<br>(128X16)           | 1mA/0μA                 | 1MHZ                | 8             | PDIP, SOIC   | 2.5-6.0V      |

| 64LC40 | C, I           | 4Kb<br>(256X16)           | 1mA/0μA                 | 1MHZ                | 8             | PDIP, SOIC   | 2.5-6.0V      |

# SERIAL E<sup>2</sup>PROMs

# Secure Access (Data Book Section 5)

| Device  | Temp.<br>Range |                 | Density<br>(Organization) | ICC<br>(Active/Standby) | Max. Clock<br>Freq. | Lead<br>Count | Pkg<br>Types       | Oprtg<br>Vitg |

|---------|----------------|-----------------|---------------------------|-------------------------|---------------------|---------------|--------------------|---------------|

| 35C704  | C, I           | Synchronous     | 4Kb<br>(256X16/512X8)     | 3mA/250μA               | 3MHZ                | 8             | PDIP, SOIC         | 4.5-5.5V      |

| 33C704  | C, I           | Synchronous     | 4Kb<br>(256X16/512X8)     | 3mA/250μA               | 1MHZ                | 8             | PDIP, SOIC         | 2.7-3.3V      |

| 35C804A | C, I           | UART Compatible | 4Kb<br>(256X16/512X8)     | 3mA/250µA               | 5MHZ                | 8<br>16       | PDIP, SOIC<br>SOIC | 4.5-5.5V      |

| 33C804A | C, I           | UART Compatible | 4Kb<br>(256X16/512X8)     | 3mA/250μA               | 5MHZ                | 8<br>16       | PDIP, SOIC<br>SOIC | 2.7-3.3V      |

# NVRAMs

| (Data I | Book | Sectio | on 6) |

|---------|------|--------|-------|

|         |      |        |       |

| Device | Temp.<br>Range | Density<br>(Organization) | Access Time (ns)/<br>Max. CLK Freq | ICC<br>(Active/Standby) | Lead<br>Count | Pkg<br>Types | Oprtg<br>Vitg Range |

|--------|----------------|---------------------------|------------------------------------|-------------------------|---------------|--------------|---------------------|

| 22C10  | C, I           | 256b                      | 200, 300<br>(64X4)                 | 40mA/30μA               | 18<br>16      | PDIP<br>SOIC | 4.5-5.5V            |

| 24C44  | C, I           | 256b                      | 1MHZ<br>(16X16)                    | 3mA/30µA                | 8             | PDIP, SOIC   | 4.5-5.5V            |

#### Flash Memories (Data Book Section 7)

| Device | Temp.<br>Range | Density<br>(Organization) | Access<br>Time (ns) | ICC<br>(Active/Standby) | Lead<br>Count  | Pkg<br>Types                     | Oprtg<br>Vitg Range |

|--------|----------------|---------------------------|---------------------|-------------------------|----------------|----------------------------------|---------------------|

| 28F512 | C, I           | 512Kb<br>(64KX8)          | 90/120/150          | 30mA/100µA              | 32             | PDIP, PLCC,<br>TSOP              | 12V                 |

| 28F010 | C, I           | 1Mb<br>(128KX8)           | 90/120/150          | 30mA/100μA              | 32             | PDIP, PLCC,<br>TSOP              | 12V                 |

| 28F020 | C, I           | 2Mb<br>(256KX8)           | 120/150/200         | 30mA/100μA              | 32             | PDIP, PLCC,<br>TSOP              | 12V                 |

| 28F102 | C, I           | 1Mb<br>(64KX16)           | 90/120/150          | 30mA/100µA              | 40<br>44       | PDIP, TSOP<br>PLCC               | 12V                 |

| 28F202 | C, I           | 2Mb<br>(128KX16)          | 120/150/200         | 30mA/100µA              | 40<br>44       | PDIP, TSOP<br>PLCC               | 12V                 |

| 28F001 | C,I            | 1Mb<br>(128KX8)           | 90/120/150          | -                       | 32             | PDIP, PLCC,<br>TSOP              | 12V                 |

| 28F002 | C,I            | 2Mb<br>(256KX8)           | 120/150/200         | -                       | 32<br>40<br>44 | PDIP, PLCC, TSOP<br>TSOP<br>PSOP | 12V                 |

# PARALLEL E<sup>2</sup>PROMs

(Data Book Section 8)

| Device | Temp.<br>Range | Compatibility | Density<br>(Organization) | Access<br>Time (ns) | ICC<br>(Active/Standby) | Lead<br>Count | Pkg<br>Types                   | Oprtg<br>Vitg |

|--------|----------------|---------------|---------------------------|---------------------|-------------------------|---------------|--------------------------------|---------------|

| 28C16A | C, I           | Industry      | 16Kb<br>(2KX8)            | 200, 250            | 35mA/100μA              | 24<br>32      | PDIP, SOIC<br>PLCC             | 4.5-5.5V      |

| 28C17A | C, I           | Industry      | 16Kb<br>(2KX8)            | 200, 250            | 35mA/100μA              | 28<br>32      | PDIP, SOIC<br>PLCC             | 4.5-5.5V      |

| 28C64B | C, I           | Industry      | 64Kb<br>(8KX8)            | 120, 150,<br>200    | 30mA/100μA              | 28<br>32      | PDIP, SOIC, TSOP<br>TSOP, PLCC | 4.5-5.5V      |

| 28C65B | C, I           | Industry      | 64Kb<br>(8KX8)            | 120, 150,<br>200    | 30mA/100μA              | 28<br>32      | PDIP, SOIC, TSOP<br>TSOP, PLCC | 4.5-5.5V      |

| 28C256 | C, I           | Industry      | 256Kb<br>(32KX8)          | 150, 200,<br>250    | 30mA/150µA              | 28<br>32      | PDIP, TSOP<br>TSOP, PLCC       | 4.5-5.5V      |

# **PARALLEL E<sup>2</sup>PROMs**

Low Voltage (Data Book Section 8)

| Device  | Temp.<br>Range | Density<br>(Organization) | Access<br>Time (ns) | ICC<br>(Active/Standby) | Lead<br>Count | Pkg<br>Types                   | Oprtg<br>Vitg |

|---------|----------------|---------------------------|---------------------|-------------------------|---------------|--------------------------------|---------------|

| 28LV64  | C, I           | 64Kb<br>(8KX8)            | 200, 250, 300       | 8mA/150µA               | 28<br>32      | PDIP, SOIC, TSOP<br>TSOP, PLCC | 3.0-3.6V      |

| 28LV65  | C, I           | 64Kb<br>(8KX8)            | 200, 250, 300       | 8mA/150µA               | 28<br>32      | PDIP, SOIC, TSOP<br>TSOP, PLCC | 3.0-3.6V      |

| 28LV256 | C, I           | 256Kb<br>(32KX8)          | 200, 250, 300       | 15mA/150μA              | 28<br>32      | PDIP, TSOP<br>TSOP, PLCC       | 3.0-3.6V      |

# Mixed Signal Products (Data Book Section 9)

| Device | Temp | Bits<br>Resolution | Linearity<br>Error(LSB) | Data Latch | NV MEM. | #DACs/Pkg | Pkg Types  | Settling<br>Time(ns) |

|--------|------|--------------------|-------------------------|------------|---------|-----------|------------|----------------------|

| 104A   | C, I | 12                 | 1/2 LSB                 | No         | No      | 1         | CerDIP     | 40                   |

| 104B   | C, I | 12                 | 1LSB                    | No         | No      | 1         | CerDIP     | 40                   |

| 105A   | C, I | 12                 | 1/2 LSB                 | Yes        | No      | 1         | CerDIP     | 40                   |

| 105B   | C, I | 12                 | 1 LSB                   | Yes        | No      | 1         | CerDIP     | 40                   |

| 504    | C, I | 8                  | 1LSB                    | Yes        | Yes     | 4         | PDIP, SOIC | 10µs                 |

| 505    | C, I | 8                  | 1LSB                    | Yes        | Yes     | 4         | PDIP, SOIC | 10µs                 |

| 506A   | С    | 12                 | 1/2 LSB                 | Yes        | No      | 1         | CerDIP     | 25                   |

| 506B   | С    | 12                 | 1LSB                    | Yes        | No      | 1         | CerDIP     | 25                   |

Product Information I<sup>2</sup>C Bus Serial E<sup>2</sup>PROMs Microwire Bus Serial E<sup>2</sup>PROMs **SPI Bus Serial E<sup>2</sup>PROMs** Secure Access Serial E<sup>2</sup>PROMs **NVRAMs Flash Memories** Parallel E<sup>2</sup>PROMs **Mixed Signal Products Application Notes Quality and Reliability** Die Products **General Information**

2

# Contents

| Section 2   | I <sup>2</sup> C Bus Serial E <sup>2</sup> PROMs |                                               |     |

|-------------|--------------------------------------------------|-----------------------------------------------|-----|

| CAT24C01/02 | 2/04/08/16                                       | 1K/2K/4K/8K/16K-Bit                           | 2-1 |

| CAT24WC01   | /02/04/08/16                                     | 1K/2K/4K/8K/16K-Bit with Write Protection Pin | 2-9 |

| CAT24C32/64 | 4                                                | 32K/64K-Bit2                                  | -17 |

| CAT24WC32   | /64                                              | 32K/64K-Bit with Write Protection Pin 2       | -25 |

2

.

# CAT24C01/02/04/08/16

1K/2K/4K/8K/16K-Bit Serial E<sup>2</sup>PROM

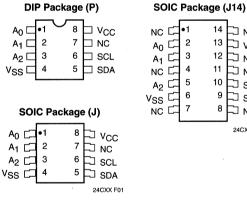

# **FEATURES**

- 400 KHZ I<sup>2</sup>C Bus Compatible\*

- 1.8 to 6.0 Volt Operation

- Low Power CMOS Technology

- Page Write Buffer

- Self-Timed Write Cycle with Auto-Clear

- 100,000 Program/Erase Cycles

- 100 Year Data Retention

- 8-pin DIP, 8-pin SOIC or 14-pin SOIC Package

- Commercial and Industrial Temperature Ranges

2

## DESCRIPTION

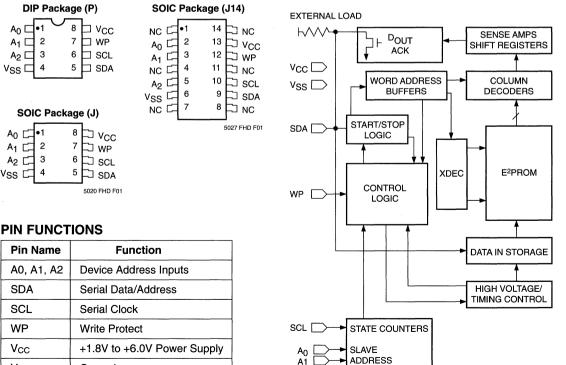

The CAT24C01/02/04/08/16 is a 1K/2K/4K/8K/16K-bit Serial CMOS E<sup>2</sup>PROM internally organized as 128/256/ 512/1024/2048 words of 8 bits each. Catalyst's advanced CMOS technology substantially reduces device power requirements. The CAT24C01/02 features an 8-

14

13

12

11 С ПС

10 SCL

9

8

Э NC

⊐ vcc

🗅 sda

🗅 NC

24CXX E02

П КС

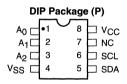

#### **PIN CONFIGURATION**

#### **PIN FUNCTIONS**

| Pin Name   | Function                    |

|------------|-----------------------------|

| A0, A1, A2 | Device Address Inputs       |

| SDA        | Serial Data/Address         |

| SCL        | Serial Clock                |

| NC         | No Connect                  |

| Vcc        | +1.8V to +6.0V Power Supply |

| Vss        | Ground                      |

byte page write buffer, and the CAT24C04/08/16 features an 16-byte page write buffer. The device operates via the I<sup>2</sup>C bus serial interface and is available in 8-pin DIP, 8-pin SOIC or 14-pin SOIC packages.

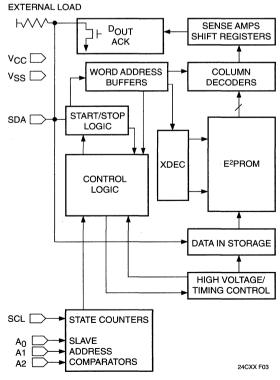

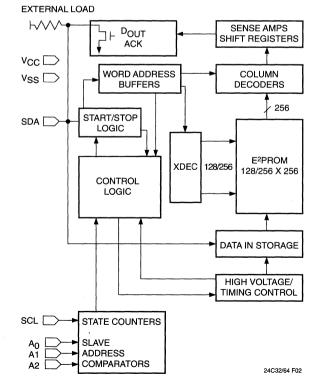

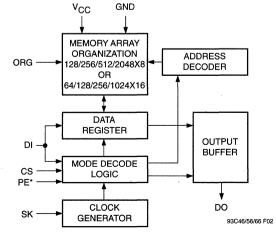

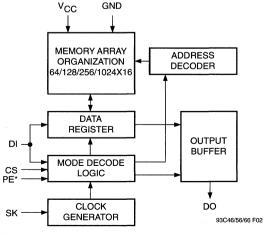

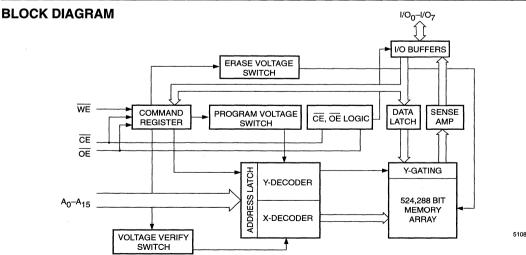

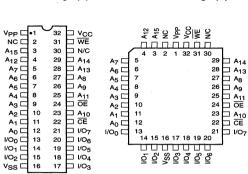

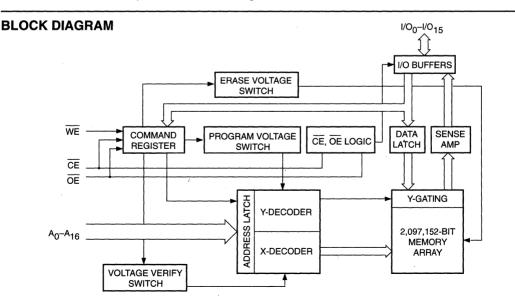

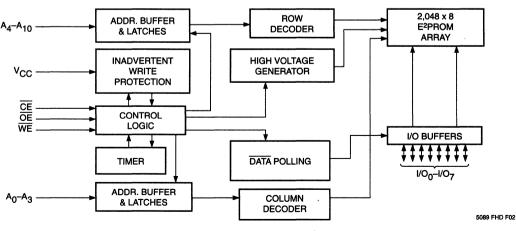

# **BLOCK DIAGRAM**

\* Catalyst Semiconductor is licensed by Philips Corporation to carry the I<sup>2</sup>C Bus Protocol.

© 1996 by Catalyst Semiconductor, Inc.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias –55°C to +125°C                                                      |

|---------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                           |

| Voltage on Any Pin with<br>Respect to Ground <sup>(1)</sup> 2.0V to +V <sub>CC</sub> + 2.0V |

| V <sub>CC</sub> with Respect to Ground2.0V to +7.0V                                         |

| Package Power Dissipation<br>Capability (Ta = 25°C) 1.0W                                    |

| Lead Soldering Temperature (10 secs)                                                        |

#### **\*COMMENT**

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

#### **RELIABILITY CHARACTERISTICS**

| Symbol                             | Parameter          | Min.    | Max. | Units       | Reference Test Method         |

|------------------------------------|--------------------|---------|------|-------------|-------------------------------|

| NEND <sup>(3)</sup>                | Endurance          | 100,000 | *    | Cycles/Byte | MIL-STD-883, Test Method 1033 |

| T <sub>DR</sub> <sup>(3)</sup>     | Data Retention     | 100     |      | Years       | MIL-STD-883, Test Method 1008 |

| Vzap <sup>(3)</sup>                | ESD Susceptibility | 2000    |      | Volts       | MIL-STD-883, Test Method 3015 |

| I <sub>LTH</sub> <sup>(3)(4)</sup> | Latch-up           | 100     |      | mA          | JEDEC Standard 17             |

#### **D.C. OPERATING CHARACTERISTICS**

$V_{CC} = +1.8V$  to +6.0V, unless otherwise specified.

|                    |                                             | L                     | Limits                                                                                                          |                       |       |                                   |

|--------------------|---------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------|-------|-----------------------------------|

| Symbol             | Parameter                                   | Min.                  | Тур.                                                                                                            | Max.                  | Units | Test Conditions                   |

| lcc                | Power Supply Current                        |                       | 1997 - 1998 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - | 3                     | mA    | f <sub>SCL</sub> = 100 KHz        |

| IsB <sup>(5)</sup> | Standby Current (V <sub>CC</sub> = 5.0V)    |                       |                                                                                                                 | 0.                    | μA    | $V_{IN} = GND \text{ or } V_{CC}$ |

| ١LI                | Input Leakage Current                       |                       |                                                                                                                 | 10                    | μA    | $V_{IN} = GND$ to $V_{CC}$        |

| ILO                | Output Leakage Current                      |                       |                                                                                                                 | 10                    | μA    | VOUT = GND to VCC                 |

| VIL                | Input Low Voltage                           | -1                    |                                                                                                                 | V <sub>CC</sub> x 0.3 | V     |                                   |

| VIH                | Input High Voltage                          | V <sub>CC</sub> x 0.7 |                                                                                                                 | V <sub>CC</sub> + 0.5 | V     |                                   |

| V <sub>OL1</sub>   | Output Low Voltage (V <sub>CC</sub> = 3.0V) |                       |                                                                                                                 | 0.4                   | V     | I <sub>OL</sub> = 3 mA            |

| V <sub>OL2</sub>   | Output Low Voltage (V <sub>CC</sub> = 1.8V) |                       |                                                                                                                 | 0.5                   | V     | I <sub>OL</sub> = 1.5 mA          |

#### **CAPACITANCE** $T_A = 25^{\circ}C$ , f = 1.0 MHz, $V_{CC} = 5V$

| Symbol                          | Test                                | Max. | Units | Conditions     |

|---------------------------------|-------------------------------------|------|-------|----------------|

| C <sub>I/O</sub> <sup>(3)</sup> | Input/Output Capacitance (SDA)      | 8    | pF    | $V_{I/O} = 0V$ |

| C <sub>IN</sub> <sup>(3)</sup>  | Input Capacitance (A0, A1, A2, SCL) | 6    | рF    | $V_{IN} = 0V$  |

Note:

(2) Output shorted for no more than one second. No more than one output shorted at a time.

(3) This parameter is tested initially and after a design or process change that affects the parameter.

(4) Latch-up protection is provided for stresses up to 100 mA on address and data pins from -1V to V<sub>CC</sub> +1V.

(5) Standby Current (I<sub>SB</sub>) = 0μA (<900nA).

<sup>(1)</sup> The minimum DC input voltage is -0.5V. During transitions, inputs may undershoot to -2.0V for periods of less than 20 ns. Maximum DC voltage on output pins is V<sub>CC</sub> +0.5V, which may overshoot to V<sub>CC</sub> + 2.0V for periods of less than 20ns.

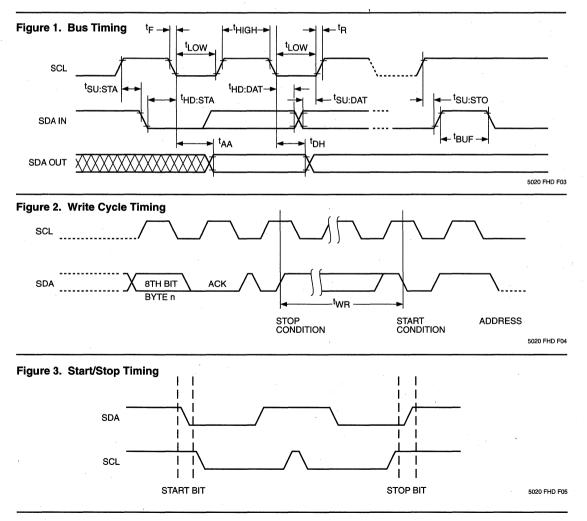

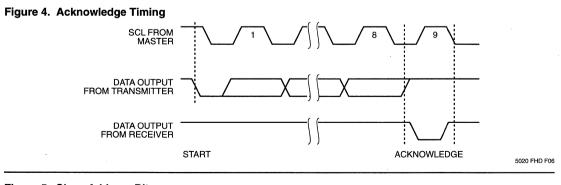

#### A.C. CHARACTERISTICS

$V_{CC}$  = +1.8V to +6.0V, unless otherwise specified.

#### **Read & Write Cycle Limits**

| Symbol                          | Parameter                                                     | V <sub>cc</sub> =1 | .8V - 6V | V <sub>CC</sub> =4.5 | iV - 5.5V |       |

|---------------------------------|---------------------------------------------------------------|--------------------|----------|----------------------|-----------|-------|