# FEATURES

- Single-Chip IEEE 802.3 Ethernet Controller with Direct ISA-Bus Interface

- Maximum Current Consumption = 55 mA (5V Supply)

- 3 V Operation

- Industrial Temperature Range

- Comprehensive Suite of Software Drivers Available

- Efficient PacketPage™ Architecture Operates in I/O and Memory Space, and as DMA Slave

- Full Duplex Operation

- On-Chip RAM Buffers Transmit and Receive Frames

- 10BASE-T Port with Analog Filters, Provides:

- Automatic Polarity Detection and Correction

- AUI Port for 10BASE2, 10BASE5 and 10BASE-F

- Programmable Transmit Features:

- Automatic Re-transmission on Collision

- Automatic Padding and CRC Generation

- Programmable Receive Features:

- Stream Transfer™ for Reduced CPU Overhead

- Auto-Switch Between DMA and On-Chip Memory

- Early Interrupts for Frame Pre-Processing

- Automatic Rejection of Erroneous Packets

- EEPROM Support for Jumperless Configuration

- Boot PROM Support for Diskless Systems

- Boundary Scan and Loopback Test

- LED Drivers for Link Status and LAN Activity

- Standby and Suspend Sleep Modes

# Crystal LAN™ Ethernet Controller

# DESCRIPTION

The CS8900A is a low-cost Ethernet LAN Controller optimized for the Industry Standard Architecture (ISA) bus and general purpose microcontroller busses. Its highlyintegrated design eliminates the need for costly external components required by other Ethernet controllers. The CS8900A includes on-chip RAM, 10BASE-T transmit and receive filters, and a direct ISA-Bus interface with 24 mA Drivers.

In addition to high integration, the CS8900A offers a broad range of performance features and configurationoptions. Its unique PacketPage architecture automatically adapts to changing network traffic patterns and available system resources. The result is increased system efficiency.

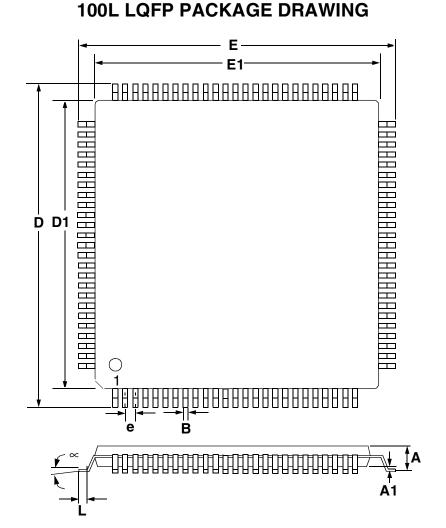

The CS8900A is available in a 100-pin LQFP package ideally suited for small form-factor, cost-sensitive Ethernet applications. With the CS8900A, system engineers can design a complete Ethernet circuit that occupies less than 1.5 square inches (10 sq. cm) of board space.

#### **ORDERING INFORMATION**

| CS8900A-CQ   | 0° to 70°   | C 5V     | LQFP-100     |

|--------------|-------------|----------|--------------|

| CS8900A-IQ   | -40° to 85° | °C 5V    | LQFP-100     |

| CS8900A-CQ3  | 0° to 70°   | °C 3.3V  | LQFP-100     |

| CS8900A-CQ3Z | 0° to 70°   | ° C 3.3V | LQFP-100     |

| CS8900A-IQ3  | -40° to 85° | °C 3.3V  | LQFP-100     |

| CRD8900A-1   |             | E        | aluation Kit |

# TABLE OF CONTENTS

|             | CTION                                                                |    |

|-------------|----------------------------------------------------------------------|----|

| 1.1 Genera  | I Description                                                        | 8  |

| 1.1.1       | Direct ISA-Bus Interface                                             | 8  |

| 1.1.2       | Integrated Memory                                                    | 8  |

|             | 802.3 Ethernet MAC Engine                                            |    |

|             | EEPROM Interface                                                     |    |

|             | Complete Analog Front End                                            |    |

|             | Applications                                                         |    |

|             | Motherboard LANs                                                     |    |

|             | Ethernet Adapter Cards                                               |    |

|             | atures and Benefits                                                  |    |

|             | Very Low Cost                                                        |    |

|             | High Performance                                                     |    |

|             | Low Power and Low Noise                                              |    |

|             |                                                                      |    |

|             | Complete Support                                                     |    |

|             |                                                                      |    |

|             | IAL DESCRIPTION                                                      |    |

|             | ew                                                                   |    |

|             | Configuration                                                        |    |

|             | Packet Transmission                                                  |    |

|             | Packet Reception                                                     |    |

|             | s Interface                                                          |    |

|             | Memory Mode Operation                                                |    |

|             | I/O Mode Operation                                                   |    |

|             | Interrupt Request Signals                                            |    |

|             | DMA Signals                                                          |    |

| 3.3 Reset a | and Initialization                                                   | 19 |

| 3.3.1       | Reset                                                                | 19 |

|             | 3.3.1.1 External Reset, or ISA Reset                                 | 19 |

|             | 3.3.1.2 Power-Up Reset                                               | 19 |

|             | 3.3.1.3 Power-Down Reset                                             | 19 |

|             | 3.3.1.4 EEPROM Reset                                                 | 19 |

|             | 3.3.1.5 Software Initiated Reset                                     | 19 |

|             | 3.3.1.6 Hardware (HW) Standby or Suspend                             |    |

|             | 3.3.1.7 Software (SW) Suspend                                        |    |

| 3.3.2       | Allowing Time for Reset Operation                                    |    |

|             | Bus Reset Considerations                                             |    |

|             | Initialization                                                       |    |

|             | Irations with EEPROM                                                 |    |

|             | EEPROM Interface                                                     |    |

|             | EEPROM Memory Organization                                           |    |

|             | Reset Configuration Block                                            |    |

| 0.4.0       | 3.4.3.1 Reset Configuration Block Structure                          |    |

|             | 3.4.3.2 Reset Configuration Block Header                             |    |

|             | 3.4.3.3 Determining the EEPROM Type                                  |    |

|             | 3.4.3.4 Checking EEPROM for presence of Reset Configuration Block    |    |

|             | 3.4.3.5 Determining Number of Bytes in the Reset Configuration Block |    |

| 0 4 4       | • • •                                                                |    |

| 3.4.4       | Groups of Configuration Data                                         |    |

| 0.4 5       | 3.4.4.1 Group Header                                                 |    |

|             | Reset Configuration Block Checksum                                   |    |

|             | EEPROM Example                                                       |    |

| 3.4.7       | EEPROM Read-out                                                      | 24 |

|             |                                                                      |    |

| 3.4.7.1 Determining EEPROM Size                       | 24 |

|-------------------------------------------------------|----|

| 3.4.7.2 Loading Configuration Data                    | 24 |

| 3.4.8 EEPROM Read-out Completion                      | 24 |

| 3.5 Programming the EEPROM                            | 25 |

| 3.5.1 EEPROM Commands                                 |    |

| 3.5.2 EEPROM Command Execution                        | 25 |

| 3.5.3 Enabling Access to the EEPROM                   | 26 |

| 3.5.4 Writing and Erasing the EEPROM                  |    |

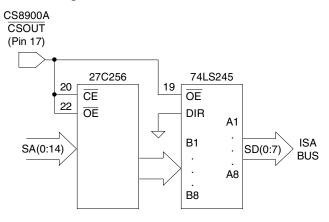

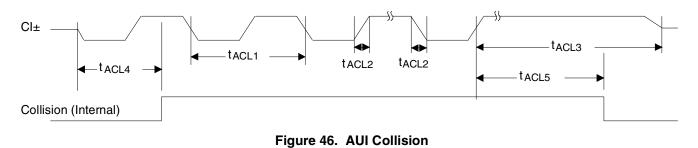

| 3.6 Boot PROM Operation                               |    |

| 3.6.1 Accessing the Boot PROM                         |    |

| 3.6.2 Configuring the CS8900A for Boot PROM Operation |    |

| 3.7 Low-Power Modes                                   |    |

| 3.7.1 Hardware Standby                                |    |

| 3.7.2 Hardware Suspend                                |    |

| 3.7.3 Software Suspend                                |    |

| 3.8 LED Outputs                                       |    |

| 3.8.1 LANLED                                          |    |

| 3.8.2 LINKLED or HC0                                  |    |

| 3.8.3 BSTATUS or HC1                                  |    |

| 3.8.4 LED Connection                                  |    |

| 3.9 Media Access Control                              |    |

| 3.9.1 Overview                                        |    |

| 3.9.1 Overview                                        |    |

| 3.9.2.1 Transmission                                  |    |

| 3.9.2.2 Reception                                     |    |

| 3.9.2.3 Enforcing Minimum Frame Size                  |    |

| 3.9.3 Transmit Error Detection and Handling           |    |

| 3.9.3.1 Loss of Carrier                               |    |

| 3.9.3.2 SQE Error                                     |    |

| 3.9.3.3 Out-of-Window (Late) Collision                |    |

| 3.9.3.4 Jabber Error                                  |    |

| 3.9.3.5 Transmit Collision                            |    |

| 3.9.3.6 Transmit Underrun                             |    |

| 3.9.4 Receive Error Detection and Handling            |    |

| 3.9.4.1 CRC Error                                     |    |

| 3.9.4.2 Runt Frame                                    |    |

| 3.9.4.3 Extra Data                                    |    |

| 3.9.4.4 Dribble Bits and Alignment Error              |    |

| 3.9.5 Media Access Management                         |    |

| 3.9.5.1 Collision Avoidance                           |    |

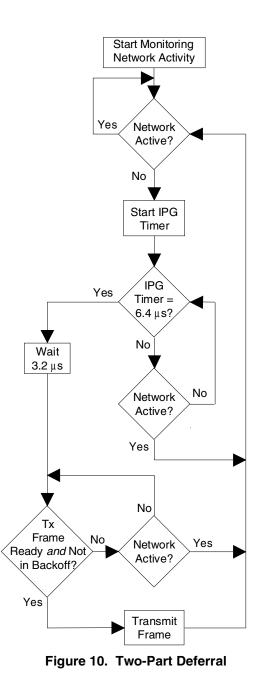

| 3.9.5.2 Two-Part Deferral                             |    |

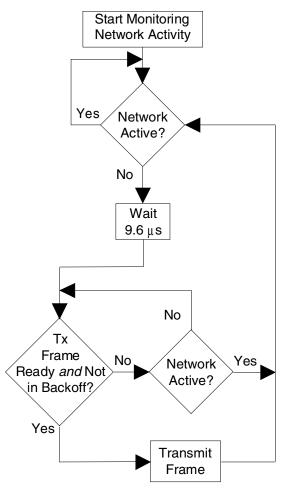

| 3.9.5.3 Simple Deferral                               |    |

| 3.9.5.4 Collision Resolution                          |    |

| 3.9.5.5 Normal Collisions                             |    |

| 3.9.5.6 Late Collisions                               |    |

| 3.9.5.7 Backoff                                       |    |

| 3.9.5.8 Standard Backoff                              |    |

| 3.9.5.9 Modified Backoff                              |    |

| 3.9.5.10 SQE Test                                     |    |

|                                                       |    |

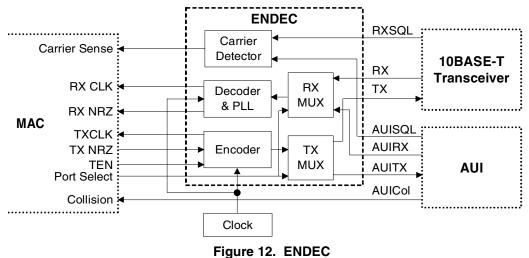

| 3.10 Encoder/Decoder (ENDEC)                          |    |

| 3.10.1 Encoder                                        |    |

| 3.10.2 Carrier Detection                              |    |

| 5.10.5 Clock and Data necovery                        | 30 |

|     |        | 3.10.4     | Interface Selection                       |    |

|-----|--------|------------|-------------------------------------------|----|

|     |        |            | 3.10.4.1 10BASE-T Only                    | 36 |

|     |        |            | 3.10.4.2 AUI Only                         |    |

|     |        |            | 3.10.4.3 Auto-Select                      | 36 |

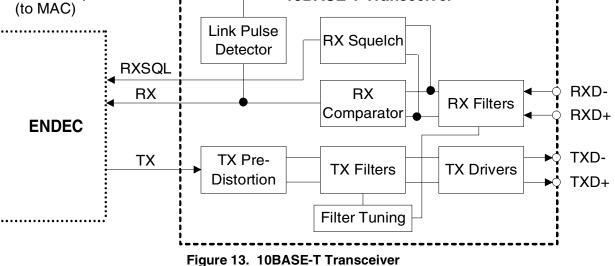

|     | 3.11   |            | E-T Transceiver                           |    |

|     |        | 3.11.1     | 10BASE-T Filters                          | 37 |

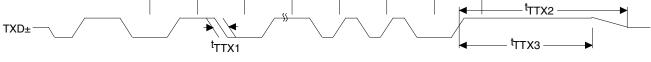

|     |        | 3.11.2     | Transmitter                               | 37 |

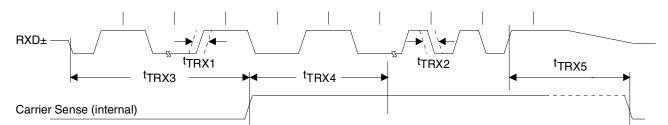

|     |        | 3.11.3     | Receiver                                  | 37 |

|     |        |            | 3.11.3.1 Squelch Circuit                  | 37 |

|     |        |            | 3.11.3.2 Extended Range                   |    |

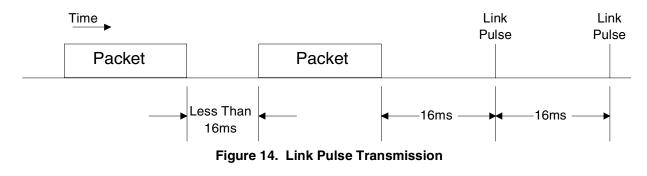

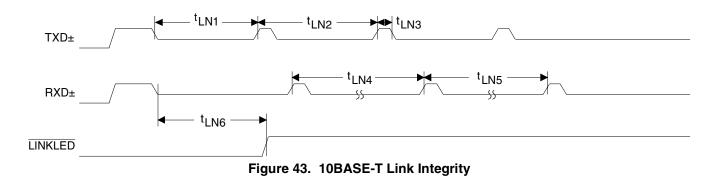

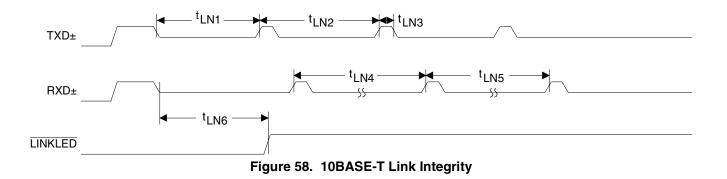

|     |        | 3.11.4     | Link Pulse Detection                      | 38 |

|     |        | 3.11.5     | Receive Polarity Detection and Correction | 38 |

|     |        | 3.11.6     | Collision Detection                       | 39 |

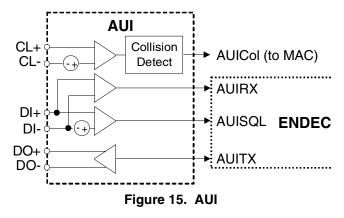

|     | 3.12   |            | nent Unit Interface (AUI)                 |    |

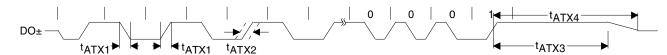

|     |        | 3.12.1     | AUI Transmitter                           | 39 |

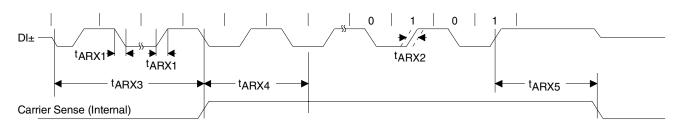

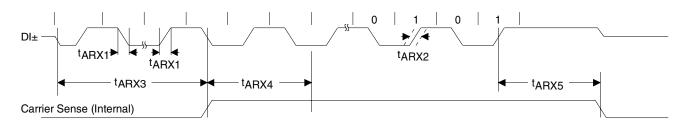

|     |        | 3.12.2     | AUI Receiver                              | 39 |

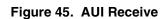

|     |        |            | Collision Detection                       |    |

|     |        |            | I Clock Oscillator                        |    |

| 4.0 |        |            | GE ARCHITECTURE                           |    |

|     | 4.1 F  | PacketPa   | age Overview                              | 41 |

|     |        | 4.1.1 Ir   | ntegrated Memory                          | 41 |

|     |        | 4.1.2 B    | Bus Interface Registers                   | 41 |

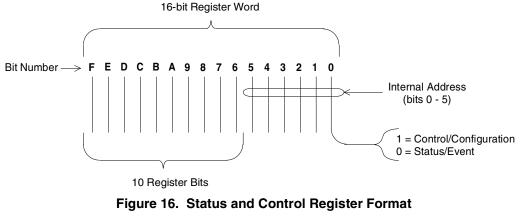

|     |        | 4.1.3 S    | Status and Control Registers              | 41 |

|     |        | 4.1.4 Ir   | nitiate Transmit Registers                | 41 |

|     |        |            | ddress Filter Registers                   |    |

|     |        | 4.1.6 F    | Receive and Transmit Frame Locations      | 41 |

|     | 4.2 F  |            | age Memory Map                            |    |

|     | 4.3 E  | Bus Inter  | face Registers                            | 44 |

|     |        |            | nd Control Registers                      |    |

|     |        | 4.4.1 C    | Configuration and Control Registers       | 49 |

|     |        |            | Status and Event Registers                |    |

|     |        | 4.4.3 S    | Status and Control Bit Definitions        | 50 |

|     |        |            | 4.4.3.1 Act-Once Bits                     | 50 |

|     |        |            | 4.4.3.2 Temporal Bits                     | 50 |

|     |        |            | 4.4.3.3 Interrupt Enable Bits and Events  | 50 |

|     |        |            | 4.4.3.4 Accept Bits                       |    |

|     |        | 4.4.4 S    | Status and Control Register Summary       | 51 |

|     | 4.5 lı | nitiate Tr | ransmit Registers                         | 69 |

|     | 4.6 A  | ddress     | Filter Registers                          | 71 |

|     | 4.7 F  | Receive a  | and Transmit Frame Locations              | 72 |

|     |        | 4.7.1 F    | Receive PacketPage Locations              | 72 |

|     |        | 4.7.2 T    | ransmit Locations                         | 72 |

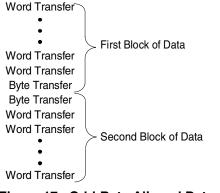

|     | 4.8 E  | Eight and  | Sixteen Bit Transfers                     | 72 |

|     |        |            | ransferring Odd-Byte-Aligned Data         |    |

|     |        |            | Random Access to CS8900A Memory           |    |

|     | 4.9 N  | lemory l   | Mode Operation                            | 73 |

|     |        |            | Accesses in Memory Mode                   |    |

|     |        |            | Configuring the CS8900A for Memory Mode   |    |

|     |        |            | Basic Memory Mode Transmit                |    |

|     |        |            | Basic Memory Mode Receive                 |    |

|     |        |            | Polling the CS8900A in Memory Mode        |    |

|     | 4.10   | I/O Spa    | ce Operation                              | 75 |

|     |        | 4.10.1     | Receive/Transmit Data Ports 0 and 1       | 75 |

| 4.10.2 TxCMD Port                                                            | 75 |

|------------------------------------------------------------------------------|----|

| 4.10.3 TxLength Port                                                         |    |

| 4.10.4 Interrupt Status Queue Port                                           |    |

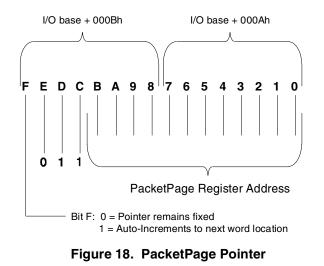

| 4.10.5 PacketPage Pointer Port                                               |    |

| 4.10.6 PacketPage Data Ports 0 and 1                                         |    |

| 4.10.7 I/O Mode Operation                                                    |    |

| 4.10.8 Basic I/O Mode Transmit                                               |    |

| 4.10.9 Basic I/O Mode Receive                                                |    |

| 4.10.10 Accessing Internal Registers                                         |    |

| 4.10.11 Polling the CS8900A in I/O Mode                                      |    |

| 5.0 OPERATION                                                                |    |

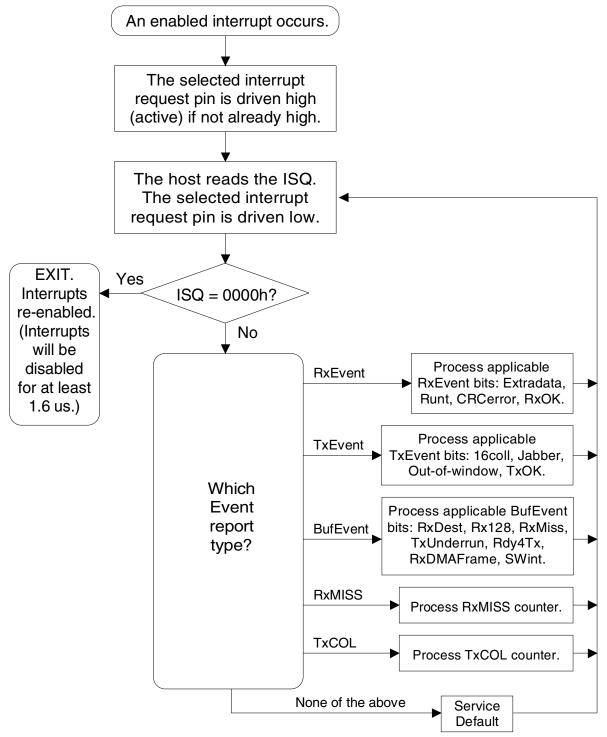

| 5.1 Managing Interrupts and Servicing the Interrupt Status Queue             |    |

| 5.2 Basic Receive Operation                                                  |    |

| 5.2.0.1 Overview                                                             |    |

| 5.2.1 Terminology: Packet, Frame, and Transfer                               |    |

| 5.2.1.1 Packet                                                               |    |

| 5.2.1.2 Frame                                                                |    |

| 5.2.1.3 Transfer                                                             |    |

| 5.2.2 Receive Configuration                                                  |    |

| 5.2.2.1 Configuring the Physical Interface                                   |    |

| 5.2.2.2 Choosing which Frame Types to Accept                                 |    |

| 5.2.2.3 Selecting which Events Cause Interrupts                              |    |

|                                                                              |    |

| 5.2.2.4 Choosing How to Transfer Frames                                      |    |

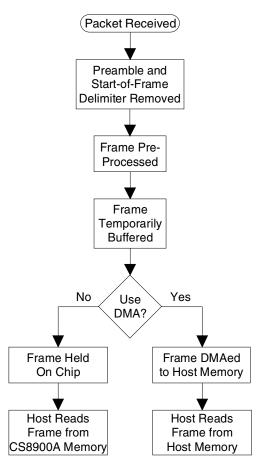

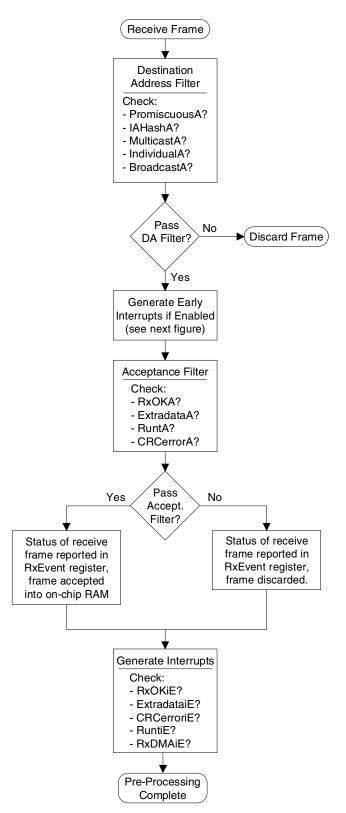

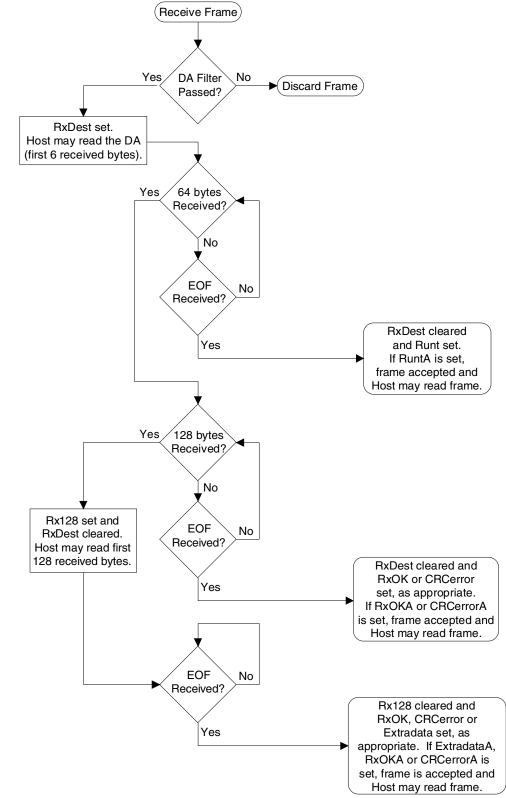

| 5.2.3 Receive Frame Pre-Processing                                           |    |

| 5.2.3.1 Destination Address Filtering<br>5.2.3.2 Early Interrupt Generation  |    |

| 5.2.3.3 Acceptance Filtering                                                 |    |

| 5.2.3.4 Normal Interrupt Generation                                          |    |

| 5.2.4 Held vs. DMAed Receive Frames                                          |    |

| 5.2.5 Buffering Held Receive Frames                                          |    |

| -                                                                            |    |

| 5.2.6 Transferring Held Receive Frames                                       |    |

| 5.2.7 Receive Frame Visibility                                               |    |

| 5.2.8 Example of Memory Mode Receive Operation                               |    |

| 5.2.9 Receive Frame Byte Counter                                             |    |

| 5.2.10 Receive Frame Address Filtering<br>5.2.10.1 Individual Address Frames |    |

|                                                                              |    |

| 5.2.10.2 Multicast Frames                                                    |    |

| 5.2.10.3 Broadcast Frames                                                    |    |

| 5.2.11 Configuring the Destination Address Filter                            |    |

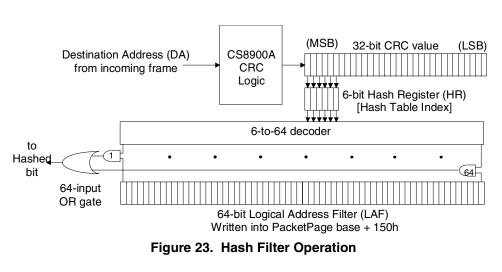

| 5.2.12 Hash Filter                                                           |    |

| 5.2.12.1 Hash Filter Operation                                               |    |

| 5.2.13 Broadcast Frame Hashing Exception                                     |    |

| 5.3 Receive DMA                                                              |    |

| 5.3.1 Overview                                                               |    |

| 5.3.2 Configuring the CS8900A for DMA Operation                              |    |

| 5.3.3 DMA Receive Buffer Size                                                |    |

| 5.3.4 Receive-DMA-Only Operation                                             |    |

| 5.3.5 Committing Buffer Space to a DMAed Frame                               |    |

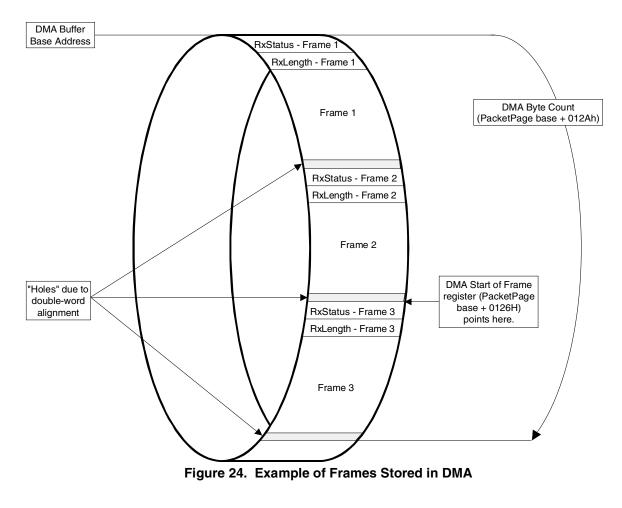

| 5.3.6 DMA Buffer Organization                                                |    |

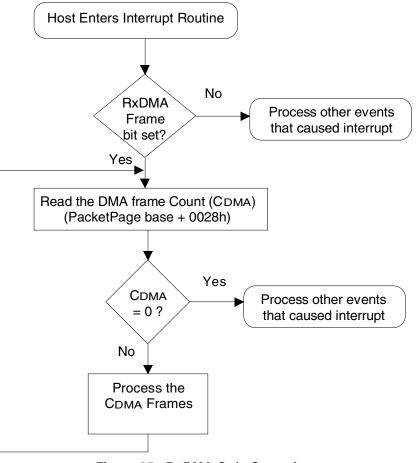

| 5.3.7 RxDMAFrame Bit                                                         |    |

| 5.3.8 Receive DMA Example Without Wrap-Around                                |    |

| 5.3.9 Receive DMA Operation for RxDMA-Only Mode                              |    |

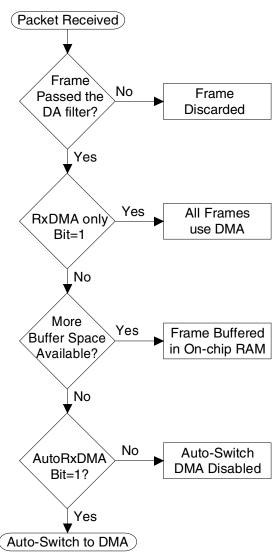

| 5.4 Auto-Switch DMA                                                          | 94 |

|      |      | 5.4.1 Overview                                      |    |

|------|------|-----------------------------------------------------|----|

|      |      | 5.4.2 Configuring the CS8900A for Auto-Switch DMA   | 94 |

|      |      | 5.4.3 Auto-Switch DMA Operation                     | 94 |

|      |      | 5.4.4 DMA Channel Speed vs. Missed Frames           | 95 |

|      |      | 5.4.5 Exit From DMA                                 |    |

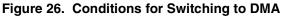

|      |      | 5.4.6 Auto-Switch DMA Example                       |    |

|      | 55   | StreamTransfer                                      |    |

|      | 0.0  | 5.5.1 Overview                                      |    |

|      |      | 5.5.2 Configuring the CS8900A for StreamTransfer    |    |

|      |      | 5.5.3 StreamTransfer Operation                      |    |

|      |      | 5.5.4 Keeping StreamTransfer Mode Active            | 00 |

|      |      | 5.5.5 Example of StreamTransfer                     |    |

|      |      | 5.5.6 Receive DMA Summary                           |    |

|      | FC   | Transmit Operation                                  |    |

|      | 0.0  |                                                     |    |

|      |      | 5.6.1 Overview                                      |    |

|      |      | 5.6.2 Transmit Configuration                        |    |

|      |      | 5.6.2.1 Configuring the Physical Interface          |    |

|      |      | 5.6.2.2 Selecting which Events Cause Interrupts1    |    |

|      |      | 5.6.3 Changing the Configuration1                   | 00 |

|      |      | 5.6.4 Enabling CRC Generation and Padding1          |    |

|      |      | 5.6.5 Individual Packet Transmission1               |    |

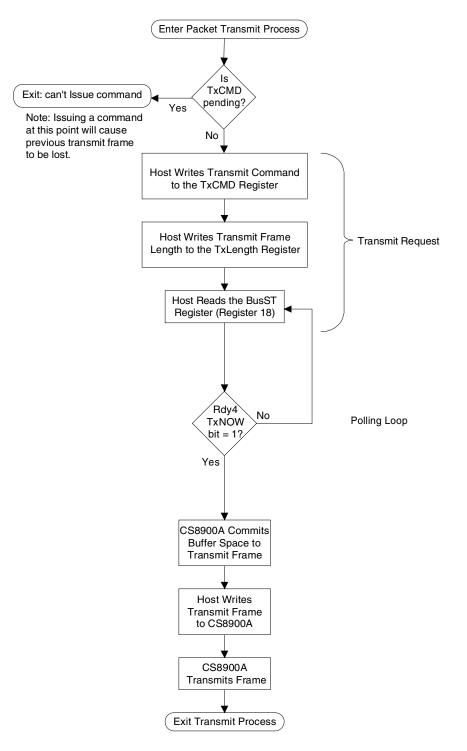

|      |      | 5.6.6 Transmit in Poll Mode1                        |    |

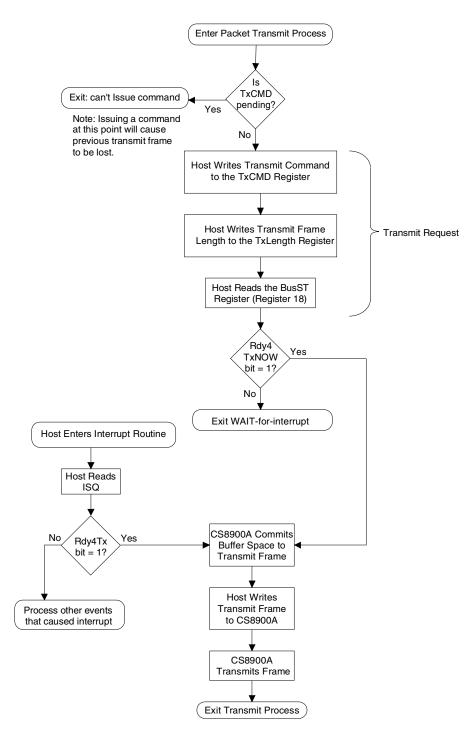

|      |      | 5.6.7 Transmit in Interrupt Mode1                   |    |

|      |      | 5.6.8 Completing Transmission1                      | 03 |

|      |      | 5.6.9 Rdy4TxNOW vs. Rdy4Tx1                         | 04 |

|      |      | 5.6.10 Committing Buffer Space to a Transmit Frame1 | 05 |

|      |      | 5.6.11 Transmit Frame Length1                       | 05 |

|      | 5.7  | Full duplex Considerations                          | 05 |

|      |      | Auto-Negotiation Considerations1                    |    |

| 6.0  | TES  | ۲1                                                  | 07 |

|      | 6.1  | TEST MODES1                                         | 07 |

|      |      | 6.1.1 Loopback & Collision Diagnostic Tests1        |    |

|      |      | 6.1.2 Internal Tests1                               |    |

|      |      | 6.1.3 External Tests1                               |    |

|      |      | 6.1.4 Loopback Tests1                               |    |

|      |      | 6.1.5 10BASE-T Loopback and Collision Tests         |    |

|      |      | 6.1.6 AUI Loopback and Collision Tests              |    |

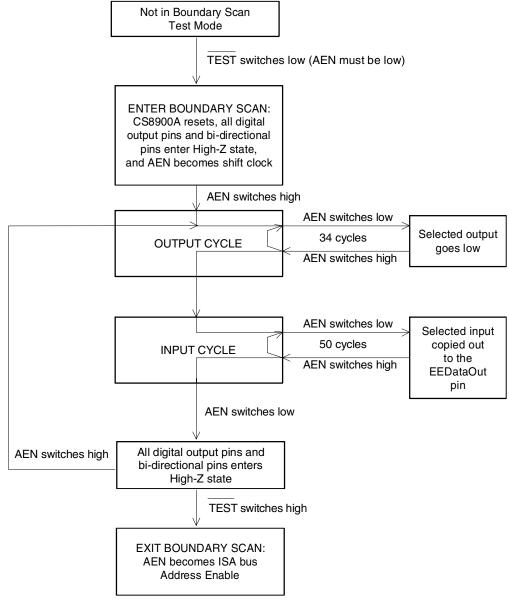

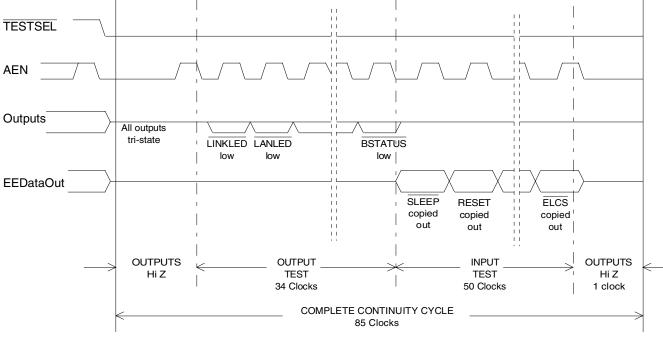

|      | 62   | Boundary Scan                                       |    |

|      | 0.2  | 6.2.1 Output Cycle1                                 |    |

|      |      | 6.2.2 Input Cycle                                   |    |

|      |      | 6.2.3 Continuity Cycle                              |    |

| 70   | сц   | ARACTERISTICS/SPECIFICATIONS - COMMERCIAL1          |    |

|      |      | ARACTERISTICS/SPECIFICATIONS - COMMERCIAL           |    |

|      |      | SICAL DIMENSIONS                                    |    |

|      |      | I OSSARY OF TERMS                                   |    |

| 10.0 |      |                                                     |    |

|      |      | Acronyms                                            |    |

|      |      | Definitions                                         |    |

|      |      | Acronyms Specific to the CS8900A                    |    |

|      |      | Definitions Specific to the CS8900A1                |    |

|      | 10.5 | Suffixes Specific to the CS8900A1                   | 38 |

| Release | Date          | Changes                                                              |  |

|---------|---------------|----------------------------------------------------------------------|--|

| PP1     | November 1997 | Preliminary Release, revision 1                                      |  |

| PP2     | December 1998 | Preliminary Release, revision 2                                      |  |

| PP3     | March 1999    | Preliminary Release, revision 3                                      |  |

| PP4     | April 2001    | Preliminary Release, revision 4                                      |  |

|         |               | Page 13: INTRQ[0:2] changed to INTRQ[03]                             |  |

|         |               | Page 41: Added bit definitions for Revisions C and D                 |  |

|         |               | Page 56: PacketPage base + 0218h changed to PacketPage base + 0128h  |  |

|         |               | Page 81: Table 19: Register 5, LRxCTL changed to Register 5, RxCTL   |  |

|         |               | Page 86: Table 23: 0410h to 011h changed to 0410h to 0411h           |  |

| F1      | January 2004  | Final Release, revision 1                                            |  |

|         |               | Page 1: Changed package option from TQFP to LQFP.                    |  |

|         |               | Page 134: Changed package drawing and from TQFP to LQFP, and updated |  |

|         |               | dimensions.                                                          |  |

#### Table 1. Revision History

#### **Contacting Cirrus Logic Support**

For all product questions and inquiries contact a Cirrus Logic Sales Representative. To find one nearest you go to <u>www.cirrus.com</u>

#### **IIMPORTANT NOTICE**

"Preliminary" product information describes products that are in production, but for which full characterization data is not yet available. Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other parts of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for reseale.

An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan. An export license and/or quota needs to be obtained from the competent authorities of the Chinese Government if any of the products or technologies described in this material is subject to the PRC Foreign Trade Law and is to be exported or taken out of the PRC.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANT ED FOR USE IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS (INCLUDING MEDICAL DEVICES, AIRCRAFT SYSTEMS OR COMPONENTS AND PERSONAL OR AUTOMOTIVE SAFETY OR SECURITY DEVICES). INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOM-ER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks or service marks of their respective owners.

I2C is a registered trademark of Philips Semiconductor. Purchase of I2C Components of Cirrus Logic, Inc., or one of its sublicensed Associated Companies conveys a license under the Philips I2C Patent Rights to use those components in a standard I2C system.

# **1.0 INTRODUCTION**

# 1.1 General Description

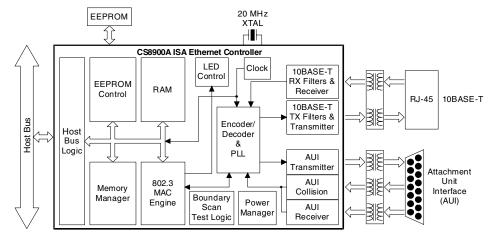

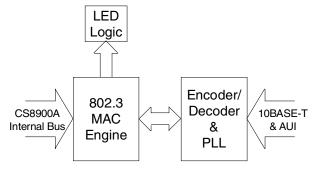

The CS8900A is a true single-chip, full-duplex, Ethernet solution, incorporating all of the analog and digital circuitry needed for a complete Ethernet circuit. Major functional blocks include: a direct ISA-bus interface; an 802.3 MAC engine; integrated buffer memory; a serial EEPROM interface; and a complete analog front end with both 10BASE-T and AUI.

## 1.1.1 General Purpose and ISA-Bus Interface

Included in the CS8900A is a direct ISA-bus interface with full 24 mA drive capability. Its configuration options include a choice of four interrupts and three DMA channels (one of each selected during initialization). In Memory Mode, it supports Standard or Ready Bus cycles without introducing additional wait states. The bus can be configured to support many microcontroller and microcomputer busses.

# 1.1.2 Integrated Memory

The CS8900A incorporates a 4-Kbyte page of on-chip memory, eliminating the cost and board area associated with external memory chips. Unlike most other Ethernet controllers, the CS8900A buffers entire transmit and receive frames on chip, eliminating the need for complex, inefficient memory management schemes. In addition, the CS8900A operates in either Memory space, I/O space, or with external DMA controllers, providing maximum design flexibility.

# 1.1.3 802.3 Ethernet MAC Engine

The CS8900A's Ethernet Media Access Control (MAC) engine is fully compliant with the IEEE 802.3 Ethernet standard (ISO/IEC 8802-3, 1993), and supports full-duplex operation. It handles all aspects of Ethernet frame transmission and reception, including: collision detection, preamble generation and detection, and CRC generation and test. Programmable MAC features include automatic retransmission on collision, and automatic padding of transmitted frames.

## 1.1.4 EEPROM Interface

The CS8900A provides a simple and efficient serial EEPROM interface that allows configuration information to be stored in an optional EEPROM, and then loaded automatically at power-up. This eliminates the need for costly and cumbersome switches and jumpers.

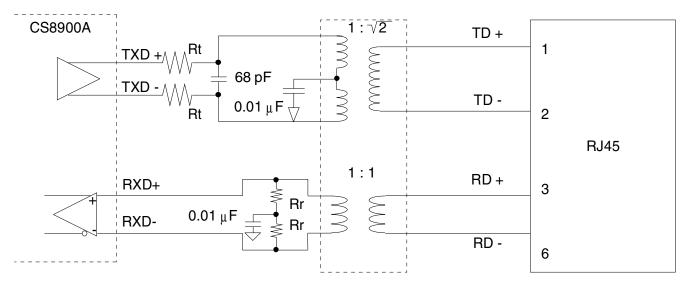

# 1.1.5 Complete Analog Front End

The CS8900A's analog front end incorporates a Manchester encoder/decoder, clock recovery circuit, 10BASE-T transceiver, and complete Attachment Unit Interface (AUI). It provides manual and automatic selection of either 10BASE-T or AUI, and offers three onchip LED drivers for link status, bus status, and Ethernet line activity.

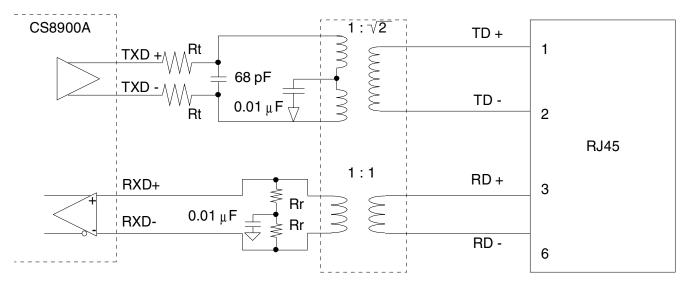

The 10BASE-T transceiver includes drivers, receivers, and analog filters, allowing direct connection to low-cost isolation transformers. It supports 100, 120, and 150  $\Omega$  shielded and unshielded cables, extended cable lengths, and automatic receive polarity reversal detection and correction.

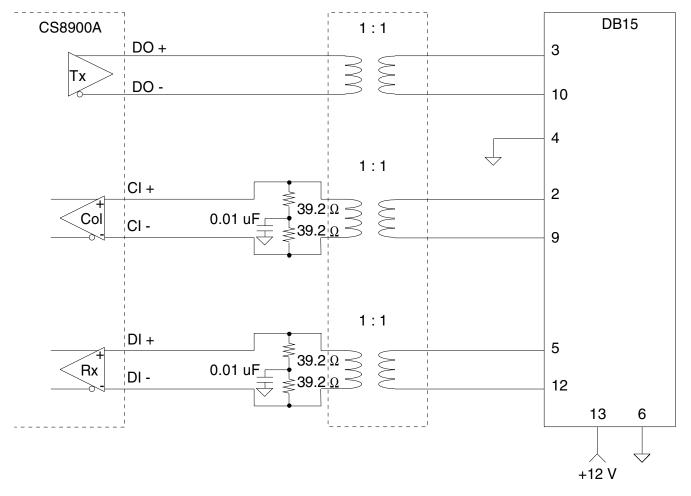

The AUI port provides a direct interface to 10BASE-2, 10BASE-5 and 10BASE-FL networks, and is capable of driving a full 50-meter AUI cable.

# **1.2 System Applications**

The CS8900A is designed to work well in either motherboard or adapter applications.

# 1.2.1 Motherboard LANs

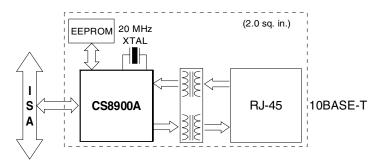

The CS8900A requires the minimum number of external components needed for a full Ethernet node. Its small-footprint package and

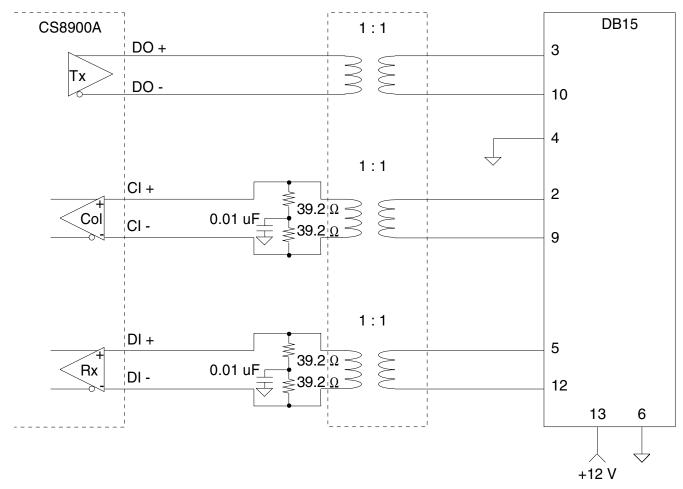

Figure 1. Complete Ethernet Motherboard Solution

high level of integration allow System Engineers to design a complete Ethernet circuit that occupies as little as 1.5 square inches of PCB area (Figure 1). In addition, the CS8900A's power-saving features and CMOS design make it a perfect fit for power-sensitive portable and desktop PCs. Motherboard design options include:

- An EEPROM can be used to store nodespecific information, such as the Ethernet Individual Address and node configuration.

- The 20 MHz crystal oscillator may be replaced by a 20 MHz clock signal.

#### 1.2.2 Ethernet Adapter Cards

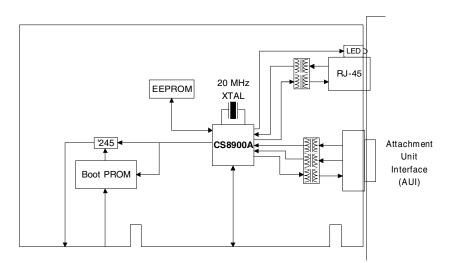

The CS8900A's highly efficient PacketPage architecture, with StreamTransfer<sup>™</sup> and Auto-

Switch DMA options, make it an excellent choice for high-performance, low-cost ISA adapter cards (Figure 2). The CS8900A's wide range of configuration options and performance features allow engineers to design Ethernet solutions that meet their particular system requirements. Adapter card design options include:

- A Boot PROM can be added to support diskless applications.

- The 10BASE-T transmitter and receiver impedance can be adjusted to support 100, 120, or 150 Ohm twisted pair cables.

- An external Latchable-Address-bus decode circuit can be added to operate the CS8900A in Upper-Memory space.

Figure 2. Full-Featured ISA Adapter Solution

On-chip LED ports can be used for either optional LEDs, or as programmable outputs.

## 1.3 Key Features and Benefits

## 1.3.1 Very Low Cost

The CS8900A is designed to provide the lowest-cost Ethernet solution available for embedded applications, portable motherboards, non-ISA bus systems and adapter cards. Cost-saving features include:

- Integrated RAM eliminates the need for expensive external memory chips.

- On-chip 10BASE-T filters allow designers to use simple isolation transformers instead of more costly filter/transformer packages.

- The serial EEPROM port, used for configuration and initialization, eliminates the need for expensive switches and jumpers.

- The CS8900A is designed to be used on a 2-layer circuit board instead of a more expensive multilayer board.

- The 8900A-based solution offers the smallest footprint available, saving valuable printed circuit board area.

- A set of certified software drivers is available at no charge, eliminating the need for costly software development.

## 1.3.2 High Performance

The CS8900A is a full 16-bit Ethernet controller designed to provide optimal system performance by minimizing time on the ISA bus and CPU overhead per frame. It offers equal or superior performance for less money when compared to other Ethernet controllers. The CS8900A's PacketPage architecture allows software to select whichever access method is best suited to each particular CPU/ISA-bus configuration. When compared to older I/O- space designs, PacketPage is faster, simpler and more efficient.

To boost performance further, the CS8900A includes several key features that increase throughput and lower CPU overhead, including:

- StreamTransfer cuts up to 87% of interrupts to the host CPU during large block transfers.

- Auto-Switch DMA allows the CS8900A to maximize throughput while minimizing missed frames.

- Early interrupts allow the host to preprocess incoming frames.

- On-chip buffering of full frames cuts the amount of host bandwidth needed to manage Ethernet traffic.

## 1.3.3 Low Power and Low Noise

For low power needs, the CS8900A offers three power-down options: Hardware Standby, Hardware Suspend, and Software Suspend. In Standby mode, the chip is powered down with the exception of the 10BASE-T receiver, which is enabled to listen for link activity. In either Hardware or Software Suspend mode, the receiver is disabled and power consumption drops to the micro-ampere range.

In addition, the CS8900A has been designed for very low noise emission, thus shortening the time required for EMI testing and qualification.

## 1.3.4 Complete Support

The CS8900A comes with a suite of software drivers for immediate use with most industry standard network operating systems. In addition, complete evaluation kits and manufacturing packages are available, significantly reducing the cost and time required to produce new Ethernet products.

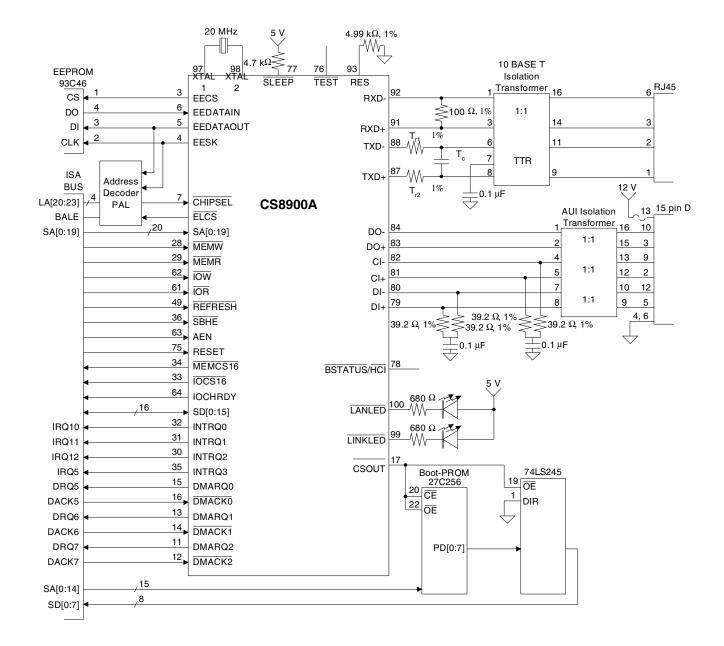

|                       | 5 Volt    | 3 Volt  |

|-----------------------|-----------|---------|

| TTR                   | 1 : 1.414 | 1 : 2.5 |

| $T_{r1}$ and $T_{r2}$ | 24.3 Ω    | 8.0 Ω   |

| T <sub>c</sub>        | 69 pF     | 560 pF  |

Figure 3. Typical ISA Bus Connection Diagram

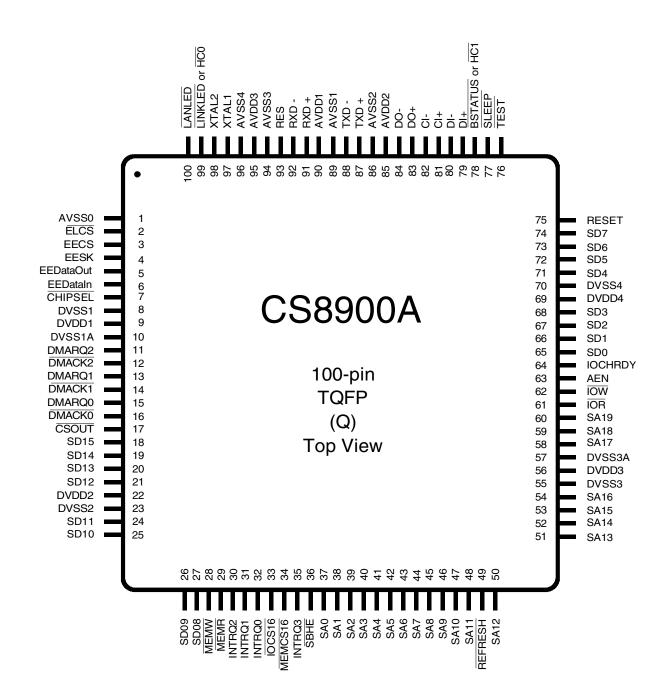

#### 2.0 PIN DESCRIPTION

#### ISA Bus Interface

#### SA[0:19] - System Address Bus, Input PINS 37-48, 50-54, 58-60.

Lower 20 bits of the 24-bit System Address Bus used to decode accesses to CS8900A I/O and Memory space, and attached Boot PROM. SA0-SA15 are used for I/O Read and Write operations. SA0-SA19 are used in conjunction with external decode logic for Memory Read and Write operations.

# SD[0:15] - System Data Bus, Bi-Directional with 3-State Output PINS 65-68, 71-74, 27-24, 21-18.

Bi-directional 16-bit System Data Bus used to transfer data between the CS8900A and the host.

#### **RESET - Reset, Input PIN 75.**

Active-high asynchronous input used to reset the CS8900A. Must be stable for at least 400 ns before the CS8900A recognizes the signal as a valid reset.

#### AEN - Address Enable, Input PIN 63.

When TEST is high, this active-high input indicates to the CS8900A that the system DMA controller has control of the ISA bus. When AEN is high, the CS8900A will not perform slave I/O space operations. When TEST is low, this pin becomes the shift clock input for the Boundary Scan Test. AEN should be inactive when performing an IO or memory access and it should be active during a DMA cycle.

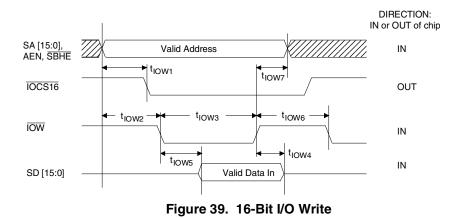

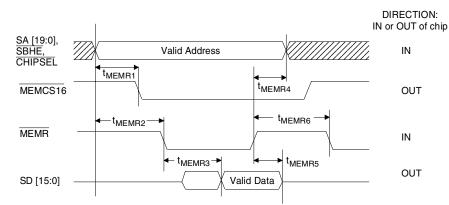

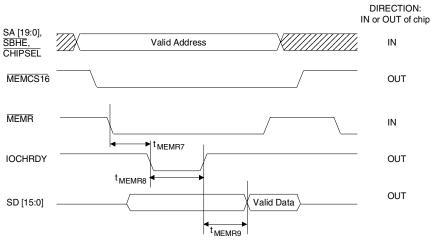

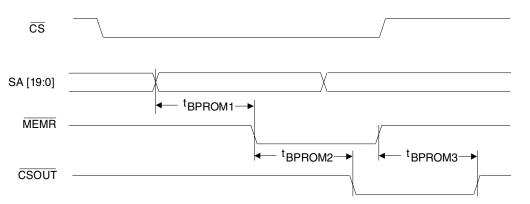

#### MEMR - Memory Read, Input PIN 29.

Active-low input indicates that the host is executing a Memory Read operation.

#### MEMW - Memory Write, Input PIN 28.

Active-low input indicates that the host is executing a Memory Write operation.

#### MEMCS16 - Memory Chip Select 16-bit, Open Drain Output PIN 34.

Open-drain, active-low output generated by the CS8900A when it recognizes an address on the ISA bus that corresponds to its assigned Memory space (CS8900A <u>must be in</u> Memory Mode with the MemoryE bit (Register 17, BusCTL, Bit A) set for MEMCS16 to go active). 3-Stated when not active.

#### **REFRESH - Refresh, Input PIN 49.**

Active-low input indicates to the CS8900A that a DRAM refresh cycle is in progress. When REFRESH is low, MEMR, MEMW, IOR, IOW, DMACK0, DMACK1, and DMACK2 are ignored.

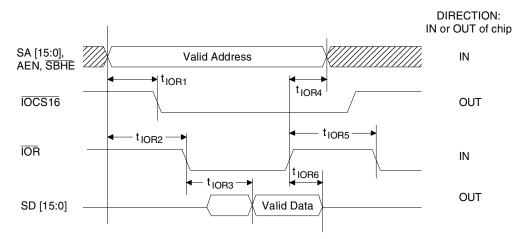

#### IOR - I/O Read, Input PIN 61.

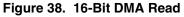

When IOR is low and a valid address is detected, the CS8900A outputs the contents of the selected 16-bit I/O register onto the System Data Bus. IOR is ignored if REFRESH is low.

#### IOW - I/O Write, Input PIN 62.

When IOW is low and a valid address is detected, the <u>CS8900A</u> writes th<u>e data on the</u> System Data Bus into the selected 16-bit I/O register. IOW is ignored if REFRESH is low.

#### IOCS16 - I/O Chip Select 16-bit, Open Drain Output PIN 33.

Open-drain, active-low output generated by the CS8900A when it recognizes an address on the ISA bus that corresponds to its assigned I/O space. 3-Stated when not active.

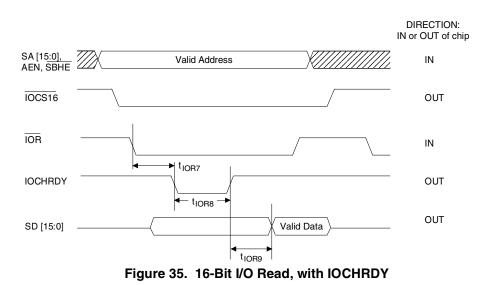

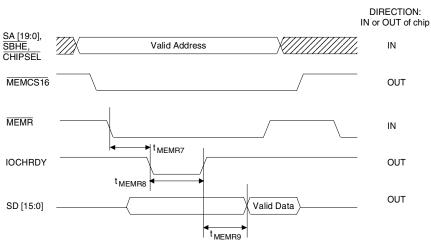

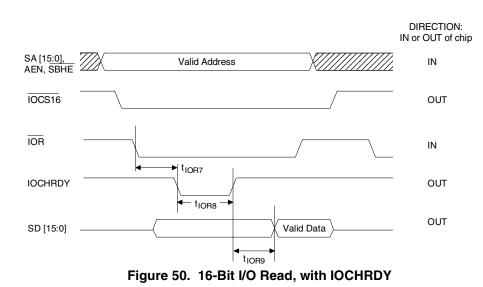

#### IOCHRDY - I/O Channel Ready, Open Drain Output PIN 64.

When driven low, this open-drain, active-high output extends I/O Read and Memory Read cycles to the CS8900A. This output is functional when the IOCHRDYE bit in the Bus Control register (Register 17) is clear. This pin is always 3-Stated when the IOCHRDYE bit is set.

#### SBHE - System Bus High Enable, Input PIN 36.

Active-low input indicates a data transfer on the high byte of the System Data Bus (SD8-SD15). After a hardware or a software reset, the CS8900A will be in 8-bit mode. Provide a HIGH to LOW and then LOW to HIGH transition on the SBHE signal before any 16-bit IO or memory access is done to the CS8900A.

#### INTRQ[0:3] - Interrupt Request, 3-State PINS 30-32, 35.

Active-high output indicates the presence of an interrupt event. Interrupt Request goes low once the Interrupt Status Queue (ISQ) is read as all 0's. Only one Interrupt Request output is used (one is selected during configuration). All non-selected Interrupt Request outputs are placed in a high-impedance state. (Section 3.2 on page 18 and Section 5.1 on page 78.)

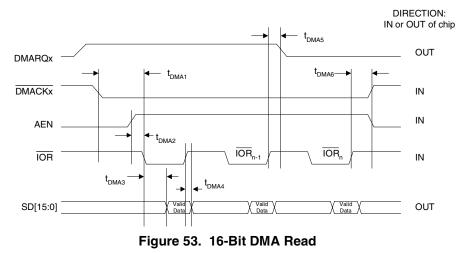

#### DMARQ[0:2] - DMA Request, 3-State PINS 11, 13, and 15.

Active-high, 3-Stateable output used by the CS8900A to request a DMA transfer. Only one DMA Request output is used (one is selected during configuration). All non-selected DMA Request outputs are placed in a high-impedance state.

#### DMACK[0:2] - DMA Acknowledge, Input PINS 12, 14, and 16.

Active-low input indicates acknowledgment by the host of the corresponding DMA Request output.

#### CHIPSEL - Chip Select, Input PIN 7.

Active-low input generated by external Latchable Address bus decode logic when a valid memory address is present on the ISA bus. If Memory Mode operation is not needed, CHIPSEL should be tied low. The CHIPSEL is ignored for IO and DMA mode of the CS8900A.

#### EEPROM and Boot PROM Interface

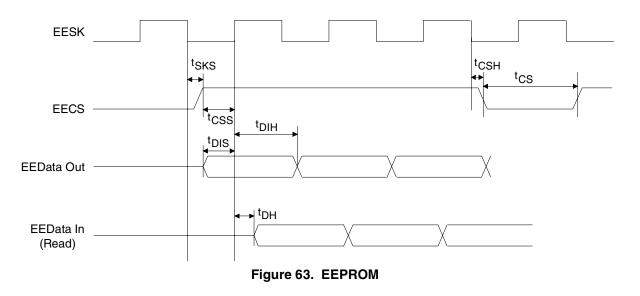

#### EESK - EEPROM Serial Clock, PIN 4.

Serial clock used to clock data into or out of the EEPROM.

#### EECS - EEPROM Chip Select, PIN 3.

Active-high output used to select the EEPROM.

#### EEDataIn - EEPROM Data In, Input Internal Weak Pullup PIN 6.

Serial input used to receive data from the EEPROM. Connects to the DO pin on the EEPROM. EEDataIn is also used to sense the presence of the EEPROM.

#### ELCS - External Logic Chip Select, Internal Weak Pullup PIN 2.

Bi-directional signal used to configure external Latchable Address (LA) decode logic. If external LA decode logic is not needed, ELCS should be tied low.

#### EEDataOut - EEPROM Data Out, PIN 5.

Serial output use<u>d to send</u> data to the EEPROM. Connects to the DI pin on the EEPROM. When TEST is low, this pin becomes the output for the Boundary Scan Test.

#### CSOUT - Chip Select for External Boot PROM, PIN 17.

Active-low output used to select an external Boot PROM when the CS8900A decodes a valid Boot PROM memory address.

#### 10BASE-T Interface

#### TXD+/TXD- - 10BASE-T Transmit, Differential Output Pair PINS 87 and 88.

Differential output pair drives 10 Mb/s Manchester-encoded data to the 10BASE-T transmit pair.

#### RXD+/RXD- - 10BASE-T Receive, Differential Input Pair PINS 91 and 92.

Differential input pair receives 10 Mb/s Manchester-encoded data from the 10BASE-T receive pair.

Attachment Unit Interface (AUI)

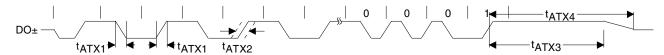

#### DO+/DO- - AUI Data Out, Differential Output Pair PINS 83 and 84.

Differential output pair drives 10 Mb/s Manchester-encoded data to the AUI transmit pair.

#### DI+/DI- - AUI Data In, Differential Input Pair PINS 79 and 80.

Differential input pair receives 10 Mb/s Manchester-encoded data from the AUI receive pair.

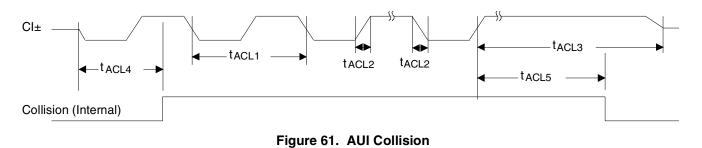

#### CI+/CI- - AUI Collision In, Differential Input Pair PINS 81 and 82.

Differential input pair connects to the AUI collision pair. A collision is indicated by the presence of a 10 MHz  $\pm$  15% signal with duty cycle no worse than 60/40.

#### General Pins

#### XTAL[1:2] - Crystal, Input/Output PINS 97 and 98.

A 20 MHz crystal should be connected across these pins. If a crystal is not used, a 20 MHz signal should be connected to XTAL1 and XTAL2 should be left open. (See Section 7.3 on page 112 and Section 7.7 on page 122.)

#### SLEEP - Hardware Sleep, Input Internal Weak Pullup PIN 77.

Active-low input used to enable the two hardware sleep modes: Hardware Suspend and Hardware Standby. (See Section 3.7 on page 27.)

# LINKLED or HC0 - Link Good LED or Host Controlled Output 0, Open Drain Output PIN 99.

When the HCE0 bit of the Self Control register (Register 15) is clear, this active-low output is low when the CS8900A detects the presence of valid link pulses. When the HC0E bit is set, the host may drive this pin low by setting the HCBO in the Self Control register.

#### BSTATUS or HC1 - Bus Status or Host Controlled Output 1, Open Drain Output PIN 78.

When the HC1E bit of the Self Control register (Register 15) is clear, this active-low output is low when receive activity causes an ISA bus access. When the HC1E bit is set, the host may drive this pin low by setting the HCB1 in the Self Control register.

#### LANLED - LAN Activity LED, Open Drain Output PIN 100.

During normal operation, this active-low output goes low for 6 ms whenever there is a receive packet, a transmit packet, or a collision. During Hardware Standby mode, this output is driven low when the receiver detects network activity.

#### TEST - Test Enable, Input Internal Weak Pullup PIN 76.

Active-low input used to put the CS8900A in Boundary Scan Test mode. For normal operation, this pin should be high.

#### **RES - Reference Resistor, Input PIN 93.**

This input should be connected to a 4.99K $\Omega$  ± 1% resistor needed for biasing of internal analog circuits.

#### DVDD[1:4] - Digital Power, Power PINS 9, 22, 56, and 69.

Provides 5 V  $\pm$  5% power to the digital circuits of the CS8900A.

# DVSS[1:4} and DVSS1A, DVSS3A - Digital Ground, Ground PINS 8, 10, 23, 55, 57, and 70.

Provides ground reference (0 V) to the digital circuits of the CS8900A.

#### AVDD[1:3] - Analog Power, Power PINS 90, 85, and 95.

Provides 5 V  $\pm$  5% power to the analog circuits of the CS8900A.

#### AVSS[0:4] - Analog Ground, Ground PINS 1, 89, 86, 94, 96.

Provide ground reference (0 V) to the analog circuits of the CS8900A.

## 3.0 FUNCTIONAL DESCRIPTION

#### 3.1 Overview

During normal operation, the CS8900A performs two basic functions: Ethernet packet transmission and reception. Before transmission or reception is possible, the CS8900A must be configured.

## 3.1.1 Configuration

The CS8900A must be configured for packet transmission and reception at power-up or reset. Various parameters must be written into its internal Configuration and Control registers such as Memory Base Address; Ethernet Physical Address; what frame types to receive; and which media interface to use. Configuration data can either be written to the CS8900A by the host (across the ISA bus), or loaded automatically from an external EE-PROM. Operation can begin after configuration is complete.

Section 3.3 on page 19 and Section 3.4 on page 21 describe the configuration process in detail. Section 4.4 on page 49 provides a detailed description of the bits in the Configuration and Control Registers.

## 3.1.2 Packet Transmission

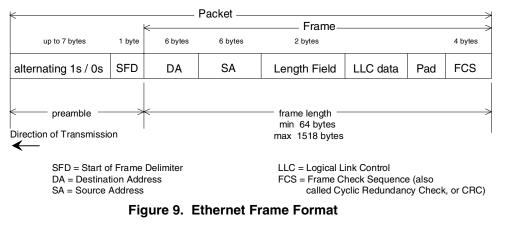

Packet transmission occurs in two phases. In the first phase, the host moves the Ethernet frame into the CS8900A's buffer memory. The first phase begins with the host issuing a Transmit Command. This informs the CS8900A that a frame is to be transmitted and tells the chip when to start transmission (i.e. after 5, 381, 1021 or all bytes have been transferred) and how the frame should be sent (i.e. with or without CRC, with or without pad bits, etc.). The Host follows the Transmit Command with the Transmit Length, indicating how much buffer space is required. When buffer space is available, the host writes the Ethernet frame into the CS8900A's internal memory, either as a Memory or I/O space operation.

In the second phase of transmission, the CS8900A converts the frame into an Ethernet packet then transmits it onto the network. The second phase begins with the CS8900A transmitting the preamble and Start-of-Frame delimiter as soon as the proper number of bytes has been transferred into its transmit buffer (5, 381, 1021 bytes or full frame, depending on configuration). The preamble and Start-of-Frame delimiter are followed by the Destination Address, Source Address, Length field and LLC data (all supplied by the host). If the frame is less than 64 bytes, including CRC, the CS8900A adds pad bits if configured to do so. Finally, the CS8900A appends the proper 32bit CRC value.

The Section 5.6 on page 99 provides a detailed description of packet transmission.

## 3.1.3 Packet Reception

Like packet transmission, packet reception occurs in two phases. In the first phase, the CS8900A receives an Ethernet packet and stores it in on-chip memory. The first phase of packet reception begins with the receive frame passing through the analog front end and Manchester decoder where Manchester data is converted to NRZ data. Next, the preamble and Start-of-Frame delimiter are stripped off and the receive frame is sent through the address filter. If the frame's Destination Address matches the criteria programmed into the address filter, the packet is stored in the CS8900A's internal memory. The CS8900A then checks the CRC, and depending on the configuration, informs the processor that a frame has been received.

In the second phase, the host transfers the receive frame across the ISA bus and into host memory. Receive frames can be transferred

as Memory space operations, I/O space operations, or as DMA operations using host DMA. Also, the CS8900A provides the capability to switch between Memory or I/O operation and DMA operation by using Auto-Switch DMA and StreamTransfer.

The Section 5.2 on page 78 through Section 5.5 on page 96 provide a detailed description of packet reception.

#### 3.2 ISA Bus Interface

The CS8900A provides a direct interface to ISA buses running at clock rates from 8 to 11 MHz. Its on-chip bus drivers are capable of delivering 24 mA of drive current, allowing the CS8900A to drive the ISA bus directly, without added external "glue logic".

The CS8900A is optimized for 16-bit data transfers, operating in either Memory space, I/O space, or as a DMA slave.

Note that ISA-bus operation below 8 MHz should use the CS8900A's Receive DMA mode to minimize missed frames. See Section 5.3 on page 90 for a description of Receive DMA operation.

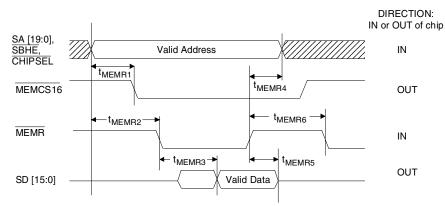

## 3.2.1 Memory Mode Operation

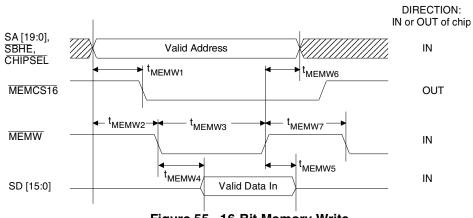

When configured for Memory Mode operation, the CS8900A's internal registers and frame buffers are mapped into a contiguous 4-Kbyte block of host memory, providing the host with direct access to the CS8900A's internal registers and frame buffers. The host initiates Read operations by driving the MEMR pin low and Write operations by driving the MEMW pin low.

For additional information about Memory Mode, see Section 4.9 on page 73.

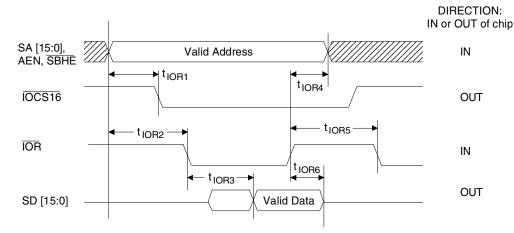

## 3.2.2 I/O Mode Operation

When configured for I/O Mode operation, the CS8900A is accessed through eight, 16-bit I/O ports that are mapped into sixteen contiguous

I/O locations in the host system's I/O space. I/O Mode is the default configuration for the CS8900A and is always enabled.

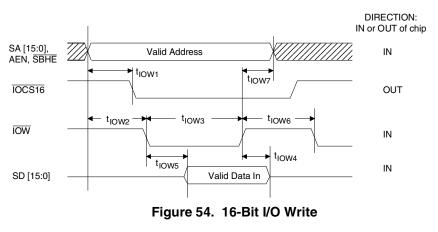

For an I/O Read or Write operation, the AEN pin must be low, and the 16-bit I/O address on the ISA System Address bus (SA0 - SA15) must match the address space of the CS8900A. For a Read, IOR must be low, and for a Write, IOW must be low.

For additional information about I/O Mode, see Section 4.10 on page 75.

## 3.2.3 Interrupt Request Signals

The CS8900A has four interrupt request output pins that can be connected directly to any four of the ISA bus Interrupt Request signals. Only one interrupt output is used at a time. It is selected during initialization by writing the interrupt number (0 to 3) into PacketPage Memory base + 0022h. Unused interrupt request pins are placed in a high-impedance state. The selected interrupt request pin goes high when an enabled interrupt is triggered. The pin goes low after the Interrupt Status Queue (ISQ) is read as all 0's (see Section 5.1 on page 78 for a description of the ISQ).

Table 2 presents one possible way of connecting the interrupt request pins to the ISA bus that utilizes commonly available interrupts and facilitates board layout.

| CS8900A Interrupt<br>Request Pin | ISA Bus<br>Interrupt | PacketPage<br>base + 0022h |

|----------------------------------|----------------------|----------------------------|

| INTRQ3 (Pin 35)                  | IRQ5                 | 0003h                      |

| INTRQ0 (Pin 32)                  | IRQ10                | 0000h                      |

| INTRQ1 (Pin 31)                  | IRQ11                | 0001h                      |

| INTRQ2 (Pin 30)                  | IRQ12                | 0002h                      |

Table 2. Interrupt Assignments

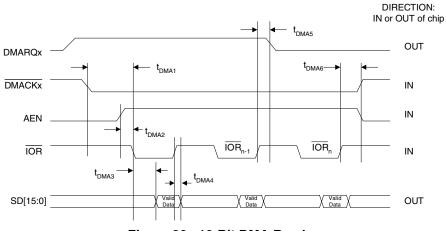

#### 3.2.4 DMA Signals

The CS8900A interfaces directly to the host DMA controller to provide DMA transfers of receive frames from CS8900A memory to host

memory. The CS8900A has three pairs of DMA pins that can be connected directly to the three 16-bit DMA channels of the ISA bus. Only one DMA channel is used at a time. It is selected during initialization by writing the number of the desired channel (0, 1 or 2) into PacketPage Memory base + 0024h. Unused DMA pins are placed in a high-impedance state. The selected DMA request pin goes high when the CS8900A has received frames to transfer to the host memory via DMA. If the DMABurst bit (register 17, BusCTL, Bit B) is clear, the pin goes low after the DMA operation is complete. If the DMABurst bit is set, the pin goes low 32 µs after the start of a DMA transfer.

The DMA pin pairs are arranged on the CS8900A to facilitate board layout. Crystal recommends the configuration in Table 3 when connecting these pins to the ISA bus.

| CS8900A DMA<br>Signal (Pin #) | ISA DMA<br>Signal | PacketPage<br>base + 0024h |

|-------------------------------|-------------------|----------------------------|

| DMARQ0 (Pin 15)               | DRQ5              | 0000h                      |

| DMACK0 (Pin 16)               | DACK5             |                            |

| DMARQ1 (Pin 13)               | DRQ6              | 0001h                      |

| DMACK1 (Pin 14)               | DACK6             |                            |

| DMARQ2 (Pin 11)               | DRQ7              | 0002h                      |

| DMACK2 (Pin 12)               | DACK7             |                            |

Table 3. DMA Assignments

For a description of DMA mode, see Section 5.3 on page 90.

#### 3.3 Reset and Initialization

#### 3.3.1 Reset

Seven different conditions cause the CS8900A to reset its internal registers and circuits.

#### 3.3.1.1 External Reset, or ISA Reset

There is a chip-wide reset whenever the RE-SET pin is high for at least 400 ns. During a

chip-wide reset, all circuitry and registers in the CS8900A are reset.

## 3.3.1.2 Power-Up Reset

When power is applied, the CS8900A maintains reset until the voltage at the supply pins reaches approximately 2.5 V. The CS8900A comes out of reset once Vcc is greater than approximately 2.5 V *and* the crystal oscillator has stabilized.

## 3.3.1.3 Power-Down Reset

If the supply voltage drops below approximately 2.5 V, there is a chip-wide reset. The CS8900A comes out of reset once the power supply returns to a level greater than approximately 2.5 V *and* the crystal oscillator has stabilized.

## 3.3.1.4 EEPROM Reset

There is a chip-wide reset if an EEPROM checksum error is detected (see Section 3.4 on page 21).

## 3.3.1.5 Software Initiated Reset

There is a chip-wide reset whenever the RE-SET bit (Register 15, SelfCTL, Bit 6) is set.

## 3.3.1.6 Hardware (HW) Standby or Suspend

The CS8900A goes though a chip-wide reset whenever it enters or exits either HW Standby mode or HW Suspend mode (see Section 3.7 on page 27 for more information about HW Standby and Suspend).

## 3.3.1.7 Software (SW) Suspend

Whenever the CS8900A enters SW Suspend mode, all registers and circuits are reset except for the ISA I/O Base Address register (located at PacketPage base + 0020h) and the SelfCTL register (Register 15). Upon exit, there is a chip-wide reset (see Section 3.7 on page 27 for more information about SW Suspend).

## 3.3.2 Allowing Time for Reset Operation

After a reset, the CS8900A goes through a self configuration. This includes calibrating on-chip analog circuitry, and reading EEPROM for validity and configuration. Time required for the reset calibration is typically 10 ms. Software drivers should not access registers internal to the CS8900A during this time. When calibration is done, bit INITD in the Self Status Register (register 16) is set indicating that initialization is complete, and the SIBUSY bit in the same register is cleared indicating the EE-PROM is no longer being read or programmed.

#### 3.3.3 Bus Reset Considerations

After reset, the CS8900A packet page pointer register (IObase+0Ah) is set to 3000h. The 3000h value can be used as part of the CS8900A signature when the system scans for the CS8900A. See Section 4.10 on page 75.

After a reset, the ISA bus outputs INTRx and DMARQx are 3-Stated, thus avoiding any interrupt or DMA channel conflicts on the ISA bus at power-up time.

## 3.3.4 Initialization

After each reset (except EEPROM Reset), the CS8900A checks the sense of the EEDataIn pin to see if an external EEPROM is present. If EEDI is high, an EEPROM is present and the CS8900A automatically loads the configuration data stored in the EEPROM into its internal registers (see next section). If EEDI is low, an EEPROM is not present and the CS8900A comes out of reset with the default configuration shown in Table 4.

A low-cost serial EEPROM can be used to store configuration information that is automatically loaded into the CS8900A after each reset (except EEPROM reset). The use of an EEPROM is optional.

The CS8900A operates with any of six standard EEPROM's shown in Table 5.

| PacketPage<br>Address | Register<br>Contents   | Register Descriptions        |

|-----------------------|------------------------|------------------------------|

| 0020h                 | 0300h                  | I/O Base Address*            |

| 0022h                 | XXXX XXXX<br>XXXX X100 | Interrupt Number             |

| 0024h                 | XXXX XXXX<br>XXXX XX11 | DMA Channel                  |

| 0026h                 | 0000h                  | DMA Start of Frame<br>Offset |

| 0028h                 | X000h                  | DMA Frame Count              |

| 002Ah                 | 0000h                  | DMA Byte Count               |

| 002Ch                 | XXX0 0000h             | Memory Base Address          |

| 0030h                 | XXX0 0000h             | Boot PROM Base<br>Address    |

| 0034h                 | XXX0 0000h             | Boot PROM Address<br>Mask    |

| 0102h                 | 0003h                  | Register 3 - RxCFG           |

| 0104h                 | 0005h                  | Register 5 - RxCTL           |

| 0106h                 | 0007h                  | Register 7 - TxCFG           |

| 0108h                 | 0009h                  | Register 9 - TxCMD           |

| 010Ah                 | 000Bh                  | Register B - BufCFG          |

| 010Ch                 | Undefined              | Reserved                     |

| 010Eh                 | Undefined              | Reserved                     |

| 0110h                 | Undefined              | Reserved                     |

| 0112h                 | 00013h                 | Register 13 - LineCTL        |

| 0114h                 | 0015h                  | Register 15 - SelfCTL        |

| 0116h                 | 0017h                  | Register 17 - BusCTL         |

| 0118h                 | 0019h                  | Register 19 - TestCTL        |

\* I/O base address is unaffected by Software Suspend mode. Table 4. Default Configuration

| EEPROM Type           | Size (16-bit words) |

|-----------------------|---------------------|

| 'C46 (non-sequential) | 64                  |

| 'CS46 (sequential)    | 64                  |

| 'C56 (non-sequential) | 128                 |

| 'CS56 (sequential)    | 128                 |

| 'C66 (non-sequential) | 256                 |

| 'CS66 (sequential)    | 256                 |

Table 5. Supported EEPROM Types

#### 3.4 Configurations with EEPROM

## 3.4.1 EEPROM Interface

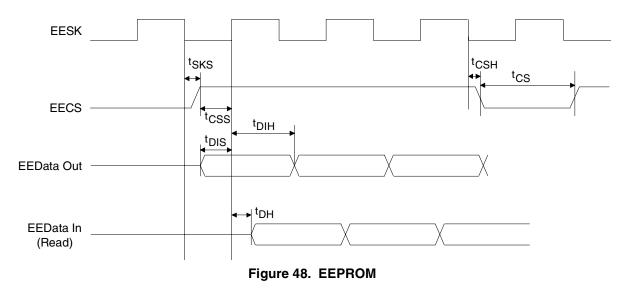

The interface to the EEPROM consists of the four signals shown in Table 6.

| CS8900A Pin<br>(Pin #) | CS8900A Function                     | EEPROM<br>Pin |

|------------------------|--------------------------------------|---------------|

| EECS (Pin 3)           | EEPROM Chip Select                   | Chip Select   |

| EESK (PIN 4)           | 1 MHz EEPROM<br>Serial Clock output  | Clock         |

| EEDO (Pin 5)           | EEPROM Data Out<br>(data to EEPROM)  | Data In       |

| EEDI (Pin 6)           | EEPROM Data in<br>(data from EEPROM) | Data Out      |

Table 6. EEPROM Interface

#### 3.4.2 EEPROM Memory Organization

If an EEPROM is used to store initial configuration information for the CS8900A, the EE-PROM is organized in one or more blocks of 16-bit words. The first block in EEPROM, referred to as the Configuration Block, is used to configure the CS8900A after reset. An example of a typical Configuration Block is shown in Table 7. Additional blocks containing user data may be stored in the EEPROM. However, the Configuration Block must always start at address 00h and be stored in contiguous memory locations.

#### 3.4.3 Reset Configuration Block

The first block in EEPROM, referred to as the Reset Configuration Block, is used to automatically program the CS8900A with an initial configuration after a reset. Additional user data may also be stored in the EEPROM if space is available. The additional data are stored as 16-bit words and can occupy any EEPROM address space beginning immediately after the end of the Reset Configuration Block up to address 7Fh, depending on EEPROM size. This additional data can only be accessed through software control (refer to Section 3.5 on page 25 for more information on accessing

| Word Address                                            | Value    | Description                                                                                                                                                                                                                                                         |  |  |

|---------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| FIRST WORD in DA                                        | TA BLOCK |                                                                                                                                                                                                                                                                     |  |  |

| 00h A120h                                               |          | Configuration Block Header.<br>The high byte, A1h, indicates a 'C46 EEPROM is attached. The Link Byte,<br>20h, indicates the number of bytes to be used in this block of configuration<br>data.                                                                     |  |  |

| FIRST GROUP of W                                        | 'ORDS    | · ·                                                                                                                                                                                                                                                                 |  |  |

| 01h                                                     | 2020h    | Group Header for first group of words.<br>Three words to be loaded, beginning at 0020h in PacketPage memory.                                                                                                                                                        |  |  |

| 02h                                                     | 0300h    | I/O Base Address                                                                                                                                                                                                                                                    |  |  |

| 03h                                                     | 0003h    | Interrupt Number                                                                                                                                                                                                                                                    |  |  |

| 04h                                                     | 0001h    | DMA Channel Number                                                                                                                                                                                                                                                  |  |  |

| SECOND GROUP of                                         | f WORDS  |                                                                                                                                                                                                                                                                     |  |  |

| 05h                                                     | 502Ch    | Group Header for second group of words.<br>Six words to be loaded, beginning at 002Ch in PacketPage memory.                                                                                                                                                         |  |  |

| 06h                                                     | E000h    | Memory Base Address - low word                                                                                                                                                                                                                                      |  |  |

| 07                                                      | 000Fh    | Memory Base Address - high word                                                                                                                                                                                                                                     |  |  |

| 08h                                                     | 0000h    | Boot PROM Base Address - low word                                                                                                                                                                                                                                   |  |  |

| 09h                                                     | 000Dh    | Boot PROM Base Address - high word                                                                                                                                                                                                                                  |  |  |

| 0Ah                                                     | C000h    | Boot PROM Address Mask - low word                                                                                                                                                                                                                                   |  |  |

| 0Bh                                                     | 000Fh    | Boot PROM Address Mask - high word                                                                                                                                                                                                                                  |  |  |

| THIRD GROUP of W                                        | /ORDS    |                                                                                                                                                                                                                                                                     |  |  |

| 0Ch                                                     | 2158h    | Group Header for third group of words.<br>Three words to be loaded, beginning at 0158 in PacketPage memory.                                                                                                                                                         |  |  |

| 0Dh                                                     | 0010h    | Individual Address - Octet 0 and 1                                                                                                                                                                                                                                  |  |  |

| 0Eh                                                     | 0000h    | Individual Address - Octet 2 and 3                                                                                                                                                                                                                                  |  |  |

| 0Fh                                                     | 0000h    | Individual Address - Octet 4 and 5                                                                                                                                                                                                                                  |  |  |

| CHECKSUM Value                                          |          | · ·                                                                                                                                                                                                                                                                 |  |  |

| sum includes word addres<br>the bytes is D8h, resulting |          | The high byte, 28h, is the Checksum Value. In this example, the check-<br>sum includes word addresses 00h through 0Fh. The hexadecimal sum of<br>the bytes is D8h, resulting in a 2's complement of 28h. The low byte, 00h,<br>provides a pad to the word boundary. |  |  |

\* FFFFh is a special code indicating that there are no more words in the EEPROM.

#### Table 7. EEPROM Configuration Block Example

the EEPROM). Address space 80h to AFh is reserved.

#### 3.4.3.1 Reset Configuration Block Structure

The Reset Configuration Block is a block of contiguous 16-bit words starting at EEPROM address 00h. It can be divided into three logical sections: a header, one or more groups of configuration data words, and a checksum value. All of the words in the Reset Configuration Block are read sequentially by the CS8900A after each reset, starting with the header and ending with the checksum. Each group of configuration data is used to program a PacketPage register (or set of PacketPage registers in some cases) with an initial non-default value.

#### 3.4.3.2 Reset Configuration Block Header

The header (first word of the block located at EEPROM address 00h) specifies the type of EEPROM used, whether or not a Reset Configuration block is present, and if so, how many

bytes of configuration data are stored in the Reset Configuration Block.

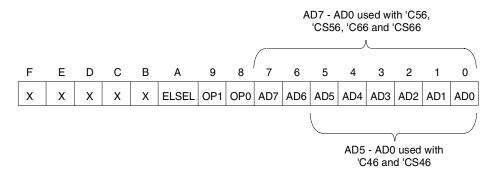

## 3.4.3.3 Determining the EEPROM Type

The LSB of the high byte of the header indicates the type of EEPROM attached: sequential or non-sequential. An LSB of 0 (XXXX-XXX0) indicates a sequential EEPROM. An LSB of 1 (XXXX-XX1) indicates a non-sequential EEPROM. The CS8900A works equally well with either type of EEPROM. The CS8900A will automatically generate sequential addresses while reading the Reset Configuration Block if a non-sequential EEPROM is used.

# 3.4.3.4 Checking EEPROM for presence of Reset Configuration Block

The read-out of either a binary 101X-XXX0 or 101X-XXX1 (X = do not care) from the high byte of the header indicates the presence of configuration data. Any other readout value terminates initialization from the EEPROM. If an EEPROM is attached but not used for configuration, Crystal recommends that the high byte of the first word be programmed with 00h in order to ensure that the CS8900A will not attempt to read configuration data from the EE-PROM.

# *3.4.3.5 Determining Number of Bytes in the Reset Configuration Block*

The low byte of the Reset Configuration Block header is known as the link byte. The value of the Link Byte represents the number of bytes of configuration data in the Reset Configuration Block. The two bytes used for the header are excluded when calculating the Link Byte value.

For example, a Reset Configuration Block header of A104h indicates a non-sequential EEPROM programmed with a Reset Configuration Block containing 4 bytes of configuration data. This Reset Configuration Block occupies 6 bytes (3 words) of EEPROM space (2 bytes for the header and 4 bytes of configuration data).

## 3.4.4 Groups of Configuration Data

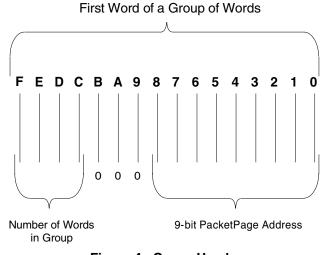

Configuration data are arranged as groups of words. Each group contains one or more words of data that are to be loaded into PacketPage registers. The first word of each group is referred to as the Group Header. The Group Header indicates the number of words in the group and the address of the PacketPage register into which the first data word in the group is to be loaded. Any remaining words in the group are stored in successive PacketPage registers.

## 3.4.4.1 Group Header

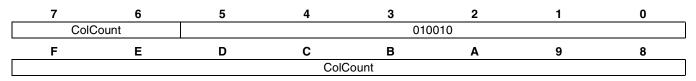

Bits F through C of the Group Header specify the number of words in each group that are to be transferred to PacketPage registers (see Figure 4). This value is two less than the total number of words in the group, including the Group Header. For example, if bits F through C contain 0001, there are three words in the group (a Group Header and two words of configuration data).

Figure 4. Group Header

Bits 8 through 0 of the Group Header specify a 9-bit PacketPage Address. This address defines the PacketPage register that will be loaded with the first word of configuration data from the group. Bits B though 9 of the Group Header are forced to 0, restricting the destination address range to the first 512 bytes of PacketPage memory. Figure 4 shows the format of the Group header.

#### 3.4.5 Reset Configuration Block Checksum

A checksum is stored in the high byte position of the word immediately following the last group of data in the Reset Configuration Block. (The EEPROM address of the checksum value can be determined by dividing the value stored in the Link Byte by two). The checksum value is the 2's complement of the 8-bit sum (any carry out of eighth bit is ignored) of all the bytes in the Reset Configuration Block, excluding the checksum byte. This sum includes the Reset Configuration Block header at address 00h. Since the checksum is calculated as the 2's complement of the sum of all preceding bytes in the Reset Configuration Block, a total of 0 should result when the checksum value is added to the sum of the previous bytes.

## 3.4.6 EEPROM Example

Table 7 shows an example of a Reset Configuration Block stored in a C46 EEPROM. Note that little-endian word ordering is used, i.e., the least significant word of a multiword datum is located at the lowest address.

## 3.4.7 EEPROM Read-out

If the EEDI pin is asserted high at the end of reset, the CS8900A reads the first word of EE-PROM data by:

- 1) Asserting EECS

- 2) Clocking out a Read-Register-00h com-

mand on EEDO (EESK provides a 1MHz serial clock signal)

3) Clocking the data in on EEDI.

If the EEDI pin is low at the end of the reset signal, the CS8900A does not perform an EE-PROM read-out (uses its default configuration).

## 3.4.7.1 Determining EEPROM Size