# MB86291A/291AS

# <SCARLET> Graphics Controller Specifications

Revision 1.1 Apr 2004

Copyright © FUJITSU LIMITED 2003 **ALL RIGHTS RESERVED**

#### <Notes>

- The specifications in this manual are subject to change without notice. Contact our Sales Department before purchasing the product described in this manual.

- Information and circuit diagrams in this manual are only examples of device applications, they are not intended to be used in actual equipment. Also, Fujitsu accepts no responsibility for infringement of patents or other rights owned by third parties caused by use of the information and circuit diagrams.

- The contents of this manual must not be reprinted or duplicated without permission of Fujitsu.

- Fujitsu's semiconductor devices are intended for standard uses (such as office equipment (computers and OA equipment), industrial/communications/measuring equipment, and personal/home equipment). Customers using semiconductor devices for special applications (including aerospace, nuclear, military and medical applications) in which a failure or malfunction might endanger life or limb and which require extremely high reliability must contact our Sales Department first. If damage is caused by such use of our semiconductor devices without first consulting our Sales Department, Fujitsu will not assume any responsibility for the loss.

- Semiconductor devices fail with a known probability. Customers must use safety design (such as redundant design, fireproof design, over-current prevention design, and malfunction prevention design) so that failures will not cause accidents, injury or death).

- If the products described in this manual fall within the goods or technologies regulated by the Foreign Exchange and Foreign Trade Law, permission must be obtained before exporting the goods or technologies.

There is a danger of burns because the IC surface is heated depending on the IC operating conditions. In this case, take safety measures.

## **Update history**

| Date       | Version | Page count | Change                                                      |

|------------|---------|------------|-------------------------------------------------------------|

| 2003.10.27 | 1.0     | 178        | First release (Refer Differential file "mb86291vsmb86291a") |

| 2004.4.19  | 1.1     | 183        | Refer Differential file "Rev10vsRev11"                      |

|            |         |            |                                                             |

|            |         |            |                                                             |

|            |         |            |                                                             |

|            |         |            |                                                             |

|            |         |            |                                                             |

|            |         |            |                                                             |

|            |         |            |                                                             |

#### CONTENTS

| 1. Overview                                 | 1               |

|---------------------------------------------|-----------------|

| 1.1 Introduction                            | 1               |

| 1.2 System Configuration                    |                 |

| 1.3 Outline                                 |                 |

| 1.3 Outline                                 |                 |

| 1.4 Block Diagram                           |                 |

| 1.5 Functional Overview                     |                 |

|                                             |                 |

| 1.5.1 System Configuration                  |                 |

| 1.5.2 Display Controller                    |                 |

| 1.5.3 Frame Control                         |                 |

| 1.5.4 Video Capture                         |                 |

| 1.5.5 Geometry Processing                   |                 |

| 1.5.6 2D Drawing                            |                 |

| 1.5.7 3D Drawing                            |                 |

| 1.5.8 Special Effects                       |                 |

| 1.5.9 Display List                          |                 |

| 2. Signal Pins                              | 11              |

| 2.1 Signals                                 |                 |

| 2.1.1 Signals                               |                 |

| 2.2 Pin Assignment                          | 12              |

| 2.2.1 Pin Assignment Diagram                | 12              |

| 2.2.2 Pin Assignment Table                  | 13              |

| 2.2.3 Pin Treatment Table                   | 15              |

| 2.3 Signal Descriptions                     | 17              |

| 2.3.1 Host CPU Interface                    | 17              |

| 2.3.2 Video output Interface                | 18              |

| 2.3.3 Video capture Interface               |                 |

| 2.3.4 Clock Input                           |                 |

| 3. Procedure of the hardware initialization | 22              |

| 4. Host Interface                           | 23              |

| 4.1 Operation Mode                          | 23              |

| 4.1.1 Host CPU Mode                         | 23              |

| 4.1.2 Ready Signal Mode                     | 23              |

| 4.1.3 Endian                                | 23              |

| 4.2 Access Mode                             | 24              |

| 4.2.1 SRAM Interface                        | 24              |

| 4.2.2 FIFO Interface                        |                 |

| 4.3 DMA Transfer                            |                 |

| 4.3.1 Data Transfer Unit                    |                 |

| 4.3.2 Address Mode                          |                 |

| 4.3.3 Bus Mode                              |                 |

| 4.3.4 DMA Transfer Request                  |                 |

| 4.3.5 Ending DMA Transfer                   |                 |

| 4.4 Interrupt Request                       |                 |

| 4.5 Transfer of Local Display List          |                 |

| 4.6 Memory Map                              |                 |

| 5. Graphics Memory                          | 29<br><b>30</b> |

| 5.1 Configuration                           |                 |

| •                                           |                 |

| 5.1.1 Data Type                             |                 |

| 5.1.2 Memory Data Format                    |                 |

| J. I.J. IVICITIUTY DALA FUTITIAL            | उ ।             |

| 5.2 Frame Management                                                               | . 33               |

|------------------------------------------------------------------------------------|--------------------|

| 5.2.1 Single Buffer                                                                | . 33               |

| 5.2.2 Double Buffer                                                                | . 33               |

| 5.3 Memory Access                                                                  | . 34               |

| 5.3.1 Memory Access by Host CPU                                                    | . 34               |

| 5.3.2 Priority of Memory Access                                                    | . 34               |

|                                                                                    | 35                 |

| 6.1 Overview                                                                       |                    |

| 6.2 Display Function                                                               |                    |

| 6.2.1 Layer Configuration                                                          |                    |

| 6.2.2 Overlay                                                                      |                    |

| 6.2.3 Display Parameters                                                           |                    |

| 6.2.4 Display Position Control                                                     |                    |

| 6.3 Display Color                                                                  |                    |

| 6.3.1 Color Look-up Table                                                          |                    |

| 6.4 Cursor                                                                         |                    |

| 6.4.1 Cursor Display Function                                                      |                    |

| 6.4.2 Cursor Management                                                            |                    |

| 5.5 Processing Flow for Display Data                                               |                    |

| 6.6 Synchronization Control                                                        |                    |

| 6.6.1 Applicable Display Resolution                                                |                    |

| 6.6.2 Interlace Display                                                            |                    |

| <ul><li>5.7 Video Interface, NTSC/PAL Output</li></ul>                             | . 4 <i>1</i><br>48 |

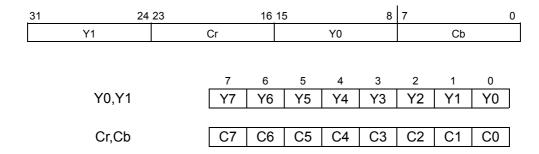

| 7.1 Format                                                                         |                    |

| 7.1.1 Input Data Format                                                            |                    |

| 7.1.1 Input Data Format                                                            |                    |

| 7.1.3 Non-interlace Transformation                                                 |                    |

| 7.2 Video Buffer                                                                   |                    |

| 7.2.1 Data Format                                                                  |                    |

| 7.2.2 Synchronous Control                                                          |                    |

| 7.2.3 Area Allocation                                                              |                    |

| 7.2.4 Window Display                                                               |                    |

| 7.2.5 Interlace Display                                                            |                    |

| 7.3 Scaling                                                                        |                    |

| 7.3.1 Video Reduction Function                                                     |                    |

| 7.3.2 Vertical Interpolation                                                       |                    |

| 7.4 Error Handling                                                                 |                    |

| 7.4.1 Error Detection Function                                                     |                    |

|                                                                                    | 52                 |

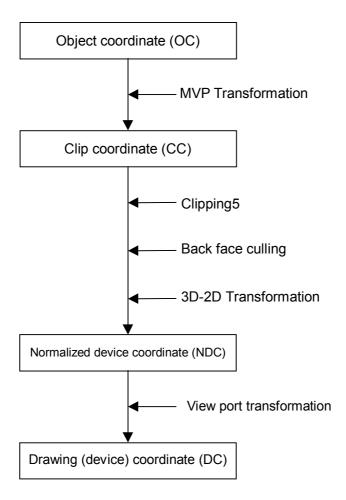

| 8.1 Geometry Pipeline                                                              | -                  |

| 8.1.1 Processing Flow                                                              |                    |

| 8.1.2 Model-View-Projection (MVP) Transformation (OC→CC Coordinate Transformation) |                    |

| 8.1.3 3D-2D Transformation (CC→NDC Coordinate Transformation)                      |                    |

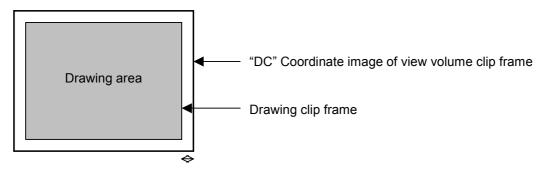

| 8.1.4 View Port Transformation (NDC→DC Coordinate Transformation)                  |                    |

| 8.1.5 View Volume Clipping                                                         |                    |

| 8.1.6 Back face carling                                                            |                    |

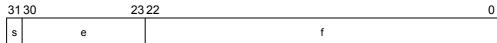

| 8.2 Data Format                                                                    |                    |

| 8.2.1 Data Format                                                                  |                    |

| 8.3 Setup Engine                                                                   |                    |

| 8.3.1 Setup Processing                                                             |                    |

| 9. Drawing Processing                                                              | 58                 |

| 9.1 Coordinate System                      | 58  |

|--------------------------------------------|-----|

| 9.1.1 Drawing Coordinate                   | 58  |

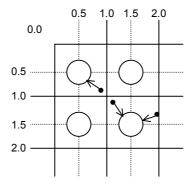

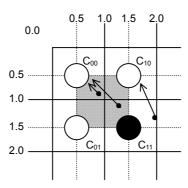

| 9.1.2 Texture Coordinate                   | 59  |

| 9.1.3 Frame Buffer                         | 59  |

| 9.2 Figure Drawing                         | 60  |

| 9.2.1 Drawing Primitives                   | 60  |

| 9.2.2 Polygon Drawing                      | 60  |

| 9.2.3 Drawing Parameters                   | 60  |

| 9.2.4 Anti-aliasing Function               | 62  |

| 9.3 Bit Map Processing                     | 63  |

| 9.3.1 BLT                                  | 63  |

| 9.3.2 Pattern Data Format                  | 63  |

| 9.4 Texture Mapping                        | 64  |

| 9.4.1 Texture Size                         | 64  |

| 9.4.2 Texture Memory                       | 64  |

| 9.4.3 Texture Lapping                      | 64  |

| 9.4.4 Filtering                            | 65  |

| 9.4.5 Perspective Collection               | 65  |

| 9.4.6 Texture Blending                     | 66  |

| 9.5 Rendering                              | 67  |

| 9.5.1 Tiling                               | 67  |

| 9.5.2 Alpha Blending                       | 67  |

| 9.5.3 Logical Calculation                  | 67  |

| 9.5.4 Hidden Surface Management            | 68  |

| 9.6 Drawing Attributes                     | 69  |

| 9.6.1 Line Draw Attributes                 | 69  |

| 9.6.2 Triangle Draw Attributes             | 69  |

| 9.6.3 Texture Attributes                   | 69  |

| 9.6.4 BLT Attributes                       | 70  |

| 9.6.5 Character Pattern Drawing Attributes | 70  |

| 10 Display List                            | 71  |

| 10.1 Overview                              |     |

| 10.1.1 Header Format                       | 71  |

| 10.1.2 Parameter format                    |     |

| 10.2 Geometry Commands                     | 73  |

| 10.2.1 Geometry command list               |     |

| 10.2.2 Explanation of Geometry Commands    |     |

| 10.3 Rendering Command                     |     |

| 10.3.1 Command Overview                    |     |

| 10.3.2 Details of Rendering Commands       |     |

| 11. Registers                              | 91  |

| 11.1 Description                           |     |

| 11.1.1 Host Interface Registers            |     |

| 11.1.2 Graphics Memory Interface Registers |     |

| 11.1.3 Display Control Register            |     |

| 11.1.4 Video Capture Registers             |     |

| 11.1.5 Draw Control Registers              |     |

| 11.1.6 Draw mode Registers                 |     |

| 11.1.8 Line Draw Registers                 |     |

| 11.1.9 Pixel Plot Registers                |     |

| 11.1.10 Rectangle Draw Registers           |     |

| 11.1.11 Blt Registers                      | 139 |

| 11.1.12 Fast2DLine Draw Registers                                           | 140               |

|-----------------------------------------------------------------------------|-------------------|

| 11.1.13 Fast2DTriangle Draw Registers                                       | 141               |

| 11.1.14 Geometry Control Register                                           | 141               |

| 11.1.15 Geometry Mode Registers                                             | 142               |

| 11.1.16 DisplayList FIFO Registers                                          | 145               |

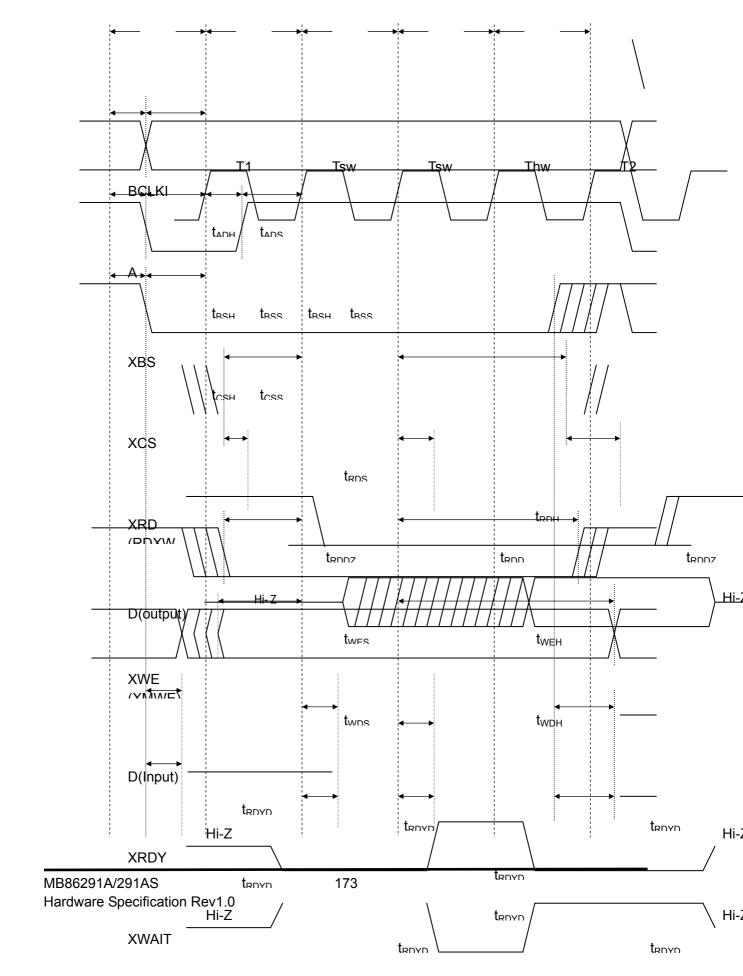

| 12. Timing Diagram                                                          | 146               |

| 12.1 Host Interface                                                         |                   |

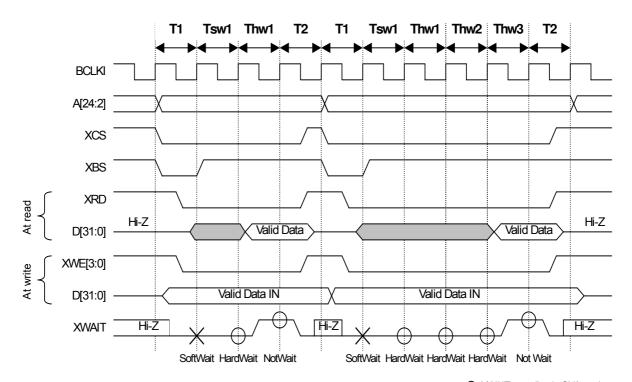

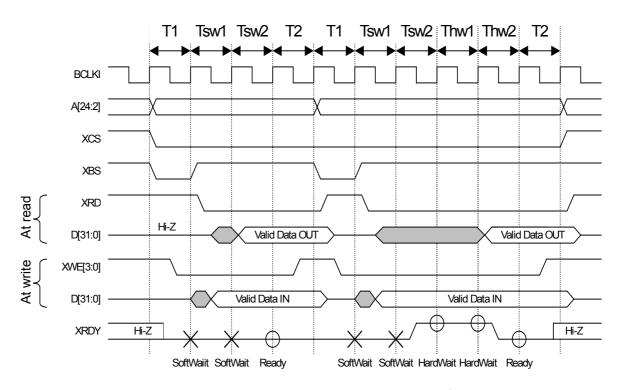

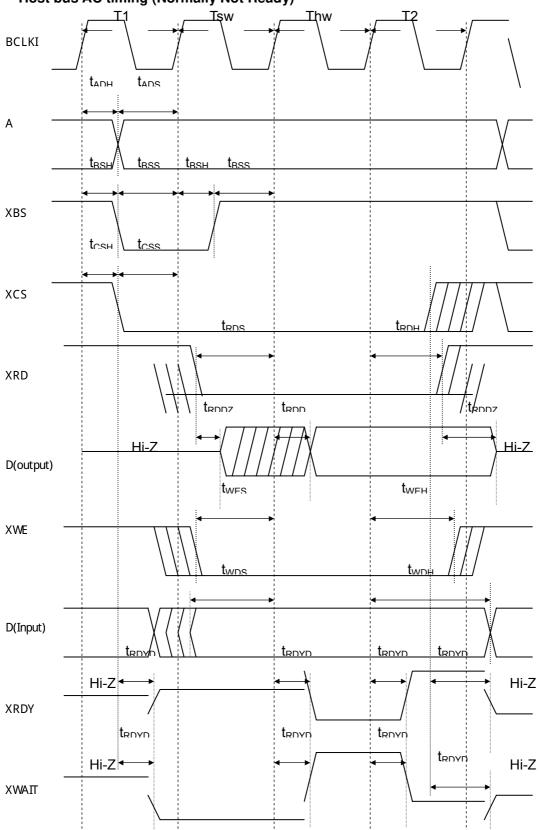

| 12.1.1 CPU Read/Write Timing Diagram for SH3 Mode (Normally Not Ready Mode) |                   |

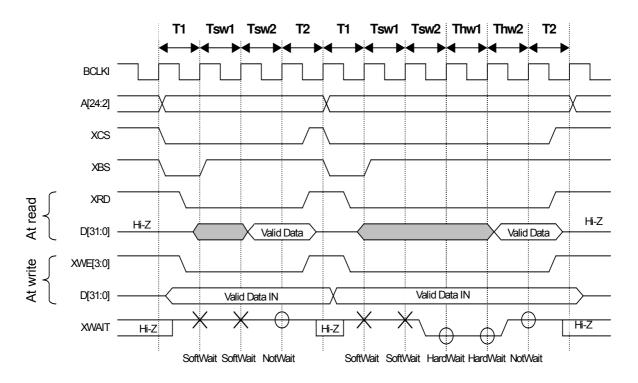

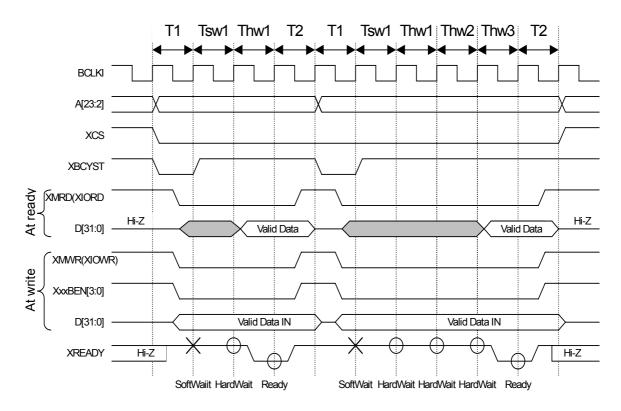

| 12.1.2 CPU Read/Write Timing Diagram for SH3 Mode (Normally Ready Mode)     |                   |

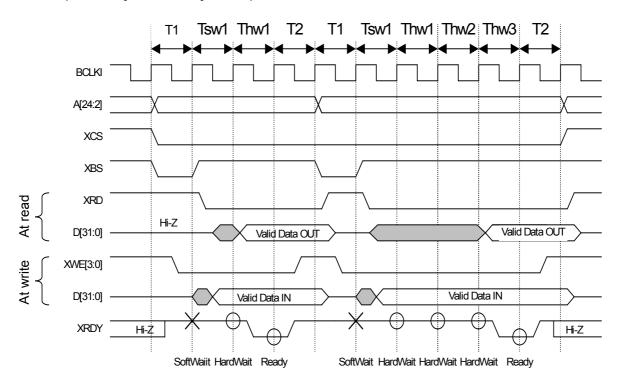

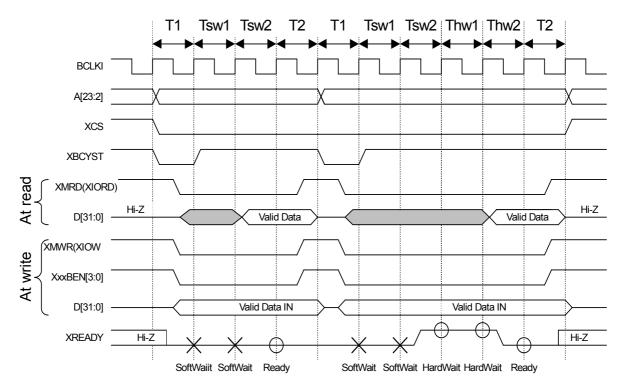

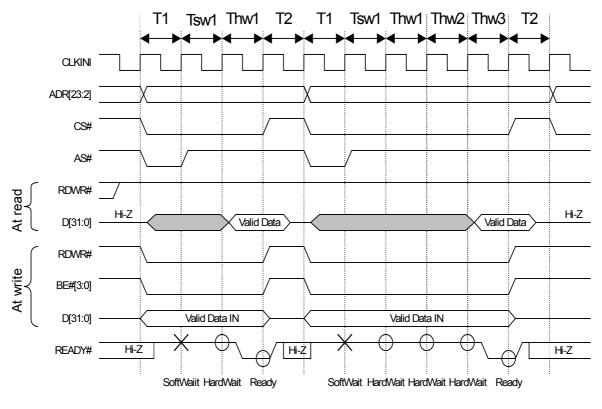

| 12.1.3 CPU Read/Write Timing Diagram for SH4 Mode                           |                   |

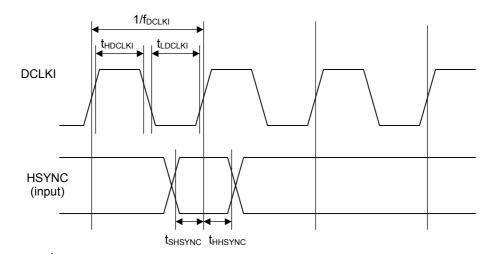

| 12.2 Display Timing                                                         |                   |

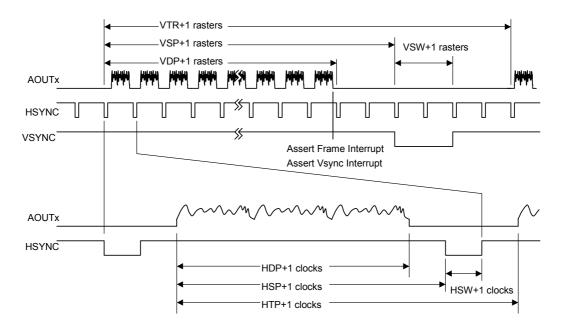

| 12.2.1 Non-interlaced Video Mode                                            |                   |

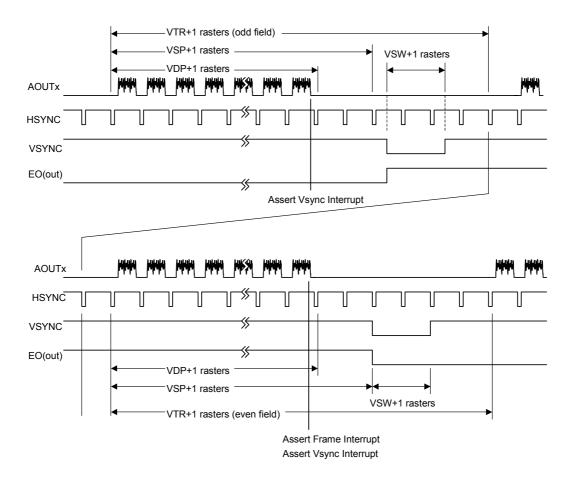

| 12.2.2 Interlaced Video Mode                                                |                   |

| Cautions                                                                    | 162               |

| 12.3 CPU Cautions                                                           |                   |

| 12.4 SH3 Mode                                                               |                   |

| 12.5 SH4 Mode                                                               |                   |

| 12.6 V832 Mode                                                              |                   |

| 12.7 SPARClite                                                              |                   |

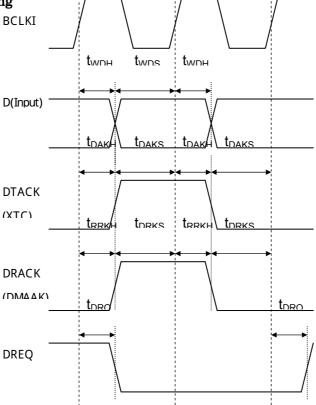

| 12.8 DMA Transfer Modes Supported by SH3, SH4, and V832                     | 163<br><b>164</b> |

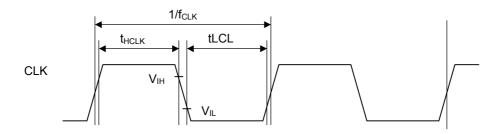

| 13.1 Absolute Maximum Ratings                                               |                   |

|                                                                             |                   |

| 13.2 Recommended Operating Conditions                                       |                   |

| 13.2.1 Recommended Operating Conditions                                     |                   |

| 13.3 DC Characteristics                                                     |                   |

| 13.4 AC Characteristics                                                     |                   |

| 13.4.1 Host Interface                                                       |                   |

| 13.4.2 Video Interface                                                      |                   |

| 13.4.3 Video Capture Interface                                              |                   |

| 13.4.4 PLL Specifications                                                   |                   |

| 13.5 Timing Diagram                                                         |                   |

| 13.5.1 Host Interface                                                       |                   |

| 13.5.2 Video Interface                                                      |                   |

| 13.5.2 Video Interface                                                      |                   |

| 13.5.3 Video Capture Interface                                              |                   |

| 10.0.0 Video Oupture interface                                              | 170               |

## 1. Overview

#### 1.1 Introduction

The MB86291A/291AS <SCARLET2> graphics controller develops the FUJITSU MB86290A graphics controller; it enables geometry processing and digital video capture.

Building SDRAM into this controller also achieves high-band graphics data transfer, providing high-speed graphics processing.

The MB86291AS is graphics controller LSI which is added the I<sup>2</sup>C interface function to MB86291A.

For details of the I<sup>2</sup>C interface function, please refer an another additional manual for MB86291AS.

#### **Target applications**

Car navigation systems

Mobile equipment

Digital information home electric appliance

Amusement equipment

## 1.2 System Configuration

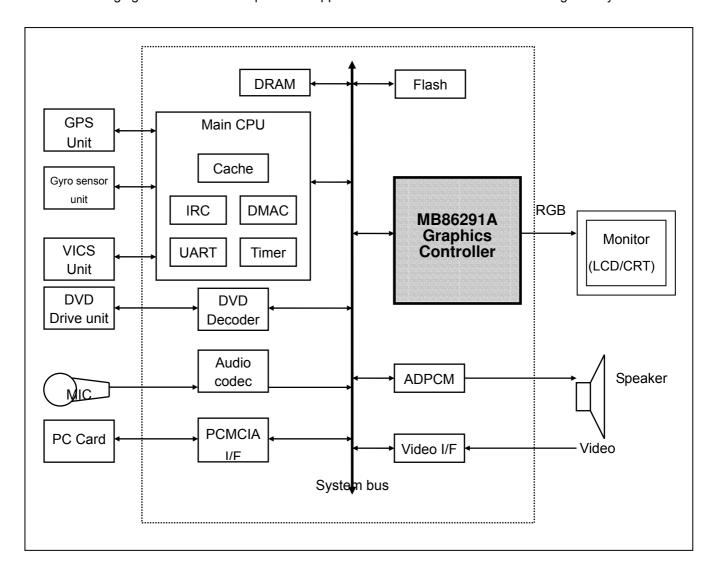

The following figure shows an example of the application of the MB86291A to a car navigation system.

Fig.1.1 System Configuration (TBD)

PRELIMINARY and CONFIDENTIAL

#### 1.3 Outline

#### Built-in graphics memory

The MB86291A has built-in 16-Mbit SDRAM to enable high bandwidth data transfer. This permits high-speed memory access, which is the bottleneck of graphics processing.

#### Built-in geometry engine

The MB86291A has a built-in hardware engine that performs geometry processing such as coordinate transformation. This enables a large reduction in numerical computation for graphics processing with high CPU loads in the embedded system.

#### Digital video capture

The digital video capture function can store digital video data such as TV in graphics memory; it can display rendered graphics and video graphics on the same screen.

#### Display controller

The MB86291A has a built-in display controller that is compatible with the MB86290A.

This controller provides functions such as XGA display (1024 x 768 pixels), 4-layer overlay, left/right split display, wrap-around scrolling, double buffers, and translucent display.

In addition to analog RGB output, this controller supports digital RBG output and picture-in-picture video data.

#### 2D and 3D Rendering

The MB86291A has a rendering function that is compatible with the MB86290A. It can render data with the display list created for the MB86290A.

The MB96291 also supports 3D rendering, such as perspective texture mapping with perspective collection and Gouraud shading, alpha bending, and anti-aliasing for rendering smooth lines.

#### Others

CMOS technology with 0.25-µm DRAM

HQFP208 Package (lead pitch 0.5 mm)

Supply voltage: 2.5 V (internal operation)/3.3 V (I/O)

Power Current (TYPICAL)

2.5V: 650mA 3.3V: 50mA

## 1.4 Block Diagram

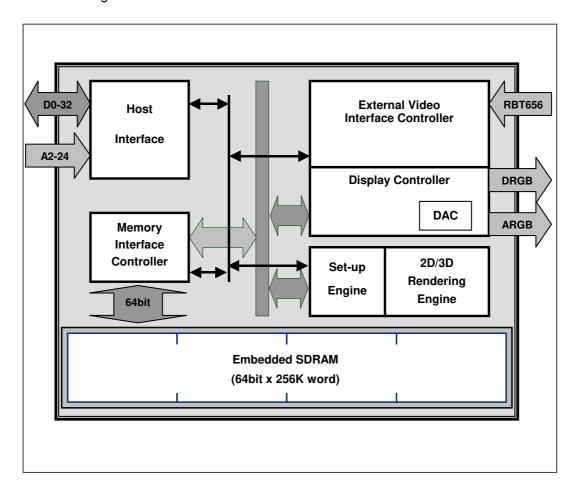

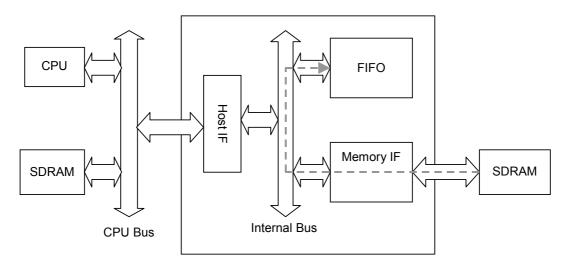

SCARLET block diagram is shown below:

Fig.1.2 SCARLET Block Diagram (TBD)

#### 1.5 Functional Overview

#### 1.5.1 System Configuration

#### **Host CPU interface**

The MB86291A can be connected to Hitachi's SH3 or SH4 CPUs, NEC's V832 microprocessor and Fujitsu SPARClite (MB86833) without an external circuit. The host MB86291A CPU interface transfer display list, texture pattern data from the main memory to the SCARLET graphic memory or internal registers by using an external DMA controller.

#### **Graphics memory**

The MB86291A has built-in 16-Mbit SDRAM and no external memory is required. The operation frequency of the graphics memory is 100 MHz.

#### **Graphics output**

MB86290A has three channels of 8-bit D/A converters and outputs analog RGB signals. The MB86291A also has 8-bit RGB digital video graphics output pins each of which can be connected to an external digital video encoder, etc.

#### Video input pin

The MB86291A has an 8-bit video input pin that can be connected to an external digital video decoder thereby supporting input of digital video in accordance with ITU RBT-656.

#### 1.5.2 Display Controller

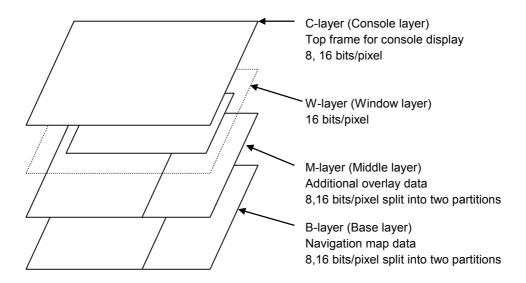

#### Screen resolution

Various resolutions are achieved by using a programmable timing generator as follows:

#### **Screen Resolutions**

| Resolution |

|------------|

| 1024 × 768 |

| 1024 × 600 |

| 800 × 600  |

| 854 × 480  |

| 640 × 480  |

| 480 × 234  |

| 400 × 234  |

| 320 × 234  |

#### **Display colors**

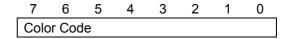

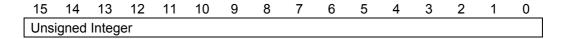

There are two pixel color modes (indirect and direct). In the indirect mode, each pixel is expressed in 8-bit code. The actual display color is referenced using a color look-up table (color pallet). In this mode, each color of the look-up table is represented as 17 bits (RGB 6 bits each and independent alpha-blend bit), and 256 colors are selected from 262,144 colors. In the direct mode, each pixel is expressed as 16-bit code (RGB 5 bits each and reserved intensity bit). In this mode, 32,768 colors can be displayed.

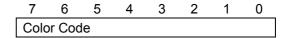

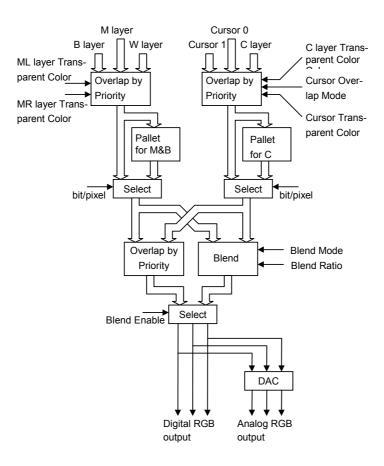

#### Overlay

Up to three extra layers can be overlaid on the base window. When multiple layers are overlaid, the lower layer image can be displayed according to the setting of the transparency option. Any

#### FUJITSU LIMITED

#### PRELIMINARY and CONFIDENTIAL

codes in the color pallet can be assigned a transparent color. Code 0 in the indirect mode or color value 0 in the direct mode sets this transparent option.

#### Hardware cursor

MB86291A supports two separate hardware cursor functions. Each of these hardware cursors is specified as a  $64 \times 64$ -pixel area. Each pixel of these hardware cursors is 8 bits and uses the indirect mode look-up table.

#### 1.5.3 Frame Control

#### **Double buffer scheme**

This mode provides smooth animation. The display frame and drawing frame are switched back and forth at each scan frame. A program in the vertical blanking period controls flipping.

#### Scroll scheme

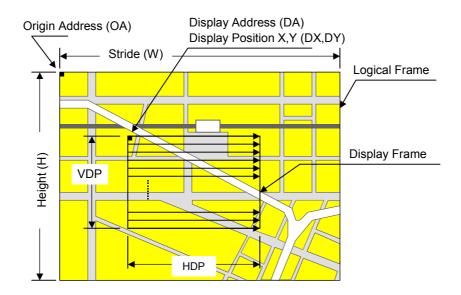

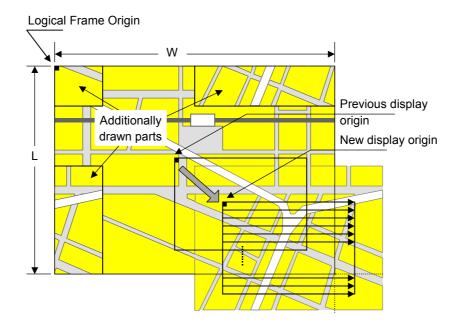

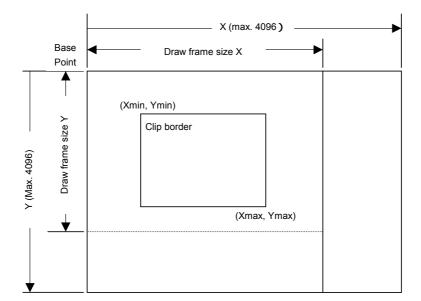

Wrap around scrolling can be done by setting the drawing area, display area, display size and start address independently.

#### Windows display

The whole screen can be split into two vertically separate windows. Both windows can be controlled independently.

#### 1.5.4 Video Capture

The video capture function captures ITU RBT-656 format videos. Video data is stored in graphics memory once and then displayed on the screen in synchronization with the display scan.

Both NTSC and PAL video formats are supported.

#### 1.5.5 Geometry Processing

The MB86291A has a geometry engine for performing the numerical operations required for graphics processing. The geometry engine uses the floating-point format to perform high-precision numerical operations. It selects the required geometry processing according to the set drawing mode and primitive type and executes processing to the final drawing.

#### **MVP Transformation**

**MVP** Transformation

Setting a 4 x 4 conversion matrix enables transformation of a 3D model view projection. Twodimensional affine transformation is also possible.

#### Clipping

Clipping stops drawing of figures outside the screen (field of view). Polygons (including concave shapes) can also be clipped.

#### **3D-2D Transformation**

This functions transforms 3D coordinates (normalization) into 2D coordinates in orthogonal or perspective projections.

#### View port transformation

This function transforms normalized 2D coordinates into drawing (device) coordinates.

#### **Primitive setup**

This function automatically performs a variety of slope computations, etc., based on transforming vertex data into coordinates and sets up (preprocesses) rendering.

#### 1.5.6 2D Drawing

#### 2D Primitives

MB86291A provides automatic drawing of various primitives and patterns (drawing surfaces) to frame memory in either indirect color (8 bits/pixel referencing appropriate palette) or direct color (16 bits/pixel) mode. Alpha blending and anti-aliasing features are useful when the direct color mode is selected.

A triangle is drawn in a single color, mapped with a style image formed by a single color or 2D pattern (tiling), or mapped with a texture pattern by designating coordinates of the 2D pattern at each vertex (texture mapping). Alpha blending can be applied either per entire shape in single color mode or per pixel in tiling/texture mapping mode. When an object is drawn in single color or filled with a 2D pattern (without using Gouraud shading or texture mapping), dedicated primitives, such as Fast2DLine and Fast2DTriangle, are used. Only vertex coordinates are set for these primitives. Fast2Dtriangle is also used to draw polygons.

#### **2D Primitives**

| Primitive type | Description                                                                                                                                              |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Point          | Plots point                                                                                                                                              |

| Line           | Draws line                                                                                                                                               |

| Triangle       | Draws triangle                                                                                                                                           |

| Fast2DLine     | Draws lines The number of parameters set for this primitive is less than that for Line. The CPU load to use this primitive is lighter than using Line.   |

| Fast2DTriangle | Draws triangles. When a triangle is drawn in one color or filled with a 2D pattern, the CPU load to apply this primitive is lighter than using Triangle. |

#### Polygon draw

This function draws various random shapes formed using multiple vertices. There is no restriction on the number of vertices number, however, if any sides forming the random shape cross each

#### FUJITSU LIMITED

#### PRELIMINARY and CONFIDENTIAL

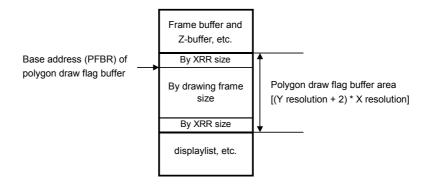

other, the shape is unsupported. The Polygon draw flag buffer must be defined in graphics memory as a work field to draw random shapes.

#### **BLT/Rectangle fill**

This function draws a rectangle using logical calculations. It is used to clear the frame memory and Z buffer. At scrolling, the rolled over part can be cleared by using this function in the blanking time period.

#### **BLT Attributes**

| Attribute              | Description                                                            |

|------------------------|------------------------------------------------------------------------|

| Raster operation       | Selects two source logical operation mode                              |

| Transparent processing | This functions does not draw the pixel matching the transparent color. |

#### Pattern (Text) drawing

This function draws a binary pattern (text) in a designated color.

#### **Pattern (Text) Drawing Attributes**

| Attribute | Description      |  |

|-----------|------------------|--|

| Enlarge   | 2 × 2            |  |

|           | Horizontally × 2 |  |

| Shrink    | Horizontally 1/2 |  |

|           | 1/2 × 1/2        |  |

#### Clipping

This function sets a rectangular window in a frame memory drawing surface and disables drawing of anything outside that window.

#### 1.5.7 3D Drawing

#### **3D Primitives**

This function draws 3D objects in frame memory in the direct color mode.

#### 3D Primitives

| Primitive | Description       |

|-----------|-------------------|

| Point     | Plots 3D point    |

| Line      | Draws 3D line     |

| Triangle  | Draws 3D triangle |

#### 3D Drawing attributes

MB86291A has various professional 3D graphics features, including Gouraud shading and texture mapping with bi-linear filtering/automatic perspective correction, and provides high- quality realistic 3D drawing. A built-in sophisticated texture mapping unit delivers fast pixel calculations. This unit also delivers color blending between the shading color and texture color as well as alpha blending per pixel.

#### Hidden surface management

MB86291A supports the Z buffer for hidden surface management.

#### 1.5.8 Special Effects

#### **Anti-aliasing**

Anti-aliasing manipulates lines and borders of polygons in sub-pixel units to eliminate jaggies on bias lines. It is used as a functional option for 2D drawing (in direct color mode only).

#### Line drawing

This function draws lines of a specific width. Detecting a line pattern can also draw a broken line. The anti-aliasing feature is also useful to draw smooth lines.

#### **Line Draw Attributes**

| Attribute   | Description                                    |

|-------------|------------------------------------------------|

| Width       | Selectable from 1 to 32 pixels                 |

| Broken line | Set by 32 bit or 24 bit of broken line pattern |

#### Alpha blending

Alpha blending blends two separate colors to provide a transparency effect. SCARLET supports two types of alpha blending; blending two different colors at drawing, and blending overlay planes at display. Transparent color is not used for these blending options.

#### **Alpha Blending**

| Туре            | Description                                                                                     |

|-----------------|-------------------------------------------------------------------------------------------------|

| Drawing         | Transparent ratio set in particular register                                                    |

|                 | While one primitive (polygon, pattern, etc.), being drawn, registered transparent ratio applied |

| Overlay display | Blends top layer pixel color and lower layer pixel at same position                             |

|                 | Transparent ratio set in particular register                                                    |

|                 | Registered transparent ratio applied during one frame scan                                      |

#### **Shading**

Gouraud shading is supported in the direct color mode to provide realistic 3D objects and color gradation.

#### **Texture mapping**

MB86291A supports texture mapping to map a style pattern onto the surface of 3D polygons. Perspective correction is calculated automatically. For 2D pattern texture mapping, MB86291A has a built-in buffer memory for a field of up to  $64 \times 64$  pixels. Texture mapping is performed at high speeds while texture patterns are stored in this buffer. The texture pattern can also be stored in the graphics memory. In this case, a large pattern of up to  $256 \times 256$  pixels can be used.

#### **Texture Mapping**

| Function                      | Description      |

|-------------------------------|------------------|

| Texture filtering             | Point sample     |

| -                             | Bi-linear filter |

| Texture coordinate correction | Linear           |

|                               | Perspective      |

| Texture blending              | Decal            |

|                               | Modulate         |

|                               | Stencil          |

| Texture alpha blending        | Normal           |

|                               | Stencil          |

|                               | Stencil alpha    |

| Texture wrap                  | Repeat           |

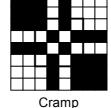

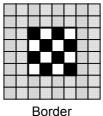

|                               | Cramp            |

|                               | Border           |

#### 1.5.9 Display List

SCARLET is operated by feeding display lists which consists of a set of display commands, arguments and pattern data for them. Normally, these display lists are stored either in off- screen frame memory (part of SCARLET's local buffer) or host (main) memory that the DMAC of the host CPU can access directly. SCARLET reads these display lists, decodes the commands, and executes them after reading all the necessary arguments. By executing this operation set until the end of the display list, all graphics operations, including image/object drawing and display control, are separated from the CPU. Of course, the CPU program can also feed the display list information directly to MB86291A's designated registers.

## 2. Signal Pins

## 2.1 Signals

## 2.1.1 Signals

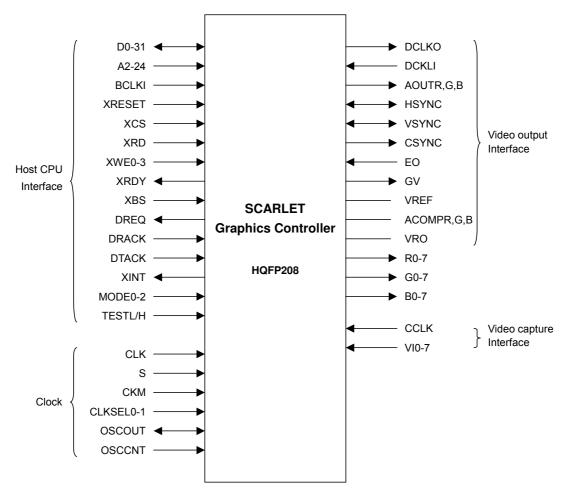

Fig. 2.1 SCARLET Signals

#### 2.2 Pin Assignment

#### 2.2.1 Pin Assignment Diagram

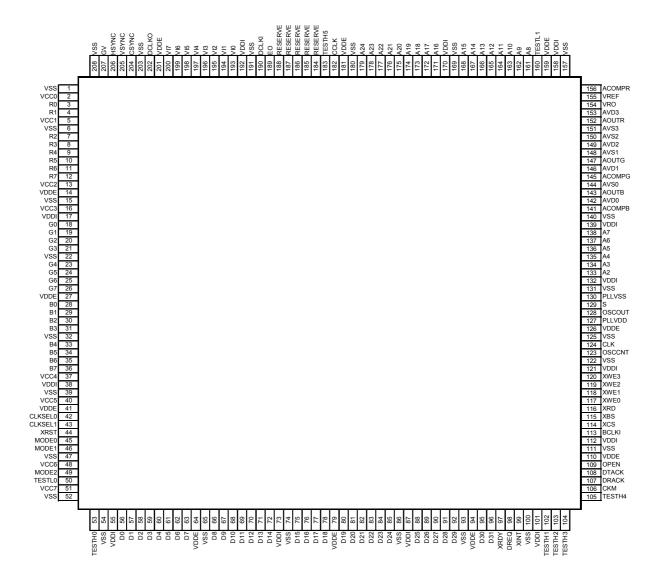

Fig. 2.2 SCARLET Pin Assignment

#### 2.2.2 Pin Assignment Table

**Table 2.1 Pin Assignment**

| No. | Name             | No. | Name             | No. | Name               | No. | Name             |

|-----|------------------|-----|------------------|-----|--------------------|-----|------------------|

| 1   | $V_{SS}$         | 53  | TESTH0           | 105 | TESTH4             | 157 | $V_{SS}$         |

| 2   | V <sub>CC0</sub> | 54  | V <sub>SS</sub>  | 106 | CKM                | 158 | $V_{DDI}$        |

| 3   | R0               | 55  | $V_{DDI}$        | 107 | DRACK              | 159 | $V_{DDE}$        |

| 4   | R1               | 56  | D0               | 108 | DTACK              | 160 | TESTL1           |

| 5   | V <sub>CC1</sub> | 57  | D1               | 109 | OPEN               | 161 | A8               |

| 6   | V <sub>SS</sub>  | 58  | D2               | 110 | $V_{DDE}$          | 162 | A9               |

| 7   | R2               | 59  | D3               | 111 | V <sub>SS</sub>    | 163 | A10              |

| 8   | R3               | 60  | D4               | 112 | V <sub>DDI</sub>   | 164 | A11              |

| 9   | R4               | 61  | D5               | 113 | BCLKI              | 165 | A12              |

| 10  | R5               | 62  | D6               | 114 | XCS                | 166 | A13              |

| 11  | R6               | 63  | D7               | 115 | XBS                | 167 | A14              |

| 12  | R7               | 64  | $V_{DDE}$        | 116 | XRD                | 168 | A15              |

| 13  | V <sub>CC2</sub> | 65  | V <sub>SS</sub>  | 117 | XWE0               | 169 | V <sub>SS</sub>  |

| 14  | V <sub>DDE</sub> | 66  | D8               | 118 | XWE1               | 170 | $V_{DDI}$        |

| 15  | V <sub>SS</sub>  | 67  | D9               | 119 | XWE2               | 171 | A16              |

| 16  | V <sub>CC3</sub> | 68  | D10              | 120 | XWE3               | 172 | A17              |

| 17  | V <sub>DDI</sub> | 69  | D11              | 121 | V <sub>DDI</sub>   | 173 | A18              |

| 18  | G0               | 70  | D12              | 122 | V <sub>SS</sub>    | 174 | A19              |

| 19  | G1               | 71  | D13              | 123 | OSCCNT             | 175 | A20              |

| 20  | G2               | 72  | D14              | 124 | CLK                | 176 | A21              |

| 21  | G3               | 73  | V <sub>DDI</sub> | 125 | V <sub>SS</sub>    | 177 | A22              |

| 22  | V <sub>SS</sub>  | 74  | V <sub>SS</sub>  | 126 | V <sub>DDE</sub>   | 178 | A23              |

| 23  | G4               | 75  | D15              | 127 | PLLV <sub>DD</sub> | 179 | A24              |

| 24  | G5               | 76  | D16              | 128 | OSCOUT             | 180 | VSS              |

| 25  | G6               | 77  | D17              | 129 | S                  | 181 | V <sub>DDE</sub> |

| 26  | G7               | 78  | D18              | 130 | PLLV <sub>SS</sub> | 182 | CCLK             |

| 27  | V <sub>DDE</sub> | 79  | V <sub>DDE</sub> | 131 | V <sub>SS</sub>    | 183 | TESTH5           |

| 28  | B0               | 80  | D19              | 132 | V <sub>DDI</sub>   | 184 | RESERVE          |

| 29  | B1               | 81  | D20              | 133 | A2                 | 185 | RESERVE          |

| 30  | B2               | 82  | D21              | 134 | A3                 | 186 | RESERVE          |

| 31  | B3               | 83  | D22              | 135 | A4                 | 187 | RESERVE          |

| 32  | V <sub>SS</sub>  | 84  | D23              | 136 | A5                 | 188 | RESERVE          |

| 33  | B4               | 85  | D24              | 137 | A6                 | 189 | EO               |

| 34  | B5               | 86  | V <sub>SS</sub>  | 138 | A7                 | 190 | DCLKI            |

| 35  | B6               | 87  | V <sub>DDI</sub> | 139 | V <sub>DDI</sub>   | 191 | V <sub>SS</sub>  |

| 36  | B7               | 88  | D25              | 140 | V <sub>SS</sub>    | 192 | $V_{DDI}$        |

| 37  | V <sub>CC4</sub> | 89  | D26              | 141 | ACOMPB             | 193 | VIO              |

| 38  | V <sub>DDI</sub> | 90  | D27              | 142 | AV <sub>D0</sub>   | 194 | VI1              |

| 39  | V <sub>SS</sub>  | 91  | D28              | 143 | AOUTB              | 195 | VI2              |

| 40  | V <sub>CC5</sub> | 92  | D29              | 144 | AV <sub>S0</sub>   | 196 | VI3              |

| 41  | V <sub>DDE</sub> | 93  | V <sub>SS</sub>  | 145 | ACOMPG             | 197 | VI4              |

| 42  | CLKSEL0          | 94  | V <sub>DDE</sub> | 146 | AV <sub>D1</sub>   | 198 | VI5              |

| 43  | CLKSEL1          | 95  | D30              | 147 | AOUTG              | 199 | VI6              |

| 44  | XRST             | 96  | D31              | 148 | AV <sub>S1</sub>   | 200 | VI7              |

| 45  | MODE0            | 97  | XRDY             | 149 | AV <sub>D2</sub>   | 201 | $V_{DDE}$        |

| 46  | MODE1            | 98  | DREQ             | 150 | AV <sub>S2</sub>   | 202 | DCLKO            |

| 47  | V <sub>SS</sub>  | 99  | XINT             | 151 | AV <sub>S3</sub>   | 203 | Vss              |

| 48  | V <sub>CC6</sub> | 100 | V <sub>SS</sub>  | 152 | AOUTR              | 204 | CSYNC            |

| 49  | MODE2            | 101 | V <sub>DDI</sub> | 153 | AV <sub>D3</sub>   | 205 | VSYNC            |

| 50  | TESTL0           | 102 | TESTH1           | 154 | V <sub>RO</sub>    | 206 | HSYNC            |

| 51  | V <sub>CC7</sub> | 103 | TESTH2           | 155 | V <sub>REF</sub>   | 207 | GV               |

| 52  | V <sub>SS</sub>  | 104 | TESTH3           | 156 | ACOMPR             | 208 | V <sub>SS</sub>  |

#### FUJITSU LIMITED

#### PRELIMINARY and CONFIDENTIAL

#### **Notes**

$V_{SS}/AV_{S}/PLLV_{SS}$  : Ground

$\begin{array}{lll} V_{DDH}(V_{DDE}) & : & 3.3\text{-V power supply} \\ V_{DDL}(V_{DDI})/AV_D/PLLV_{DD}/V_{CC} & : & 2.5\text{-V power supply} \\ AV_D & : & Analog power supply} \\ PLLV_{DD} & : & PLL Power supply \end{array}$

$V_{CC}$ : Built-in DRAM power supply

OPEN : NC

TESTL : TESTL signal (Pull-down)

TESTH : TESTH signal (Pull-up)

RESERVE : RESERVE signal (Pull-up)

- $AV_D$  and  $PLLV_{DD}$  should be isolated on the PCB.

- Insert a bypass capacitor with good high frequency characteristics between the power supply and ground.

Position the capacitor as near as possible to the pin.

#### 2.2.3 Pin Treatment Table

|                              | Pin Name                  | Direct<br>i on*1 | Default Treatment                                                                   | Treatment of unused *2     | Comment                                                                                                    |

|------------------------------|---------------------------|------------------|-------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------|

|                              | MDDE0- 2                  |                  | Connect to VDDH or GND according to the CPU mode.                                   | <=                         | See "4.1 Cepration Mode"                                                                                   |

| XRST                         |                           | I                | Input hardware reset signal                                                         | <=                         | Have to be "Low" I evel<br>when power-n. See "13. 2. 2<br>Power on Precaution"                             |

|                              | D0- 31                    | IO               | Connect to CPU data bus                                                             | <=                         |                                                                                                            |

|                              | A2- A24                   | I                | Connect to CPU address bus                                                          | <=                         | Connect A24 to XMWR in the V832 mode                                                                       |

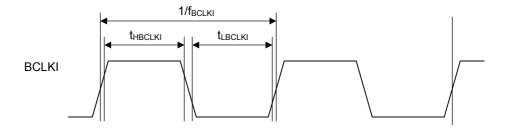

|                              | BCLKI                     | I                | Connect to CPU bus clock                                                            | <=                         | Max 100MHz. Input the clock when power- onSee "13.2.2 Power on Precaution"                                 |

|                              | XBS                       | I                | Connect to CPU bus cycle start indicating signal                                    | <=                         | This signal is 1 shot BCLKI pulse that indicates the bus cycle start                                       |

|                              | XCS                       | I                | Connect to chip select signal                                                       | <=                         |                                                                                                            |

| Host<br>Interface            | XRD                       | I                | Connect to CPU read strobe signal                                                   | <=                         |                                                                                                            |

|                              | XWE0-XWE4                 | I                | Connect to CPU write byte enable signals                                            | <=                         | Connect byte enable signal in V832 mode                                                                    |

|                              | XRDY Q(T)                 |                  | Connect to CPU Ready (Wait)<br>signal and Pull Up/Down<br>according to MDDE setting | <=                         | See "4.1 Operation Mode"                                                                                   |

|                              | DREQ                      | 0                | Connect to CPU DREQ signal                                                          | OPEN                       | SH3/4,V832=Low Active,<br>See "4.3 DMA Transfer"                                                           |

| _                            | DRACK/ DIVIA<br>AK        | I                | Connect to CPU DRACK signal                                                         | GND                        | Connect to DMAAK signal in<br>V832 Mode,<br>SH3/4,V832=High Active,<br>See "4.3 DMA Transfer "             |

|                              | DTACK/XTC                 | I                | Connect to CPU DTACK signal                                                         | S H3/ 4=GND,<br>V832=V DDH | Connect to XTC signal in<br>V832 mode,<br>SH3/4=High Active,<br>V832=Low Active, See "4.3<br>DMA Transfer" |

|                              | XI NT                     | 0                | Connect to CPU interrupt signal                                                     | OPEN                       | SH3/4=Low<br>Active,V832=High Active                                                                       |

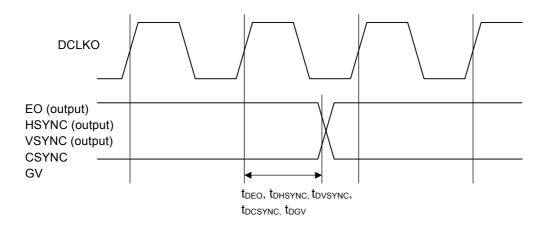

| Video<br>Output<br>Interface | DCLKO                     | 0                | Connect to dot clock                                                                | <=                         | Selectable clock source,<br>See DCM Register in "11.1.3<br>Display Controller Register"                    |

|                              | DCLKI                     | I                | Connect to clock for dot clock                                                      | GND                        |                                                                                                            |

|                              | HSYNC                     | IO               | Connect to HSYNC signal and Pull<br>Up                                              | <=                         |                                                                                                            |

|                              | VSYNC                     | IO               | Connect to VSYNC signal and Pull Up                                                 | <=                         |                                                                                                            |

|                              | CSYNC                     | 0                | Connect to CSYNC signal                                                             | OPEN                       |                                                                                                            |

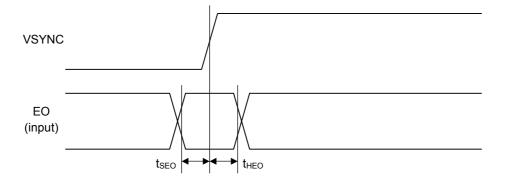

|                              | EO                        | IO               | Connect to even/ odd identification signal and Pull down                            | <=                         |                                                                                                            |

|                              | GV                        | 0                | Connect to select signal of analog video switch                                     | OPEN                       | Scarlet's display=High Level                                                                               |

|                              | RO- R7, GO-<br>G7, BO- B7 | 0                | Connect to video signals                                                            | <=                         | R7,G7,B7 are MSB                                                                                           |

|                              | AOUTR, G, B               | Anal og<br>O     | terminate at 75 ohm                                                                 | GND*3                      |                                                                                                            |

#### FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

| PRELIMINA         | ARY and CON               | LIDENII | AL                                                                                                               |              |                                                                                                    |

|-------------------|---------------------------|---------|------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------|

|                   | VREF Anal og good<br>must |         | Input 1.1V. A bypass capacitor (with good high-frequency characteristics) must be inserted between VREF and AVS. | GND*3        |                                                                                                    |

|                   | acompr, G,<br>B           | Anal og | Tied to analog ADD via 0.1uF ceremic capacitor                                                                   | GND*3        |                                                                                                    |

|                   | VRO                       | Anal og | Pull-down to analog ground by a 2.7K ohm resister.                                                               | GND*3        |                                                                                                    |

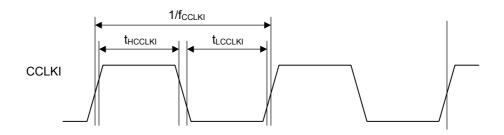

| Video<br>Capture  | CCLK                      | I       | Connect to RBT656 clock signal (27MHz)                                                                           | <=           |                                                                                                    |

| Interface         | VIO-VI7                   | I       | Connect to RBT656 video stream signals                                                                           | GND          |                                                                                                    |

|                   | CLKSEL1-<br>0             | I       | Connect to GND or VDDH according to the input frequency to CLK                                                   | <=           | See "2,3.4 Clock Input"                                                                            |

| Clock/Sy stem S I |                           | I       | Input a clock according to the setting of CLKSEL1-0                                                              | <=           | Input the clock when power-<br>on.<br>See "2.3.4 Clock<br>Input","13.2.2 Power on<br>Precation"    |

|                   |                           | I       | Input PLL reset                                                                                                  | <b>&lt;=</b> | Have to be Low level when<br>power- on. See "2.3.4 Clock<br>Input", "13.2.2 Power on<br>Precation" |

|                   | СКМ                       | I       | BCLKI=90-100MHz => VDDH<br>BCLKI=less than 90MHz => GND                                                          | <b>&lt;=</b> | See "2.3.4" Clock Input"                                                                           |

|                   | OSCOUT                    | IO      | OPEN                                                                                                             | <=           |                                                                                                    |

|                   | OSCCNT                    | I       | VDDH                                                                                                             | <b>&lt;=</b> |                                                                                                    |

## Note ) This device is warranted under the above listed condition. No warranty made with other combination or treatments.

<sup>\*1:</sup>I=Input pin, O=Output pin , O(T)= Output Tri-state pin, IO=Bi-directional pin, Analog O=Analog output, Analog=Analog pin for

<sup>\*2:&</sup>quot;<=" mark means treat a pin same as default

<sup>\*3:</sup>All of analog pins are possible to connect to GND when NOT use DAC. But if connect to GND, all of analog pins(includes analog VDD pins) have to connect GND.

#### 2.3 Signal Descriptions

#### 2.3.1 Host CPU Interface

**Table 2.2 Host CPU Interface Signals**

| Signal Name | I/O                 | Description                                                                                                                                                                          |

|-------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE0-2     | Input               | Host CPU mode, ready mode selection,                                                                                                                                                 |

| XRESET      | Input               | Hardware reset ("L"=Reset, Set low level when power on)                                                                                                                              |

| D0-31       | In/Out              | Host CPU bus data                                                                                                                                                                    |

| A2-A24      | Input               | Host CPU bus address (In the V832 mode, A[24] is connected to XMWR.)                                                                                                                 |

| BCLKI       | Input               | Host CPU bus clock                                                                                                                                                                   |

| XBS         | Input               | Bus cycle start                                                                                                                                                                      |

| XCS         | Input               | Chip select                                                                                                                                                                          |

| XRD         | Input               | Read strobe                                                                                                                                                                          |

| XWE0        | Input               | Write strobe for D0-D7                                                                                                                                                               |

| XWE1        | Input               | Write strobe for D8-D15                                                                                                                                                              |

| XWE2        | Input               | Write strobe for D16-D23                                                                                                                                                             |

| XWE3        | Input               | Write strobe for D24-D31                                                                                                                                                             |

| XRDY        | Output<br>Tri-state | Wait request signal (In the SH3 mode, when this signal is 0, it indicates the wait state; in the SH4, V832 and SPARClite modes, when this signal is 1, it indicates the wait state.) |

| DREQ        | Output              | DMA request signal (This signal is low-active in both the SH mode and V832 mode.)                                                                                                    |

| DRACK/DMAAK | Input               | Acknowledge signal issued in response to DMA request (DMAAK is used in the V832 mode; this signal is high-active in both the SH mode and V832 mode.)                                 |

| DTACK/XTC   | Input               | DMA transfer strobe signal (XTC is used in the V832 mode. In the SH mode, this signal is high-active; in the V832 mode, it is low-active.)                                           |

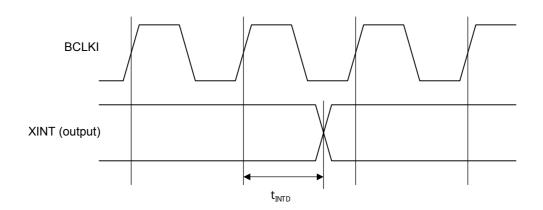

| XINT        | Output              | Interrupt signal issued to host CPU (In the SH mode, this signal is low-active; in the V832 mode, it is high-active)                                                                 |

MB86291A can be connected to the Hitachi SH4 (SH7750), SH3 (SH7709/09A) NEC V832 and Fujitsu SPARClite (MB86833). In the SRAM interface mode, MB86291A can be used with any other CPU as well. The host CPU is specified by the MODE0 and 1 pins.

| MODE 1 | MODE 0 | CPU       |

|--------|--------|-----------|

| L      | L      | SH3       |

| L      | Н      | SH4       |

| Н      | L      | V832      |

| Н      | Н      | SPARClite |

When the bus cycle terminates, a ready signal level can be set by the MODE2 pin. When using the high-level MODE2 signal, set two cycles as the CPU software wait of the CPU.

| MODE 2 | Ready signal mode                                                            |  |  |

|--------|------------------------------------------------------------------------------|--|--|

| L      | When the bus cycle terminate, sets the XRDY signal to the 'not ready' level. |  |  |

| Н      | When the bus cycle terminates, sets the XRDY signal to the 'ready' level.    |  |  |

The host interface data bus is 32-bits wide (fixed).

The address bus is 24-bits wide (per double word), and has a 32-Mbyte address field. MB86290A uses a 32-Mbyte address field.

The external bus frequency is up to 100 MHz.

In the SH4 mode and V832 mode, when the XRDY signal is low, it is in the ready state. In the SH3 mode, when the XRDY signal is low, it is in the wait state.

DMA data transfer is supported using an external DMAC.

An interrupt request signal is generated to the host CPU.

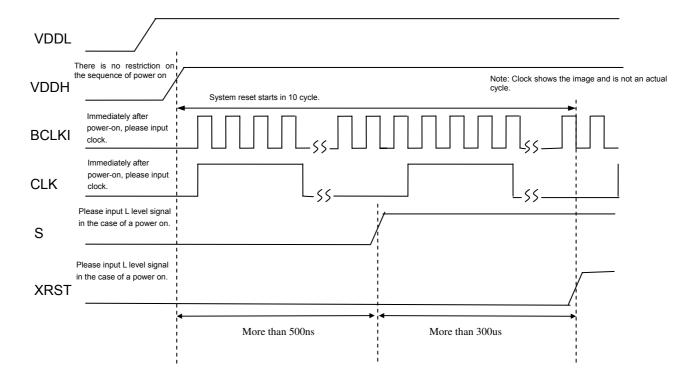

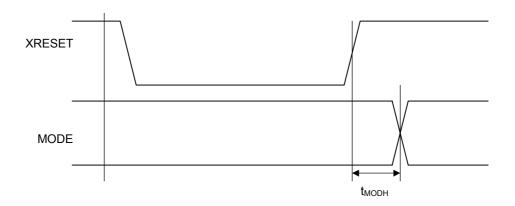

The XRESET input must be kept low (active) for at least 300 µs after setting the S (PLL reset) signal to high.

In the V832 mode, MB86291A signals are connected to the V832 CPU as follows:

| SCARLET Signal Pins | V832 Signal Pins |

|---------------------|------------------|

| A24                 | XMWR             |

| DTACK               | XTC              |

| DRACK               | DMAAK            |

#### 2.3.2 Video output Interface

**Table 2.3 Video Output Interface Signals**

| Signal Name | I/O           | Description                                 |

|-------------|---------------|---------------------------------------------|

| DCLKO       | Output        | Dot clock signal for display                |

| DCLKI       | Input         | Dot clock signal input                      |

| HSYNC       | I/O           | Horizontal sync signal output               |

|             |               | Horizontal sync input in external sync mode |

| VSYNC       | I/O           | Vertical sync signal output                 |

|             |               | Vertical sync input in external sync mode   |

| CSYNC       | Output        | Composite sync signal output                |

| EO          | I/O           | Even/odd field identification input         |

| GV          | Output        | Graphics/video switch                       |

| R0-7        | Output        | Degital signal (R) output                   |

| G0-7        | Output        | Degital signal (G) output                   |

| B0-7        | Output        | Degital signal (B) output                   |

| AOUTR       | Analog output | Analog signal (R) output                    |

| AOUTG       | Analog output | Analog signal (G) output                    |

| AOUTB       | Analog output | Analog signal (B) output                    |

| VREF        | Analog        | Reference-Nottage input pin                 |

| ACOMPR      | Analog        | R Signal complement output                  |

| ACOMPG      | Analog        | G Signal complement output                  |

| ACOMPB      | Analog        | R Signal complement output                  |

| VRO         | Analog        | Reference current output                    |

PRELIMINARY and CONFIDENTIAL

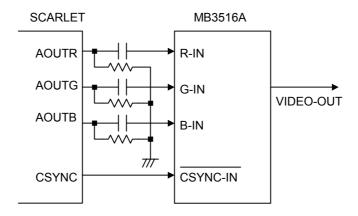

Contains 8-bit precision D/A converters and outputs analog RGB signals. It is also possible to connect each 8-bit RGB digital output pin to an external digital video encoder.

External circuits to generate composite video signal

Can display synchronously to external video signal

Can synchronize to either DCLKI signal input or internal dot clock

HSYNC and VSYNC reset to output mode. These signals must be pulled up externally.

AOUTR, AOUTG and AOUTB must be terminated at 75  $\Omega$ .

1.1 V is input to VREF. A bypass capacitor (with good high-frequency characteristics) must be inserted between VREF and AVS.

ACOMPR, ACOMPG and ACOMPB are tied to analog VDD via 0.1-µF ceramic capacitors.

VRO must be pulled down to analog ground by a 2.7-k $\Omega$  resistor.

Input low level to the EO pin by using a pull-down resistor, etc.

The GV signal switches graphics and video at chroma key operation. When video I is selected, the L level is output.

When not using DAC, it is possible to connect all of analog pins(AVD, AOUTR,G,B, ACOMPR,G,B, VREF, VRO) to GND.

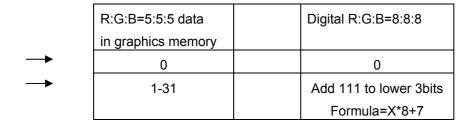

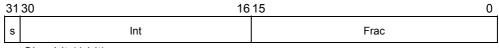

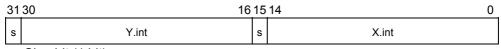

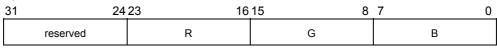

The 16bit/pixel color mode and 8bit/pixel color mode are converted to digital R:G:B=8:8:8 as the below.

#### A) 16bit/pixel color mode

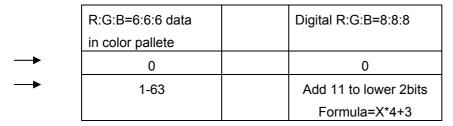

#### B) 8bit/pixel color mode

The Y,Cb,Cr mode is converted to R:G:B=8:8:8 directly.

#### 2.3.3 Video capture Interface

Table 2.4 Video capture Interface Signals

| Signal Name | I/O   | Description                            |

|-------------|-------|----------------------------------------|

| CCLK        | Input | Digital video input clock signal input |

| VI0-7       | Input | Digital video data input               |

Inputs ITU-RBT-656 format digital video signal

#### 2.3.4 Clock Input

**Table 2.5 Clock Input Signals**

| Signal Name  | I/O   | Description                                               |

|--------------|-------|-----------------------------------------------------------|

| CLK          | Input | Clock input signal                                        |

| S            | Input | PLL reset signal ("L"=Reset, Set low level when power-on) |

| CKM          | Input | Clock mode signal                                         |

| CLKSEL [1:0] | Input | Clock rate selection signal                               |

| OSCOUT*1     | I/O   | Crystal oscillator connection pin (reserved)              |

| OSCCNT*2     | Input | Crystal oscillator selection pin (reserved)               |

<sup>\*1</sup> Do not connect anything.

Inputs source clock for generating internal operation clock and display dot clock. Normally, 4 Fsc(= 14.31818 MHz:NTSC) is input. An internal PLL generates the internal operation clock of 100 MHz and the display base clock of 200 MHz.

For the internal operation clock, use either the output clock of the internal PLL (100  $MH_Z$ ) or the bus clock input (BCLK1) from the host CPU. When the host CPU bus speed is 100  $MH_Z$ , the BCLK1 input should be selected.

| СКМ | Clock mode                          |  |  |

|-----|-------------------------------------|--|--|

| L   | Output from internal PLL selected   |  |  |

| Н   | Host CPU bus clock (BCLK1) selected |  |  |

In case of use BCLKI as internal clock (CKM=H) and use DCLKI as dot clock, it is possible to set the pins as the follows.

#### A) In case of MB86291A

Connect S pin to low level, and input a clock to CCLK pin.(The clock has to input to CCLK before releasing a hardware reset.)

#### B) In case of MB86291AS

Don't stop the PLL (Not fixed the S pin to low level).

<sup>\*2</sup> Input a high-level OSCCNT signal.

When CKM = L, selects input clock frequency when built-in PLL used according to setting of CLKSEL pins

| CLKSEL1 | CLKSEL1 | Clock frequency                  |  |

|---------|---------|----------------------------------|--|

| L       | L       | Inputs 13.5-MHz clock frequency  |  |

| L       | Н       | Inputs 14.32-MHz clock frequency |  |

| Н       | L       | Inputs 17.73-MHz clock frequency |  |

| Н       | Н       | Reserved                         |  |

At power-on, a low-level signal must be input to the S-signal pin for more than 500 ns and then set to high. After the S-signal input is set to high, a low-level signal must be input to XRESET for another  $300 \, \mu s$ .

## 3. Procedure of the hardware initialization

After the reset, please set the registers as the below.

- 1. Set MMR(Memory Mode Register, HostBase+0xFFFC) to "0x00000000".

- 2. Set SID(Scarlet ID register, HostBase+0x003C) to "0x000000003".

## 4. Host Interface

#### 4.1 Operation Mode

#### 4.1.1 Host CPU Mode

Select the host CPU by setting the MODE0 to MODE1 signals as follows:

Table 4.1 CPU Type Setting

| MODE1 | MODE0 | CPU Type  |

|-------|-------|-----------|

| L     | L     | SH3       |

| L     | Н     | SH4       |

| Н     | L     | V832      |

| Н     | Н     | SPARClite |

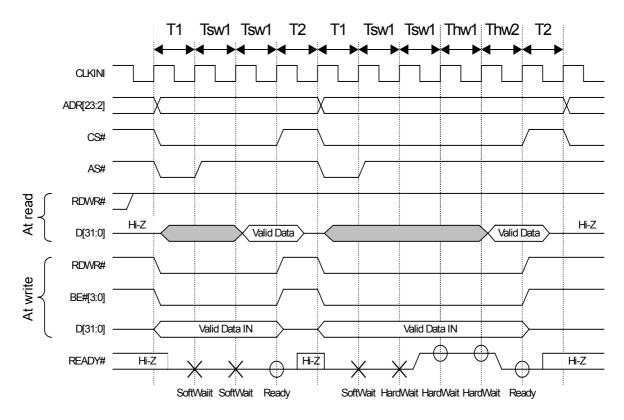

#### 4.1.2 Ready Signal Mode

The MODE2 pin can be used to set the ready signal level when the bus cycle of the host CPU terminates. When using this device in the normal ready mode, set two cycles as the CPU software wait. When using this device in the 'normal not ready' mode, set one cycle as the software wait.

The 'normal not ready mode' is the mode in which the SCARLET XRDY signal is always in the wait status and Ready is returned only when read/write is made ready.

The 'normal ready mode' is the mode in which the SCARLET XRDY signal is always in the Ready status and it is put into the wait status only when read/write cannot be performed immediately.

**Table 4.2 Ready Signal Mode**

| MODE 2 | Ready signal operation                                                                       |  |  |

|--------|----------------------------------------------------------------------------------------------|--|--|

| L      | Recognizes XRDY signal as 'not ready level' and terminates bus cycle (normal not ready mode) |  |  |

| Н      | Recognizes XRDY signal as 'ready level' and terminates bus cycle (normal ready mode)         |  |  |

#### 4.1.3 Endian

SCARLET operates in little-endian mode. All the register address descriptions in these specifications are byte address in little endian. When using a big-endian CPU, note that the byte or word addresses are different from these descriptions.

#### 4.2 Access Mode

#### 4.2.1 SRAM Interface

Data can be transferred to/from SCARLET using a typical SRAM access protocol. SCARLET internal registers, internal memory and external memory are all mapped to the physical address field of the host CPU.

SCARLET uses hardware wait based on the XRDY signal; enable the hardware wait setting of the host CPU. When using the 'normal not ready mode,' set the software wait to 1. When using the 'normal ready mode,' set the software wait to 2. Switch the ready mode using the MODE[2] signal.

#### **CPU Read**

The host CPU reads data from internal registers and memory of SCARLET in double-word (32 bit) units. Valid data is output continuously while XRD and XCS are being asserted at a low level after XRDY has been asserted.

#### **CPU Write**

The host CPU writes data to internal registers and memory of SCARLET in byte units.

#### 4.2.2 FIFO Interface

This interface transfers display lists in host memory. Display list information is transferred efficiently by using a single address mode DMA operation. This FIFO is mapped to the physical address field of the host CPU so that the same data transfer can be performed in either the SRAM mode or dual address DMA mode by specifying the FIFO in the destination address.

#### 4.3 DMA Transfer

#### 4.3.1 Data Transfer Unit

DMA transfer is performed in double-word (32 bit) units or 8 double-word (32 Byte) units. Byte and word access is not supported.

Note: 8 double-word transfer is supported only in the SH4 mode.

#### 4.3.2 Address Mode

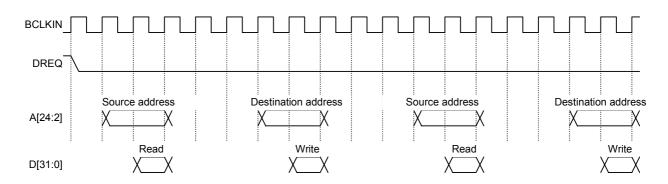

#### **Dual address mode**

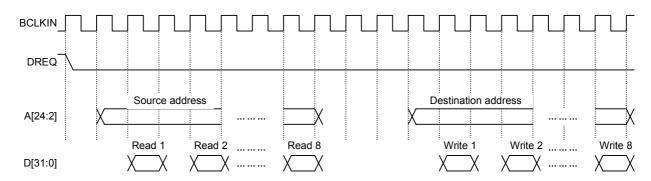

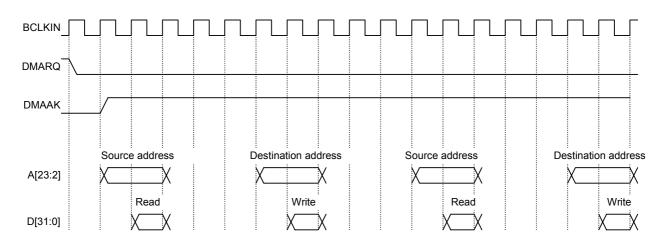

DMA is performed at memory-to-memory transfer between host memory (source) and MB86291A internal registers, memory, or external memory (destination). Both the host memory address and SCARLET is used. In the SH4 mode, the 1 double-word transfer (32 bits) and 8 double-word transfer (32 bytes) can be used.

When the CPU transfer destination address is fixed, data can also be transferred to the FIFO interface. However, in this case, even the SH4 mode supports only the 1 double-word transfer.

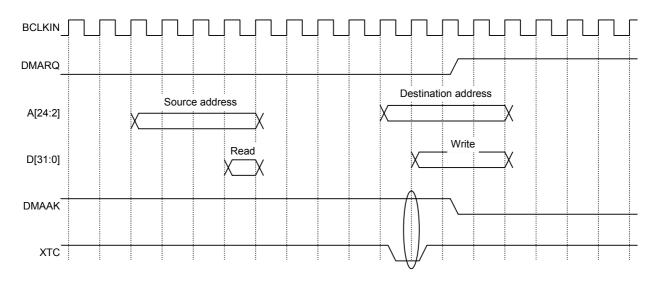

DREQ and DRACK pins and SRAM interface signals are used. In V832, the DREQ, DMAAK, and XTC pins and SRAM interface signals are used.

Note: The SH3 mode supports the direct address mode; it does not support the indirect address mode.

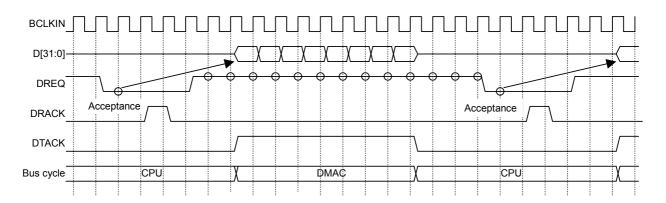

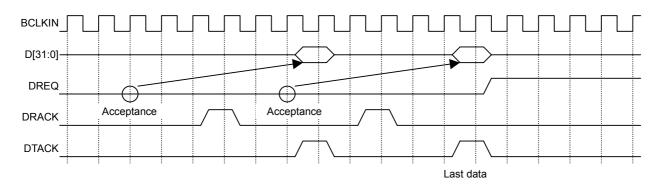

#### Single address mode (FIFO interface)

DMA is performed between host memory (source) and FIFO (destination). Address output from the host CPU is only applied to designate the source, and the data output from the host memory is transferred to the FIFO using the DACK signal. In this mode, data read from the host memory and data write to the FIFO occur in the same bus cycle. This mode does not support data write to the host memory. When the FIFO is full, the DREQ signal is tentatively negated and the DMA transfer is suspended until the FIFO has room for more data.

The 1 double-word transfer (32 bits) and the 8 double-word transfer (32 Bytes) can be used.

DREQ, DTACK, and DRACK signal pins are used.

Note: The single-address mode is supported only in the SH4 mode.

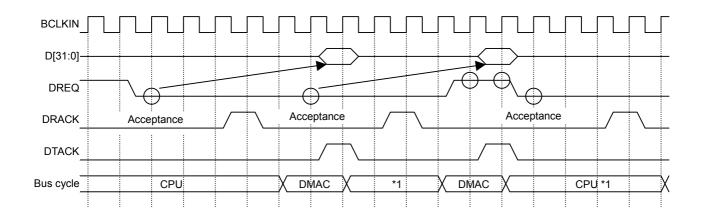

#### 4.3.3 Bus Mode

MB86290A supports the DMA transfer cycle steal mode and burst mode. Either mode is selected by setting to the external DMA mode.

#### Cycle steal mode (In the V832 mode, the burst mode is called the single transfer mode.)

In the cycle steal mode, the bus right is transferred back to the host CPU at every DMA transaction unit. The DMA transaction unit is either 1 double-word (32 bits) or 8 double-words (32 B).

#### Burst mode (In the V832 mode, the burst mode is called the demand transfer mode.)

When DMA transfer is started, the right to use the bus is acquired and the transfer begins. The data transfer unit can be selected from between the 1 double word (32 bits) and 8 double words (32 B).

Note: When performing DMA transfer in the dual-address mode, a function for automatically negating DREQ is provided based on the setting of the DBM register.

#### FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

#### 4.3.4 DMA Transfer Request

#### Single-address mode

DMA is started when the SCARLET issues an external request to DMAC of the host processor.

Set the transfer count in the transfer count register of the SCARLET and then issue DREQ.

Fix the CPU destination address to the FIFO address.

#### Dual-address mode

DMA is started by two procedures: SCARLET issues an external request to DMAC of the host processor, or the CPU itself is started (auto request mode, etc.). Set the transfer count in the transfer count register of SCARLET and then issue DREQ.

Note: The V832 mode requires no setting of the transfer count register.

#### 4.3.5 Ending DMA Transfer

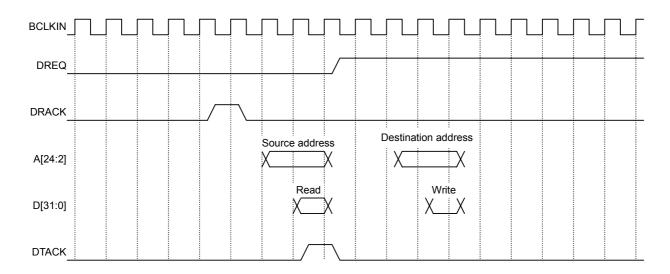

#### SH3/SH4

When the SCARLET transfer count register is set to 0, DMA transfer ends and DREQ is negated.

#### V832

When the XTC signal from the CPU is low-asserted while the DMAAK signal to SCARLET is high-asserted, the end of DMA transfer is recognized and DREQ is negated.

The end of DMA transfer is detected in two ways: the DMA status register (DST) is polled, and an interrupt to end the drawing command (FD000000H) is added to the display list and the interrupt is detected.

PRELIMINARY and CONFIDENTIAL

#### 4.4 Interrupt Request

MB86291A issues interrupt requests to the host CPU. The following events issue interrupt requests. An interrupt request caused by each of these events is enabled/disabled independently by IMR (Interrupt Mask Register).

Vertical synchronization timing detect

Field synchronization timing detect

External synchronization error detect

Command error

Command complete

#### 4.5 Transfer of Local Display List

This is the mode in which the SCARLET internal bus is used to transfer the display list stored in the graphics memory to the FIFO interface.

During transfer of the local display list, the host bus can be used to perform read/write for the CPU.

How to transfer list: Store the display list in the local memory of SCARLET, set the transfer source local address (LSA) and the transfer count (LCO), and then issue a request (LREQ). Whether or not the local display list is currently being transferred is checked using the local transfer status register (LSTA).

**Transfer Path for Local Display List**

#### 4.6 Memory Map

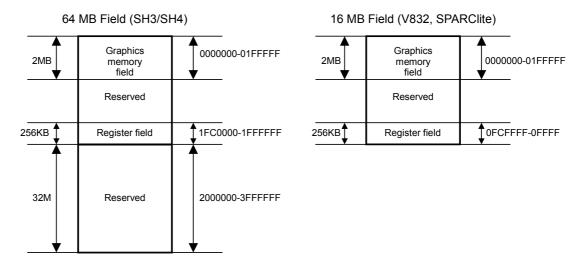

The following table shows the memory map of SCARLET to the host CPU address field. The physical address is mapped differently in each CPU type (SH3, SH4 or V832).

Fig. 4.1 Memory Map

Table 4-3 Address Mapping in SH3/SH4 Mode

| Size  | Resource                  | Base address | (Name)         |

|-------|---------------------------|--------------|----------------|

| 2 MB  | Graphics memory           | 00000000     |                |

| 64 KB | Host interface registers  | 01FC0000     | (HostBase)     |

| 32 KB | Display engine registers  | 01FD0000     | (DisplayBase)  |

| 32 KB | Video capture registers   | 01FD8000     | (CaptureBase)  |

| 64 KB | Internal texture memory   | 01FE0000     | (TextureBase)  |

| 32 KB | Drawing engine registers  | 01FF0000     | (DrawBase)     |

| 32 KB | Geometry engine registers | 01FF8000     | (GeometryBase) |

| 32 MB | Reserved *                | 02000000     |                |

The memory contents of 00000000-01FFFFFF are duplicated in this reserved field.

Table 4-4 Address Mapping in V832, SPARClite Mode

| Size  | Resource                  | Base address | (Name)         |

|-------|---------------------------|--------------|----------------|

| 2 MB  | Graphics memory           | 00000000     |                |

| 64 KB | Host interface registers  | 00FC0000     | (HostBase)     |

| 32 KB | Display engine registers  | 00FD0000     | (DisplayBase)  |

| 32 KB | Video capture registers   | 00FD8000     | (CaptureBase)  |

| 64 KB | Internal texture memory   | 00FE0000     | (TextureBase)  |

| 32 KB | Drawing engine registers  | 00FF0000     | (DrawBase)     |

| 32 KB | Geometry engine registers | 00FF8000     | (GeometryBase) |

# 5. Graphics Memory

## 5.1 Configuration

SCARLET uses local external memory (Graphics Memory) for drawing and display management. The configuration of this Graphics Memory is described as follows:

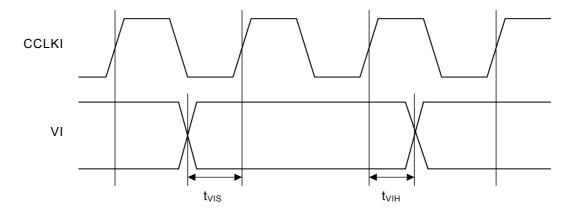

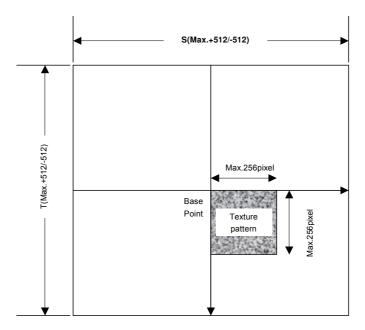

## 5.1.1 Data Type