# WinPLACE<sup>™</sup> Software User's Manual

# Integrated Circuit Technology Corp. September 2000

## **Table of Contents**

| 1                                      | Introduction to WinPLACE™                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1-1                                                                                       |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 1.1<br>1.2<br>1.3<br>1.4               | <ul> <li>WinPLACE<sup>™</sup> Advanced Development Software</li> <li>WinPLACE<sup>™</sup> Features</li> <li>WinPLACE<sup>™</sup> Introduction</li> <li>PEEL<sup>™</sup> Device and PEEL<sup>™</sup> Array support</li> <li>Translation</li> <li>Converting APEEL<sup>™</sup> File ".APL" to WinPLACE<sup>™</sup> File ".PSF"</li> <li>JEDEC File Translation</li> <li>Devices that translate to the PEEL<sup>™</sup> 18CV8</li> <li>Devices that translate to the PEEL<sup>™</sup> 18CV8Z or the PEEL<sup>™</sup> 18LV8Z</li> <li>Devices that translate to the PA7536</li> <li>Devices that translate to the PA7572</li> <li>WinPLACE<sup>™</sup> System Requirements</li> <li>Hard Disk Installation Procedure</li> </ul> | 1-1<br>1-2<br>1-2<br>1-2<br>1-2<br>1-3<br>1-3<br>1-3<br>1-3<br>1-3<br>1-3<br>1-5<br>1-5   |

| 2                                      | Getting Started with WinPLACE™                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                           |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5        | Running the WinPLACE <sup>™</sup> Software<br>Using the Mouse<br>"Click" - press/release left button<br>"Click-R" press/release right button<br>"Click-LH" or press/hold the left button while moving the mouse<br>"Click-RH" and "Click-MH" or press/hold the right and middle button resp<br>while moving the mouse<br>Mouse Support in the WinPLACE <sup>™</sup> Text Editor<br>Mouse Support in the WinPLACE <sup>™</sup> Design Operation<br>Getting HELP<br>Guided Tour through the WinPLACE <sup>™</sup> software<br>The WinPLACE <sup>™</sup> Design Process<br>Design<br>Compile<br>Simulate                                                                                                                       | 2-1<br>2-1<br>2-2<br>2-2<br>pectively<br>2-2<br>2-3<br>2-3<br>2-3<br>2-13<br>2-13<br>2-14 |

| 3                                      | Operation Reference Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-1                                                                                       |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6 | File Menu<br>Design Menu<br>Labeling Methods<br>Renaming labels<br>Operation Menu<br>Options Menu<br>Help Menu<br>Design Operation Pin Block Diagram Right-Click Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-3<br>3-8<br>3-9<br>3-10<br>3-11<br>3-13                                                 |

| 3.7<br>3.8                             | Design Operation – Pin Block Diagram Screen<br>Design Operation – LCC and IOC Screen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-15                                                                                      |

|     | Select Indicators: PEEL™ Arrays (7024, 7540, 7128, 7536, 7140, and 757 Select Indicators in the PEEL™ Devices |      |

|-----|---------------------------------------------------------------------------------------------------------------|------|

| 3.9 |                                                                                                               | 3-22 |

| 3.1 |                                                                                                               |      |

| ••• | Global Cells A and B                                                                                          |      |

|     | Global Signals                                                                                                |      |

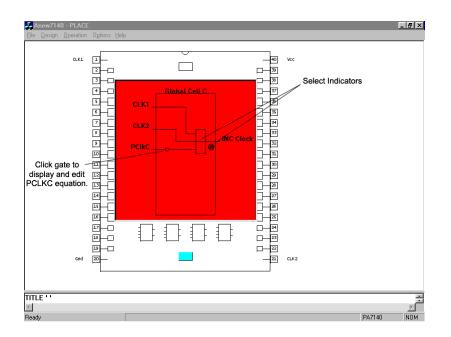

|     | Global Cell C (PA7536, PA7572, PA7128 and PA7140 only)                                                        |      |

| 3.1 |                                                                                                               |      |

| 3.1 | 2 Design Operation – State Diagram Designs                                                                    |      |

| 3.1 |                                                                                                               |      |

| 3.1 |                                                                                                               |      |

| 3.1 |                                                                                                               |      |

| 3.1 |                                                                                                               |      |

|     | Simulate Operation – Waveform Screen                                                                          |      |

|     | Scrolling in the waveform display                                                                             |      |

|     | Functions of the waveform signals                                                                             | 3-38 |

| 3.1 | 7 Simulate Operation – Simulate Menu                                                                          | 3-39 |

| 3.1 | 8 Test Vectors for Asynchronous Clock – Sum or Product term clock                                             | 3-41 |

| 3.1 | 9 Preloading the LCC registers (in logic simulation only)                                                     | 3-42 |

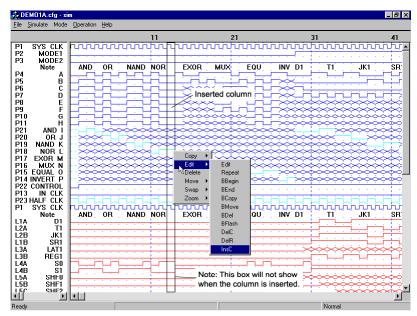

| 3.2 | 20 Simulation Operation – Entering or Editing Waveforms                                                       | 3-43 |

| 3.2 | 21 Simulation Operation – Organizing Waveforms                                                                | 3-47 |

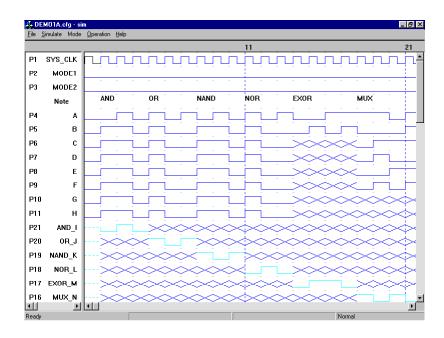

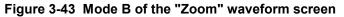

| 3.2 | 22 Simulate Operation – Zoom Command                                                                          | 3-49 |

| 3.2 | 23 Simulate Operation – PSF Command                                                                           | 3-50 |

|     | Paging Up and Down                                                                                            | 3-51 |

|     | Sizing the Display Window                                                                                     | 3-51 |

|     | Moving the Display Window                                                                                     |      |

| 3.2 |                                                                                                               |      |

|     | Using a mouse in the editor                                                                                   | 3-53 |

|     | Sizing the Text Editor                                                                                        |      |

|     | Paging Up and Down                                                                                            | 3-54 |

| 4   | WinPLACE™ Design Language                                                                                     | 4-1  |

| 4.1 | Introduction                                                                                                  |      |

|     | WinPLACE™ Source File Format                                                                                  | 4-1  |

| 4.2 | 2 Design Description                                                                                          | 4-6  |

|     | Title                                                                                                         | 4-6  |

|     | Designer                                                                                                      | 4-6  |

|     | Date                                                                                                          | 4-6  |

|     | Description                                                                                                   |      |

| 4.3 | B Device Type                                                                                                 | 4-7  |

| 4.4 |                                                                                                               |      |

|     | Security Bit                                                                                                  |      |

|     | Signature Word                                                                                                |      |

| 4.5 |                                                                                                               |      |

| 4.6 |                                                                                                               |      |

| 4.7 |                                                                                                               |      |

|     | Parameters for the INC Format (PA7536, 7572, 7128 and 7140 only)                                              |      |

|     | Parameters for the IOC Format (PEEL <sup>™</sup> Arrays only)                                                 | 4-11 |

|   |      | Parameters for the LCC Format (PEEL <sup>™</sup> Arrays only)    |     |

|---|------|------------------------------------------------------------------|-----|

|   |      | Parameters for the IOC Format (PEEL <sup>™</sup> Devices)        |     |

|   | 4.8  | Global Configurations                                            |     |

|   |      | PEEL™ Arrays                                                     |     |

|   |      | PEEL <sup>™</sup> Devices                                        |     |

|   | 4.9  | Comments                                                         |     |

|   | 4.10 | Macro Definitions                                                |     |

|   |      | Macro Constants                                                  |     |

|   |      | Macro Equations                                                  |     |

|   |      | Macro State Cell Assignments for STATE DIAGRAMS                  |     |

|   |      | Macro Set Variables in State Diagrams                            |     |

|   |      | Macro Cell Allocation for Truth Tables                           |     |

|   |      | Macro Counter Function                                           |     |

|   | 4.11 | State Diagrams                                                   |     |

|   |      |                                                                  |     |

|   |      |                                                                  |     |

|   |      | WITH-ENDWITH                                                     |     |

|   |      | Register Types of the "allocated" state cells                    |     |

|   |      | Outputs of the State Diagram                                     |     |

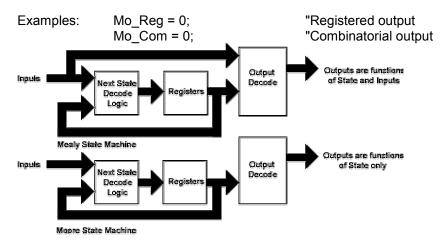

|   |      | Mealy Machine                                                    |     |

|   |      | How the WinPLACE <sup>™</sup> State Diagram works                |     |

|   | 1 12 | Truth Tables                                                     |     |

|   | 4.12 |                                                                  |     |

|   | 4.15 | Functions of the Dot Extensions in the equation labels           |     |

|   |      | Logic Reduction Compiler Directive (For Equations Only)          |     |

|   |      | Equations of the Outputs used for State Diagrams or Truth Tables |     |

| 5 |      | WinPLACE <sup>™</sup> Application Examples                       |     |

| 5 |      |                                                                  |     |

|   | 5.1  | Overview                                                         | 5-1 |

|   | 5.2  | DEMO1 A.PSF PA7540                                               |     |

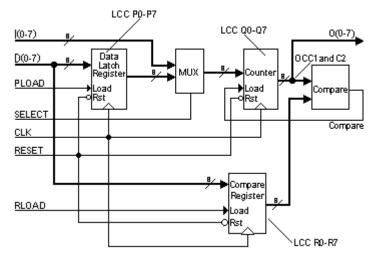

|   | 5.3  | TIMER.PSF PA7024                                                 |     |

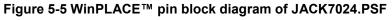

|   | 5.4  | JACK7024.PSF PA7024                                              |     |

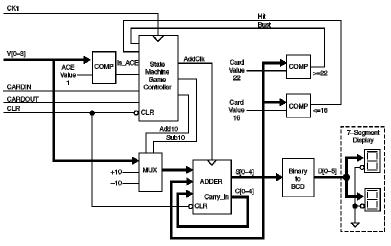

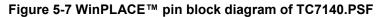

|   | 5.5  | TC7140.PSF PA7140                                                |     |

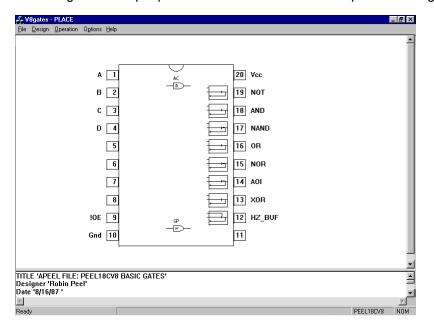

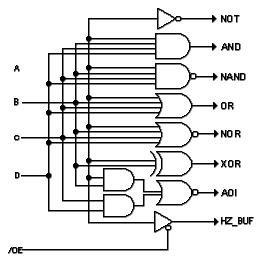

|   | 5.6  | V8GATES.PSF PEEL18CV8                                            |     |

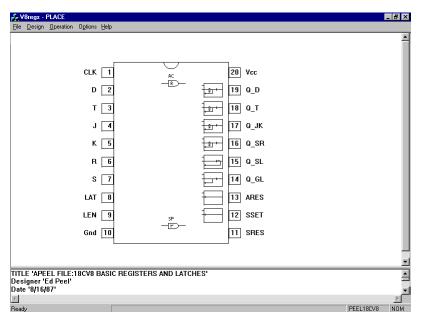

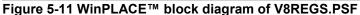

|   | 5.7  | V8REGS PEEL18CV8                                                 |     |

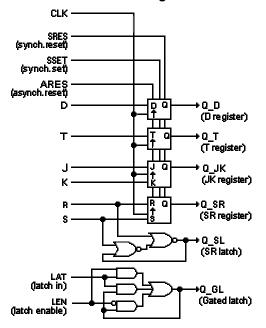

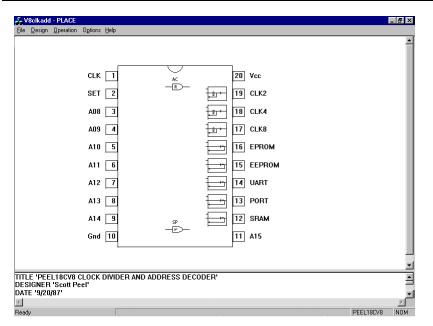

|   | 5.8  | V8CLKADD.PSF PEEL18CV8                                           |     |

# **1.1 WinPLACE™ Advanced Development Software**

Welcome to the WinPLACE<sup>™</sup> Advanced Development Software from Integrated Circuit Technology Corporation. WinPLACE<sup>™</sup> (PEEL<sup>™</sup> Logic Architectural Compiler and Editor) is an enhanced development package that offers complete support for ICT's family of PEEL<sup>™</sup> (Programmable Electrically Erasable Logic) Arrays and Devices.

The WinPLACE<sup>™</sup> Advanced Development Software is free to qualified PLD users. To obtain a copy of WinPLACE<sup>™</sup> please contact your local <u>ICT</u> representative.

#### WinPLACE<sup>™</sup> Features

#### Architectural Editor

WinPLACE<sup>™</sup> incorporates an innovative architectural editor that graphically illustrates and controls the architectures, logic equations, state-diagram and truth-table entries, hence making the overall design easy to understand while allowing for optimum utilization.

#### Logic Compiler

The WinPLACE<sup>™</sup> compiler performs logic transformation, allowing equations to be specified in a variety of formats. The compiler also features five levels of user-selectable logic reduction (including "auto-demorganization") making it possible to fit more logic into every design.

#### Logic Simulator

WinPLACE<sup>™</sup> provides a multi-level logic simulator that lets the external and internal signals be fully simulated, analyzed and edited via a graphically illustrated waveform display.

# **1.2 WinPLACE™ Introduction**

The WinPLACE<sup>™</sup> Software portion of this description is organized in six sections. Before trying to design with the WinPLACE<sup>™</sup> software, make sure you read through the three sections: "Introduction", "Installation" and "Getting Started". By doing so you will save yourself time.

After you have completed installing the WinPLACE<sup>™</sup> software and have become familiar with the basic operations, you can refer to the "Operation Reference Guide" and "WinPLACE<sup>™</sup> Design Language Reference Guide" section as you implement your first design. Documentation describing several application examples is provided in Chapter 5. These examples are also included on diskette and will automatically be loaded during installation.

While using this manual and the software you may need to reference the product specifications in the data book.

The software operations and features described in this manual are referenced to WinPLACE<sup>™</sup> Version 0.5.4. For additional information on new features and manual corrections, please refer to the README.DOC file on the WinPLACE<sup>™</sup> disk.

# **1.3 PEEL<sup>™</sup> Device and PEEL<sup>™</sup> Array support**

The devices supported in the WinPLACE<sup>™</sup> software include:

#### PEEL™ Arrays

| -                         |              |               |

|---------------------------|--------------|---------------|

| PA7024                    | PA7128       | PA7140        |

| PA7536                    | PA7540       | PA7572        |

| PEEL <sup>™</sup> Devices |              |               |

| PEEL™18CV8                | PEEL™18CV8Z  | PEEL™18LV8Z   |

| PEEL™16CV8                | PEEL™22CV10A | PEEL™22CV10AZ |

| PEEL™22LV10AZ             |              |               |

|                           |              |               |

Additional devices will be supported in future software versions.

### 1.4 Translation

#### Converting APEEL<sup>™</sup> File ".APL" to WinPLACE<sup>™</sup> File ".PSF"

ICT has discontinued further development of its original PEEL<sup>™</sup> software named APEEL. WinPLACE<sup>™</sup> now supports all products. If you still use APEEL for development your designs can be converted to the WinPLACE<sup>™</sup> design language format. This allows the WinPLACE<sup>™</sup> enhanced features available for the PEEL<sup>™</sup> Arrays to be used to implement designs for the lower density PEEL<sup>™</sup> devices.

Use Translators  $\rightarrow$  APEEL to PSF under the Options menu in the design window to convert your designs.

The extension of the filename defaults to ".APL" if not specified.

#### **JEDEC File Translation**

The JEDEC-file translation utility of the WinPLACE<sup>™</sup> Software translates JEDEC files created for programming other PLD's (PAL's, GAL's, EPLD's etc.,) to JEDEC files used for programming PEEL<sup>™</sup> Devices. The translated JEDEC file will program a PEEL<sup>™</sup> Device to be a pin-to-pin replacement for the original PLD.

The JEDEC file translation is available in Options  $\rightarrow$  Translators  $\rightarrow$  JEDEC to JEDEC in the design window.

The translated PEEL<sup>™</sup> JEDEC file is given the name of the original file with the ".JED" extension modified to ".JEX". The ".JEX" file can then be used to program your PEEL<sup>™</sup> devices.

| <i>lev</i> | ices that transie | ale to the PEEL |          |          |

|------------|-------------------|-----------------|----------|----------|

|            | PAL16L8           | PAL16R8         | PAL16R6  | PAL16R4  |

|            | PAL16P8           | PAL16RP8        | PAL16RP6 | PAL16RP4 |

|            | PAL10L8           | PAL12L6         | PAL14L4  | PAL16L2  |

|            | PAL10H8           | PAL12H6         | PAL14H4  | PAL16H2  |

|            | PAL16H8           | PAL16LD8        | PAL16HD8 | PAL18P8  |

|            | PAL18V8           | GAL16V8         | EP310    | EP320    |

|            | 5C031             | 5C032           | EP330    | PAL18U8  |

|            | PALCE16V8         | 85C220          |          |          |

# Devices that translate to the PEEL<sup>™</sup>18CV8

#### Devices that translate to the PEEL<sup>™</sup>22CV10A

| PAL20L8   | PAL20R8   | PAL20R6   | PAL20R4    |

|-----------|-----------|-----------|------------|

| PAL20L10  | PAL20L2   | PAL18L4   | PAL16L6    |

| PAL14L8   | PAL12L10  | PAL22V10  | PAL20G10   |

| PAL20AP10 | PAL20RP8  | PAL20RP6  | PAL20RP4   |

| PAL20ARP4 | PAL20ARP6 | PAL20ARP8 | PAL20ARP10 |

| GAL20V8   | PALCE20V8 | GAL22V10  |            |

# Note: For any devices on the following list, please contact ICT Technical Support for translations

# Devices that translate to the PEEL™18CV8Z or the PEEL™18LV8Z

PLC18V8Z35/I PLC18V8Z25/IA

#### **Devices that translate to the PA7536**

| Lattice      |              |              |              |  |

|--------------|--------------|--------------|--------------|--|

| 26CV12B-15LP | 26CV12B-15LJ | 26CV12B-20LP | 26CV12B-20LJ |  |

|              | Vantis (AMD) |              |              |  |

| 24V10H-15P   | 24V10H-15J   | 24V10H-25P   | 24V10H-25J   |  |

| 26V10H-15P   | 26V10H-15J   | 26V10H-25P   | 26V10H-25J   |  |

### Devices that translate to the PA7540

| Altera       |              |              |              |

|--------------|--------------|--------------|--------------|

| EP312        | EP600PC      | EP600PC-45   | EP600PC-3    |

| EP600DC*     | EP600DC-3*   | EP610PC-35   | EP610PC-30   |

| EP610PC-25T  | EP610PC-25   | EP610PC-20T  | EP610PC-20   |

| EP610PC-15T  | EP610PC-15   | EP610PI-30   | EP610DC-35*  |

| EP610DC-30*  | EP610DI-35*  | EP610DI-30*  | EP610SC-25   |

| EP610DC-20   | EP610DC-15   |              |              |

|              | Atı          | mel          |              |

| ATV750-20DC* | ATV750-20GC* | ATV750-20JC  | ATV750-20KC* |

| ATV750-20PC  | ATV750-20SC  | ATV750-25DC* | ATV750-25GC* |

| ATV750-25JC  | ATV750-25KC* | ATV750-25PC  | ATV750-25SC  |

| ATV750-30DC* | ATV750-30GC* | ATV750-30JC  | ATV750-30KC* |

| ATV750-30PC  | ATV750-30SC  | ATV750-35DC* | ATV750-35GC* |

| ATV750-35JC  | ATV750-35KC  | ATV750-35PC  | ATV750-35SC  |

|              | Сур          | ress         |              |

| 20RA10-15PC  | 20RA10-15WC* | 20RA10-20PC  | 20RA10-20WC* |

| 7C324-A15HC* | 7C324-A15JC  | 7C324-A20HC* | 7C324-A20JC  |

|              | In           | tel          |              |

| PPLD610-15   | PDLD610-15*  | PPLD610-25   | PDLD610-25*  |

| D5C060-45*   | P5C060-45    | D5C060-55*   | P5C060-55    |

| D5AC312-25*  | P5AC312-25   | D5AC312-30*  | P5AC312-30   |

|              | Lat          | tice         |              |

| 20RA10-15LP  | 20RA10-15LJ  | 20RA10-20LP  | 20RA10-20LJ  |

| 20RA10-30LP  | 20RA10-30LJ  | 20XV10B-15LP | 20XV10B-15LJ |

| 20XV10B-20LP | 20XV10B-20LJ | 6001B-30LP   | 6001B-30LJ   |

| 6002B-15LP   | 6002B-15LJ   | 6002B-20LP   | 6002B-20LJ   |

|              | Nati         | onal         |              |

| 20RA10-15NC  | 20RA10-20NC  | 20RA10-25NC  | 20RA10-15VC  |

| 20RA10-20VC  | 20RA10-25VC  | 6001-30LNC   | 6001-30LVC   |

| Philips     |             |             |              |  |

|-------------|-------------|-------------|--------------|--|

| PLS173N     | PLS173BN    | PLS179N     | PLC42VA12FA* |  |

| PLC42VA12N  | PLCVA12A    |             |              |  |

| TI          |             |             |              |  |

| EP630-15CNT | EP630-20CNT |             |              |  |

|             | Vantis      | (AMD)       |              |  |

| 29M16H-25P  | 29M16H-25J  | 29MA16H-25P | 29MA16H-25J  |  |

| 610H-15P    | 610H-25P    | 20RA10H-20P | 20RA10H-20J  |  |

\*These devices use ceramic DIP or J-lead packages; the equivalent ICT device uses plastic devices.

#### Devices that translate to the PA7572

| Altera      |             |            |             |  |

|-------------|-------------|------------|-------------|--|

| EP910L      | EP900PC     | EP900PC-3  | EP900PC-2   |  |

| EP910PC-40  | EP910PC-35  | EP910PC-30 | EP910PC-30T |  |

| EP910DC-40* | EP910DC-35* | EP910DC30* |             |  |

|             | In          | tel        |             |  |

| PPLD910-15  | DPLD910-15* | PPLD910-25 | DPLD910-25* |  |

| D5C090-50*  | P5C090-50   | D5C090-60  | P5C090-60   |  |

\*These devices use ceramic DIP or J-lead packages; the equivalent ICT device uses plastic devices.

# **1.5 WinPLACE™ System Requirements**

- IBM PC-AT, 386, 486, Pentium or compatible

- Minimum 32 MB of RAM

- A hard disk with at least 8.0 MB of free space

- · Logitech or Microsoft mouse with driver

- Windows 95 or 98

## **1.6 Hard Disk Installation Procedure**

- Please uninstall any earlier versions of WinPLACE software you may have on your computer before you install this version.

- Turn the computer on.

- Boot-up Windows 95 or 98.

- Insert the WinPLACE<sup>™</sup> CD into your CD-ROM drive.

- Open your CD drive and click on the Setup program. This will automatically load the installation process.

- Click "Next" on the Welcome screen.

- Read and accept the software license agreement.

- Now you will be asked for the destination folder. The default is: C:\Program Files\WinPLACE\ If this is ok, click "Next". If you would like to change the destination folder click "Browse". Select the folder you want, then click "OK" followed with "Next".

- Finally, add a program icon to the "Program Folder", which will be placed in the "Start Menu". The default directory is "WinPLACE". Click "Next" when done.

- The WinPLACE<sup>™</sup> installer will now copy the correct files onto your hard drive. When it is done, click "Finish".

- Setup is now complete.

# **2** Getting Started with WinPLACE<sup>TM</sup>

# 2.1 Running the WinPLACE<sup>™</sup> Software

Once WinPLACE<sup>TM</sup> is properly installed; it can be invoked in one of three ways:

- 1) Click on the "Start" menu, and then click on "Programs". Click on WinPLACE™

- 2) Double-click on the "My Computer" folder on the desktop. Then, open the drive that WinPLACE™ was installed in. Locate the WinPLACE folder (it is most likely in the Program Files folder). Open the folder and double-click on the WinPLACE™ program (place\_w5.exe).

- Create a shortcut for WinPLACE<sup>™</sup> and place it on the desktop. Then, from now on, open the program by double-clicking on the shortcut.

Before using the WinPLACE<sup>™</sup> software, please read through the following sections on "Using the Mouse" and "Getting HELP"

### 2.2 Using the Mouse

The WinPLACE<sup>™</sup> software and manual will commonly refer to several mouse actions using the nomenclatures specified in Table 2-1.

| Term              | Mouse Action                                                                                                                                                           |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Click             | Press/release the left button of the mouse.                                                                                                                            |

| Click - R         | Press/release the right button of the mouse.                                                                                                                           |

| Click - LH        | Press/hold the left button of the mouse while moving the mouse.                                                                                                        |

| Click - RH        | Press/hold the right button of the mouse while moving the mouse.                                                                                                       |

| Double - Click    | Press/release the left button twice.                                                                                                                                   |

| The Middle Button | The middle button is not used in WinPLACE™.<br>However, if your mouse comes equipped with a scroll<br>button in the middle, it may be used only in the Text<br>Editor. |

#### Table 2-1 Nomenclatures for WinPLACE mouse actions

#### "Click" - press/release left button

"Click" is used in all operations and modes to make a selection. Make a selection by moving the mouse cursor to the desired item and then press/release the left button of the mouse. In many cases the selected item

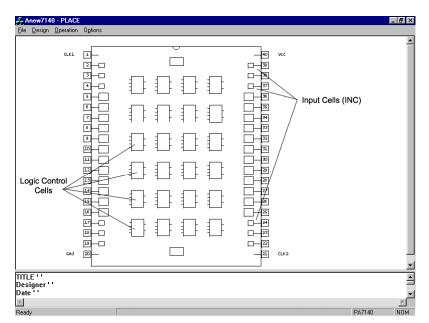

will be highlighted. Items that can be selected include pop-down and pop-up menu windows, architectural elements in the design operation such as Logic Control Cells (LCC), I/O Cells (IOC), Input Cells (INC), Global Cells (GBC), test vector waveforms (Simulate operation), etc.

#### "Click-R" press/release right button

"Click-R" in most cases is used to exit, complete or return from the current function being performed. It also has two different functions in the Pin Block Diagram and in the Text Editor. In the Pin Block Diagram, it displays a popup menu, which contains the commands: "Copy", "Swap", and "Clear". In the Text Editor, it displays a different pop-up menu containing the commands: "Undo", "Cut", "Copy", "Paste", "Delete", and "Select All".

#### "Click-LH" or press/hold the left button while moving the mouse

Click-LH is used in the Design and Simulate operations and also in the Text Editor. In the Design operation, it is used to scroll from one LCC/IOC to another in the LCC/IOC screen. In the Simulate operation, it is used for panning in the waveform screen as well as block selection for the copy, move, and delete functions in the "Edit" mode.

#### "Click-RH" and "Click-MH" or press/hold the right and middle button respectively while moving the mouse

For 3-button mouse systems, click-MH (click-RH for 2-button mouse) is used to display the menu options in the WinPLACE<sup>™</sup> text editor utilized in the Design operation. While holding the middle mouse button down (right button for 2-button mouse), move the mouse cursor and click at the menu option. Once the option is selected, the middle button can be released.

#### Mouse Support in the WinPLACE<sup>™</sup> Text Editor

The mouse is supported in the WinPLACE<sup>™</sup> Text Editor and Compile Operation. You can find the Text Editor at the bottom of the screen in the Design and Compile functions. Refer to Section 3.24 "WinPLACE<sup>™</sup> Text Editor" for detailed information on the Text Editor. To initiate the mouse support, right click in the WinPLACE<sup>™</sup> Text Editor. A pop-down menu will appear next to the cursor containing the following commands:

- Undo......Reverses the last action that was made in the editor.

- Copy.....Copies the currently highlighted text into the computer's clipboard.

- Cut.....Almost the same as the "Copy" function however, it clears the text as well as copying it onto a clipboard.

- Paste......Re-inserts the text that was either "Cut" or "Copied" from the document.

- Delete......This is simply to clear the highlighted text without using the keyboard.

- Select All...This function will highlight <u>all</u> of the text in the WinPLACE™ Text Editor.

#### Mouse Support in the WinPLACE<sup>™</sup> Design Operation

The mouse is also supported in the WinPLACE<sup>™</sup> Design Operation. This is mainly for the Pin Block Diagram screen. For the Text Editor mouse support, refer to the above. To initiate the mouse support, right click in the WinPLACE<sup>™</sup> Pin Block Diagram screen. A pop-down menu will appear next to the cursor containing the following commands:

- Copy......Copies the selected cell and all of its configurations (except the Label) into the computer's clipboard.

- Swap......Switches two I/O cells, two Input cells, or two logic control cells with each other. (i.e., I/O-to-I/O or Input-to-Input or LCC-to-LCC)

- Clear......Deletes all the user-entered attributes on the cell, reverting it to a default cell.

# 2.3 Getting HELP

The WinPLACE<sup>™</sup> software incorporates an on-line HELP feature, which provides information and procedures for most WinPLACE<sup>™</sup> functions and modes. A general HELP menu is provided in the Help pop-down menu.

# 2.4 Guided Tour through the WinPLACE<sup>™</sup> software

To quicken the learning process, this section discusses some basic procedures commonly used in the WinPLACE<sup>™</sup> software. The device used in this guided tour is the PA7540. Some of the terms used in this section may only be applicable to the PA7540 device (or the PEEL<sup>™</sup> Array family of devices). For instance, terms such as LCC (Logic Control Cell) and GBC (Global Cell) pertain only to devices in the PEEL<sup>™</sup> Array family.

If you are a first-time WinPLACE<sup>™</sup> user, ICT recommends that you run the WinPLACE<sup>™</sup> software while reading this section. By actually performing the instructions (specified in italics), you will be able to get a more complete understanding of the features, modes or functions found in the WinPLACE<sup>™</sup> software.

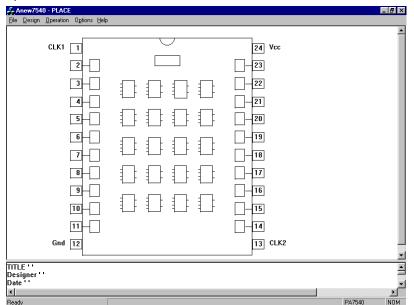

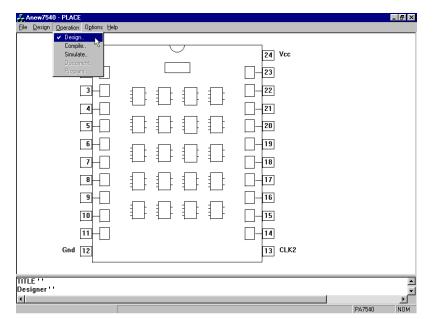

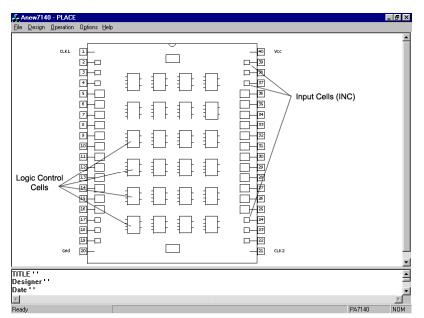

There are three main operations that can be performed with WinPLACE<sup>™</sup>: Design, Compile, and Simulate. When first entering WinPLACE<sup>™</sup>, it will default to the Design Operation. The display will show the PA7540 PEEL<sup>™</sup> Array pin block diagram (Figure 2-1).

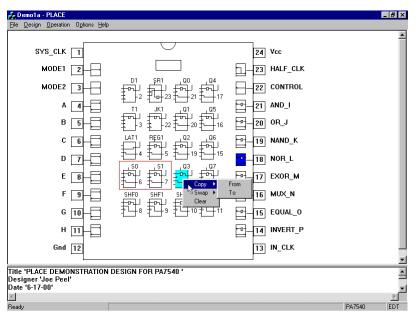

Note that WinPLACE<sup>™</sup> automatically loads the ANEW template file upon initial boot-up. In Figure 2-1, the WinPLACE<sup>™</sup> software has loaded the ANEW file (ANEWPA7540.PSF) for the PA7540 device. There is an ANEW template file for each device supported by the WinPLACE<sup>™</sup> software. For instance, the ANEWPA7140.PSF file is the template file for the PA7140 device. Each ANEW file contains the device's default cell configurations.

At the top of the screen, there are five pop-down menu options: File, Design, Operation, Utilities, and Options (available only in the Design operation). Move the mouse cursor to the "Operation" menu. A pop-down window will appear showing the three main operations (Figure 2-2). Note the menu option titled "Design" to the left of the Operation menu. This menu is called the "command" menu. Each time a new operation is selected, this command menu will change to allow the selection of commands specific for that

operation. The command menu is also used as an indicator for the current operation.

| 🚑 Anew7540 - PLACE                                       |                      | _ 8 ×      |

|----------------------------------------------------------|----------------------|------------|

| File Design Operation Options Help                       |                      |            |

| ✓ Design.<br>Compile.<br>Simulate<br>Document<br>Program | 24 Vcc               |            |

|                                                          | 22<br>21<br>20<br>19 |            |

|                                                          |                      |            |

|                                                          |                      |            |

| Gnd 12                                                   | 13 CLK2              |            |

|                                                          |                      | PA7540 NOM |

#### Figure 2-2 The Operations pop-down menu

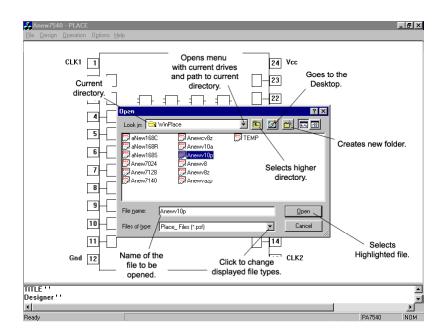

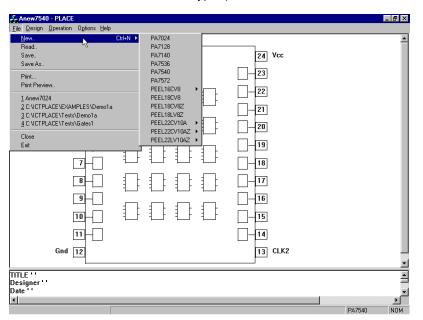

Move the mouse cursor to the "File" menu option and Click the "Read" command. A list of example WinPLACE<sup>™</sup> Source Files (.PSF) will appear (Figure 2-3). The design examples provided with the WinPLACE<sup>™</sup> software include:

- · Multiple-Application Design Example (PA7540, DEMO1A.PSF)

- · 8-Bit Counter with Hold, Reset and Preset (PA7024, COUNTER1 .PSF)

- · Bi-Directional I/O Port (PA7024, BI\_PORT.PSF)

- · Bus Programmable Clock Generator/Timer (PA7024, TIMER.PSF)

- · Blackjack Machine Example (PA7024, JACK7024.PSF)

- · Timer/Counter (PA7140, TC7140.PSF)

- . Register Configurations (REG7536.PSF)

- · Basic Gates (18CV8, V8GATES.PSF)

- · Basic Registers and Latches (18CV8, V8REGS.PSF)

- · Clock Divider and Address Decoder (18CV8, V8CLKADD.PSF)

- · Bus Programmable 8-to-1 Multiplexer (18CV8, V8BUSMUX.PSF)

- · 8-Bit Counter with Function Controls (18CV8, V8FCNTR.PSF)

- · Change-of-state Input Port with Interrupt (18CV8, V8CPORT.PSF)

- · Octal Synchronization Circuits (18CV8, V8SYNC.PSF)

- · 8-Bit Up/Down Loadable Counter with Carry-out or Borrow-in (PEEL22CV10A, V10CNT8.PSF)

- · 9-Bit Even/Odd Parity Generator/Checker (PEEL22CV10A, PARV10A.PSF)

- · 8-Bit Change-of-State Input Port with Interrupt (PEEL22CV10A+, V10ZPORT.PSF)

As shown in Figure 2-3, there are two methods of making a selection from the file menu window:

1. Click to highlight a file or directory and then click the "Open" button.

2. "Double-Click" at the file or directory. The first click highlights the selection and makes the name appear in the "File Name" text box. The second click makes the selection.

#### Figure 2-3 Reading a demonstration file from the File menu

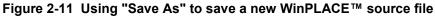

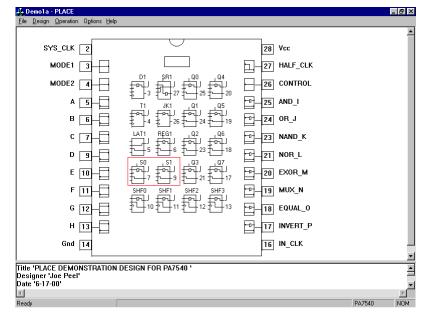

*Click the DEMO1A.PSF file.* The WinPLACE<sup>™</sup> Design operation will once again be displayed, but this time with the DEMO1A demonstration design tile. For more detailed information on the demonstration example files refer to Chapter 5 of this manual.

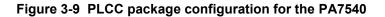

| 👍 Demo1a - PLACE                                                      |                                        |               |             | _ 8 ×    |

|-----------------------------------------------------------------------|----------------------------------------|---------------|-------------|----------|

| <u>File</u> <u>Design</u> <u>Operation</u> <u>Options</u> <u>Help</u> |                                        |               |             |          |

| Edit Eqn.,                                                            |                                        |               |             | <b></b>  |

| Description. N 1                                                      |                                        | 24 Vcc        |             |          |

| Allocate  2 Macro                                                     | D1 \$R1 ,Q0 ,Q4                        | HALF_CLK      |             |          |

| Auxiliary 3<br>Global>2                                               |                                        |               |             |          |

| A 4                                                                   |                                        | 21 AND_I      |             |          |

| B 5                                                                   |                                        | -20 OR_J      |             |          |

| C 6                                                                   |                                        | 19 NAND_K     |             |          |

| D 7                                                                   |                                        |               |             |          |

| E 8                                                                   |                                        | TT EXOR_M     |             |          |

| F 9                                                                   | SHF0 SHF1 SHF2 SHF3<br>문자니 문자니 문자니 문자니 | 16 MUX_N      |             |          |

| G 10                                                                  | ₽₩8 ₽₩9 ₽₩10₽₩11                       | 15 EQUAL_0    |             |          |

| + 11-□                                                                |                                        | P-14 INVERT_P |             |          |

| Gnd 12                                                                |                                        | 13 IN_CLK     |             | <br>• 1  |

| Title 'PLACE DEMONSTRATION D                                          | ESIGN FOB PA7540 '                     |               |             |          |

| Designer 'Joe Peel'                                                   | 201011-01010-0                         |               |             |          |

| Date 6-17-00                                                          |                                        |               |             | <b>_</b> |

| <u> </u>                                                              |                                        |               | - Income of | Þ        |

|                                                                       |                                        |               | PA7540      | NOM      |

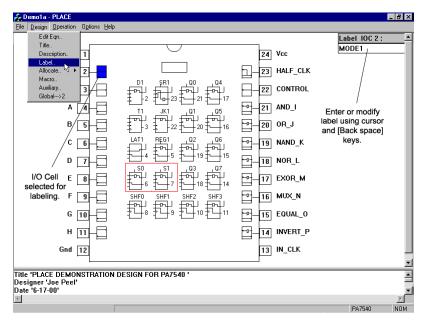

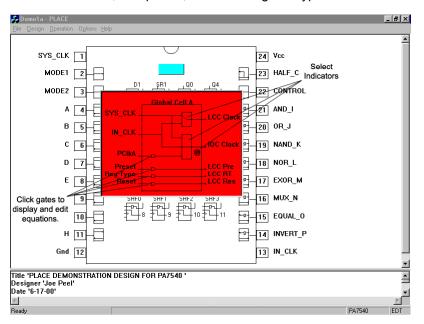

Figure 2-4 The "Design" command menu

Once the file is loaded, move the mouse to the "Design" menu option at the top of the screen (Figure 2-4). Click at the "TITLE" command. The cursor in the text edit area will automatically skip the "TITLE" section between the single quotation marks. The title of the design can now be entered with your keyboard (Figure 2-5). Use the down/up arrows or click to move the cursor to the next Title field.

Move the cursor to the next line labeled, "Designer." (Figure 2-5) Click between the single quotation marks to edit the name of the current designer. The program does not require this, but it is convenient for other user reference.

By clicking to the next line, labeled "Date," you can edit the last entered date. (Figure 2-5) This option is convenient to signify when the device was created, edited last, completed, etc. This option is liable to change at any time, without affecting the device.

Move the mouse cursor back to the "Design" menu option and click the command listed as "Description". (Figure 2-5) This procedure allows the design description to be entered or modified by having the WinPLACE<sup>™</sup> software automatically move the text cursor to the "Description" area in the Text Editor.

The size of the Text Editor may be freely changed to add or subtract view space of both sections in the window. Click-LH (left-click and hold) on the line that separates the Text Editor and the Pin Block Diagram, then drag it up or down to increase/decrease the window of your choice. In Figure 2-5 the size of the Text Editor has been increased, blocking out some of the Diagram.

| 🚣 Demo1a - PLACE                          |                                                                       |                              | _ 8 × |

|-------------------------------------------|-----------------------------------------------------------------------|------------------------------|-------|

| <u>File Design Operation Options Help</u> |                                                                       |                              |       |

|                                           |                                                                       |                              | -     |

| SYS_CLK 1                                 |                                                                       | 24 Vcc                       |       |

| MODE1 2                                   |                                                                       | 1 – 23 HALF_CLK              |       |

| MODE2 3                                   |                                                                       | 22 CONTROL                   |       |

| A 4                                       |                                                                       | 21 AND_I                     |       |

| B 5                                       |                                                                       | -20 OR_J                     |       |

| C 6                                       | LAT1 REG1 , Q2 , Q6<br>1 - 고리 두자리 두자리 두자리                             | 19 NAND_K                    |       |

| The Title can be                          |                                                                       | 18 NOR_L                     |       |

| typed in here.                            | Fml         Fml         Fml           1         6         1         1 | TT EXOR_M                    |       |

|                                           | Enter the Designe                                                     | er's name hereN              |       |

| Put the Date in t                         | the this section.                                                     |                              |       |

| G 10                                      |                                                                       | 15 EQUAL_0                   | -     |

| Title PLACE DEMONSTRATION                 | DESIGN FOR PA7540 '                                                   |                              |       |

| Designer 'Joe Peel'                       |                                                                       |                              | _     |

| Date '6-17-00'                            |                                                                       |                              |       |

| Description<br>PLACE Demonstration [      | Design for PA7540                                                     | Update the Description here. |       |

| <br>  This design example impleme         | nts four applications in one PA7540.                                  |                              | -1    |

| <u>م</u>                                  |                                                                       |                              |       |

| Ready                                     |                                                                       | PA7540                       | NOM   |

#### Figure 2-5 The "Description" window

From the pin block diagram screen move the mouse cursor to the "Design" menu option and click the "Label" command. A window will appear containing two parts. The top part should be gray and the bottom part should be white, both are empty. Now move the cursor to one of the Logic Control Cells (LCC's), Input/Output Cells (IOC's), or Input Cells (INC's - PA7140 only) and click the mouse button. The window will now display the current label (or name) for that Cell. The gray (top) half of the window will contain the name of the cell selected, and the white (bottom) half of the window will display the user-given label. Figure 2-6 shows that I/O cell #2 was selected in the Label mode. To change the label, use the [Back Space] key and type in the new label followed by the [Enter] key. If the label is

already blank then simply type in the new label followed by the [Enter] key. The Label command is used to define all IOC's, INC's and LCC's that are used in a design.

The architecture of the LCC's, IOC's, or INC's can be configured prior to labeling. However, labels must be specified before the equations, statediagrams, or truth-tables can be entered. Click-R once to exit the "Label" mode. Please refer to Chapter 3 "Operation Reference Guide" for options on the "Label" command.

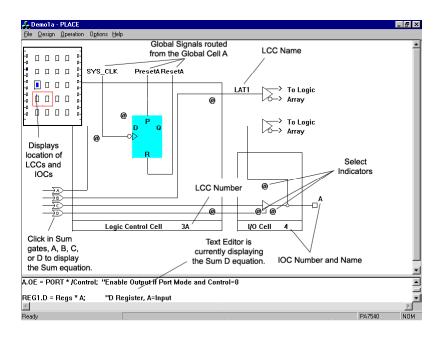

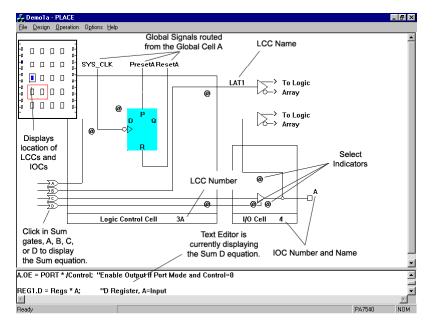

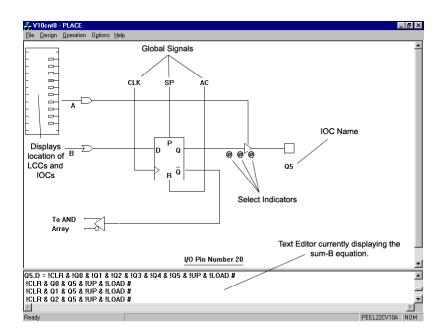

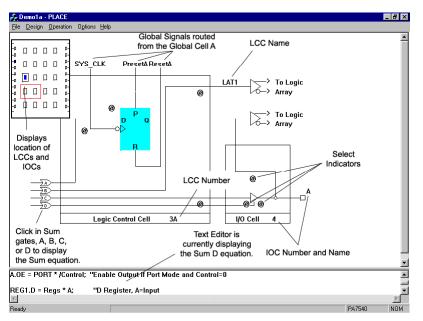

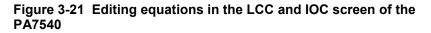

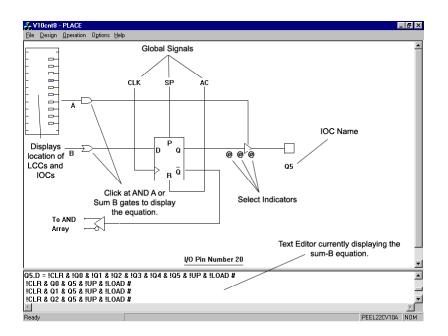

Now, move the cursor to one of the LCC's. Note that both the LCC and its interconnected IOC will be highlighted. Click the mouse to bring up the associated "LCC and IOC Screen". This screen displays a close-up view of the selected LCC and its associated IOC configuration.

Figure 2-6 The "Label" command for Pin, INC, IOC and LCC

#### Figure 2-7 Configuring the LCC and IOC Architecture

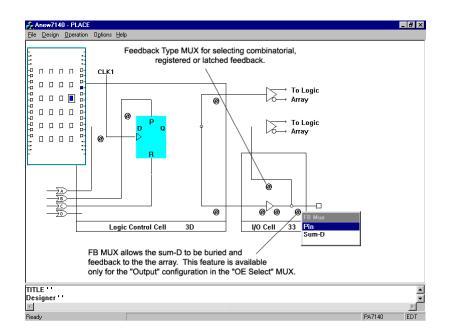

Select the configuration of the cells by clicking at any of the "Select Indicators" (Figure 2-7). With the PA7540 device, over 4000 configurations can be selected by clicking at each of the select indicators. Any time the mouse cursor is moved away from a select indicator, the pop-up window will be cleared. *Click-LH (press/hold left mouse button) and move the cursor left and right or up and down.* This allows panning from one cell to another without returning to the pin block screen. Notice that the miniature pin block diagram in the upper left corner displays the current LCC/IOC location.

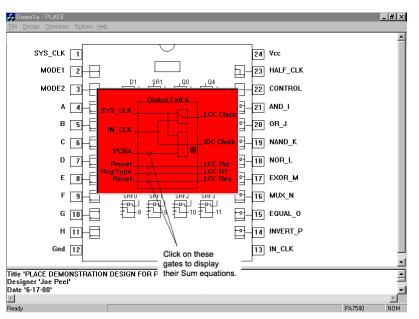

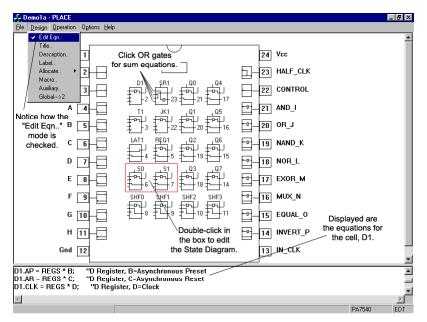

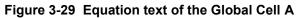

#### Figure 2-8 Configuring the Global Cell A (GBC) Architecture

Move the cursor into the "D" OR or Sum-D gate (shown in Figure 2-7) and double-click the mouse button. In the Text Editor, the cursor will

automatically jump to the current equation for the selected OR gate. *To return to the pin block diagram screen, simply click on the diagram.*

The same process can select the Global Cell (GBC) configuration, i.e. by clicking the select indicators in the cell (Figure 2-8).

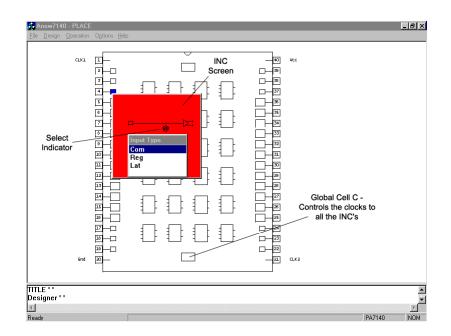

There are multiple global cells in all PEEL<sup>™</sup> Arrays. For instance, the PA7540 device has two global cells that are called Global Cell A and B. The default condition for the PA7540 (and all PEEL<sup>™</sup> Arrays) is the one global cell mode. The two global cell mode can be selected by clicking at the "Global = 2" command found in the "Design" menu window. With two global cells, Global Cells A and B control global signals for all LCC's connected to the IOC's located on the left (pins 2 to 11) and right side (pins 14 to 23) of the pin block diagram respectively. Please refer to the PEEL<sup>™</sup> Array data sheet for more information on the global cells.

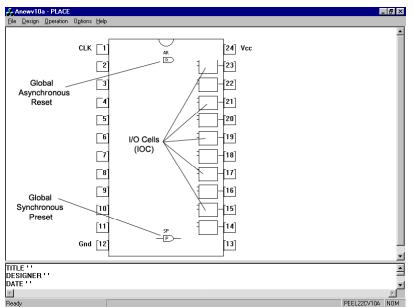

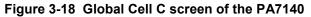

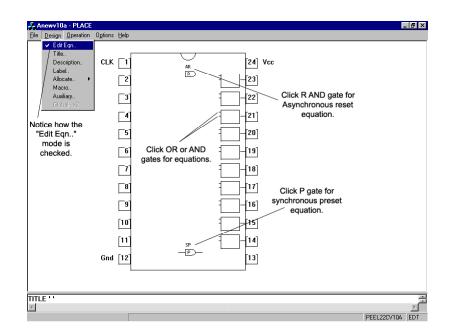

In the pin block screen, move the mouse cursor to the "Design" Command pop-down menu again. Click the command listed as "Edit Eqn" (this stands for Edit Equation). You will notice that there is now a check mark next to the "Edit Eqn" mode name in the "Design" menu. Move the cursor to one of the four inputs of any LCC and the input will be highlighted. Click to select the input equation. In Figure 2-9, the cursor in the Text Editor, automatically jumps to the Sum equation for that cell.

The Text Editor, which is located at the bottom of the screen, is used for editing Boolean equations, state diagram and truth table syntax. Once inside the editor, most of the standard WordStar™ commands can be used. Also, the separation bar can be pulled all the way to the top of the window, so that solely text can be seen. Figure 2-10 shows this.

| 💑 Demo1a - PLACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                |                                                          | - 8 ×  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------|

| File Design Operation Options Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                |                                                          |        |

| V         Gdl Egn.           V         Edl Egn.           Description.         1           Label.         2           Alcoate         2           Accio.         3           Accio.         3           Auxilay         3           Sched.         C           Global->2         A           Mode is         5           Checked.         C         6           D         7         1           E         8         1           G         10         7           E         8         1           G         10         7           E         8         1           G         10         1           G         10         1           Gnd         12 | D1<br>SR1<br>2<br>2<br>3<br>3<br>4<br>4<br>4<br>5<br>1<br>1<br>2<br>2<br>3<br>4<br>4<br>4<br>4<br>4<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 24 Vcc<br>23 HALF_CLK<br>22 CONTROL<br>22 CONTROL<br>22 OR_J<br>20 OR_J<br>20 OR_J<br>21 AND_K<br>21 NAND_K<br>21 NOR_L<br>21 NOR_L<br>21 EXOR_M<br>21 EXOR_M<br>21 EXOR_M<br>22 CONTROL<br>21 AND_J<br>21 AND_J<br>21 AND_J<br>21 AND_L<br>21 EXOR_M<br>21 EXOR_M<br>21 INVERT_P<br>13 IN_CLK | Click "Allocated<br>Block" to edit<br>the state-diagram. |        |

| AND_I.COM = GATES * A * B * C<br>Hegs * D1 +<br>Counter * Q0 +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | * D * E * F * G * H + "8 input AND ga<br>"D reg output<br>"Bit 0 of counter                                                                                          | ate                                                                                                                                                                                                                                                                                            |                                                          | ▲<br>↓ |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                |                                                          | Þ      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                | PA7540                                                   | EDT    |

Figure 2-9 Selecting equations from the block diagram screen

#### Figure 2-10 Inside the WinPLACE™ text editor

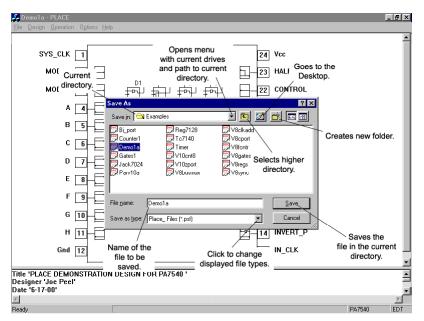

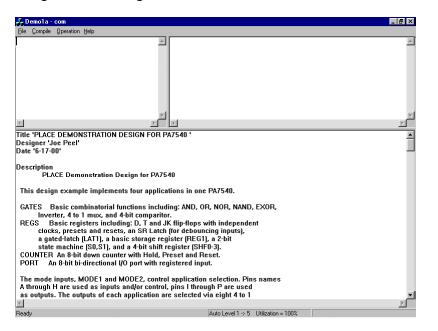

If you have followed the instructions up to this point you have now familiarized yourself with the basic functions of the Design operation in the WinPLACE<sup>™</sup> software. Now, move the cursor to the "File" menu option and click the "Save As" command. The file window will appear (Figure 2-11). Move the cursor to the box named "File <u>n</u>ame:" and click the mouse button. Type in the name "TEMP", or any other new name, to save your modified file. If the file extension is omitted, then it will be defaulted to ".psf". You can change the folder where you want the file to be saved. To jump up multiple folders, click on the pull-down menu that has the name of the current folder. Once the menu is down, locate the folder you want and click on it. The contents of that folder will now be displayed in the big box. If you want to enter a folder in the big box, simply double-click on it. Once the correct location has been found, click on the button labeled "<u>S</u>ave".

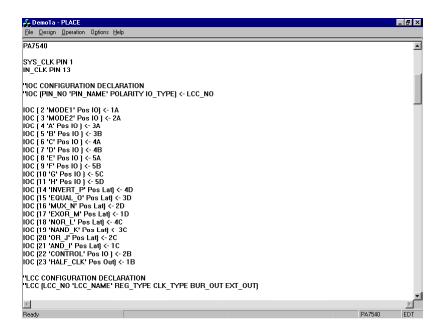

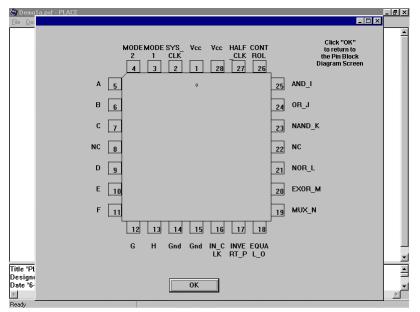

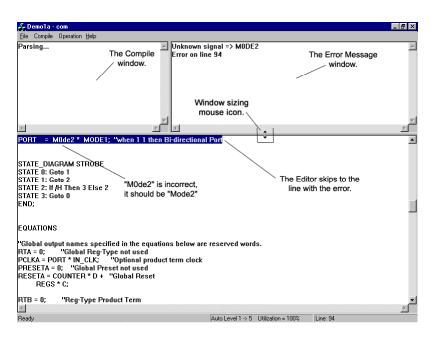

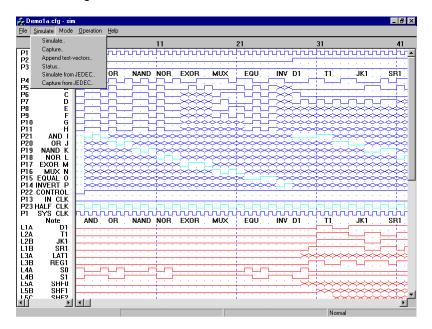

Once your Design file is saved, select the "File" pop-down window again and read in the "GATES1.PSF" design example. Move the mouse cursor to the Operations pop-down window and try selecting the other operations starting with Compile, Simulate and back to Design. **Note that you cannot open the Simulate Operation without compiling your design file. To compile, simply go to the "Compile" pop-down window and select "Run." Now the Simulate option can be entered without error.** The screens should look as displayed in Figure 2-12 and Figure 2-13. For more information on the commands and functions for the four main operations, please refer to the "Operation Reference Guide" in Chapter 3.

Figure 2-12 The Compile Operation Screen (Standard version only)

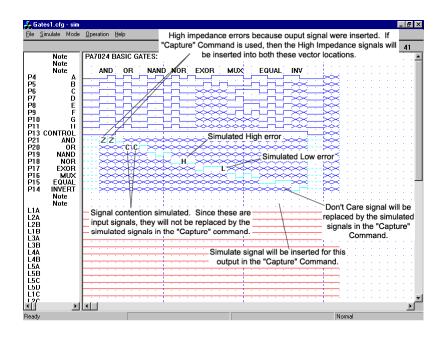

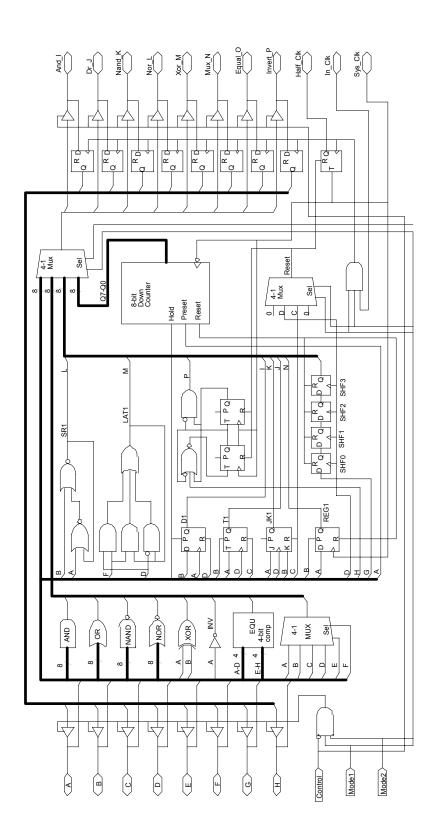

| P4 A<br>P5 B<br>P6 C<br>P7 D<br>P9 D<br>P9 F<br>P9 F<br>P10 G<br>P11 H<br>P21 AND I<br>P21 AND I<br>P21 AND I<br>P21 AND I<br>P21 AND I<br>P21 AND I<br>P3 NOR L<br>P18 NOR L<br>P18 NOR L<br>P18 NOR L<br>P19 NOR L<br>P10 OF J<br>P10 OF J<br>P11 NOR L<br>P11 NOR L<br>P12 AND I<br>P13 NAND K<br>P14 INVERT P<br>P15 EQUAL O<br>P15 EQUAL O<br>P14 INVERT P<br>P15 EQUAL O<br>P15 EQUAL O<br>P15 EQUAL O<br>P15 EQUAL O<br>P14 INVERT P<br>P15 EQUAL O<br>P15 EQUAL O<br>P14 INVERT P<br>P15 EQUAL O<br>P14 INVERT P<br>P15 EQUAL O<br>P15 EQUAL O<br>P14 INVERT P<br>P15 EQUAL O<br>P14 INVERT                                                                                                                                                | o Dimanaro modo   | Operation He                          | lp                 |                                              |                                            |                                              |                                  |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |                                                            |                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------|--------------------|----------------------------------------------|--------------------------------------------|----------------------------------------------|----------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------|--------------------------------------------|

| P2       MODE1         P3       MODE2         AND       OR         P4       AND         P5       B         P6       C         P7       D         P8       E         P9       F         P9       F         P1       H         P2       OR J         P11       H         P21       AND I         P20       OR J         P11       H         P20       OR J         P11       H         P20       OR J         P11       H         P12       AND I         P13       NACK         P14       INVERT P         P13       IN CLK         P14       INVERT P         P13       IN CLK         P14       INVERT P         P15       EQUAL O         P13       IN CLK         P14       INVERT P         P15       SY3 CLK         AND OR       NOR EXOR         MUX       NOT         L2A       T1         L2B       SK1         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |                                       |                    |                                              |                                            |                                              |                                  |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |                                                            | 41                                         |

| P3         MODE2           P4         AND         OR         NAND         NOR         EXOR         MUX         EQU         INV         D1         T1         JK1         S           P5         B         C         C         O         O         NAND         NOR         EXOR         MUX         EQU         INV         D1         T1         JK1         S           P6         C         C         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   | بنبنبن                                | بنبنبن             | بنبخ                                         | بىنىن                                      | بنبن                                         | بنبنخ                            | بنبن                   | , inin                                                                                                                                                                                                                                                                                                                                                                                                                                             | بىبىب                 | ببببب                                                      | بنبين                                      |

| P4 A<br>P5 B<br>P6 C<br>P7 D<br>P7 D<br>P8 F<br>P9 F<br>P9 F<br>P10 G<br>P11 H<br>P21 AND I<br>P21 AND I<br>P21 AND I<br>P18 NOR L<br>P18 NOR L<br>P18 NOR L<br>P18 NOR L<br>P18 NOR L<br>P18 NOR L<br>P19 NOR L<br>P10 NOR L<br>P10 NOR L<br>P10 NOR L<br>P10 NOR L<br>P10 NOR L<br>P11 SYS CLK<br>AND OR NAND NOR EXOR MUX EQU INV D1 T1 JK1 S<br>LA D1<br>L2A SHU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3 MODE2           |                                       |                    |                                              |                                            |                                              |                                  |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |                                                            |                                            |

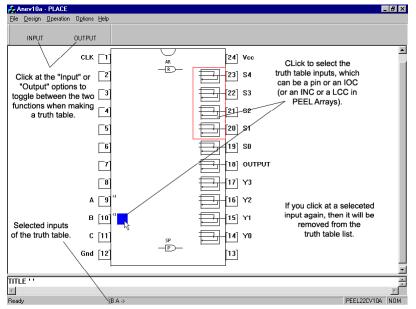

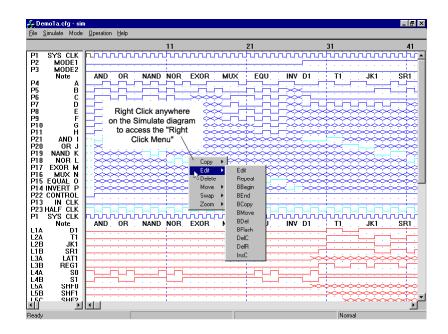

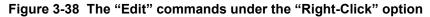

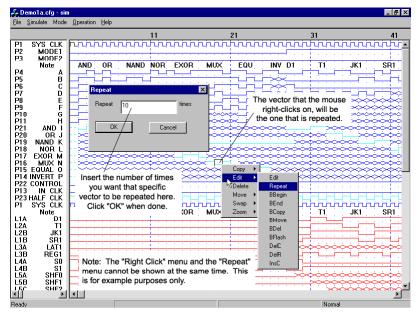

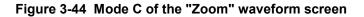

| P5 B<br>P6 C<br>P7 D<br>P8 E<br>P9 F<br>P10 G<br>P11 H<br>P21 AND I<br>P21 AND I<br>P18 NAND K<br>P19 NAND K<br>P10 G<br>P11 NCH<br>P11 NCH<br>P11 AND I<br>P12 AND I<br>P12 AND I<br>P13 NN CLK<br>P13 NN CLK<br>P23 HALF CLK<br>P24 NO OR NAND NOR EXOR MUX EQU INV D1 T1 JK1 S<br>P28 CLK<br>AND OR NAND NOR EXOR MUX EQU INV D1 T1 JK1 S<br>P28 CLK<br>AND OR NAND NOR EXOR MUX EQU INV D1 T1 JK1 S<br>P28 CLK<br>AND OR NAND NOR EXOR MUX EQU INV D1 T1 JK1 S<br>P28 CLK<br>AND OR NAND NOR EXOR MUX EQU INV D1 T1 JK1 S<br>P28 CLK<br>AND OR NAND NOR EXOR MUX EQU INV D1 T1 JK1 S<br>P28 CLK<br>AND OR NAND NOR EXOR MUX EQU INV D1 T1 JK1 S<br>P28 CLK<br>AND OR NAND NOR EXOR MUX EQU INV D1 T1 JK1 S<br>P28 CLK<br>AND OR NAND NOR EXOR MUX EQU INV D1 T1 JK1 S<br>P28 CLK<br>P28 CLK<br>P29 CLK<br>P29 CLK<br>P20                                                                                                   |                   | AND O                                 | R NAND             | NOR                                          | EXOR                                       | MUX                                          | EQU                              | INV                    | וט 👝                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u> </u>              | JK1                                                        | SR1                                        |