# IDT79R3721 DRAM Controller

INTEGRATED DEVICE TECHNOLOGY, INC.

## The IDT R3721 DRAM Controller Hardware User's Manual

**Preliminary Information**

**Revision 2.0**

August 12, 1992

©1992 Integrated Device Technology, Inc.

## ABOUT THIS MANUAL

This manual has been constructed as a detailed applications guide on the use of the IDT R3721 and IDT73720 to construct appropriate DRAM subsystems for an R3051 family CPU. The manual has been written to describe a wide variety of memory subsystems. The manual has been written assuming that the system designer will primarily study the types of subsystems appropriate to the application at hand; it is not assumed that each system designer will read the manual in its entirety.

In addition to the design information, the manual contains overview chapters on the DRAM controller (IDT R3721), Bus Exchanger (IDT73720) and R3051 family bus interface. Also included is a brief review of DRAM fundamentals.

A quantitative description of the R3721 electrical interface is provided in the data sheet for this product. Also included in the data sheets are the mechanical descriptions of the part, including packaging and pin-out.

Additional information on development tools, additional support chips, the R3051 family, and the use of these products in various applications, are provided in separate data sheets and applications notes.

Any of this information is readily available from your local IDT sales representative.

## **CONTENTS OVERVIEW**

**Chapter 1** contains a brief overview of the capabilities of the R3721 DRAM controller.

Chapter 2 contains a description of the R3051 family bus interface.

**Chapter 3** contains a brief overview of the fundamentals of DRAM operation.

Chapter 4 describes how the R3721 DRAM controller operates.

**Chapter 5** describes how to program the R3721 to enable the various features and timing models it supports.

**Chapter 6** describes the various interfaces of the R3721, and describes how to connect it to the CPU, the DRAMs, the data path, and also how to use it with other memory subsystems.

**Chapter 7** describes the considerations involved in the construction of a noninterleaved DRAM subsystem. Various DRAM configurations are described.

**Chapter 8** provides a detailed analysis of a particular non-interleaved memory configuration. This chapter contains information on how to perform the timing analysis required to properly program the R3721 in such a system.

**Chapter 9** describes the considerations involved in the construction of an interleaved DRAM subsystem.

**Chapter 10** contains a detailed description of a particular interleaved memory configuration. This chapter also contains a detailed analysis of how to properly program the R3721 for an interleaved memory system.

**Chapter 11** describes the reset sequence, the refresh timing, and the clocking of the R3721.

Appendix A describes the IDT73720 Bus Exchanger.

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- 1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

The IDT logo is a registered trademark and RISController, R3051, and RISChipset are trademarks of Integrated Device Technology, Inc. MIPS is a registered trademarks of MIPS Computer Systems, Inc. UNIX is a registered trademark of AT&T.

All others are trademarks of their respective companies.

## TABLE OF CONTENTS

## Chapter 1: R3721 Overview

| Introduction                               | 1-1          |

|--------------------------------------------|--------------|

| Description                                | 1-2          |

| Configurability                            | 1-4          |

| Performance Considerations                 | 1-5          |

| Applications                               | 1-5          |

|                                            | 10           |

| Chapter 2: R3051 Family Interface Overview |              |

|                                            | 2-2          |

| R3051 Bus Interface Pin Description        |              |

| Read Transactions                          | 2-5          |

| Read Interface Timing Overview             | 2-5          |

| Memory Addressing                          | 2-5          |

| Bus Turn Around                            | 2-6          |

| Bringing Data into the Processor           | 2-7          |

| Terminating the Read                       | 2-8          |

| Read Timing Diagrams                       | 2-8          |

| Single Word Reads                          | 2-8          |

| Quad Word Reads                            | 2-8          |

| Write Interface                            | 2-15         |

| Types of Write Transactions                | 2-15         |

| Write Interface Timing Overview            | 2-16         |

|                                            | 2-10<br>2-16 |

| Memory Addressing                          | -            |

| Data Phase                                 | 2-16         |

| Terminating the Write                      | 2-17         |

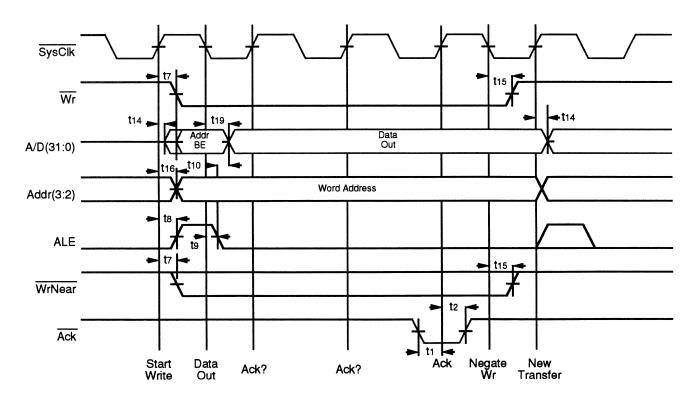

| Write Timing Diagrams                      | 2-18         |

| Basic Write                                | 2-18         |

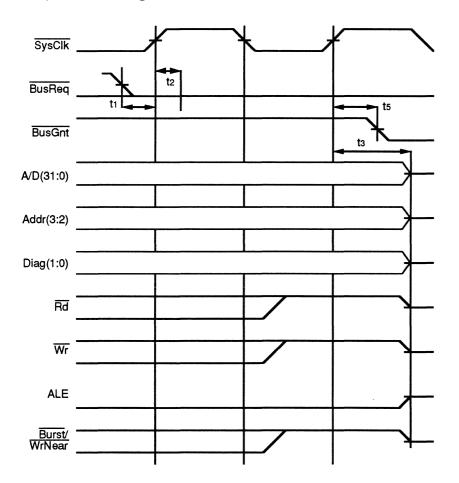

| DMA Arbiter Interface                      | 2-19         |

| Interface Overview                         | 2-19         |

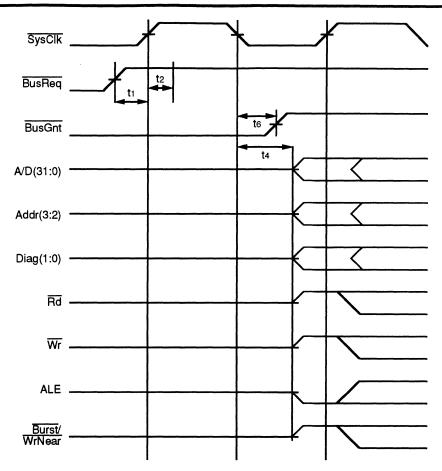

| DMA Arbiter Timing Diagrams                | 2-19         |

| Initiation of DMA Mastership               | 2-19         |

| Relinquishing Mastership Back to the CPU   | 2-20         |

|                                            |              |

| Chapter 3: Fundamentals of DRAM Operation  |              |

| Introduction                               | 3-1          |

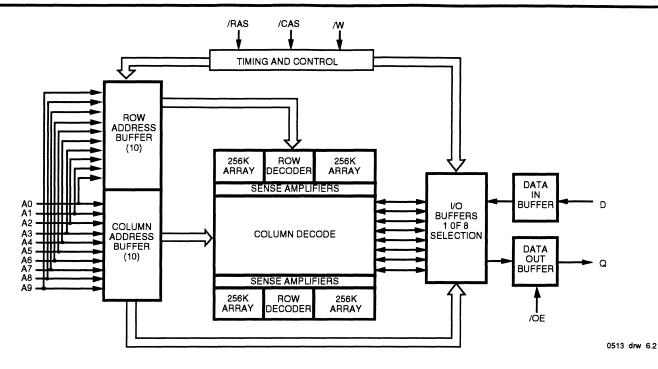

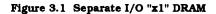

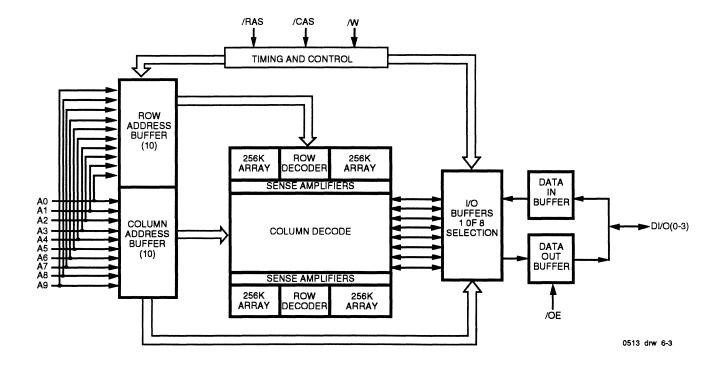

| DRAM Architecture                          | 3-1          |

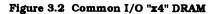

| Normal Access                              | 3-3          |

|                                            | 3-3          |

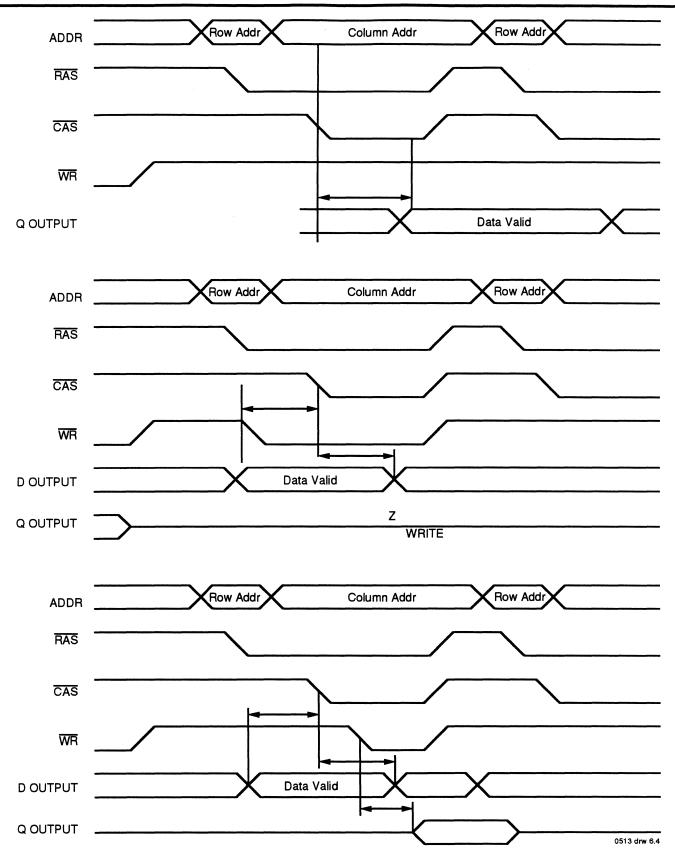

| Page Mode and Static Column Accesses       |              |

| DRAM Refresh and Pre-charge                | 3-3          |

| Memory System Configurations               | 3-6          |

| Summary                                    | 3-7          |

|                                            |              |

| Chapter 4: R3721 Operation Overview        |              |

| Introduction                               | 4-1          |

| R3051 Bus Interface                        | 4-1          |

| R3721 DRAM Interface                       | 4-2          |

| Pin Description                            | 4-5          |

| •                                          | -            |

| Chapter 5: Programming the R3721           |              |

| Introduction                               | 5-1          |

| The Mode Register                          | 5-1          |

| Programming the Mode Register              | 5-1<br>5-1   |

|                                            | 5-1          |

| DRAM Size Field                            |              |

| External Memory Configuration              | 5-2          |

| Write Near                                                                    | 5-2                          |

|-------------------------------------------------------------------------------|------------------------------|

| $\overline{RAS}$ to $\overline{CAS}$ Delay                                    | 5-2                          |

| RAS Timing                                                                    | 5-3                          |

| CAS Pulse Width                                                               | 5-4                          |

| CAS Pre-charge Time                                                           | 5-5                          |

| Refresh Period                                                                | 5-5                          |

| Delayed Chip-select                                                           | 5-6                          |

| Default Settings                                                              | 5-7                          |

| Writing to the Mode Register                                                  | 5-7                          |

| Auto Configuration Detection and Initialization                               | 5-8                          |

|                                                                               |                              |

| Chapter 6: R3721 Interfacing                                                  |                              |

| Introduction                                                                  | 6-1                          |

| R3051 Bus Interface                                                           | 6-1                          |

| R3721 DRAM Interface                                                          | 6-4                          |

| Data Path Control Interface                                                   | 6-6                          |

| Summary                                                                       | 6-8                          |

|                                                                               |                              |

| Chapter 7: The Use of the R3721 in a Non-interleaved Memory System            |                              |

| Introduction                                                                  | 7-1                          |

| Non-Interleaved System Design                                                 | 7-1                          |

| Single Read Transaction Timings                                               | 7-2                          |

| Start of Single Read Access                                                   | 7-2                          |

| Memory Control Signals for Single Read Accesses                               | 7-4                          |

| End of a Single Read Access                                                   | 7-5                          |

| Page Read Accesses                                                            | 7-3<br>7-8                   |

| Single Read Access Outside of Page                                            | <b>7</b> -10                 |

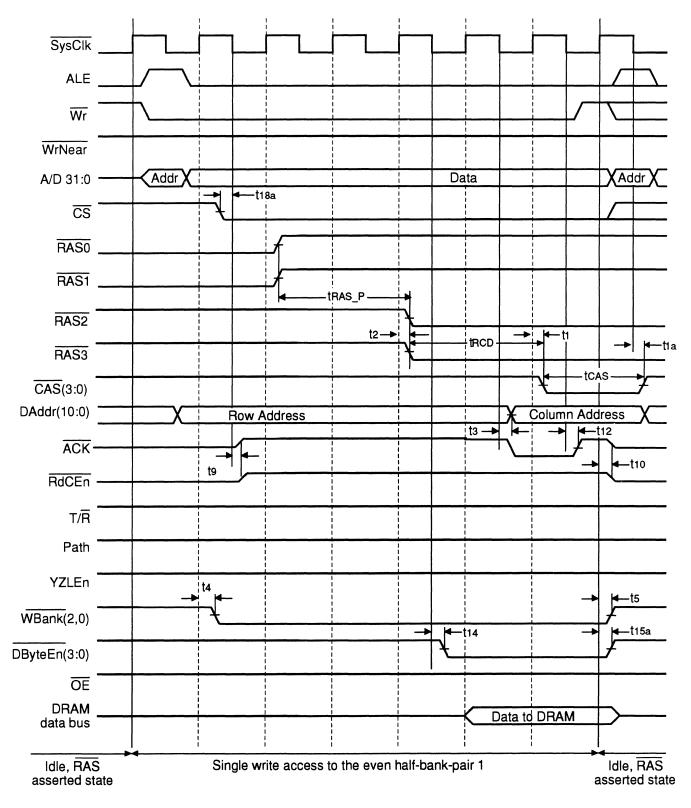

| Single Write Transaction Timings                                              | <b>7-</b> 10<br><b>7-</b> 11 |

| Start of Write Access                                                         | 7-11<br>7-11                 |

| Memory Control Signals for Single Write Accesses                              | 7-11<br>7-11                 |

| End of a Single Write Access                                                  | 7-11                         |

| Page Write Accesses                                                           | 7-13                         |

| Single Write Access Outside of Page                                           | 7-17<br>7-24                 |

|                                                                               | 7-24<br>7-25                 |

| Partial Word Write Operation                                                  |                              |

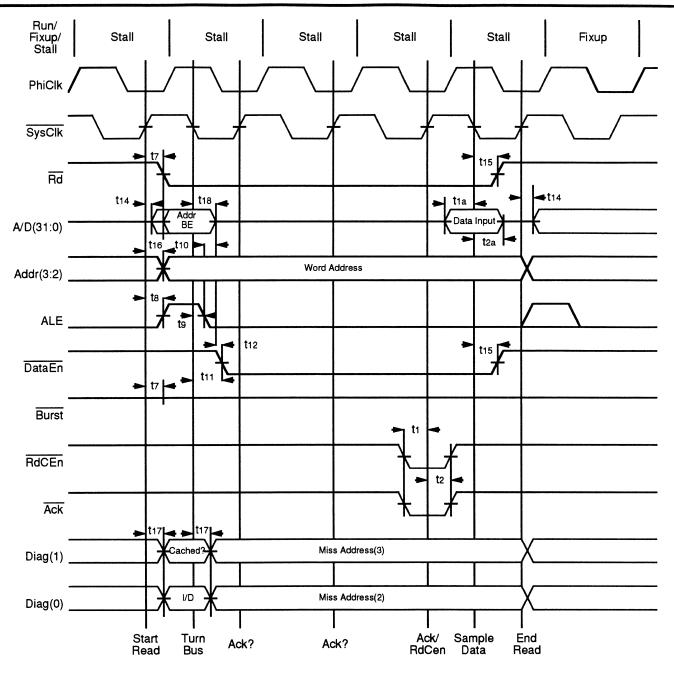

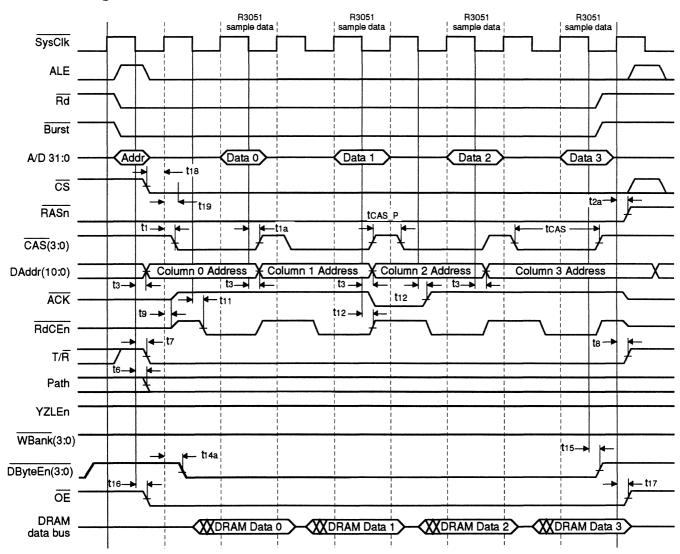

| Quad Word Read Transaction Timings                                            | 7-26                         |

| Start of Quad Word Read Access                                                | 7-26                         |

| Memory Control Signals During Quad Word Read Accesses                         | 7-26                         |

| End of a Quad Word Read Access                                                | 7-26                         |

| Page Quad Word Read Accesses                                                  | 7-30                         |

| Observer Q. Application Promoto: A New interlaged (The Deal Manage Containing |                              |

| Chapter 8: Application Example: A Non-interleaved Two Bank Memory System      |                              |

| Introduction                                                                  | 8-1                          |

| General System Description                                                    | 8-1                          |

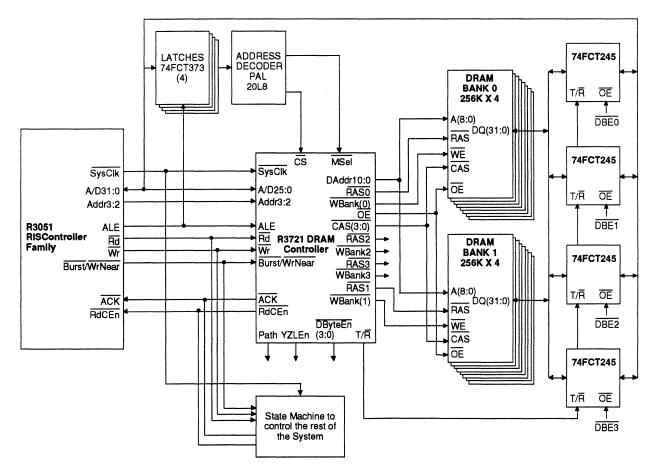

| Detailed Description of the R3721 Connections                                 | 8-3                          |

| Multiple Banks of "x1" DRAMs                                                  | 8-4                          |

| Setting the Mode Register                                                     | 8-6                          |

| Derating Effect Due to Capacitive Loading                                     | 8-6                          |

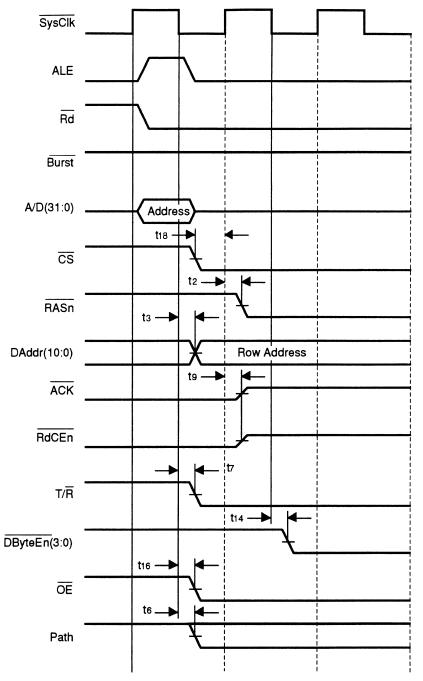

| System Timing Diagrams                                                        | 8-15                         |

| Charter O. The line of the DOZO1 in an Interior 1 Marcon Content              |                              |

| Chapter 9: The Use of the R3721 in an Interleaved Memory System               | 0.1                          |

| Introduction                                                                  | 9-1                          |

| Interleaved System Design                                                     | 9-1                          |

| Single Read Transaction Timings                                               | 9-2                          |

| Start of Single Read Access                                                   | 9-2                          |

| Memory Control Signals for Single Read Accesses                               | 9-3                          |

| End of a Single Read Access                                                   | 9-3                          |

| Page Read Accesses                                                            | 9-5                          |

| Single Read Access Outside of Page                                            | 9-6                          |

| Single Write Transaction Timings                                           | 9-7   |

|----------------------------------------------------------------------------|-------|

| Start of Write Access                                                      | 9-7   |

| Memory Control Signals for Single Write Accesses                           | 9-7   |

| End of a Single Write Access                                               | 9-8   |

| Page Write Accesses                                                        | 9-8   |

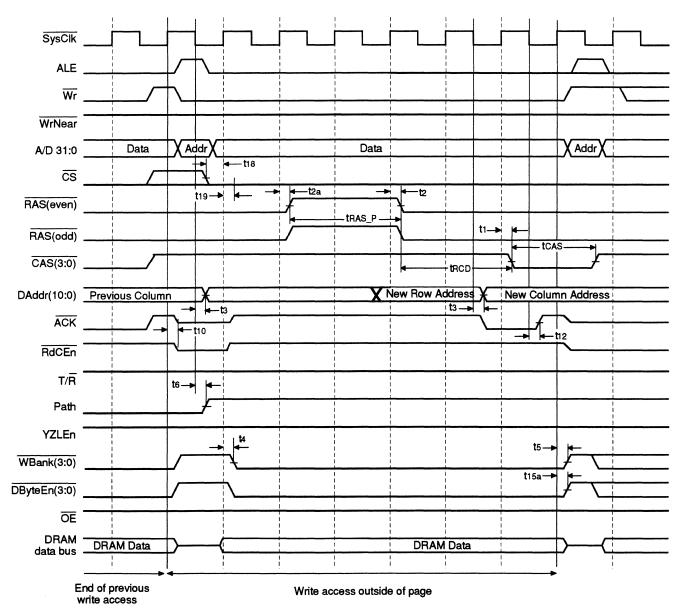

| Single Write Access Outside of Page                                        | 9-11  |

| Partial Word Write Operation                                               | 9-11  |

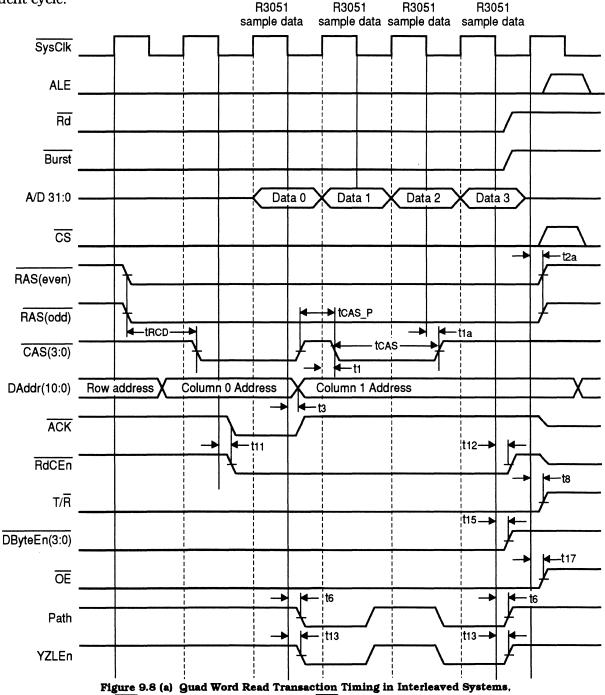

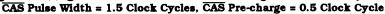

| Quad Word Read Transaction Timings                                         | 9-12  |

| Start of Quad Word Read Access                                             | 9-12  |

| Memory Control Signals During Quad Word Read Accesses                      | 9-13  |

| End of a Quad Word Read Access                                             | 9-14  |

| Page Quad Word Read Accesses                                               | 9-17  |

|                                                                            |       |

| Chapter 10: Application Example: An Interleaved Two Bank-Pair Memory Syste | em    |

| Introduction                                                               | 10-1  |

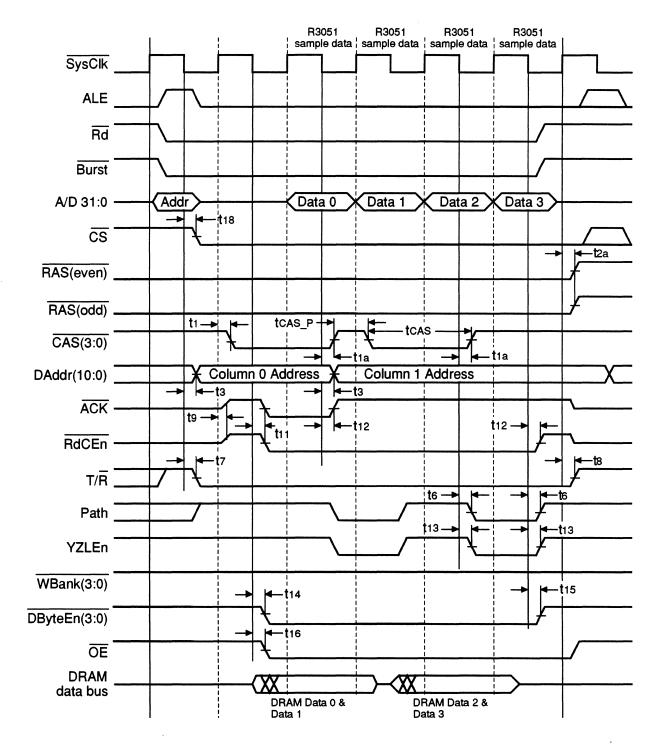

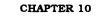

| General System Description                                                 | 10-1  |

| Detailed Description of the R3721 Connections                              | 10-2  |

| Setting the Mode Register                                                  | 10-4  |

| Derating Effect Due to Capacitive Loading                                  | 10-4  |

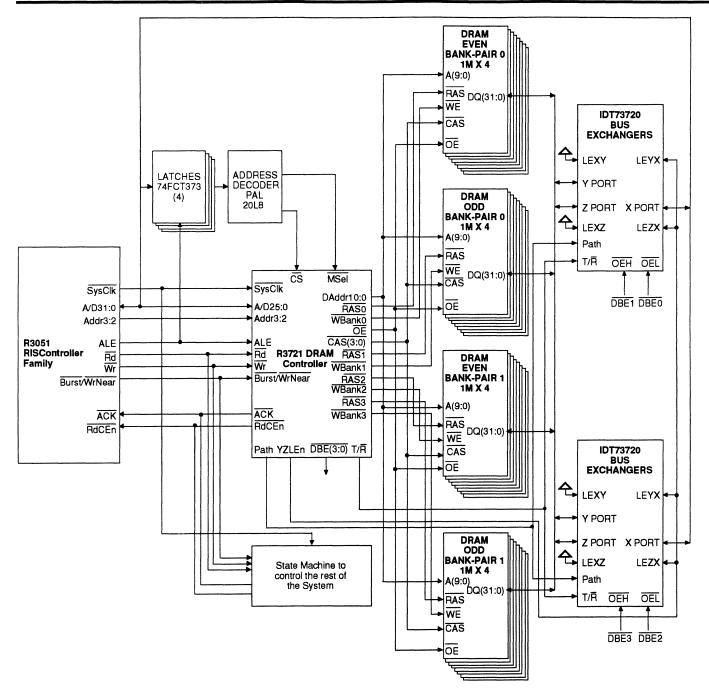

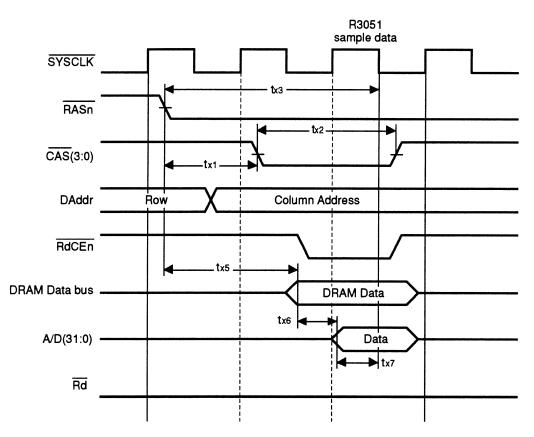

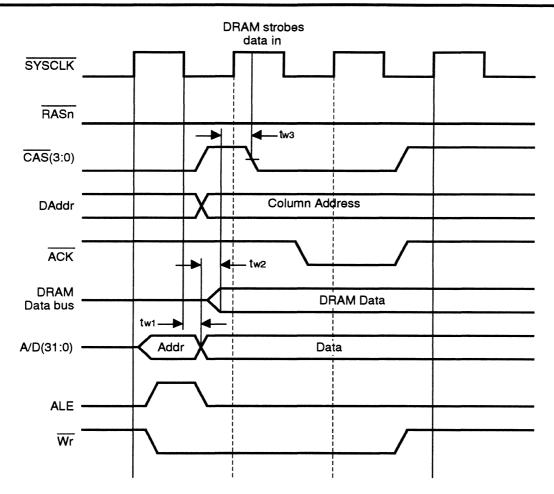

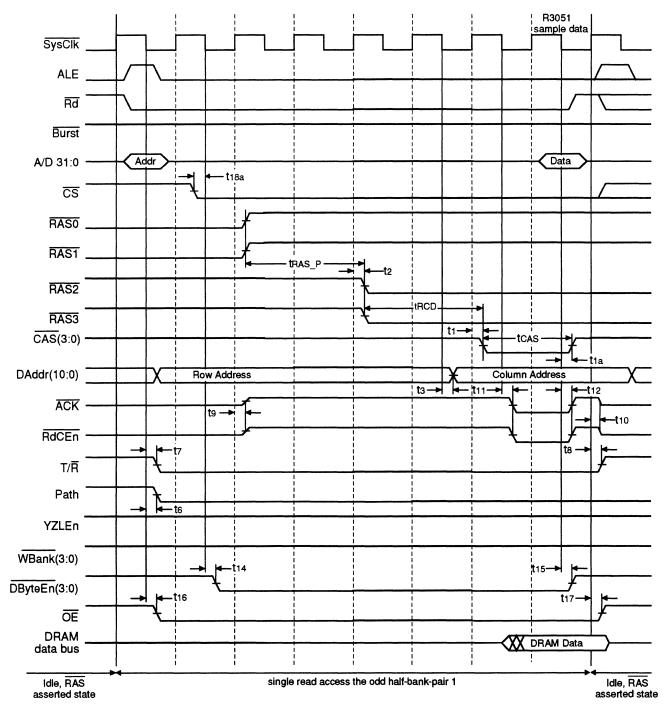

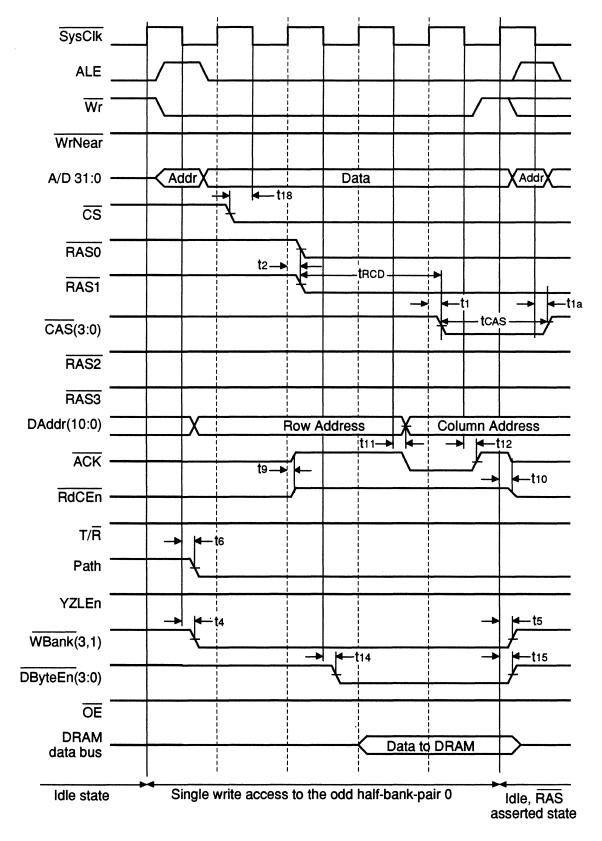

| System Timing Diagrams                                                     | 10-12 |

|                                                                            |       |

| Chapter 11: Reset Initialization, Refresh and Input Clocking               |       |

| Introduction                                                               | 11-1  |

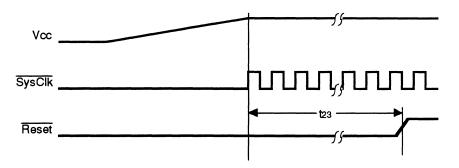

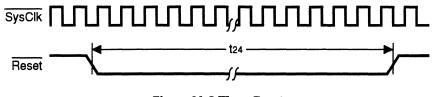

| Power-up and Reset                                                         | 11-1  |

| DRAM Initialization                                                        | 11-1  |

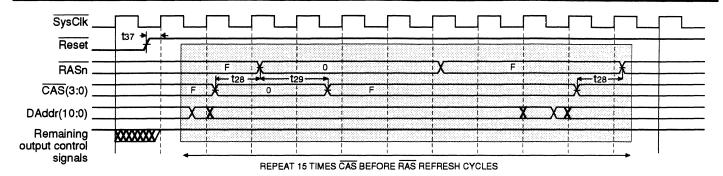

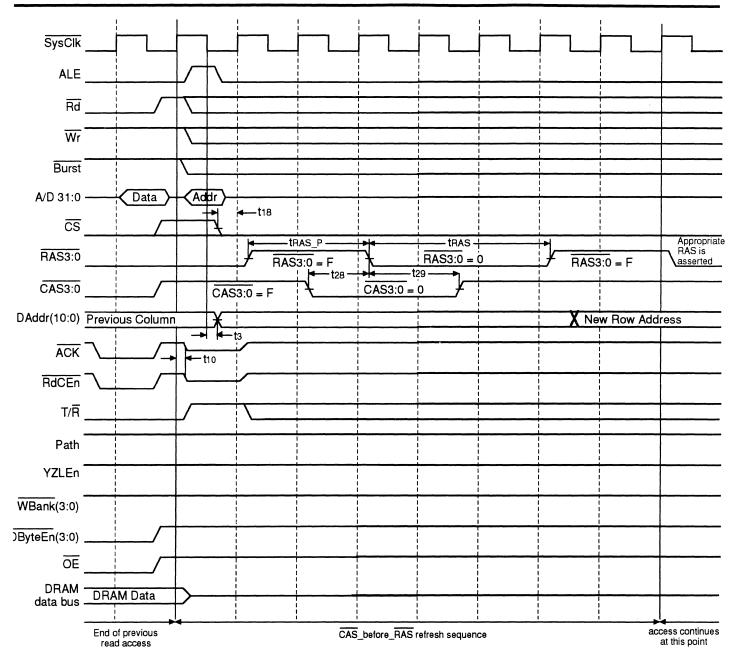

| CAS Before RAS Refresh Timings                                             | 11-2  |

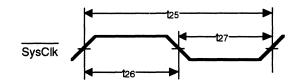

| Input Clock Requirements                                                   | 11-4  |

|                                                                            |       |

| Appendix A: IDT73720 Bus Exchanger Overview                                |       |

| Introduction                                                               | A-1   |

| Major Features                                                             | A-1   |

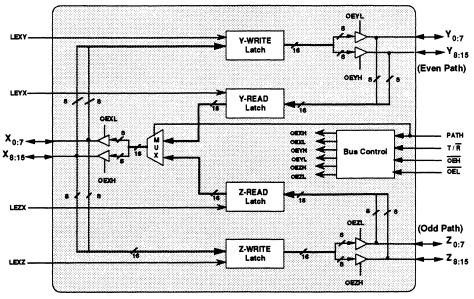

| Description                                                                | A-2   |

| Architecture Overview                                                      | A-2   |

| Data Flow Control Signals                                                  | A-2   |

| Memory Read Operations                                                     | A-3   |

| Memory Write Operations                                                    | A-3   |

| Pin Description                                                            | A-4   |

|                                                                            |       |

#### LIST OF FIGURES

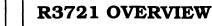

| Figure 1.1      | R3721 Dynamic Memory Controller                                           | 1-2        |

|-----------------|---------------------------------------------------------------------------|------------|

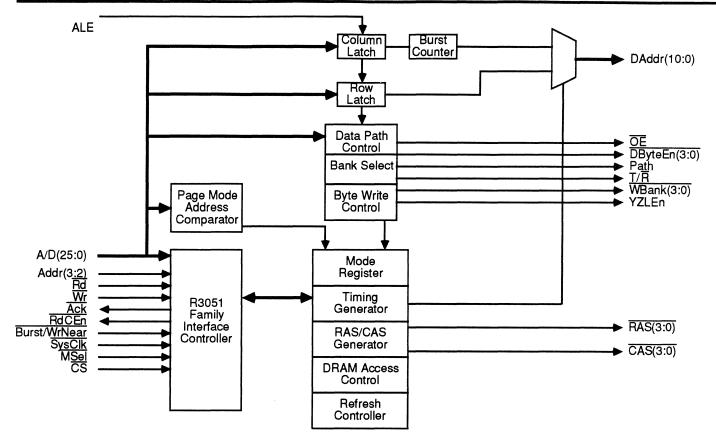

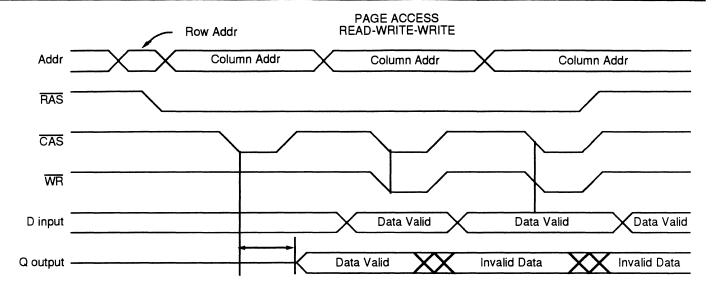

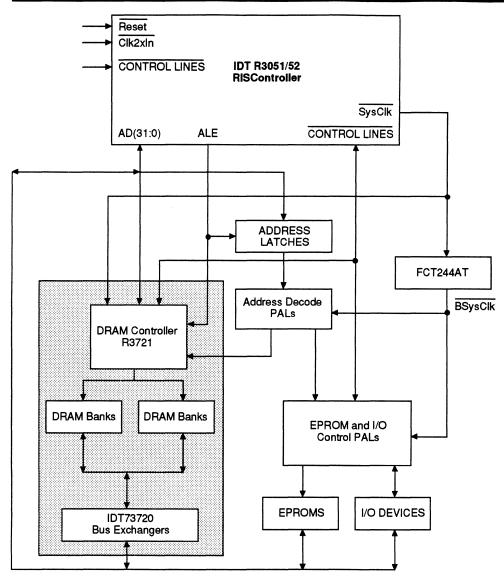

| Figure 1.2      | R3051-based System Using R3721 DRAM Controller                            | 1-3        |

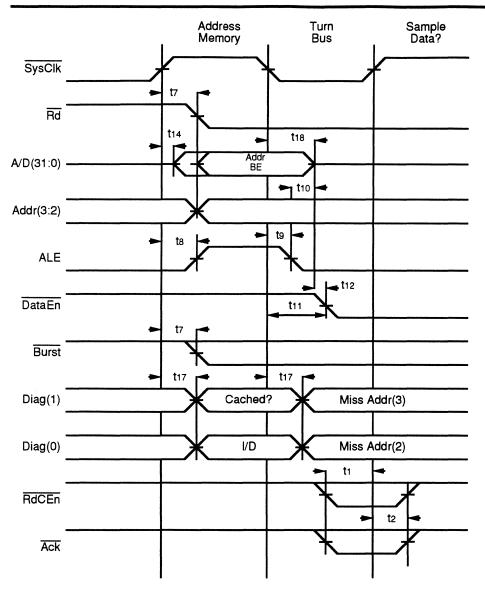

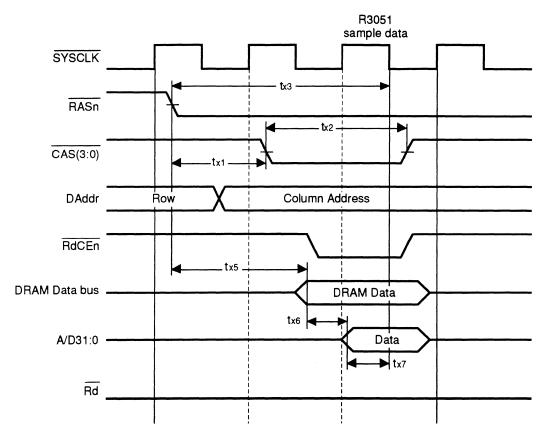

| Figure 2.1      | Start of Processor Read                                                   | 2-6        |

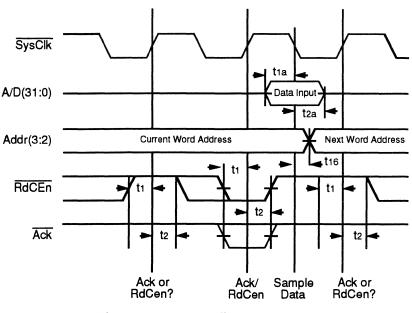

| Figure 2.2      | Data Sampling by R3051                                                    | 2-7        |

| Figure 2.3      | End of Read                                                               | 2-9        |

| Figure 2.4      | Single Word Read Cycle                                                    | 2-10       |

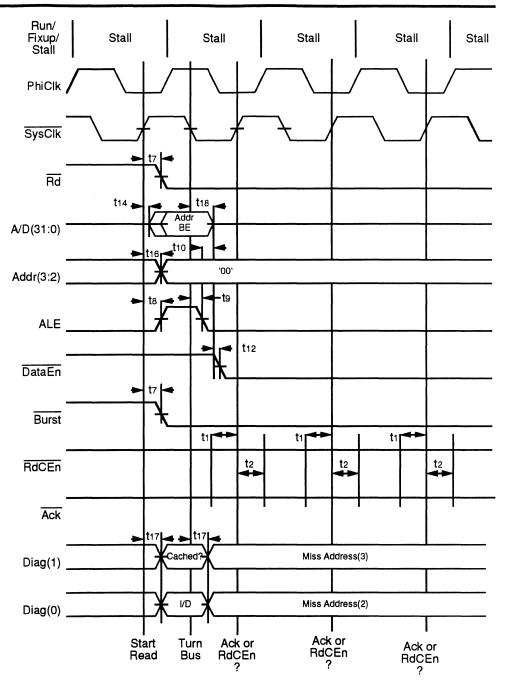

| Figure 2.5 (a)  | Start of Burst Quad Word Read                                             | 2-11       |

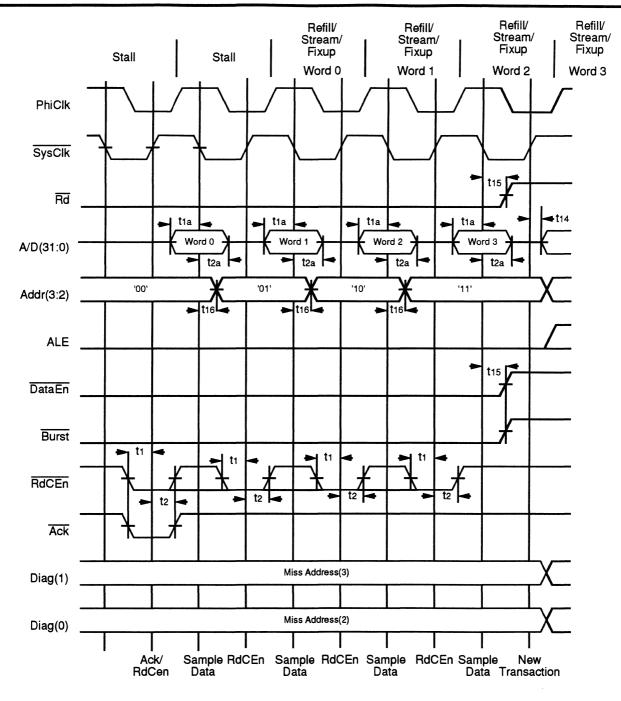

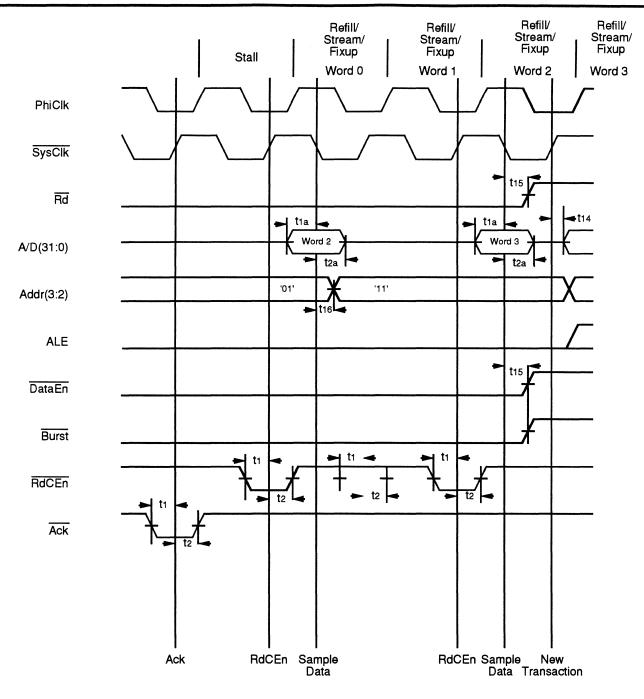

| Figure 2.5 (b)  | End of Burst Quad Word Read                                               | 2-12       |

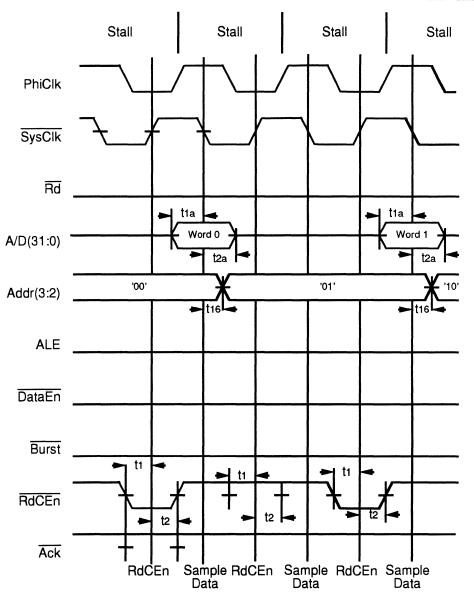

| Figure 2.6 (a)  | Start of Throttled Quad Word Read                                         | 2-13       |

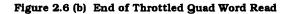

| Figure 2.6 (b)  | End of Throttled Quad Word Read                                           | 2-14       |

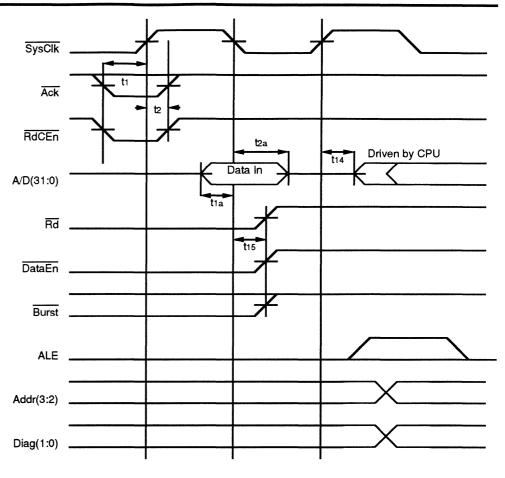

| Figure 2.7      | Start of Write                                                            | 2-17       |

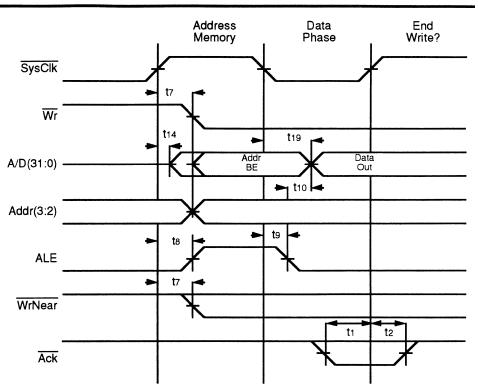

| Figure 2.8      | End of Write                                                              | 2-18       |

| Figure 2.9      | Basic Write                                                               | 2-18       |

| Figure 2.10     | DMA Mastership Request                                                    | 2-20       |

| Figure 2.11     | Relinquishing DMA Mastership                                              | 2-21       |

| Figure 3.1      | Separate I/O "x1" DRAM                                                    | 3-2        |

|                 |                                                                           | 3-2        |

| Figure 3.2      | Common I/O "x4" DRAM                                                      |            |

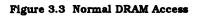

| Figure 3.3      | Normal DRAM Access                                                        | 3-4        |

| Figure 3.4      | Page Mode DRAM Access                                                     | 3-5        |

| Figure 3.5      | Interleaved Memory System                                                 | 3-6        |

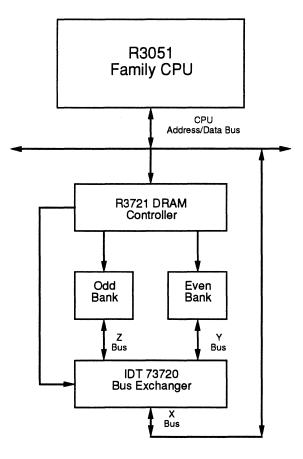

| Figure 4.1      | R3721 State Machine                                                       | 4-3        |

| Figure 4.2      | Mode Register of DRAM Controller                                          | 4-4        |

| D               |                                                                           | - 1        |

| Figure 5.1      | The Mode Register                                                         | 5-1        |

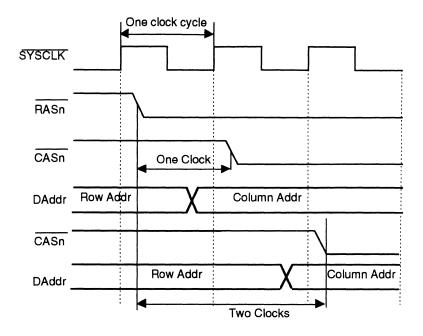

| Figure 5.2      | RAS to CAS Delay                                                          | 5-3        |

| Figure 5.3      | RAS to Signals Timing                                                     | 5-4        |

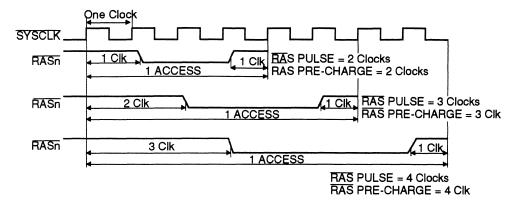

| Figure 5.4      | CAS Pulse Width Timing                                                    | 5-4        |

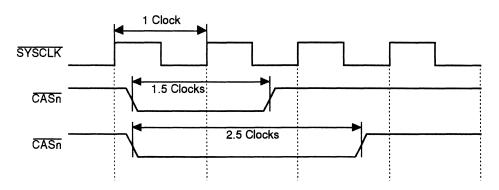

| Figure 5.5      | CAS Pre-Charge Timing                                                     | 5-5        |

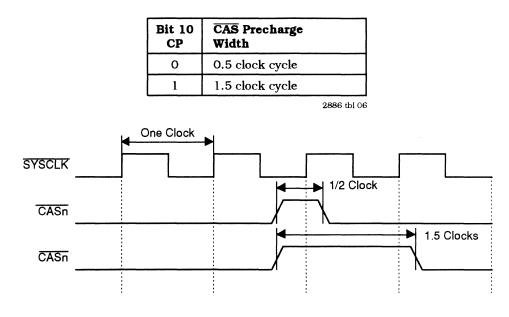

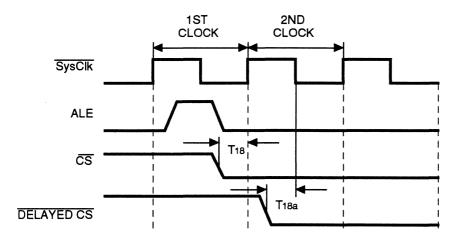

| Figure 5.6      | Chip-select Timing                                                        | 5-6        |

| Figure 5.7      | Settings of Mode Register at Power Up                                     | 5-7        |

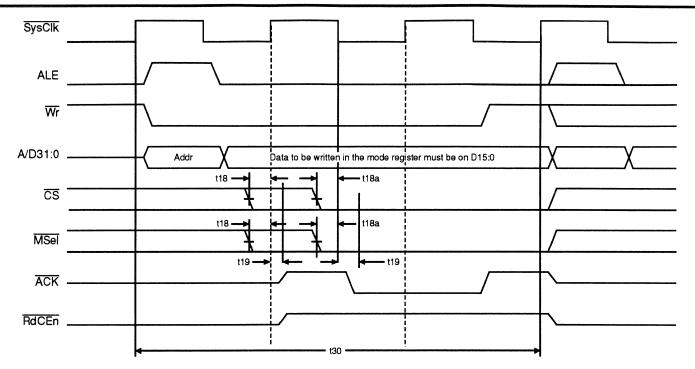

| Figure 5.8      | Writing to the Mode Register                                              | 5-8        |

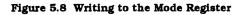

| Figure 6.1      | R3721 CPU Interface Connections                                           | 6-2        |

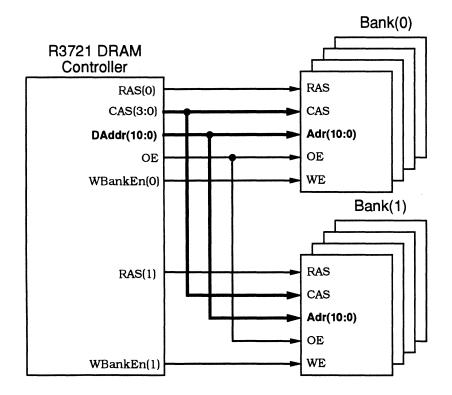

| Figure 6.2      | R3721 DRAM Control Interface                                              | 6-4        |

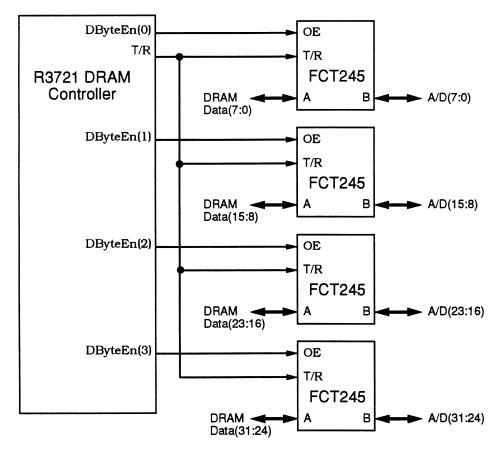

| Figure 6.3      | R3721 Data Path Interface to 74FCT245s                                    | 6-6        |

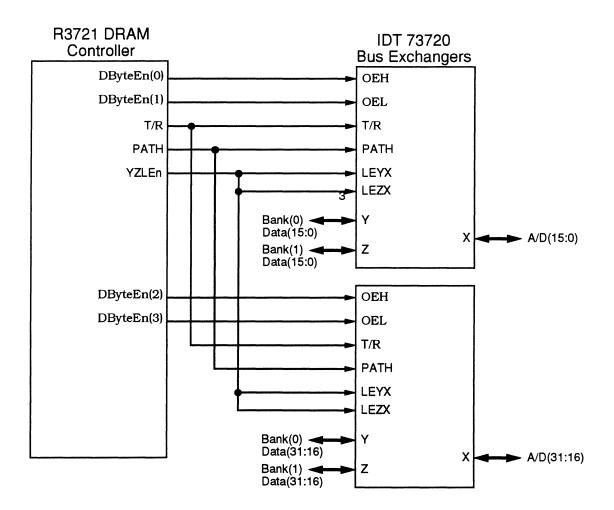

| Figure 6.4      | R3721 Data Path Interface to IDT73720 Bus Exchangers                      | 6-7        |

|                 | Outline of the Mode Destates Handles on Description to the Observe        | <b>7</b> 1 |

| Figure 7.1      | Settings of the Mode Register Used as an Example in this Chapter          | 7-1        |

| Figure 7.2 (a)  | Start of Single Read Access for Fast Chip-select                          | 7-3        |

| Figure 7.2 (b)  | Start of Single Read Access for Slow Chip-select                          | 7-4        |

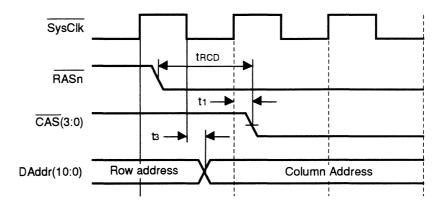

| Figure 7.3 (a)  | DRAM Control for RCD=0 (Single Read)                                      | 7-5        |

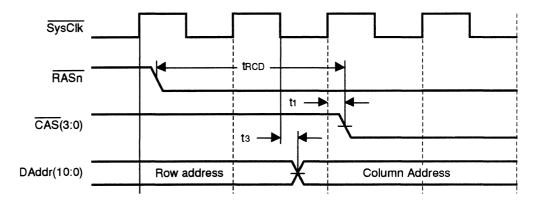

| Figure 7.3 (b)  | DRAM Control for RCD=1 (Single Read)                                      | 7-5        |

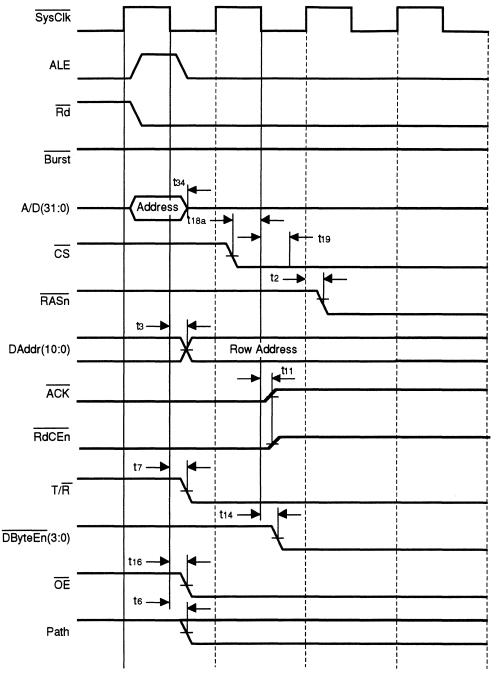

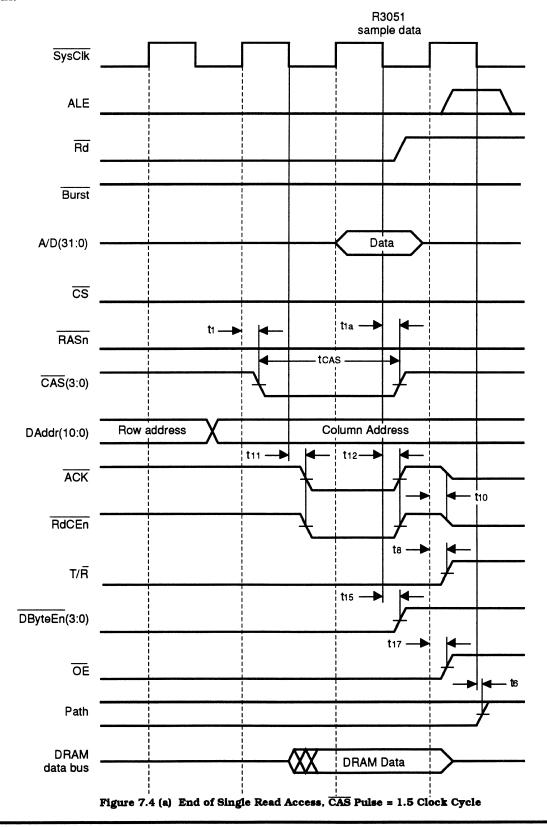

| Figure 7.4 (a)  | End of Single Read Access, $\overline{CAS}$ Pulse = 1.5 Clock Cycle       | 7-6        |

| Figure 7.4 (b)  | End of Single Read Access, CAS Pulse = 2.5 Clock Cycle                    | 7-7        |

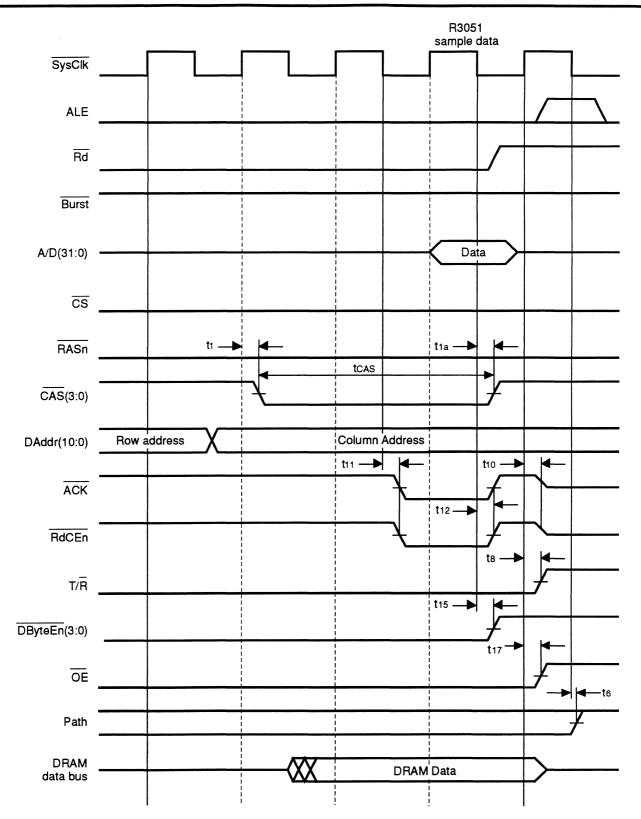

| Figure 7.5      | Example of a Single Read Access                                           | 7-8        |

| Figure 7.6      | Page Read Access Timing Diagram                                           | 7-9        |

| Figure 7.7      | Single Read Access Outside of Page                                        | 7-10       |

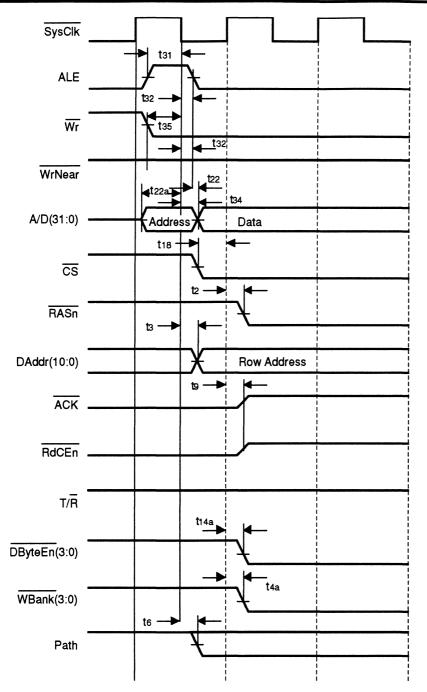

| Figure 7.8      | Start of a Single Write Access for Fast Chip-select                       | 7-12       |

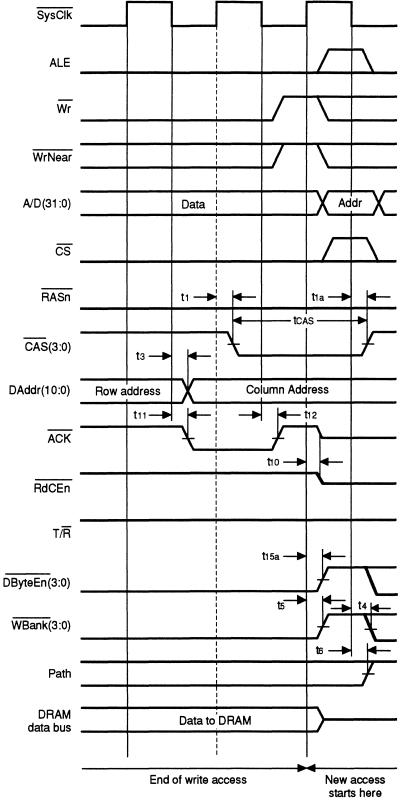

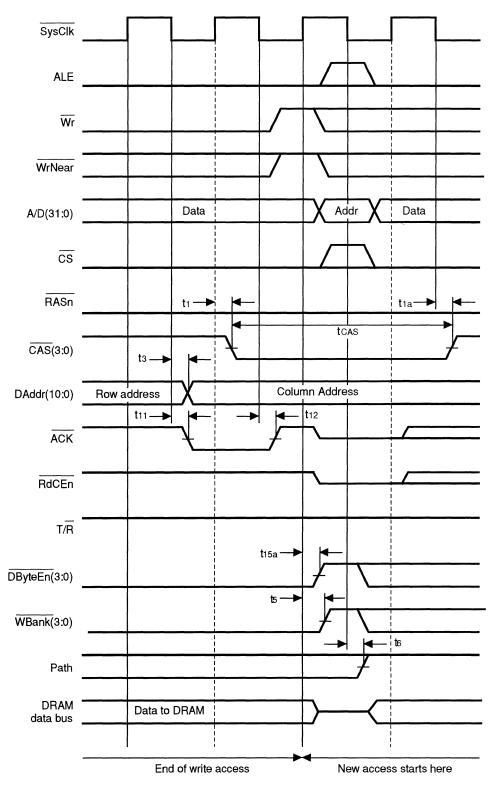

| Figure 7.9 (a)  | End of Single Write Access, CAS pulse = 1.5 Clock Cycle                   | 7-14       |

| Figure 7.9 (b)  | End of Single Write Access, CAS pulse = 2.5 Clock Cycle                   | 7-15       |

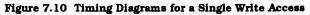

| Figure 7.10     | Timing Diagrams for a Single Write Access                                 | 7-16       |

| Figure 7.11 (a) | Optimum Page Write in Two Clock Cycles. $\overline{CS}$ and Internal Page |            |

|                 | Comparator Bypassed.                                                      | 7-18       |

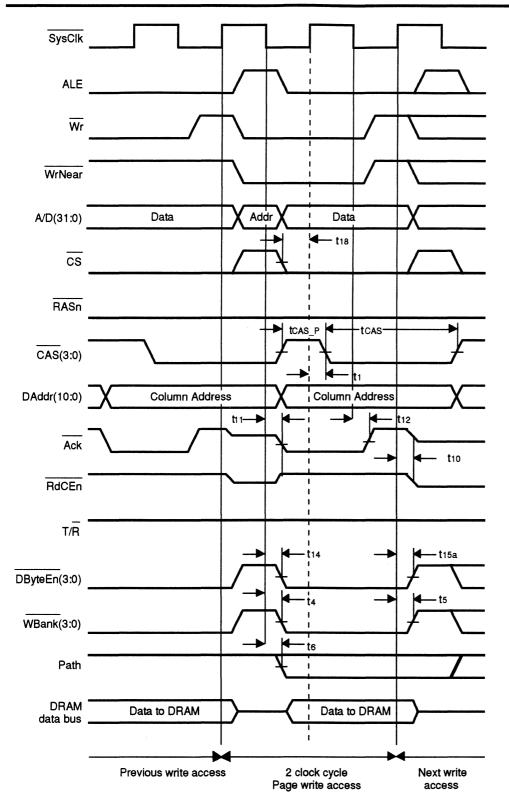

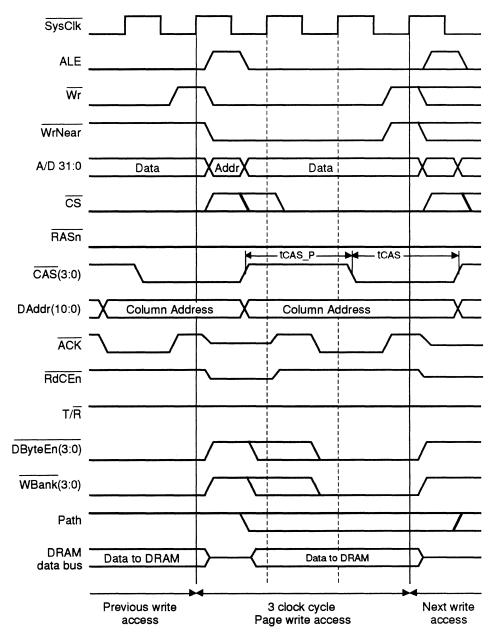

| Figure 7.11 (b)                                                                                                                                                                 | 3 Clock Cycles Page Write with Slow Chip-select, $\overline{CAS}$ Pulse<br>Width = 1.5 Clock Cycles, $\overline{CAS}$ Pre-charge = 0.5 Clock Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-19                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

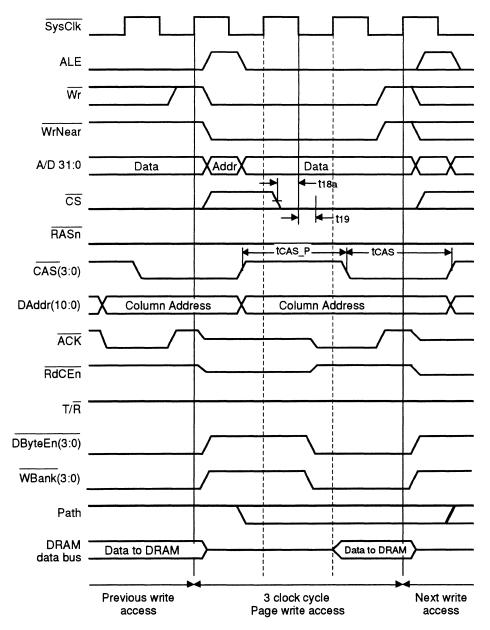

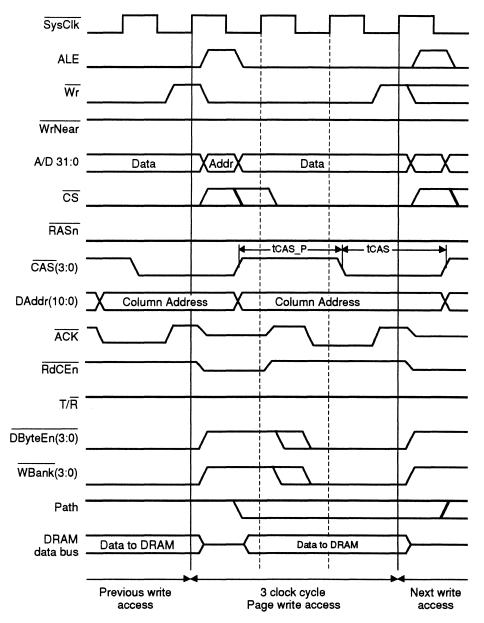

| Figure 7.11 (c)                                                                                                                                                                 | 3 Clock Cycles Page Write with Slow Chip-select, CAS Pulse<br>Width = 2.5 Clock Cycles, CAS Pre-charge = 0.5 Clock Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-20                                                                                     |

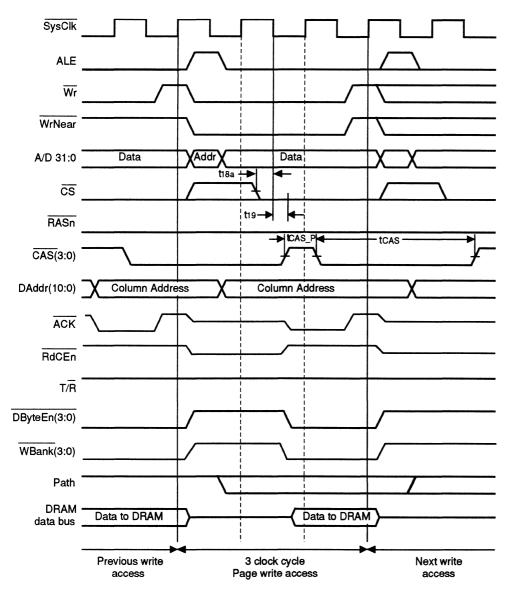

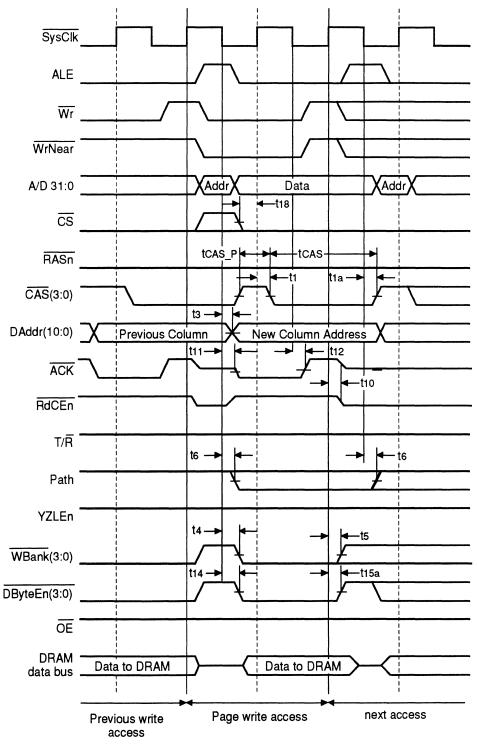

| Figure 7.11 (d)                                                                                                                                                                 | 3 Clock Cycles Page Write with $\overline{CAS}$ Pulse Width = 1.5 Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7 20                                                                                     |

| 0                                                                                                                                                                               | Cycles, CAS Pre-charge = 1.5 Clock Cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-21                                                                                     |

| Figure 7.11 (e)                                                                                                                                                                 | Page Write Using Internal Comparator, WrNear Not Asserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-22                                                                                     |

| Figure 7.12                                                                                                                                                                     | Page Write Access Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-23                                                                                     |

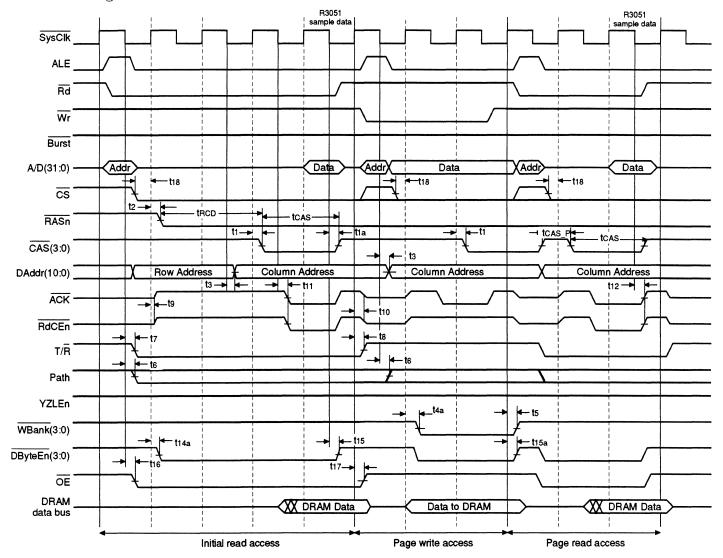

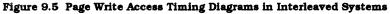

| Figure 7.13                                                                                                                                                                     | Single Read Followed by a Single Write Followed by a Single Read Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7-24                                                                                     |

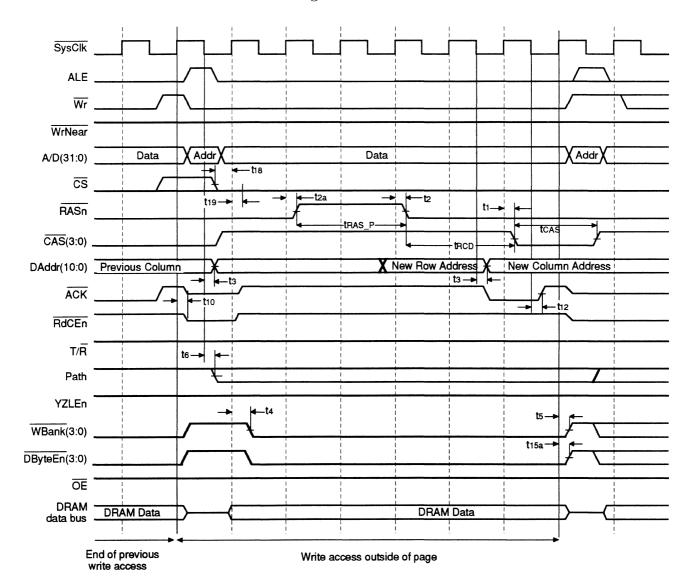

| Figure 7.14                                                                                                                                                                     | Single Write Access Outside of Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-25                                                                                     |

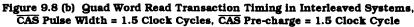

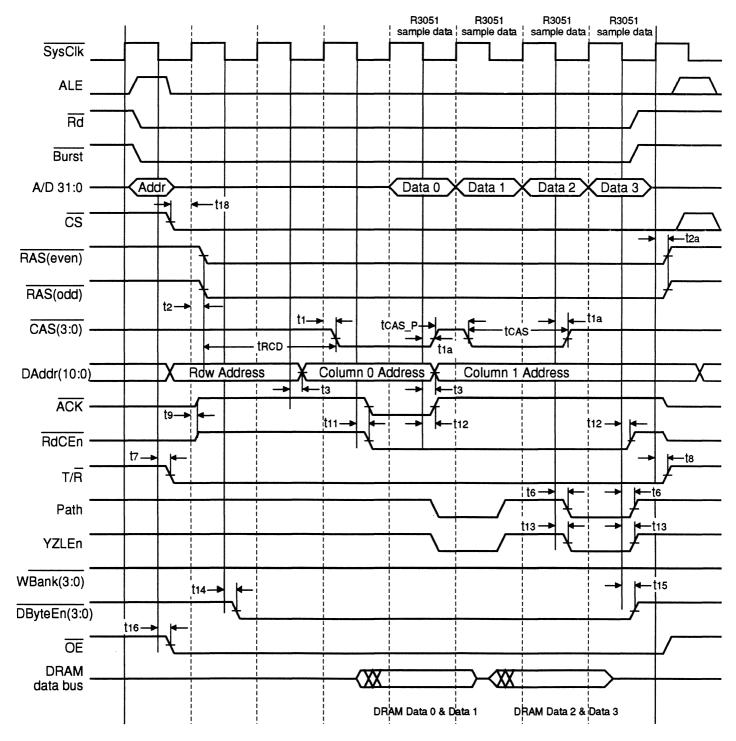

| Figure 7.15 (a)                                                                                                                                                                 | Quad Word Read Transaction Timing, $\overline{CAS}$ Pulse Width = 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                          |

| - garo o (a)                                                                                                                                                                    | Clock Cycles, CAS Pre-charge = 0.5 Clock Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7-27                                                                                     |

| Figure 7.15 (b)                                                                                                                                                                 | Quad Word Read Transaction Timing, $\overline{CAS}$ Pulse Width = 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                          |

| Bare                                                                                                                                                                            | Clock Cycles, CAS Pre-charge = 1.5 Clock Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7-28                                                                                     |

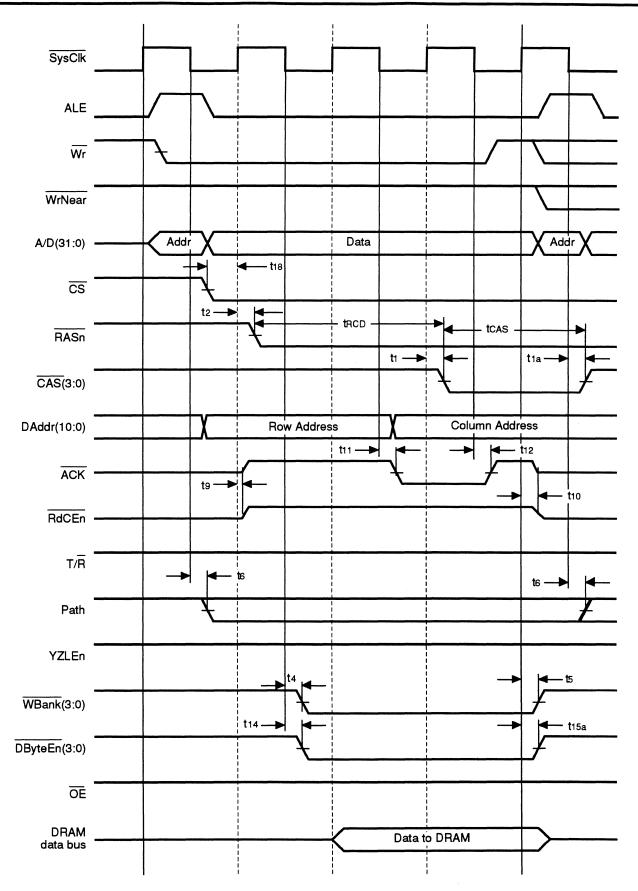

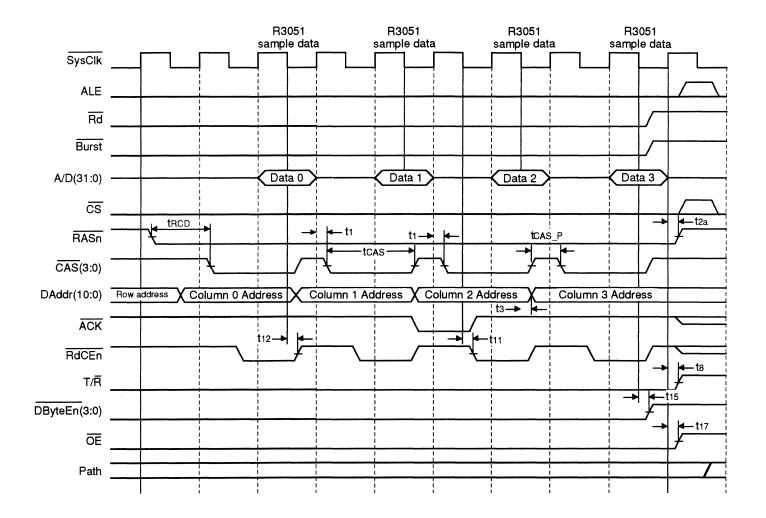

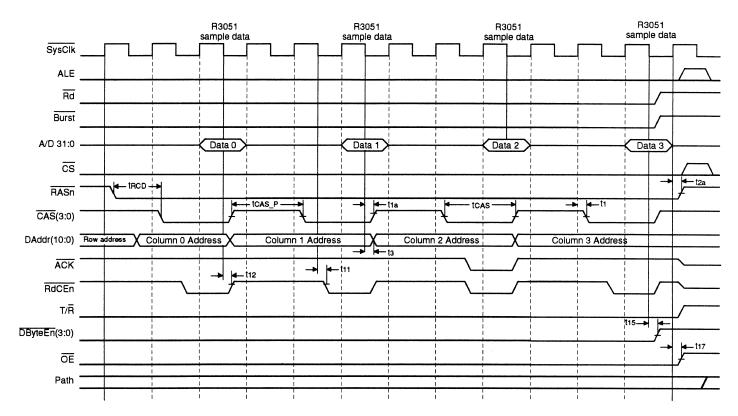

| Figure 7.16                                                                                                                                                                     | Quad Word Read Access Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-29                                                                                     |

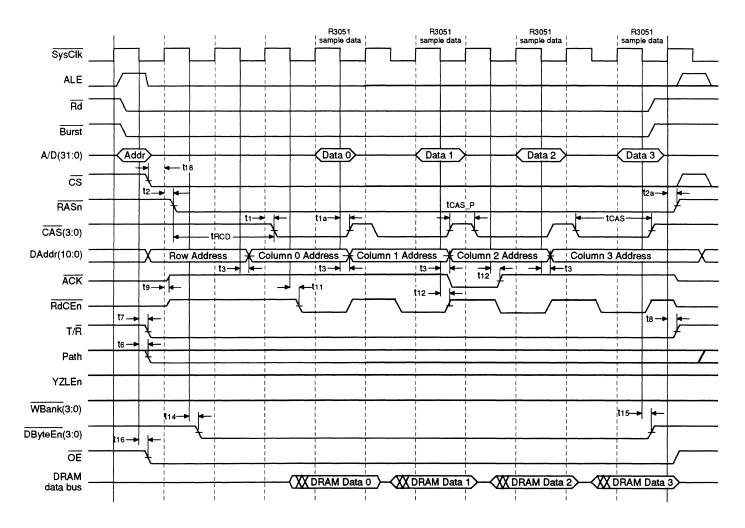

| Figure 7.17                                                                                                                                                                     | Page Quad Word Read Access Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-30                                                                                     |

| i igai c i i i i                                                                                                                                                                | rado Anna 1101a rona 1100000 111112 5 meruno 111111111111111111111111111111111111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                          |

| Figure 8.1                                                                                                                                                                      | General System Using the R3051 and the R3721                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8-2                                                                                      |

| Figure 8.2                                                                                                                                                                      | Address Decoder PAL Equations for DRAM_CS and MSel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8-3                                                                                      |

| Figure 8.3                                                                                                                                                                      | Detailed Connections for the R3721 in a Two Banks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                          |

| 0                                                                                                                                                                               | Non-interleaved Memory System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8-4                                                                                      |

| Figure 8.4                                                                                                                                                                      | Analysis to Set RCD in the Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8-9                                                                                      |

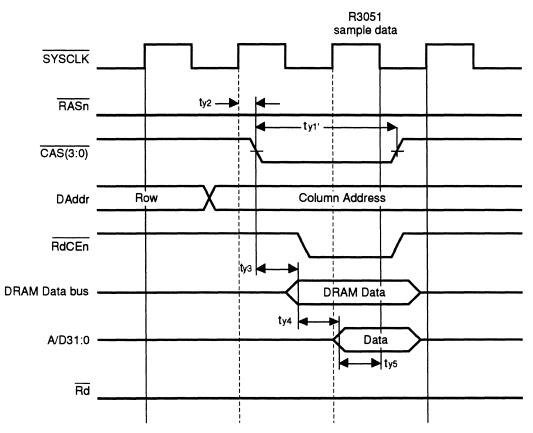

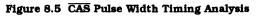

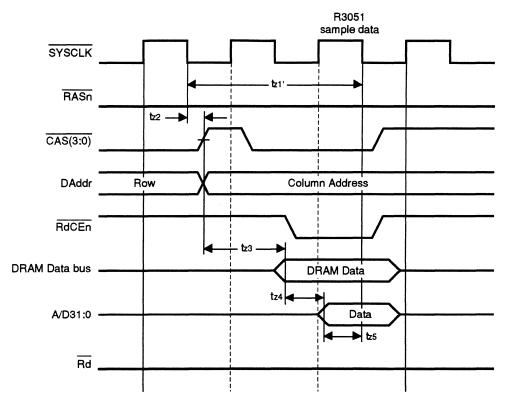

| Figure 8.5                                                                                                                                                                      | CAS Pulse Width Timing Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8-10                                                                                     |

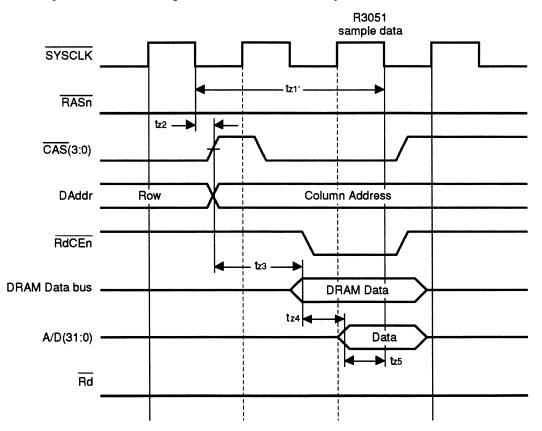

| Figure 8.6 (a)                                                                                                                                                                  | CAS Pre-charge Time Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8-12                                                                                     |

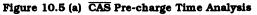

| Figure 8.6 (b)                                                                                                                                                                  | CAS Pre-charge Time Analysis During Writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8-13                                                                                     |

| Figure 8.7                                                                                                                                                                      | Mode Register Settings for a Two Bank Non-interleaved System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8-14                                                                                     |

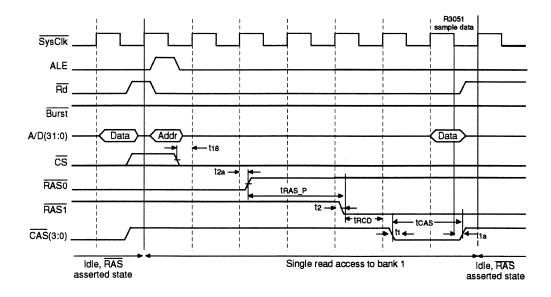

| Figure 8.8                                                                                                                                                                      | Single Read Access to Bank(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8-15                                                                                     |

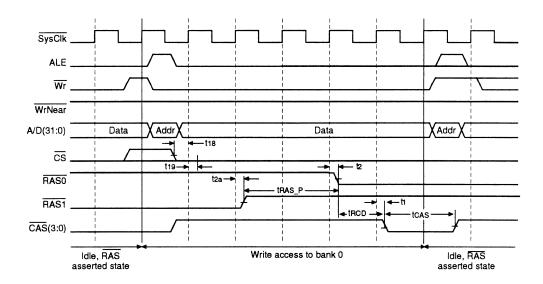

| Figure 8.9                                                                                                                                                                      | Single Write Access to Bank(0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8-16                                                                                     |

|                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                          |

| Figure 9.1                                                                                                                                                                      | Settings of the Mode Register Used as an Example in this                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                          |

| Ģ                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                          |

|                                                                                                                                                                                 | Chapter for Interleaved Memory Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9-1                                                                                      |

| Figure 9.2                                                                                                                                                                      | Chapter for Interleaved Memory Systems<br>Example of a Single Read Access for Interleaved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                          |

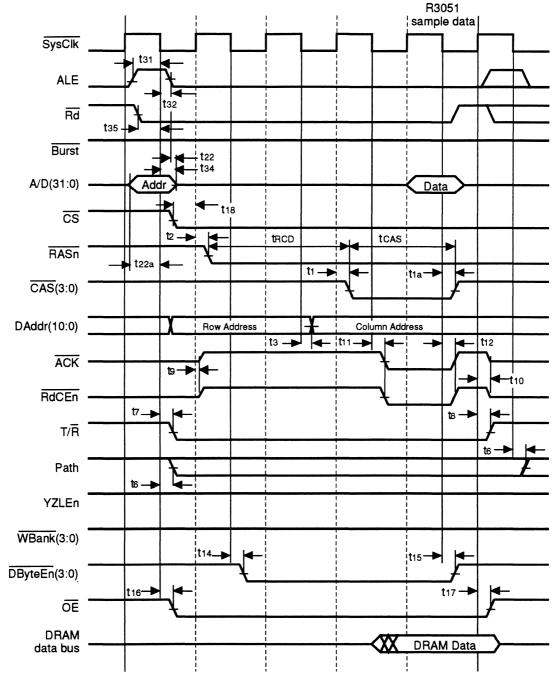

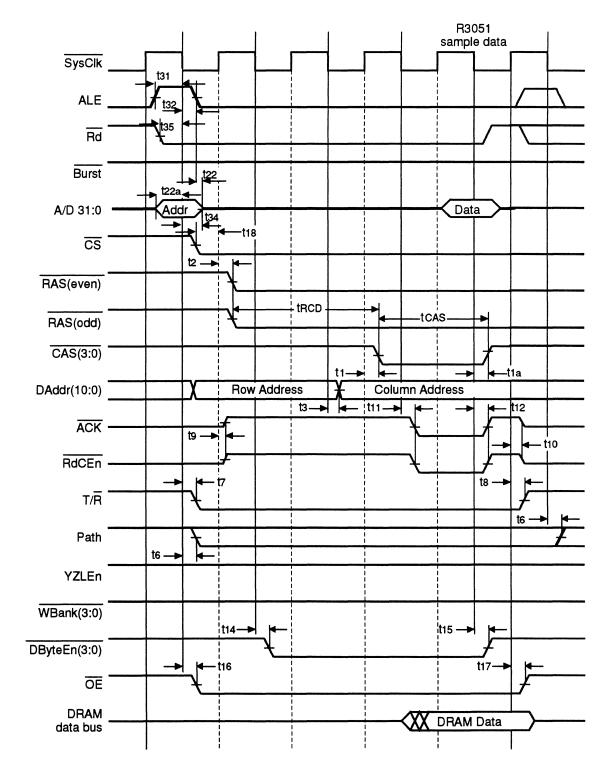

| Figure 9.2                                                                                                                                                                      | Chapter for Interleaved Memory Systems<br>Example of a Single Read Access for Interleaved<br>Memory Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9-1<br>9-4                                                                               |

|                                                                                                                                                                                 | Chapter for Interleaved Memory Systems<br>Example of a Single Read Access for Interleaved<br>Memory Systems<br>Page Read Access Timing Diagrams in Interleaved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9-4                                                                                      |

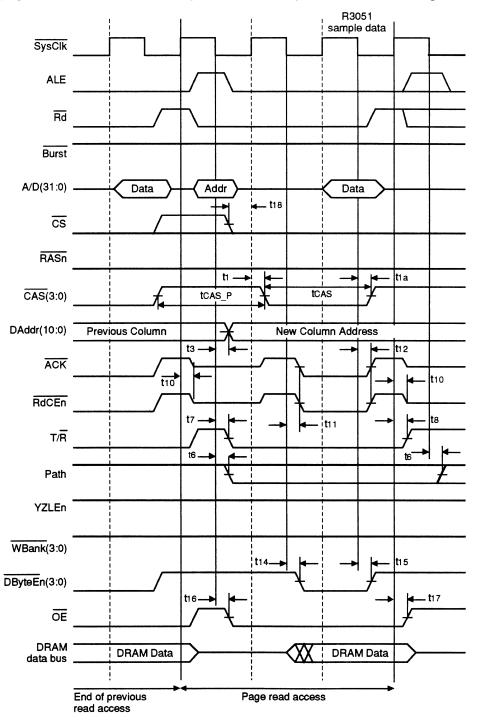

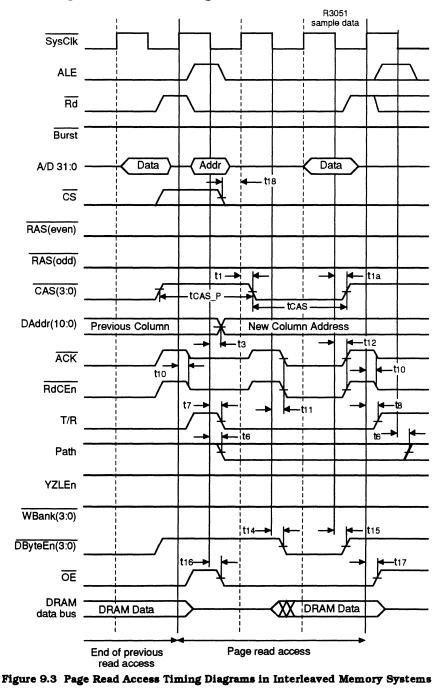

| Figure 9.2<br>Figure 9.3                                                                                                                                                        | Chapter for Interleaved Memory Systems<br>Example of a Single Read Access for Interleaved<br>Memory Systems<br>Page Read Access Timing Diagrams in Interleaved<br>Memory Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          |

| Figure 9.2                                                                                                                                                                      | Chapter for Interleaved Memory Systems<br>Example of a Single Read Access for Interleaved<br>Memory Systems<br>Page Read Access Timing Diagrams in Interleaved<br>Memory Systems<br>Single Read Access Outside of Page for the Interleaved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9-4<br>9-5                                                                               |

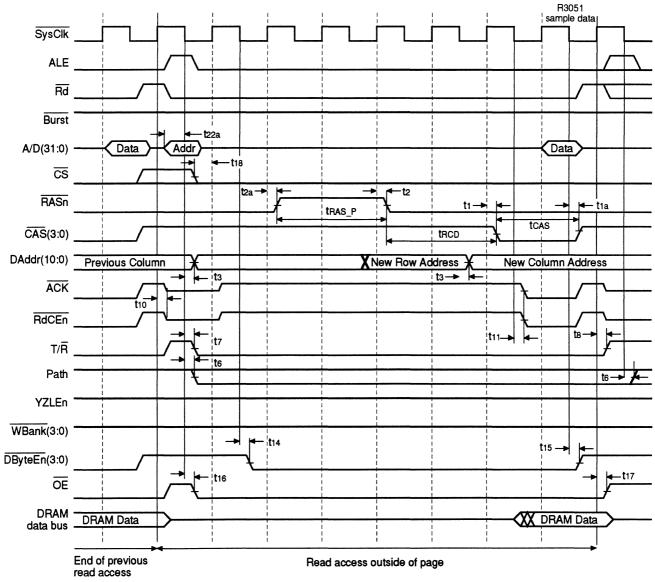

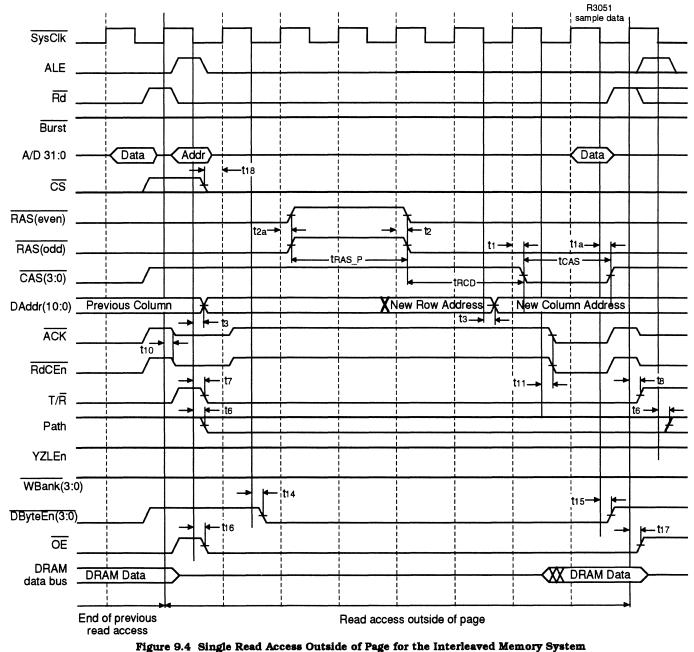

| Figure 9.2<br>Figure 9.3<br>Figure 9.4                                                                                                                                          | Chapter for Interleaved Memory Systems<br>Example of a Single Read Access for Interleaved<br>Memory Systems<br>Page Read Access Timing Diagrams in Interleaved<br>Memory Systems<br>Single Read Access Outside of Page for the Interleaved<br>Memory System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9-4<br>9-5<br>9-6                                                                        |

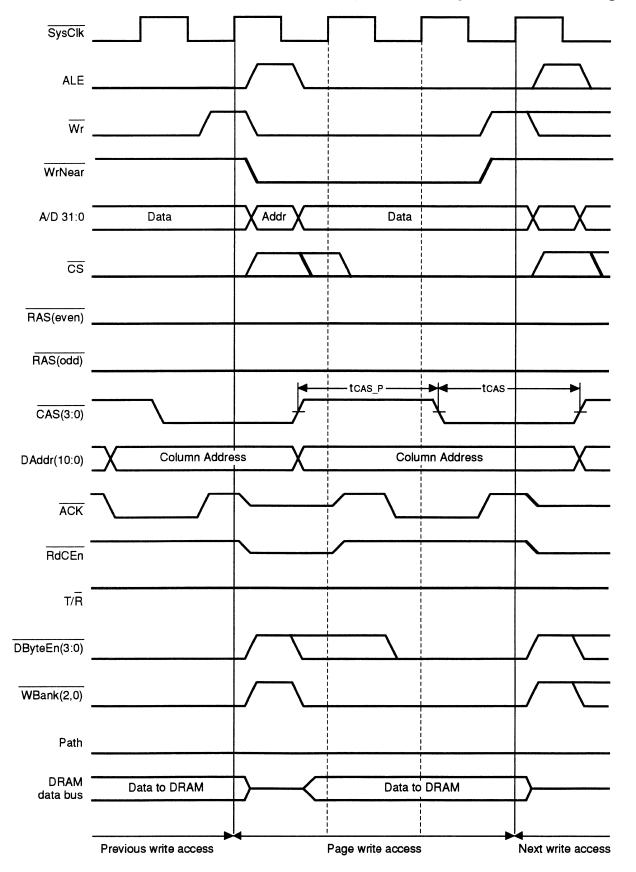

| Figure 9.2<br>Figure 9.3<br>Figure 9.4<br>Figure 9.5                                                                                                                            | Chapter for Interleaved Memory Systems<br>Example of a Single Read Access for Interleaved<br>Memory Systems<br>Page Read Access Timing Diagrams in Interleaved<br>Memory Systems<br>Single Read Access Outside of Page for the Interleaved<br>Memory System<br>Page Write Access Timing Diagrams in Interleaved Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9-4<br>9-5                                                                               |