# Intel486<sup>™</sup> Microprocessor Family Programmer's Reference Manual

# intel

## LITERATURE

To order Intel literature or obtain literature pricing information in the U.S. and Canada call or write Intel Literature Sales. In Europe and other international locations, please contact your *local* sales office or distributor.

### INTEL LITERATURE SALES P.O. Box 7641 Mt. Prospect, IL 60056-7641

In the U.S. and Canada call toll free (800) 548-4725 This 800 number is for external customers only.

## **CURRENT HANDBOOKS**

Product line handbooks contain data sheets, application notes, article reprints and other design information. All handbooks can be ordered individually, and most are available in a pre-packaged set in the U.S. and Canada.

| Title                                                              | Intel<br>Order Number | ISBN          |

|--------------------------------------------------------------------|-----------------------|---------------|

| SET OF FOURTEEN HANDBOOKS<br>(Available in U.S. and Canada)        | 231003                | N/A           |

| CONTENTS LISTED BELOW FOR INDIVIDUAL ORDERING                      | :                     |               |

| CONNECTIVITY                                                       | 231658                | 1-55512-202-7 |

| EMBEDDED MICROCONTROLLERS                                          | 270646                | 1-55512-203-5 |

| EMBEDDED MICROPROCESSORS                                           | 272396                | 1-55512-204-3 |

| FLASH MEMORY (2 volume set)                                        | 210830                | 1-55512-214-0 |

| MICROPROCESSORS, VOL. 1:<br>Intel386™ 80286 & 8086 MICROPROCESSORS | 230843                | 1-55512-196-9 |

| MICROPROCESSORS, VOL. 2:<br>Intel486™ MICROPROCESSORS              | 241731                | 1-55512-197-7 |

| MICROPROCESSORS, VOL. 3:<br>PENTIUM™ PROCESSORS                    | 241732                | 1-55512-198-5 |

| i750®, i860™, i960® PROCESSORS AND RELATED PRODUCTS                | 272084                | 1-55512-217-5 |

| OEM BOARDS, SYSTEMS & SOFTWARE                                     | 280407                | 1-55512-201-9 |

| PACKAGING                                                          | 240800                | 1-55512-208-6 |

| PERIPHERAL COMPONENTS                                              | 296467                | 1-55512-207-8 |

| PRODUCT OVERVIEW                                                   | 210846                | N/A           |

| PROGRAMMABLE LOGIC                                                 | 296083                | 1-55512-206-X |

| NETWORKING                                                         | 297360                | 1-55512-220-5 |

| ADDITIONAL LITERATURE:<br>(Not included in handbook set)           |                       |               |

| AUTOMOTIVE PRODUCTS                                                | 231792                | 1-55512-212-4 |

| COMPONENTS QUALITY/RELIABILITY                                     | 210997                | 1-55512-132-2 |

| CUSTOMER LITERATURE GUIDE                                          | 210620                | N/A           |

| EMBEDDED APPLICATIONS (1993/94)                                    | 270648                | 1-55512-179-9 |

| INTERNATIONAL LITERATURE GUIDE<br>(Available in Europe only)       | E00029                | N/A           |

| MILITARY AND SPECIAL PRODUCTS (2 volume set)                       | 210461                | 1-55512-213-2 |

| SYSTEMS QUALITY/RELIABILITY                                        | 231762                | 1-55512-046-6 |

# intel.

## **U.S. and CANADA LITERATURE ORDER FORM**

| NAME:                                                            |                                                   |                                                                |                                      |                                       |         |

|------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------|--------------------------------------|---------------------------------------|---------|

| COMPANY:                                                         |                                                   |                                                                |                                      |                                       | · ·     |

| ADDRESS:                                                         |                                                   |                                                                |                                      |                                       |         |

| CITY:                                                            |                                                   | STA                                                            | TE:                                  | ZIP:                                  |         |

| COUNTRY:                                                         |                                                   |                                                                |                                      |                                       |         |

| PHONE NO.: _(                                                    | )                                                 |                                                                |                                      |                                       |         |

| ORDER NO.                                                        | TITLE                                             | Ē                                                              | QTY.                                 | PRICE                                 | TOTAL   |

|                                                                  |                                                   |                                                                | ×                                    |                                       | =       |

|                                                                  |                                                   |                                                                | ×                                    |                                       | =       |

|                                                                  |                                                   |                                                                | ×                                    |                                       | =       |

|                                                                  |                                                   |                                                                | ×                                    | · · · · · · · · · · · · · · · · · · · | =       |

|                                                                  |                                                   |                                                                | ×                                    |                                       |         |

|                                                                  |                                                   |                                                                | ×                                    |                                       |         |

|                                                                  |                                                   |                                                                | ×                                    | :                                     | =       |

|                                                                  |                                                   |                                                                | ×                                    | ·                                     |         |

|                                                                  |                                                   |                                                                | ×                                    |                                       |         |

|                                                                  |                                                   |                                                                | ×                                    |                                       | <b></b> |

|                                                                  |                                                   |                                                                |                                      | Subtotal                              |         |

|                                                                  |                                                   |                                                                |                                      | t Add Your<br>Sales Tax _             |         |

| Include postage:<br>Must add 15% of Subtotal                     | to cover U.S.                                     |                                                                | >                                    | Postage _                             | 1       |

| and Canada postage. (20%                                         |                                                   |                                                                |                                      | -                                     |         |

| Pay by check, money or<br>accept VISA, MasterCard<br>delivery.   | der, or include company<br>or American Express. M | purchase order w<br>ake payment to In                          | vith this form (<br>tel Literature S |                                       |         |

| UISA MasterCard                                                  | American Express                                  | Expiration Date                                                |                                      |                                       |         |

| Account No                                                       |                                                   |                                                                |                                      |                                       |         |

| Signature                                                        |                                                   |                                                                |                                      | ·                                     | · · ·   |

| Mail To: Intel Literature S<br>P.O. Box 7641<br>Mt. Prospect, IL | sho                                               | ernational Custo<br>buld use the Intern<br>tact their local Sa | national order f                     | form on the r                         |         |

For phone orders in the U.S. and Canada, call Toll Free: (800) 548-4725 or FAX to (708) 296-3699. Please print clearly in ink to expedite your order.

Prices good until 12/31/94. Source HB

# intel

## INTERNATIONAL LITERATURE ORDER FORM

| NAME:                                                                                                          |   |       | -            |         | e State  |

|----------------------------------------------------------------------------------------------------------------|---|-------|--------------|---------|----------|

| COMPANY:                                                                                                       |   |       |              |         |          |

| ADDRESS:                                                                                                       |   |       |              |         |          |

| CITY:                                                                                                          |   |       | STATE: _     |         | ZIP:     |

| COUNTRY:                                                                                                       |   |       |              |         |          |

| PHONE NO.: _(                                                                                                  | ) |       |              |         |          |

| ORDER NO.                                                                                                      |   | TITLE | an <b>QT</b> | Y. PRIC | CE TOTAL |

|                                                                                                                |   |       |              | ×       |          |

|                                                                                                                |   |       |              | ×       | =        |

|                                                                                                                |   |       |              | ×       |          |

|                                                                                                                |   |       |              | ×       |          |

|                                                                                                                |   |       |              | X       |          |

|                                                                                                                |   |       | ·            | ×       | ,        |

|                                                                                                                |   |       |              | ×       | =        |

|                                                                                                                |   |       |              | ×;      |          |

|                                                                                                                |   |       |              | ×       |          |

|                                                                                                                |   |       |              | ×       | =        |

| a a status                                                                                                     |   |       |              | Subt    | otal     |

| and a second |   |       |              |         | Тах      |

|                                                                                                                |   |       |              | Т       | otal     |

### PAYMENT

Cheques should be made payable to your *local* Intel Sales Office (see inside back cover).

Other forms of payment may be available in your country. Please contact the Literature Coordinator at your *local* Intel Sales Office for details.

The completed form should be marked to the attention of the LITERATURE COORDINATOR and returned to your *local* Intel Sales Office.

Founded in 1968 to pursue the integration of large numbers of transistors onto tiny silicon chips, Intel's history has been marked by a remarkable number of scientific breakthroughs and innovations. In 1971, Intel introduced the 4004, the first microprocessor. Containing 2300 transistors, this first commercially-available computer on a chip is considered primitive compared with today's million-plus transistor products.

Innovations such as the microprocessor, the erasable programmable read-only memory (EPROM) and the dynamic random access memory (DRAM) revolutionized electronics by making integrated circuits the mainstay of both consumer and business computing products.

Over the last two and a half decades, Intel's business has evolved and today the company's focus is on delivering an extensive line of component, module and system-level building block products to the computer industry. The company's product line covers a broad spectrum, and includes microprocessors, flash memory, microcontrollers, a broad line of PC enhancement and local area network products, multimedia technology products, and massively parallel supercomputers. Intel's 32-bit X86 architecture, represented by the Intel386<sup>™</sup> and Intel486<sup>™</sup> microprocessor families, are the de facto standard of modern business computing and installed in millions of PCs worldwide.

Intel has over 25,000 employees located in offices and manufacturing facilities around the world. Today, Intel is the largest semiconductor company in the United States and the second largest in the world.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\*Other brands and names are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

©INTEL CORPORATION, 1993

# intel

# Intel486<sup>™</sup> MICROPROCESSOR FAMILY PROGRAMMER'S REFERENCE MANUAL

1992

그는 문서 수 많은 것이 많이 잘 많은 것이 없다.

## **TABLE OF CONTENTS**

| CHAPTER 1                                                       |      |

|-----------------------------------------------------------------|------|

| INTRODUCTION TO THE                                             |      |

| Intel486 <sup>™</sup> MICROPROCESSOR FAMILY                     | Dage |

| 1.1 ORGANIZATION OF THIS MANUAL                                 | 1-2  |

| 1.1.1 Part I-Application Programming                            | 1-3  |

| 1.1.2 Part II – System Programming                              | 1-3  |

| 1.1.3 Part III – Numeric Processing                             | 1-4  |

| 1.1.4 Part IV – Compatibility                                   | 1-5  |

| 1.1.5 Part V-Instruction Set                                    | 1-6  |

| 1.1.6 Appendices                                                | 1-6  |

| 1.2 RELATED LITERATURE                                          | 1-6  |

| 1.3 NOTATIONAL CONVENTIONS                                      | 1-7  |

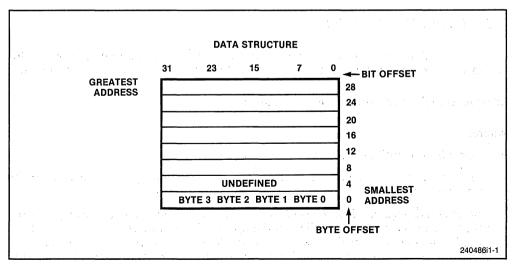

| 1.3.1 Bit and Byte Order                                        | 1-7  |

| 1.3.2 Undefined Bits and Software Compatibility                 | 1-8  |

| 1.3.3 Instruction Operands                                      | 1-8  |

| 1.3.4 Hexadecimal Numbers                                       | 1-9  |

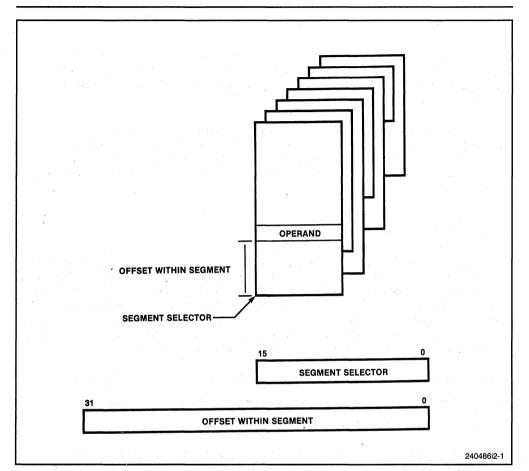

| 1.3.5       Segmented Addressing         1.3.6       Exceptions | 1-9  |

| 1.3.6 Exceptions                                                | 1-9  |

|                                                                 |      |

## PART I-APPLICATION PROGRAMMING

## CHAPTER 2

----

| BASIC PROGRAMMING MODEL               |        |          |

|---------------------------------------|--------|----------|

| 2.1 MEMORY ORGANIZATION               |        | <br>2-1  |

| 2.1.1 Unsegmented or "Flat" Model     |        | <br>2-3  |

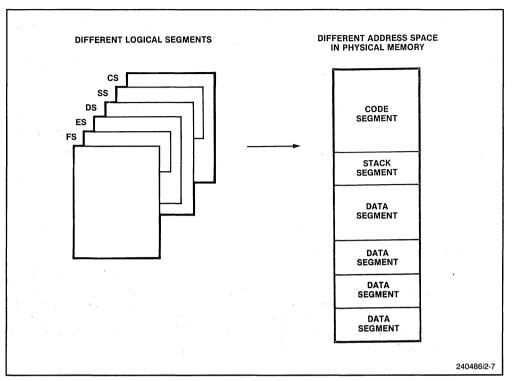

| 2.1.2 Segmented Model                 |        | <br>2-3  |

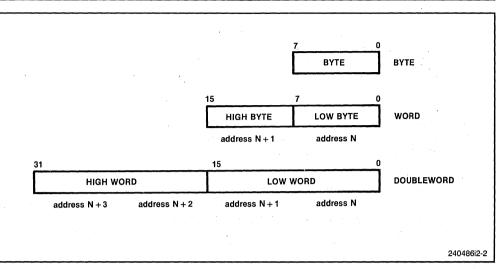

| 2.2 DATĂ TYPES                        |        | <br>2-3  |

| 2.3 REGISTERS                         |        | <br>2-8  |

| 2.3.1 General Registers               |        | <br>2-8  |

| 2.3.2 Segment Registers               |        | <br>2-10 |

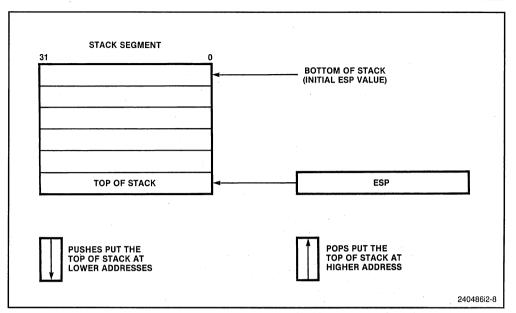

| 2.3.3 Stack Implementation            |        | <br>2-12 |

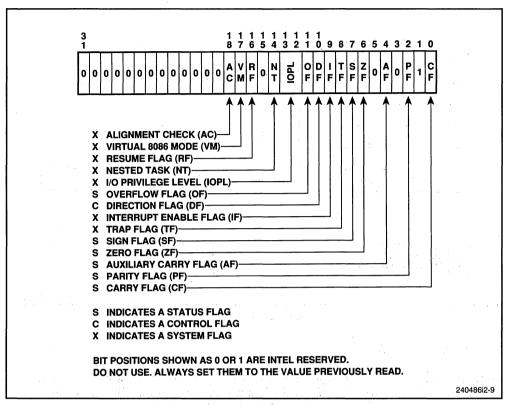

| 2.3.4 Flags Register                  |        | 2-13     |

| 2.3.4.1 STATUS FLAGS                  |        | <br>2-13 |

| 2.3.4.2 CONTROL FLAG                  |        | 2-13     |

| 2.3.4.3 INSTRUCTION POINTER           |        | <br>2-14 |

| 2.4 INSTRUCTION FORMAT                | •••••• | <br>2-15 |

| 2.5 OPERAND SELECTION                 | •••••• | <br>2-17 |

| 2.5.1 Immediate Operands              |        | <br>2-18 |

| 2.5.2 Register Operands               |        | 2-19     |

| 2.5.3 Memory Operands                 |        | 2-19     |

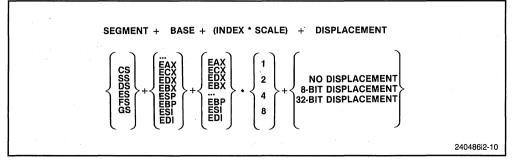

| 2.5.3.1 SEGMENT SELECTION             |        | <br>2-20 |

| 2.5.3.2 EFFECTIVE-ADDRESS COMPUTATION |        | <br>2-20 |

| 2.6 INTERRUPTS AND EXCEPTIONS         |        | <br>2-23 |

# CHAPTER 3 APPLICATION PROGRAMMING

| 3.1 DATA MOVEMENT INSTRUCTIONS                   | 3-1 |

|--------------------------------------------------|-----|

| 3.1.1 General-Purpose Data Movement Instructions |     |

| 3.1.2 Stack Manipulation Instructions            |     |

| 3.1.3 Type Conversion Instructions               |     |

|                                                        | Page         |

|--------------------------------------------------------|--------------|

| 3.2 BINARY ARITHMETIC INSTRUCTIONS                     | 3-6          |

| 3.2.1 Addition and Subtraction Instructions            |              |

| 3.2.2 Comparison and Sign Change Instruction           | 3-8          |

| 3.2.3 Multiplication Instructions                      | 3-8          |

| 3.2.4 Division Instructions                            | 3-9          |

| 3.3 DECIMAL ARITHMETIC INSTRUCTIONS                    | 3-10         |

| 3.3.1 Packed BCD Adjustment Instructions               | 3-10         |

| 3.3.2 Unpacked BCD Adjustment Instructions             | 3-10         |

| 3.4 LOGICAL INSTRUCTIONS                               | 3-11         |

| 3.4.1 Boolean Operation Instructions                   | 3-11         |

| 3.4.2 Bit Test and Modify Instructions                 | 3-12         |

| 3.4.3 Bit Scan Instructions                            | 3-12         |

| 3.4.4 Shift and Rotate Instructions                    | 3-13         |

| 3.4.4.1 SHIFT INSTRUCTIONS                             | 3-13         |

| 3.4.4.2 DOUBLE-SHIFT INSTRUCTIONS                      | 3-14         |

| 3.4.4.3 ROTATE INSTRUCTIONS                            | 3-16         |

| 3.4.4.4 FAST "bit bit" USING DOUBLE-SHIFT INSTRUCTIONS | 3-19         |

| 3.4.4.5 FAST BIT STRING INSERT AND EXTRACT             | 3-20         |

| 3.4.5 Byte-Set-On-Condition Instructions               | 3-23         |

| 3.4.6 Test Instruction                                 | 3-23         |

| 3.5 CONTROL TRANSFER INSTRUCTIONS                      | 3-23         |

| 3.5.1 Unconditional Transfer Instructions              | 3-23         |

| 3.5.1.1 JUMP INSTRUCTION                               | 3-23         |

| 3.5.1.2 CALL INSTRUCTIONS                              | 3-24         |

| 3.5.1.3 RETURN AND RETURN-FROM-INTERRUPT INSTRUCTIONS  | 3-24         |

|                                                        | 3-25         |

| 3.5.2.1 CONDITIONAL JUMP INSTRUCTIONS                  | 3-25         |

| 3.5.2.2 LOOP INSTRUCTIONS                              | 3-26         |

| 3.5.2.3 EXECUTING A LOOP OR REPEAT ZERO TIMES          | 3-26         |

| 3.5.3 Software Interrupts                              | 3-27         |

| 3.6 STRING OPERATIONS                                  |              |

| 3.6.1 Repeat Prefixes                                  | 3-28         |

| 3.6.2 Indexing and Direction Flag Control              | 3-29         |

| 3.6.3 String Instructions                              | 3-30         |

| 3.7 INSTRUCTIONS FOR BLOCK-STRUCTURED LANGUAGES        | 3-30         |

| 3.8 FLAG CONTROL INSTRUCTIONS                          | 3-37         |

| 3.8.1 Carry and Direction Flag Control Instructions    |              |

| 3.8.2 Flag Transfer Instructions                       | 3-37         |

| 3.9 NUMERIC INSTRUCTIONS                               |              |

| 3.10 SEGMENT REGISTER INSTRUCTIONS                     | 3-30         |

| 3.10.1 Segment-Register Transfer Instructions          | 3-40         |

| 3.10.2 Far Control Transfer Instructions               | 3-40         |

| 3.10.3 Data Pointer Instructions                       |              |

| 3.11 MISCELLANEOUS INSTRUCTIONS                        | 3-40         |

|                                                        | 3-41         |

| 3.11.1 CPU_ID Detection Code                           |              |

| 3.11.2 Address Calculation Instruction                 | 3-46         |

| 3.11.3 No-Operation Instruction                        | 3-46         |

| 3.11.4 Translate Instruction                           | 3-46         |

| 3.11.5 Byte Swap Instruction                           | 3-46         |

| 3.11.6 Exchange-and-Add Instruction                    | 3-47         |

| 3.11.7 Compare-and-Exchange Instruction                | <u>3</u> -47 |

## PART II-SYSTEM PROGRAMMING

| CHAPTER 4                                     |              |

|-----------------------------------------------|--------------|

| SYSTEM ARCHITECTURE                           | Page         |

| 4.1 SYSTEM REGISTERS                          | 4-1          |

| 4.1.1 System Flags                            | 4-2          |

| 4.1.2 Memory-Management Registers             | 4-4          |

| 4.1.3 Control Registers                       | 4-5          |

| 4.1.4 Debug Registers                         | 4-8          |

| 4.1.5 Test Registers                          | 4-8          |

| 4.2 SYSTEM INSTRUCTIONS                       | 4-9          |

|                                               |              |

| CHAPTER 5                                     |              |

| MEMORY MANAGEMENT                             |              |

| 5.1 SELECTING A SEGMENTATION MODEL            | 5-3          |

| 5.1.1 Flat Model                              | 5-3          |

| 5.1.2 Protected Flat Model                    |              |

| 5.1.3 Multi-Segment Model                     | 5-4          |

| 5.2 SEGMENT TRANSLATION                       | 5-5          |

| 5.2.1 Segment Registers                       | 5-7          |

| 5.2.2 Segment Selectors                       |              |

| 5.2.3 Segment Descriptors                     | 5-10         |

| 5.2.3 Segment Descriptor Tables               | 5-15         |

| 5.2.4 Segment description rables              | 5-15         |

| 5.2.5 Descriptor Table Base Registers         | 5-16         |

| 5.3 Page Translation                          | 5-17<br>5-18 |

| 5.3.1 PG Bit Enables Paging                   | 5-18         |

| 5.3.2 Linear Address                          |              |

| 5.3.3 Page Tables                             | 5-19         |

| 5.3.4 Page-Table Entries                      | 5-20         |

| 5.3.4.1 PAGE FRAME ADDRESS                    | 5-20         |

| 5.3.4.2 PRESENT BIT                           | 5-20         |

| 5.3.4.3 ACCESSED AND DIRTY BITS               | 5-21         |

| 5.3.4.4 READ/WRITE AND USER/SUPERVISOR BITS   | 5-22         |

| 5.3.4.5 PAGE-LEVEL CACHE CONTROL BITS         | 5-22         |

| 5.3.5 Translation Lookaside Buffer            | 5-22         |

| 5.4 COMBINING SEGMENT AND PAGE TRANSLATION    | 5-23         |

| 5.4.1 Flat Model                              | 5-23         |

| 5.4.2 Segments Spanning Several Pages         | 5-24         |

| 5.4.3 Pages Spanning Several Segments         | 5-24         |

| 5.4.4 Non-Aligned Page and Segment Boundaries | 5-24         |

| 5.4.5 Aligned Page and Segment Boundaries     | 5-24         |

| 5.4.6 Page-Table Per Segment                  | 5-24         |

|                                               |              |

### CHAPTER 6 PROTECTION

| 6.1 SEGMENT-LEVEL PROTECTION           |      |

|----------------------------------------|------|

| 6.2 SEGMENT DESCRIPTORS AND PROTECTION | 6-2  |

| 6.2.1 Type Checking                    | 6-3  |

| 6.2.2 Limit Checking                   | 6-4  |

| 6.2.3 Privilege Levels                 | 6-5  |

| 6.3 RESTRIČTING ACCESS TO DATA         |      |

| 6.3.1 Accessing Data in Code Segments  | 6-8  |

| 6.4 RESTRICTING CONTROL TRANSFERS      | 6-9  |

| 6.5 GATE DESCRIPTORS                   | 6-11 |

|                                        |      |

| n de la companya de l | Page |

|-----------------------------------------------------------------------------------------------------------------|------|

|                                                                                                                 | 6-13 |

|                                                                                                                 | 6-17 |

|                                                                                                                 | 6-19 |

| 6.6.1 Privileged Instructions                                                                                   | 6-19 |

| 6.6.2 Sensitive Instructions                                                                                    | 6-19 |

| 6.7 INSTRUCTIONS FOR POINTER VALIDATION                                                                         | 6-20 |

|                                                                                                                 | 6-21 |

| 6.7.2 Pointer Integrity and RPL                                                                                 | 6-22 |

| 6.8 PAGE-LEVEL PROTECTION                                                                                       | 6-22 |

| 6.8.1 Page-Table Entries Hold Protection Parameters                                                             | 6-23 |

|                                                                                                                 | 6-23 |

|                                                                                                                 | 6-24 |

| 6.8.2 Combining Protection of Both Levels of Page Tables                                                        | 6-24 |

|                                                                                                                 | 6-24 |

|                                                                                                                 | 6-25 |

## CHAPTER 7 MULTITASKING

| 1 TASK STATE SEGMENT                      | 7-2  |

|-------------------------------------------|------|

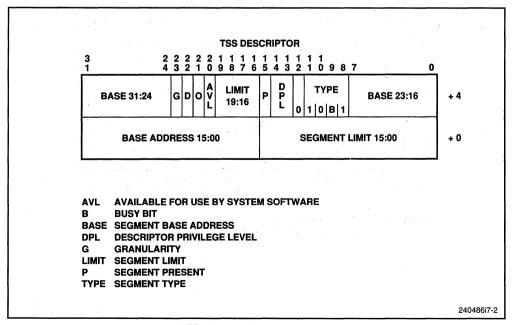

| 2 TSS DESCRIPTOR                          | 7-4  |

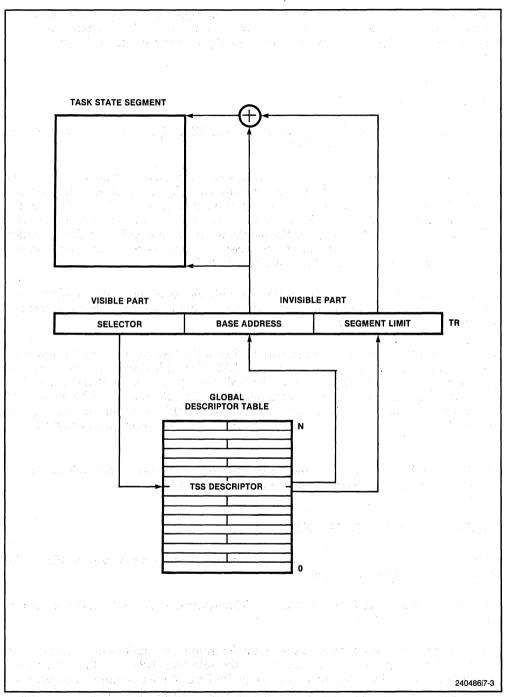

| 7.3 TASK REGISTER                         | 7-5  |

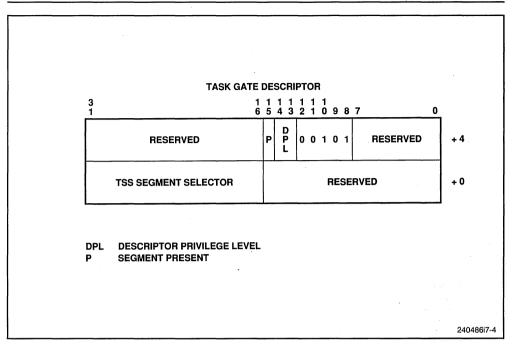

| 7.4 TASK GATE DESCRIPTOR                  | 7-5  |

| 7.5 TASK SWITCHING                        | 7-8  |

| 7.6 TASK LINKING                          | 7-10 |

| 6.1 Busy Bit Prevents Loops               | 7-10 |

| 7.6.2 Modifying Task Linkages             | 7-13 |

| 7.7 TASK ADDRESS SPACE                    | 7-13 |

| 7.1 Task Linear-to-Physical Space Mapping | 7-14 |

| 7.2 Task Logical Address Space            | 7-14 |

|                                           |      |

## CHAPTER 8 INPUT/OUTPUT

| 8.1 I/O ADDRESSING              | 8-1 |

|---------------------------------|-----|

| 8.1.1 I/O Address Space         | 8-2 |

| 8.1.2 Memory-Mapped I/O         | 8-3 |

| 8.2 I/O INSTRUCTIONS            | 8-4 |

| 8.2.1 Register I/O Instructions | 8-4 |

| 8.2.2 Block I/O Instructions    | 8-5 |

| 8.3 PROTECTION AND I/O          | 8-6 |

| 8.3.1 I/O Privilege Level       |     |

| 8.3.2 I/O Permission Bit Map    |     |

## **CHAPTER 9**

| EXCEPTIONS AND INTERRUPTS                                   |     |

|-------------------------------------------------------------|-----|

| 9.1 EXCEPTION AND INTERRUPT VECTORS                         | 9-1 |

| 9.2 INSTRUCTION RESTART                                     | 9-2 |

| 9.3 ENABLING AND DISABLING INTERRUPTS                       | 9-3 |

| 9.3.1 NMI Masks Further NMIs                                |     |

| 9.3.2 IF Masks INTR                                         |     |

| 9.3.3 RF Masks Debug Faults                                 |     |

| 9.3.4 MOV or POP to SS Masks Some Exceptions and Interrupts | 9-4 |

| 9.4 PRIORITY AMONG SIMULTANEOUS EXCEPTIONS AND INTERRUPTS   | 9-5 |

| 9.5 INTERRUPT DESCRIPTOR TABLE                              | 9-5 |

|                                                              | Page |

|--------------------------------------------------------------|------|

| 9.6 IDT DESCRIPTORS                                          | 9-7  |

| 9.7 INTERRUPT TASKS AND INTERRUPT PROCEDURES                 |      |

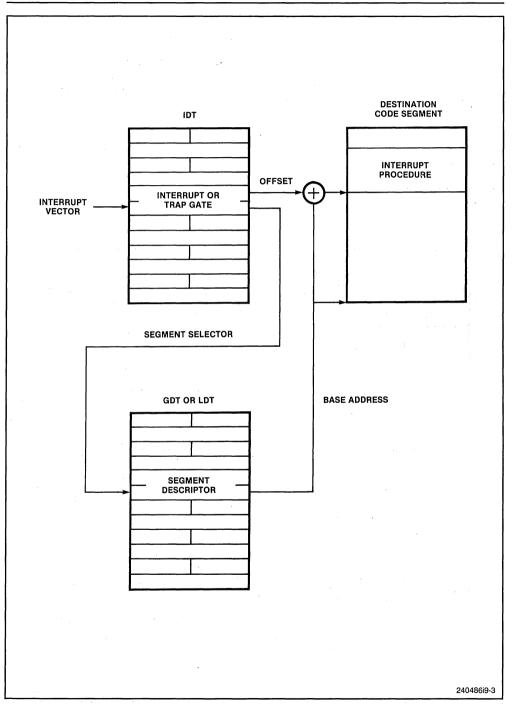

| 9.7.1 Interrupt Procedures                                   | 9-7  |

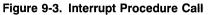

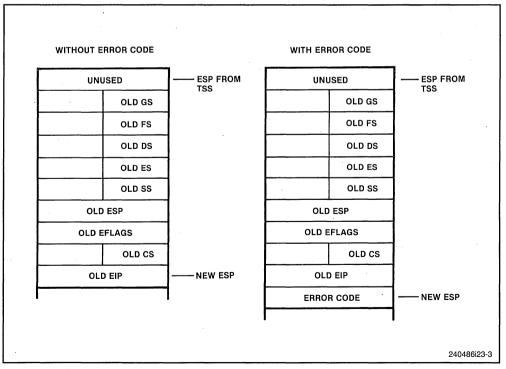

| 9.7.1.1 STACK OF INTERRUPT PROCEDURE                         | 9-10 |

| 9.7.1.2 RETURNING FROM AN INTERRUPT PROCEDURE                | 9-11 |

| 9.7.1.3 FLAG USAGE BY INTERRUPT PROCEDURE                    | 9-11 |

| 9.7.1.4 PROTECTION IN INTERRUPT PROCEDURES                   | 9-11 |

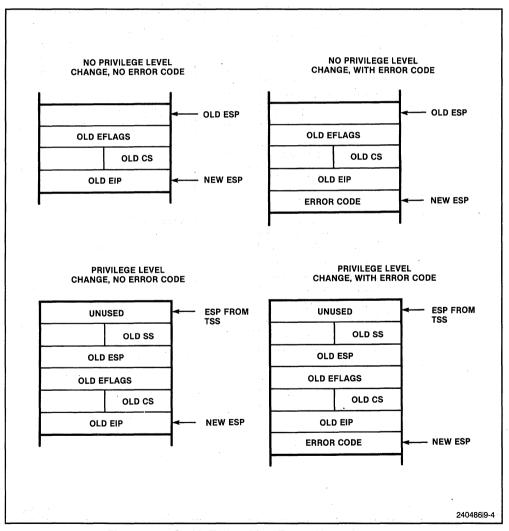

| 9.7.2 Interrupt Tasks                                        | 9-12 |

| 9.8 ERROR CODE                                               | 9-13 |

| 9.9 EXCEPTION CONDITIONS                                     | 9-14 |

| 9.9.1 Interrupt 0 – Divide Error                             | 9-14 |

| 9.9.2 Interrupt 1-Debug Exceptions                           | 9-14 |

| 9.9.3 Interrupt 3-Breakpoint                                 | 9-15 |

| 9.9.4 Interrupt 4-Overflow                                   | 9-15 |

| 9.9.5 Interrupt 5-Bounds Check                               | 9-15 |

| 9.9.6 Interrupt 6-Invalid Opcode                             | 9-15 |

| 9.9.7 Interrupt 7-Device Not Available                       | 9-16 |

| 9.9.8 Interrupt 8-Double Fault                               |      |

| 9.9.9 Interrupt 9 – (Intel reserved. Do not use.)            | 9-18 |

| 9.9.10 Interrupt 10-Invalid TSS                              | 9-18 |

| 9.9.11 Interrupt 11 – Segment Not Present                    | 9-19 |

| 9.9.12 Interrupt 12–Stack Exception                          | 9-20 |

| 9.9.13 Interrupt 13–General Protection                       | 9-20 |

| 9.9.14 Interrupt 14-Page Fault                               | 9-21 |

| 9.9.14.1 PAGE FAULT DURING TASK SWITCH                       | 9-23 |

| 9.9.14.2 PAGE FAULT WITH INCONSISTENT STACK POINTER          |      |

| 9.9.15 Interrupt 16—Floating-Point Error                     |      |

| 9.9.16 Interrupt 17-Alignment Check                          | 9-24 |

| 9.10 EXCEPTION SUMMARY                                       |      |

| 9.11 ERROR CODE SUMMARY                                      |      |

|                                                              | 5,25 |

| CHAPTER 10                                                   |      |

|                                                              |      |

| INITIALIZATION<br>10.1 PROCESSOR STATE AFTER RESET           | 10.1 |

| 10.2 Intel486 SX MICROPROCESSOR/Intel487 SX MATH COPROCESSOR | 10-1 |

| INITIALIZATION                                               | 10.2 |

| 10.3 SOFTWARE INITIALIZATION IN REAL-ADDRESS MODE            | 10-5 |

| 10.3.1 System Tables                                         |      |

| 10.3.2 NMI Interrupt                                         | 10-5 |

| 10.3.3 First Instruction                                     |      |

|                                                              |      |

| 10.3.4 Enabling Caching<br>10.4 SWITCHING TO PROTECTED MODE  | 10-5 |

| 10.4.1 System Tables                                         | 10-6 |

| 10.4.1 System Tables                                         | 10-6 |

| 10.4.2 NMI Interrupt<br>10.4.3 PE Bit                        | 10-6 |

|                                                              | 10-6 |

| 10.5 SOFTWARE INITIALIZATION IN PROTECTED MODE               | 10-6 |

| 10.5.1 Segmentation                                          | 10-7 |

| 10.5.2 Paging                                                |      |

| 10.5.3 Tasks                                                 |      |

| 10.6 TLB TESTING                                             |      |

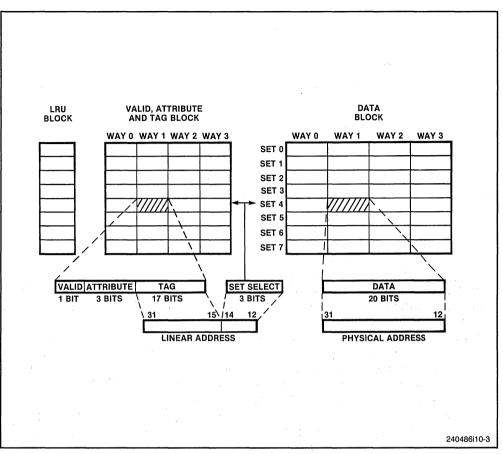

| 10.6.1 Structure of the TLB                                  | 10-8 |

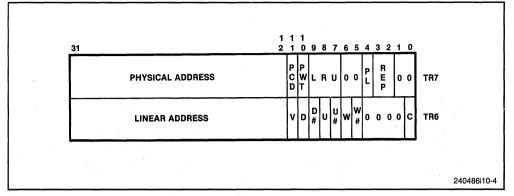

10.6.2 Test Registers

10-9

10.6.3 Test Operations

10-11

|                                                                                                                       | Page  |

|-----------------------------------------------------------------------------------------------------------------------|-------|

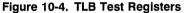

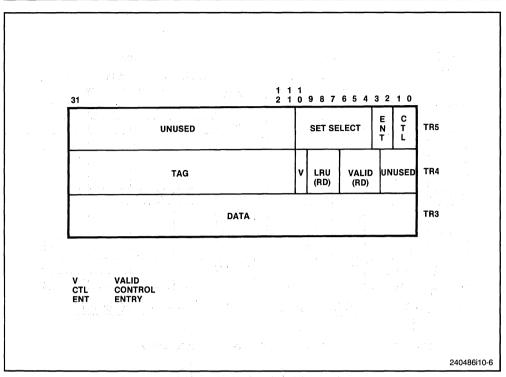

| 10.7 CACHE TESTING                                                                                                    | 10-12 |

| 10.7.1 Structure of the Cache                                                                                         | 10-12 |

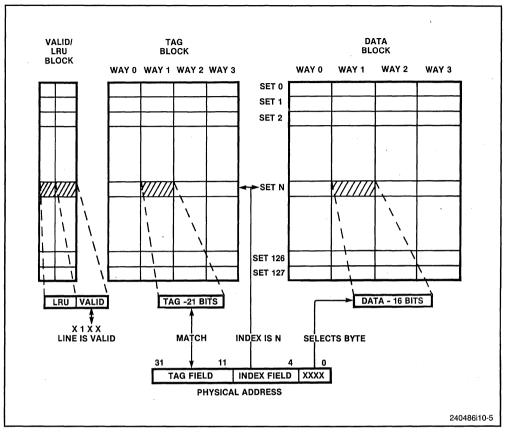

| 10.7.2 Test Registers                                                                                                 | 10-13 |

| 10.7.3 Test Operations                                                                                                | 10-15 |

| 10.8 INITIALIZATION EXAMPLE                                                                                           | 10-16 |

|                                                                                                                       |       |

| CHAPTER 11                                                                                                            |       |

| DEBUGGING                                                                                                             |       |

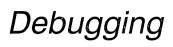

| 11.1 DEBUGGING SUPPORT                                                                                                | 11_1  |

| 11.2 DEBUG REGISTERS                                                                                                  | 11-1  |

| 11.2.1 Dobug Address Registers (DR0 DR2)                                                                              | 11 0  |

| 11.2.1 Debug Address Registers (DR0-DR3)<br>11.2.2 Debug Control Register (DR7)<br>11.2.3 Debug Status Register (DR6) | 11-2  |

| 11.2.2 Debug Control Register (DR7)                                                                                   | 11-2  |

| 11.2.3 Debug Status Register (DR6)                                                                                    | 11-4  |

| 11.2.4 Breakpoint Field Recognition                                                                                   | 11-5  |

| 11.3 DEBUG EXCEPTIONS                                                                                                 | 11-6  |

| 11.3.1 Interrupt 1 – Debug Exceptions<br>11.3.1.1 INSTRUCTION-BREAKPOINT FAULT                                        | 11-6  |

| 11.3.1.1 INSTRUCTION-BREAKPOINT FAULT                                                                                 | 11-6  |

| 11.3.1.2 DATA-BREAKPOINT TRAP                                                                                         | 11-7  |

| 11.3.1.2 DATA-BREAKPOINT TRAP<br>11.3.1.3 GENERAL-DETECT FAULT                                                        | 11-7  |

| 11.3.1.4 SINGI F-STEP TRAP                                                                                            | 11-8  |

| 11.3.1.5 TASK-SWITCH TRAP                                                                                             | 11-8  |

| 11.3.2 Interrupt 3-Breakpoint Instruction                                                                             | 11-8  |

### CHAPTER 12 CACHING

| 12.1 INTRODUCTION TO CACHING         |                                           | 12-1 |

|--------------------------------------|-------------------------------------------|------|

| 12.2 OPERATION OF THE INTERNAL CACHE |                                           |      |

| 12.2.1 Cache Disabling Bits          | <br>                                      | 12-2 |

| 12.2.2 Cache Management Instructions |                                           |      |

| 12.2.3 Self-Modifying Code           |                                           |      |

| 12.3 PAGE-LEVEL CACHE MANAGEMENT     |                                           |      |

| 12.3.1 Cache Management Bits         |                                           |      |

| 12.3.1.1 PCD BIT                     |                                           |      |

| 12.3.1.2 PWT BIT                     | <br>· · · · · · · · · · · · · · · · · · · | 12-4 |

## CHAPTER 13

| MOLTIFROCESSING                          |          |

|------------------------------------------|----------|

| 13.1 LOCKED AND PSEUDO-LOCKED BUS CYCLES | <br>13-1 |

| 13.1.1 LOCK Prefix and the LOCK# Signal  |          |

| 13.1.2 Automatic Locking                 |          |

| 13.1.3 Pseudo-Locking                    |          |

|                                          |          |

## PART III-NUMERIC PROCESSING

### CHAPTER 14

## INTRODUCTION TO NUMERIC APPLICATIONS

| 14.1 | HISTORY     | ······ | 14-1 |

|------|-------------|--------|------|

|      |             |        |      |

| 14.3 | EASE OF USE |        | 14-3 |

|      |             |        |      |

|      |             |        |      |

| 14.0 |             |        | 14-0 |

| CHAPTER 15                                       |       |

|--------------------------------------------------|-------|

| ARCHITECTURE OF THE FLOATING-POINT UNIT          | Page  |

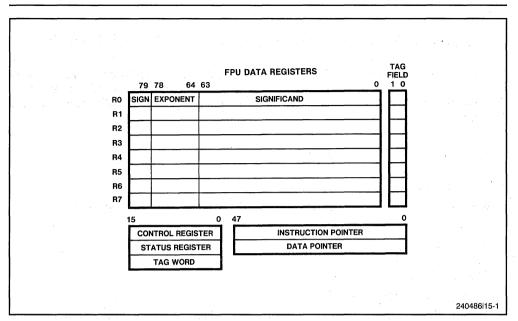

| 15.1 NUMERICAL REGISTERS                         | 15-1  |

| 15.1.1 The FPU Register Stack                    | 15-1  |

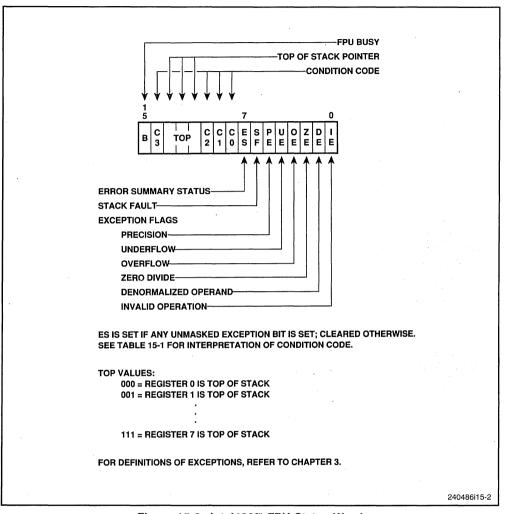

| 15.1.2 The FPU Status Word                       | 15-2  |

| 15.1.3 Control Word                              |       |

| 15.1.4 The FPU Tag Word                          | 15-6  |

| 15.1.5 Opcode Field of Last Instruction          | 15-7  |

| 15.1.6 The Numeric Instruction and Data Pointers | 15-8  |

| 15.2 COMPUTATION FUNDAMENTALS                    | 15-9  |

| 15.2.1 Number System                             | 15-10 |

| 15.2.2 Data Types and Formats                    | 15-12 |

| 15.2.2.1 BINARY INTEGERS                         | 15-13 |

| 15.2.2.2 DECIMAL INTEGERS                        | 15-13 |

| 15.2.2.3 REAL NUMBERS                            | 15-13 |

| 15.2.3 Rounding Control                          | 15-16 |

| 15.2.4 Precision Control                         | 15-17 |

|                                                  |       |

## **CHAPTER 16**

| SPECIAL COMPUTATIONAL SITUATIONS                     |        |

|------------------------------------------------------|--------|

| 16.1 SPECIAL NUMERIC VALUES                          | . 16-1 |

| 16.1.1 Denormal Real Numbers                         | . 16-1 |

| 16.1.1.1 DENORMALS AND GRADUAL UNDERFLOW             | . 16-4 |

| 16.1.2 Zeros                                         | . 16-6 |

| 16.1.3 Infinity                                      | . 16-8 |

| 16.1.3 Infinity                                      | . 16-8 |

| 16.1.4.1 SIGNALING NaNs                              | 16-10  |

| 16.1.4.2 QUIET NaNs                                  | 16-11  |

| 16.1.5 Indefinite                                    | 16-12  |

| 16.1.6 Encoding of Data Types                        | 16-13  |

| 16.1.7 Unsupported Formats                           | 16-13  |

| 16.2 NUMERIC EXCEPTIONS                              |        |

| 16.2.1 Handling Numeric Exceptions                   | 16-19  |

| 16.2.1.1 AUTOMATIC EXCEPTION HANDLING                |        |

| 16.2.1.2 SOFTWARE EXCEPTION HANDLING                 |        |

| 16.2.2 Invalid Operation                             | 16-21  |

| 16.2.2.1 STACK EXCEPTION                             | 16-21  |

| 16.2.2.2 INVALID ARITHMETIC OPERATION                |        |

| 16.2.3 Division by Zero                              |        |

| 16.2.4 Denormal Operand                              |        |

| 16.2.5 Numeric Overflow and Underflow                |        |

| 16.2.5.1 OVERFLOW                                    |        |

| 16.2.5.2 UNDERFLOW                                   |        |

| 16.2.6 Inexact (Precision)                           |        |

| 16.2.7 Exception Priority                            | 16-27  |

| 16.2.8 Standard Underflow/Overflow Exception Handler | 16-28  |

## CHAPTER 17

| FLO/ | ATING-POINT INSTRUCTION SET     |      |

|------|---------------------------------|------|

| 17.1 | SOURCE AND DESTINATION OPERANDS | 17-1 |

| 17.2 | DATA TRANSFER INSTRUCTIONS      | 17-2 |

| 17.3 | NONTRANSCENDENTAL INSTRUCTIONS  | 17-2 |

| 17.4 | COMPARISON INSTRUCTIONS         | 17-4 |

|                                                                       | Dere     |

|-----------------------------------------------------------------------|----------|

| 17.5 TRANSCENDENTAL INSTRUCTIONS                                      | Page     |

| 17.6 CONSTANT INSTRUCTIONS                                            |          |

| 17.7 CONTROL INSTRUCTIONS                                             |          |

|                                                                       |          |

| CUADTED 10                                                            |          |

| CHAPTER 18                                                            |          |

| NUMERIC APPLICATIONS 18.1 PROGRAMMING FACILITIES                      | 10 1     |

| 18.1 PROGRAMMING FACILITIES                                           | 10-1     |

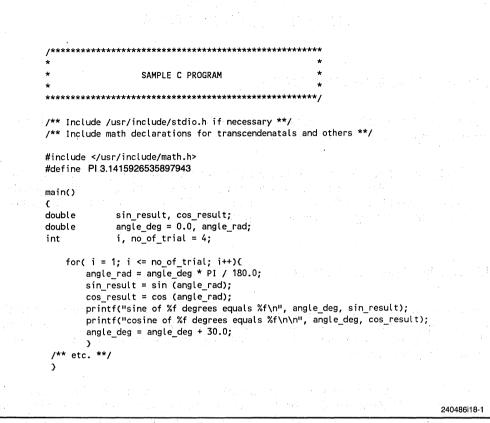

| 18.1.1 High-Level Languages                                           | 10-1     |

| 18.1.2 C Programs                                                     | 1071     |

| 18.1.4 ASM386/486                                                     | 10-2     |

| 18.1.4 ASM/360/466                                                    |          |

| 18.1.4.2 RECORDS AND STRUCTURES                                       | 10-4     |

|                                                                       |          |

| 18.1.4.3 Addressing Methods<br>18.1.5 Comparative Programming Example | 10-0     |

| 18.2 CONCURRENT PROCESSING                                            | 10-7     |

| 18.2.1 Managing Concurrency                                           |          |

| 18.2.1.1 INCORRECT EXCEPTION SYNCHRONIZATION                          | 10-12    |

| 18.2.1.2 PROPER EXCEPTION SYNCHRONIZATION                             | 10-13    |

| 10.2.1.2 FROPER EXCEPTION STINGROUNIZATION                            | 10-14    |

| CHAPTER 19                                                            | •.       |

|                                                                       |          |

| CHAPTER 19<br>SYSTEM-LEVEL CONSIDERATIONS<br>19.1 ARCHITECTURE        | 10_1     |

| 19.1.1 Independent of Addressing Mode                                 | 10-1     |

| 19.2 PROCESSOR INITIALIZATION AND CONTROL                             | 19-1     |

| 19.2.1 System Initialization                                          | 19-2     |

| 19.2.2 Configuring the Numerics Environment                           | 19-2     |

| 19.2.3 Initializing the FPU                                           | 19-2     |

| 19.2.3.1 Intel486 DX CPU SOFTWARE EMULATION                           | 19-3     |

| 19.2.3.2 Intel486 SX CPU SOFTWARE EMULATION PROCEDURE                 | 19-3     |

| 19.2.4 Handling Numerics Exceptions                                   |          |

| 19.2.5 Simultaneous Exception Response                                |          |

| 19.2.6 Exception Recovery Examples                                    | 19-5     |

|                                                                       |          |

| CHAPTER 20                                                            |          |

|                                                                       | <i>t</i> |

| 20.1 CONDITIONAL BRANCHING EXAMPLE                                    | 20-1     |

| 20.2 EXCEPTION HANDLING EXAMPLES                                      | 20-2     |

| 20.3 FLOATING-POINT TO ASCII CONVERSION EXAMPLES                      | . 20-7   |

| 20.3.1 Function Partitioning                                          | . 20-7   |

| 20.3.2 Exception Considerations                                       | 20-7     |

| 20.3.3 Special Instructions                                           | 20-21    |

| 20.3.4 Description of Operation                                       | 20-21    |

| 20.3.5 Scaling the Value                                              | 20-22    |

| 20.3.5.1 INACCURACY IN SCALING                                        | 20-22    |

xiv

20.3.5.2 AVOIDING UNDERFLOW AND OVERFLOW20-2320.3.5.3 FINAL ADJUSTMENTS20-2320.3.6 Output Format20-2320.4 TRIGONOMETRIC CALCULATION EXAMPLES20-23

## PART IV-COMPATIBILITY

| CHAPTER 21                                                       |       |

|------------------------------------------------------------------|-------|

| EXECUTING 286 AND Intel386 DX OR SX CPU PROGRAMS                 | Page  |

| 21.1 TWO WAYS TO RUN 286 CPU TASKS                               |       |

| 21.2 DIFFERENCES FROM 286 CPU                                    |       |

| 21.2.1 Wraparound of 286 Processor 24-Bit Physical Address Space | 21-2  |

| 21.2.2 Reserved Word of Segment Descriptor                       | 21-2  |

| 21.2.3 New Segment Descriptor Type Codes                         | 21-3  |

| 21.2.4 Restricted Semantics of LOCK Prefix                       | 21-3  |

| 21.2.5 Additional Exceptions                                     | 21-3  |

| 21.3 DIFFERENCES FROM Intel386 CPU                               | 21-4  |

| 21.3.1 New Flag                                                  |       |

| 21.3.2 New Exception                                             | 21-4  |

| 21.3.3 New Instructions                                          |       |

| 21.3.4 New Control Register Bits                                 | 21-5  |

| 21.3.5 New Page-Table Entry Bits                                 | 21-5  |

| 21.3.6 Changes in Segment Descriptor Loads                       | 21-5  |

| CHAPTER 22                                                       |       |

|                                                                  |       |

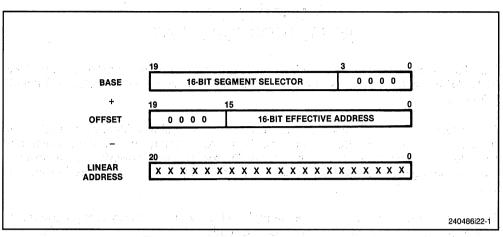

| REAL-ADDRESS MODE<br>22.1 ADDRESS TRANSLATION                    | 00 1  |

| 22.1 ADDRESS TRANSLATION                                         | 22-1  |

| 22.3 INTERRUPT AND EXCEPTION HANDLING                            |       |

| 22.3 INTERROFT AND EXCEPTION HANDLING                            | 22-3  |

| 22.4 ENTERING AND LEAVING REAL-ADDRESS MODE                      | 22-4  |

| 22.4.1 Switching to Protected Mode                               | 22-4  |

| 22.6 REAL-ADDRESS MODE EXCEPTIONS                                | 22-4  |

| 22.7 DIFFERENCES FROM 8086 CPU                                   | 22-5  |

| 22.8 DIFFERENCES FROM 286 CPU IN REAL-ADDRESS MODE               | 22-0  |

| 22.8.1 Bus Lock                                                  |       |

| 22.8.2 Location of First Instruction                             |       |

| 22.8.3 Initial Values of General Registers                       | 22-10 |

| 22.8.4 Bus Hold                                                  | 22-11 |

| 22.8.5 Math Coprocessor Differences                              | 22-11 |

| 22.9 DIFFERENCES FROM Intel386 DX CPU IN REAL-ADDRESS MODE       | 22-11 |

| 22.10 PROCESSOR DETECTION CODE                                   |       |

|                                                                  |       |

| CHAPTER 23                                                       |       |

| VIRTUAL-8086 MODE<br>23.1 EXECUTING 8086 CPU CODE                |       |

| 23.1 EXECUTING 8086 CPU CODE                                     | 23-1  |

| 23.1.1 Registers and Instructions                                | 23-1  |

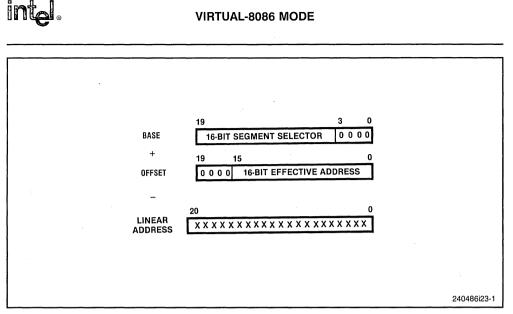

| 23.1.2 Address Translation                                       | 23-2  |

| 23.2 STRUCTURE OF A VIRTUAL-8086 TASK                            | 23-3  |

| 23.2.1 Paging for Virtual-8086 Tasks                             | 23-4  |

| 23.2.2 Protection within a Virtual-8086 Task                     | 23-5  |

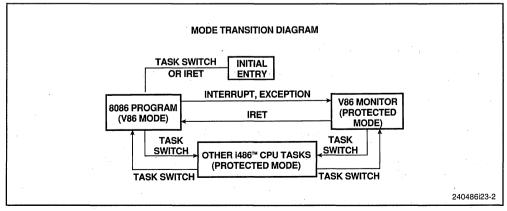

| 23.3 ENTERING AND LEAVING VIRTUAL-8086 Mode                      |       |

| 23.3.1 Transitions Through Task Switches                         | 23-6  |

|                                                    | Page  |

|----------------------------------------------------|-------|

| 23.5.2 Memory-Mapped I/O                           | 23-10 |

| 23.5.3 Special I/O Buffers 2                       | 23-10 |

| 23.6 DIFFERENCES FROM 8086 CPU 2                   | 23-11 |

| 23.7 DIFFERENCES FROM 286 CPU IN REAL-ADDRESS MODE | 23-14 |

| 23.7.1 Privilege Level                             | 23-14 |

| 23.7.2 Bus Lock                                    |       |

| 23.8 DIFFERENCES FROM Intel386 DX AND SX CPUs      | 23-15 |

## CHAPTER 24

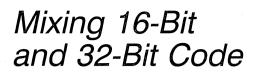

| MIXING 16-BIT AND 32-BIT CODE                      |              |  |

|----------------------------------------------------|--------------|--|

| 24.1 USING 16-BIT AND 32-BIT ENVIRONMENTS          | 24-2         |  |

| 24.2 MIXING 16-BIT AND 32-BIT OPERATIONS           |              |  |

| 24.3 SHARING DATA AMONG MIXED-SIZE CODE SEGMENTS . | 24-3         |  |

| 24.4 TRANSFERRING CONTROL AMONG MIXED-SIZE CODE S  | EGMENTS 24-4 |  |

| 24.4.1 Size of Code-Segment Pointer                | 24-4         |  |

| 24.4.2 Stack Management for Control Transfers      | 24-5         |  |

| 24.4.2.1 CONTROLLING THE OPERAND SIZE FOR A CALL   | 24-6         |  |

| 24.4.2.2 CHANGING SIZE OF A CALL                   |              |  |

| 24.4.3 Interrupt Control Transfers                 |              |  |

| 24.4.4 Parameter Translation                       |              |  |

| 24.4.5 The Interface Procedure                     | 24-7         |  |

|                                                    |              |  |

## CHAPTER 25

| COMPATIBILITY WITH THE 8087, Intel287 AND Intel387 MATH COPROCESSORS |       |

|----------------------------------------------------------------------|-------|

| 25.1 DIFFERENCES FROM Intel386 CPU/Intel387 NPX SYSTEMS              | 25-1  |

| 25.2 DIFFERENCES FROM 286/Intel287 SYSTEMS                           | 25-2  |

| 25.2.1 Data Types and Exception Handling                             | 25-3  |

| 25.2.2 Tag, Status, and Control Words                                |       |

| 25.2.3 Instruction Set                                               |       |

| 25.3 DIFFERENCES FROM 8086/8087 SYSTEMS 2                            | 25-11 |

# PART V-INSTRUCTION SET

## CHAPTER 26

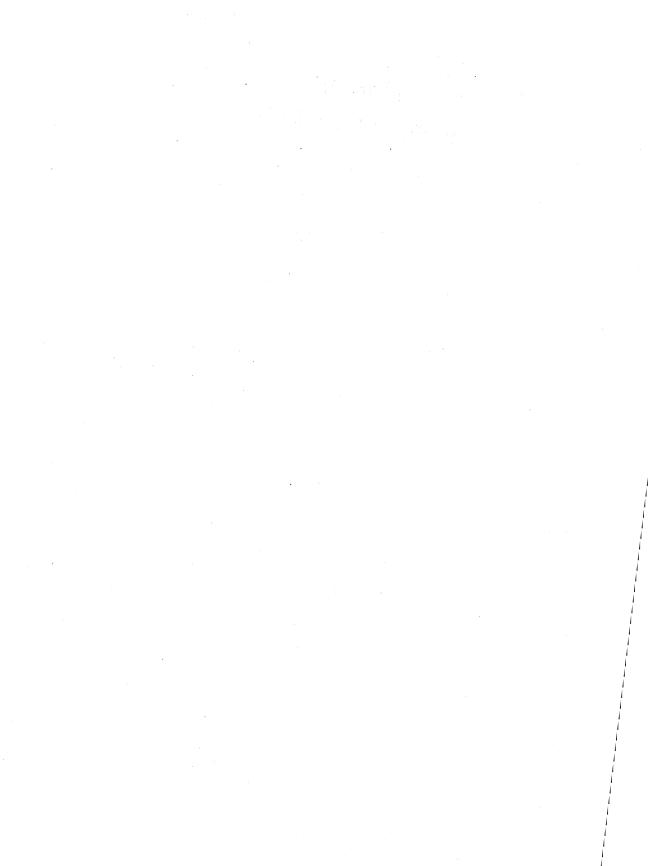

| 26.1 OPERAND-SIZE AND ADDRESS-SIZE ATTRIBUTES             | . 26-1 |

|-----------------------------------------------------------|--------|

| 26.1.1 Default Segment Attribute                          | . 26-1 |

| 26.1.2 Operand-Size and Address-Size Instruction Prefixes | . 26-1 |

| 26.1.3 Address-Size Attribute for Stack                   | . 26-2 |

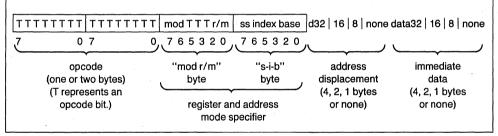

| 26.2 INSTRUCTION FORMAT                                   |        |

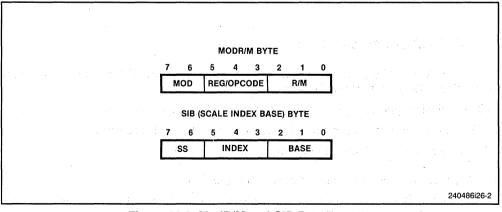

| 26.2.1 ModR/M and SIB Bytes                               | . 26-3 |

| 26.2.1 ModR/M and SIB Bytes                               | . 26-8 |

| 26.2.2.1 OPCODE COLUMN                                    | . 26-8 |

| 26.2.2.2 INSTRUCTION COLUMN                               |        |

| 26.2.2.3 CLOCKS COLUMN                                    | 26-11  |

| 26.2.2.4 DESCRIPTION COLUMN                               | 26-12  |

| 26.2.2.5 OPERATION                                        | 26-12  |

| 26.2.2.6 DESCRIPTION                                      |        |

| 26.2.2.7 FLAGS AFFECTED                                   | 26-16  |

| 26.2.2.8 PROTECTED MODE EXCEPTIONS                        | 26-17  |

|                                                           | 26-17  |

|                                                           |        |

|                                        | Page  |

|----------------------------------------|-------|

| 26.2.2.10 VIRTUAL-8086 MODE EXCEPTIONS | 26-17 |

| AAA                                    | 26-18 |

| AAD                                    |       |

| AAM                                    |       |

| AAS                                    |       |

| ADC                                    |       |

| ADD                                    |       |

| AND                                    |       |

| ARPL                                   |       |

| BOUND                                  |       |

| BSF                                    |       |

| BSR                                    |       |

| BSWAP                                  |       |

| BT                                     | 26-36 |

| BTC                                    |       |

| BTR                                    |       |

| BTS                                    |       |

| CALL                                   | 26-44 |

| CBW/CWDE                               |       |

| CLC                                    |       |

| CLD                                    |       |

| CLI                                    | 26-54 |

| CLTS                                   | 26-55 |

| CMC                                    | 26-56 |

| CMP                                    | 26-57 |

| CMPS/CMPSB/CMPSW/CMPSD                 | 26-59 |

| CMPXCHG                                | 26-62 |

| CWD/CDQ                                | 26-64 |

| DAA                                    | 26-65 |

| DAS                                    | 26-66 |

| DEC                                    | 26-67 |

| DIV                                    |       |

| ENTER                                  | 26-70 |

| F2XM1                                  | 26-72 |

| FABS                                   |       |

| FADD/FADDP/FIADD                       | 26-75 |

| FBLD                                   | 26-77 |

| FBSTP                                  | 26-79 |

| FCHS                                   |       |

| FCLEX/FNCLEX                           | 26-81 |

| FCOM/FCOMP/FCOMPP                      | 26-82 |

| FCOS                                   | 26-84 |

| FDECSTP                                | 26-86 |

| FDIV/FDIVP/FIDIV                       |       |

| FDIVR/FDIVPR/FIDIVR                    | 26-89 |

| FFREE                                  | 26-91 |

| FICOM/FICOMP                           | 26-92 |

| FILD                                   |       |

| FINCSTP                                | 26-96 |

| FINIT/FNINIT                           | 26-97 |

| FIST/FISTP                             | 26-99 |

| FLD 2                                  | 6-101 |

| FLD1/FLDL2T/FLDL2E/<br>FLDPI/FLDLG2/FLDLN2/FLDZ | Page   |

|-------------------------------------------------|--------|

| FLD1/FLDL21/FLDL2E/                             |        |

| FLDPI/FLDLG2/FLDLN2/FLDZ                        | 26-103 |

| FLDCW                                           |        |

|                                                 | 26-107 |

| FMUL/FMULP/FIMUL                                |        |

| FNOPFPATAN                                      |        |

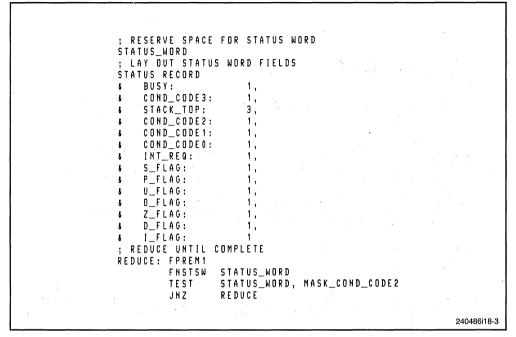

| FPREM                                           | 20-112 |

| FPREM                                           |        |

| FPTAN                                           |        |

| FRNDINT                                         |        |

| FRSTOR                                          |        |

| FSAVE/FNSAVE                                    |        |

| FSCALE                                          |        |

| FSIN                                            |        |

| FSINCOS                                         |        |

| FSQRT                                           |        |

| FST/FSTP                                        | 26-130 |

| FSTCW/FNSTCW                                    |        |

| FSTENV/FNSTENV                                  |        |

| FSTSW/FNSTSW                                    | 26-135 |

| FSUB/FSUBP/FISUB                                | 26-137 |

| FSUBR/FSUBPR/FISUBR                             |        |

| FTST                                            | 26-141 |

| FUCOM/FUCOMPP                                   | 26-143 |

| FWAIT                                           |        |

| FXAM                                            |        |

| FXCH                                            |        |

| FXTRACT                                         |        |

| FYL2X                                           |        |

| FYL2XP1                                         |        |

|                                                 |        |

|                                                 |        |

| IMUL                                            |        |

|                                                 |        |

| INC<br>INS/INSB/INSW/INSD                       |        |

| INJ/INSB/INSW/INSD<br>INT/INTO                  |        |

| INVD                                            |        |

| INVLPG                                          |        |

| IRET/IRETD                                      | 26-173 |

| Jcc                                             |        |

| JMP                                             |        |

| LAHF                                            |        |

| LAR                                             |        |

| LEA                                             | 26-190 |

| LEAVE                                           | 26-192 |

| LGDT/LIDT                                       |        |

| LGS/LSS/LDS/LES/LFS                             | 26-195 |

| LLDT                                            | 26-198 |

| LMSW                                            |        |

| LOCK                                            | 26-201 |

| LODS/LODSB/LODSW/LODSD                          | 26-203 |

|                           | Page   |

|---------------------------|--------|

| LOOP/LOOPcond             |        |

| LSL                       |        |

| LTR                       |        |

| MOV                       |        |

| MOV                       | 26-212 |

| MOVS/MOVSB/MOVSW/MOVSD    | 26-214 |

| MOVSX                     | 26-216 |

| MOVZX                     |        |

| MUL                       |        |

| NEG                       |        |

| NOP                       |        |

| NOT                       |        |

| OR                        |        |

|                           |        |

|                           |        |

| OUTS/OUTSB/OUTSW/OUTSD    | 26-227 |

| POP                       |        |

| POPA/POPAD                | 26-233 |

| POPF/POPFD                | 26-235 |

| PUSH                      |        |

| PUSHA/PUSHAD              | 26-238 |

| PUSHF/PUSHFD              | 26-240 |

| RCL/RCR/ROL/ROR           | 26-241 |

| REP/REPE/REPZ/REPNE/REPNZ | 26-244 |

| RET                       |        |

| SAHF                      | 26 251 |

| SAL/SAR/SHL/SHR           |        |

| SBB                       |        |

|                           |        |

| SCAS/SCASB/SCASW/SCASD    | 20-207 |

| SETcc                     |        |

| SGDT/SIDT                 |        |

| SHLD                      |        |

| SHRD                      |        |

| SLDT                      |        |

| SMSW                      |        |

| STC                       |        |

| STD                       | 26-270 |

| STI                       |        |

| STOS/STOSB/STOSW/STOSD    |        |

| STR                       |        |

| SUB                       |        |

| TEST                      |        |

| VERR, VERW                |        |

|                           |        |

|                           |        |

| WBINVD                    |        |

| XADD                      |        |

| XCHG                      |        |

| XLAT/XLATB                |        |

| XOR                       | 26-287 |

### TABLE OF CONTENTS

## intel

### **APPENDICES**

### APPENDIX A OPCODE MAP

APPENDIX B FLAG CROSS-REFERENCE

APPENDIX C STATUS FLAG SUMMARY

APPENDIX D CONDITION CODES

APPENDIX E INSTRUCTION FORMAT AND TIMING

APPENDIX F NUMERIC EXCEPTION SUMMARY

APPENDIX G CODE OPTIMIZATION

APPENDIX H REVISION HISTORY

### GLOSSARY

INDEX

## **Figures**

Page

1-7

2-4

2 - 5

2-5

2-7

2.0

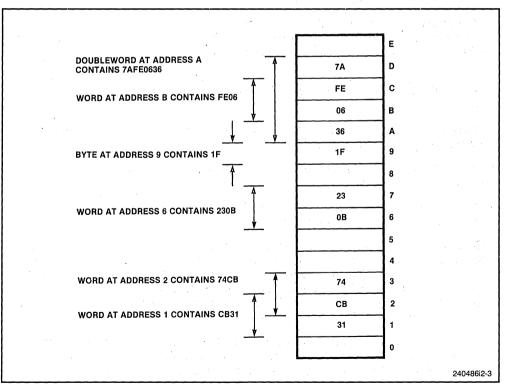

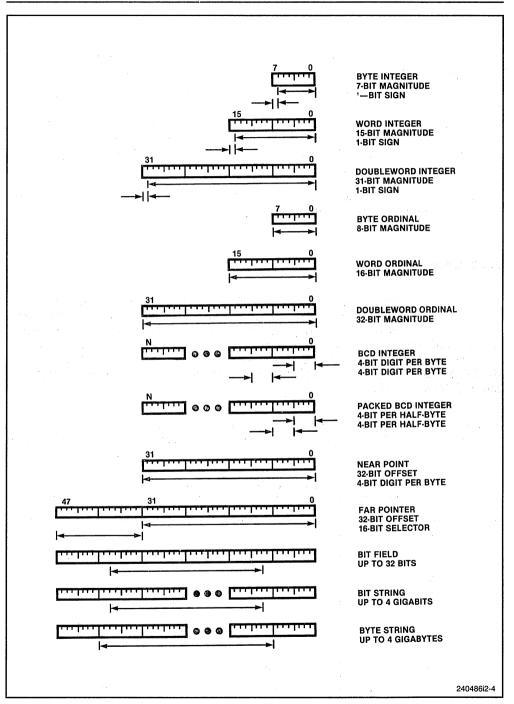

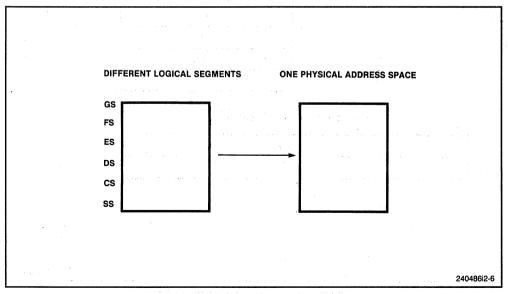

# Figure Title 1-1 Bit and Byte Order 2-1 Segmented Addressing 2-2 Fundamental Data Types 2-3 Bytes, Words, and Doublewords in Memory 2-4 Data Types 2-5 Application Register Set

| An Unsegmented Memory         |

|-------------------------------|

| A Segmented Memory            |

| Stacks                        |

| EFLAGS Register               |

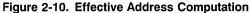

| Effective Address Computation |

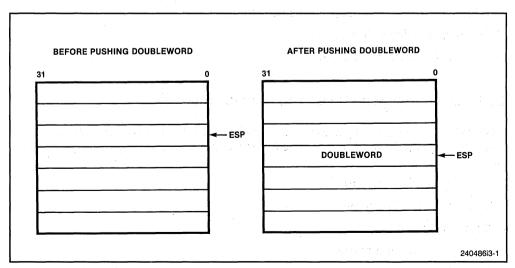

| PUSH Instruction              |

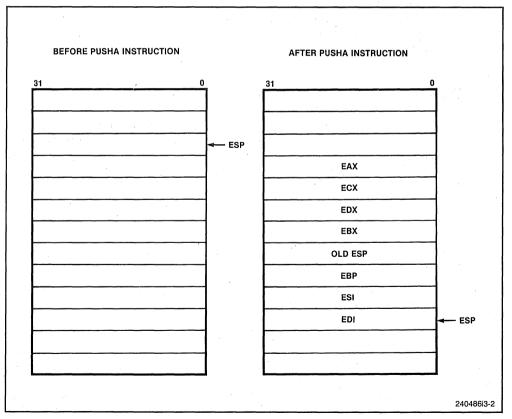

| PUSHA Instruction             |

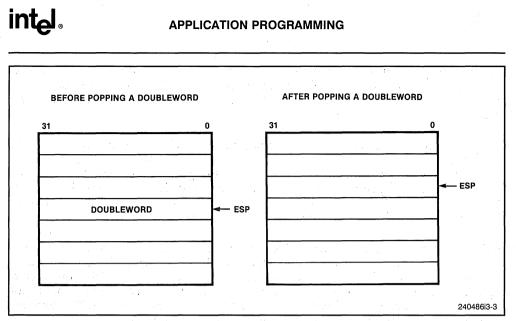

| POP Instruction               |

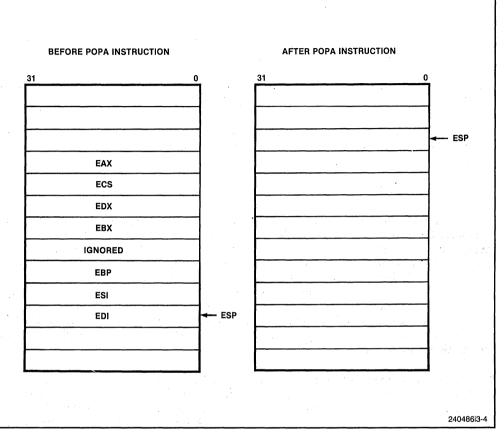

| POPA Instruction              |

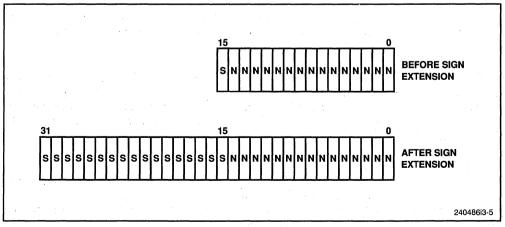

| Sign Extension                |

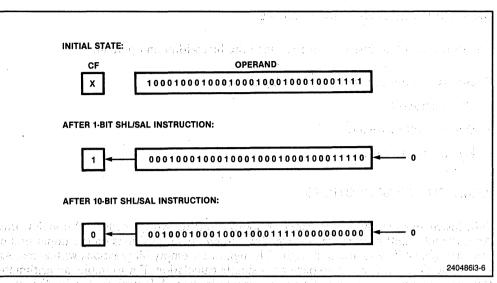

| SHL/SAL Instruction           |

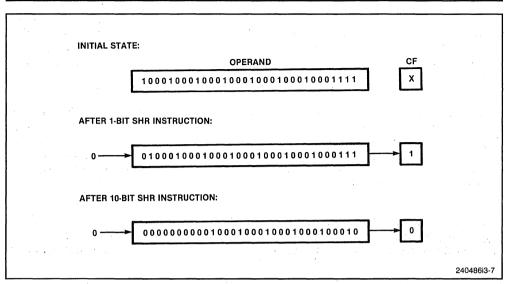

| SHR Instruction               |

|                               |

## Figures

## Title

## Page

| Figure      | Title                                               | Page        |

|-------------|-----------------------------------------------------|-------------|

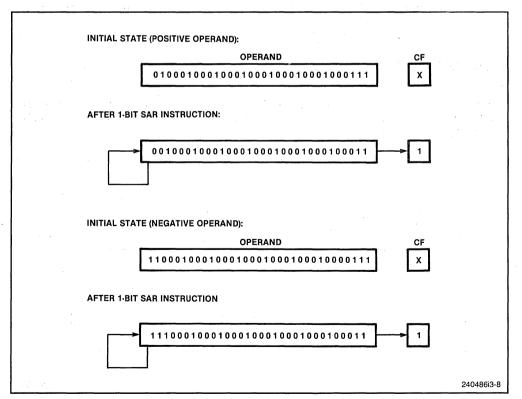

| 3-8         | SAR Instruction                                     | 3-15        |

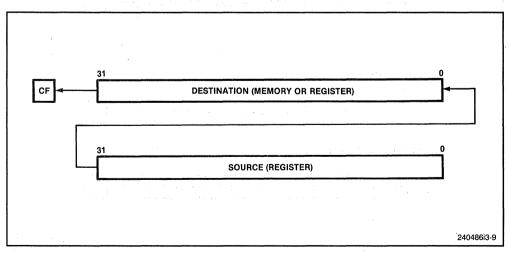

| 3-9         | SHLD Instruction                                    | 3-16        |

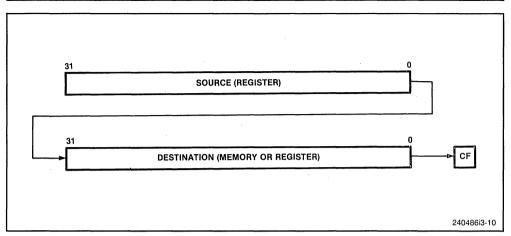

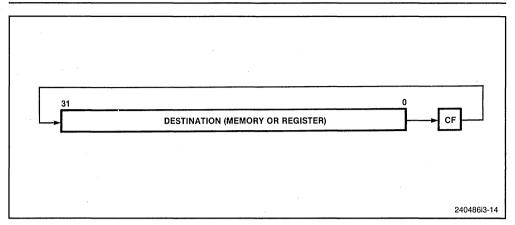

| 3-10        | SHRD Instruction                                    | 3-17        |

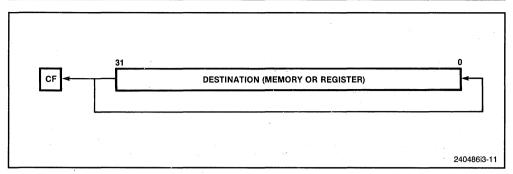

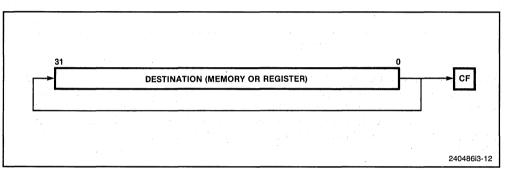

| 3-11        | ROL Instruction                                     | 3-18        |

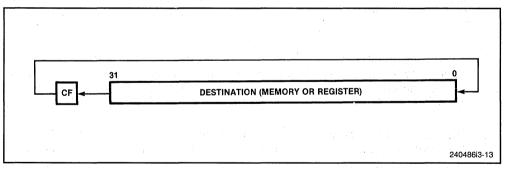

| 3-12        | ROR Instruction                                     | 3-18        |

| 3-13        | RCL Instruction                                     | 3-18        |

| 3-14        | RCR Instruction                                     | 3-19        |

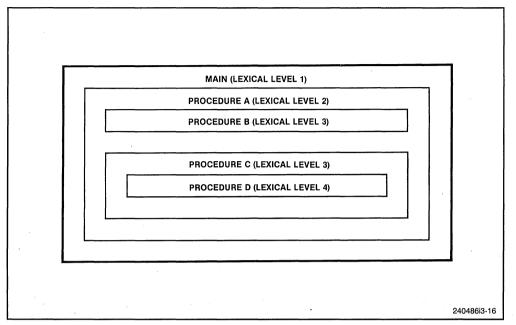

| 3-15        | Formal Definition of the ENTER Instruction          | 3-32        |

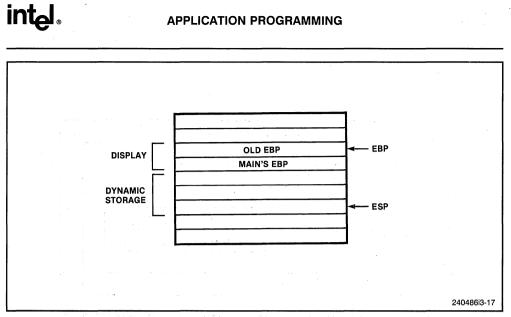

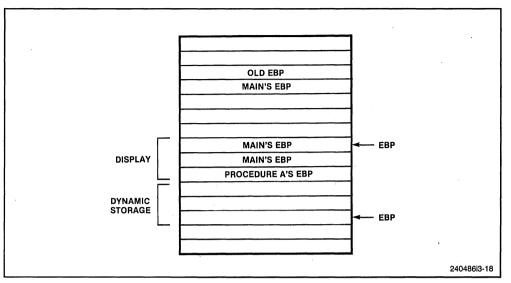

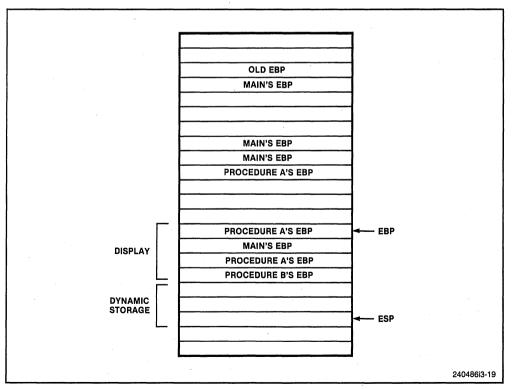

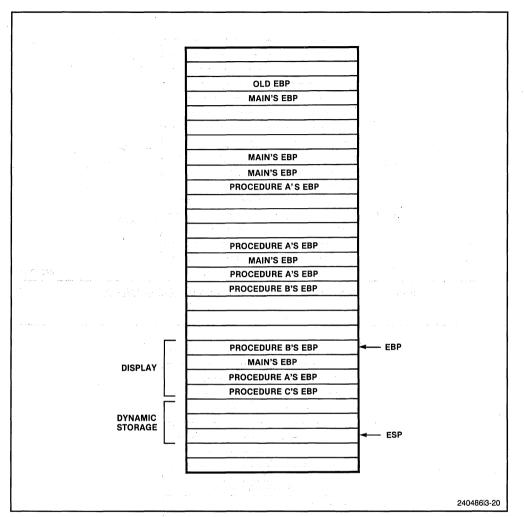

| 3-16        | Nested Procedures                                   | 3-33        |

| 3-17        | Stack Frame After Entering MAIN                     | 3-34        |

| 3-18        | Stack Frame After Entering PROCEDURE A              | 3-35        |

| 3-19        | Stack Frame After Entering PROCEDURE B              | 3-35        |

| 3-20        | Stack Frame After Entering PROCEDURE C              | 3-36        |

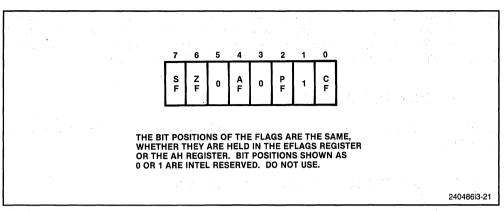

| 3-21        | Low Byte of EFLAGS Register                         | 3-38        |

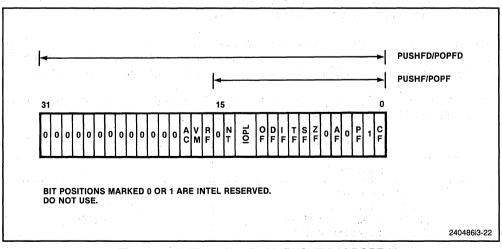

| 3-22        | Flags Used with PUSHF and POPF                      | 3-38        |

| 3-23        | CPU_ID, MCP_ID Detection Code                       | 3-42        |

| 3-24        | ASCII Arithmetic Using BSWAP                        | 3-48        |

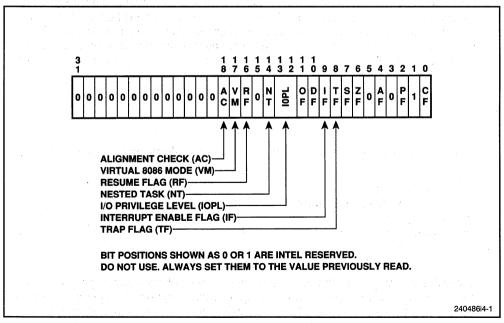

| 4-1         | System Flags                                        | 4-2         |

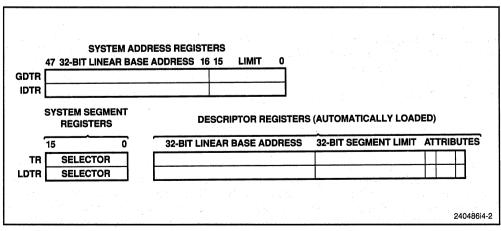

| 4-2         | Memory Management Registers                         | 4-4         |

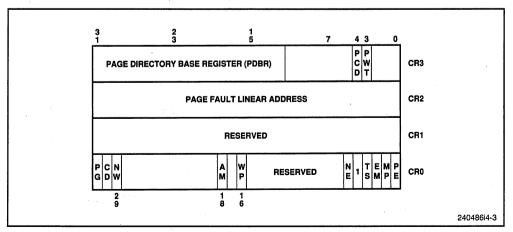

| 4-3         | Control Registers                                   | 4-5         |

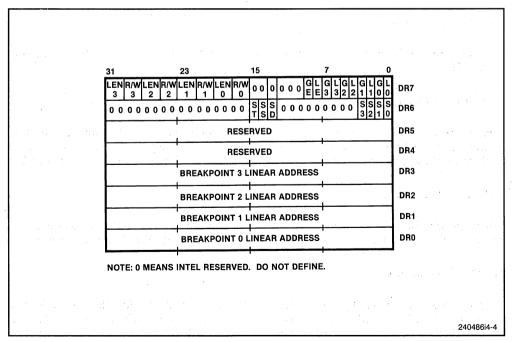

| 4-4         | Debug Registers                                     | 4-8         |

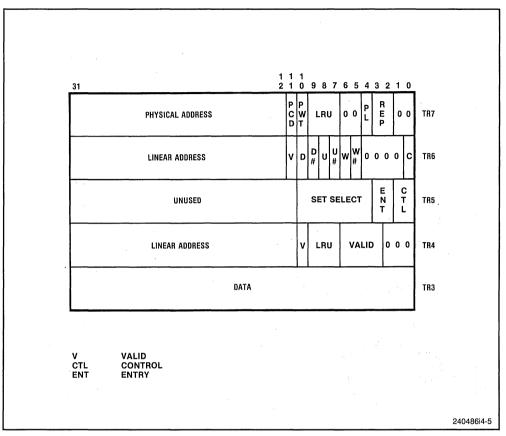

| 4-5         | Test Registers                                      | 4-9         |

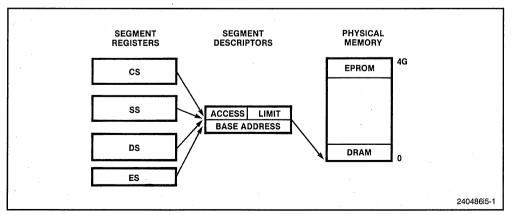

| 5-1         | Flat Model                                          | 5-3         |

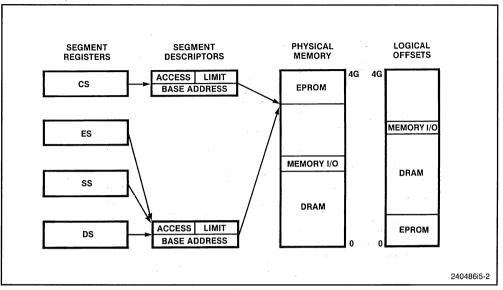

| 5-2         | Protected Flat Model                                | 5-5         |

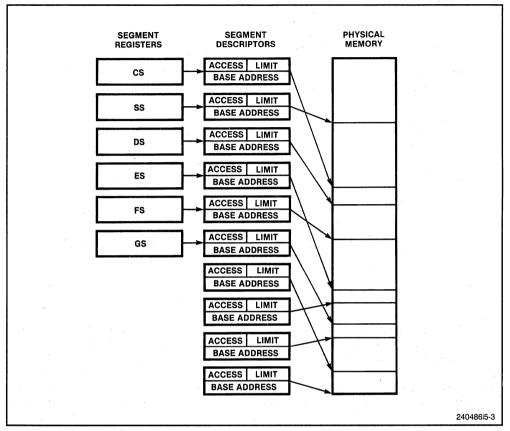

| 5-3         | Multi-Segment Model                                 | 5-6         |

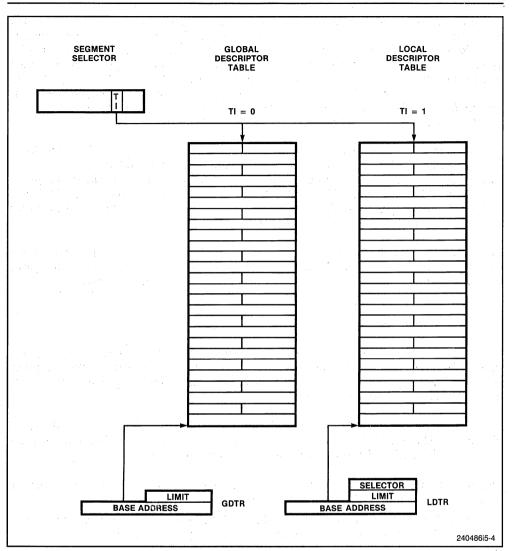

| 5-4         | TI Bit Selects Descriptor Table                     | 5-8         |

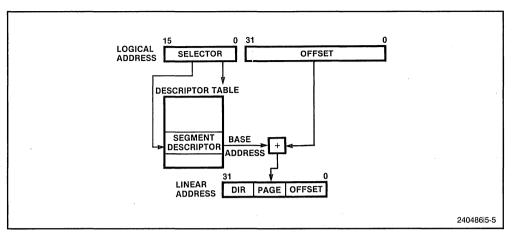

| 5-5         | Segment Translation                                 | 5-9         |

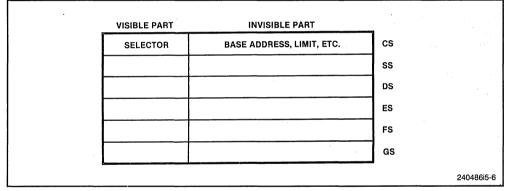

| 5-6         | Segment Registers                                   | 5-9         |

| 5-7         | Segment Selector                                    | 5-10        |

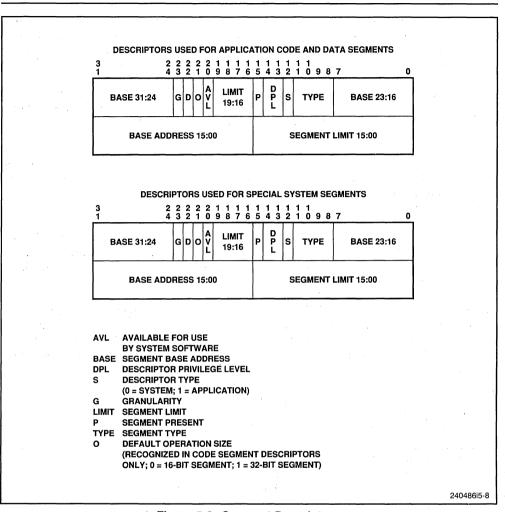

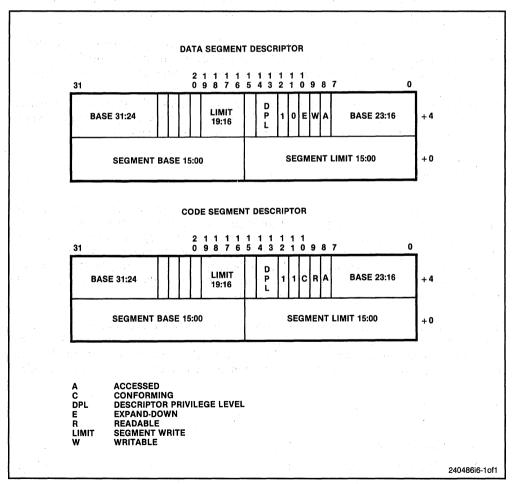

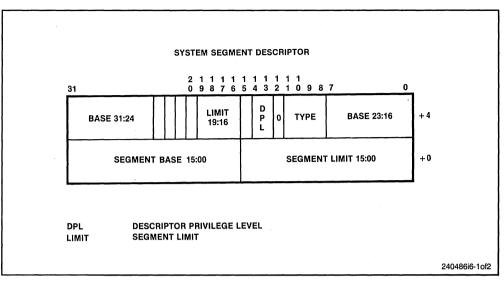

| 5-8         | Segment Descriptors                                 | 5-11        |

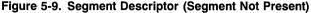

| 5-9         | Segment Descriptor (Segment Not Present)            | 5-14        |

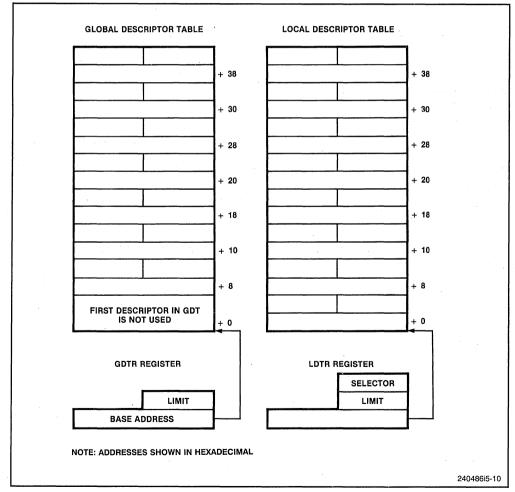

| 5-10        | Descriptor Tables                                   | 5-15        |

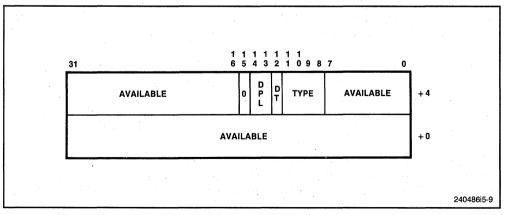

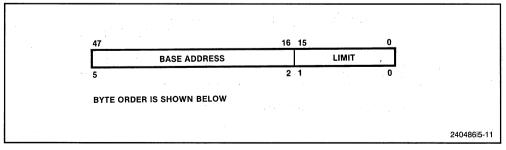

| 5-11        | Pseudo-Descriptor Format                            | 5-16        |

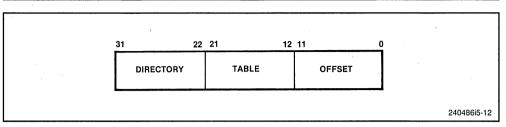

| 5-12        | Format of a Linear Address                          | 5-19        |

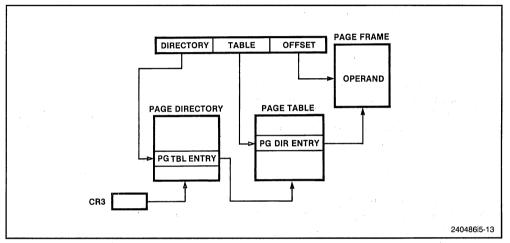

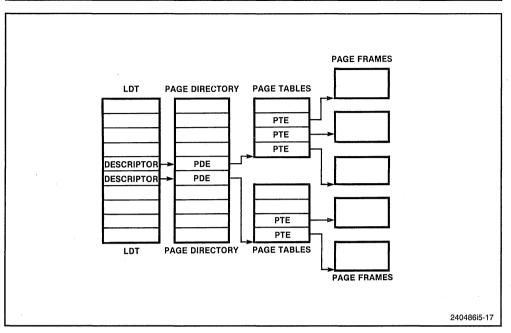

| 5-13        | Page Translation                                    | 5-19        |

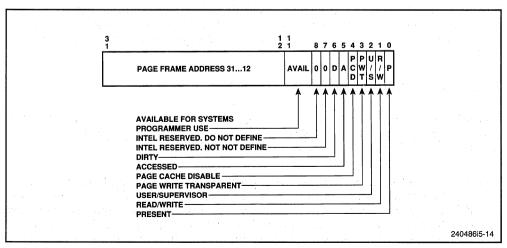

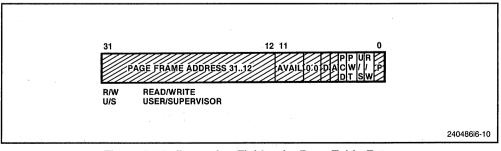

| 5-14        | Format of a Page Table Entry                        | 5-20        |

| 5-15        | Format of a Page Table Entry for a Not-Present Page | 5-21        |

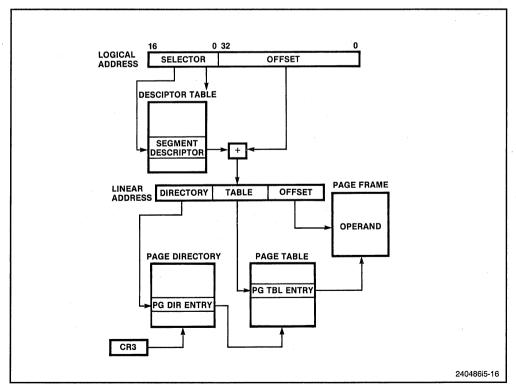

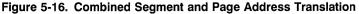

| 5-16        | Combined Segment and Page Address Translation       | 5-23        |

| 5-17        | Each Segment Can Have Its Own Page Table            | 5-25        |

| 6-1         | Descriptor Fields Used for Protection               | .6-2        |

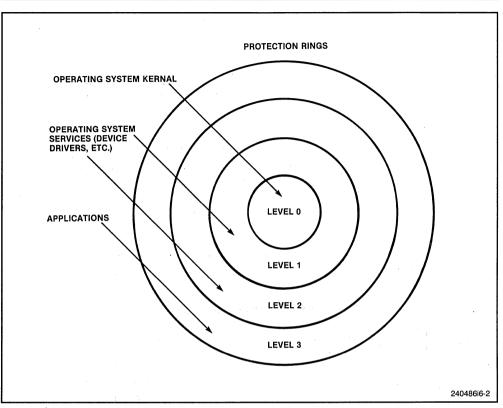

| 6-2         | Protection Rings                                    | 6-7         |

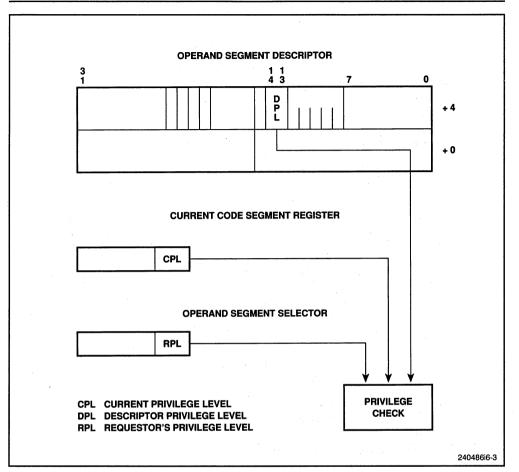

| 6-3         | Privilege Check for Data Access                     | 6-8         |

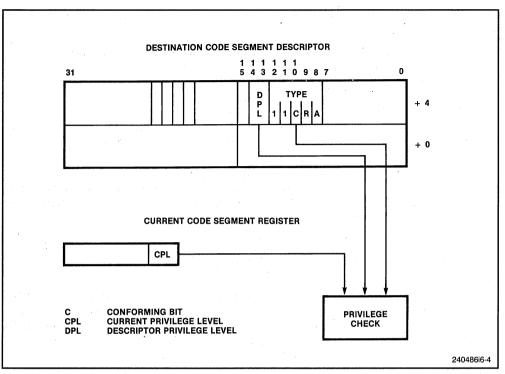

| 6-4         | Privilege Check for Control Transfer Without Gate   | 6-10        |

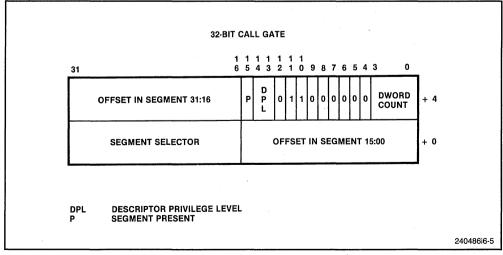

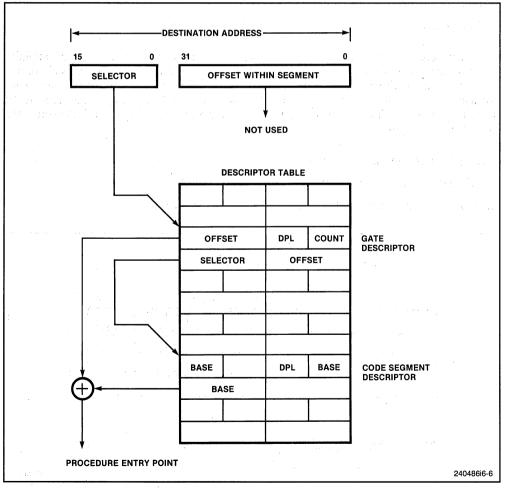

| 6-5         | Call Gate                                           | 6-11        |

| 6-6         | Call Gate Mechanism                                 | 6-12        |

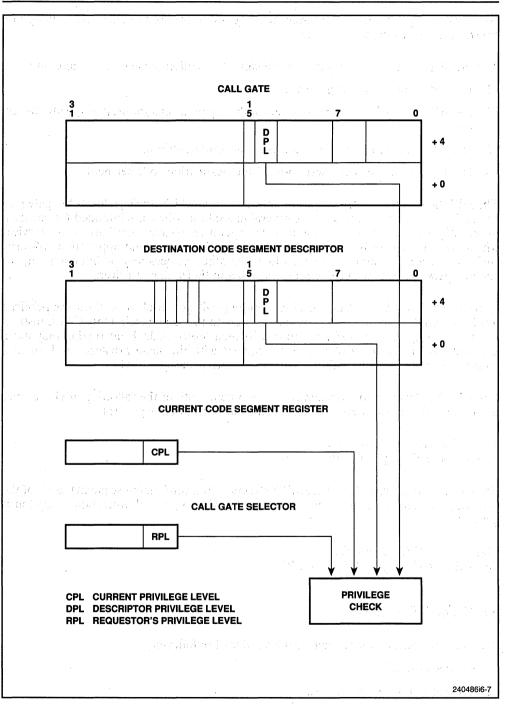

| 6-7         | Privilege Check for Control Transfer with Call Gate | 6-12        |

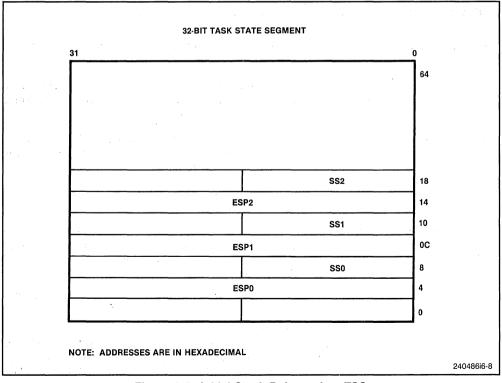

| 6-8         | Initial Stack Pointers in a TSS                     | 6-14        |

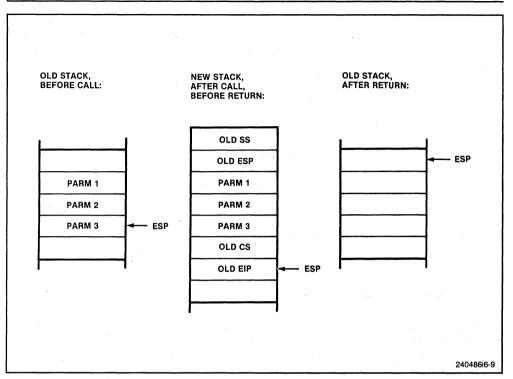

| 6-9         | Stack Frame During Interlevel Call                  | 6-15        |

| 6-10        | Protection Fields of a Page Table Entry             | 6-23        |

| 6-10<br>7-1 |                                                     | 6-23<br>7-3 |

| 7-1         | Task State Segment                                  | 7-3         |

intel

Figure

TABLE OF CONTENTS

## **Figures**

## Title

## Page

| 7-2                    | TSS Descriptor                                                               | 7-4   |

|------------------------|------------------------------------------------------------------------------|-------|

| 7-3                    | TR Register                                                                  | 7-6   |

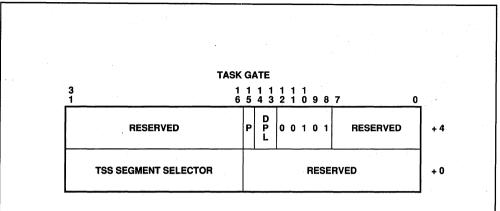

| 7-4                    | Task Gate Descriptor                                                         | 7-7   |

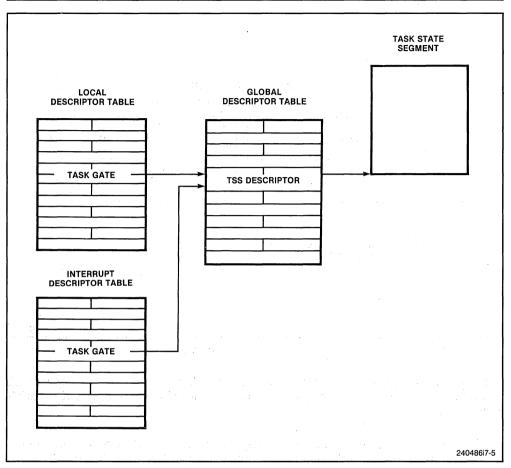

| 7-5                    | Task Gates Reference Tasks                                                   | 7-8   |

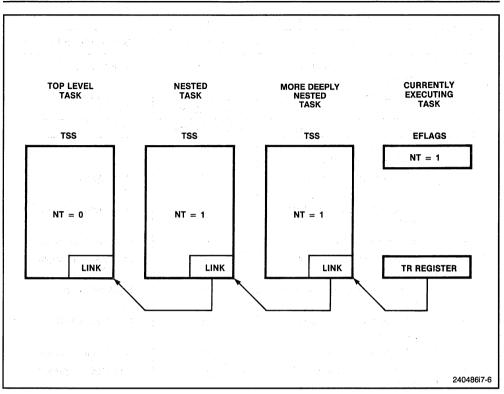

| 7-6                    | Nested Tasks                                                                 | 7-12  |

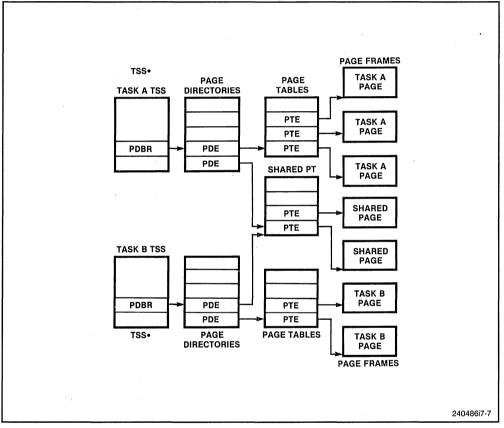

| 7-7                    | Overlapping Linear-to-Physical Mappings                                      | 7-15  |

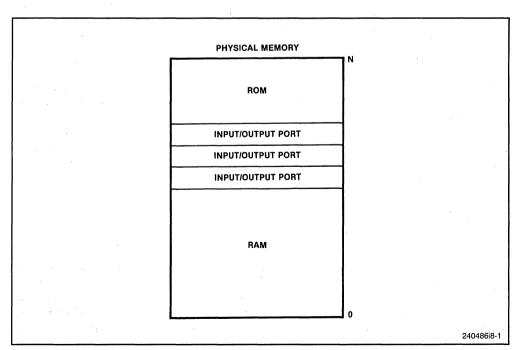

| 8-1                    | Memory-Mapped I/O                                                            | 8-3   |

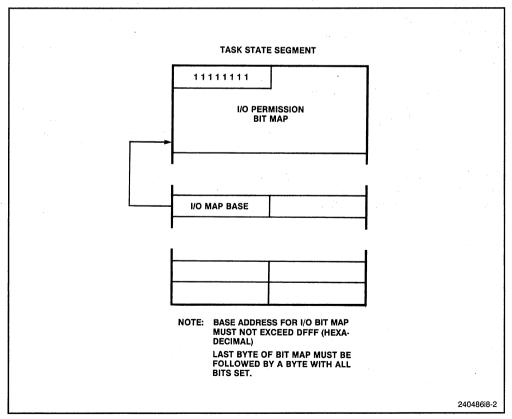

| 8-2                    | I/O Permission Bit Map                                                       | 8-7   |

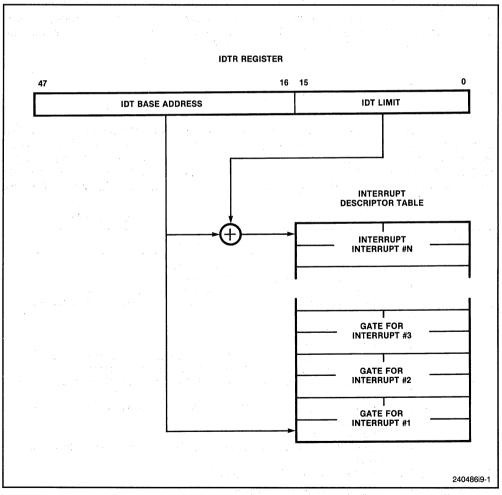

| 9-1                    | IDTR Register Locates IDT in Memory                                          | 9-6   |

| 9-2                    | IDT Gate Descriptors                                                         | 9-8   |

| 9-3                    | Interrupt Procedure Call                                                     | 9-9   |

| 9-4                    | Stack Frame After Exception or Interrupt                                     | 9-10  |

| 9-5                    | Interrupt Task Switch                                                        | 9-12  |

| 9-6                    | Error Code                                                                   | 9-13  |

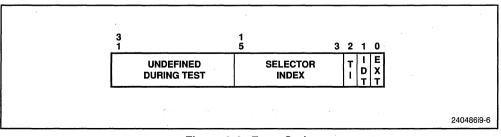

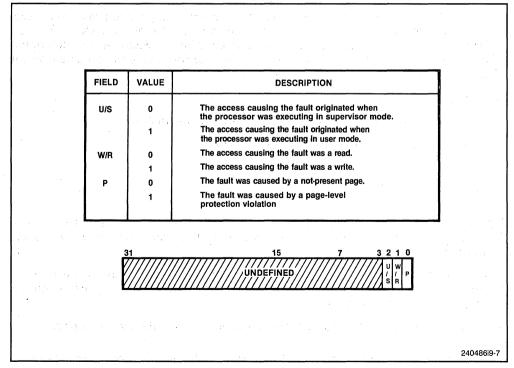

| 9-7                    | Page Fault Error Code                                                        | 9-22  |

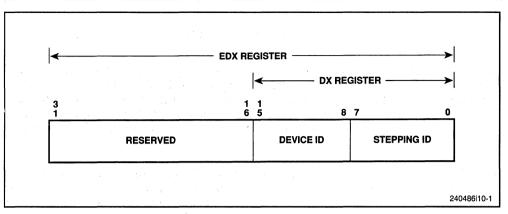

| 10-1                   | Contents of the EDX Register After Reset                                     | 10-2  |

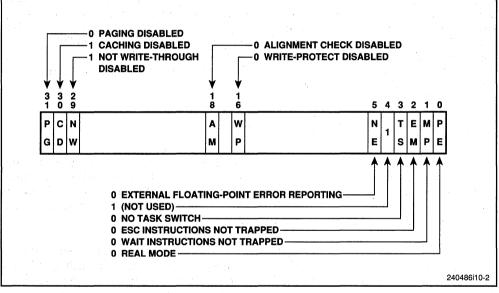

| 10-2                   | Contents of the CR0 Register After Reset                                     | 10-2  |

| 10-3                   | TLB Structure                                                                | 10-9  |

| 10-4                   | TLB Test Registers                                                           | 10-10 |

| 10-4                   | Cache Structure                                                              | 10-13 |

| 10-5                   | Cache Test Registers                                                         | 10-13 |

| 11-1                   | Debug Registers                                                              | 11-3  |

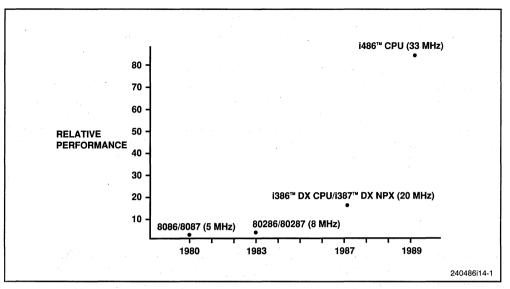

| 14-1                   | Evolution and Performance of Numeric Processors                              | 14-2  |

| 15-1                   | Intel486 <sup>™</sup> FPU Register Set                                       | 14-2  |

| 15-2                   | Intel486 ™ FPU Status Word                                                   | 15-2  |

| 15-2                   | Intel400 FFU Status Word Format                                              | 15-3  |

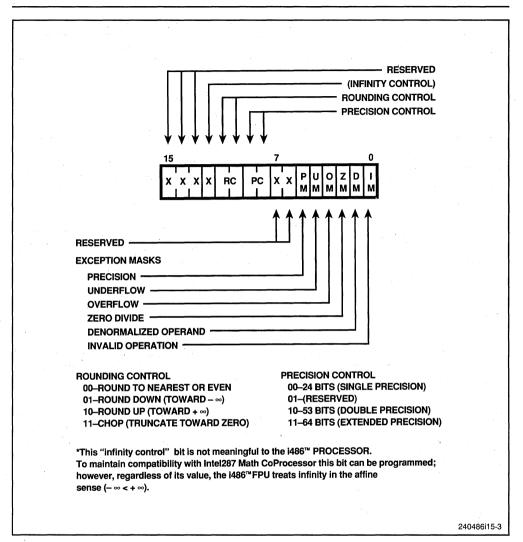

| 15-3                   | Intel486 <sup>™</sup> FPU Control Word Format                                | 15-6  |

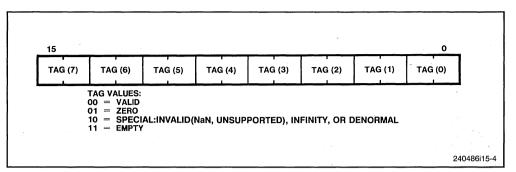

|                        | Tag Word Format                                                              | 15-7  |

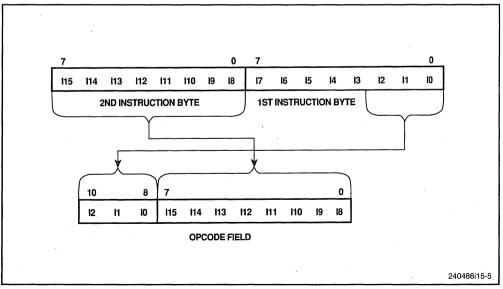

| 15-5                   | Opcode Field<br>Protected Mode Numeric Instruction and Data Pointer Image in | 10-7  |

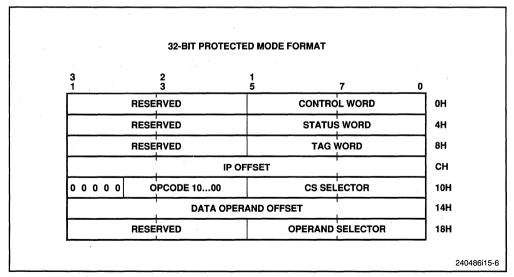

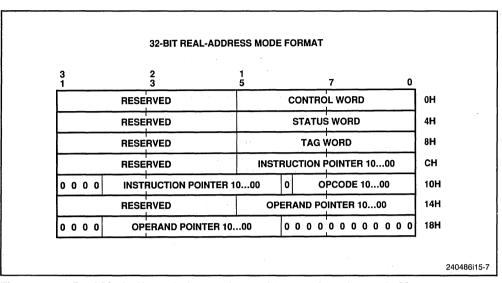

| 15-6                   |                                                                              | 15 0  |

|                        | Memory, 32-Bit Format                                                        | 15-8  |

| 15-7                   | Real Mode Numeric Instruction and Data Pointer Image in Memory,              | 45.0  |

|                        | 32-Bit Format                                                                | 15-9  |

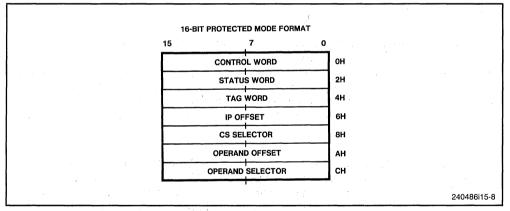

| 15-8                   | Protected Mode Numeric Instruction and Data Pointer Image in Memory,         |       |

|                        | 16-Bit Format                                                                | 15-9  |

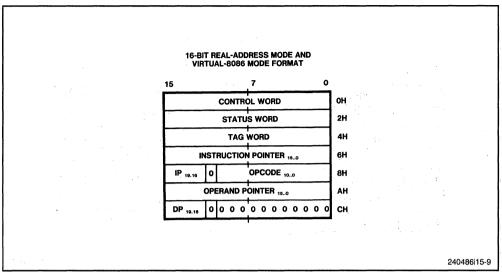

| 15-9                   | Real Mode Numeric Instruction and Data Pointer Image in Memory,              |       |

| 1999<br>1 <b>- 1</b> - | 16-Bit Format                                                                | 15-10 |

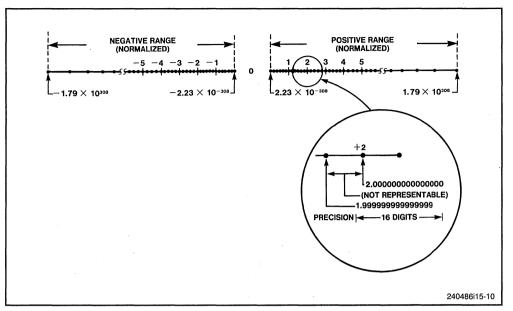

| 15-10                  | Double-Precision Number System                                               | 15-11 |

| 15-11                  | Numerical Data Formats                                                       | 15-12 |

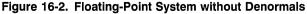

| 16-1                   | Floating-Point System with Denormals                                         | 16-5  |

| 16-2                   | Floating-Point System without Denormals                                      | 16-5  |

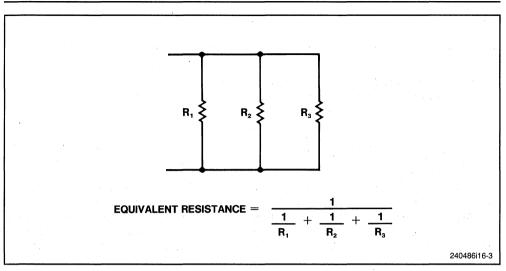

| 16-3                   | Arithmetic Example Using Infinity                                            | 16-20 |