## INTEL'S SC ARCHITECTURE Designing Portable Applications

DESMOND YUEN

Intel's SL Architecture

.

BUNZEL AND MORRIS • Multimedia Applications Development: Using DVI<sup>®</sup> Technology

EDELHART • Intel's Official Guide to 386<sup>™</sup> Computing

GUREWICH • Communication Systems: Practical Hardware and Firmware Implementation of LANs

INTEL • i486 Microprocessor Programming Reference Manual

$\texttt{INTEL} ~ \bullet ~ \textit{Intel 386^{\texttt{TM}} Family Binary Compatibility Specification 2}$

LUTHER • Digital Video in the PC Environment, 2nd edition

MARGULIS • *i860 Microprocessor Architecture*

RAGSDALE • Parallel Programming

## Intel's SL Architecture

**Designing Portable Applications**

**Desmond Yuen**

McGraw-Hill, Inc.

New York San Francisco Washington, D.C. Auckland Bogotá Caracas Lisbon London Madrid Mexico City Milan Montreal New Delhi San Juan Singapore Sydney Tokyo Toronto

#### Library of Congress Cataloging-in-Publication Data

Yuen, Desmond.

Intel's SL architecture : designing portable applications /

Desmond Yuen.

p. cm.—(Intel/McGraw Hill series)

Includes bibliographical references and index.

ISBN 0-07-911336-2

1. Intel i386SL (Microprocessor) 2. Portable computers—Design and construction. I. Title. II. Series.

QA76.8.1266Y84 1993

004.165—dc20

92-43722

CIP

Copyright © 1993 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

#### 1234567890 DOH/DOH 9876543

#### ISBN 0-07-072693-0

The sponsoring editor for this book was Neil Levine, and the production supervisor was Pamela A. Pelton. This book was set in Century Schoolbook by North Market Street Graphics.

Printed and bound by R. R. Donnelley & Sons Company.

i386, i486, Intel386, Intel486, and Intel387 are trademarks of Intel Corp. MS-DOS is a registered trademark of Microsoft Corp. Microsoft Windows is a trademark of Microsoft Corp. PS/2 is a registered trademark of International Business Machines Corp. CHMOS and HMOS are patented processes of Intel Corp.

Intel Literature may be obtained from: Intel Corporation, Literature Sales, P.O. Box 7641, Mt. Prospect, IL 60056-7641 (1-800-548-4725)

#### LIMITS OF LIABILITY AND DISCLAIMER OF WARRANTY

The author and publisher have exercised care in preparing this book and the programs contained in it. They make no representation, however, that the programs are error-free or suitable for every application to which a reader may attempt to apply them. The author and publisher make no warranty of any kind, expressed or implied, including the warranties of merchantability or fitness for a particular purpose, with regard to these programs or the documentation or theory contained in this book, all of which are provided "as is." The author and publisher shall not be liable for damages in an amount greater than the purchase price of this book, or in any event for incidental or consequential damages in connection with, or arising out of the furnishing, performance, or use of these programs or the associated descriptions or discussions.

Readers should test any program on their own systems and compare results with those presented in this book. They should then construct their own test programs to verify that they fully understand the requisite calling conventions and data formats for each of the programs. Then they should test the specific application thoroughly. To Angelina, Annie, Jimmy, Lisa, and Patricia

.

.

## Contents

Foreword xi Preface xiii Acknowledgments xv

| Chapter 1. Introduction                                  | 1   |

|----------------------------------------------------------|-----|

| Organization of the Book                                 | 2   |

| Basic Concepts                                           | 5   |

| Hardware Platform                                        | 6   |

| Notation                                                 | 6   |

| Useful References                                        | 8   |

| Summary                                                  | 8   |

| Chapter 2. The History and Future of the SL Architecture | 11  |

| The SL Challenge                                         | 11  |

| The Solution                                             | 12  |

| System Partitioning                                      | 12  |

| Power Management                                         | 13  |

| Notebook Computer Functions                              | 13  |

| Suspend/Resume                                           | 14  |

| Global Standby                                           | 14  |

| Detailed Design                                          | 15  |

| First Silicon and Debug                                  | 15  |

| First Customer Shipment                                  | 16  |

| General Marketing of the Product                         | 16  |

| The Success of the SMM Architecture                      | 16  |

| Support for Product-Specific Functions                   | 16  |

| Future SL Generations                                    | 17  |

| Conclusion                                               | 17  |

| Chapter 3. SL Architecture Overview                      | 19  |

| Intel386™ SL CPU and Intel486™ SL CPU                    | 19  |

| 82360SL Peripheral Controller                            | 28  |

| Register Resources                                       | 29  |

| Summary                                                  | 30  |

| References                                               | 30  |

|                                                          | vii |

| Chapter 4. System Management Mode                 | 31 |

|---------------------------------------------------|----|

| System Management Mode Architecture               | 31 |

| Applications of SMM                               | 36 |

| SMI and RSM Latency                               | 41 |

| Writing an SMM Program                            | 43 |

| Summary                                           | 53 |

| hapter 5. Introduction to Power Management        | 55 |

| History of Power Management in Personal Computers | 55 |

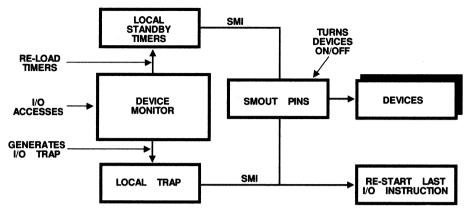

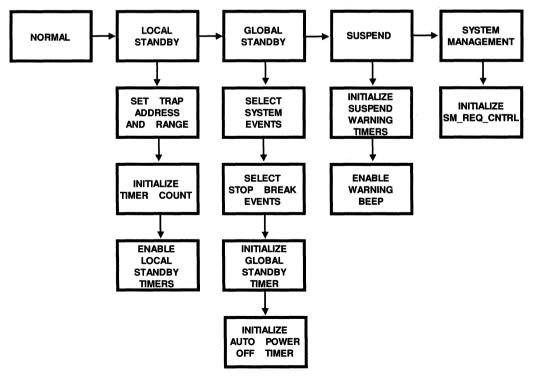

| Overview of the SL Power Management Support       | 57 |

| Initiation of Power Management Services           | 58 |

| Local Standby Operation                           | 59 |

| Power Management at the System Level              | 63 |

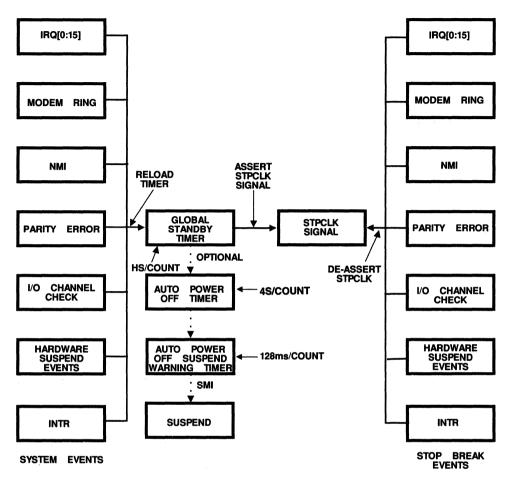

| Global Standby                                    | 63 |

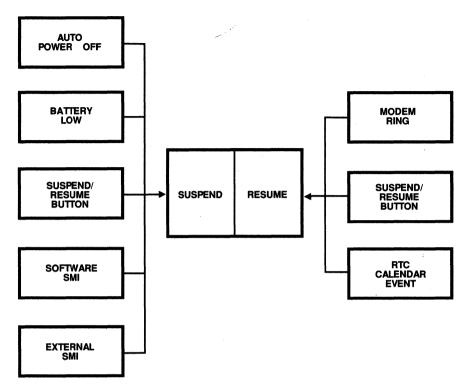

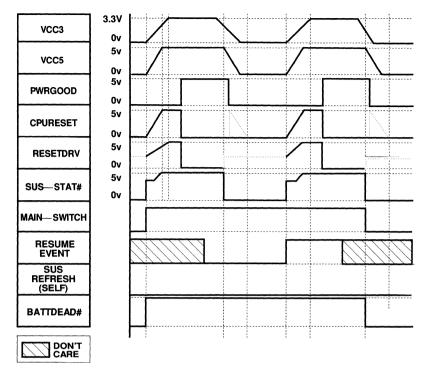

| Suspend Operation                                 | 65 |

| Suspend Requests                                  | 65 |

| Warming Timers                                    | 67 |

| Enabling Suspend                                  | 68 |

| Resume                                            | 69 |

| Battery Monitoring                                | 69 |

| Advanced Power Management                         | 69 |

| Summary                                           | 70 |

| hapter 6. Power Management Software               | 71 |

| Power Management Hardware Initialization          | 72 |

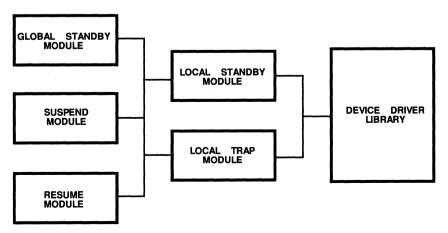

| Power Management Software Architecture            | 73 |

| Power Management Timers                           | 73 |

| Serial Port                                       | 78 |

| System Management FILO                            | 78 |

| Clearing Status Bits                              | 79 |

| Saving Memory Overlaid by SMRAM<br>Global Standby | 79 |

| Math CoProcessor                                  | 80 |

| Suspend                                           | 81 |

| Save-Restore                                      | 81 |

| Shadow Registers                                  | 82 |

| BIOS Shadowing                                    | 82 |

| Multiple SMIs                                     | 82 |

| APM Interface                                     | 82 |

| Programming Guidelines                            | 84 |

| Summary                                           | 84 |

| References                                        | 85 |

|                                                   |    |

| hapter 7. Power Management Techniques             | 87 |

| The Basics                                        | 87 |

| Component Selection                               | 87 |

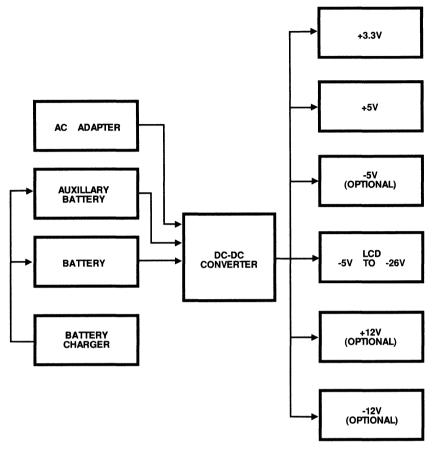

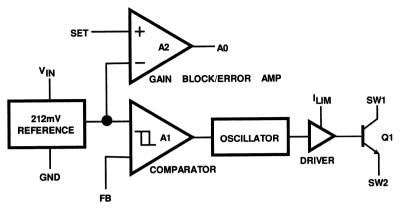

| Supplying Power                                   | 88 |

| Power Management Implementation                   | 93 |

| Power Management Design Considerations            | 95 |

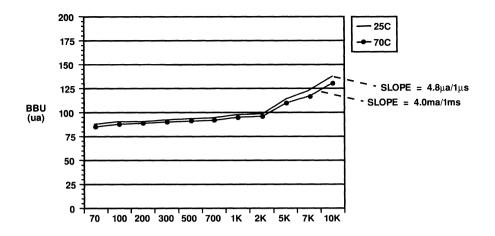

| Current Drain<br>Summary                                           | 98<br>103  |

|--------------------------------------------------------------------|------------|

| References                                                         | 103        |

|                                                                    | 100        |

| Chapter 8. Portable Computer Design                                | 105        |

| Overview of an SL CPU-Based System                                 | 105        |

| Putting It Together                                                | 116        |

| Design Considerations                                              | 118        |

| Summary<br>References                                              | 118        |

| nelelences                                                         | 118        |

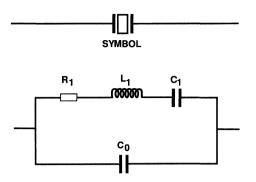

| Chapter 9. Clock Control                                           | 121        |

| The SL Clock System                                                | 121        |

| Oscillator Design Considerations                                   | 131        |

| Summary                                                            | 134        |

| References                                                         | 134        |

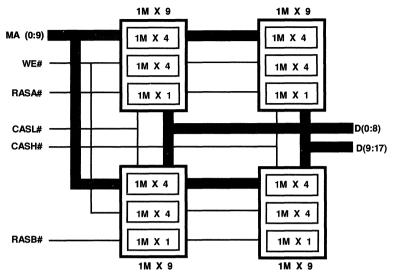

| Chapter 10. Intel386 SL CPU Memory Interfacing                     | 135        |

| Designing a DRAM Memory System                                     | 135        |

| Designing an SRAM Memory System                                    | 144        |

| External SMRAM Interface                                           | 147        |

| Memory Options                                                     | 147        |

| Cache Controller                                                   | 149        |

| Summary                                                            | 154        |

| References                                                         | 154        |

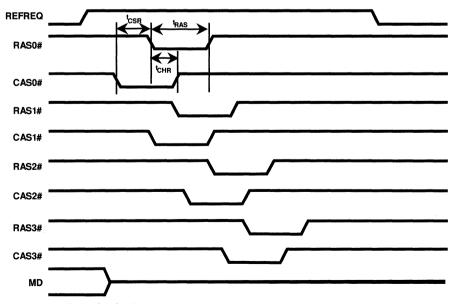

| Chapter 11. Intel486 SL CPU Memory Interfacing                     | 155        |

| Memory Controller                                                  | 156        |

| Designing a DRAM Memory System                                     | 156        |

| Cache Controller                                                   | 170        |

| DRAM Considerations for PC Memory Design                           | 172        |

| Summary                                                            | 182        |

| References                                                         | 182        |

| Chapter 12. PI-Bus Interfacing                                     | 183        |

| PI-Bus Architecture                                                | 183        |

| PI-Bus Applications                                                | 188        |

| Design Guidelines                                                  | 193        |

| Summary                                                            | 194        |

| References                                                         | 194        |

|                                                                    |            |

| Chapter 13. Enhanced Parallel Port                                 | 195        |

| Applications of the Enhanced Parallel Port                         | 195        |

| Comparison of the ISA Parallel Port and the Enhanced Parallel Port | 196        |

| Hardware Interface                                                 | 197        |

| Software Interface                                                 | 203        |

| Summary<br>References                                              | 206<br>207 |

|                                                                    | 207        |

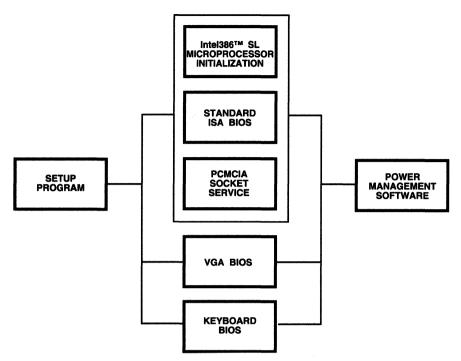

| Chapter 14. Writing an SL BIOS                                 | 209 |

|----------------------------------------------------------------|-----|

| What Is the SL BIOS?                                           | 209 |

| Special Feature Set                                            | 232 |

| I/O Cycle Recovery Time                                        | 234 |

| Reset                                                          | 235 |

| Modular Approach                                               | 235 |

| Summary                                                        | 236 |

| References                                                     | 236 |

| Chapter 15. System Development Tools and Debugging             | 237 |

| Hardware Development Tools                                     | 237 |

| Software Development Tools                                     | 237 |

| Create Your Own Tools                                          | 238 |

| Debugging                                                      | 238 |

| Debugging Tools                                                | 238 |

| Testing Methodology                                            | 241 |

| Common Errors                                                  | 243 |

| What to Do If a System Hangs Up                                | 247 |

| What If Everything Else Fails?                                 | 247 |

| Development Methodology                                        | 247 |

| Summary                                                        | 247 |

| References                                                     | 248 |

| Chapter 16. Performance and Potential                          | 249 |

| Introduction                                                   | 249 |

| Common Terminology                                             | 250 |

| Intel386 SL Microprocessor Performance Summary                 | 251 |

| Impact of System Attributes on Performance                     | 251 |

| Impact of Power Management on Performance                      | 254 |

| Performance and Cost                                           | 255 |

| Power Consumption Benchmarks                                   | 255 |

| Interpreting Benchmark Results                                 | 256 |

| Benchmark Collection Methodology                               | 256 |

| Summary                                                        | 257 |

| Chapter 17. The Future                                         | 259 |

| What Next?                                                     | 259 |

| Appendix A. List of Vendors                                    | 263 |

| Appendix B. Software Emulation of Hardware Using SMI           | 271 |

| Appendix C. Intel386™ SL Microprocessor DRAM Configurations    | 273 |

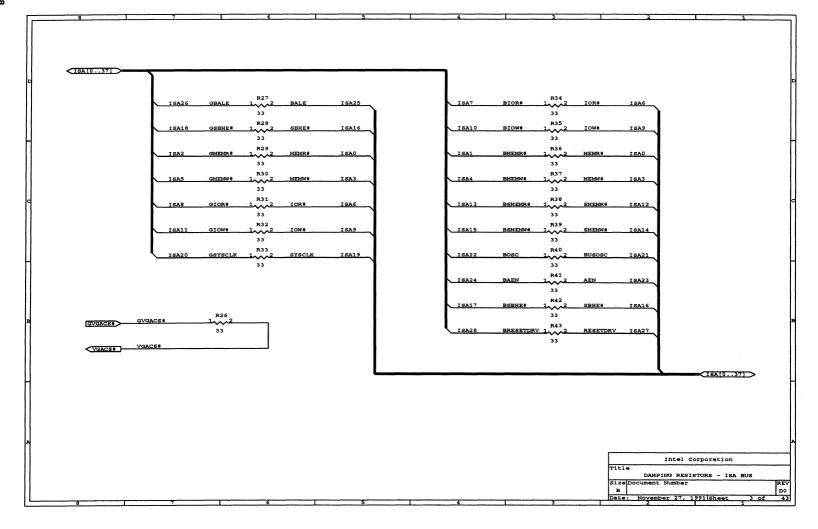

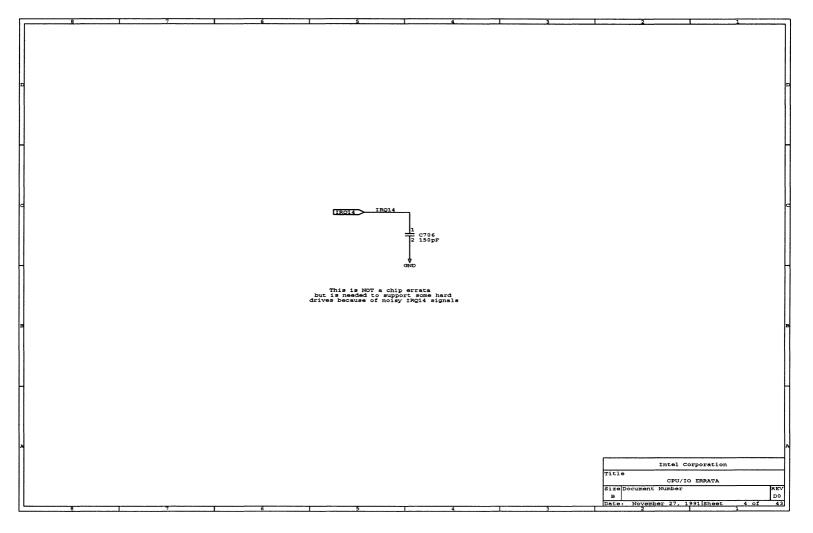

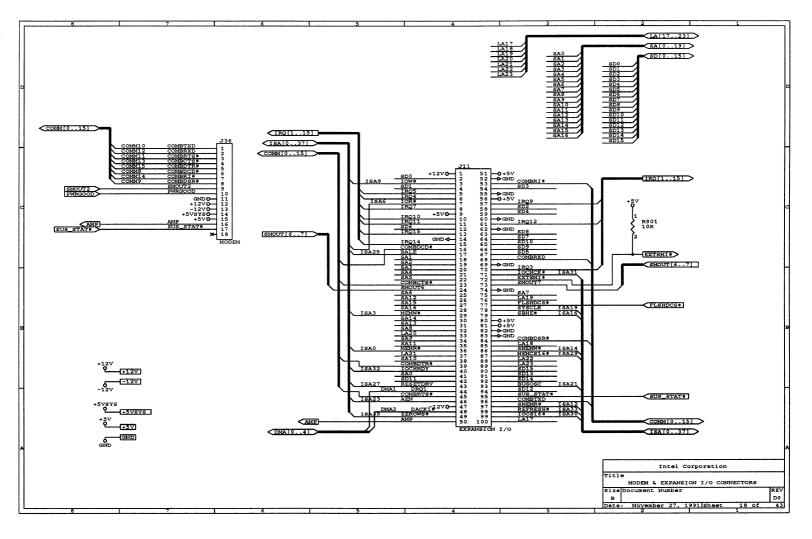

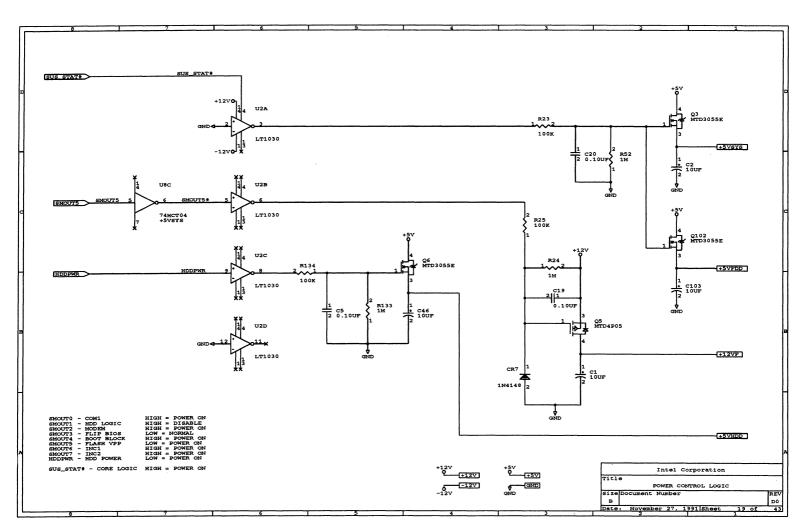

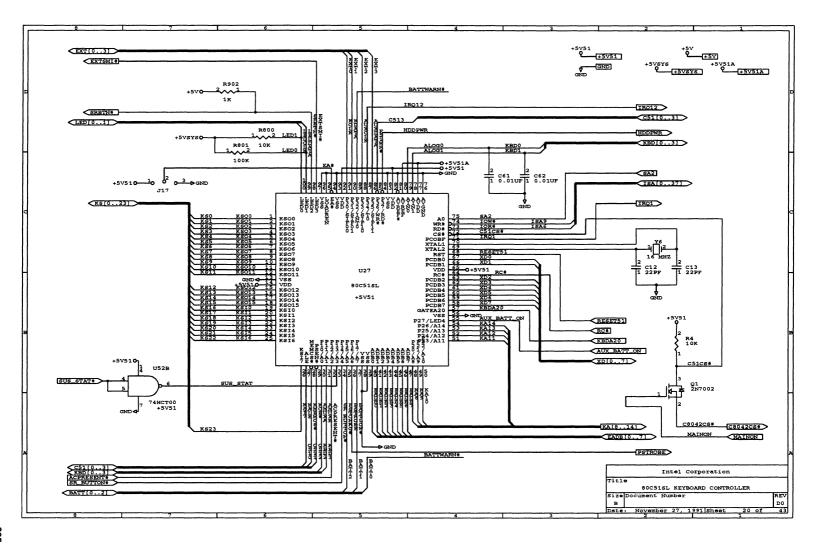

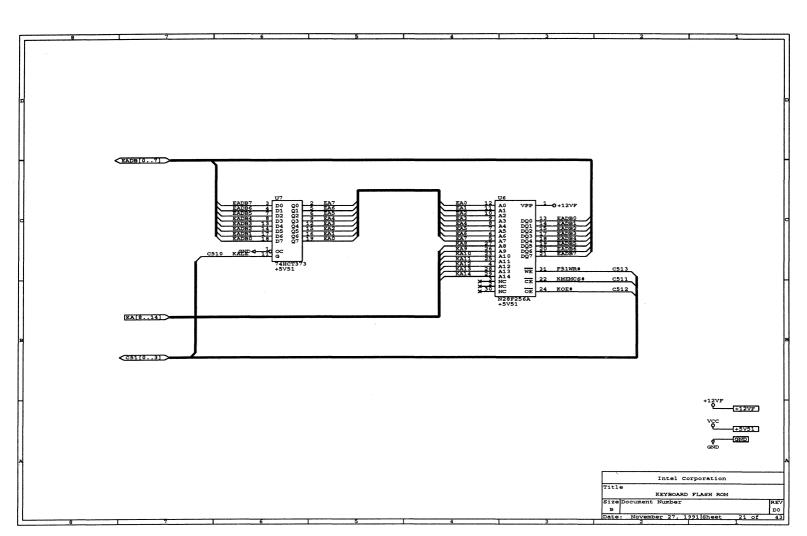

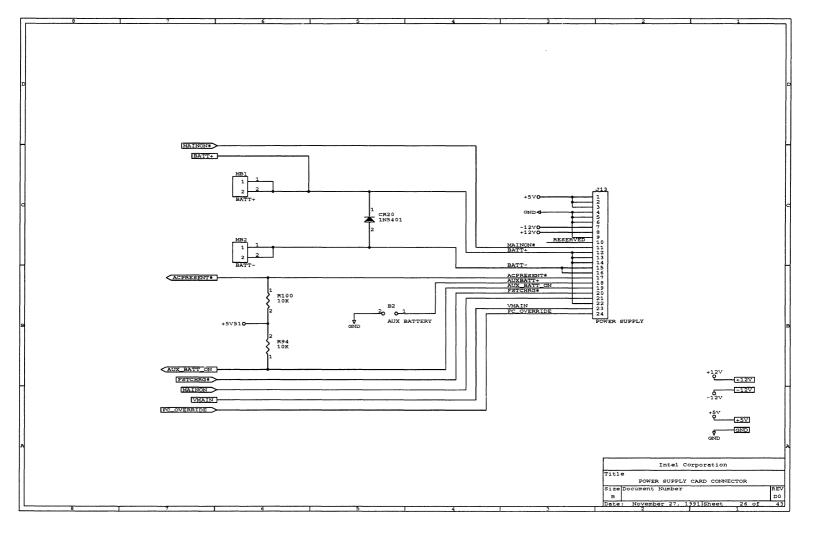

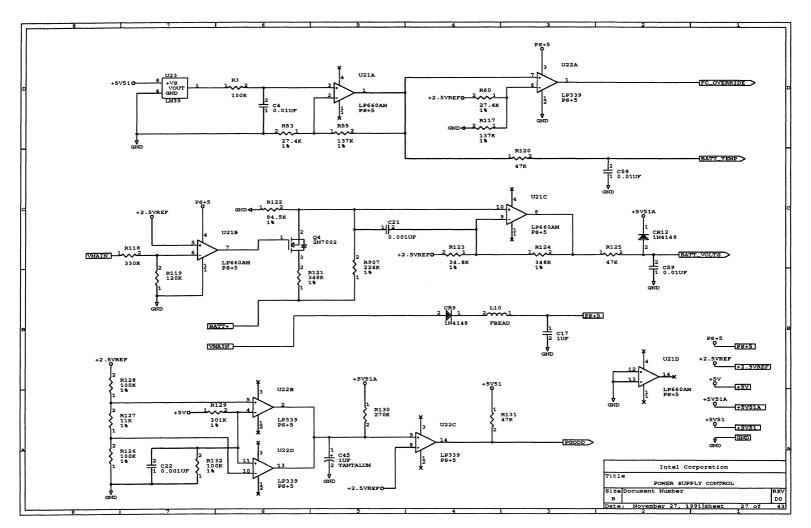

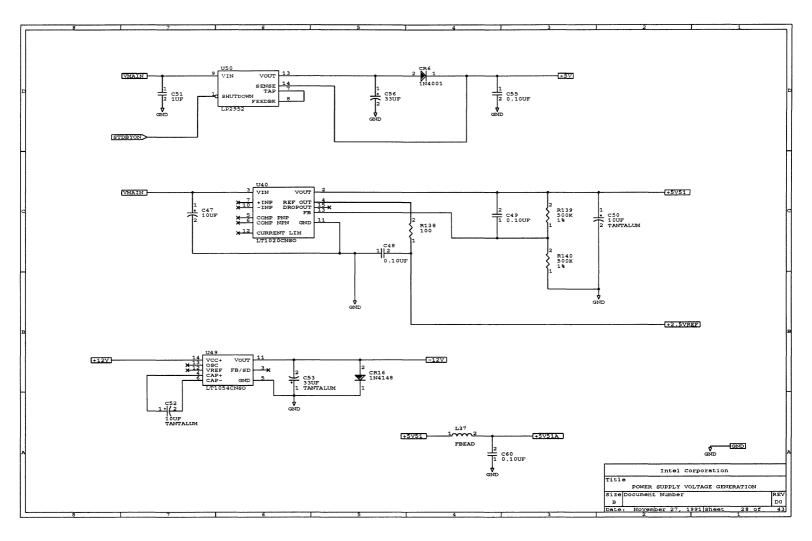

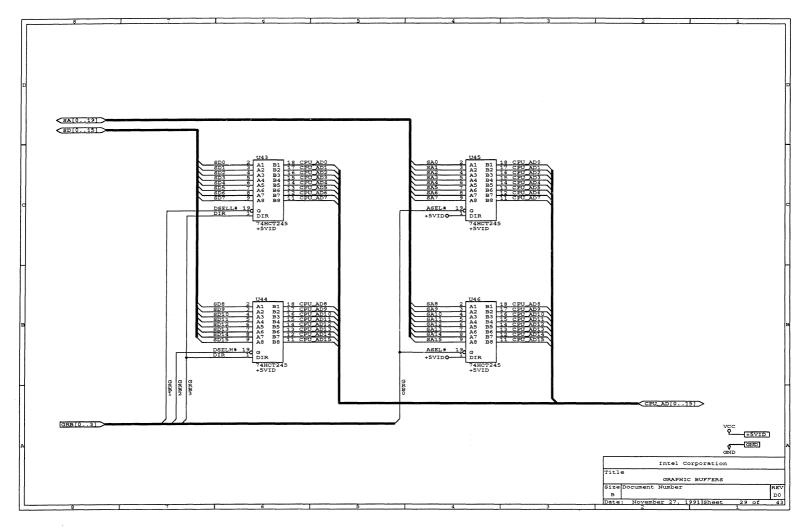

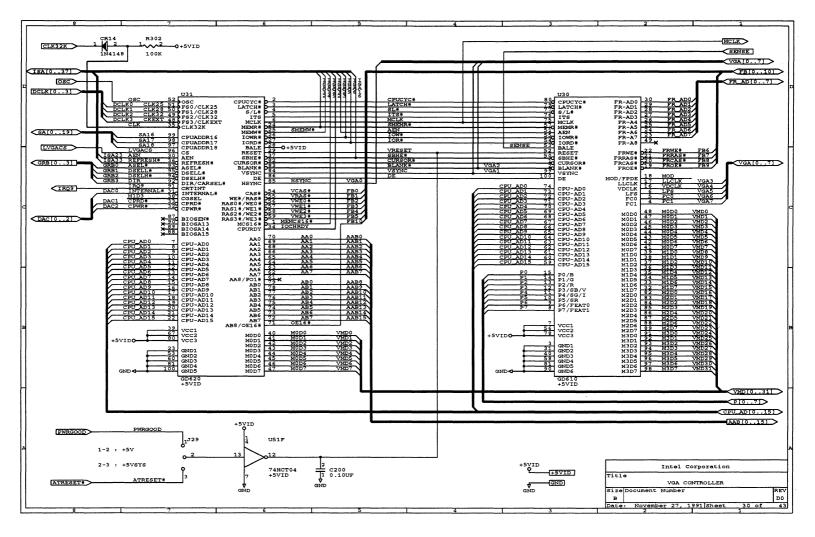

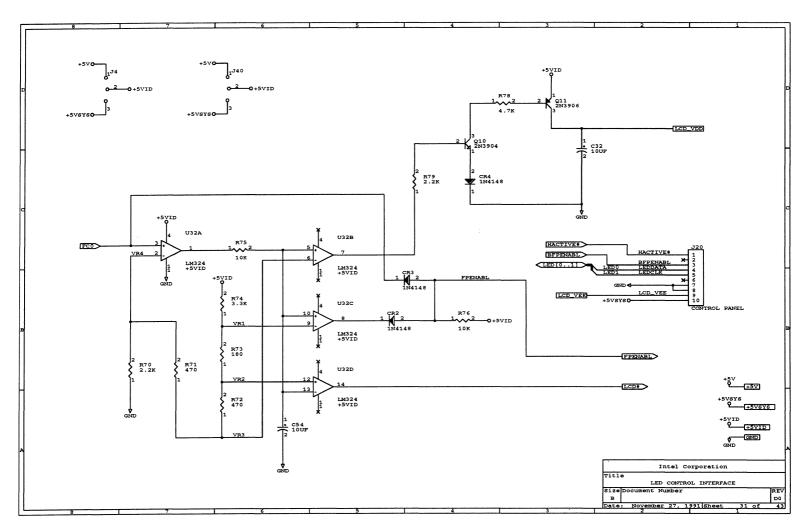

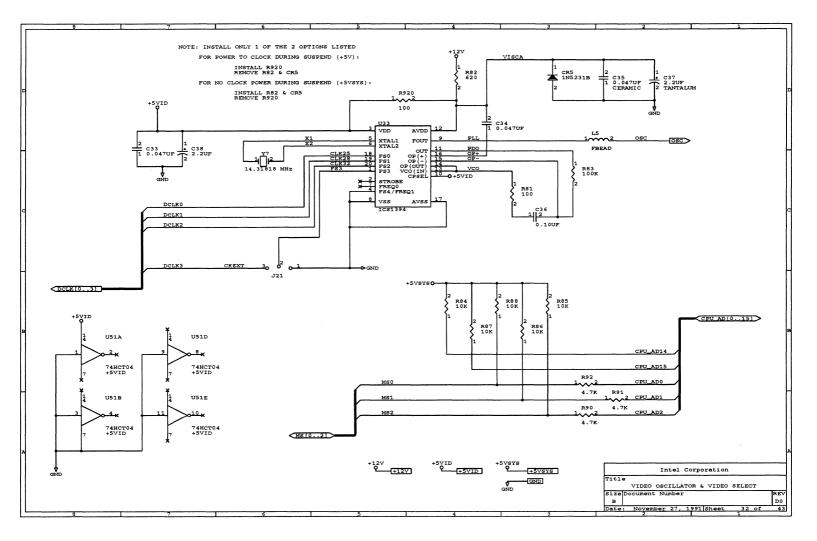

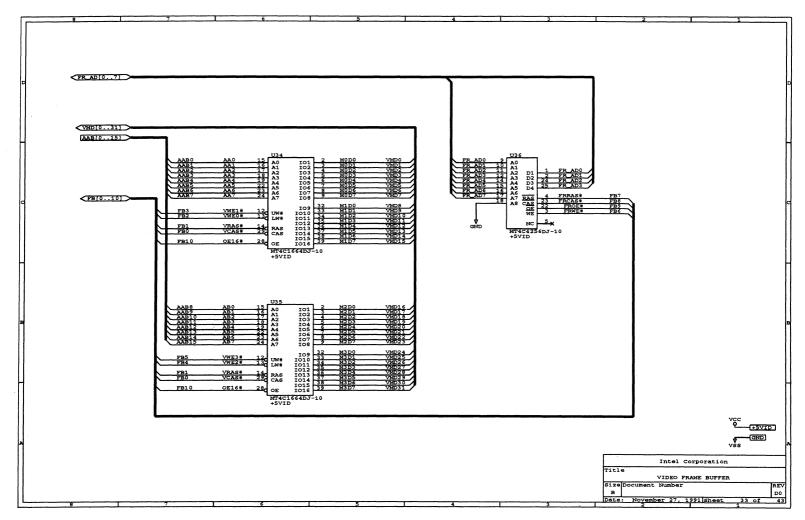

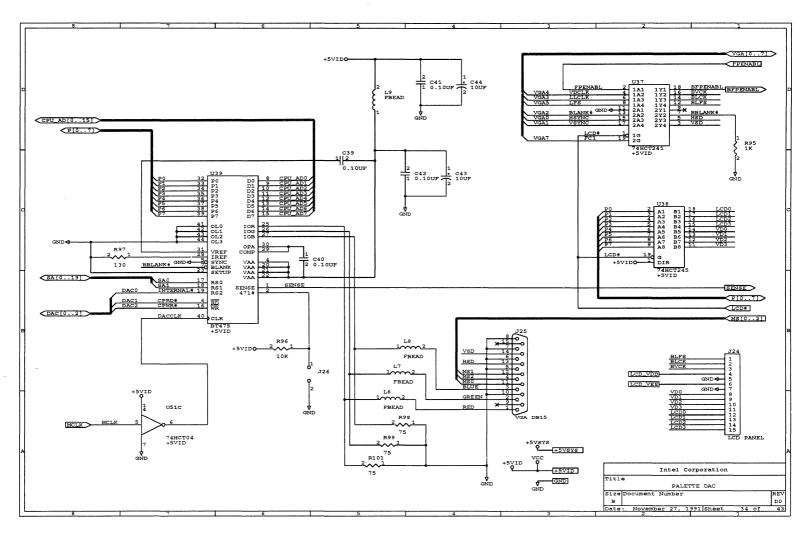

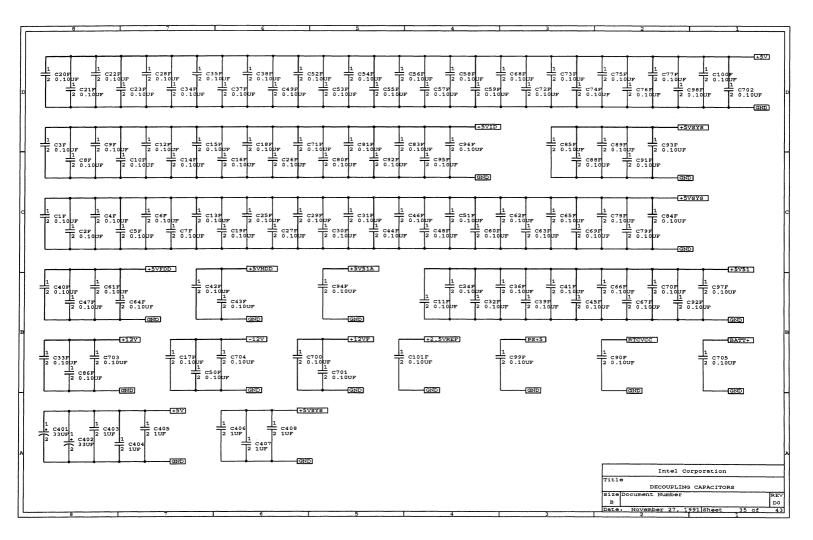

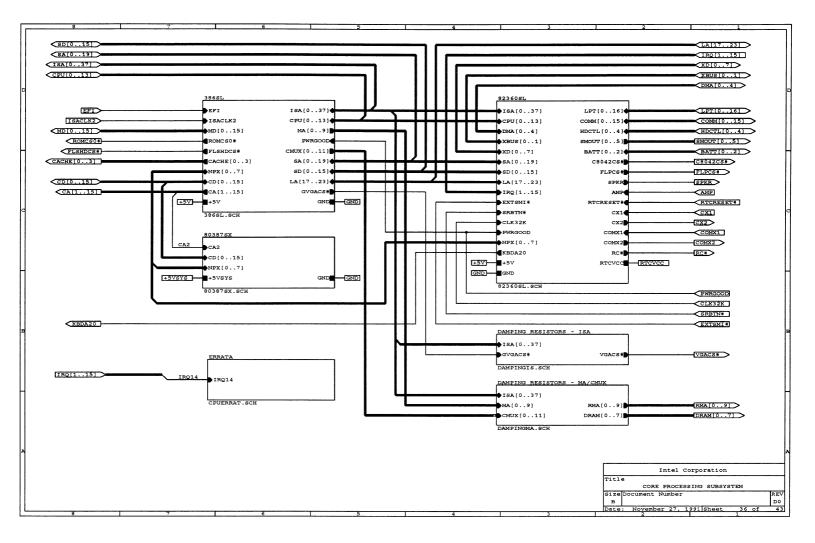

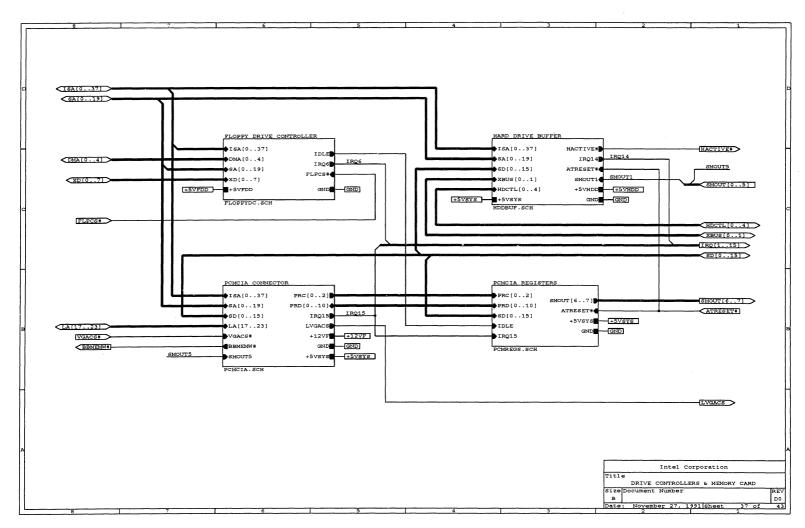

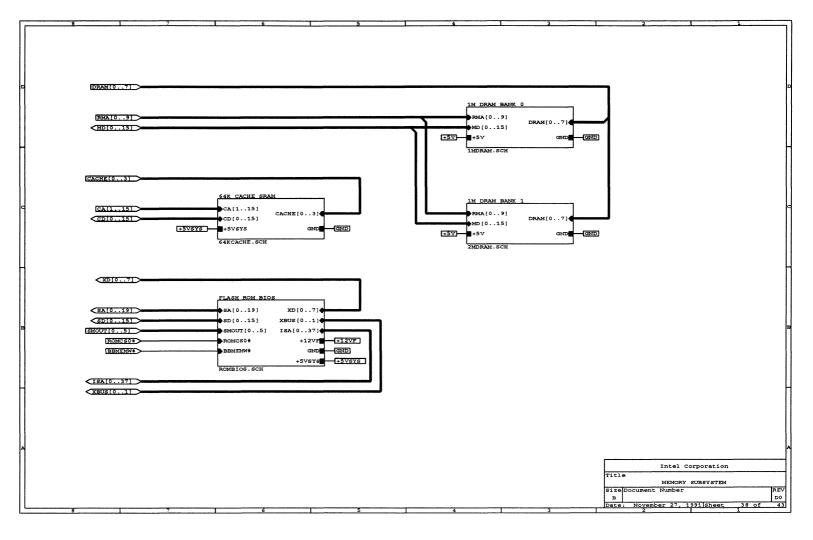

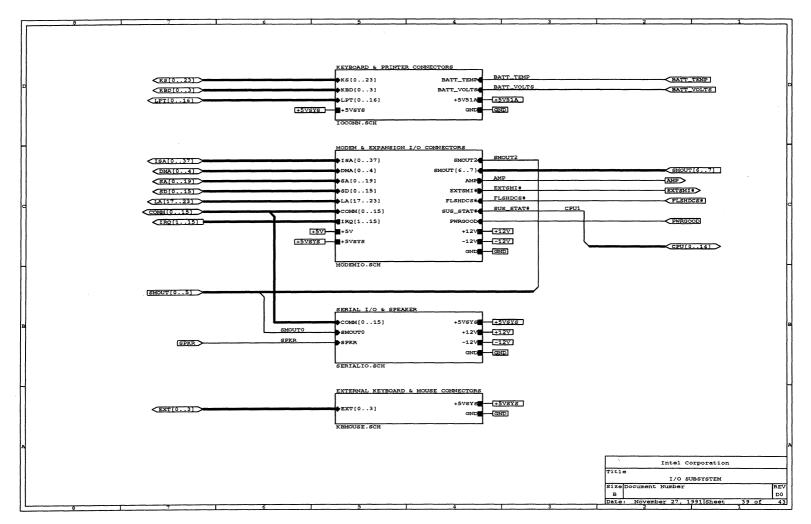

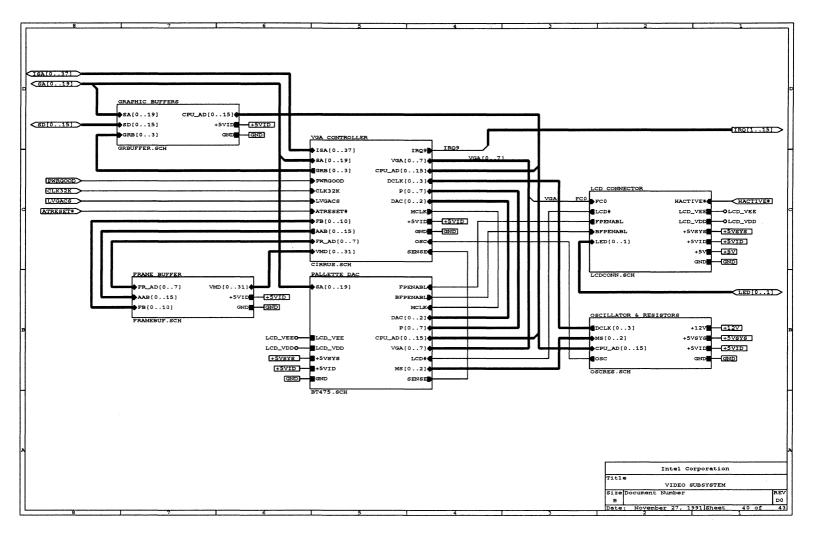

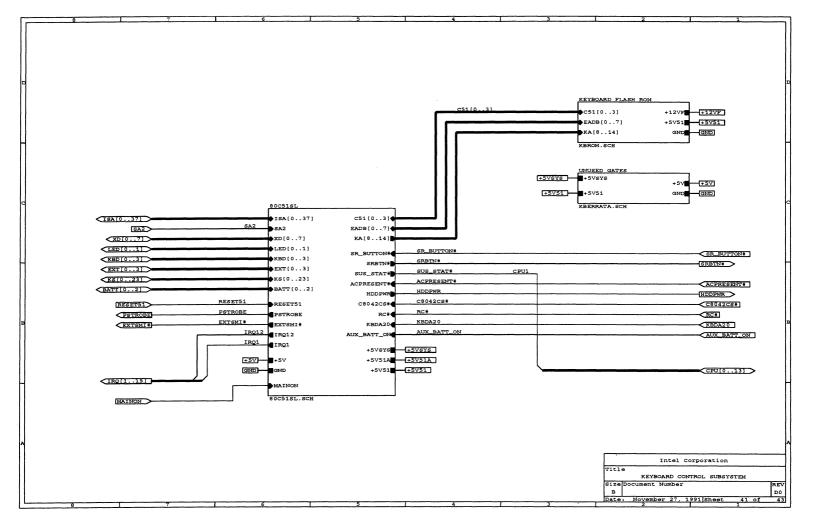

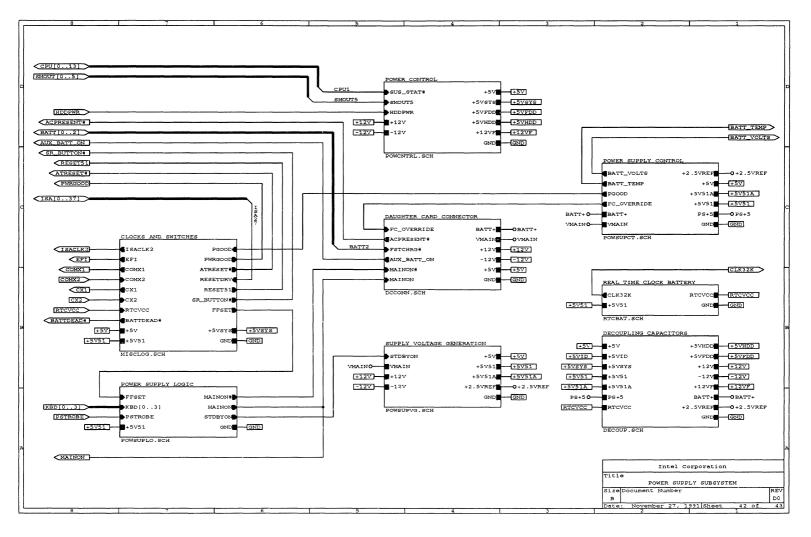

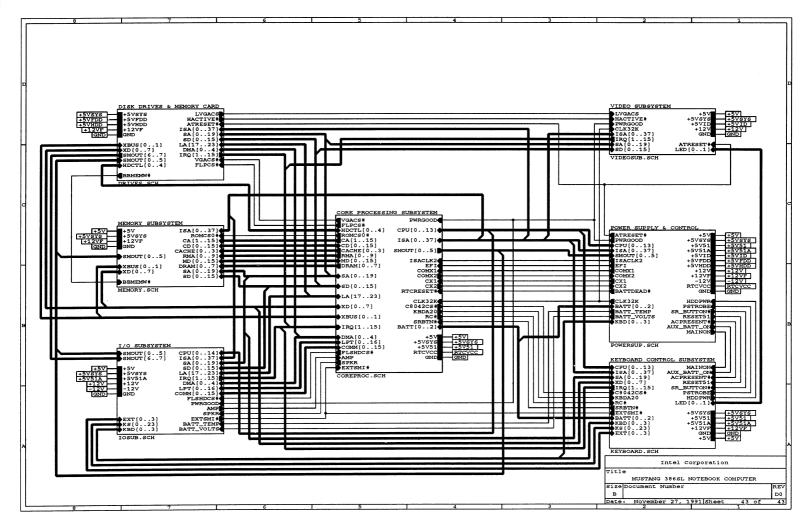

| Appendix D. Schematics for a Complete Notebook Computer Design | 275 |

## Foreword

This book contains a wealth of technical information about how to design an Intel486<sup>™</sup> SL CPU and Intel386<sup>™</sup> SL CPU-based portable computer. It is designed to help you better exploit the pioneering SL architecture. It provides concise overviews of the various features of the SL CPU, and the 82360SL peripheral controller. It also gives a great many examples of how these features can be used in your designs, with emphasis on System Management Mode (SMM), power management, and memory subsystem design. Finally, it provides many software and hardware design tips to help you avoid some of the common pitfalls inherent in portable computer design. Before you begin your portable computer design journey, I would like to give you some insight into the birth and development of the SL architecture.

The SL architecture was conceived as a product that would help spur the growth of the portable computer market. When Intel began the SL project, portables were quite heavy (ranging from 12 to 20 lbs) and had battery lives of 30 minutes to just over 2 hours. Many were also limited in the kind and amount of software that the users could run. Although the market for portable computers was growing rapidly, users were clamoring for lighter-weight, longer-battery-life machines.

Let me offer a personal anecdote that I hope will help you better understand the demands of the portable computer user. Several years ago, my job required me to work in two different states with a lot of airplane travel in between. In an attempt to simplify my life, I decided to get a portable computer so that I could carry my office with me in electronic format. The idea seemed simple enough, but in practice it turned into a new kind of nightmare! The weight of the portable machine I chose gave me a constantly bruised shoulder, and it was so big that it took up most of my leg room on the plane. Its limited battery life caused me to constantly seek wall outlets. I also found it cumbersome to open up the computer, boot the system, and load my application, especially during short waits in airports. As a result of my experiment with the electronic office, I was actually getting less work done using this wonderful "productivity enhancer" than when I was using paper!

Initially, I didn't think that a silicon company like Intel could really impact any of these problems. But as I started piecing together technical and marketing information, I realized that electronics could play a key role in solving all of my problems. Hardware support for power management could extend battery life. Greater component integration could make machines smaller and lighter. And performance could be improved by using an Intel386 CPU in place of the 80286 technology.

As I visited our customers and discussed the problems of portable computer design, I quickly realized that everyone was trying to solve the same problems and that Intel could offer viable solutions.

Many people were involved in nurturing the concepts that became the SL architecture. The team included people from both inside and outside of Intel. Most of the team was composed of silicon and system engineers; however, it also included people from marketing, fabrication, applications, software development, and product validation.

The resulting SL architecture introduced many advances to microprocessor architectures, including on-chip power management facilities, suspend/resume capability, high integration, a high-speed Peripheral Interface bus (PI bus), a faster parallel port, and support for emerging technologies like Flash Memory. It also brought 32-bit computing to the portable computer arena, giving PCs the processing power to run any software package at the required level of performance.

Perhaps the greatest achievement of the SL architecture was the introduction of System Management Mode. SMM is an environment which provides system designers—Intel's customers—with the ability to take control of the system regardless of the software being run. Not only does SMM provide a simple and robust mechanism for implementing power management facilities in a portable computer, but it also enables system designers to add other productspecific features to their machines without having to worry about compatibility with the operating system and application programs. Portable computer designers can thus easily "differentiate" their machines by adding features that offer unique benefits to their users. Our customers continue to find innovative ways of using the SMM "tool box."

I would like to give credit to everyone involved with making the SL architecture a reality. This includes well over a hundred Intel employees, as well as many of our customers and design partners. Without them our better mouse trap would simply be collecting dust in a corner of a dark shelf. Worse, I'd still be looking for a way to protect my bruised shoulder.

> DAVE VANNIER Chief Architect of the SL Architecture and Co-Architect of the Intel386 Architecture

## Preface

Since the introduction of the Intel386 SL Microprocessor Superset, many exciting things have happened in the laptop world. The introduction of the Intel386 SL microprocessor has certainly changed the way people think about laptop computers.

While working at Intel as an applications engineer, I accumulated a wealth of knowledge about how to design SL architecture-based products through working with PC manufacturers and the BIOS vendors. Instead of letting this information get lost, I decided to write this book to share the experience and knowledge I have gained over the years. Hopefully, the information contained in this book will spur further growth in the PC industry.

This book has been written primarily for system designers and programmers who are developing products based on the Intel486 SL microprocessor and the Intel386 SL microprocessor. This book is for anyone who wants to understand the SL architecture to improve their hardware, BIOS, and support software designs. The main goal of this book is to show readers how to design innovative products using the SL architecture.

This book should be of particular interest to readers wishing to use the system management mode of the SL processor for better power management. Even though the concept of power management has been around for a long time (probably since the day the battery was invented), power management on PCs is still a myth to many people. One of the goals of this book is to demystify power management.

I believe that the best way to learn about the SL architecture is to experiment with it. Many examples are given throughout the book to assist readers in experimenting with the Intel486 SL microprocessor and the Intel386 SL microprocessor. To make it easier to use this book, the software (including program listings) and examples are included on a disk.

It is difficult to master a subject that is continuously evolving. You have to constantly adapt to changes and take advantage of the new technology. Instead of trying to catch up with the technology, my advice is to be innovative and stay ahead of the technology. I hope this book will help many of you to achieve that goal.

## Acknowledgments

There are many people at Intel who provided tremendous support on this project. Dave Ryan sponsored my book and his confidence in me helped me to take the initiative to write it. Without Dave's support, this book would not exist. Dave Vannier, co-architect for the Intel386 microprocessor and grandfather of the SL architecture, wrote an excellent foreword. Tom Rossi, my boss and my coach, provided continuous support and encouragement.

Pauline Albert, Janet Brownstone, and Barbara Holtz provided continuous encouragement to keep me going. Janet, my coordinator for the book, has been very protective and supportive. She took care of a lot of details for me so that I could concentrate on writing.

Gregg Wyant deserves special thanks for spending a lot of time (including weekends) working with me on the organization and technical contents of the book. Bob Albers did a thorough critique of the first draft of the manuscript and made many valuable suggestions. Simon Ellis, one of the key architects for the Intel386 SL microprocessor, wrote an excellent chapter on the history of the SL architecture.

Betsy Jones provided very useful input and suggestions throughout this project. Darci Worth has done a lot of work with power consumption measurements and some of the information used in the book is based on her work. Patrick Murray and Phil Cloud were very helpful in checking the accuracy of the technical contents of the book. Jessie Garcia built the flash disk card for the PI bus. My thanks to Suresh Marisetty for writing the appendix on hardware emulation using SMI. K. J. Jun reviewed the page proofs for technical accuracy.

It is extremely hard to find qualified reviewers who can spend time to evaluate a book of this magnitude. I am fortunate enough to have many good technical reviewers who sacrificed their spare time to review my book. I would like to thank the following people for providing suggestions on the manuscript. Bill Rallis of SystemSoft Inc. and Dennis Chang of Award Software Inc. reviewed the source listing and the chapters related to programming. Scott Schaefer of Micron Technology checked materials related to DRAM, SRAM, and cache RAM and also put forth extra effort to review in detail the other chapters as well. Jim Williams of Linear Technology evaluated the power supply material. Paul Cahill of Gates Energy Products checked battery information. Mark Singer and Ed Garcia of Cirrus Logic Inc. checked chapters on PI bus and graphics-related chapters. Frank Barry of IBM reviewed the overall organization of the book. David Schwabe did an excellent job on the copyediting. Special thanks to my acquisition editor Neil Levine and his production staff at McGraw-Hill for their excellent support.

### Intel's SL Architecture

# Chapter

1

### Introduction

From the day the personal computer (PC) was invented, people have anxiously awaited the PC on a chip. Intel took a big step toward this goal with the introduction in 1990 of the SL architecture. This architecture offers two important features that foster the development of small, lightweight PCs. First, the SL architecture embraces almost all of the CPU, memory management, system control, and peripheral control functions required to make a PC. When implemented in silicon using very large scale integration (VLSI) circuitry, the SL architecture allows a PC to be designed with only a handful of components.

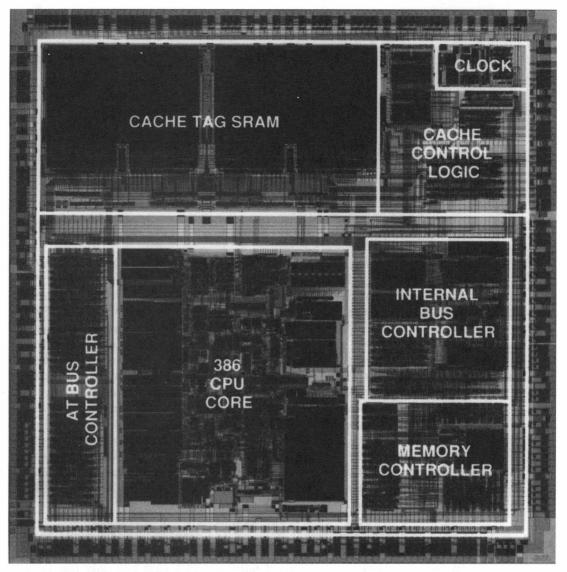

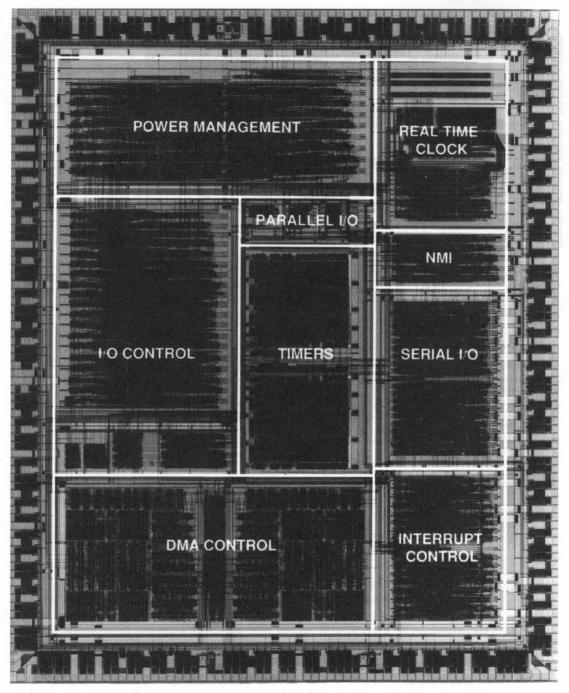

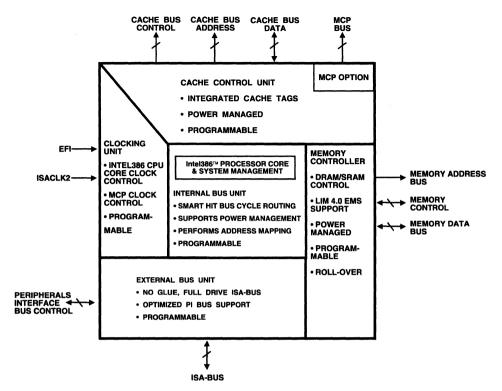

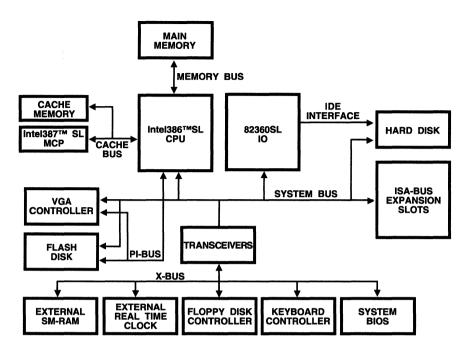

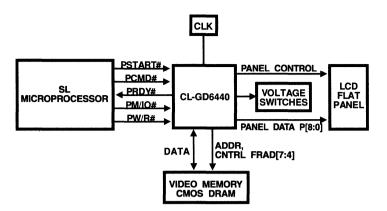

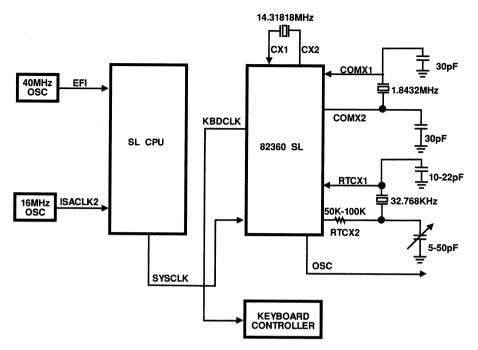

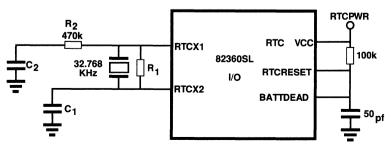

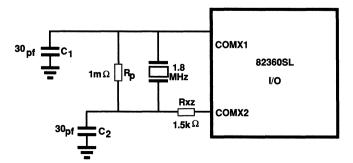

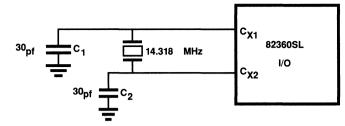

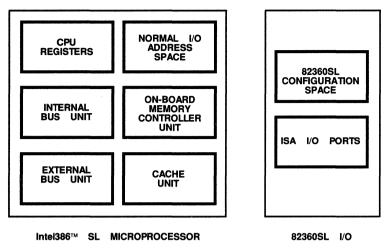

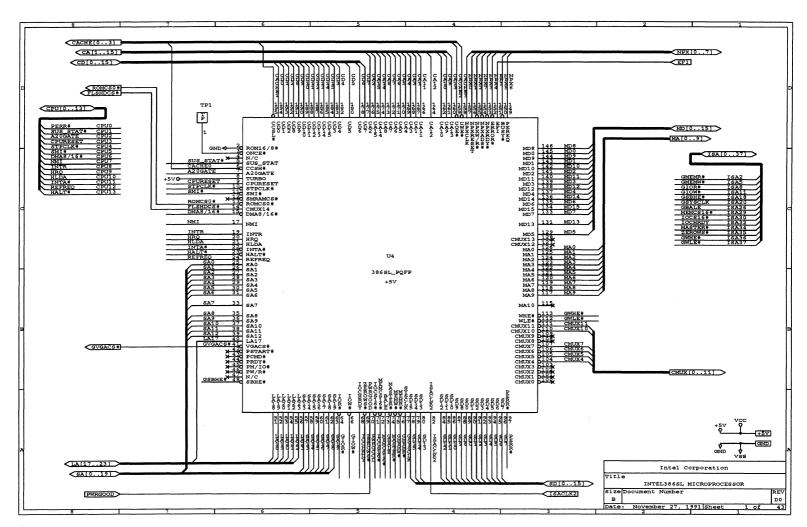

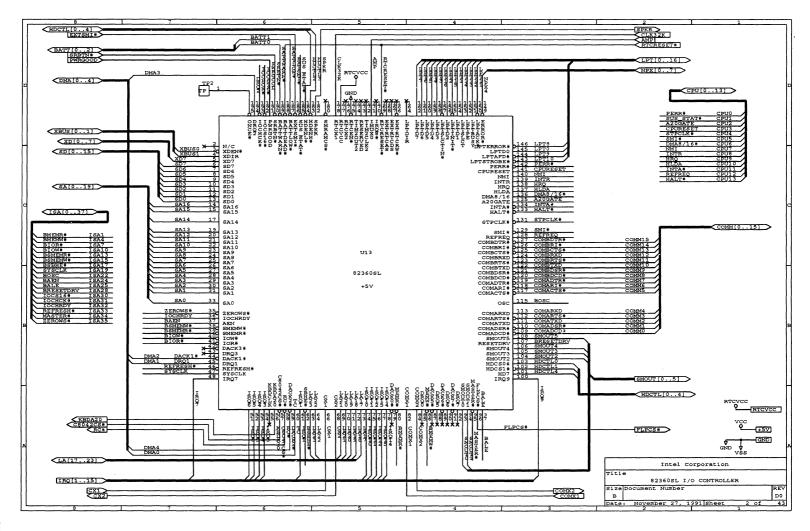

Second, the SL architecture offers several power management features that allow the design of PCs that can run for many hours on a single battery. The most important of these features is the system management mode (SMM), a unique operating mode that allows the CPU to execute system management software transparently from the operating system and application programs. In the first implementation of the SL architecture, Intel engineers were able to pack all the SL circuitry into two components: the Intel386 SL CPU and the 82360SL peripheral controller. (See Figs. 1.1 and 1.2.)

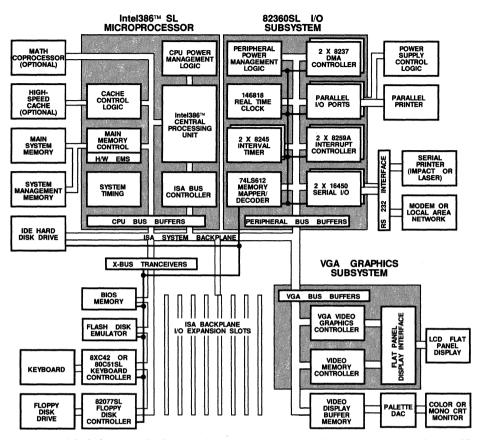

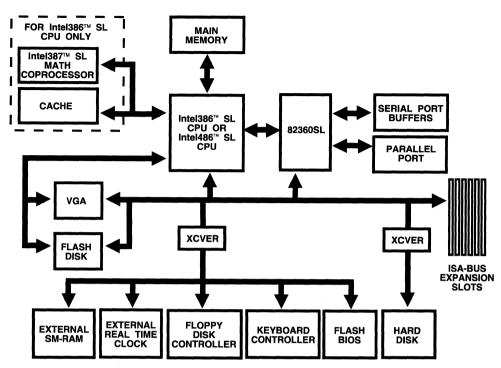

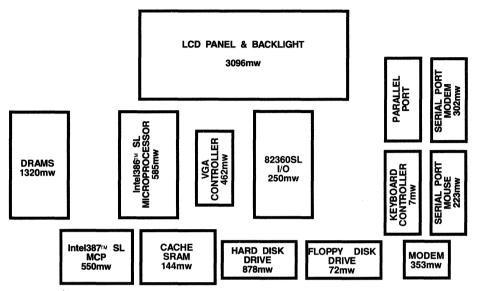

Using Intel's CMOS IV chip technology, these components provide Intel386 CPU-class computational power, plus all the memory management, system management, bus control, and peripheral control hardware required to build a PC. In fact, Intel386 SL CPU-based notebook PCs that use only ten components (not counting the memory devices) are already on the market. These chips also provide a wide range of power management features that have allowed designers to extend the operating time of battery-powered notebooks to eight hours or more. (See Fig. 1.3.) In the spring of 1992, Intel introduced a 3.3-volt version of the Intel386 SL CPU, and in the fall of 1992, they introduced the Intel486 SL CPU.

This book describes the SL architecture and its implementation in the Intel486 SL CPU, Intel386 SL CPU, and 82360SL peripheral controller components. It also discusses a broad selection of system design considerations, divided into various topic areas. The design tips given in each topic area include sample circuits and assembly-language routines.

Figure 1.1 Die photograph of the Intel386 SL microprocessor.

The intention of this book is to help you understand the operation of the SL CPU and 82360SL components and learn how to exploit various features of these components to develop profitable and innovative portable PCs, penbased systems, and Personal Application Devices (PADs).

#### **Organization of the Book**

Your introduction to the SL architecture begins in Chap. 2 with an insightful look at the history of the architecture written by Simon Ellis, one of the archi-

Figure 1.2 Die photograph of the 82360SL peripheral controller.

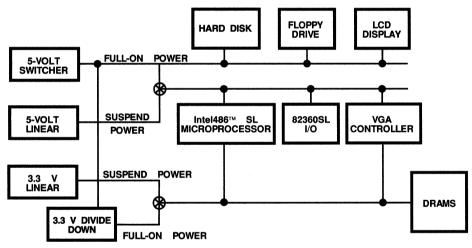

Figure 1.3 Block diagram of PC system based on the Intel386 SL microprocessor and 82360SL.

tects of the SL architecture. This chapter explains the motivation behind the "Genesis Project," the Intel code name for the SL development project, and the reasons for many of the features in the architecture.

Chapter 3 provides a brief overview of the SL architecture. It describes the underlying design of the architecture and introduces you to the basic components of a PC system. The remaining chapters of this book cover system design considerations and give valuable hardware and software design tips.

Chapter 4 describes the most innovative feature of the SL architecture: the System Management Mode. The SMM is a special operating mode that allows the execution of system and power management routines to be isolated from the operating system and application program to prevent incompatibility with BIOS routines. This chapter describes the architecture of the SMM and gives several examples of how it can be used in a PC design.

Chapters 5, 6, and 7 describe the power management features provided in the SL architecture to reduce power consumption in a battery-operated portable computer. These features include using the SMM to execute power management routines; a mechanism for powering down idle peripheral devices; the ability to stop the clock to the CPU and other system components; and the suspend/resume mechanism that enables a system to be powered down, then powered up again without losing the state of the machine.

Chapter 8 discusses several issues that must be considered in portable computer designs and how the SL architecture addresses these issues.

Chapter 9 describes the clock control facilities and the mechanisms available to slow or stop various system clocks to reduce power consumption in system components.

Chapters 10 and 11 describe the memory management facilities of the Intel486 SL CPU and Intel386 SL CPU. The emphasis in these chapters is on the facilities provided to reduce the power consumption of memory components during normal operation and in a number of power-down modes.

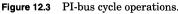

Chapter 12 describes a special enhanced version of the ISA bus, called the *peripheral interface bus* (PI bus), which the SL CPUs support. This chapter also shows how this bus can be used as an interface to a flash disk and a VGA graphics frame memory.

Chapter 13 describes the ISA-bus interface and ISA peripheral controllers provided in the 82360SL. It also gives guidelines for interfacing other peripheral controllers such as a keyboard controller, floppy-drive controller, and IDE hard disk controller to the 82360SL.

Chapter 14 describes the 82360SL's enhanced parallel port, a simpler and faster parallel port interface that shares the same signal lines as the ISA parallel port.

Chapter 15 gives guidelines for writing BIOS routines to control various aspects of system operation in SL CPU-based products of an operating system.

Chapter 16 gives some guidelines for debugging SL architecture-based products. It also shows how to build some of your own debugging tools using the SMM mode to execute debugging routines.

Chapter 17 describes several mechanisms and issues that affect the performance of the SL CPU-based products.

Chapter 18 offers some insights into the future of the SL architecture.

#### **Basic Concepts**

Before we start looking at the SL architecture in great detail, it is important to review some of the fundamental concepts we will be using throughout this book.

#### System management

System management mode is a special execution mode of the Intel486 SL CPU and Intel386 SL CPU used to support applications such as power management software and to ensure compatibility with existing operating systems and applications software.

#### **Power management**

Power management is a mechanism of controlling the power consumption of a system to extend battery life.

#### 6 Chapter One

#### **Battery management**

Battery management involves performing functions like monitoring the battery temperature and voltage, recharging the battery, and detecting batterylow condition. Do not get battery management confused with power management—they are not the same.

#### Power mode

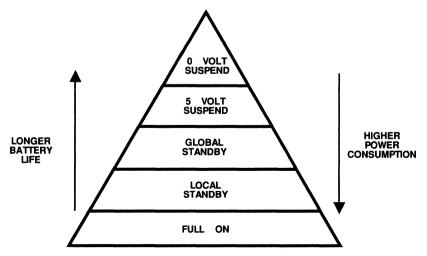

Power mode is a representation of the power consumption level of a device or system. An SL CPU-based system can be programmed for local standby, global standby, or suspend mode to conserve power. (See Table 1.1.)

#### **Hardware Platform**

Most of the examples and programs in this book were designed to run on the SL microprocessor evaluation board. This board was chosen because the configuration jumpers, test points, connectors, ISA-bus expansion slots, and the breadboarding area on the evaluation board make experimentation easy. The schematics for the evaluation board are available from your local Intel sales office.

#### Notation

The following notation and conventions are used throughout this book.

Signal descriptions. # denotes active low signal.

**Bit notation.** Bits field within a byte or word are shown as a range of decimal numbers separated by a dash, such as y-x. (*Example:* Bits [2-0].)

**Hexadecimal numbers.** Hexadecimal numbers are represented by a string of hexadecimal digits followed by the character H. A leading zero is added if the number would otherwise begin with one of the digits A-F. (*Example:* 38H, 0FFH.)

| Mode           | Relative power | Typical power       | User overhead    | Main advantage            |

|----------------|----------------|---------------------|------------------|---------------------------|

| Full on        | Full           | 8410 mW<br>@ 20 MHz | None             | Full speed operation      |

| Local standby  | Low            | 4410 mW<br>@ 20 MHz | Low              | Peripherals<br>disabled   |

| Global standby | Medium low     | 2455 mW<br>@ 20 MHz | Moderate to high | Code execution<br>stopped |

| Suspend        | Lowest         | 53 mW<br>@ 20 MHz   | High             | Long battery<br>life      |

| TABLE 1.1 Summary of Power Modes in a Typical Intel386 SL CPU- | CPU-based System |

|----------------------------------------------------------------|------------------|

|----------------------------------------------------------------|------------------|

**Bytes, words, double words.** A byte is 8 bits. A word is 16 bits. A double word (dword) is 32 bits.

**Configuration spaces.** The following abbreviations are used to represent the five hidden configuration spaces in the SL architecture:

| IBU   | Internal Bus Unit configuration space          |

|-------|------------------------------------------------|

| OMCU  | On-board Memory Controller configuration space |

| CU    | Cache controller Unit configuration space      |

| EBU   | External Bus Unit configuration space          |

| INDEX | 82360SL configuration space                    |

**Configuration space addresses.** The following format is used to show the configuration space address for registers inside the SL architecture configuration spaces:

mnemonic (configuration space address, configuration space)

For example:

MCMODE (300H, OMCU)

In this example, MCMODE is the mnemonic for the Memory Controller Mode Register, 300H is the configuration space address, and OMCU is the configuration space where MCMODE register resides.

**Normal I/O space addresses.** The following format is used to show the address for registers inside the normal I/O address space:

mnemonic (address)

For example:

CPUPWRMODE (22H)

In this example, CPUPWRMODE is the mnemonic for the CPU Power Mode register and 22H is the I/O address.

Units of measure. The following units of measure are used throughout the book.

| Symbol | Unit        |

|--------|-------------|

| А      | ampere      |

| Kbyte  | kilobyte    |

| Mbyte  | megabyte    |

| MHz    | megahertz   |

| mA     | milliamp    |

| ms     | millisecond |

|        |             |

| Symbol | Unit        |

|--------|-------------|

| mW     | milliwatt   |

| ns     | nanosecond  |

| s      | second      |

| W      | watt        |

| μs     | microsecond |

| V      | volt        |

#### **Useful References**

You will find the following books, papers, and data sheets useful when designing an SL CPU-based product. All of these publications are available from Intel.

The Intel486 SL Microprocessor SuperSet Programmer's Reference Manual, Order Number 241327-001

The Intel486 SL Microprocessor SuperSet System Design Guide, Order Number 241326-001

The Intel486 SL Microprocessor SuperSet Data Sheet, Order Number 241325-001

"The Intel486 SL Microprocessor SuperSet Family Product Brief"

"The Intel486 SL Microprocessor Family Overview"

The Intel386 SL Microprocessor SuperSet Programmer's Reference Manual, Order Number 240815-004

The Intel386 SL Microprocessor SuperSet System Design Guide, Order Number 240816-002

The Intel386 SL Microprocessor SuperSet Data Sheet, Order Number 240814-005

"The Intel386 SL Microprocessor Family Overview," Order Number 240865-001

"The Intel386 SL Microprocessor SuperSet Family Product Brief," Order Number 240851-001

"Notebook Market Overview—The New Computers," Order Number 240864-001

#### Summary

The most interesting thing about the Intel386 SL PCU project is how the architecture evolved along the course of development. The changes are largely due to changes in the market and feedback from customers. We worked with the customers to find out what they really needed. The process involved talking with the notebook computer manufacturers and software vendors. Input from the alpha and beta sites was key in defining the SL architecture. The end

result is a highly flexible architecture. Direct input from customers also influenced the design specification process. The most significant thing we have heard from customers is that they want a better mechanism to handle power management. In response, the system management mode was implemented. Not only does system management mode make power management much more efficient and reliable, it also opens up a world of opportunity for new applications.

# Chapter

## The History and Future of the Intel SL Architecture\*

The Intel SL research and development program started in the middle of 1988, at which time Intel established a task force to evaluate the PC marketplace and determine where we could add value. At the time, the industry was based on the 80286 CPU with the Intel386 architecture about to overtake it. The portable PC market was taking off and was proclaimed by industry observers to be the fastest growing market segment. Because of this predicted growth potential, we decided to focus on battery-operated portable computers.

#### The SL Challenge

Having evolved from desktop designs, the first portable computers contended with power management and form factor as their chief design challenges. Intel's development team was driven by three motivating challenges: to make significant progress toward the "PC on a chip"; to provide on-board power management facilities; and to provide a transparent "suspend/resume" capability from any Intel386 CPU operating mode. (*Suspend/resume* is the ability to suspend operation while the computer is powered off, then to resume the exact state from which the machine was suspended when the computer is powered up again.)

The original PC was made from 180 components, which were reduced to about 30 by 1988. Intel decided on a target of ten or fewer components.

Our power management research centered around finding ways to add new power saving functions to an architecture that was originally designed for the desktop. We believed that the most convenient way to preserve battery life is to control the power going to the PC subsystem and to provide power only when necessary. However, this particular power management technique does not

<sup>\*</sup> The author wishes to gratefully acknowledge that this chapter has been contributed by Simon Ellis.

always maintain strict PC compatibility. The compatibility problem became even more severe in systems that used the Intel386 CPU architecture. The Intel386 CPU architecture extended the capabilities of the PC platform by adding more sophisticated operating modes, such as extended memory management and paging. As the PC operating system software was developed to utilize these capabilities, the problem of managing power transparently suddenly became more difficult by an order of magnitude.

After deciding which market to address and diagnosing the major problems in that segment, we began to engage our customer base. Fortunately, most portable computer manufacturers were already Intel customers and were willing to listen to our proposal. Moreover, most of them were already trying to solve these very same portable PC design problems in their own ways.

For Intel to provide the solutions, we knew we would have to take a fullsystem approach. The problem of PC compatibility was equal to that of the power management, however, and Intel did not have a proven track record in the compatibility arena. We understood that we would have to learn more and to prove that our power management strategy would yield PC-compatible computers before our customers would take us seriously. Intel of course had some major competencies to offer in other areas. We understood X86 compatibility and PC performance, and we were able to manufacture high-transistor-count devices at high volume. In the end, we partnered with one major customer and began designing the detailed architecture.

#### **The Solution**

When we began our design phase, high-volume Intel silicon processes were capable of integrating one million transistors, and our packaging was in the 196 lead range. The Intel386 CPU core has about 275,000 transistors, giving us room for some significant integration. We established a two-chip solution that consisted of the Intel386 SL CPU, containing the CPU and high-performance devices, and the 82360SL peripheral unit, containing the PC peripherals and the bulk of the power management logic.

#### **System Partitioning**

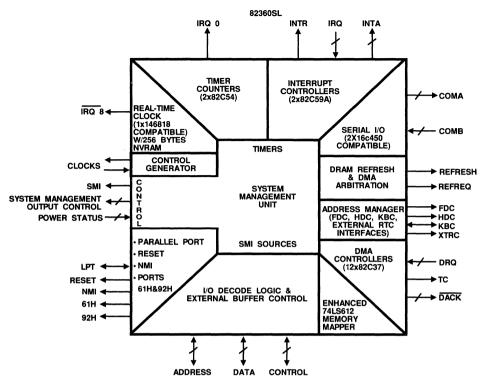

The Intel386 SL CPU contains about 880,000 transistors. It has a modified Intel386 CPU core, memory controller, EMS 4.0 mapper, ISA-bus controller, cache controller, and PC address mapper. Intel's ability to integrate these devices on a single piece of silicon offers many design benefits. For example, interfacing between the modules is done in the metal layers on the die. The signals are not limited in number and do not have to be buffered to drive pins and high loads. The addresses coming out of the CPU core are available two clocks earlier than the equivalent stand-alone CPU. These benefits were utilized to increase performance and reduce the number of cycles. The full cache lookup is done internally before the cycle and only goes to the memory controller if the cycle is a cache miss or write. The 82360SL is a complete IBM PC-AT-compatible peripheral subsystem chip that contains: Programmable Interval Timer (PIT), Programmable Interrupt Controller (PIC), DMA (plus, mapper), dual serial ports, enhanced (fast) parallel port, Real Time Clock plus CMOS (RTC), and the system monitoring functions for power management.

#### **Power Management**

Transparent power management presented a different problem. Chip vendors offered many partial solutions, including: static CPUs, power management controllers with system event timers and monitors, sleep modes, low-power devices, and software drivers. None of these solutions addressed the fundamental problem of how to maintain PC compatibility while power managing the computer. Existing notebook computers used standard PC resources, such as Nonmaskable Interrupt (NMI) handlers or TSRs, as interfaces between the power management software and hardware and the rest of the system. These notebooks achieved a level of "compatibility by testing." Once systems had been designed, they had to be extensively tested with many applications to ensure that applications would not clash with power management code. These systems were then prey to any changes or new releases of software. The Intel386 CPU architecture is established as the basis for today's operating systems and applications. The protected mode programs such as Windows 3.0, UNIX and the various DOS extenders make the traditional power management approaches even more difficult to implement.

When Intel started assessing portable computing requirements, it soon became apparent that the Intel386 CPU architecture itself had to be extended with a system management mode (SMM). Only with SMM can a system achieve "compatibility by design" for all operating systems and applications, including those that use the Intel386 protected modes.

The SL architecture's SMM enables the CPU and peripheral controller to combine the power management elements, such as static CPU and system event timers, in a complete solution. Vendors can fine-tune power management for their boxes. The whole system tradeoff between performance, latency, weight, and battery life can be also be improved. Once implemented in the BIOS, the system performance is enhanced and unaffected by operating systems, applications, and the way the user has set up his or her machine. The thousands of PC compatibility features have been resolved with the transparent power management functions such as suspend/resume and are offered as a foundation whereby PC vendors add to their own special differentiation for a new class of notebook computers.

#### **Notebook Computer Functions**

The next generation of notebook PCs must support power management functions and special utilities for on-the-road operation. They must be simple to operate, automatic if possible, and foolproof if they are to change the behavior of the computer user. To maintain strict PC compatibility and utilize the huge base of existing PC software, these operations must run independently from an application or operating system. The SMM architecture is ideally suited to these tasks. It allows these functions to be implemented in such a way that they are robust, yet transparent to the user.

#### Suspend/Resume

After we had settled on our SMM design, the implementation of suspend/resume became much easier. To understand the power of suspend/resume, imagine a notebook computer user in an airport, working on his or her expense or trip report and account database while waiting for a plane. The multitasking Intel386 operating system is finely tuned, and provides the necessary functions to perform these multiple tasks. When the flight is called, the user closes the lid of his or her notebook, without saving the work or exiting the applications. A suspend request is immediately initiated, causing a graceful shutdown of the machine that leaves it in a low power state which could last 30 days or more. After dinner on the plane, the user opens the notebook lid, and the machine instantly resumes its state prior to the initiation of the suspend (perhaps with the cursor blinking in the "\$" column of the expense report spreadsheet).

The scenario just discussed presents the SL architecture's suspend/resume functionality in a nutshell. We designed this function to be very simple to initiate, highly reliable, and very fast. We knew that if there were a 10-second delay for the suspend to take effect, the function would seldom be used.

#### **Global Standby**

Another important feature of the SL power management architecture is global standby. In global standby mode, a machine that is left idle for a programmable period of time will shut down to a lower-powered state. The idle state is detected when the global standby timer count expires. This counter is reset by system events. When the time-out occurs, a system management interrupt (SMI) is generated and the CPU is placed in SMM. Power management routines running in SMM then turn off the display, power down the disk drives, and stop the CPU clock. Code execution also stops in the middle of the power management routine. The system is restarted by a STOP\_BREAK event (similar to system events). The CPU clock is then restarted and power management code continues to execute, restoring power to the screen and disk drives and executing the RSM instruction to exit SMM. We estimated that this mode would save up to 60 percent of the total system power.

While the system is in global standby, the Auto Power off timer can optionally be used to put the machine into the lower-power suspend state. When this timer expires during a standby, the CPU clock is restored and an SMI is generated to initiate the suspend sequence.

#### **Detailed Design**

After defining the high-level architecture, our engineering team then had to engage in the internal design. We had to learn all about the PC platform—compatibility, function, performance, and how different companies had extended the architecture over the past 10 years.

We approached compatibility from two different directions: ISA-bus compatibility for the more than 1000 plug-in adapters, and software compatibility for the more than 25,000 available software packages. We knew a lot about the original IBM AT-339 design; most of the components were designed by Intel, and we had accurate schematic and BIOS information. The biggest challenges facing us included third-party vendors' usage of the PC and how they had extended the platform. To aid us in our ISA-bus design, we decided to create a "compatibility bible." Six specs had been given to us by various customers, and we also had the IEEE-996 document. The "bible" was created by performing extensive experiments on ISA hardware and comparing them to the specifications and our detailed knowledge of the inner working of the devices. The programming model was developed in a similar way. Our X86 knowledge gave us most of the information required. This, along with customer input and many experiments with applications, enabled us to create the specifications for our part.

After defining the Intel386 SL architecture, we started to evaluate the BIOS. To separate the initial powering up of hardware from new software, we made the chips power up in a default state so that a regular AT BIOS would boot and work. After that, the configuration and power management software could be brought up. We worked closely with our partner, a major BIOS vendor, and with internal programming teams to validate our defined programming model.

The silicon development teams were also very active. One of these teams, in charge of "full-chip" simulation, was developing the capability to simulate the entire PC platform on our models. The team had to generate models of all the PC peripherals and system behavior. Their efforts enabled us to boot DOS on the silicon model. This involved executing the system configuration, POST tests, system initialization, and BIOS calls. All of this ran on the low-level transistor model of our product—a task which took our largest mainframe approximately two weeks to execute.

#### **First Silicon and Debug**

After 18 months of definition and development, we finally produced the first silicon. This was a very exciting time—would our baby work? It took us six days to get to the point of booting DOS. The part was functional! We were able to get our test board to work with the first silicon—a miracle! Working on one platform with some applications is one thing, but getting to a full "worst-case" design and PC compatibility is another. At the Intel386 SL Microprocessor introduction in October 1990, we were able to demonstrate a fully transparent

#### 16 Chapter Two

suspend/resume sequence while the board, with less than 10 components, was running in enhanced 386 mode. We had met our challenge.

#### **First Customer Shipment**

Before our first partner could announce and ship product, we had to prove that the Intel386 SL CPU was compatible, competitive, and functional, and had met the performance and power expectations in a mass-produced notebook product. We also had to prove that it could run any of the 25,000 PC applications in any combination at any time of day. This took some time. For all of the engineers, this was an important time, and we gained significant PC experience.

#### **General Marketing of the Product**

After the introduction of our first partner's notebook PC, we started to engage with more customers. The Intel386 SL CPU worked, and we had proved that we could resolve some of the system and compatibility issues. The power management architecture was a success. We made some changes to the parts to support the needs of the rest of the PC industry: increasing the operating frequency to 25 MHz and adding more flexible configurations so that the whole customer base could implement their own specific features.

#### The Success of the SMM Architecture

The power management architecture was working, but we needed to separate power management from the system management mode (SMM). (Power management is just one of the applications for SMM.) Customers were beginning to use SMM for some other applications. A longer-term strategy and road map for SMM was thus required.

To distinguish SMM from power management facilities in the Intel386 SL processor, we decided to make it the sixth operating mode of the extended Intel386 architecture. This mode will be implemented in all future X86-compatible CPUs produced at Intel.

#### Support for Product-Specific Functions

A common request from our customers is to give them the ability to differentiate their boxes. The Intel SL architecture provides this support with more than 120 configuration registers and the flexibility of SMM. There are many, very different, Intel386 SL CPU-based systems in the market today. The features and functions of the SL architecture that will be used in a product are up to the system designer. He or she has to consider several tradeoffs: performance, system weight, battery life, features, and peripherals. What the SL architecture offers to all of these designers is the base of a compatible PC with many extensions and hooks. Product design teams can spend their resources on these new differentiating features and can rely on the Intel386 SL CPU to provide the base-compatible platform for all of the available PC applications.

#### **Future SL Generations**

After completing the first generation of SL products, we started to plan for future products. We believe that the SL SMM and power management architecture and system partitioning will be good for the next three or four generations of products.

Performance and battery life are two major areas identified for new development. Intel had solutions to both the problems in the next X86 core, as well as the ability to reduce the core voltage to 3.3 volts. With these two mechanisms alone, we estimated that we could easily double the system performance and halve the power consumption. The next X86 core is easily implemented and keeps the programming interface the same. This keeps binary compatibility with SL BIOS and power management software. The only changes required are in the system configuration and setup.

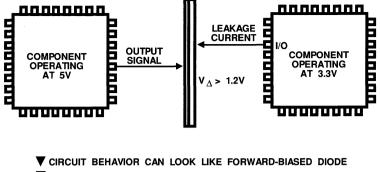

Reducing the supply voltage in CMOS technology has a square proportionality to power. Going from 5 volts to 3.3 volts results in a 60 percent power saving. The speed of the silicon switching is proportional to the supply voltage. Both of these facts provided Intel with challenges, including performance to be reclaimed, reliability issues, and reduced system noise margins. All of this requires us to tune the silicon process.

In the spring of 1992, Intel announced the low-voltage Intel386 SL CPU which uses a hybrid voltage design in which any circuit that operates above 8 MHz runs at 3.3 volts, and the rest of the circuitry runs at 5 volts. In the fall of 1992, Intel announced the Intel486 SL CPU that combines an Intel486 SX core with 3.3-volt operation.

#### Conclusion

Working on the design and development of the SL architecture was gratifying for many reasons. The most gratifying feeling for us derives from witnessing the success of Intel386 SL-based products and the great strides that have been taken toward making portable computers more useful, more convenient, and more reliable.

# **SL Architecture Overview**

The Intel SL architecture is the first microprocessor architecture to be designed specifically for notebook computer and hand-held computer applications. It was designed with two goals in mind:

- To capture as many of the components required to make an ISA-compatible PC as possible on a few VLSI chips

- To provide power management tools that work transparently to the operating system and applications programs and that give designers complete control over power usage by system components

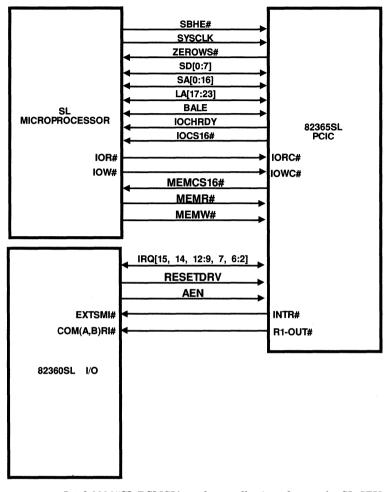

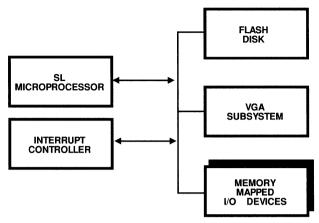

Figure 3.1 shows a block diagram of an ISA-compatible PC, implemented with the SL architecture. As this diagram illustrates, all you need to build a complete PC in addition to the SL CPU and 82360SL I/O are memory chips, a VGA controller, a floppy disk controller, a keyboard controller, an optional math coprocessor (MCP), and buffers for optional I/O peripherals, such as a flash disk.

The following sections describe the internal design of the Intel486 SL CPU, Intel386 SL CPU and the 82360SL peripheral controller. It also describes the various buses in the system.

# Intel386 SL CPU and Intel486 SL CPU

# Intel386 SL microprocessor

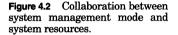

The Intel386 SL microprocessor is the first processor for portable computers. The memory controller inside the Intel386 SL CPU contains all the control and interface logic to drive a 20-Mbyte DRAM memory system or a 32-Mbyte SRAM memory system and a cache controller to maximize performance. The memory controller supports common memory options such as shadowing and memory roll-over. Also, the on-chip hardware implements LIM 4.0-compatible expanded memory system (EMS). (See Fig. 3.2.)

Figure 3.1 Block diagram of a portable PC based on the Intel SL architecture.

The Intel386 SL microprocessor also contains bus drivers and control circuitry for two expansion bus interfaces: Industry Standard Architecture (ISA) bus interface and Peripheral Interface (PI) bus interface. The PI-bus interface shares the same address and data buses with the ISA-bus interface but has a much higher performance control interface. Bus cycles can be programmed to be directed to either the PI-bus interface or the ISA-bus interface.

#### Low voltage Intel386 SL microprocessor

The low-voltage Intel386 SL microprocessor with "flexible voltage" operation combines a selectable 3.3- or 5-volt peripheral interface with a 3.3-volt static CPU and a 3.3-volt memory interface. The selectable voltage feature allows for pin-for-pin compatibility with both 3.3- and 5-volt peripherals, eliminating the translation logic typically necessary to connect 5-volt components to a 3.3-volt CPU. In addition, the "selectable voltage" operation is 100 percent software-compatible with the standard Intel386 SL processor.

#### Hardware implementation

The Intel386 SL Microprocessor SL SuperSet is manufactured using Intel's CHMOS IV process, combining the high performance of HMOS with the low power dissipation of CMOS. Double metal layers and 1.0-micron lithography allow a chip density of more than one million transistors. The Intel386 SL

Figure 3.2 Main building blocks of the Intel386 SL microprocessor.

microprocessor is available in a 196-pin plastic Quad Flat Package (PQFP) or 227 lead ceramic Land-Grid Array (LGA) package, a package that is designed for easy upgrade. The 82360SL I/O is available in 196-pin PQFP package and 208-pin SQFP package.

#### Intel486 SL microprocessor

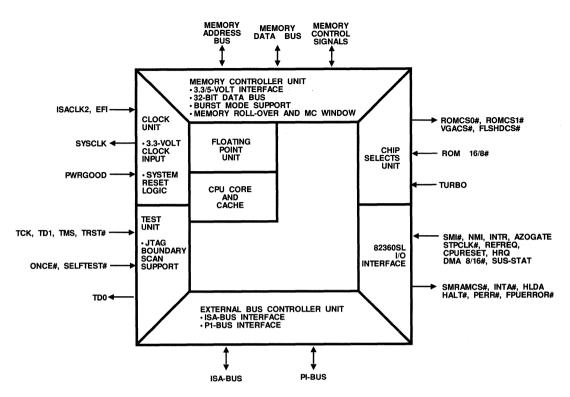

The Intel486 SL microprocessor is the newest generation of microprocessor for notebook computers, and offers the highest performance and lowest power consumption. Building on the success of the SL architecture, the Intel486 SL microprocessor offers 3.3-volt CPU core and memory interface. (See Fig. 3.3.) It is 100 percent binary compatible with the Intel386 SL microprocessor. The Intel486 SL CPU provides higher performance by virtue of the reduced clocks per instruction (CPIs) associated with the Intel486 CPU. The Intel486 SL CPU integrates a fully static Intel486 microprocessor core, cache controller with 8 Kbytes of internal cache, Floating Point Unit (FPU), on-board memory controller, and external bus controller. The higher integration allows the system designer to create a smaller notebook computer.

The Intel486 SL CPU with FPU provides both integer and floating-point performance improvements over the Intel386 SL CPU and Intel387 SL mobile math coprocessor combination. Intel486 SL CPU floating-point performance

Figure 3.3 Main building blocks of the Intel486 SL microprocessor.

will offer an increase of between two to three times the performance of the Intel386 SL microprocessor and Intel387 SL mobile math coprocessor combination at equivalent clock speeds.

Power consumption is further reduced by using a lower supply voltage (3.3volt) for the majority of the Intel486 SL CPU internal logic. The on-board DRAM buffers may be selectively powered to support either 3.3- or 5-volt DRAMs. The ISA-bus and 82360SL peripheral I/O interfaces are powered by 5volt. The 5-volt interface to the ISA-bus and 82360SL ensures compatibility of the Intel486 SL processor with existing ISA-bus peripherals and I/O devices. The Intel486 SL processor further reduces system power by minimizing offchip bus cycles when executing from the cache or floating-point unit.

BIOS and System Setup software written for the Intel386 SL microprocessor may be easily modified to support the new DRAM memory configurations without impacting applications software. The other existing Intel386 SL microprocessor components are supported without any required modifications. The new Intel486SL processor features are transparent to applications software running in existing Intel386 SL microprocessor systems.

#### Software compatibility

The Intel386 SL microprocessor is binary code compatible with all the Intel386 microprocessors. All the existing programs that are running on an Intel386

ISA PC will run on an Intel386 SL CPU-based machine without recompilation or reassembly. For programs such as power management software, the processor provides system management mode, which establishes a protected environment transparent to the operating systems and applications software. In this environment, applications software can take advantage of the transparency of system management mode without having to worry about interference from operating system and applications software that are running on the system.

# Differences between the Intel386 SL microprocessor and the Intel386 SX microprocessor

The best way to describe the differences between the Intel386 SX CPU and the Intel386 SL processor is that the Intel386 SX processor is a subset of the Intel386 SL processor. The following is a list of features that are supported by the Intel386 SL CPU only.

- The Intel386 SL processor provides direct support for DRAMs and SRAMs.

- The maximum physical memory address space is 32 Mbytes on the Intel386 SL processor.

- Direct hardware support compatible with LIM EMS 4.0 is included in the Intel386 SL processor.

- Memory options such as EPROM shadowing and memory roll-over are supported by the Intel386 SL processor.

- System management mode is supported by the Intel386 SL processor.

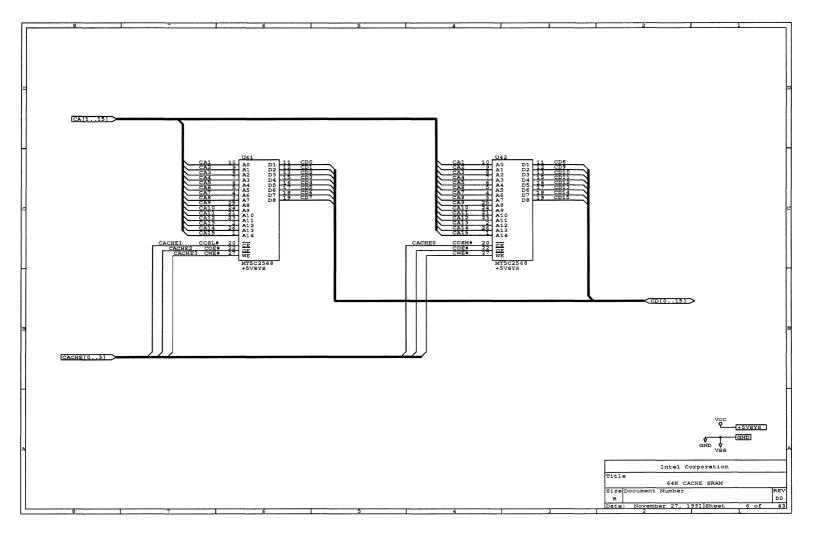

- A cache controller is embedded inside the Intel386 SL processor which can support 16, 32, and 64 Kbytes of cache.

- ISA-bus and PI-bus peripherals can interface directly to the Intel386 SL processor.

- The Intel386 SL CPU is fully static and the clock can be stopped whenever the HLT instruction is executed or *after an I/O read to the* STP\_CLK *register*.

- The Intel386 SL CPU supports suspend operation.

- In addition to the component ID, a signature register is available for software to identify CPU type and stepping information.

# Differences between the Intel486 SL CPU and the Intel386 SL CPU

The Intel486 SL CPU and the Intel386 SL CPU were designed to provide the highest level of integration and performance at the lowest possible level of power consumption. The following are the more important features of the CPU:

• It has an integrated memory controller. The Intel386 SL CPU's on-chip memory management unit supports DRAMs and SRAMs directly and provides a maximum physical address space of 32 Mbytes. The Intel486 SL CPU's on-chip memory controller supports up to 64 Mbytes of physical memory. (SRAM is not supported.)

- Support for LIM EMS 4.0 is provided in the Intel386 SL CPU (not in the Intel486 SL CPU).

- The SMM is provided to allow execution of power management and other system management software to be isolated from the operating system and application programs.

- The memory controller supports EPROM shadowing and memory roll-over.

- An embedded cache controller supports a 16-, 32-, and 64-Kbyte-cache (but not in the Intel486 SL CPU, where the cache is internal to the CPU and is fixed at 8 Kbytes).

- ISA bus and PI bus (unique to the SL CPU) provide a direct interface between the CPU and peripherals.

- Suspend/resume operation is supported (allowing the system to be powered down and powered up again without losing the state of the machine).

- The SL CPUs are fully static, allowing software to stop the CPU clock without losing the state of the machine.

In addition to the core CPU, the SL CPU consists of five main building blocks: the internal bus unit, the on-board memory controller unit, the external bus unit, the cache unit (not in the Intel486 core CPU), and the clock unit.

# Core CPU

The core CPU of the Intel486 SL processor is based on the core CPU of the Intel486 SX processor, and the core CPU of the Intel386 SL is based on the core of the Intel386 SX processor. The Intel486 SL CPU and the Intel386 SL CPU provide the same register set and instruction set as in the stand-alone Intel486 SX CPU and Intel386 SX CPU. Like the Intel486 SX CPU, the Intel486 SL CPU also has 8 Kbytes of internal cache. Any program that runs on the Intel486 SX CPU will run on the Intel486 SL CPU and likewise for the Intel386 SX CPU.

#### Internal bus unit

The internal bus unit is the router between the CPU core and the other four CPU units. It directs bus cycles to the external bus unit, the cache unit, and the on-board memory controller unit. It uses configuration registers to determine where to send each cycle. These registers control roll-over of memory, the on-board memory limit, the disabling of memory in 64-Kbyte segments in the bottom 1-Mbyte memory address space, BIOS shadowing, and caching of memory-mapped I/O address space.

Normally the internal bus controller sends a bus cycle either to the external bus unit (ISA-bus or PI-bus) or the on-board memory controller unit (for onboard memory), and determines whether the cycle should be cached. All cycles to on-board memory are directed to the on-board memory controller. The internal bus unit determines the size of the on-board memory space by inspecting the OMLCR register. This register specifies the on-board memory limit in 512Kbyte blocks (the minimum block of memory that can be addressed in a single bank by the on-board memory controller unit). A value of zero for the limit indicates that accesses above 512 Kbytes are to off-board memory.

### Clock unit

The clock unit provides clock signals and clock control for the CPU. The clock source for the clock units comes from two oscillator inputs: the External Frequency Input (EFI) and the ISA clock (ISACLK2). The EFI provides the basis for the CPU clock (CPUCLK). This clock has a maximum rate of EFI/2, but can be programmed for slower speeds or stopped. When the clock is stopped, the static design of the CPU allows it to maintain its state without being refreshed. The programmable MCP clock (NPXCLK) is derived from the CPUCLK.

The ISACLK2 provides the basis for the system clock (SYSCLK) that clocks the system bus. The SYSCLK is an ISA-type clock and is required to be 8 MHz in SL CPU-based systems.

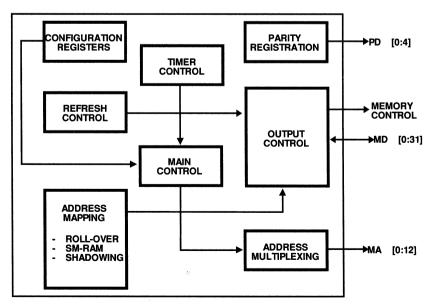

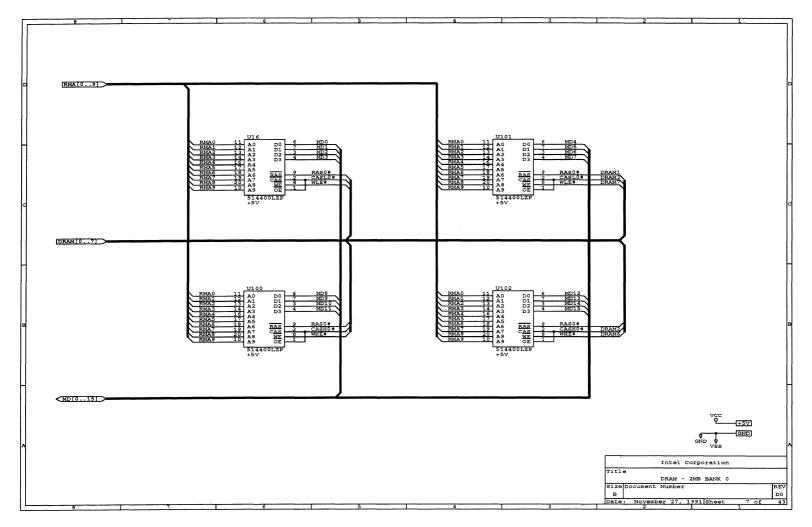

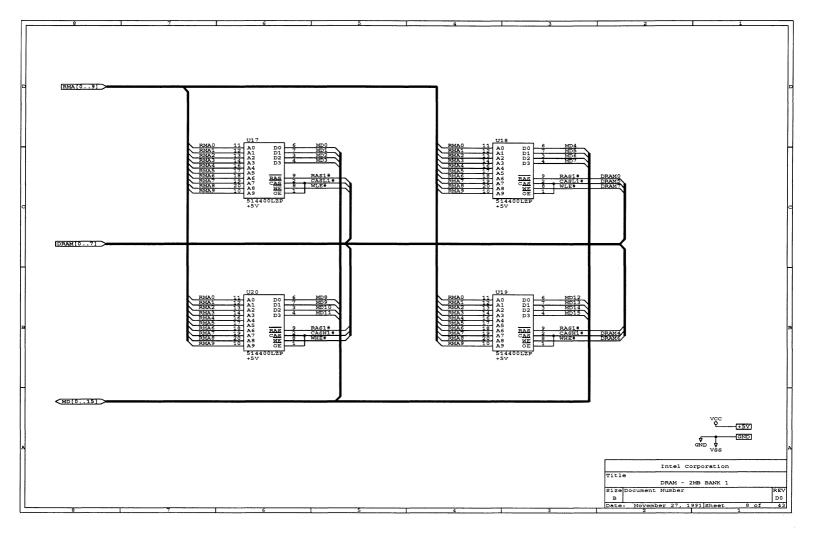

## **On-board memory controller unit**

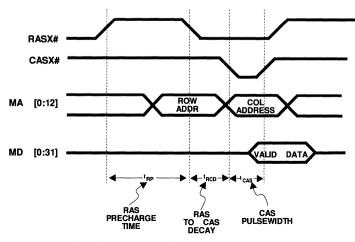

The on-board memory controller unit supports both DRAM and SRAM (Intel386 SL CPU only) subsystems. When configured for DRAM mode, the DRAM controller inside the memory controller unit controls how the CPU interfaces to the DRAMs. The prime functions of the DRAM controller are address and refresh generation. The refresh logic inside the memory controller provides refresh to the DRAMs during normal operation as well as during suspend. Please note that ISA-bus refresh is not performed by the memory controller.

When programmed for SRAM mode, the SRAM controller inside the Intel386 SL CPU controls the interface between the processor and the SRAMs. The SRAM controller is responsible for generating the control signals for the data transceivers and wait state to support SRAM of different speeds. The memory controller works in conjunction with the cache controller. When the cache controller is enabled, the memory controller is activated only during CPU write cycles or cache-miss read cycles to conserve power. When the cache controller is disabled, all memory accesses occur to the memory controller.

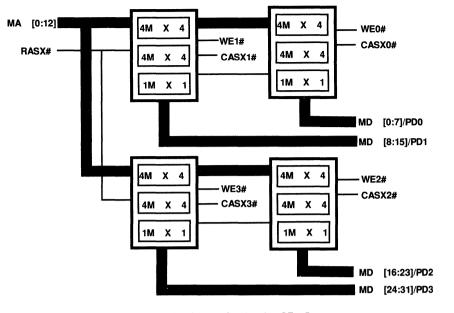

#### **On-board memory bus**

Addresses, data, and memory control signals are transmitted on the on-board memory bus. This bus supports DRAMs or SRAMs. In the Intel386 SL processor, the address bus for the DRAM interface is multiplexed. The address bus and data bus for the SRAM interface are multiplexed together. The DRAM and SRAM interfaces share the CMUX interface (CMUX[0:13]) in the Intel386SL processor. The definitions of the CMUX signals are described in Table 3.1.

## Cache controller unit

The cache controller unit (Intel386 SL CPU only) consists of the cache interface module and the Intel387SL math coprocessor (MCP) interface module.

| Signal name | DRAM mode | SRAM mode |

|-------------|-----------|-----------|

| CMUX0       | CASL3#    | DIR       |

| CMUX1       | CASH3#    | LE        |

| CMUX2       | CASL2#    | DEN3#     |

| CMUX3       | CASH2#    | DEN2#     |

| CMUX4       | CASL1#    | DEN1#     |

| CMUX5       | CASH1#    | DEN1#     |

| CMUX6       | CASL0#    | DEN0#     |

| CMUX7       | CASH0#    | DEN0#     |

| CMUX8       | RAS3#     | CE3#      |

| CMUX9       | RAS2#     | CE2#      |

| CMUX10      | RAS1#     | CE1#      |

| CMUX11      | RAS0#     | CE0#      |

| CMUX12      | PARL      | OLE#      |

| CMUX13      | PARH      | OHE#      |

TABLE 3.1 On-Board Memory Bus Signals for Intel386 SL CPU

The cache interface module controls how the cache controller interfaces to the cache SRAM. The 8 Kbytes of cache inside the Intel486 SL CPU is part of the CPU core.

#### Cache memory bus

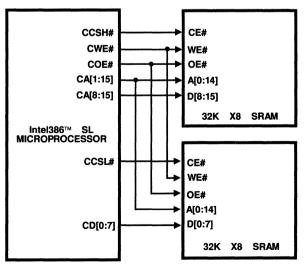

The cache memory bus is a 16-bit bus which can address up to 64 Kbytes of cache memory. The bus interface consists of data and control signals. The control signals include Cache Write Enable (CWE#), Cache Output Enable (COE#), Cache Chip Select High (CCSH#), and Cache Chip Select Low (CCSL#).

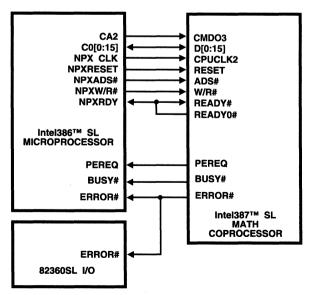

#### Math coprocessor (MCP) interface module

The MCP interface module provides an interface between the CPU core and the MCP. This interface includes a register that allows the CPU to slow or stop the clock to the MCP if a static MCP such as the Intel387 SL is used.

#### MCP bus

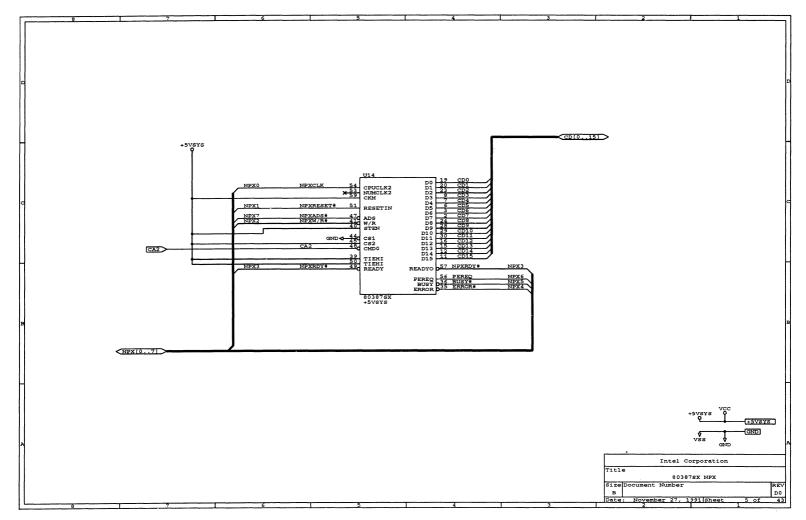

The MCP bus provides a direct path between the MCP and the CPU core. It shares the same address bus and data bus with the cache memory bus. Eight additional control and clock signals are provided in the MCP bus: BUSY#, ERROR#, NPXRDY#, NPXADS#, NPXW/R#, NPXRESET, NPXCLK, and PEREQ.

## External bus unit

The external bus unit consists of the system bus (ISA-bus) controller, the PIbus controller, and byte-swapping logic for the data bus. The external bus interface is programmable.

#### System bus

The system bus is a 16-bit parallel memory and I/O bus. It is compatible with the standard ISA bus found in ISA-compatible PCs, and conforms with the IEEE P996 standard. Unlike some implementations of the ISA bus (such as the Intel386 SL CPU), the drive capability of the system bus is programmable in the Intel486 SL CPU. The ISA-bus clock speed is fixed at 8 MHz to maintain compatibility with existing ISA-bus peripherals.

The system bus is an extension of the CPU's local processor bus, with a maximum memory address space of 16 Mbytes (24 address lines). Memory accesses above 16 Mbytes wrap around to the beginning of memory.

Three buses are derived from the system bus: the peripheral interface bus (PI bus), the X bus, and the expansion bus.

#### PI bus

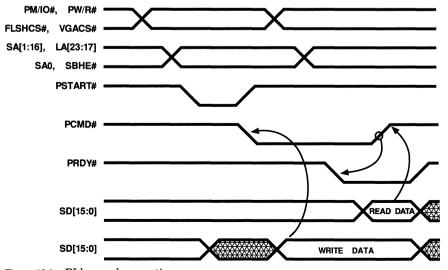

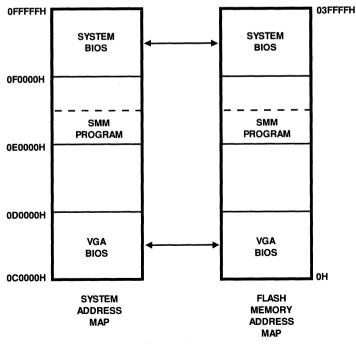

The PI bus is a high-speed, asynchronous bus for interfacing with peripherals such as a flash disk or a high-speed VGA graphics frame memory. It is like a decoded local bus and is derived from the ISA bus. The PI bus shares address and data signals of the system bus. It also provides special support for a VGA graphics controller interface and a flash disk interface. Chapter 12 contains a thorough description of PI bus.

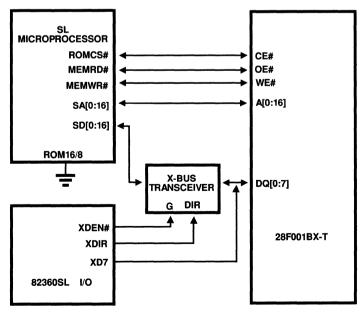

# X bus

The X bus is a buffered version of the system bus to support devices such as the keyboard controller, floppy disk controller, flash BIOS, external real-time clock, and EPROMs. The buffers are always enabled, with the direction of data transmission controlled by the XDIR signal. The X bus provides an 8-bit data bus (16-bit for 16-bit flash BIOS) and a 17-bit address bus. High or low system bus data bytes can be directed to the X-bus data bus through byte swapping.

#### **Expansion** bus

The expansion bus is an extension of the system bus to support ISA-bus expansion slots in the system. This bus provides the complete set of signals commonly found in the ISA bus of an ISA-compatible PC. It can support any standard ISA-bus card, including memory boards, video controllers, fax/ modems, and ethernet interface boards. The bus clock rate is fixed at 8 MHz by the SYSCLK signal. The 82360SL also provides a separate OSC clock signal for this bus.

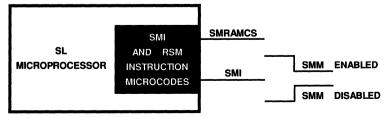

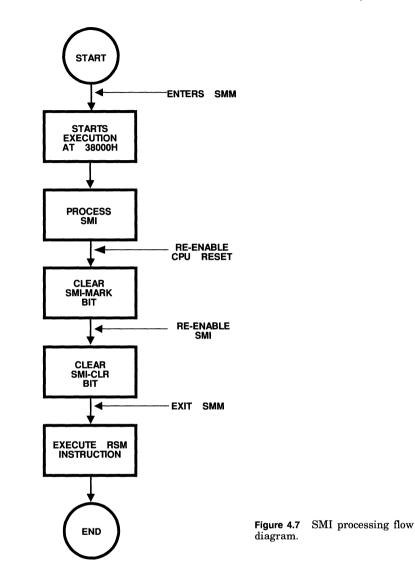

#### System management mode (SMM)

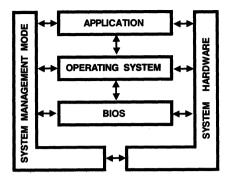

The SL architecture introduced a new operating mode for microprocessors: the system management mode (SMM). The SMM provides a separate execution environment for system and power management routines that is transparent to the operating system and application programs. A special system manage-

ment interrupt (SMI) activates the SMM. Upon receipt of an SMI, the CPU temporarily suspends execution of its current operating system or application program, enters the SMM, and begins executing SMM routines located in a dedicated System Management RAM (SMRAM) address space. When the CPU exits the SMM (with an RSM) instruction, the CPU resumes executing the operating system or application program where it left off when the SMI occurred.

The SMM is the main component in the various power management facilities that the SL CPU and 82360SL provide. It is also available to designers to handle other system management tasks when it is important to prevent conflict with the operating system or application program. The SMM is described in detail in Chap. 4.

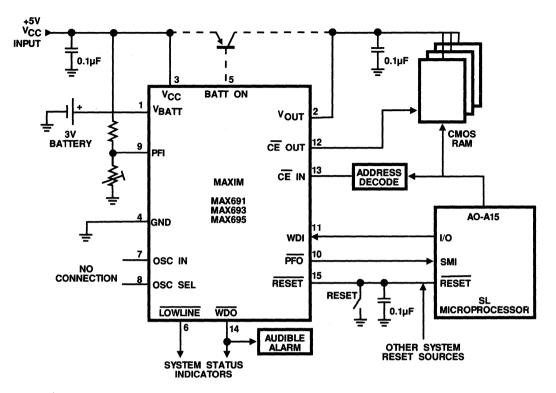

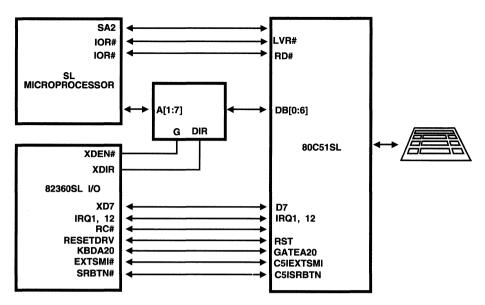

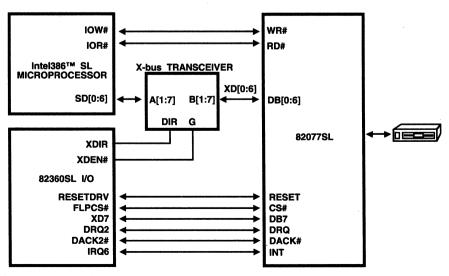

# 82360SL Peripheral Controller

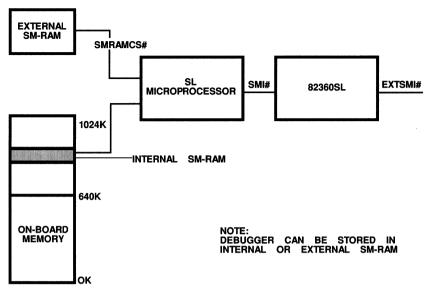

The 82360SL peripheral controller contains dedicated logic to interface with the Intel486 SL or Intel386 SL CPU and a complete set of standard ISAcompatible peripheral controllers, including two serial port controllers, one parallel port, two programmable interrupt timers, two interrupt controllers, and two DMA controllers. It also provides interfaces for a keyboard controller, a floppy drive controller, and an IDE hard disk. The software and hardware interfaces to the peripherals embedded inside the 82360SL are identical to those for the discrete components commonly found in an ISA system. (See Fig. 3.4.)

## Power management hardware

One of the highlights of the 82360SL is its comprehensive set of power management features. The power management facilities are tightly coupled with SMM of the SL CPU to provide a robust and efficient mechanism for managing the power consumption of a battery-powered PC. The power management mechanism includes facilities for powering down idle peripheral devices, slowing or stopping the clock to system components, and suspend/resume operation. Chapters 5, 6, and 7 describe the power management features of the SL CPU in detail.

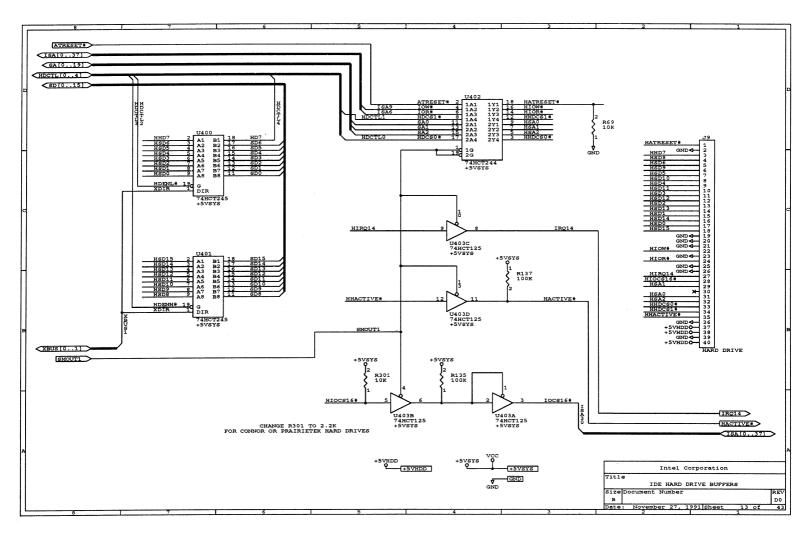

## **IDE** interface

The IDE (Integrated Drive Electronics) interface is a simple, hard disk drive interface that consists of 40 signals. This interface allows an IDE hard disk drive to be connected to the system with a simple adapter card containing a minimum of logic. The IDE interface uses a register-based command status protocol standardized by the DOS operating system and BIOS.

The IDE interface is derived from the system bus; therefore, bus cycles for the IDE interface are the same as the system bus. For example, an 8-bit IDE access requires 6 SYSCLKS, and 16-bit IDE access requires 3 SYSCLKS. Zero wait state operation is not supported on the IDE interface. The IDE bus shares

Figure 3.4 Main building blocks of the 82360 SL.

some signal lines with the system bus, plus it has several signals that are unique to it. Table 3.2 shows the IDE bus signals.

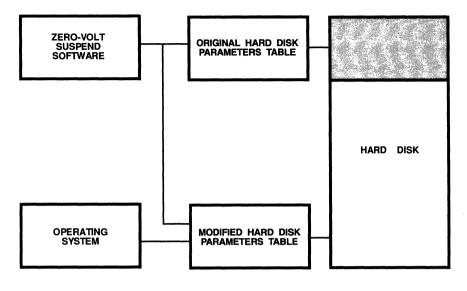

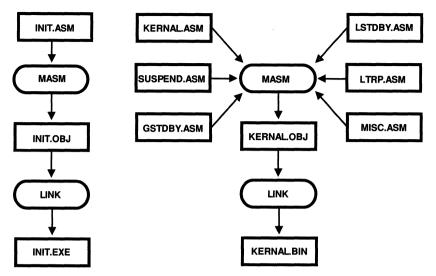

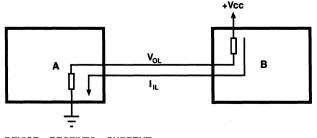

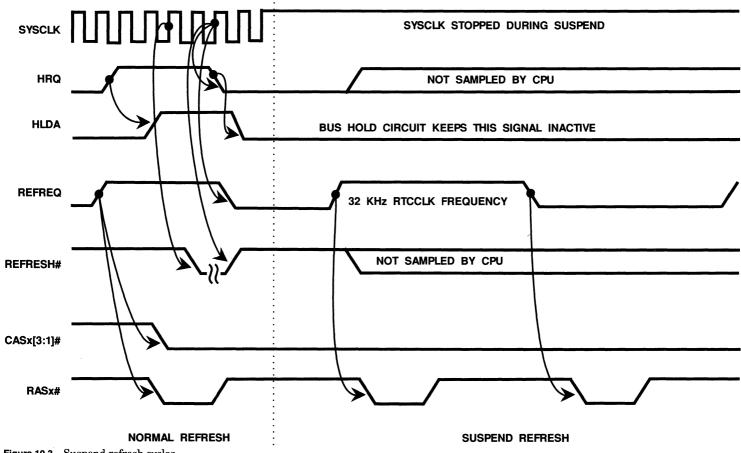

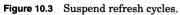

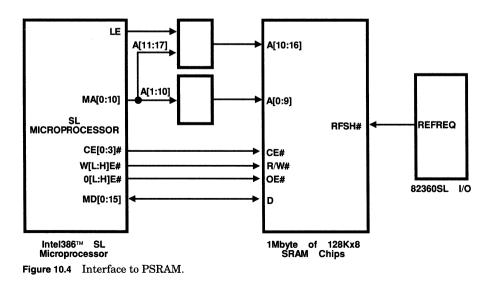

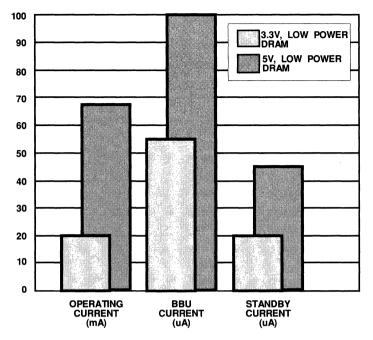

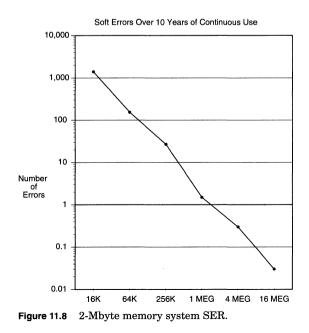

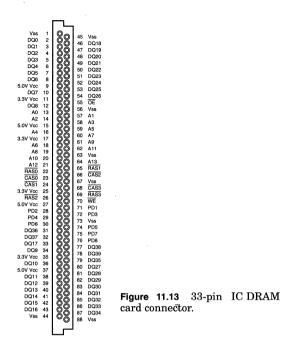

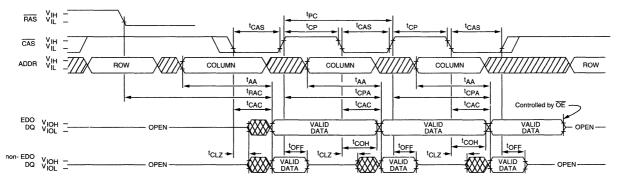

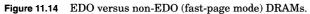

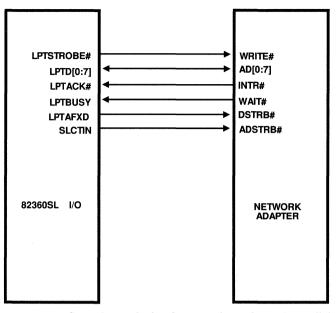

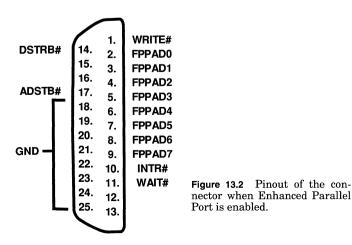

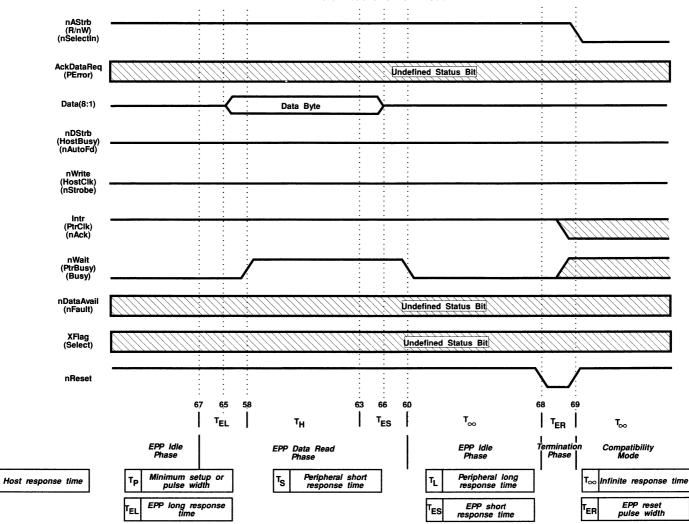

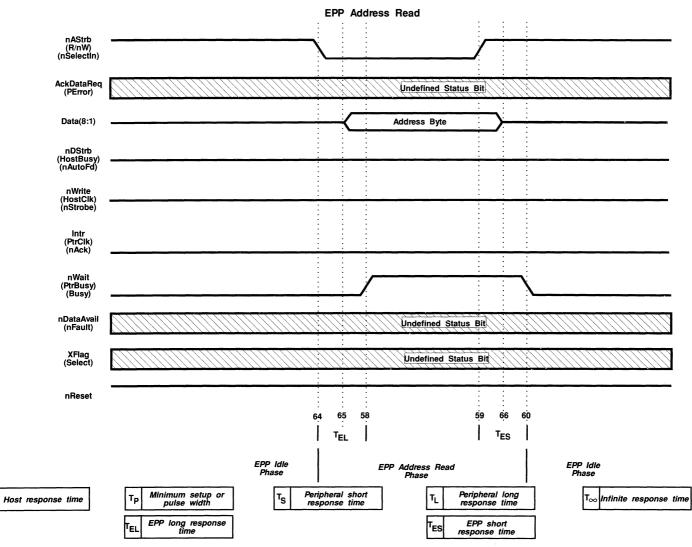

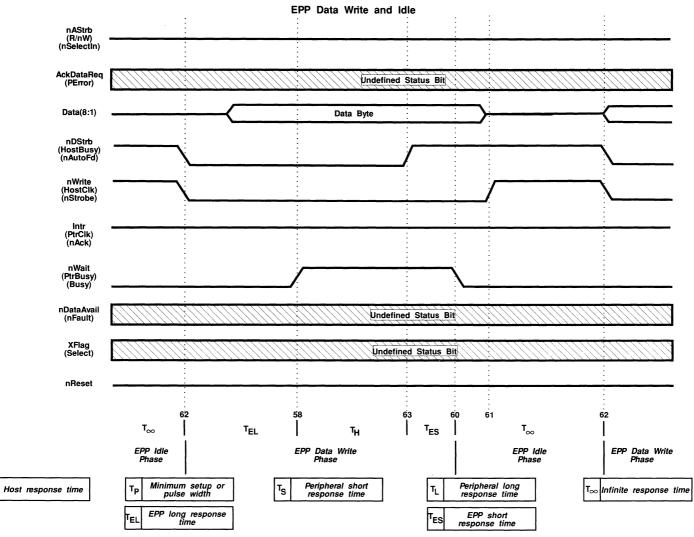

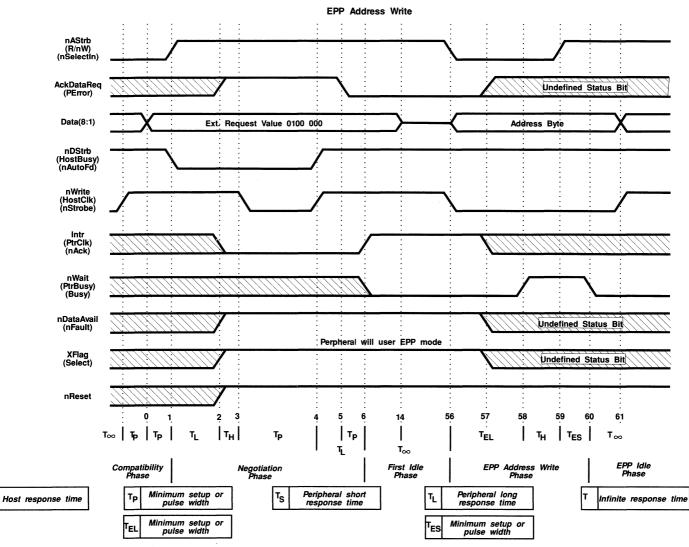

## Parallel and serial ports