© INTEL CORPORATION, 1980

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9 (a) (9). Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

No part of this document may be copies or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and may only be used to identify Intel products:

Library Manager

Megachassis

Micromap

Intellec

**iSBC**

MCS

| 1            |   |  |

|--------------|---|--|

| ICE          |   |  |

| ICS          |   |  |

| im           |   |  |

| Insite       |   |  |

| Intel        |   |  |

| Intelevisior | 1 |  |

|              |   |  |

Multimodule PROMPT Promware RMX UPI µScope

and the combinations of ICE, iCS, iSBC, MCS or RMX and a numerical suffix.

Additional copies of this or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

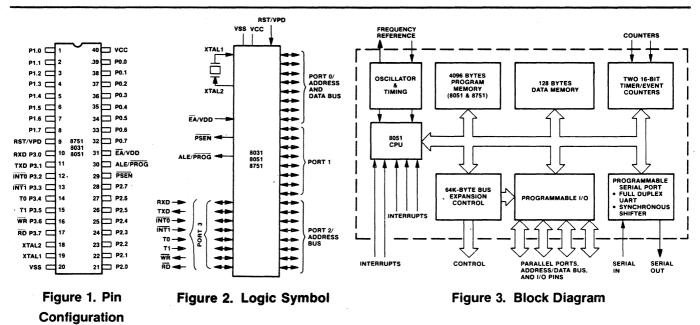

## 8031/8051/8751 SINGLE-COMPONENT 8-BIT MICROCOMPUTER

- 8031 Control Oriented CPU With RAM and I/O

- 8051 An 8031 With Factory Mask- Programmable ROM

- 8751 An 8031 With User Programmable/Erasable EPROM

- 4K x 8 ROM/EPROM

- 128 x 8 RAM

- Four 8-Bit Ports, 32 I/O Lines

- Two 16-Bit Timer/Event Counters

- High-Performance Full-Duplex Serial Channel

- Boolean Processor

- Compatible with MCS-80<sup>™</sup>/MCS-85<sup>™</sup> Peripherals

- External Memory Expandable to 128K

- MCS-48<sup>™</sup> Architecture Enhanced with:

- Non-Paged Jumps

- Direct Addressing

- Four 8-Register Banks

- Stack Depth Up to 128-Bytes

- Multiply, Divide, Subtract, Compare

- Most Instructions Execute in  $1\mu$ s

- 4µs Multiply and Divide

The Intel® 8031/8051/8751 is a stand-alone, high-performance single-chip computer fabricated with Intel's highly-reliable +5 Volt, depletion-load, N-Channel, silicon-gate HMOS technology and packaged in a 40-pin DIP. It provides the hardware features, architectural enhancements and new instructions that are necessary to make it a powerful and cost effective controller for applications requiring up to 64K bytes of program memory and/or up to 64K bytes of data storage.

The 8051/8751 contains a non-volatile 4K x 8 read only program memory; a volatile 128 x 8 read/write data memory; 32 I/O lines; two 16-bit timer/counters; a five-source, two-priority-level, nested interrupt structure; a serial I/O port for either multi-processor communications, I/O expansion, or full duplex UART; and on-chip oscillator and clock circuits. The 8031 is identical, except that it lacks the program memory. For systems that require extra capability, the 8051 can be expanded using standard TTL compatible memories and the byte oriented MCS-80 and MCS-85 peripherals.

The 8051 microcomputer, like its 8048 predecessor, is efficient both as a controller and as an arithmetic processor. The 8051 has extensive facilities for binary and BCD arithmetic and excels in bit-handling capabilities. Efficient use of program memory results from an instruction set consisting of 44% one-byte, 41% two-byte, and 15% three-byte instructions. With a 12 MHz crystal, 58% of the instructions execute in  $l\mu$ s, 40% in  $2\mu$ s and multiply and divide require only  $4\mu$ s. Among the many instructions added to the standard 8048 instruction set are multiply, divide, subtract and compare.

Intel Corporation Assumes No Responsibility for the Use of Any Circuitry Other Than Circuitry Embodied in an Intel Product. No Other Circuit Patent Licenses Are Implied. © INTEL CORPORATION, 1980.

| 8051 Single-Chip                              | Contents   |                                                                  |     |

|-----------------------------------------------|------------|------------------------------------------------------------------|-----|

| Microcomputer                                 | CHAPTER 1  |                                                                  | 1   |

| Architectural Specification                   | 1.0<br>1.1 | Abstract<br>Intel's Complete Line of Single-Chip                 |     |

| and                                           | 1.2        | Microcomputers                                                   | 1   |

| Functional Description                        | 1.2        | Enhancing the 8048 Architecture for the 80's                     | 1   |

|                                               | CHAPTER 2  | ARCHITECTURAL OVERVIEW AND                                       |     |

|                                               |            | FUNCTIONAL DESCRIPTION                                           |     |

|                                               | 2.0<br>2.1 | The 8051 FamilyMacro-view of the 8051 Architecture               |     |

|                                               | 2.1        | 2.1.1 8051 CPU Architecture                                      |     |

|                                               |            | 2.1.2 On-Chip Peripheral Functions                               |     |

|                                               |            | 2.1.2.1 Interrupt System                                         |     |

|                                               |            | 2.1.2.2 I/O Facilities                                           |     |

|                                               |            | 2.1.2.2.1 Open Drain I/O Pins                                    | 4   |

|                                               |            | 2.1.2.2.2 Quasi-Bidirectional<br>I/O Pins                        | ٨   |

|                                               |            | 2.1.2.2.3 Microprocessor Bus                                     |     |

|                                               |            | 2.1.2.3 Timer/Event Counters                                     |     |

|                                               |            | 2.1.2.4 Serial Communications                                    |     |

|                                               | 2.2        | CPU Hardware                                                     |     |

|                                               |            | 2.2.1 Instruction Decoder                                        |     |

|                                               |            | 2.2.2 Program Counter                                            |     |

|                                               |            | 2.2.3.1 Internal Data RAM                                        |     |

|                                               |            | 2.2.3.2 Register Banks                                           | 9   |

|                                               |            | 2.2.3.3 Special Function Registers                               |     |

|                                               |            | 2.2.3.4 A Register                                               |     |

|                                               |            | 2.2.3.6 PSW Register                                             |     |

|                                               |            | 2.2.3.7 Stack Pointer                                            |     |

|                                               |            | 2.2.3.8 Data Pointer                                             | 11  |

|                                               |            | 2.2.4 Arithmetic Section                                         |     |

|                                               |            | 2.2.5 Program Control Section                                    |     |

|                                               |            | 2.2.6 Oscillator and Timing Circuitry<br>2.2.7 Boolean Processor |     |

|                                               | 2.3        | Memory Organization                                              |     |

|                                               | 2.4        | Operand Addressing                                               |     |

|                                               | 2.5        | Data Manipulation                                                |     |

|                                               |            | 2.5.1 Data Transfer Operations                                   |     |

|                                               | •          | 2.5.2 Logic Operations                                           |     |

|                                               | 2.6        | Control Transfer                                                 |     |

|                                               | 2.7        | Instruction Set                                                  | 18  |

|                                               |            | 2.7.1 What the Instruction Set Is                                |     |

|                                               |            | 2.7.2 Organization of the Instruction Set 1                      | 18  |

|                                               |            | 2.7.3 Operand Addressing Modes and<br>Associated Operations      | 21  |

|                                               | 2.8        | Interrupt System                                                 |     |

| · · · · · · · · · · · · · · · · · · ·         |            | 2.8.1 External Interrupts                                        |     |

|                                               |            | 2.8.1.1 Transition-Activated                                     | 1   |

|                                               |            | Interrupts                                                       |     |

| ©Intel Corporation 1980. All rights reserved. | 2.9        | 2.8.1.2 Level-Activated Interrupts2 Ports and I/O Pins           |     |

| and corporation 1000. An fights reserved.     | 2.0        |                                                                  |     |

|                                               |            | AFN-01488A                                                       | -03 |

.

#### CHAPTER 2 ARCHITECTURAL OVERVIEW AND FUNCTIONAL DESCRIPTION (Continued)

| Accessing External Memory 25            |

|-----------------------------------------|

| 2.10.1 Operation of Ports               |

| 2.10.2 Bus Cycle Timing                 |

| Timer/Counter                           |

| 2.11.1 T/C Mode Selection               |

| 2.11.2 Configuring the T/C Input        |

| 2.11.3 T/C Operation 29                 |

| 2.11.4 Reading and Reloading the T/C 29 |

| Serial Channel 29                       |

| 2.12.1 Serial Port Control Register and |

| Serial Data Registers                   |

| 2.12.2 Operating Modes                  |

| 2.12.2.1 Operating Mode 0 31            |

| 2.12.2.2 Operating Modes 1              |

| through 3 32                            |

| 2.12.3 The Serial Frame                 |

| 2.12.4 Transmission Rate Generation 32  |

| 2.12.5 UART Message Error Conditions 33 |

| External Interface 33                   |

| 2.13.1 Processor Reset and              |

| Initialization                          |

| 2.13.2 Power Down Operation of          |

| Internal RAM 33                         |

| EPROM Programming                       |

| The 8051 as an Evolution of the 8048 34 |

| Development System and Software         |

| Support                                 |

| 8051 Pin Description                    |

| Instruction Set Summary 37              |

|                                         |

AFN-01488A-04

## **1.0 ABSTRACT**

The 8031, 8051, and 8751 are the latest additions to Intel's line of single-chip microcomputers. The CPU architecture and on-chip peripheral functions of the 8051 are described in this document. A user familiar with the MCS-48 family should be able to evaluate and design-in the 8051 using the information included herein.

A detailed description of the hardware required to expand the 8051 with more program memory, data memory, I/O, specialized peripherals and into multiprocessor configurations is described in the 8051 Family User's Manual.

## 1.1 INTEL'S COMPLETE LINE OF SINGLE-CHIP MICROCOMPUTERS

In 1976 Intel introduced the 8748 microcomputer. This marked the first time in history that technology permitted a complete 8-bit computer to be fabricated on a single silicon die. This single chip can control a limitless variety of products ranging from appliances to automobiles to computer terminals.

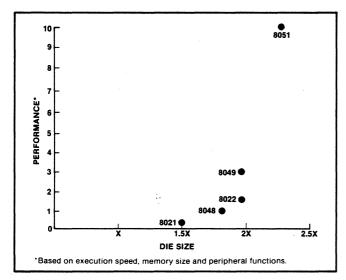

Since 1976 Intel has offered products for the full range of single-chip microcomputer applications by pushing the 8048's architecture in several directions. The 8049 ran nearly twice as fast as the 8748/8048 while doubling the amount of on-chip program memory and data memory. Applications requiring solely external program memory were satisfied with the 8035 and 8039. Cost sensitive and less I/O intensive applications incorporated the 8021 which executed a subset of the 8048's instruction set at a slower speed. Finally, the 8022 integrated an 8-bit A/D converter onto the 8021 die to allow the chip to interface directly to a world in which most signals are analog. Figure 1.1 positions these products on a performance versus die-size curve.

Now, thanks to the density of HMOS, technology has once again permitted the birth of a microcomputer with performance to leap into new product areas. The 8051 achieves a 10X function/speed improvement over the 8048 by packing 60,000 transistors onto a die 230 mils square.

The 8051 family addresses the high-end of the single-chip computer market. It is the highest performance microcomputer family in the world and out-performs all microprocessors and microcomputers in control oriented applications. It offers an upward compatible growth path for 8048 users with ten times the power of the 8048 as shown in Table 1.1.

- 4X Program Memory (4k Bytes)

- 2X Data Memory (128 Bytes)

- 2X Register Banks (4 vs. 2)

- 2X Timers (Two 16-bit Timers)

- New Full-Duplex Serial I/O Port

- More I/O Pins (32 vs. 27)

- Enhanced MCS-48 Architecture

- 21/2 X To 10X Execution Speed

- 1.4X Die Size

## Table 1.1: 8051 Functions/Speed/Cost Relative to 8048

## 1.2 ENHANCING THE 8048 ARCHITEC-TURE FOR THE 80's

The goal of the 8051 is to extend the architecture of the industry standard 8048 single-chip microcomputer into the 80's. This meant increasing the power of the 8048's CPU as well as increasing the power, variety and quantity of on-chip CPU peripherals.

The 8048's CPU architecture is ideal for control-oriented applications demanding a low-cost microcomputer because of its hardware simplicity and resulting silicon efficiency. A simple ALU is used in virtually all operations: arithmetic, logic, data moves, bit testing and I/O. Since all data is moved through the ALU this also simplifies the internal data path. The 8048's simple addressing methods of Register-, Register-Indirect- and Immediate-Addressing minimize hardware. The conditional branch logic simply concatenates an immediate value to the upper bits of the program counter to economize on silicon, but results in page boundaries. The simplicity of the tablelook-up circuitry also results in page boundaries. The user flags and test pins provided for monitoring program and external status in an efficient manner are limited to two of each. This architecture, and the choice of instruction encodings that it permits, results in 1,024 byte programs of unsurpassed byte efficiency.

AFN-01488A-05

The silicon economic architecture of the 8048 causes some inconvenience to the programmer but the relatively short programs (one or two kilobytes) keep frustration levels in check. The 8051 challenge was to maintain software and feature compatibility with the 8048 while providing a more powerful microcomputer that is easier to program and use. This allows a designer currently using the 8048 to easily upgrade to the 8051 while protecting his investment in algorithm development and the knowledge he gained by designing with the 8048.

Some of the achievements of the 8051 were to extend the maximum program memory address space to 64K-bytes, extending on-chip peripheral functions (counters, serial ports and parallel ports) to satisfy emerging single-chip applications, and enhancing a paged architecture to make it suitable for the relocatable and re-entrant code generated by modern programming techniques. Op codes were reassigned to add new high-power operations and to permit new addressing modes which make the old operations more orthogonal. During this process special care was taken to provide optimum byte efficiency and maximum execution speed. The 8051 is typically 20% more code efficient than the 8049 for programs longer than 2048 bytes. Efficient use of program memory results from an instruction set consisting of 44% one-byte, 41% two-byte and 15% three-byte instructions. With a 12 MHz crystal, 58% of the instructions execute in  $1\mu$ s, 40% in  $2\mu$ s and multiply and divide require only  $4\mu$ s.

## 2.0 THE 8051 FAMILY

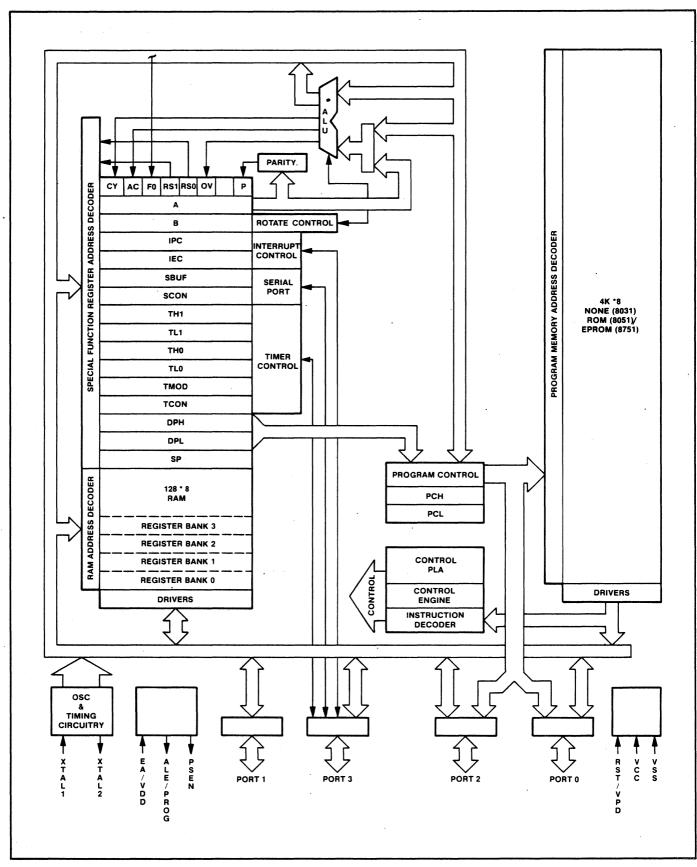

The 8051 is a stand-alone high-performance single-chip computer intended for use in sophisticated real-time applications such as instrumentation, industrial control and intelligent computer peripherals. It provides the hardware features, architectural enhancements and new instructions that make it a powerful and cost effective controller for applications requiring up to 64K-bytes of program memory and/or up to 64K-bytes of data storage. A Block Diagram is shown in Figure 3.

The 8031 is a control-oriented CPU without on-chip program memory. It can address 64K-bytes of external Program Memory in addition to 64K-bytes of External Data Memory. For systems requiring extra capability, each member of the 8051 family can be expanded using standard memories and the byte oriented MCS-80 and MCS-85 peripherals. The 8051 is an 8031 with the lower 4K-bytes of Program Memory filled with on-chip mask programmable ROM while the 8751 has 4K-bytes of UVlight-erasable/electrically-programmable ROM.

The three pin-compatible versions of this component reduce development problems to a minimum and provide maximum flexibility. The 8751 is well suited for development, prototyping, low-volume production and applications requiring field updates; the 8051 for low-cost, high-volume production and the 8031 for applications desiring the flexibility of external Program Memory which can be easily modified and updated in the field.

## 2.1 MACRO-VIEW OF THE 8051 ARCHI-TECTURE

On a single die the 8051 microcomputer combines CPU; non-volatile 4K x 8 read-only program memory; volatile 128 x 8 read/write data memory; 32 I/O lines; two 16-bit timer/event counters; a five-source, two-priority-level, nested interrupt structure; serial I/O port for either multiprocessor communications, I/O expansion, or full duplex UART; and on-chip oscillator and clock circuits. This section will provide an overview of the 8051 by providing a high-level description of its major elements: the CPU architecture and the on-chip functions peripheral to the CPU. The generic term "8051" is also used to refer collectively to the 8031, 8051, and 8751.

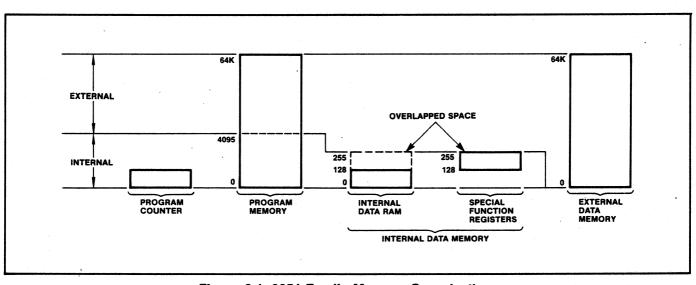

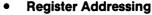

## 2.1.1 8051 CPU Architecture

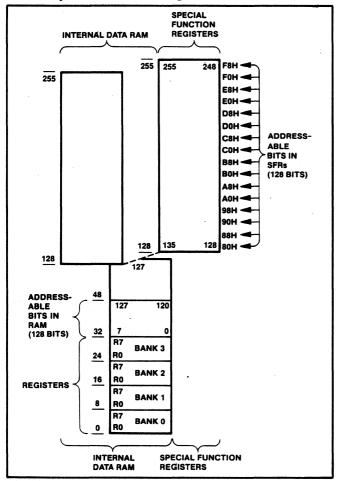

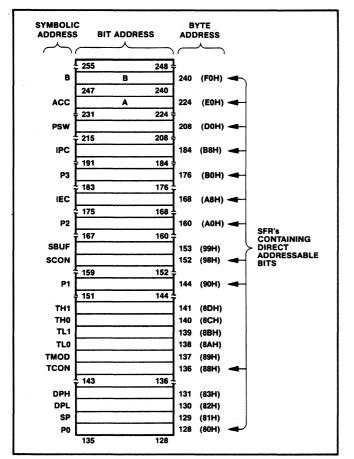

The 8051 CPU manipulates operands in four memory spaces. These are the 64K-byte Program Memory, 64Kbyte External Data Memory, 384-byte Internal Data Memory and 16-bit Program Counter spaces. The Internal Data Memory address space is further divided into the 256-byte Internal Data RAM and 128-byte Special Function Register (SFR) address spaces shown in Figure 2.1. Four Register Banks (each with eight registers), 128 addressable bits, and the stack reside in the Internal Data RAM. The stack depth is limited only by the available Internal Data RAM and its location is determined by the 8-bit Stack Pointer. All registers except the Program Counter and the four 8-Register Banks reside in the Special Function Register address space. These memory mapped registers include arithmetic registers, pointers, I/O ports, and registers for the interrupt system, timers and serial channel. 128 bit locations in the SFR address space are addressable as bits. The 8051 contains 128 bytes of Internal Data RAM and 20 SFRs.

The 8051 provides a non-paged Program Memory address space to accommodate relocatable code. Conditional branches are performed relative to the Program Counter. The register-indirect jump permits branching relative to a 16-bit base register with an offset provided by an 8-bit index register. Sixteen-bit jumps and calls permit branching to any location in the contiguous 64K Program Memory address space.

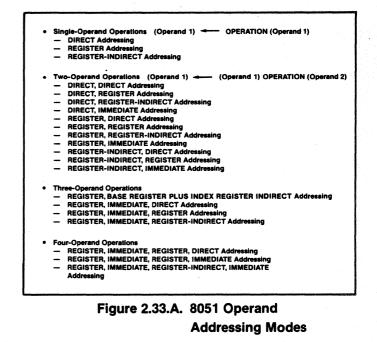

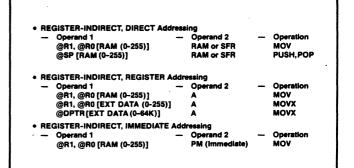

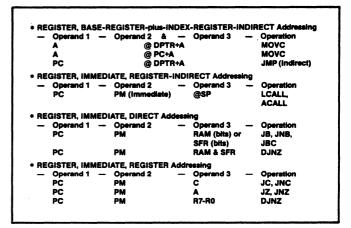

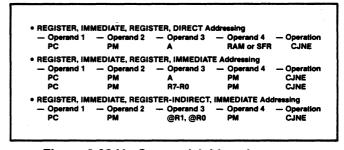

The 8051 has five methods for addressing source operands: Register, Direct, Register-Indirect, Immediate, and Base-Register- plus Index-Register- Indirect Addressing.

Figure 2.1. 8051 Family Memory Organization

The first three methods can be used for addressing destination operands. Most instructions have a "destination, source" field that specifies the data type, addressing methods and operands involved. For operations other than moves, the destination operand is also a source operand.

Registers in the four 8-Register Banks can be accessed through Register, Direct, or Register-Indirect Addressing; the 128 bytes of Internal Data RAM through Direct or Register-Indirect Addressing; and the Special Function Registers through Direct Addressing. External Data Memory is accessed through Register-Indirect Addressing. Look-Up-Tables resident in Program Memory can be accessed through Base-Register- plus Index-Register- Indirect Addressing.

The 8051 is classified as an 8-bit machine since the internal ROM, RAM, Special Function Registers, Arithmetic/Logic Unit and external data bus are each 8-bits wide. The 8051 performs operations on bit, nibble, byte and double-byte data types.

The 8051 has extensive facilities for byte transfer, logic, and integer arithmetic operations. It excels at bit handling since data transfer, logic and conditional branch operations can be performed directly on Boolean variables.

The 8051's instruction set is an enhancement of the instruction set familiar to MCS-48 users. It is enhanced to allow expansion of on-chip CPU peripherals and to optimize byte efficiency and execution speed. Op codes were reassigned to add new high-power operations and to permit new addressing modes which make the old operations more orthogonal. Efficient use of program memory results from an instruction set consisting of 49

single-byte, 45 two-byte and 17 three-byte instructions. When using a 12 MHz oscillator, 64 instructions execute in  $1\mu$ s and 45 instructions execute in  $2\mu$ s. The remaining instructions (multiply and divide) require only  $4\mu$ s. The number of bytes in each instruction and the number of oscillator periods required for execution are listed in the appended 8051 Instruction Set Summary.

## 2.1.2 On-Chip Peripheral Functions

Thus far only the CPU and memory spaces of the 8051 have been described. In addition to the CPU and memories, an interrupt system, extensive I/O facilities, and several peripheral functions are integrated on-chip to relieve the CPU of repetitious, complicated or time-critical tasks and to permit stringent real-time control of external system interfaces. The extensive I/O facilities include the I/O pins, parallel I/O ports, bidirectional address/data bus and the serial port for I/O expansion. The CPU peripheral functions integrated on-chip are the two 16-bit counters and the serial port. All of these work together to greatly boost system performance.

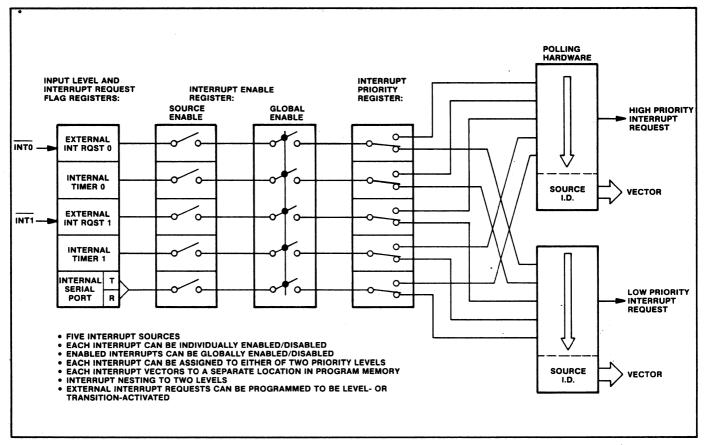

#### 2.1.2.1 INTERRUPT SYSTEM

External events and the real-time-driven on-chip peripherals require service by the CPU asynchronous to the execution of any particular section of code. To tie the asynchronous activities of these functions to normal program execution, a sophisticated multiple-source, twopriority-level, nested interrupt system is provided. Interrupt response latency ranges from  $3\mu$ s to  $7\mu$ s when using a 12 MHz crystal.

The 8051 acknowledges interrupt requests from five sources: Two from external sources via the  $\overline{INT0}$  and  $\overline{INT1}$  pins, one from each of the two internal counters and

one from the serial I/O port. Each interrupt vectors to a separate location in Program Memory for its service program. Each of the five sources can be assigned to either of two priority levels and can be independently enabled and disabled. Additionally all enabled sources can be globally disabled or enabled. Each external interrupt is programmable as either level- or transition-activated and is active-low to allow the "wire or-ing" of several interrupt sources to the input pin. The interrupt system is shown diagrammatically in Figure 2.2.

#### 2.1.2.2 I/O FACILITIES

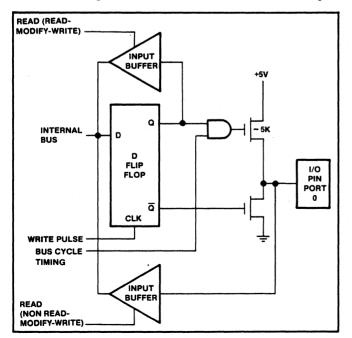

The 8051 has instructions that treat its 32 I/O lines as 32 individually addressable bits and as four parallel 8-bit ports addressable as Ports 0, 1, 2 and 3. Ports 0, 2 and 3 can also assume other functions. Port 0 provides the multiplexed low-order address and data bus used for expanding the 8051 with standard memories and peripherals. Port 2 provides the high-order address bus when expanding the 8051 with external Program Memory or more than 256 bytes of External Data Memory. The pins of Port 3 can be configured individually to provide external interrupt request inputs, counter inputs, the serial port's receiver input and transmitter output, and to generate the control signals used for reading and writing External Data Memory. The generation or use of an alternate function on a Port 3 pin is done automatically by the 8051 as long as the pin is configured as an input. The configuration of the ports is shown on the 8051 Family Logic Symbol of Figure 2.

#### 2.1.2.2.1 Open Drain I/O Pins

Each pin of Port 0 can be configured as an open drain output or as a high impedance input. Resetting the microcomputer programs each pin as an input by writing a one (1) to the pin. If a zero (0) is later written to the pin it becomes configured as an output and will continuously sink current. Re-writing the pin to a one (1) will place its output driver in a high-impedance state and configure the pin as an input. Each I/O pin of Port 0 can sink two TTL loads.

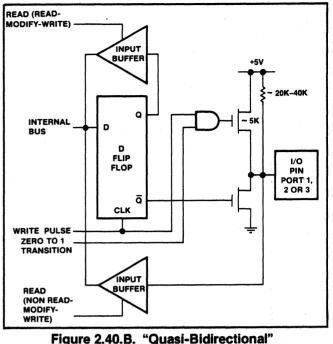

#### 2.1.2.2.2 Quasi-Bidirectional I/O Pins

Ports 1, 2 and 3 are quasi-bidirectional buffers. Resetting the microcomputer programs each pin as an input by writing a one (1) to the pin. If a zero (0) is later written to the pin it becomes configured as an output and will continuously sink current. Any pin that is configured as an output will be reconfigured as an input when a one (1) is written to the pin. Simultaneous to this reconfiguration the output driver of the quasi-bidirectional port will source current for two oscillator periods. Since current is sourced only when a bit previously written to a zero (0) is

Figure 2.2. 8051 Interrupt System

updated to a one (1), a pin programmed as an input will not source current into the TTL gate that is driving it if the pin is later written with another one (1). Since the quasibidirectional output driver sources current for only two oscillator periods, an internal pullup resistor of approximately 20K- to 40K-ohms is provided to hold the external driver's loading at a TTL high level. Ports 1, 2 and 3 can sink/source one TTL load.

## 2.1.2.2.3 Microprocessor Bus

A microprocessor bus is provided to permit the 8051 to solve a wide range of problems and to allow the upward growth of user products. This multiplexed address and data bus provides an interface compatible with standard memories, MCS-80 peripherals and the MCS-85 memories that include on-chip programmable I/O ports and timing functions. These are summarized in the 8051 Microcomputer Expansion Components chart of Figure 2.3.

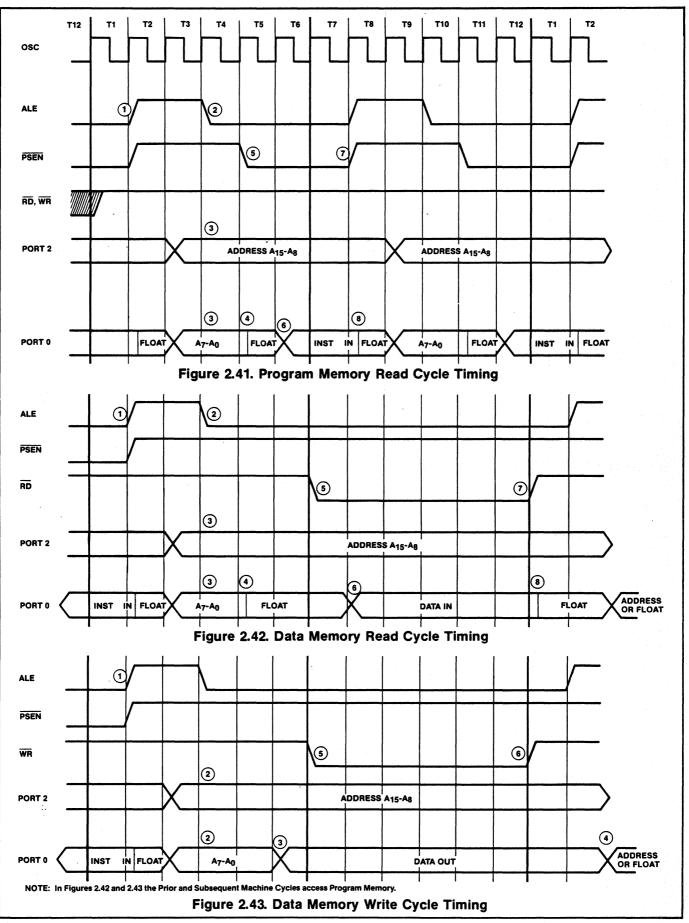

When accessing external memory the high-order address is emitted on Port 2 and the low-order address on Port 0.

The ALE signal is provided for strobing the address into an external latch. The program store enable (PSEN) signal is provided for enabling an external memory device to Port 0 during a read from the Program Memory address space. When the MOVX instruction is executed Port 3 automatically generates the read  $(\overline{RD})$  signal for enabling an External Data Memory device to Port 0 or generates the write  $(\overline{WR})$  signal for strobing the external memory device with the data emitted by Port 0. Port 0 emits the address and data to the external memory through a push/pull driver that can sink/source two TTL loads. At the end of the read/write bus cycle Port 0 is automatically reprogrammed to its high impedance state and Port 2 is returned to the state it had prior to the bus cycle. The 8051 generates the address, data and control signals needed by memory and I/O devices in a manner that minimize the requirements placed on external program and data memories. At 12 MHz, the Program Memory cycle time is 500ns and the access times required from stable address and PSEN are approximately 320ns and 150ns respectively. The External Data Memory cycle

|                                 | Category                                                     | I.D.                                                  | Description                                                                                                                                                                                                                                                                                  | Comments                                                                                                                                                                          |

|---------------------------------|--------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | I/O Expander                                                 |                                                       | 8 Line I/O Expander (Shift Register)                                                                                                                                                                                                                                                         | Low Cost I/O Expander                                                                                                                                                             |

|                                 | Standard EPROMs                                              | 2758<br>2716-1<br>2732<br>2732A                       | 1K x 8 450 ns Light Erasable<br>2K x 8 350 ns Light Erasable<br>4K x 8 450 ns Light Erasable<br>4K x 8 250 ns Light Erasable                                                                                                                                                                 | User programmable and erasable.                                                                                                                                                   |

|                                 | Standard RAMs                                                | 2114A<br>2148<br>2142-2                               | 1K x 4 100 ns RAM<br>1K x 4 70 ns RAM<br>1K x 4 200 ns RAM                                                                                                                                                                                                                                   | Data memory can be easily expanded<br>using standard NMOS RAMs.                                                                                                                   |

| its                             | Multiplexed Address/<br>Data RAMs                            | 8185A                                                 | 1K x 8 300 ns RAM                                                                                                                                                                                                                                                                            |                                                                                                                                                                                   |

| Compatible MCS-80/85 Components | Standard I/O                                                 | 8212<br>8282<br>8283<br>8255A<br>8251A                | 8-Bit I/O Port<br>8-Bit I/O Port<br>8-Bit I/O Port<br>Programmable Peripheral Interface<br>Programmable Communications<br>Interface                                                                                                                                                          | Serves as Address Latch or I/O port.<br>Three 8-bit porgrammable I/O ports.<br>Serial Communcations Receiver/<br>Transmitter.                                                     |

| Compatible MCS                  | Standard Peripherals                                         | 8205<br>8286<br>8287<br>8253A<br>8279<br>8291<br>8292 | <ul> <li>1 of 8 Binary Decoder</li> <li>Bi-directional Bus Driver</li> <li>Bi-directional Bus Driver (Inverting)</li> <li>Programmable Interval Timer</li> <li>Programmable Keyboard/Display</li> <li>Interface (128 Keys)</li> <li>GPIB Talker/Listener</li> <li>GPIB Controller</li> </ul> | MCS-80 and MCS-85 peripheral devices<br>are compatible with the 8051 allowing<br>easy addition of specialized interfaces.<br>Future MCS-80/85 devices will also be<br>compatible. |

|                                 | Universal Peripheral<br>Interfaces                           | 8041A<br>8741A                                        | ROM Program Memory<br>EPROM Program Memory                                                                                                                                                                                                                                                   | User programmable to perform custom I/O and control functions.                                                                                                                    |

|                                 | Memories with<br>on-chip I/O and<br>Peripheral<br>Functions. | 8155-2<br>8355-2<br>8755-2                            | 256 x 8 330 ns RAM<br>2K x 8 300 ns ROM<br>2K x 8 300 ns EPROM                                                                                                                                                                                                                               |                                                                                                                                                                                   |

#### Figure 2.3. 8051 Microcomputer Expansion Components

time is  $l\mu s$  and the access times required from stable address and from read ( $\overline{RD}$ ) or write ( $\overline{WR}$ ) command are approximately 600ns and 250ns respectively.

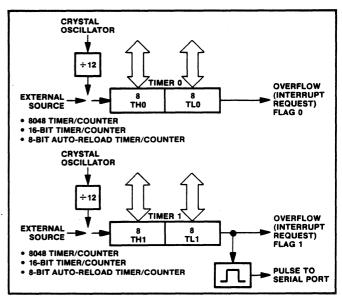

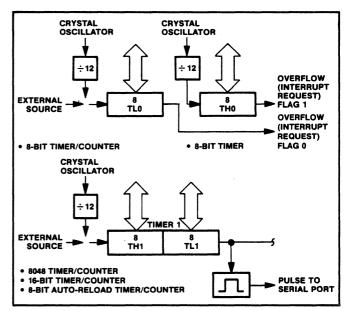

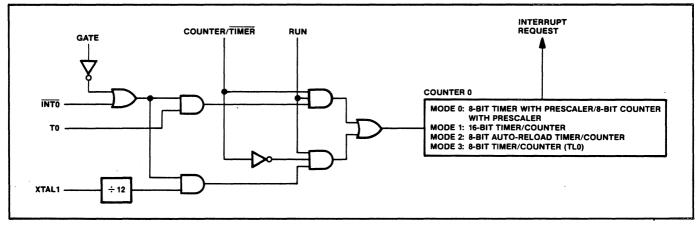

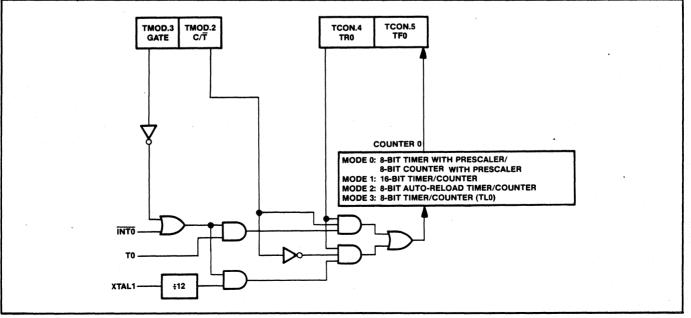

## 2.1.2.3 TIMER/EVENT COUNTERS

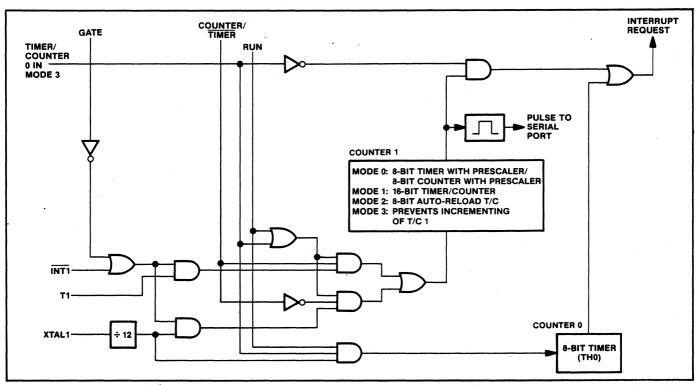

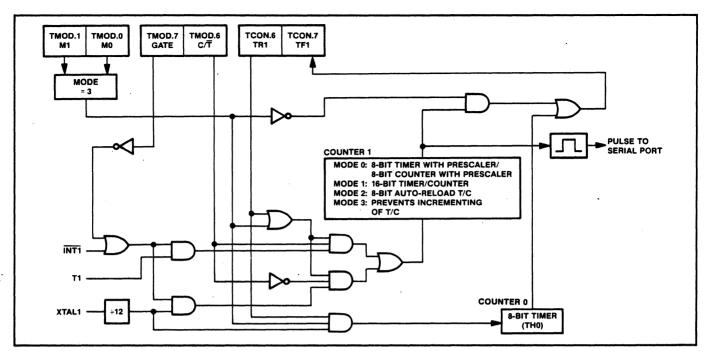

The 8051 contains two 16-bit counters for measuring time intervals, measuring pulse widths, counting events and generating precise, periodic interrupt requests. Each can be programmed independently to operate similar to an 8048 8-bit timer with divide by 32 prescaler or 8-bit counter with divide by 32 prescaler (Mode 0), as a 16-bit time-interval or event counter (Mode 1), or as an 8-bit time-interval or event counter with automatic reload upon overflow (Mode 2).

Additionally, counter 0 can be programmed to a mode that divides it into one 8-bit time-interval or event counter and one 8-bit time-interval counter (Mode 3).

When counter 0 is in Mode 3, counter 1 can be programmed to any of the three aforementioned modes, although it cannot set an interrupt request flag or generate an interrupt. This mode is useful because counter 1's overflow can be used to pulse the serial port's transmission-rate generator. Along with their multiple operating modes and 16-bit precision, the counters can also handle very high input frequencies. These range from 0.1 MHz to 1.0 MHz (for 1.2 MHz to 12 MHz crystal) when programmed for an input that is a division by 12 of the oscillator frequency and from 0 Hz to an upper limit of 50 KHz to 0.5 MHz (for 1.2 MHz to 12 MHz crystal) when programmed for external inputs. Both internal and external inputs can be gated to the counter by a second external source for directly measuring pulse widths.

The counters are started and stopped under software control. Each counter sets its interrupt request flag when it overflows from all ones to all zeros (or auto-reload value). The operating modes and input sources are summarized in Figures 2.4A and 2.4B. The effects of the configuration flags and the status flags are shown in Figures 2.5A and 2.5B.

Figure 2.4.A. Timer/Event Counter Modes 0, 1, and 2

Figure 2.4.B. Timer/Event Counter Mode 3

Figure 2.5.B. Timer/Counter 1 Control and Status Flag Circuitry

Figure 2.6. Serial Port—UART Modes 1, 2, and 3

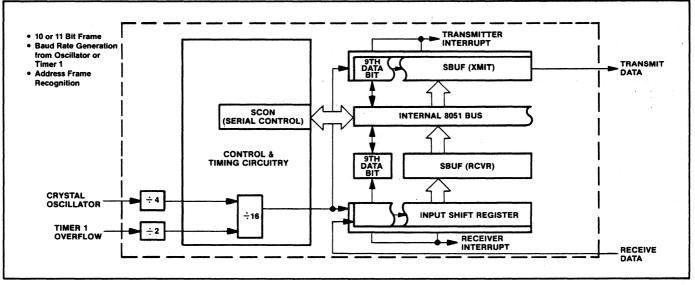

#### 2.1.2.4 SERIAL COMMUNICATIONS

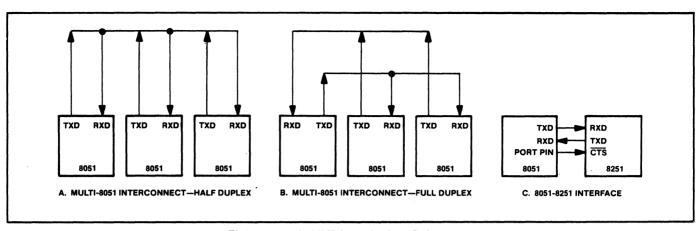

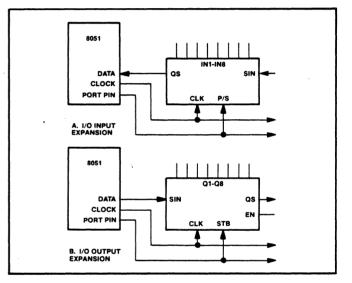

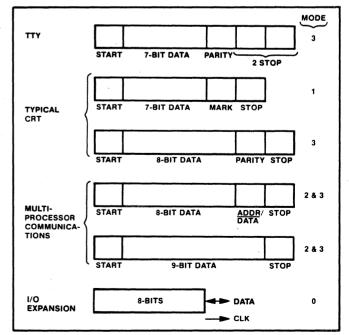

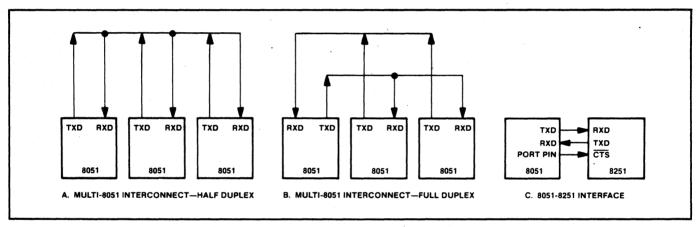

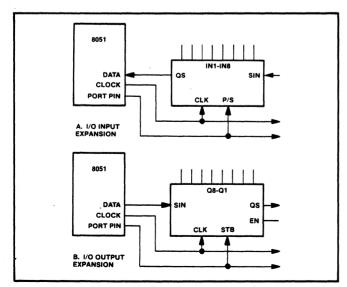

The 8051 has a serial I/O port that is useful for serially linking peripheral devices as well as multiple 8051s through standard asynchronous protocols with fullduplex operation. The serial port also has a synchronous mode for expansion of I/O lines using CMOS and TTL shift registers. This hardware serial communications interface saves ROM code and permits a much higher transmission rate than could be achieved through software. In response to a serial port interrupt request the CPU has only to read/write the serial port's buffer to service the serial link. A block diagram of the serial port is shown in Figure 2.6. Methods for linking UART (universal asynchronous receiver/transmitter) devices are shown in Figure 2.7 and a method for I/O expansion is shown in Figure 2.8.

The full-duplex serial I/O port provides asynchronous modes to facilitate communications with standard UART devices, such as printers and CRT terminals, or communications with other 8051s in multi-processor systems.

The receiver is double buffered to eliminate the overrun that would occur if the CPU failed to respond to the receiver's interrupt before the beginning of the next frame. Double buffering of the transmitter is not needed since the 8051 can generally maintain the serial link at its maximum rate without it. A minor degradation in transmission rate can occur in rare events such as when the servicing of the transmitter has to wait for a lengthy interrupt service program to complete. In asynchronous modes, false start-bit rejection is provided on received frames. For noise rejection a best two-out-of-three vote is taken on three samples near the center of each received bit.

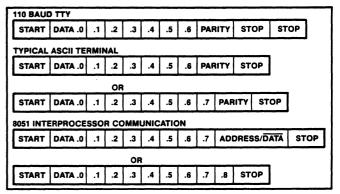

When interfacing with standard UART devices the serial channel can be programmed to a mode (Mode 1) that transmits/receives a ten-bit frame or programmed to a mode (Mode 2 or 3) that transmits/receives an eleven-bit frame as shown in Figure 2.9. The frame consists of a start bit, eight or nine data bits and a stop bit. In Modes 1 and 3, the transmission-rate timing circuitry receives a pulse from counter 1 each time the counter overflows. The input to counter 1 can be an external source or a division by 12 of the oscillator frequency. The auto-reload mode of the counter provides communication rates of 122 to 31,250 bits per second (including start and stop bits) for a 12 MHz crystal. In Mode 2 the communication rate is a division by 64 of the oscillator frequency yielding a transmission rate of 187,500 bits per second (including start and stop bits) for a 12 MHz crystal.

Distributed processing offers a faster, more powerful system than can be provided by a single CPU processor. This results from a hierarchy of interconnected processors, each with its own memories and I/O. In multiprocessing, a host 8051 microcomputer controls a multiplicity of 8051s configured to operate simultaneously on separate portions of the program, each controlling a portion of the overall process. The interconnected 8051s reduce the load on the host processor and result in a low-cost system of data transmission. This form of distributed

Figure 2.8. I/O Expansion Technique

processing is especially effective in systems where controls in a complex process are required at physically separated locations.

In Modes 2 and 3 the automatic wake-up of slave processors through interrupt driven address-frame recognition is provided to facilitate interprocessor communications. The protocol for interprocessor communications is shown in Figure 2.10.

- 1. Slaves Configure serial port to interrupt CPU if the received ninth data bit is a one (1).

- 2. Master—Transmit frame containing address in first 8 data bits and set ninth data bit (i.e., ninth data bit designates address frame).

- 3. Slaves Serial port interrupts CPU when address frame is received. Interrupt service program compares received address to its address. The slave which has been addressed reconfigures its serial port to interrupt the CPU on all subsequent transmissions.

- 4. Master—Transmit control frames and data frames (these will be accepted only by the previously addressed slave.)

#### Figure 2.10. Protocol for Multi-Processor Communications

In synchronous mode (Mode 0) the high-speed serial port provides an efficient, low-cost method of expanding I/O lines using standard TTL and CMOS shift registers. The serial channel provides a clock output for synchronizing the shifting of bits to/from an external register. The data rate is a division by 12 of the oscillator frequency and is 1M bits per second at 12 MHz.

## 2.2 CPU HARDWARE

This section describes the hardware architecture of the 8051's CPU in detail. The interrupt system and on-chip functions peripheral to the CPU are described in subsequent sections. A detailed 8051 Functional Block Diagram is displayed in Figure 2.11.

#### 2.2.1 Instruction Decoder

Each program instruction is decoded by the instruction decoder. This unit generates the internal signals that control the functions of each unit within the CPU section. These signals control the sources and destination of data, as well as the function of the Arithmetic/Logic Unit (ALU).

#### 2.2.2 Program Counter

The 16-bit Program Counter (PC) controls the sequence in which the instructions stored in program memory are executed. It is manipulated with the Control Transfer instructions listed in section 2.7.2.

#### 2.2.3 Internal Data Memory

The 8051 contains a 128-byte Internal Data RAM (which includes registers R7-R0 in each of four Banks), and twenty memory-mapped Special Functional Registers.

#### 2.2.3.1 INTERNAL DATA RAM

The Internal Data RAM provides a convenient 128-byte scratch pad memory.

#### 2.2.3.2 REGISTER BANKS

There are four 8-Register Banks within the Internal Data RAM, each containing registers R7-R0.

#### 2.2.3.3 SPECIAL FUNCTION REGISTERS

The Special Function Registers include arithmetic registers (A, B, PSW), pointers (SP, DPH, DPL) and registers that provide an interface between the CPU and the on-chip peripheral functions.

#### 2.2.3.4 A REGISTER

The A register is the accumulator register. ACC is the location of the accumulator in the Internal Data Memory.

#### 2.2.3.5 B REGISTER

The B register is dedicated during multiply and divide and serves as both a source and a destination. During all other operations the B register is simply another location of the Internal Data Memory.

#### 2.2.3.6 PSW REGISTER

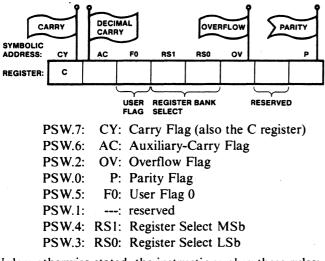

The carry (CY), auxialiary carry (AC), user flag 0 (FO), register bank select 1 (RS1), register bank select 0 (RSO), overflow (OV) and parity (P) flags reside in the Program Status Word (PSW) Register. These flags are bitmemory-mapped within the byte-memory-mapped PSW. The PSW flags record processor status information and control the operation of the processor.

The CY, AC, and OV flags generally reflect the status of the latest arithmetic operation. The P flag always reflects the parity of the A register. The carry flag is also a Boolean accumulator for bit operations. Specific details are provided in the "Flag Register Settings" section of 2.7.2.

F0 is a general purpose flag which is pushed onto the stack as part of a PSW save.

The two Register Bank select bits (RS1 and RS0) determine which of the four 8-Register Banks is selected.

#### 2.2.3.7 STACK POINTER

The 8-bit Stack Pointer (SP) contains the address at which the last byte was pushed onto the stack. This is also the address of the next byte that will be popped. SP is updatable under software control.

Figure 2.11. 8051 Family Functional Block Diagram

#### 2.2.3.8 DATA POINTER

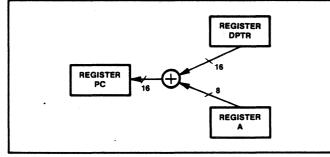

The 16-bit Data Pointer (DPTR) register is the concatination of registers DPH (data pointer's high-order byte) and DPL (data pointer's low-order byte). The DPTR is used in Register-Indirect Addressing to move Program Memory constants, to move External Data Memory variables, and to branch over the 64K Program Memory address space.

## 2.2.4 Arithmetic Section

The arithmetic section of the processor performs many data manipulation functions and is comprised of the Arithmetic/Logic Unit (ALU), A register, B register and PSW register.

The ALU accepts 8-bit data words from one or two sources and generates an 8-bit result under the control of the instruction decoder. The ALU performs the arithmetic operations of add, subtract, multiply, divide, increment, decrement, BCD-decimal-add-adjust and compare and the logic operations of and, or, exclusive-or, complement and rotate [right, left, or nibble swap (left four)].

## 2.2.5 Program Control Section

The program control section controls the sequence in which the instructions stored in program memory are executed. The conditional branch logic enables conditions internal and external to the processor to cause a change in the sequence of program execution.

#### 2.2.6 Oscillator and Timing Circuitry

Timing generation for the 8051 is completely selfcontained, except for the frequency reference which can be a crystal or external clock source. The on-board oscillator is a parallel anti-resonant circuit with a frequency range of 1.2 to 12 MHz. The XTAL2 pin is the output of a high-gain amplifier, while XTAL1 is its input. A crystal connected between XTAL1 and XTAL2 provides the feedback and phase shift required for oscillation. The 1.2 to 12 MHz range is also accomodated when an external TTL compatible clock is applied to XTAL1 as the frequency source.

## 2.2.7 Boolean Processor

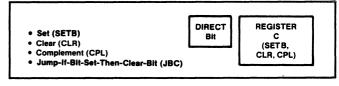

Although the Boolean processor is an integral part of the 8051's architecture, it may be considered an independent bit processor since it has its own instruction set, its own accumulator (the carry flag), and its own bit-addressable RAM and I/O.

The bit-manipulation instructions allow the Direct Addressing of 128 bits within the Internal Data RAM and 128 bits within the Special Function Registers. The Special Function Registers with an address evenly divisable by eight (P0, TCON, P1, SCON, P2, IEC, P3, IPC, PSW, A, and B) contain Direct Addressable bits. On any addressable bit, the Boolean processor can perform the bit operations of set, clear, complement, jump-if-set, jump-if-not-set, jump-if-set-then-clear and move to/from carry. Between any addressable bit (or its complement) and the carry flag it can perform the bit operation of logical and or logical or with the result returned to the carry flag.

The bit-manipulation instructions provide optimum code and speed efficiency in "bit-banging" applications such as the control of the 8051's on-chip peripherals. The Boolean processor also provides a straightforward means of converting logic equations (like those used in random logic design) directly into software. Complex combinatorial-logic functions can be resolved without extensive data movement, byte masking and test-and-branch trees.

## 2.3 MEMORY ORGANIZATION

In the 8051 family the memory is organized over three address spaces and the program counter. The memory spaces shown in Figure 2.1 are the:

- 16-bit Program Counter

- 64K-byte Program Memory address space

- 64K-byte External Data Memory address space

- 384-byte Internal Data Memory address space

The 16-bit Program Counter register provides the 8051 with its 64K addressing capabilities. The Program Counter allows the user to execute calls and branches to any location within the Program Memory space. There are no instructions that permit program execution to move from the Program Memory space to any of the data memory spaces.

In the 8051 and 8751 the lower 4K of the 64K Program Memory address space is filled by internal ROM and EPROM, respectively. By trying the  $\overline{EA}$  pin high, the processor can be forced to fetch from the internal ROM/EPROM for Program Memory addresses 0 through 4K. Bus expansion for accessing Program Memory beyond 4K is automatic since external instruction fetches occur automatically when the Program Counter increases above 4095. If the  $\overline{EA}$  pin is tied low all Program Memory fetches are from external memory. The execution speed of the 8051 is an same regardless of whether fetches are from internal or external Program Memory. If all program storage is on-chip, byte location 4095 should be left vacant to prevent an undesired prefetch from external Program Memory address 4096.

Certain locations in Program Memory are reserved for specific programs. Locations 0000 through 0002 are reserved for the initialization program. Following reset, the CPU always begins execution at location 0000. Locations 0003 through 0042 are reserved for the five interrupt-request service programs. Each resource that can request an interrupt requires that its service program be stored at its reserved location. The 64K-byte External Data Memory address space is automatically accessed when the MOVX instruction is executed.

Functionally the Internal Data Memory is the most flexible of the address spaces. The Internal Data Memory space is subdivided into a 256-byte Internal Data RAM address space and a 128-byte Special Function Register address space as shown in Figure 2.12.

Figure 2.12. Internal Data Memory Address Space

The Internal Data RAM address space is 0 to 255. Four 8-Register Banks occupy locations 0 through 31. The stack can be located anywhere in the Internal Data RAM address space. In addition, 128 bit locations of the on-chip RAM are accessible through Direct Addressing. These bits reside in Internal Data RAM at byte locations 32 through 47. Currently locations 0 through 127 of the Internal Data RAM address space are filled with on-chip RAM. Locations 128 through 255 may be filled on later products without affecting existing software.

The stack depth is limited only by the available Internal Data RAM, thanks to an 8-bit reloadable Stack Pointer. The stack is used for storing the Program Counter during subroutine calls and may be used for passing parameters. Any byte of Internal Data RAM or Special Function Register accessible through Direct Addressing can be pushed/popped.

The Special Function Register address space is 128 to 255. All registers except the Program Counter and the four 8-Register Banks reside here. Memory mapping the Special Function Registers allows them to be accessed as easily as internal RAM. As such, they can be operated on by most instructions. In addition, 128 bit locations within the Special Function Register address space can be accessed using Direct Addressing. These bits reside in the Special Function Register byte locations divisible by eight. The twenty Special Function Registers are listed in Figure 2.13. Their mapping in the Special Function Register address space is shown in Figure 2.14.

| ARITHMETIC REGISTERS:                        |  |

|----------------------------------------------|--|

| ACCumulator*, B register*,                   |  |

| Program Status Word*                         |  |

| POINTERS:                                    |  |

| Stack Pointer, Data Pointer (high & low)     |  |

| PARALLEL I/O PORTS:                          |  |

| Port 3*, Port 2*, Port 1*, Port 0*           |  |

| INTERRUPT SYSTEM:                            |  |

| Interrupt Priority Control*,                 |  |

| Interrupt Enable Control*                    |  |

| TIMERS:                                      |  |

| Timer MODe, Timer CONtrol*, Timer 1          |  |

| (high & low), Timer 0 (high & low)           |  |

| SERIAL I/O PORT:                             |  |

| Serial CONtrol*, Serial data BUFfer          |  |

| *Bits in these registers are bit addressable |  |

Figure 2.13. Special Function Registers

Performing a read from a location of the Internal Data Memory where neither a byte of Internal Data RAM (i.e. RAM addresses 128-255) nor a Special Function Register exists will access data of indeterminable value.

Architecturally, each memory space is a linear sequence of 8-bit wide bytes. By Intel convention the storage of multi-byte address and data operands in program and data memories is least significant byte at the low-order address and the most significant byte at the high-order address. Within byte X, the most significant bit is represented by X.7 while the least significant bit is X.0. Any deviation from these conventions will be explicitly stated in the text.

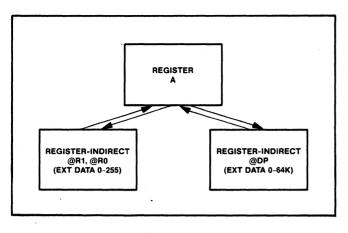

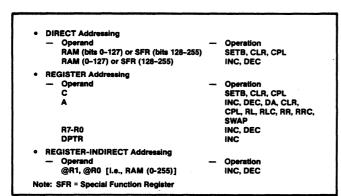

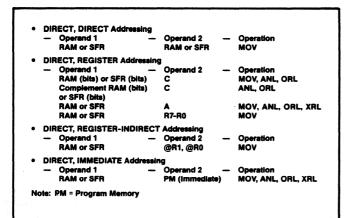

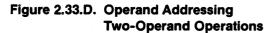

## 2.4 OPERAND ADDRESSING

There are five methods of addressing source operands. They are Register Addressing, Direct Addressing, Register-Indirect Addressing, Immediate Addressing, and Base-Register- plus Index-Register- Indirect Addressing. The first three of these methods can also be used to

Figure 2.14. Mapping Of Special Function Registers

address a destination operand. Since operations in the 8051 require 0 (NOP only), 1, 2, 3 or 4 operands, these five addressing methods are used in combinations to provide the 8051 with its 21 addressing modes.

Most instructions have a "destination, source" field that specifies the data type, addressing methods and operands involved. For operations other than moves, the destination operand is also a source operand. For example, in "subtract-with-borrow A,#5" the A register receives the result of the value in register A minus 5, minus C.

Most operations involve operands that are located in Internal Data Memory. The selection of the Program Memory space or External Data Memory space for a second operand is determined by the operation mnemonic unless it is an immediate operand. The subset of the Internal Data Memory being addressed is determined by the addressing method and address value. For example, the Special Function Registers can be accessed only thorugh Direct Addressing with an address of 128-255. A summary of the operand addressing methods is shown in Figure 2.15. The following paragraphs describe the five addressing methods.

Register Addressing permits access to the eight registers

- R7-R0

- A, B, C (bit), AB (two bytes),

DPTR (double byte)

- Direct Addressing

- Lower 128 bytes of Internal Data RAM

- Special Function Registers

- 128 bits in subset of Internal Data RAM address space

- 128 bits in subset of Special Function Register address space

- Register-Indirect Addressing

- Internal Data RAM [@R1, @R0, @SP (PUSH and POP only)]

- Least Significant Nibbles in Internal Data RAM (@R1, @R0)

- External Data Memory (@R1, @R0, @DPTR)

- Immediate Addressing

Program Memory (in-code constant)

- Base Register- plus Index-Register- Indirect Addressing

- Program Memory (@ DPTR+A, @ PC+A)

Figure 2.15. Operand Addressing Methods

(R7-R0) of the selected Register Bank (RB). One of the four 8-Register Banks is selected by a two-bit field in the PSW. The registers may also be accessed through Direct Addressing and Register-Indirect Addressing since the four Register Banks are mapped into the lowest 32 bytes of Internal Data RAM as shown in Figure 2.16. Other Internal Data Memory locations that are addressed as registers are A, B, C, AB and DPTR.

Direct Addressing provides the only means of accessing the memory-mapped byte-wide Special Function Registers and memory mapped bits within the Special Function Registers and Internal Data RAM. Direct Addressing of bytes may also be used to access the lower 128 bytes of Internal Data RAM. Direct Addressing of bits gains access to a 128 bit subset of the Internal Data RAM and 128 bit subset of the Special Function Registers as shown in Figures 2.12, 2.14 and 2.16.

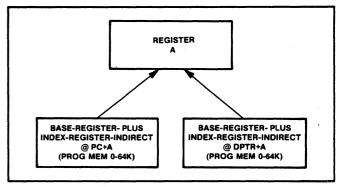

Register-Indirect Addressing using the content of R1 or R0 in the selected Register Bank, or using the content of the Stack Pointer (PUSH and POP only), addresses the Internal Data RAM. Register-Indirect Addressing is also used for accessing the External Data Memory. In this case, either R1 or R0 in the selected Register Bank may be used for accessing locations within a 256-byte block. The block number can be preselected by the contents of a port. The 16-bit Data Pointer may be used for accessing any location within the full 64K external address space. Immediate Addressing allows constants which are part

AFN-01488A-17

of the instruction to be accessed from the Program Memory.

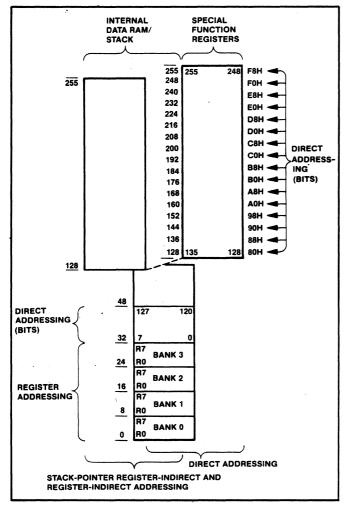

Base-Register- plus Index-Register- Indirect Addressing simplifies accessing look-up-tables (LUT) resident in Program Memory. A byte may be accessed from a LUT via an indirect move from a location whose address is the sum of a base register (the DPTR or PC) and the index<sup>•</sup> register (A).

## 2.5 DATA MANIPULATION

The 8051 microcomputer is efficient both as an arithmetic processor and as a controller. In addition to the capabilities of its 8048 predecessor, the 8051 was enhanced with improved data transfer, logic manipulation, arithmetic processing, and real-time control capabilities. The 8051 performs operations on bit, nibble (4-bit), byte (8-bit) and double-byte (16-bit) data types. It is classified as an 8-bit machine since the internal ROM, RAM, Special Function Registers, Arithmetic/Logic Unit (ALU) and the external data bus are each 8-bits wide. The double-byte data type is used only by the Data Pointer and the Program Counter. The Data Pointer can be manipulated as a single double-byte register (DPTR) or as two locations in Internal Data Memory (DPH & DPL). The Program Counter is always manipulated as a single double-byte register.

While the 8051 has extensive facilities for byte logic operations as well as byte binary and two-digit BCD arithmetic, it excels in its bit handling capabilities. 128 bits in the Special Function Registers and 128 software flags in the Internal Data RAM are all supported orthogonally by the logic operations of and, or, set, clear, and complement; the conditional branch operations of jump-if-bit-set, jump-if-bit-not-set, and jump-if-bit-setthen-clear-bit; and the transfer operation of move bit. Performing conditional branch, logical, and transfer operations directly on Boolean variables is a breakthrough for microcomputers, since this makes the 8051 both a byte processor and a Boolean processor.

## 2.5.1 Data Transfer Operations

Look-up-tables resident in Program Memory can be accessed by indirect moves. A byte constant can be transferred to the A register (i.e. accumulator) from the Program Memory location whose address is the sum of a base register (the PC or DPTR) and the index register (A). This provides a convenient means for programming translation algorithms such as ASCII to seven segment conversions. The Program Memory move operations are shown diagrammatically in Figure 2.17.

Figure 2.17 Program Memory Move Operations

A byte location within a 256-byte block of External Data Memory can be accessed using R1 or R0 in Register-Indirect Addressing. Any location within the full 64K External Data Memory address space can be accessed through Register-Indirect Addressing using a 16-bit bask register (i.e. the Data Pointer). These moves are shown in Figure 2.18.

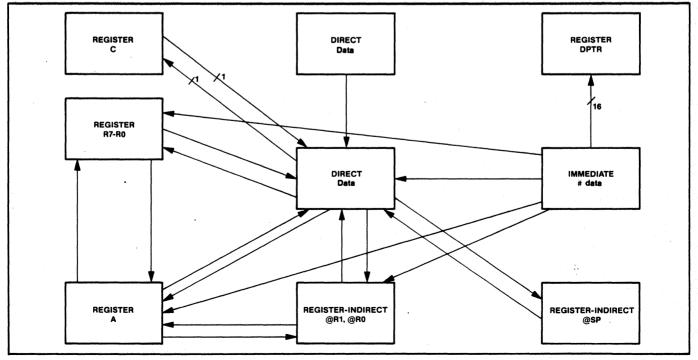

The byte in-code-constant (immediate) moves and byte variable moves within the 8051 are highly orthogonal as detailed in Figure 2.19. When one considers that the accumulator and the registers in the Register Banks can be Direct Addressed, the two-operand data transfer operations allow a byte to be moved between any two of the RB registers, Internal Data RAM, accumulator and Special Function Registers. Also, immediate operands

Figure 2.18. External Data Memory Move Operations

can be moved to any of these locations. Of particular interest is the Direct Address to Direct Address move which permits the value in a port to be moved to the Internal Data RAM without using any RB registers or the accumulator. The Data Pointer register can be loaded with a double-byte immediate value. Also, the 8051's Boolean Processor can move any Direct Addressed bit to or from the carry flag.

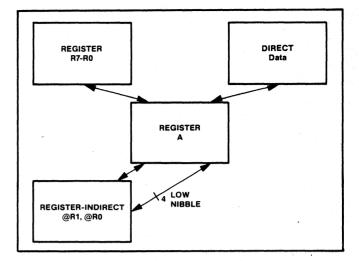

The A register can be exchanged with a register in the selected Register Bank, with a Register-Indirect Addressed byte in the Internal Data RAM or with a Direct Addressed byte in the Internal Data RAM or Special Function Register. The least significant nibble of the A register can also be exchanged with the least significant nibble of a Register-Indirect Addressed byte in the Internal Data RAM. The exchange operation is shown in Figure 2.20

Figure 2.20. Internal Data Memory Exchange Operations

#### 2.5.2 Logic Operations

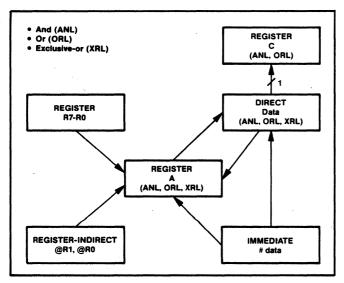

The 8051 permits the logic operations of and, or, and exlusive-or to be performed on the A register by a second operand which can be immediate value, a register in the selected Register Bank, a Register-Indirect Addressed byte of Internal Data RAM or a Direct Addressed byte of Internal Data RAM or Special Function Register. In addition, these logic operations can be performed on a Direct Addressed byte of the Internal Data RAM or Special Function Register using the A register as the second operand. Also, use of Immediate Addressing with Direct Addressing permits these logic operations to set, clear or complement any bit anywhere in the Internal Data RAM or Special Function Registers without

Figure 2.19. Internal Data Memory Move Operations

affecting the PSW, RB registers or accumulator. When one takes into account that registers R7-R0 and the accumulator can be Direct Addressed, the two-operand logic operations allow the destination (first operand) to be a byte in the Internal Data RAM, a Special Function Register, RB registers (R7-R0) or the accumulator while the choice of the second operand can be any of the aforementioned or an immediate value. The 8051 can also perform a logical or, or a logical and, between the Boolean accumulator (i.e. the carry flag) and any bit, or its complement, that can be accessed through Direct Addressing. The and, or, and exclusive-or logic operations are summarized in Figure 2.21.

Figure 2.21. Internal Data Memory Logic Operations

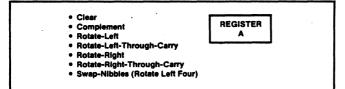

In addition to the logic operations that are performed on Internal Data Memory as shown in Figure 2.21, there are also logic operations that are performed specifically on the A register. These are summarized in Figure 2.22.

Figure 2.22. Internal Data Memory Logic Operations (Register A Specific)

In addition to the and and or bit logicals shown in Figure 2.21, there are logicals that can operate exclusively on a Direct Addressed bit. These operations are listed in Figure 2.23. The carry flag is also addressed as a register and can be set, cleared or complemented with one-byte instructions.

## 2.5.3 Arithmetic Operations

Along with the existing 8048 arithmetic operations of

Figure 2.23. Internal Data Memory Logic Operations (Bit-Specific)

add, increment, decrement, compare-to-zero, decrementand-compare-to-zero, and decimal-add-adjust, the 8051 implemented subtract-with-borrow, compare, multiply and divide.

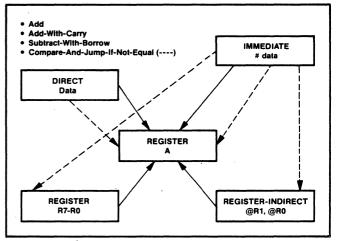

Only unsigned binary integar arithmetic is performed in the Arithmetic/Logic Unit. In the two-operand operations of add, add-with-carry and subtract-with-borrow, the A register is the first operand and receives the result of the operation. The second operand can be an immediate byte, a register in the selected Register Bank, a Register-Indirect Addressed byte or a Direct Addressed byte. These instructions affect the overflow, carry, auxiliarycarry and parity flags in the Program Status Word (PSW). The carry flag facilitates nonsigned integer and multi-precision addition and subtraction and multiprecision rotation. Handling two's-complement-integer (signed) addition and subtraction can easily be accomodated with software's monitoring of the PSW's overflow flag. The auxiliary-carry flag simplifies BCD arithmetic. An operation that has an arithmetic aspect similar to a subtract is the compare-and-jump-if-not-equal operation. This operation performs a conditional branch if a register in the selected Register Bank, or an Indirect Addressed byte of Internal Data RAM, does not equal an immediate value; or if the A register does not equal a byte in the Direct Addressable Internal Data RAM, or a Special Function Register. While the destination operand is not updated and neither source operand is affected by the compare operation, the carry flag is. A summary of the two-operand add/subtract operations is shown in Figure 2.24.

Figure 2.24. Internal Data Memory Arithmetic Operations

AFN-01488A-20

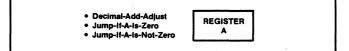

There are three arithmetic operations that operate exclusively on the A register. These are the decimaladjust for BCD addition and the two test conditions shown in Figure 2.25. The decimal-adjust operation converts the result from a binary addition of two two-digit BCD values to yield the correct two-digit BCD result. During this operation the auxiliary-carry flag helps effect the proper adjustment. Conditional branches may be taken based on the value in the A register being zero or not zero.

Figure 2.25. Internal Data Memory Arithmetic Operations (Register A Specific)

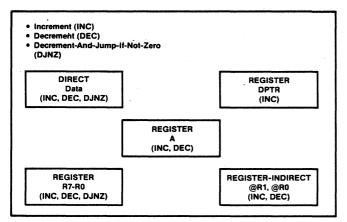

The 8051 simplifies the implementation of software counters since the increment and decrement operations can be performed on the A register, a register in the selected Register Bank, an Indirect Addressed byte in the Internal Data RAM or a byte in the Direct Addressed Internal Data RAM or Special Function Register. The 16-bit Data Pointer can be incremented. For efficient loop control the decrement-and-jump-if-not-zero operation is provided. This operation can test a register in the selected Register Bank, any Special Function Register or any byte of Internal Data RAM accessible through Direct Addressing and force a branch if it is not zero. The increment/decrement operations are summarized in Figure 2.26.

Figure 2.26. Internal Data Memory Arithmetic Operations

The multiply operation multiplies the one-byte A register by the one-byte B register and returns a double-byte result (MSB in B, LSB in A). The divide operation divides the one-byte A register by the one-byte B register and returns a byte quotient to the A register and a byte remainder to the B register. These are shown in Figure 2.27.

#### 2.6 CONTROL TRANSFER

The 8051 has a non-paged Program Memory to accom-

|                                           |          | the second s |  |

|-------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------|--|

| <ul><li>Multiply</li><li>Divide</li></ul> | REGISTER | REGISTER<br>B                                                                                                  |  |

|                                           | L        | ليستعد ويتبع بالشقاص                                                                                           |  |

#### Figure 2.27. Internal Data Memory Arithmetic Operations (Register A with B Specific)

modate relocatable code. The advantage of a non-paged memory is that a minor change to a program that causes a shift of the code's position in memory will not cause page boundary readjustments to be necessary. This also makes relocation possible. Relocation is desirable since it permits several programmers to write relocatable modules in various assembly and high-level languages which can later be linked together to form the machine object code.

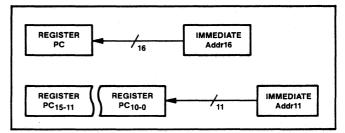

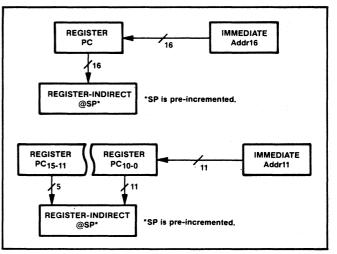

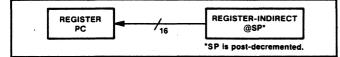

Sixteen-bit jumps and calls are provided to allow branching to any location in the contiguous 64K Program Memory address space and preempt the need for Program Memory bank switching. Eleven-bit jumps and calls are also provided to maintain compatibility with the 8048 and to provide an efficient jump within a 2K program module. Unlike the 8048, the 8051's call operations do not push the Program Status Word (PSW) to the stack along with the Program Counter, since many subroutines written for the 8051 do not affect the PSW. Hence the 8051 return operations pop only the Program Counter. The 8051's branch, call and return operations are shown diagrammatically in Figures 2.28, 2.29 and 2.30 respectively.

Figure 2.28. Unconditional Branch Operations

Figure 2.29. Call Operations

AFN-01488A-21

Figure 2.30. Return Operation

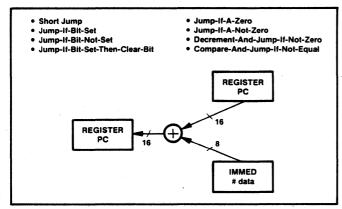

The 8051 also provides a method for performing conditional and unconditional branching relative to the starting address of the next instruction (PC - 128 to PC +127). The bit test operations allow a conditional branch to be taken on the condition of a Direct Addressed bit being set or not set. The accumulator test operations allow a conditional branch based on the accumulator being zero or non-zero. Also provided are compare-and-jump-ifnot-equal and decrement-and-compare-to-zero. These are shown in Figure 2.31.

Figure 2.31. Unconditional Short Branch and Conditional Branch Operations

The register-indirect jump in the 8051 permits branching relative to a base register (DPTR) with an offset provided by the non-signed integer value in the index register (A). This accommodates N-way branching. The indirect jump is shown in Figure 2.32.

Figure 2.32. Unconditional Branch (Indirect) Operation

## 2.7 INSTRUCTION SET

#### 2.7.1 What the Instruction Set Is

An instruction set is a set of codes that directs a computer to perform its operations. The ease of understanding the instruction set does not depend upon the structure of the machine codes that the computer recognizes, so much as it depends upon the structure of the symbolic language that is used to describe the machine codes.

The 8051 assembly language needs only forty-two mnemonics to specify the 8051's thirty-three functions. A function may have several mnemonics (e.g., MOV, MOVX, MOVC) since the function mnemonic specifies when the Program Memory or External Data Memory is used in conjunction with the Internal Data Memory. When the function mnemonics are combined with unique address combinations specified in the "destination, source" field, 111 instructions are possible. The "destination, source" field specifies the data type and the combination of addressing methods to be used to address the destination and source operands. A summary of the 8051 instruction set is provided in Table 2-1.

The syntax of most 8051 assembly language instructions consists of a function mnemonic followed by a "destination, source" operand field. Thus "MOV @R0, Data" may be interpreted as "The content of the Internal Data Memory location addressed by the content of Register 0 receives the content of the Internal Data Memory location addressed by Data." In two operand instructions, the destination address also serves as the address of the first source. As an example of this, "ANL Data, #5" may be interpreted as "The content of the Internal Data Memory location addressed by Data receives the result of the operation when the content of the memory location specified by Data is and-ed with the immediate 5."

The 8051's instruction set is an enhancement of the instruction set familiar to MCS-48 users. It is enhanced to allow expansion of on-chip CPU peripherals and to optimize byte efficiency and execution speed. Efficient use of program memory results from an instruction set consisting of 49 single-byte, 45 two-byte and 17 threebyte instructions. Most arithmetic, logical and branching operations can be performed using an instruction that appends either a short address or a long address. For example, Register Addressing allows a two byte equivalent of the three byte Direct Addressing instructions. Also, short branches are more code efficient than long branches. 64 instructions execute in twelve oscillator periods, 45 instructions execute in twenty-four oscillator periods, and multiply and divide take only forty-eight oscillator periods. The number of bytes in each instruction and the number of oscillator periods required for execution are listed in Table 2-1.

## 2.7.2 Organization of the Instruction Set

Instructions are described here in four functional groups:

- Data Transfer

- Arithmetic

- Logic

- Control Transfer

The Data Transfer, Arithmetic and Logic groups mentioned in the preceding list are further subdivided into an array of codes that specify whether the operation is to act upon immediate, RB register, accumulator, SFR or memory locations; whether bits, nibbles, bytes or doublebytes are to be processed; and what addressing methods are to be employed.

#### DATA TRANSFER

Data transfer operations are divided into three classes:

- General Purpose

- Accumulator-Specific

- Address-Object

None affect the flag settings except a POP or MOV into the PSW.

General Purpose Transfers. Three general purpose data transfer operations are provided. These may be applied to most operands, though there are specific exceptions.

- MOV performs a bit or a byte transfer from the source operand to the destination operand.

- PUSH increments the SP register and then transfers a byte from the source operand to the stack element currently addressed by SP.

- POP transfers a byte operand from the stack element addressed by the SP register to the destination operand and then decrements SP.

Accumulator-Specific Transfers. Four accumulator-specific transfer operations are provided:

- XCH exchanges the byte source operand with register A (accumulator).

- XCHD exchanges the low-order nibble of the byte source operand with the low-order nibble of register A.

- MOVX performs a byte move between the External Data Memory and the A register. The external address can be specified by the DPTR register (16-bit) or the R1 or R0 register (8-bit).

- MOVC performs the move of a byte from the Program Memory to register A as follows. The operand in the A register is used as an index into a 256-byte table pointed to by the base register (DPTR or PC). The byte operand accessed is transferred to A. MOVC is used for table-look-up byte translation and for accessing operands from code-in-line tables.

#### Address-Object Transfer

MOV DPTR,#data loads 16-bits of immediate data into a pair of destination registers, DPH and DPL (DPH from low-order address, DPL from high-order address).

#### LOGIC

The 8051 performs the basic logic operations on both bit and byte operands.

Single-Operand Operations. Seven single-operand logical operations are provided:

- CLR is used to set either the A register, the C register, or any Direct Addressed bit to zero (0).

- SETB sets either the C register or any Direct Addressed bit to one (1).

- CPL either forms the one's complement of the operand in the A register and returns the result to the A register without affecting flags or forms the one's complement of the C register or any Direct Addressed bit.

- RL, RLC, RR, RRC, SWAP. Five rotate operations can be performed on the A register; RL (rotate left), RR (rotate right), RLC (rotate left through C), RRC (rotate right through C) and SWAP (rotate left four). For RLC and RRC the C flag becomes equal to the last bit rotated out. SWAP rotates the A register left four places to exchange bits 3 through 0 with bits 7 through 4.

- **Two-Operand Operations.** Three two-operand logical operations are provided:

- ANL performs the bitwise logical conjunction of two source operands (for both bit and byte operands) and returns the result to the location of the first operand.

- ORL performs the bitwise logical inclusive disjunction of two source operands (for both bit and byte operands) and returns the result to the location of the first operand.

- XRL performs the bitwise logical exclusive disjunction of the two source operands (byte operands) and returns the result to the location of the first operand.

#### ARITHMETIC

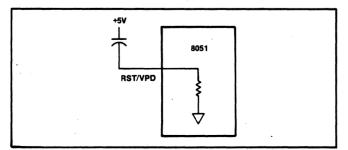

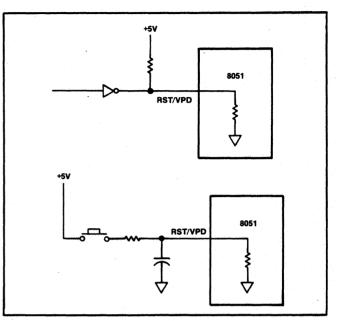

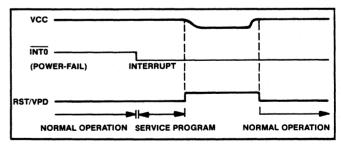

The 8051 provides the four basic mathematical operations. Only 8-bit operations using unsigned arithmetic are supported directly. The overflow flag permits the addition and subtraction operations to serve for both unsigned and signed binary integers. A correction operation is also provided to allow arithmetic to be performed directly on packed decimal (BCD) representations.