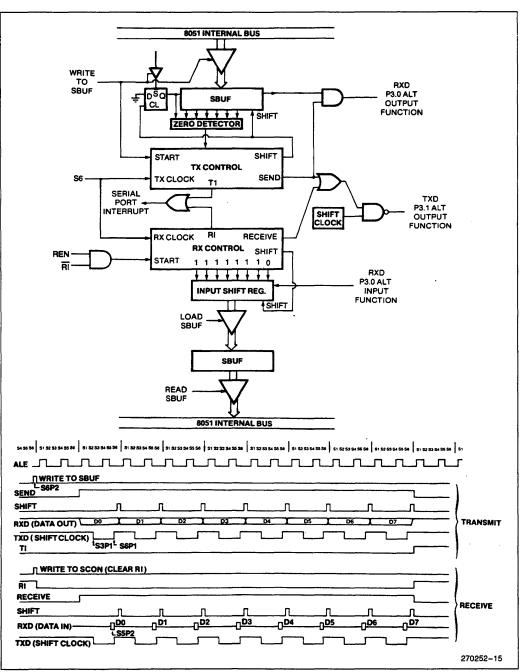

# MCS<sup>®</sup> 51 Microcontroller Family User's Manual

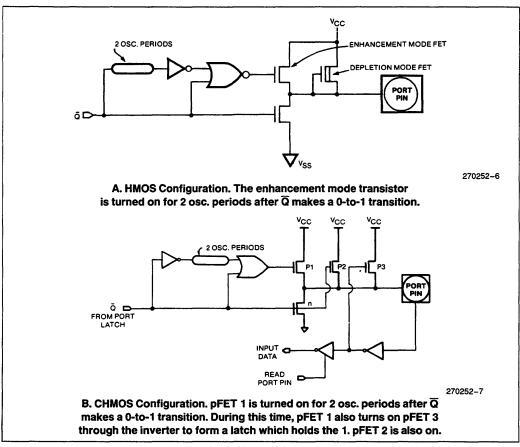

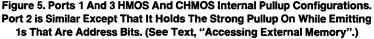

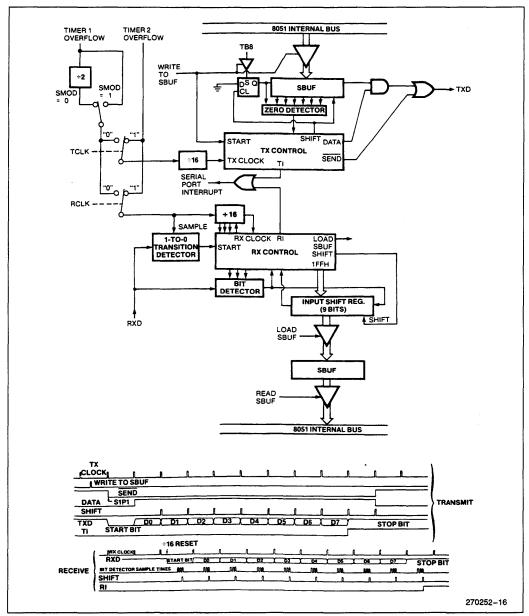

Order Number: 272383-002 February 1994

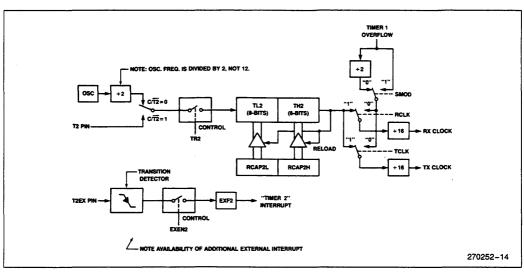

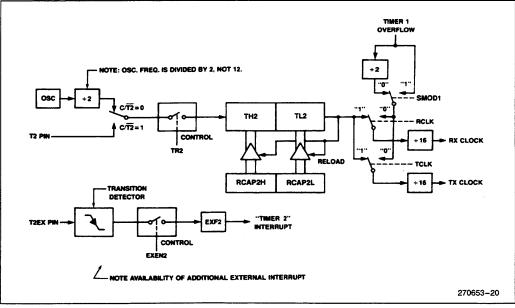

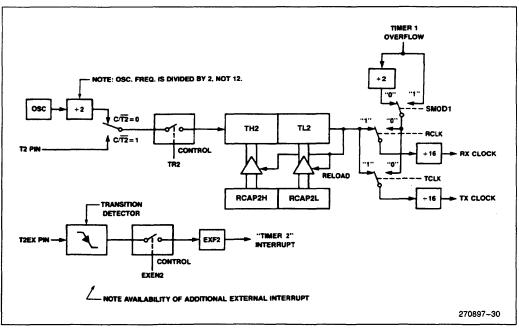

intal

intel

# MCS<sup>®</sup> 51 MICROCONTROLLER FAMILY USER'S MANUAL

ORDER NO.: 272383-002 FEBRUARY 1994

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\*Other brands and names are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

c-INTEL CORPORATION, 1993

### PAGE

### MCS® 51 MICROCONTROLLER FAMILY USER'S MANUAL

| CHAPTER 1<br>MCS 51 Family of Microcontrollers<br>Architectural Overview1-1 |

|-----------------------------------------------------------------------------|

| CHAPTER 2<br>MCS 51 Programmer's Guide and<br>Instruction Set2-1            |

| CHAPTER 3<br>8051, 8052 and 80C51 Hardware<br>Description3-1                |

| CHAPTER 4<br>8XC52/54/58 Hardware Description4-1                            |

| CHAPTER 5<br>8XC51FX Hardware Description5-1                                |

| CHAPTER 6<br>87C51GB Hardware Description6-1                                |

| CHAPTER 7<br>83C152 Hardware Description7-1                                 |

CONTENTS

MCS<sup>®</sup> 51 Family of Microcontrollers Architectural Overview

.

### ONTENTS PAGE

### MCS® 51 FAMILY OF CONTENTS MICROCONTROLLERS ARCHITECTURAL OVERVIEW MEMORY ORG

| INTRODUCTION                                          | 1-3   |

|-------------------------------------------------------|-------|

| CHMOS Devices                                         | 1-5   |

| MEMORY ORGANIZATION IN MCS <sup>®</sup> 51<br>DEVICES | 1-6   |

| Logical Separation of Program and Data<br>Memory      | 1-6   |

| Program Memory                                        | 1-7   |

| Data Memory                                           |       |

| THE MCS <sup>®</sup> 51 INSTRUCTION SET               | 1-9   |

| Program Status Word                                   | 1-9   |

| Addressing Modes                                      | .1-10 |

| Arithmetic Instructions                               | .1-10 |

| Logical Instructions                                  | .1-12 |

| Data Transfers                                        | .1-12 |

| Boolean Instructions                                  | .1-14 |

| Jump Instructions                                     |       |

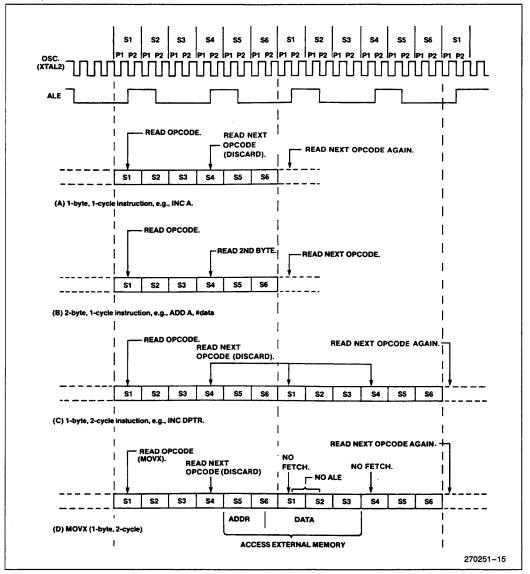

| CPU TIMING                                            | .1-17 |

| Machine Cycles                                        | .1-18 |

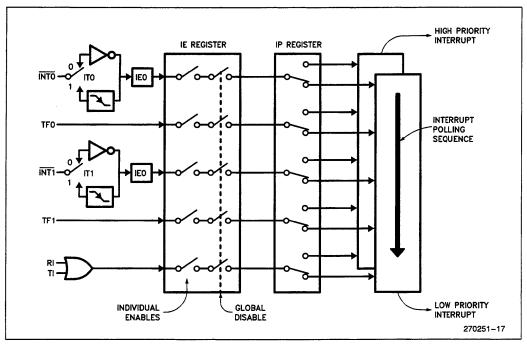

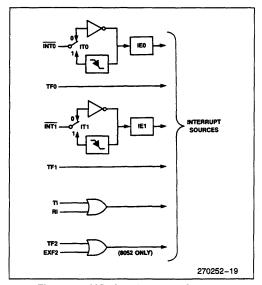

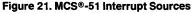

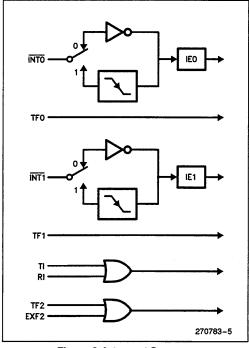

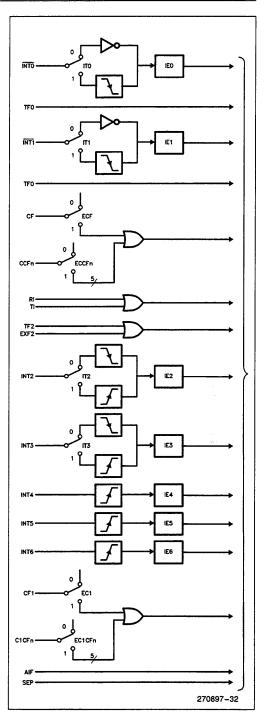

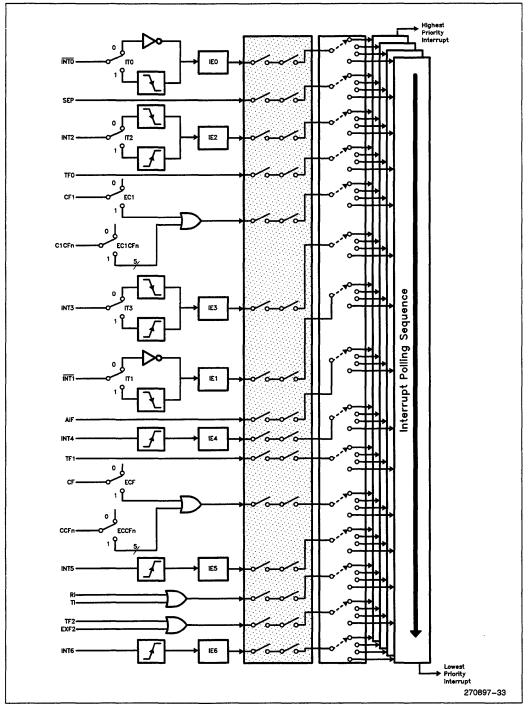

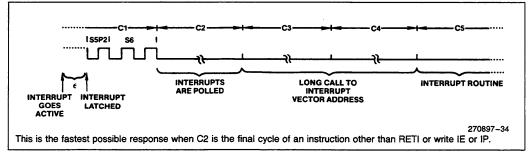

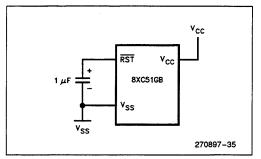

| Interrupt Structure                                   | .1-20 |

| ADDITIONAL REFERENCES                                 | .1-22 |

·

# int<sub>e</sub>l.

#### INTRODUCTION

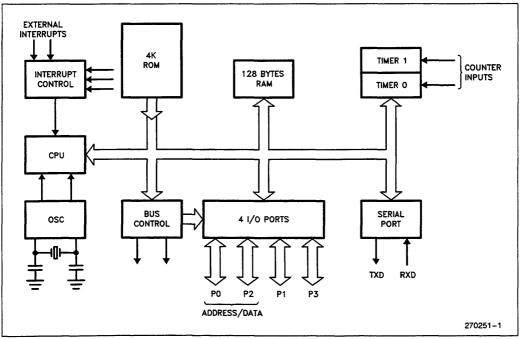

The 8051 is the original member of the MCS®-51 family, and is the core for all MCS-51 devices. The features of the 8051 core are:

- 8-bit CPU optimized for control applications

- Extensive Boolean processing (single-bit logic) capabilities

- 64K Program Memory address space

- 64K Data Memory address space

- 4K bytes of on-chip Program Memory

- 128 bytes of on-chip Data RAM

- 32 bidirectional and individually addressable I/O lines

- Two 16-bit timer/counters

- Full duplex UART

- 6-source/5-vector interrupt structure with two priority levels

- On-chip clock oscillator

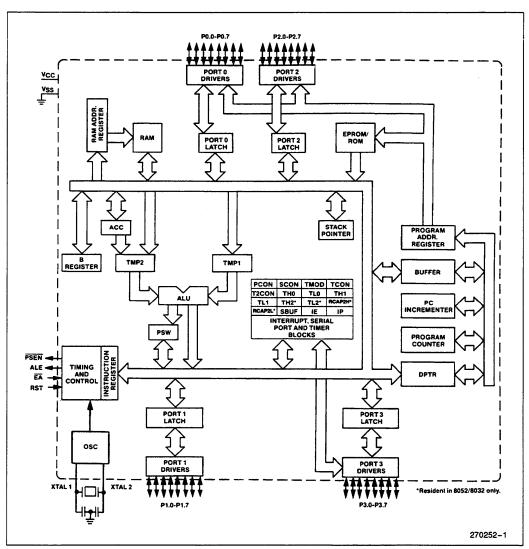

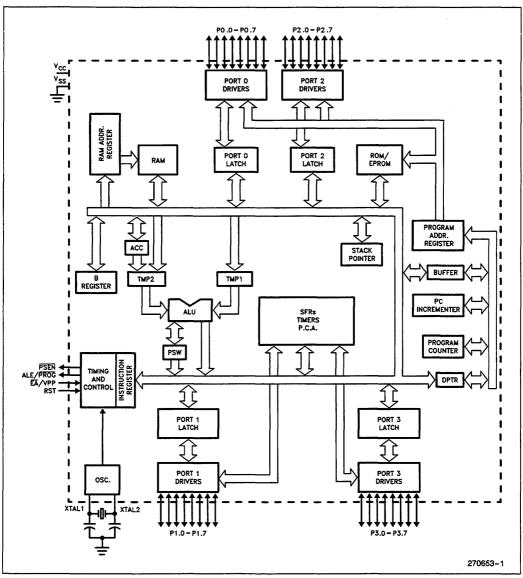

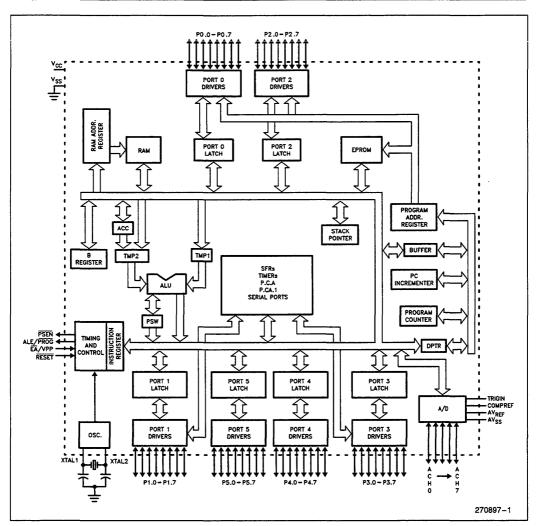

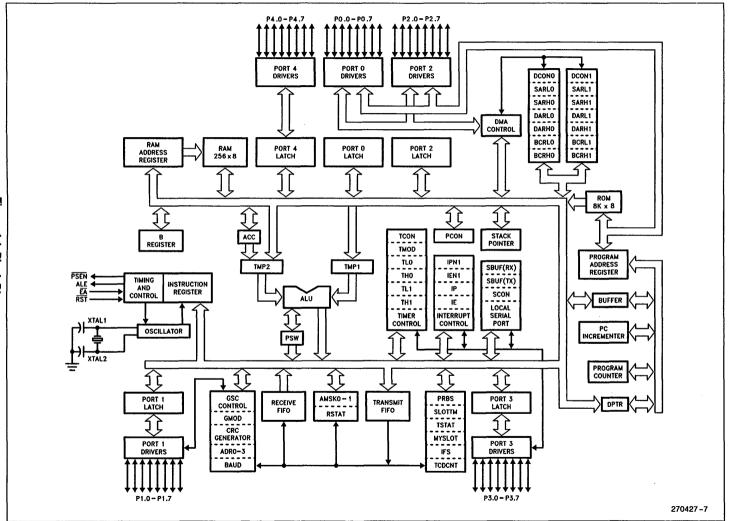

The basic architectural structure of this 8051 core is shown in Figure 1.

Figure 1. Block Diagram of the 8051 Core

### Table 1. The MCS\* 51 Family of Microcontrollers

| DEVICE      | ROM/EPROM<br>(bytes) | Register<br>RAM<br>(bytes) | Speed<br>(MHz) | l/O<br>Pins | Timer/<br>Counters | UART | Interrupt<br>Sources | PCA<br>Channels | A/D<br>Channels                         | SEP      | GSC      | DMA<br>Channels | Lock<br>Bits | Power Down<br>& Idle Modes |

|-------------|----------------------|----------------------------|----------------|-------------|--------------------|------|----------------------|-----------------|-----------------------------------------|----------|----------|-----------------|--------------|----------------------------|

| 8051 Produc | t Line               |                            | L              |             |                    |      |                      | ·               |                                         | <b>.</b> | <b>.</b> | <b>.</b>        |              |                            |

| 8031AH      | ROMLESS              | 128                        | 12             | 32          | 2                  | 1    | 5                    | 0               | 0                                       | 0        | 0        | 0               | -            | -                          |

| 8051AH      | 4K ROM               | 128                        | 12             | 32          | 2                  | 1    | 5                    | 0               | 0                                       | 0        | 0        | 0               | 0            | -                          |

| 8051AHP     | 4K ROM               | 128                        | 12             | 32          | 2                  | 1    | 5                    | 0               | 0                                       | 0        | 0        | 0               | P            | -                          |

| 8751H       | 4K EPROM             | 128                        | 12             | 32          | 2                  | 1    | 5                    | 0               | 0                                       | 0        | 0        | 0               | 1            |                            |

| 8751BH      | 4K EPROM             | 128                        | 12             | 32          | 2                  | 1    | 5                    | 0               | 0                                       | 0        | 0        | 0               | 2            | -                          |

| 8052 Produc |                      |                            |                |             |                    |      |                      |                 |                                         |          |          |                 |              | ·                          |

| 8032AH      | ROMLESS              | 256                        | 12             | 32          | 3                  | 1    | 6                    | 0               | 0                                       | 0        | 0        | 0               | -            | -                          |

| 8052AH      | 8K ROM               | 256                        | 12             | 32          | 3                  | 1    | 6                    | 0               | 0                                       | 0        | 0        | 0               | 0            | -                          |

| 8752BH      | 8K EPROM             | 256                        | 12             | 32          | 3                  | 1    | 6                    | 0               | 0                                       | 0        | 0        | 0               | 2            | -                          |

| 80C51 Produ |                      |                            |                |             |                    |      |                      |                 |                                         |          |          |                 |              |                            |

| 80C31BH     | ROMLESS              | 128                        | 12,16          | 32          | 2                  | 1    | 5                    | 0               | 0                                       | 0        | 0        | 0               | -            | Yes                        |

| 80C51BH     | 4K ROM               | 128                        | 12,16          | 32          | 2                  | 1    | 5                    | 0               | 0                                       | 0        | 0        | 0               | 0            | Yes                        |

| 80C51BHP    | 4K ROM               | 128                        | 12,16          | 32          | 2                  | 1    | 5                    | 0               | 0                                       | 0        | 0        | 0               | Р            | Yes                        |

| 87C51       | 4K EPROM             | 128                        | 12,16,20,24    | 32          | 2                  | 1    | 5                    | 0               | 0                                       | 0        | 0        | 0               | 3            | Yes                        |

| 8XC52/54/58 | Product Line         |                            | · · ·          |             | ·                  |      | ·                    | +               |                                         |          | ·        | 4.0.0           |              | ·                          |

| 80C32       | ROMLESS              | 256                        | 12,16,20,24    | 32          | 3                  | 1    | 6                    | 0               | 0                                       | 0        | 0        | 0               | -            | Yes                        |

| 80C52       | 8K ROM               | 256                        | 12,16,20,24    | 32          | 3                  | 1    | 6                    | 0               | 0                                       | 0        | 0        | 0               | 1*           | Yes                        |

| 87C52       | 8K EPROM             | 256                        | 12,16,20,24    | 32          | 3                  | 1    | 6                    | 0               | 0                                       | 0        | 0        | 0               | 3            | Yes                        |

| 80C54       | 16K ROM              | 256                        | 12,16,20,24    | 32          | 3                  | 1    | 6                    | 0               | 0                                       | 0        | 0        | 0               | 1            | Yes                        |

| 87C54       | 16K EPROM            | 256                        | 12,16,20,24    | 32          | 3                  | 1    | 6                    | 0               | 0                                       | 0        | 0        | 0               | 3            | Yes                        |

| 80C58       | 32K ROM              | 256                        | 12,16,20,24    | 32          | 3                  | 1    | 6                    | 0               | 0                                       | 0        | 0        | 0               | 1            | Yes                        |

| 87C58       | 32K EPROM            | 256                        | 12,16,20,24    | 32          | 3                  | 1    | 6                    | 0               | 0                                       | 0        | 0        | 0               | 3            | Yes                        |

| 8XL52/54/58 | Product Line         |                            |                |             | •                  |      |                      | 4               | • • • • • • • • • • • • • • • • • • • • | •        | ·        |                 |              | L                          |

| 80L52       | 8K ROM               | 256                        | 12,16,20*      | 32          | 3                  | 1    | 6                    | 0               | 0                                       | 0        | 0        | 0               | 1            | Yes                        |

| 87L52       | 8K OTP ROM           | 256                        | 12,16,20*      | 32          | 3                  | 1    | 6                    | 0               | 0                                       | 0        | 0        | 0               | 3            | Yes                        |

| 80L54       | 18K ROM              | 256                        | 12,16,20*      | 32          | 3                  | 1    | 6                    | 0               | 0                                       | 0        | 0        | 0               | 1            | Yes                        |

| 87L54       | 16K OTP ROM          | 256                        | 12,16,20*      | 32          | 3                  | 1    | 6                    | Ö               | 0                                       | Ō        | 0        | 0               | 3            | Yes                        |

| 80L58       | 32K ROM              | 256                        | 12,16,20*      | 32          | 3                  | 1    | 6                    | ō               | Ö                                       | Ō        | Ō        | Ö               | 1            | Yes                        |

| 87L58       | 32K OTP ROM          | 256                        | 12,16,20*      | 32          | 3                  | 1    | 6                    | 0               | ŏ                                       | 0        | 0        | 0               | 3            | Yes                        |

#### Table 1. The MCS® 51 Family of Microcontrollers

| DEVICE                                 | ROM/EPROM<br>(bytes) | Register<br>RAM               | Speed<br>(MHz)             | I/O<br>Pins                         | Timer/<br>Counters                           | UART        | Interrupt<br>Sources | PCA<br>Channels                         | A/D<br>Channels                       | SEP | GSC | DMA<br>Channels | Lock<br>Bits | Power Down<br>& Idle Modes |

|----------------------------------------|----------------------|-------------------------------|----------------------------|-------------------------------------|----------------------------------------------|-------------|----------------------|-----------------------------------------|---------------------------------------|-----|-----|-----------------|--------------|----------------------------|

|                                        | ,                    | (bytes)                       |                            |                                     |                                              |             |                      |                                         |                                       |     |     |                 |              |                            |

| BXC51FA/FB/                            | C Product Line       |                               |                            | L                                   |                                              | -d          | ·····                |                                         | · · · · · · · · · · · · · · · · · · · |     |     |                 |              | h                          |

| 80C51FA                                | ROMLESS              | 256                           | 12,16                      | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | -            | Yes                        |

| 83C51FA                                | 8K ROM               | 256                           | 12,16                      | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | 0            | Yes                        |

| 87C51FA                                | 8K EPROM             | 256                           | 12,16,20,24                | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | 3            | Yes                        |

| 83C51FB                                | 16K ROM              | 256                           | 12,16,20,24                | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | 1            | Yes                        |

| 87C51FB                                | 16K EPROM            | 256                           | 12,16,20,24                | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | 3            | Yes                        |

| 83C51FC                                | 32K ROM              | 256                           | 12,16,20,24                | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | 1            | Yes                        |

| 87C51FC                                | 32K EPROM            | 256                           | 12,16,20,24                | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | 3            | Yes                        |

| BXL51FA/FB/                            | C Product Line       | L                             | [                          | (                                   | L                                            |             |                      | 1                                       |                                       |     | ·   |                 | 1            | (                          |

| 80L51FA                                | ROMLESS              | 256                           | 12,16,20*                  | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | -            | Yes                        |

| B3L51FA                                | 8K ROM               | 256                           | 12,16,20*                  | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | 1            | Yes                        |

| 87L51FA                                | 8K OTP ROM           | 256                           | 12,16,20*                  | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | 3            | Yes                        |

| B3L51FB                                | 16K ROM              | 256                           | 12,16,20*                  | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | 1            | Yes                        |

| B7L51FB                                | 16K OTP ROM          | 256                           | 12,16,20*                  | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | 3            | Yes                        |

| 33L51FC                                | 32K ROM              | 256                           | 12,16,20*                  | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | 1            | Yes                        |

| 37L51FC                                | 32K OTP ROM          | 256                           | 12,16,20*                  | 32                                  | 3                                            | 1           | 7                    | 5                                       | 0                                     | 0   | 0   | 0               | 3            | Yes                        |

| BXC51GX Pro                            |                      |                               |                            |                                     |                                              |             |                      |                                         |                                       |     |     |                 |              |                            |

| 30C51GB                                | ROMLESS              | 256                           | 12,16                      | 48                                  | 3                                            | 1           | 15                   | 10                                      | 8                                     | 1   | 0   | 0               | -            | Yes                        |

| 33C51GB                                | 8K ROM               | 256                           | 12,16                      | 48                                  | 3                                            | 1           | 15                   | 10                                      | 8                                     | 1   | 0   | 0               | 1            | Yes                        |

| 87C51GB                                | 8K EPROM             | 256                           | 12,16                      | 48                                  | 3                                            | 1           | 15                   | 10                                      | 8                                     | 1   | · 0 | 0               | 3            | Yes                        |

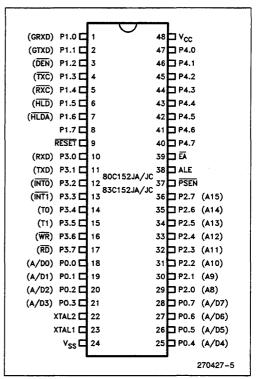

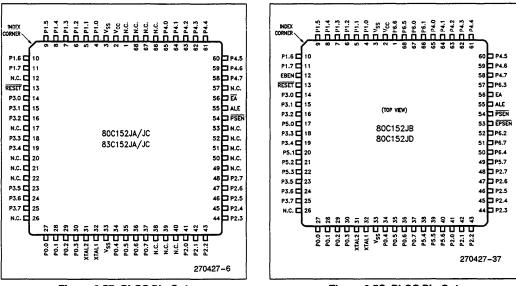

| SXC152 Produ                           |                      |                               |                            |                                     |                                              |             |                      |                                         |                                       |     |     |                 |              |                            |

| 80C152JA                               | ROMLESS              | 256                           | 16.5                       | 40                                  | 2                                            | 1           | 11                   | 0                                       | 0                                     | 1   | 1   | 2               | -            | Yes                        |

| 80C152JB                               | ROMLESS              | 256                           | 16.5                       | 56                                  | 2                                            | 1           | 11                   | 0                                       | 0                                     | 1   | 1   | 2               | -            | Yes                        |

| 83C152JA                               | 8K ROM               | 256                           | 16.5                       | 40                                  | 2                                            | 1           | 11                   | 0                                       | 0                                     | 1   | 1   | 2               | 0            | Yes                        |

| 8XC51SL Pro                            |                      |                               |                            |                                     |                                              |             |                      | T                                       |                                       |     |     |                 |              |                            |

| 30C51SL-BG                             | ROMLESS              | 256                           | 16                         | 24                                  | 2                                            | 1           | 10                   | 0                                       | 4                                     | 0   | 1   | 0               | -            | Yes                        |

| B1C51SL-BG                             | 8K *ROM              | 256                           | 16                         | 24                                  | 2                                            | 1           | 10                   | 0                                       | 4                                     | 0   | 1   | 0               | 0            | Yes                        |

| 33C51SL-BG                             | 8K ROM               | 256                           | 16                         | 24                                  | 2                                            | 1           | 10                   | 0                                       | 4                                     | 0   | 1   | 0               | 0            | Yes                        |

| BOC51SLAH                              | ROMLESS              | 256                           | 16                         | 24                                  | 2                                            | 1           | 10                   | 0                                       | 4                                     | 0   | 1   | 0               |              | Yes                        |

| B1C51SLAH                              | 16K *ROM             | 256                           | 16                         | 24                                  | 2                                            | 1           | 10                   | 0                                       | 4                                     | 0   | 1   | 0               | 0            | Yes                        |

| B3C51SLAH                              | 16K ROM              | 256                           | 16                         | 24                                  | 2                                            | 1           | 10                   | 0                                       | 4                                     | 0   | 1   | 0               | 0            | Yes                        |

| B7C51SLAH                              | 16K EPROM            | 256                           | 16                         | 24                                  | 2                                            | 1           | 10                   | 0                                       | 4                                     | 0   | 1   | 0               | 0            | Yes                        |

| 30C51SLAL                              | ROMLESS              | 256                           | 16                         | 24                                  | 2                                            | 1           | 10                   | 0                                       | 4                                     | 0   |     | 0               |              | Yes                        |

| B1C51SLAL                              | 16K *ROM             | 256                           | 16                         | 24                                  | 2                                            | 1           | 10                   | 0                                       | 4                                     | 0   | 1   | 0               | 0            | Yes                        |

| B3C51SLAL                              | 16K ROM              | 256                           | 16                         | 24                                  | 2                                            | 1           | 10                   | 0                                       | 4                                     | 0   | 1   | 0               | 0            | Yes                        |

| 37C51SLAL                              | 16K EPROM            | 256                           | 16                         | 24                                  | 2                                            | 1           | 10                   | 0                                       | 4                                     | 0   | 1   | 0               | 0            | Yes                        |

| OM/OTP ROM<br>peed (Mhz):<br>ock Bits: | //EPROM (bytes):     | *ROM<br>24i<br>20*<br>1*<br>P | = 20MHz Av<br>= 1 Lock Bit | ternal-on<br>ailable fo<br>for 20MF | ly operation<br>or Commerica<br>Iz & 24MHz p | parts, no l | ock Bit for 1        | Only<br>2 & 16MHz pa<br>s limited to 4K |                                       |     |     |                 |              |                            |

| XC152 Produc                           | t l ine*             | •                             | = Communic                 |                                     |                                              |             |                      |                                         |                                       |     |     |                 |              |                            |

| XC51SL Product                         |                      |                               | = Kevboard                 |                                     |                                              |             |                      |                                         |                                       |     |     |                 |              |                            |

|                                        |                      |                               |                            |                                     |                                              |             |                      |                                         |                                       |     |     |                 |              |                            |

**MCS®-51 ARCHITECTURAL OVERVIEW**

intel

8XC152 Product Line\* 8XC51SL Product Line\*

= Keyboard Controller

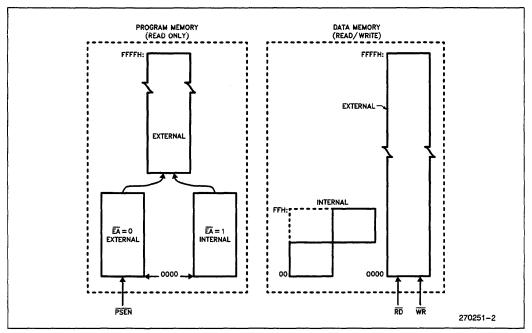

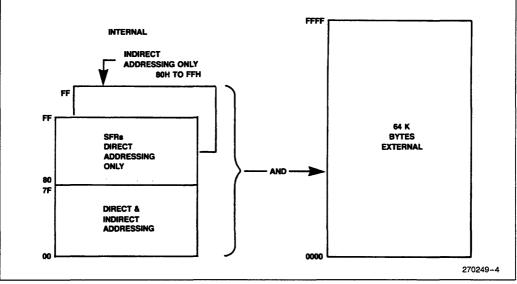

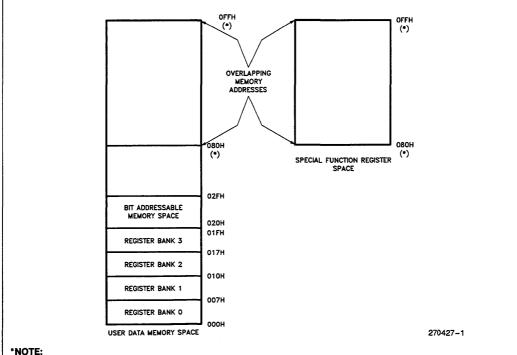

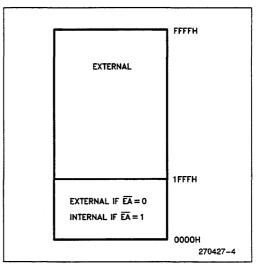

Figure 2. MCS®-51 Memory Structure

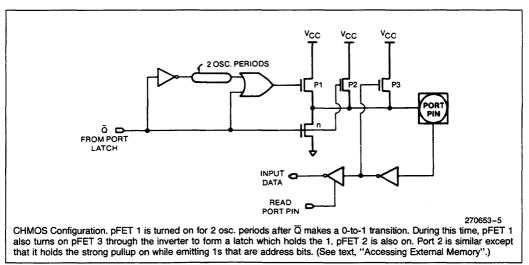

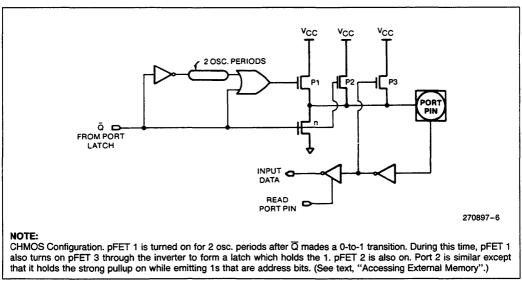

#### **CHMOS Devices**

int\_.

Functionally, the CHMOS devices (designated with "C" in the middle of the device name) are all fully compatible with the 8051, but being CMOS, draw less current than an HMOS counterpart. To further exploit the power savings available in CMOS circuitry, two reduced power modes are added:

- Software-invoked Idle Mode, during which the CPU is turned off while the RAM and other on-chip peripherals continue operating. In this mode, current draw is reduced to about 15% of the current drawn when the device is fully active.

- Software-invoked Power Down Mode, during which all on-chip activities are suspended. The on-chip RAM continues to hold its data. In this mode the device typically draws less than 10 μA.

Although the 80C51BH is functionally compatible with its HMOS counterpart, specific differences between the two types of devices must be considered in the design of an application circuit if one wishes to ensure complete interchangeability between the HMOS and CHMOS devices. These considerations are discussed in the Application Note AP-252, "Designing with the 80C51BH".

For more information on the individual devices and features listed in Table 1, refer to the Hardware Descriptions and Data Sheets of the specific device.

# MEMORY ORGANIZATION IN MCS®-51 DEVICES

# Logical Separation of Program and Data Memory

All MCS-51 devices have separate address spaces for Program and Data Memory, as shown in Figure 2. The logical separation of Program and Data Memory allows the Data Memory to be accessed by 8-bit addresses, which can be more quickly stored and manipulated by an 8-bit CPU. Nevertheless, 16-bit Data Memory addresses can also be generated through the DPTR register.

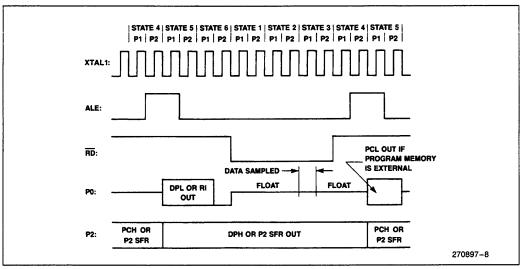

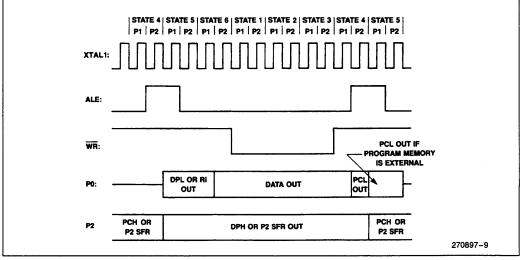

Program Memory can only be read, not written to. There can be up to 64K bytes of Program Memory. In the ROM and EPROM versions of these devices the lowest 4K, 8K or 16K bytes of Program Memory are provided on-chip. Refer to Table 1 for the amount of on-chip ROM (or EPROM) on each device. In the ROMless versions all Program Memory is external. The read strobe for external Program Memory is the signal PSEN (Program Store Enable). Data Memory occupies a separate address space from Program Memory. Up to 64K bytes of external RAM can be addressed in the external Data Memory space. The CPU generates read and write signals, RD and WR, as needed during external Data Memory accesses.

External Program Memory and external Data Memory may be combined if desired by applying the  $\overline{\text{RD}}$  and  $\overline{\text{PSEN}}$  signals to the inputs of an AND gate and using the output of the gate as the read strobe to the external Program/Data memory.

#### **Program Memory**

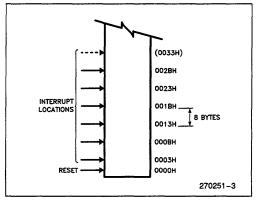

Figure 3 shows a map of the lower part of the Program Memory. After reset, the CPU begins execution from location 0000H.

As shown in Figure 3, each interrupt is assigned a fixed location in Program Memory. The interrupt causes the CPU to jump to that location, where it commences execution of the service routine. External Interrupt 0, for example, is assigned to location 0003H. If External Interrupt 0 is going to be used, its service routine must begin at location 0003H. If the interrupt is not going to be used, its service location is available as general purpose Program Memory.

Figure 3. MCS®-51 Program Memory

The interrupt service locations are spaced at 8-byte intervals: 0003H for External Interrupt 0, 000BH for Timer 0, 0013H for External Interrupt 1, 001BH for Timer 1, etc. If an interrupt service routine is short enough (as is often the case in control applications), it can reside entirely within that 8-byte interval. Longer service routines can use a jump instruction to skip over subsequent interrupt locations, if other interrupts are in use. The lowest 4K (or 8K or 16K) bytes of Program Memory can be either in the on-chip ROM or in an external ROM. This selection is made by strapping the  $\overline{EA}$  (External Access) pin to either V<sub>CC</sub> or V<sub>SS</sub>.

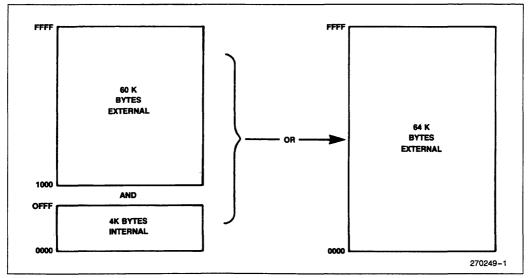

In the 4K byte ROM devices, if the  $\overline{EA}$  pin is strapped to V<sub>CC</sub>, then program fetches to addresses 0000H through 0FFFH are directed to the internal ROM. Program fetches to addresses 1000H through FFFFH are directed to external ROM.

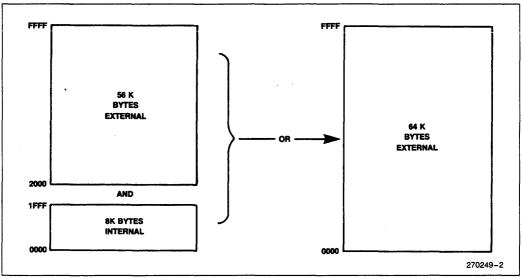

In the 8K byte ROM devices,  $\overline{EA} = V_{CC}$  selects addresses 0000H through 1FFFH to be internal, and addresses 2000H through FFFFH to be external.

In the 16K byte ROM devices,  $\overline{EA} = V_{CC}$  selects addresses 0000H through 3FFFH to be internal, and addresses 4000H through FFFFH to be external.

If the  $\overline{EA}$  pin is strapped to  $V_{SS}$ , then all program fetches are directed to external ROM. The ROMless parts must have this pin externally strapped to  $V_{SS}$  to enable them to execute properly.

The read strobe to external ROM,  $\overline{\text{PSEN}}$ , is used for all external program fetches.  $\overline{\text{PSEN}}$  is not activated for internal program fetches.

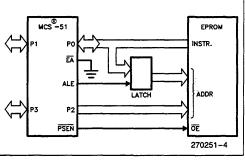

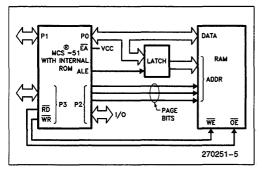

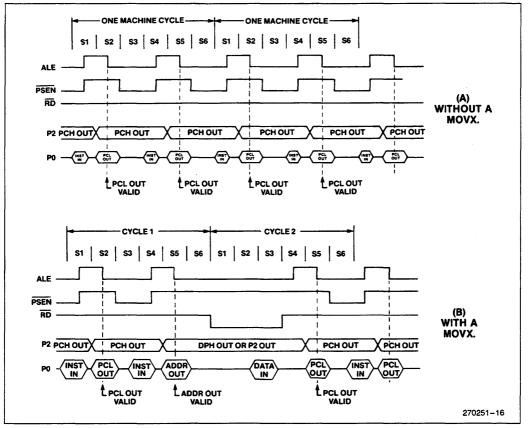

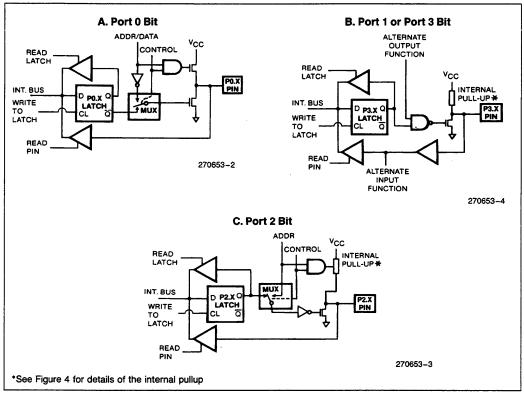

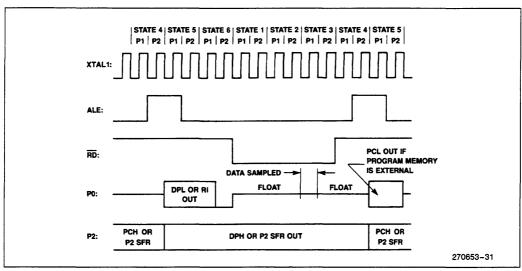

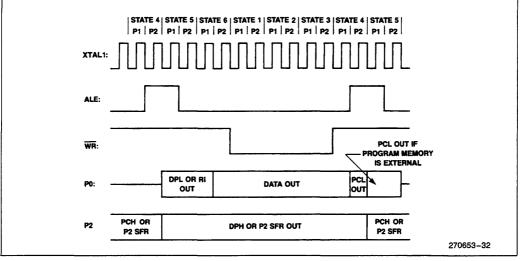

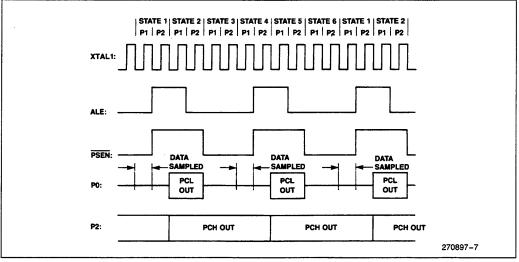

Figure 4. Executing from External Program Memory

The hardware configuration for external program execution is shown in Figure 4. Note that 16 I/O lines (Ports 0 and 2) are dedicated to bus functions during external Program Memory fetches. Port 0 (P0 in Figure 4) serves as a multiplexed address/data bus. It emits the low byte of the Program Counter (PCL) as an address, and then goes into a float state awaiting the arrival of the code byte from the Program Memory. During the time that the low byte of the Program Counter is valid on P0, the signal ALE (Address Latch Enable) clocks this byte into an address latch. Meanwhile, Port 2 (P2 in Figure 4) emits the high byte of the Program Counter (PCH). Then  $\overline{PSEN}$  strobes the EPROM and the code byte is read into the microcontroller. Program Memory addresses are always 16 bits wide, even though the actual amount of Program Memory used may be less than 64K bytes. External program execution sacrifices two of the 8-bit ports, P0 and P2, to the function of addressing the Program Memory.

#### **Data Memory**

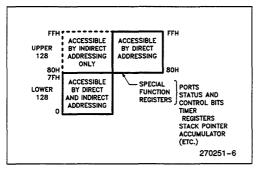

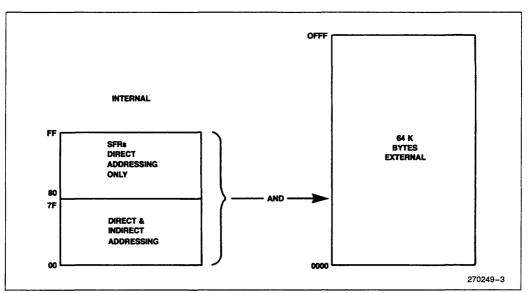

The right half of Figure 2 shows the internal and external Data Memory spaces available to the MCS-51 user.

Figure 5 shows a hardware configuration for accessing up to 2K bytes of external RAM. The CPU in this case is executing from internal ROM. Port 0 serves as a multiplexed address/data bus to the RAM, and 3 lines of Port 2 are being used to page the RAM. The CPU generates  $\overline{RD}$  and  $\overline{WR}$  signals as needed during external RAM accesses.

#### Figure 5. Accessing External Data Memory. If the Program Memory is Internal, the Other Bits of P2 are Available as I/O.

There can be up to 64K bytes of external Data Memory. External Data Memory addresses can be either 1 or 2 bytes wide. One-byte addresses are often used in conjunction with one or more other I/O lines to page the RAM, as shown in Figure 5. Two-byte addresses can also be used, in which case the high address byte is emitted at Port 2.

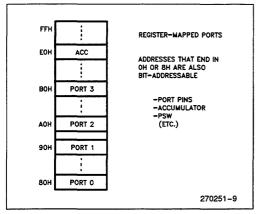

Figure 6. Internal Data Memory

Internal Data Memory is mapped in Figure 6. The memory space is shown divided into three blocks, which are generally referred to as the Lower 128, the Upper 128, and SFR space.

Internal Data Memory addresses are always one byte wide, which implies an address space of only 256 bytes. However, the addressing modes for internal RAM can in fact accommodate 384 bytes, using a simple trick. Direct addresses higher than 7FH access one memory space, and indirect addresses higher than 7FH access a different memory space. Thus Figure 6 shows the Upper 128 and SFR space occupying the same block of addresses, 80H through FFH, although they are physically separate entities.

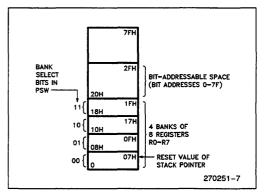

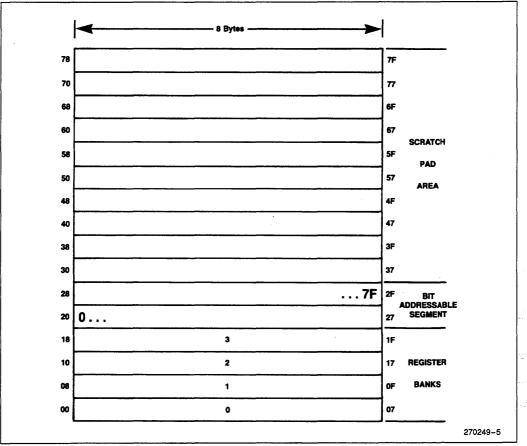

Figure 7. The Lower 128 Bytes of Internal RAM

The Lower 128 bytes of RAM are present in all MCS-51 devices as mapped in Figure 7. The lowest 32 bytes are grouped into 4 banks of 8 registers. Program instructions call out these registers as R0 through R7. Two bits in the Program Status Word (PSW) select which register bank is in use. This allows more efficient use of code space, since register instructions are shorter than instructions that use direct addressing.

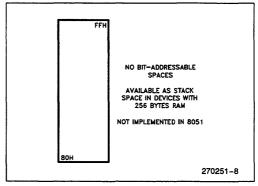

Figure 8. The Upper 128 Bytes of Internal RAM

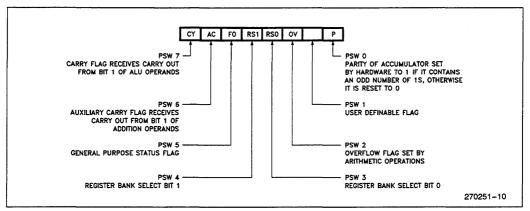

Figure 10. PSW (Program Status Word) Register in MCS®-51 Devices

The next 16 bytes above the register banks form a block of bit-addressable memory space. The MCS-51 instruction set includes a wide selection of single-bit instructions, and the 128 bits in this area can be directly addressed by these instructions. The bit addresses in this area are 00H through 7FH.

int\_l.

All of the bytes in the Lower 128 can be accessed by either direct or indirect addressing. The Upper 128 (Figure 8) can only be accessed by indirect addressing. The Upper 128 bytes of RAM are not implemented in the 8051, but are in the devices with 256 bytes of RAM. (See Table 1).

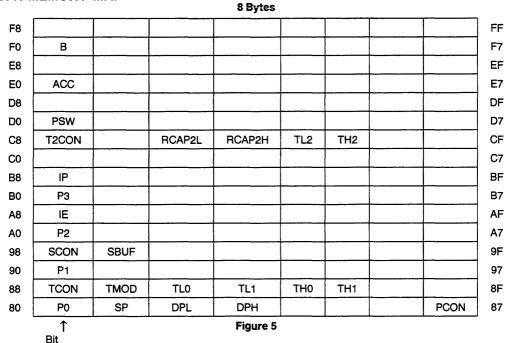

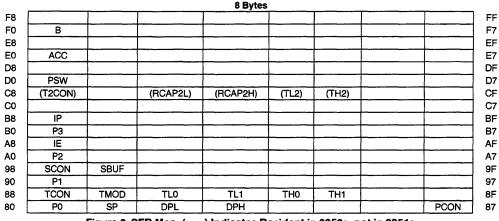

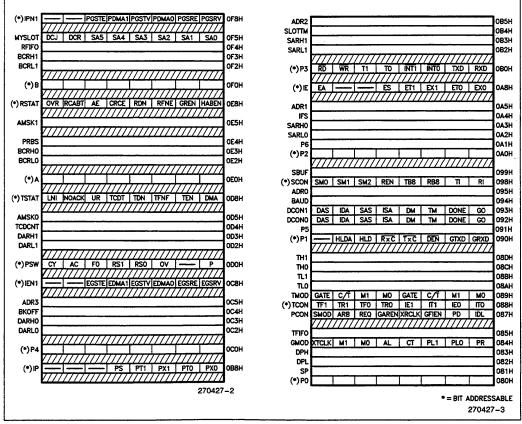

Figure 9 gives a brief look at the Special Function Register (SFR) space. SFRs include the Port latches, timers, peripheral controls, etc. These registers can only be accessed by direct addressing. In general, all MCS-51 microcontrollers have the same SFRs as the 8051, and at the same addresses in SFR space. However, enhancements to the 8051 have additional SFRs that are not present in the 8051, nor perhaps in other proliferations of the family.

Sixteen addresses in SFR space are both byte- and bitaddressable. The bit-addressable SFRs are those whose address ends in 000B. The bit addresses in this area are 80H through FFH.

#### **THE MCS®-51 INSTRUCTION SET**

All members of the MCS-51 family execute the same instruction set. The MCS-51 instruction set is optimized for 8-bit control applications. It provides a variety of fast addressing modes for accessing the internal RAM to facilitate byte operations on small data structures. The instruction set provides extensive support for one-bit variables as a separate data type, allowing direct bit manipulation in control and logic systems that require Boolean processing.

An overview of the MCS-51 instruction set is presented below, with a brief description of how certain instructions might be used. References to "the assembler" in this discussion are to Intel's MCS-51 Macro Assembler, ASM51. More detailed information on the instruction set can be found in the MCS-51 Macro Assembler User's Guide (Order No. 9800937 for ISIS Systems, Order No. 122752 for DOS Systems).

#### **Program Status Word**

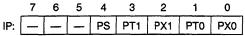

The Program Status Word (PSW) contains several status bits that reflect the current state of the CPU. The PSW, shown in Figure 10, resides in SFR space. It contains the Carry bit, the Auxiliary Carry (for BCD operations), the two register bank select bits, the Overflow flag, a Parity bit, and two user-definable status flags.

The Carry bit, other than serving the functions of a Carry bit in arithmetic operations, also serves as the "Accumulator" for a number of Boolean operations.

Figure 9. SFR Space

The bits RS0 and RS1 are used to select one of the four register banks shown in Figure 7. A number of instructions refer to these RAM locations as R0 through R7. The selection of which of the four banks is being referred to is made on the basis of the bits RS0 and RS1 at execution time.

The Parity bit reflects the number of 1s in the Accumulator: P = 1 if the Accumulator contains an odd number of 1s, and P = 0 if the Accumulator contains an even number of 1s. Thus the number of 1s in the Accumulator plus P is always even.

Two bits in the PSW are uncommitted and may be used as general purpose status flags.

#### Addressing Modes

The addressing modes in the MCS-51 instruction set are as follows:

#### DIRECT ADDRESSING

In direct addressing the operand is specified by an 8-bit address field in the instruction. Only internal Data RAM and SFRs can be directly addressed.

#### INDIRECT ADDRESSING

In indirect addressing the instruction specifies a register which contains the address of the operand. Both internal and external RAM can be indirectly addressed.

The address register for 8-bit addresses can be R0 or R1 of the selected register bank, or the Stack Pointer. The address register for 16-bit addresses can only be the 16-bit "data pointer" register, DPTR.

#### **REGISTER INSTRUCTIONS**

The register banks, containing registers R0 through R7, can be accessed by certain instructions which carry a 3-bit register specification within the opcode of the instruction. Instructions that access the registers this way are code efficient, since this mode eliminates an address byte. When the instruction is executed, one of the eight registers in the selected bank is accessed. One of four banks is selected at execution time by the two bank select bits in the PSW.

#### **REGISTER-SPECIFIC INSTRUCTIONS**

Some instructions are specific to a certain register. For example, some instructions always operate on the Accumulator, or Data Pointer, etc., so no address byte is needed to point to it. The opcode itself does that. Instructions that refer to the Accumlator as A assemble as accumulator-specific opcodes.

#### **IMMEDIATE CONSTANTS**

The value of a constant can follow the opcode in Program Memory. For example,

MOV A, #100

loads the Accumulator with the decimal number 100. The same number could be specified in hex digits as 64H.

#### INDEXED ADDRESSING

Only Program Memory can be accessed with indexed addressing, and it can only be read. This addressing mode is intended for reading look-up tables in Program Memory. A 16-bit base register (either DPTR or the Program Counter) points to the base of the table, and the Accumulator is set up with the table entry number. The address of the table entry in Program Memory is formed by adding the Accumulator data to the base pointer.

Another type of indexed addressing is used in the "case jump" instruction. In this case the destination address of a jump instruction is computed as the sum of the base pointer and the Accumulator data.

#### **Arithmetic Instructions**

The menu of arithmetic instructions is listed in Table 2. The table indicates the addressing modes that can be used with each instruction to access the  $\langle byte \rangle$  operand. For example, the ADD A,  $\langle byte \rangle$  instruction can be written as:

| ADD | A,7FH          | (direct addressing)   |

|-----|----------------|-----------------------|

| ADD | A,@R0          | (indirect addressing) |

| ADD | A,R7           | (register addressing) |

| ADD | <b>A,</b> #127 | (immediate constant)  |

The execution times listed in Table 2 assume a 12 MHz clock frequency. All of the arithmetic instructions execute in 1  $\mu$ s except the INC DPTR instruction, which takes 2  $\mu$ s, and the Multiply and Divide instructions, which take 4  $\mu$ s.

Note that any byte in the internal Data Memory space can be incremented or decremented without going through the Accumulator.

One of the INC instructions operates on the 16-bit Data Pointer. The Data Pointer is used to generate 16-bit addresses for external memory, so being able to increment it in one 16-bit operation is a useful feature.

The MUL AB instruction multiplies the Accumulator by the data in the B register and puts the 16-bit product into the concatenated B and Accumulator registers.

| Mnemonic              | Operation                                         |                | Execution |             |     |           |

|-----------------------|---------------------------------------------------|----------------|-----------|-------------|-----|-----------|

| Milenonic             | Operation                                         | Dir            | Ind       | Reg         | Imm | Time (μs) |

| ADD A, <byte></byte>  | $A = A + \langle byte \rangle$                    | X              | X         | X           | X   | 1         |

| ADDC A, <byte></byte> | $A = A + \langle byte \rangle + C$                | X              | X         | X           | X   | 1         |

| SUBB A, <byte></byte> | $A = A - \langle byte \rangle - C$                | X              | X         | Х           | Х   | 1         |

| INC A                 | A = A + 1                                         |                | Accum     | ulator only |     | 1         |

| INC <byte></byte>     | $\langle byte \rangle = \langle byte \rangle + 1$ | Х              | X         | X           |     | 1         |

| INC DPTR              | DPTR = DPTR + 1                                   |                | 2         |             |     |           |

| DEC A                 | A = A - 1                                         |                | 1         |             |     |           |

| DEC <byte></byte>     | <byte> = <byte> - 1</byte></byte>                 | х              | X         | Х           |     | 1         |

| MUL AB                | $B:A = B \times A$                                |                | ACC a     | nd B only   |     | 4         |

| DIV AB                | A = Int [A/B]<br>B = Mod [A/B]                    | ACC and B only |           |             |     | 4         |

| DA A                  | Decimal Adjust                                    |                | 1         |             |     |           |

The DIV AB instruction divides the Accumulator by the data in the B register and leaves the 8-bit quotient in the Accumulator, and the 8-bit remainder in the B register.

Oddly enough, DIV AB finds less use in arithmetic "divide" routines than in radix conversions and programmable shift operations. An example of the use of DIV AB in a radix conversion will be given later. In shift operations, dividing a number by  $2^n$  shifts its n bits to the right. Using DIV AB to perform the division completes the shift in 4  $\mu$ s and leaves the B register holding the bits that were shifted out.

The DA A instruction is for BCD arithmetic operations. In BCD arithmetic, ADD and ADDC instructions should always be followed by a DA A operation, to ensure that the result is also in BCD. Note that DA A will not convert a binary number to BCD. The DA A operation produces a meaningful result only as the second step in the addition of two BCD bytes.

| Mnemonic |                     | Operation                                 | A                | ddress | Execution |     |           |

|----------|---------------------|-------------------------------------------|------------------|--------|-----------|-----|-----------|

|          |                     | operation                                 | Dir              | Ind    | Reg       | Imm | Time (μs) |

| ANL      | A, <byte></byte>    | A = A .AND. <byte></byte>                 | X                | X      | X         | X   | 1         |

| ANL      | <byte>,A</byte>     | <byte> = <byte> .AND. A</byte></byte>     | X                |        |           |     | 1         |

| ANL      | <byte>,#data</byte> | <byte> = <byte> .AND. #data</byte></byte> | X                |        |           |     | 2         |

| ORL      | A, <byte></byte>    | A = A .OR. <byte></byte>                  | X                | X      | X         | X   | 1         |

| ORL      | <byte>,A</byte>     | <byte> = <byte> .OR. A</byte></byte>      | X                |        |           |     | 1         |

| ORL      | <byte>,#data</byte> | <byte> = <byte> .OR. #data</byte></byte>  | X                |        |           |     | 2         |

| XRL      | A, <byte></byte>    | A = A .XOR. <byte></byte>                 | X                | X      | X         | X   | 1         |

| XRL      | <byte>,A</byte>     | <byte> = <byte> .XOR. A</byte></byte>     | X                |        |           |     | 1         |

| XRL      | <byte>,#data</byte> | <byte> = <byte> .XOR. #data</byte></byte> | X                |        |           |     | 2         |

| CRL      | A                   | A = 00H                                   |                  | Accum  | ulator or | nly | 1         |

| CPL      | Α                   | A = .NOT. A                               |                  | Accum  | ulator or | nly | 1         |

| RL       | Α                   | Rotate ACC Left 1 bit                     |                  | Accum  | ulator or | ıly | 1         |

| RLC      | A                   | Rotate Left through Carry                 | Accumulator only |        |           | ıly | 1         |

| RR       | A                   | Rotate ACC Right 1 bit                    | Accumulator only |        |           | ıly | 1         |

| RRC      | A                   | Rotate Right through Carry                |                  | Accum  | 1         |     |           |

| SWAF     | PA                  | Swap Nibbles in A                         |                  | Accum  | ulator or | ıly | 1         |

#### Logical Instructions

Table 3 shows the list of MCS-51 logical instructions. The instructions that perform Boolean operations (AND, OR, Exclusive OR, NOT) on bytes perform the operation on a bit-by-bit basis. That is, if the Accumulator contains 00110101B and <byte> contains 01010011B, then

ANL A, <byte>

will leave the Accumulator holding 00010001B.

The addressing modes that can be used to access the <br/>byte> operand are listed in Table 3. Thus, the ANL<br/>A, <br/>byte> instruction may take any of the forms

| ANL | A,7FH  | (direct addressing)   |

|-----|--------|-----------------------|

| ANL | A,@R1  | (indirect addressing) |

| ANL | A,R6   | (register addressing) |

| ANL | A,#53H | (immediate constant)  |

All of the logical instructions that are Accumulatorspecific execute in  $1\mu s$  (using a 12 MHz clock). The others take 2  $\mu s$ .

Note that Boolean operations can be performed on any byte in the lower 128 internal Data Memory space or the SFR space using direct addressing, without having to use the Accumulator. The XRL <byte>, #data instruction, for example, offers a quick and easy way to invert port bits, as in

#### XRL P1,#0FFH

If the operation is in response to an interrupt, not using the Accumulator saves the time and effort to stack it in the service routine.

The Rotate instructions (RL A, RLC A, etc.) shift the Accumulator 1 bit to the left or right. For a left rotation, the MSB rolls into the LSB position. For a right rotation, the LSB rolls into the MSB position. The SWAP A instruction interchanges the high and low nibbles within the Accumulator. This is a useful operation in BCD manipulations. For example, if the Accumulator contains a binary number which is known to be less than 100, it can be quickly converted to BCD by the following code:

| MOV  | <b>B</b> , #10 |

|------|----------------|

| DIV  | AB             |

| SWAP | Α              |

| ADD  | A,B            |

Dividing the number by 10 leaves the tens digit in the low nibble of the Accumulator, and the ones digit in the B register. The SWAP and ADD instructions move the tens digit to the high nibble of the Accumulator, and the ones digit to the low nibble.

#### **Data Transfers**

#### **INTERNAL RAM**

Table 4 shows the menu of instructions that are available for moving data around within the internal memory spaces, and the addressing modes that can be used with each one. With a 12 MHz clock, all of these instructions execute in either 1 or 2  $\mu$ s.

The MOV  $\langle dest \rangle$ ,  $\langle src \rangle$  instruction allows data to be transferred between any two internal RAM or SFR locations without going through the Accumulator. Remember the Upper 128 byes of data RAM can be accessed only by indirect addressing, and SFR space only by direct addressing.

Note that in all MCS-51 devices, the stack resides in on-chip RAM, and grows upwards. The PUSH instruction first increments the Stack Pointer (SP), then copies the byte into the stack. PUSH and POP use only direct addressing to identify the byte being saved or restored,

| Mnemonic                       | Operation                           | A   | ddress | Execution |     |           |

|--------------------------------|-------------------------------------|-----|--------|-----------|-----|-----------|

| Milenionio                     | operation                           | Dir | Ind    | Reg       | Imm | Time (μs) |

| MOV A, <src></src>             | $A = \langle src \rangle$           | X   | x      | X         | X   | 1         |

| MOV <dest>,A</dest>            | <dest> = A</dest>                   | X   | X      | X         |     | 1         |

| MOV <dest>, <src></src></dest> | <dest> = <src></src></dest>         | X   | X      | X         | X   | 2         |

| MOV DPTR,#data16               | DPTR = 16-bit immediate constant.   | [   |        |           | X   | 2         |

| PUSH <src></src>               | INC SP : MOV "@SP", < src>          | X   |        |           |     | 2         |

| POP <dest></dest>              | MOV <dest>, "@SP": DEC SP</dest>    | X   |        |           |     | 2         |

| XCH A, <byte></byte>           | ACC and <byte> exchange data</byte> | X   | х      | X         |     | 1         |

| XCHD A,@Ri                     | ACC and @Ri exchange low nibbles    |     | X      |           |     | 1         |

but the stack itself is accessed by indirect addressing using the SP register. This means the stack can go into the Upper 128, if they are implemented, but not into SFR space.

In devices that do not implement the Upper 128, if the SP points to the Upper 128, PUSHed bytes are lost, and POPped bytes are indeterminate.

The Data Transfer instructions include a 16-bit MOV that can be used to initialize the Data Pointer (DPTR) for look-up tables in Program Memory, or for 16-bit external Data Memory accesses.

The XCH A,  $\langle byte \rangle$  instruction causes the Accumulator and addressed byte to exchange data. The XCHD A,@Ri instruction is similar, but only the low nibbles are involved in the exchange.

To see how XCH and XCHD can be used to facilitate data manipulations, consider first the problem of shifting an 8-digit BCD number two digits to the right. Figure 11 shows how this can be done using direct MOVs, and for comparison how it can be done using XCH instructions. To aid in understanding how the code works, the contents of the registers that are holding the BCD number and the content of the Accumulator are shown alongside each instruction to indicate their status after the instruction has been executed.

|                               |              |       |        | -        |    | -    |     |

|-------------------------------|--------------|-------|--------|----------|----|------|-----|

|                               |              | 24    | A   28 | 20       | 2D | 2E   | ACC |

| MOV                           | A,2EH        | 00    | ) 12   | 34       | 56 | 78   | 78  |

| MOV                           | 2EH,2DH      | 1 00  | )   12 | 34       | 56 | 56   | 78  |

| MOV                           | 2DH,2CH      | 1 00  | )   12 | 34       | 34 | 56   | 78  |

| MOV                           | 2CH,2BH      | 1 00  | )   12 | 12       | 34 | 56   | 78  |

| MOV                           | 2BH,#0       | 00    | )   00 | 12       | 34 | 56   | 78  |

| (a) Usi                       | ing direct N | AOVs: | 14 by  | tes, 9 j | uS |      |     |

|                               |              | 2A    | 2B     | 2C       | 2D | 2E   | ACC |

| CLR                           | A            | 00    | 12     | 34       | 56 | 78   | 00  |

| XCH                           | A,2BH        | 00    | 00     | 34       | 56 | 78   | 12  |

| XCH                           | A,2CH        | 00    | 00     | 12       | 56 | 78   | 34  |

| XCH                           | A,2DH        | 00    | 00     | 12       | 34 | 78   | 56  |

| XCH                           | A,2EH        | 00    | 00     | 12       | 34 | 56 I | 78  |

| (b) Using XCHs: 9 bytes, 5 μs |              |       |        |          |    |      |     |

Figure 11. Shifting a BCD Number Two Digits to the Right

After the routine has been executed, the Accumulator contains the two digits that were shifted out on the right. Doing the routine with direct MOVs uses 14 code bytes and 9  $\mu$ s of execution time (assuming a 12 MHz clock). The same operation with XCHs uses less code and executes almost twice as fast.

To right-shift by an odd number of digits, a one-digit shift must be executed. Figure 12 shows a sample of code that will right-shift a BCD number one digit, using the XCHD instruction. Again, the contents of the registers holding the number and of the Accumulator are shown alongside each instruction.

|            |              | 2A  | 2B       | 2C | 2D   | 2E  | ACC |

|------------|--------------|-----|----------|----|------|-----|-----|

| MOV        | R1,#2EH      |     | 12<br>12 |    |      |     |     |

| MOV        | R0, #2DH     | 100 | 112      | 34 | 1 20 | 170 |     |

| loop for l | R1 = 2EH:    |     |          |    |      |     |     |

| LOOP: MOV  | A,@R1        | 00  | 12       | 34 | 56   | 78  | 78  |

| XCHD       | A,@R0        | 00  | 12       | 34 | 58   | 78  | 76  |

| SWAP       | A            | 00  | 12       | 34 | 58   | 78  | 67  |

| MOV        | @R1,A        | 00  | 12       | 34 | 58   | 67  | 67  |

| DEC        | R1           | 00  | 12       | 34 | 58   | 67  | 67  |

| DEC        | R0           | 00  | 12       | 34 | 58   | 67  | 67  |

| CJNE       | R1,#2AH,LOOP |     |          |    |      |     |     |

| loop for F | R1 = 2DH:    | 00  | 12       | 38 | 45   | 67  | 45  |

| loop for l | R1 = 2CH:    | 00  | 18       | 23 | 45   | 67  | 23  |

| loop for I | R1 = 2BH:    | 08  |          |    |      |     |     |

| CLR        | A            | 08  | 01       | 23 | 45   | 67  | 00  |

| ХСН        | A,2AH        | 00  | 01       | 23 | 45   | 67  | 08  |

#### Figure 12. Shifting a BCD Number One Digit to the Right

First, pointers R1 and R0 are set up to point to the two bytes containing the last four BCD digits. Then a loop is executed which leaves the last byte, location 2EH, holding the last two digits of the shifted number. The pointers are decremented, and the loop is repeated for location 2DH. The CJNE instruction (Compare and Jump if Not Equal) is a loop control that will be described later.

The loop is executed from LOOP to CJNE for R1 = 2EH, 2DH, 2CH and 2BH. At that point the digit that was originally shifted out on the right has propagated to location 2AH. Since that location should be left with 0s, the lost digit is moved to the Accumulator.

#### EXTERNAL RAM

Table 5 shows a list of the Data Transfer instructions that access external Data Memory. Only indirect addressing can be used. The choice is whether to use a one-byte address, @Ri, where Ri can be either R0 or R1 of the selected register bank, or a two-byte address, @DPTR. The disadvantage to using 16-bit addresses if only a few K bytes of external RAM are involved is that 16-bit addresses use all 8 bits of Port 2 as address bus. On the other hand, 8-bit addresses allow one to address a few K bytes of RAM, as shown in Figure 5, without having to sacrifice all of Port 2.

All of these instructions execute in 2  $\mu$ s, with a 12 MHz clock.

Table 5. A List of the MCS®-51 Data Transfer Instructions that Access External Data Memory Space

| Address<br>Width | Mnemonic     | Operation                   | Execution<br>Time (µs) |

|------------------|--------------|-----------------------------|------------------------|

| 8 bits           | MOVX A,@Ri   | Read external<br>RAM @Ri    | 2                      |

| 8 bits           | MOVX @Ri,A   | Write external<br>RAM @Ri   | 2                      |

| 16 bits          | MOVX A,@DPTR | Read external<br>RAM @DPTR  | 2                      |

| 16 bits          | MOVX @DPTR,A | Write external<br>RAM @DPTR | 2                      |

Note that in all external Data RAM accesses, the Accumulator is always either the destination or source of the data.

The read and write strobes to external RAM are activated only during the execution of a MOVX instruction. Normally these signals are inactive, and in fact if they're not going to be used at all, their pins are available as extra I/O lines. More about that later.

#### LOOKUP TABLES

Table 6 shows the two instructions that are available for reading lookup tables in Program Memory. Since these instructions access only Program Memory, the lookup tables can only be read, not updated. The mnemonic is MOVC for "move constant".

If the table access is to external Program Memory, then the read strobe is **PSEN**.

#### Table 6. The MCS®-51 Lookup Table Read Instructions

| Mnemonic |           | Operation                        | Execution<br>Time (µs) |

|----------|-----------|----------------------------------|------------------------|

| MOVC     | A,@A+DPTR | Read Pgm Memory<br>at (A + DPTR) | 2                      |

| MOVC     | A,@A+PC   | Read Pgm Memory<br>at (A + PC)   | 2                      |

The first MOVC instruction in Table 6 can accommodate a table of up to 256 entries, numbered 0 through 255. The number of the desired entry is loaded into the Accumulator, and the Data Pointer is set up to point to beginning of the table. Then

MOVC A,@A+DPTR

copies the desired table entry into the Accumulator.

The other MOVC instruction works the same way, except the Program Counter (PC) is used as the table base, and the table is accessed through a subroutine. First the number of the desired entry is loaded into the Accumulator, and the subroutine is called:

| MOV  | A,ENTRYNUMBER |

|------|---------------|

| CALL | TABLE         |

The subroutine "TABLE" would look like this:

TABLE: MOVC A,@A+PC RET

The table itself immediately follows the RET (return) instruction in Program Memory. This type of table can have up to 255 entries, numbered 1 through 255. Number 0 can not be used, because at the time the MOVC instruction is executed, the PC contains the address of the RET instruction. An entry numbered 0 would be the RET opcode itself.

#### **Boolean Instructions**

MCS-51 devices contain a complete Boolean (single-bit) processor. The internal RAM contains 128 addressable bits, and the SFR space can support up to 128 other addressable bits. All of the port lines are bit-addressable, and each one can be treated as a separate singlebit port. The instructions that access these bits are not just conditional branches, but a complete menu of move, set, clear, complement, OR, and AND instructions. These kinds of bit operations are not easily obtained in other architectures with any amount of byteoriented software.

| Mnemonic |         | Operation                | Execution<br>Time (µs) |

|----------|---------|--------------------------|------------------------|

| ANL      | C,bit   | C = C .AND. bit          | 2                      |

| ANL      | C,/bit  | C = C .ANDNOT. bit       | 2                      |

| ORL      | C,bit   | C = C.OR. bit            | 2                      |

| ORL      | C,/bit  | C = C.ORNOT. bit         | 2                      |

| MOV      | C,bit   | C = bit                  | 1                      |

| MOV      | bit,C   | bit = C                  | 2                      |

| CLR      | С       | C = 0                    | 1                      |

| CLR      | bit     | bit = 0                  | 1                      |

| SETB     | С       | C = 1                    | 1                      |

| SETB     | bit     | bit = 1                  | 1                      |

| CPL      | С       | C = .NOT. C              | 1                      |

| CPL      | bit     | bit = .NOT. bit          | 1                      |

| JC       | rel     | Jump if $C = 1$          | 2                      |

| JNC      | rel     | Jump  if  C = 0          | 2                      |

| JB       | bit,rel | Jump if bit $= 1$        | 2                      |

| JNB      | bit,rel | Jump if bit $= 0$        | 2                      |

| JBC      | bit,rel | Jump if bit = 1; CLR bit | 2                      |

#### Table 7. A List of the MCS®-51 Boolean Instructions

The instruction set for the Boolean processor is shown in Table 7. All bit accesses are by direct addressing. Bit addresses 00H through 7FH are in the Lower 128, and bit addresses 80H through FFH are in SFR space.

Note how easily an internal flag can be moved to a port pin:

| MOV | C,FLAG |

|-----|--------|

| MOV | P1.0,C |

In this example, FLAG is the name of any addressable bit in the Lower 128 or SFR space. An I/O line (the LSB of Port 1, in this case) is set or cleared depending on whether the flag bit is 1 or 0.

The Carry bit in the PSW is used as the single-bit Accumulator of the Boolean processor. Bit instructions that refer to the Carry bit as C assemble as Carry-specific instructions (CLR C, etc). The Carry bit also has a direct address, since it resides in the PSW register, which is bit-addressable. Note that the Boolean instruction set includes ANL and ORL operations, but not the XRL (Exclusive OR) operation. An XRL operation is simple to implement in software. Suppose, for example, it is required to form the Exclusive OR of two bits:

C = bit1 .XRL. bit2

The software to do that could be as follows:

|       | MOV      | C,bit1    |

|-------|----------|-----------|

|       | JNB      | bit2,OVER |

|       | CPL      | С         |

| OVER: | (continu | ie)       |

First, bit1 is moved to the Carry. If bit2 = 0, then C now contains the correct result. That is,  $bit1 \cdot XRL$ . bit2= bit1 if bit2 = 0. On the other hand, if bit2 = 1 C now contains the complement of the correct result. It need only be inverted (CPL C) to complete the operation.

This code uses the JNB instruction, one of a series of bit-test instructions which execute a jump if the addressed bit is set (JC, JB, JBC) or if the addressed bit is not set (JNC, JNB). In the above case, bit2 is being tested, and if bit2 = 0 the CPL C instruction is jumped over.

JBC executes the jump if the addressed bit is set, and also clears the bit. Thus a flag can be tested and cleared in one operation.

All the PSW bits are directly addressable, so the Parity bit, or the general purpose flags, for example, are also available to the bit-test instructions.

#### RELATIVE OFFSET

The destination address for these jumps is specified to the assembler by a label or by an actual address in Program Memory. However, the destination address assembles to a relative offset byte. This is a signed (two's complement) offset byte which is added to the PC in two's complement arithmetic if the jump is executed.

The range of the jump is therefore -128 to +127 Program Memory bytes relative to the first byte following the instruction.

#### Jump Instructions

Table 8 shows the list of unconditional jumps.

#### Table 8. Unconditional Jumps in MCS®-51 Devices

| Mnemonic    | Operation               | Execution<br>Time (µs) |

|-------------|-------------------------|------------------------|

| JMP addr    | Jump to addr            | 2                      |

| JMP @A+DPTR | Jump to A + DPTR        | 2                      |

| CALL addr   | Call subroutine at addr | 2                      |

| RET         | Return from subroutine  | 2                      |

| RETI        | Return from interrupt   | 2                      |

| NOP         | No operation            | 1                      |

The Table lists a single "JMP addr" instruction, but in fact there are three—SJMP, LJMP and AJMP—which differ in the format of the destination address. JMP is a generic mnemonic which can be used if the programmer does not care which way the jump is encoded.

The SJMP instruction encodes the destination address as a relative offset, as described above. The instruction is 2 bytes long, consisting of the opcode and the relative offset byte. The jump distance is limited to a range of -128 to +127 bytes relative to the instruction following the SJMP.

The LJMP instruction encodes the destination address as a 16-bit constant. The instruction is 3 bytes long, consisting of the opcode and two address bytes. The destination address can be anywhere in the 64K Program Memory space.

The AJMP instruction encodes the destination address as an 11-bit constant. The instruction is 2 bytes long, consisting of the opcode, which itself contains 3 of the 11 address bits, followed by another byte containing the low 8 bits of the destination address. When the instruction is executed, these 11 bits are simply substituted for the low 11 bits in the PC. The high 5 bits stay the same. Hence the destination has to be within the same 2K block as the instruction following the AJMP.

In all cases the programmer specifies the destination address to the assembler in the same way: as a label or as a 16-bit constant. The assembler will put the destination address into the correct format for the given instruction. If the format required by the instruction will not support the distance to the specified destination address, a "Destination out of range" message is written into the List file.

The JMP @A+DPTR instruction supports case jumps. The destination address is computed at execution time as the sum of the 16-bit DPTR register and

the Accumulator. Typically, DPTR is set up with the address of a jump table, and the Accumulator is given an index to the table. In a 5-way branch, for example, an integer 0 through 4 is loaded into the Accumulator. The code to be executed might be as follows:

| MOV | DPTR, #JUMPTABLE |

|-----|------------------|

| MOV | A,INDEXNUMBER    |

| RL  | Α                |

| JMP | @A+DPTR          |

The RL A instruction converts the index number (0 through 4) to an even number on the range 0 through 8, because each entry in the jump table is 2 bytes long:

| JUMP_TABLE: |        |

|-------------|--------|

| AJMP        | CASE0  |

| AJMP        | CASE_1 |

| AJMP        | CASE_2 |

| AJMP        | CASE_3 |

| AJMP        | CASE_4 |

Table 8 shows a single "CALL addr" instruction, but there are two of them—LCALL and ACALL—which differ in the format in which the subroutine address is given to the CPU. CALL is a generic mnemonic which can be used if the programmer does not care which way the address is encoded.

The LCALL instruction uses the 16-bit address format, and the subroutine can be anywhere in the 64K Program Memory space. The ACALL instruction uses the 11-bit format, and the subroutine must be in the same 2K block as the instruction following the ACALL.

In any case the programmer specifies the subroutine address to the assembler in the same way: as a label or as a 16-bit constant. The assembler will put the address into the correct format for the given instructions.

Subroutines should end with a RET instruction, which returns execution to the instruction following the CALL.

RETI is used to return from an interrupt service routine. The only difference between RET and RETI is that RETI tells the interrupt control system that the interrupt in progress is done. If there is no interrupt in progress at the time RETI is executed, then the RETI is functionally identical to RET.

Table 9 shows the list of conditional jumps available to the MCS-51 user. All of these jumps specify the destination address by the relative offset method, and so are limited to a jump distance of -128 to +127 bytes from the instruction following the conditional jump instruction. Important to note, however, the user specifies to the assembler the actual destination address the same way as the other jumps: as a label or a 16-bit constant.

| Mnemonic                     | Operation                      | Addressing Modes |     |     |     | Execution |  |

|------------------------------|--------------------------------|------------------|-----|-----|-----|-----------|--|

| Milenionic                   | Operation                      | Dir              | Ind | Reg | Imm | Time (μs) |  |

| JZ rel                       | Jump  if  A = 0                | Accumulator only |     | 2   |     |           |  |

| JNZ rel                      | Jump if $A \neq 0$             | Accumulator only |     | 2   |     |           |  |

| DJNZ <byte>,rel</byte>       | Decrement and jump if not zero | Х                |     | X   |     | 2         |  |

| CJNE A, <byte>,rel</byte>    | Jump if A $\neq$ <byte></byte> | Х                |     |     | Х   | 2         |  |

| CJNE <byte>,#data,rel</byte> | Jump if <byte> ≠ #data</byte>  |                  | X   | X   |     | 2         |  |

Table 9. Conditional Jumps in MCS®-51 Devices

There is no Zero bit in the PSW. The JZ and JNZ instructions test the Accumulator data for that condition.

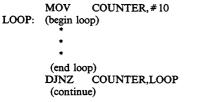

The DJNZ instruction (Decrement and Jump if Not Zero) is for loop control. To execute a loop N times, load a counter byte with N and terminate the loop with a DJNZ to the beginning of the loop, as shown below for N = 10:

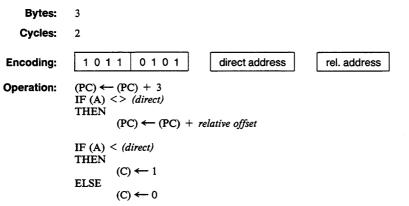

The CJNE instruction (Compare and Jump if Not Equal) can also be used for loop control as in Figure 12. Two bytes are specified in the operand field of the instruction. The jump is executed only if the two bytes are not equal. In the example of Figure 12, the two bytes were the data in R1 and the constant 2AH. The initial data in R1 was 2EH. Every time the loop was executed, R1 was decremented, and the looping was to continue until the R1 data reached 2AH.

Another application of this instruction is in "greater than, less than" comparisons. The two bytes in the operand field are taken as unsigned integers. If the first is less than the second, then the Carry bit is set (1). If the first is greater than or equal to the second, then the Carry bit is cleared.

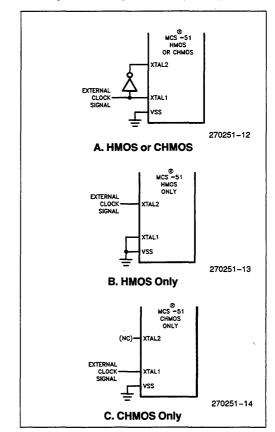

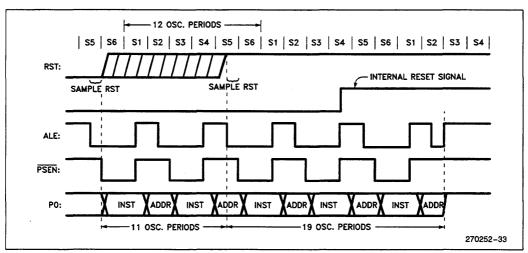

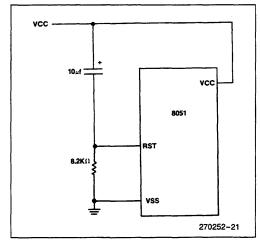

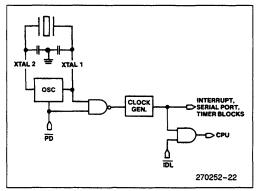

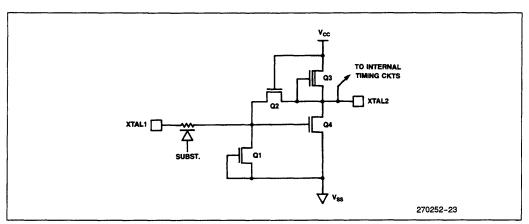

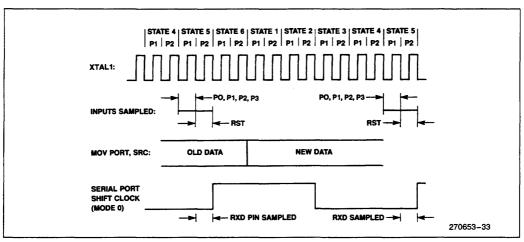

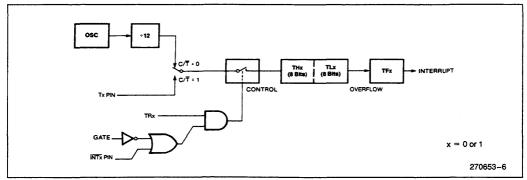

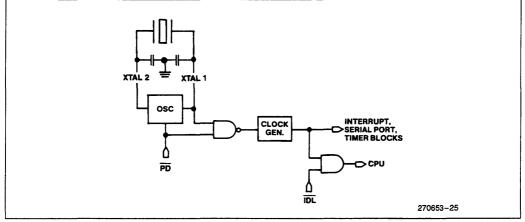

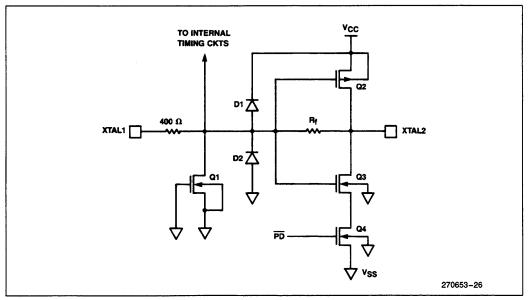

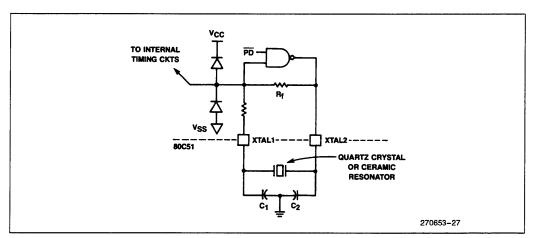

#### **CPU TIMING**

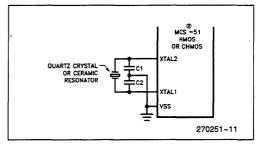

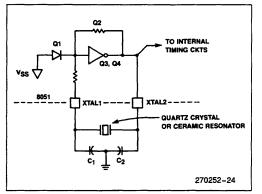

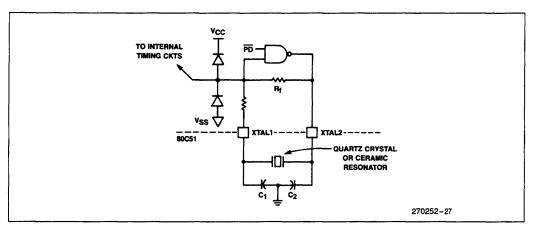

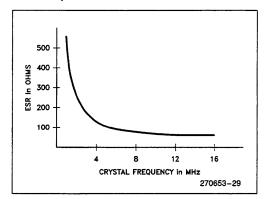

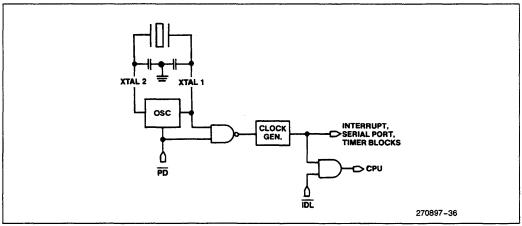

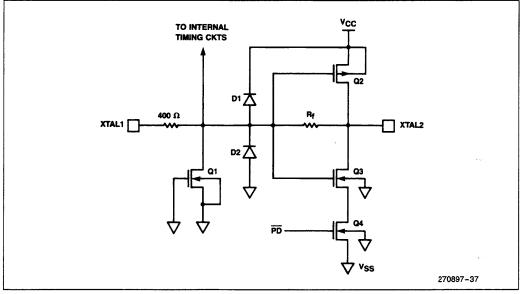

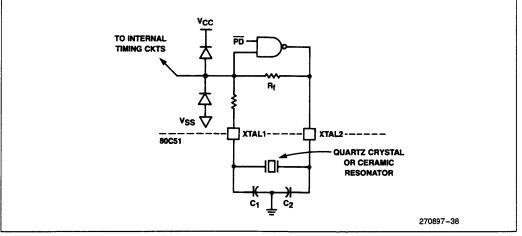

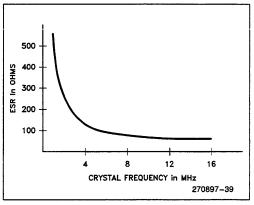

All MCS-51 microcontrollers have an on-chip oscillator which can be used if desired as the clock source for the CPU. To use the on-chip oscillator, connect a crystal or ceramic resonator between the XTAL1 and XTAL2 pins of the microcontroller, and capacitors to ground as shown in Figure 13.

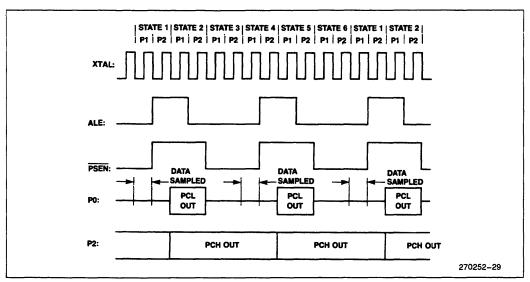

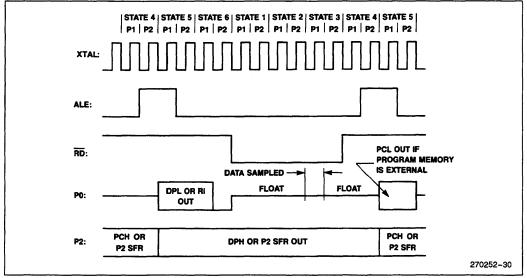

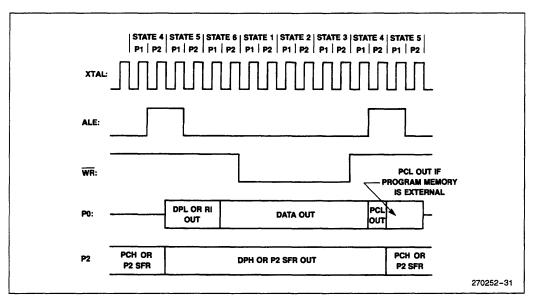

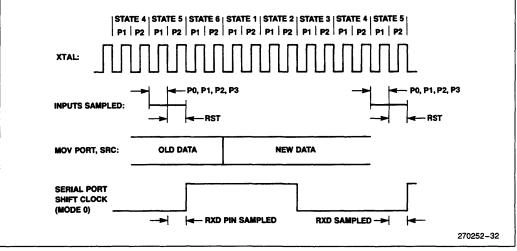

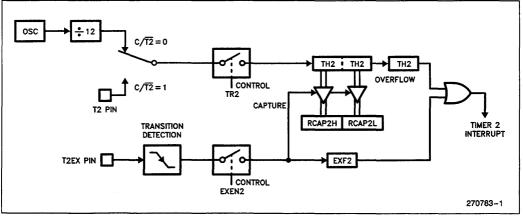

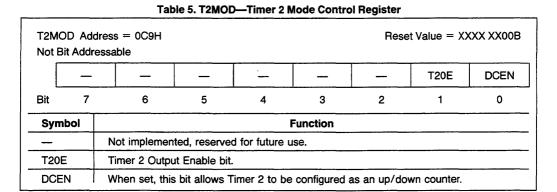

Figure 13. Using the On-Chip Oscillator

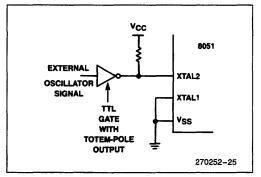

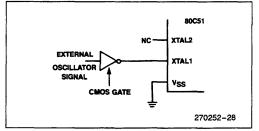

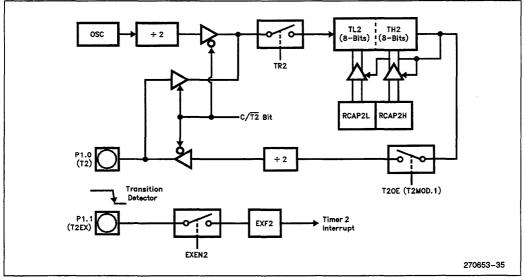

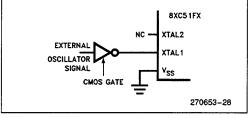

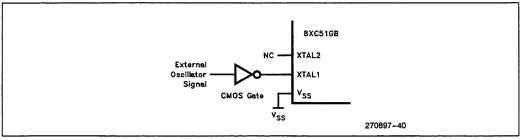

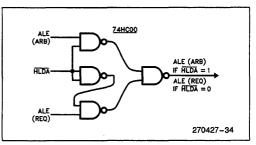

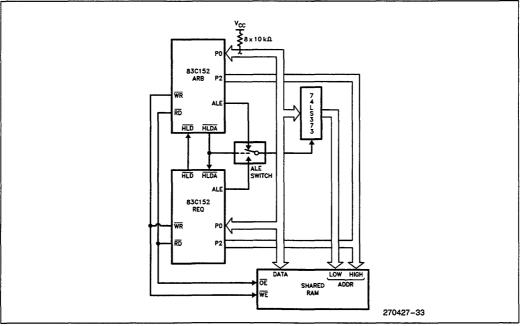

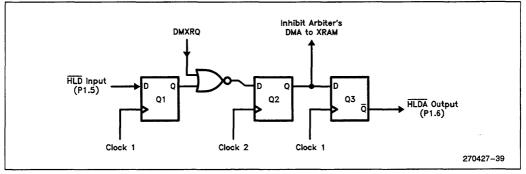

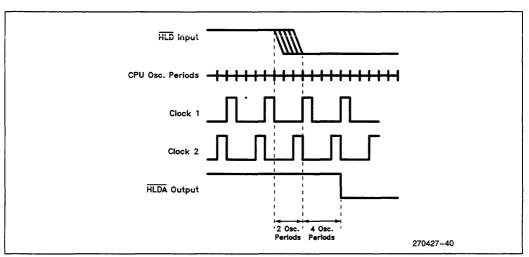

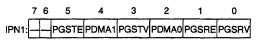

Figure 14. Using an External Clock