## E<sup>2</sup> Prom Family Applications Handbook

## Book II

Order No. 210273-001

### E<sup>2</sup>PROM FAMILY APPLICATIONS HANDBOOK

) ) ) **BOOK II**

**NOVEMBER 1981**

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products

BXP, CREDIT, I, ICE, ICS, I<sub>m</sub>, Insite, Intel, Int<sub>e</sub>l, Intelevision, Intellec, IRMX, ISBC, ISBX, Library Manager, MCS, Megachassis, Micromainframe, Micromap, Multimodule, Plug-A-Bubble, PROMPT, RMX/80, System 2000 and UPI

MDS is an ordering code only and is not used as a product name or trademark MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\* MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from

Intel Corporation Literature Department SV3-3 3065 Bowers Avenue Santa Clara, CA 95051

#### **Table of Contents**

| CHAPTER 1 Introduction                                                                             | 1-1          |

|----------------------------------------------------------------------------------------------------|--------------|

| Acknowledgement                                                                                    | 1-1          |

| CHAPTER 2                                                                                          | •••          |

| E <sup>2</sup> PROM Backgrounder Information                                                       | 2-1          |

| E <sup>2</sup> PROM Backgrounder                                                                   | 2-1          |

| AR-118A 16K Electrically Erasable Non-Volatile Memory                                              | 2-5          |

| AR-119 16K EE-PROM Relies on Tunneling For Byte-Erasable Program Storage                           | 2-9          |

| CHAPTER 3                                                                                          |              |

| Applications Briefs                                                                                | 3-1          |

| AB-1 A Variable-Attribute CRT Terminal                                                             | 3-1          |

| AB-2 Point-of-Sale Terminal                                                                        | 3-5          |

| AB-3 E <sup>2</sup> PROM Eliminates PROM Programmer Obsolescence                                   |              |

| AB-4 ROMs Become Flexible with E <sup>2</sup> PROMs                                                | 3-13         |

| AB-5 Robotics—E <sup>2</sup> PROMs Show Them the Way                                               | 3-21         |

| AB-6 Prototyping with E <sup>2</sup> PROMs                                                         | 3-25         |

| AB-7 E <sup>2</sup> PROMs as an Error Accumulation Medium                                          | 3-29         |

| AB-8 PC and Data Loggers—E <sup>2</sup> PROMs Benefit User and Manufacturer Both                   | 3-35         |

| CHAPTER 4                                                                                          |              |

| E <sup>2</sup> PROM Applications AP-100 Reliability Aspects of a Floating-Gate E <sup>2</sup> PROM | 4-1          |

|                                                                                                    | 4-1          |

| Introduction                                                                                       | 4-2          |

| Device Operation                                                                                   | 4-2          |

| Read Retention                                                                                     | 4-3<br>4-4   |

| Intrinsic Charge Trapping Defect Charge Loss                                                       | 4-4<br>4-5   |

| Accelerated Test Results                                                                           | 4-6          |

| Summary                                                                                            | 4-7          |

| AP-101 2816 Electrical Description                                                                 | 4-9          |

|                                                                                                    | 4-10         |

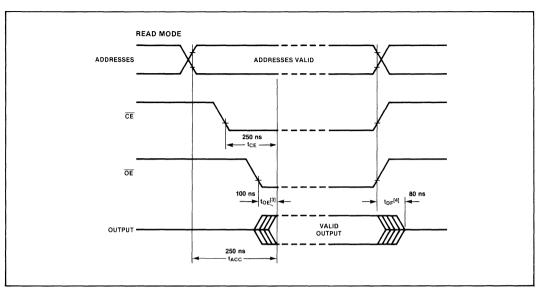

| Read Access Mode                                                                                   | 4-10         |

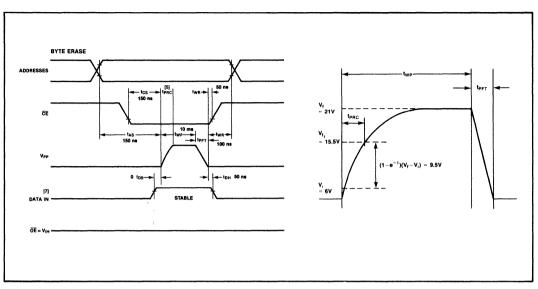

| Erase Access Mode                                                                                  | 4-13         |

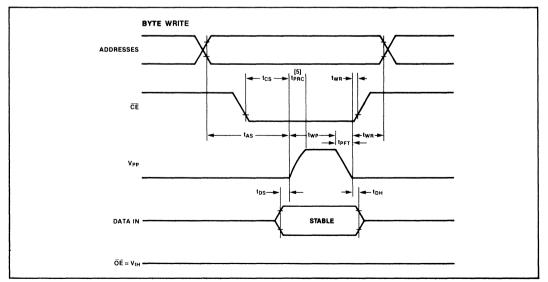

| Write Access Mode                                                                                  | 4-14         |

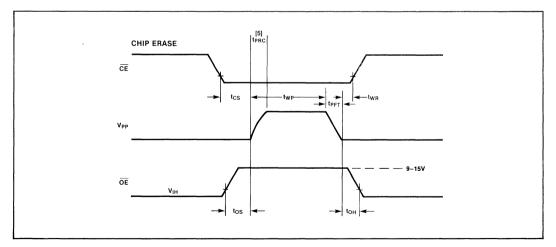

| Chip Erase Access                                                                                  | 4-15         |

| DC Voltage Conditions                                                                              | 4-15         |

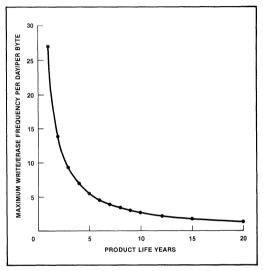

| Endurance Issues                                                                                   | 4-16         |

| Conclusion                                                                                         | 4-16         |

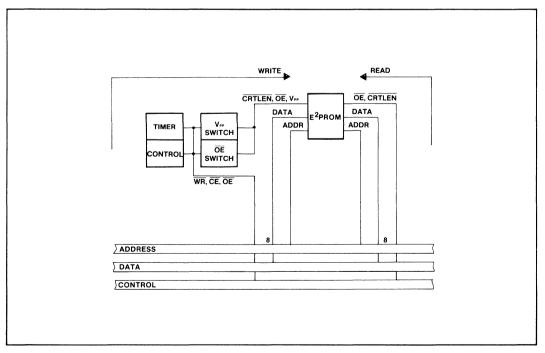

| AP-102 2816 Microprocessor Interface Considerations                                                | 4-17         |

| Introduction                                                                                       | 4-18<br>4-18 |

| Bus Dependent Transfer                                                                             | 4-18         |

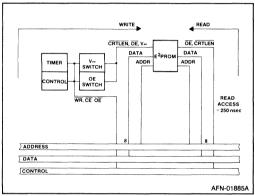

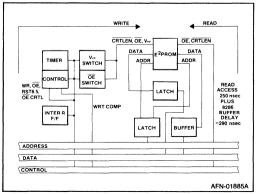

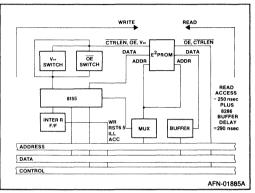

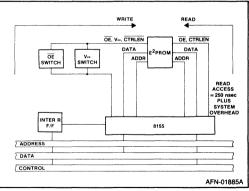

| Interface Overview                                                                                 | 4-19         |

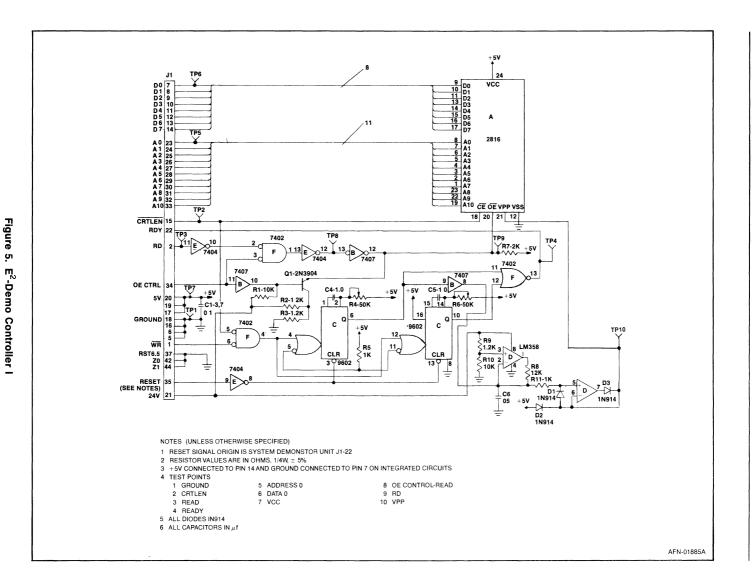

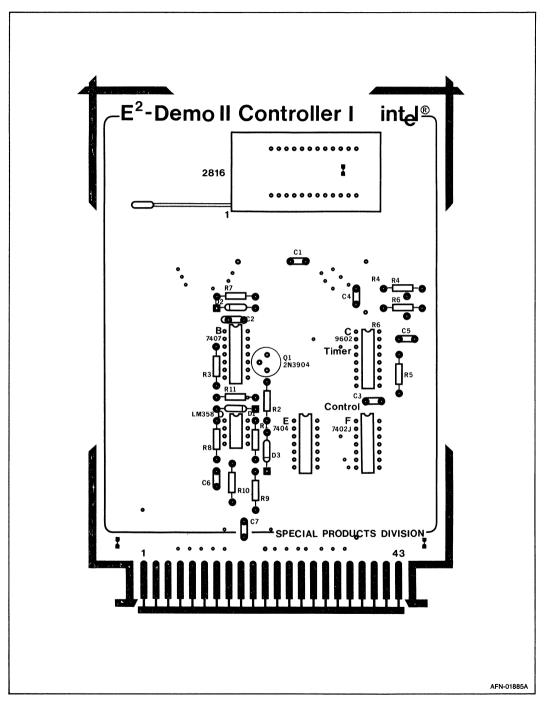

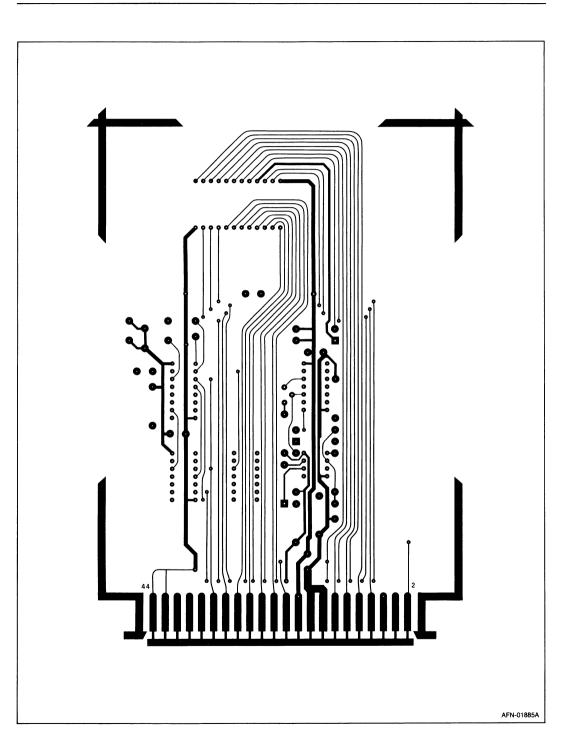

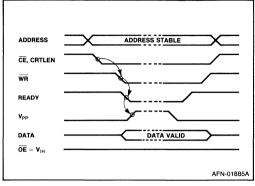

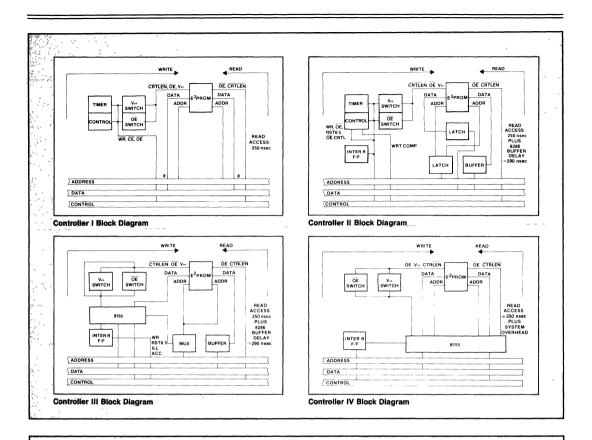

| Controller I Description                                                                           | 4-20         |

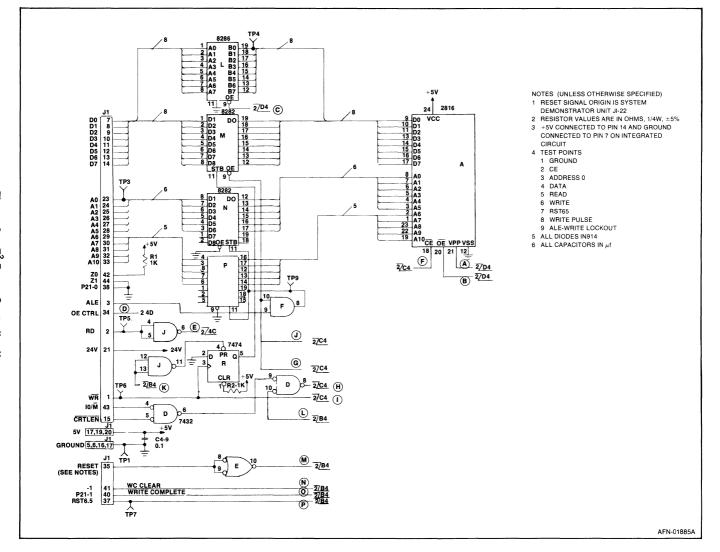

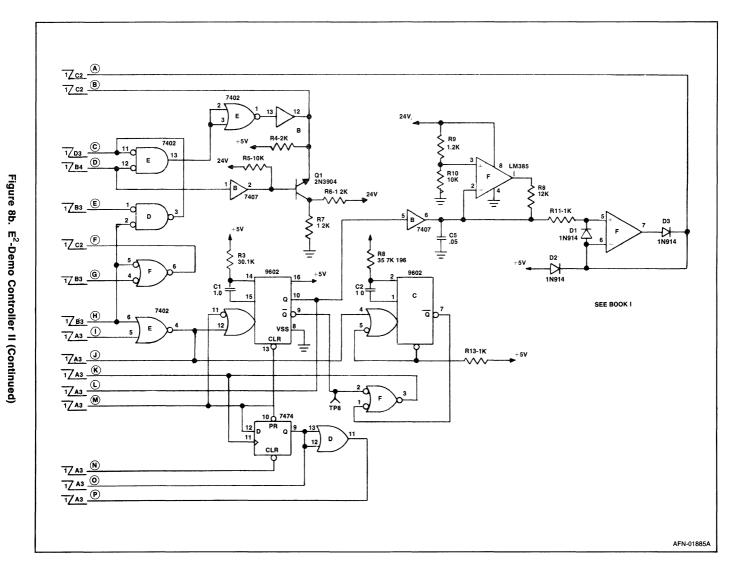

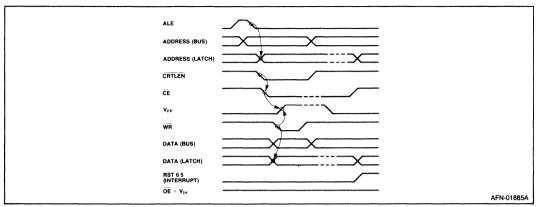

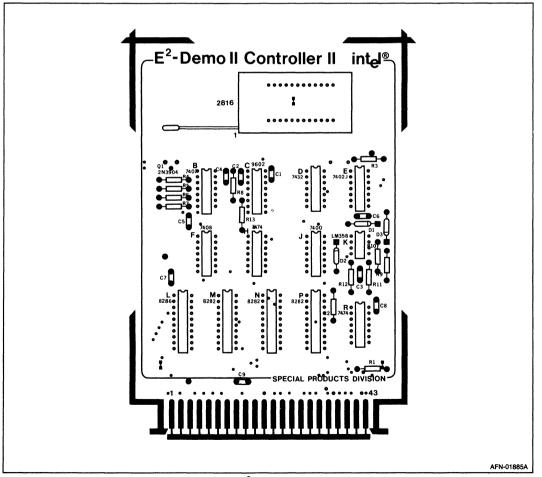

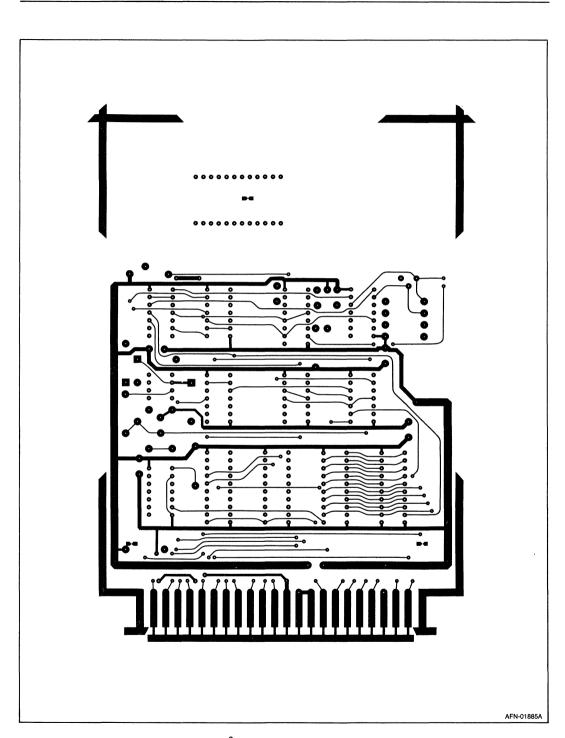

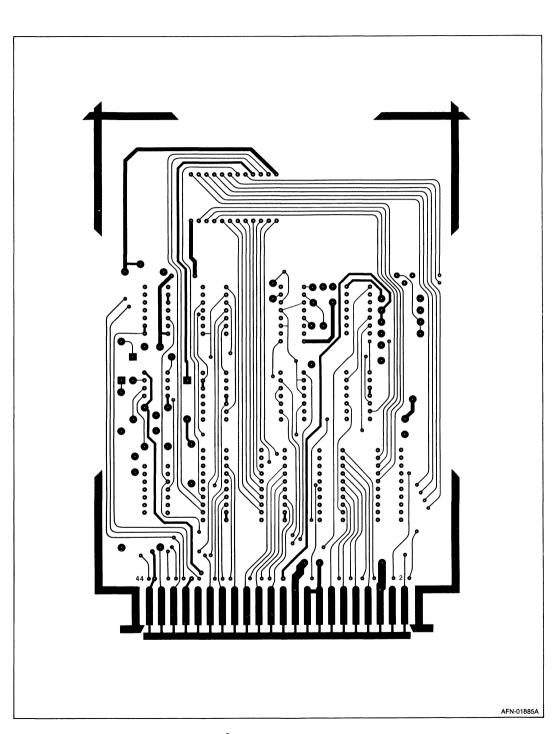

| Controller II Description                                                                          | 4-24         |

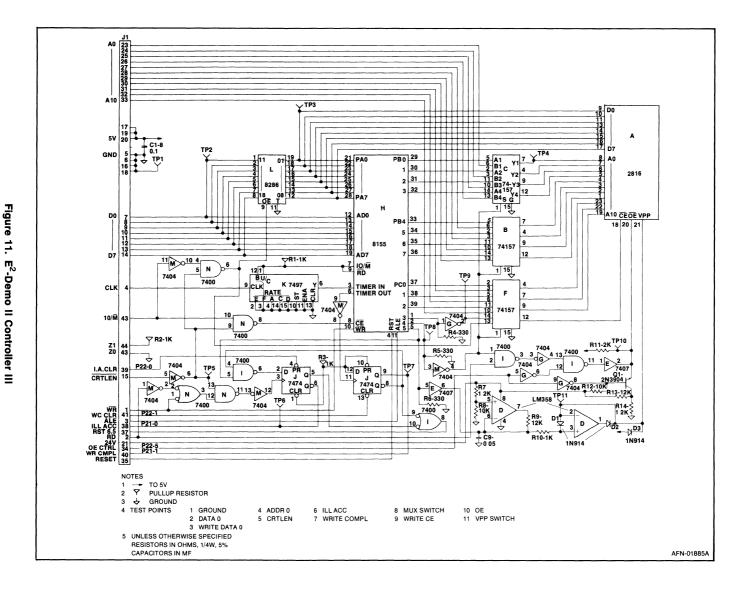

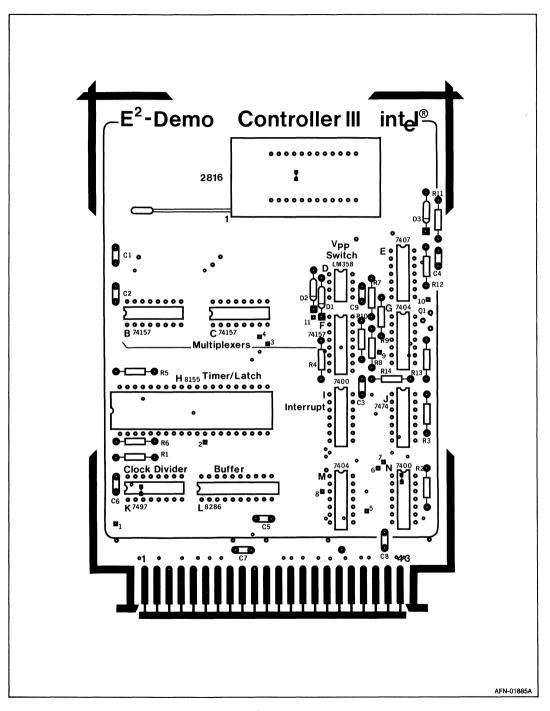

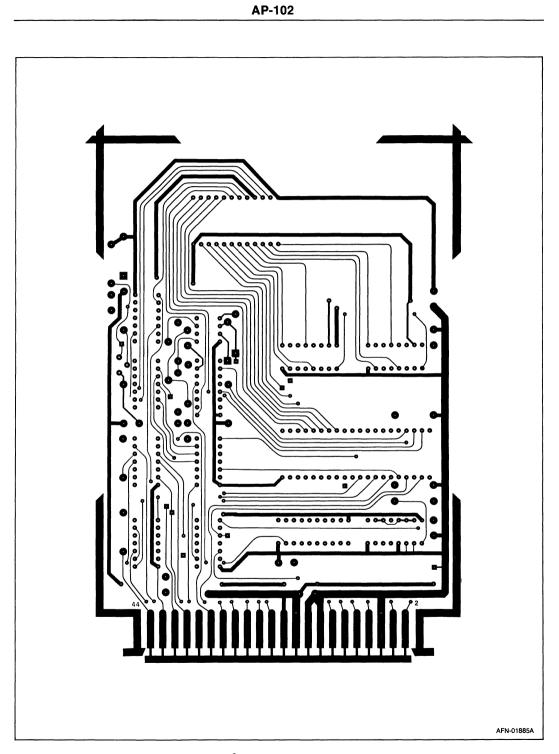

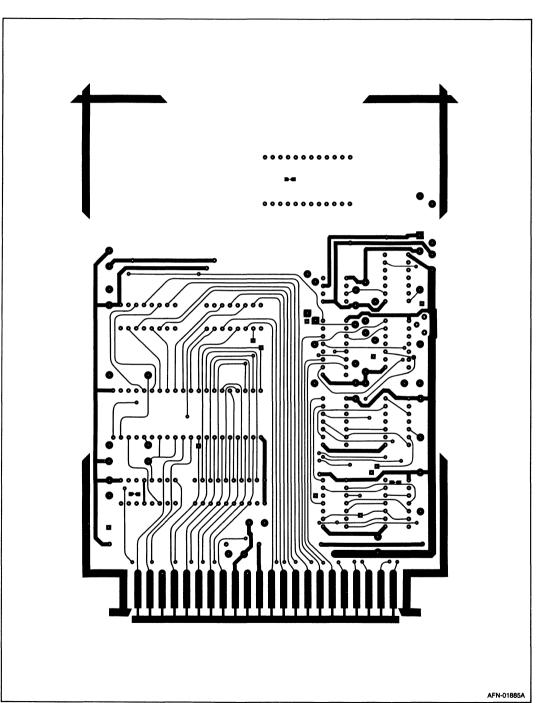

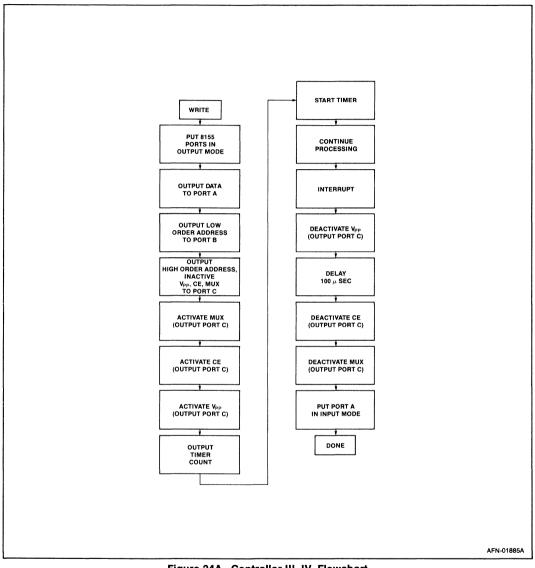

| Controller III Description                                                                         | 4-30         |

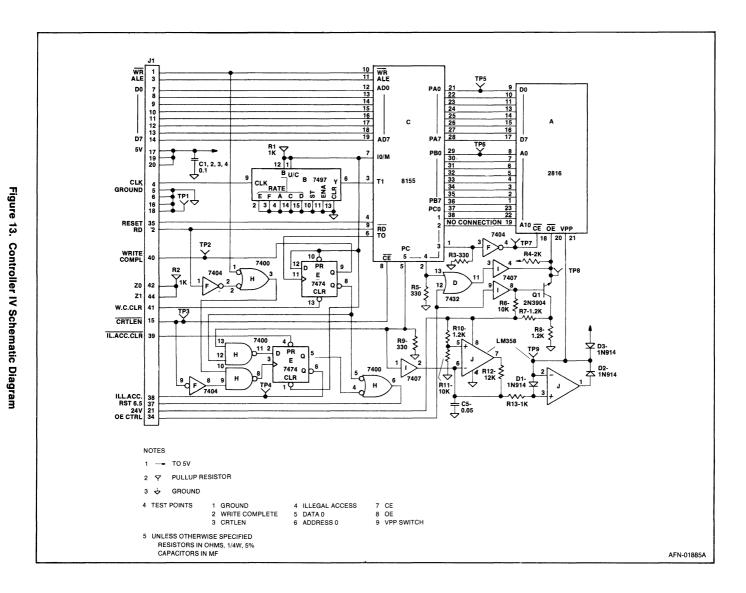

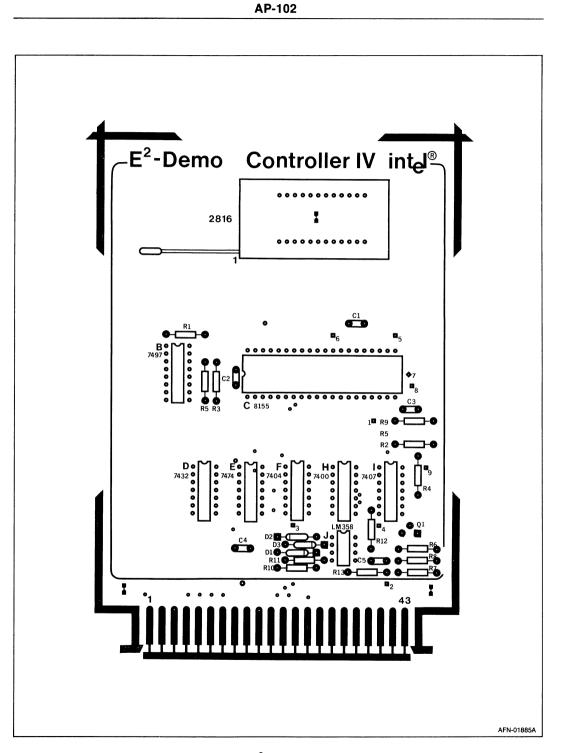

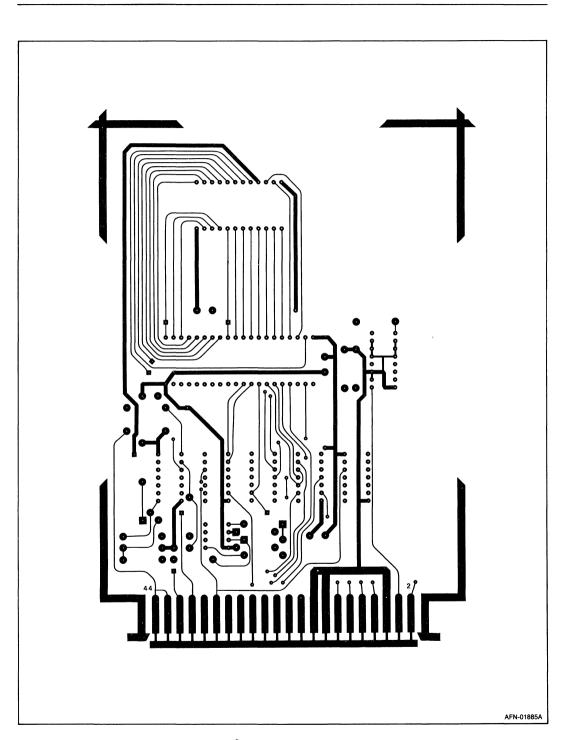

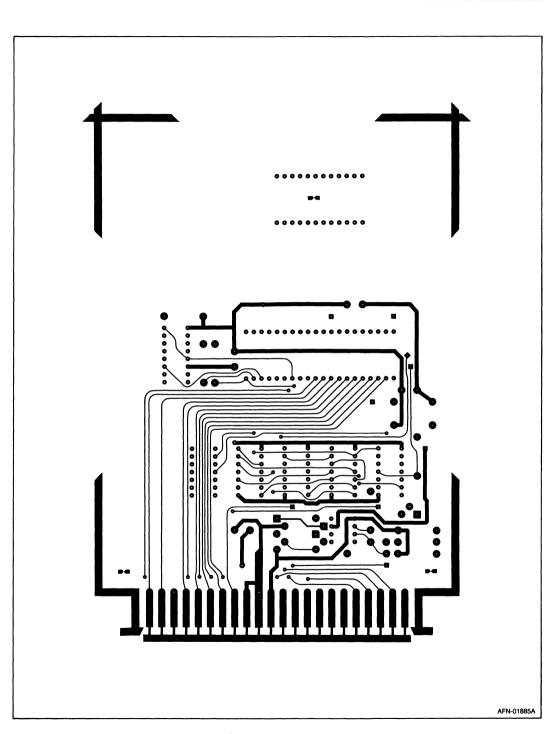

| Controller IV Description                                                                          | 4-35         |

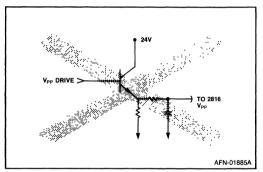

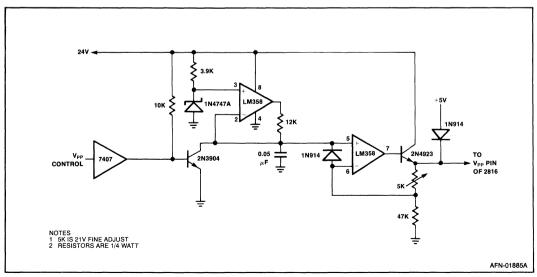

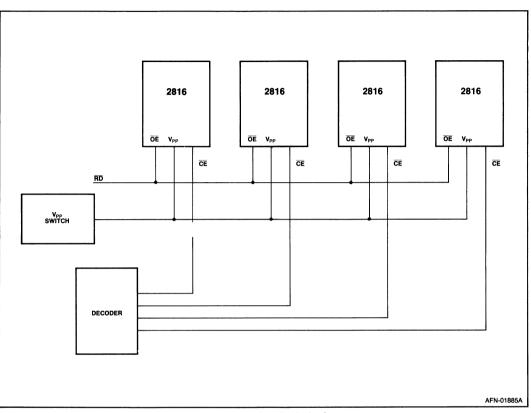

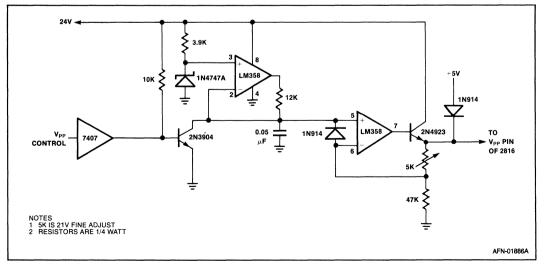

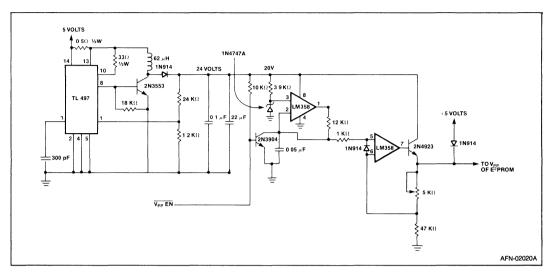

| V <sub>PP</sub> Switching                                                                          | 4-40         |

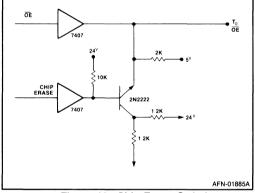

| OE Switching                                                                                       | 4-41         |

| Multiple 2816s                                                                                     | 4-41         |

| Interface Software Requirements                                                                    | 4-41<br>4-42 |

|                                                                                                    |              |

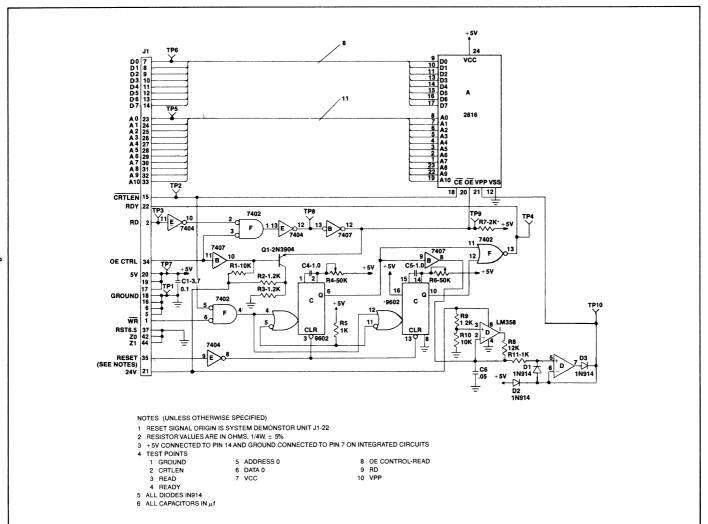

| AP-103 Programming E <sup>2</sup> PROM with a Single 5-Volt Power Supply                           | 4-69         |

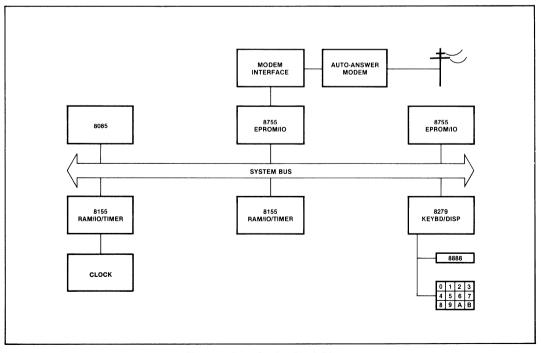

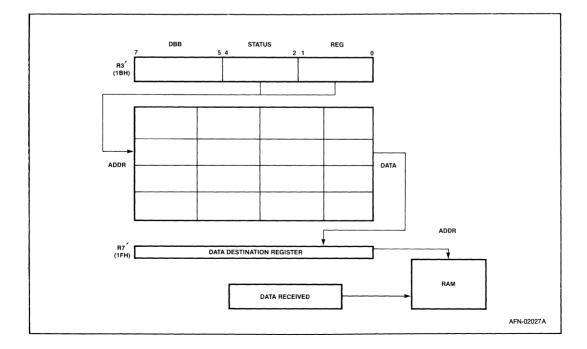

| AP-107 Hardware and Software Download Techniques with 2816                     | 4-73  |

|--------------------------------------------------------------------------------|-------|

| Introduction                                                                   | 4-74  |

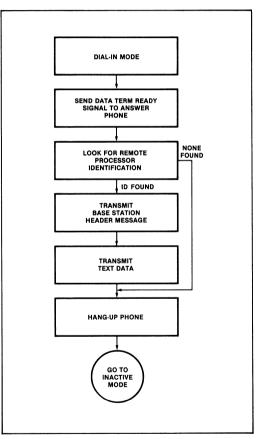

| In-Field Software Updates                                                      | 4-74  |

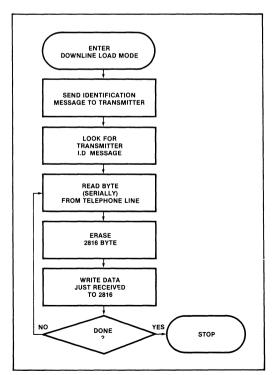

| Downline Load Philosophy                                                       | 4-75  |

| 2816 Remote Configuration Options                                              | 4-75  |

| Receiver                                                                       |       |

| Transmitter                                                                    | 4-79  |

| Conclusion                                                                     | 4-80  |

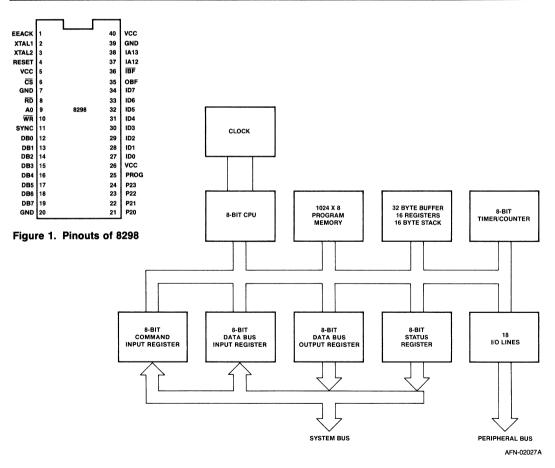

| AP-135 8298 Integrated E <sup>2</sup> Controller                               | 4-81  |

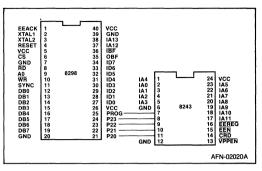

|                                                                                | 4-82  |

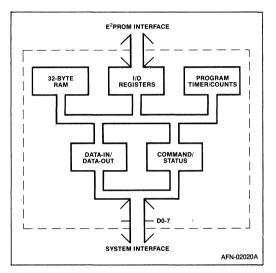

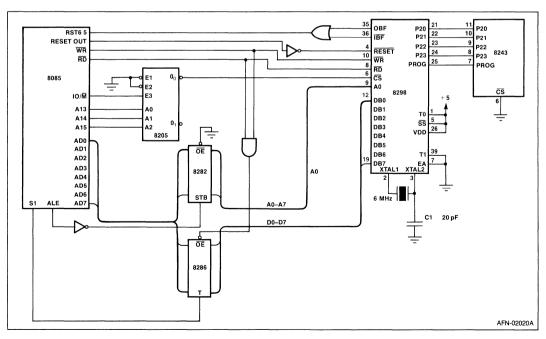

| 8298 Hardware                                                                  |       |

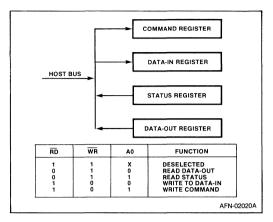

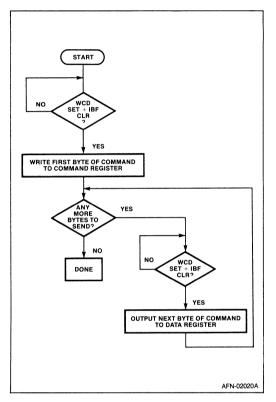

| 8298 Operation                                                                 |       |

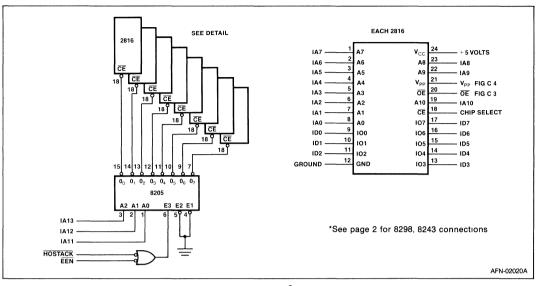

| System Configuration                                                           | 4-86  |

| Direct Configuration                                                           |       |

| Appendix A: Command Summary                                                    |       |

| Appendix B: Configuration Command Summary                                      | 4-92  |

| Appendix C: Hardware Schematics                                                | 4-93  |

| AP-136 A Multibus-Compatible 2816 E <sup>2</sup> PROM Memory-Board Description |       |

| Introduction                                                                   |       |

|                                                                                |       |

| Installation Instructions                                                      |       |

| Procedure                                                                      |       |

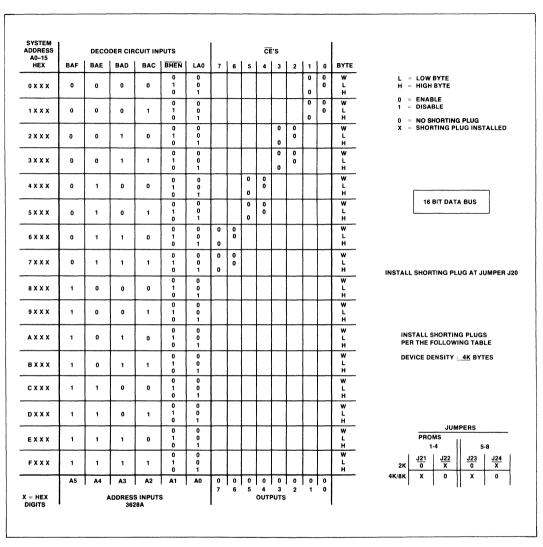

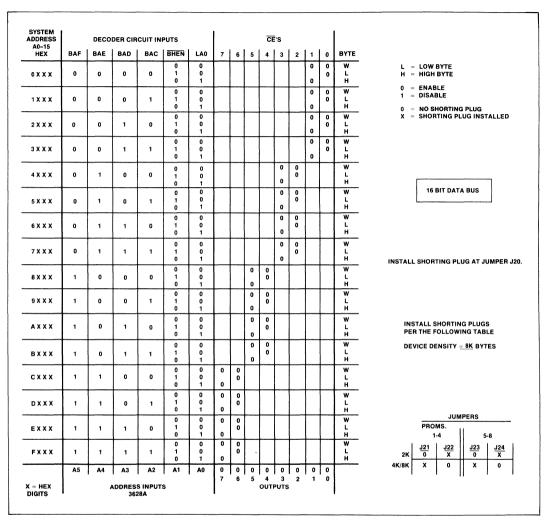

| Board Address Location                                                         | 4-98  |

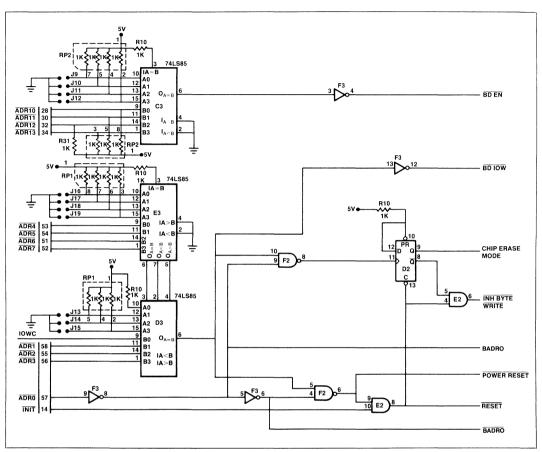

| Reset and Chip Erase Functions                                                 |       |

| Interrupt Line Selection                                                       |       |

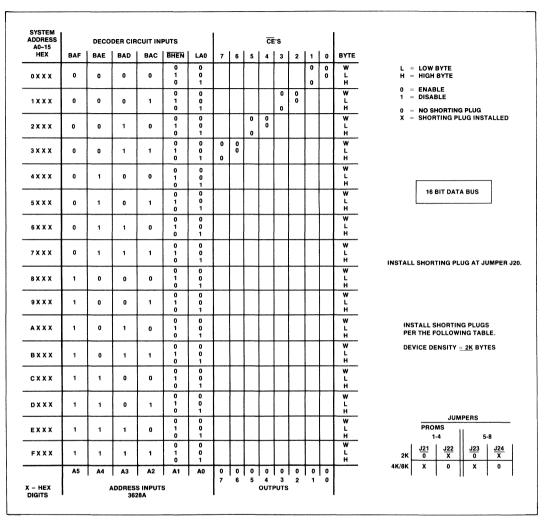

| Data Bus Width                                                                 |       |

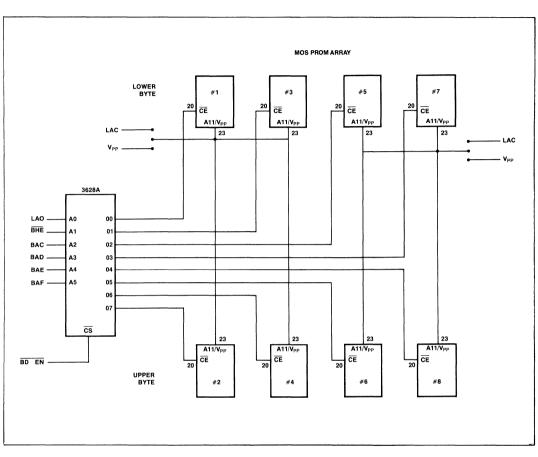

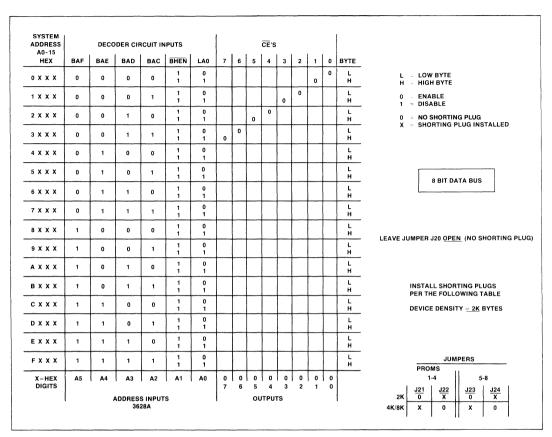

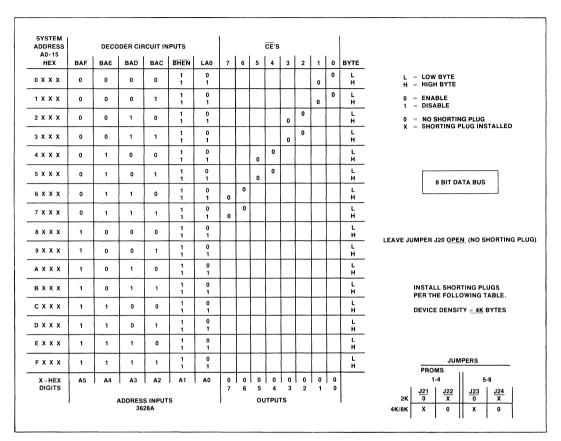

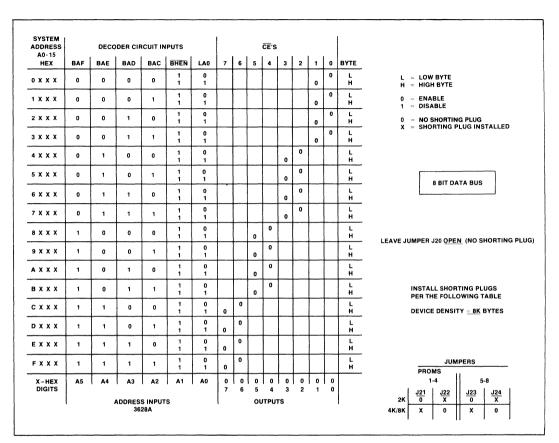

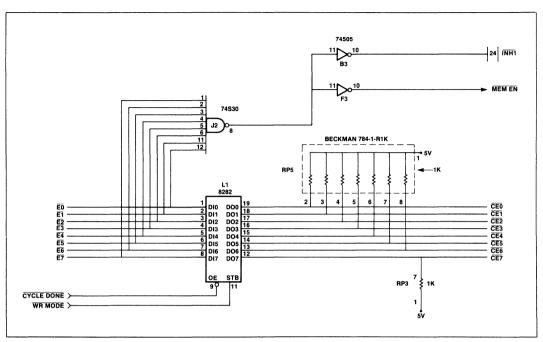

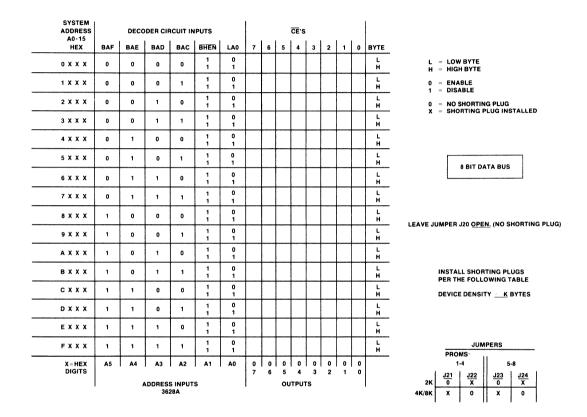

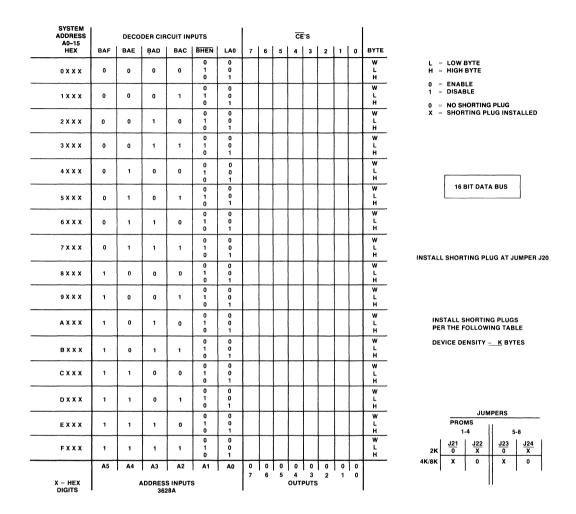

| MOS PROM Array Decoder                                                         |       |

| PROM/RAM Selection                                                             |       |

| V <sub>PP</sub> Pulse Width Selection                                          |       |

| Adjusting the V <sub>PP</sub> High Level                                       |       |

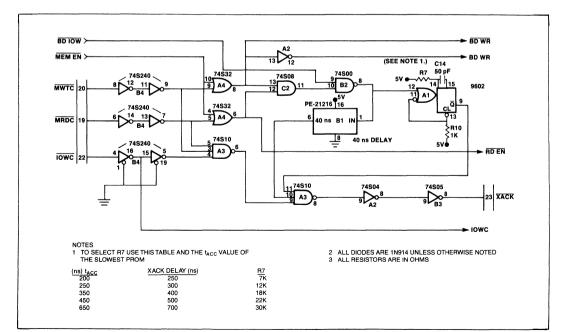

| XACK Delay                                                                     |       |

| User's Operation Instructions                                                  |       |

| User Program Example                                                           |       |

| 16-Bit Data Bus Structure                                                      |       |

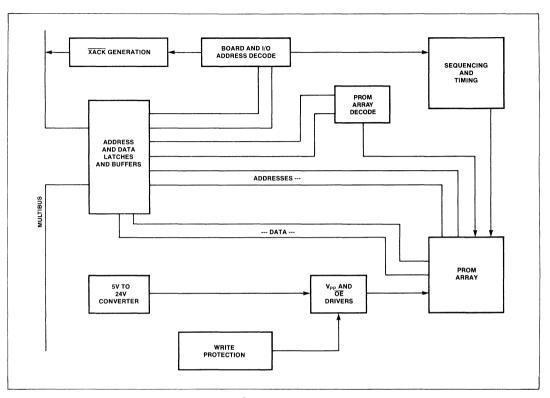

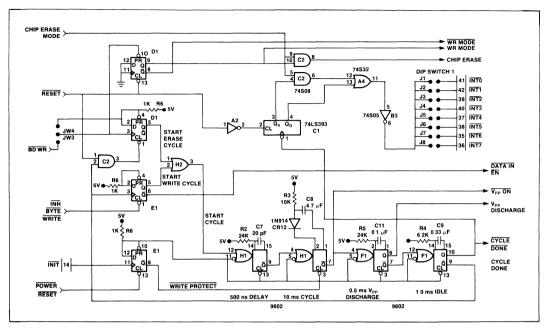

| Hardware Description                                                           |       |

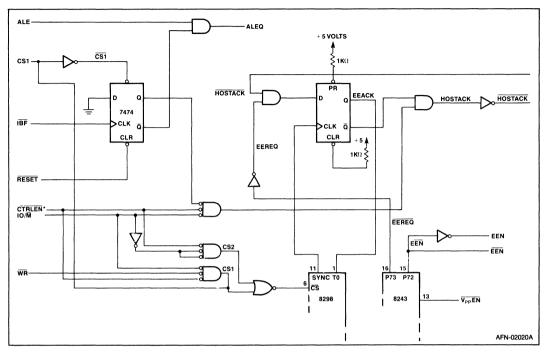

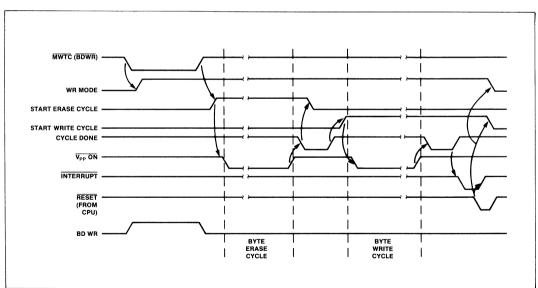

| Sequencing and Timing                                                          |       |

| XACK Generation                                                                |       |

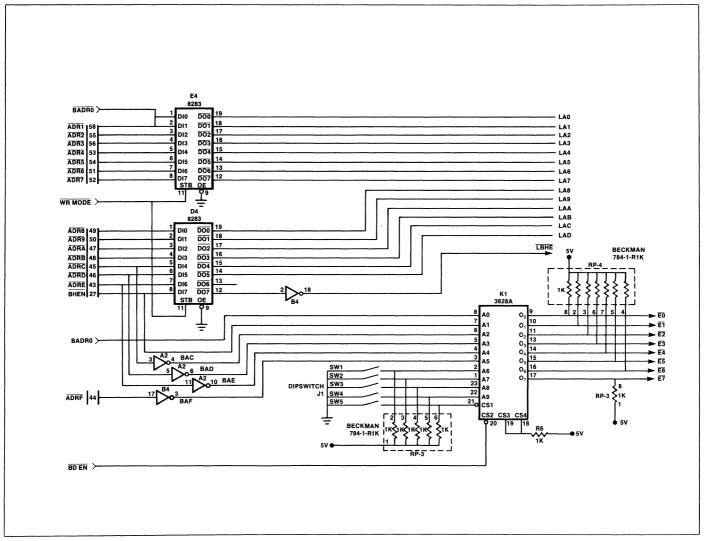

| Bus Address Decoding                                                           |       |

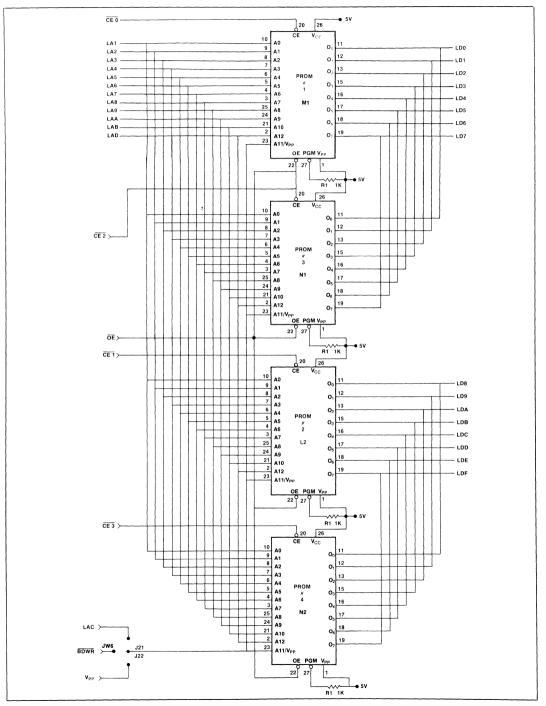

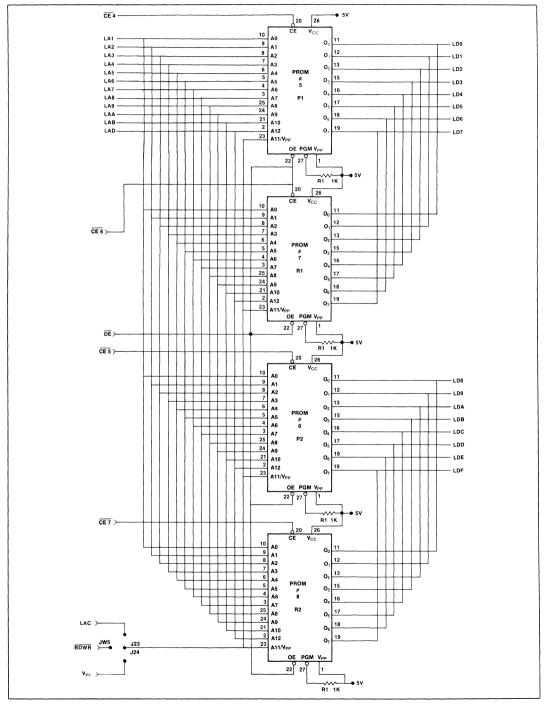

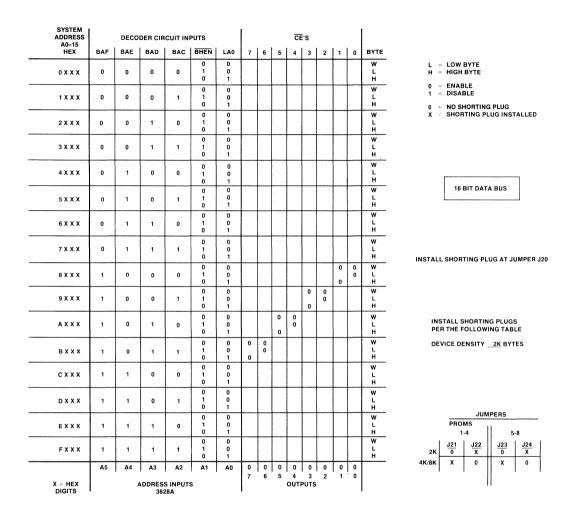

| MOS PROM Array Decoding                                                        |       |

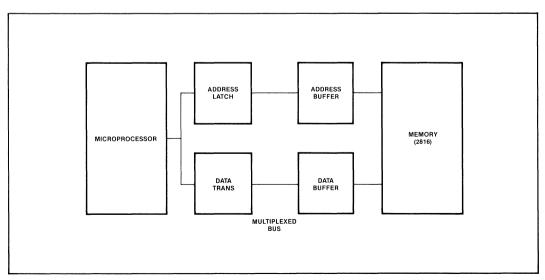

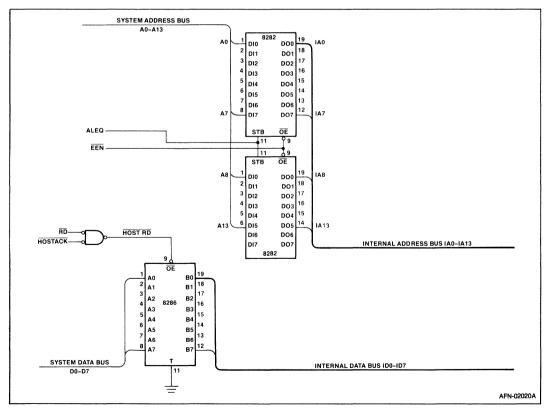

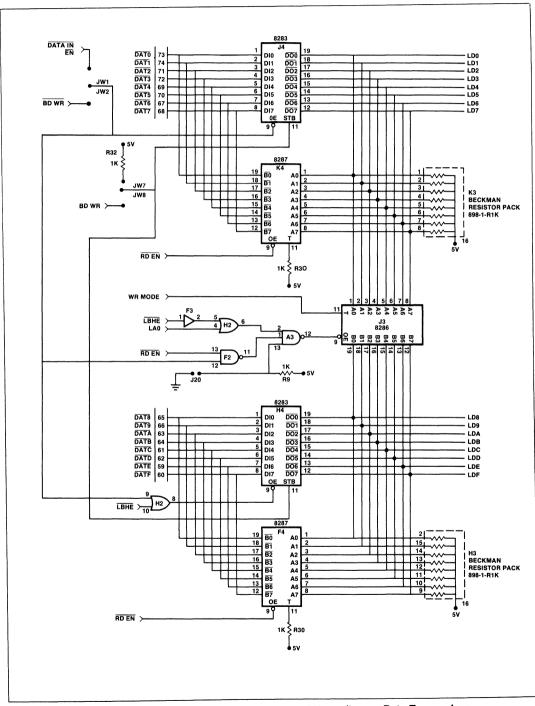

| Data and Address Latches and Buffers                                           |       |

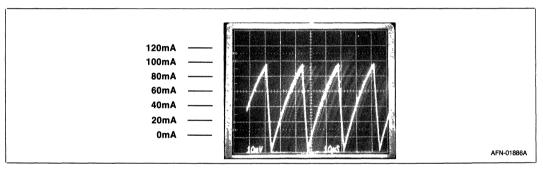

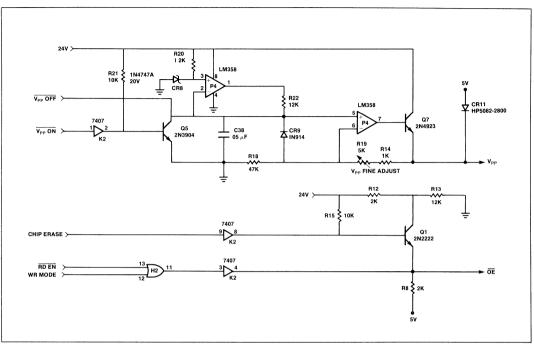

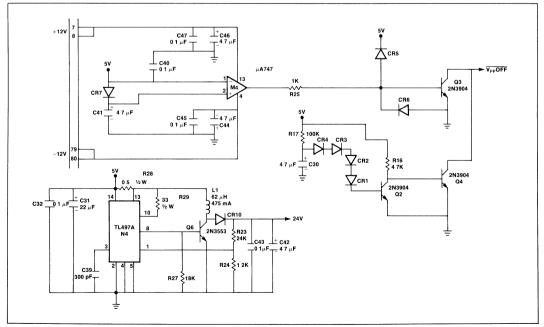

| V <sub>PP</sub> and OE Drivers                                                 |       |

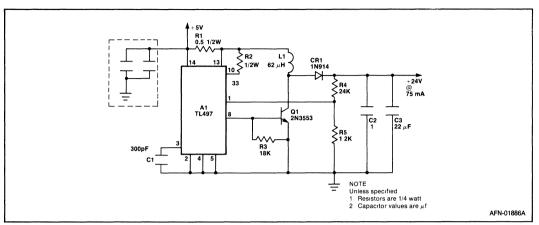

| 5V to 24V Converter                                                            |       |

| Write Protection Circuitry                                                     |       |

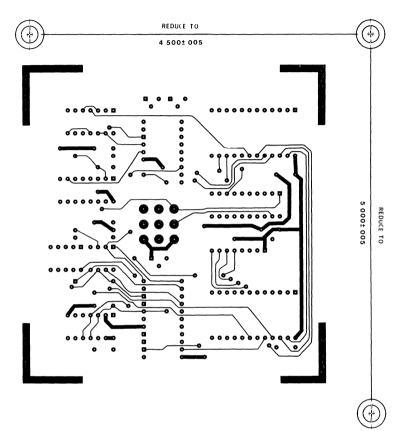

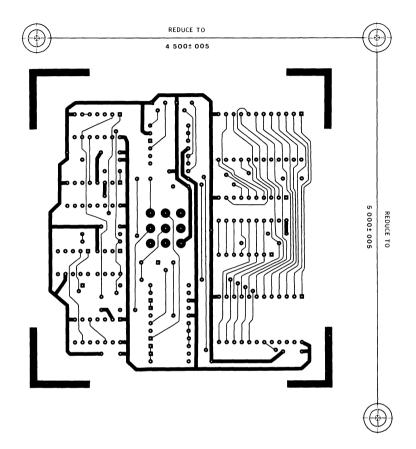

| Schematics Diagrams                                                            |       |

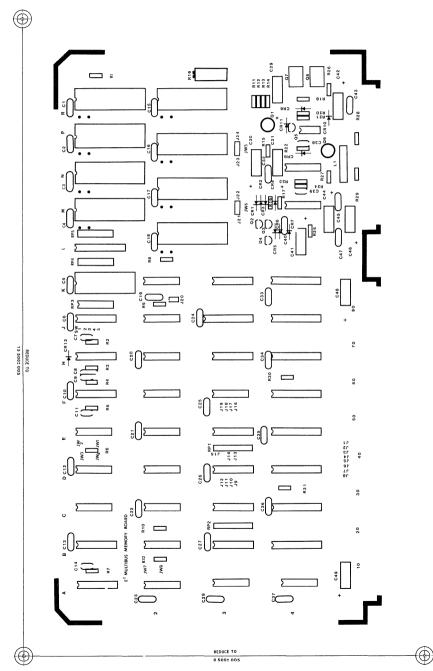

| Assembly Instructions                                                          |       |

| Appendix A: Jumper List                                                        |       |

| Appendix B: Bipolar Decoder Data Format                                        |       |

| Appendix C: Parts Lists                                                        |       |

| Appendix D: Assembly Drawing                                                   | 4-134 |

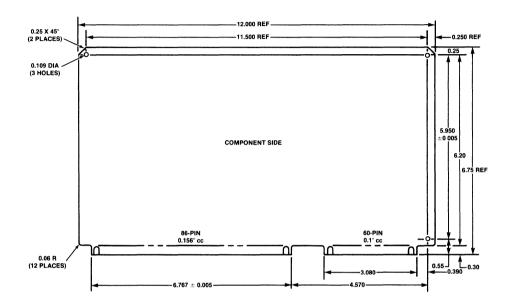

| Appendix E: Multibus PCB Dimensions                                            | 4-135 |

| Appendix F: Multibus Signal List                                               |       |

| Appendix G: Blank PROM Decoder Charts                                          | 4-137 |

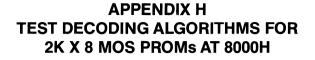

| Appendix H: Test Decoding Algorithms for 2K x 8 MOS PROMs at 8000H             | 4-139 |

| AP-137 8298 Functional Specification and Firmware Description                  | 4-141 |

|--------------------------------------------------------------------------------|-------|

| General Description                                                            |       |

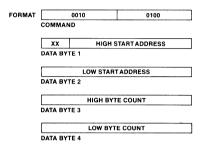

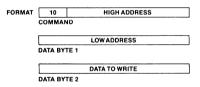

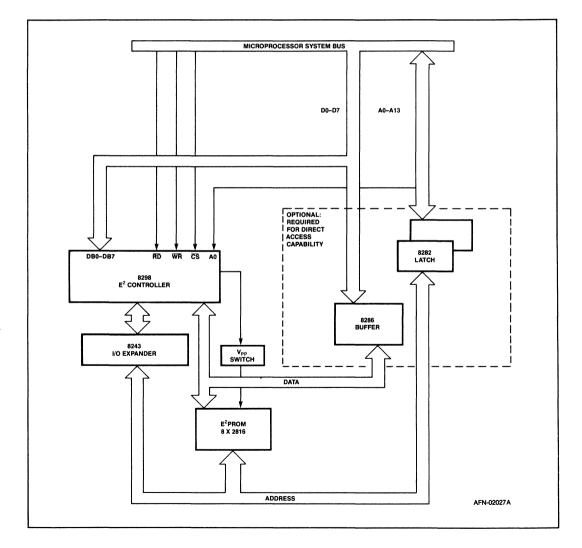

| E <sup>2</sup> Operation                                                       | 4-144 |

| Host CPU Interaction                                                           |       |

| Commands                                                                       |       |

| E <sup>2</sup> PROM Interface                                                  | 4-150 |

| V <sub>PP</sub> Switch                                                         | 4-150 |

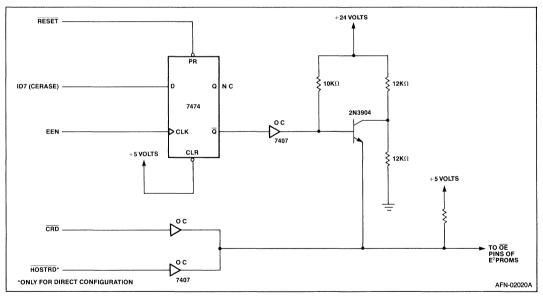

| OE Switching                                                                   |       |

| Direct Access Circuits                                                         |       |

| Chip Erase Signal                                                              |       |

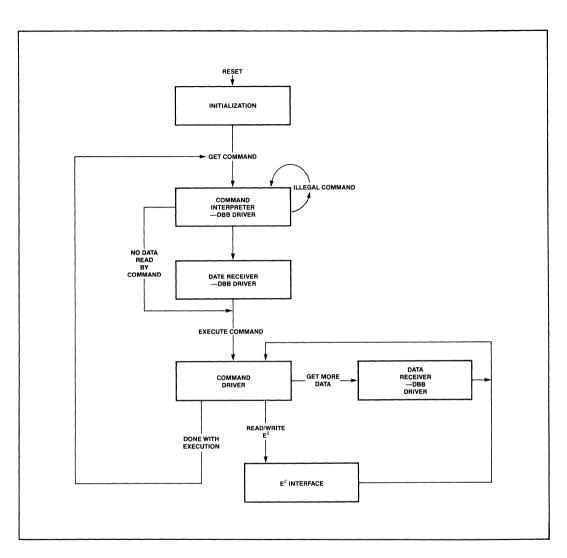

| System Operation                                                               |       |

| Reset and Power-Up Procedure                                                   |       |

| Appendix A: 8298 Electrical Characteristics                                    |       |

| Appendix B: 8243 Electrical Characteristics                                    |       |

| Appendix C: 8298 Firmware Description                                          | 4-165 |

| Appendix D: 8298 UPI-41A-Based E <sup>2</sup> PROM Controller Firmware Listing | 4-167 |

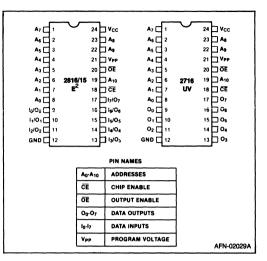

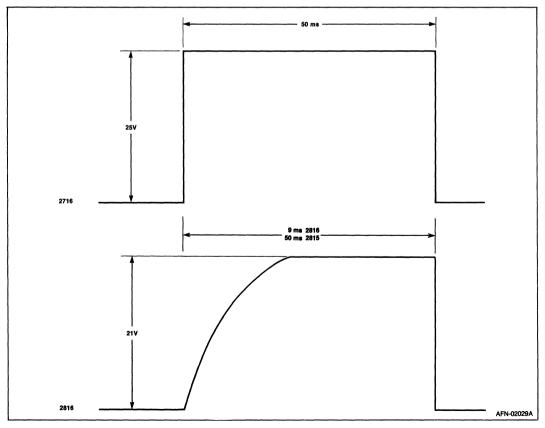

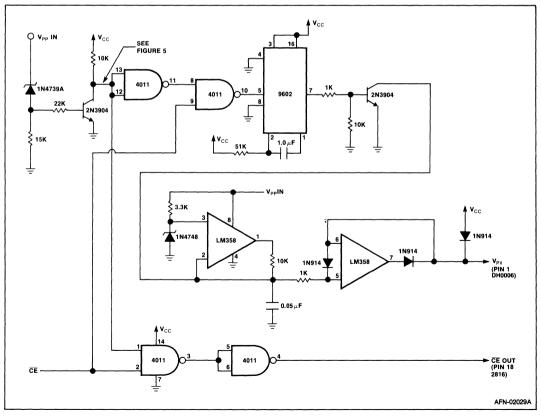

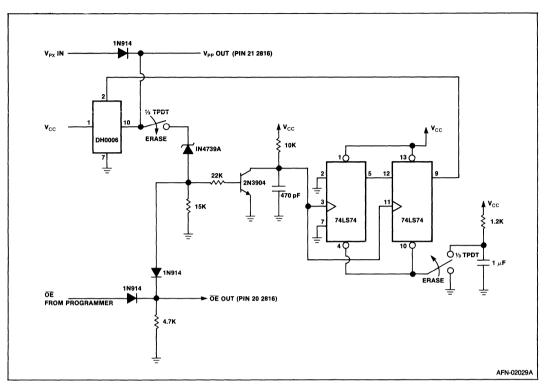

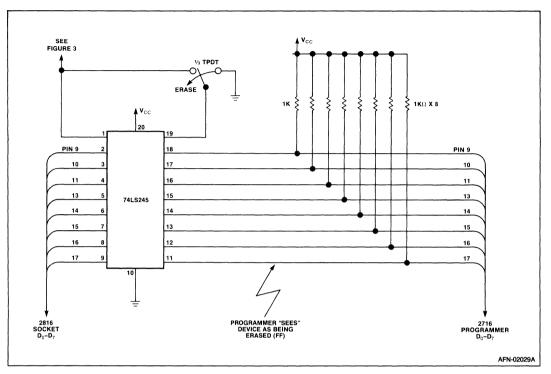

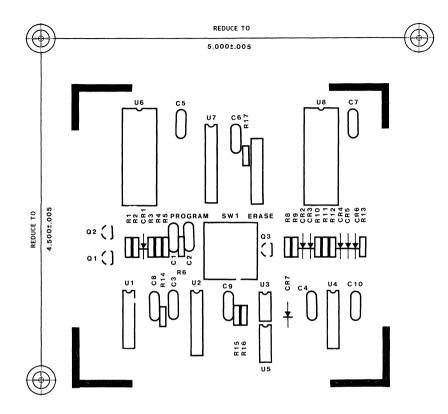

| AP-138 A 2716-to-2816 Programming Socket Adapter                               | 4-191 |

| Introduction                                                                   | 4-192 |

| Hardware                                                                       | 4-192 |

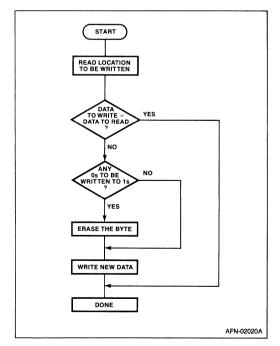

| Operation                                                                      | 4-194 |

| Conclusion                                                                     | 4-195 |

| AR-174 Hardware and Software Download Techniques with 2816                     | 4-201 |

| AR-177 Preview Reprint                                                         | 4-207 |

During the past ten years, Intel has developed EPROMs to meet the needs of the most demanding customer systems. The quest for a perfect non-volatile memory has been led by Intel from ROM to PROM to EPROM and now, after intense development, to the  $E^2$ PROM. The  $E^2$ PROM technology promises to alter dramatically the microprocessor systems of today and offer end users greatly enhanced flexibility and system cost-effectiveness.

With regard to adding functions and benefits to your systems, only you can understand the doors that the 2816 will open. Intel is committed to the technology of electrically erasable PROMs and we see it as truly a revolution in non-volatile memory.

Within this handbook are articles, application notes, application briefs, and other data which will tell you all you need to know to design the  $E^2$ PROM into your system today.

If you would like further information, contact one of the Intel Sales Representatives listed in the back or return the reply card.

#### ACKNOWLEDGEMENT

The author wishes to acknowledge the following contributors to the 2816 development and introduction: K. Armstrong, A. Baluni, B.L. Barfield, N. Boruta, R. Battat, A. Chan, V. Dham, B. Euzent, H. Fung, G. Gongwer, K. Gudger, W.S. Johnson, L.N. Jordan, D. Kijanka, P. Mareno, D. Oto, B. Pochowski, D. Schaedler, B. Shiner, and R. Wood.

Without their limitless perseverance and dedication, the 2816 would not have been possible.

# E<sup>2</sup>PROM 2 Backgrounder Information

E<sup>2</sup>PROM BACKGROUNDER

November 1980

#### INTRODUCTION

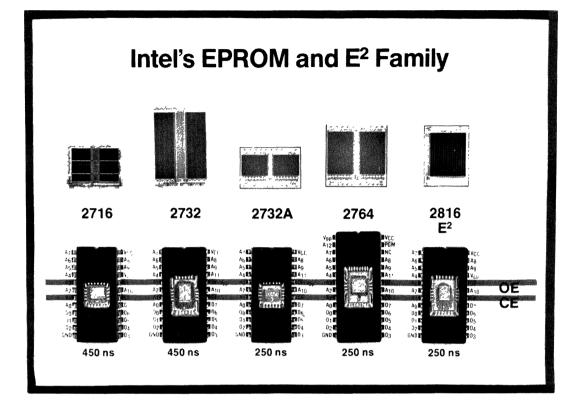

Intel Corporation, the leading manufacturer of microprocessors, semiconductor memories and microcomputer system components, has just introduced its first electrically erasable programmable read-only memory ( $E^2$ PROM). Designated the 2816, this 16kilobit  $E^2$ PROM is the first of a new breed of memory that will eventually become the standard storage medium for microprocessor programs.

Not only is the 2816 non-volatile, fully static and fast enough to support a high-performance microprocessor, but it can be reprogrammed electrically in the field, without removal from in-service equipment. It can even be reprogrammed remotely, via a radio or telephone link. This flexibility permits design engineers to realize applications that were either impossible to implement with less-flexible program-store devices, or prohibitively expensive due to the high cost of downtime or labor incurred by the user when changing the program.

#### TRENDS IN PROGRAM-STORE PERFORMANCE AND FLEXIBILITY

Since their introduction nearly a decade ago, microprocessors have become smaller, faster and much more powerful. Each new generation has been accompanied by a new class of program-store memory devices with greater flexibility—to make it easier for the original-equipment manufacturer (OEM) or end user to change its stored program—and improved performance—to match the speed of faster microprocessors.

#### Flexibility—From Zero to Total

The first program-store device was the masked readonly memory (ROM). Masked ROMs are custom devices programmed by the semiconductor manufacturer with instructions specified by the OEM buyer. Once programmed, they cannot be altered, so that each program change requires the purchase and manufacture of a new ROM, which may take months to obtain. ROMs are inexpensive to buy in large volumes, but they require a large initial investment by the OEM and a commitment to large quantities of each program.

Next came the programmable ROM, or PROM. PROMs can be "burned" by the OEM or end user but they can be programmed only once; however, they can be bought in advance and programmed and installed when needed. PROMs are costlier than ROMs on a per-unit basis, but they eliminate the risk and wait for delivery of a new batch of masked ROMs from the semiconductor manufacturer.

Erasable PROMs, or EPROMs, added considerable flexibility to the programming step. Like PROMs, EPROMs can be stocked and programmed by the OEM or end user, but they can be reprogrammed thousands of times. This eliminates the need to scrap expensive parts each time a program change is needed.

With regard to flexibility, the only drawback to EPROMs is that they must be removed from the equipment to be reprogrammed. EPROMs are erased optically, through exposure to ultraviolet light, and then rewritten electrically with the new program.

Despite this inconvenience, EPROMs are today the most popular program-store memory device. Originally envisioned as a development tool for designers who change programs frequently while prototyping and debugging a system, EPROMs have often been shipped in production equipment due to their potential value to the user who may wish to make a program change.

Electrically erasable  $(E^2)$  PROMs are the ultimate in program-store flexibility. They can be electrically reprogrammed by the OEM or end user, but without the inconvenience, time or expense it takes to remove an EPROM from equipment, send it to a service facility, erase and reprogram it and then reinstall it in the field.

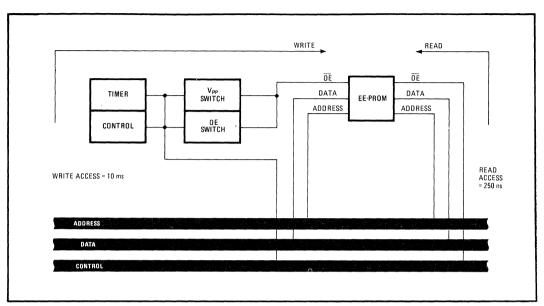

The Intel<sup>®</sup> 2816 requires only the application of a 21volt pulse for 10 milliseconds to erase or write any byte of memory. The only hardware needed to interface the 2816 to a microprocessor are a programming pulse generator and a timer circuit.

Intel's 2816  $E^2$  PROM also features an additional degree of flexibility unmatched by other high-density  $E^2$ PROM-type devices: individual byte-erase capability. To end users, this means that a single line program edit can be made in 20 milliseconds, or 100 times faster than it can be done on a bulk-erase part that must be completely erased and rewritten.

#### Performance—Ever Faster

Each new class of program-store memory must have performance comparable to that of the microprocessor it serves. Most important is access time, since a microcomputer system can only operate as fast as its slowest component. A slow program-store device can reduce the throughput and efficiency of a microprocessor which is kept waiting for its instructions. A recent trend which affects program-store memories is toward more complex systems, with multiplexed address and data lines. Program-store memories must be able to be precisely controlled by the microprocessor, to ensure that they do not read instructions onto the bus when the microprocessor is not expecting them.

The 2816  $E^2$ PROM has both the speed and controllability required for service in a state-of-the-art microcomputer system. It has an access time of 250 nanoseconds, which is fast enough to eliminate the need to insert so-called wait states in a highperformance microprocessor's program, just to allow for slow program memory.

The 2816 also features Two-line control, a systemcontrol function that has become essential in large, high-speed microcomputer systems. Two-line control eliminates contentions between addresses and data on bus lines. The chip has separate output-enable and chipenable pins that permit the microprocessor to control exactly when it is enabled.

In addition, the 2816 comes in a 24-pin package that conforms to the new industry-standard pinout for highdensity, byte-wide memories recently approved by the Joint Electron Device Engineering Council (JEDEC). By using the 2816 and printed-circuit boards with 28-pin sockets, system designers can be assured of future compatibility and interchangeability of microcomputersystem memory components up to 256 kilobits in density.

#### IMPLICATIONS AND APPLICATIONS

$E^2$ PROMs will have a profound impact on microcomputer system design. As designers learn to fully use their flexibility,  $E^2$ PROMs' cost per function will fall dramatically through greater design efficiency.

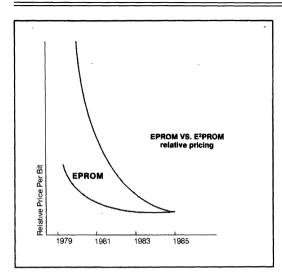

The semiconductor cost/volume learning curve will reduce  $E^2$ PROM prices to parity with EPROMs by the mid-1980s, when they will replace EPROMs as the standard program-store medium in microprocessor-based equipment. In the interim,  $E^2$ PROMs will be designed into those applications where their cost is offset by the

functional value their flexibility adds to the end-user product.

#### **Near-Term Applications**

One market segment that will find  $E^2$ PROMs attractive immediately is industrial process control. In large plants with distributed processing stations under control of a central computer,  $E^2$ PROMs can improve local process monitoring and control.

In such configurations, the central computer alters the  $E^2$ PROMs' contents remotely when a change in process occurs, to optimize local processor operation to the new conditions. The  $E^2$ PROMs can also be used as data store devices to monitor flow rates, value closures and like information, freeing the central computer for more important duties.

Another obvious application for  $E^2$ PROMs today is as replacements for core memory or fuse-link PROMs in military equipment and commercial aircraft. Here, the cost of an  $E^2$ PROM is more than offset by the alternative cost of replacing expensive parts each time the user wishes to change flight coordinates or radio frequencies.

Point-of-sale (POS) terminals are an ideal application for  $E^2$ PROMs, where they function as look-up tables whose contents—product pricing, for example—do not change frequently. The central computer can poll and update the  $E^2$ PROMs after business hours of the retail store, to monitor sales volumes and adjust pricing to inflation.

Another application for  $E^2$ PROMs is in programmable robots like those used in automobile manufacturing or industrial metalworking. Presently, program changes require replacing the paper or magnetic tape that controls the robot's operation. An alterable, non-volatile semiconductor memory like the 2816 has distinct advantages here, especially in light of its superior reliability in dirty industrial environments. Besides its ability to be reprogrammed quickly and remotely by a central computer, an  $E^2$ PROM can easily pay for itself by avoiding retooling charges and by preventing failures that could destroy an expensive piece of material.

**AR-118**

#### SESSION XII: ROMs, PROMs AND EROMs

#### THPM 12.6: A 16Kb Electrically Erasable Nonvolatile Memory

William S. Johnson, George Perlegos, Alan Renninger, Greg Kuhn and T. R. Ranganath<sup>†</sup>

Intel Corp.

Santa Clara, CA

FLOATING GATE STRUCTURES have been highly successful as nonvolatile devices because of their compatibility with silicon gate processing and their excellent charge retentivity with applied voltage at operating temperature. The accepted method of erasure in the commercial marketplace is ultra-violet light (EPROM)<sup>1</sup>, although proposals have been made to erase electrically by avalanche injection of holes<sup>2</sup>, electron tunneling<sup>3,4</sup>, or a combination of both<sup>5</sup>. These methods, however, have typically suffered from poor reproducibility and very fast wearout during program/erase cycling

To realize nonvolatile devices which can be erased electrically with high program/crase endurance, many have resorted to MNOS structures<sup>6</sup> which are programmed and erased by direct tunneling through a thin oxide. In this approach, charge is stored in traps within the nitride dielectric A major problem with this approach is that the properties of the nitride/oxide dielectric are difficult to control and are adversely affected by normal silicon gate processing. Furthermore, the threshold voltages of these structures are vulnerable to disturbance by even small applied voltages and data retention is not easily guaranteed for long periods (vears)

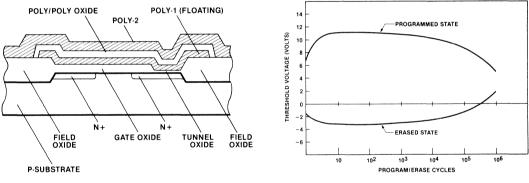

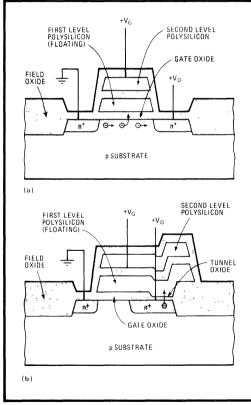

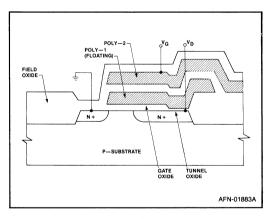

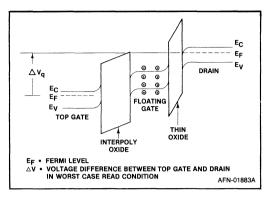

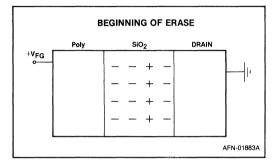

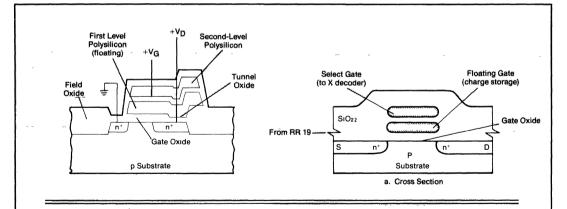

The device reported (FLOTOX, for floating gate tunnel oxide) retains the processing and the retention advantages of floating gate over MNOS while solving the traditional endurance problem This is accomplished by utilizing an oxide less than 200Å thick between a floating poly gate and an N<sup>+</sup> region, as shown in

<sup>†</sup>Current Address Hughes Research, Malibu, CA \*2716.

1

<sup>1</sup>Salsbury, P.J., Morgan, W.L., Perlegos, G. and Simko, R.T., "High Performance MOS EPROMs Using A Stacked Gate Cell", ISSCC DIGEST OF TECHNICAL PAPERS, p. 186; Feb , 1977

<sup>2</sup>Gosney, W.M., "DIFMOS — A Floating-Gate Electrically Erasable Nonvolatile Semiconductor Memory Technology", *IEEE Transactions on Electron Devices*, ED-24, p. 594, May, 1977.

<sup>3</sup>Gulterman, D.C., Rimari, I.H., Halvorson, R.D., McElroy, D.J. and Chan, W W, "Electrically Alterable Hot-Electron Injection Floating Gate MOS Memory Cell With Series Enhancement", *IEDM Technical Digest*, p. 340; Dec., 1978

<sup>4</sup>Haran, E, Schmitz, L, Troutman, B and Wang, S., "A 256-Bit Nonvolatile Static RAM", *ISSCC DIGEST OF TECH-NICAL PAPERS*, p. 108; Feb , 1978.

<sup>5</sup>Scheibe, A and Schulte, H., "Technology of a New N-Channel One-Transistor EAROM Cell Called SIMOS", *IEEE Transactions on Electron Devices*, ED-24, p. 600; May, 1977.

<sup>6</sup>Hagiwara, T., Kondo, R., Yatusuda, Y., Minami, S and Itoh, Y., "A 16Kb Electrically Erasable Programmable ROM", ISSCC DIGEST OF TECHNICAL PAPERS, p. 50, Feb., 1979

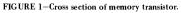

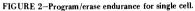

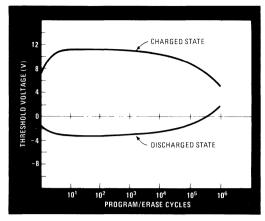

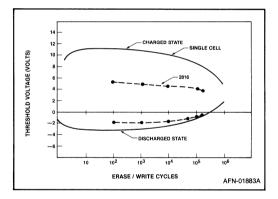

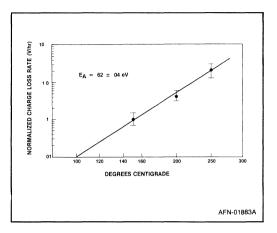

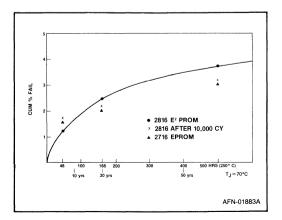

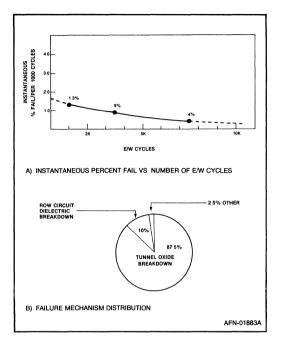

<sup>7</sup>Lenzlinger, M. and Snow, E.H., "Fowler-Nordheim Tunnelling into Thermally Grown SiO<sub>2</sub>", J of Applied Physics, 40, p. 278-283, Jan., 1969. Figure 1. In FLOTOX both program and erase are accomplished by tunneling<sup>7</sup> of electrons through the tunnel oxide using voltages of less than 25V. A typical endurance plot for a single cell appears in Figure 2. This shows that the threshold window remains open beyond 100,000 cycles. Also by keeping voltages low during read, this structure can retain charge over 10 years under full power, at operating temperatures. There is no refresh requirement no matter how many read accesses are made.

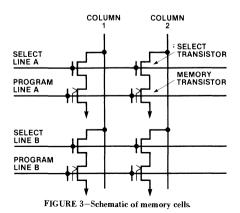

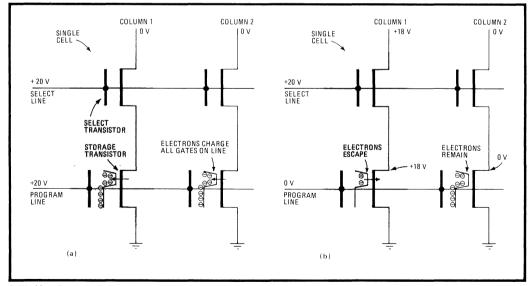

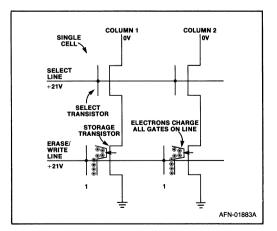

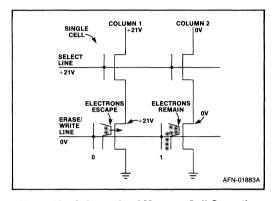

The FLOTOX cell configuration, shown in Figure 3, uses two devices, a select transistor and a memory transistor Cell area is 0.85mil<sup>2</sup>. Clearing of the memory is accomplished by programming every device in a row. This is done by selecting a row and raising the program line to VPP, which attracts electrons to the floating gate. Writing is accomplished by erasing selected bits within a word. This is done by again selecting a row, but now the program line is held at zero volts while selected columns go to VPP. Electrons are thus removed from the floating gates of the selected devices.

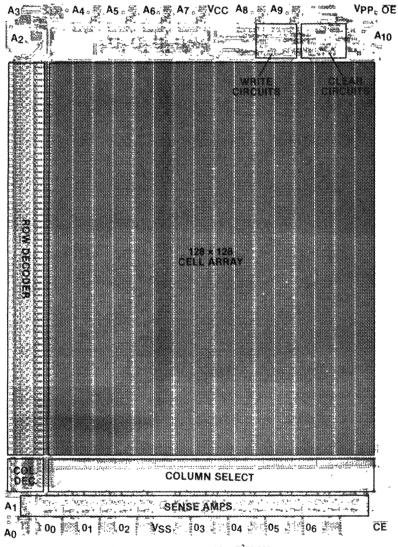

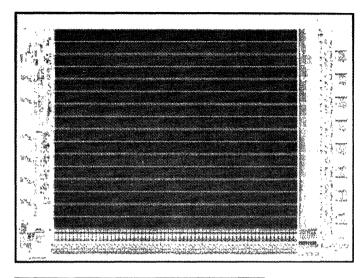

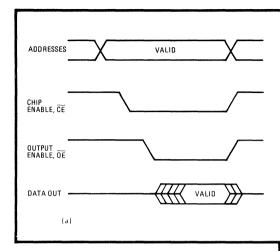

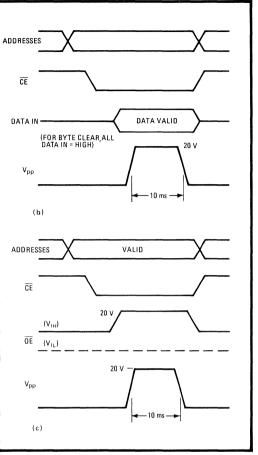

Figure 4 shows the 16K chip, which is arranged as 2K/8b words. It is packaged with 24 leads with a pinout identical to the 16K EPROM<sup>\*</sup>. The chip is automatically powered down until selected ( $\overline{CE}$  low). Read is accomplished by selecting the part and enabling the output buffers ( $\overline{OE}$  low). On the other hand, selecting the part and taking VPP to 20V for 10ms puts the chip in write mode and writes a word. If the incoming data are all 1's, then the chip automatically goes into clear mode and clears the addressed word. Thus, a clear-write sequence requires merely two 10ms writes, first all 1s, then the data desired. If clearing of the entire chip is desired, this can be accomplished with one 10ms pulse by applying VPP to  $\overline{OE}$  as well as the VPP pin with the chip selected. This approach allows a wide variety of functions while maintaining simple control and complete EPROM compatibility.

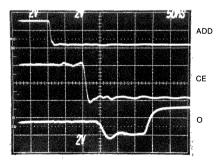

FLOTOX utilizes a new high performance N-channel twolevel-poly silicon gate technology with channel lengths of  $3.5\mu$ . Access times for the 16K FLOTOX  $E^2$ PROM are below 200ns as shown in Figure 5. This allows use of the device with the newer microprocessors which operate in the 5-8MHz range without wait states Other features of the 16K  $E^2$ PROM are listed in the table

FIGURE 5-Access time for  $E^2$ PROM.

|                     | 16K E <sup>2</sup> PROM | 16K EPROM              |

|---------------------|-------------------------|------------------------|

| Configuration       | 2K X 8                  | 2K X 8                 |

| Package             | 24 pin                  | 24 pin                 |

| Power Supplies      |                         |                        |

| read mode           | +5                      | +5                     |

| clear/write         | +5, +20                 | +5, +25                |

| Write               |                         |                        |

| method              | tunnel injection        | hot electron injection |

| time/word           | 10ms                    | 50ms                   |

| Clear               |                         |                        |

| method              | tunnel ejection         | UV hght                |

| time/word           | 10ms                    | -                      |

| time/chip           | 10ms                    | 30 min                 |

| Access Time         | 200ns                   | 450ns                  |

| Power Dissipation   |                         |                        |

| active              | 500mW                   | 550mW                  |

| standby             | 100mW                   | 100mW                  |

| Data Retention      | 10 years                | 10 years               |

| Refresh Requirement | None                    | None                   |

TABLE 1

[See page 271 for Figure 4.]

AR-119

March 1980

he electrically erasable programmable read-only memory, or EE-PROM, will one day be the standard form of program storage in microprocessor-based systems. It will follow in the steps of the ultraviolet-light-erasable PROM, for it, too, will become available in increasingly larger byte-wide arrays and will in time share silicon with single-chip microcomputers. As with the E-PROM, the success of the EE-PROM described in this article hinges upon the mastery of a difficult process. The floating-gate avalanche cell, also pioneered by Intel. is a tricky construction that still eludes many a memory maker. Likewise, the widespread availability of large EE-PROMs is still years off. The EE PROM process will be perfected, though, because the rewards go beyond the elimination of the expensive quartz window on the E-PROM package. The electrically erasable memory will usher in systems

previously not practical. The microprocessor system whose programs can be altered remotely, as by phone, is one example. Another is the system that is immine to power outages, as it protects its contents in ROM. Perhaps most important, systems will be able to adjust their own program memory to environmental changes.

To be sure, there is more than one way to build an EE-PROM. The metal-nitride-oxide-semiconductor (MNOS) structure has served for years in modest-sized arrays for TV tuning applications, for example. In fact, a year ago Hitachi Ltd. announced a 2-K-by-8-bit MNOS replacement for the 2716 E-PROM. Compatibility with the 2716 is the impetus behind the device described in the following article, but it uses only silicon and its derivatives, plus metal. Also, in place of avalanche injection, which can injure a cell, electrons tunnel to and from a floating gate. -John G. Posa

# 16-K EE-PROM relies on tunneling for byte-erasable program storage

Thin oxide is key to floating-gate tunnel-oxide (Flotox) process used in 2,048-by-8-bit replacement for UV-light–erasable 2716 E-PROM

by W. S. Johnson, G. L. Kuhn, A. L. Renninger, and G Perlegos, Intel Corp., Santa Clara, Calif

□ The erasable programmable read-only memory, or E-PROM, is the workhorse program memory for microprocessor-based systems. It is able to retain data for years, and it can be reprogrammed, but to clear out its contents for new data, ultraviolet light must be made to stream through its quartz window. This works well for many applications, but the technique foregoes singlebyte—in favor of bulk—erasure and in-circuit selfmodification schemes.

Electrical erasability is clearly the next step for such memories, but like ultraviolet erasure a few years back, it is hard to achieve. In fact, the design of an electrically erasable read-only memory is paradoxical. In each cell, charge must somehow be injected into a storage node in a matter of milliseconds. Once trapped, however, this charge may have to stay put for years while still allowing the cell to be read millions of times. Although these criteria are easily met individually, the combination makes for a design with conflicting requirements.

These demands are more than met in a new EE-PROM, which is a fully static, 2-K-by-8-bit, byte- or chip-erasable nonvolatile memory. At 16,384 bits, this new design not only meets the goal of high density, but also has long-term retention, high performance, and no refreshing requirement, in addition to functional simplicity unmatched by present nonvolatile memories. The device need not be removed from a board for alterations, and performance is consistent with the latest generation of 16-bit microprocessors such as the 8086.

This achievement required the development of a new nonvolatile process technology, HMOS-E, as well as a new cell structure, Flotox, for floating-gate tunnel oxide.

#### **Conflicting requirements**

Nonvolatile semiconductor memories generally store information in the form of electron charge. At cell sizes achievable today, this charge is represented by a few million electrons. To store that many electrons in a 10-millisecond program cycle requires an average current on the order of  $10^{-10}$  amperes. On the other hand, if it is essential that less than 10% of this charge leaks away in 10 years, then a leakage current on the order of

Electronics / February 28, 1980

The next memory. The 16-K electrically erasable programmable read-only memory is eminently suitable for microprocessor program storage Organized as 2,048 by 8 bits, the EE-PROM allows full-chip or individual-byte erasure using the same supply ( $V_{\rm sc}$ ) as for programming

1. First Famos, now Flotox. The Famos cell (a) found in all E-PROMs stores charge on the floating gate by avalanche means Flotox cell (b), the heart of the EE-PROM, relies on electron tunneling through thin oxide to charge and discharge the floating gate

$10^{-21}$  A or less must be guaranteed during read or storage operations. The ratio of these currents,  $1:10^{11}$ , represents a difficult design problem. Few charge-injecting mechanisms are known that can be turned off reliably during nonprogram periods for such a ratio.

One structure that has proven capable of meeting such stringent reliability requirements has done so for many millions of devices over the last nine years. This is the floating-gate avalanche-injection MOS (Famos) device used in the 1702, 2708, 2716, and 2732 E-PROM families In the Famos structure, shown in Fig. 1a, a polysilicon gate is completely surrounded by silicon dioxide, one of the best insulators around. This ensures the low leakage and long-term data retention.

To charge the floating gate, electrons in the underlying MOS device are excited by high electric fields in the channel, enabling them to jump the silicon-silicon-dioxide energy barrier between the substrate and the thin gate dielectric. Once they penetrate the gate oxide, the electrons flow easily toward the floating gate as it was previously capacitively coupled with a positive bias to attract them.

Because of Famos' proven reliability, the floating-gate approach was favored for the EE-PROM. The problem, of course, was to find a way to discharge the floating gate electrically. In an E-PROM, this discharge is effected by exposing the device to ultraviolet light. Electrons absorb photons from the UV radiation and gain enough energy to jump the silicon/silicon-dioxide energy barrier in the reverse direction as they return to the substrate. This suffices for off-board program rewriting, but the object of the EE-PROM is to satisfy new applications that demand numerous alterations of the stored data without removing the memory from its system environment. What evolved was the new cell structure called Flotox (Fig. 1b).

In the quest for electrical erasability, many methods were considered, and several potentially viable solutions were pursued experimentally. One initially attractive

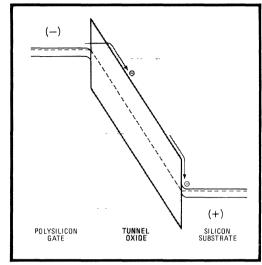

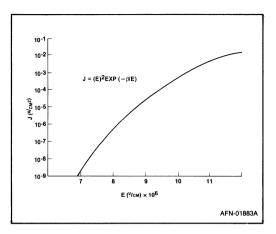

**2. Tunneling.** For a thin enough oxide, as shown here, under a field strength of 10<sup>7</sup> V/cm, Fowler-Nordheim tunneling predicts that a certain number of electrons will acquire enough energy to jump the forbidden gap and make it from the gate to the substrate

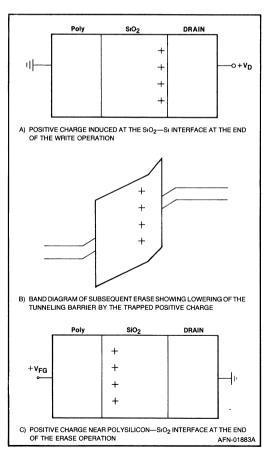

approach attempts to harness a parasitic charge-loss mechanism discovered in the earliest E-PROMs. Referring again to Fig. 1a, the polysilicon grains on the top surface of the floating gate tend, under certain processing conditions, to form sharp points called asperities. The sharpness of the asperities creates a very high local electric field between the polysilicon layers, shoving electrons from the floating gate toward the second level of polysilicon. This effect is purposely subdued in today's E-PROMs by controlling oxide growth on top of the floating gate because this parasitic electron-injection mechanism would otherwise interfere with proper E-PROM programming.

It was first thought that asperity injection could be used to erase the chip. In fact, fully functional, electrically erasable test devices were produced; but the phenomenon proved unreproducible and the devices tended to wear out quickly after repeated program and erase cycling. After over a year's effort, that approach was abandoned.

#### **Tunneling solution**

The solution turned out to be the one that initially seemed impossible. After investigating many methods of producing energetic electrons, it was decided to approach the problem from a different direction: to pass low-energy electrons through the oxide. This could be accomplished through Fowler-Nordheim tunneling, a well-known mechanism, depicted by the band diagram in Fig. 2. Basically, when the electric field applied across an insulator exceeds approximately  $10^7$  volts per centimeter, electrons from the negative electrode (the polysilicon in Fig. 2) can pass a short distance through the forbidden gap of the insulator and enter the conduction band. Upon their arrival there, the electrons

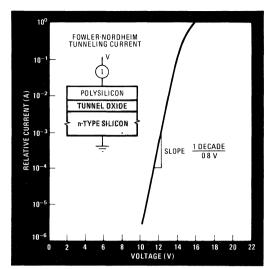

3. Current characteristic. In Fowler-Nordheim tunneling, current flow depends strongly on voltage across the oxide, rising an order of magnitude for every 0.8 V Charge retention is adequate so long as the difference between programming and reading is at least 8.8 V

flow freely toward the positive electrode.

This posed two fundamental problems. First, it was commonly believed that silicon dioxide breaks down catastrophically at about  $10^7$  V/cm, and MOS FETs are normally operated at field strengths 10 times below this. Second, to induce Fowler-Nordheim tunneling at reasonable voltages (20 V), the oxide must be less than 200 angstroms thick. Oxide thickness below about 500 Å had rarely even been attempted experimentally, and it was feared that defect densities might prove prohibitively high.

To be weighed against these risks, however, were several advantages. Tunneling in general is a low-energy, efficient process that eliminates power dissipation. Fowler-Nordheim tunneling in particular is bilateral and can be used for charging the gate as well as discharging it. Finally, the tunnel oxide area could be made very small, which is of course consistent with the needs of high-density processing.

With these motivating factors, development was initiated to grow reliable, low-defect oxides less than 200 Å thick. The success of this effort resulted in the realization of a working cell structure called Flotox.

The Flotox device cross section is pictured in Fig. 1b. It resembles the Famos structure except for the additional tunnel-oxide region over the drain. With a voltage  $V_g$  applied to the top gate and with the drain voltage  $V_d$  at 0 v, the floating gate is capacitively coupled to a positive potential. Electrons are attracted through the tunnel oxide to charge the floating gate. On the other hand, applying a positive potential to the drain and grounding the gate reverses the process to discharge the floating gate.

Flotox, then, provides a simple, reproducible means for both programming and erasing a memory cell. But

**4. Good endurance.** The endurance of the EE-PROM depends on the threshold-voltage difference between the charged and discharged states Though repeated cycling degrades thresholds, the chip should stay within tolerable limits for  $10^4$  to  $10^6$  cycles

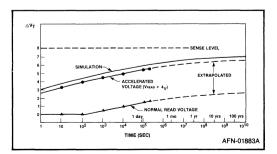

what about charge retention and refresh considerations with such a thin oxide? The key to avoiding such problems is given in Fig. 3, which shows the exceedingly strong dependence of the tunnel current on the voltage across the oxide. This is characteristic of Fowler-Nordheim tunneling.

The current in Fig. 3 rises one order of magnitude for every 0.8-v change in applied voltage. If the 11 orders of magnitude requirement is recalled, it is apparent that the difference between the voltage across the tunnel oxide during programming and that during read or storage operations must be in excess of 8.8 V. This value, including margins for processing variations, is reasonable. Furthermore, data is not disrupted during reading or storage so that no refreshing is required under normal operating or storage conditions. Extensive experimental testing has verified that data retention exceeding 10 years at a temperature of  $125^{\circ}$ C is possible.

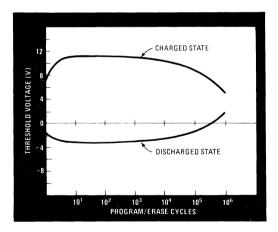

Another important consideration is the behavior of the electrically erasable memory cell under repeated program erase cycling. This is commonly referred to as endurance. The threshold voltage of a typical Flotox cell, in both the charged and discharged states, is shown in Fig. 4 as a function of the number of programming or erasing cycles. There is some variation in the threshold voltages with repeated cycling but this remains within tolerable limits out to very high numbers of cycles—somewhere between  $10^4$  and  $10^6$  cycles

#### **Putting Flotox to work**

The Flotox cell is assembled into a memory array using two transistors per cell as shown in Fig. 5 The Flotox device is the actual storage device, whereas the upper device, called the select transistor, serves two purposes. First, when discharged, the Flotox device exhibits a negative threshold. Without the select transistor, this could result in sneak paths for current flow through nonselected memory cells. Secondly, the select transistor prevents Flotox devices on nonselected rows from discharging when a column is raised high.

The array must be cleared before information is entered. This returns all cells to a charged state as shown schematically in Fig 5a. To clear the memory all the select lines and program lines are raised to 20 v while all the columns are grounded. This forces electrons through the tunnel oxide to charge the floating gates on all of the

5. Working. To clear a Flotox cell, select and program lines are raised to 20 V and columns are grounded (a). To write a byte of data, the program line is grounded and the columns of the selected byte are raised or lowered according to the data pattern (b).

AFN-01913A

selected rows. An advantage of this EE-PROM over E-PROMs is the availability of both byte- and chip-clear operations. The byte-clear one is particularly useful for a memory of this size. When it is initiated, only the select and program lines of an addressed byte rise to 20 V.

To write a byte of data, the select line for the addressed byte is raised to 20 v while the program line is grounded as shown in Fig. 5b. Simultaneously, the columns of the selected byte are raised or lowered according to the incoming data pattern. The bit on the left in Fig. 5b, for example, has its column at a high voltage, causing the cell to discharge, whereas the bit on the right has its column at ground so its cell will experience no change. Reading is accomplished by applying a positive bias to the select and program lines of the current. A cell with a charged gate will remain off in this condition but a discharged cell will be turned on.

#### From the outside

In terms of its pinout and control functions, the EE-PROM has evolved from the 2716 E-PROM. Both are housed in 24-pin dual in-line packages, for instance, and both offer a power-down standby mode. In addition, both utilize the same powerful two-line control architecture for optimal compatibility with high-performance microprocessor systems. Referring to Fig. 6a, it is seen that both control lines, chip enable ( $\overline{OE}$ ) and output enable ( $\overline{OE}$ ), are taken low to initiate a read operation. The purpose of chip enable is to bring the memory out of standby to prepare it for addressing and sensing. Until the outputs remain in the high-impedance state to avoid system bus contention. In its read mode, the EE-PROM is functionally identical to the 2716.

A single + 5-v supply is all that is needed for carrying out a read. For the clear and write functions, an additional supply ( $V_{PP}$ ) of 20 v is necessary. The timing for writing a byte is shown in Fig. 6b. The chip is powered up by bringing  $\overline{CE}$  low. With address and data applied, the write operation is initiated with a single 10-ms, 20-v pulse applied to the V<sub>PP</sub> pin. During the

**6. Timing.** The Flotox memory's operating modes are shown for reading (a), writing or clearing of bytes (b), and chip clearing (c) Both writing and erasing require a 10-ms program-voltage pulse The read mode is functionally identical to that of a 2716 E-PROM.

write operation,  $\overline{OE}$  is not needed and is held high.

A byte clear is really no more than a write operation. As indicated in Fig. 6b, a byte is cleared merely by being written with all 1s (high). Thus altering a byte requires nothing more than two writes to the addressed byte, first with the data set to all 1s and then with the desired data. This alteration of a single byte takes only 20 ms. In other nonvolatile memories, changing a single byte requires that the entire contents be read out into an auxiliary memory. Then the entire memory is rewritten. This process not only requires auxiliary memory; for a 2-kilobyte device it takes about one thousand times as long (20 ms vs 20 seconds).

Chip clear timing is shown in Fig. 6c. The only difference between byte clear and chip clear is that  $\overline{OE}$  is raised to 20 v during chip clear. The entire 2 kilobytes are cleared with a single 10-ms pulse. Addresses and data are not all involved in a chip-clear operation.

APPLICATION BRIEF AB-1

April 1981

#### A VARIABLE ATTRIBUTE CRT TERMINAL

As the proliferation of the microcomputer continues, there will be an ever increasing requirement for local CRT terminals in households, businesses, and offices. This proliferation is expected to occur throughout the world, which places a burden on the terminal designer to accomodate a wide variety of languages, processing speeds, and transmission protocols. Given memory elements and tools available today, it is difficult to achieve a cost-effective design that will deal with all these variables. The 2816 offers an excellent alternative in the design of the CRT controller by allowing a high degree of universality and a virtually unlimited number of terminal attributes.

The  $E^2$  family offers an excellent alternative to the system designer for use of a non-volatile Electrically Erasable memory device. The 2816 can contain both the raw program needed by the CRT terminal to perform basic functions, in addition to storage of the parameter information needed for local configuration. Some of the information that can be contained is baud rate transmission information, configuration of the terminal information such as parity detection reverse video, and full or half duplex modes. 2816s can contain these fundamentally basic constants which can be updated in the field by the user. This removes all of the switching components required in the past, and adds a higher degree of manufacturability and reliability to the terminal design.

In addition, the 2816 can be used as a look-up table for specific character fonts or graphic generation capabilities. This allows the terminal manufacturer to configure the font and language characteristics after manufacture, before shipment. For example, if a specific terminal is going to be shipped to a Far-Eastern nation, the font characters for that typeset can be programmed into the 2816 and shipped to that particular country. Another alternative is to allow programming of the font characters locally at the final destination of the terminal. The user can then program specific fonts and characters as required. Even greater flexibility is possible from the graphics generation standpoint. It is simple for a user to place the terminal into a graphics mode and generate special graphics characters unique to the application. This can occur through local configuration of graphic types. The terminal could have a graphics mode, where a basic map of the character is presented on the monitor. The user then locates inside the graphic boundaries the necessary information he wishes to display. After this special graphics character is composed, the user simply pushes a command key on the terminal which loads that graphic character into  $E^2$ PROM. This is an extremely powerful application for the device because it allows each user to fit the particular terminal to a particular application. Scientific users can construct scientific or calculational characters and fonts, while businesses can configure business- or table-oriented fonts.

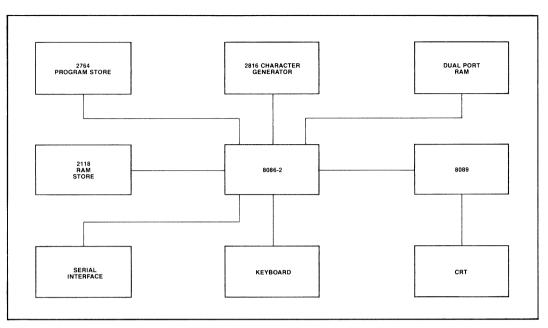

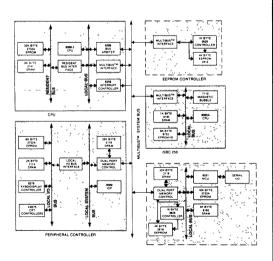

The block diagram of the system indicates that is used 2816 as a character generator store. The microprocessor used could be a high-speed 8086-2, or perhaps a 8088 microprocessor. Within the system is a 8279 keyboard display controller, which is used to interface with a standard terminal keyboard. In addition, we can use an Intel 8275 or 8276 CRT controller to generate graphic information on the face of the CRT. Also local to the system is an  $E^2$  controller which is used to interface the 2816 to the microprocessor.

Other than the basic components within the system, we may wish to add a serial I/O interface which will allow remote configuring of the characters and communication protocols. The terminal can have a serial load operation where the 2816 is updated after receiving a command character. Other than the basic components, much of the functional operation of the terminal is determined by software.

The 2816 adds the capability of custom graphics, userdefinable fonts and character sets, and programmable communication protocols. All this is possible because of the capabilities that the  $E^2$  brings to system designs.

AB-1

Figure 1. Variable Font C.R.T. Terminal

intel

) ))) - APPLICATION BRIEF

April 1981

#### **POINT OF SALE TERMINAL**

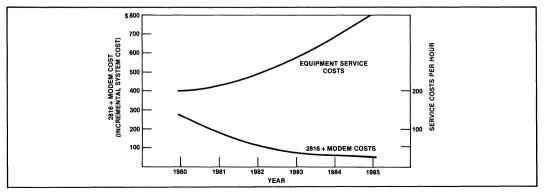

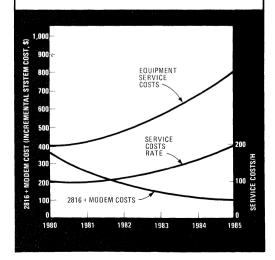

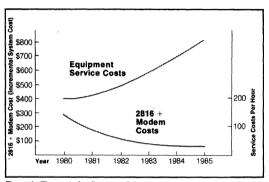

Remote reconfiguration capability—that design feature can save millions of dollars in Point Of Sale Terminal service costs. With the capability of Intel's 2816 Electrically Erasable PROM, remote changes in terminal constants are now possible—no service personnel are necessary. How often have product codes and pricing information needed changes? In today's economy, one might answer "too frequently". With service costs today of over \$100 per hour, those changes can be very expensive. The 2816 benefits users of Point of Sale Terminals by eliminating service costs. In this application brief the system architecture and user benefits of a 2816-based terminal will be discussed.

Point of Sale Terminals typically use look-up tables to contain product descriptions and pricing information. These tables require several different characteristics to operate optimally in a point of sale environment. The first storage attribute is non-volatility; look-up table data must be held without power for many months or years. Secondly, a dense storage media is required because typically many products with complex encoding schemes are loaded into the look-up tables. Finally, a media that can be changed relatively easily is needed because pricing and product information changes frequently. All of these necessary features have been satisfied in the past with EPROM memory, or CMOS RAM with battery backup.

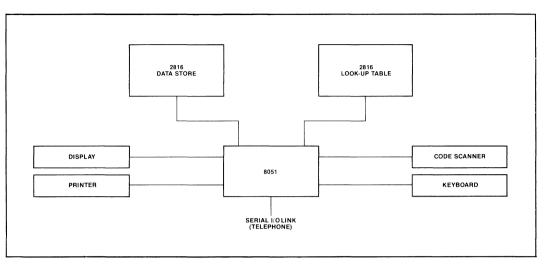

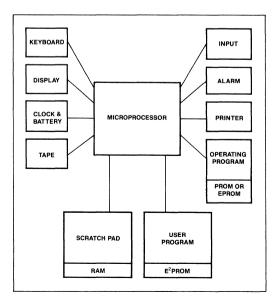

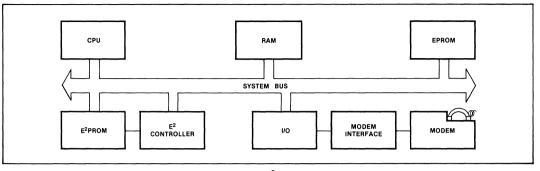

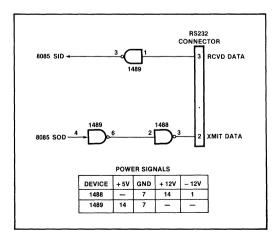

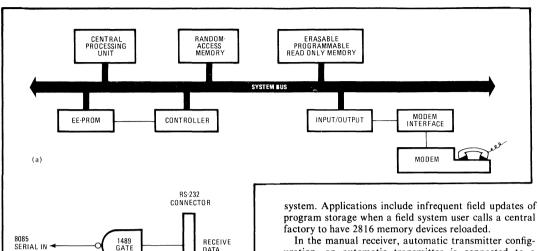

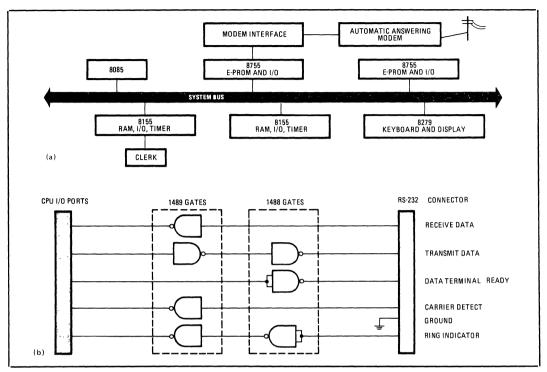

Unfortunately, these media have drawbacks. EPROMs, while low cost, dense, and non-volatile, cannot be changed in the field without the use of a service technician. CMOS and battery backup offer more flexibility at a lower density, but can suffer reliability problems if the battery and backup system aren't properly designed. The 2816 E<sup>2</sup>PROM from Intel offers users all the characteristics of EPROM with the flexible advantages of battery backed up RAMs. Look-up table data can be stored non-volatily, but can be changed while in system. Figure 1 shows the block diagram for such a system. The terminal is composed of a highperformance microcomputer, such as the 8051. In addition, 2816 memory is used as data and as look-up table storage. The typical I/O device structure for a terminal also exists in the system as shown. The most important interface indicated on the block diagram is the serial I/O link. This datacom or telecom link provides the system with remote reconfiguration capability. The contents of the 2816 can be changed from a central location, without need for costly human service.

The look-up table contains product description and pricing information. Once the table has been written, the CPU can read from it as necessary to translate product entry codes to price information. If for some reason the table data needs to be changed for pricing or product updates, then the central computer simply sends update commands and new data to the remote POS processor. Since all remote terminals are linked together at a central location and are in periodic communication with other, such an update can occur as a part of normal inter-processor communication.

The in-system erase capability of 2816 memory allows the table data to be changed remotely, while preserving the stand alone nature of the terminals. Without  $E^2$  capability, a service technician would be required to change the table data.

In addition to containing product description and pricing data, the 2816 can store special data unique to a particular location. If a set of locations within the memory is set aside for reorder codes, then as a location runs short of a particular item, the computer can automatically restock it. If particular information is sensitive, the 2816 can store encryption codes and software lockout mechanisms.

Another capability gained from the use of  $E^2$  memory is that daily totals in sales volume and product quantities can be stored in the 2816 memory. This information can be accessed by both the local users as well as the central data bank.

To summarize, in the 2816-based P.O.S. terminal described here, flexibility and greatly reduced service costs are the key. The  $E^2$  memory contains product information that can now be changed from a central location without the use of very costly service personnel. The 2816 yields an ideal solution to data table storage problems in frequently altered point of sale systems.

Figure 1. Point of Sale Terminal

•

### inte

APPLICATION BRIEF AB-3

August 1981

#### AB-3 INSTRUMENTATION: 2816 E<sup>2</sup>PROM ELIMINATES PROM PROGRAMMER OBSOLESCENCE

How often are you unable to program a vendor's new PROM because programmer personality modules and software is unavailable? And how often as a programmer vendor do you lose customers because the latest programming algorithms do not exist in your machines? If the answers to the questions above are ever "too frequently," then Intel has a solution.

If a programmer vendor could eliminate hardware redesign and tooling, and a user could eliminate costly purchase of socket adaptors—would such a programmer design be attractive? If so, the Intel 2816  $E^2$ PROM provides a system level solution. Due to the capability of the 2816 to be erased and written electrically while soldered to a Printed Circuit Board, PROM programming systems can be free of hardware redesign and socket adaptors. The 2816 can contain both pinout and algorithm data for a universal PROM socket. When a new device becomes available—a simple code change is all that is required to update the system. With such capability, the machine can operate and be revised nearly indefinitely—thereby eliminating obsolescence.

In this Application Brief, the concept of a Programmable PROM Programmer will be discussed. The basic architectural system structure will be detailed in general, then several implementation options will be discussed specifically.

#### SYSTEM ARCHITECTURE

Imagine the basic architecture of such a programmer system—the user must have the capability to easily adapt the program to suit a new device or modification of an existing algorithm. In addition, the programmer itself must be flexible enough to accept a wide variety of vendors, device types and unique algorithms. The most straightforward approach, but not the simplest, is the concept of a universal socket that is programmable through software. In such a system, each pin on the socket can be software configured to perform any function. Now, when a new device or algorithm becomes available, the software need only to change—no hardware modification is necessary. The physical constraints required on the system in many ways will dictate what type memory device is appropriate.

First, the area of memory used to contain the pinout and electrical algorithms must be non-volatile-when the machine is shut off, it must not lose the critical device data. Second, since the software will be permanently imbedded into the equipment, the data must be able to be altered electrically. Third, the memory used must be low cost-the value it presents the vendor in socket adaptors or tooling must be offset by the cost it adds to the equipment. Fourth, only those locations containing new algorithm data, or modifications to existing data, need be changed. If the entire memory contents are reset, all pinout data must be reloaded-with room for error and device programming problems. Finally, the memory must be dense enough to hold a wide variety of algorithm data, and fast enough to execute high speed programming algorithms.

The 2816  $E^2$ PROM from Intel satisfies all of the above system requirements: 1) It is completely non-volatile, 2) it can be written and erased electrically while soldered to a printed circuit card, 3) the 2815 is priced at less than \$20 in quantity—making it highly cost effective, 4) the device allows byte erase operations—only those locations that need to change can change, 5) its 2KX8 density, and 6) 250 ns access time make it dense and fast enough for most applications.

#### **BLOCK DIAGRAM**

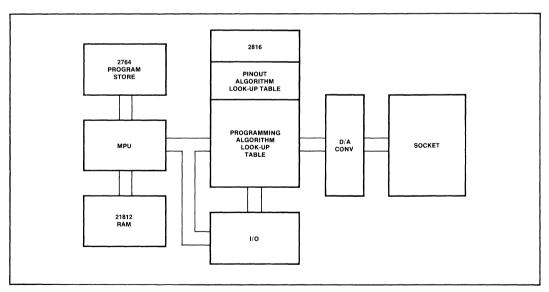

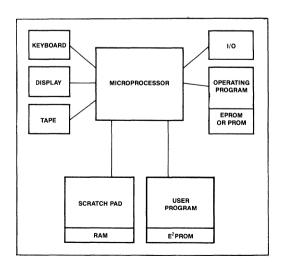

To design such a system, let us first examine the general architecture. A conceptual block diagram is shown in the figure below (Fig. A). An Intel 2764 EPROM is used to store the basic operating software that the programmer runs on. A byte wide static RAM, the 21812, is used for scratch pad and temporary data storage. 2816 is used on both pinout and programming algorithm look-up tables. Digital to Analog converters are used to interface the digital MPU commands to the programmed PROM's analog requirements. I/O is used to instruct the machine how to operate, and allows modification of  $E^2$  memory.

The overall operation of the programmer would go as follows: The user selects a device type and pushes a few keys on the I/O device. The MPU translates those keys into a device pinout and programming algorithm type. This programming data is selected from the 2816 look-up tables. The pinout is then configured at the universal socket. The device is then programmed according to the programming look-up tables. Should a new device become available, then the user need only to modify the  $E^2$  look-up table to allow the device to be programmed.

#### LOOK-UP TABLE MODIFICATION

Modifying the look-up table can be done in several different ways. Changing parameters through the keyboard is an option—but has the disadvantage that the data could be entered incorrectly, or other portions of the look-up table could be changed inadvertently.

Linking the machine to a central data computer through a modem is another option that is probably too expensive for both end-user and programmer manufacturer. Using magnetic paper tapes or cards is another possibility, but now additional I/O devices are required. The option that seems the most effective is to use the programmer itself to modify its look-up table.

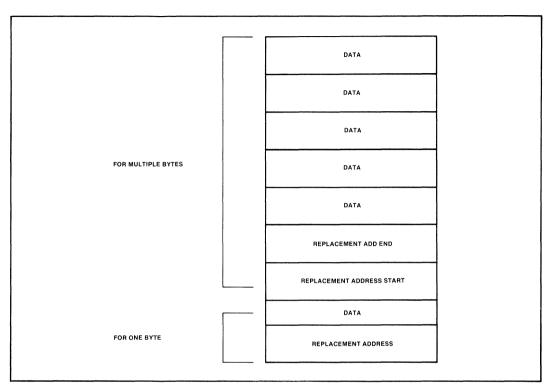

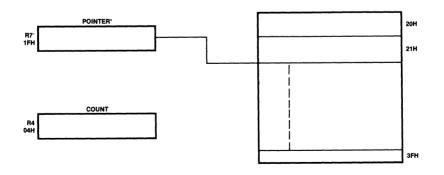

In this case the programmer manufacturer need only send a low cost EPROM to the user. The user would simply place the EPROM in the programmer, placing the programmer into a "Learn" mode. This special mode would simply copy the contents of the EPROM into the  $E^2$ PROM, free from user error or inadvertent tampering. Because the EPROM is so low in cost, the user would simply discard it after use. A low density EPROM could be used (such as a 2716) because only a small portion of the  $E^2$  storage area needs to be changed. Figure B shows the possible memory map of the "Loader" PROM. Pointers are used for address and data and only those locations needing to be changed are modified in the  $E^2$  memory.

#### CONCLUSION

Dealing with changing vendor algorithms and rapidly advancing technology can be a difficult task for both PROM programmer vendors and users alike. The 2816  $E^2$ PROM from Intel can eliminate problems associated with the above, through the use of software controlled pinout and programming algorithms. Changes to operating look-up tables can be done simply, easily, and error free.  $E^2$  benefits users with more up-to-date programming systems with reduced adaptor costs.  $E^2$ benefits programmer manufacturers through reduced hardware tooling, faster algorithm changes, and more rapid time to market entrance. Generally, it is an excellent and cost effective addition to PROM programmers of today.

**Figure A**

Figure B

3-12

ROMS 2816 FROMS Fire winner hopposed **AB-4**

August 1981

Users of ROMs for program storage in microprocessor based systems gain the advantage of very dense, very low cost program storage. But how often are these advantages lost when a ROM code is incorrect, or not optimized for a given customers needs? When a software bug is discovered, or an end user wants a slight program modification, ROMs must be discarded to be replaced with modified versions. If many systems undergo such a change, literally thousands of ROM's are wasted. Intel has an excellent solution to ROM modification problems that gives the end user the best of both worlds-low cost and high code flexiblity. The 2816 E<sup>2</sup>PROM, from Intel, used as a front end ROM patch allows bugs to be easily removed, and code changes simply made-without costly throwaway of incorrect Read Only Memories.

The memory systems employing both ROM and  $E^2$ PROM gains benefits of both, through a technique called ROM patching. A ROM patch is essentially a replacement (through a software, or hardware branch) of existing ROM code. When the microprocessor requests data from a ROM that is incorrect, the  $E^2$  patch system recognizes the bad address, disables the ROM and outputs the modified or correct data that is stored in  $E^2$  memory. If a entire section of code is bad, then the  $E^2$  memory is simply "patched in" through subroutine branches. Because the branch routine need only be a relatively small portion of code, the economics of

dense, low cost ROMs can be supplemented with the flexibility of higher cost, less dense  $E^2$ PROMs. The dramatic flexibility of  $E^2$ PROMs is gained at nearly the same low cost as ROM.

$E^2$ PROM is used to advantage because now ROM patched can be made through the CPU's I/O systems. New patch data can be loaded into the  $E^2$  electrically, without having to disassemble the equipment and swap EPROMs or PROMs. To extend the concept even further, these ROM patches can be made from a remote service processor through a data-com or telecom link. No service personnel would be necessary.

The 2816 offers features ideal for such an application. Its access time of 250ns is necessary to allow fast patching without slowing down the CPU. Because only certain bytes of information would change, the capability for individual byte erase is necessary.

A heavy user or ROMs, Tektronix, of Beaverton, Oregon, is now using the ROM patch technique. They currently use EPROMs as the patch medium, but  $E^2$ offers a simple and more optimum use of the technique.

Attached is a reprint of an article written by Tektronix that discusses in great detail the technical implementation and advantages of such a scheme.

# Field-programmable patches simplify firmware maintenance

The need to modify design firmware is virtually inevitable. Of several possible approaches to the job, one can offer higher efficiency and greater ease of use than the rest.

#### Kirk Wimmer, Tektronix Inc

You can use the ROM-modification technique developed in this article to easily and efficiently patch the firmware for your  $\mu C$ -based designs. And the users of those designs can also employ the method—without resorting to a service call. The technique overcomes most of the shortcomings of traditional firmware-modification methods, also discussed here.

The need for firmware modification arises from several sources. Implementation errors (bugs in the code) might be present, for example, or your initial design might exhibit specification errors. More importantly, though, your design will very likely require modification over its lifetime to accommodate expanded features and new options.

Planning for such changes is thus absolutely necessary. But actually changing ROM masks is an unacceptable approach because of its expense, long leadtimes and minimum-order-size requirements. Thus, you need an efficient way of fooling your design's  $\mu$ C into sensing the required firmware changes even though those changes are not actually made in the system's masked ROM. Several methods of performing this task exist.

#### Try a transfer table

One such method, the transfer-table approach, involves dedicating approximately 20% of the ROM's address space to the task of adding a patch PROM's contents. In this PROM, you store a transfer (jump) table that serves as a directory for the ROM's routines. Every time your system's software program calls a routine, it vectors to that routine via the transfer table. To correct a firmware error, therefore, you first write a new routine in the remaining PROM space. Then you alter the transfer table so the system gains access to the new PROM routine rather than the erroneous version in ROM. Because the amount of patch space available determines the scheme's correction capacity, the approach requires that you reserve adequate patch space for several software modules and that you partition the firmware into small modules.

Transfer-table patching has several advantages. It not only works for firmware coded in assembly language, but also applies to firmware written in a high-level language. That is, you needn't be concerned about the details of the microprocessor instructions in the area where the problem exists. Additionally, after you finalize the firmware code and complete all desired modifications, you can replace the patch PROM with a pin-compatible ROM to minimize cost.

The scheme also has two disadvantages, though. First, an error in a particular routine requires—at minimum—replacement of a module from the routine's entry point through the point of the desired change. In some applications, you might need to replace the entire module, rapidly consuming available patch space. Second, the patch PROM must always be part of the system, even if you make no firmware corrections, because the method always employs the transfer table.

#### Vary the transfer-table approach

In another ROM-patching scheme that's similar to the transfer-table approach, you initially group the firmware modules functionally and then distribute them into several small ROMs. Next, you construct a transfer table in RAM from information found in the ROM headers upon power-up. Alternatively, you can use a dedicated, fixed location in each ROM to house the transfer table for its modules. In either case, if a problem exists in one functional area, you need replace only that function's ROM. For that purpose, you can use a pin-compatible PROM until a new masked ROM becomes available. When you install the new device, the transfer table gets updated automatically.

A disadvantage of this approach is that you must provide expansion space in each ROM when locating the firmware modules. Furthermore, if you require more patch space than is available in a particular ROM, you

### Transfer-table scheme reserves address space for a patch PROM

might have to change a second ROM to also utilize its patch space. And obviously, because it uses smaller ROMs, this approach consumes more space and power than the transfer-table scheme.

#### Field-programmable patch solves some problems

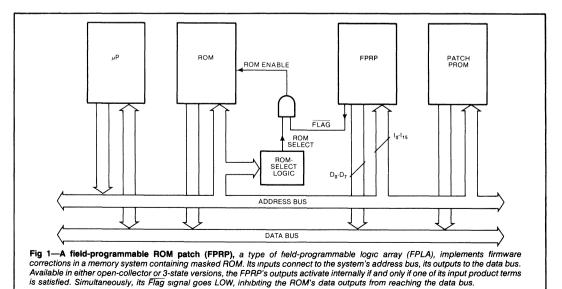

A more hardware-oriented approach to the problem of modifying a masked ROM's contents (Fig 1) utilizes a device termed a field-programmable ROM patch (FPRP). (See EDN, April 5, 1980, pg 88 for more information on these devices.) In this approach, the  $\mu P$ places addresses on the address bus during ROM read cycles, and the FPRP monitors those addresses. If the bus carries an address that the FPRP has been programmed to recognize, the FPRP's Flag output goes LOW, disabling the ROM and preventing it from putting its data on the 8-bit data bus. Instead, the FPRP's data outputs activate and supply the bus with a replacement byte. The µP interprets this byte as having come from the ROM. The strategy thus involves programming the FPRP to recognize addresses where erroneous ROM code exists; the FPRP in turn supplies the data bytes needed to correct the code.

You must often make insertions to existing ROM code without offsetting those insertions with deletions of corresponding size. To solve this problem, you can program the FPRP to substitute a Jump instruction to the address bus; the instruction's destination is a location in the patch PROM. You also write into the patch PROM the code slated for insertion, followed by another Jump instruction, which returns program flow back to ROM. However, because the FPRP has substituted a Jump for several bytes of ROM code, you must also duplicate the displaced bytes in the patch PROM.

You can see that the FPRP approach permits flexible firmware correction both on a byte-for-byte basis and in cases where an entire ROM routine needs modification. Its chief disadvantage is rapid consumption of FPRP capacity, because the FPRP outputs connect directly to the data bus. Furthermore, the approach uses one FPRP product term (with 16 word blocks per product term) for each byte it places on the bus. Consequently, when you need a Jump instruction, one product term serves the Jump opcode and two more serve the high and low address bytes. With only 48 product terms available, this ROM-patching configuration can thus soon become limited.

Another disadvantage of the FPRP method stems from the fact that changes occur in machine code at specific address locations, which are not readily accessible if you write the firmware in a high-level language. And if you require a 16-bit data bus, you need two FPRPs to drive the bus with the higher and lower data bytes.

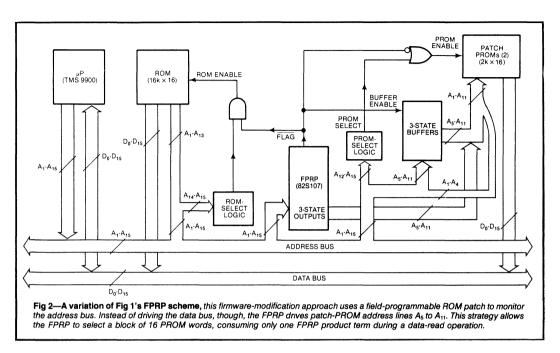

#### An FPRP variation does the job

A variation on the FPRP approach overcomes most disadvantages. It was developed to modify firmware for Tektronix's Model 7854 oscilloscope and uses the FPRP to monitor a 15-bit address bus. But it doesn't connect the FPRP's outputs to the data bus (**Fig 2**). Instead, those outputs drive the seven most significant

address lines ( $A_5$  to  $A_{11}$ ) of two 2716 (2k×8) patch PROMs. The address bus directly drives the four least significant address lines ( $A_1$  to  $A_4$ ) of these PROMs.

This setup allows the FPRP to select a block of 16 words in the PROMs. Thus, unique data gets read while consuming only one FPRP product term. This read process takes advantage of the fact that you can program the FPRP inputs to the Don't Care state.

To employ the technique, you partition the two patch PROMs into two sections. The first contains 768 words (48 product terms  $\times$  16 word blocks per product term), reserved for access only by the FPRP. The second stores the remaining 1280 words, which serve as patch space to hold replacement routines and code sections that in effect get inserted into the ROM. For added storage, you can install two more PROMs and obtain another 2048 words of patch space.

You can alter a single ROM word by programming the FPRP to recognize its address. You store the correct word in the appropriate location in the patch PROM. Several consecutive words might get corrected with only one FPRP product term by programming Don't Cares into the least significant inputs. All addresses affected, however, must fall within the same block of 16 words (ie, addresses  $A_5$  through  $A_{15}$  common to each).

If a particular modification requires code insertion into the stream of instructions already in ROM, you can substitute a Branch instruction for two ROM-code words at the appropriate location. The code overlaid by this instruction and the code to be added can all reside in the patch-PROM area. You can address this area as ordinary memory without FPRP intervention. However, you must follow the added code with an instruction to branch back to ROM.

You can usually implement a 2-word Branchinstruction substitution of this kind with only one FPRP product term. The determining factor is whether or not address bits  $A_5$  through  $A_{15}$  are identical for the two address locations where the branch substitution occurs. In the 7854's firmware, two FPRP product terms always get consumed to correct checksum and header information—a process that leaves 46 product terms available to fix firmware problems. Chances are thus one in 16 that a particular correction requires two product terms rather than one. Therefore, the 7854 implementation of this approach permits 40 or more separate corrections with better than a 93% confidence level.

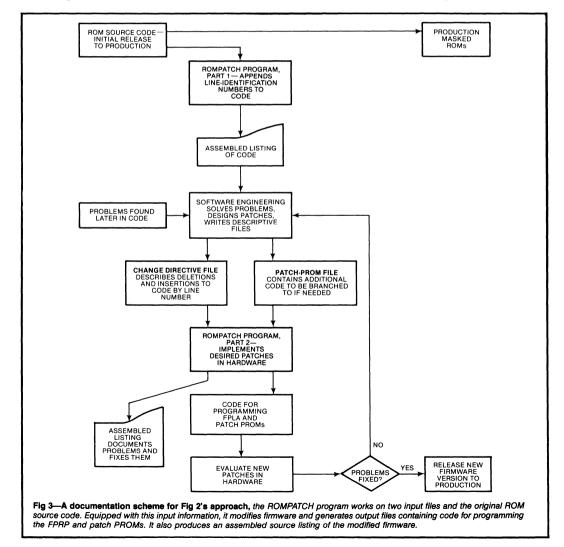

#### An efficient software tool

Once you've recognized the necessity of providing for firmware modification and chosen a particular method, carefully consider the procedures required to actually make the changes. In the 7854's design process, for example, questions arose regarding how to program code into the FPRP and the patch PROMs. Hand coding proved undesirable because of its complexity and high error probability. Instead, an "intelligent" software tool implemented the desired firmware changes in hardware, easily and with minimum error. The tool also

### Using small ROMs for patching consumes space and power

provided for (or encouraged) clear firmware-change documentation, which is important not only for archiving but also for adding feature modifications and, eventually, for making new ROM masks.

This intelligent software tool centers on a computer program, termed ROMPATCH (Fig 3), that permits design and documentation of firmware changes at the source-code level. To structure a program of this type, proceed in several steps.

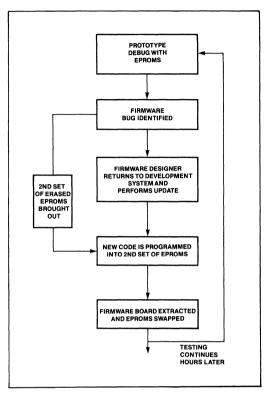

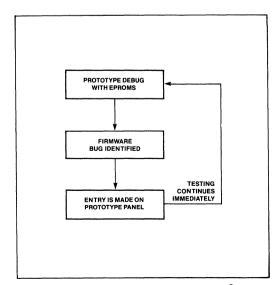

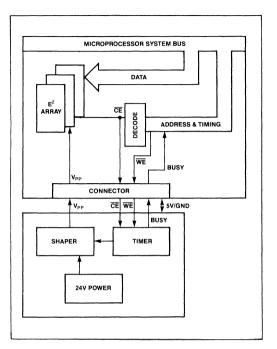

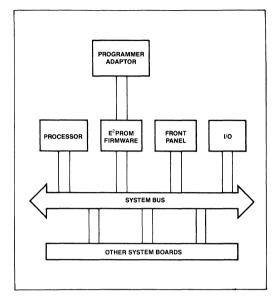

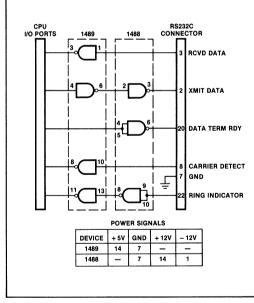

First, assign to each ROM source-code line a unique