The Idealogic Exchange (09-26) Monolithic Memories Inc. 2175 Mission College Blvd. Santa Clara, CA 95054 (408)970-9700

Dear PLEASM User,

PLEASM is the cousin of PALASM, as PROMs are akin to PALs. PALASM and PLEASM constitute MMI's current Programmable logic Support Software. Together, they demonstrate MMI's commitment to providing total support for fusible link logic. By making these tools available, we hope to encourage the design engineer to take advantage of the flexibility offered by semi-custom logic in general, and fusible link technology in particular.

As with PALASM, PLEASM is available for a variety of computers and operating systems. Please check that you have the correct disks or tapes for your particular machine.

By your order, you will have been enrolled in the Idealogic Exchange. To ensure that you will recieve new product announcements and any software updates, please fill out and return the Purchace Registration Card located at the front of this binder. For post-sale service, contact your local MMI representative or Field Applications Engineer or call the Software Services Group at MMI directly.

Be sure to back-up your PLEASM disks/tapes before proceeding any further.

Also, please check the Errata sheet at the back for late changes.

Thank you.

Very truly yours,

The Idealogic Exchange Monolithic Memories Inc.

THE PLEASM MANUAL - FIRST RELEASE

To be used with PLEASM Version 1.2

Date February 15, 1984

Prepared by the Software Services Group

Product Planning and Applications Department

Monolithic Memories, Inc.

(c) 1984 Copyright

All Rights Reserved.

### COPYRIGHT

(C) Copyright 1984 Monolithic Memories, Inc. The copying and distribution of this manual or the PLEASM software is encouraged for the private use of the original purchaser provided this notice is included in all copies. No commercial resale or outside distribution rights are allowed by this notice. This material remains the property of Monolithic Memories Inc. All other rights reserved worldwide by Monolithic Memories Inc., 2175 Mission College Blvd., Santa Clara, CA. 95050.

### TRADEMARKS

The following are registered trademarks of MMI: PAL, HAL, PLE. MMI also has the trademarks: PALASM, PLEASM.

The following are registered trademarks of Digital Equipment Corporation: VAX, VMS, PDP, RSX.

IBM Corporation has the trademarks: IBM PC, PC DOS.

The Osborne PC is a trademark of the Osborne Computer Corporation.

UNIX is a trademark of AT & T.

Intel/MDS is a registered trademark of Intel Corporation.

CP/M is a trademark of Digital Research, Inc.

MS-DOS is a trademark of Microsoft.

SSFORTRAN is a trademark of Supersoft Inc.

### DISCLAIMER

Monolithic Memories Inc. makes no representations or warranties with respect to the contents within and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, Monolithic Memories Inc. reserves the right to revise this publication and the product it describes and to otherwise make changes to the product without obligation of Monolithic Memories Inc. to notify any person or organization of such revision or changes.

# Table of Contents

| Section:        | Title:                                                                                                 |

|-----------------|--------------------------------------------------------------------------------------------------------|

| 0               | Copyright Notices                                                                                      |

| 1               | Introduction                                                                                           |

| 2.1 2.2         | PROMs vs. PLEs The PROM as a Memory Element The PROM as a Programmable Logic Element                   |

| 3<br>3.1<br>3.2 | Equipment needed and set-up functions Load/Go system Development system                                |

| 4               | Running PLEASM - command descriptions                                                                  |

| 5               | PLEASM - An Example                                                                                    |

| 6               | The Syntax of PLEASM                                                                                   |

| APPENDIX        | TITLE                                                                                                  |

| A A.1 A.2       |                                                                                                        |

| В               | PROM/PLE Programmer Information                                                                        |

| С               | PLEASM Error Messages                                                                                  |

| D               | PLE Design File Library                                                                                |

| E               | HELP!! and where to get it                                                                             |

| F               | User Customization                                                                                     |

| G               | Source License Agreement                                                                               |

| Н               | HIGH SPEED BIPOLAR PROMS FIND NEW APPLICATIONS AS PROGRAMMABLE LOGIC ELEMENTS (PLES) : Article Reprint |

<sup>(</sup>c) Copyright Monolithic Memories Inc. 1984 All Rights Reserved.

### Introduction

PLEASM (Programmable Logic Element Assembler) is a software package developed by Monolithic Memories Inc. used for designing with PROM's as Programmable Logic Elements(PLE's). PLEASM is a FORTRAN IV program which assembles and simulates PLE Design Specifications. It also generates programming formats for direct download to PROM programmers and can therefore be regarded as a tool that reduces the design-to-production time considerably.

### **Key Features:**

- Assembles Logic or Arithmetic equations into a PROM truth table.

- Provides INTEL HEX and ASCII HEX programming formats along with the hex check sum.

- Programming formats can be directly downloaded to standard PROM programmers.

- Simulates the Function Table, in the design equations.

- Reports design errors.

The purpose of this manual is to aid the user in running PLEASM and getting to know and understand all its capabilities It begins with an article that describes the wide range of PROM applications and the motivation for developing a software tool to aid in designing these applications. The next section states the system requirements for PLEASM. The next two sections give a detailed account of how to run the program with an explanation of what each of the options accomplish. This is strengthened by an example where all the operations have been performed on an input file that has the PLE specifications for basic logic gates. The PLEASM syntax is described next. This is best understood if this section is read in accompaniment with some of the design examples that come with the PLEASM program. A detailed PLE applications handbook will be available shortly.

The Appendix gives some machine specific information about PLEASM along with details on PROM programmers, the PLE design files supplied as examples, and user customization. An important part of the Appendix is the section on the errors detected by PLEASM. This should be very useful when creating your own PLE designs.

The new PLEASM user should read Sections 3 to 5 initially and then try to run the demonstration examples. Once the user is ready to create his own design, Sections 2 and 6 will provide ideas and details of the specification format. The Appendices serve to provide additional supporting information on a number of subtleties the user should be aware of in fully utilizing the software.

### PROMs vs. PLEs

PROMs have grown steadily in size and speed since their introduction in 1971, when Monolithic Memories introduced the world's first 1K bit bipolar PROM. Today, 16K and 32K PROMs are readily available and their speeds have improved such that the maximum address time (address to output) of these devices is down to 60-70 nanoseconds, over the complete operating temperature and VCC range. This means that PROMs can be used effectively in both high speed memory and logic replacement applications.

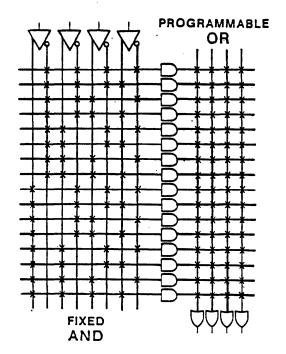

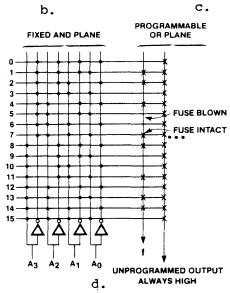

The PROM implements a sum-of products boolean transfer function in which any possible input (address) combination can be transferred to any output variable (data out). Figure 1.1 shows logical structure of a typical PROM. The input Fixed-AND array is a decoder and the output Programmable-OR array is a decoder. It is this decoder area that is field programmable to implement any boolean transfer function.

Each output of the AND array is connected to an input of the OR array by thin metal wire (e.g. nichrome, titanium-tungsten, platinum-silicide) which can be selectively removed from the circuit by passing a current through it. This is referred to as "programming" or "blowing" a "fuse".

# 2.1 The PROM as a Memory Element

Because of their high speeds, bipolar PROMs are ideal for use in systems requiring fast Address-to Data access times. PROM applications can be found in both the data and control paths of a system.

In data paths, PROMs are used mainly as storage elements to implement different table look-up applications such as trigonometric functions, signal processing coefficients, bootstrapping and initialization programs, etc. In particular, the PROM can be used to advantage in the design of digital filters and Fast Fourier Transforms. In character generator applications, the PROM user has the flexibility of modifying the conventional fonts to his/her particular requirements.

In control paths, PROMs are used mainly to store microprograms. Microprogrammed controllers may be simple PROM-register finite state machines or they may be complex microprogrammed CPUs, where the complete instruction set of the system resides in PROM. It is thus possible, by using PROMs for microprogramming, to use the same hardware to emulate the characteristics of various processors.

Since most memory applications involve storing PROM memory data in a temporary register before it is used (pipelining), this has spawned a new generation of PROMs with on-board D-type edgetriggered registers. These registered PROMs operate faster than discrete PROM-register combinations, and the registered PROMs also occupy less space.

|         | A        | • 8 | (   | C •        | D . F4 |          |                |                |    |

|---------|----------|-----|-----|------------|--------|----------|----------------|----------------|----|

|         | <b>A</b> | + 8 | + ( | C +        | 0 - F3 |          |                |                |    |

|         | A        |     | • ( | <b>C</b> • | D • F2 |          |                |                |    |

| UNCTION |          | • 8 | + ( | c •        | D - F1 | F        | F <sub>2</sub> | F <sub>3</sub> | F4 |

| ADDRESS | 40       | Aı  | A2  | <b>A</b> 3 | OUTPUT | 0,       | 02             | 03             | 04 |

|         | +-       | _   |     | !          |        | <u> </u> |                |                |    |

|         | •        | -   |     | 0          |        | 1        |                | 1 1            |    |

| · 1     | 1        | 9   | 0   | 0          |        | 1        |                | 1              |    |

| 2       | 0        | 1 1 | ٥   | 0          |        | 1        |                | 1              |    |

| 3       | 1        | ١   | 0   | 0          |        | 1        |                | 1              | •  |

| 4       | 0        | 0   | 1   | 0          |        |          |                | 1              |    |

| 5       | 1        | 0   | 1   | 0          |        |          |                | ,              | 1  |

| 6       | 0        | 1   | 1   | 0          |        | T        |                | 1              | 1  |

| ,       | 1        | 1   | 1   | 0          |        | 1        |                | ,              |    |

|         | 0        | 0   | 0   | 1 1        |        | 1        |                | 1              |    |

| 9       | ,        | 0   | 0   | 1          |        |          |                | 1              | 1. |

| 10      | .0       | 1   | 0   | 1          |        | 1        | 1              | 1              | 1  |

| 11      | 1        | 1   | 0   | 1          |        | 1        |                | 7 1            | _  |

| 12      | 0        | 0   | ! 1 | _,         |        |          |                | 1              |    |

| 13      | 1        | 0   | 1 1 | 1          |        |          |                | 1              |    |

| 14      | 0        | 1   | 1 1 | 1          |        |          |                | 1              |    |

| 15      | 1        | 1   | 1   | 1          |        |          | 1              | 1              | T  |

Figure 1.1 Typical PROM structure

Figure 1.2 Combinatorial functions available in a 16x4 PROM

# 2.2 The PROM as a Programmable Logic Element.

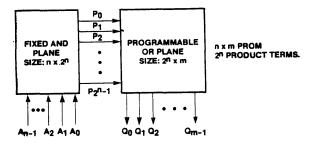

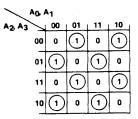

The PROM implements a sum-of-products boolean transfer function so that any function of x inputs and y outputs may be generated in a PROM with x addresses and y data outputs. Figure 1.2 shows the combinational functions available in a 16 X 4 PROM.

The AND-OR structure of the PROM can be viewed as a two-level logic circuit. The fixed AND plane contains all possible input combinations. Each input combination is a product term and it is connected to the output in the OR plane.

In terms of a PLE, a product term is the equivalent of an AND gate equal in size to the number of inputs. Each output is equivalent to an OR gate connected to all the AND gates. Programming a fuse blows this connection between the AND gate and the OR gate. The PROM thus conveniently implements combinatorial logic when a large number of input combinations are required or a large number of product terms per output is desired.

Most applications of PLEs are in synchronous control systems where they replace random logic or customise logic functions. In data paths, they are used to generate complex functions such as pseudo random number generators, ALU operations, multiplications, reciprocals, etc.

# 3.1 Equipment/Set-Up for Load/Go system

PLEASM should run with minimal modifications on the following CPU's provided the minimum system requirements mentioned later in this section are satisfied.

Mainframe Computers

VAX-VMS, VAX-UNIX, or IBM.

Minicomputers

PDP-11/RSX or PDP-11/RT-11

Microcomputers

IBM-PC/MS-DOS or the CP-M system on Radio Shack, Apple, Kaypro or Osborne computers.

Other requirements are:

Removable Media: 5.25'' or 8'' disks, or tape.

Memory : 64K bytes minimum.

One EIA RS232 serial communications port.

PROM programmers suggested:

DATA I/O Model 19 Programmer with Unipak. DATA I/O Model 29 A with Unipak.

DIGELEC Model UP-803 with FAM 12.

KONTRON Model MPP-80S

### 3.2 Equipment/Set-Up for Development system

For software development and user customization of the program, the requirements presented earlier are necessary.

In addition, a FORTRAN compiler/linker and another disk drive are necessary to create the executable version of the program. The compiler recommended is the Supersoft FORTRAN compiler which was used to develop and test the program on microcomputers at Monolithic Memories Inc.

PLEASM is compatible with both FORTRAN IV LEVEL G and FORTRAN 77 standards. Additionally, only standard FORTRAN constructs are used to ensure portability to many computer systems.

# USER'S GUIDE TO PLEASM(tm) - PLE Assembler version 1.2A

To get started with PLEASM, turn the computer ON. Check your directory to make sure you have the files mentioned in Appendix A. Once this has been verified, run the program as explained below with one of the example files. Our suggestion is to start with the file P5000.TXT which contains the PLE Design Specifications for the basic logic gates. Once the capabilities of the program have been understood, you can work with any of the other examples or attempt to create your own designs.

### Using PLEASM:

Type the system's execute command to run the program. PLEASM will respond....

MONOLITHIC MEMORIES PLEASM(tm) VERSION 1.2A (C) COPYRIGHT 1984 MONOLITHIC MEMORIES

WHAT IS THE SOURCE FILENAME (d:filename.ext) ?:P5000.TXT

At this point enter the name of the file containing the specifications for the PLE being designed. If you are using this package for the first time, we suggest you try out one of the design examples that was sent along with PLEASM. PLEASM next prompts you for the name of the file you could have the output sent to, defaulting to the console....

### OUTPUT FILENAME - PRESS <ENTER> FOR NO OUTPUT FILE ?:<CR>

If you press <enter>/<return> the output will be sent to the console after each operation. At this point, the input file is read, and a count of lines and characters in the file is written out to the screen. The next prompt is for the operation you want performed and is....

E=ECHO INPUT S=SIMULATE T=TRUTH TABLE B=BRIEF TABLE

A=HEX TABLE I=INTEL HEX H=ASCII HEX C=CATALOG Q=OUIT

### ENTER OPERATION CODE:C

You can now enter the appropriate operation code, IN UPPER CASE!!.

The various options are briefly discussed below.

E ECHO INPUT - Prints the input PLE specifications file. Useful as a ready reference while working interactively with PLEASM.

S SIMULATE - Exercises the logic values in the optional function table in the logic equations provided. Errors in the function table are detected along with fairly explicit diagnostic messages. An important point to note is that all "don't care" conditions are treated as low logic values. This option can be successfully invoked only when a function table is present in the input specifications.

T TRUTH TABLE - Prints out the entire binary truth table for all the input variables in the PLE by substitutions into the Boolean equations specified. The output has a tabular format for ease of reading. The program also provides a hex checksum for the entries in the truth table at the end.

B BRIEF TABLE - Prints out the truth table only for the used input addresses in the PLE, again by substitutions into the Boolean equations. The output is tabulated as before, this time with a partial hex checksum corresponding to the possibly shorter table.

A HEX TABLE - Prints out the entire truth table as before, except the inputs and outputs are translated into hex. Also generates a tabular format with a hex checksum.

I INTEL HEX - Generates the Intel Hex format for PROM programmers for both 4- and 8-bit data downloading. The format is shown below....

###

: --> Starting colon marker

AA --> Record Length in hex

BBBB --> Record starting address in hex

C..C --> Data

DD --> Hex checksum

Here all data is sent in streams of 16 8-bit bytes starting at 0000H. 4-bit data is padded up with zeros in the most significant four places. The checksum is the negative of the sum of all 8-bit bytes starting at "AA" upto "DD", modulo 256. Transmission is terminated by the string ":00000001FF".

H ASCII HEX SPACE - Generates the ASCII Hex format for PROM programmers for 4- and 8-bit data downloading. The format is shown below....

A --> Record start character (STX)

BB --> Data byte

C --> End of text character (ETX)

Data is sent in streams of 16 8-bit bytes separated by spaces. An execute character, the ASCII period ".", is sent at the end of each stream of data. 4-bit data is padded up with zeros in the most significant 4 places. In addition, a hex checksum is passed at the end of the transmission.

C CATALOG - Prints a one-line description of each option provided by PLEASM. Always displays to the console.

CATALOG OF OPERATION CODES:

MONOLITHIC MEMORIES PLEASM(tm) VERSION 1.2A

PLEASM --PLE ASSEMBLER-- PROVIDES THE FOLLOWING OPTIONS:

C CATALOG - PRINTS THE PLEASM CATALOG OF OPERATIONS

E ECHO INPUT - PRINTS THE PLE DESIGN SPECIFICATIONS

T TRUTH TABLE - PRINTS THE ENTIRE TRUTH TABLE

B BRIEF TABLE - PRINTS ONLY USED ADDRESSES IN THE TRUTH TABLE

A HEX TABLE - PRINTS THE TRUTH TABLE IN HEX FORM

S SIMULATE - EXERCISES THE FUNCTION TABLE IN THE LOGIC EQUATIONS

I INTEL HEX - GENERATES INTEL HEX PROGRAMMING FORMAT

H ASCII HEX - GENERATES ASCII HEX PROGRAMMING FORMAT

Q QUIT - EXITS PLEASM

Q QUIT - Exits the PLEASM program and prompts for restarting with another input specifications file.

ENTER OPERATION CODE: E

( Echoes the input PLE Design Specifications file. This will

( help verify that the input file has been read in correctly.

PLE5P8 P5000 BASIC GATES MMI SANTA CLARA, CALIFORNIA PLE DESIGN SPECIFICATION VINCENT COLI 10/03/82

| 01 = 10  |                      | ; BUFFER             |

|----------|----------------------|----------------------|

| 02 = /10 |                      | ; INVERTER           |

| 03 = 10  | * I1 * I2 * I3       | ; AND GATE           |

| 04 = I0  | + 11 + 12 + 13       | ; OR GATE            |

| 05 = /10 | + /I1 + /I2 + /I3    | ; NAND GATE          |

| 06 = /10 | * /I1 * /I2 * /I3    | ; NOR GATE           |

| 07 = 10  | :+: I1 :+: I2 :+: I3 | ; EXCLUSIVE OR GATE  |

| 08 = 10  | :*: I1 :*: I2 :*: I3 | ; EXCLUSIVE NOR GATE |

### FUNCTION TABLE

10 11 12 13 01 02 03 04 05 06 07 08

| ;INPUT          |         | ruo | PUTS | FROM BASIC GATES |      |     |         |      |                   |

|-----------------|---------|-----|------|------------------|------|-----|---------|------|-------------------|

| ;0123           | BUF     | INV | AND  | OR               | NAND | NOR | XOR     | XNOR | COMMENTS          |

|                 |         |     |      |                  |      |     |         |      |                   |

| LLLL            | L       | H   | L    | L                | H    | H   | ${f L}$ | H    | ALL ZEROS         |

| нннн            | H       | L   | H    | H                | L    | L   | L       | H    | ALL ONES          |

| HLHL            | H       | L   | L    | H                | H    | L   | ${f L}$ | H    | ODD CHECKERBOARD  |

| $\mathtt{LHLH}$ | ${f L}$ | H   | L    | H                | H    | L   | ${f L}$ | H    | EVEN CHECKERBOARD |

|                 |         |     |      |                  |      |     |         |      |                   |

### DESCRIPTION

THIS EXAMPLE ILLUSTRATES THE USE OF PLES TO IMPLEMENT THE BASIC GATES: BUFFER, INVERTER, AND GATE, OR GATE, NAND GATE, NOR GATE, EXCLUSIVE OR GATE, AND EXCLUSIVE NOR GATE.

NOTE ALSO THAT THREE-STATE OUTPUTS ARE PROVIDED WITH ONE ACTIVE LOW OUTPUT ENABLE CONTROL (/E).

# ENTER OPERATION CODE: S ( This option verifies that the output entries in the function Table are correct for the given Boolean equations and input vectors. Any discrepancy between the expected output value as given in the Function Table and the output value as (computed from the Boolean equations is flagged as an error. ( The following are acceptable input entries in the Function (Table: ( H - High level ( L - Low level ( X - Irrelevant

FUNCTION TABLE

10 11 12 13 01 02 03 04 05 06 07 08

| ;INPUT;0123          | BUF              | OUT<br>VNI       | PUTS<br>AND      | FRC<br>OR   | M BAS            | IC G<br>NOR      | ATES<br>XOR | <br>XNOR    | COMMENTS                                                       |

|----------------------|------------------|------------------|------------------|-------------|------------------|------------------|-------------|-------------|----------------------------------------------------------------|

| THTH<br>HPHT<br>TTTT | L<br>H<br>H<br>L | H<br>L<br>L<br>H | L<br>H<br>L<br>L | L<br>H<br>H | H<br>L<br>H<br>H | H<br>L<br>L<br>L | L<br>L<br>L | Н<br>Н<br>Н | ALL ZERCS<br>ALL ONES<br>ODD CHECKERBOARD<br>EVEN CHECKERBOARD |

PASS SIMULATION

# ENTER OPERATION CODE: T

( Generates an exhaustive binary truth table for all the given (inputs by substitution in the Boolean equations.

BASIC GATES

| ADD            | A0          | Al          | A2          | A3          | A4          | 01          | 02          | 03          | 04          | 05          | 06          | 07          | 08          |

|----------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 0<br>1<br>2    | L<br>H<br>L | L<br>L<br>H | L           | L<br>L<br>L | L<br>L<br>L | H           |             | L<br>L<br>L | H           | H<br>H<br>H | H<br>L<br>L | L<br>H<br>H | H<br>L<br>L |

| 29<br>30<br>31 | H<br>L<br>H | L<br>H<br>H | H<br>H<br>H | H<br>H<br>H | н<br>Н<br>Н | H<br>L<br>H | L<br>H<br>L | L<br>L<br>H | H<br>H<br>H | H<br>H<br>L | L<br>L<br>L | H<br>H<br>L | L<br>L<br>H |

HEX CHECK SUM = 00F48

ENTER OPERATION CODE: B

( Prints the truth table for only the used input and output

BASIC GATES

| ADD            |   | A0          | A1          | A2          | A3          | 01          | 02          | 03          | 04          | 05          | 06          | 07          | 08          |

|----------------|---|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 0 1 2          | • | L<br>H<br>L | L<br>L<br>H | L<br>L<br>L | L<br>L<br>L | L<br>H<br>L | H<br>L<br>H | L<br>L<br>L | L<br>H<br>H | H<br>H<br>H | H<br>L<br>L | L.<br>H     | H<br>L<br>L |

| 13<br>14<br>15 | • | H<br>L<br>H | L<br>H<br>H | H<br>H<br>H | н<br>Н<br>Н | H<br>L<br>H | L<br>H<br>L | L<br>L<br>H | H<br>H<br>H | H<br>H<br>L | L<br>L<br>L | H<br>H<br>L | L<br>L<br>H |

PARTIAL HEX CHECK SUM = 007A4

ENTER OPERATION CODE: A

( Generates the truth table with input and output vectors ( translated into hex.

BASIC GATES

| ADD | HEX ADDRESS | HEX DATA |

|-----|-------------|----------|

| 0   | 000         | 00B2     |

| 1   | 001         | 0059     |

| 2   | . 002       | 005A     |

| 29  | 01D         | 0059     |

| 30  | 01E         | 005A     |

| 31  | 01F         | 008D     |

HEX CHECK SUM = 00F48

ENTER OPERATION CODE: I

( Generates the Intel Hex programming format for downloading ( to a PROM programmer.

:10000000B2595A995A999A595A999A599A595A8D4C :10001000B2595A995A999A595A999A599A595A8D3C :00000001FF

ENTER OPERATION CODE: H

( Generates the ASCII Hex Space programming format for ( downloading to a PROM programmer, with the required <STX>, ( <SOH>, and <ETX> control characters delimiting the ( transmission.

^B^A

B2 59 5A 99 5A 99 9A 59 5A 99 9A 59 9A 59 5A 8D .

B2 59 5A 99 5A 99 9A 59 5A 99 9A 59 9A 59 5A 8D .

C 00F48

ENTER OPERATION CODE: Q

( Exits PLEASM and prompts for restarting with another input ( file.

RESTART PLEASM(Y/N) ?:

### PLE Design Specification:

The PLE Design Specification is the input file used with PLEASM. It is also the recommended data sheet format for describing the function of a PROM, once it has acquired the unique personality of a particular fuse pattern. This format for creating an input specifications file can be best understood by studying the examples that come along with this package. The format for the PLE Design Specification is:

- Line 1 PLE part number, starting in column 1, followed by the words <u>PLE DESIGN SPECIFICATION</u>.

- Line 2 User's part number followed by the designer's name and the date, starting in column 1. This may be an identifier that defines the application and is used for reference.

- Line 3 Device Application name, starting in column 1.

- Line 4 User's company name and address, starting in column 1.

Lines 2-4 are without formal rules and are provided for documentation purposes.

- Line 5 Address pin list, prefixed by <u>ADD</u>, starting in column 1. The pin list should be ordered LSB first.

- Line 6 Data pin list, prefixed by <u>.DAT</u>, starting in column 1. The pin list should be ordered LSB first.

The pin list is a sequence of symbolic names separated by one or more spaces on one or more lines in the order of the device pin numbers. Each symbolic name is unique (except the unused pins which may have the same name). All pins including power and ground must be named. Names may use any printable characters except the operators ';', '.', ',', '=', '\*', and '+'. The prefix '/' is used to logically complement the name.

# Line m EQUATIONS

The transfer function of the device is expressed in the following form :

SYMBOL = EXPRESSION

The following terms are used to construct the equations:

SYMBOL Pin Name with optional prefix '/'

EXPRESSION A sequence of SYMBOLS separated by operators.

### OPERATORS (in hierarchy of evaluation)

- ; Comment follows

- Dot operator ( pin list or arithmetic operator follows)

- ADD Address pins (Inputs)

- DAT Data Pins (Outputs)

- , Delimiter, separates binary bits (MSB first)

- = Equality (combinatorial)

### **BOOLEAN OPERATORS**

- / Complement, prefix to a pin name

- \* AND (PRODUCT)

- + OR (SUM)

- :+: XOR (EXCLUSIVE OR)

- :\*: XNOR (EXCLUSIVE NOR)

### ARITHMETIC OPERATORS

- .\*. Multiply (Arithmetic multiplication)

- .+. PLUS (Arithmetic addition)

### Line n FUNCTION TABLE

The function table begins with the key word <u>FUNCTION</u> TABLE, starting in column 1 of a line following the equation list. It is followed by a pin list which may be in a different order and polarity from the pin list in Lines 5 and 6. The pin list is followed by a line of dashes (-'s) which is in turn followed by a list of vectors, one vector per line. One state must be specified for each pin name and optionally separated by spaces.

A vector is a sequence of states listed in the same order as the pin list and followed by an optional comment. The vector list is followed by another dashed line.

An important restriction is that blank lines are not permitted in the body of the function table. To separate logically distinct parts of the function table, however, comments can be used. In other words, blank lines are permitted with a semicolon (;) in the first column. Additionally, comments can be placed in this line. Extra blank lines might result in the simulator scanning past the end of the function table and detect "-" as an error symbol, resulting in failure to pass simulation.

A function table is optional and need be present only for simulation to be performed. The keyword <u>FUNCTION TABLE</u>, however, is necessary in the input file. This should start in column 1, and should follow the equation list.

Definition of Function Table States:

| Symbol | Definition | Input                | Output      |

|--------|------------|----------------------|-------------|

| H      | HIGH LEVEL | Drive High           | Test High   |

| L      | LOW LEVEL  | Drive Low            | Test Low    |

| X      | IRRELEVANT | Don't Care Condition | Do Not Test |

# Line o DESCRIPTION (optional)

This begins with the keyword <u>DESCRIPTION</u>, starting in column 1. The device operation and application are described here. All the lines following the keyword <u>DESCRIPTION</u> are treated as comments. Even though the lines following may be blank, the keyword <u>DESCRIPTION</u> is necessary in the input file for assembly.

An informal grammar for the input specifications file is given below:

PLE\_SPECIFICATIONS\_FILE --> PLE\_TYPE\_LINE

PLE\_PATTERN\_LINE

APPLICATION\_DESCRIPTION\_LINE

COMPANY\_INFORMATION\_LINE

ADDRESS\_PIN\_LIST

DATA\_PIN\_LIST

EQUATION\_LIST

FUNCTION\_TABLE

[FUNCTION\_TABLE\_PIN\_LIST]

[FUNCTION\_TABLE]

DESCRIPTION

[COMMENTS]

PLE\_TYPE\_LINE --> PLE<PLE PART NUMBER> ... PLE DESIGN SPECIFICATIONS

PLE\_PATTERN\_LINE --> <REFERENCE NUMBER FOR APPLICATION, AUTHOR'S NAME>

APPLICATION\_DESCRIPTION\_LINE --> <APPLICATION NAME>

COMPANY\_INFORMATION\_LINE --> < COMPANY NAME AND ADDRESS>

ADDRESS\_PIN\_LIST --> .ADD <PIN NAME LIST FOR INPUT PINS>

DATA\_PIN\_LIST --> .DAT <PIN NAME LIST FOR OUTPUT PINS>

EQUATION\_LIST --> <LIST OF BOOLEAN EQUATIONS>

FUNCTION\_TABLE\_PIN\_LIST --> <LIST OF PINS TO BE SIMULATED>

FUNCTION\_TABLE --> H|L|X <ENTRIES DEFINING LOGIC VALUES FOR THE PINS>

COMMENTS --> < COMMENTS DESCRIBING APPLICATION>

where, [..] denotes an optional expression,

<..> denotes an informal representation for the expression,

'\_\_\_' denotes a keyword,

and ' | ' denotes the "OR" operator.

# Important notes on PLEASM input specifications:

- 1. The specifications file must contain the keywords FUNCTION TABLE and DESCRIPTION starting in column 1 for assembly to occur.

- 2. All responses to PLEASM prompts should be in upper case.

- 3. The input specifications file should preferably be entirely in upper case.

- 4. The number of characters in the file, the number of lines in the file, and the number of characters in each line should be within the limits set in the I/O initialization package. The current limits set are 6000 chars/file, 250 lines/file, and 80 chars/line.

# A.1 PLEASM on the VAX11/VMS

The following files should be in your tape if you have the Load/Go System:

PLEASM.EXE - This is the executable file that can be invoked to assemble your input PLE specifications.

P5000.TXT through P5017.TXT - These are the example files containing some applications. They are useful for studying how the input file should be written, and can be run with PLEASM to provide an on-line demonstration of how the program works. Details on the contents of these files can be found in Appendix D.

If you have ordered the Development system, you should have in addition the files:

PLEASM.FOR - This file contains the FORTRAN source for the PLEASM program and can be compiled by any FORTRAN compiler you have at your disposal.

IOLIB.FOR - This file contains the I/O features that make this version of PLEASM compatible with that on the IBM-PC. This will have to be linked in with the main program during compilation.

# Unloading Your Mag Tape under VAX/VMS

# Helpful Hints:

- The volume is labelled PLEASM and is recorded in Files-11 format, 1600 BPI and 9-track mag tape.

- For the neophytes who wish to learn everything there is to learn about mag tapes and more, Digital Equipment Corporation has published The Magnetic Tape Users' Guide (Order No. AA-M539A-TE).

- Your tape drive goes by many different names. For example, MTAO: or MSAO:. To list all devices on your installation, type SH DEV M<cr> when you see the \$ prompt.

After loading your tape on the drive, when you see the \$ prompt, type the following:

# \$ ALL MTAO: TAPE

( Allocates space for TAPE on device MTAO:

# \$MOUNT/OVER=IDENT TAPE

- ( This mounts the tape and overrides any tape labels. Operator ( privileges are sometimes required to do this.

- (c) Copyright Monolithic Memories Inc. 1984 All Rights Reserved.

\$CREATE/DIR [.PLEASM] \$SET DEFAULT [.PLEASM]

( Sets up the directory appropriately.

\$COPY TAPE: \*.\*; \* [] \*

( This copies the tape files to your directory.

\$DISMOUNT TAPE

( Dismounts tape and wraps things up.

DISREGARD THIS MARKED SECTION IF YOU HAVE THE LOAD/GO SYSTEM !!

Compile and link the source program using the following sequence of commands, to create the executable version:

- \$ FORTRAN PLEASM, IOLIB

- \$ LINK PLEASM, IOLIB

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

Using PLEASM:

Create your PLE Design Specification file using one of your system's editors.

Then type the following:

### \$ RUN PLEASM

The program PLEASM should now run. At this point, refer to Section 4. for step-by-step instructions on how to use the program.

Dumping a File From the VAX(VMS) to the Data I/O:

Cable Connections: '

The RS-232C cable that connects the VAX-11 to the Data I/O has lines 2 and 3 reversed. The only other pins that must be connected are pins 1 and 7.

Operating Procedures:

- 1. Turn Data I/O power off.

- Connect the Data I/O programmer to the modem and VT100 terminal as shown in Fig. A.1-1.

- 3. Turn the Data I/O programmer on.

- 4. Press the "SELECT" (Data I/O).

- (c) Copyright Monolithic Memories Inc. 1984 All Rights Reserved.

- 5. Enter "EB" (Data I/O)

- 6. Press the "START" (Data I/O).

- 7. Type "TY FILENAME.DAT" (VT100).

- 8. Press "RETURN" on the VT100.

- 9. Disconnect VT-100 terminal from the modem and Data I/O.

- 10. Reconnect Data I/O to VT-100 as shown in Fig. A.1-2.

- 11. Press the "SELECT" (Data I/O).

- 12. Press the "SELECT" (Data I/O).

- 13. Enter "El" (Data I/O).

- 14. Press "START" (Data I/O).

- 15. Use VT-100 keyboard in order to communicate with the Data I/O.

|                 | PROGRAMME | R | MODI    | EM   | VT100 |                   |  |  |

|-----------------|-----------|---|---------|------|-------|-------------------|--|--|

|                 | !         | 1 | I       | !    | !     | <b>!</b> ,        |  |  |

| PROTECTIVE GND. | ! 1 0     | ! | 1 0 1 0 |      | ! 0 1 | ! PROTECTIVE GND. |  |  |

| SEND DATA       | ! 2 0     | ! | 0 2 0   |      | 0 2   | ! SEND DATA       |  |  |

| RECEIVE DATA    | ! 3 0     | İ | 0 3 0   |      | 0 3   | RECEIVE DATA      |  |  |

| RTS             | ! 4 0     | ! | 0 4 0   | <br> | 0 4   | :<br>!            |  |  |

| CTS             | 1 5 0     | ! | 0 5 0   |      | . 0 5 | :<br>[<br>]       |  |  |

| DSR             | 1 6 0     | ! | 0 6 0   |      | 0 6   | <u>.</u><br>!     |  |  |

| SIGNAL GND.     | ! 7 0     | 1 | 1 0 7 0 |      | ! 0 7 | !! SIGNAL GND.    |  |  |

|                 | •         | • | •       | •    | •     | •                 |  |  |

Fig. A.1-1: Downloading from host (VAX-11) to Programmer. (VAX talking to Programmer and VT100).

| P               | VT100      |                           |               |                 |

|-----------------|------------|---------------------------|---------------|-----------------|

| PROTECTIVE GND. | !<br>! 1 C | !                         | !!<br>! 0 1 ! | PROTECTIVE GND. |

| PROTECTIVE GND. | : 1 0<br>! | 1                         | !!            | PROTECTIVE GND. |

| SEND DATA       | ! 2 0      | !!                        | 0 2 !         | SEND DATA       |

| RECEIVE DATA    | 1 3 0      | !<br>!                    | 0 3           | RECEIVE DATA    |

| RTS             | . 4 O      | !<br>[                    | 0 4           |                 |

| CTS             | . 5 O      | !<br>[                    | 0 5 !         |                 |

| DSR             | 1 6 0      | !<br>[                    | 0 6           |                 |

| SIGNAL GND.     | 1 7 0      | :<br>[]                   | 0 7           | SIGNAL GND.     |

| Fig.            | A.1-2:     | using Programmer as host. | •             |                 |

<sup>(</sup>c) Copyright Monolithic Memories Inc. 1984 All Rights Reserved.

Please note that for the IBM PC, system requirements are as follows:

- 8088 based microprocessor system

- 64K bytes minimum of memory

- MS-DOS (PC-DOS) operating system

- Optional text printer

- 1 disk drive.

The IBM PC version comes with a diskette which contains the following files:

Disk #1: PLEASM.EXE ( if the Load/Go system has been ordered)

PLEASM.FOR ( if the Development system was ordered )

P5000.TXT - P5017.TXT

PALCOM.EXE & PALSETUP.EXE

PLEASM.EXE is the executable version of PLEASM.

PLEASM.FOR is the FORTRAN source for the program.

P5000.TXT - P5017.TXT contain the example applications.

PALCOM.EXE is the program used for downloading.

PALSETUP.EXE allows the user to specify communications protocol

DISREGARD THIS MARKED SECTION IF YOU HAVE THE LOAD/GO SYSTEM !!

To create the executable version for the source program you have to compile and link the source file using any FORTRAN compiler/linker you have at your disposal. The one recommended is the Supersoft FORTRAN compiler which was used during the development and testing of this program. For this compiler the sequence of commands to create the executable file would be (with the compiler/linker in drive B: and the source in drive A:):

- A> B:SFOR PLEASM.FOR PLEASM.REL

- A> B:CNV PLEASM.REL PLEASM.OBJ/R

- A> B:LINK S+SEMU+@PLEASM.RSP,PLEASM,NUL,SFLIB+MLIB,,

This creates the executable file PLEASM.EXE.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

<sup>(</sup>c) Copyright Monolithic Memories Inc. 1984 All Rights Reserved.

To use PLEASM on the IBM PC, two steps are necessary:

- 1. Create and edit the PLE Specification File.

- 2. Run PLEASM.

To run PLEASM with Disk #1 in drive A, type the following when you see the A> prompt:

### A>PLEASM

At this point, PLEASM begins running. For step-by-step instructions on how to use the program, please refer to Section 4.

# General:

- 1. Do NOT terminate the program abnormally by pressing CTRL-C, CTRL-BREAK, etc. when you are sending the output to a file rather that the screen. Use instead the QUIT option to terminate your session. If the session is terminated using CTRL-C, this may result in lost files on your disk. This is because your output file will not have been properly closed.

- 2. The approximate run-times for the programs vary depending on the size of the PLE and the length of the input specifications file. Simulation takes between 1 and 3 minutes, while generating programming formats could take anywhere between 3 and 10 minutes.

# PROGRAMMER VENDOR LIST

Following is a list of MMI approved programmer vendors. Although the list below is mostly for the San Francisco Bay Area offices, you should be able to obtain information about their regional sales offices by calling the telephone numbers listed.

| 1. | Data I/O<br>473 Sapena Court/Suite 4<br>Santa Clara, CA 95050          | (408)727-0641  |

|----|------------------------------------------------------------------------|----------------|

| 2. | Structured Design<br>1700 Wyatt Drive/Suite 3<br>Santa Clara, CA 95054 | (408) 988-0725 |

| 3. | Kontron<br>630 Price Avenue<br>Redwood City, CA 94063                  | (415)361-1012  |

| 4. | Stag<br>528-5 Weddell<br>Sunnyvale, CA 94029                           | (408)745-1991  |

| 5. | Digelec<br>7335 E. Acoma Drive/Suite 103<br>Scottsdale, AZ 85260       | (602)991-7268  |

| 6. | Storey Systems<br>3213 N. Hwy 67/Suite 103<br>Mesquite, TX 75150       | (214)270-4135  |

| 7. | Varix<br>122 Spanish Village #608<br>Dallas, TX 75248                  | (214)620-0925  |

| 8. | Citel<br>3060 Raymond Street<br>Santa Clara, CA 95050                  | (408)727-6562  |

## PROM/PLE Programmer Information:

# DATA I/O Model 19 Programmer with UniPak:

# Key Features:

- Accepts PLE HEX programming format.

- Allows user limited communication via RS232 interface to computer development system.

# Using the DATA I/O Model 19 with UniPak:

# RS232 Serial Interface:

Prior to powering up the DATA I/O it is important that the RS232 interface be connected to the host computer correctly. The correct interface is described below:

| Model 19 |   |   | L9 Termin | Terminal |      | le: | 1 ] | .9 Terminal |

|----------|---|---|-----------|----------|------|-----|-----|-------------|

|          |   |   |           |          |      |     |     |             |

| Gnd      | 1 | 1 | !! 1 !    | Gnd      | Gnd  | !   | 1   | !! 1 ! Gnd  |

|          |   |   | !1(2)!    |          |      |     |     | !!(2)! Rec  |

| Rec      | ! | 3 | !1(3)!    | Send     | Rec  | Ī   | 3   | !!(3)! Send |

| RSend    | ! | 4 | 1! (4) !  | CSend    | SGnd | 1   | 7   | !! 7 ! SGnd |

| CSend    | Ţ | 5 | !!(5)!    | RSend    |      |     |     |             |

| SGnd     | ! | 7 | 11 7 1    | SGnd     |      |     |     |             |

|          |   |   |           |          |      |     |     |             |

With Handshake

Without Handshake

Turn on the DATA I/O programmer. After it finishes its self check routine, type the following key sequence on the DATA I/O keyboard:

<LOAD> - Select device type

<SELECT>

Prepares DATA I/O to receive data via RS232 <D1> <START> interface port

The DATA I/O Model 19 is now ready to accept data from the computer development system. After the file is entered, the data may be reviewed on the terminal by typing the following on the DATA I/O:

> <KEYBOARD> <ENTER> Sends data to remote terminal

For additional information please refer to the DATA I/O Model 19 users manual.

# DATA I/O Model 29A with UniPak:

# **Key Features:**

- Accepts PLE HEX programming format.

- Allows interactive communication via RS232 interface to computer development system.

# Using the DATA I/O Model 29A with UniPak:

# RS232 Serial Interface:

Prior to powering up the DATA I/O it is important that the RS232 interface be connected to the host computer correctly. The correct interface is described below:

| Mode                                                         | 21 | 29 | A Termin | nal   | Mode | 21 | 29 | A Terminal               |

|--------------------------------------------------------------|----|----|----------|-------|------|----|----|--------------------------|

|                                                              |    |    |          |       |      |    |    | tem tip tip tem tip      |

| Gnd                                                          | 1  | 1  | !! 1 !   | Gnd   | Gnd  | Ţ  | 1  | !! 1 ! Gnd               |

| Send                                                         | !  | 2  | 1!(2)!   | Rec   | Send | 1  | 2  | !!(2)! Rec               |

| Rec                                                          | !  | 3  | 1!(3)!   | Send  | Rec  | !  | 3  | !!(3)! Send              |

| RSend                                                        | !  | 4  | !!(4)!   | CSend | SGnd | !  | 7  | !! 7 ! SGnd              |

| CSend                                                        | !  | 5  | !!(5)!   | RSend |      |    |    | Open Open Open Open Open |

| SGnd                                                         | !  | 7  | 11 7 1   | SGnd  |      |    |    |                          |

| Office State State State State State State State State State |    |    |          |       |      |    |    |                          |

|                                                              |    |    |          |       |      |    | _  |                          |

With Handshake

Without Handshake

Turn on the DATA I/O programmer. After it finishes its self check routine, type the following key sequence on the DATA I/O keyboard:

<COPY> <DEVICE> <RAM> <FFCC> - Enter family and pin code

<SELECT> <F7> - Configure for HEX input format

The DATA I/O Model 29A is now ready to accept data from the computer development system. After the file is entered, the data may be reviewed on the terminal by typing the following on the DATA I/O:

Interactive communication may be achieved by typing on the DATA I/O:

For additional information please refer to the DATA I/O Model 29A users manual.

### DIGELEC Model UP-803 with FAM 12:

### **Key Features:**

- Accepts PLE HEX programming format.

- Allows limited communication via RS232 interface to computer development system.

# Using the DIGELEC Model UP-803 with FAM 12:

### RS232 Serial Interface:

Prior to powering up the DIGELEC it is important that the RS232 interface be connected to the host computer correctly. The correct interface is described below:

| Model UP | -803 | Terminal    |                      |

|----------|------|-------------|----------------------|

|          |      |             |                      |

| Gnd !    | 1 !  | -! 1 ! Gnd  | Insure that the lab  |

|          |      | -!(2)! RXD  | switch is set, the   |

|          |      | -!(3)! TXD  | serial communication |

|          |      | -!(4)! CTS  | switch setting is    |

| CTS !    | 5 !  | -!(5)! RTS  | used, matching baud  |

| DSR !    | 6 !  | -!(6)! DTR  | rates are used, and  |

| SGnd !   | 7 !  | -! 7 ! SGnd | ASCII HEX format is  |

| DTR !    | 20 ! | -!20 !DSR   | specified.           |

|          |      |             |                      |

Turn on the DIGELEC programmer. Prepare the DATA TRANSFER function of the UP-803 as follows:

SOURCE : SERIAL INPUT

DESTINATION : RAM

DESTINATION INITIAL ADDRESS: XXXX

BLOCK LENGTH : YYYY ( FFFF if unknown )

Press the <EXECUTE> key on the UP-803.

The DIGELEC Model UP-803 is now ready to accept data from the computer development system. After the file is entered, the data may be reviewed on the remote terminal by selecting the following on the DIGELEC:

SOURCE : RAM

DESTINATION : SERIAL OUTPUT

Press the <EXECUTE> key on the UP-803.

For additional information on the use of the DIGELEC Model UP-803 please refer to the users manual.

### KONTRON Model MPP-80S

### **Key Features:**

- Accepts PLE Intel HEX programming format.

- Allows limited communication via RS232 interface to computer development system.

# Using the KONTRON Model MPP-80S:

### RS232 Serial Interface:

Prior to powering up the KONTRON it is important that the RS232 interface be connected to the host computer correctly. The correct interface is described below:

| Model MPP-80S Terminal |                          |

|------------------------|--------------------------|

|                        |                          |

| Gnd ! 1 !! 1 ! Gnd     | The baud rate, parity,   |

| TXD ! 2 !!(2)! RXD     | and number of start/stop |

| RXD ! 3 !!(3)! TXD     | bits should be the same  |

| SGnd ! 7 !! 7 ! SGnd   |                          |

|                        | terminal.                |

Turn on the KONTRON programmer. Prepare the DATA TRANSFER function of the MPP-80S by performing the following:

- Select proper device type

- Press the white <IN> key (Select input port)

- Press the grey <A> key (Select port A)

- Enter <40> for Intel HEX format

- Press the grey <ENTER> key

The KONTRON Model MPP-80S is now ready to accept data from the computer development system. After the file is entered, the data may be reviewed on the remote terminal by selecting the following on the KONTRON:

- Press the white <OUT> key (Select output port)

- Press the grey <A> key (Select port A)

- Enter output format desired

- Press the grey <ENTER> key

For additional information on the use of the KONTRON model MPP-80S please refer to the users manual.

### PLEASM Error messages:

PLEASM detects and reports the following errors encountered while running the program. These include incorrect file naming, syntax errors in the input specifications file, and errors in simulation.

1. Non-existent filename specified in response to the query for the name of the source file.

DISK I/O ERROR - MAYBE WRONG FILENAME ???

2. Open file named in response to query for the name of the output file.

DISK I/O ERROR - MAYBE WRONG FILENAME ???

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

3. Input file size in number of characters exceeds the maximum dimensions specified in the initialization subroutine. See Appendix I for details.

TOO MANY CHARACTERS IN INPUT FILE

This will probably lead to a run-time error with an output message appropriate to your system.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

- 4. Keyword <u>FUNCTION TABLE</u> missing in input specifications.

- \*\*\* KEYWORD "FUNCTION TABLE" MISSING. ASSEMBLY TERMINATED

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

- Keyword <u>DESCRIPTION</u> missing in input specifications.

- \*\*\* KEYWORD "DESCRIPTION" MISSING. ASSEMBLY TERMINATED

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

6. Invalid PLE name in line 1 of the input specifications.

PLE PART TYPE PLE\$\$\$\$ IS INCORRECT

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

| 7. Number of pin names specified in the address list exceeds<br>the number of input pins available in the PLE being used.                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *** TOO MANY PIN NAMES IN INPUT PIN LIST ***                                                                                                                 |

| ****************                                                                                                                                             |

| 8. Number of pin names specified in the data list exceeds the number of output pins available in the PLE being used.                                         |

| *** TOO MANY PIN NAMES IN OUTPUT PIN LIST ***                                                                                                                |

| ******************                                                                                                                                           |

| 9. A pin name specified in the equations or in the function<br>table pin list does not match any of the names declared in the<br>address and data pin lists. |

| ERROR SYMBOL = \$\$\$\$\$\$\$                                                                                                                                |

| *****************                                                                                                                                            |

| 10. The "SIMULATE" option has been invoked without a function table being present in the input specifications.                                               |

| FUNCTION TABLE MUST BE SUPPLIED IN ORDER TO PERFORM SIMULATION                                                                                               |

| **************                                                                                                                                               |

| 11. The number of pin names in the function table pin list exceeds the number of pins being used in the PLE.                                                 |

| *** TOO MANY PIN NAMES IN FUNCTION TABLE PIN LIST ***                                                                                                        |

| *************                                                                                                                                                |

| 12. A symbol other than H(high), L(low), or X(don't care) has been entered in the function table.                                                            |

| ERROR SYMBOL **\$** IN LINE \$\$\$ OF FUNCTION TABLE                                                                                                         |

| **************                                                                                                                                               |

| 13. Simulation error caused by an entry in the function table (expected) not agreeing with that evaluated from the Boolean equations (actual).               |

| FUNCTION TABLE ERROR IN LINE \$\$\$ PIN = \$\$\$\$\$\$\$ EXPECTED \$ ACTUAL \$                                                                               |

| The offending line in the function table is then printed out with a question mark in place of the incorrect entry.                                           |

| ***************                                                                                                                                              |

| (c) Copyright Monolithic Memories Inc. 1984 All Rights Reserved.                                                                                             |

14. Overall count of function table errors if there are one or more simulation errors.

ERRORS IN FUNCTION TABLE = \$\$\$\$

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

15. PLEASM could not generate HEX programming formats for the PLE being used.

PLEASM DOES NOT SUPPLY HEX PROGRAMMING FORMAT FOR \$\$\$\$ BY \$\$ PLE'S

# PLE DESIGN LIBRARY

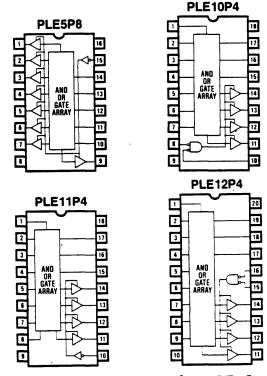

| PAT # | TITLE                                          | PLE TYPE |

|-------|------------------------------------------------|----------|

| P5000 | BASIC GATES                                    | PLE5P8   |

| P5001 | MEMORY ADDRESS DECODER                         | PLE8P8   |

| P5002 | 6-BIT TRUE/INVERT AND CLEAR/SET LOGIC FUNCTION | PLE8P8   |

| P5003 | EXPANDABLE 3-TO-8 DEMULTIPLEXER                | PLE5P8   |

| P5004 | DUAL 2:1 MULTIPLEXER                           | PLE10P4  |

| F5005 | QUAD 2:1 MULTIPLEXER                           | PLE10P4  |

| F5006 | HEXADECIMAL TO SEVEN SEGMENT DECODER           | PLE5P8   |

| P5007 | 5-BIT BINARY TO BCD CONVERTER                  | PLE5P8   |

| F5008 | 4-BIT BCD TO GRAY CODE CONVERTER               | PLE5P8   |

| F5009 | 4-BIT GRAY CODE TO BCD CONVERTER               | PLE5P8   |

| F5010 | 8-BIT PRIORITY ENCODER                         | PLE8P4   |

| F5011 | 4-BIT MAGNITUDE COMPARATOR                     | PLE8P4   |

| P5012 | 6-BIT MAGNITUDE COMPARATOR                     | PLE12P4  |

| F5013 | 4-BIT MULTIPLIER                               | PLE8P8   |

| P5014 | PARTIAL PRODUCTS ADDER                         | PLE10P4  |

| P5015 | PARTIAL PRODUCTS ADDER                         | PLE8P4   |

| F5016 | PARTIAL PRODUCTS ADDER                         | PLE12P8  |

| F5017 | PARTIAL PRODUCTS ADDER                         | PLE12P8  |

|       | · · · · · · · · · · · · · · · · · · ·          | · · ·    |

### P5000.TXT

THIS EXAMPLE ILLUSTRATES THE USE OF PLES TO IMPLEMENT THE BASIC GATES: BUFFER, INVERTER, AND GATE, OR GATE, NAND GATE, NOR GATE, EXCLUSIVE OR GATE, AND EXCLUSIVE NOR GATE.

NOTE ALSO THAT THREE-STATE OUTPUTS ARE PROVIDED WITH ONE ACTIVE LOW OUTPUT ENABLE CONTROL (/E).

PLEASM GENERATES THE PROM TRUTH TABLE FROM THE LOGIC EQUATIONS AND SIMULATES THE FUNCTION TABLE IN THE LOGIC EQUATIONS.

### P5001.TXT

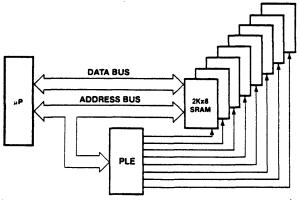

THIS PLEAPE PROVIDES A SINGLE CHIP ADDRESS DECODER FOR USE WITH MANY POPULAR 8-BIT MICROPROCESSORS SUCH AS THE Z80 AND 8080. FIVE MSB ADDRESS LINES (All-Al5) AND THE MEMORY REQUEST LINE (/MREQ) FROM THE Z80 MICROPROCESSOR ARE DECODED TO PRODUCE EIGHT ACTIVE LOW CHIP ENABLES (/CE1-/CE8) TO SELECT A RANGE OF 2K BYTES FROM A BANK OF EIGHT 2Kx8 STATIC RAMS. THIS BANK OF STATIC RAMS WILL OCCUPY THE LOWEST 16K BYTES OF ADDRESS SPACE LEAVING THE UPPER 48K BYTE SPACE AVAILABLE FOR OTHER MEMORIES AND I/O. THE PLE8P8 HAS THREE ADDITIONAL INPUTS WHICH CAN BE RESERVED FOR FUTURE SYSTEM EXPANSION.

# P5002.TXT

THIS PLEAP IS A 6-BIT TRUE/COMPLEMENT AND CLEAR/SET LOGIC THE CONTROL LINES (I1 AND I2) SELECT ONE OF FOUR FUNCTIONS. LOGIC FUNCTIONS FOR THE 6-BIT INPUT DATA (D1-D6) AND THE 6-BIT OUTPUT FUNCTION (Y1-Y6). WHEN II IS FALSE (II=LOW) THE FUNCTION IS INVERT IF 12 IS FALSE (12=LOW) OR TRUE IF 12 IS TRUE (12=HIGH). WHEN II IS TRUE (11=HIGH) THE FUNCTION IS CLEAR IF 12 IS FALSE (I2=LOW) OR SET IF I2 IS TRUE (I2=HIGH).

THE PLE8P8 ALSO FEATURES THREE-STATE OUTPUTS WITH TWO ACTIVE LOW OUTPUT ENABLE CONTROLS (/El AND /E2).

| Il | 12 | D1-D6 | Y1-Y6 | OPERATION |

|----|----|-------|-------|-----------|

| L  | L  | D     | /D    | INVERT    |

| L  | H  | D     | D     | TRUE      |

| H  | L  | X     | H     | CLEAR     |

| H  | H  | X     | L     | SET       |

|    |    |       |       |           |

# P5003.TXT

THIS PLE5P8 IMPLEMENTS A 3-TO-8 DEMULTIPLEXER. THE DEVICE WILL DEMULTIPLEX THREE SELECT SIGNALS (S2-S0) INTO EIGHT OUTPUTS (Y7-YO) USING THE INPUT DI WITH POLARITY SFLECT PO. THIS CHIP ALSO HAS CASCADABLE CAPABILITY AND THREE-STATE OUTPUTS. Pln ASSIGNMENTS:

- 1. PO HIGH INDICATES OUTPUT IS ACTIVE HIGH. LOW INDICATES OUTPUT IS ACTIVE LOW.

- DATA INPUT (DEMULTIPLEXING INPUT). ACTIVE LOW IF PO 2. DI IS LOW.

- (c) Copyright Monolithic Memories Inc. 1984 All Rights Reserved.

- 3. S2-S0 SELECT PINS. S2 IS THE MOST SIGNIFICANT BIT. ACTIVE HIGH REGARDLESS OF PO.

- 4. Y7-Y0 OUTPUTS. CAN BE ACTIVE HIGH OR ACTIVE LOW DEPENDING ON PO. ACTIVE LOW IF PO IS LOW.

# P5004.TXT

THE DEVICE WILL SWITCH BETWEEN TWO PAIRS OF 2-BIT INPUTS (A, B AND C, D), AS DETERMINED BY THE TWO SELECT LINES (SX, SZ), FOR OUTPUT THROUGH TWO PAIRS OF 2-BIT OUTPUTS (X AND Z). THREE-STATE OUTPUTS ARE ALSO PROVIDED WITH TWO ACTIVE LOW ENABLE PINS (/E1 AND /E2). THE FUNCTIONS OF THE DEVICE ARE SUMMARIZED IN THE TABLE BELOW:

| SEL              |        | IN     | PUT | A,      | В | IN      | PUT                | С,      | D       |    | ָטט!     | rput                 | X        | , Z      |                                                          |

|------------------|--------|--------|-----|---------|---|---------|--------------------|---------|---------|----|----------|----------------------|----------|----------|----------------------------------------------------------|

| S<br>X           | S      | A<br>1 |     | B<br>1  | _ | C<br>1  | C<br>2             | D<br>1  |         | -  |          | X<br>2               |          |          | FUNCTION                                                 |

| L<br>L<br>H<br>H | H<br>L |        |     | X<br>Bl |   | X<br>Cl | C2<br>X<br>C2<br>X | D1<br>X | D2<br>X | !! | Al<br>Bl | A2<br>A2<br>B2<br>B2 | Dl<br>Cl | D2<br>C2 | SELECT A, B<br>SELECT A, D<br>SELECT B, C<br>SELECT B, D |

#### P5005.TXT

THIS IS AN EXAMPLE OF A QUAD 2-TO-1 MULTIPLEXER IMPLEMENTED IN A PLE10P4. THE DEVICE FUNCTION IS TO SWITCH BETWEEN TWO 4-BIT INPUTS (A1-A4 AND B1-B4) TO ONE 4-BIT OUTPUT (Z1-Z4) AS DETERMINED BY TWO INPUT SELECT LINES (S2,S1). THE PLE10P4 ALSO FEATURES THREE-STATE OUTPUTS WITH TWO ACTIVE LOW ENABLE PINS (/E1 AND /E2). THE FUNCTION IS SUMMARIZED BELOW:

| SEL<br>LIN  | ECT<br>ES | I       | NPU'   | r | A      | I                 | יטפא    | <b>I</b> ' ] | В      |                                         | OUTPUT Z |    |          | Z        |                                                                     |

|-------------|-----------|---------|--------|---|--------|-------------------|---------|--------------|--------|-----------------------------------------|----------|----|----------|----------|---------------------------------------------------------------------|

| S<br>1      |           | A<br>1  | A<br>2 |   | A<br>4 | В<br>1            |         | -            | B<br>4 | !<br>!                                  | Z<br>1   |    |          | Z<br>4   | FUNCTION                                                            |

| L<br>L<br>H |           | Al<br>X | X      |   |        | X<br>X<br>B1<br>X | X<br>B2 | X<br>B3      |        | !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!! | Bl       | A2 | A3<br>B3 | A4<br>B4 | SELECT ALL LOWS<br>SELECT A1-A4<br>SELECT B1-B4<br>SELECT ALL HIGHS |

#### P5006.TXT

THIS EXAMPLE ILLUSTRATES THE USE OF A PLESP8 AS A HEXADECIMAL TO SEVEN SEGMENT DECODER. THE DEVICE DECODES A 4-BIT BINARY INPUT (D,C,B,A) INTO THE SEVEN SEGMENT OUTPUTS NEEDED TO DRIVE AN LED DISPLAY. NOTE THAT THIS DESIGN IS AN IMPROVEMENT FROM THE 74LS47 SINCE ALL SIXTEEN HEXADECIMAL DIGITS (0-F) CAN BE DISPLAYED. A LAMP TEST IS PROVIDED TO ILLUMINATE ALL SEVEN SEGMENTS AND THE DECIMAL POINT (IF DP IS CONNECTED) BY BRINGING LAMP TEST HIGH (LT=HIGH) REGARDLESS OF THE OTHER BINARY INPUTS. THREE-STATE OUTPUTS ARE ALSO PROVIDED WITH ONE ACTIVE LOW ENABLE PIN (/E).

| DIGIT | ! | LT |   |   | PU!<br>B |   |     | !        | SFGMENT<br>ON | 1 | OUTPUT<br>DISPLAY |

|-------|---|----|---|---|----------|---|-----|----------|---------------|---|-------------------|

| 0     | ! | L  | L | L | L        | L | • • | !        | ABCDEF        | ! | С                 |

| 1     | 1 | L  | L | L | L        | Н |     | !        | BC            | 1 | 1                 |

| 2     | 1 | L  | L | L | H        | L |     | !        | ABDEG         | 1 | 2                 |

| 3     | Ţ | L  | L | L | Н        | Н |     | <u>1</u> | ABCDG         | 1 | 3                 |

| 4     | ! | L  | L | H | L        | L |     | 1        | BCDFG         | 1 | 4                 |

| 5     | ! | L  | L | Н | L        | H |     | !        | ACDFG         | į | 5                 |

| 6     | ! | L  | L | Н | H        | L |     | !        | ACDEFG        | ! | 6                 |

| 7     | ! | L  | L | Н | Η        | Н |     | 1        | ABC           | ! | 7                 |

| 8     | ! | L  | Н | L | L        | L |     | !        | ABCDEFG       | į | 8                 |

| 9     | ! | L  | H | L | L        | Н |     | 1        | ABCFG         | 1 | 9                 |

| Α     | ! | L  | Н | L | H        | L |     | 1        | ABCEFG        | Ī | A                 |

| В     | 1 | L  | H | L | Н        | H |     | !        | CDEFG         | 1 | b                 |

| С     | ī | L  | Η | Η | L        | L |     | 1        | ADEF          | ! | С                 |

| D     | ! | L  | H | Н | L        | Н |     | 1        | BCDEG         | ! | đ                 |

| E     | i | L  | H | H | H        | L |     | 1        | ADEFG         | 1 | E                 |

| F     | ! | L  | Η | Н | H        | Η |     | 1        | AEFG          | 1 | F                 |

| G     | ! | Н  | X | X | X        | X |     | !        | ABCDEFG       | ! | 8 *               |

## \* BLANK TEST OF DISPLAY

# P5007.TXT

THIS 5-BIT BINARY TO 2-DIGIT BCD CONVERTER IS IMPLEMENTED IN A PLE5P8. THE DEVICE ACCEPTS A 5-BIT BINARY INPUT (BI) AND CONVERTS THIS INTO TWO 4-BIT BINARY CODED DECIMAL (BCD) OUTPUTS (B1 AND B0). THREE-STATE OUTPUTS ARE ALSO PROVIDED WITH ONE ACTIVE LOW ENABLE PIN (/E).

# P5008.TXT

THIS PLE5P8 WILL CONVERT A 4-BIT BCD INPUT (B3-B0) INTO A 4-BIT GRAY CODE REPRESENTATION (G3-G0) FOR OUTPUT.

### P5009.TXT

THIS PLE5P8 WILL CONVERT A 4-BIT GRAY CODE INPUT (G3-G0) INTO A 4-BIT BINARY REPRESENTATION (B3-B0) FOR OUTPUT.

# P5010.TXT

THIS 8-BIT PRIORITY ENCODER SCANS FOR THE FIRST HIGH INPUT LINE (17-10) FROM 17 (WHICH HAS THE HIGHEST PRIORITY) TO 10 (WHICH HAS THE LOWEST PRIORITY). IT WILL GENERATE A BINARY ENCODED OUTPUT (S2-S0) WHICH WILL POINT TO THE HIGHEST PRIORITY INPUT WHICH IS AT A HIGH STATE. IF NO INPUT LINES ARE HIGH (17-10=LOW), THEN THE BINARY ENCODED OUTPUTS WILL BE ZERO (S2-S0=LOW) AND THE ENABLE OUTPUT WILL BE HIGH (EN=HIGH) INDICATING A CARRY OUT TO THE NEXT PRIORITY ENCODER. THE OUTPUT ENABLE WILL BE LOW (EN=LOW) IF ANY OF THE INPUT LINES ARE HIGH. THE PLE8P4 ALSO HAS THREE-STATE OUTPUTS WITH TWO ACTIVE-LOW OUTPUT ENABLE CONTROL PINS (/E1 AND /E2).

### P5011.TXT

THIS PLE8P4 COMPARES TWO 4-BIT NUMBERS (A3-A0 AND B3-B0) TO ESTABLISH IF THEY ARE EQUAL (A = B => EQ=H), NOT EQUAL (A NOT = B => NE=H), LESS THAN (A < B => LT=H), OR GREATER THAN (A > B => GT=H) AND REPORTS THE COMPARISON STATUS ON THE OUTPUTS (EQ, NE, LT, GT) AS ILLUSTRATED IN THE OPERATIONS TABLE BELOW. THE PLE8P4 ALSO FEATURES THREE-STATE OUTPUTS WITH TWO ACTIVE-LOW OUTPUT ENABLE CONTROL PINS (/E1 AND /E2).

| INPUT NUMBERS<br>A3-A0 B3-B0         | COMPARISON STATUS EQ NE LT GT            | OPERATION                                                                                    |

|--------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------|

| A = B<br>A NOT = B<br>A < B<br>A > B | H L L L<br>L H X X<br>L H H L<br>L H L H | COMPARE A EQUAL TO B COMPARE A NOT EQUAL TO B COMPARE A LESS THAN B COMPARE A GREATER THAN B |

# P5012.TXT

THIS PLE12P4 COMPARES TWO 6-BIT NUMBERS (A5-A0 AND B5-B0) TO ESTABLISH IF THEY ARE EQUAL (A = B => EQ=H), NOT EQUAL (A NOT = B => NE=H), LESS THAN (A < B => LT=H), OR GREATER THAN (A > B => GT=H) AND REPORTS THE COMPARISON STATUS ON THE OUTPUTS (EQ, NE, LT, GT) AS ILLUSTRATED IN THE OPERATIONS TABLE BELOW. THE PLE12P4 ALSO FEATURES THREE-STATE OUTPUTS WITH TWO ACTIVE-LOW OUTPUT ENABLE CONTROL PINS (/E1 AND /E2).

| INPUT N<br>A5-A0 | NUMBERS<br>B5-B0    | COMPAI<br>EQ     |                  |                  | ATUS<br>GT       | OPERATION                                                                                    |

|------------------|---------------------|------------------|------------------|------------------|------------------|----------------------------------------------------------------------------------------------|

| A = A NOTA       | = B<br>T = B<br>C B | H<br>L<br>L<br>L | L<br>H<br>H<br>H | L<br>X<br>H<br>L | L<br>X<br>L<br>H | COMPARE A EQUAL TO B COMPARE A NOT EQUAL TO B COMPARE A LESS THAN B COMPARE A GREATER THAN B |

P5013.TXT

THIS PLE8P8 PERFORMS 4-BIT LOOK-UP TABLE MULTIPLICATION. DEVICE ACCEPTS TWO 4-BIT OPERANDS (X3-X0 AND Y3-Y0) TO PRODUCE THE 8-BIT PRODUCT (S7-S0). THE PLESPS ALSO HAS THREE-STATE OUTPUTS WITH TWO ACTIVE-LOW OUTPUT ENABLE CONTROL PINS (/El AND /E2).

> X3 X2 X1 X0 X Y3 Y2 Y1 Y0 S7 S6 S5 S4 S3 S2 S1 S0

P5014.TXT

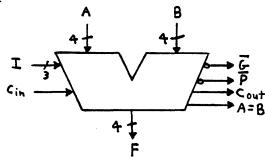

THIS PLE10P4 PERFORMS THE PARTIAL PRODUCTS REDUCTION FOR A WALLACE TREE ADDER. FIVE ROWS OF 2-BIT NUMBERS (A1-A0, B1-B0, C1-C0, D1-D0, AND E1-E0) ARE ADDED TO PRODUCE A 4-BIT SUM (P3-PO).

> Al AO B1 B0 C1 C0 D1 D0 E1 E0 \_\_\_\_ P3 P2 P1 P0

P5015.TXT

THIS PLE8P4 PERFORMS THE PARTIAL PRODUCTS REDUCTION FOR A WALLACE TREE ADDER. SEVEN ROWS OF 1-BIT NUMBERS (A, B, C, D, E, F, AND G) ARE ADDED TOGETHER TO PRODUCE A 3-BIT SUM.

> Α В C D E F G P2 P1 P0

P5016.TXT

THIS PLE12P8 PERFORMS THE PARTIAL PRODUCTS REDUCTION FOR A WALLACE TREE ADDER. FOUR ROWS OF 3-BIT NUMBERS (A2-A0, B2-B0, C2-C0, AND D2-D0) ARE ADDED TOGETHER TO PRODUCE A 5-BIT SUM (P4-PO).

A2 A1 A0 B2 B1 B0 C2 C1 C0 D2 D1 D0 P4 P3 P2 P1 F0

P5017.TXT

THIS PLE12P8 PERFORMS THE PARTIAL PRODUCTS REDUCTION FOR A WALLACE TREE ADDER. THREE ROWS OF 4-BIT NUMBERS (A3-A0, B3-B0, AND C3-C0) ARE ADDED TOGETHER TO PRODUCE A 6-BIT SUM.

> A3 A2 A1 A0 B3 B2 B1 B0 C3 C2 C1 C0 P5 P4 P3 P2 P1 P0

# HELP!! And where to get it:

Should you encounter any problems with PLEs or PLEASM, write or call:

The IdeaLogic Exchange Mail-Stop (08-26) Monolithic Memories Inc. 2175 Mission College Blvd. Santa Clara, CA 95050

Tel: (408)970-9700

<sup>(</sup>c) Copyright Monolithic Memories Inc. 1984 All Rights Reserved.

# Input/Output:

Prior to running the program, the user has access to an I/O package which can be used to specify I/O unit numbers and array sizes without having to recompile the program. The variables associated with this I/O routine are explained below....

CPG(6000) - Maximum number of characters permitted in the input specifications file

LLN(250) - Maximum number of lines permitted in the input specifications file

CLN(250) - Maximum number of characters permitted per line in the input file

CONINP - The Logical Unit Number for <READ>'s from the console CONOUT - The Logical Unit Number for <WRITE>'s to the console FILINP - The Logical Unit Number for <READ>'s from a named file FILOUT - The Logical Unit Number for <WRITE>'s to a named file

The Data Set Reference Numbers for INPUT and OUTPUT files are then assigned as variables at the begining of the program, as follows....

INPUT PLE DESIGN SPECIFICATION RPD=FILINP

INPUT OPERATION CODES ROC=CONINP

OUTPUT ECHO AND TRUTH TABLE POF=CONOUT

OUTPUT HEX AND BINARY PROGRAMMING FORMATS PDF=CONOUT/FILOUT

OUTPUT PROMPTS AND ERROR MESSAGES PMS=CONOUT/FILOUT

To perform the customization corresponding to your needs, you need to have access to the source code which means that you should have the Development system. These changes can help reduce the memory requirements and facilitate I/O.

The dimension of arrays CPG, LLN, and CLN can be modifed by making the appropriate changes in the subroutine IOINIT located at the top of the source code. This could be done to reduce memory requirements, since the arrays are statically allocated during compilation.

The logical unit numbers for the console are fixed for any given system and must be changed accordingly. For example, the logical unit number for reading from the console with VAX/VMS FORTRAN is 5 and for writing to the console is 6. These numbers are different with Supersoft FORTRAN used on the IBM-PC.

The logical unit numbers for writing and reading to and from files can be normally allocated to be between 0 and 19 excluding those reserved for the console.

# HIGH SPEED BIPOLAR PROMS FIND NEW APPLICATIONS AS PROGRAMMABLE LOGIC ELEMENTS (PLES)

Vincent J. Coli and Frank Lee

Product Planning and Applications

Monolithic Memories Inc.

2175 Mission College Boulevard

Santa Clara, California 95050

(408) 970-9700

Classic applications for bipolar PROMs include instruction storage for microprogram control store and software for microprocessor programs. However, due to a new design methodology and state of the art performance, PROMs are finding increasing numbers of applications as Programmable Logic Elements (or PLEs). This paper will cover the architecture, applications, and software support for PLEs.

# Fuse-Programmable Logic Families

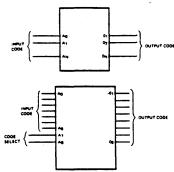

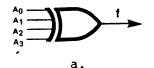

A typical combinatorial Boolean equation can be written in sum-of-product form, which consists of several AND gates summed at an OR gate. In general, a set of combinatorial Boolean equations with n inputs (I0,I1,...,In-1) and produces m outputs (O0,O1,...,Om-1) can be generated through one level of AND gates followed by one level of OR gates. Custom logic functions can be defined using programmable logic.

FIGURE 1. Structure of Programmable Logic Devices.

Fuse-programmable devices normally consist of two levels of logic -- AND-array and OR-array -- as suggested above. There are three basic types of fuse-programmable devices -- PROM (Programmable Read Only Memory), PLA (Programmable Logic Array), and PAL (Programmable Array Logic). Which arrays are fuse programmable distinguish these three types of devices.

PLAs offer the greatest flexibility since both the AND and OR arrays are programmable. This flexibility comes with the cost of lower performance, higher power dissipation, and generally higher price.

A PAL device has only the AND-array programmable; the OR array is fixed. Each output has an OR gate associated with it which sums a fixed number of product terms (AND combinations). Statistically there is only a limited number of product terms in any equation. So the flexibility of a PLA is normally not needed. This is a compromise between flexibility and cost and performance.

The OR-array is programmable in a PROM, but the fixed AND-array consists of all combinations of literals for each of the input variables. For example, there are 32 product terms available in a PROM with 5 inputs a,b,c,d,e (corresponding to words 0 through 31 in the PROM memory):

where '\*' represents the Boolean AND operator and '/' represents the Boolean NOT or inverter operator. The fuses in the OR-array are programmed to select the desired AND combinations.

PROGRAMMABLE ARRAY LOGIC PROGRAMMABLE LOGIC ARRAY PROGRAMMABLE LOGIC ELEMENT

PROGRAMMABLE AND ARRAY FIXED OR ARRAY BOTH ARRAYS PROGRAMMABLE FIXED AND ARRAY PROGRAMMABLE OR ARRAY

FIGURE 2. Structural differences between PLA, PAL, and PLE (PROM). Note that the PALs and PLEs complement each other. The PAL has many input terms while the PLE is rich in product terms.

existence of combinations of literals for all inputs make it possible to define functions which cannot be implemented in a PLA or a PAL. For example, a 5input Exclusive-OR (XOR) function can be implemented using 16 product terms. This may exceed the number of product terms available in a PAL and will consume too many product terms in a PLA, but can be constructed quite efficiently in a PROM. It is important to realize that any combination of inputs can be decoded in a PROM as long sufficient input pins are provided since a PROM provides 2<sup>n</sup> product terms (where n is the number of inputs). way of looking at this is that PROMs store the logic transfer function in a memory. The fixed AND-array (or AND-plane) consists of the row and column decoders while the fuses in the OR-array (or OR-plane) are the bits in the memory. In a memory, a fuse blown versus a fuse intact distinguishes a HIGH from a LOW.

FIGURE 3. Block diagram of a PROM viewed as a PLE. Notice that the PLE provides many (2<sup>n</sup> where n is the number of inputs) product terms. A by-product of this is programmable output polarity; either Active High or Active Low output polarity is available.

Due to this special characteristic of abundant product terms, PROMs are also often used as logic devices. In this paper, PROMs are referred to as PLEs (Programmable Logic Elements).

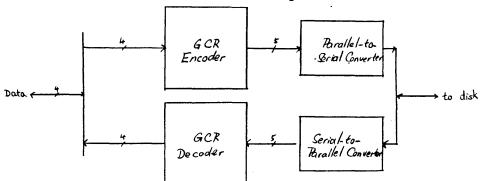

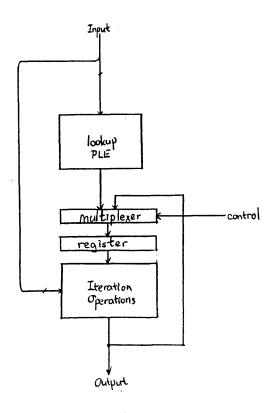

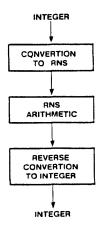

# Advantages of PLEs