MOTOROLA

# MC145474 MC145475

**ISDN**

S/T Interface Transceiver

Coming through loud and clear.

MOTOROLA

# MC145474 MC145475

**ISDN**

S/T Interface Transceiver

Coming through loud and clear.

# NOTICE PRODUCT ENHANCEMENT AND DATA UPDATE

This notice outlines changes made to the first and second printings of the Advance Information MC145474/75 data sheet. Changes incorporated into this revision reflect enhancements made to the MC145474/75 ISDN S/T Transceiver as well as additional information gathered to keep up with recent standards and to ensure Motorola's commitment to Total Customer Satisfaction.

#### **Product Enhancements**

The following two enhancements are now incorporated into the MC145474/75. The enhanced MC145474 ISDN S/T Transceiver is fully compatible with all previous versions of the chip.

1. Far End Code Violation (FECV) detection

This enhancement provides an additional interrupt (IRQ#6) that indicates when an FECV has occurred. The following sections of the MC145474/75 data sheet have been changed or added to support this enhancement:

Section 1.3

Features

Section 6.20

IRQ pin

Section 7.5.3.2

NR3(1) IRQ #6

Section 7.6.3

NR4(1) IRQ #6 Enable

Section 10.9

Multiframing — FECV Detection

Section 13.7

Interrupts — IRQ #6

2. Force IDL Transmit

This enhancement is an additional SCP control bit which allows a TE configured MC145474/75 to continue transmission onto the IDL interface regardless of the state of its transmitter. The TE's receiver, though, must be synchronized to INFO 4 incoming from the NT. The following sections of the MC145474/75 data sheet have been changed or added to support this enhancement:

Section 7.2.2 NR0(2) Transmit Power Down Section 8.15.7 BR13(1) Force IDL Transmit

## **General Data Sheet Updates**

In addition to the data sheet changes made above due to product enhancement the following sections have also been changed or added:

Section 6.24

Crystal specification changed to include ±100 ppm requirement.

Section 14.3

Description of receive filter delay compensation added.

Section 14.4.1

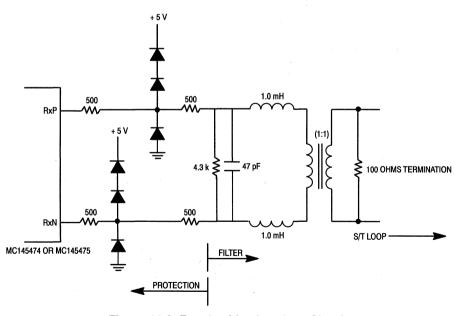

Recommended transformer vendor addresses updated.

Section 14.4.4

New section added for PCB layout recommendations.

Section 15.9

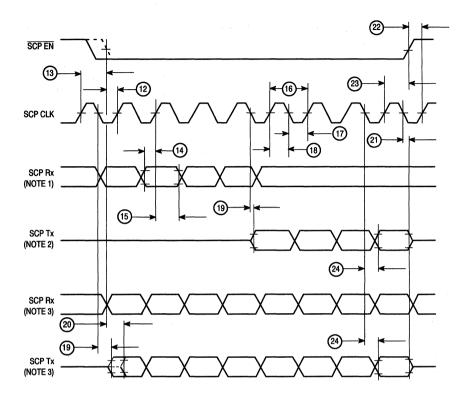

SCP timing definitions 20, 22 and 23 updated in Figure 15-2.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was neglignent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

This document replaces MC145474/D ADI1523.

| Paragra<br>Numl                                                               |                                                                                                                                                                                                                                                                               | Page<br>Number                                       |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                                               | SECTION 1<br>INTRODUCTION                                                                                                                                                                                                                                                     |                                                      |

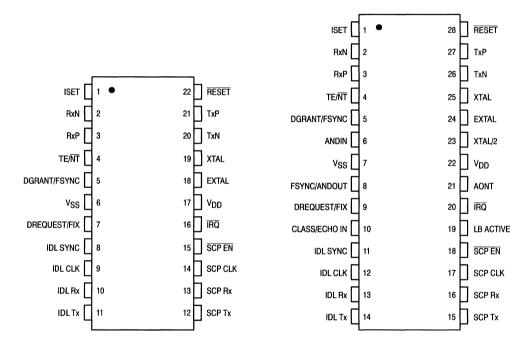

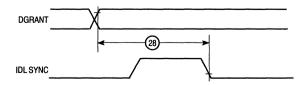

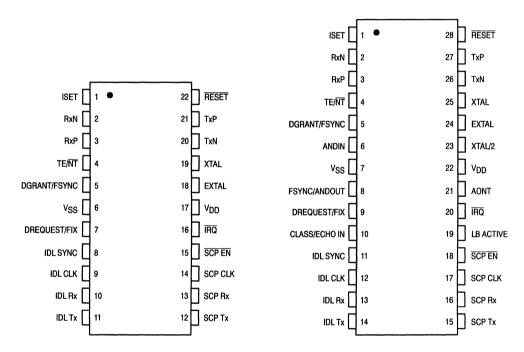

| 1.1<br>1.2<br>1.3<br>1.4                                                      | INTRODUCTION ORGANIZATION OF DATA SHEET FEATURES PACKAGING                                                                                                                                                                                                                    | 1-1<br>1-2                                           |

|                                                                               | SECTION 2 WIRING CONFIGURATIONS                                                                                                                                                                                                                                               |                                                      |

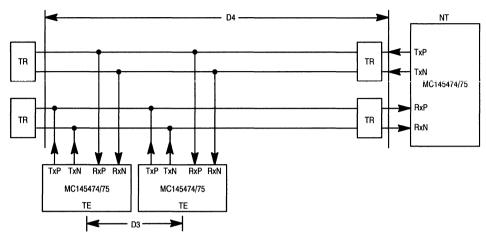

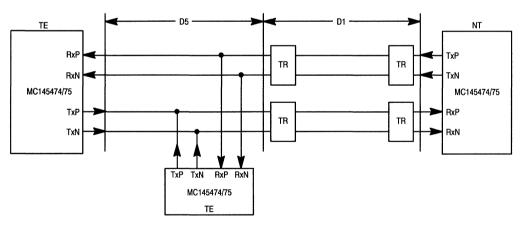

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                                        | INTRODUCTION POINT TO POINT OPERATION SHORT PASSIVE BUS OPERATION EXTENDED PASSIVE BUS OPERATION BRANCHED PASSIVE BUS OPERATION NT1 STAR MODE OF OPERATION                                                                                                                    | 2-1<br>2-2<br>2-2<br>2-2                             |

|                                                                               | SECTION 3 ACTIVATION/DEACTIVATION OF S/T TRANSCEIVER                                                                                                                                                                                                                          |                                                      |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.7.1<br>3.7.2<br>3.8<br>3.9 | INTRODUCTION TRANSMISSION STATES FOR NT MODE S/T TRANSCEIVER TRANSMISSION STATES FOR TE MODE S/T TRANSCEIVER ACTIVATION OF S/T LOOP BY NT ACTIVATION OF S/T LOOP BY TE ACTIVATION PROCEDURES IGNORED FRAME SYNC NT Mode TE Mode ACTIVATION INDICATION DEACTIVATION PROCEDURES | 3-1<br>3-1<br>3-1<br>3-2<br>3-2<br>3-2<br>3-2<br>3-3 |

| 3.10<br>3.10.1<br>3.10.2<br>3.11<br>3.11.1<br>3.11.2<br>3.11.3<br>3.11.4      | INITIAL STATE OF B1 AND B2 CHANNELS  NT  TE  ADDITIONAL NOTES  E Channel  A Bit  SCP Nomenclature  SCP Indication of Transmit and Receive States                                                                                                                              | 3-3<br>3-3<br>3-3<br>3-3<br>3-3<br>3-4               |

| Paragra<br>Numb                                                                                                    |                                                                                                                                                                                                                                                                                                            | Page<br>Number                                                                             |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

|                                                                                                                    | SECTION 4 THE INTERCHIP DIGITAL LINK                                                                                                                                                                                                                                                                       |                                                                                            |

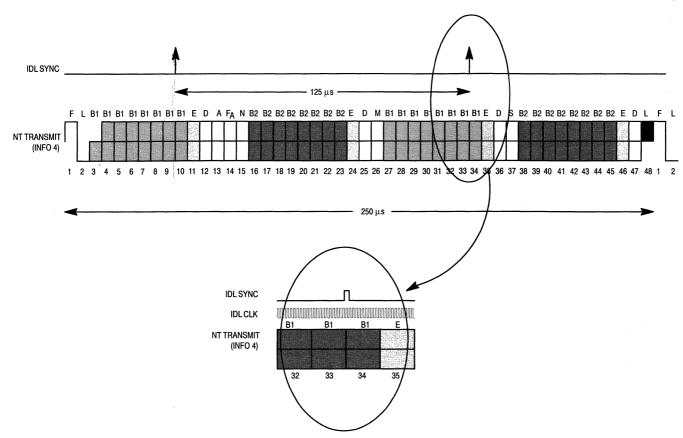

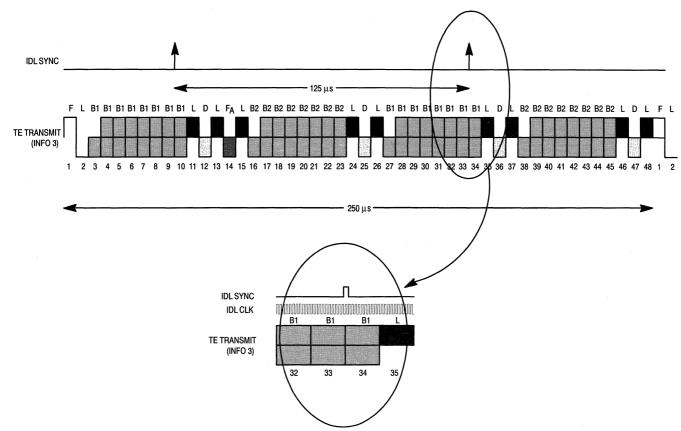

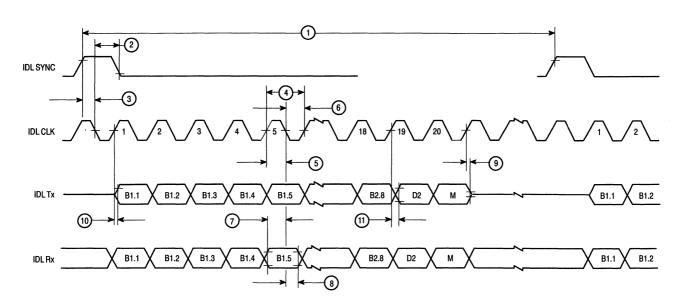

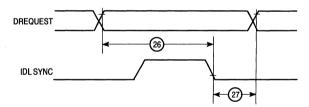

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.7.1<br>4.7.2<br>4.7.3       | INTRODUCTION SIGNAL DESCRIPTION IDL SYNC IDL CLK IDL Tx IDL Rx NT IDL SLAVE NT IDL MASTER TE IDL MASTER TE IDL MASTER FREE RUN ADDITIONAL NOTES IDL A and IDL M Bits Phase Relationship of NTs Transmit Signal with Respect to IDL SYNC Phase Relationship of TEs Transmit Signal with Respect to IDL SYNC | . 4-1<br>. 4-1<br>. 4-2<br>. 4-2<br>. 4-4<br>. 4-4<br>. 4-4<br>. 4-5<br>. 4-5<br>. 4-5     |

|                                                                                                                    | SECTION 5 THE SERIAL CONTROL PORT                                                                                                                                                                                                                                                                          |                                                                                            |

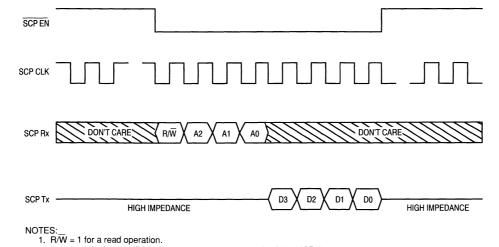

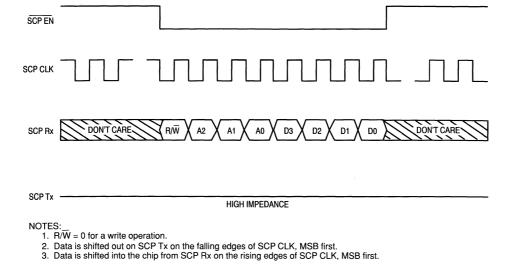

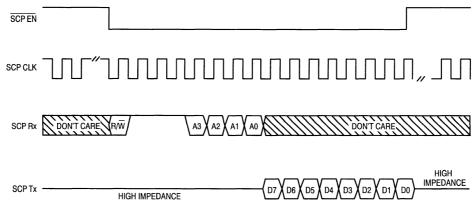

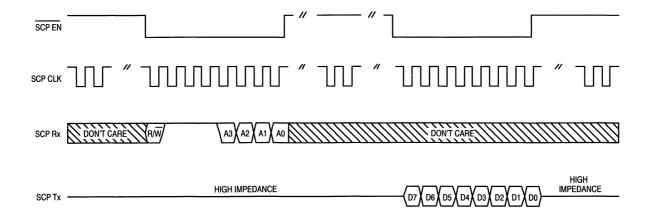

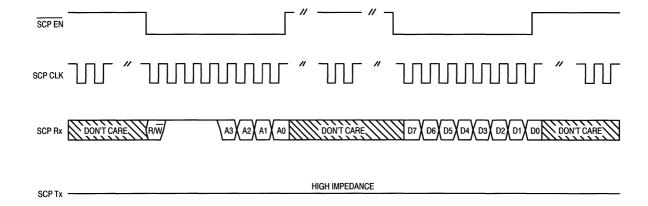

| 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.5<br>5.5.1<br>5.5.2 | INTRODUCTION SCP TRANSACTIONS SCP Nibble Read SCP Nibble Write SCP Byte Read SCP Byte Write SIGNAL DESCRIPTION SCP Tx SCP Rx SCP CLK SCP EN SCP HIGH-IMPEDANCE DIGITAL OUTPUT MODE (SCP HIDOM) ADDITIONAL NOTES Independence of Crystal SCP Slave                                                          | . 5-1<br>. 5-1<br>. 5-2<br>. 5-2<br>. 5-9<br>. 5-9<br>. 5-10<br>. 5-10<br>. 5-10<br>. 5-10 |

|                                                                                                                    | SECTION 6 PIN DESCRIPTIONS                                                                                                                                                                                                                                                                                 |                                                                                            |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5                                                                                    | INTRODUCTION ISET RxN, RxP TE/NT DGRANT/FSYNC                                                                                                                                                                                                                                                              | . 6-1<br>. 6-1<br>. 6-2                                                                    |

| Paragra<br>Numb |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ile        | Page<br>Number |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|

| 6.5.1           | DGRANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | . 6-2          |

| 6.5.2           | FSYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | . 6-3          |

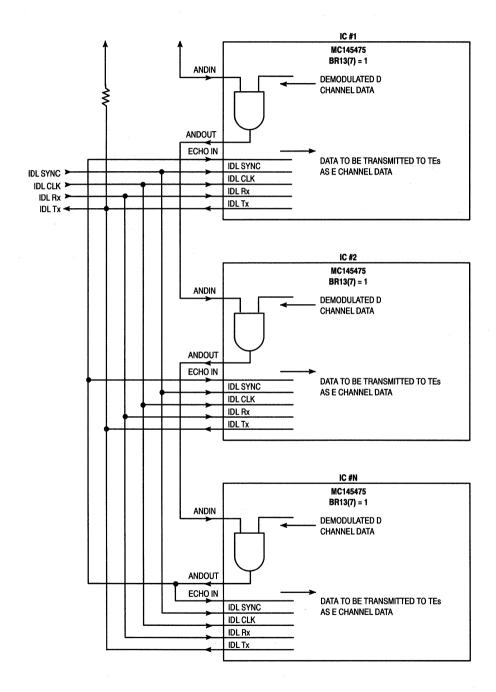

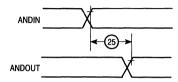

| 6.6             | ANDIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |                |

| 6.7             | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                |

| 6.8             | FSYNC/ANDOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                |

| 6.8.1           | FSYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | . 6-3          |

| 6.8.2           | ANDOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | . 6-4          |

| 6.9             | DREQUEST/FIX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | . 6-4          |

| 6.9.1           | DREQUEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | . 6-4          |

| 6.9.2           | FIX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            | . 6-4          |

| 6.10            | CLASS/ECHO IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            | . 6-5          |

| 6.10.1          | CLASS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | . 6-5          |

| 6.10.2          | ECHO IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | . 6-5          |

| 6.11            | IDL SYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | . 6-6          |

| 6.12            | IDL CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | . 6-6          |

| 6.13            | IDL Rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | . 6-6          |

| 6.14            | IDL Tx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | . 6-7          |

| 6.15            | SCP Tx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | . 6-7          |

| 6.16            | SCP Rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | . 6-7          |

| 6.17            | SCP CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | . 6-8          |

| 6.18            | SCP EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | . 6-8          |

| 6.19            | LOOPBACK ACTIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | . 6-8          |

| 6.20            | ĪRQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            | . 6-8          |

| 6.21            | AONT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | . 6-8          |

| 6.22            | V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | . 6-9          |

| 6.23            | XTAL/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                |

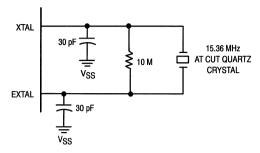

| 6.24            | XTAL AND EXTAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            | . 6-9          |

| 6.25            | TxP, TxN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | . 6-10         |

| 6.26            | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | . 6-10         |

| 6.27            | ADDITIONAL NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | . 6-11         |