MPC105 PCI Bridge/Memory Controller User's Manual

## MPC105 PCI Bridge/Memory Controller User's Manual

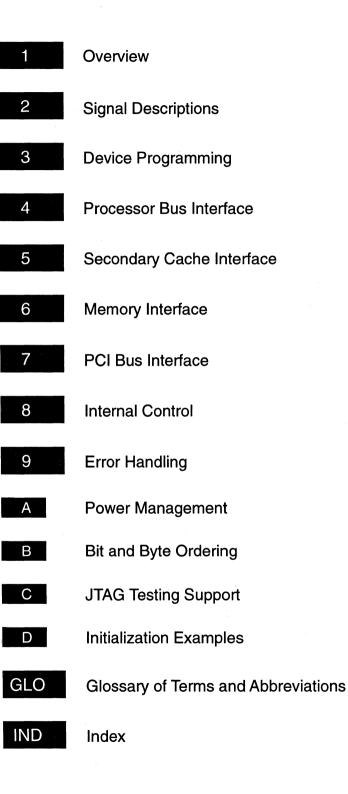

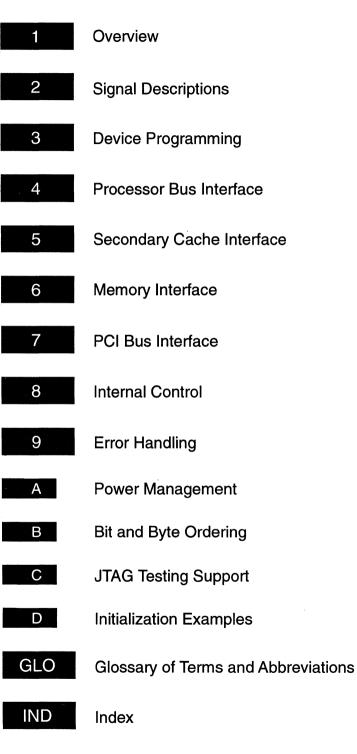

| Overview                            | 1   |

|-------------------------------------|-----|

| Signal Descriptions                 | 2   |

| Device Programming                  | 3   |

| Processor Bus Interface             | 4   |

| Secondary Cache Interface           | 5   |

| Memory Interface                    | 6   |

| PCI Bus Interface                   | 7   |

| Internal Control                    | 8   |

| Error Handling                      | 9   |

| Power Management                    | А   |

| Bit and Byte Ordering               | B   |

| JTAG Testing Support                | C   |

| Initialization Examples             | D   |

| Glossary of Terms and Abbreviations | GLO |

| Index                               | IND |

MPC105UM/AD 5/95

# MPC105

#### PCIB/MC User's Manual

PowerPC

© Motorola Inc. 1995. All rights reserved.

This document contains information on a new product under development. Motorola reserves the right to change or discontinue this product without notice. Information in this document is provided solely to enable system and software implementers to use PowerPC microprocessors. There are no express or implied copyright licenses granted hereunder to design or fabricate PowerPC integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to sustain life, or for any other application whole the altive of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

IBM is a registered trademark of IBM Corp. The PowerPC name, PowerPC logotype, PowerPC Architecture, PowerPC 601, PowerPC 603, PowerPC 604, and PowerPC 602 are trademarks of IBM Corp. used by Motorola under license from IBM Corp.

Paragraph Number

Title

Page Number

#### **About This Book**

| Audience                   | xix |

|----------------------------|-----|

| Organization               | xx  |

| Additional Reading         |     |

| Conventions                |     |

| Acronyms and Abbreviations |     |

#### Chapter 1 Overview

| 1.1   | MPC105 PCIB/MC Features                  |  |

|-------|------------------------------------------|--|

| 1.2   | MPC105 Major Functional Units            |  |

| 1.2.1 | 60x Processor Interface                  |  |

| 1.2.2 | Secondary (L2) Cache/Processor Interface |  |

| 1.2.3 | PCI Interface                            |  |

| 1.2.4 | Memory Interface                         |  |

| 1.3   | Power Management                         |  |

| 1.3.1 | Full-On Mode                             |  |

| 1.3.2 | Doze Mode                                |  |

| 1.3.3 | Nap Mode                                 |  |

| 1.3.4 | Sleep Mode                               |  |

| 1.3.5 | Suspend Mode                             |  |

#### Chapter 2 Signal Descriptions

| 2.1       | Signal Configuration            |  |

|-----------|---------------------------------|--|

| 2.2       | Signal Descriptions             |  |

| 2.2.1     | 60x Processor Interface Signals |  |

| 2.2.1.1   | Bus Request 0 (BR0)—Input       |  |

| 2.2.1.2   | Bus Grant 0 (BG0)—Output        |  |

| 2.2.1.3   | Transfer Start (TS)             |  |

| 2.2.1.3.1 | Transfer Start (TS)—Output      |  |

| 2.2.1.3.2 | Transfer Start (TS)—Input       |  |

|           |                                 |  |

#### Paragraph Number

Page Number

| 2.2.1.4    | Extended Address Transfer Start (XATS)—Input                    |

|------------|-----------------------------------------------------------------|

| 2.2.1.4    | Address Bus (A0–A31)                                            |

| 2.2.1.5    | Address Bus (A0–A31)                                            |

| 2.2.1.5.1  | Address Bus (A0–A31)—Output                                     |

| 2.2.1.5.2  |                                                                 |

|            | Transfer Type (TT0–TT4)                                         |

| 2.2.1.6.1  | Transfer Type (TT0–TT4)—Output                                  |

| 2.2.1.6.2  | Transfer Type (TT0–TT4)—Input                                   |

| 2.2.1.7    | Transfer Size (TSIZ0–TSIZ2)                                     |

| 2.2.1.7.1  | Transfer Size (TSIZ0–TSIZ2)—Output                              |

| 2.2.1.7.2  | Transfer Size (TSIZ0–TSIZ2)—Input                               |

| 2.2.1.8    | Transfer Burst (TBST)                                           |

| 2.2.1.8.1  | Transfer Burst (TBST)—Output                                    |

| 2.2.1.8.2  | Transfer Burst (TBST)—Input                                     |

| 2.2.1.9    | Address Acknowledge (AACK)                                      |

| 2.2.1.9.1  | Address Acknowledge (AACK)—Output                               |

| 2.2.1.9.2  | Address Acknowledge (AACK)—Input2-7                             |

| 2.2.1.10   | Address Retry (ARTRY)                                           |

| 2.2.1.10.1 | Address Retry (ARTRY)—Output                                    |

| 2.2.1.10.2 | Address Retry (ARTRY)—Input                                     |

| 2.2.1.11   | Data Bus Grant 0 (DBG0)—Output2-8                               |

| 2.2.1.12   | Data Bus (DH0-DH31, DL0-DL31)2-9                                |

| 2.2.1.12.1 | Data Bus (DH0-DH31, DL0-DL31)-Output2-9                         |

| 2.2.1.12.2 | Data Bus (DH0–DH31, DL0–DL31)–Input                             |

| 2.2.1.13   | Write-Through (WT)—Input/Output                                 |

| 2.2.1.14   | Caching-Inhibited (CI)—Input/Output                             |

| 2.2.1.15   | Global (GBL)—Input/Output                                       |

| 2.2.1.16   | Transfer Acknowledge (TA)2-10                                   |

| 2.2.1.16.1 | Transfer Acknowledge (TA)—Output2-10                            |

| 2.2.1.16.2 | Transfer Acknowledge (TA)—Input                                 |

| 2.2.1.17   | Transfer Error Acknowledge (TEA)—Output                         |

| 2.2.2      | Secondary Cache/Processor Interface Signals                     |

| 2.2.2.1    | Secondary (L2) Cache Signals2-12                                |

| 2.2.2.1.1  | Address Strobe/Data Address Latch Enable (ADS/DALE)—Output 2-12 |

| 2.2.2.1.2  | Bus Address Advance/Burst Address 1 (BAA/BA1)-Output 2-13       |

| 2.2.2.1.3  | Data RAM Output Enable (DOE)—Output                             |

| 2.2.2.1.4  | Data RAM Write Enable (FNR/DWE0, DWE/DWE1, DWE2,                |

|            | CKO/DWE3, DWE4-DWE6, CKE/DWE7)-Output2-13                       |

| 2.2.2.1.5  | Hit (HIT)—Input                                                 |

| 2.2.2.1.6  | Tag Address Latch Enable/Burst Address 0 (TALE/BA0)—Output 2-14 |

| 2.2.2.1.7  | Tag Address Latch Output Enable (TALOE)—Output                  |

| 2.2.2.1.8  | Tag Write Enable (TWE)—Output    2-15                           |

| 2.2.2.1.9  | Tag Valid (TV)—Output2-15                                       |

| 2.2.2.1.10 | Dirty In (DIRTY_IN/BR1)—Input2-15                               |

|            |                                                                 |

| Paragraph<br>Number | Title P<br>Num                                                   | age<br>Iber |

|---------------------|------------------------------------------------------------------|-------------|

| 2.2.2.1.11          | Dirty Out (DIRTY_OUT/BG1)—Output                                 | . 2-16      |

| 2.2.2.1.12          | Tag Output Enable (TOE/DBG1)—Output                              |             |

| 2.2.2.2             | Secondary Processor Signals                                      |             |

| 2.2.2.2.1           | Bus Request 1 (DIRTY_IN/BR1)—Input                               |             |

| 2.2.2.2.2           | Bus Grant 1 (DIRTY_OUT/BG1)—Output                               |             |

| 2.2.2.2.3           | Data Bus Grant 1 (TOE/DBG1)—Output                               |             |

| 2.2.3               | Memory Interface Signals                                         |             |

| 2.2.3.1             | Row Address Strobe/Command Select (RAS/CS0-                      |             |

| 2121011             | RAS/CS7)—Output                                                  | . 2-18      |

| 2.2.3.2             | Column Address Strobe/Data Qualifier (CAS/DQM0-                  |             |

|                     | CAS/DQM7)—Output                                                 | . 2-18      |

| 2.2.3.3             | Write Enable (WE)—Output                                         |             |

| 2.2.3.4             | Memory Address/ROM Address (MA0–MA11/AR8–AR19)—Output            |             |

| 2.2.3.5             | Memory Parity/ROM Address (PAR0–PAR7/AR0–AR7)                    |             |

| 2.2.3.5.1           | Memory Parity/ROM Address (PAR0–PAR7/AR0–AR7)—Output             |             |

| 2.2.3.5.2           | Memory Parity (PAR0–PAR7/AR0–AR7)—Input                          |             |

| 2.2.3.6             | Memory Clock Enable (CKE/DWE7)—Output                            |             |

| 2.2.3.7             | SDRAM Row Address Strobe (SDRAS)—Output                          |             |

| 2.2.3.8             | SDRAM Column Address Strobe/External Latch Enable (SDCAS/ELE)    |             |

| 2.2.3.0             | Output                                                           |             |

| 2.2.3.9             | ROM Bank 0 Select (RCS0)—Output                                  |             |

| 2.2.3.10            | Flash ROM Output Enable/ROM Bank 1 Select (FOE/RCSI)—Output.     |             |

| 2.2.3.11            | Buffer Control (BCTL0–BCTL1)—Output                              |             |

| 2.2.3.12            | Real Time Clock (RTC)—Input                                      |             |

| 2.2.4               | PCI Interface Signals                                            |             |

| 2.2.4.1             | PCI Address/Data Bus (AD31–AD0)                                  |             |

| 2.2.4.1.1           | Address/Data (AD31–AD0)—Output                                   |             |

| 2.2.4.1.2           | Address/Data (AD31–AD0)—Input                                    |             |

| 2.2.4.2             | Command/Byte Enables ( $\overline{C/BE3}$ – $\overline{C/BE0}$ ) |             |

| 2.2.4.2.1           | Command/Byte Enables (C/BE3–C/BE0)—Output                        |             |

| 2.2.4.2.2           | Command/Byte Enables (C/BE3–C/BE0)—Input                         |             |

| 2.2.4.3             | Parity (PAR)                                                     |             |

| 2.2.4.3.1           | Parity (PAR)—Output                                              |             |

| 2.2.4.3.2           | Parity (PAR)—Input                                               |             |

| 2.2.4.4             | Target Ready (TRDY)                                              |             |

| 2.2.4.4.1           | Target Ready (TRDY)—Output                                       |             |

| 2.2.4.4.2           | Target Ready (TRDY)—Input                                        | 2-25        |

| 2.2.4.5             | Initializer Ready (IRDY)                                         |             |

| 2.2.4.5.1           | Initializer Ready (IRDY)—Output                                  | 2-25        |

| 2.2.4.5.2           | Initializer Ready (IRDY)—Input                                   | 2-25        |

| 2.2.4.6             | Frame (FRAME)                                                    |             |

| 2.2.4.6.1           | Frame (FRAME)—Output                                             |             |

| 2.2.4.6.2           | Frame (FRAME)—Input                                              |             |

| Paragraph<br>Number | Title                                          | Page<br>Number |

|---------------------|------------------------------------------------|----------------|

| 2.2.4.7             | Stop (STOP)                                    |                |

| 2.2.4.7.1           | Stop (STOP)—Output                             |                |

| 2.2.4.7.2           | Stop (STOP)—Input                              |                |

| 2.2.4.8             | Lock (LOCK)—Input                              |                |

| 2.2.4.9             | Device Select (DEVSEL)                         |                |

| 2.2.4.9.1           | Device Select (DEVSEL)—Output                  |                |

| 2.2.4.9.2           | Device Select (DEVSEL)—Input                   |                |

| 2.2.4.10            | PCI Bus Request (REQ)—Output                   |                |

| 2.2.4.11            | PCI Bus Grant (GNT)—Input                      |                |

| 2.2.4.12            | Parity Error (PERR)                            |                |

| 2.2.4.12.1          | Parity Error (PERR)—Output                     |                |

| 2.2.4.12.2          | Parity Error (PERR)—Input                      |                |

| 2.2.4.13            | System Error (SERR)                            |                |

| 2.2.4.13.1          | System Error (SERR)—Output                     |                |

| 2.2.4.13.2          | System Error (SERR)—Input                      |                |

| 2.2.4.14            | PCI Sideband Signals                           |                |

| 2.2.4.14.1          | ISA Master (ISA_MASTER)—Input                  |                |

| 2.2.4.14.2          | Flush Request (FLSHREQ)-Input                  |                |

| 2.2.4.14.3          | Flush Acknowledge (MEMACK)—Output              |                |

| 2.2.5               | Interrupt, Clock, and Power Management Signals |                |

| 2.2.5.1             | Nonmaskable Interrupt (NMI)-Input              |                |

| 2.2.5.2             | Hard Reset (HRST)—Input                        |                |

| 2.2.5.3             | Machine Check (MCP)—Output                     |                |

| 2.2.5.4             | System Clock (SYSCLK)—Input                    |                |

| 2.2.5.5             | Test Clock (CK0/DWE3)—Output                   |                |

| 2.2.5.6             | Quiesce Request (QREQ)—Input                   |                |

| 2.2.5.7             | Quiesce Acknowledge (QACK)—Output              |                |

| 2.2.5.8             | Suspend (SUSPEND)—Input                        |                |

| 2.2.6               | IEEE 1149.1 Interface Signals                  |                |

| 2.2.6.1             | JTAG Test Data Output (TDO)—Output             |                |

| 2.2.6.2             | JTAG Test Data Input (TDI)—Input               |                |

| 2.2.6.3             | JTAG Test Clock (TCK)—Input                    |                |

| 2.2.6.4             | JTAG Test Mode Select (TMS)—Input              |                |

| 2.2.6.5             | JTAG Test Reset (TRST)—Input                   |                |

| 2.2.7               | Configuration Signals                          |                |

| 2.2.7.1             | Flash/Nonvolatile ROM (FNR/DWE0)—Input         |                |

| 2.2.7.2             | ROM Location (RCS0)—Input                      |                |

| 2.2.7.3             | 60x Data Bus Width (DL0)—Input                 |                |

| 2.2.7.4             | Address Map (XATS)—Input                       |                |

| 2.2.7.5             | Clock Mode (PLL0-PLL3)—Input                   |                |

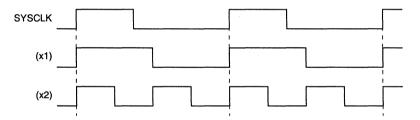

| 2.3                 | Clocking                                       |                |

Paragraph Number

#### Title

#### Page Number

#### Chapter 3 Device Programming

| 3.1     | Address Maps                                        |  |

|---------|-----------------------------------------------------|--|

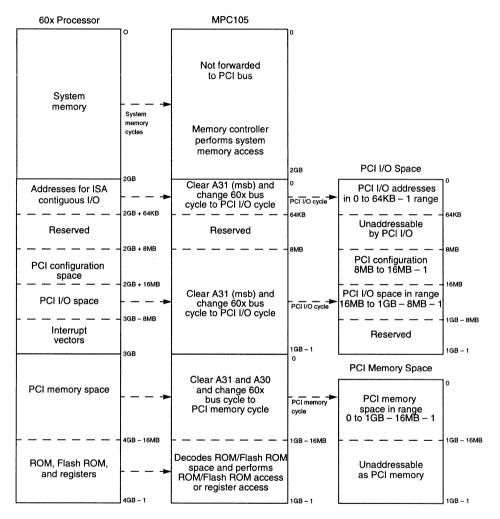

| 3.1.1   | Address Map A                                       |  |

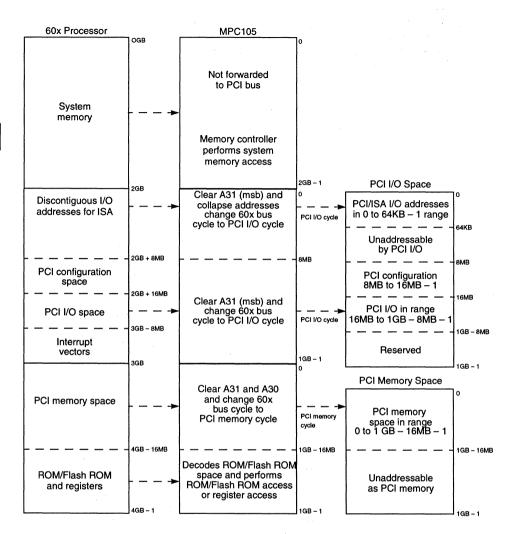

| 3.1.2   | Address Map B                                       |  |

| 3.2     | Configuration Registers                             |  |

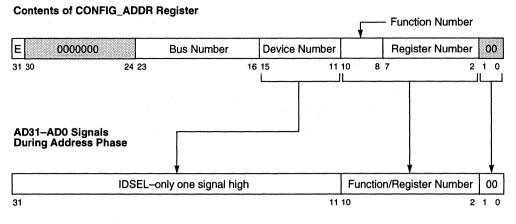

| 3.2.1   | Configuration Register Access                       |  |

| 3.2.1.1 | Configuration Register Access in Little-Endian Mode |  |

| 3.2.1.2 | Configuration Register Access in Big-Endian Mode    |  |

| 3.2.2   | Configuration Register Summary                      |  |

| 3.2.3   | PCI Registers                                       |  |

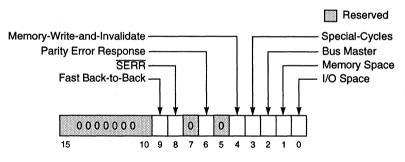

| 3.2.3.1 | PCI Command Register                                |  |

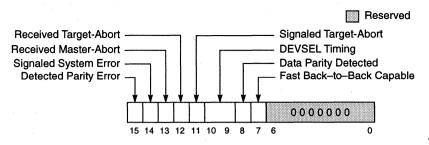

| 3.2.3.2 | PCI Status Register                                 |  |

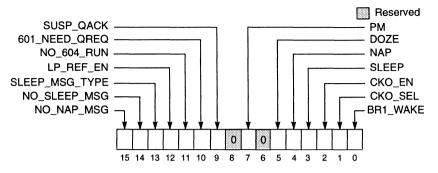

| 3.2.4   | Power Management Configuration Register (PMCR)      |  |

| 3.2.5   | Error Handling Registers                            |  |

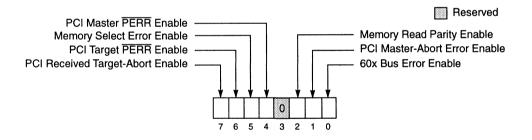

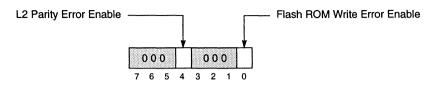

| 3.2.5.1 | Error Enabling Registers                            |  |

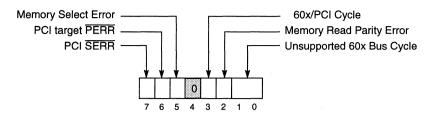

| 3.2.5.2 | Error Detection Registers                           |  |

| 3.2.5.3 | Error Status Registers                              |  |

| 3.2.6   | Memory Interface Configuration Registers            |  |

| 3.2.6.1 | Memory Boundary Registers                           |  |

| 3.2.6.2 | Memory Bank Enable Register                         |  |

| 3.2.6.3 | Memory Control Configuration Registers              |  |

| 3.2.7   | Processor Interface Configuration Registers         |  |

| 3.2.8   | Alternate OS-Visible Parameters Registers           |  |

| 3.2.9   | External Configuration Registers                    |  |

|         |                                                     |  |

#### Chapter 4 Processor Bus Interface

| 4.1     | MPC105 Processor Bus Configuration                |  |

|---------|---------------------------------------------------|--|

| 4.1.1   | Single-Processor System Configuration             |  |

| 4.1.2   | Multiprocessor System Configuration               |  |

| 4.2     | Processor Bus Protocol Overview                   |  |

| 4.2.1   | MPC105 Arbitration                                |  |

| 4.2.2   | Address Pipelining and Split-Bus Transactions     |  |

| 4.3     | Address Tenure Operations                         |  |

| 4.3.1   | Address Arbitration                               |  |

| 4.3.2   | Address Transfer Attribute Signals                |  |

| 4.3.2.1 | Transfer Type Signal Encodings                    |  |

| 4.3.2.2 | TBST and TSIZ0–TSIZ2 Signals and Size of Transfer |  |

| 4.3.2.3 | Burst Ordering During Data Transfers              |  |

#### Paragraph Number

#### Title

#### Page Number

| 4.3.2.4 | Effect of Alignment on Data Transfers (64-Bit Data Bus) |  |

|---------|---------------------------------------------------------|--|

| 4.3.2.5 | Effect of Alignment in Data Transfers (32-Bit Data Bus) |  |

| 4.3.3   | Address Transfer Termination                            |  |

| 4.3.3.1 | MPC105 Snoop Response                                   |  |

| 4.3.3.2 | Address Tenure Timing Configuration                     |  |

| 4.4     | Data Tenure Operations                                  |  |

| 4.4.1   | Data Bus Arbitration                                    |  |

| 4.4.2   | Data Bus Transfers and Normal Termination               |  |

| 4.4.3   | Data Tenure Timing Configurations                       |  |

| 4.4.4   | Data Bus Termination by TEA                             |  |

| 4.4.5   | 60x Bus Slave Support                                   |  |

|         |                                                         |  |

#### Chapter 5 Secondary Cache Interface

| L2 Cache Interface Operation                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| L2 Cache Initialization                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| L2 Cache Address Operations                                         | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Asynchronous SRAM Interface                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| L2 Cache Response to Bus Operations                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Write-Back L2 Cache Response                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Write-Through L2 Cache Response                                     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| L2 Cache Configuration Registers                                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| L2 Cache Interface Mode Configuration                               | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| L2 Cache Interface Control Configuration                            | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CF_L2_HIT_DELAY[1-0] 5-1'                                           | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CF_DOE                                                              | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CF_WDATA                                                            | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CF_WMODE5-2                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| L2 Cache Interface Timing Examples                                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Synchronous Burst SRAM L2 Cache Timing5-2                           | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

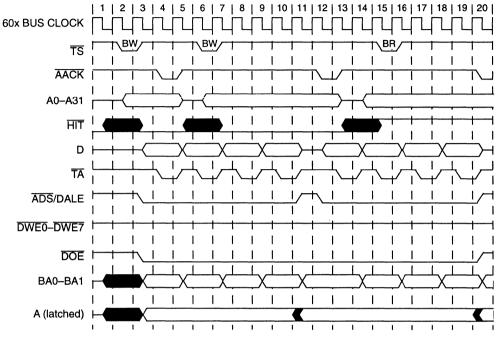

| L2 Cache Read Hit Timing5-2                                         | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| L2 Cache Write Hit Timing                                           | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

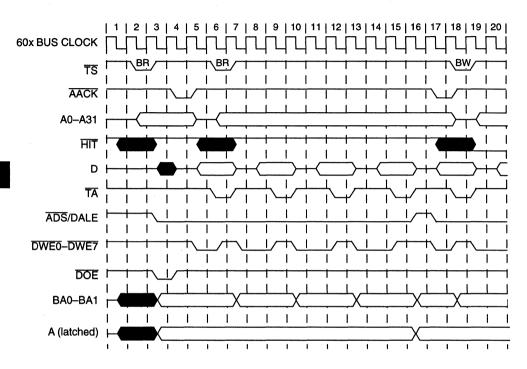

| L2 Cache Line Update Timing5-2                                      | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

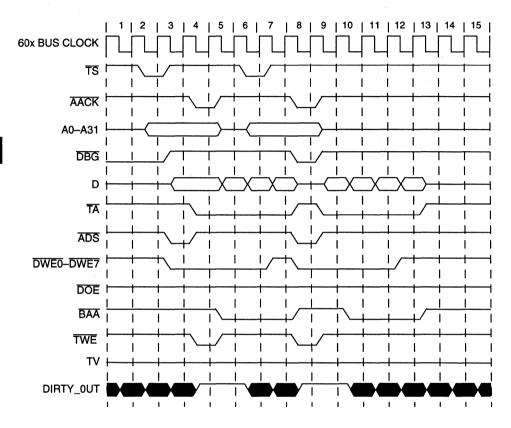

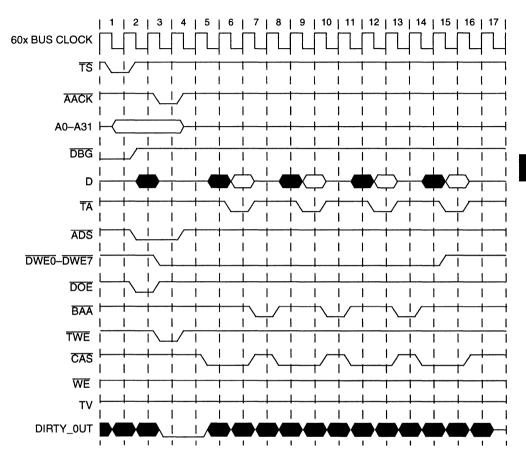

| L2 Cache Line Cast-Out Timing5-2                                    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

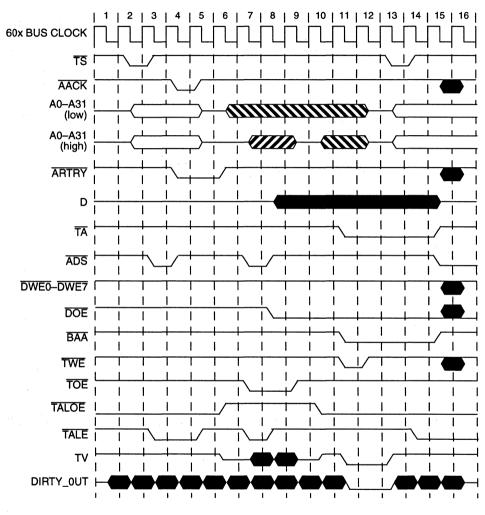

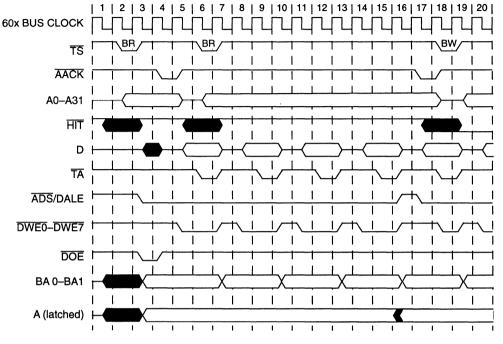

| L2 Cache Hit Timing Following PCI Read Snoop5-2                     | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| L2 Cache Line Push Timing Following PCI Write Snoop5-3              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| L2 Cache Line Invalidate Timing Following PCI Write with Invalidate |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Snoop                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Asynchronous SRAM L2 Cache Timing                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

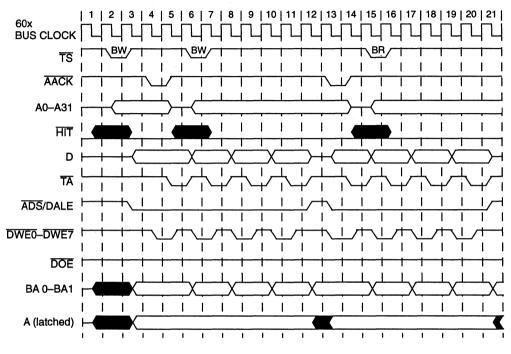

| Burst Read Timing5-3                                                | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                     | L2 Cache Address Operations5Asynchronous SRAM Interface5L2 Cache Response to Bus Operations5Write-Back L2 Cache Response51L2 Cache Configuration Registers5-1L2 Cache Interface Mode Configuration5-1L2 Cache Interface Control Configuration5-1L2 Cache Interface Control Configuration5-1CF_L2_HIT_DELAY[1-0]5-1CF_WDATA5-1CF_WMODE5-2L2 Cache Interface Timing Examples5-2Synchronous Burst SRAM L2 Cache Timing5-2L2 Cache Line Update Timing5-2L2 Cache Line Nath Timing Following PCI Read Snoop5-3L2 Cache Line Invalidate Timing Following PCI Write with Invalidate5-3Snoop5-35-3Asynchronous SRAM L2 Cache Timing5-3Snoop5-3L2 Cache Line Invalidate Timing Following PCI Write with Invalidate5-3Snoop5-3L2 Cache Line Invalidate Timing Following PCI Write with Invalidate5-3Snoop5-35-3Asynchronous SRAM L2 Cache Timing5-3Snoop5-3Snoop5-3Snoop5-3L2 Cache Line Invalidate Timing Following PCI Write With InvalidateSnoop5-3L2 Cache Line Invalidate Timing Following PCI Write With InvalidateSnoop |

| Paragraph<br>Number | Title                                  | Page<br>Number |

|---------------------|----------------------------------------|----------------|

| 5.4.2.2             | L2 Cache Burst Read Line Update Timing |                |

| 5.4.2.3             | Burst Write Timing                     |                |

#### Chapter 6 Memory Interface

| 6.1       | Overview                                 |

|-----------|------------------------------------------|

| 6.2       | Memory Interface Signal Buffering6-2     |

| 6.2.1     | Flow-Through Buffers                     |

| 6.2.2     | Transparent Latch-Type Buffers           |

| 6.2.3     | Registered Buffers                       |

| 6.2.4     | Parity Path Read Control                 |

| 6.3       | DRAM Interface Operation                 |

| 6.3.1     | Supported DRAM Organizations             |

| 6.3.2     | DRAM Power-On Initialization             |

| 6.3.3     | DRAM Interface Timing                    |

| 6.3.3.1   | DRAM Burst Wrap                          |

| 6.3.3.2   | DRAM Latency                             |

| 6.3.4     | DRAM Refresh                             |

| 6.3.4.1   | DRAM Refresh Timing                      |

| 6.3.4.2   | DRAM Refresh and Power Saving Modes      |

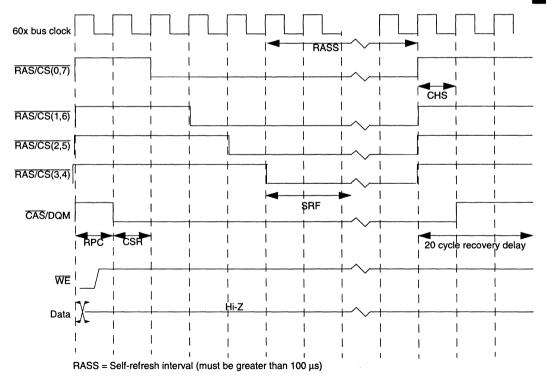

| 6.3.4.2.1 | Self-Refresh in Sleep and Suspend Modes  |

| 6.3.4.2.2 | RTC Refresh in Suspend Mode              |

| 6.4       | SDRAM Interface Operation                |

| 6.4.1     | Supported SDRAM Organizations            |

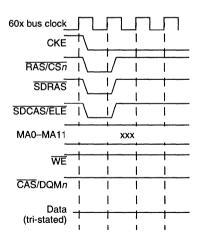

| 6.4.2     | SDRAM Power-On Initialization            |

| 6.4.3     | JEDEC Standard SDRAM Interface Commands  |

| 6.4.4     | SDRAM Interface Timing                   |

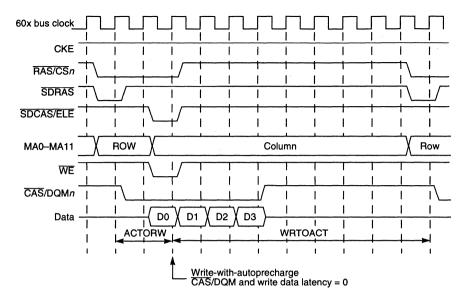

| 6.4.4.1   | SDRAM Burst and Single-Beat Transactions |

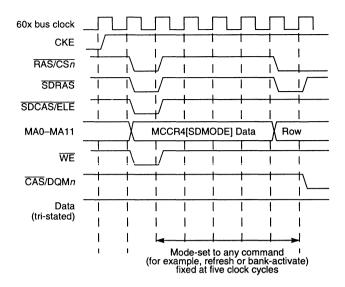

| 6.4.4.2   | SDRAM Mode-Set Command Timing            |

| 6.4.5     | SDRAM Refresh                            |

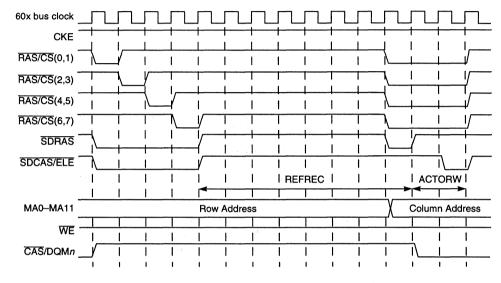

| 6.4.5.1   | SDRAM Refresh Timing                     |

| 6.4.5.2   | SDRAM Refresh and Power Saving Modes     |

| 6.5       | ROM Interface Operation                  |

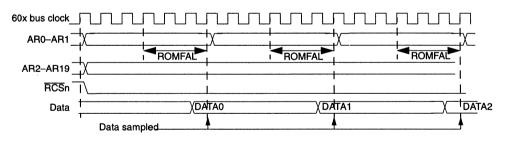

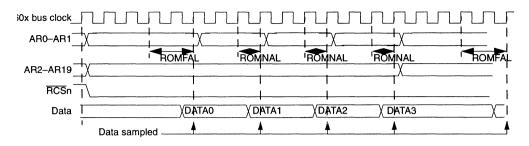

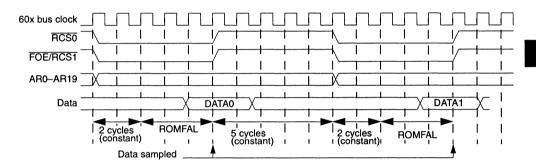

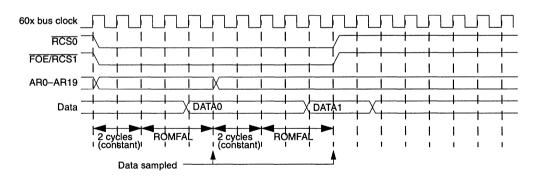

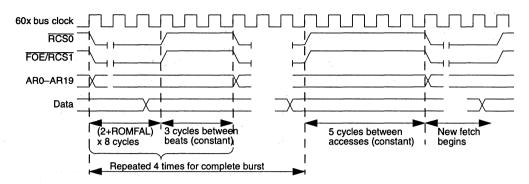

| 6.5.1     | ROM Interface Timing                     |

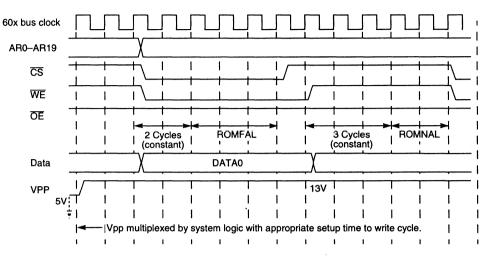

| 6.6       | Flash ROM Interface Operation            |

| 6.6.1     | Flash ROM Interface Timing               |

| 6.6.2     | Writing to Flash ROM                     |

Paragraph Number

#### Title

Page Number

#### Chapter 7 PCI Bus Interface

| 7.1     | PCI Interface Overview                      |

|---------|---------------------------------------------|

| 7.1.1   | The MPC105 as a PCI Master7-2               |

| 7.1.2   | The MPC105 as a PCI Target                  |

| 7.2     | PCI Bus Arbitration                         |

| 7.2.1   | Exclusive Access                            |

| 7.3     | PCI Bus Protocol                            |

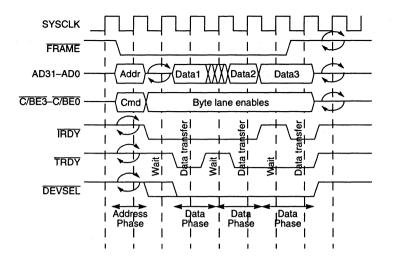

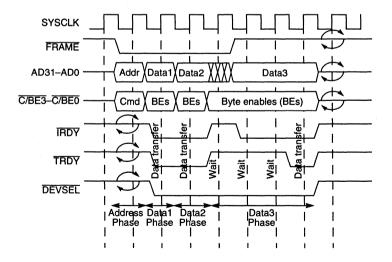

| 7.3.1   | Basic Transfer Control                      |

| 7.3.2   | PCI Bus Commands7-4                         |

| 7.3.3   | Addressing                                  |

| 7.3.4   | Device Selection                            |

| 7.3.5   | Byte Alignment7-8                           |

| 7.3.6   | Bus Driving and Turnaround7-8               |

| 7.4     | PCI Bus Transactions                        |

| 7.4.1   | Read Transactions                           |

| 7.4.2   | Write Transactions                          |

| 7.4.3   | Transaction Termination7-11                 |

| 7.4.3.1 | Master-Initiated Termination7-11            |

| 7.4.3.2 | Target-Initiated Termination7-11            |

| 7.4.4   | Fast Back-to-Back Transactions7-12          |

| 7.4.5   | Configuration Cycles                        |

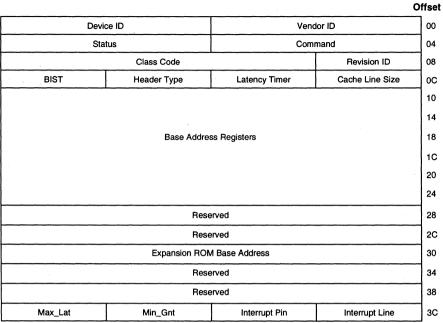

| 7.4.5.1 | The Configuration Space Header7-13          |

| 7.4.5.2 | Accessing the PCI Configuration Space       |

| 7.4.6   | Other Bus Transactions                      |

| 7.4.6.1 | Interrupt Acknowledge7-18                   |

| 7.4.6.2 | Special Cycle                               |

| 7.5     | PCI Error Functions                         |

| 7.5.1   | Parity                                      |

| 7.5.2   | Error Reporting                             |

| 7.6     | MPC105-Implemented PCI Sideband Signals7-21 |

| 7.6.1   | ISA_MASTER7-21                              |

| 7.6.2   | FLSHREQ and MEMACK                          |

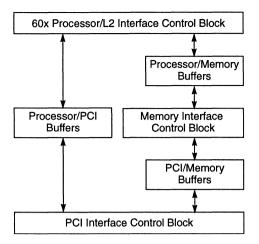

#### Chapter 8 Internal Control

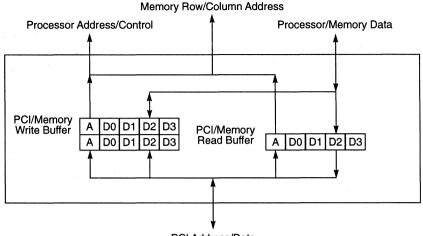

| 8.1     | Internal Buffers                        | 8-1 |

|---------|-----------------------------------------|-----|

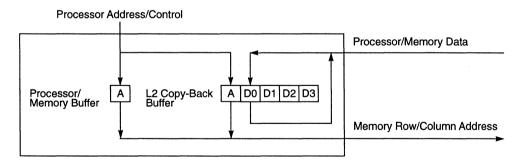

| 8.1.1   | 60x Processor/System Memory Buffers     |     |

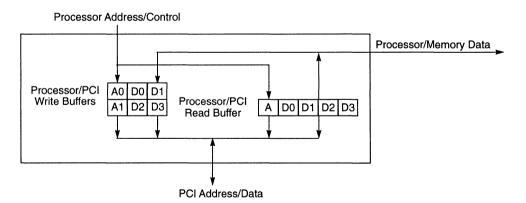

| 8.1.2   | 60x Processor/PCI Buffers               |     |

| 8.1.2.1 | Processor-Read-from-PCI Buffer (PRPRB)  |     |

| 8.1.2.2 | Processor-to-PCI-Write Buffers (PRPWBs) | 8-5 |

|         |                                         |     |

| Paragraph<br>Number | Title                                       | Page<br>Number |

|---------------------|---------------------------------------------|----------------|

| 8.1.3               | PCI/System Memory Buffers                   |                |

| 8.1.3.1             | PCI-Read-from-System-Memory Buffer (PCMRB)  |                |

| 8.1.3.2             | PCI-to-System-Memory-Write Buffers (PCMWBs) |                |

| 8.1.3.2.1           | Speculative PCI Reads from System Memory    |                |

| 8.2                 | Internal Arbitration                        |                |

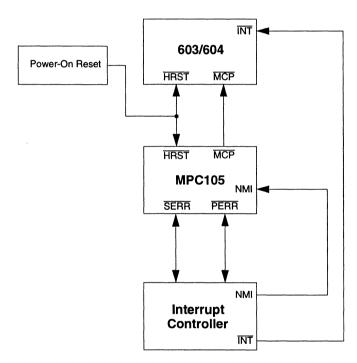

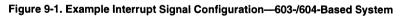

#### Chapter 9 Error Handling

| Priority of Externally-Generated Interrupts | 9-1                         |

|---------------------------------------------|-----------------------------|

| Interrupt And Error Signals                 | 9-2                         |

| System Reset                                | 9-2                         |

| 60x Processor Bus Error Signals             | 9-2                         |

| Machine Check (MCP)                         | 9-3                         |

| Transfer Error Acknowledge (TEA)            | 9-3                         |

| PCI Bus Error Signals                       | 9-3                         |

| System Error (SERR)                         | 9-3                         |

| Parity Error (PERR)                         | 9-4                         |

| Nonmaskable Interrupt (NMI)                 | 9-4                         |

| Error Reporting                             | 9-4                         |

| 60x Processor Interface                     | 9-5                         |

| Flash ROM Write Error                       | 9-5                         |

| Unsupported 60x Bus Error                   | 9-5                         |

| Memory Interface                            | .9-5                        |

| System Memory Read Data Parity Error        | 9-6                         |

| System Memory Select Error                  | 9-6                         |

| L2 Cache Read Data Parity Error             | . 9-6                       |

| PCI Interface                               | 9-6                         |

| Address Parity Error                        | . 9-7                       |

| Data Parity Error                           | . 9-7                       |

| Master-Abort Transaction Termination        | . 9-8                       |

| Cases of Target-Abort Signaled by MPC105    | . 9-8                       |

| Received Target-Abort Error                 | . 9-8                       |

| NMI (Nonmaskable Interrupt)                 | . 9-8                       |

| Interrupt Latencies                         | . 9-9                       |

| Example Signal Connections                  | . 9-9                       |

|                                             | Interrupt And Error Signals |

Paragraph Number

#### Title

Page Number

#### Appendix A Power Management

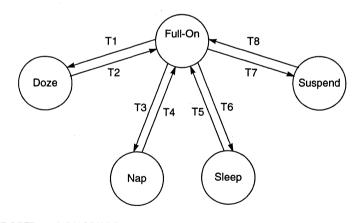

| A.1   | MPC105 Power Modes                              |     |

|-------|-------------------------------------------------|-----|

| A.1.1 | MPC105 Power Mode Transition                    | A-1 |

| A.1.2 | Full-On Mode                                    | A-3 |

| A.1.3 | Doze Mode                                       | A-3 |

| A.1.4 | Nap Mode                                        | A-3 |

| A.1.5 | Sleep Mode                                      | A-4 |

| A.1.6 | Suspend Mode                                    |     |

| A.2   | MPC105 Power Management Support                 | A-6 |

| A.2.1 | Power Management Configuration Register         | A-6 |

| A.2.2 | Clock Configuration                             | A-6 |

| A.2.3 | PCI Address Bus Decoding                        |     |

| A.2.4 | PCI Bus Special-Cycle Operations                | A-7 |

| A.2.5 | Processor Bus Request Monitoring                | A-7 |

| A.2.6 | Memory Refresh Operations in Sleep/Suspend Mode |     |

| A.2.7 | Device Drivers                                  | A-8 |

|       |                                                 |     |

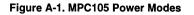

#### Appendix B Bit and Byte Ordering

| B.1 | Big-Endian Mode    | B-1 |

|-----|--------------------|-----|

| B.2 | Little-Endian Mode | B-4 |

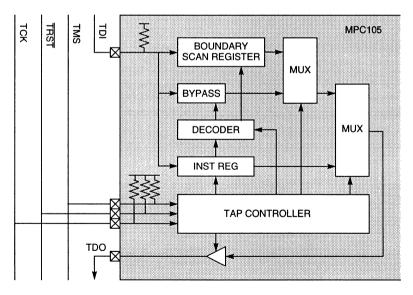

#### Appendix C JTAG/Testing Support

| C.1     | JTAG Interface Description     | C-1 |

|---------|--------------------------------|-----|

| C.1.1   | JTAG Signals                   | C-2 |

| C.1.2   | JTAG Registers and Scan Chains | C-2 |

| C.1.2.1 | Bypass Register                |     |

| C.1.2.2 | Boundary-Scan Registers        |     |

| C.1.2.3 | Instruction Register           |     |

| C.1.3   | TAP Controller                 |     |

#### Appendix D Initialization Example

#### **Glossary of Terms and Abbreviations**

#### INDEX

MOTOROLA

#### Figure Number

#### Title

#### Page Number

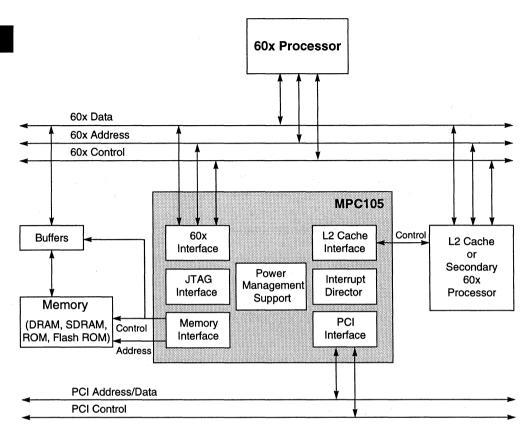

| 1-1  | System Implementation and Block Diagram1-2                             |   |

|------|------------------------------------------------------------------------|---|

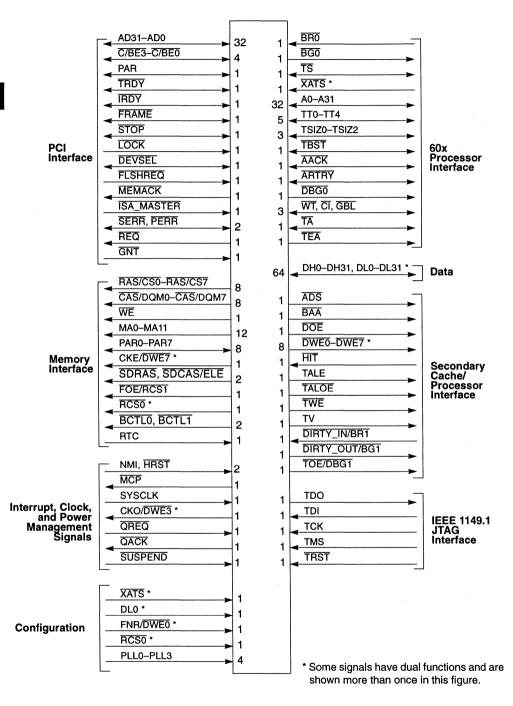

| 2-1  | MPC105 Signal Groupings2-2                                             |   |

| 2-2  | SYSCLK Input with Internal Multiples2-34                               | , |

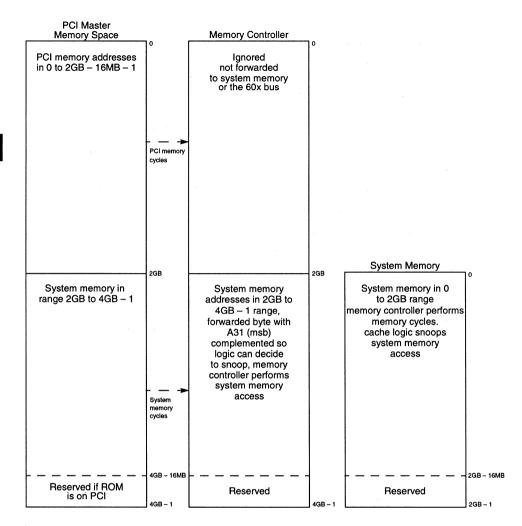

| 3-1  | Address Map A (Contiguous Map)                                         |   |

| 3-2  | Address Map A (Discontiguous Map)                                      | , |

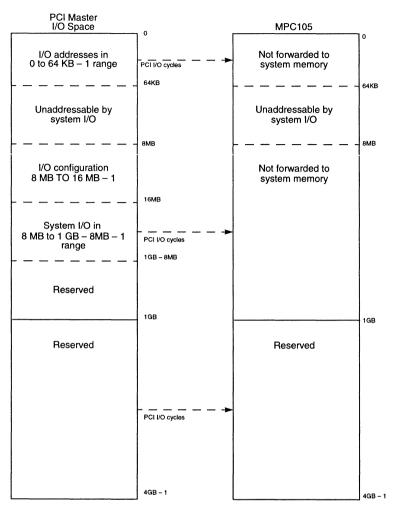

| 3-3  | PCI I/O Map (Address Map A)                                            | j |

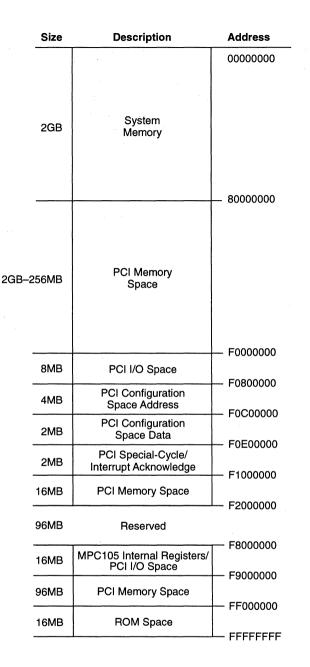

| 3-4  | PCI Memory Map (Map A)                                                 | ) |

| 3-5  | Address Map B 3-8                                                      | 5 |

| 3-6  | MPC105 Configuration Registers                                         | - |

| 3-7  | PCI Command Register                                                   | j |

| 3-8  | PCI Status Register                                                    | 5 |

| 3-9  | Power Management Configuration Register (PMCR)                         | ) |

| 3-10 | Error Enabling Register 1 (ErrEnR1)                                    |   |

| 3-11 | Error Enabling Register 2 (ErrEnR2)                                    | 5 |

| 3-12 | Error Detection Register 1 (ErrDR1)-0xC1                               | Ļ |

| 3-13 | Error Detection register 2 (ErrDR2)-0xC5                               |   |

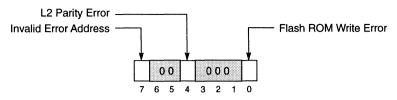

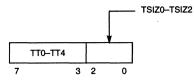

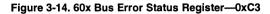

| 3-14 | 60x Bus Error Status Register-0xC3                                     | ĵ |

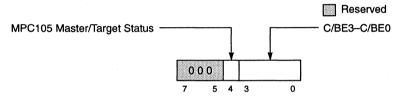

| 3-15 | PCI Bus Error Status Register—0xC7                                     | ) |

| 3-16 | 60x/PCI Error Address Register—0xC8                                    | 1 |

| 3-17 | Memory Starting Address Register 1-0x80                                | ; |

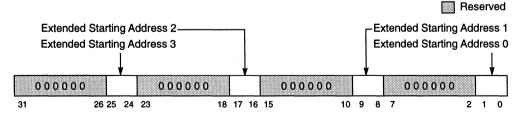

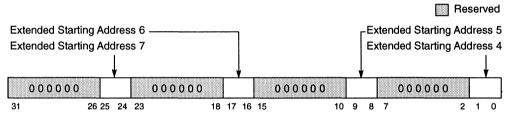

| 3-18 | Memory Starting Address Register 2-0x84                                | ; |

| 3-19 | Extended Memory Starting Address Register 1-0x88                       | 3 |

| 3-20 | Extended Memory Starting Address Register 2-0x8C                       |   |

| 3-21 | Memory Ending Address Register 1-0x90                                  | ) |

| 3-22 | Memory Ending Address Register 2-0x94                                  | ) |

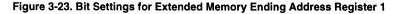

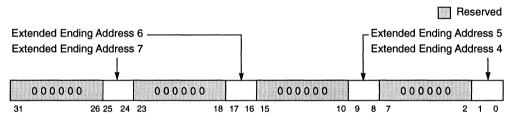

| 3-23 | Bit Settings for Extended Memory Ending Address Register 1             | ) |

| 3-24 | Extended Memory Ending Address Register 2-0x9C                         |   |

| 3-25 | Memory Bank Enable Register—0xA0                                       | 2 |

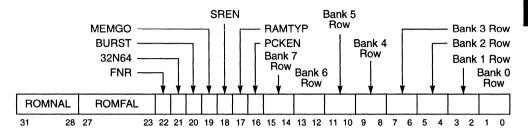

| 3-26 | Memory Control Configuration Register 1 (MCCR1)-0xF03-33               | 3 |

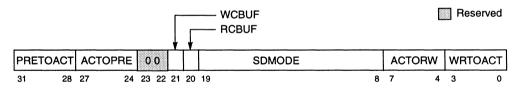

| 3-27 | Memory Control Configuration Register 2 (MCCR2) (RAM Access Time) 3-36 | 5 |

| 3-28 | Memory Control Configuration Register 3 (MCCR3)                        | 1 |

| 3-29 | Memory Control Configuration Register 4 (MCCR4)                        | ) |

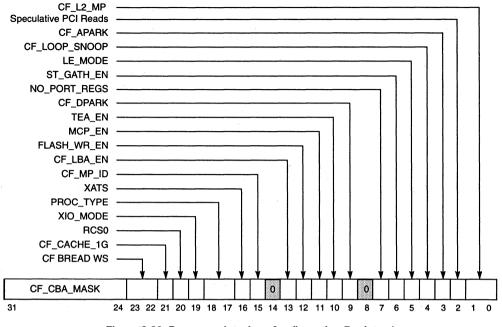

| 3-30 | Processor Interface Configuration Register 1                           | 2 |

| 3-31 | Processor Interface Configuration Register 2                           | 5 |

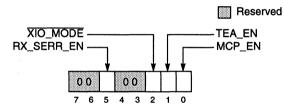

| 3-32 | Alternate OS-Visible Parameters Register 1                             | ) |

| 3-33 | Alternate OS-Visible Parameter Register 2                              | l |

|      |                                                                        |   |

| Figure<br>Number | Title                                                                         | Page<br>Number |

|------------------|-------------------------------------------------------------------------------|----------------|

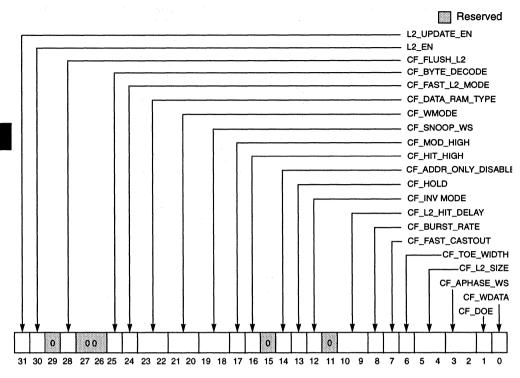

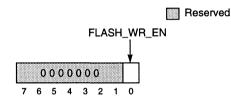

| 3-34             | External Configuration Register 1-0x8000_0092                                 |                |

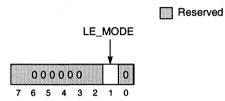

| 3-35             | External Configuration Register 2-0x8000_081C                                 |                |

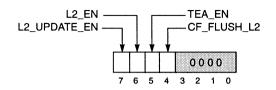

| 3-36             | External Configuration Register 3-0x8000_0850                                 |                |

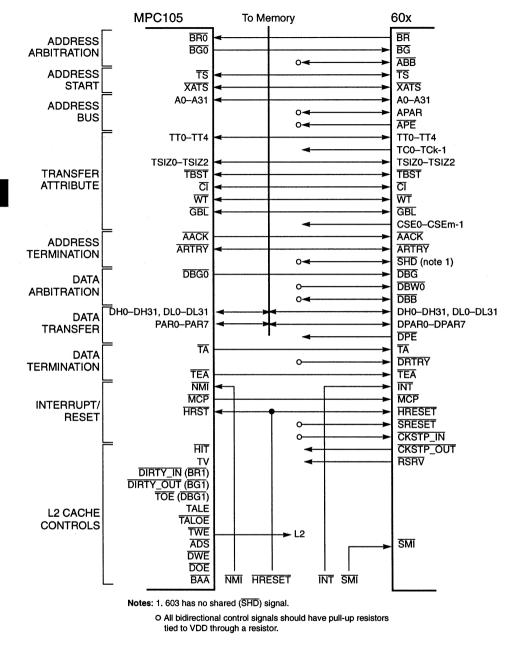

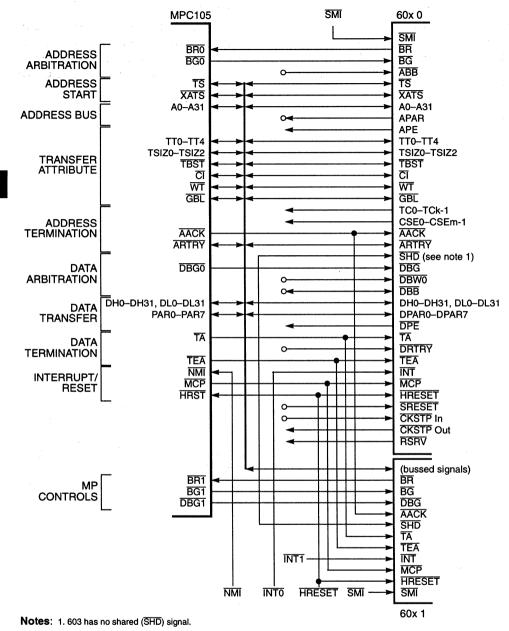

| 4-1              | Single-Processor Configuration with Optional L2 Cache                         |                |

| 4-2              | Multiprocessor Configuration                                                  |                |

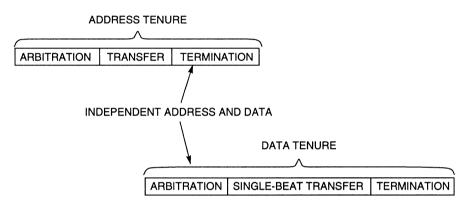

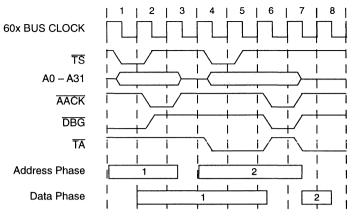

| 4-3              | Overlapping Tenures on the 60x Bus for a Single-Beat Transfer                 |                |

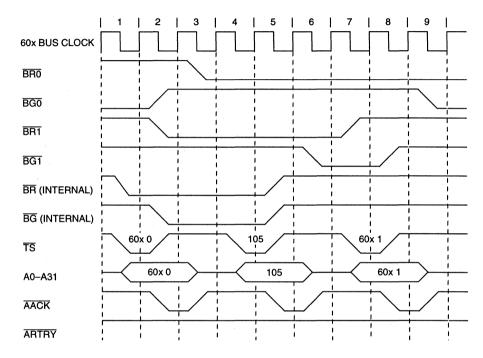

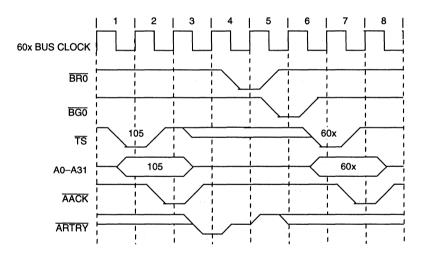

| 4-4              | Address Bus Arbitration with Dual Processors                                  |                |

| 4-5              | Address Pipelining                                                            |                |

| 4-6              | Snooped Address Transaction with ARTRY and L1 Cache Copy-Bac                  |                |

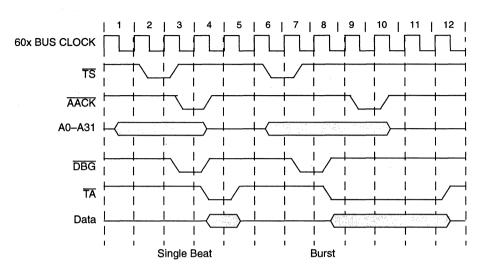

| 4-7              | Single-Beat and Burst Data Transfers                                          |                |

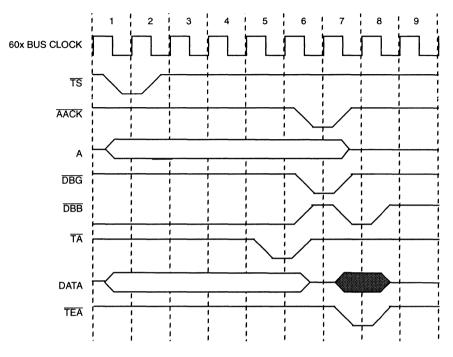

| 4-8              | Data Tenure Terminated by Assertion of TEA                                    |                |

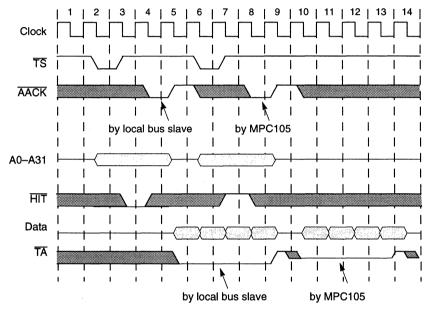

| 4-9              | 60x Bus Slave Transaction                                                     |                |

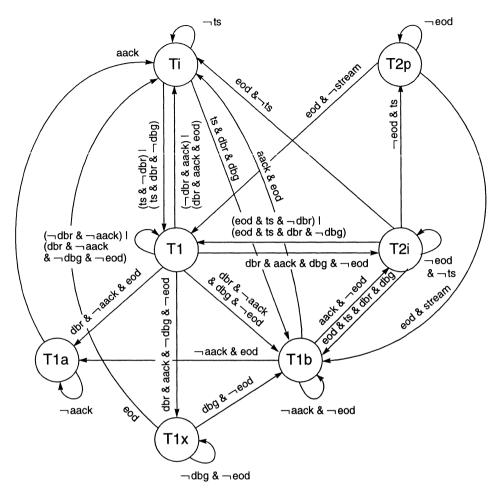

| 4-10             | 60x Bus State Diagram                                                         |                |

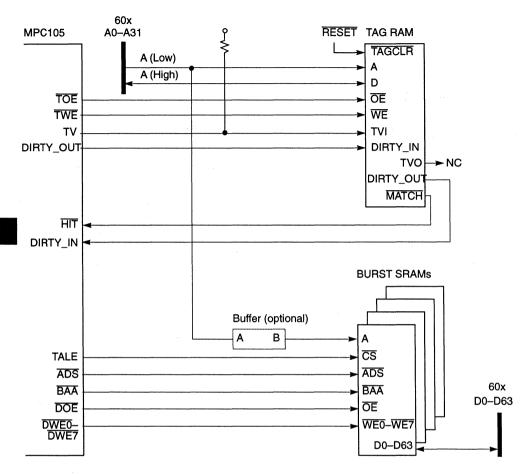

| 5-1              | MPC105 with Write-Back L2 Cache                                               |                |

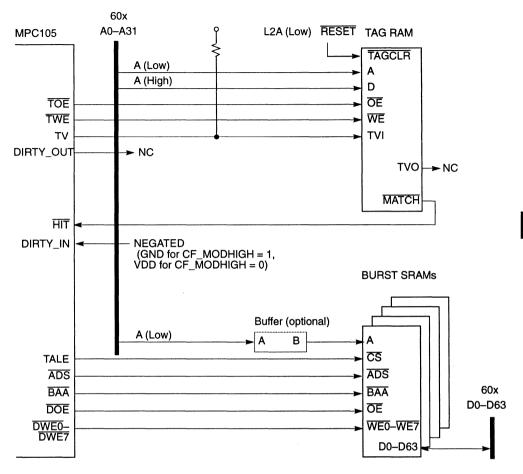

| 5-2              | MPC105 with Write-Through Cache                                               |                |

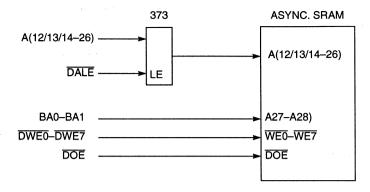

| 5-3              | Asynchronous SRAM Interface                                                   |                |

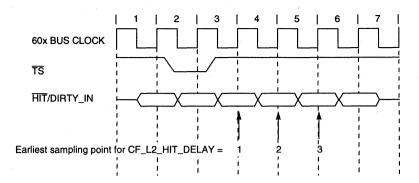

| 5-4              | HIT and DIRTY_IN Delay Configuration                                          |                |

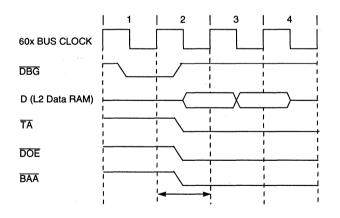

| 5-5              | Data Access Timing with CF_DOE = 0                                            |                |

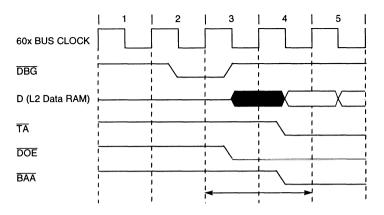

| 5-6              | Data Access Timing with CF_DOE = 1                                            |                |

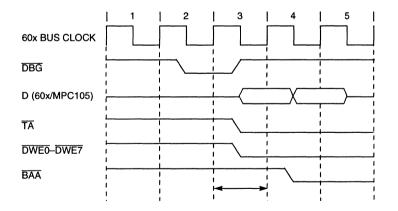

| 5-7              | Write Data Setup Timing with CF_WDATA = 0                                     |                |

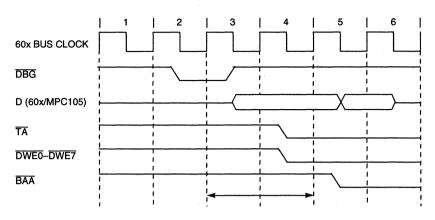

| 5-8              | Write Data Setup Timing with CF_WDATA = 1                                     |                |

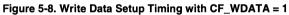

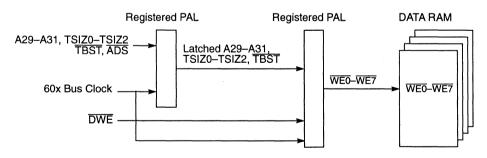

| 5-9              | External Byte Decode Logic Requiring CF_WMODE =1                              |                |

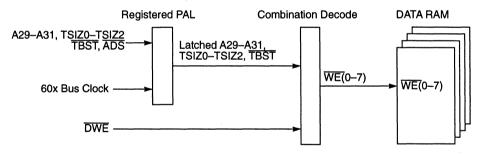

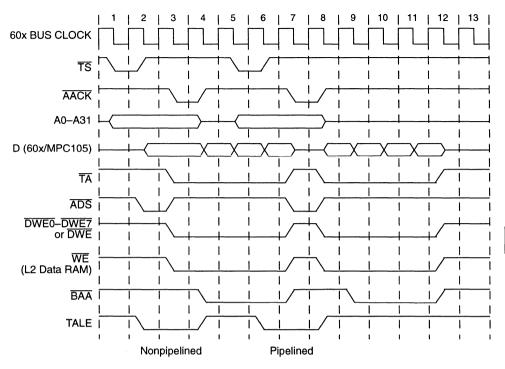

| 5-10             | Pipelined and Nonpipelined Operations with CF_WMODE = 1                       |                |

| 5-11             | External Byte Decode Logic Requiring CF_WMODE = 2                             |                |

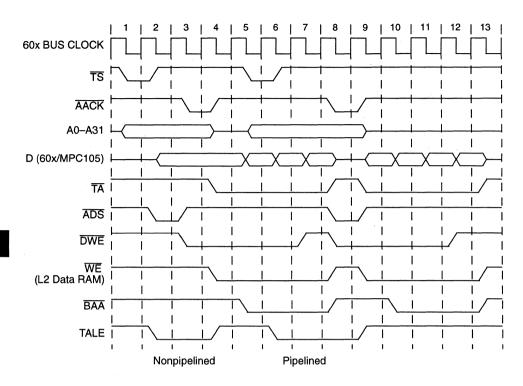

| 5-12             | Pipelined and Nonpipelined Operations with CF_WMODE = 2                       |                |

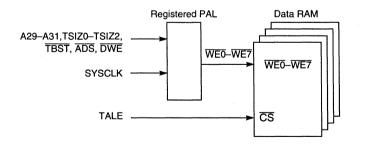

| 5-13             | External Byte Decode Logic Requiring CF_WMODE = 3                             |                |

| 5-14             | Pipelined and Nonpipelined Operations with CF_WMODE = 3                       |                |

| 5-15             | Timing Diagram Legend                                                         |                |

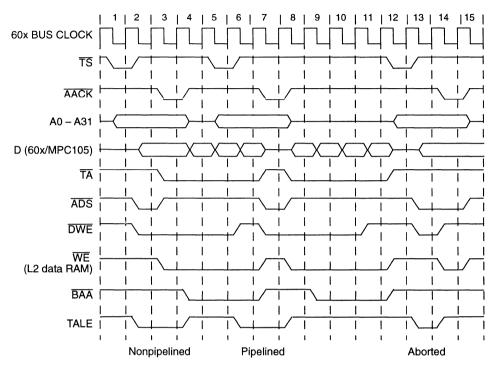

| 5-16             | L2 Cache Read Hit Timing with $CF_DOE = 0$                                    |                |

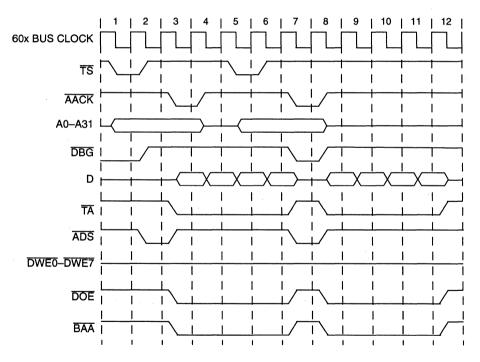

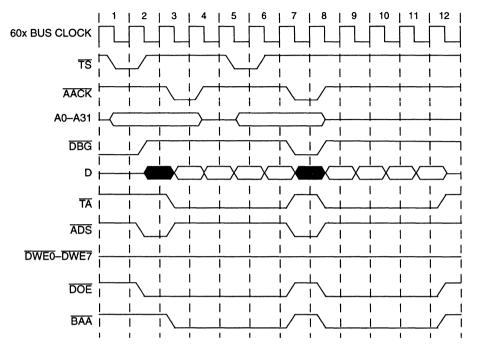

| 5-17             | L2 Cache Read Hit Timing with CF_DOE = 1                                      |                |

| 5-18             | L2 Cache Write Hit Timing                                                     |                |

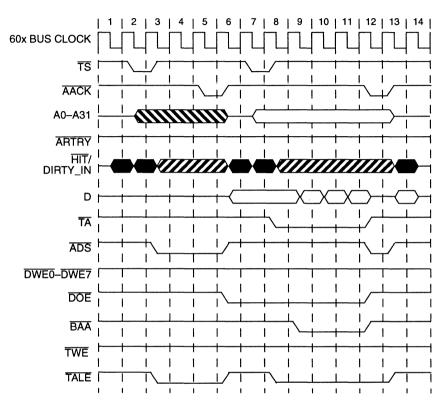

| 5-19<br>5-20     | L2 Cache Line Update Timing                                                   |                |

| 5-20<br>5-21     | L2 Cache Line Cast-Out Timing<br>L2 Cache Hit Timing Following PCI Read Snoop |                |

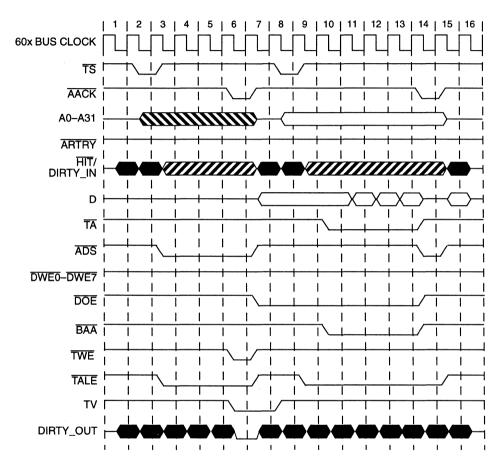

| 5-21             | Modified L2 Cache Line Push Timing Following PCI Write Snoop                  |                |

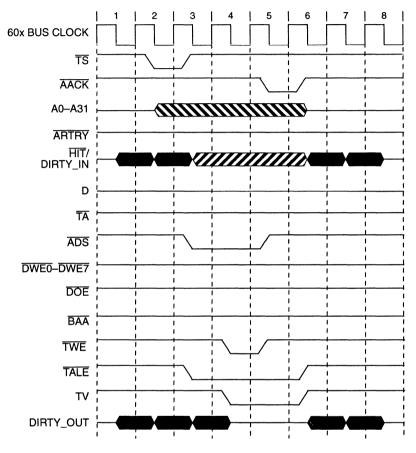

| 5-22             | L2 Cache Line Invalidate Timing Following PCI Write with Invalidate           |                |

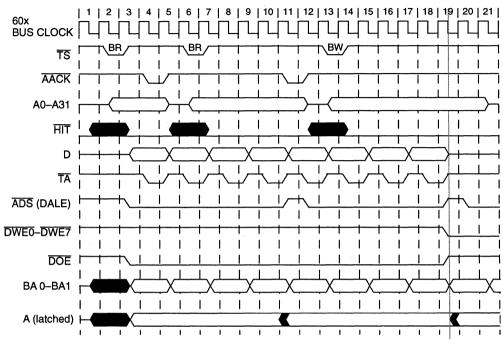

| 5-23             | L2 Cache Burst Read Timing with CF_DOE = 0                                    |                |

| 5-24<br>5-25     | L2 Cache Burst Read Timing with CF_DOE = 0                                    |                |

| 5-26             | L2 Cache Burst Read Line Update Timing with CF_WDATA = 0                      |                |

| 5-27             | L2 Cache Burst Read Line Update Timing with CF_WDATA = 0                      |                |

| 5-28             | L2 Cache Burst Write Timing with $CF_WDATA = 0.1$                             |                |

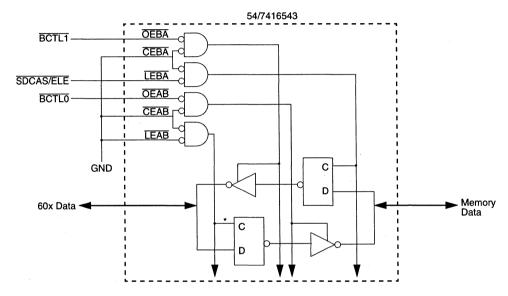

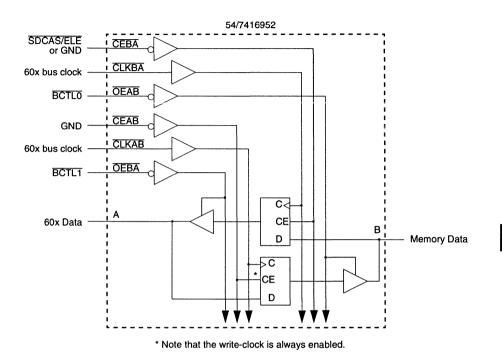

| 5-28<br>6-1      | Transparent Latch-Type Buffer                                                 |                |

| 6-2              | Registered Buffer                                                             |                |

| Figure<br>Number | Title                                                           | Page<br>Number |

|------------------|-----------------------------------------------------------------|----------------|

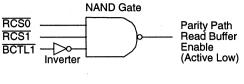

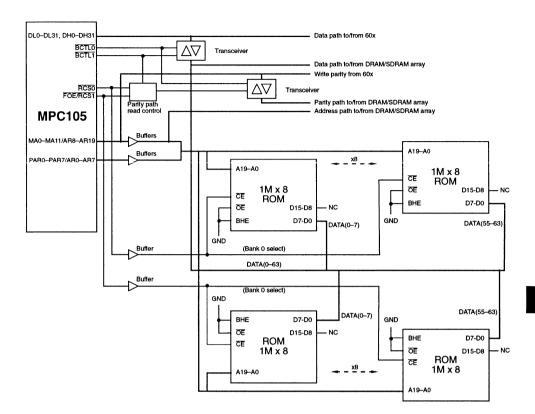

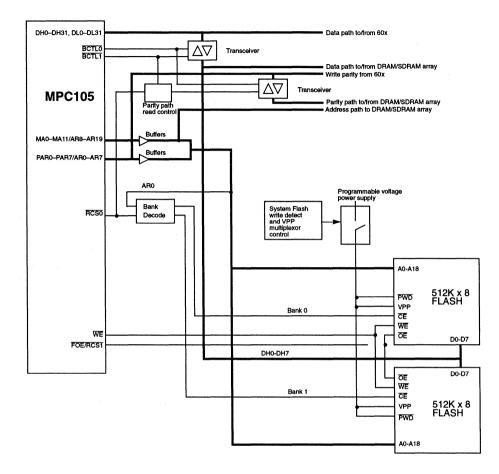

| 6-3              | Parity Path Read Control Logic for ROM-Based Systems            | 6-6            |

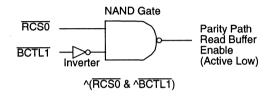

| 6-4              | Parity Path Read Control Logic for Flash ROM-Based Systems      | 6-6            |

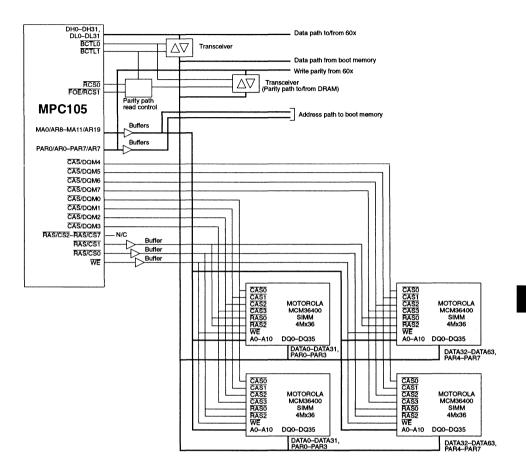

| 6-5              | 16-Mbyte DRAM System with Parity                                |                |

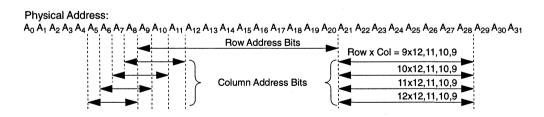

| 6-6              | DRAM Address Multiplexing-64-Bit Data Bus Mode                  | 6-8            |

| 6-7              | DRAM Address Multiplexing-32-Bit Data Bus Mode                  |                |

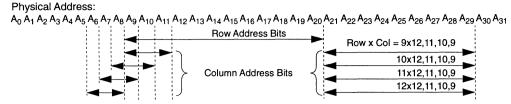

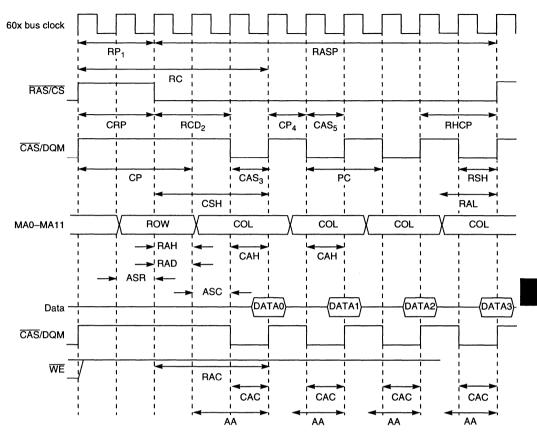

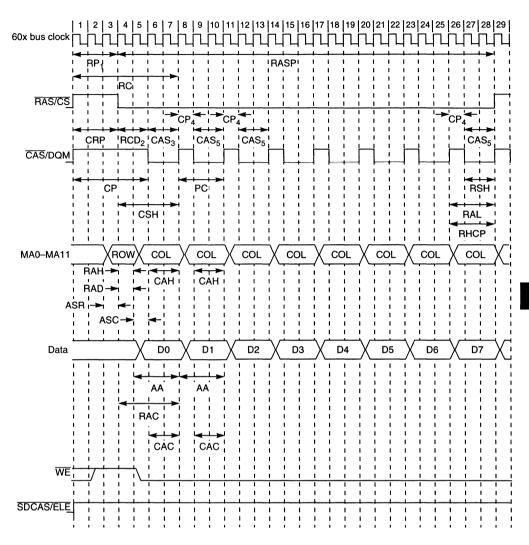

| 6-8              | DRAM Single-Beat Read Timing                                    |                |

| 6-9              | DRAM Burst-of-Four Read Timing                                  |                |

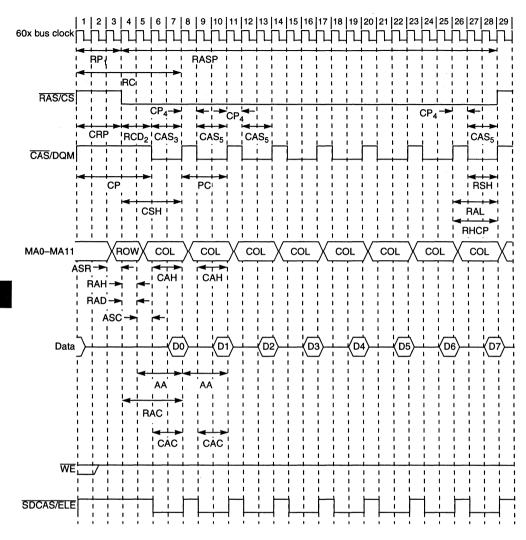

| 6-10             | DRAM Burst-of-Eight Read Timing                                 |                |

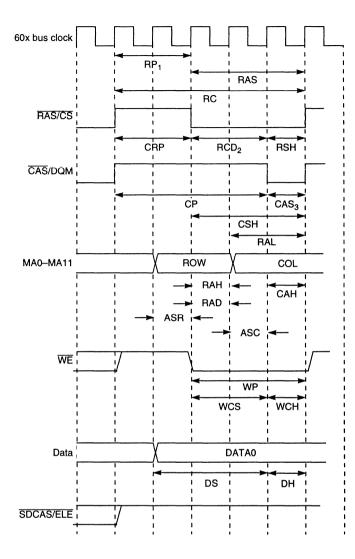

| 6-11             | DRAM Single-Beat Write Timing                                   |                |

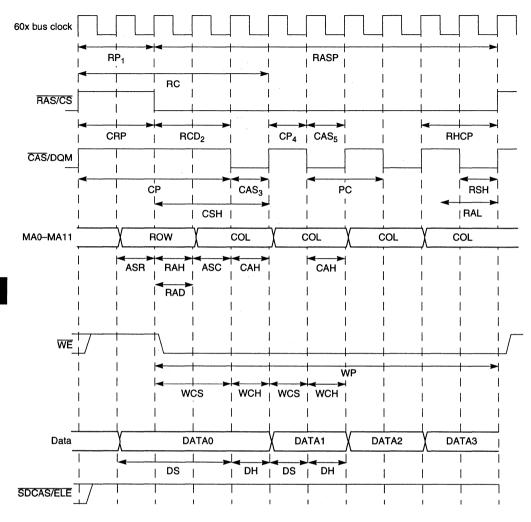

| 6-12             | DRAM Burst-of-Four Write Timing                                 |                |

| 6-13             | DRAM Burst-of-Eight Write Timing                                |                |

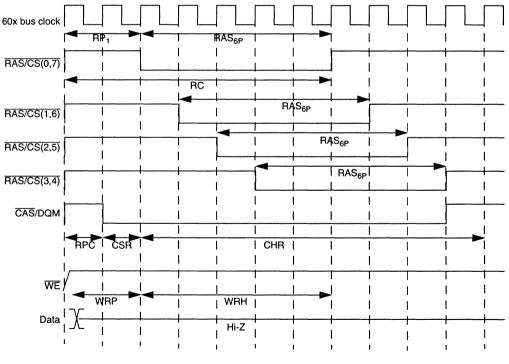

| 6-14             | DRAM Bank Staggered CBR Refresh Timing                          |                |

| 6-15             | DRAM Self-Refresh Timing in Sleep and Suspend Modes             |                |

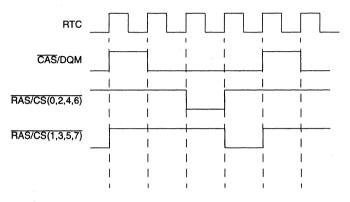

| 6-16             | Suspend Mode—Real Time Clock Refresh                            |                |

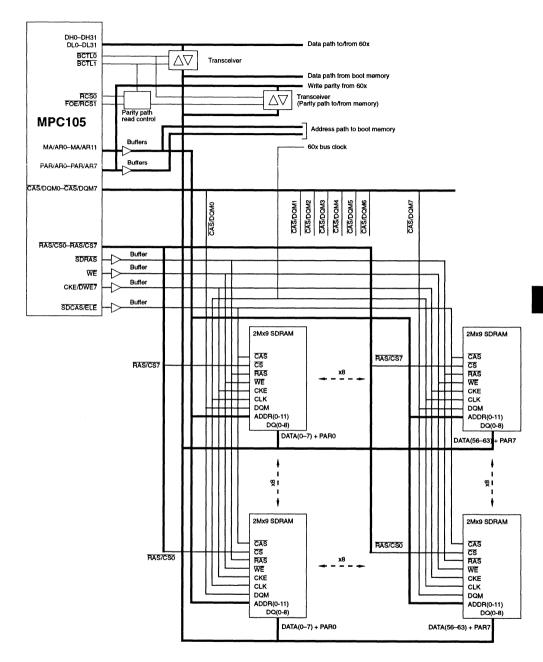

| 6-17             | 128-Mbyte SDRAM System with Parity                              |                |

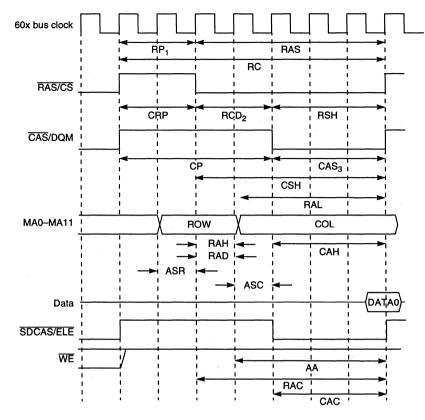

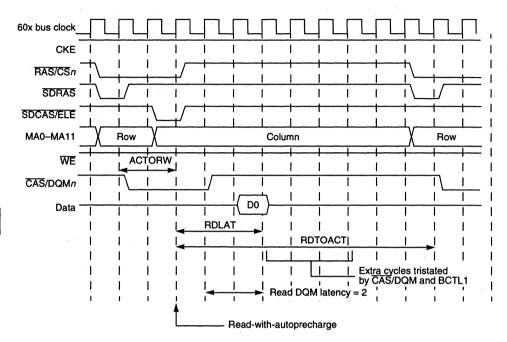

| 6-18             | SDRAM Single-Beat Read Timing                                   |                |

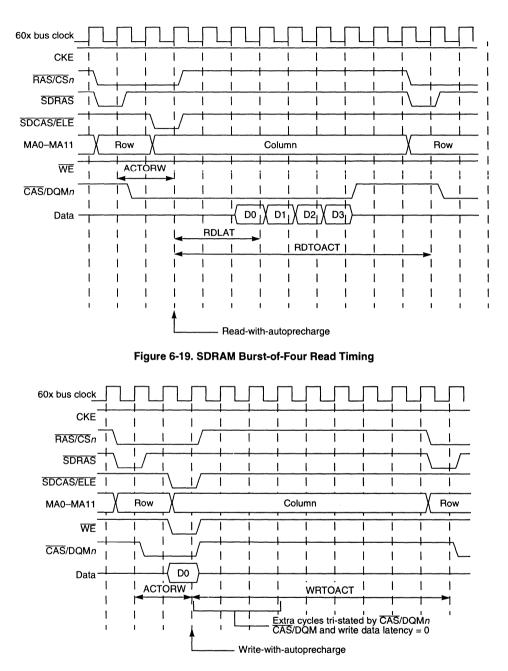

| 6-19             | SDRAM Burst-of-Four Read Timing                                 |                |

| 6-20             | SDRAM Single-Beat Write Timing                                  |                |

| 6-21             | SDRAM Burst-of-Four Write Timing                                |                |

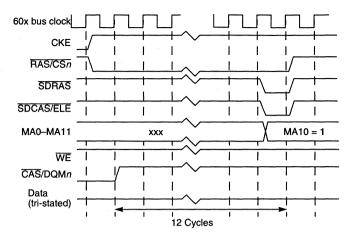

| 6-22             | SDRAM Mode-Set Command Timing                                   |                |

| 6-23             | SDRAM Bank-Staggered CBR Refresh Timing                         |                |

| 6-24             | SDRAM Self-Refresh Entry Timing                                 |                |

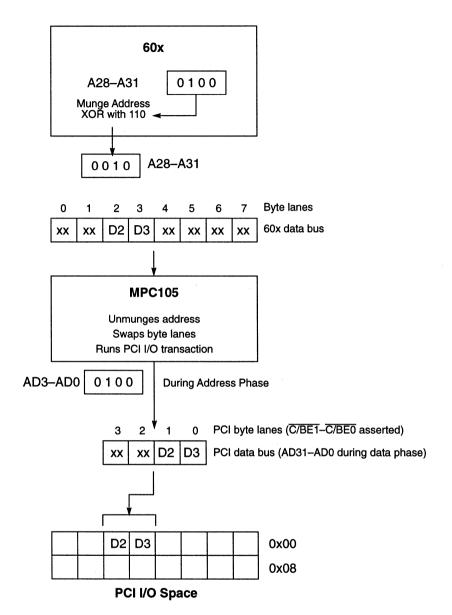

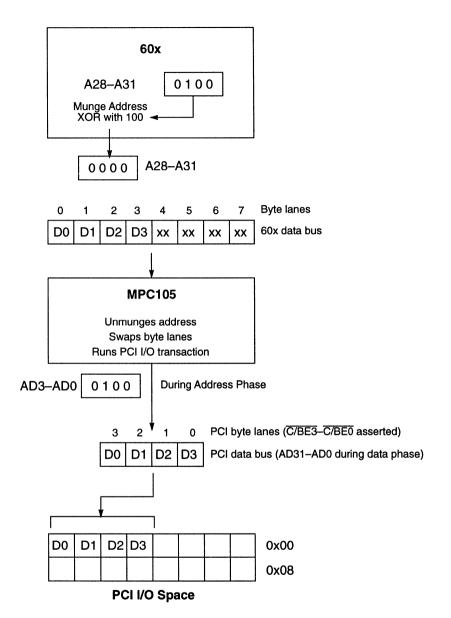

| 6-25             | SDRAM Self-Refresh Exit Timing                                  |                |