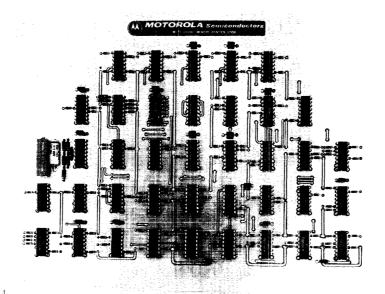

MOTOROLA Semiconductor Products Inc.

# MECL SYSTEM DESIGN HANDBOOK

Second Edition

Compiled by the Computer Applications Engineering Department

#### Author

William R. Blood Jr.

#### Contributors

Jon M. DeLaune Jerry E. Prioste

#### **Editor**

Edmund C. Tynan Jr.

Circuit diagrams external to Motorola products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information in this book has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola Inc. or others.

MECL, MECL I, MECL II, MECL III, MECL 10,000, MTTL, MTTL III, Micro T, and MDTL are trademarks of Motorola Inc.

Second Edition December, 1972

©MOTOROLA INC., 1972

#### **PREFACE**

In response to the demand for higher performance systems, engineers are looking at digital integrated circuit families which are faster than the popular TTL and DTL types. Motorola's Emitter Coupled Logic (MECL) circuits have the characteristics to meet the performance requirements for present and future systems. MECL 10,000 is ideal for computer and communications systems, while state-of-the-art instrumentation equipment uses MECL III.

As circuit speeds increase, wiring rules and system design techniques must be adjusted accordingly. Designing with MECL is no more difficult than designing high performance equipment with slower forms of logic. High performance system design for any form of logic, however, does require an understanding of the factors which affect system performance. In fact, many of the MECL features such as transmission line drive capability, complementary outputs, Wired-OR, and versatile logic functions can add as much to system performance as the short propagation delays and high toggle rates.

In the past, several articles and application notes have been written about MECL circuits and systems. However, there was a need for a book which would completely define MECL operation. This book has been written to give the designer the information to establish design rules for his own high performance systems.

The information in this book is based on equations derived from electronic theory, laboratory tests, and inputs from MECL users. All of the rules and tables are for conservative system design with MECL circuits. It is important to realize that the circuits can operate properly under conditions much more adverse than suggested in this book.

In addition to the technical contributors, Jon DeLaune and Jerry Prioste, the author would like to thank Lloyd Maul, Mike Lee, Reg Hamer, Jim Hively, Howard Gnauden, Don Murray, Tom Balph, and Colin Crook whose knowledge of MECL has added to the completeness and accuracy of this book. Finally, great appreciation is due to the many technicians, engineers, and managers who took their valuable time to read all or part of this book as it was developed.

This edition differs from the first primarily because of the addition of chapters 9 and 10, and a brief appendix describing some of the hardware and components available for MECL Systems. The few minor errors discovered in the first edition have also been corrected. The author wishes to thank George Adams for preparing Chapter 10 in this edition.

# **Table of Contents**

| Introduction vi                           |    |

|-------------------------------------------|----|

| What Is MECL? vi                          |    |

| History of MECL vi                        |    |

| Why Use MECL? vii                         |    |

| The Advantages of MECLviii                |    |

| MECL Areas of Application ix              |    |

| Purpose of This Book x                    |    |

| CHAPTER 1 – MECL Families                 | 1  |

| The Basic MECL Gate                       | 1  |

| Noise Margin                              | 5  |

| MECL Circuit Types                        | 6  |

| MECL Flip-Flops                           | 8  |

| Operation of Flip-Flop                    | 8  |

| MECL Family Comparison                    | 0  |

| CHAPTER 2 – Using MECL                    | 5  |

|                                           | 5  |

| A. Logic Design Considerations            | 5  |

| B. System Layout Considerations           | 9  |

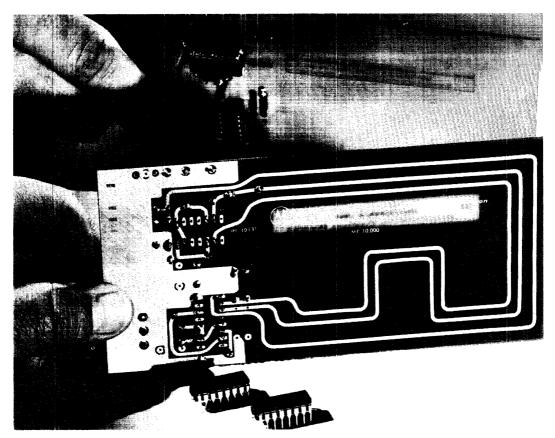

| C. Circuit Board Layout Techniques        | 0  |

| D. Backplane Wiring                       | 21 |

| E. System Considerations                  | 22 |

| MECL 10,000 Design Rules                  | 23 |

|                                           | 23 |

| B. Printed Circuit Card Layout Techniques | 23 |

|                                           | 4  |

| D. Backplane and Loading Considerations   | 4  |

| E. System Distribution and Grounding      | 25 |

| F. Loading Rules for MECL 10,000          | 25 |

| MECL III Design Rules                     | 9  |

|                                           | 9  |

| · ·                                       | 0  |

|                                           | 0  |

|                                           | 1  |

| E. Testing MECL III                       | 1  |

|                                           | 5  |

|                                           | 7  |

|                                           | 2  |

|                                           | 3  |

|                                           | 6  |

|                                           | 2  |

| Transmission Line Comparison              | 3  |

| Wirewrapped Cards                         | 5  |

| CHAPTER 4 – System Interconnections       | 7  |

| ·                                         | 9  |

|                                           | 9  |

|                                           | 4  |

|                                           | 0  |

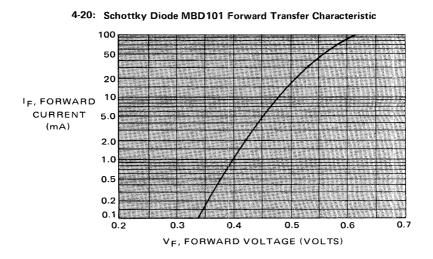

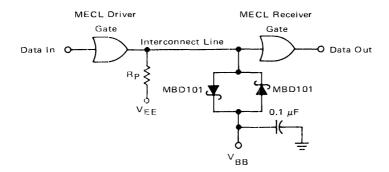

| Schottky Diode Termination                | 1  |

|                                           | 6  |

| Twisted Pair Cable, Driven Single-Ended   | 3  |

| CHAPTER 5 — Power Distribution                                                  | 87  | 7      |

|---------------------------------------------------------------------------------|-----|--------|

| System Power Calculations                                                       | 88  | 3      |

| Power Supply Considerations                                                     | 91  |        |

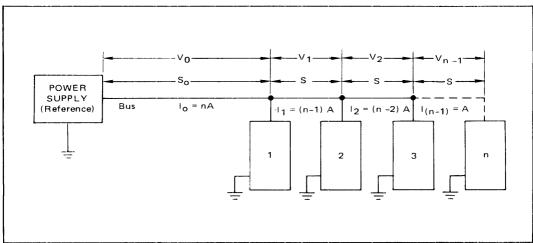

| System Power Distribution                                                       | 92  | 2      |

| Backplane Power Distribution                                                    | 95  | 5      |

| On-Card Power Distribution                                                      |     | ·<br>) |

| V <sub>TT</sub> Termination Voltage Distribution                                |     | )      |

| CHAPTER 6 — Thermal Considerations                                              |     | 1      |

| MECL Integrated Circuit Heat Transfer                                           |     |        |

| MECL DC Thermal Characteristics                                                 |     |        |

|                                                                                 |     |        |

| Heat Dissipation Techniques                                                     |     |        |

| Mounting Techniques                                                             |     |        |

| CHAPTER 7 — Transmission Line Theory                                            |     |        |

| Transmission Line Design Information, With Examples                             | 115 | j      |

| Signal Propagation Delay for Microstrip and Strip Lines With                    |     |        |

| Distributed or Lumped Loads                                                     | 123 | ;      |

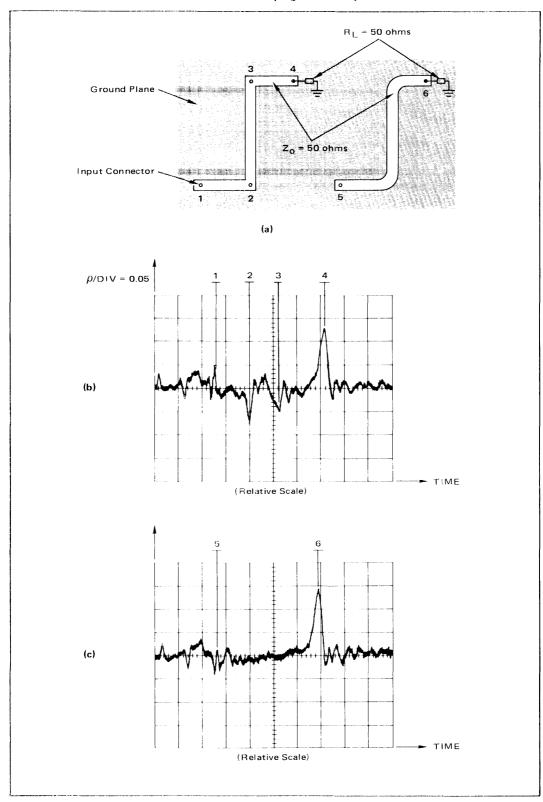

| Microstrip Transmission Line Techniques, Evaluated Using TDR                    | 100 |        |

| Measurements, With Examples                                                     | 126 | ,      |

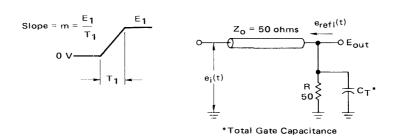

| The Effect of Loading on a Parallel Terminated Transmission Line, With Examples | 130 | ,      |

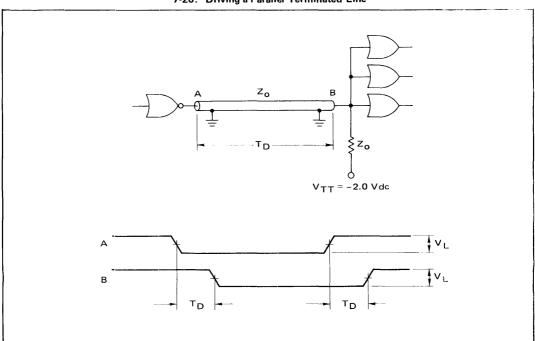

| Analysis: Series Terminated Lines Compared to Parallel Terminated               | 133 |        |

| Lines, With Example                                                             | 146 |        |

| Analysis of Series Damping Terminations                                         |     |        |

| Bibliography                                                                    |     |        |

|                                                                                 |     |        |

| CHAPTER 8 – MECL Applications                                                   |     |        |

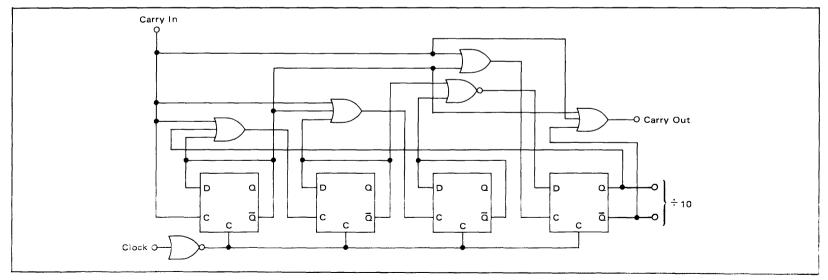

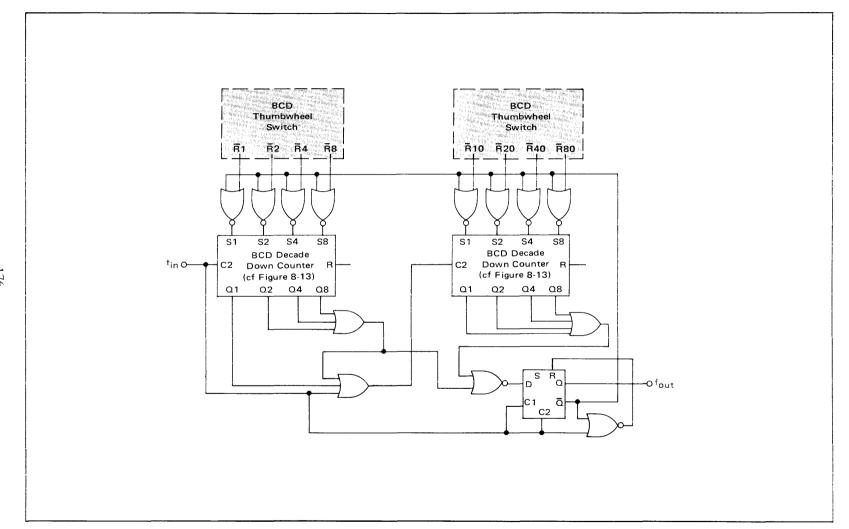

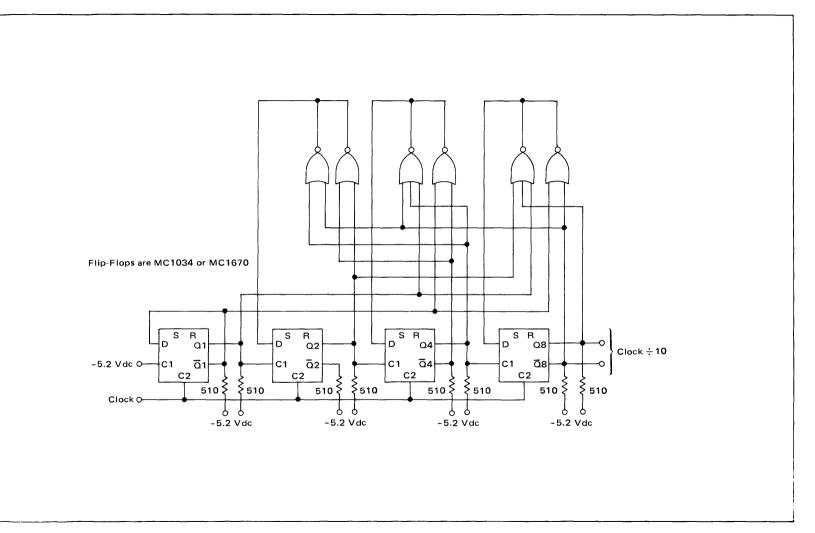

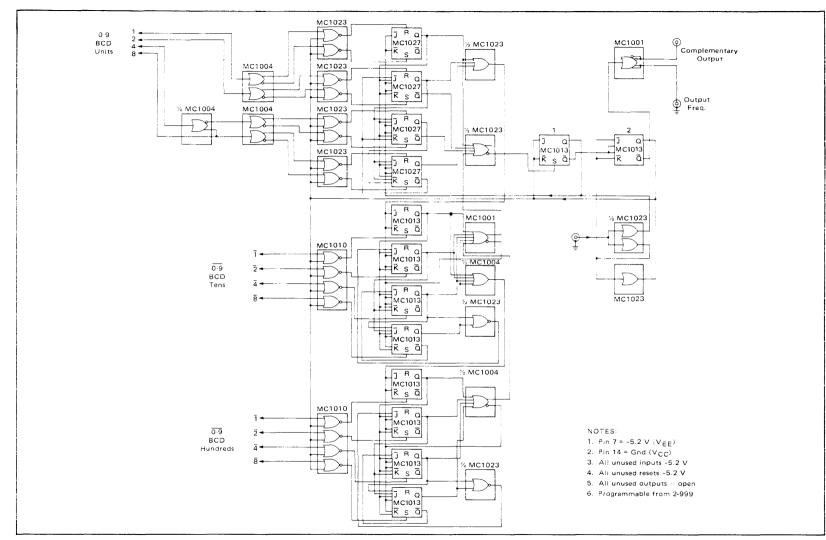

| Counters                                                                        |     |        |

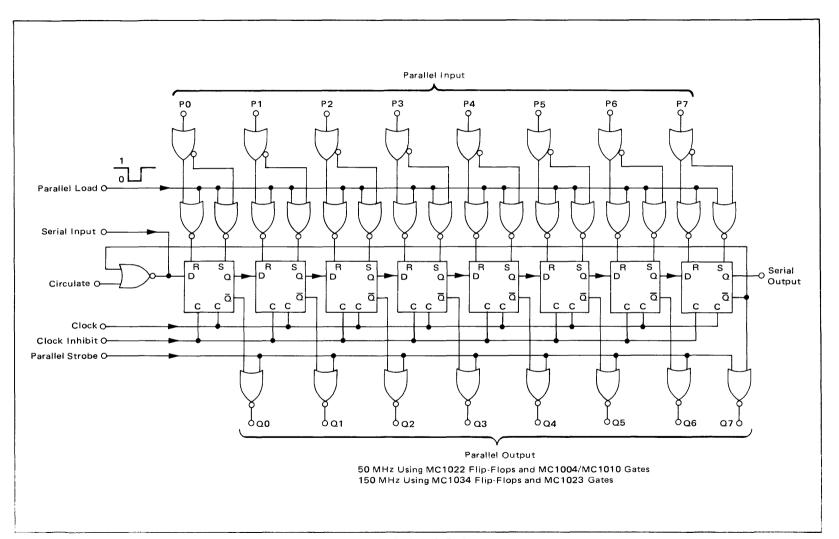

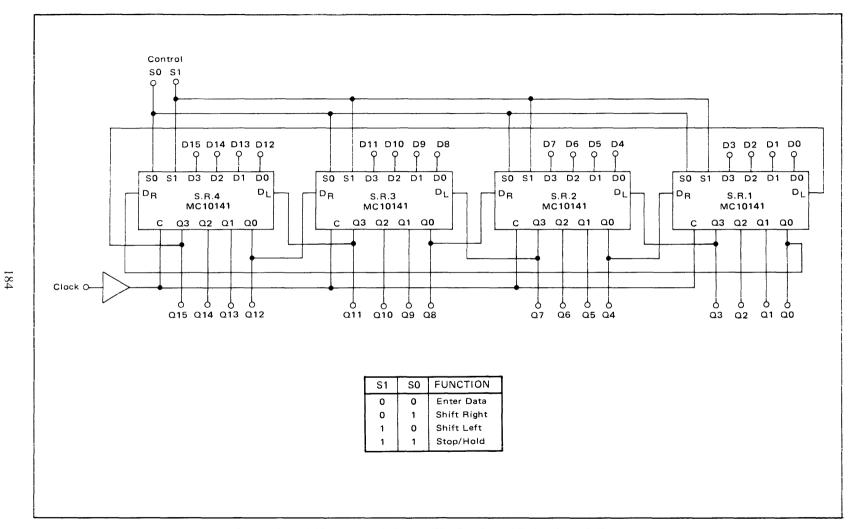

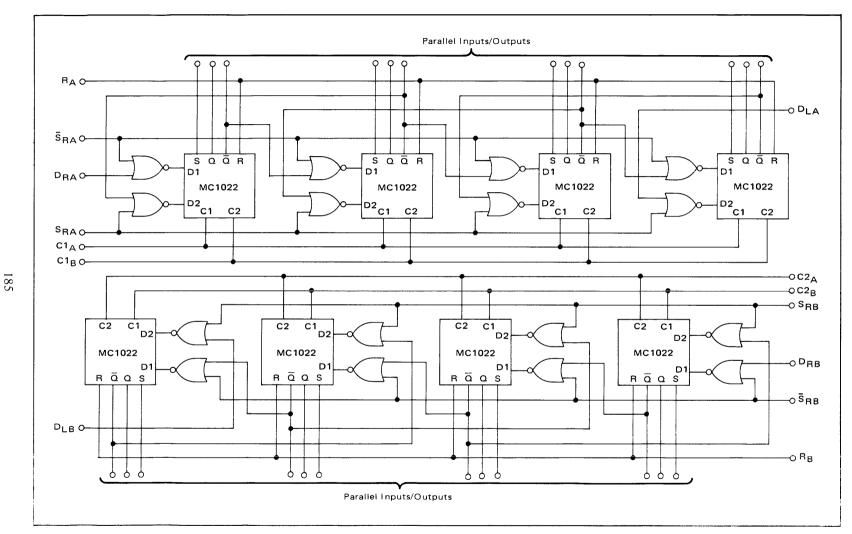

| Shift Registers                                                                 |     |        |

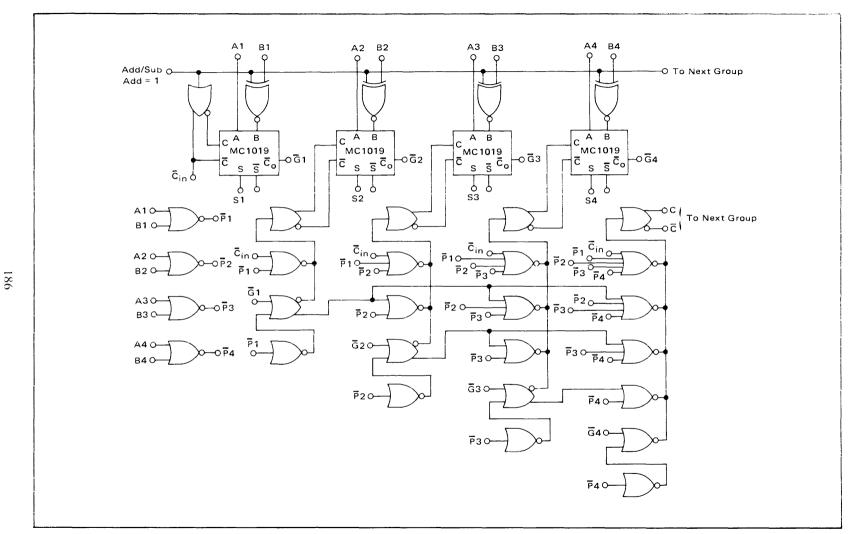

| Adders                                                                          |     |        |

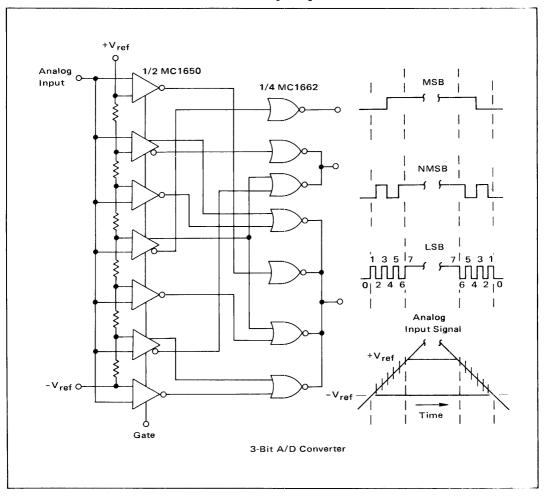

| Code Converters                                                                 |     |        |

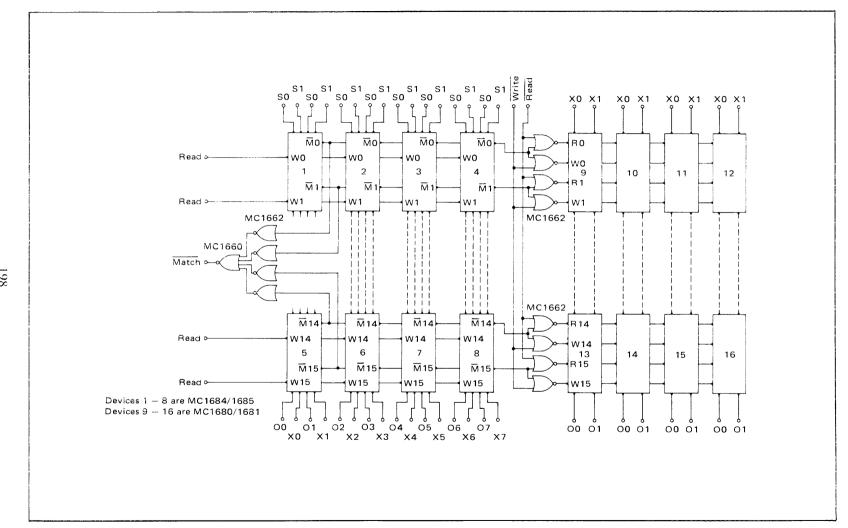

| Memories                                                                        |     |        |

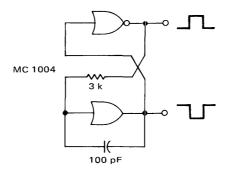

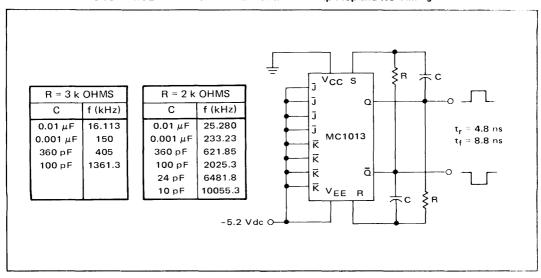

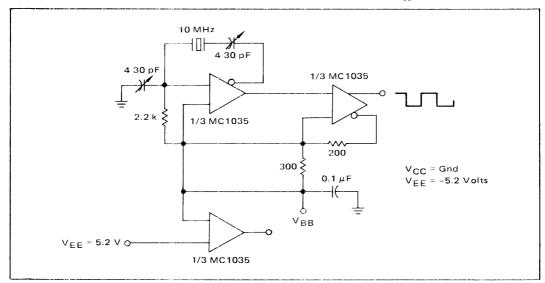

| Oscillators                                                                     |     |        |

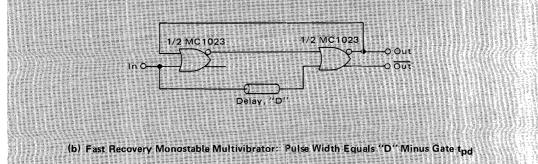

| One-Shot Multivibrators                                                         |     |        |

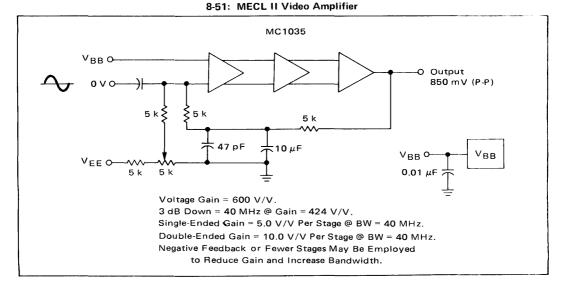

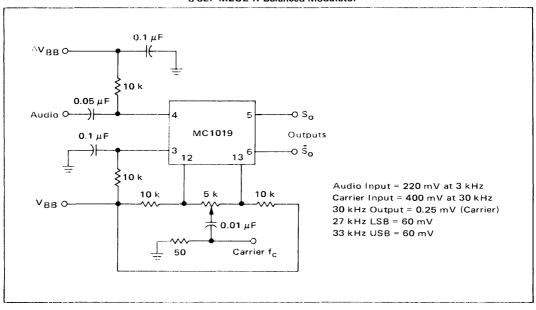

| Linear Applications                                                             |     |        |

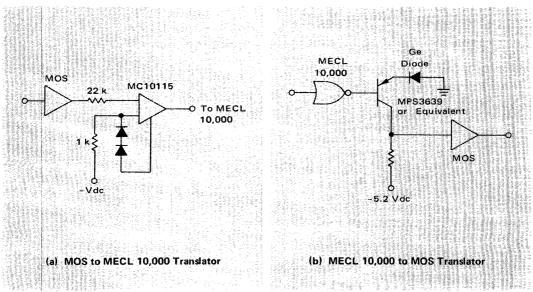

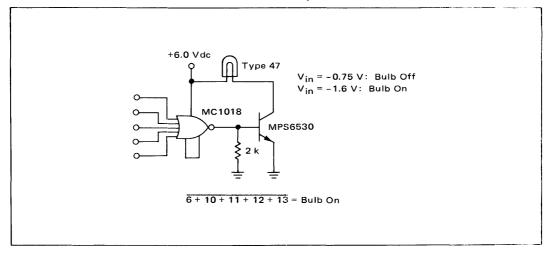

| Translators                                                                     |     |        |

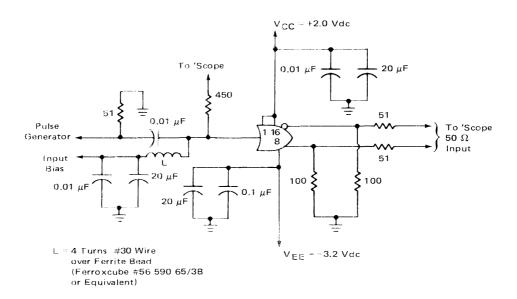

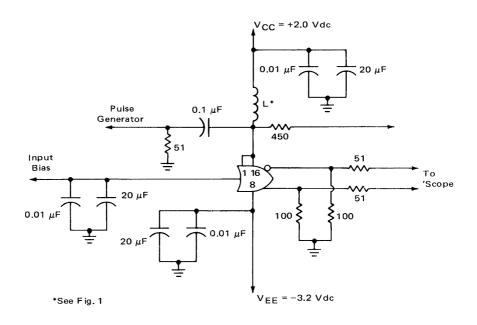

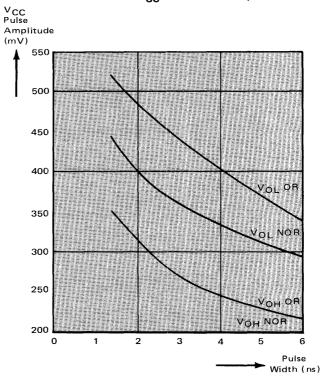

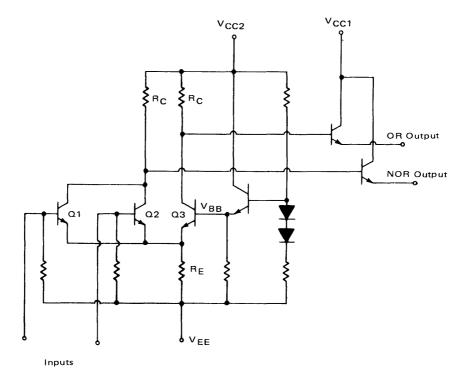

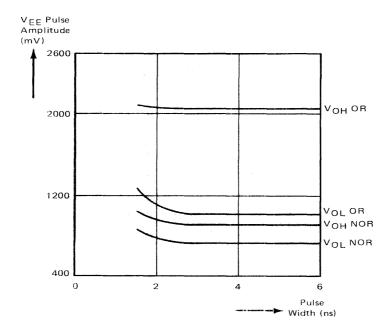

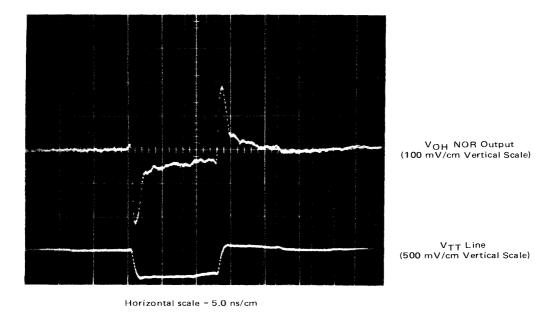

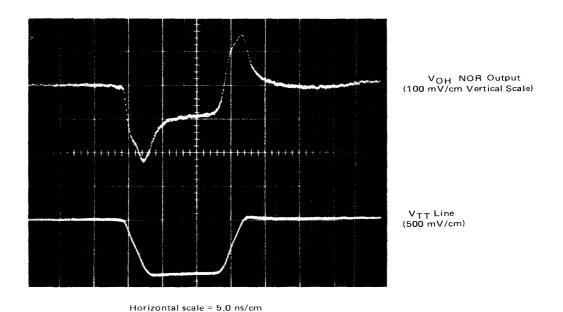

| CHAPTER 9 — AC Noise Immunity                                                   | 213 | ;      |

| Introduction                                                                    |     |        |

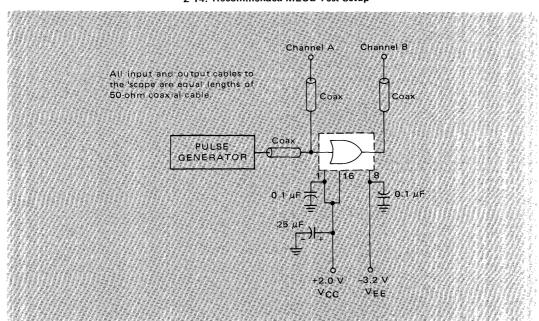

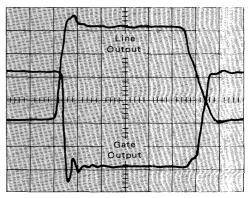

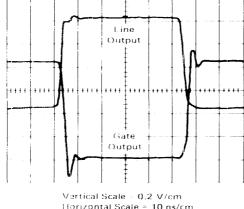

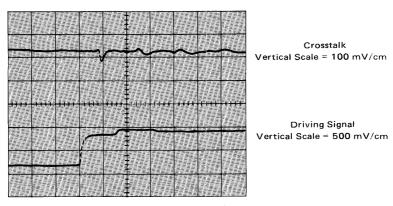

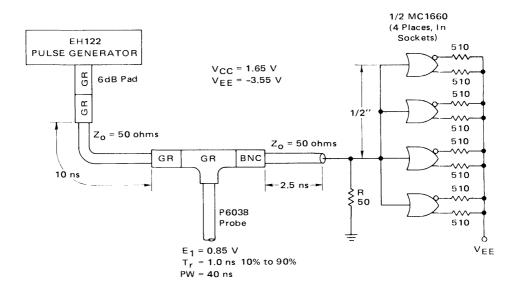

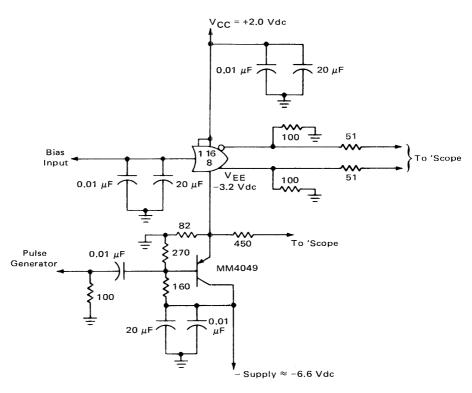

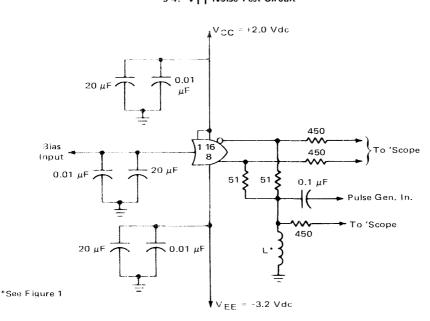

| Test Circuits                                                                   |     |        |

| Test Conditions                                                                 | 216 | •      |

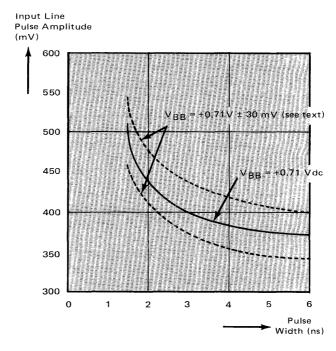

| Test Results                                                                    |     |        |

| Conclusions                                                                     | 222 | !      |

| CHAPTER 10 – MECL 10,000 For Military Applications                              | 225 | ;      |

| Fanout                                                                          |     |        |

| Termination and Interconnect Techniques                                         |     |        |

| Power                                                                           |     |        |

| Noise Margin                                                                    |     |        |

| AC Performance                                                                  |     |        |

|                                                                                 |     |        |

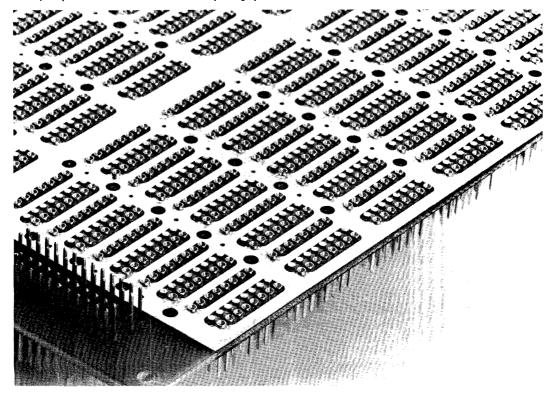

| APPENDIX I — MECL Hardware & Components                                         | 233 | j      |

| General Index                                                                   | 237 | ,      |

# Introduction

#### What is MECL?

The term MECL identifies Motorola's emitter coupled logic. Emitter coupled logic is a non-saturating form of digital logic which eliminates transistor storage time as a speed limiting characteristic, permitting very high speed operation. "Emitter Coupled" refers to the manner in which the emitters of a differential amplifier within the integrated circuit are connected. The differential amplifier provides high impedance inputs and voltage gain within the circuit. Emitter follower outputs restore the logic levels and provide low output impedance for good line driving and high fanout capability.

#### **History of MECL**

Motorola offers MECL circuits in four logic families: MECL I, MECL II, MECL III, and MECL 10.000.

The MECL I family was the first digital monolithic integrated circuit line produced by Motorola. Introduced in 1962, MECL I was considerably beyond the state-of-the-art at that time. Several years passed before any other form of logic could equal the 8 ns gate propagation delays and 30 MHz toggle rates of MECL I. As a result of its reliability and performance, MECL I was designed into many advanced systems.

Nearly a decade later, MECL I is still being produced by Motorola. It finds wide usage in existing products. However, several features of the more advanced MECL II, III, and 10,000 favor their being used in new designs. For example, MECL I requires a separate bias driver package, MC304/MC354, to be connected to the logic functions. This means increased package count and extra circuit board wiring. Also the 10-pin packages used for MECL I limit the number of gates per package and the number of gate inputs. No provision was made for operation of MECL I with transmission lines, as they were unnecessary with the 8 ns rise and fall times.

In 1966 Motorola introduced the more advanced MECL II. The basic gate featured 4 ns propagation delays and flip-flop circuits that would toggle at over 70 MHz. MECL II immediately set a new standard for performance that has been equaled by non-ECL logic only with the introduction of Schottky TTL in 1970.

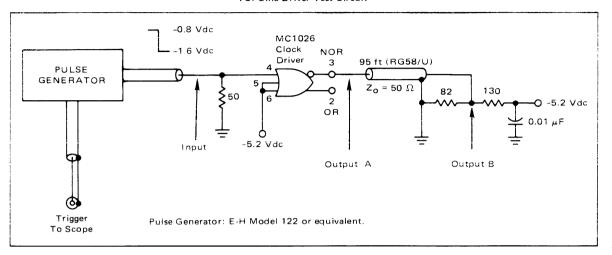

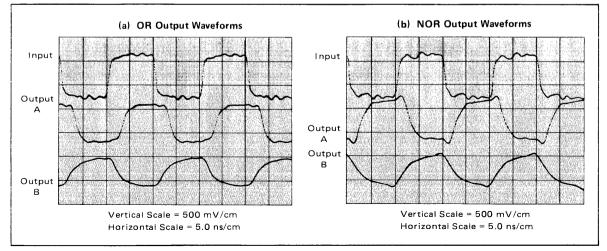

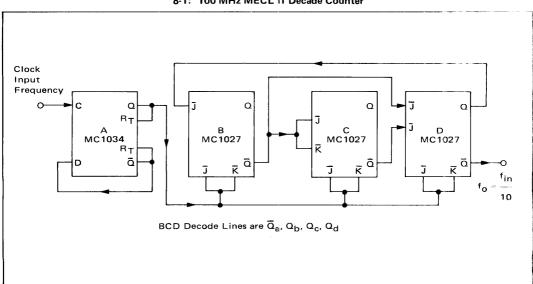

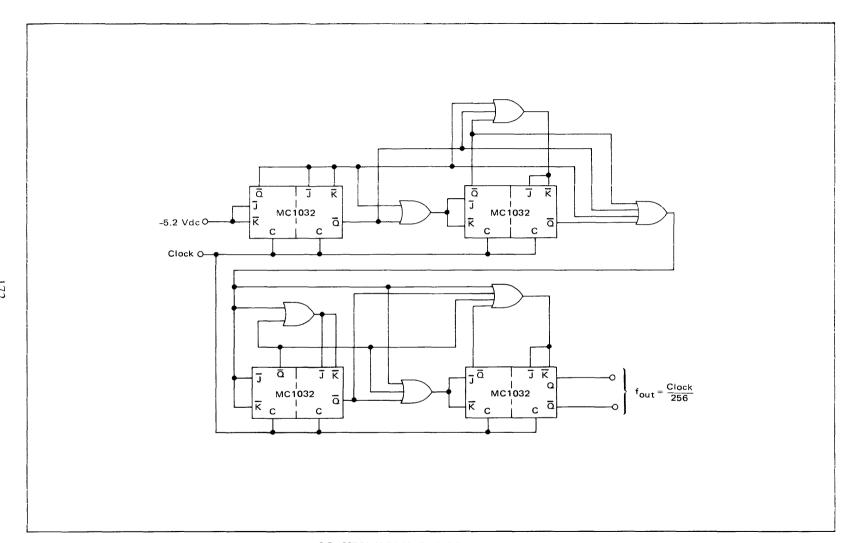

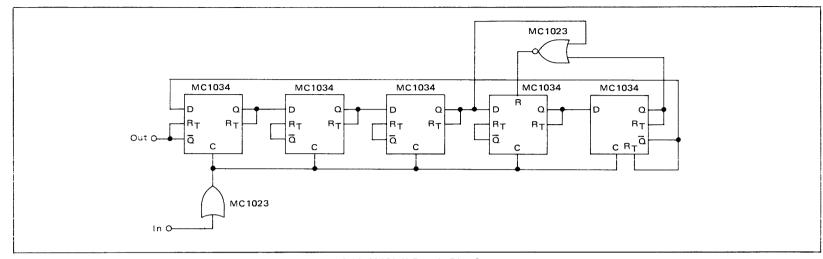

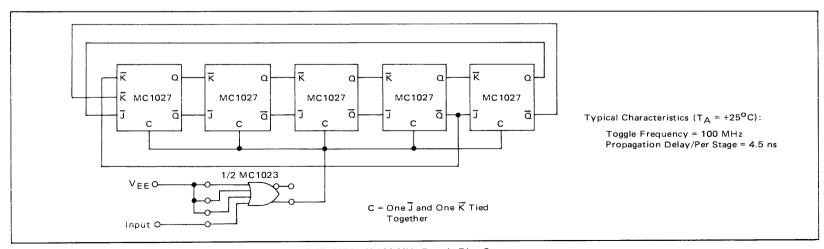

Motorola continued with the development of MECL II and flip-flop speeds were increased first to 120 MHz for the MC1027/MC1227 JK circuit, and then to 180 MHz for the MC1034 type D flip-flop. To drive these high speed flip-flops, high speed line drivers were introduced with 2 ns propagation delays and 2 ns rise and fall times. With 2 ns edges, transmission lines could be used to preserve the waveforms and limit overshoot and ringing on longer lines. Consequently, the MC1026 was designed to drive 50-ohm lines. Because of the significant speed increase of the line drivers and high speed flip-flops over the basic MECL II parts, these circuits are commonly called MECL II-1/2, although they are part of the MECL II family.

MECL II is continuing to gain in popularity and is being designed into many high speed systems. MECL II circuits have a temperature compensated bias driver internal to the circuits (except for the MC1020/MC1220 line receiver which requires no internal bias). The internal bias source simplifies circuit interconnections and tracks with both temperature and supply voltage to retain noise margin under varied operating conditions.

Complex functions became available in MECL II when trends shifted toward more complicated circuits. The family now has adders, data selectors, multiplexers, decoders and a Nixie\* tube decoder/driver. MECL II is a growing line, with new products currently being designed and introduced.

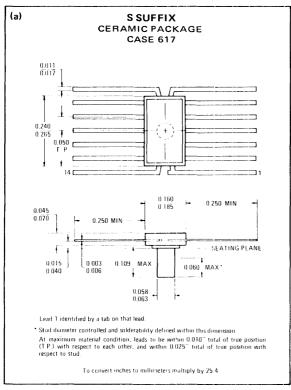

Motorola's continuing development of ECL made possible an even faster logic family. As a result, MECL III was introduced in 1968. Its 1 ns gate propagation delays and greater than 500 MHz flip-flop toggle rates remain the industry leaders. The 1 ns rise and fall times require a transmission line environment for all but the smallest systems. For this reason, all circuit outputs are designed to drive transmission lines and all output logic levels are specified when driving 50-ohm loads. Because of MECL III's fast edge speeds, multi-layer boards are recommended above 200 MHz. For the first time with MECL, internal input pulldown resistors are included with the circuits to eliminate the need to tie unused inputs to  $V_{\rm EE}$ . The Hi-Z 50  $k\Omega$  input resistors are used with transmission lines for most applications. Optional Low-Z 2  $k\Omega$  input resistors can be used in place of pulldown resistors when the chips are used in a hybrid circuit or when line lengths are very short. MECL III is gaining in popularity — especially in high speed test and communications equipment. As a result, Motorola is continuing to expand and develop this product line.

Trends in large high speed systems have shown the need for an easy to use logic family with 2 ns propagation delays. To fill this requirement, Motorola introduced the MECL 10,000 series in 1971. In order to make the circuits comparatively easy to use, edge speed was slowed to 3.5 ns while the important propagation delay was held to 2.0 ns. The slow edge speed permits use of wire wrap and standard printed circuit lines. However, the circuits are specified to drive transmission lines for optimum performance.

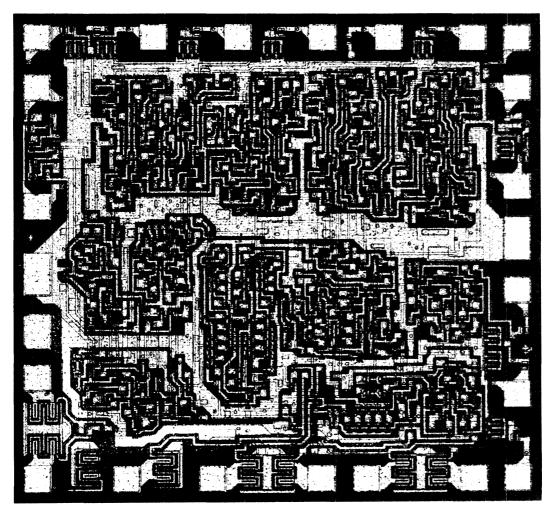

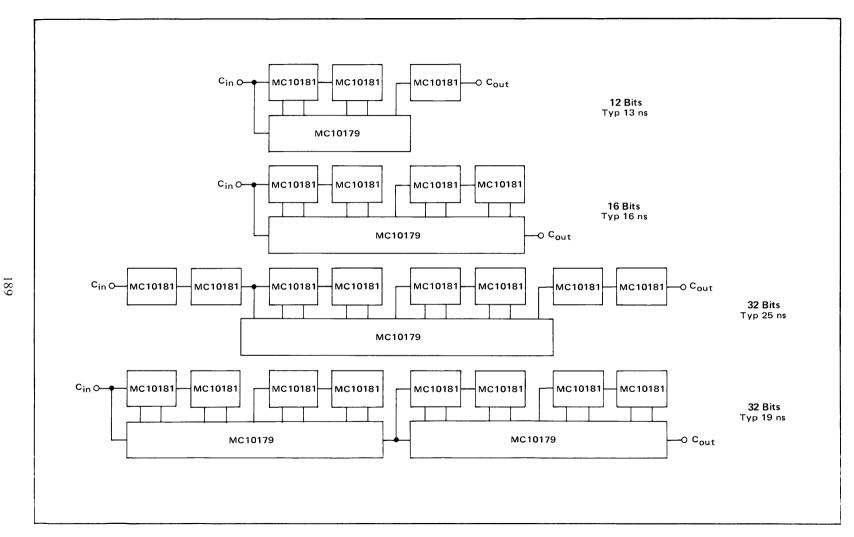

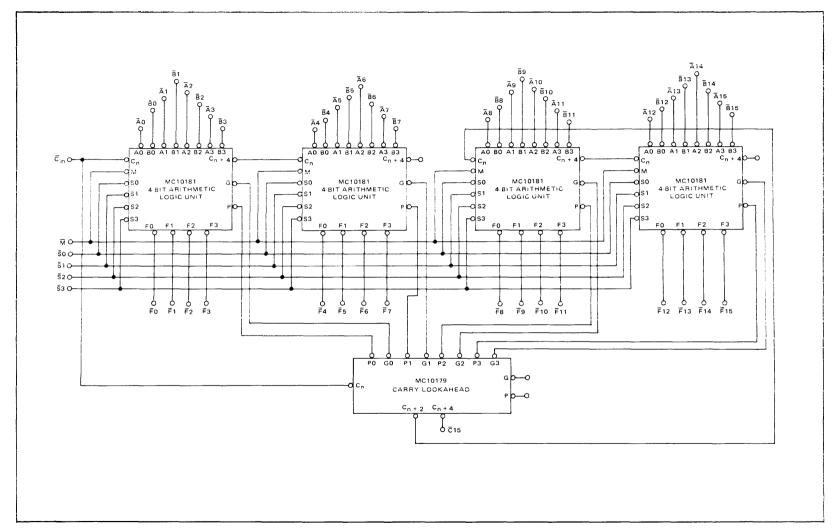

MECL 10,000 is provided with logic levels that are completely compatible with MECL III to facilitate using both families in the same system. A second important feature of MECL 10,000 is the significant power reduction. MECL 10,000 gates use less than one-half the power of MECL III or high speed MECL II gates. Finally, the low gate power and advanced circuit design techniques have permitted a new level of MECL complex circuits. For example, complexity of the MC10181 four-bit arithmetic unit compares favorably to that of any bipolar integrated circuit on the market. MECL 10,000 is the fastest growing ECL family in the industry and Motorola is designing and introducing many versatile complex functions to expand the line.

## Why Use MECL?

Circuit speed is, of course, an obvious reason for designing with MECL. MECL III is significantly faster than any other digital logic family. MECL 10,000 offers shorter propagation delays and higher toggle rates than any non-ECL type of

<sup>\*</sup>T.M. – Burroughs Corp.

logic. Equally important to the circuit speed are the characteristics of MECL circuits which permit entire systems to operate at high speeds.

The ability of the faster MECL families to drive transmission lines becomes increasingly important in larger and faster systems. While a transmission line environment imposes some additional design rules and restrictions, the advantages of longer signal paths, better fanout, improved noise immunity, and faster operation, often more than compensate for the restrictions.

When using MECL II or MECL 10,000 without transmission lines, their high input impedances permit the use of series-damping resistors to increase wiring lengths and to improve waveforms. Unlike non-ECL forms of logic, MECL circuits have constant power supply requirements, independent of operating frequency. This simplifies power supply design, since circuit speed need not be considered a variable. At fast circuit speeds MECL can offer a considerable power saving over the other types of logic.

In addition to faster operation, the line driving features of MECL circuits can be exploited to improve system performance. For one, the parts specified to drive transmission lines will drive coaxial cables over distances limited only by the bandwidth of the cable. In addition, the shielding in coaxial cable gives good isolation from external noise.

More economical than using coaxial cable, is the ability of the MECL circuits to differentially drive and receive signals on twisted pair lines. Using this technique, signals have been sent over twisted pair lines up to 1000 feet in length.

The complementary outputs and Wired-OR capabilities of MECL circuits result in faster system operation with reduced package count and a power saving. The complementary outputs are inherent in the circuit design and both outputs have equal propagation delay. This eliminates the timing problems associated with using an inverter to get a complement signal. The logic OR function is obtained by wiring circuit-outputs together. The propagation delay of the Wired-OR connection is much less than a gate function and can save power, as only one pulldown resistor or termination is required per Wired-OR.

Another advantage when designing with MECL is the low noise generated by the circuits. Unlike totem pole outputs, the emitter follower does not generate a large current spike when switching logic states, so the power lines stay comparatively noise free. The low current-switching in signal paths, relatively small voltage swing (typically 800 mV), and low output impedances, cut down crosstalk and noise.

Generated noise is also reduced by MECL's relatively slow rise and fall times. For each MECL family the edge speed is equal to or greater than the propagation delay. The low noise associated with MECL is especially important when the logic circuits are to be used in a system which contains low level analog or communications signals.

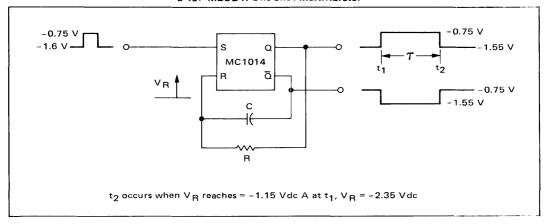

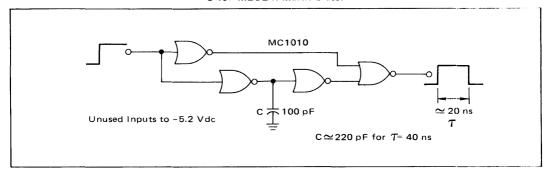

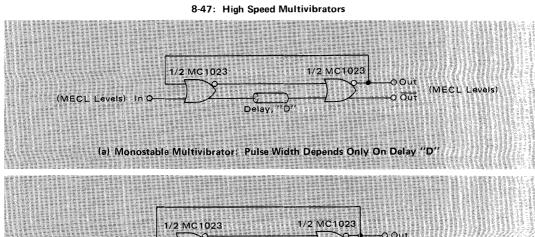

The flexibility of the MECL line receivers and Schmitt triggers to act as linear amplifiers leads to many functions that may be performed with standard MECL circuits. For example, in addition to amplifying low level signals to MECL levels, these MECL circuits can be used as crystal oscillators, zero crossing detectors, power buffers, Schmitt triggers, RF and video amplifiers, one-shot multivibrators, etc.

## The Advantages of MECL

- 1. Highest speed IC logic available

- 2. Low cost

- 3. Low output impedance

- 4. High fanout capability

- 5. Constant supply current as a function of frequency or logic state

- 6. Very low noise generation

- 7. Complementary logic outputs save on package count

- 8. Low crosstalk between signal leads

- 9. All outputs are buffered

- 10. Outputs can be tied together giving the Implied-OR function

- 11. Common mode rejection of noise and supply variations is 1 V or greater for differential line receiving

- 12. Bias supplies are internal, allowing MECL use with a single power supply

- 13. Minimal degradation of parameters occurs with temperature variations

- 14. Large family of devices yields economical designs

- 15. Power dissipation can be reduced through use of Implied-OR and the "Series Gating" technique

- 16. Easy data transmission over long distances by using the balanced twisted pair technique with standard parts

- 17. Constant noise immunity versus temperature

- 18. Best speed-power product available

- 19. All positive logic functions are available

- 20. Adapts easily to MSI and LSI techniques

#### **MECL Areas of Application**

- 1. Instrumentation

- 2. High speed counters

- 3. Computers

- 4. Medical electronics

- 5. Military systems

- 6. Large real-time computers

- 7. Aerospace and communication satellite systems

- 8. Ground support system

- 9. High speed A/D conversion

- 10. Digital communication systems

- 11. Data transmission (twisted pair)

- 12. Frequency synthesizers

- 13. Phase array radar

- 14. High speed memories

- 15. Data delay lines

#### **Purpose of This Book**

Rules and guidelines for using the various MECL families comprise the subject matter of this book. Because of edge speed and bit rate capabilities, each family has differing system requirements. The family name will therefore be referenced for the examples and figures in the text, whenever applicable. The information in this book is meant to apply to MECL II, MECL III, and MECL 10,000. The information about MECL II will generally apply to MECL I, although the data would be conservative because of the slower MECL I speed. This book aims at giving the reader an understanding of the MECL families, as well as the knowledge needed to confidently design with and use MECL.

Chapter 1 discusses the operation of MECL circuits and the characteristics of the various families. It also shows methods for internally connecting the basic gates to provide efficient complex functions. Of more importance to the user is Chapter 2 – a list of rules providing a condensed reference for *using* the various MECL families.

Chapters 3, 4, 5, and 6 elaborate on those rules giving a technical background for good system design and presenting test results showing MECL circuits in various modes of operation. Chapter 3 describes circuit-to-circuit interconnections on a card. Both open wire and transmission line techniques are covered. Chapter 4 expands the wiring techniques to show methods for card-to-card and panel-to-panel interconnections. Chapter 5 elaborates on power distribution, showing how voltage drops and power line noise affect noise immunity. Chapter 6 discusses thermal considerations. Attention is given to the problems of calculating chip temperature, removing heat from the system, and to the effect of thermal differences on noise immunity.

Chapter 7 provides background necessary for understanding transmission lines as they apply to MECL. Derivations of equations are shown, along with test results correlating with the theoretical analysis. This chapter should be especially useful when selecting a transmission line impedance and when determining the effect of fanout or stray capacitance on the line.

Chapter 8 contains application ideas for MECL circuits. Included are methods for interfacing various logic families with MECL, and numerous useful circuits designed with MECL for high performance.

Chapter 9 discusses ac noise immunity characteristics exhibited by MECL 10,000 devices, and describes methods for testing circuit performance when subjected to electrical noise.

In Chapter 10 is contained a short discussion of the system use of MECL 10,000 devices designed for use over the military temperature range.

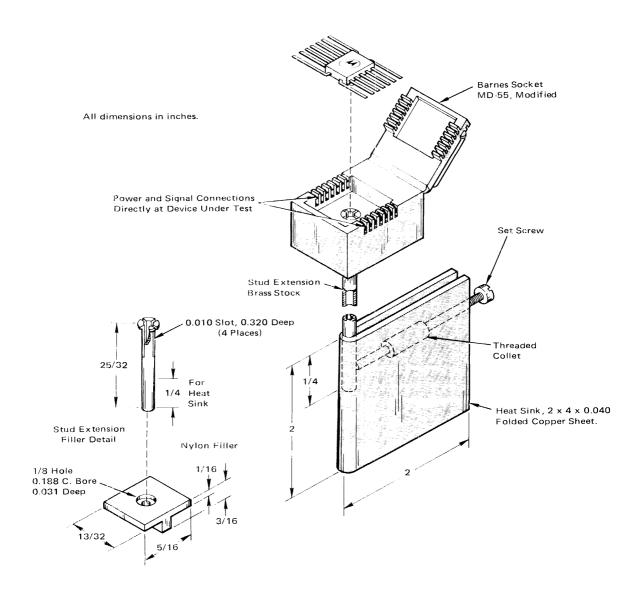

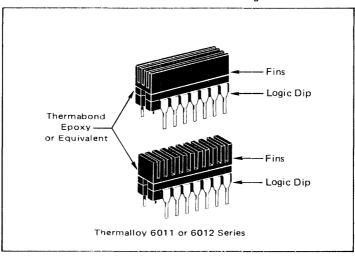

Finally, a brief appendix illustrates some of the peripheral hardware and components of use in MECL Systems.

#### The Basic MECL Gate

An understanding of the basic circuits used in the construction of a logic family is important in order to successfully design and trouble-shoot a system which uses the family. This chapter describes MECL circuits, compares MECL families, and gives some suggested rules for using MECL circuits in system design.

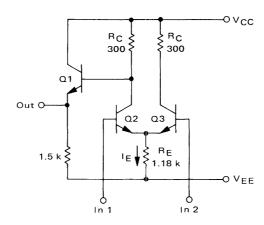

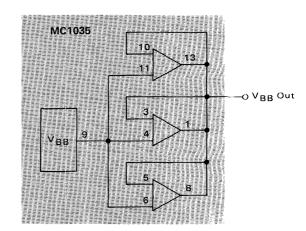

Figure 1-1 shows a typical MECL gate, — the basic gate circuit for the MECL 10,000 family. (Similar schematics are provided for each other MECL logic family, in the general information section of the MECL Data Book). The figure shows the separate functional circuits within the gate.

The differential amplifier section contains the current steering element that provides the actual logic gating of the circuit. It also provides the voltage gain necessary for a narrow linear threshold region.

An internal temperature and voltage compensated bias driver supplies a reference voltage for the differential amplifier. The bias voltage,  $V_{BB}$ , is set at the midpoint of the signal logic swing. With the recommended –5.2 volts supply voltage

Internal Temperature and Voltage Emitter Compensated Follower Differential Input Amplifier Bias Network Outputs V<sub>CC2</sub> V<sub>CC1</sub> R<sub>C2</sub> § 245 **≨** 907 Rc1 \$ 220 OR ۱B Output Q7 NOR O  $V_{BB}$ Output Q5 Q1 Q3 ١E Rp Rp Rp  $R_{P}$ 6.1 k 4.98 k 50 k 50 k 50 k VEE Inputs

1-1: MECL 10,000 Basic Gate

and 25°C ambient temperature, VBB is -1.29 volts dc for either MECL 10,000 or MECL III, and -1.175 volts dc for MECL II. The diodes in the voltage divider line, together with Q6, provide temperature compensation by maintaining a level consistent with the midpoint of the logic levels despite changing temperatures.

One additional feature of the bias supply is its ability to track supply voltage changes. Consequently MECL II gates, for example, are specified to operate from a -5.2 volt  $\pm 20\%$  supply. In fact, they are capable of working over a much wider range (-3.0 to -8.0 volts) although ac performance would be degraded.

The emitter followers are output drivers. They provide level shifting from the differential amplifier to MECL output levels, and provide a low output impedance for driving transmission lines. Both MECL 10,000 and MECL III circuits use open emitter outputs. The reason is that since these circuits are designed for use with transmission lines, and since the line termination provides an output load, internal pulldown resistors would be a waste of power.

However MECL II, which is not specified to drive transmission lines, offers gates both with and without pulldown resistors. In general, the circuits without pulldown resistors are intended for use in Wired-OR circuit designs rather than for driving high fanout loads. MECL II circuits with internal output pulldown resistors use 1.5 k $\Omega$  values for standard speed parts, and as low as 600  $\Omega$  values for the high speed circuits.

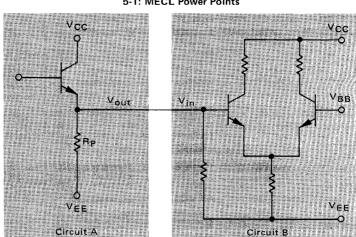

MECL 10,000 and MECL III circuit families, designed to drive transmission lines, have two  $V_{CC}$  power voltage inputs.  $V_{CC1}$  is used to supply current to the output drivers, while  $V_{CC2}$  supplies the remainder of the circuit. Separate  $V_{CC}$  lines are used to eliminate crosstalk between circuits in a package. More important, the use of two lines speeds up circuit performance by eliminating a voltage spike which otherwise would occur on the bias voltage,  $V_{BB}$ , caused by the relatively heavy currents associated with transmission lines. Each  $V_{CC}$  pin should be connected to the system ground by as short a path as possible (all  $V_{CC}$  pins are connected to the same system ground). Standard speed MECL II circuits are not designed to drive transmission lines and consequently require only a single  $V_{CC}$  package pin.

The input pulldown resistors shown in Figure 1-1 are characteristic of MECL 10,000 and MECL III. MECL 10,000 and Hi-Z MECL III use 50 k $\Omega$  "pinch" resistors which serve to drain off the input transistor leakage current. These resistors hold unused inputs at a fixed zero level, so unused inputs are left open. On the other hand, MECL II without input pulldown resistors, requires unused inputs be tied to  $V_{\rm EE}$  or  $V_{\rm OL}$ .

The following calculations illustrate the current switching operation of a MECL 10,000 gate. Similar calculations may be performed for the other MECL families by substituting appropriate resistor values and voltage levels.

When all gate inputs are at a voltage,  $V_{in}$ , equal to a logic  $\emptyset$  level,  $|V_{IL}| \min | > |V_{in}| > |V_{IL}| \max |$ , the input transistors Q1 through Q4 in Figure 1-1 will not be conducting current, because the common emitter point of these four transistors is at about -2.09 V: i.e.,  $V_{BB} + V_{BEQ5} \approx -1.29 \text{ V} + (-0.80 \text{ V})$ . This is not enough forward bias (base to emitter) on Q1 through Q4 for conduction. Thus, current flows through  $R_{C2}$ , Q5, and  $R_E$ . This current,  $I_{E\emptyset}$ , is:

$$I_{E\emptyset} = \frac{V_{EE} - (V_{BB} + V_{BE})}{R_E} \approx -4.0 \text{ mA}.$$

The voltage drop at the collector resistor. RC2, may be calculated as:

$$V_{RC2} = I_{E0}R_{C2} + I_{B}R_{C2} \approx (-4.0 \text{ mA}) \cdot (245 \Omega) = -0.98V.$$

The output transistor base current, IB, is small compared to the switch current, so the second term above can be ignored.

The OR output is then obtained through an emitter-follower, Q8, which cuts the output level by one base-emitter drop, giving a voltage level:

$$V_{OL\ OR} = V_{RC2} + V_{BE}$$

where: V<sub>BE</sub> = base to emitter drop on Q8, with logic zero current level (i.e., 6 mA thru Q8).

So:

$$V_{OL OR} \approx -0.98 \text{ V} + (-0.77 \text{ V}) \approx -1.75 \text{ V},$$

typical at  $T_A = 25^{\circ}C$ .

The base of the NOR output emitter-follower, Q7, is at about -0.05 V, yielding an output of -0.924 V typical, at an output device current level of 22.5 mA and  $T_A = 25^{\circ}$ C. (These output voltage and current levels assume 50-ohm loads to a terminating voltage,  $V_{TT}$ , of -2.0 V).

If one or more of the gate inputs is switched to a voltage level,  $V_{in}$ , equal to a nominal logic 1 level,  $|V_{IH\ min}| \ge |V_{in}| \ge |V_{IH\ max}|$ , a current  $I_{E1}$  flows through  $R_{C1}$ , Q1-Q4, and  $R_{E}$ . This current is:

$$I_{E1} = \frac{V_{EE} - (V_{in} + V_{BE})}{R_{E}} \approx -4.49 \text{ mA},$$

where:  $V_{in} = -0.924 \text{ V}$

$$V_{BE} = -0.79 \text{ V}.$$

The current flow through  $R_{C1}$  produces a voltage at the collector nodes of Q1 through Q4:

$$V_{RC1} \approx I_{E1}R_{C1} = (-4.49 \text{ mA}) \cdot (220 \Omega) \approx -0.98 \text{ V}.$$

Finally, the output is obtained through an emitter follower, Q7, which drops the collector voltage level one base-emitter drop, so that:

$$V_{OL\ NOR} = V_{RC1} + V_{BE}$$

(output device at 6 mA)

$\approx -0.98 \text{ V} + (-0.77 \text{ V}) = -1.75 \text{ V},$

typical at  $T_A = 25^{\circ}C$ .

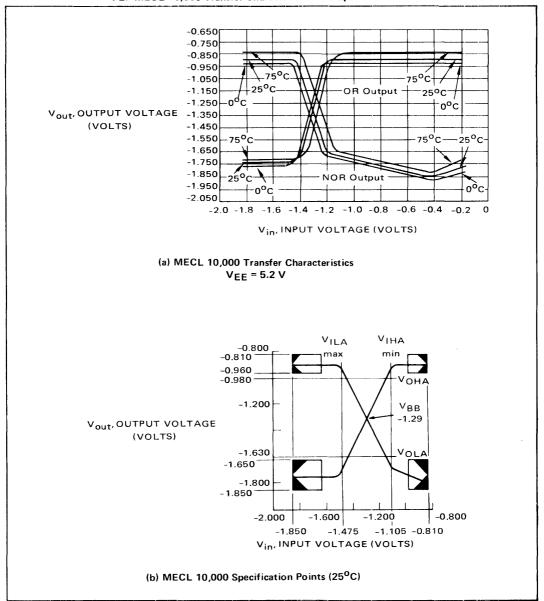

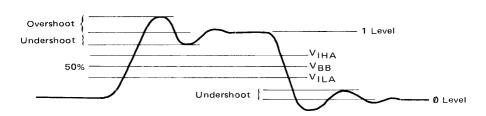

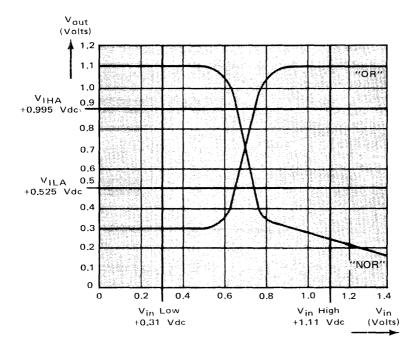

The transfer curves in Figures 1-2(a) and (b) indicate the behavior of the MECL gate while switching. Note from the data in Figure 1-3 and from the NOR transfer characteristic: for  $V_{in}$  increasing from  $V_{IL}$  min to  $V_{ILA}$  max, the output remains at a high level. When  $V_{in}$  increases from  $V_{ILA}$  max to  $V_{IHA}$  min, the NOR output

1-2: MECL 10,000 Transfer Characteristics and Specification Points

1-3: MECL 10,000 and MECL III Specified Logic Levels and Thresholds

| PARAMETER                                 | 0°C         |          | +25 <sup>o</sup> C |          | +75 <sup>o</sup> C |          |

|-------------------------------------------|-------------|----------|--------------------|----------|--------------------|----------|

| (VOLTS)                                   | MECL 10,000 | MECL III | MECL 10,000        | MECL III | MECL 10,000        | MECL III |

| V <sub>IH max</sub> & V <sub>OH max</sub> | -0.850      | -0.840   | -0.810             | -0.810   | -0.720             | -0.720   |

| VOH min                                   | -1.010      | -1.000   | -0.960             | -0.960   | -0.900             | -0.900   |

| VOHA min                                  | -1.030      | -1.020   | -0.980             | -0.980   | -0.920             | -0.920   |

| VIHA min                                  | -1.155      | -1.135   | -1.105             | -1.095   | -1.045             | -1.035   |

| VILA max                                  | -1.485      | -1.500   | -1.475             | -1.485   | -1,445             | -1.460   |

| VOLA max                                  | -1.640      | ~1.615   | -1.630             | -1.600   | -1.600             | -1.575   |

| VOL max                                   | -1.660      | -1.635   | -1.650             | -1.620   | -1.620             | -1.595   |

| VIL min & VOL min                         | -1.870      | -1.870   | -1.850             | -1.850   | -1.830             | -1.830   |

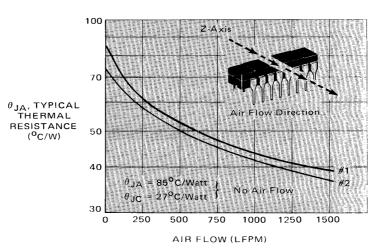

Conditions: Ceramic DIL package stabilized with  $\geq$ 500 lfm air flow.

will switch to a low level. Then, as the input continues more positive than  $V_{IHA\ min}$ , the output continues more negative with a slope of about -0.24. This is caused by the collector input node going more negative because of increasing collector current as  $V_{in}$  goes more positive.

If the input continues in the positive direction, saturation will be reached at an input of about -0.4 volts. Beyond that point, the base-collector junction is forward biased to saturation and the collector voltage and output will go more positive with the increasing input level. Since the saturation point is well above  $V_{OH\ max}$ , operation in this mode will not occur in normal system operation. The OR output level depends on Q5's collector voltage (cf Fig. 1-1). This output is unaffected by input levels except in the active transfer region.

Suffice it to say that while the manufacture of MECL circuits is not a primary concern of the user, nevertheless ease of manufacture does translate directly into end product cost. Although not as easy to build as some slower logic families because of smaller transistor geometries, MECL does have some features which facilitate processing. First, the voltage gain of the basic gate circuit (approximately 4.5 for MECL 10,000) is essentially independent of transistor beta. So transistor beta can be allowed to vary from a low of about 70 in high speed MECL (40 for MECL II) to a high in excess of 300, which permits easy processing limits. Second, the output voltage levels depend on diode drops for a high output, and diode drops and resistor ratios for a low output. Resistance ratios can be held to within ±5% even though absolute values vary by ±20%. Again, this eases processing.

Third, since the transistors used do not saturate, the gold doping which is normally required to decrease storage time is not required in MECL processing; therefore yields are better. Fourth, collector-emitter voltages are low, due to circuit design, again relaxing processing restrictions. Such advantages, together with Motorola's ability to control processing, permit high volume production of all MECL circuits. In effect, this means low-cost high performance circuits for the designer.

#### Noise Margin

Noise margin is a dc voltage specification which measures the immunity of a circuit to adverse operating conditions. Noise margin is defined as the difference between the worse case input logic level ( $V_{IHA\ min}$  or  $V_{ILA\ max}$ ) and the guaranteed worst case output ( $V_{OHA\ min}$  or  $V_{OLA\ max}$ ) for those inputs. Figure 1-3 lists the worst case limits for MECL 10,000 and MECL III. (MECL II levels may be found in the general information section of the Motorola "MECL Integrated Circuits Data Book").

High level noise margin is obtained by subtracting ( $V_{IHA\ min}$ ) from ( $V_{OHA\ min}$ ); similarly, low level noise margin is ( $V_{ILA\ max}$ ) minus ( $V_{OLA\ max}$ ). Worst-case noise margin is guaranteed to be at least 0.175 volts for MECL II, 0.125 volts for MECL 10,000 (and MECL III in stud packages), and 0.115 volts for MECL III in dual in-line packages. Using typical output voltage levels for MECL circuits, noise margins are usually better than guaranteed — by about 75 millivolts.

A second noise parameter of interest to the designer is obtained by cascading worst case gates and measuring the minimum "noise" input that will propagate through the gates. This measurement is more indicative of actual system operation than de noise margin, and is often referred to as "noise immunity" or "ac noise immunity". Testing has shown that this "noise immunity" is typically at least 40 millivolts greater than the de noise margin specified by voltage levels. However, ac

noise immunity is rather difficult to measure. Consequently it is not specified on the data sheets.

In system design, the user is concerned with noise margin when devices at different temperatures and different power supply voltages interface with each other. Figure 1-3 tabulates the worst case change in logic levels as a function of temperature. Equally important is the change in output levels as a function of supply voltage (cf Figure 5-2). The logic 1 levels are relatively independent of power supply voltage, and the change in the output level is typically less than 0.05 of the  $V_{EE}$  change. The change in the  $\emptyset$  level is a function of the resistor ratios in the current switch and is typically 0.25 of the  $V_{EE}$  change. These values illustrate the rejection of power supply variations that is characteristic of MECL. Detailed information on noise margin changes due to power supply and temperature variations is given in Chapters 5 and 6.

#### **MECL Circuit Types**

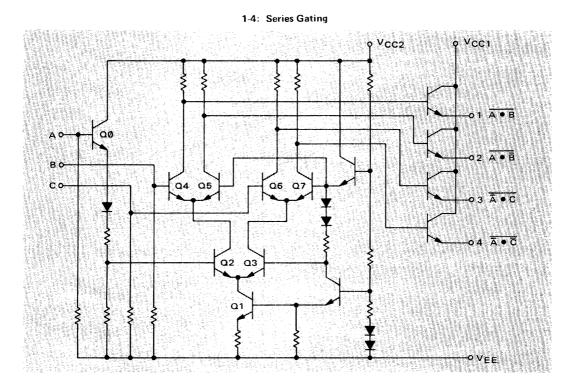

It is possible to connect the basic MECL differential amplifiers together within a circuit to increase logic flexibility, speed, and power efficiency. Two techniques, series gating and collector dotting, add the NAND and AND logic functions to the basic OR and NOR operation of the MECL gate with very little increase in propagation delay. A third technique, Wired-OR, gives the logic OR function by tying together two or more emitter-follower transistors. This is used internally in complex functions to save speed and power and, unlike collector dotting, may also be used externally by connecting logic outputs together.

Series gating is accomplished by connecting MECL differential amplifiers in a current-switch "tree", building up from a current source, Q1, as shown in Figure 1-4. The A input controls the switch, Q2/Q3 through the level shifter  $Q\emptyset$  and the

6

1-5: Collector Dotting

associated resistor diode network. The bias network is modified to provide the proper voltage level at Q3, a level which is lower than that on Q7 and Q5. The two upper switch pairs are controlled by inputs B and C. The overall circuit generates the four logic functions:  $\overline{A \cdot B}$ ,  $\overline{A \cdot B}$ ,  $\overline{A \cdot C}$ , and  $\overline{\overline{A \cdot C}}$ . MECL circuits use up to three levels of series gating, permitting up to eight logic functions with one current source.

The propagation delay from an input, to a top current switch is approximately one gate delay. The propagation delay from an input to a lower level current switch is slightly longer because of the input level shifter  $Q\emptyset$ . Typically, the latter takes about 1.5 gate delays. More specific information is found on the data sheet for a particular part.

Because of the bias network design, some of the MECL II series gated circuits require unused inputs to be connected to  $V_{OL}$  instead of to the normal  $V_{EE}$  connection. These circuits are identified by specifying  $V_{IL\ min}$  other than -5.2 V on the data sheets.

Series gating is an advantage in MECL logic since it provides the AND or NAND logic functions. Together with the OR/NOR function of the basic gate, MECL has the four basic logic functions needed for efficient logic design. Series gating is used internally in most MECL complex functions and flip flops.

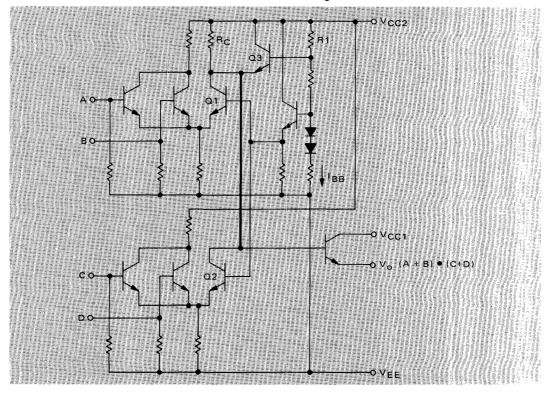

Collector dotting is a second logic technique which is used in the MECL 10,000 series. With it, the logic AND function can be generated by interconnecting one collector node of separate differential current switches as shown in Figure 1-5. When connected this way the two 2-input OR gates give the logic function:

$$V_O = (A + B) \cdot (C + D)$$

Only one collector resistor ( $R_C$ ) is used for the two transistors Q1 and Q2. The interconnection requires that at least one input to each gate be at a logic 1 level for the output to be at the logic 1 level. Since it is possible to have both Q1 and Q2 conducting at the same time (all inputs low), a clamp is used to limit the current in  $R_C$  and maintain the output  $\emptyset$  logic level voltage. This clamp consists of R1 and Q3. They insure that the Q1/Q2 collector node never goes more negative than ( $I_BR_1 + V_{BEQ3}$ ). Propagation delays for all inputs to collector dotted circuits are equal and are typically about 20% greater than the basic gate delay.

To allow for temperature variations, the collector-dotted logic functions are designed to have the same  $V_{OL}$  as normal logic gates at  $T_A = 75^{\circ}\text{C}$  when only *one* gate has all of its inputs at a logic  $\emptyset$  level. Therefore, when *all* gates have all their inputs at a logic  $\emptyset$  level,  $V_{OL}$  will be slightly more negative than a normal gate. This does not limit device operation, but does give an increase in noise immunity for the logic  $\emptyset$  level.

The collector dot (OR-AND) logic function, series gating, and the Wired-OR characteristics of MECL combine to provide the means for designing very efficient and fast complex logic functions.

#### **MECL Flip-Flops**

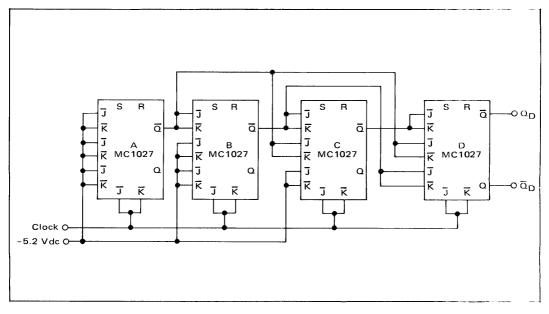

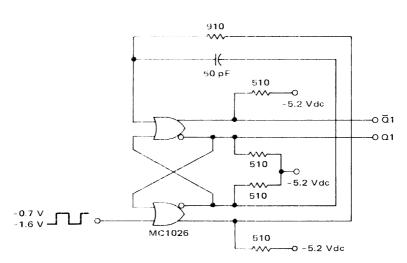

In addition to the basic gate, the flip-flops in a logic line provide a necessary building block. MECL employs two types of flip-flop circuits; the ac coupled JK flip-flops found in MECL I and MECL II, and the direct coupled master-slave flip-flops used in MECL II, MECL 10,000 and MECL III.

The MECL II ac coupled flip-flops are characterized by small capacitors (25 to 30 pF) coupling the J and K inputs to the storage section of the circuit. Because of this capacitive coupling, the circuit is somewhat sensitive to input rise time. However, the circuits will trigger on signals of MECL amplitude with edges up to 100 ns long — much longer than any MECL edge. The multiple J and K inputs of the MC1013/MC1213 and MC1027/MC1227 are especially useful in synchronous counters or counters with non-binary counting sequences.

A limitation on these flip-flop circuits is their susceptibility to some types of noise on the input line. For example, a positive going input with a large overshoot on a J input will override a 1 level on another J input intended to inhibit that positive going signal. The overshoot will couple through the capacitor and look like a J input. A similar condition exists on the K inputs. Fortunately the problem is not a serious one and its solution requires only that the input signals do not have excessive ringing. It is recommended that overshoot on the J and K inputs be held to 100 millivolts.

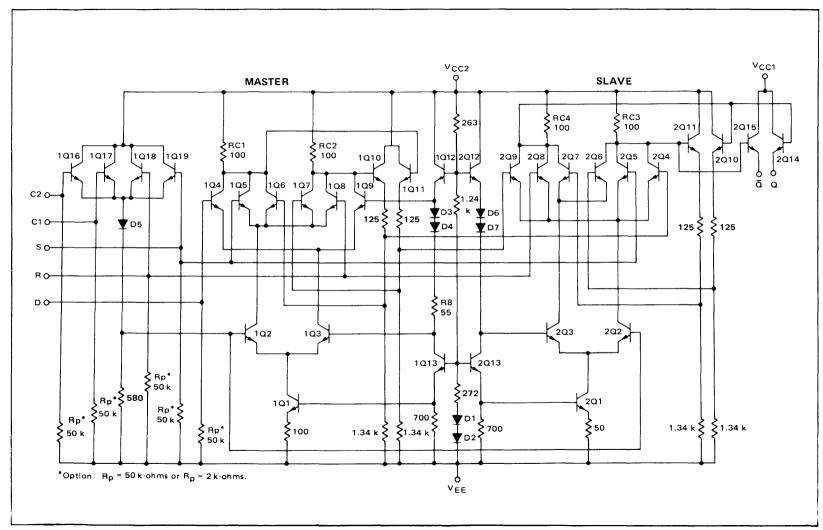

The MECL II type D, and all MECL 10,000 and MECL III flip-flops, use the direct coupled master-slave circuit as shown in Figure 1-6 for the MC1670. In each direct coupled circuit the master is updated while the clock is low, and data is transferred to the slave on the positive excursion of the clock. This type of circuit offers better noise protection than the ac coupled circuit and is not susceptible to overshoot on the inputs. Also, the master-slave flip-flops do not have the rise time limitations of the ac coupled circuits.

#### **Operation Of Flip-Flop**

In the circuit of Figure 1-6 assume that initially Q,  $C_1$ ,  $C_2$ , R, S, and D are at  $\emptyset$  levels and that Q is at the 1 level. Since the clocks and the R and S inputs are low,

9

1-6: MECL III Master-Slave Type D Flip-Flop (MC1670)

transistors 1Q3 and 2Q3 are conducting. In the slave section only transistors 2Q6 and 2Q7 are in series with 2Q3. The output of the slave section is fed back to these two transistors in order to form a latch. Thus, when the clock is low, the output state of the slave is maintained. In the master section, the current path is through 1O3 and 1O9.

Now assume that the D input goes high. The high-input signal on the base of 1Q4 causes it to conduct, and 1Q9 to turn off. The voltage drop across resistor RC1 causes a low-state voltage on the base of 1Q11 and therefore on the emitter of 1Q11. Since there is essentially no current flow through RC2, the base of transistor 1Q10 is in a high state. This is reflected in the emitter of 1Q10, and in turn is transferred to the base of 1Q6. 1Q6 is biased for conduction but, since there is no current path, it does not conduct.

Now assume one of the clocks goes high. As the clock signal rises, transistor 1Q2 turns on and transistor 1Q3 turns off. This provides a current path for the common-emitter transistors 1Q5, 1Q6, 1Q7, and 1Q8. Since the bases of all these devices except 1Q6 are in the low state, current flow is through 1Q6. This maintains the base and emitter of 1Q11 low, and the base and emitter of 1Q10 high. The high state on 1Q10 is transferred to 2Q4 of the slave section.

As the clock continues to rise 2Q2 begins to turn on and 2Q3 to turn off. (Reference voltages in the master and slave units are slightly offset to insure prior clocking of the master section). With transistor 2Q2 conducting and the base of 2Q4 in a high state, the current path now includes 2Q2, 2Q4, and resistor RC3. The voltage drop across the resistor places a low-state voltage on the base of 2Q11, and therefore on the emitter, of 2Q11. The lack of current flow through RC4 causes a high-state input to the base of 2Q10. Finally these states are fed back to the latch transistors, 2Q6 and 2Q7 and appear on the Q and Q outputs.

As the clock voltage falls, transistor 2Q2 turns off and 2Q3 turns on. This provides a current path through the latch transistors, "locking in" the slave output.

In the master section, the falling clock voltage turns on transistor 1Q3 and turns off 1Q2. This enables the input transistor 1Q4 so that the master section will again track the D input.

A separation of thresholds between the master and slave flip-flops is caused by R8. The current through this resistor produces an offset between the thresholds of the transistor pairs 1Q2/1Q3 and 2Q2/2Q3. This offset disables the D input of the master flip-flop prior to the enabling of the information transfer from master to slave via transistors 2Q4 and 2Q9. This disabling operation prevents false information from being transferred directly from master to slave during the clock transition, particularly likely if the D input changes at this time. The offsetting resistor, R8, also allows a relatively slow-rising clock waveform to be used without the danger of losing information during the transition of the clock.

Both set and reset inputs are symmetrically connected. Therefore, their action is similar although results are opposite. As a logic 1 level is applied to the S input transistor, 1Q2 begins to conduct because its base is now being driven through 1Q19 which is in turn connected to S. Transistor 1Q5 is now on, and the feedback devices 1Q6 and 1Q7 latch this information into the master flip-flop. A similar action takes place in the slave with transistors 2Q2, 2Q5, 2Q6, and 2Q7.

#### **MECL Family Comparison**

A list of MECL circuit characteristics is tabulated in Figure 1-7. The various families are compared with respect to both features and performance. Because of the

big speed difference between standard MECL II and the higher speed MECL II clock drivers, many of the figures in the MECL II column do not apply to the complete line. The following paragraphs describe the MECL characteristics in the order of Figure 1-7. Differences between standard and high-speed MECL II are pointed out when significant.

1-4... The first four items in Figure 1-7 are self-explanatory and have been discussed in the introduction and the preceding section on the basic gate.

1-7: MECL Family Comparison

| FEATURE                                               | MECLI     | MECLII   | MECL 10,000 | MECL III       |  |

|-------------------------------------------------------|-----------|----------|-------------|----------------|--|

| 1. Year Introduced                                    | 1962      | 1966     | 1971        | 1968           |  |

| 2. Bias Driver Source                                 | MC304/354 | Internal | Internal    | Internal       |  |

| 3. Output Pulldown Resistors                          | Yes       | Optional | No          | No             |  |

| 4. Input Pulldown Resistors                           | No        | No       | 50 k-ohm    | 2 k & 50 k ohm |  |

| 5. Maximum Input D.C.<br>Loading Current              | 100 μΑ    | 100 μΑ   | 240 µA      | 350 μΑ         |  |

| 6. Specified Output Current                           | 2.5 mA    | 2.5 mA   | ≈ 22 mA     | ≈ 22 mA        |  |

| 7. Maximum Output Current                             | 20 mA     | 20 mA    | 40 mA       | 40 mA          |  |

| 8. Transmission Line Capability                       | No        | No       | Yes         | Yes            |  |

| 9. D.C. Loading Fan Out                               | 25        | 25       | 92          | 63             |  |

| 10. Input Capacitance                                 | 3.6 pF    | 3.6 pF   | 2.9 pF      | 3.3 pF         |  |

| 11. Output Impedance                                  | 22 ohm    | 15 ohm   | 7 ohm       | 5 ohm          |  |

| 12. Gate Propagation Delay                            | 8 ns      | 4 ns     | 2 ns        | 1 ns           |  |

| 13. Gate Edge Speed                                   | 8.5 ns    | 4 ns     | 3,5 ns      | 1 ns           |  |

| 14. Flip-Flop Toggle Speed                            | 30 MHz    | 180 MHz  | 125 MHz     | 500MHz         |  |

| 15. Gate Power                                        | 31 mW     | 22 mW    | 25 mW       | 60 mW          |  |

| 16. Open Wire Length (Less<br>Than 100 mV Undershoot) | 18"       | 12'      | 6"          |                |  |

| 17. Wire Wrap Capability                              | Yes       | Yes      | Yes         | No             |  |

| 18. Use of Series Damping<br>Resistors                | Yes       | Yes      | Yes         | Hi-Z Only      |  |

| 19. Separate V <sub>CC</sub> Inputs                   | No        | No       | Yes         | Yes            |  |

| 20. Speed-Power Product                               | 250 pJ    | 88 pJ    | 50 pJ       | 60 pJ          |  |

| 21. Wired Or Capability                               | Yes       | Yes      | Yes         | Yes            |  |

| 22. Full Military Temperature<br>Range                | Yes       | Yes      | No          | Nσ             |  |

| 23. Flat-Package                                      | Yes       | Yes      | Yes         | No             |  |

| 24. Dual In-Line Package                              | No        | Yes      | Yes         | Yes            |  |

| 25. TO 5 Package                                      | Yes       | No       | No          | No             |  |

<sup>\*-30°</sup>C to +85°C

5... Maximum input de loading current is specified on individual circuit data sheets. The numbers listed here apply to a single input of a basic gate. If a package input goes to more than one point in a circuit, such as a gate strobe line would, additional current may be required. Because of higher power in the MECL II clock drivers, these inputs are specified at 300  $\mu$ A maximum input current. The input current difference between the MECL II and MECL 10,000 circuits is due to the 50 k $\Omega$  input resistor used with MECL 10,000.

Calculating the input current,  $l_{in}$ , for MECL 10,000 with a worst-case input resistor value of 30 k $\Omega$  ( $R_{in}$ ) gives an input resistor current of:

$$I_{in} = \frac{V_R}{R_{in}} = 143 \,\mu\text{A}$$

$$V_R = |V_{EE} - V_1| = 4.3 \,\text{V},$$

where:  $V_R$  = voltage drop across the input resistor,  $R_{in}$ , with a logic 1 input,

$V_{EE} = -5.2 \text{ V}$  supply voltage,

$V_1 = -0.9 \text{ V (a typical logic 1 level)}.$

The typical 50 k $\Omega$  value will use slightly less current, but either resistance value is very high compared to the output circuit impedance or the line impedance. The 350  $\mu A$  specification for MECL III applies only to the Hi-Z circuits. The 2 k $\Omega$  input impedance of the Lo-Z circuits requires an additional input current of:

$$\frac{V_R}{R_{in}} = \frac{4.3 \text{ V}}{2 \text{ k}\Omega} = 2.15 \text{ mA}.$$

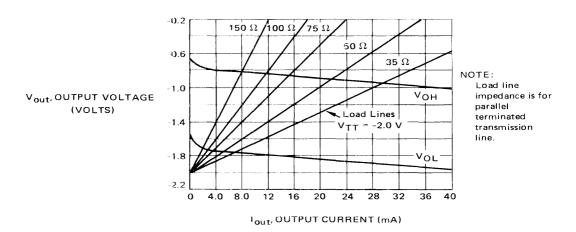

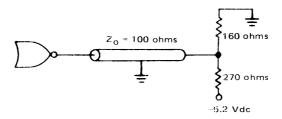

6-8... Output voltage levels are specified at currents representative of circuit operation. MECL I and MECL II are normally used with unterminated lines and are specified for a fanout of 25, i.e., 2.5 mA total output current. Although the MECL II line driver will drive transmission lines, the output levels are given at 2.5 mA to maintain consistency with the rest of the MECL II family. MECL 10,000 and MECL III are designed to drive 50  $\Omega$  transmission lines terminated to  $-2~\mathrm{Vdc}$  (measured from  $V_{CC}$ ). The current, ITT, required by the line termination is:

$$I_{TT} = \frac{V_{TT} - V_1}{Z_0} = \frac{(-2.0 + 0.9) \text{ V}}{50 \Omega} = -22 \text{ mA}.$$

Consequently, the outputs are specified with 50 ohm loads. The maximum permissible output currents of 20 mA for MECL I and MECL II, 50 mA for MECL 10,000, and 40mA for MECL III, insure a good safety margin over the specified currents.

- 9... The dc loading fanouts for MECL 10,000 and MECL III are computed by dividing the output current by the input current. However, both ac limitations and current needed in the transmission line termination can be expected to restrict the system fanout to a smaller number than the one computed.

- 10... Two techniques are used to measure circuit input capacitance. One method uses an impedance meter, such as the H.P. 4815A RF Vector Impedance Meter, to measure impedance and phase angle. The other technique uses a time domain reflectometer (TDR) to measure the effect of capacitance on the impedance of a transmission line. (The mathematical relationships used to calculate input capacitance from TDR data are presented later in Chapter 7). Although small, the

input capacitance will affect system rise time and transmission line propagation delay as a function of fanout at high MECL speeds.

- 11... DC output impedance can be calculated from measurements of the output voltage as a function of output current:  $Z = \Delta V/\Delta I$ . The gate output impedance must be much lower than the line characteristic impedance in order to provide full MECL signal levels when driving transmission lines. The output impedance (resistive load) is the parallel value of the output transistor and pulldown resistor. It should be noted that capacitance charging rate during a negative transition is limited by current flow through the pulldown circuit.

- 12-13... Gate propagation delay, edge speed, toggle rate, and power dissipation are standard data sheet information. Propagation delay  $(t_{pd})$  is measured from the 50% amplitude point on the input signal to the 50% amplitude point on the output signal. Normally the edge speed given is measured between the 10 and the 90% amplitude points on the output signal. However, because of the amount of rounding on the upper 10% of the MECL 10,000 edges, this family is specified with 20 to 80% edge speeds for easier correlation. Nevertheless, 3.5 ns is a typical 10 to 90% figure which can be compared with other families.

- 14... Toggle speeds are minimum rates for the flip-flops in a family. MECL II has flip-flops with speed figures ranging from 70 to 180 MHz. The 180 MHz figure listed in the table is for the MC1034, the highest-speed MECL II flip-flop.

- 15... Gate power here is specified for MECL II, MECL 10,000 and MECL III with open emitter outputs. The MECL I power figure is higher since that family is only available with output pulldown resistors. MECL II gates with pulldown resistors have specified powers ranging from 29 to 47 mW per gate depending on the number of gates per package which share a bias supply, and on the number of complementary outputs. Gate power for the MECL 10,000 and MECL III gates is specified with open emitter outputs, as is usual with most ECL product lines. The wide variety of output loads both resistors used with transmission lines and pulldown resistors makes a power specification under load difficult to define. In a system, the output power is added to the gate power to find total power.

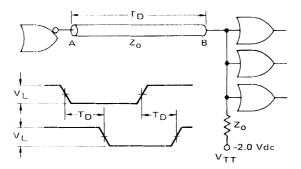

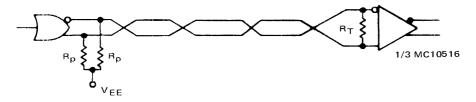

- 16-17... Open wire length and wire wrap usage are a function of edge speed and the propagation velocity of the wire. The distances shown are maxima, selected to give less than 100 mV undershoot at the receiving end of the line with a fanout of one. Additional information on line driving is found in Chapter 3. Wire wrap may be used with all families but MECL III. The 1 ns edges associated with MECL III cause too much reflection from the wire wrap connection to permit practical use. The open wire maximum line lengths still apply when using wire wraps, unless some form of resistor damping or line termination is used.

- 18...Damping resistors consist of small resistors (5 to 75 ohms) that are placed in series with a line at the output of the driving circuit to extend the permissible line length. The resistor provides a closer match between the line and the output impedance of the circuit than a direct connection. This match limits overshoot and ringing, and allows the use of line lengths somewhat greater than twice the non-damped lengths.

This technique is useful with all MECL circuits except low impedance (Lo-Z) MECL III. The reason is that the 2.2 mA input current required by the 2 k $\Omega$  input resistor would cause a voltage drop which would impose prohibitive loss of noise margin in the logic 1 state.

19... Separate  $V_{CC}$  inputs ( $V_{CC1}$ ,  $V_{CC2}$ ) are characteristic of MECL 10,000, MECL III, and some of the high speed MECL II circuits. The separate  $V_{CC}$  pins are used

to minimize any crosstalk between circuits in a package which might occur with the high switching currents when driving transmission lines. MECL I and MECL II circuits, not designed to be used with transmission lines, have no requirement for separate  $V_{CC}$  lines. Separate  $V_{CC}$  lines do not affect using the parts and only require that two package pins be connected to a single ground plane or ground bus.

- 20... Speed-power product is a measure of a logic family's efficiency. Propagation delay (nanoseconds) is multiplied by the gate power dissipation (milliwatts) to get a measure of efficiency in terms of energy (picojoules). It is interesting to note that gate efficiency has improved with each succeeding logic line introduced. The speed-power product is slightly inaccurate because power figures are used which do not include output loading (discussed previously). However, TTL speed-power products can be inaccurate also as they are generally computed for the circuits operating at a low rate. Such figures would be much worse for circuits operating near top switching rates.

- 21... Wired-OR is a technique used with all MECL circuits to obtain the logic OR function by connecting circuit outputs together. With MECL II a maximum of two output load resistors are recommended per Wired-OR connection to limit output current. When several (more than 5) circuits are connected with Wired-OR outputs, it is possible to get a noise spike on the output if all gates are at a 1 output, and all gates but one are simultaneously changed to a logic  $\emptyset$ . The noise spike is due to the one gate suddenly having to source the output current previously supplied by the other circuits. The pulse width is normally less than the gate propagation delay and of insufficient amplitude to propagate in the system.

- 22-25... The remaining family features are self-explanatory. Packaging and temperature range for MECL 10,000 are based on initially introduced circuits. Other configurations are being investigated to meet future requirements.

The design guidelines presented here are intended to assist the MECL user to apply MECL families in a system. The rules listed have been tried out in complete systems with good results. As rise times become less than 3 ns, special design rules must be followed. For rise times of 1.5 ns or shorter, designing with transmission lines is necessary.

MECL II, MECL 10,000, and MECL III logic families are treated separately because of the differences in their capabilities and in design techniques to be used. Reasons for the rules, methods for applying them, and test data are found in the following chapters under associated subjects. High speed MECL II clock drivers and flip-flops are not treated separately and should be used in the manner described for MECL 10,000. Otherwise the faster edges of these MECL II circuits may cause sufficient overshoot and ringing to seriously reduce noise immunity or cause false operation.

#### 1. MECL II Design Rules

The MECL II family of integrated circuits is designed to provide high circuit speed without special system layout techniques. This feature simplifies design with this form of emitter coupled logic because most of the techniques used with saturated logic apply to MECL II. The ability of MECL II to interface with the faster MECL 10,000 and MECL III families enables MECL II to be used in slower sections of very high speed systems to gain power economy, eased layout rules, and a large choice of logic functions.

Since MECL II rise, fall, and propagation delay times are typically each 4 ns, transmission line techniques are not required. Standard double-sided circuit boards and backplane wiring are normally used with MECL II.

Because of the wide variety of MECL II system sizes and interfaces, not all techniques will apply to every system. The designer should use these rules as guides, modifying them sensibly as required by his particular system.

#### A. Logic Design Considerations

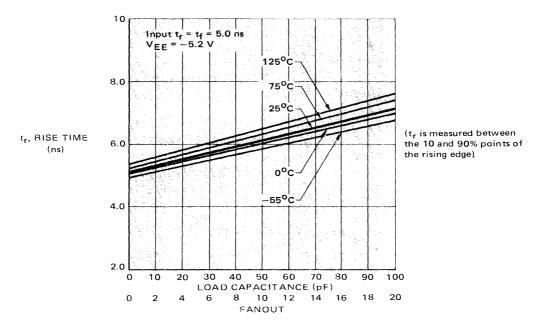

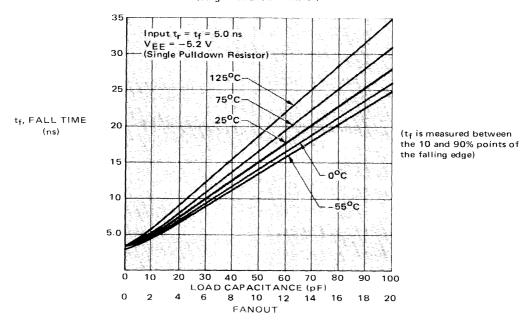

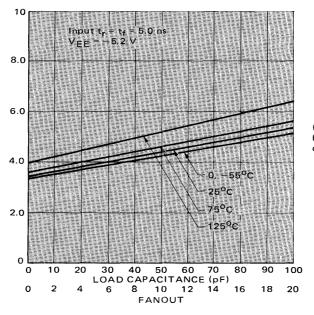

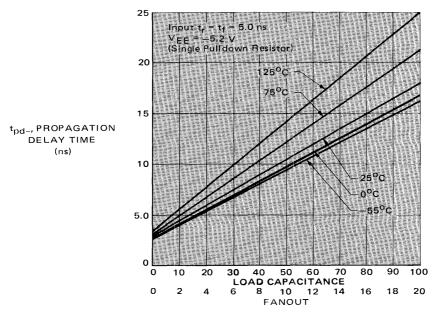

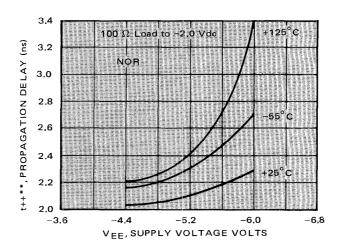

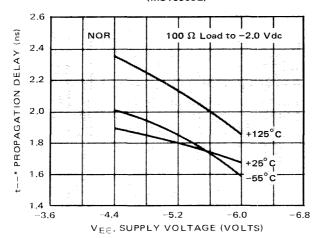

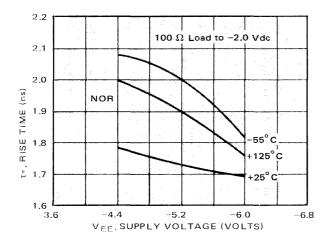

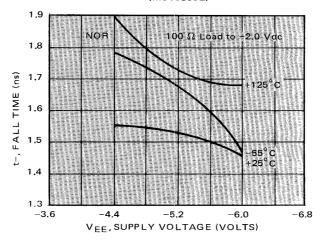

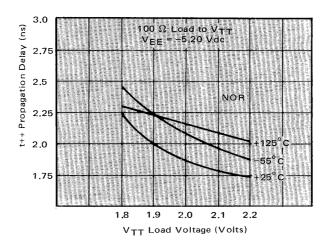

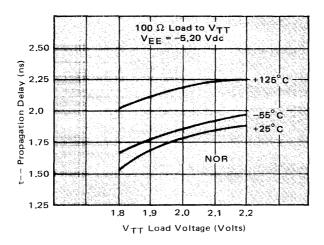

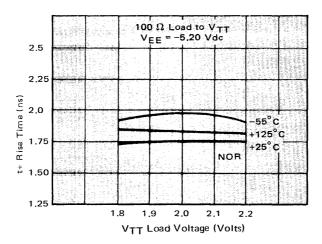

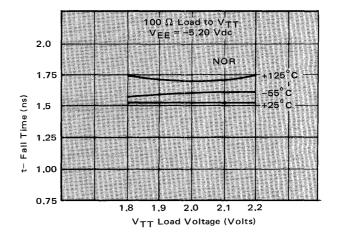

- 1. MECL rise, fall, and propagation delay times are a function of fanout and capacitive loading. Figures 2-1 through 2-4 show the reduction in speeds with load for MECL II. Consequently, when MECL II is operating near its upper speed limit, fanout should be restricted as indicated by the curves. Because of the emitter follower outputs, fall time and propagation delay to a  $\emptyset$  level is more affected by capacitive loading than rise time and propagation delay to a 1 level (note that the curves in Figure 2-4 are steeper than those in Figure 2-3).

- 2. Fall time and  $t_{pd}$  may be improved by adding a load resistor between the output and  $-5.2~Vdc.~A~1.8~k\Omega$  resistor will cut the delay caused by capacitive

#### 2-1: Rise Time versus Loading and Temperature

# 2-2: Fall Time versus Loading and Temperature (Single Pulldown Resistor)

#### 2-3: Propagation Delay tpd+ versus Loading and Temperature

tpd+, PROPAGATION

DELAY TIME (ns) (t<sub>pd+</sub> is measured between 50% points of the rising edges)

#### 2-4: Propagation Delay tpd- versus Loading and Temperature

(t<sub>pd</sub> - is measured between 50% points of the falling edges) loading nearly in half. Load resistors less than 1.8 k $\Omega$  and any load resistors with fanout greater than 10 should be avoided when using circuits with internal pulldown resistors. There may be a reduction in noise immunity when the output is in the 1 state, due to increased output emitter-follower VRF drop.

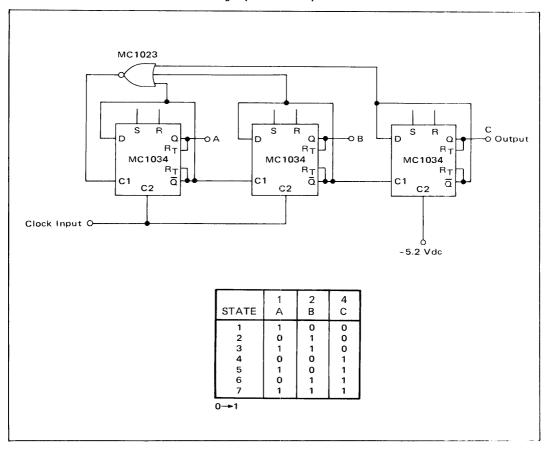

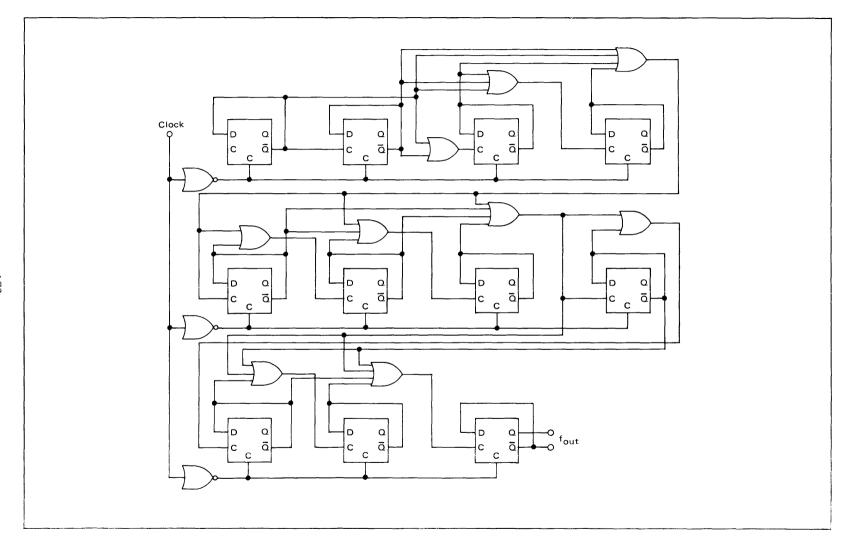

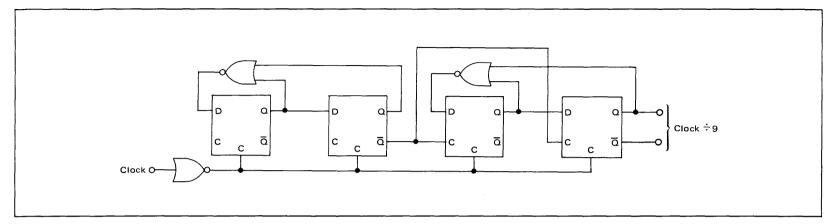

- 3. When driving flip-flops at high speed, clock driver circuits should be used. Such circuits are about twice as fast as the standard MECL II gates. As a result, clock drivers such as the MC1023 or MC1026 can provide the bandwidth necessary for clocking several flip-flops at once as in a shift register or a synchronous counter operating at high speed.

- 4. When driving a long string of flip-flops at speeds lower than 50 MHz (clock), two gates may be operated in parallel for additional drive. The MC1001 circuit is useful in this application since its multiple OR or NOR outputs may be wired together.

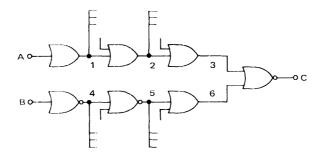

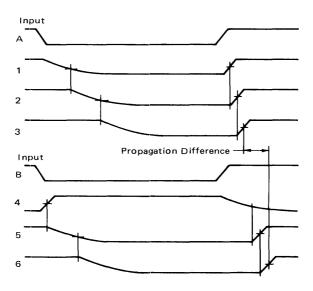

- 5. The high operating speed of MECL and the effect of loading on propagation delay must be considered when parallel circuits converge at one point, as shown in Figure 2-5. Unequal delays along paths A and B can result in momentary outputs at point C, each lasting a time equal to the propagation delay difference between A and B. This can be compensated for by additional timing in the form of a strobe, or by adjusting the fanouts along A and B. If possible, unused gate inputs can be paralleled to simulate a larger fanout where required; otherwise a small capacitor can be substituted for the needed fanout (about 5 pF per gate input is recommended).

2.5: Parallel Signal Paths

Under heavy loading, propagation delay along path A will be less than along path B because of the use of OR outputs in A as opposed to the NOR outputs in B. This difference (Figure 2-6) is due to the effect of loading on the fall time, rather than being due to a timing difference between OR and NOR outputs. As a matter of fact, under light loading, propagation delays for both NOR and OR outputs are identical.

When designing clocks for the high speed flip-flops, these timing differences become increasingly important. For example, the MC1034 flip-flop can toggle on a 2.5 ns pulsewidth clock. Consequently, timing chain skewing in the order of 2.5 ns can cause false operation.

#### 2-6: Propagation Differences

#### B. System Layout Considerations

- 1. System grounding and propagation delays in interconnecting leads are factors to be considered before laying out a system. Depending on the type of wire used, the wiring propagation time of a signal can greatly affect overall system speed. In normal backplane wiring it is realistic to expect a 2 ns per foot delay. Propagation delay is less in coaxial cable, but more for signal conductors in a multilayer circuit board.

- 2. System sections such as shift registers and synchronous counters should be on one card. Propagation delay between shift register clocks on separate boards can cause erroneous operation. Where timing is critical, equal length clock lines (to shift registers or other circuits on separate cards) should be run from a common clock to the card connectors. Such lines will also help limit overshoot and ringing (discussed further in section D, "Backplane Wiring").

- 3. The Wire-OR capability of MECL can be a powerful tool for reducing power, propagation delay, and package count. However, since the Wire-OR connection switches current when in operation (2.5 mA per load resistor), these leads should be kept as short as possible to avoid crosstalk. It is recommended that Wire-OR gates be kept within a package or between nearby packages. Wire-OR between circuit boards should be avoided. An increased propagation delay of 0.5 ns per Wire-OR should be allowed for.

- 4. Sections of a system where high fanout may be necessary (such as adders with lookahead carry) should be kept on one card. Signal path length should be reduced as fanout is increased to minimize both line delay and reflections.

#### C. Circuit Board Layout Techniques

- 1. The size of a MECL II system circuit board is not restricted by the logic family. System requirements should determine card size.

- 2. Standard single- or double-sided circuit boards with a good ground distribution may be used with MECL II. A low impedance ground is necessary since any noise on the ground line may be coupled into signal lines. Also, any voltage drop across ground will subtract from the noise immunity of the MECL II circuits. Grounding techniques are discussed at length in Chapter 5, "Power Distribution".

- 3. As with TTL, bypass capacitors, between ground and -5.2 V should be used with MECL. A 1.0  $\mu$ F capacitor should be located on the board at the power supply inputs. Bypass capacitors, 0.01  $\mu$ F to 0.1  $\mu$ F, should be connected-in once every four or five packages. When breadboarding with MECL II without an effective ground bus, an 0.1  $\mu$ F bypass capacitor should be used for every two packages. RF quality capacitors (low inductance) are recommended because of high circuit speeds.

Unlike TTL, MECL II does not have large current spikes in the circuit during switching, nor large current changes in the interconnecting circuit board paths during the transition between 1 and  $\emptyset$  levels. The function of the bypass capacitors during switching is to charge the small circuit input capacitance and circuit board stray capacitance, thus preventing spikes on the power leads.

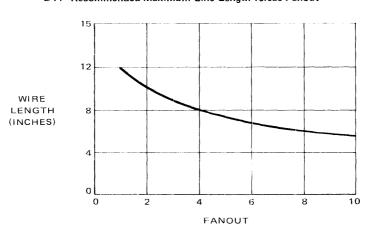

4. As with any high speed system, signal lines should be kept as short as possible to minimize ringing and overshoot, as well to simplify timing considerations arising from the propagation delay of a signal along a conductor. Ringing and overshoot are due to the intrinsic inductance and capacitance of the line itself, as well as lumped capacitance at the end of the line. Intrinsic inductance and capacitance are reduced by shortening the lines. A graph of recommended maximum line length as a function of fanout is shown in Figure 2-7. Since increased fanout adds capacitance at the end of the line, the line should be shortened as shown by the following curve.

2-7: Recommended Maximum Line Length versus Fanout

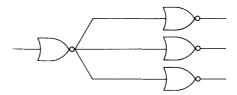

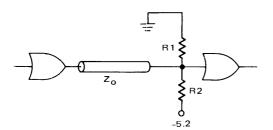

5. Longer line lengths are possible if a series damping resistor is used. The resistor is placed at the output of a gate, in series with the signal line as shown in

Figure 2-8. The resistor value depends on the fanout and the required line length. Resistors under 220 ohms for a fanout of one, or under 100 ohms for fanouts

#### 2-8: Damping Resistor

greater than five, are normally used for damping. Values larger than these produce rise and fall time degradation and loss of noise immunity due to IR voltage drop in the resistor. Resistor values are typically 47 ohms, and can be calculated exactly, if desired, from the information given in Chapters 3 and 7. Standard 1/4 watt carbon resistors are commonly used.

6. When driving large fanouts, line lengths can be increased by running parallel leads as shown in Figure 2-9. The distance between the parallel leads is not critical.

2-9: Parallel Signal Paths

This technique should be used for shift register clocks, counter resets, and other high fanout applications. Of course, for synchronous clock lines, clock skew delays should be matched. Series damping may also be used with parallel signal paths.

7. With most MECL II circuits, undershoot ringing on the logic 1 level is critical, since it subtracts from the noise immunity. For safe operating margins, undershoot should be limited to 150 mV. Exceptions to this rule are the MC1013, MC1027, and MC1032 ac coupled flip-flops. Because of their ac coupling, *overshoot* on the inputs should be limited to 100 mV. Shorter signal leads than shown in Figure 2-7 may be required when driving these circuits. Master-slave flip-flops, such as the MC1022 and MC1034, do not have this limitation and can be used with the same *undershoot* rules as the basic gates.

#### D. Backplane Wiring

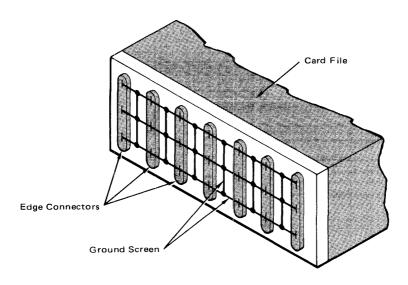

1. A ground screen is a good means for running a ground in the backplane wiring. A ground screen is made by connecting heavy bus wires to the connectors in a grid pattern before wiring the signal lines. The ground screen lines are wired both parallel to the connectors (tying to the connector pins), and perpendicular to the connectors (contacting multiple ground pins of each connector). This forms a grid network (cf Figure 5-6) of approximately 1 to 2 inch squares over which signals lines are then located.

- 2. Ferrite beads may be used in backplane wiring for longer signal runs. The recommended line lengths discussed for circuit cards also apply to backplane wiring. A ferrite bead on a wire limits rise and fall time to about 7 ns by attenuating the high frequency components of the signal. With a bead, lines up to three feet long can be driven without excessive overshoot.

- 3. Standard backplane wiring techniques are used with MECL II. Both wire wrapped and soldered connections perform well. Point-to-point wiring is recommended instead of a laced harness, to lessen line length and reduce crosstalk.

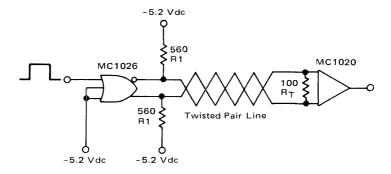

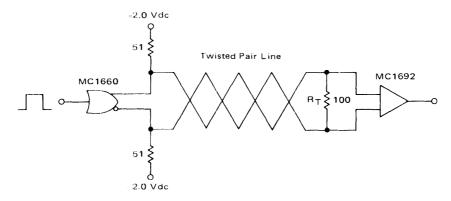

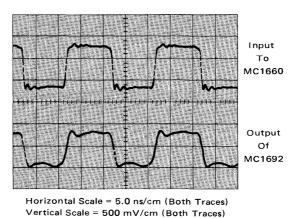

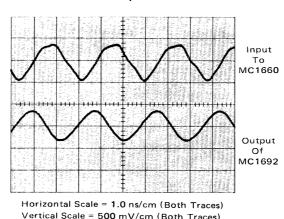

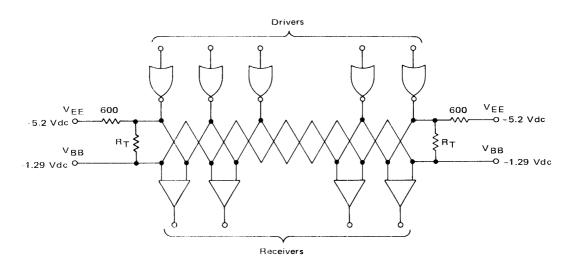

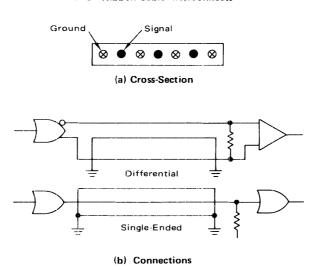

- 4. For longer signal paths (e.g. between panels or between cabinets) twisted pair lines are recommended. The twisted pair is connected to the OR and NOR outputs at the sending end and to an MC1020 line receiver at the receiving end. With this technique, long lines (hundreds of feet) have been driven with no system degradation other than propagation delay down the line.

#### E. System Considerations

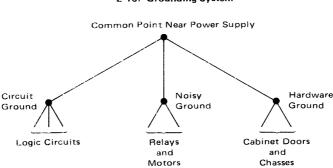

1. A good system ground is required for best performance. All grounds should be connected to a common ground point — normally near the power supply. All logic circuits are connected to a circuit ground. All relays, solenoids, motors and other noise generating devices are wired to a separate ground network connected to the common ground point. Standard noise suppression techniques should be employed (i.e. diodes across relays, and capacitors across dc motor brushes).

All mechanical parts such as panels, chassis, and cabinet doors should be grounded with a third ground. A mounting frame is often used for this if good conduction can be made at points of contact. If some pieces of equipment in the system are left ungrounded they may carry transient voltages that will interfere with the rest of the system. The three separate ground systems connected to a common

2-10: Grounding System

point will eliminate noise on the signal ground (cf Figure 2-10). Heavy ground leads should be used on large systems to minimize any voltage drop along the ground line run.

2. Twisted pair lines and line receivers are normally used between sections of a system unless line lengths can be kept short. Twisted pair lines should always be used between sections operating at widely differing temperatures (>40°C), or between sections not connected with a solid ground network.

#### 2. MECL 10,000 Design Rules

The MECL 10,000 family is a high speed (2 ns propagation delay), economical logic family designed to fill the gap between the MECL II (4 ns) and MECL III (1 ns) families and to meet the requirements for future high performance systems. The family is designed to drive terminated transmission lines with impedances as low as 50 ohms. Also, increased circuit complexity is possible due to high component densities and very low speed-power products. Finally, the relatively slow edge speeds of MECL 10,000 minimize wiring constraints on a logic system.

This section contains layout and design guidelines for power distribution, ground planes, terminations, line lengths, fanout loading, clock distribution, thermal considerations, and packaging, applicable to MECL 10,000.

#### A. General Considerations

- 1. Standard double-sided plated-through-hole printed circuit boards may be used with the MECL 10,000 family. However multilayer boards will permit a higher component density for a given board area. As a result interconnect lengths are reduced, making the highest speed systems possible.

- 2. Backplane wire wrapping is also acceptable using commercially available boards. Rules and techniques will be discussed for interconnection lengths and terminations as a function of loading.

- 3. Coaxial cable, ribbon cable, or twisted pair line is normally required to interface between drawers and card racks in a large system. Microstrip lines are normally required for clock distribution with either series or parallel termination. Series damping resistors can be used to facilitate driving long, unterminated lines.

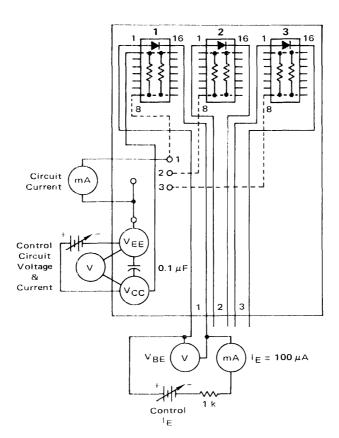

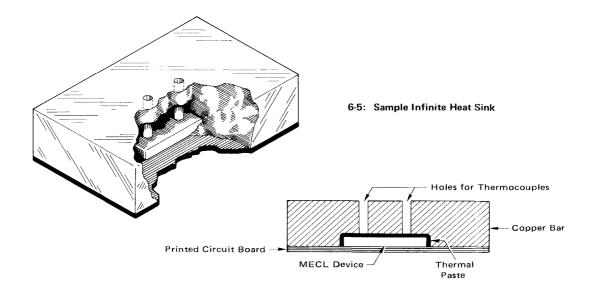

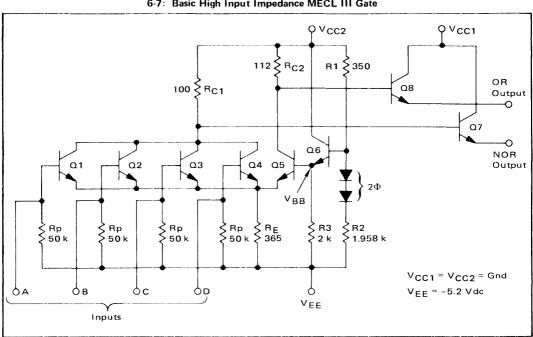

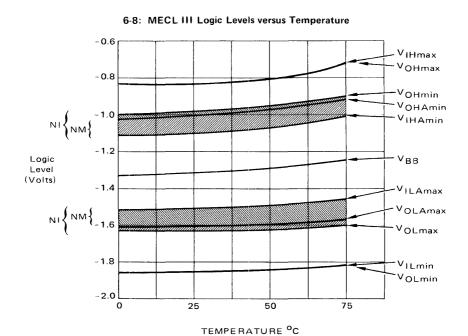

#### B. Printed Circuit Card Layout Techniques