# MOTOROLA

MOTOROLA Semiconductor Products Inc.

#### **LOW POWER SCHOTTKY**

**Design Considerations**

**Device Index and Selector Information**

**SSI Data Sheets**

MSI Data Sheets

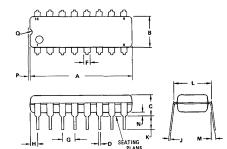

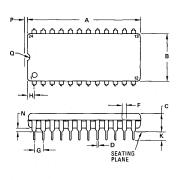

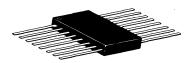

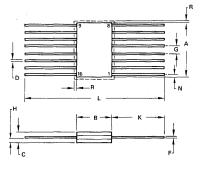

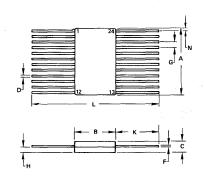

Ordering Information and Package Outlines

# **Volume 9/Series A**

prepared by Technical Information Center

# Semiconductor Data Library

#### LOW-POWER SCHOTTKY TTL

This book presents technical data for a broad line of low-power Schottky TTL integrated circuits. Complete specifications for the individual circuits are provided in the form of data sheets. In addition, the general characteristics and design considerations of this popular family are discussed, and selection guides are included to simplify the task of choosing the best combination of circuits for a system.

The information in this book has been carefully checked and is believed to be reliable; however, no responsibility is assumed for inaccuracies. Furthermore, this information does not convey to the purchaser of microelectronic devices any license under the patent rights of any manufacturer.

This information is published with permission of Fairchild Camera and Instrument Corp. under their copyright:

© 1975, Semiconductor Components Group, Fairchild Camera and Instrument Corp. "All Rights Reserved"

#### **TABLE OF CONTENTS**

| P                                         | age |

|-------------------------------------------|-----|

| INTRODUCTION                              | 1-1 |

| General Description                       | 1-3 |

| Circuit Characteristics                   | 1-4 |

| Input Configuration                       | 1-4 |

| Output Configuration                      | 1-4 |

| Output Characteristics                    |     |

| AC Switching Characteristics              | 1-6 |

| Definition of Terms and Symbols           |     |

|                                           |     |

| DESIGN CONSIDERATIONS                     | 2-1 |

| Supply Voltage and Temperature Range      |     |

| Noise Immunity                            |     |

| Fan-in and Fan-out                        |     |

| Wired-OR Applications                     |     |

| Unused Inputs                             |     |

| Interconnection Delays                    |     |

|                                           |     |

| DEVICE INDEX AND SELECTOR INFORMATION     | 3-1 |

| Numerical Index of Devices                | 3-2 |

| SSI Selector Guide                        | 3-6 |

| MSI Selector Guide by Function            |     |

|                                           |     |

| SSI DATA SHEETS                           | 4-1 |

|                                           |     |

| MSI DATA SHEETS                           | 5-1 |

|                                           |     |

| ORDERING INFORMATION AND PACKAGE OUTLINES | 6-1 |

# Introduction

## **LOW POWER SCHOTTKY**

#### INTRODUCTION

General Description — For many years TTL has been the most popular digital integrated circuit technology, offering a good compromise between cost, speed, power consumption and ease of use. As the price of TTL circuits decreased and the average IC complexity increased to MSI (medium scale integration), the cost and size of the power supply and the difficulty of removing the heat dissipated in the TTL circuits became increasingly important factors. Recent improvements in semiconductor processing have made it possible to not only reduce TTL power consumption significantly, but also to improve the speed over that of standard TTL.

LS Low Power Schottky TTL family combines a current and power reduction by a factor 5 (compared to 7400 TTL) with anti-saturation Schottky diode clamping and advanced processing, using shallower diffusions and higher sheet resistivity to achieve circuit performance better than conventional TTL. With a full complement of popular TTL functions available in LS, Low Power Schottky is destined to become the dominating TTL logic family.

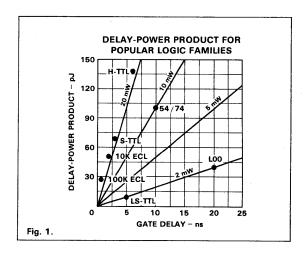

LS represents more than just a conventional speed versus power trade-off. This is best illustrated by *Figure 1* which compares LS to other TTL technologies. Note that LS dissipates eleven times less power than S or 74S, suffering a delay increase of only 1.7 times.

To the system designer the advantages of this new TTL family are many:

- Less supply current allows smaller, cheaper power supplies, reducing equipment cost, size and weight.

- Lower power consumption means less heat is generated, which simplifies thermal design. Packing density can be increased or cooling requirements reduced, or perhaps both. The number of cooling fans can be reduced, or slower, quieter ones substituted.

- Reliability is enhanced, since lower dissipation causes less chip temperature rise above ambient; lower junction temperature increases MTBF. Also, lower chip current densities minimizes metal related failure mechanisms.

- Less noise is generated, since the improved transistors and lower operating currents lead to much smaller current spikes than standard TTL, which means that fewer or smaller power supply decoupling capacitors are needed. In addition, load currents are only 25% of standard TTL and 20% of HTTL, which means that when a logic transition occurs that current changes along signal lines are proportionately smaller, as are the changes in ground current. Rise and fall times, and thus wiring rules, are the same as for standard TTL and more relaxed than for HTTL or STTL.

- Simplified MOS to TTL interfacing is provided, since the input load current of LSTTL is only 25% of a standard TTL load.

- Ideally suited for CMOS to TTL interfacing, CMOS and most other 4000 or 74C CMOS are designed to drive one LS input load at 5.0 V. The LS can also interface directly with CMOS operating up to 15 V due to the high voltage Schottky input diodes.

- Best TTL to MOS or CMOS driver. With the modest input current of MOS or CMOS as a load, any LS output will rise up to within 1 V of V<sub>CC</sub>, and can be pulled up to 10 V with an external resistor.

- Interfaces directly with other TTL types, as indicated in the input and output loading tables.

- The functions and pinouts are the same as the familiar 7400/9300 series, which means that no extensive learning period is required to become adept in their use.

#### Circuit Characteristics

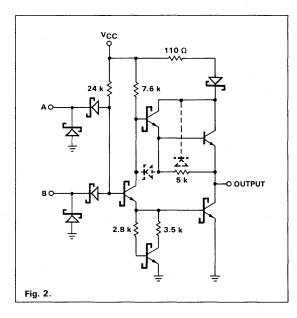

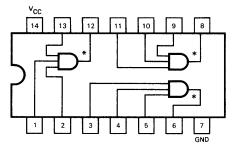

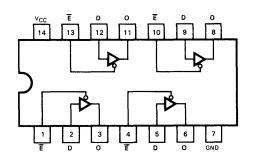

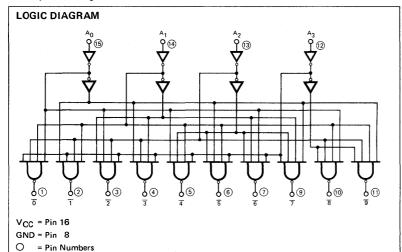

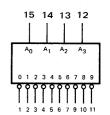

The LS circuit features are easiest explaned by using the LS00 2-input NAND gate as an example. The input/output circuits of all LS TTL, including, SSI, MSI are almost identical. While the logic function and the basic structure of LS circuits are the same as conventional TTL, there are also significant differences, as explained below:

#### Input Configuration

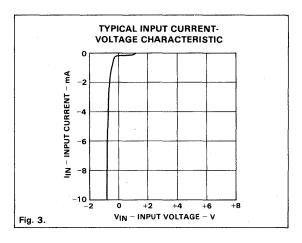

LSTTL is considered part of the TTL family, but it does not use the multi-emitter input structure that originally gave TTL its name. All LS TTL, with the exception of some early designs, employ a DTL-type input circuit which uses Schottky diodes to perform the AND function. Compared to the classical multi-emitter structure, this circuit is faster and it increases the input breakdown voltage to 15 V. Each input has a Schottky clamping diode which conducts when an input signal goes negative, as indicated by the input characteristic of Figure 3. This helps to simplify interfacing with those MOS circuits whose output signal tends to go negative. For a long TTL interconnection, which acts like a transmission line, the clamp diode acts as a termination for a negative-going signal and thus minimizes ringing. Otherwise, ringing could become significant when the finite delay along an interconnection is greater than one-fourth the fall time of the driving signal.

The effective capacitance of an LSTTL input is approximately 3.3 pF. For an input which serves more than one internal function, each additional function adds 1.5 pF.

#### **Output Configuration**

The output circuits of Low Power Schottky TTL have several features not found in conventional TTL. A few of these features are discussed below.

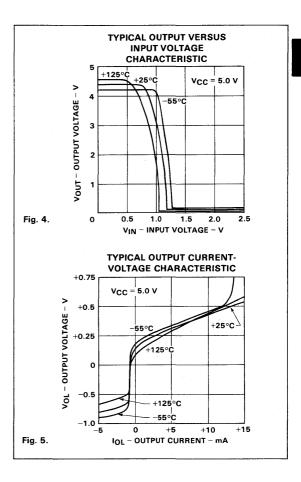

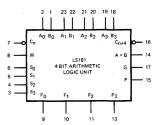

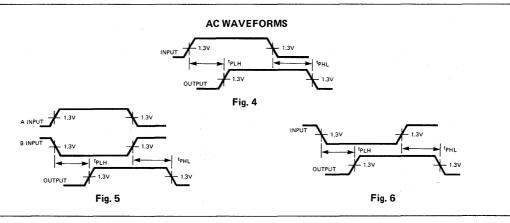

- The base of the pull-down output transistor is returned to ground through a resistor-transistor network instead of through a simple resistor. This squares up the transfer characteristics since it prevents conduction in the phase-splitter until base current is supplied to the pull-down output transistor. This also improves the propagation delay and transition time. (See Figure 4)

- The output pull-up circuit is a 2-transistor Darlington circuit with the base of the output transistor returned through a 5 kΩ resistor to the output terminal. (Unlike 74H and 74S where it is returned to ground, which is a more power consuming configuration). This configuration allows the output to pull-up to one VBE below VCC for low values of output current.

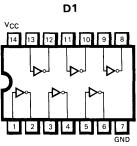

- As a unique feature, the LS outputs use a Schottky diode in series with the Darlington collector resistor. This diode allows the output to be pulled substantially higher than  $V_{CC}$  (e.g., to +10 V, convenient for interfacing with CMOS). For the same reason the parasistic diode of the base return resistor is connected to the Darlington common collector, not to VCC. Some early LS designs - the LS04, 32, 37, 40, 86, 112, 113, 114, 196, and 197 - do not have the diode in series with the Darlington collector resistor. These outputs are, therefore, clamped one diode drop above the positive supply voltage (V<sub>CC</sub>). These older circuits also contain a "speed-up" diode that supplies additional phase splitter current while the output goes from HIGH to LOW and also limits the maximum output voltage to one diode drop above V<sub>CC</sub>. Since this is the fastest transition even without additional speed-up, this diode is omitted in all new designs.

#### **Output Characteristics**

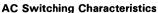

Figure 5 shows the LOW state output characteristics. For low I<sub>OL</sub> values, the pull-down transistor is clamped out of deep saturation which contributes to speed. The curves also show the clamping effect when I<sub>OL</sub> tends to go negative, as it often does due to reflections on a long interconnection after a negative-going transition. This clamping effect helps to minimize ringing.

The waveform of a rising output signal resembles an exponential, except that the signal is slightly rounded at the beginning of the rise. Once past this initial rounded portion, the starting edge rate is approximately 0.5 V/ns with a 15 pF load and 0.25 V/ns with a 50 pF load. For analytical purposes, the rising waveform can be approximated by the following expression.

$$v(t) = V_{OI} + 3.7 [1 - \exp(-t/T)]$$

where

T = 8 ns for

$$C_L$$

= 15 pF

= 16 ns for  $C_I$  = 50 pF

The waveform of a falling output signal resembles that part of a cosine wave between angles of 0° and 180°. Fall times from 90% to 10% are approximately 4.5 ns with a 15 pF load and 8.5 ns with a 50 pF load. Equivalent edge rates are approximately 0.8 V/ns and 0.4 V/ns, respectively. For analytical purposes, the falling waveform can be approximated by the following expression.

$$v(t) = V_{OL} + 1.9 \mu(t) [1 + \cos \omega t] - 1.9 \mu(t-a) [1 + \cos \omega (t-a)]$$

where

$\mu(t) = 0 \text{ for } t < 0$ = 1 for t > 0

and

$\mu(t-a) = 0$  for t < a= 1 for t > a For t in nanoseconds and  $C_L = 15$  pF,

$a = 7.5 \text{ ns}, \omega = 0.42$

For  $C_L = 50 pF$ ,

$a = 14 \text{ ns}, \ \omega = 0.23$

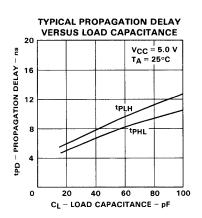

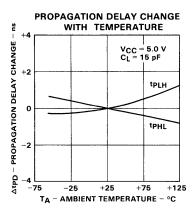

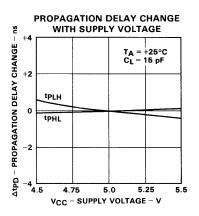

The average propagation delay of a Low Power Schottky gate is 5 ns at a load of 15 pF as shown in *Figure 6*. The delay times increase at an average of 0.08 ns/pF for larger values of capacitance load. These delay times are relatively insensitive to variations in power supply and temperature. The average propagation delay time changes less than 1.0 ns over temperature and less than

0.5 ns with V<sub>CC</sub> for the military temperature and voltage ranges. (See *Figures 8* and *9*).

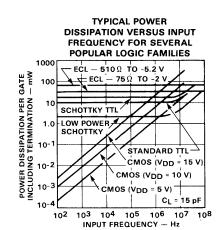

The power versus frequency characteristics of the LS family, as shown in *Figure 7*, indicate that at operating frequencies above 1 MHz the Low Power Schottky devices are more efficient than CMOS for most applications.

Fig. 6.

Fig. 8.

Fig. 7.

Fig. 9.

#### **DEFINITION OF SYMBOLS AND TERMS USED IN THIS DATA SHEET**

**CURRENTS** — Positive current is defined as conventional current flow into a device. Negative current is defined as conventional current flow out of a device. All current limits are specified as absolute values.

Supply current – The current flowing into the V<sub>CC</sub> supply terminal of a circuit with the specified input conditions and the outputs open. When not specified, input conditions are chosen to guarantee worst case operation.

I<sub>IH</sub> Input HIGH current – The current flowing into an input when a specified HIGH voltage is applied.

I<sub>|L</sub> Input LOW current — The current flowing out of an input when a specified LOW voltage is applied.

IOH

Output HIGH current — The leakage current flowing into a turned off open collector output with a specified HIGH output voltage applied. For devices with a pull-up circuit, the IOH is the current flowing out of an output which is in the HIGH state.

I<sub>OL</sub> Output LOW current - The current flowing into an output which is in the LOW state.

Output short circuit current — The current flowing out of an output which is in the HIGH state when that output is short circuited to ground (or other specified potential).

I<sub>OZH</sub>

Output off current HIGH — The current flowing into a disabled 3-state output with a specified HIGH output voltage applied.

I<sub>OZL</sub> Output off current LOW — The current flowing out of a disabled 3-state output with a specified LOW output voltage applied.

**VOLTAGES** — All voltages are referenced to ground. Negative voltage limits are specified as absolute values (*i.e.*, -10 V is greater than -1.0 V).

V<sub>CC</sub> Supply voltage – The range of power supply voltage over which the device is guaranteed to operate within the specified limits.

V<sub>CD(MAX)</sub> Input clamp diode voltage — The most negative voltage at an input when 18 mA is forced out of that input terminal. This parameter guarantees the integrity of the input diode which is intended to clamp negative ringing at the input terminal.

V<sub>IH</sub> Input HIGH voltage – The range of input voltages that represents a logic HIGH in the system.

V<sub>IH(MIN)</sub> Minimum input HIGH voltage — The minimum allowed input HIGH in a logic system. This value represents the guaranteed input HIGH threshold for the device.

V<sub>IL</sub> Input LOW voltage – The range of input voltages that represents a logic LOW in the system.

V<sub>IL(MAX)</sub> Maximum input LOW voltage — The maximum allowed input LOW in a system. This value represents the guaranteed input LOW threshold for the device.

V<sub>OH(MIN)</sub> Output HIGH voltage – The minimum voltage at an output terminal for the specified output current I<sub>OH</sub> and at the minimum value of V<sub>CC</sub>.

V<sub>OL(MAX)</sub> Output LOW voltage — The maximum voltage at an output terminal sinking the maximum specified load current I<sub>OL</sub>.

#### **DEFINITION OF SYMBOLS AND TERMS USED IN THIS DATA SHEET (Cont'd)**

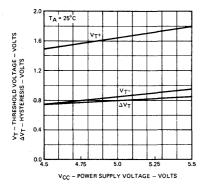

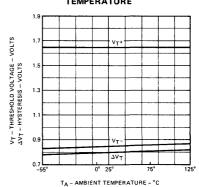

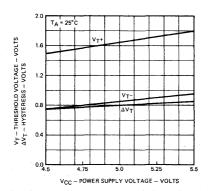

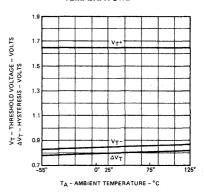

Positive-going threshold voltage - The input voltage of a variable threshold device  $V_{T+}$ (i.e., Schmitt Trigger) that is interpreted as a VIH as the input transition rises from below VT-(MIN)

Negative-going threshold voltage - The input voltage of a variable threshold device  $V_{T-}$ (i.e., Schmitt Trigger) that is interpreted as a V<sub>II</sub> as the input transition falls from above  $V_{T+(MAX)}$

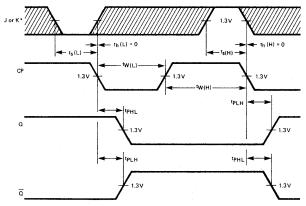

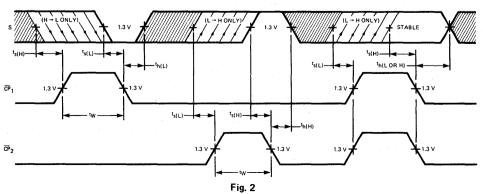

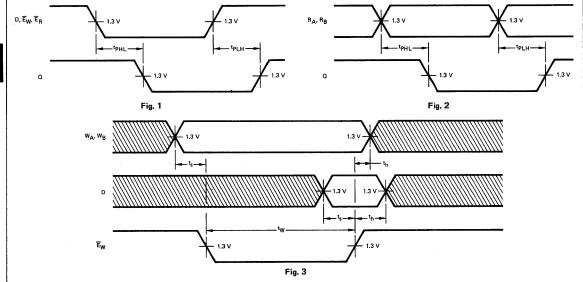

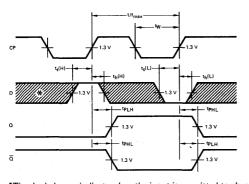

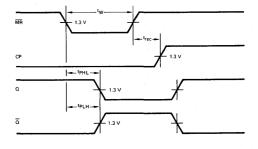

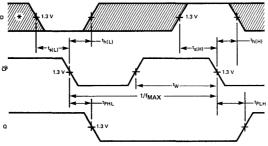

#### AC SWITCHING PARAMETERS

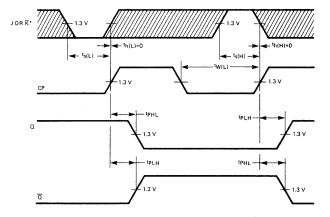

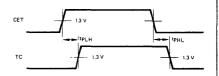

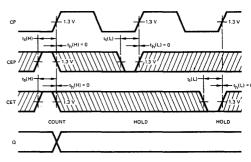

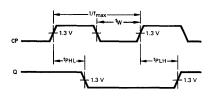

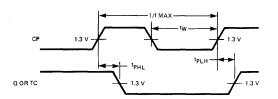

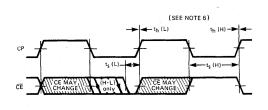

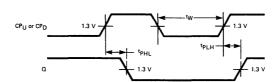

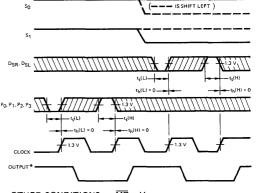

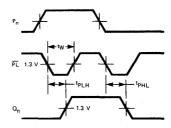

Toggle frequency/operating frequency — The maximum rate at which clock pulses may **fMAX** be applied to a sequential circuit. Above this frequency the device may cease to function.

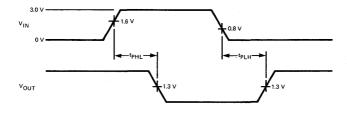

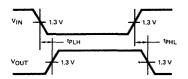

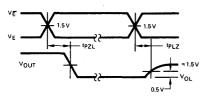

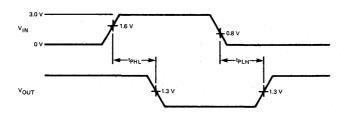

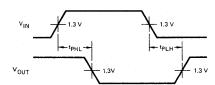

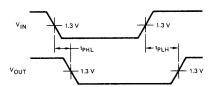

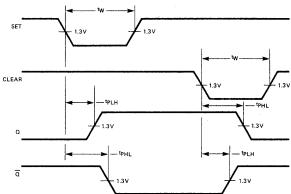

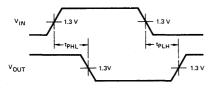

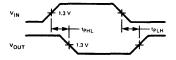

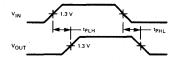

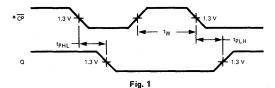

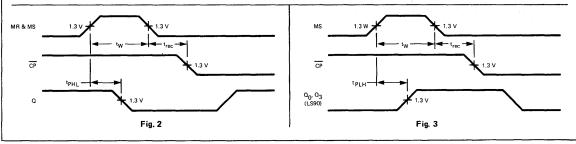

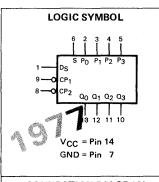

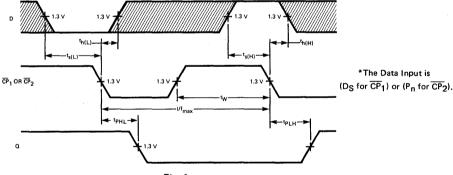

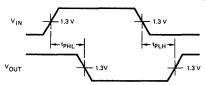

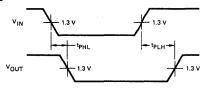

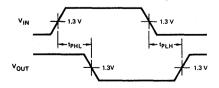

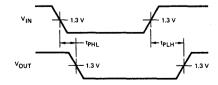

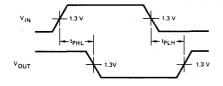

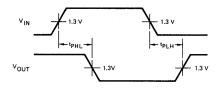

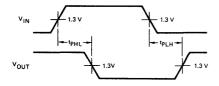

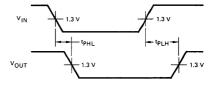

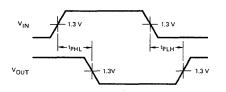

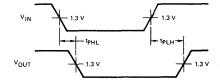

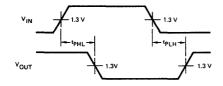

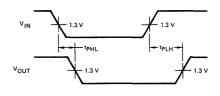

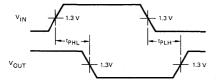

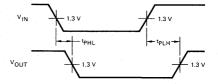

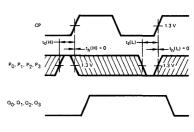

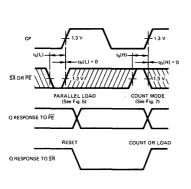

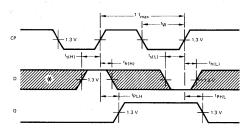

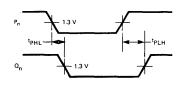

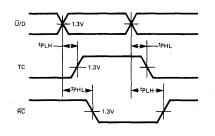

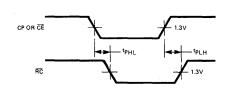

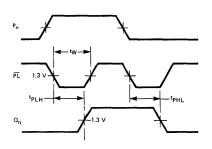

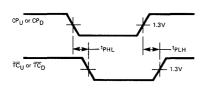

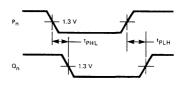

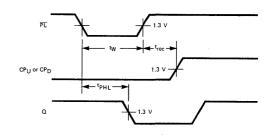

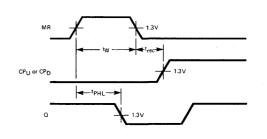

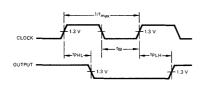

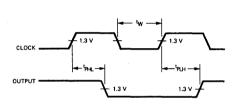

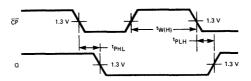

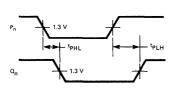

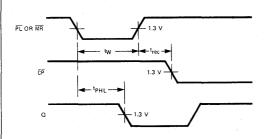

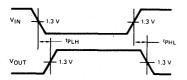

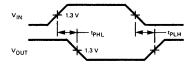

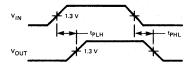

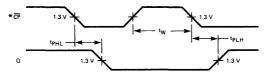

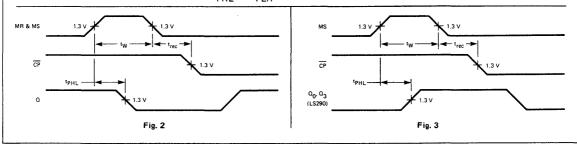

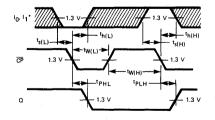

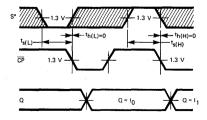

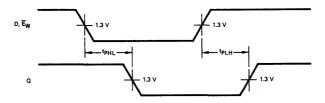

Propagation delay time — The time between the specified reference points, normally 1.3 V <sup>t</sup>PLH on the input and output voltage waveforms, with the output changing from the defined LOW level to the defined HIGH level.

Propagation delay time - The time between the specified reference points, normally 1.3 V <sup>t</sup>PHL on the input and output voltage waveforms, with the output changing from the defined HIGH level to the defined LOW level.

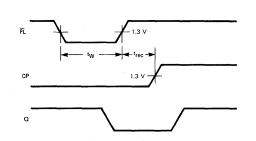

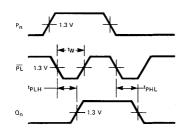

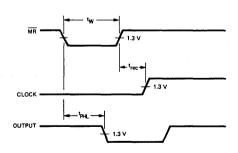

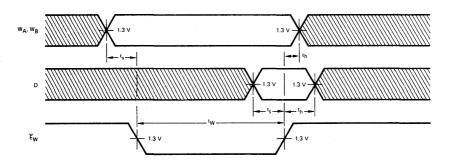

Pulse width - The time between 1.3 V amplitude points on the leading and trailing edges tw of a pulse.

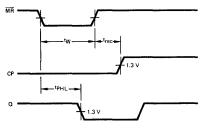

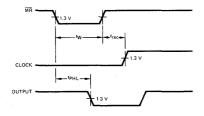

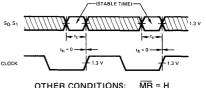

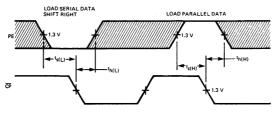

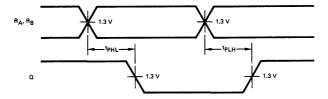

Hold time - The interval immediately following the active transition of the timing pulse th (usually the clock pulse) or following the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its continued recognition. A negative hold time indicates that the correct logic level may be released prior to the active transition of the timing pulse and still be recognized.

Set-up time - The interval immediately preceding the active transition of the timing pulse ts (usually the clock pulse) or preceding the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its recognition. A negative set-up time indicates that the correct logic level may be initiated sometime after the active transition of the timing pulse and still be recognized.

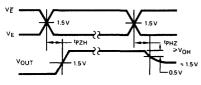

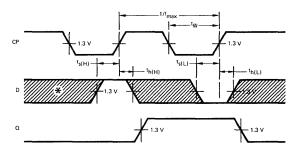

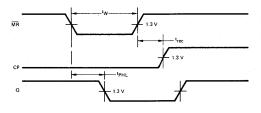

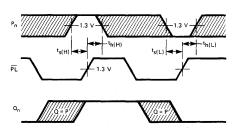

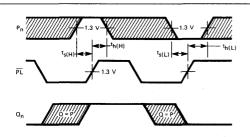

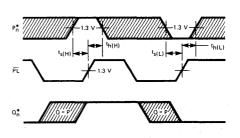

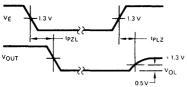

Output disable time (of a 3-state output) from HIGH level - The time between the <sup>t</sup>PHZ 1.3 V level on the input and a voltage 0.5 V below the steady state output HIGH level with the 3-state output changing from the defined HIGH level to a high-impedance (off) state.

Output disable time (of a 3-state output) from LOW level - The time between the 1.3 V <sup>t</sup>PLZ level on the input and a voltage 0.5 V above the steady state output LOW level with the 3-state output changing from the defined LOW level to a high-impedance (off) state.

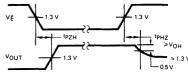

Output enable time (of a 3-state output) to a HIGH level — The time between the 1.3 V <sup>t</sup>PZH levels of the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to a HIGH level.

Output enable time (of a 3-state output) to a LOW level - The time between the 1.3 V <sup>t</sup>PZL levels of the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to a LOW level.

Recovery time - The time between the 1.3 V level on the trailing edge of an asynchronous input control pulse and the 1.3 V level on a synchronous input (clock) pulse such that the device will respond to the synchronous input.

trec

#### **LOW POWER SCHOTTKY**

# **Design Considerations**

mV mV mV mV mV

#### **DESIGN CONSIDERATIONS**

#### Supply Voltage and Temperature Range

The nominal supply voltage ( $V_{CC}$ ) for all TTL circuits is  $\pm 5.0$  V. Commercial grade parts are guaranteed to perform with a  $\pm 5\%$  supply tolerance ( $\pm 250$  mV) over an ambient temperature range of 0°C to 75°C. MIL-grade parts are guaranteed to perform with a  $\pm 10\%$  supply

tolerance ( $\pm 500$  mV) over an ambient temperature range of -55°C to +125°C.

TTL families may be mixed for optimum system design. The following tables specify the worst case noise immunity in mixed systems.

#### Worst Case TTL DC Noise Immunity / Noise Margins

#### **Electrical Characteristics**

|      |        | Military (-55 to +125°C) Commercial (0 to 75°C) |     |     |     |     |     |     |     |     |       |

|------|--------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| Item | Symbol | TTL Families                                    | VIL | VIH | VOL | Vон | VIL | VIH | VOL | Vон | Units |

| 6    | TTL    | Standard TTL (54/74)                            | 0.8 | 2.0 | 0.4 | 2.4 | 0.8 | 2.0 | 0.4 | 2.4 | V     |

| 7    | HTTL   | High Speed TTL (54H/74H)                        | 0.8 | 2.0 | 0.4 | 2.4 | 0.8 | 2.0 | 0.4 | 2.4 | V     |

| 8    | LPTTL  | Low Power TTL, LOO (MSI)                        | 0.7 | 2.0 | 0.3 | 2.4 | 0.8 | 2.0 | 0.3 | 2.4 | V     |

| 9    | STTL   | Schottky TTL (54S/74S), 93S00                   | 0.8 | 2.0 | 0.5 | 2.5 | 0.8 | 2.0 | 0.5 | 2.7 | V     |

| 10   | LSTTL  | Low Power Schottky TTL (54LS/74LS)              | 0.7 | 2.0 | 0.4 | 2.5 | 0.8 | 2.0 | 0.5 | 2.7 | V     |

$V_{OL}$  and  $V_{OH}$  are the voltages generated at the output.  $V_{IL}$  and  $V_{IH}$  are the voltage required at the input to generate the appropriate output levels. The numbers given above are guaranteed worst-case values.

#### LOW Level Noise Margins (Military)

#### HIGH Level Noise Margins (Military)

| <       |     |      |       |      |       | T     |

|---------|-----|------|-------|------|-------|-------|

| From To | TTL | HTTL | LPTTL | STTL | LSTTL | Units |

| TTL     | 400 | 400  | 300   | 400  | 300   | mV    |

| HTTL    | 400 | 400  | 300   | 400  | 300   | mV    |

| LPTTL   | 500 | 500  | 400   | 500  | 400   | mV    |

| STTL    | 300 | 300  | 200   | 300  | 200   | mV    |

| LSTTL   | 400 | 400  | 300   | 400  | 300   | mV    |

| F '//   |     |      |       |      |       |       |

| From To | TTL | HTTL | LPTTL | STTL | LSTTL | Units |

|---------|-----|------|-------|------|-------|-------|

| TTL     | 400 | 400  | 400   | 400  | 400   | mV    |

| HTTL    | 400 | 400  | 400   | 400  | 400   | mV    |

| LPTTL   | 400 | 400  | 400   | 400  | 400   | mV    |

| STTL    | 500 | 500  | 500   | 500  | 500   | mV    |

| LSTTL   | 500 | 500  | 500   | 500  | 500   | mV    |

From "VOL" to "VIL" From "VOH" to "VIH"

#### LOW Level Noise Margins (Commercial)

#### **HIGH Level Noise Margins (Commercial)**

|         |     | iviu. g | .5 (00 |      | ,     |       |         | 10.00 | 14191110 | 100   | o. o.a., |       |

|---------|-----|---------|--------|------|-------|-------|---------|-------|----------|-------|----------|-------|

| From To | TTL | HTTL    | LPTTL  | STTL | LSTTL | Units | From To | TTL   | HTTL     | LPTTL | STTL     | LSTTL |

| TTL     | 400 | 400     | 400    | 400  | 400   | mV    | TTL     | 400   | 400      | 400   | 400      | 400   |

| HTTL    | 400 | 400     | 400    | 400  | 400   | mV    | HTTL    | 400   | 400      | 400   | 400      | 400   |

| LPTTL   | 500 | 500     | 500    | 500  | 500   | mV    | LPTTL   | 400   | 400      | 400   | 400      | 400   |

| STTL    | 300 | 300     | 300    | 300  | 300   | mV    | STTL    | 700   | 700      | 700   | 700      | 700   |

| LSTTL   | 300 | 300     | 300    | 300  | 300   | mV    | LSTTL   | 700   | 700      | 700   | 700      | 700   |

om "VOL" to "VIL" From "VOH" to "VIH"

#### Fan-in and Fan-out

In order to simplify designing with Motorola TTL devices, the input and output loading parameters of all families are normalized to the following values:

- 1 TTL Unit Load (U.L.) = 40 μA in the HIGH state (logic "1")

- 1 TTL Unit Load (U.L.) = 1.6 mA in the LOW state (logic "0")

Input loading and output drive factors of all products described in this handbook are related to these definitions.

#### **EXAMPLES-INPUT LOAD**

- A 7400 gate, which has a maximum I<sub>1L</sub> of 1.6 mA and I<sub>1H</sub> of 40 µA is specified as having an input load factor of 1 U.L. (Also called a fan-in of 1 load.)

- 2. The 74LS95 which has a value of I<sub>IL</sub> = 0.8 mA and I<sub>IH</sub> of 40  $\mu$ A on the CP terminal, is specified as having an input LOW load factor of

$$\frac{0.8 \text{ mA}}{1.6 \text{ mA}}$$

or 0.5 U.L.

and an input HIGH load factor of

$$\frac{40 \mu A}{40 \mu A}$$

or 1 U.L.

3. The 74LSOO gate which has an I<sub>IL</sub> of 0.36 mA and an I<sub>IH</sub> of 20  $\mu$ A, has an input LOW load factor of

(normally rounded to 0.25 U.L.) and an input HIGH load factor of

$$\frac{20 \mu A}{40 \mu A}$$

or 0.5 U.L.

#### **EXAMPLES-OUTPUT DRIVE**

1. The output of the 7400 will sink 16 mA in the LOW (logic "0") state and source  $800~\mu\text{A}$  in the HIGH (logic "1") state. The normalized output LOW drive factor is therefore

$$\frac{16 \text{ mA}}{1.6 \text{ mA}} = 10 \text{ U.L.}$$

and the output HIGH drive factor is

$$\frac{800 \, \mu A}{40 \, \mu A}$$

or 20 U.L.

The output of the 74LSOO (Commercial Grade) will sink 8.0 mA in the LOW state and source 400 μA in the HIGH state. The normalized output LOW drive factor is

$$\frac{8.0 \text{ mA}}{1.6 \text{ mA}}$$

or 5 U.L.

and the output HIGH drive factor is

$$\frac{400 \, \mu A}{40 \, \mu A}$$

or 10 U.L.

Relative load and drive factors for the basic TTL families are given in *Table I*.

TABLE I

| 5 4 1 4 11 V | INPUT     | LOAD      | OUTPU   | T DRIVE  |  |

|--------------|-----------|-----------|---------|----------|--|

| FAMILY       | HIGH      | LOW       | HIGH    | LOW      |  |

| 74LS00       | 0.5 U.L.  | 0.25 U.L. | 10 U.L. | 5 U.L.   |  |

| 7400         | 1 U.L.    | 1 U.L.    | 20 U.L. | 10 U.L.  |  |

| 9000         | 1 U.L.    | 1 U.L.    | 20 U.L. | 10 U.L.  |  |

| 74H00        | 1.25 U.L. | 1.25 U.L. | 25 U.L. | 12.5 U.L |  |

| 74S00        | 1.25 U.L. | 1.25 U.L. | 25 U.L. | 12.5 U.L |  |

Values for MSI devices vary significantly from one element to another. Consult the appropriate data sheet for actual characteristics.

#### **Wired-OR Applications**

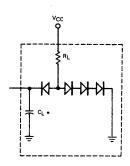

Certain TTL devices are provided with an "open" collector output to permit the Wired-OR (actually Wired-AND) function. This is achieved by connecting open collector outputs together and adding an external pull-up resistor.

The value of the pull-up resistor is determined by considering the fan-out of the OR tie and the number of devices in the OR tie. The pull-up resistor value is chosen from a range between a maximum value (established to maintain the required V<sub>OH</sub> with all the OR tied outputs HIGH) and a minimum value (established so that the OR tie fan-out is not exceeded when only one output is LOW).

# MINIMUM AND MAXIMUM PULL-UP RESISTOR VALUES

$$R_{X(MIN)} = \frac{V_{CC(MAX)} - V_{OL}}{I_{OL} - N_2(LOW) \cdot 1.6 \text{ mA}}$$

$$R_{X(MAX)} = \frac{V_{CC(MIN)} - V_{OH}}{N_1 \cdot I_{OH} + N_2(HIGH) \cdot 40 \mu A}$$

where:

$R_X$  = External Pull-up Resistor

N<sub>1</sub> = Number of Wired-OR Outputs

N<sub>2</sub> = Number of Input Unit Loads being Driven

I<sub>OH</sub> = I<sub>CEX</sub> = Output HIGH Leakage Current

I<sub>OL</sub> = LOW Level Fan-out Current of Driving Element

V<sub>OL</sub> = Output LOW Voltage Level (0.5 V) V<sub>OH</sub> = Output HIGH Voltage Level (2.4 V)

V<sub>CC</sub> = Power Supply Voltage

Example: Four 74LS03 gate outputs driving four other 74LS gates or MSI inputs.

$$R_{X \text{(MIN)}} = \frac{5.25 \text{ V} - 0.5 \text{ V}}{8 \text{ mA} - 1.6 \text{ mA}} = \frac{4.75 \text{ V}}{6.4 \text{ mA}} = 742 \Omega$$

$$R_{X(MAX)} = \frac{4.75 \text{ V} - 2.4 \text{ V}}{4 \cdot 100 \, \mu\text{A} + 2 \cdot 40 \, \mu\text{A}} = \frac{2.35 \text{ V}}{0.48 \text{ mA}} = 4.9 \text{ k}\Omega$$

where:

$N_1 = 4$

$N_2(HIGH) = 4 \cdot 0.5 \text{ U.L.} = 2 \text{ U.L.}$

$N_2(LOW) = 4 \cdot 0.25 \text{ U.L.} = 1 \text{ U.L.}$

$I_{OH} = 100 \,\mu A$

$I_{OL}$  = 8 mA

$V_{OL} = 0.5 V$

$V_{OH} = 2.4 V$

Any value of pull-up resistor between 742  $\Omega$  and 4.9 k $\Omega$  can be used. The lower values yield the fastest speeds while the higher values yield the lowest power dissipation.

#### **Unused Inputs**

For best noise immunity and switching speed, unused TTL inputs should not be left floating, but should be held between 2.4 V and the absolute maximum input voltage.

Two possible ways of handling unused inputs are:

- 1. Connect unused input to V<sub>CC</sub>. Most 74LS inputs have a breakdown voltage > 15 V and require, therefore, no series resistor. For all multi-emitter conventional TTL inputs, a 1 to 10 k $\Omega$  current limiting series resistor is recommended, to protect against V<sub>CC</sub> transients that exceed 5.5 V.

- Connect the unused input to the output of an unused gate that is forced HIGH.

CAUTION: Do not connect an unused LSTTL input to another input of the same NAND or AND function. This method, recommended for normal TTL, increases the input coupling capacitance and thus reduces the ac noise immunity.

#### Interconnection Delays

For those parts of a system in which timing is critical, designers should take into account the finite delay along the interconnections. These range from about 0.12 to 0.15 ns/inch for the type of interconnections normally used in TTL systems. Exceptions occur in systems using ground planes with STTL to reduce ground noise during a logic transition; ground planes give higher distributed capacitance and delays of about 0.15 to 0.22 ns/inch.

Most interconnections on a logic board are short enough that the wiring and load capacitance can be treated as a lumped capacitance for purposes of estimating their effect on the propagation delay of the driving circuit. When an interconnection is long enough that its delay is one-fourth to one-half of the signal transition time. the driver output waveform exhibits noticeable slope changes during a transition. This is evidence that during the initial portion of the output voltage transition the driver sees the characteristic impedance of the interconnection (normally 150  $\Omega$  to 200  $\Omega$ ), which for transient conditions appears as a resistor returned to the quiescent voltage existing just before the beginning of the transition. This characteristic impedance forms a voltage divider with the driver output impedance, tending to produce a signal transition having the same rise or fall time as in the no-load condition but with a reduced amplitude. This attenuated signal travels to the far end of the interconnection, which is essentially an unterminated transmission line, whereupon the signal starts doubling. Simultaneously, a reflection voltage is generated which has the same amplitude and polarity as the original signal, e.g., if the driver output signal is positive-going the reflection will be positive-going, and as it travels back toward the driver it adds to the line voltage. At the instant the reflection arrives at the driver it adds algebraically to the still-rising driver output, accelerating the transition rate and producing the noticeable change in slope.

If an interconnection is of such length that its delay is longer than half the signal transition time, the attenuated output of the driver has time to reach substantial completion before the reflection arrives. In the limit, the waveform observed at the driver output is a 2-step signal with a pedestal. In this circumstance the first load circuit to receive a full signal is the one at the far end, because of the doubling effect, while the last one to receive a full signal is the one nearest the driver since it must wait for the reflection to complete the transi-

tion. Thus, in a worst-cast situation, the net contribution to the overall delay is twice the delay of the interconnection because the initial part of the signal must travel to the far end of the line and the reflection must return.

When load circuits are distributed along an interconnection, the input capacitance of each will cause a small reflection having a polarity opposite that of the signal transition, and each capacitance also slows the transition rate of the signal as it passes by. The series of small reflections, arriving back at the driver, is subtractive and has the effect of reducing the apparent amplitude of the signal. The successive slowing of the transition rate of the transmitted signal means that it takes longer for the signal to rise or fall to the threshold level of any particular load circuit. A rough but workable approach is to treat the load capacitances as an increase in the intrinsic distributed capacitance of the interconnection. Increasing the distributed capacitance of a transmission line reduces its impedance and increases its delay. A good approximation for ordinary TTL interconnections is that distributed load capacitance decreases the characteristic impedance by about one-third and increases the delay by one-half.

Another advantage of LSTTL has to do with its output impedance during a positive-going transition. Whereas the low output impedance of STTL and HTTL allows these circuits to force a larger initial swing into a low impedance interconnection, the low output impedance also has a disadvantage. It makes the reflection coefficient negative at the driven end of the interconnection, a circumstance that exists any time a transmission line is terminated by an impedance lower than its characteristic impedance. This means that when the reflection from the (essentially) open end of the interconnection arrives back at the driver it will be re-reflected with the opposite polarity. The result is a sequence of reflected signals which alternate in sign and decrease in magnitude, commonly known as ringing. The lower the driver output impedance, the greater the amplitude of the ringing and the longer it takes to damp out.

The output impedance of LSTTL, on the other hand, is closer to the characteristic impedance of the interconnections commonly used with TTL, and ringing is practically non-existent. Thus no special packaging is required. This advantage, combined with excellent speed, modest edge rates and very low transient currents, are some of the reasons that designers have found LSTTL extremely easy to work with and very cost effective.

# **LOW POWER SCHOTTKY**

# **Device Index and Selector Information**

#### **NUMERICAL INDEX OF DEVICES**

| DEVICE              | DESCRIPTION                               | PAGE   |

|---------------------|-------------------------------------------|--------|

| SN54LS00/SN74LS00   | Quad 2-Input NAND Gate                    | 4-3    |

| SN54LS02/SN74LS02   | Quad 2-Input NOR Gate                     | 4-4    |

| SN54LS03/SN74LS03   | Quad 2-Input NAND Gate (Open Collector)   |        |

| SN54LS04/SN74LS04   | Hex Inverter                              | 4-6    |

| SN54LS05/SN74LS05   | Hex Inverter (Open Collector)             | 4-7    |

| SN54LS08/SN74LS08   | Quad 2-Input AND Gate                     | 4-8    |

| SN54LS09/SN74LS09   | Quad 2-Input AND Gate (Open Collector)    |        |

| SN54LS10/SN74LS10   | Triple 3-Input NAND Gate                  | 4-10   |

| SN54LS11/SN74LS11   | Triple 3-Input AND Gate                   |        |

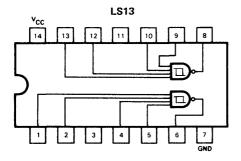

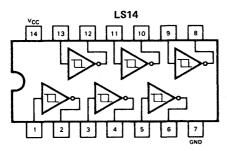

| SN54LS13/SN74LS13   | Dual 4-Input Schmitt Trigger              | 4-12   |

| SN54LS14/SN74LS14   | Hex Schmitt Trigger                       | 4-12   |

| SN54LS15/SN74LS15   | Triple 3-Input AND Gate (Open Collector)  |        |

| SN54LS20/SN74LS20   | Dual 4-Input NAND Gate                    |        |

| SN54LS21/SN74LS21   | Dual 4-Input AND Gate                     |        |

| SN54LS22/SN74LS22   | Dual 4-Input NAND Gate (Open Collector)   |        |

| SN54LS27/SN74LS27   | Triple 3-Input NOR Gate                   | 4-18   |

| SN54LS30/SN74LS30   | 8-Input NAND Gate                         | 4-19   |

| SN54LS32/SN74LS32   | Quad 2-Input OR Gate                      |        |

| SN54LS37/SN74LS37   | Quad 2-Input NAND Buffer                  | 4-21   |

| SN54LS38/SN74LS38   | Quad 2-Input NAND Buffer (Open Collector) |        |

| SN54LS40/SN74LS40   | Dual 4-Input NAND Buffer                  | 4-23   |

| SN54LS42/SN74LS42   | 1-of-10 Decoder                           | 5-2    |

| SN54LS51/SN74LS51   | Dual AND-OR-Invert Gate                   | 4-24   |

| SN54LS54/SN74LS54   | 2-3-3-2-Input                             | 4-25   |

| SN54LS55/SN74LS55   | 2-Wide 4-Input                            |        |

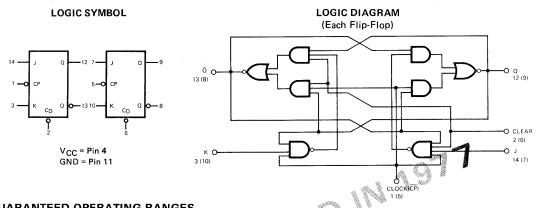

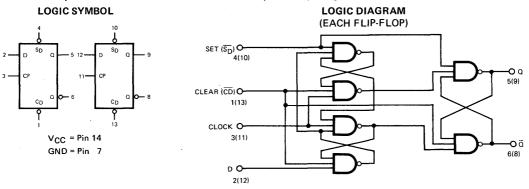

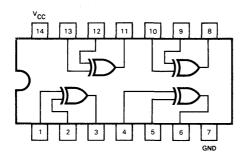

| SN54LS73/SN74LS73   | Dual JK Flip-Flop                         | 4-27   |

| SN54LS74/SN74LS74   | Dual D Flip-Flop                          | 4-29   |

| SN54LS83/SN74LS83   | 4-Bit Full Adder                          | 5-5    |

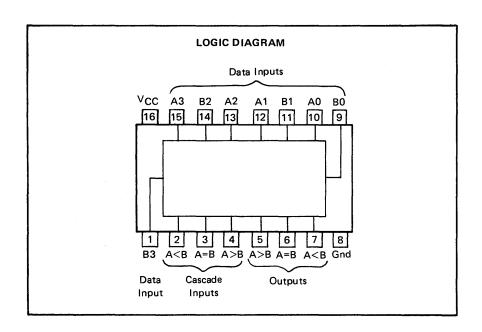

| SN54LS85/SN74LS85   | 4-Bit Magnitude Comparator                | 5-8    |

| SN54LS86/SN74LS86   | Quad Exclusive OR Gate                    | . 4-31 |

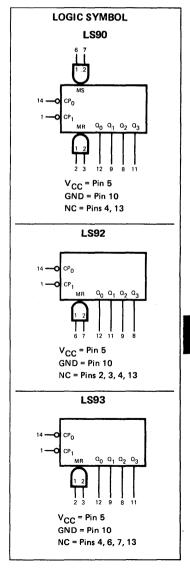

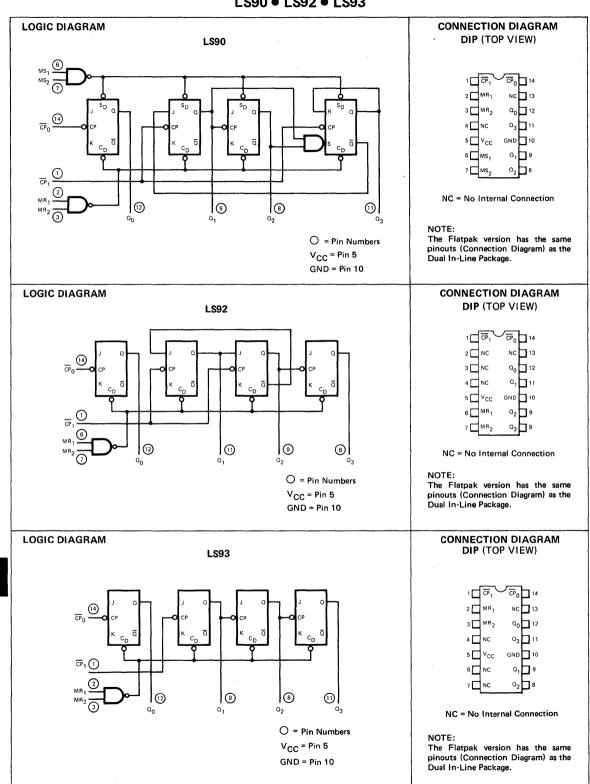

| SN54LS90/SN74LS90   | Decade Counter                            | 5-9    |

| SN54LS92/SN74LS92   | Divide-by-12 Counter                      | . 5-9  |

| SN54LS93/SN74LS93   | 4-Bit Binary Counter                      | . 5-9  |

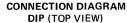

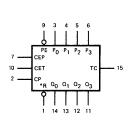

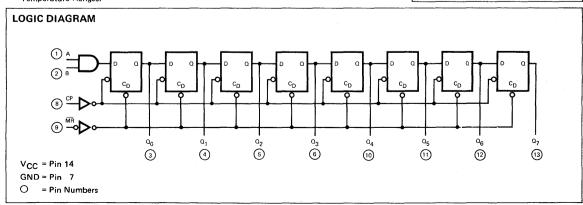

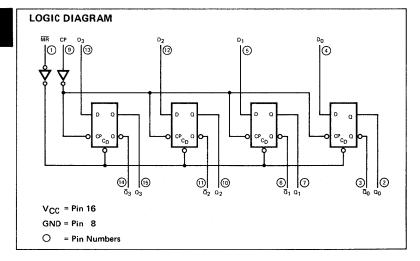

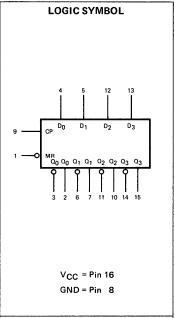

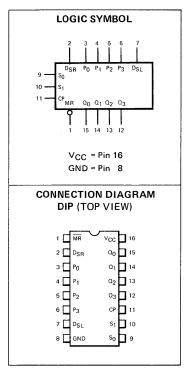

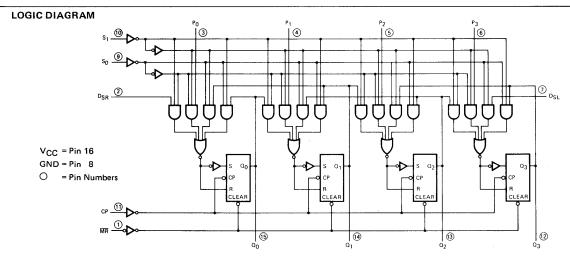

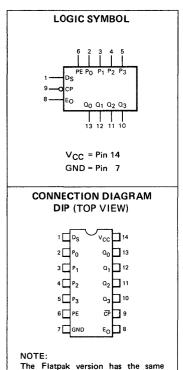

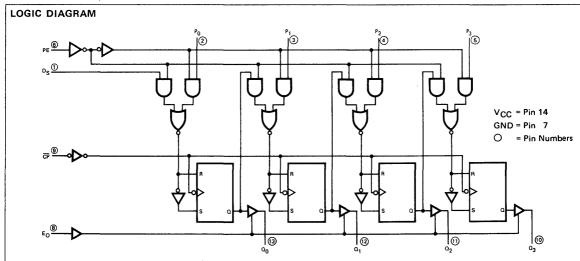

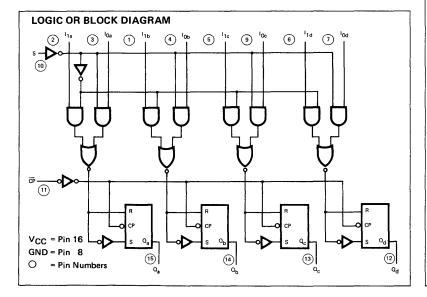

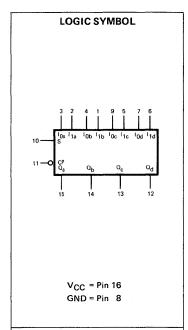

| SN54LS95/SN74LS95   | 4-Bit Shift Register                      | 5-15   |

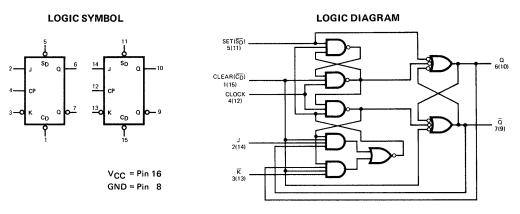

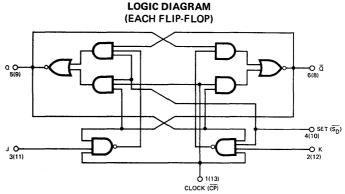

| SN54LS109/SN74LS109 | Dual JK Edge-Triggered Flip-Flop          | 4-32   |

| SN54LS112/SN74LS112 | Dual JK Edge-Triggered Flip-Flop          | . 4-34 |

| SN54LS113/SN74LS113 | Dual JK Edge-Triggered Flip-Flop          | 4-36   |

| SN54LS114/SN74LS114 | Dual JK Edge-Triggered Flip-Flop          |        |

| SN54LS125/SN74LS125 | Quad 3-State Buffer (LOW Enable)          | . 4-40 |

| SN54LS126/SN74LS126 | Quad 3-State Buffer (HIGH Enable)         | 4-40   |

| SN54LS132/SN74LS132 | Quad 2-Input Schmitt Trigger              | 4-42   |

| SN54LS133/SN74LS133 | 13-Input NAND Gate                        | . 4-44 |

| SN54LS136/SN74LS136 | Quad Exclusive OR (Open Collector)        | 4-45   |

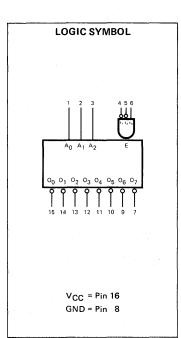

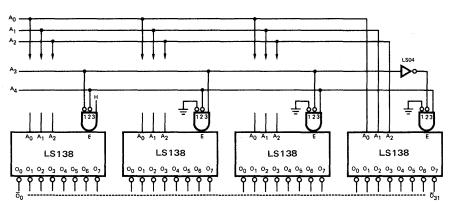

| SN54LS138/SN74LS138 | 1-of-8 Decoder/Demultiplexer              | 5-19   |

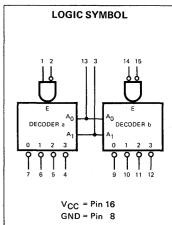

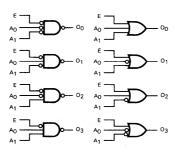

| SN54LS139/SN74LS139 | Dual 1-of-4 Decoder/Demultiplexer         | 5-22   |

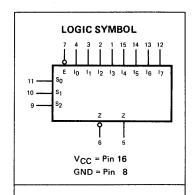

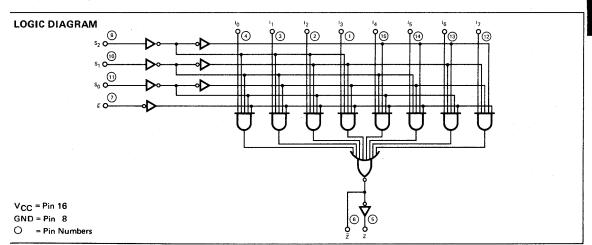

| SN54LS151/SN74LS151 | 8-Input Multiplexer                       | 5-25   |

| SN54LS152/SN74LS152 | 8-Input Multiplexer                       |        |

| SN54LS153/SN74LS153 | Dual 4-Input Multiplexer                  |        |

| SN54LS155/SN74LS155 | Dual 1-of-4 Decoder                       | 5-34   |

#### NUMERICAL INDEX OF DEVICES (Cont'd)

| DEVICE              | DESCRIPTION                                   | PAGE    |

|---------------------|-----------------------------------------------|---------|

| SN54LS156/SN74LS156 | Dual 1-of-4 Decoder (Open Collector)          | . 5-34  |

| SN54LS157/SN74LS157 | Quad 2-Input Multiplexer (Non-Inverting)      |         |

| SN54LS158/SN74LS158 | Quad 2-Input Multiplexer (Inverting)          |         |

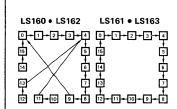

| SN54LS160/SN74LS160 | BCD Decade Counter, Asynchronous Reset        |         |

| SN54LS161/SN74LS161 | 4-Bit Binary Counter, Asynchronous Reset      |         |

| SN54LS162/SN74LS162 | BCD Decade Counter, Synchronous Reset         |         |

| SN54LS163/SN74LS163 | 4-Bit Binary Counter, Synchronous Reset       |         |

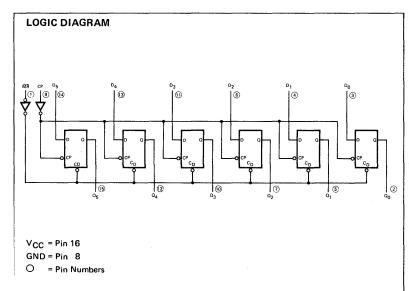

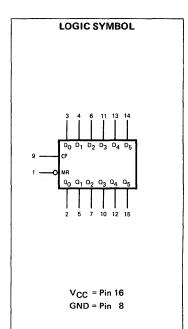

| SN54LS164/SN74LS164 | 8-Bit Shift Register (Serial In-Parallel Out) |         |

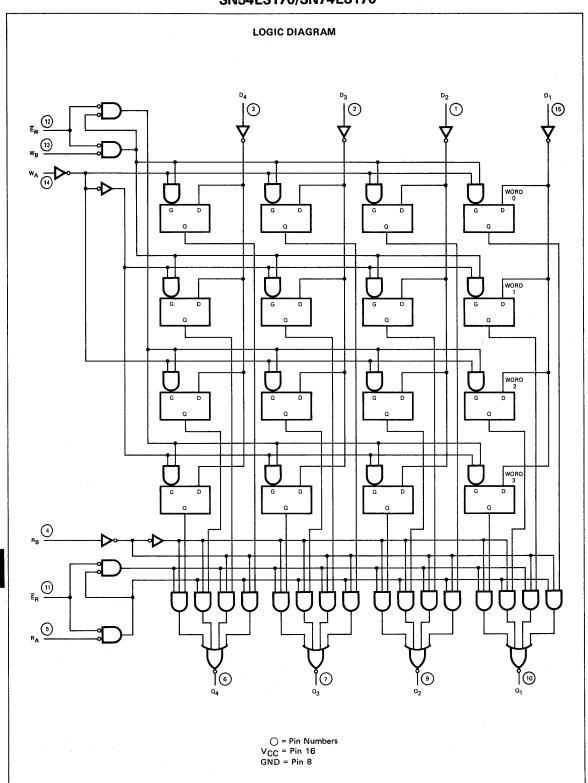

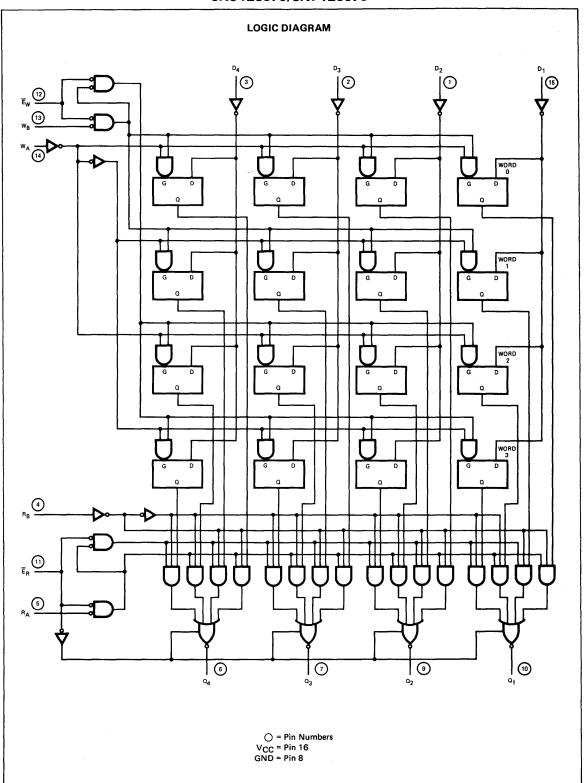

| SN54LS170/SN74LS170 | 4 x 4 Register File (Open Collector)          |         |

| SN54LS174/SN74LS174 | Hex D Flip-Flop w/Clear                       |         |

| SN54LS175/SN74LS175 | Quad D Flip-Flop w/Clear                      |         |

| SN54LS181/SN74LS181 | 4-Bit ALU                                     |         |

| SN54LS190/SN74LS190 | Up/Down Decade Counter                        | . 5-68  |

| SN54LS191/SN74LS191 | Up/Down Binary Counter                        |         |

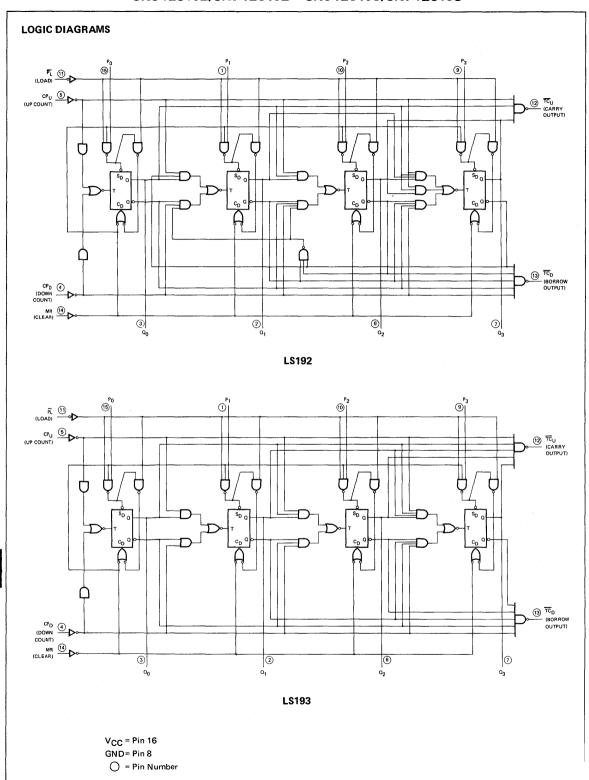

| SN54LS192/SN74LS192 | Up/Down Decade Counter                        | . 5-75  |

| SN54LS193/SN74LS193 | Up/Down Binary Counter                        |         |

| SN54LS194/SN74LS194 | 4-Bit Right/Left Shift Register               | . 5-81  |

| SN54LS195/SN74LS195 | 4-Bit Shift Register                          | . 5-85  |

| SN54LS196/SN74LS196 | Decade Counter                                | . 5-89  |

| SN54LS197/SN74LS197 | 4-Bit Binary Counter                          | . 5-89  |

| SN54LS251/SN74LS251 | 8-Input Multiplexer (3-State)                 |         |

| SN54LS253/SN74LS253 | Dual 4-Input Multiplexer (3-State)            | . 5-99  |

| SN54LS257/SN74LS257 | Quad 2-Input Multiplexer (3-State)            | . 5-102 |

| SN54LS258/SN74LS258 | Quad 2-Input Multiplexer (3-State)            | . 5-105 |

| SN54LS259/SN74LS259 | 8-Bit Addressable Latch                       | 5-108   |

| SN54LS266/SN74LS266 | Quad Exclusive NOR (Open Collector)           |         |

| SN54LS279/SN74LS279 | Quad Set-Reset Latch                          |         |

| SN54LS283/SN74LS283 | 4-Bit Full Adder (Rotated LS83)               | . 5-109 |

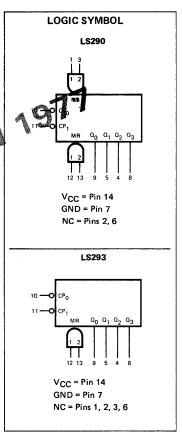

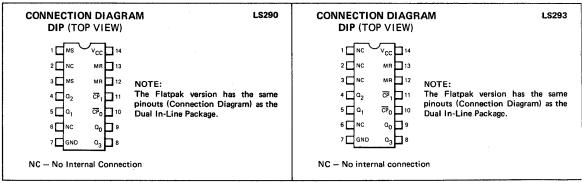

| SN54LS290/SN74LS290 | Decade Counter                                |         |

| SN54LS293/SN74LS293 | 4-Bit Binary Counter                          |         |

| SN54LS295/SN74LS295 | 4-Bit Shift Register (3-State)                |         |

| SN54LS298/SN74LS298 | Quad 2-Input Multiplexer w/Output Latches     |         |

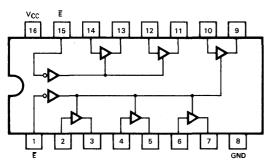

| SN54LS365/SN74LS365 | Hex Buffer w/Common Enable (3-State)          |         |

| SN54LS366/SN74LS366 | Hex Inverter w/Common Enable (3-State)        |         |

| SN54LS367/SN74LS367 | Hex Buffer, 4-Bit & 2-Bit (3-State)           |         |

| SN54LS368/SN74LS368 | Hex Inverter, 4-Bit & 2-Bit (3-State)         | . 4-48  |

| SN54LS670/SN74LS670 | 4 x 4 Register File (3-State)                 | 5-124   |

#### DEVICES TO BE INTRODUCED

Quad 2-Input NAND Gate (Open Collector)

DESCRIPTION

#### SN54LS12/SN74LS12 Triple 3-Input NAND Gate (Open Collector) SN54LS28/SN74LS28 Quad 2-Input NOR Buffer SN54LS47/SN74LS47 BCD-to-Seven Segment Decoder/Driver (Open Collector) SN54LS48/SN74LS48 BCD-to-Seven Segment Decoder/Driver SN54LS49/SN74LS49 BCD-to-Seven Segment Decoder/Driver (Open Collector) SN54LS76/SN74LS76 Dual JK Flip-Flop SN54LS78/SN74LS78 Dual JK Flip-Flop SN54LS89/SN74LS89 16 x 4 RAM SN54LS122/SN74LS122 Retriggerable Monostable Multivibrator (Int Res) SN54LS123/SN74LS123 Dual Retriggerable Monostable Multivibrator

SN54LS124/SN74LS124 Dual VCO

**DEVICE**

SN54LS01/SN74LS01

SN54LS165/SN74LS165 8-Bit Parallel In/Serial Out Shift Register

SN54LS168/SN74LS168 Up/Down Decade Counter SN54LS169/SN74LS169 Up/Down Binary Counter SN54LS173/SN74LS173 4-Bit Register, 3-State SN54LS182/SN74LS182 Carry Look-Ahead Generator SN54LS221/SN74LS221 Dual One-Shot (Very Stable) SN54LS240/SN74LS240 Octal Inverting Bus/Line Driver

Octal Bus/Line Driver SN54LS241/SN74LS241

SN54LS256/SN74LS256 Dual 4-Bit Addressable Latch

SN54LS260/SN74LS260 Dual 5-Input NOR Gate

Octal D Flip-Flop w/Master Reset (20-pin) SN54LS273/SN74LS273

SN54LS280/SN74LS280 9-Bit Parity Generator/Checker SN54LS299/SN74LS299 8-Bit Universal Shift Register SN54LS324/SN74LS324 VCO w/2-Phase Outputs

SN54LS352/SN74LS352 Dual 4-Input Multiplexer (Inverting LS153)

SN54LS353/SN74LS353 Dual 4-Input Multiplexer, 3-State SN54LS373/SN74LS373 Octal Transparent Latch (20-pin)

SN54LS374/SN74LS374 Octal D Flip-Flop SN54LS375/SN74LS375 Quad Latch

SN54LS377/SN74LS377 Octal D Flip-Flop w/Enable SN54LS378/SN74LS378 Hex D Flip-Flop w/Enable SN54LS379/SN74LS379 4-Bit D Flip-Flop w/Enable

SN54LS386/SN74LS386 Quad Exclusive OR SN54LS390/SN74LS390 **Dual Decade Counter** SN54LS393/SN74LS393 Dual 4-Bit Binary Counter SN54LS395/SN74LS395 Shift Register, 3-State

SN54LS398/SN74LS398 Quad 2-Input Multiplexer w/Output Register

SN54LS399/SN74LS399 LS398 w/Q & Q Outputs SN54LS490/SN74LS490 **Dual Decade Counter**

SN54LS502/SN74LS502 8-Bit Successive Approximation Register SN54LS503/SN74LS503 8-Bit Successive Approximation Register SN54LS504/SN74LS504 12-Bit Successive Approximation Register SN54LS540/SN74LS540 240 w/Inputs one side, Output on other SN54LS541/SN74LS541 241 w/Inputs one side. Output on other SN54LS573/SN74LS573 373 w/Inputs one side, Output on other

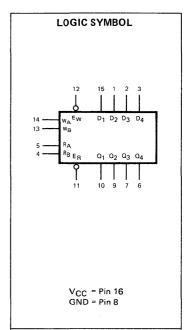

#### **SSI SELECTOR GUIDE**

| Function                                    | Low Power<br>Schottky<br>5 ns/2 mW | Std. TTL<br>54/74<br>10 ns/10 mW | High Speed<br>54/74H<br>6 ns/22 mW | High Speed<br>Schottky<br>3 ns/19 mW | Logic<br>Symbol | LSTTL<br>Data Sheet<br>Page No. |

|---------------------------------------------|------------------------------------|----------------------------------|------------------------------------|--------------------------------------|-----------------|---------------------------------|

| NAND Gates                                  |                                    |                                  |                                    |                                      |                 |                                 |

| Hex Inverters                               | 54/74LS04                          | 54/7404                          | 54/74H04                           | 54/74S04                             | D-1             | 4-6                             |

| Hex Inverts (O.C.)                          | 54/74LS05                          | 54/7405                          | 54/74H05                           | 54/74S05                             | D-1             | 4-7                             |

| Dual 4-Input Schmitt<br>Hex Schmitt Trigger | 54/74LS13<br>54/74LS14             | 54/7413<br>54/7414               |                                    |                                      | D-4<br>D-1      | 4-12<br>4-12                    |

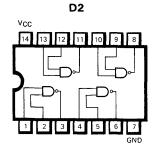

| Quad 2-Input                                | 54/74LS00                          | 54/7400                          | 54/74H00                           | 54/74S00                             | D-2             | 4-3                             |

| Quad 2-Input (O.C.)                         | 54/74LS03                          | 54/7403                          | 54/74H01                           | 54/74S03                             | D-2             | 4-5                             |

| Quad 2-Input (48 mA)                        | 54/74LS37                          | 54/7437                          |                                    |                                      | D-2             | 4-21                            |

| Quad 2-Input (O.C.<br>48 mA)                | 54/74LS38                          | 54/7438                          |                                    |                                      | D-2             | 4-22                            |

| Quad 2-Input Schmitt                        | 54/74LS132                         | 54/74132                         |                                    | 54/74S132                            | D-2             | 4-42                            |

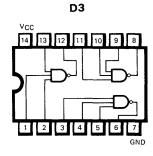

| Triple 3-Input                              | 54/74LS10                          | 54/7410                          | 54/74H10                           | 54/74S10                             | D-3             | 4-10                            |

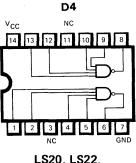

| Dual 4-Input                                | 54/74LS20                          | 54/7420                          | 54/74H20                           | 54/74S20                             | D-4             | 4-15                            |

| Dual 4-Input (O.C.)                         | 54/74LS22                          | 54/7422                          | 54/74H22                           | <b>5</b> 4/7 <b>4</b> S22            | D-4             | 4-17                            |

| Dual 4-Input Buffer                         | 54/74LS40                          | 54/7440                          | 54/74H40                           | 54/74S40                             | D-4             | 4-23                            |

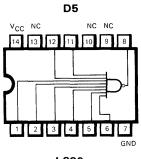

| 8-Input                                     | 54/74LS30                          | 54/7430                          | 54/74H30                           | 54/74S30                             | D-5             | 4-19                            |

| NOR Gates                                   |                                    |                                  |                                    |                                      |                 |                                 |

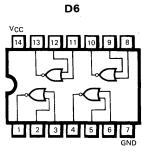

| Quad 2-Input                                | 54/74LS02                          | 54/7402                          |                                    | 54/74S02                             | D-6             | 4-4                             |

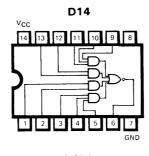

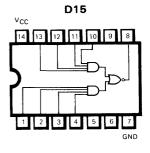

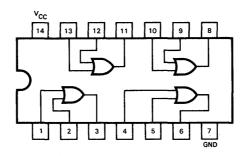

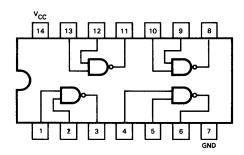

#### **SSI LOGIC SYMBOLS**

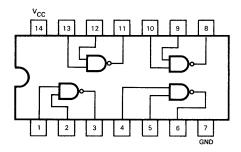

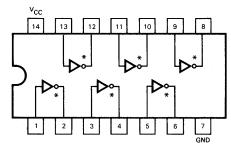

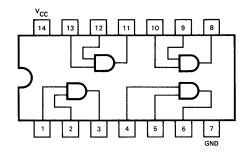

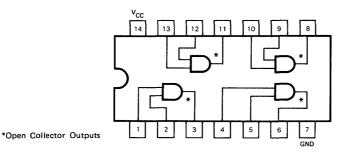

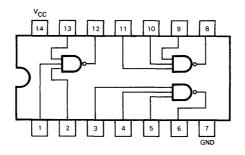

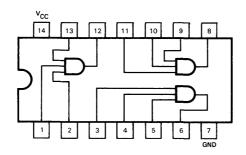

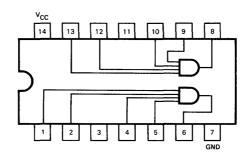

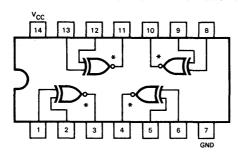

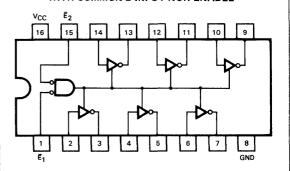

LS00, LS03, LS37 LS38, LS132

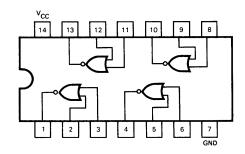

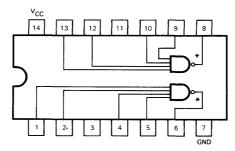

LS10

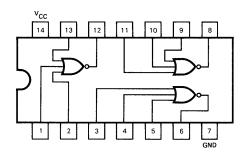

LS20, LS22, LS40

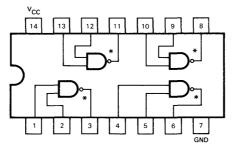

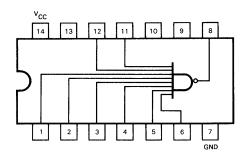

LS30

LS02

## **SSI SELECTOR GUIDE**

| Function              | Low Power<br>Schottky<br>5 ns/2 mW | Std. TTL<br>54/74<br>10 ns/10 mW | High Speed<br>54/74H<br>6 ns/22 mW | High Speed<br>Schottky<br>3 ns/19 mW | Logic<br>Symbol | LSTTL<br>Data Sheet<br>Page No. |

|-----------------------|------------------------------------|----------------------------------|------------------------------------|--------------------------------------|-----------------|---------------------------------|

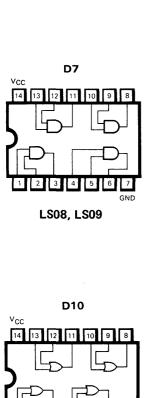

| AND Gates             |                                    |                                  |                                    |                                      | <b>I</b>        | I                               |

| Quad 2-Input          | 54/74LS08                          | 54/7408                          | 54/74H08                           | 54/74S08                             | D-7             | 4-8                             |

| Quad 2-Input (O.C.)   | 54/74LS09                          | 54/7409                          | 54/74H09                           | 54/74S09                             | D-7             | 4-9                             |

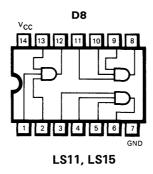

| Triple 3-Input        | 54/74LS11                          | 54/7411                          | 54/74H11                           | 54/74S11                             | D-8             | 4-11                            |

| Triple 3-Input (O.C.) | 54/74LS15                          |                                  | 54/74H15                           | 54/74S15                             | D-8             | 4-14                            |

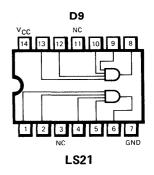

| Dual 4-Input          | 54/74LS21                          | 54/7421                          | 54/74H21                           |                                      | D-9             | 4-16                            |

| OR Gates              |                                    |                                  |                                    |                                      |                 |                                 |

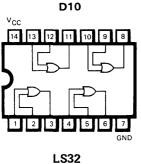

| Quad 2-Input          | 54/74LS32                          | 54/7432                          |                                    | 54/74832                             | D-10            | 4-20                            |

| Exclusive OR Gate     |                                    |                                  |                                    |                                      |                 |                                 |

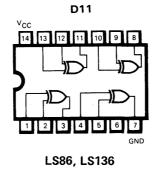

| Quad 2-Input          | 54/74LS86                          | 54/7486                          |                                    | 54/74\$86                            | D-11            | 4-31                            |

| Quad 2-Input (O.C)    | 54/74LS136                         |                                  |                                    |                                      | D-11            | 4-45                            |

| Exclusive NOR Gate    |                                    |                                  |                                    |                                      |                 |                                 |

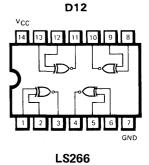

| Quad 2-Input (O.C.)   | 54/74LS266                         | 8242                             |                                    |                                      | D-12            | 4-46                            |

| AND-OR-INVERT Gate    | s                                  |                                  |                                    |                                      |                 |                                 |

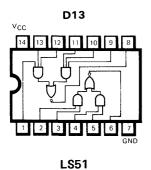

| Dual 2-2 Input        | 54/74LS51                          | 54/7451                          | 54/74H51                           | 54/74S51                             | D-13            | 4-24                            |

| 2-2-3-3 Input         | 54/74LS54                          |                                  |                                    |                                      | D-14            | 4-25                            |

| 4-4 Input             | 54/74LS55                          |                                  |                                    |                                      | D-15            | 4-26                            |

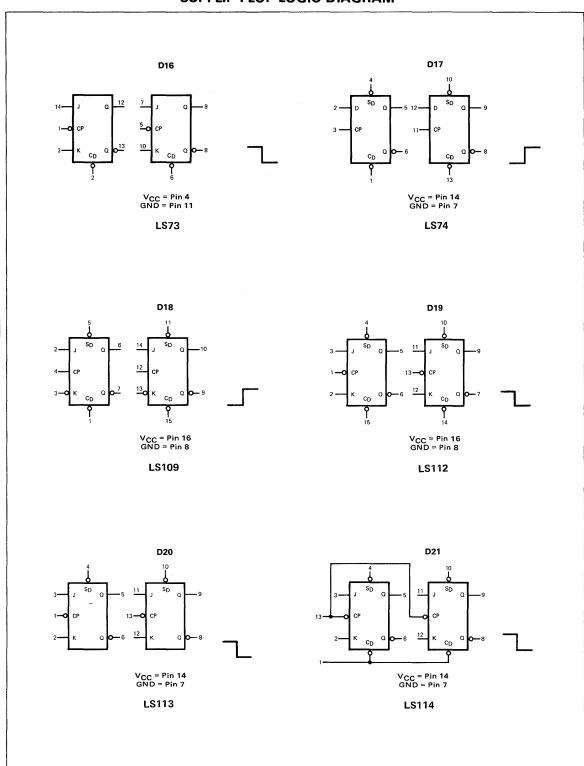

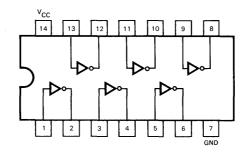

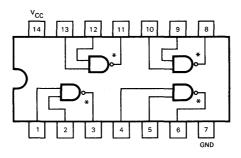

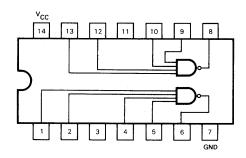

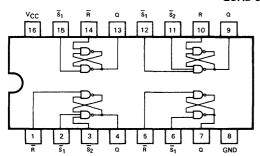

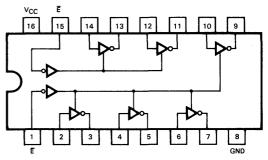

#### SSI LOGIC SYMBOLS

## **SSI SELECTOR GUIDE**

| Function        | Low Power<br>Schottky<br>5 ns/2 mW | Std. TTL<br>54/74<br>10 ns/10 mW | High Speed<br>54/74H<br>6 ns/22 mW | High Speed<br>Schottky<br>3 ns/19 mW | Logic<br>Symbol | LSTTL<br>Data Sheet<br>Page No. |

|-----------------|------------------------------------|----------------------------------|------------------------------------|--------------------------------------|-----------------|---------------------------------|

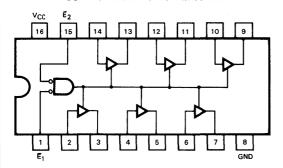

| Dual Flip-Flops |                                    |                                  |                                    |                                      |                 |                                 |

| Dual JK         | 54/74LS73                          | 54/7473                          | 55/74H73,<br>54/74H103             |                                      | D-16            | 4-27                            |

| Dual D          | 54/74LS74                          | 54/7474                          | 54/74H74                           | 54/74874                             | D-17            | 4-29                            |

| Dual JK         | 54/74LS109                         | 54/74109                         |                                    | 54/74S109                            | D-18            | 4-32                            |

| Dual JK         | 54/74LS112                         |                                  |                                    | 54/74S112                            | D-19            | 4-34                            |

| Dual JK         | 54/74LS113                         |                                  |                                    | 54/74S113                            | D-20            | 4-36                            |

| Dual JK         | 54/74LS114                         |                                  |                                    | 54/74S114                            | D-21            | 4-38                            |

#### 3

# **MSI SELECTOR GUIDE BY FUNCTION**

# **Arithmetic Operators** (CLA = Carry Lookahead)

| Function              | DEVICE NO. | Description                 | No. of Bits | pd<br>ns | Power Dissipation<br>mW (typ) | LSTTL<br>Data Sheet<br>Page No. |

|-----------------------|------------|-----------------------------|-------------|----------|-------------------------------|---------------------------------|

| Adder                 | 74LS83     | Full Binary 4-Bit w / Carry | 4           | 15       | 95                            | 5-6                             |

| Adder                 | 74LS283    | Full Binary 4-Bit w / Carry | 4           | 15       | 95                            | 5-109                           |

| Arithmetic Logic Unit | 74LS181    | ALU with External CLA       | 4           | 20       | 105                           | 5-63                            |

#### **Counters**

A = Asynchronous

S = Synchronous

| Function     | DEVICE NO. | Modulo            | Parallel Load | Clock Transition | Max Clock Rate<br>MHz (typ) | Clock to Q Output<br>Delay ns (typ) | Power Dissipation<br>mW (typ) | LSTTL<br>Data Sheet<br>Page No. |

|--------------|------------|-------------------|---------------|------------------|-----------------------------|-------------------------------------|-------------------------------|---------------------------------|

| Asynchronous | 74LS90     | 2x5               |               |                  | 50                          | 33                                  | 45                            | 5-9                             |

| Asynchronous | 74LS92     | 2x6               |               | Z                | 50                          | 33                                  | 45                            | 5-9                             |

| Asynchronous | 74LS93     | 2x8               |               | 7_               | 50                          | 46                                  | 45                            | 5-9                             |

| Asynchronous | 74LS196    | 2x5               | Α             | ٦_               | 60                          | 48                                  | 60                            | 5-89                            |

| Asynchronous | 74LS197    | 2x8               | Α             | 7_               | 70                          | 60                                  | 60                            | 5-89                            |

| Synchronous  | 74LS160    | 10<br>Presettable | s             | ٦                | 45                          | 15                                  | 95                            | 5-44                            |

| Synchronous  | 74LS161    | 16<br>Presettable | s             |                  | 45                          | 15                                  | 95                            | 5-44                            |

| Synchronous  | 74LS162    | 10<br>Presettable | s             | ٦                | 45                          | 15                                  | 95                            | 5-44                            |

| Synchronous  | 74LS163    | 16<br>Presettable | s             |                  | 45                          | 15                                  | 95                            | 5-44                            |

| Up / Down    | 74LS192    | 10                | Α             |                  | 40                          | 30                                  | 85                            | 5-75                            |

| Up / Down    | 74LS193    | 16                | Α             | 丁                | 40                          | 30                                  | 85                            | 5-75                            |

| Up / Down    | 74LS190    | 10                | Α             |                  | 40                          | 20                                  | 90                            | 5-68                            |

| Up / Down    | 74LS191    | 16                | Α             | J                | 40                          | 20                                  | 90                            | 5-68                            |

# Decoders/Demultiplexers Unit Load (UL) = 40 $\mu$ A HIGH/1.6 mA LOW

| Function    | DEVICE NO. | Address Inputs | Active LOW Enable | Active LOW Outputs | Open Collector<br>Output Voltage | Address Delay<br>ns (typ) | Enable Delay<br>ns (typ) | Power Dissipation<br>mW (typ) | Fan-out (UL) | LSTTL<br>Data Sheet<br>Page No. |

|-------------|------------|----------------|-------------------|--------------------|----------------------------------|---------------------------|--------------------------|-------------------------------|--------------|---------------------------------|

| Dual 1-of-4 | 74LS139    | 2+2            | 1+1               | 4+4                |                                  | 22                        | 19                       | 34                            | 5            | 5-22                            |

| Dual 1-of-4 | 74LS155    | 2              | 2+2               | 4+4                |                                  | 18                        | 15                       | 30                            | 5            | 5-34                            |

| Dual 1-of-4 | 74LS156    | 2              | 2+2               | 4+4                | 5.5 V                            | 33                        | 26                       | 31                            | 5            | 5-34                            |

| 1-Of-8      | 74LS259    | 3              | 1                 | 8                  |                                  | 30                        | 19                       | 60                            | 5            | 5-108                           |

| 1-of-8      | 74LS42     | 3              | 1                 | 8                  |                                  | 17                        | 17                       | 35                            | 5            | 5-3                             |

| 1-of-8      | 74LS138    | 3              | 3                 | 8                  |                                  | 22                        | 21                       | 34                            | - 5          | 5-19                            |

| 1-of-10     | 74LS42     | 4 (BCD)        |                   | 10                 |                                  | 17                        |                          | 35                            | 5            | 5-3                             |

| Lat | tche | <b>3</b> S/ | Flip | -FIC | ps |

|-----|------|-------------|------|------|----|

|     |      |             |      |      |    |

|                             | l          | 1           | Γ            | 1                              | I                                             |                                     | 1                           | T                             | <del></del>                     |

|-----------------------------|------------|-------------|--------------|--------------------------------|-----------------------------------------------|-------------------------------------|-----------------------------|-------------------------------|---------------------------------|

| Function                    | DEVICE NO. | Data Inputs | Common Clear | Enable/Clock<br>Inputs (Level) | Required Enable/Clock<br>Pulse Width ns (typ) | Enable/Clock to Q<br>Delay ns (typ) | Data to Q Delay<br>ns (typ) | Power Dissipation<br>mW (typ) | LSTTL<br>Data Sheet<br>Page No. |

| 4-Bit R-S Latch             | 74LS279    | 4x(RS)      | -            | -                              | -                                             | <b>-</b>                            | 14                          | 19                            | 4-47                            |

| 4-Bit D Latch               | 74LS196    | 4xD         | L            | 1(L)                           | 20                                            | 28                                  | 24                          | 60                            | 5-89                            |

| 4-Bit D Latch               | 74LS197    | 4xD         | L            | 1(L)                           | 20                                            | 28                                  | 24                          | 60                            | 5-89                            |

| 4-Bit D Flip-Flop           | 74LS175    | 4xD         | L            | 1()                            | 20                                            | 21                                  | -                           | 55                            | 5-60                            |

| 4-Bit D Flip-Flop           | 74LS298    | 4x2         | -            | 1(¬_ )                         | 20                                            | 20                                  | -                           | 65                            | 5-121                           |

| 6-Bit D Flip-Flop           | 74LS174    | 6           | L            | 1()                            | 20                                            | 21                                  | -                           | 80                            | 5-57                            |

| 8-Bit Add. Latch            | 74LS259    | 1xD         | L            | 1(L)<br>3 add. bits            | 11                                            | 18                                  | 28                          | 70                            | 5-108                           |

| 4x4 Register File           | 74LS170    | 4xD         | -            | 2                              | 25                                            | -                                   | 26                          | 125                           | 5-53                            |

| 4x4 Register File (3-state) | 74LS670    | 4xD         | -            | 2                              | 25                                            | -                                   | 24                          | 150                           | 5-124                           |

####

| Function     | DEVICE NO. | Enable Inputs             | True Output  | Complement Output | Select Delay<br>ns (typ) | Enable Delay<br>ns (typ) | Data Delay<br>ns (typ) | Power Dissipation<br>mW (typ) | Fan-Out (UL) | LSTTL<br>Data Sheet<br>Page No. |

|--------------|------------|---------------------------|--------------|-------------------|--------------------------|--------------------------|------------------------|-------------------------------|--------------|---------------------------------|

| Quad 2-Input | 74LS157    | 1                         | x            |                   | 18                       | 14                       | 9                      | 49                            | 5            | 5-38                            |

| Quad 2-Input | 74LS158    | 1                         |              | ×                 | 16                       | 12                       | 7                      | 24                            | 5            | 5-41                            |

| Quad 2-Input | 74LS257    | 1                         | 3-State      |                   | 14                       | 16                       | 12                     | 50                            | 5            | 5-102                           |

| Quad 2-Input | 74LS258    | 1                         |              | 3-State           | 12                       | 16                       | 10                     | 35                            | 5            | 5-105                           |

| Quad 2-Input | 74LS298    | Clocked<br>(edge-trigger) | X<br>Latched |                   | _                        | 20                       | -                      | 65                            | 5            | 5-121                           |

| Dual 4-Input | 74LS153    | 2                         | x            |                   | 18                       | 16                       | 10                     | 31                            | 5            | 5-31                            |

| Dual 4-Input | 74LS253    | 2                         | 3-State      |                   | 18                       | 16                       | 10                     | 43                            | 5            | 5-99                            |

| 8-Input      | 74LS151    | 1                         | х            | x                 | 28                       | 25                       | 18                     | 30                            | 5            | 5-25                            |

| 8-Input      | 74LS251    | 1                         | 3-State      | 3-State           | 29                       | 21                       | 18                     | 33                            | 5            | 5-95                            |

| 8-Input      | 74LS152    |                           |              | x                 | 22                       | -                        | 11                     | 28                            | 5            | 5-28                            |

### **MSI SELECTOR GUIDE BY FUNCTION**

|                                              | A = Asyn   |             | Regist       | t <b>ers</b><br>S = Sy        | nchro      | nous                        |                                   |                               |                                 |

|----------------------------------------------|------------|-------------|--------------|-------------------------------|------------|-----------------------------|-----------------------------------|-------------------------------|---------------------------------|

| Function                                     | DEVICE NO. | No. of Bits | Serial Entry | Parallel Entry<br>No. of Bits | Clock Edge | Max Clock Freq<br>MHz (typ) | Clock to Output<br>Delay ns (typ) | Power Dissipation<br>mW (typ) | LSTTL<br>Data Sheet<br>Page No. |

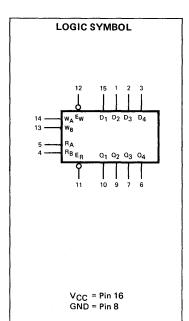

| Parallel-in / Parallel-out<br>Shift Right    | 74LS95     | 4           | D            | 48                            | 7          | 36                          | 20                                | 65                            | 5-15                            |

| Parallel-in / Parallel-out<br>Shift Right    | 74LS195    | 4           | J, K         | 48                            | J          | 39                          | 17                                | 70                            | 5-85                            |

| Parallel-in / Parallel-out<br>Shift Right    | 74LS295    | 4           | D            | 48                            |            | 28                          | 40                                | 75                            | 5-117                           |

| Parallel-in / Parallel-out<br>Bi-Directional | 74LS194    | 4           | DR,<br>DL    | 48                            |            | 36                          | 16                                | 75                            | 5-81                            |

| Serial-in / Parallel-out                     | 74LS164    | 8           | 2D           | -                             |            | 18                          | 50                                | 95                            | 5-49                            |

| Parallel-in / Parallel-out                   | 74LS174    | 6           | -            | 6S                            |            | 40                          | 21                                | 65                            | 5-57                            |

| Parallel-in / Parallel-out                   | 74LS175    | 4           | -            | 48                            | 丁          | 40                          | 21                                | 45                            | 5-60                            |

| Parallel-in / Parallel-out                   | 74LS298    | 4           | _            | 2D<br>MUX                     | Z          | 30                          | 21                                | 65                            | 5-121                           |

| Multiport Registers                          | 74LS170    | 16          | -            | 4A                            | L          | -                           | 25                                | 125                           | 5-53                            |

| Multiport Registers                          | 74LS670    | 16          | -            | 4A                            | ٦          | -                           | 30                                | 150                           | 5-124                           |

#### **LOW POWER SCHOTTKY**

**SSI Data Sheets**

4

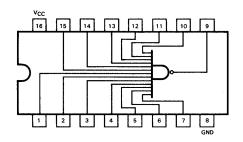

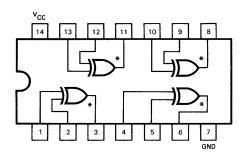

#### **QUAD 2-INPUT NAND GATE**

**GUARANTEED OPERATING RANGES**

| DADT NUMBERS |        | SUPPLY VOLTAGE |        | TEMPERATURE    |

|--------------|--------|----------------|--------|----------------|

| PART NUMBERS | MIN    | TYP            | MAX    | TEMPERATURE    |

| SN54LS00X    | 4.5 V  | 5.0 V          | 5.5 V  | -55°C to 125°C |

| SN74LS00X    | 4.75 V | 5.0 V          | 5.25 V | 0°C to 75°C    |

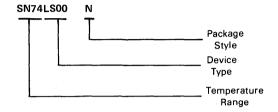

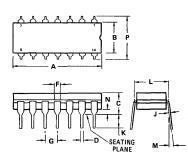

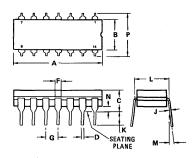

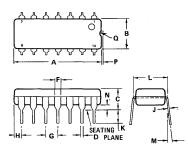

X = package type; W for Flatpak, J for Ceramic Dip, N for Plastic Dip. See Packaging Information Section for packages available on this product.

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| CVMDO              | DADAMETED                                |       |             | LIMITS |       | LINITE                   | TECT COMPLETIONS (No 1)                                         |  |

|--------------------|------------------------------------------|-------|-------------|--------|-------|--------------------------|-----------------------------------------------------------------|--|

| SYMBOL             | PARAMETER                                |       | MIN TYP MAX |        | UNITS | TEST CONDITIONS (Note 1) |                                                                 |  |

| V <sub>IH</sub>    | Input HIGH Voltage                       |       | 2.0         |        |       | V                        | Guaranteed Input HIGH Voltage                                   |  |

|                    | Innut I OW Valence                       | 54    | -           |        | 0.7   | V                        | Current and Innet LOW Valence                                   |  |

| V <sub>IL</sub>    | Input LOW Voltage                        | 74    |             |        | 0.8   | 7 '                      | Guaranteed Input LOW Voltage                                    |  |

| v <sub>CD</sub>    | Input Clamp Diode Volta                  | ge    |             | -0.65  | -1.5  | V                        | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -18 mA                 |  |

|                    | Outros IIICII Valence                    | 54    | 2.5         | 3.4    |       | V                        | V - MIN I - 400 - A V - V                                       |  |

| V <sub>OH</sub> Ou | Output HIGH Voltage                      | 74    | 2.7         | 3.4    |       | 1 <b>'</b> 1             | $V_{CC} = MIN, I_{OH} = -400 \mu A, V_{IN} = V_{IL}$            |  |

| V                  | Output LOW Voltage                       | 54,74 |             | 0.25   | 0.4   | V                        | $V_{CC} = MIN, I_{OL} = 4.0 \text{ mA}, V_{IN} = 2.0 \text{ V}$ |  |

| VOL                | Output LOVV Voltage                      | 74    |             | 0.35   | 0.5   | V                        | $V_{CC} = MIN, I_{OL} = 8.0 \text{ mA}, V_{IN} = 2.0 \text{ V}$ |  |

| liH                | Input HIGH Current                       | *     |             | 1.0    | 20    | μΑ                       | $V_{CC} = MAX$ , $V_{IN} = 2.7 V$                               |  |

| 'IH                | input man current                        |       |             |        | 0.1   | mA                       | $V_{CC} = MAX$ , $V_{IN} = 10 V$                                |  |

| l <sub>IL</sub>    | Input LOW Current                        |       |             | -      | -0.36 | mA                       | $V_{CC} = MAX$ , $V_{IN} = 0.4 V$                               |  |

| los                | Output Short Circuit<br>Current (Note 3) |       | -15         |        | -100  | mA                       | V <sub>CC</sub> = MAX, V <sub>OUT</sub> = 0 V                   |  |

| <sup>I</sup> ссн   | Supply Current HIGH                      |       |             | 0.8    | 1.6   | mA                       | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0 V                    |  |

| I <sub>CCL</sub>   | Supply Current LOW                       | -     |             | 2.4    | 4.4   | mA                       | V <sub>CC</sub> = MAX, Inputs Open                              |  |

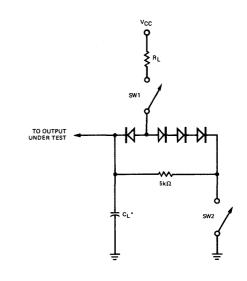

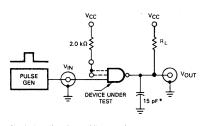

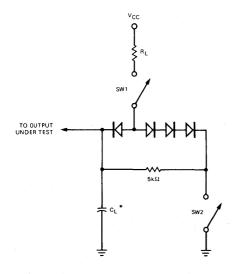

#### AC CHARACTERISTICS: $T_A = 25$ °C (See Page 4-50 for Waveforms)

| CVMPOL           | DARAMETER                       |     | LIMITS |     | LINUTO | TEST SOMETIONS          |  |

|------------------|---------------------------------|-----|--------|-----|--------|-------------------------|--|

| SYMBOL           | PARAMETER                       | MIN | TYP    | MAX | UNITS  | TEST CONDITIONS         |  |

| <sup>t</sup> PLH | Turn Off Delay, Input to Output | 3.0 | 5.0    | 10  | ns     | V <sub>CC</sub> = 5.0 V |  |

| <sup>t</sup> PHL | Turn On Delay, Input to Output  | 3.0 | 5.0    | 10  | ns     | C <sub>L</sub> = 15 pF  |  |

- For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

- Typical limits are at V<sub>CC</sub> = 5.0 V, T<sub>A</sub> = 25°C.

- 3. Not more than one output should be shorted at a time.

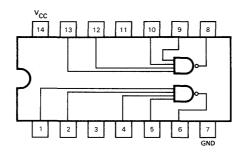

#### **QUAD 2-INPUT NOR GATE**

**GUARANTEED OPERATING RANGES**

| PART NUMBERS |        | SUPPLY VOLTAGE |        |                |  |  |  |

|--------------|--------|----------------|--------|----------------|--|--|--|

|              | MIN    | TYP            | MAX    | TEMPERATURE    |  |  |  |

| SN54LS02X    | 4.5 V  | 5.0 V          | 5.5 V  | -55°C to 125°C |  |  |  |

| SN74LS02X    | 4.75 V | 5.0 V          | 5.25 V | 0°C to 75°C    |  |  |  |

X = package type; W for Flatpak, J for Ceramic Dip, N for Plastic Dip. See Packaging Information Section for packages available on this product.

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| CVAADOL                               | DADAMETED                                | ADABATTD |         | LIMITS |       | LINITE     | TEST CONDITIONS (Note 1)                                                 |  |

|---------------------------------------|------------------------------------------|----------|---------|--------|-------|------------|--------------------------------------------------------------------------|--|