SCHWEBER ELECTRONICS 904 CAMBRIDGE DRIVE ELK GROVE VILLAGE, ILLINOIS 60007 312-364-3750

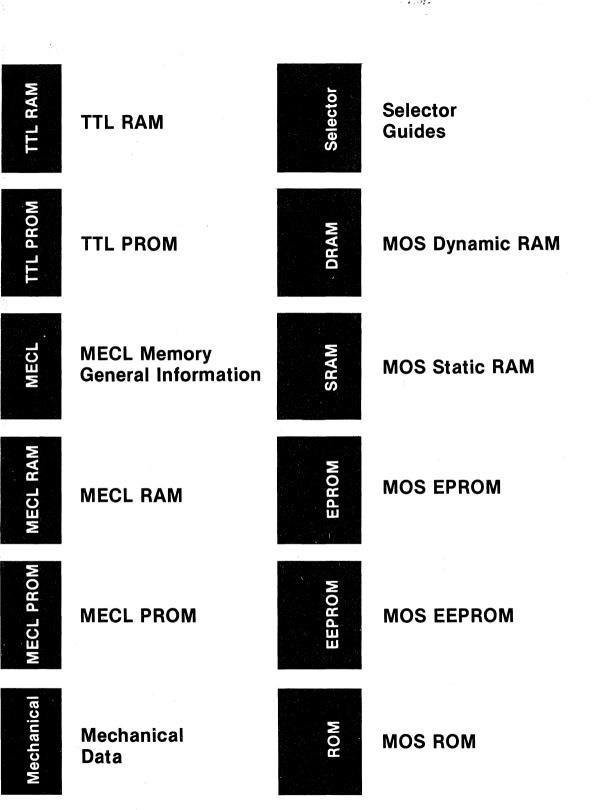

# MOTOROLA MEMORY DATA MANUAL

- QUALITY

- **RELIABILITY**

- TECHNOLOGY

Guides

SRA

:

Selector

TTL RAM

**TTL PROM**

**MECL Memory** General Information

**MOS Static RAM**

**MOS Dynamic RAM**

**MECL RAM**

ECL PRO

ECL RA

**MECL PROM**

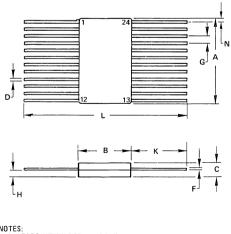

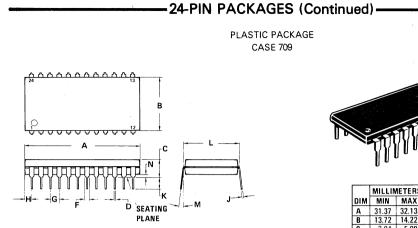

**Mechanical** Data

**MOS ROM**

Prepared by Technical Information Center

Motorola has developed a very broad range of reliable MOS and bipolar memories for virtually any digital data processing system application. Complete specifications for the individual circuits are provided in the form of data sheets. In addition, selector guides are included to simplify the task of choosing the best combination of circuits for optimum system architecture.

New Motorola memories are being introduced continually. For the latest releases, and additional technical information or pricing, contact your nearest authorized Motorola distributor or Motorola sales office.

The information in this book has been carefully checked; no responsibility, however, is assumed for inaccuracies. Furthermore, this information does not convey to the purchaser of microelectronic devices any license under the patent rights of the manufacturer.

> Series C ©MOTOROLA INC., 1982 Previous Edition ©1980 "All Rights Reserved"

MECL, EXORmacs, and VERSAmodule are trademarks of Motorola Inc.

# Table of Contents

|                                                                                                                                                                                                                                                                           | Organization                                                                                                                                   | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Alphanumeric Index                                                                                                                                                                                                                                                        |                                                                                                                                                | v    |

|                                                                                                                                                                                                                                                                           | r Guide and Custom Memory Systems                                                                                                              |      |

| CHAPTER 2 — MOS Dynamic I<br>MCM4027A<br>MCM4116B<br>MCM4517<br>MCM6632A<br>MCM6633A<br>MCM6664A<br>MCM6665A                                                                                                                                                              | RAMs<br>4K × 1<br>16K × 1<br>16K × 1<br>32K × 1<br>32K × 1<br>64K × 1<br>64K × 1                                                               |      |

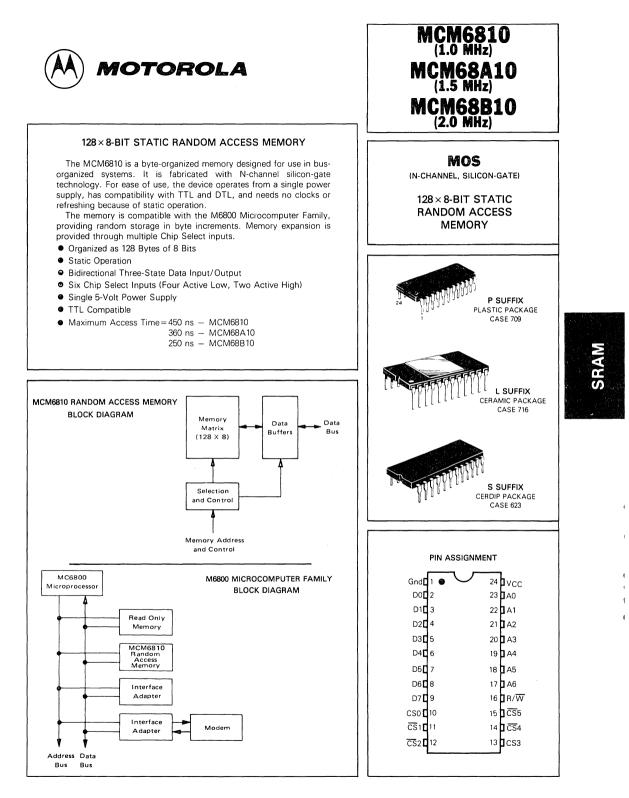

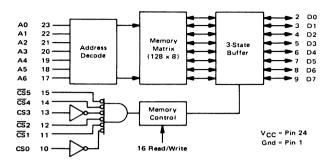

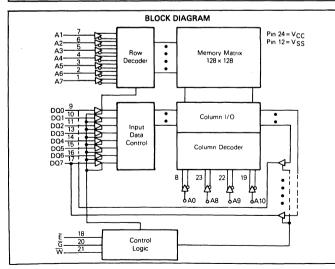

| MCM6256<br>CHAPTER 3 — MOS Static RA<br>MCM2115A/25A<br>MCM5101, 51L01<br>MCM6810, 68A10, 68B10<br>MCM2114, 21L14<br>MCM2147<br>MCM65147<br>MCM66147, 66L41<br>MCM65116                                                                                                   | 256K × 1<br>Ms<br>1K × 1<br>256 × 4<br>128 × 8<br>1K × 4<br>4K × 1<br>4K × 1<br>4K × 1<br>2K × 8<br>                                           |      |

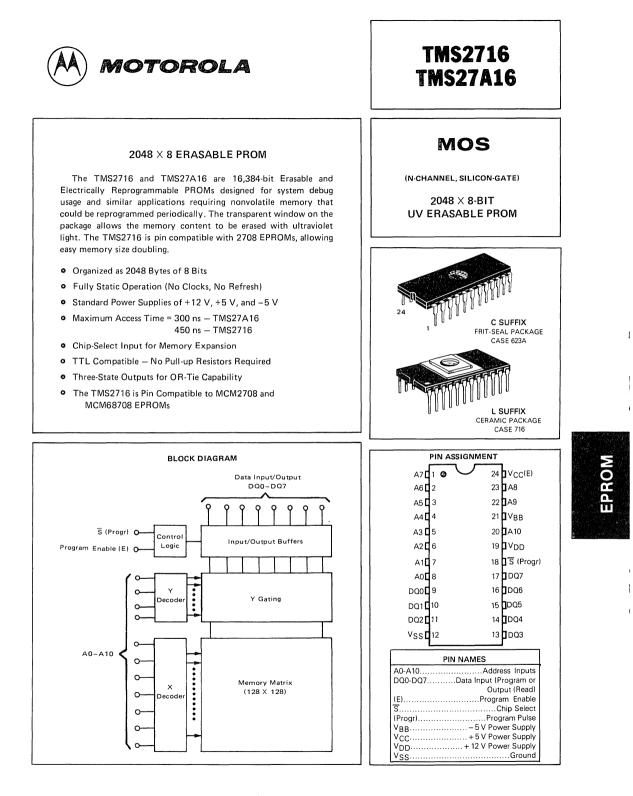

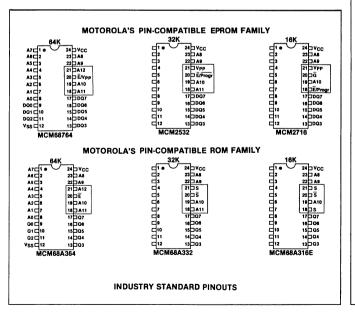

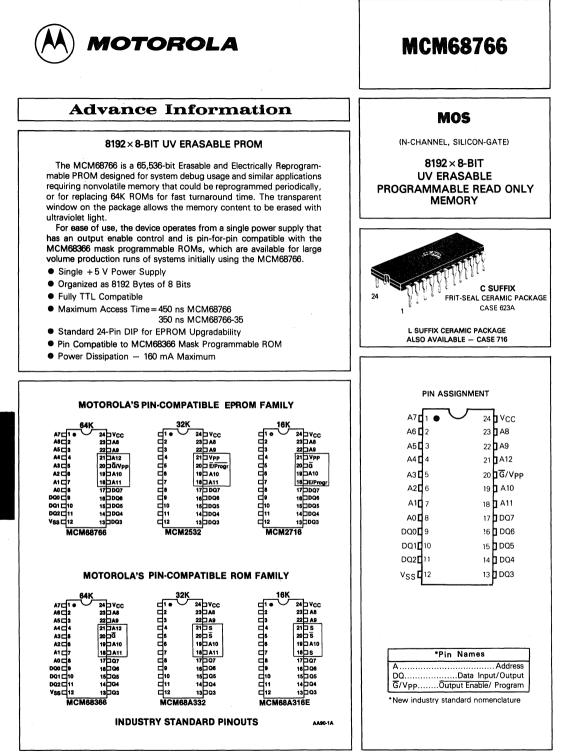

| CHAPTER 4 — MOS EPROMs<br>MCM2708, 27A08<br>TMS2716, 27A16<br>MCM2716<br>MCM2532<br>MCM68764<br>MCM68766<br>CHAPTER 5 — MOS EEPROMs<br>MCM2801<br>MCM2802                                                                                                                 | 1K × 8<br>2K × 8<br>2K × 8<br>4K × 8<br>8K × 8<br>8K × 8<br>16K × 16<br>32K × 32                                                               |      |

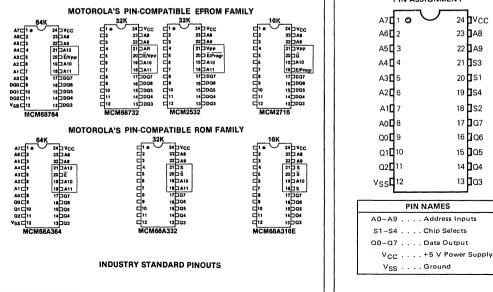

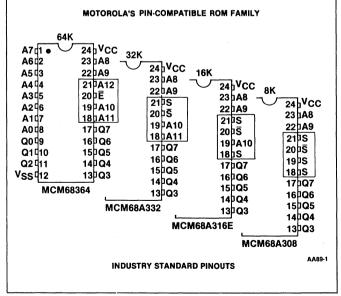

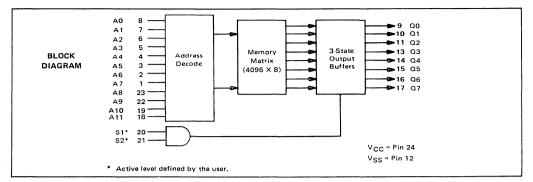

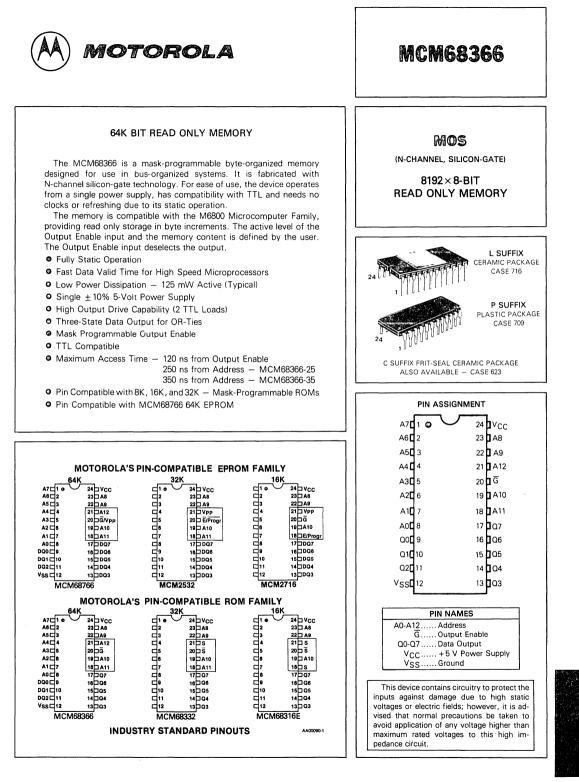

| MCM2816<br>CHAPTER 6 — MOS ROMs<br>MCM6670, 6674<br>MCM66700, 710, 714, 720, 730, 734<br>740, 750, 751, 760, 770, 780, 790<br>MCM68A30A, 68B30A<br>MCM68A308, 68B308<br>MCM68A3316E<br>MCM68A332<br>MCM68A332<br>MCM68365<br>MCM68366<br>MCM68366<br>MCM63256<br>MCM65256 | 2K × 8<br>128 × (7 × 5)<br>128 × (7 × 9)<br>1K × 8<br>1K × 8<br>2K × 8<br>2K × 8<br>4K × 8<br>8K × 8<br>8K × 8<br>8K × 8<br>32K × 8<br>32K × 8 |      |

1

## Table of Contents (Continued)

|                                                                                                         | Organization                                         | Page               |

|---------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------|

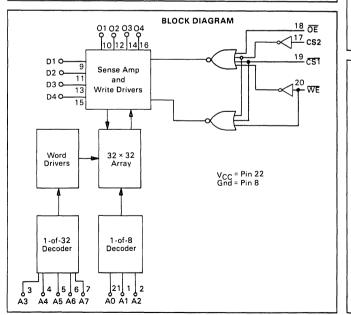

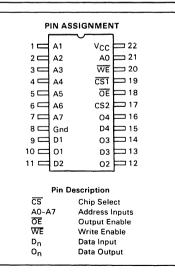

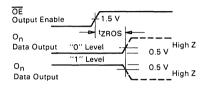

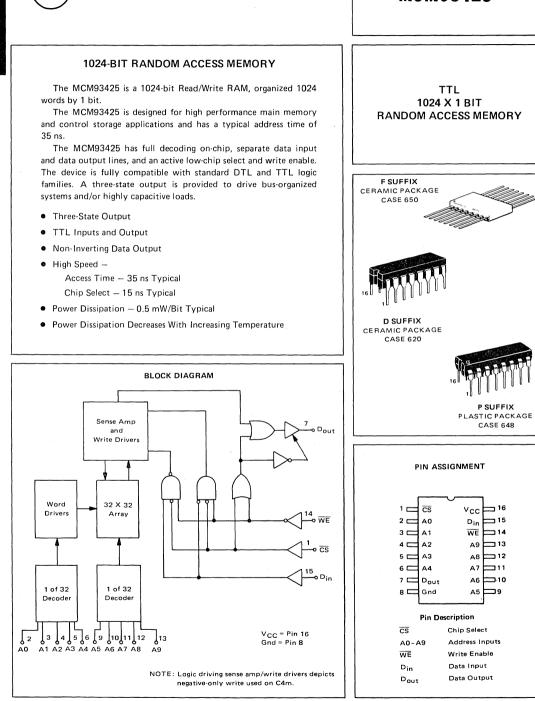

| CHAPTER 7 — TTL RAMs<br>MCM93412, 93422<br>MCM93415<br>MCM93425                                         | 256 × 4<br>1024 × 1<br>1024 × 1                      | 7-8                |

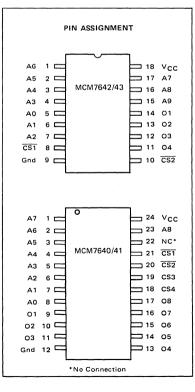

| CHAPTER 8 — TTL PROMs<br>MCM7620, 7621<br>MCM7640, 7641<br>7642, 7643<br>MCM7680, 7681<br>MCM7684, 7685 | 512 × 4<br>512 × 8<br>1024 × 4<br>1024 × 8<br>2K × 4 | 8-7<br>8-7<br>8-11 |

| CHAPTER 9 — MECL Memories<br>General Information                                                        | 5                                                    | 9-2                |

| CHAPTER 10 - MECL RAMs                                                                                  |                                                      |                    |

| MCM10143                                                                                                | 8×2                                                  |                    |

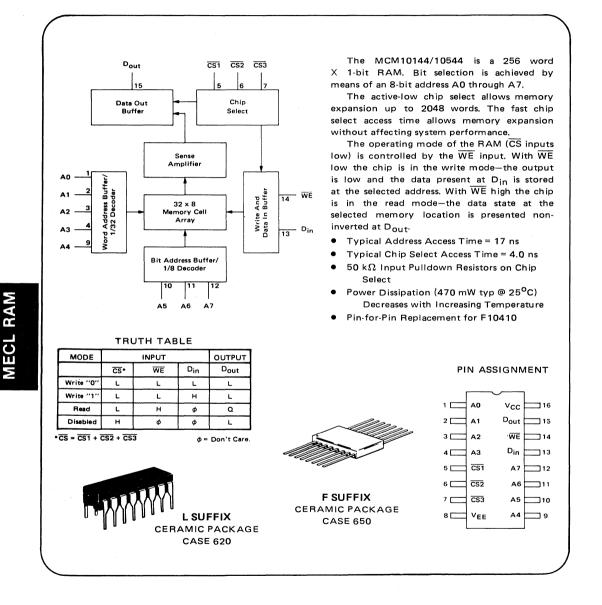

| MCM10144, 10544                                                                                         | 256 × 1                                              |                    |

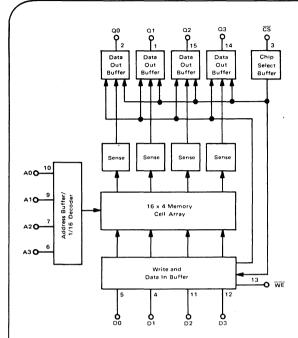

| MCM10145, 10545                                                                                         | 16 × 4                                               | 10-10              |

| MCM10146, 10546                                                                                         | 1024 × 1                                             | 10-12              |

| MCM10147, 10547                                                                                         | 128 × 1                                              | 10-14              |

| MCM10148, 10548                                                                                         | 64 × 1                                               | 10-16              |

| MCM10152, 10552                                                                                         | 256 × 1                                              |                    |

| MCM10422                                                                                                | 256 × 4                                              |                    |

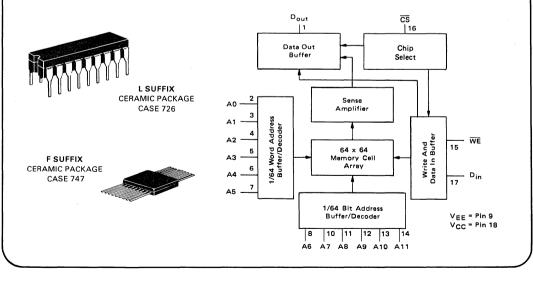

| MCM10470                                                                                                | 4096 × 1                                             | 10-24              |

| CHAPTER 11 — MECL PROMs<br>MCM10139, 10539                                                              | 32 × 8                                               |                    |

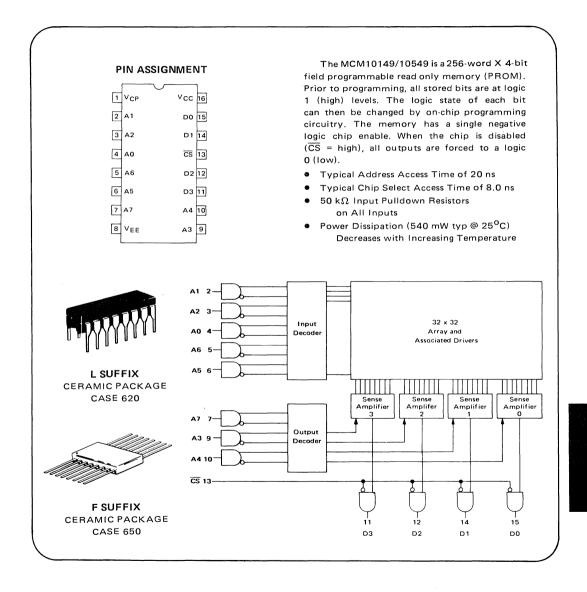

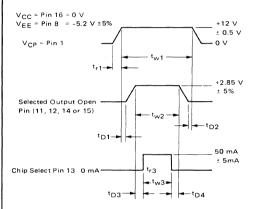

| MCM10149, 10549                                                                                         | 256 × 4                                              |                    |

| CHAPTER 12 — Mechanical Data                                                                            | a                                                    | 12-1               |

#### ALPHANUMERIC INDEX

| Device     | Page | Device     | Page  |

|------------|------|------------|-------|

| MCM21L14   | 3-18 | МСМ7684    | 8-15  |

| MCM21L15A  | 3-3  | MCM7685    | 8-15  |

| MCM21L25A  | 3-3  | MCM10139   | 11-3  |

| MCM27A08   | 4-3  | MCM10143   |       |

| MCM51L01   | 3-9  | MCM10144   |       |

| MCM66L41   | 3-32 | MCM10145   | 10-10 |

| MCM68A10   | 3-13 | MCM10146   | 10-12 |

| MCM68A30A  | 6-24 | MCM10147   | 10-14 |

| MCM68A308  | 6-29 | MCM10148   | 10-16 |

| MCM68A316E | 6-34 | MCM10149   | 11-7  |

| MCM68A332  | 6-44 | MCM10152   | 10-18 |

| MCM68B10   | 3-13 | MCM10422   | 10-20 |

| MCM68B30A  | 6-24 | MCM10470   | 10-24 |

| MCM68B308  | 6-29 | MCM10539   | 11-3  |

| MCM2114    | 3-18 | MCM10544   |       |

| MCM21L14   | 3-18 | MCM10545   | 10-10 |

| MCM2115A   | 3-3  | MCM10546   | 10-12 |

| MCM21L15A  | 3-3  | MCM10547   | 10-14 |

| MCM2125A   | 3-3  | MCM10548   | 10-16 |

| MCM21L25A  | 3-3  | MCM10549   | 11-7  |

| MCM2147    | 3-23 | MCM10552   | 10-18 |

| MCM2532    | 4-21 | MCM63256   | 6-62  |

| MCM2708    | 4-3  | MCM65116   | 3-36  |

| MCM27A08   | 4-3  | MCM65147   | 3-28  |

| MCM2716    | 4-15 | MCM65256   | 6-63  |

| MCM2801    | 5-3  | MCM65516   | 6-38  |

| MCM2802    | 5-8  | MCM66700   | 6-10  |

| MCM2816    | 5-9  | MCM66710   | 6-10  |

| MCM4027A   | 2-3  | MCM66714   | 6-10  |

| MCM4116B   | 2-13 | MCM66720   | 6-10  |

| MCM4517    | 2-20 | MCM66730   | 6-10  |

| MCM5101    | 3-9  | MCM66734   | 6-10  |

| MCM51L01   | 3-9  | MCM66740   |       |

| MCM6256    | 2-89 | MCM66750   |       |

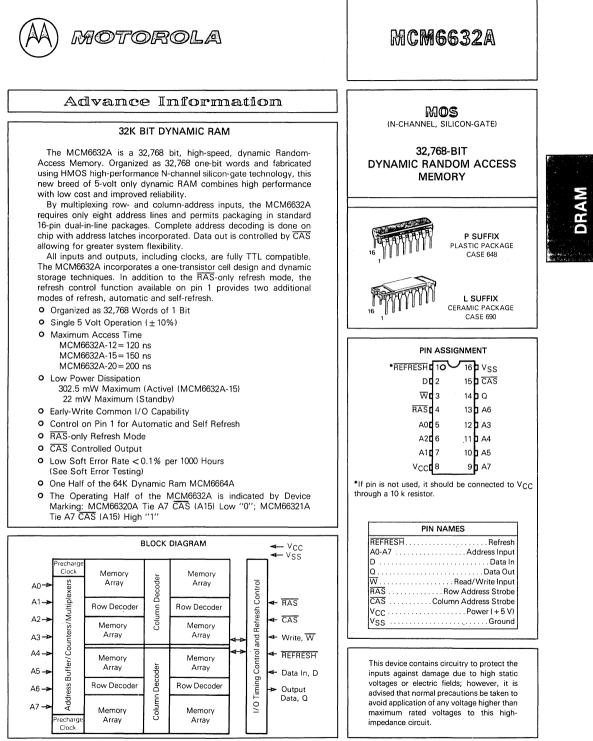

| MCM6632A   |      | MCM66751   |       |

| MCM6633A   | 2-43 | MCM66760   |       |

| MCM6641    |      | MCM66770   |       |

| MCM66L41   |      | MCM66780   |       |

| MCM6664A   |      | MCM66790   |       |

| MCM6665A   |      | MCM68A308  |       |

| MCM6670    |      | MCM68B308  |       |

| MCM6674    |      | MCM68A316E |       |

| MCM6810    |      | MCM68A332  |       |

| MCM68A10   |      | MCM68364   |       |

| MCM68B10   |      | MCM68365   |       |

| MCM68A30A  |      | MCM68366   |       |

| MCM68B30A  |      | MCM68764   |       |

| MCM7620    |      | MCM68766   |       |

| MCM7621    |      | MCM93412   |       |

| MCM7640    |      | MCM93415   |       |

| MCM7641    |      | MCM93422   |       |

| MCM7642    |      | MCM93425   |       |

| MCM7643    |      | TMS2716    |       |

| MCM7680    |      | TMS27A16   | 4-9   |

| MCM7681    | ð-11 |            |       |

ł

# Selector Guides

#### MEMORIES SELECTOR GUIDE

#### NOTES

Not all package options are listed.

Operating temperature ranges:

$MOS - 0^{\circ}C$  to  $70^{\circ}C$

ECL - Consult individual data sheets

TTL - Military - 55°C to + 125°C, Commercial 0°C to 70°C

#### FOOTNOTES

<sup>1</sup>Motorola's innovative pin #1 refresh

<sup>2</sup>All MOS memory outputs are three-state except the open collector MCM2115A series.

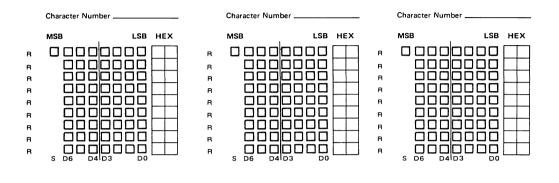

<sup>3</sup>Character generators include shifted and unshifted characters, ASCII, alphanumeric control, math, Japanese, British, German, European and French symbols.

<sup>4</sup>Standard Patterns for MOS ROMs:

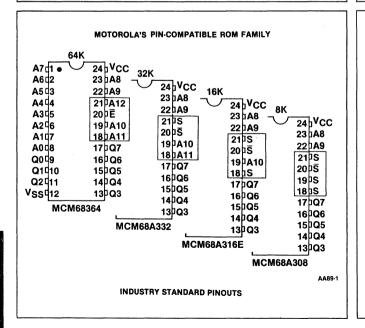

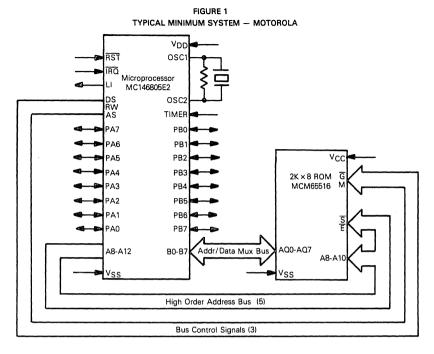

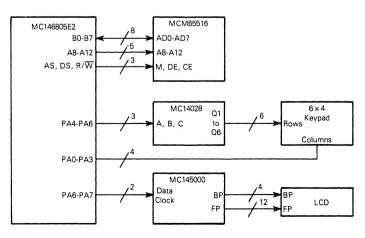

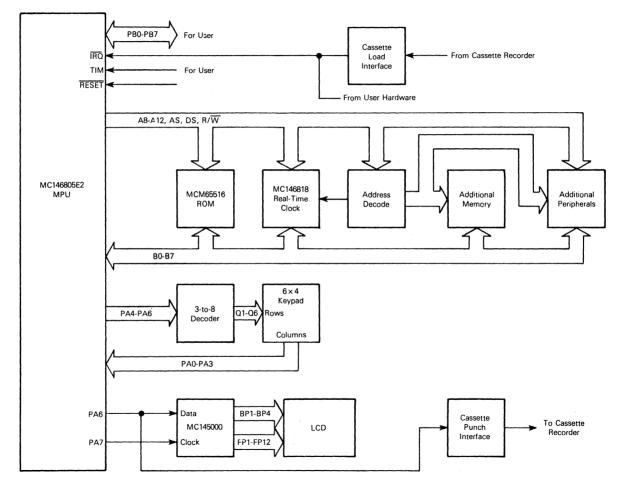

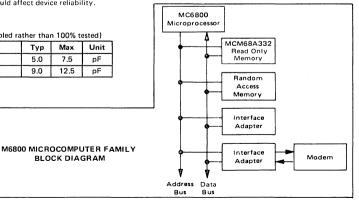

MCM68A308P7 – MC6800 MIKbug/MINIbug ROM MCM68A316EP91 – Universal Code Converter and Character Generator MCM68A332P2 – Sine/Cosine Look-Up Table MCM68364P35-3 – Log/Antilog Look-Up Table MCM65516P43M – MC146805 Monitor Program

\*To be introduced. (Not all speed selections shown)

# RAMS MOS DYNAMIC RAMS

| Organization | Part Number              | Access Time<br>(ns_max) | Power<br>Supplies | No. of<br>Pins |

|--------------|--------------------------|-------------------------|-------------------|----------------|

| 4096 × 1     | MCM4027AC-2              | 150                     | + 12, ±5 V        | 16             |

| 4096 × 1     | MCM4027AC-3              | 200                     | + 12, ±5 V        | 16             |

| 4096 × 1     | MCM4027AC-4              | 250                     | + 12, ±5 V        | 16             |

| 16384 × 1    | MCM4116BP15              | 150                     | + 12, ±5 V        | 16             |

| 16384 × 1    | MCM4116BP20              | 200                     | + 12, ±5 V        | 16             |

| 16384 × 1    | MCM4116BP25              | 250                     | + 12, ±5 V        | 16             |

| 16384 × 1    | MCM4517P10               | 100                     | + 5 V             | 16             |

| 16384 × 1    | MCM4517P12               | 120                     | +5 V              | 16             |

| 16384 × 1    | MCM4517P15               | 150                     | + 5 V             | 16             |

| 16384 × 1    | MCM4517P20               | 200                     | +5 V              | 16             |

| 32768×1      | MCM6632AP15 <sup>1</sup> | 150                     | +5 V              | 16             |

| 32768 × 1    | MCM6632AP20 <sup>1</sup> | 200                     | +5 V              | 16             |

| 32768 × 1    | MCM6633AP15              | 150                     | +5 V              | 16             |

| 32768 × 1    | MCM6633AP20              | 200                     | +5 V              | 16             |

| 65536 × 1    | MCM6664AP121             | 120                     | +5 V              | 16             |

| 65536 × 1    | MCM6664AP15 <sup>1</sup> | 150                     | +5 V              | 16             |

| 65536×1      | MCM6664AP20 <sup>1</sup> | 200                     | +5 V              | 16             |

| 65536×1      | MCM6665AP12              | 120                     | +5 V              | 16             |

| 65536×1      | MCM6665AP15              | 150                     | +5 V              | 16             |

| 65336 × 1    | MCM6665AP20              | 200                     | +5 V              | 16             |

Selector

ł

## TTL BIPOLAR RAMs

| Organization | Part Number | Access Time<br>(ns max) | Output         | No. of<br>Pins |

|--------------|-------------|-------------------------|----------------|----------------|

| 256×4        | MCM93412    | 45                      | Open Collector | 22             |

| 256 × 4      | MCM93422*   | 45                      | 3-State        | 22             |

| 256 × 4      | MCM93L422*  | 60                      | 3-State        | 22             |

| 1024 × 1     | MCM93415    | 45                      | Open Collector | 16             |

| 1024 × 1     | MCM93425    | 45                      | 3-State        | 16             |

1-3

### **MEMORIES SELECTOR GUIDE (Continued)**

## MOS STATIC RAMs (+5 Volts)

| 2         (in max)         (Prins)           128 × 8         MCM6810         450         24           128 × 8         MCM68810         360         24           128 × 8         MCM68810         250         24           1024 × 4         MCM2114P20         200         18           1024 × 4         MCM2114P25         250         18           1024 × 4         MCM2114P25         250         18           1024 × 4         MCM2114P25         250         18           1024 × 4         MCM2114P30         300         18           1024 × 4         MCM21L14P20         200         18           1024 × 4         MCM21L14P25         250         18           1024 × 4         MCM21L14P25         250         18           1024 × 4         MCM21L14P25         250         18           1024 × 1         MCM2115AC45 <sup>2</sup> 45         16           1024 × 1         MCM2115AC45 <sup>2</sup> 45         16           1024 × 1         MCM2115AC45 <sup>2</sup> 45         16           1024 × 1         MCM2125AC45         45         16           1024 × 1         MCM2125AC45         45         16                                                                                         | Organization | Organization Part Number Access Time |          |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------|----------|------|

| 128 × 8         MCM68A10         360         24           128 × 8         MCM68B10         250         24           1024 × 4         MCM2114P20         200         18           1024 × 4         MCM2114P25         250         18           1024 × 4         MCM2114P30         300         18           1024 × 4         MCM2114P45         450         18           1024 × 4         MCM21L14P20         200         18           1024 × 4         MCM21L14P25         250         18           1024 × 4         MCM21L14P25         250         18           1024 × 4         MCM21L14P25         250         18           1024 × 4         MCM21L14P30         300         18           1024 × 4         MCM21L14P35         450         18           1024 × 1         MCM21L5AC45 <sup>2</sup> 45         16           1024 × 1         MCM2115AC55 <sup>2</sup> 55         16           1024 × 1         MCM21L16AC45 <sup>2</sup> 45         16           1024 × 1         MCM21L5AC45         45         16           1024 × 1         MCM2125AC45         45         16           1024 × 1         MCM2125AC45         45                                                                             | Organization | Fait Number                          | (ns max) | Pins |

| 128×8         MCM68810         250         24           1024×4         MCM2114P20         200         18           1024×4         MCM2114P25         250         18           1024×4         MCM2114P30         300         18           1024×4         MCM2114P35         250         18           1024×4         MCM2114P45         450         18           1024×4         MCM21L14P20         200         18           1024×4         MCM21L14P25         250         18           1024×4         MCM21L14P25         250         18           1024×4         MCM21L14P30         300         18           1024×4         MCM21L14P45         450         18           1024×1         MCM2115AC452         45         16           1024×1         MCM2115AC452         45         16           1024×1         MCM2115AC452         45         16           1024×1         MCM2125AC45         45         16           1024×1         MCM2125AC45         45         16           1024×1         MCM2125AC45         45         16           1024×1         MCM2125AC70         70         16           10                                                                                                    | 128×8        | MCM6810                              | 450      | 24   |

| $1024 \times 4$ MCM2114P20 $200$ 18 $1024 \times 4$ MCM2114P25 $250$ 18 $1024 \times 4$ MCM2114P25 $250$ 18 $1024 \times 4$ MCM2114P25 $300$ 18 $1024 \times 4$ MCM2114P25 $250$ 18 $1024 \times 4$ MCM21L14P25 $250$ 18 $1024 \times 4$ MCM21L14P25 $250$ 18 $1024 \times 4$ MCM21L14P25 $250$ 18 $1024 \times 4$ MCM21L14P30 $300$ 18 $1024 \times 4$ MCM21L16AC45 <sup>2</sup> $450$ 18 $1024 \times 4$ MCM2115AC45 <sup>2</sup> $455$ 16 $1024 \times 1$ MCM2115AC45 <sup>2</sup> $455$ 16 $1024 \times 1$ MCM2115AC70 <sup>2</sup> 7016 $1024 \times 1$ MCM21L5AC45 <sup>2</sup> $455$ 16 $1024 \times 1$ MCM21L5AC45 <sup>2</sup> $455$ 16 $1024 \times 1$ MCM2125AC55 $555$ 16 $1024 \times 1$ MCM2125AC45 $455$ 16 $1024 \times 1$ MCM6641P20 $200$ 18 $4096 \times 1$ MCM6641P25 $250$ 18 $4096 \times 1$ MCM6641P30 $300$ 18 $4096 \times 1$ MCM66L41P25 $250$ 18 $4096 \times 1$ MCM66L41P36 $450$ 18 $4096 \times 1$ MCM66L41P36 $55$ 18 $4096 \times 1$ MCM66L41P30 $300$ 18 $4096 \times 1$ MCM66L41P30 $300$ <t< td=""><td>128×8</td><td>MCM68A10</td><td>360</td><td>24</td></t<> | 128×8        | MCM68A10                             | 360      | 24   |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 128×8        | MCM68B10                             | 250      | 24   |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |                                      |          |      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |                                      |          |      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              | MCM2114P25                           |          |      |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              | MCM2114P30                           |          |      |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              | MCM2114P45                           |          |      |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1024 × 4     | MCM21L14P20                          | 200      |      |

| $1024 \times 4$ MCM21L14P4545018 $1024 \times 1$ MCM2115AC4524516 $1024 \times 1$ MCM2115AC7025516 $1024 \times 1$ MCM2115AC7027016 $1024 \times 1$ MCM21L15AC7027016 $1024 \times 1$ MCM21L15AC7027016 $1024 \times 1$ MCM21L15AC7027016 $1024 \times 1$ MCM2125AC454516 $1024 \times 1$ MCM2125AC455516 $1024 \times 1$ MCM2125AC454516 $1024 \times 1$ MCM2125AC707016 $1024 \times 1$ MCM2125AC707016 $1024 \times 1$ MCM6641P2020018 $4096 \times 1$ MCM6641P3030018 $4096 \times 1$ MCM6641P3030018 $4096 \times 1$ MCM6641P4545018 $4096 \times 1$ MCM6641P4525018 $4096 \times 1$ MCM6641P4545018 $4096 \times 1$ MCM66141P3030018 $4096 \times 1$ MCM66141P3030018 $4096 \times 1$ MCM66141P4545018 $4096 \times 1$ MCM66141P4545018 $4096 \times 1$ MCM66141P4545018 $4096 \times 1$ MCM2147C555518 $4096 \times 1$ MCM2147C707018                                                                                                                                                                                                                                                                                                                                                                     | 1024 × 4     | MCM21L14P25                          | 250      | 18   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1024 × 4     | MCM21L14P30                          | 300      | 18   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1024 × 4     | MCM21L14P45                          | 450      | 18   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                      |          |      |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1024 × 1     |                                      | 45       | 16   |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1024 × 1     |                                      | 55       | 16   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1024 × 1     |                                      | 70       | 16   |

| 1024 × 1         MCM2125AC45         45         16           1024 × 1         MCM2125AC55         55         16           1024 × 1         MCM2125AC70         70         16           1024 × 1         MCM2125AC45         45         16           1024 × 1         MCM21125AC45         45         16           1024 × 1         MCM21125AC70         70         16           1024 × 1         MCM21125AC70         70         16           1024 × 1         MCM21125AC70         70         16           4096 × 1         MCM6641P20         200         18           4096 × 1         MCM6641P25         250         18           4096 × 1         MCM6641P45         450         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P30         300         18           4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM66L41P45         55         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18 </td <td>1024 × 1</td> <td></td> <td>45</td> <td>16</td>                   | 1024 × 1     |                                      | 45       | 16   |

| 1024 × 1         MCM2125AC55         55         16           1024 × 1         MCM2125AC70         70         16           1024 × 1         MCM21125AC70         70         16           1024 × 1         MCM21L25AC45         45         16           1024 × 1         MCM21L25AC70         70         16           4096 × 1         MCM6641P20         200         18           4096 × 1         MCM6641P25         250         18           4096 × 1         MCM6641P45         450         18           4096 × 1         MCM6641P45         200         18           4096 × 1         MCM6641P45         200         18           4096 × 1         MCM6641P45         450         18           4096 × 1         MCM66141P20         200         18           4096 × 1         MCM66141P25         250         18           4096 × 1         MCM66141P30         300         18           4096 × 1         MCM66141P45         450         18           4096 × 1         MCM66141P45         55         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18 <td>1024 × 1</td> <td>MCM21L15AC70<sup>2</sup></td> <td>70</td> <td>16</td> | 1024 × 1     | MCM21L15AC70 <sup>2</sup>            | 70       | 16   |

| 1024 × 1         MCM2125AC70         70         16           1024 × 1         MCM21L25AC45         45         16           1024 × 1         MCM21L25AC70         70         16           4096 × 1         MCM6641P20         200         18           4096 × 1         MCM6641P25         250         18           4096 × 1         MCM6641P30         300         18           4096 × 1         MCM6641P45         450         18           4096 × 1         MCM66L41P20         200         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P30         300         18           4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM66L41P45         55         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18                                                                                                                                        | 1024 × 1     | MCM2125AC45                          | 45       | 16   |

| 1024 × 1         MCM21L25AC45         45         16           1024 × 1         MCM21L25AC70         70         16           4096 × 1         MCM6641P20         200         18           4096 × 1         MCM6641P25         250         18           4096 × 1         MCM6641P30         300         18           4096 × 1         MCM6641P45         450         18           4096 × 1         MCM66141P20         200         18           4096 × 1         MCM66141P20         200         18           4096 × 1         MCM66141P25         250         18           4096 × 1         MCM66141P25         250         18           4096 × 1         MCM66141P25         250         18           4096 × 1         MCM66141P30         300         18           4096 × 1         MCM66141P30         300         18           4096 × 1         MCM66141P45         450         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18                                                                                                                                                                                                    | 1024 × 1     | MCM2125AC55                          | 55       | 16   |

| 1024 × 1         MCM21L25AC70         70         16           4096 × 1         MCM6641P20         200         18           4096 × 1         MCM6641P25         250         18           4096 × 1         MCM6641P30         300         18           4096 × 1         MCM6641P45         450         18           4096 × 1         MCM6641P25         250         18           4096 × 1         MCM66L41P20         200         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P30         300         18           4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18                                                                                                                                                                                                                                                                                                                                 | 1024 × 1     | MCM2125AC70                          | 70       | 16   |

| 4096 × 1         MCM6641P20         200         18           4096 × 1         MCM6641P25         250         18           4096 × 1         MCM6641P30         300         18           4096 × 1         MCM6641P45         450         18           4096 × 1         MCM66L41P20         200         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P30         300         18           4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1024 × 1     | MCM21L25AC45                         | 45       | 16   |

| 4096 × 1         MCM6641P25         250         18           4096 × 1         MCM6641P30         300         18           4096 × 1         MCM6641P45         450         18           4096 × 1         MCM66L41P20         200         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P30         300         18           4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM66L41P45         55         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1024 × 1     | MCM21L25AC70                         | 70       | 16   |

| 4096 × 1         MCM6641P25         250         18           4096 × 1         MCM6641P30         300         18           4096 × 1         MCM6641P45         450         18           4096 × 1         MCM66L41P20         200         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P30         300         18           4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM66L41P45         55         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4096 × 1     | MCM6641P20                           | 200      | 18   |

| 4096 × 1         MCM6641P30         300         18           4096 × 1         MCM6641P45         450         18           4096 × 1         MCM66L41P20         200         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P30         300         18           4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM66L41P45         55         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |                                      |          |      |

| 4096 × 1         MCM6641P45         450         18           4096 × 1         MCM66L41P20         200         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P30         300         18           4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM66L41P45         55         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                                      |          |      |

| 4096 × 1         MCM66L41P20         200         18           4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P30         300         18           4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                      |          |      |

| 4096 × 1         MCM66L41P25         250         18           4096 × 1         MCM66L41P30         300         18           4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                                      |          |      |

| 4096 × 1         MCM66L41P30         300         18           4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                                      |          |      |

| 4096 × 1         MCM66L41P45         450         18           4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                                      |          |      |

| 4096 × 1         MCM2147C55         55         18           4096 × 1         MCM2147C70         70         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |                                      |          |      |

| 4096 × 1 MCM2147C70 70 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                                      |          |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                                      |          |      |

| 440470XI I WUW7/4/U85 I 18 I 18 I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4096 × 1     | MCM2147C85                           | 85       | 18   |

# CMOS STATIC RAMs (+5 Volts)

| Organization | Part Number  | Access Time<br>(ns max) | No. of<br>Pins |

|--------------|--------------|-------------------------|----------------|

| 256×4        | MCM5101P65   | 650                     | 22             |

| 256×4        | MCM5101P80   | 800                     | 22             |

| 256×4        | MCM51L01P45  | 450                     | 22             |

| 256×4        | MCM51L01P65  | 650                     | 22             |

| 2048×8       | MCM65116P15* | 150                     | 24             |

| 4096×1       | MCM65147P55  | 55                      | 18             |

| 4096 × 1     | MCM65147P70  | 70                      | 18             |

# Selector

l

## ECL BIPOLAR RAMs

| Organization | Part Number | Access Time<br>(ns max) | No. of<br>Pins |

|--------------|-------------|-------------------------|----------------|

| 8×2          | MCM10143    | 15                      | 24             |

| 256 × 1      | MCM10144    | 26                      | 16             |

| 16×4         | MCM10145    | 15                      | 16             |

| 1024 × 1     | MCM10146    | 29                      | 16             |

| 1024 × 1     | MCM10146A*  | 15                      | 16             |

| 128×1        | MCM10147    | 15                      | 16             |

| 64×1         | MCM10148    | 15                      | 16             |

| 256×1        | MCM10152    | 15                      | 16             |

| 4096×1       | MCM10470    | 35                      | 18             |

| 4096 × 1     | MCM10470A*  | 20                      | 18             |

| 1024 × 4     | MCM10474*   | 25                      | 24             |

# EPROMS MOS EPROMS

| Organization | . Part Number | Access Time<br>(ns max) | Power<br>Supplies | No. of<br>Pins |

|--------------|---------------|-------------------------|-------------------|----------------|

| 1024×8       | MCM2708C      | 450                     | + 12, ±5 V        | 24             |

| 1024×8       | MCM27A08C     | 300                     | +12, ±5 V         | 24             |

| 2048 × 8     | TMS2716C      | 450                     | + 12, ±5 V        | 24             |

| 2048×8       | MCM2716C      | 450                     | +5 V              | 24             |

| 4096 × 8     | MCM2532C      | 450                     | +5 V              | 24             |

| 8192×8       | MCM68764C     | 450                     | +5 V              | 24             |

| 8192×8       | MCM68766C     | 450                     | +5 V              | 24             |

| 8192×8       | MCM68766C35   | 350                     | +5 V              | 24             |

# EEPROMS MOS ÉEPROM

| Organization | Part Number | Access Time<br>(ns max) | Power<br>Supplies | No. of<br>Pins |

|--------------|-------------|-------------------------|-------------------|----------------|

| 16×16        | MCM2801P    | 10 μs                   | +5 V              | 14             |

| 32 × 32      | MCM2802P*   | 15 µs                   | +5 V              | 14             |

| 2048×8       | MCM2816P*   | 450 ns                  | +5 V              | 24             |

| 2048×8       | MCM2817P*   | 150 ns                  | +5 V              | 28             |

| 4096 × 8     | MCM2832P*   | 150 ns                  | +5 V              | 28             |

# ROMS MOS STATIC ROMS (+5 Volts)

### Character Generators<sup>3</sup>

| Organization Part Number |           | Access Time<br>(ns max) | No. of<br>Pins |  |

|--------------------------|-----------|-------------------------|----------------|--|

| 128 × (7 × 5)            | MCM6670P  | 350                     | 18             |  |

| 128 × (7 × 5)            | MCM6674P  | 350                     | 18             |  |

| 128×(9×7)                | MCM66700P | 350                     | -24            |  |

| 128 × (9 × 7)            | MCM66710P | 350                     | 24             |  |

| 128 × (9 × 7)            | MCM66714P | 350                     | 24             |  |

| 128 × (9 × 7)            | MCM66720P | 350                     | 24             |  |

| 128×(9×7)                | MCM66730P | 350                     | 24             |  |

| 128×(9×7)                | MCM66734P | 350                     | 24             |  |

| 128 × (9 × 7)            | MCM66740P | 350                     | 24             |  |

| 128×(9×7)                | MCM66750P | 350                     | 24             |  |

| 128×(9×7)                | MCM66760P | 350                     | 24             |  |

| 128×(9×7)                | MCM66770P | 350                     | 24             |  |

| 128×(9×7)                | MCM66780P | 350                     | 24             |  |

| 128×(9×7)                | MCM66790P | 350                     | 24             |  |

#### Binary ROMs (+5 Volts)

| Organization | Part Number                | Access Time<br>(ns max) | No. of<br>Pins |

|--------------|----------------------------|-------------------------|----------------|

| 1024×8       | MCM68A308P                 | 350                     | 24             |

| 1024 × 8     | MCM68A308P74               | 350                     | 24             |

| 1024×8       | MCM68B308P                 | 250                     | 24             |

| 2048×8       | MCM68A316EP                | 350                     | 24             |

| 2048 × 8     | MCM68A316EP914             | 350                     | 24             |

| 4096×8       | MCM68A332P                 | 350                     | 24             |

| 4096 × 8     | MCM68A332P2 <sup>4</sup>   | 350                     | 24             |

| 8192×8       | MCM68364P35                | 350                     | 24             |

| 8192×8       | MCM68364P35-3 <sup>4</sup> | 350                     | 24             |

| 8192×8       | MCM68364P20                | 250                     | 24             |

| 8192×8       | MCM68364P25                | 200                     | 24             |

| 8192×8       | MCM68365P25                | 250                     | 24             |

| 8192×8       | MCM68365P35                | 350                     | 24             |

| 8192×8       | MCM68366P25                | 250                     | 24             |

| 8192×8       | MCM68366P35                | 350                     | 24             |

## CMOS ROMs (+5 Volts)

| Organization | Part Number               | Access Time<br>(ns max) | No. of<br>Pins |

|--------------|---------------------------|-------------------------|----------------|

| 256×4        | MCM14524                  | 1200                    | 16             |

| 2048×8       | MCM65516P43               | 430                     | 18             |

| 2048×8       | MCM65516P43M <sup>4</sup> | 430                     | 18             |

| 2048×8       | MCM65516P55               | 550                     | 18             |

# **PROMs**

| Organization | Part Number | Access Time<br>(ns max) | No. of<br>Pins |

|--------------|-------------|-------------------------|----------------|

| 32×8         | MCM10139    | 20                      | 16             |

| 256 × 4      | MCM10149    | 25                      | 16             |

### **TTL PROMs**

| Organization | Part Number | Access Time<br>(ns max) | Output  | No. of<br>Pins |

|--------------|-------------|-------------------------|---------|----------------|

| 512×4        | MCM7621*    | 70                      | 3-State | 16             |

| 512×8        | MCM7641*    | 70                      | 3-State | 24             |

| 1024×4       | MCM7643     | 70                      | 3-State | 18             |

| 1024×8       | MCM7681     | 70                      | 3-State | 24             |

| 2048×4       | MCM7685     | 70                      | 3-State | 18             |

| 2048 × 8     | MCM76161*   | -70                     | 3-State | 24             |

#### MEMORY SYSTEMS SELECTOR GUIDE

#### STANDARD MEMORY SYSTEMS

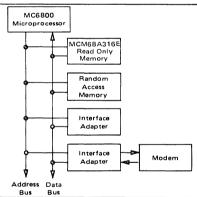

Motorola Memory Systems offers a variety of standard add-in memory modules to support LSI, PDP, VAX, UNIBUS, and MULTIBUS architectures. Many of these systems offer parity options and depopulated configurations. Some systems have EDAC for detecting and correcting erroneous data. Fast read access times are featured in all systems for compatibility with the most popular and latest computer systems.

#### **Board Selector Guide**

| Host Computer                                          | Motorola Device | Organization*                                         | Access Time<br>Typ (ns) | Parity |

|--------------------------------------------------------|-----------------|-------------------------------------------------------|-------------------------|--------|

| LS-11/23, PDP-11/03                                    | MMS1132N3128    | 128K × 16                                             | 300                     | No     |

|                                                        | MMS1132P3128    | 128K × 18                                             | 300                     | Yes    |

|                                                        | MMS1142N0016    | 16K × 16 CMOS RAMs                                    | 150                     | No     |

| PDP-11/04 through                                      | MMS1117-38PC    | 64K × 18                                              | 300                     | Yes    |

| PDP-11/60 (Uses HEX SPC Slot)                          | MMS1117-48PC    | 64K × 18                                              | 350                     | Yes    |

| PDP-11/04, PDP-11/34                                   | MMS1128P3064    | 64K × 18                                              | 300                     | Yes    |

| (Modified UNIBUS Compatible)                           | MMS1128P3096    | 96K × 18                                              | 300                     | Yes    |

| PDP-11/04, PDP-11/24                                   | MMS1119P3128    | 128K × 18                                             | 300                     | Yes    |

| PDP-11/34 (Modified and Extended<br>UNIBUS Compatible) | MMS1119P4128    | 128K × 18                                             | 350                     | Yes    |

| PDP-11/44                                              | MMS1129E4512    | 1 Mbyte with EDAC (Error<br>Detection and Correction) | 350                     | No     |

| PDP-11/70                                              | MMS1170E1064    | 256 Kbyte***                                          | ••                      | No     |

| VAX-11/750                                             | MMS750AE1064    | 256 Kbyte***                                          | ••                      | No     |

|                                                        | MMS750BE1256    | 1 Mbyte***                                            | ••                      | No     |

| VAX-11/780                                             | MMS780AE1032    | 256 Kbyte***                                          |                         | No     |

| SBC 80/-, SBC 86/-                                     | MMS8512E        | 512 Kbyte (with EDAC)                                 | 350                     | No     |

| (MULTIBUS Compatible)                                  | MM \$8256E      | 256 Kbyte (with EDAC)                                 | 350                     | No     |

| EXORmacs, VERSAmodule                                  | MMS68KE4512     | 512 Kbyte (with EDAC)                                 | 350                     | No     |

LSI, PDP, VAX, and UNIBUS are trademarks of Digital Equipment Corp.

MULTIBUS is a trademark of Intel.

\*Only the most popular versions are listed. Depopulated models are also available in most series.

\*\*Access Time is a function of DEC controller as well as listed array card.

\*\*\*These cards support EDAC. Actual circuitry is on DEC controller board.

#### CUSTOM MEMORY SYSTEMS

Motorola Memory Systems has the engineering expertise necessary to support numerous applications, ranging from industrial machine control to geophysical exploration. Designs are made to customer specifications. User-defined evaluations are performed in addition to Memory Systems' standard testing procedures.

The design engineering group has over 100 man years of experience, including the thorough knowledge of semiconductor technology that is a must when designing complete systems. State-of-the-art techniques are implemented when a system is being constructed. Interleaving and block transferring are used to enhance overall system performance. Memory Systems designers are specialists at incorporating Error Detection and Correction (EDAC) to improve reliability and increase Mean Time Between Failure (MTBF). Sophisticated computer aided design equipment enhances layout of the printed circuit boards and dense memory arrays.

The circuit boards are partially assembled using automatic insertion equipment, lowering the burden on the assembly line.

Quality Assurance is intense at every stage of production.

Every product is thoroughly tested and evaluated by computer-controlled test equipment, and must meet customer specifications or be rejected.

The customer's satisfaction is the number one priority of Motorola Memory Systems. On-time customer delivery is stressed. A computerized inventory control system provides constant data on product availability. Highly trained field service personnel and the product engineering staff are always available for customer assistance. Motorola Representatives and Systems Engineers are located nationwide to assist our customers.

For more information on custom memory systems...

CALL TOLL FREE 1-800-531-5118 (512-928-6776 in Texas)

OR WRITE Motorola Memory Systems Marketing Dept. V1230 3501 Ed Bluestein Blvd. Austin, Texas 78721

# MOS Dynamic RAM

DRAM

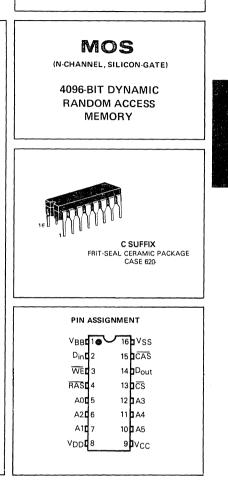

# **MCM4027A**

#### 4096-BIT DYNAMIC RANDOM ACCESS MEMORY

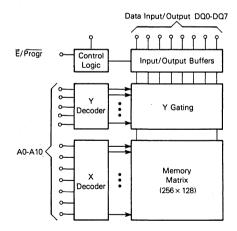

The MCM4027A is a 4096 x 1 bit high-speed dynamic Random Access Memory. It has smaller die size than the MCM4027 providing improved speed selections. The MCM4027A is fabricated using Motorola's highly reliable N-channel silicon-gate technology.

By multiplexing row and column address inputs, the MCM4027A requires only six address lines and permits packaging in Motorola's standard 16-pin dual-in-line packages. Complete address decoding is done on chip with address latches incorporated.

All inputs are TTL compatible, and the output is 3-state TTL compatible. The MCM4027A incorporates a one-transistor cell design and dynamic storage techniques, with each of the 64 row addresses requiring a refresh cycle every 2.0 milliseconds.

- Maximum Access Time = 120 ns MCM4027AC1 150 ns - MCM4027AC2 200 ns - MCM4027AC3 250 ns - MCM4027AC4

- Maximum Read and Write Cycle Time = 320 ns - MCM4027AC1, C2 375 ns - MCM4027AC3, C4

- Low Power Dissipation 470 mW Max (Active) 27 mW Max (Standby)

- 3-State Output for OR-Ties

- On-Chip Latches for Address, Chip Select, and Data In

- Power Supply Pins on Package Corners for Optimum Layout

- Industry Standard 16-Pin Package

- Page-Mode Capability

- Compatible with the Popular 2104/MK4096/MCM6604

- Second Source for MK4027

#### TRUTH TABLE

|     | Inpu | its       |    |            | Data Out   |                   | Cvcle Power       | Ref | Function                |

|-----|------|-----------|----|------------|------------|-------------------|-------------------|-----|-------------------------|

| RAS | CAS  | <u>CS</u> | WE | Previous   | Interim    | Present           | Cycle Power       | nei | Function                |

| L   | L    | L         | L  | Valid data | High Imp.  | Input data        | Full-operating    | Yes | Write cycle             |

| L   | L    | L         | н  | Valid data | High Imp.  | Valid data (cell) | Full-operating    | Yes | Read cycle              |

| L   | L    | н         | x  | Valid data | High Imp.  | High Imp.         | Full-operating    | Yes | Deselected-refresh      |

| L   | н    | х         | х  | Valid data | Valid data | Valid data        | Reduced operating | Yes | RAS only-refresh        |

| н   | L    | х         | х  | Valid data | High Imp.  | High Imp.         | Standby           | No  | Standby-output disabled |

| н   | н    | х         | x  | Valid data | Valid data | Valid data        | Standby           | No  | Standby-output valid    |

H = High, L = Low, X = Don't Care

#### **OPERATING CHARACTERISTICS**

#### ADDRESSING

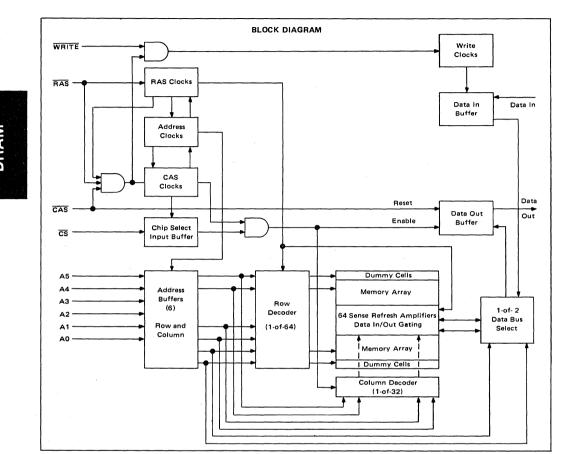

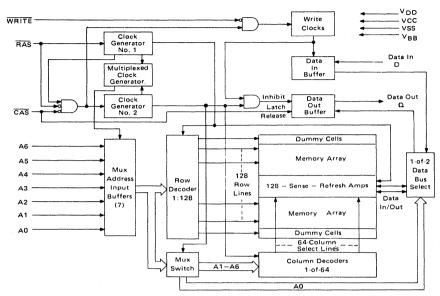

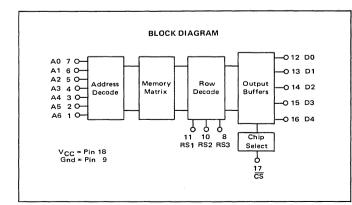

The MCM4027A has six address inputs (A0–A5) and two clock signals designated Row Address Strobe (RAS) and Column Address Strobe (CAS). At the beginning of a memory cycle, the six low order address bits A0 through A5 are strobed into the chip with RAS to select one of the 64 rows. The row address strobe also initiates the timing that will enable the 64 column sense amplifiers. After a specified hold time, the row address is removed and the six high order address bits (A6–A11) are placed on the address pins. This address is then strobed into the chip with CAS. Two of the 64 column sense amplifiers are selected by A1 through A5. A one of two data bus select is accomplished by A0 to complete the data selection. The Chip Select (CS) is latched into the port along with the column addresses.

#### DATA OUTPUT