# MOTOROLA INC.

# CMOS/NMOS SPECIAL FUNCTIONS DATA

| Handling and Design Guidelines          | 2  |

|-----------------------------------------|----|

| CMOS ADCs/DACs                          | 3  |

| CMOS Decoders/Display Drivers           | 4  |

| CMOS Operational Amplifiers/Comparators | 5  |

| CMOS/NMOS PLLs/Frequency Synthesizers   | 6  |

| CMOS Remote Control Functions           | 7  |

| CMOS Smoke Detectors                    | 8  |

| Miscellaneous Functions                 | 9  |

| Reliability                             | 10 |

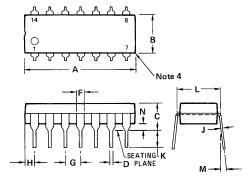

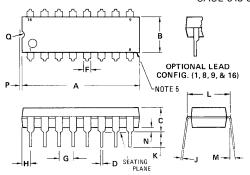

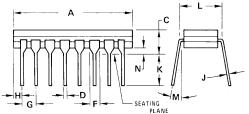

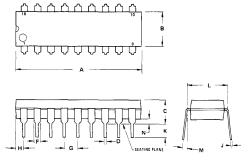

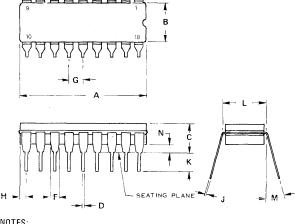

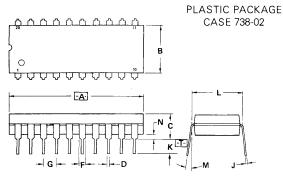

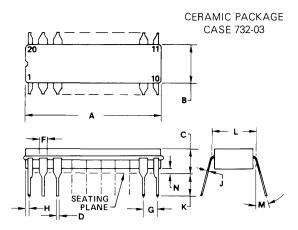

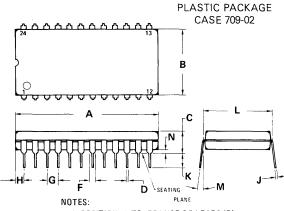

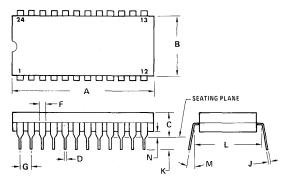

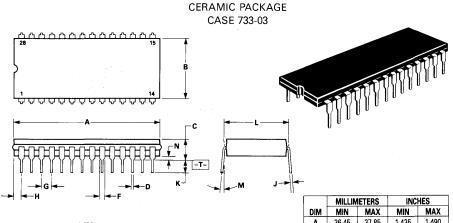

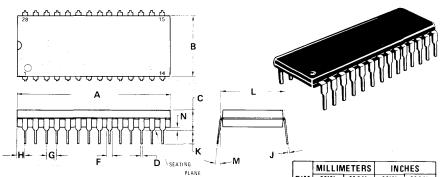

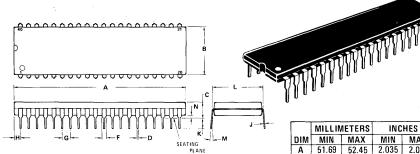

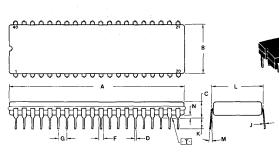

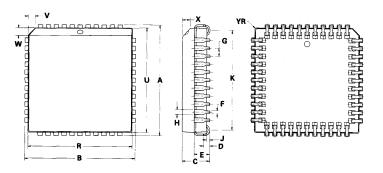

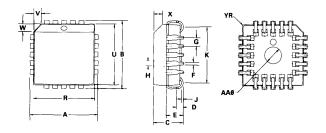

| Package Dimensions                      | 11 |

**Master Index**

Prepared by Technical Information Center

This book presents technical data for the CMOS and NMOS Special Function integrated circuits. Complete specifications are provided in the form of data sheets. In addition, a Function Selector Guide and a Handling Precautions chapter have been included to familiarize the user with these circuits.

Motorola reserves the right to make changes to any product herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights nor the rights of others.

Motorola Inc. general policy does not recommend the use of its components in life support applications where in a failure or malfunction of the component may directly threaten life or injury. Per Motorola Terms and Conditions of Sale, the user of Motorola components in life support applications assumes all risk of such use and indemnifies Motorola against all damages.

For marketing and application information contact:

Motorola Inc.

P.O. Box 6000

Austin, TX 78762

Attn: MOS Logic Marketing

Mail Stop: F-8

Series A Second Printing ©Motorola Inc., 1986 Previous Edition ©1984 "All Rights Reserved"

Product Preview data sheets herein contain information on a product under development. Motorola reserves the right to change or discontinue these products without notice. Advance Information data sheets herein contain information on new products. Specifications and information are subject to change without notice.

# Master Index

### **MASTER INDEX**

This index includes Motorola's entire MC14000 series CMOS products, although complete data sheets are included for only the Special Functions. Data sheets for devices in other books, are designated in the page number column as:

Logic - See DL131, CMOS Logic Data

Telecom - See DL136, Telecommunications Data

MCU - See DL132R1, Single-Chip Microcomputer Data

MPU - See DL133, 8-Bit Microprocessor and Peripheral Data

| Device<br>Number |                                                | Page   |

|------------------|------------------------------------------------|--------|

| MC               | Description                                    | Number |

| 6190             | N-Channel, Silicon Gate, Frequency Synthesizer | 6-3    |

| 6195             | N-Channel, Silicon Gate, Frequency Synthesizer | 6-4    |

| 6196             | N-Channel, Silicon Gate, Frequency Synthesizer | 6-4    |

| 14000UB          | Dual 3-Input NOR Gate Plus Inverter            | Logic  |

| 14001B           | Quad 2-Input NOR Gate                          | Logic  |

| 14001UB          | Quad 2-Input NOR Gate                          | Logic  |

| 14002B           | Dual 4-Input NOR Gate                          | Logic  |

| 14002UB          | Dual 4-Input NOR Gate                          | Logic  |

| 14006B           | 18-Bit Static Shift Register                   | Logic  |

| 14007UB          | Dual Complementary Pair Plus Inverter          | Logic  |

| 14008B           | 4-Bit Full Adder                               | Logic  |

| 14011B           | Quad 2-Input NAND Gate                         | Logic  |

| 14011UB          | Quad 2-Input NAND Gate                         | Logic  |

| 14012B           | Dual 4-Input NAND Gate                         | Logic  |

| 14012UB          | Dual 4-Input NAND Gate                         | Logic  |

| 14013B           | Dual D Flip-Flop                               | Logic  |

| 14014B           | 8-Bit Static Shift Register                    | Logic  |

| 14015B           | Dual 4-Bit Static Shift Register               | Logic  |

| 14016B           | Quad Analog Switch/Multiplexer                 | Logic  |

| 14017B           | Decade Counter/Divider                         | Logic  |

| 14018B           | Presettable Divide-by-N Counter                | Logic  |

| 14020B           | 14-Bit Binary Counter                          | Logic  |

| 14021B           | 8-Bit Static Shift Register                    | Logic  |

| 14022B           | Octal Counter/Divider                          | Logic  |

| 14023B           | Triple 3-Input NAND Gate                       | Logic  |

| 14023UB          | Triple 3-Input NAND Gate                       | Logic  |

| 14024B           | 7-Stage Ripple Counter                         | Logic  |

| 14025B           | Triple 3-Input NOR Gate                        | Logic  |

| 14025UB          | Triple 3-Input NOR Gate                        | Logic  |

| 14027B           | Dual J-K Flip-Flop                             | Logic  |

| 14028B           | BCD-to-Decimal/Binary-to-Octal Decoder         | Logic  |

| 14029B           | Binary/Decade Up/Down Counter                  | Logic  |

| 14032B           | Triple Serial Adder (Positive Logic)           | Logic  |

| Device                      |                                                   |                    |

|-----------------------------|---------------------------------------------------|--------------------|

| Number                      |                                                   | Page               |

| MC                          | Description                                       | Number             |

| 14034B                      | 8-Bit Universal Bus Register                      | Logic              |

| 14035B                      | 4-Bit Shift Register                              | Logic              |

| 14038B                      | Triple Serial Adder (Negative Logic)              | Logic              |

| 14040B                      | 12-Bit Binary Counter                             | Logic              |

| 14042B                      | Quad Transparent Latch                            | Logic              |

| 14043B                      | Quad NOR R-S Latch                                | Logic              |

| 14044B                      | Quad NAND R-S Latch                               | Logic              |

| 14046B                      | Phase-Locked Loop                                 | 6-13               |

| 14049UB                     | Hex Inverter/Buffer                               | Logic              |

| 14050B                      | Hex Buffer                                        | Logic              |

| 14051B                      | 8-Channel Analog Multiplexer/Demultiplexer        | Logic              |

| 14052B                      | Dual 4-Channel Analog Multiplexer/Demultiplexer   | Logic              |

| 14053B                      | Triple 2-Channel Analog Multiplexer/Demultiplexer | Logic              |

| 14060B                      | 14-Bit Binary Counter and Oscillator              | Logic              |

| 14066B                      | Quad Analog Switch/Multiplexer                    | Logic              |

| 14067B                      | 16-Channel Analog Multiplexer/Demultiplexer       | Logic              |

| 14068B                      | 8-Input NAND Gate                                 | Logic              |

| 14069UB                     | Hex Inverter                                      | Logic              |

| 14070B                      | Quad Exclusive OR Gate                            | Logic              |

| 14071B                      | Quad 2-Input OR Gate                              | Logic              |

| 14072B                      | Dual 4-Input OR Gate                              | Logic              |

| 14073B                      | Triple 3-Input AND Gate                           | Logic              |

| 14075B                      | Triple 3-Input OR Gate                            | Logic              |

| 14076B                      | Quad D-Type Register                              | Logic              |

| 14077B                      | Quad Exclusive NOR Gate                           | Logic              |

| 14078B                      | 8-Input NOR Gate                                  | Logic              |

| 14081B                      | Quad 2-Input AND Gate                             | Logic              |

| 14082B                      | Dual 4-Input AND Gate                             | Logic              |

| 14093B                      | Quad 2-Input NAND Schmitt Trigger                 | Logic              |

| 14094B                      | 8-Bit Bus-Compatible Shift/Store Latch            | Logic              |

| 14097B                      | Dual 8-Channel Analog Multiplexer/Demultiplexer   | Logic              |

| 14099B                      | 8-Bit Addressable Latch                           | Logic              |

| 14160B                      | Synchronous Programmable Decade Counter           | Logic              |

| 14161B                      | Synchronous Programmable 4-Bit Binary Counter     | Logic              |

| 14162B                      | Synchronous Programmable Decade Counter           | Logic              |

| 14163B                      | Synchronous Programmable 4-Bit Binary Counter     | Logic              |

| 14103B<br>14174B            | Hex D Flip-Flop                                   | Logic              |

| 14174B<br>14175B            | Quad D Flip-Flop                                  | Logic              |

| 14173B<br>14194B            | 4-Bit Universal Shift Register                    | Logic              |

| 14400                       | PCM Mono-circuit                                  | Telecom            |

| 14400                       | PCM Mono-circuit                                  | Telecom            |

| 1 <del>44</del> 01<br>14402 | PCM Mono-circuit                                  | Telecom            |

| 14402<br>14403              |                                                   |                    |

| 14403<br>14405              | PCM Mono circuit                                  | Telecom            |

| 14405                       | PCM Mono-circuit                                  | Telecom<br>Telecom |

| 14400                       | Dinary-to-rhone ruise Converter                   | i elecom           |

| Device<br>Number<br>MC | Description                                                | Page<br>Numbe |

|------------------------|------------------------------------------------------------|---------------|

| 14409                  | Binary-to-Phone Pulse Converter                            | Telecom       |

| 14410                  | 2-of-8 Tone Encoder                                        |               |

| 14411                  | Bit-Rate Frequency Generator                               |               |

| 14412                  | Universal Low-Speed Modem                                  |               |

| 14413                  | PCM Sampled Data Filter                                    |               |

| 14414                  | PCM Sampled Data Filter                                    | Telecom       |

| 14415                  | Quad Precision Timer/Driver                                |               |

| 14416                  | PCM Time Slot Assigner Circuit                             | Telecom       |

| 14417                  | PCM Time Slot Assigner Circuit                             | Telecom       |

| 14418                  | PCM Time Slot Assigner Circuit                             | Telecom       |

| 14419                  | 2-of-8 Keypad-to-Binary Encoder                            | Telecom       |

| 14422                  | Remote Control Transmitter (Product Cancelled)             |               |

| 14433                  | 3½ Digit A/D Converter                                     | 3-3           |

| 14435                  | 3½ Digit A/D Logic Subsystem (Product Cancelled)           | 3-15          |

| 14442                  | Microprocessor-Compatible A/D Converter                    |               |

| 14443                  | 6-Channel A/D Converter Subsystem                          |               |

| 14444                  | Microprocessor-Compatible A/D Converter                    | 3-29          |

| 14447                  | 6-Channel A/D Converter Subsystem                          | 3-39          |

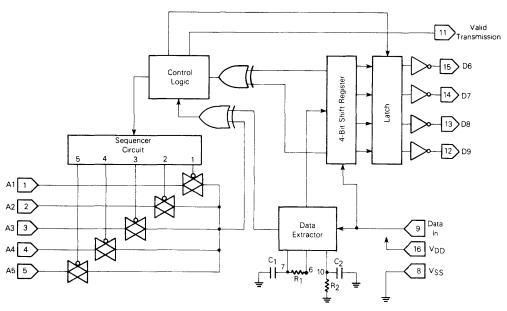

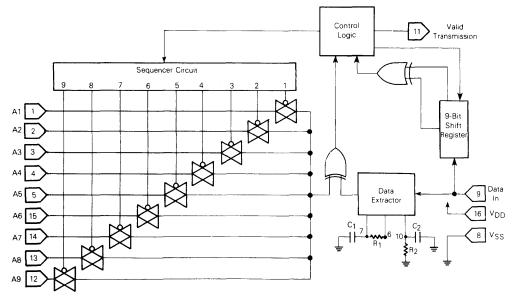

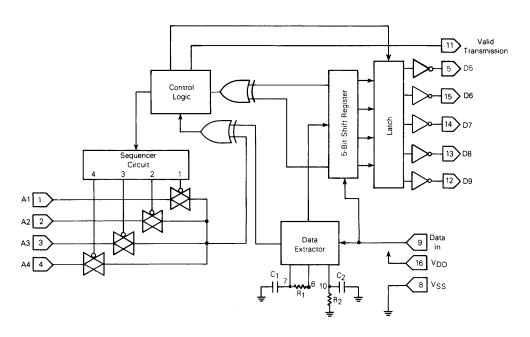

| 14457                  | Remote Control Transmitter                                 | 7-3           |

| 14458                  | Remote Control Receiver                                    | 7-3           |

| 14460                  | Automotive Speed Control Processor                         | 9-3           |

| 14461                  | Smoke Detector Circuit (Product Cancelled)                 | _             |

| 14462                  | Smoke Detector Circuit (Product Cancelled)                 |               |

| 14464                  | Smoke Detector Circuit (Product Cancelled)                 |               |

| 14465                  | Smoke Detector Circuit (Product Cancelled)                 | _             |

| 14466                  | Low Cost Smoke Detector                                    | 8-3           |

| 14467-1                | Low Cost Smoke Detector                                    | 8-8           |

| 14468                  | Interconnectable Smoke Detector                            | 8-13          |

| 14469                  | Addressable Asynchronous Receiver/Transmitter              | 7-13          |

| 14490                  | Hex Contact Bounce Eliminator                              | 9-9           |

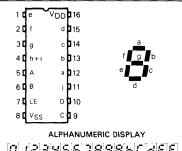

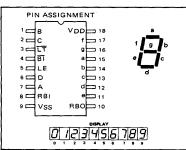

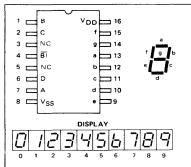

| 14495-1                | Hexadecimal-to-7 Segment Latch/Decoder ROM/Driver          | 4-3           |

| 14497                  | PCM Remote Control Transmitter                             | 7-21          |

| 14499                  | 7-Segment LED Display Decoder/Driver with Serial Interface | 4-8           |

| 14500B                 | Industrial Control Unit                                    | 9-16          |

| 14501UB                | Triple Gate                                                | Logic         |

| 14502B                 | Strobed Hex Inverter/Buffer                                | Logic         |

| 14503B                 | Hex 3-State Buffer                                         | Logic         |

| 14504B                 | Hex TTL- or CMOS-to-CMOS Level Shifter                     | Logic         |

| 14506B                 | Dual Expandable AOI Gate (Superceded by 14506UB)           | Logic         |

| 14506UB                | Dual Expandable AOI Gate                                   | Logic         |

| 14508B                 | Dual 4-Bit Latch                                           | Logic         |

| 14510B                 | BCD Up/Down Counter                                        | Logic         |

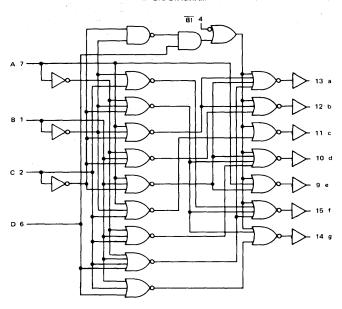

| 14511B                 | BCD-to-7-Segment Latch/Decoder/Driver                      | 4-14          |

| 14512B                 | 8-Channel Data Selector                                    | Logic         |

| 14513B                 | BCD-to-7-Segment Latch/Decoder/Driver with Ripple Blanking | 4-20          |

| Device<br>Number<br>MC | Description                                                     | Page<br>Number |

|------------------------|-----------------------------------------------------------------|----------------|

| 14514B                 | 4-Bit Transparent Latch/4-to-16 Line Decoder (High)             | Logic          |

| 14515B                 | 4-Bit Transparent Latch/4-to-16 Line Decoder (Low)              | Logic          |

| 14516B                 | Binary Up/Down Counter                                          | Logic          |

| 14517B                 | Dual 64-Bit Static Shift Register                               | Logic          |

| 14518B                 | Dual BCD Up Counter                                             | Logic          |

| 14519B                 | 4-Bit AND/OR Selector                                           | Logic          |

| 14520B                 | Dual Binary Up Counter                                          | Logic          |

| 14521B                 | 24-Stage Frequency Divider                                      | Logic          |

| 14522B                 | Programmable BCD Divide-by-N Counter                            | Logic          |

| 14526B                 | Programmable Binary Divide-by-N Counter                         | Logic          |

| 14527B                 | BCD Rate Multiplier                                             | Logic          |

| 14528B                 | Dual Monostable Multivibrator (Not Recommended for New Designs) | Logic          |

| 14529B                 | Dual 4-Channel Analog Data Selector                             | Logic          |

| 14530B                 | Dual 5-Input Majority Logic Gate                                | Logic          |

| 14531B                 | 12-Bit Parity Tree                                              | Logic          |

| 14532B                 | 8-Bit Priority Encoder                                          | Logic          |

| 14534B                 | 5-Decade Counter                                                | Logic          |

| 14536B                 | Programmable Timer                                              | Logic          |

| 14538B                 | Dual Precision Monostable Multivibrator                         | Logic          |

| 14539B                 | Dual 4-Channel Data Selector/Multiplexer                        | Logic          |

| 14541B                 | Programmable Oscillator-Timer                                   | Logic          |

| 14543B                 | BCD-to-7-Segment Latch/Decoder/Driver for Liquid Crystals       | 4-28           |

| 14544B                 | BCD-to-7-Segment Latch/Decoder/Driver with Ripple Blanking      | 4-33           |

| 14547B                 | High-Current BCD-to-7-Segment Decoder/Driver                    | 4-39           |

| 14548B                 | Dual Monostable Multivibrator (Retriggerable/Resettable)        | Logic          |

| 14549B                 | Successive Approximation Register                               | 3-40           |

| 14551B                 | Quad 2-Channel Analog Multiplexer/Demultiplexer                 | Logic          |

| 14553B                 | 3-Digit BCD Counter                                             | Logic          |

| 14554B                 | 2×2-Bit Parallel Binary Multiplier                              | Logic          |

| 14555B                 | Dual Binary to 1-of-4 Decoder                                   | Logic          |

| 14556B                 | Dual Binary to 1-of-4 Decoder (Inverting)                       | Logic          |

| 14557B                 | 1-to-64 Bit Variable Length Shift Register                      | Logic          |

| 14558B                 | BCD-to-7-Segment Decoder                                        | 4-44           |

| 14559B                 | Successive Approximation Register                               | 3-40           |

| 14560B                 | NBCD Adder                                                      | Logic          |

| 14561B                 | 9's Complementer                                                | Logic          |

| 14562B                 | 128-Bit Static Shift Register                                   | Logic          |

| 14566B                 | Industrial Time-Base Generator                                  | Logic          |

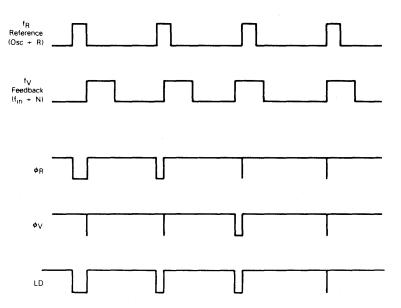

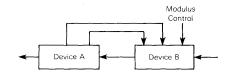

| 14568B                 | Phase Comparator and Programmable Counters                      | 6-18           |

| 14569B                 | Dual Programmable BCD/Binary Counter                            | Logic          |

| 14572UB                | Hex Gate                                                        | Logic          |

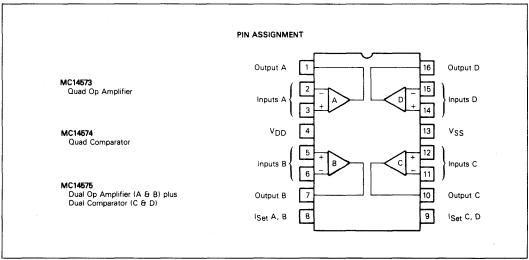

| 14573                  | Quad Programmable Op Amp                                        | 5-3            |

| 14574                  | Quad Programmable Comparator                                    | 5-3            |

| 14575                  | Programmable Dual Op Amp/Dual Comparator                        | 5-3            |

| 14580B                 | 4×4 Multiport Register                                          | Logic          |

| Number<br>MC | Description                                                         | Page<br>Number |

|--------------|---------------------------------------------------------------------|----------------|

| 14581B       | 4-Bit Arithmetic Logic Unit                                         | Logic          |

| 14582B       | Look-Ahead Carry Block                                              | Logic          |

| 14583B       | Dual Schmitt Trigger                                                | Logic          |

| 14584B       | Hex Schmitt Trigger                                                 | Logic          |

| 14585B       | 4-Bit Magnitude Comparator                                          | Logic          |

| 14597B       | 8-Bit Bus-Compatible Counter Latch                                  | Logic          |

| 14598B       | 8-Bit Bus-Compatible Addressable Latch                              | Logic          |

| 14599B       | 8-Bit Addressable Latch                                             | Logic          |

| 142100       | 4×4 Cross Point Switch                                              |                |

| 143403       | Quad Line Driver                                                    |                |

| 144110       | Hex D/A Converter with Serial Interface                             | 3-47           |

| 144111       | Quad D/A Converter with Serial Interface                            | 3-47           |

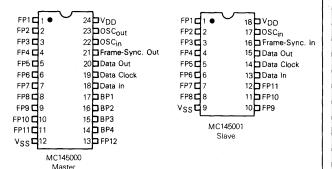

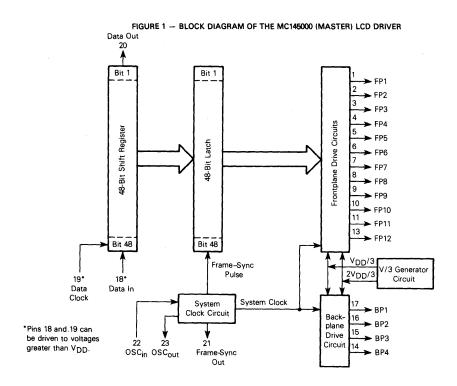

| 145000       | 48-Segment Multiplexed LCD Driver (Master)                          | 4-49           |

| 145001       | 44-Segment Multiplexed LCD Driver (Slave)                           | 4-49           |

| 145026       | Remote Control Encoder                                              | 7-27           |

| 145027       | Remote Control Decoder                                              | 7-27           |

| 145028       | Remote Control Decoder                                              | 7-27           |

| 145029       | Remote Control Decoder                                              | 7-27           |

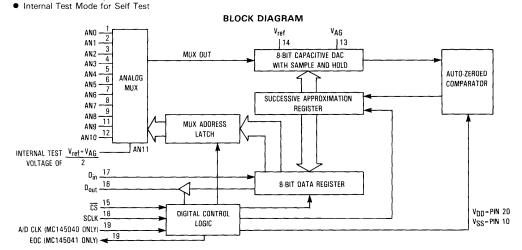

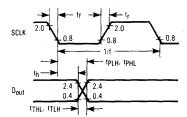

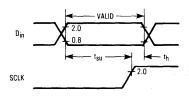

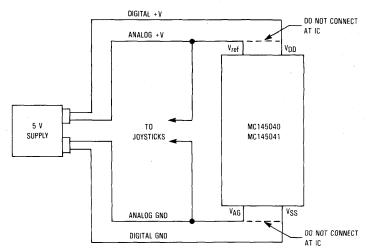

| 145040       | Analog-to-Digital Converter with Serial Interface                   | 3-52           |

| 145041       | Analog-to-Digital Converter with Serial Interface                   | 3-52           |

| 145100       | 4×4 Cross Point Switch                                              |                |

| 145104       | PLL Frequency Synthesizer (Not Recommended for New Designs)         | 6-28           |

| 145106       | PLL Frequency Synthesizer                                           | 6-29           |

| 145107       | PLL Frequency Synthesizer (Not Recommended for New Designs)         | 6-28           |

| 145109       | PLL Frequency Synthesizer (Not Recommended for New Designs)         | 6-28           |

| 145112       | PLL Frequency Synthesizer (Not Recommended for New Designs)         | 6-28           |

| 145143       | PLL Frequency Synthesizer (Not Recommended for New Designs)         | 6-35           |

| 145144       | 4-Bit Data Bus Input PLL Frequency Synthesizer                      |                |

|              | (Not Recommended for New Designs)                                   | 6-36           |

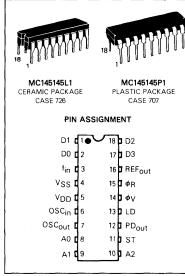

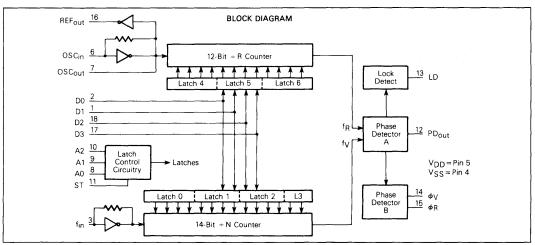

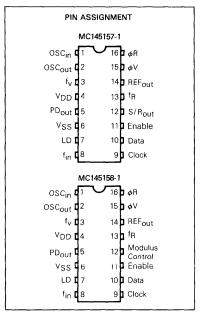

| 145145-1     | 4-Bit Data Bus Input PLL Frequency Synthesizer                      | 6-37           |

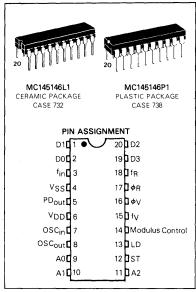

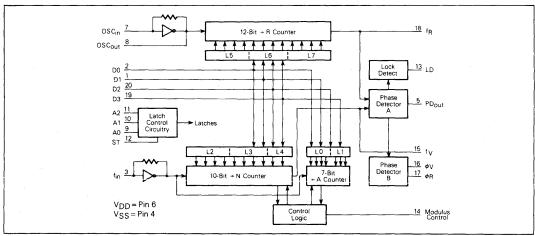

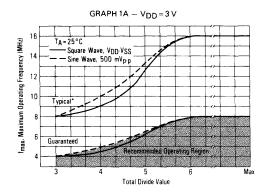

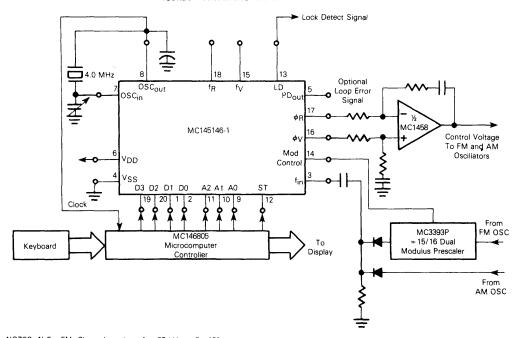

| 145146-1     | 4-Bit Data Bus Input PLL Frequency Synthesizer                      | 6-50           |

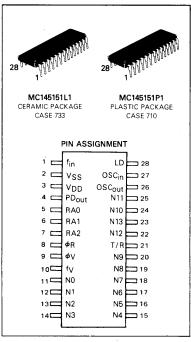

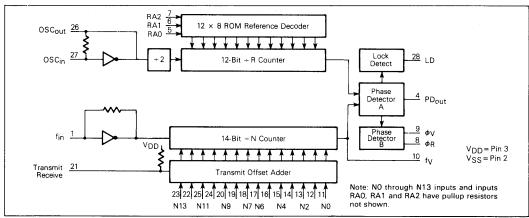

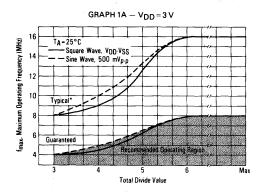

| 145151-1     | Parallel Input PLL Frequency Synthesizer                            | 6-63           |

| 145152-1     | Parallel Input PLL Frequency Synthesizer                            | 6-73           |

| 145155-1     | Serial Input PLL Frequency Synthesizer                              | 6-84           |

| 145156-1     | Serial Input PLL Frequency Synthesizer                              | 6-95           |

| 145157-1     | Serial Input PLL Frequency Synthesizer                              | 6-108          |

| 145158-1     | Serial Input PLL Frequency Synthesizer                              | 6-108          |

| 145159-1     | Serial Input PLL Frequency Synthesizer with Analog Phase Detector . | 6-120          |

| 145402       | 13-Bit Linear Codec                                                 | Telecom        |

| 145406       | RS-232 Interface                                                    | Telecom        |

| 145409       | Pulse Dialer                                                        | Telecom        |

| 145411       | Baud Rate Generator                                                 | Telecom        |

| 145414       | Dual Tuneable Low-Pass Sampled Data Filters                         | Telecom        |

| 145415       | Dual Tuneable Linear Phase Low-Pass Sampled Data Filters            |                |

| 145418       | Master Digital Loop Transceiver                                     | Telecom        |

| Device<br>Number<br>MC | Description                                              | Page<br>Number |

|------------------------|----------------------------------------------------------|----------------|

| 145419                 | Slave Digital Loop Transceiver                           | Telecom        |

| 145422                 | MDPSK Universal Digital Loop Transceiver (2-Wire Master) |                |

| 145426                 | MDPSK Universal Digital Loop Transceiver (2-Wire Slave)  |                |

| 145428                 | Data Set Interface                                       |                |

| 145429                 | Telset Audio Interface Circuit                           | Telecom        |

| 145432                 | 2600 Hz Tone Signalling Filter                           | Telecom        |

| 145433                 | Tuneable Notch/Band-Pass Filter                          | Telecom        |

| 145440                 | Low-Speed Modem Filter                                   | Telecom        |

| 145441                 | Low-Speed Modem Filter                                   | Telecom        |

| 145445                 | 300 Baud FSK Modem                                       | Telecom        |

| 145450                 | 1200 Baud FSK Modem                                      | Telecom        |

| 145453                 | 33-Segment LCD Driver with Serial Interface              | 4-59           |

| 146805                 | Family of 8-Bit CMOS MCUs/MPUs                           | MCU,MPU        |

| 146818                 | Real-Time Clock/RAM                                      | MCU,MPU        |

| 146823                 | Parallel Interface                                       | MCU,MPU        |

| 1468705                | 8-Bit CMOS MCUs with EPROM                               | MCU,MPU        |

# **Handling and Design Guidelines**

### HANDLING AND DESIGN GUIDELINES

#### HANDLING PRECAUTIONS

All MOS devices have an insulated gate that is subject to voltage breakdown. The gate oxide for Motorola's devices is about 800 Å thick and breaks down at a gate-source potential of about 100 V. The high-impedance gates on the devices are protected by resistor-diode networks. However, these on-chip networks do not make the IC immune to electrostatic damage (ESD). Laboratory tests show that devices may fail after one very high voltage discharge. They may also fail due to the cumulative effect of several discharges of lower potential.

Static-damaged devices behave in various ways, depending on the severity of the damage. The most severely damaged are the easiest to detect because the input or output has been completely destroyed and is either shorted to VDD, shorted to VSS, or open-circuited. The effect is that the device is no longer functional. Less severe cases are more difficult to detect because they appear as intermittent failures or degraded performance. Another effect of static damage is, often, increased leakage currents.

CMOS and NMOS devices are not immune to large static voltage discharges that can be generated while handling. For example, static voltages generated by a person walking across a waxed floor have been measured in the 4-15 kV range (depending on humidity, surface conditions, etc.). Therefore, the following precautions should be observed.

- Do not exceed the Maximum Ratings specified by the data sheet.

- All unused device inputs should be connected to V<sub>DD</sub> or V<sub>SS</sub>.

- All low-impedance equipment (pulse generators, etc.) should be connected to CMOS or NMOS inputs only after the device is powered up. Similarly, this type of equipment should be disconnected before power is turned off.

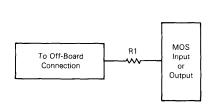

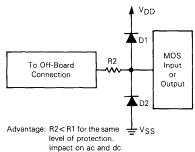

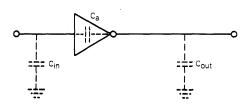

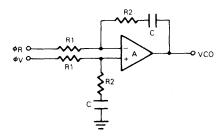

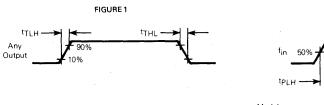

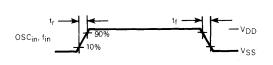

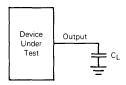

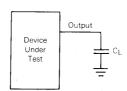

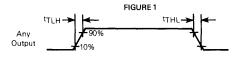

- 4. A circuit board containing CMOS or NMOS devices is merely an extension of the device and the same handling precautions apply. Contacting edge connectors wired directly to devices can cause damage. Plastic wrapping should be avoided. When external connections to a PC board address pins of CMOS or NMOS integrated circuits, a resistor should be used in series with the inputs or outputs. The limiting factor for the series resistor is the added delay caused by the time constant formed by the series resistor and input capacitance. This resistor will help limit accidental damage if the PC board is removed and brought into contact with static generating materials. For convenience, equations for added propagation delay and rise time effects due to series resistance size are given in Figure 1.

- 5. All CMOS or NMOS devices should be stored or

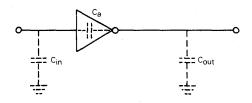

#### FIGURE 1 — NETWORKS FOR MINIMIZING ESD AND REDUCING CMOS LATCH UP SUSCEPTIBILITY

Advantage: Requires minimal board area

Disadvantage: R1 > R2 for the same level of protection, therefore rise and fall times, propagation delays, and output

drives are severely affected.

characteristics is minimized.

Disadvantage: More board area, higher initial cost

Note: These networks are useful for protecting the following:

- A. digital inputs and outputs

- B. analog inputs and outputs

- C. 3-state outputs

- D. bidirectional (I/O) ports

# EQUATION 1 — PROPAGATION DELAY vs. SERIES RESISTANCE

.....

R = the maximum allowable series resistance in ohms t= the maximum tolerable propagation delay in seconds C= the board capacitance plus the driven device's input capacitance in farads k = 0.33 for the MC145040/1 k = 0.7 for other devices

vs. SERIES RESISTANCE

$$R \approx \frac{t}{-Cabb}$$

EQUATION 2 - RISE TIME

where

where.

R = the maximum allowable series resistance in ohms

t = the maximum rise time per data sheet in seconds

C = the board capacitance plus the driven device's

input capacitance in farads

k = 0.7 for the MC145040/1

k = 2.3 for other devices

- transported in materials that are antistatic. Devices must not be inserted into conventional plastic "snow", styrofoam or plastic trays, but should be left in their original container until ready for use.

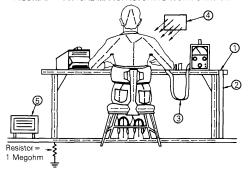

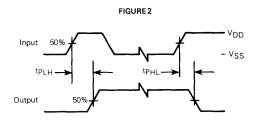

- 6. All CMOS or NMOS devices should be placed on a grounded bench surface and operators should ground themselves prior to handling devices, since a worker can be statically charged with respect to the bench surface. Wrist straps in contact with skin are strongly recommended. See Figure 2.

- 7. Nylon or other static generating materials should not come in contact with CMOS or NMOS circuits.

- 8. If automatic handling is being used, high levels of static electricity may be generated by the movement of devices, belts, or boards. Reduce static build-up by using ionized air blowers or room humidifiers. All parts of machines which come into contact with the top, bottom, and sides of IC packages must be grounded metal or other conductive material.

- Cold chambers using CO<sub>2</sub> for cooling should be equipped with baffles, and devices must be contained on or in conductive material.

- When lead-straightening or hand-soldering is necessary, provide ground straps for the apparatus used and be sure that soldering ties are grounded.

- The following steps should be observed during wave solder operations.

- The solder pot and conductive conveyor system of the wave soldering machine must be grounded to an earth ground.

- b. The loading and unloading work benches should have conductive tops which are grounded to an earth ground.

- Operators must comply with precautions previously explained.

- d. Completed assemblies should be placed in antistatic containers prior to being moved to subsequent stations.

- The following steps should be observed during board cleaning operation

- a. Vapor degreasers and baskets must be grounded to

- an earth ground. Operators must likewise be grounded.

- b. Brush or spray cleaning should not be used.

- Assemblies should be placed into the vapor degreaser immediately upon removal from the antistatic container.

- d. Cleaned assemblies should be placed in antistatic containers immediately after removal from the cleaning basket.

- e. High velocity air movement or application of solvents and coatings should be employed only when module circuits are grounded and a static eliminator is directed at the module.

- 13. The use of static detection meters for line surveillance is highly recommended.

- 14. Equipment specifications should alert users to the presence of CMOS or NMOS devices and require familiarization with this specification prior to performing any kind of maintenance or replacement of devices or modules.

- 15. Do not insert or remove CMOS or NMOS devices from test sockets with power applied. Check all power supplies to be used for testing devices to be certain there are no voltage transients present.

- Double check test equipment setup for proper polarity of voltage before conducting parametric or functional testing

- 17. Do not recycle shipping rails. Continuous use causes deterioration of their antistatic coating.

#### RECOMMENDED FOR READING

"Total Control of the Static in Your Business"

Available by writing to:

3M Company

Static Control Systems P.O. Box 2963

Austin, Texas 78769-2963

Or by Calling:

1-800-328-1368

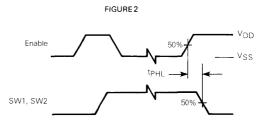

FIGURE 2 - TYPICAL MANUFACTURING WORK STATION

NOTES: 1. 1/16 inch conductive sheet stock covering bench top work area.

- 2. Ground strap.

- 3. Wrist strap in contact with skin.

- Static neutralizer. (Ionized air blower directed at work.)

Primarily for use in areas where direct grounding

is impractical.

- 5. Room humidifier. Primarily for use in areas where the relative humidity is less than 45%. Caution: building heating and cooling systems usually dry the air causing the relative humidity inside of buildings to be less than outside humidity.

#### CMOS LATCH UP

Latch up will not be a problem for most designs, but the designer should be aware of it, what causes it, and how to prevent it.

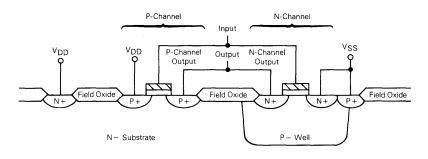

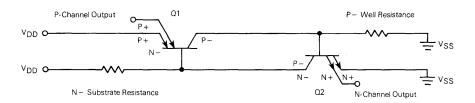

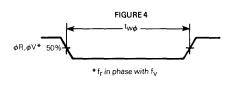

Figure 3 shows the layout of a typical CMOS inverter and Figure 4 shows the parasitic bipolar devices that are formed. The circuit formed by the parasitic transistors and resistors is the basic configuration of a silicon controlled rectifier, or SCR. In the latch-up condition, transistors Q1 and Q2 are turned on, each providing the base current necessary for the other to remain in saturation, thereby latching the devices on. Unlike a conventional SCR, where the device is turned on by applying a voltage to the base of the NPN transistor, the parasitic SCR is turned on by applying a voltage to the emitter of either transistor. The two emitters that trigger the SCR are the same point, the CMOS output. Therefore, to latch up the CMOS device, the output voltage must be greater than  $V_{DD} + 0.5 \, \text{Vdc}$  or less than  $-0.5 \, \text{Vdc}$  and have sufficient current to trigger the SCR. The latch-up mechanism is similar for the inputs.

Once a CMOS device is latched up, if the supply current is not limited, the device will be destroyed. Ways to prevent such occurrences are listed below.

Insure that inputs and outputs are limited to the maximum rated values, as follows:

- ~0.5≤Vin≤VDD+0.5 Vdc referenced to VSS

- $-0.5 \le V_{Out} \le V_{DD} + 0.5$  Vdc referenced to VSS  $|I_{ip}| \le 10 \text{ mA}$

- | I<sub>out</sub>| ≤ 10 mA when transients or dc levels exceed the supply voltages.

- 2. If voltage transients of sufficient energy to latch up the device are expected on the outputs, external protection diodes can be used to clamp the voltage. Another method of protection is to use a series resistor to limit the expected worst case current to the Maximum Ratings values. See Figure 1.

- If voltage transients are expected on the inputs, protection diodes may be used to clamp the voltage or a series resistor may be used to limit the current to a level less than the maximum rating of l<sub>in</sub> = 10 mA. See Figure 1

- Sequence power supplies so that the inputs or outputs of CMOS devices are not powered up first (e.g., recessed edge connectors may be used in plug-in board applications and/or series resistors).

- Power supply lines should be free of excessive noise.Care in board layout and filtering should be used.

- Limit the available power supply current to the devices that are subject to latch-up conditions. This can be accomplished with the power supply filtering network or with a current-limiting regulator.

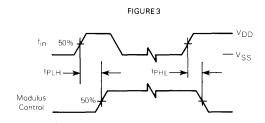

FIGURE 3 - CMOS WAFER CROSS SECTION

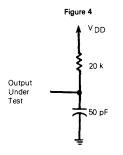

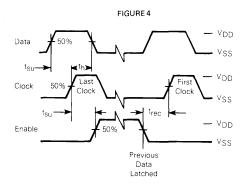

FIGURE 4 - LATCH UP CIRCUIT SCHEMATIC

# **CMOS ADCs/DACs**

### CMOS ADCs/DACs

| Device<br>Number | Function                                          |

|------------------|---------------------------------------------------|

| MC14433          | 3½ Digit A/D Converter                            |

| MC14435          | Product Cancelled - See Other A/D Converters      |

| MC14442          | Microprocessor-Compatible A/D Converter           |

| MC14443          | 6-Channel A/D Converter Subsystem                 |

| MC14444          | Microprocessor-Compatible A/D Converter           |

| MC14447          | 6-Channel A/D Converter Subsystem                 |

| MC14549B         | Successive Approximation Register                 |

| MC14559B         | Successive Approximation Register                 |

| MC144110         | Digital-to-Analog Converter with Serial Interface |

| MC144111         | Digital-to-Analog Converter with Serial Interface |

| MC145040         | Analog-to-Digital Converter with Serial Interface |

| MC145041         | Analog-to-Digital Converter with Serial Interface |

| Function                    | I/O Format                                                     | Resolution   | Number<br>of Analog<br>Channels | On-Chip<br>Oscillator | Other Features                  | Device<br>Number | Number<br>of Pins |

|-----------------------------|----------------------------------------------------------------|--------------|---------------------------------|-----------------------|---------------------------------|------------------|-------------------|

| ADC                         | Serial<br>[Compatible with                                     | 8 Bits       | 11                              |                       | Successive<br>Approximation     | MC145040         | 20                |

|                             | the Serial Peripheral<br>Interface (SPI) on<br>CMOS/NMOS MCUs] | 8 Bits       | 11                              | 1                     | Successive<br>Approximation     | MC145041         | 20                |

|                             | Parallel                                                       | 3½ Digit BCD | 1                               | ~                     | Dual Slope                      | MC14433          | 24                |

|                             | Ţ                                                              | 8 Bits       | 11                              |                       | Successive<br>Approximation     | MC14442          | 28                |

|                             |                                                                | 8 Bits       | 15                              |                       | Successive<br>Approximation     | MC14444          | 40                |

| ADC Linear<br>Subsystem     | Parallel                                                       | 8 to 10 Bits | 6                               |                       | Single Slope w/<br>Auto Zeroing | MC14443          | 16                |

|                             |                                                                | 8 to 10 Bits | 6                               |                       | Single Slope w/<br>Auto Zeroing | MC14447          | 16                |

| DAC                         | Serial<br>[Compatible with                                     | 6 Bits       | 6                               |                       | Emitter-Follower<br>Outputs     | MC144110         | 18                |

|                             | the Serial Peripheral<br>Interface (SPI)<br>on CMOS MCUs]      | 6 Bits       | 4                               |                       | Emitter-Follower<br>Outputs     | MC144111         | 14                |

| Successive<br>Approximation | Serial or Parallel                                             | ≤8 Bits      |                                 |                       | Cascadable for >8 Bits          | MC14549B         | 16                |

| Register                    |                                                                | ≤8 Bits      |                                 |                       | Cascadable for >8 Bits          | MC14559B         | 16                |

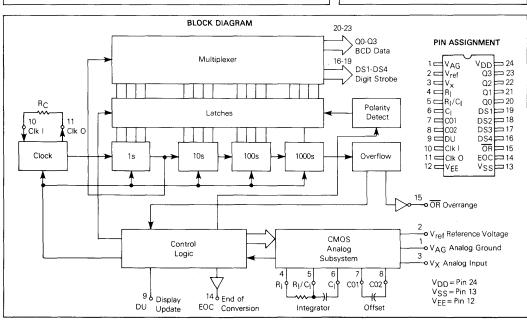

#### 3½ DIGIT A/D CONVERTER

The MC14433 is a high performance, low power, 3½ digit A/D converter combining both linear CMOS and digital CMOS circuits on a single monolithic IC. The MC14433 is designed to minimize use of external components. With two external resistors and two external capacitors, the system forms a dual slope A/D converter with automatic zero correction and automatic polarity.

The MC14433 is ratiometric and may be used over a full-scale range from 1.999 volts to 199.9 millivolts. Systems using the MC14433 may operate over a wide range of power supply voltages for ease of use with batteries, or with standard 5 volt supplies. The output drive conforms with standard B-Series CMOS specifications and can drive a low-power Schottky TTL load.

The high impedance MOS inputs allow applications in current and resistance meters as well as voltmeters. In addition to DVM/DPM applications, the MC14433 finds use in digital thermometers, digital scales, remote A/D, A/D control systems, and in MPU systems.

- Accuracy: ±0.05% of Reading ±1 Count

- Two Voltage Ranges: 1.999 V and 199.9 mV

- Up to 25 Conversions/s

- Z<sub>in</sub>>1000 M ohm

- Auto-Polarity and Auto-Zero

- Single Positive Voltage Reference

- Standard B-Series CMOS Outputs Drives One Low Power Schottky Load

- Uses On-Chip System Clock, or External Clock

- Wide Supply Range: e.g., ±4.5 V to ±8.0 V

- Overrange and Underrange Signals Available

- Operates in Auto Ranging Circuits

- Operates with LED and LCD Displays

- Low External Component Count

- See also Application Notes AN-769 and AN-770

- Chip Complexity: 1326 FETs

#### **CMOS LSI**

(LOW-POWER COMPLEMENTARY MOS)

3½ DIGIT A/D CONVERTER

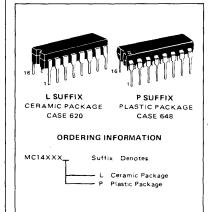

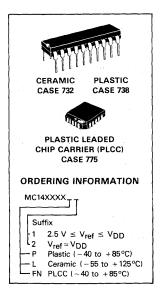

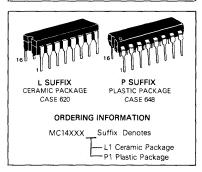

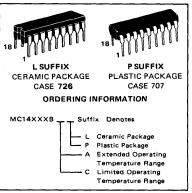

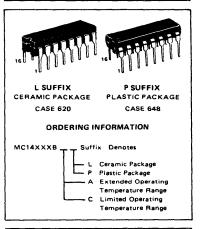

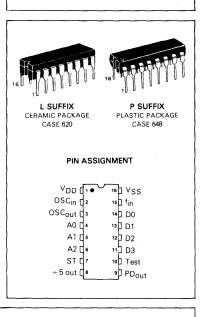

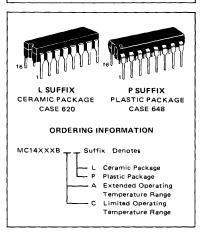

# ORDERING INFORMATION MC14XXX Suffix Denotes

MC14XXX Suffix Denotes

L Ceramic Package

P Plastic Package

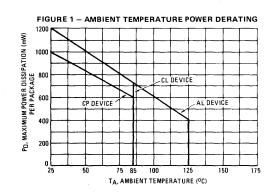

#### MAXIMUM RATINGS

| Rating                              | Symbol                             | Value                           | Unit |

|-------------------------------------|------------------------------------|---------------------------------|------|

| DC Supply Voltage                   | V <sub>DD</sub> to V <sub>FF</sub> | -0.5 to +18                     | V    |

| Voltage, any pin, referenced to VEE | V                                  | -0.5 to<br>V <sub>DD</sub> +0.5 | V    |

| DC Input Current, per Pin           | lin                                | ± 10                            | mA   |

| Operating Temperature Range         | TA                                 | - 40 to +85                     | °C   |

| Storage Temperature Range           | T <sub>stg</sub>                   | -65 to +150                     | °C   |

RECOMMENDED OPERATING CONDITIONS (VSS=0 or VEE)

| Parameter                                | Symbol          | Value          | Unit |

|------------------------------------------|-----------------|----------------|------|

| DC Supply Voltage - VDD to Analog Ground | V <sub>DD</sub> | +5.0 to +8.0   | Vdc  |

| V <sub>EE</sub> to Analog Ground         | VEE             | -2.8  to  -8.0 |      |

| Clock Frequency                          | fClk            | 32 to 400      | kHz  |

| Zero Offset Correction Capacitor         | Со              | 0.1 ± 20%      | μF   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that V<sub>in</sub> and V<sub>out</sub> be constrained to the range VEE≤(Vin or V<sub>out</sub>)≤V<sub>DD</sub>.

ELECTRICAL CHARACTERISTICS ( $C_1 = 0.1~\mu\text{F}$  mylar,  $R_1 = 470~\text{k}\Omega @V_{ref} = 2.000~\text{V}$ ,  $R_1 = 27~\text{k}\Omega @V_{ref} = 200.0~\text{mV}$ ,  $C_0 = 0.1~\mu\text{F}$ ,  $R_C = 300~\text{k}\Omega$ ; all voltages referenced to Analog Ground, pin 1, unless otherwise indicated)

|                                                                      | KM, all VC      | VDD        | VEE            |          | 0°C       |          |              | 85          |        |        |      |

|----------------------------------------------------------------------|-----------------|------------|----------------|----------|-----------|----------|--------------|-------------|--------|--------|------|

| Characteristic                                                       | Symbol          | Vdc        | Vdc            | Min      | Max       | Min      | Тур          | Max         | Min    | Max    | Unit |

| Linearity-Output Reading (Note 1)                                    | _               |            |                |          |           |          |              |             |        |        | %rdg |

| $(V_{ref} = 2.000 \text{ V})$                                        |                 | 5.0        | -5.0           | _        | -         | -0.05    | ± 0.05       | +0.05       | - 1    | - 1    |      |

|                                                                      |                 |            |                |          |           | -1 Count | 1            | +1 Count    |        |        |      |

| (V <sub>ref</sub> = 200.0 mV)                                        |                 | 5.0        | - 5.0          | _        |           | _        | ± 0.05       | _           | _      |        |      |

| Stability — Output Reading                                           | ł               |            |                |          |           |          |              |             |        |        |      |

| $(V_X = 199.0 \text{ mV}, V_{ref} = 200.0 \text{ mV})$               | -               | 5.0        | - 5.0          |          |           |          |              | 3★          |        |        | LSD  |

| Symmetry — Output Reading (Note 2)                                   |                 |            |                |          |           |          |              |             |        | l      |      |

| $(V_{ref} = 2.000 \text{ V})$                                        |                 | 5.0        | -5.0           |          |           |          |              | 4★          |        |        | LSD  |

| Zero-Output Reading                                                  |                 |            |                |          |           |          |              |             |        |        |      |

| $(V_X = 0 \ V, \ V_{ref} = 2.000 \ V)$                               |                 | 5.0        | -5.0           | _        | _         | -        | 0            | 0           | -      | -      | LSD  |

| Bias Current — Analog Input                                          | -               | 5.0        | - 5.0          | 1        | -         | - "      | ± 20         | ± 100       | -      |        | рA   |

| Reference Input                                                      |                 | 5.0        | -5.0           | -        |           | _        | ± 20         | ± 100       | - 1    | - !    |      |

| Analog Ground                                                        |                 | 5.0        | - 5.0          |          | _         |          | ± 20         | ± 500       | -      | - '    |      |

| Common Mode Rejection (f <sub>clk</sub> = 32 kHz,                    |                 | ĺ          | i I            |          |           |          |              |             | 1      |        |      |

| $V_X = 1.4 \text{ V}, V_{ref} = 2.000 \text{ V}$                     |                 | 5.0        | -5.0           | _        |           | _        | 65           | _           |        | -      | dB   |

| Input Voltage* Pins 9, 10 "0" Level                                  | VIL             |            |                |          |           |          |              |             |        |        | V    |

| $(V_0 = 4.5 \text{ or } 0.5 \text{ V})$                              |                 | 5.0        | - 1            | -        | 1.5       | -        | 2.25         | 1.5         | -      | 1.5    |      |

| $(V_0 = 9.0 \text{ or } 1.0 \text{ V})$                              |                 | 10         | -              | -        | 3.0       |          | 4.50         | 3.0         | -      | 3.0    |      |

| $(V_0 = 13.5 \text{ or } 1.5 \text{ V})$                             |                 | 15         | -              | -        | 4.0       |          | 6.75         | 4.0         | -      | 4.0    |      |

| "1" Level                                                            | VIH             |            |                |          |           |          |              |             |        |        | V    |

| $(V_O = 0.5 \text{ or } 4.5 \text{ V})$                              |                 | 5.0        | -              | 3.5      | -         | 3.5      | 2.75         | -           | 3.5    | _      |      |

| $(V_0 = 1.0 \text{ or } 9.0 \text{ V})$                              |                 | 10         | -              | 7.0      |           | 7.0      | 5.50         | _           | 7.0    | _      |      |

| $(V_0 = 1.5 \text{ or } 13.5 \text{ V})$                             |                 | 15         | -              | 11.0     |           | 11.0     | 8.25         | _           | 11.0   |        |      |

| Output Voltage - Pins 14 to 23                                       |                 |            | - 6            |          |           | 1        |              | 0.05        | i i    | 0.05   | V    |

| (V <sub>SS</sub> = 0 V) "0" Level                                    | VOL             | 5.0<br>5.0 | - 5.0<br>- 5.0 | 4.95     | 0.05      | 4.95     | 0<br>-5.0    | 0.05        | 4.95   | 0.05   |      |

| "1" Level<br>(Vss= -5.0 V) "0" Level                                 | Voh             | 5.0        | - 5.0<br>- 5.0 | 4.95     | -<br>4.95 | 4.95     | -5.0<br>-5.0 | -<br>- 4.95 | 4.95   | 4.95   |      |

| "1" Level                                                            | V <sub>OL</sub> | 5.0        | - 5.0          |          | 4.90      | 4.95     | 5.0          | -4.90       | 4.95   | - 4.33 |      |

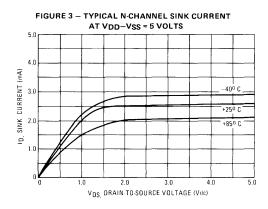

| Output Current - Pins 14 to 23                                       | VOH_            | 3.0        | - 0.0          | 4.00     |           | 4.55     | 0.0          |             | 7.00   |        | mA   |

| (VSS = 0 V)                                                          | {               | [          | ĺ              |          |           | ĺ        |              |             |        |        | IIIA |

| (V <sub>OH</sub> =4.6 V) Source                                      | ЮН              | 5.0        | -50            | - 0.25   | _         | -0.2     | - 0.36       | _           | - 0.14 | _      |      |

| $(V_{OI} = 0.4 \text{ V})$ Sink                                      | IOL             | 5.0        | -5.0           |          | _         | 0.51     | 0.88         | _           | 0.36   |        |      |

| (V <sub>SS</sub> = ~5.0 V)                                           | .01             | 0.0        | 0.0            | 0.0,     |           | 0.01     | 0.00         |             | 0.00   |        |      |

| (V <sub>OH</sub> ≈ 4.5 V) Source                                     | ЮН              | 5.0        | - 5.0          | - 0.62   | _         | -0.5     | - 0.9        |             | - 0.35 | _      |      |

| $(V_{OL} \approx -4.5 \text{ V}) \text{ Sink}$                       | 101             | 5.0        | -5.0           | 1.6      | _         | 1.3      | 2.25         | _           | 0.9    |        |      |

| Input Current — DU, Pin 9                                            | IDU             | 5.0        | - 5.0          |          | ±0.3      | -        | ± 0.00001    | ± 0.3       | _      | ± 1.0  | μA   |

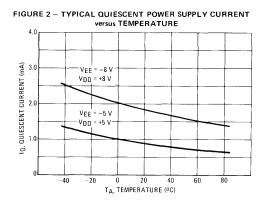

| Quiescent Current                                                    | 10              | 5.0        | - 5.0          | <u> </u> | 3.7       |          | 0.9          | 2.0         |        | 1.6    | mA   |

| (V <sub>DD</sub> to V <sub>EF</sub> , I <sub>SS</sub> = 0)           | l .a            | 8.0        | - 8.0          |          | 7.4       | _        | 1.8          | 4.0         |        | 3.2    |      |

| DC Supply Rejection                                                  |                 |            |                | $\vdash$ |           |          |              |             |        |        |      |

|                                                                      | _               | 5.0        | -5.0           | _        | _         | _        | 0.5          | _           | _      |        | mV/V |

| $(V_{DD} \text{ to } V_{EE}, I_{SS} = 0, V_{ref} = 2.000 \text{ V})$ |                 | 5.0        | -5.0           | _        | _         |          | 0.5          |             |        | _      | mV/V |

Notes: 1. Accuracy — The accuracy of the meter at full scale is the accuracy of the setting of the reference voltage. Zero is recalculated during each conversion cycle. The meaningful specification is linearity. In other words, the deviation from correct reading for all inputs other than positive full scale and zero is defined as the linearity specification.

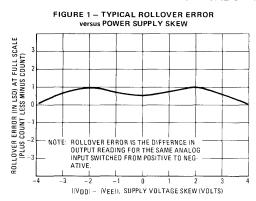

<sup>2.</sup> Symmetry - Defined as the difference between a negative and positive reading of the same voltage at or near full scale.

<sup>★</sup> Tighter tolerances are available. Consult Logic and Special Functions Product Marketing for details at (512) 928-6880.

<sup>\*</sup>Referenced to VSS for Pin 9. Referenced to VEE for Pin 10.

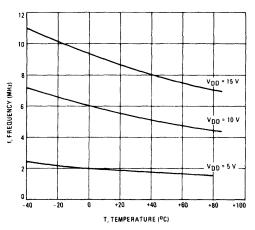

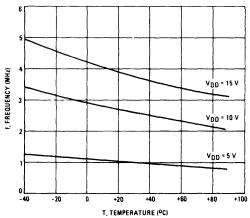

#### TYPICAL CHARACTERISTICS

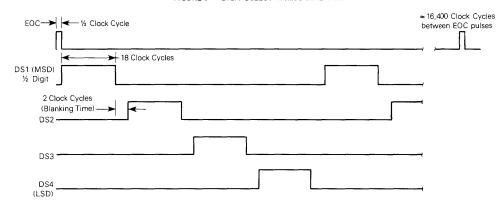

$\begin{array}{c} \text{CONVERSION RATE} = \frac{\text{CLOCK FREQUENCY}}{16,400} \pm 1.5\% \\ \\ \text{MULTIPLEX RATE} & = \frac{\text{CLOCK FREQUENCY}}{80} \\ \end{array}$

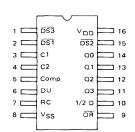

#### PIN DESCRIPTIONS

#### ANALOG GROUND (VAG, Pin 1)

Analog ground at this pin is the input reference level for the unknown input voltage (V $_{\chi}$ ) and reference voltage (V $_{\text{Tef}}$ ). This pin is a high impedance input. The allowable operating range for V $_{AG}$  is from V $_{EE}$  +2.8 V to V $_{DD}$  -4.5 V.

#### REFERENCE VOLTAGE (V<sub>ref</sub>, Pin 2) UNKNOWN INPUT VOLTAGE (V<sub>X</sub>, Pin 3)

This A/D system performs a ratiometric A/D conversion; that is, the unknown input voltage,  $V_{\chi}$ , is measured as a ratio of the reference voltage,  $V_{ref}.$  The full scale voltage is equal to that voltage applied to  $V_{ref}.$  Therefore, a full scale voltage of 1.999 V requires a reference voltage of 2.000 V while full scale voltage of 199.9 mV requires a reference voltage of 200 mV. Both Vx and  $V_{ref}$  are high impedance inputs. In addition to being a reference input, Pin 2 functions as a reset for the A/D converter. When Pin 2 is switched low (referenced to  $V_{EE}$ ) for at least 5 clock cycles, the system is reset to the beginning of a conversion cycle.

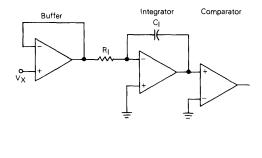

#### EXTERNAL COMPONENTS (R<sub>I</sub>, R<sub>I</sub>/C<sub>I</sub>, C<sub>I</sub>; Pins 4, 5, 6)

These pins are for external components for the integration used in the dual ramp A/D conversion. A typical value for the capacitor is 0.1  $_{\mu}\text{F}$  (polystyrene or mylar) while the resistor should be 470 k $\Omega$  for 2.0 V full scale operation and 27 k $\Omega$  for 200 mV full scale operation. These values are for a 66 kHz clock frequency which will produce a conversion time of approximately 250 ms. The equations governing the calculation for the values for integrator components are as follows:

$$R_{l} = \frac{V_{X}(max)}{C_{l}} \times \frac{T}{\triangle V}$$

$$\triangle V = V_{DD} - V_{X}(max) - 0.5 \text{ V}$$

$$T = 4000 \times \frac{1}{f_{Clk}}$$

where:

$R_I$  is in  $k\Omega$  VDD is the voltage at Pin 24 referenced to VAG VX is the voltage at Pin 3 referenced to VAG, in V  $f_{CIk}$  is the clock frequency at Pin 10 in kHz C $_I$  is in  $\mu F, \; \Delta V$  is in Volts T is the conversion time, in seconds

Example:

$$\label{eq:cj} \begin{split} &C_J = 0.1~\mu\text{F} \\ &V_DD = 5.0~\text{volts} \\ &f_{Clk} = 66~\text{kHz} \\ &For~V_X(\text{max}) = 2.0~\text{volts} \\ &R_J = 480~\text{k}\Omega~\text{(use 470~k}\Omega \pm 5\%) \end{split}$$

For

$$V_X(max) = 200 \text{ mV}$$

$R_1 = 28 \text{ k}\Omega \text{ (use 27 k}\Omega \pm 5\%)$

Note that for worst case conditions, the minimum allowable value for R<sub>I</sub> is a function of C<sub>I</sub> min, V<sub>DD</sub> min, and f<sub>CIk</sub> max. The worst-case condition does not allow  $\Delta V + V_X$  to exceed V<sub>DD</sub>. The 0.5 V factor in the above equation for  $\Delta V$  is for safety margin.

#### OFFSET CAPACITOR (C01, C02; Pins 7, 8)

These pins are used for connecting the offset correction capacitor. The recommended value is 0.1  $\mu$ F (polystyrene or mylar).

#### **DISPLAY UPDATE INPUT (DU, Pin 9)**

If a positive edge is received on this input prior to the ramp-down cycle, new data will be strobed into the output latches during that conversion cycle. When this pin is wired directly to the EOC output (Pin 14), every conversion will be displayed. When this pin is driven from an external source, the voltage should be referenced to VSS.

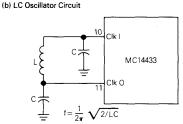

#### CLOCK (Clk I, Clk O, Pins 10, 11)

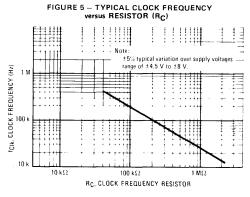

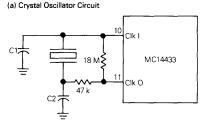

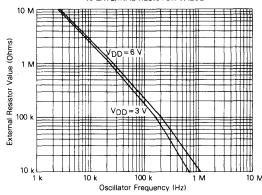

The MC14433 device contains its own oscillator system clock. A single resistor connected between pins 10 and 11 sets the clock frequency. If increased stability is desired, these pins will support a crystal or LC circuit. The clock input, Pin 10, may also be driven from an external clock source which need have only standard CMOS output drive. For external clock inputs this pin is referenced to VEE. A 300 k $\Omega$  resistor results in clock frequency of about 66 kHz. (See the typical characteristic curves.) For alternate circuits see Figure 7.

#### NEGATIVE POWER SUPPLY (VEE, Pin 12)

This is the connection for the most negative power supply voltage. The typical current is 0.8 mA. Note the current for the output drive circuit is not returned through this pin, but through Pin 13.  $V_X$ - $V_{EE}$  should be greater than 0.8 V.

# NEGATIVE POWER SUPPLY FOR OUTPUT CIRCUITRY AND INPUT DU (VSS, Pin 13)

This is the low voltage level for the output pins of the MC14433 (BCD, Digit Selects, EOC,  $\overline{OR}$ ) and the DU input. When this pin is connected to analog ground, the output voltage is from analog ground to VpD. When connected to VeE, the output swing is from Vee to VpD. The allowable operating range for Vss is between VpD -3.0 volts and Vee.

#### END OF CONVERSION (EOC, Pin 14)

The EOC output produces a positive pulse at the end of each conversion cycle. This pulse width is equivalent to one half the period of the system clock (Pin 11).

#### OVERRANGE (OR, Pin 15)

The  $\overline{\text{OR}}$  pin is low when V<sub>X</sub> exceeds V<sub>ref</sub>. Normally it is high.

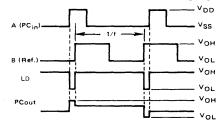

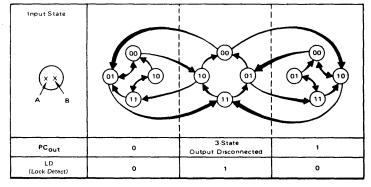

#### DIGIT SELECT (DS4, DS3, DS2, DS1; Pins 16, 17, 18, 19)

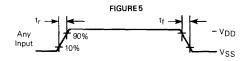

The digit select output is high when the respective digit is selected. The most significant digit (½ digit) turns on immediately after an EOC pulse followed by the remaining digits, sequencing from MSD to LSD. An interdigit blanking time of two clock periods is included to ensure that the BCD data has settled. The multiplex rate is equal to the clock frequency divided by 80. Thus with a system clock rate of 66 kHz, the multiplex rate would be 0.8 kHz. Relative timing among digital select outputs and the EOC signal is shown in the Digit Select Timing Diagram, Figure 8.

#### BCD DATA OUTPUTS (Q0, Q1, Q2, Q3, Pins 20, 21, 22, 23)

Multiplexed BCD outputs contain 3 full digits of information during DS2, 3, 4, while during DS1, the ½ digit, overange, underrange and polarity are available. The adjacent truth table shows the formats of the information during DS1.

#### POSITIVE POWER SUPPLY (VDD, Pin 24)

The most positive supply voltage pin.  $V_{DD} - V_X$  should be greater than 2.5 V.  $V_{DD} - V_{EE}$  should be greater than 7.8 V.  $V_{DD}$  determines  $V_{OH}$  for the digital outputs, and  $V_{IH}$  for the digital inputs.

#### TRUTH TABLE (DS1 = 1)

| Coded Condition of MSD | Q3 | Q2 | Q1 | Ω0 | BCD to 7 Segment<br>Decoding |

|------------------------|----|----|----|----|------------------------------|

| +0                     | 1  | 1  | 1  | 0  | Blank                        |

| -0                     | 1  | 0  | 1  | 0  | Blank                        |

| +0 UR                  | 1  | 1  | 1  | 1  | Blank                        |

| -0 UR                  | 1  | 0  | 1  | 1  | Blank                        |

| +1                     | 0  | 1  | 0  | 0  | 4 → 1 Hook up                |

| -1                     | 0  | 0  | 0  | 0  | 0 → 1 only seg b             |

| + 1 OR                 | 0  | 1  | 1  | 1  | 7 → 1 and c to               |

| - 1 OR                 | 0  | 0  | 1  | 1  | 3→1) MSD                     |

Notes for Truth Table:

- Q3 ½ digit, low for "1", high for "0"

- Q2 Polarity: "1" = positive, "0" = negative

- Q0 Out of range condition exists if Q0=1. When used in conjunction with Q3 the type of out of range condition is indicated, i.e., Q3=0→OR or Q3=1→UR.

When only segment b and c of the decoder are connected to the ½ digit of the display 4, 0, 7 and 3 appear as 1.

The overrange indication (Q3=0 and Q0=1) occurs when the count is greater than 1999, e.g., 1.999 V for a reference of 2.000 V. The underrange indication, useful for autoranging circuits, occurs when the count is less than 180, e.g., 0.180 V for a reference of 2.000 V.

Caution: If the most significant digit is connected to a display other than a "1" only, such as a full digit display, segments other than b and c must be disconnected. The BCD to seven segment decoder must blank on BCD inputs 1010 to 1111.

#### FIGURE 7 - ALTERNATE OSCILLATOR CIRCUITS

10 pF < C1 and C2 < 200 pF

For L = 5 mH and C = 0.01  $\mu$ F, f  $\approx$  32 kHz

#### FIGURE 8 — DIGIT SELECT TIMING DIAGRAM

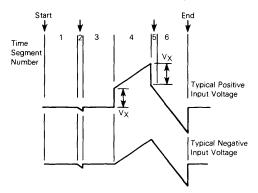

FIGURE 9 - INTEGRATOR WAVEFORMS AT PIN 6

FIGURE 10 — EQUIVALENT CIRCUIT DIAGRAMS OF THE ANALOG SECTION DURING SEGMENT 4 OF THE TIMING CYCLE

#### CIRCUIT OPERATION

The MC14433 CMOS integrated circuit, together with a minimum number of external components, forms a modified dual ramp A/D converter. The device contains the customary CMOS digital logic providing counters, latches, and multiplexing circuitry as well as the CMOS analog circuitry providing operational amplifiers and comparators required to implement a complete single chip A/D. Autozero, high input impedances, and autopolarity are features of this system. Using CMOS technology, an A/D with a wide range of power supply voltage and low power consumption is now available with the MC14433.

During each conversion, the offset voltages of the internal amplifiers and comparators are compensated for by the system's autozero operation. Also each conversion 'ratio-metrically' measures the unknown input voltage. In other words, the output reading is the ratio of the unknown voltage to the reference voltage with a ratio of 1 equal to the maximum count 1999. The entire conversion cycle requires slightly more than 16000 clock periods and may be divided into six different segments. The waveforms showing the conversion cycle with a positive input and a negative input are shown in Figure 9. The six segments of these waveforms are described below.

Segment 1 — The offset capacitor  $(C_0)$ , which compensates for the input offset voltages of the buffer and inte-

grator amplifiers, is charged during this period. Also, the integrator capacitor is shorted. This segment requires 4000 clock periods.

Segment 2 — The integrator output decreases to the comparator threshold voltage. At this time a number of counts equivalent to the input offset voltage of the comparator is stored in the offset latches for later use in the autozero process. The time for this segment is variable, and less than 800 clock periods.

Segment 3 — This segment of the conversion cycle is the same as Segment 1.

Segment 4 — Segment 4 is an up-going ramp cycle with the unknown input voltage (V<sub>X</sub>) as the input to the integrator. Figure 10 shows the equivalent configuration of the analog section of the MC14433. The actual configuration of the analog section is dependent upon the polarity of the input voltage during the previous conversion cycle.

Segment 5 — This segment is a down-going ramp period with the reference voltage as the input to the integrator. Segment 5 of the conversion cycle has a time equal to the number of counts stored in the offset storage latches during Segment 2. As a result, the system zeros automatically.

Segment 6 — This is an extension of Segment 5. The time period for this portion is 4000 clock periods. The results of the A/D conversion cycle are determined in this portion of the conversion cycle.

MC1403 +5 V ŘĈ≸ **未0.1 μ**F Segment Resistors 150 \(\Omega\) (7) 10 23 22 MC14543B MC1413 Ri\* 2 12 20 12 13 13 14 MC14433 14 15 0.1 µF \* \* ∘-5V' 13 715 16 6 -5V• Minus Sign 0.1 µF 19 18 17 16 200 Ω 5 V MPS-A12 Plus Sign DS1 DS2 110 Ω DS3 Common 88 Anode MC14013B +5V LFD Display Q Q \*R<sub>1</sub> = 470 k $\Omega$  for 2 V Range MPS-A12  $R_1 = 27 \text{ k}\Omega$  for 200 mV Range (4) \* \* Mylar Capacitor +5V

FIGURE 11 - 3½ DIGIT VOLTMETER-COMMON ANODE DISPLAYS, FLASHING OVERRANGE

#### APPLICATIONS INFORMATION

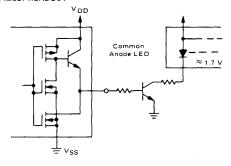

# 3½ DIGIT VOLTMETER — COMMON ANODE DISPLAYS, FLASHING OVERRANGE

An example of a  $3\frac{1}{2}$  digit voltmeter using the MC14433 is shown in the circuit diagram of Figure 11. The reference voltage for the system uses an MC1403 2.5 V reference IC. The full scale potentiometer can calibrate for a full scale of 199.9 mV or 1.999 V. When switching from 2 V to 200 mV operation,  $R_1$  is also changed, as shown on the diagram.

When using RC equal to 300 k $\Omega$ , the clock frequency for the system is about 66 kHz. The resulting conversion time is approximately 250 ms.

When the input is overrange, the display flashes on and off. The flashing rate is one-half the conversion rate. This is done by dividing the EOC pulse rate by 2 with ½ MC14013B flip-flop and blanking the display using the blanking input of the MC14543B.

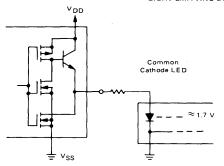

The display uses an LED display with common anode digit lines driven with an MC14543B decoder and an MC1413 LED driver. The MC1413 contains 7 Darlington transistor drivers and resistors to drive the segments of the display. The digit drive is provided by four MPS-A12 Darlington transistors operating in an emitter follower configuration. The MC14543B, MC14013B and LED displays are referenced to VEE via Pin 13 of the MC14433. This places the full power supply voltage across the display. The current for the display may be adjusted by the value of the segment resistors shown as 150 ohms in the above figure.

The power supply for the system is shown as a dual  $\pm$  5 V supply. However, the MC14433 will operate over a wide range of voltages, and balance between the  $\pm$ 5 and  $\pm$ 5 V supplies is *not* required. See the recommended operating conditions and Figure 1.

470 kt 0.1 uF 0.1 uF Cı Input ٧x Clk 300 k Clk C Resistor Network  $V_{AG}$ MC14511B MC14433 or Individual Resistors ŌR Zener Diode DU or EOC Q0 MC1403 Q1  $V_{ref}$ Reference 02 łD 03 ⇜ VILT Vss ~~ LE Vnn  $v_{DD}^g$ Vss VEE RDP DS3 DS2 DS1 DS4 for  $V_{ref} = 2.000 \text{ V}$  $R_{M}$ V<sub>X</sub>: 1.999 V full scale VEE\* +5V  $^{\dagger}$  for  $V_{ref} = 200.0 \text{ mV}$ (Minus) V<sub>X</sub>: 199.9 mV full scale (change 470 k $\Omega$  to R<sub>I</sub> = 27 k $\Omega$ Common Minus Cathode and decimal point position) Control LED \*VEE can range between -2.8 and Display -11 V. Also see Figure 18 for 5/7 MC1413 negative supply generated from a Digit Driver positive supply. Alternate Overrange Circuit with Separate LED -o+5∨ OR-1/7 MC1413

FIGURE 12 - 31/2 DIGIT VOLTMETER WITH LOW COMPONENT COUNT

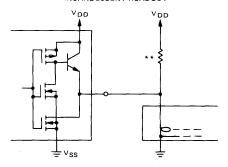

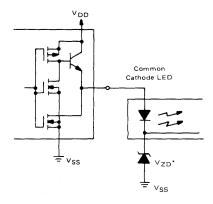

# 3½ DIGIT VOLTMETER WITH LOW COMPONENT COUNT USING COMMON CATHODE DISPLAYS

The 3½ digit voltmeter of Figure 12 is an example of the use of the MC14433 in a system with a minimum of components. This circuit uses only 11 components in addition to the MC14433 to operate the MC14433 and drive the LED displays.

In this circuit the MC14511B provides the segment drive for the 3% digits. The MC1413 provides sink for digit current. (The MC1413 is a device with 7 Darlingtons with comon emitters.) The worst case digit current is 7 times the segment current at % duty cycle. The peak segment current is limited by the value of R. The current for the display flows from VpD ( $\pm$ 0 to ground and does not flow through the VEE (negative) supply. The minus sign is controlled by one section of the MC1413 and is turned off by shunting the current through  $R_M$  to ground, bypassing the minus sign LED. The minus sign is derived from the Q2 output. The decimal point brightness is controlled by resistor  $R_{DP}$ . Since the brightness and the type and size of LED display are the

choice of the designer, the values of resistors R,  $R_M$ ,  $R_{DP}$ , and  $R_R$  that govern brightness are not given.

During an overrange condition the 3½ digit display is blanked at the BI pin on the MC14511B. The decimal point and minus sign will remain on during a negative overrange condition. In addition, an alternate overrange circuit with separate LED is shown.

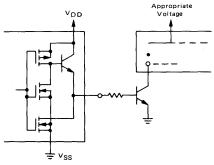

#### 3½ DIGIT VOLTMETER WITH LCD DISPLAY

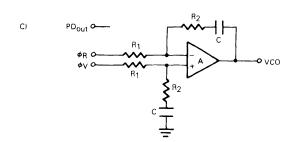

A circuit for a 3½ digit voltmeter with a liquid crystal display is shown in Figure 13. Three MC14643B LCD latch/decoder/display drivers are used to demultiplex, decode the three digits, and drive the LCD. The half digit and polarity are demultiplexed with the MC14013B dual D flip-flop.

Since the LCD is best driven by an ac signal across the LCD, the low-frequency square wave drive for the LCD is derived from the MC14024B binary counter which divides the digit select output from the A/D. This low frequency square wave is connected to the backplane of the LCD and to the individual segments through the combination of the output cir-

$0.1 \mu F$ 470 k 0.1 µF MC14024B C01 C02 RI RI/CI CI DS4 DS3 MC14433 VAG Q0 MC1403 Q1 Q2 VSS VEE 300 k MC14013B 1/4 MC14070B Q ã R | 1/4 MC14070B BIDCBAPHLD BIDCBAPhLD BIDC B APhLD MC14013B • + V MC14543B MC14543B MC14543B Plus Sign ā fedcba fedcba fedcba Q 1/4 MC14070B Minus Sign 0 0 0 0

FIGURE 13 - 31/2 DIGIT VOLTMETER WITH LCD DISPLAY

cuitry of the MC14543B and the exclusive OR gates at the outputs of the MC14013B. Alternatively the square wave can be derived from a 50/60 Hz input signal when available.

The minus sign and the decimal point to the right of the half digit are connected to the inverted low frequency square wave signal. Unused decimal points are tied directly to the low frequency square wave.

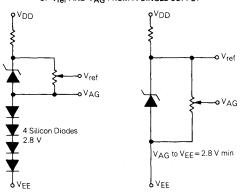

The system shown operates from two power supplies (plus and minus). Alternatively one supply can be used when VSS is connected to VEE. In this case a level must be set for analog ground, VAG, which must be at least 2.8 V above VEE. This circuit may be implemented with a resistor network, resistor/forward-biased diode network or resistor-zener diode network. For example, a 9 V supply can be used with 3 V between VAG and VEE, leaving 6 V for VDD to VAG. This system leaves a comfortable margin for battery degeneration (end of life). Two versions of this circuit for single supply operation is shown in Figure 14.

For panel meter operation from a single 5 V supply, a negative supply can be generated as shown in Figure 18.

FIGURE 14 — TWO CIRCUITS FOR GENERATION OF V<sub>ref</sub> AND V<sub>AG</sub> FROM A SINGLE SUPPLY

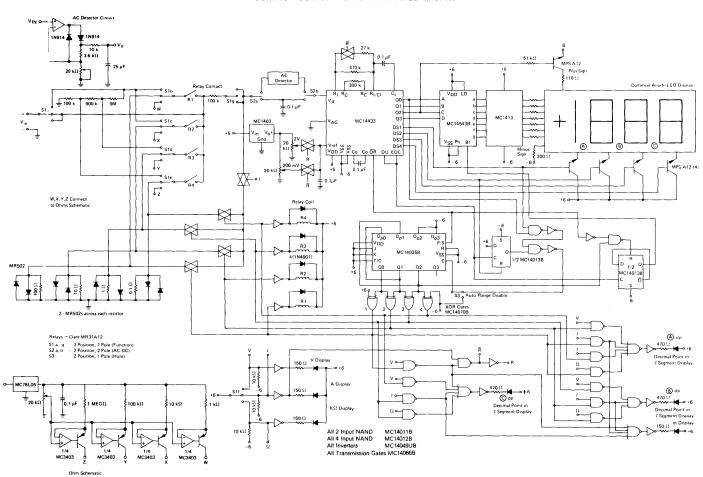

FIGURE 15 ~ 3½ DIGIT AUTORANGING MULTIMETER

#### 3½ DIGIT AUTORANGING MULTIMETER

An autoranging multimeter including ac and dc voltage ranges from 200 mV to 200 V, ac and dc current from 2 mA to 2 A fullscale and resistance ranges from 2 k $\Omega$  to 2 M $\Omega$  fullscale is shown in Figure 15. In this multimeter only two input jacks are required for all ranges and functions, eliminating the need for changing leads on the instrument when changing ranges or functions. Although only four ranges are provided for each function, the technique used may be expanded to more ranges if desired. Range switching uses mechanical relays. However, the relays may be replaced with solid state analog switches.

The MC14433 provides the overrange and underrange control signals for the automatic ranging circuits. For additional information, see Motorola Application Note AN-769, "Autoranging Digital Multimeter Using the MC14433 CMOS A/D Converter."

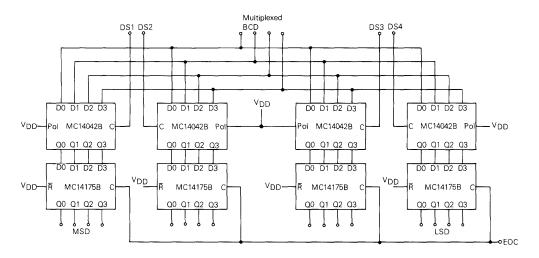

#### PARALLEL BCD DATA OUTPUT CIRCUIT

The output of the MC14433 may be demultiplexed to produce parallel BCD data as shown in Figure 16. Two levels of latches are required for a complete demultiplexing of the data since the outputs of the MC14042B latches change sequentially with the DS1 to DS4 strobe pulses. To key output validity to one leading edge, i.e., that of the EOC signal of the MC14433, information is transferred to the second set of latches (MC14175B latches). A single set of latches can be used when reading of output is restricted to within 12,000 clock pulses after EOC. This requires synchronous system operation with respect to the BCD data bus.

In this system the output ground level is V<sub>SS</sub>. In most cases, a two supply system with V<sub>SS</sub> connected to V<sub>AG</sub> is recommended. This allows connecting analog ground and digital ground together without destroying a power supply. This circuit works well with that of Figure 12.

FIGURE 16 - DEMULTIPLEXING FOR MC14433 BCD DATA

FIGURE 17 - CHANNEL DATA ACQUISITION HARDWARE

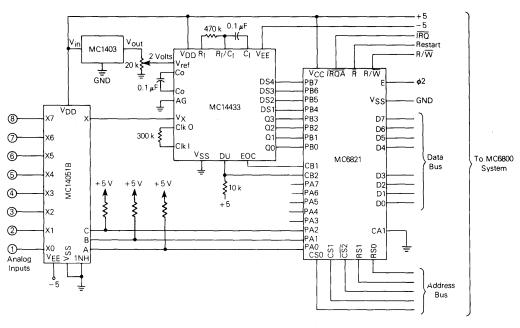

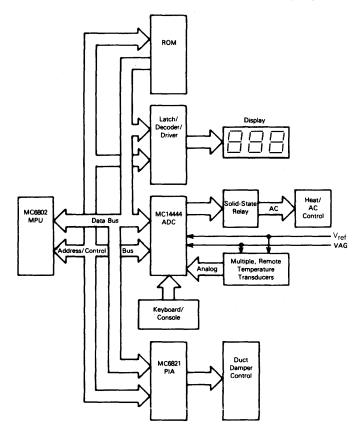

#### **8 CHANNEL DATA ACQUISITION NETWORK**

Figure 17 shows an 8-channel data acquisition network using the MC14433 and an MC6800 microprocessor system. The interface between the microprocessor data bus and the A/D system is done with an MC6821 PIA. One half of the PIA is used with the BCD and digit select outputs of the MC14433, while the second half of the PIA selects the chan-

nel to be measured via the MC14051B analog multiplexer. Control lines CB1 and CB2 are used for data flow control and are connected to DU and EOC of the MC14433.

A more detailed explanation of this system including the actual software required for the M6800 microprocessor may be found in Motorola Application Note AN-770, "Data Acquisition Networks With NMOS and CMOS."

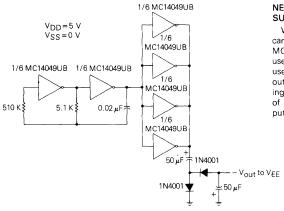

FIGURE 18 - NEGATIVE SUPPLY GENERATED FROM POSITIVE SUPPLY

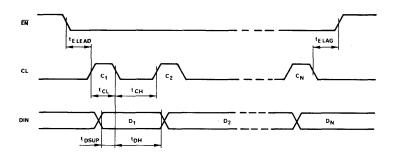

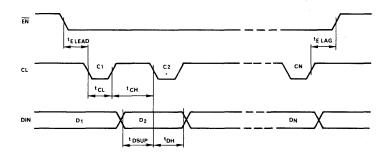

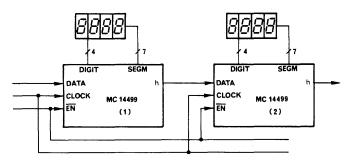

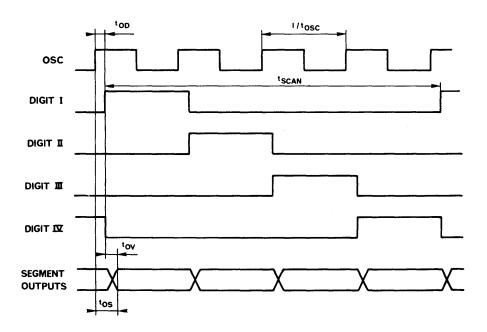

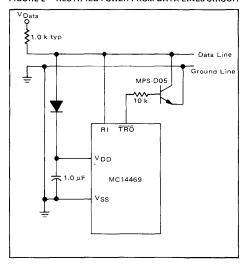

# NEGATIVE SUPPLY GENERATED FROM POSITIVE SUPPLY