# **MEMORY DATA**

| 1  | Selector Guide and Cross Reference   |

|----|--------------------------------------|

| 2  | CMOS Dynamic RAMs                    |

| 3  | DRAM Modules                         |

| 4  | Video RAMs                           |

| 5  | Pseudo Static RAMs                   |

| 6  | General MOS Static RAMs              |

| 7  | CMOS Fast Static RAMs                |

| 8  | CMOS Fast Static RAM Modules         |

| 9  | Application Specific MOS Static RAMs |

| 10 | MOS EEPROM                           |

| 11 | Military Products                    |

| 12 | Reliability Information              |

| 13 | Applications Information             |

| 14 | Mechanical Data                      |

|    |                                      |

### **DATA CLASSIFICATION**

### **Product Preview**

This heading on a data sheet indicates that the device is in the formative stages or in design (under development). The disclaimer at the bottom of the first page reads: "This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice."

### Advance Information

This heading on a data sheet indicates that the device is in sampling, preproduction, or first production stages. The disclaimer at the bottom of the first page reads: "This document contains information on a new product. Specifications and information herein are subject to change without notice."

### Fully Released

A fully released data sheet contains neither a classification heading nor a disclaimer at the bottom of the first page. This document contains information on a product in full production. Guaranteed limits will not be changed without written notice to your local Motorola Semiconductor Sales Office.

BurstRAM, DSPRAM, ParityRAM, and QuickRAM are trademarks of Motorola, Inc. SPARC is a trademark of Sun Microsystems.

## **MEMORIES**

Prepared by Technical Information Center

Motorola has developed a broad range of reliable memories for virtually any digital data processing system application. Complete specifications for the individual circuits are provided in the form of data sheets. In addition, a selector guide is included to simplify the task of choosing the best combination of circuits for optimum system architecture.

New Motorola memories are being introduced continually. For the latest releases, and additional technical information or pricing, contact your nearest authorized Motorola distributor or Motorola sales office.

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and a registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

DL113/D, Rev 6 ©MOTOROLA INC., 1990 Previous Edition © 1989 "All Rights Reserved"

### **CONTENTS**

|                            |                                                         | Page         |

|----------------------------|---------------------------------------------------------|--------------|

| Alphanumeric Index         |                                                         | ix           |

| CHAPTER 1                  |                                                         |              |

| Selector Guide             |                                                         | 1-3          |

|                            |                                                         | 1-7          |

|                            |                                                         |              |

| <b>CHAPTER 2 — CMOS D</b>  | YNAMIC RAMs                                             |              |

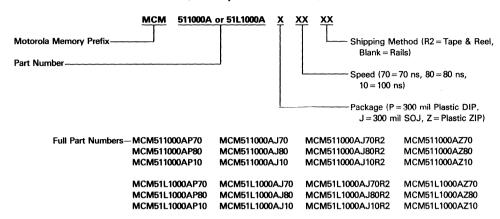

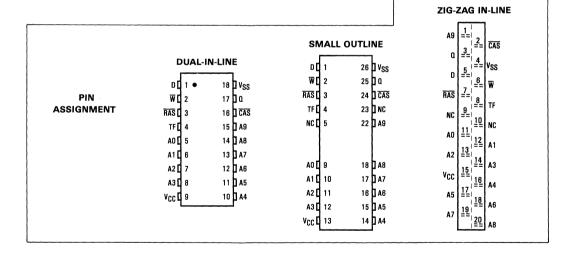

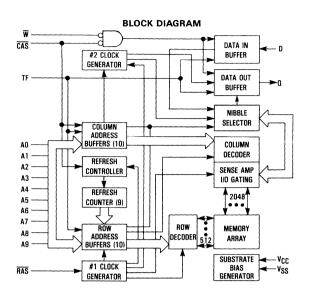

| MCM511000A                 | 1M × 1, 70/80/100 ns, Page Mode                         | 2-3          |

| MCM51L1000A                | 1M × 1, 70/80/100 ns, Page Mode, Low Power              | 2-3          |

| MCM511001A                 | 1M × 1, 70/80/100 ns, Nibble Mode                       | 2-18         |

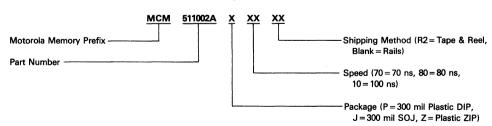

| MCM511002A                 | 1M × 1, 70/80/100 ns, Static Column                     | 2-33         |

| MCM514100                  | 4M × 1, 80/100 ns, Page Mode                            | 2-48         |

| MCM51L4100                 | 4M × 1, 80/100 ns, Page Mode, Low Power                 | 2-48         |

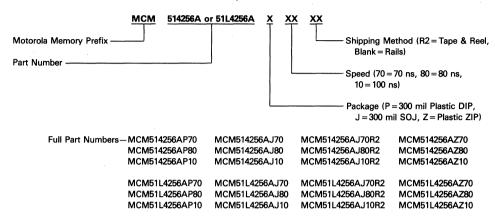

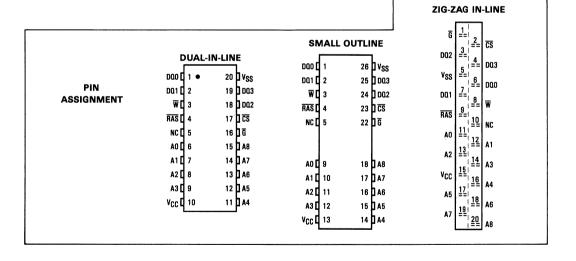

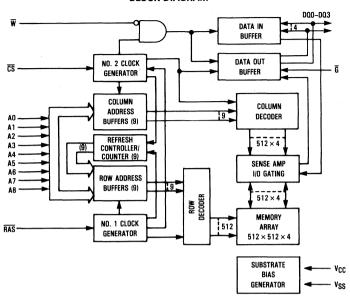

| MCM514256A                 | 256K × 4, 70/80/100 ns, Page Mode                       | 2-64         |

| MCM51L4256A<br>MCM514258A  | 256K × 4, 70/80/100 ns, Page Mode, Low Power            | 2-64<br>2-79 |

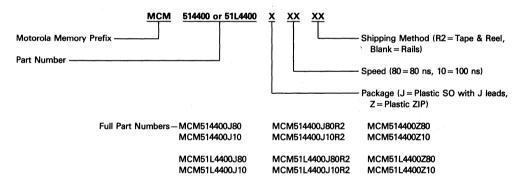

| MCM514400                  | 1M × 4, 80/100 ns, Page Mode                            | 2-79         |

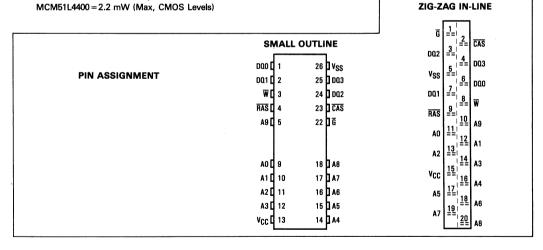

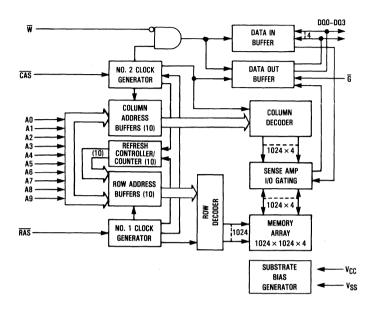

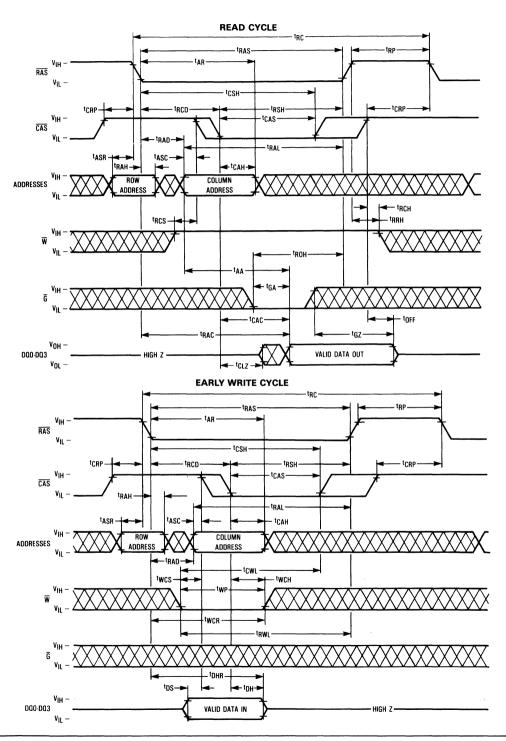

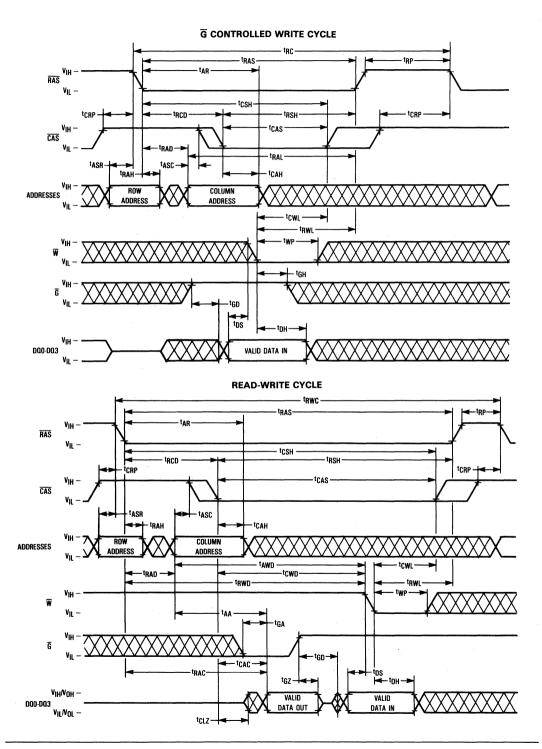

| MCM514400<br>MCM51L4400    | 1M × 4, 80/100 ns, Page Mode, Low Power                 | 2-94         |

| MONSTERFOO                 | 1W1 × 4, 00/100 113, 1 age Wode, Low 1 owel             | 2-34         |

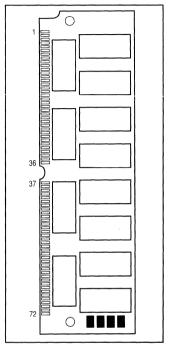

| CHAPTER 3 — DRAM M         | IODULES                                                 |              |

| MCM36100                   | 1M × 36, 80/100 ns                                      | 3-3          |

| MCM36L100                  | 1M × 36, 80/100 ns, Low Power                           | 3-3          |

| MCM36200                   | 2M × 36, 80/100 ns                                      | 3-15         |

| MCM36L200                  | 2M × 36 80/100 ns, Low Power                            | 3-15         |

| MCM36256                   | 256K × 36, 70/80/100 ns                                 | 3-27         |

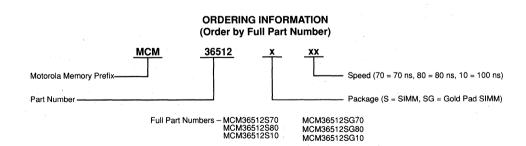

| MCM36512                   | 512K × 36, 70/80/100 ns                                 | 3-39         |

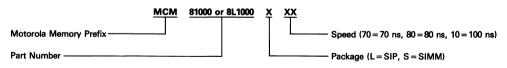

| MCM81000                   | 1M × 8, 70/80/100 ns                                    | 3-51         |

| MCM8L1000                  | 1M × 8, 70/80/100 ns, Low Power                         | 3-51         |

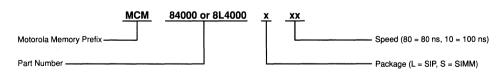

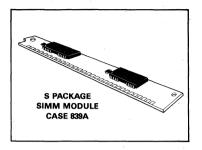

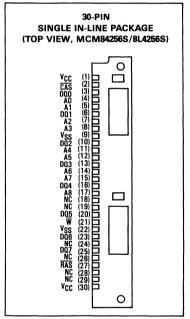

| MCM84000                   | 4M × 8, 80/100 ns                                       | 3-62         |

| MCM8L4000                  | 4M × 8, 80/100 ns, Low Power                            | 3-62         |

| MCM84256                   | 256K × 8, 70/80/100 ns                                  | 3-74         |

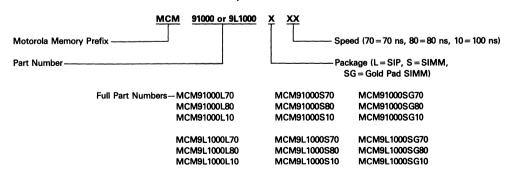

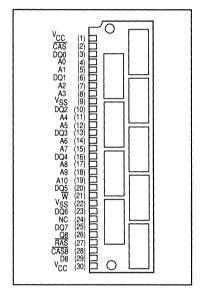

| MCM8L4256<br>MCM91000      | 256K × 8, 70/80/100 ns, Low Power                       | 3-74<br>3-85 |

| MCM9L1000                  | 1M × 9, 70/80/100 hs                                    | 3-85         |

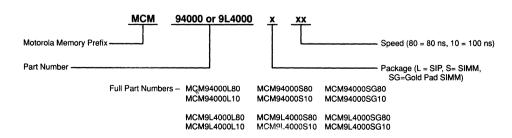

| MCM94000                   | 4M × 9, 80/100 ns                                       | 3-96         |

| MCM9L4000                  | 4M × 9, 80/100 ns, Low Power                            | 3-96         |

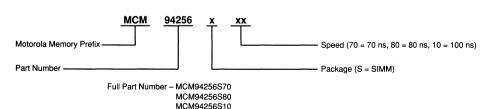

| MCM94256                   | 256K × 9, 70/80/100 ns                                  | 3-108        |

|                            | ,                                                       |              |

| <b>CHAPTER 4 — VIDEO R</b> | IAMs                                                    |              |

| MCM524258A                 | 256K × 4, 100/120 ns, Page Mode                         | 4-3          |

| MCM528128A                 | 128K × 8, 100/120 ns, Page Mode                         | 4-5          |

|                            |                                                         |              |

| CHAPTER 5 — PSEUDO         |                                                         |              |

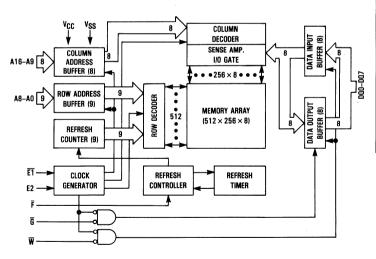

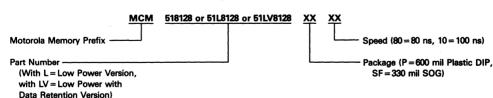

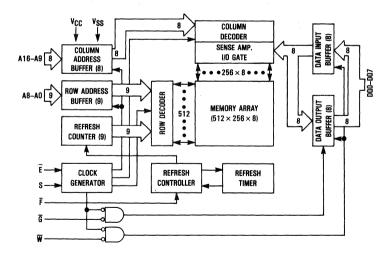

| MCM518128                  | 128K × 8, 100 ns, E1 and E2 Inputs                      | 5-3          |

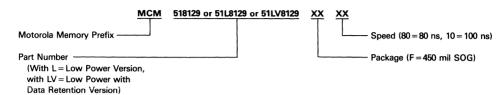

| MCM51L8128                 | 128K × 8, 80/100 ns, <u>E1</u> and E2 Inputs, Low Power | 5-3          |

| MCM51LV8128                | 128K × 8, 80/100 ns, E1 and E2 Inputs, Low Power,       | 5-3          |

| MCM518129                  | Data Retention                                          | 5-16         |

| MCM51L8129                 | 128K × 8, 80/100 ns, E and S Inputs, Low Power          | 5-16         |

| MCM51LV8129                | 128K × 8, 80/100 ns, E and S Inputs, Low Power,         | J-10         |

|                            | Data Retention                                          | 5-16         |

|                            |                                                         | 0.0          |

## **CONTENTS (Continued)**

|                           |                                          | Page                      |

|---------------------------|------------------------------------------|---------------------------|

|                           |                                          |                           |

| CHAPTER 6 — GENER         |                                          |                           |

| MCM2018A                  | 2K × 8, 35/45 ns                         | 6-3                       |

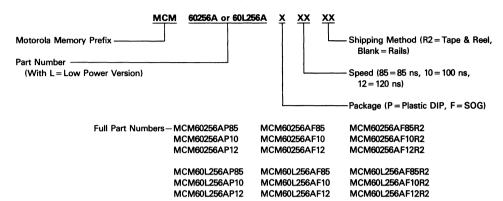

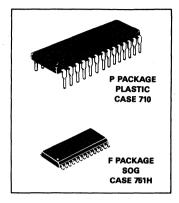

| MCM60256A                 | 32K × 8, 85/100/120 ns                   | 6-8                       |

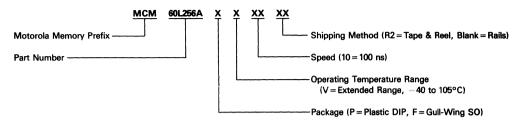

| MCM60L256A                | 32K × 8, 85/100/120 ns, Low Power        | 6-8                       |

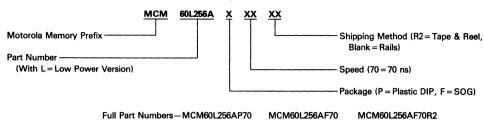

| MCM60L256A-70             | 32K × 8, 70 ns, Low Power                | 6-16                      |

| MCM60256A-C               | 32K × 8, 100 ns, –40 to 85°C             | 6-24                      |

| MCM60L256A-C              | 32K × 8, 100 ns, –40 to 85°C             | 6-24                      |

| MCM60L256A-V              | 32K × 8, 100 ns, –40 to 105°C            | 6-32                      |

| CHAPTER 7 — CMOS F        | FAST STATIC RAMS                         |                           |

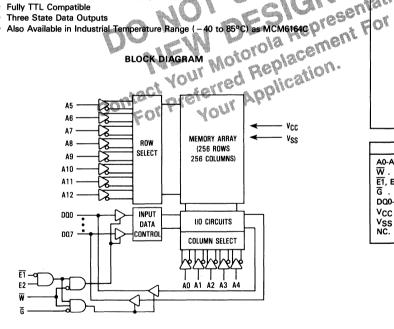

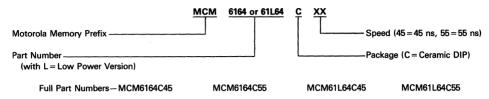

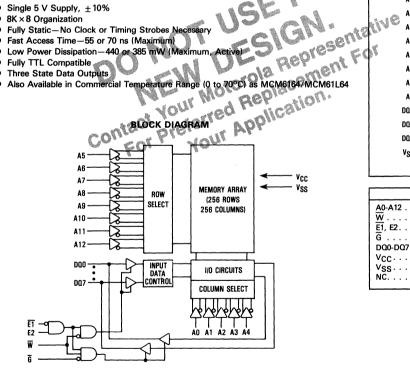

| MCM6164                   | 8K × 8, 45/55 ns                         | 7-3                       |

| MCM61L64                  | 8K × 8, 45/55 ns, Low Power              | 7-3                       |

| MCM6164C                  | 8K × 8, 55/70 ns, –40 to 85°C            | 7-11                      |

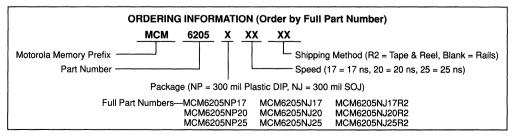

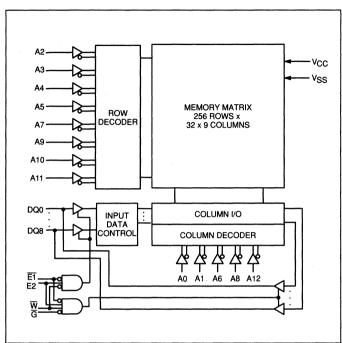

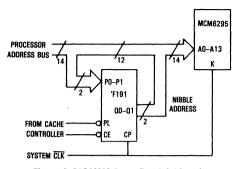

| MCM6205                   | 32K × 9, 30/35/45 ns                     | 7-19                      |

| MCM6205-17,20,25          | 32K × 9, 17/20/25 ns, See QuickRAM       | 7-122                     |

| MCM6205C-12.15            | 32K × 9, 12/15 ns, See QuickRAM II       | 7-142                     |

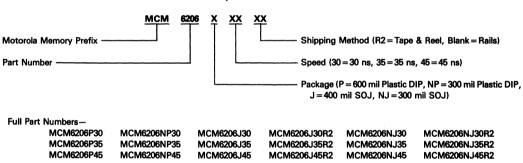

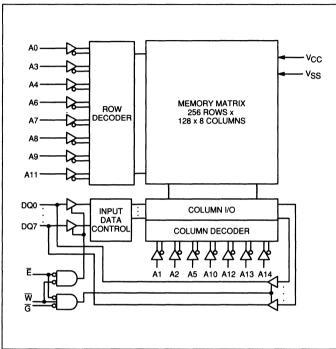

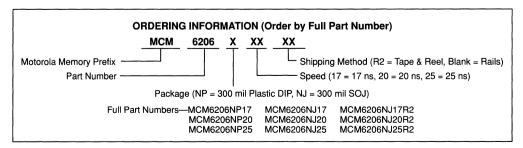

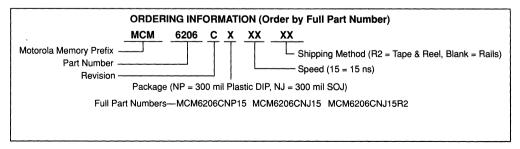

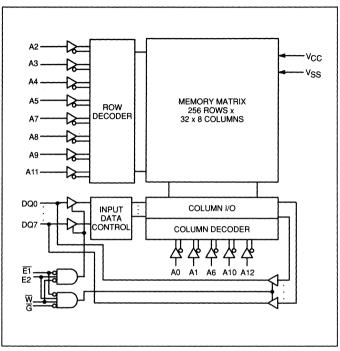

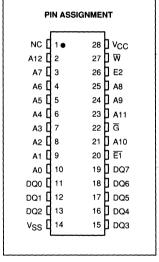

| MCM6206                   | 32K × 8, 30/35/45 ns                     | 7-26                      |

| MCM6206-17,20,25          | 32K × 8, 17/20/25 ns, See QuickRAM       | 7-122                     |

| MCM6206C-12,15            | 32K × 8, 12/15 ns, See QuickRAM II       | 7-142                     |

| MCM6206C                  | 32K × 8, 25/30/35/45/55 ns, -40 to 85°C  | 7-32                      |

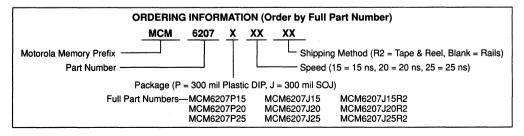

| MCM6207-15,20,25          | 256K × 1, 15/20/25 ns, See QuickRAM      | 7-122                     |

| MCM6207C-10,12            | 256K × 1, 10/12 ns, See QuickRAM II      |                           |

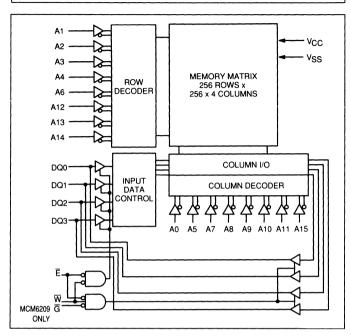

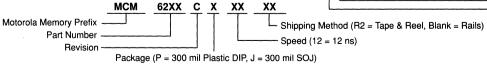

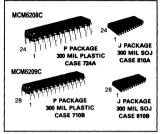

| MCM6208                   | 64K × 4, 35/45 ns                        | 7-40                      |

| MCM6208-15,20,25          | 64K × 4, 15/20/25 ns, See QuickRAM       | 7-122                     |

| MCM6208C-10,12            | 64K × 4, 10/12 ns, See QuickRAM II       | 7-142                     |

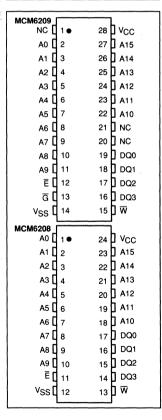

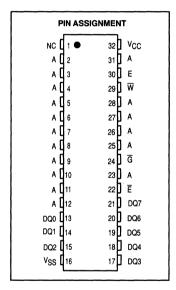

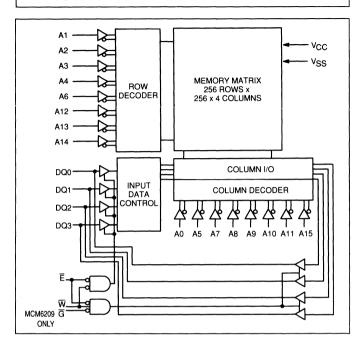

| MCM62080-10,12<br>MCM6209 | 64K × 4, 35/45 ns, Output Enable         | 7-142                     |

| MCM6209-15,20,25          | 64K × 4, 15/20/25 ns, See QuickRAM       | 7-122                     |

| MCM6209C-10.12            | 64K × 4, 10/12 ns, See QuickRAM II       | 7-142                     |

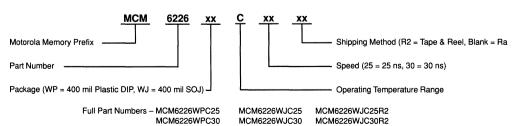

| MCM6226                   | 128K × 8, 25/30 ns                       | 7-142                     |

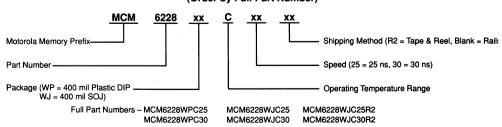

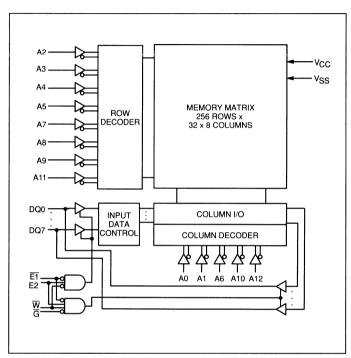

| MCM6228                   | 256K × 4, 25/30 ns                       | 7- <del>4</del> 7<br>7-53 |

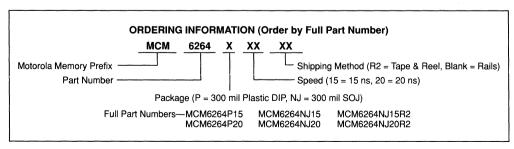

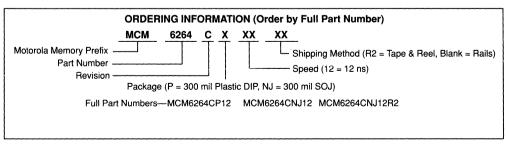

| MCM6264-15,20             | 8K × 8, 15/20 ns, See QuickRAM           | 7-33<br>7-122             |

| MCM6264C-10,12            | 8K × 8, 10/12 ns, See QuickRAM II        | 7-142                     |

|                           |                                          |                           |

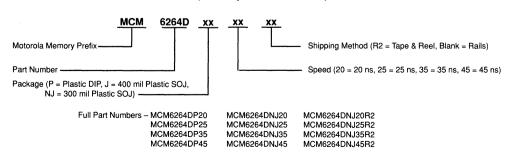

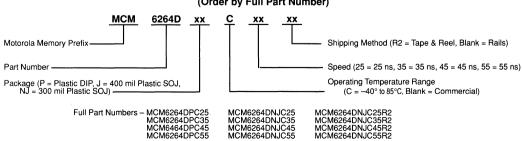

| MCM6264C<br>MCM6264D      | 8K × 8, 20/25 ns, -40 to 85°C            | 7-60                      |

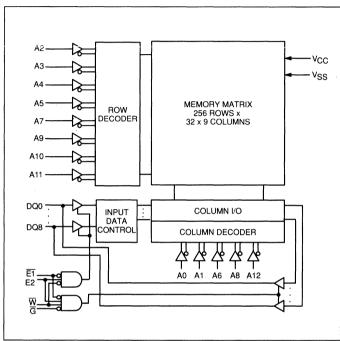

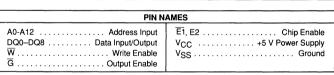

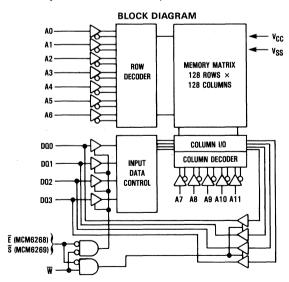

|                           | 8K × 8, 20/25/35/45 ns                   | 7-66                      |

| MCM6264D-C                | 8K × 8, 25/35/45/55 ns, -40 to 85°C      | 7-72                      |

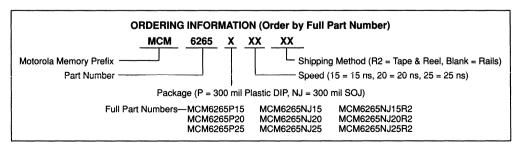

| MCM6265-15,20,25          | 8K × 9, 15/20/25 ns, See QuickRAM        | 7-122<br>7-142            |

| MCM6265C-10,12            | 8K × 9, 10/12 ns, See QuickRAM II        |                           |

| MCM6268                   | 4K × 4, 20/25/35/45/55 ns                | 7-78                      |

| MCM6269                   | 4K × 4, 20/25/35 ns, Fast Chip Select    | 7-78                      |

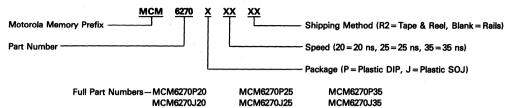

| MCM6270                   | 4K × 4, 20/25/35 ns, Output Enable       | 7-83                      |

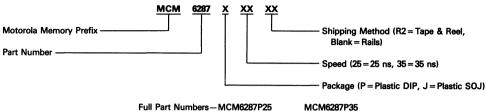

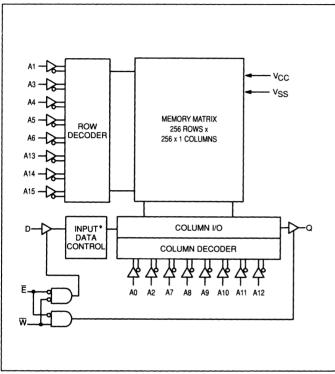

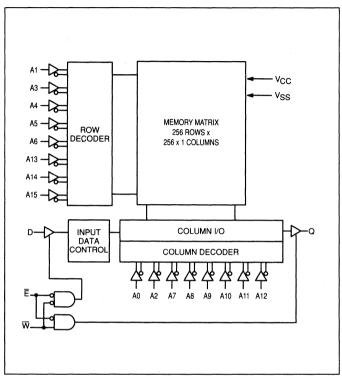

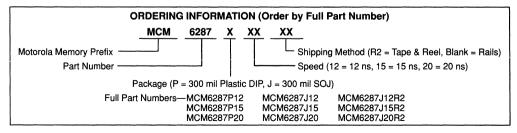

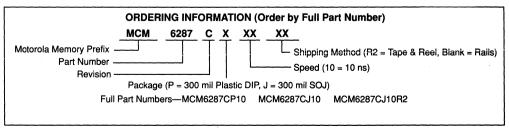

| MCM6287                   | 64K × 1, 25/35 ns                        | 7-89                      |

| MCM6287-12,15,20          | 64K × 1, 12/15/20 ns, See QuickRAM       | 7-122                     |

| MCM6287C-8,10             | 64K × 1, 8/10 ns, See QuickRAM II        | 7-142                     |

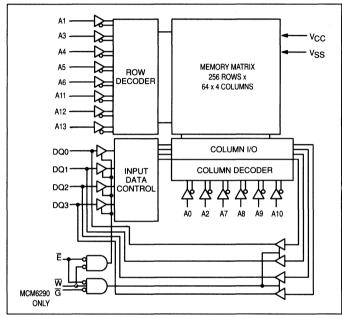

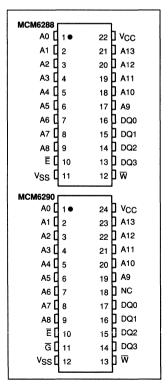

| MCM6288                   | 16K × 4, 20/25/30/35 ns                  | 7-98                      |

| MCM6288-12,15             | 16K × 4, 12/15 ns, See QuickRAM          | 7-122                     |

| MCM6288C-8,10             | 16K × 4, 8/10 ns, See QuickRAM II        | 7-142                     |

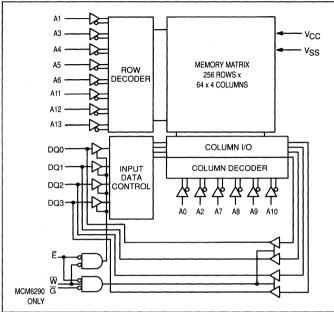

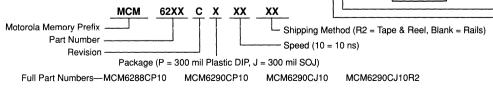

| MCM6290                   | 16K × 4, 20/25/30/35 ns, Output Enable   | 7-98                      |

| MCM6290-12,15             | 16K × 4, 12/15 ns, See QuickRAM          | 7-122                     |

| MCM6290C-8,10             | 16K × 4, 8/10 ns, See QuickRAM II        | 7-142                     |

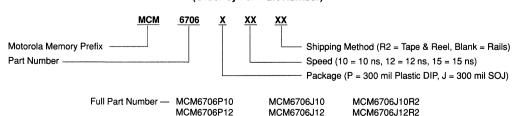

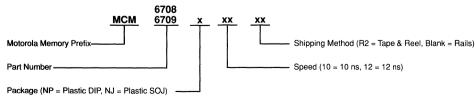

| MCM6706                   | 32K × 8, 10/12/15 ns                     | 7-105                     |

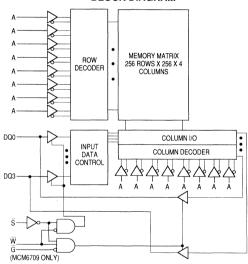

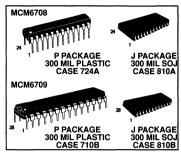

| MCM6708                   | 64K × 4, 10/12 ns                        | 7-110                     |

| MCM6709                   | $64K \times 4$ , 10/12 ns, Output Enable | 7-110                     |

## **CONTENTS (Continued)**

|                 |                                                                   | Page  |

|-----------------|-------------------------------------------------------------------|-------|

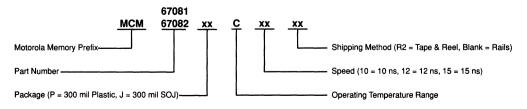

| MCM67081        | 64K × 4, 10/12/15 ns, Separate Input/Output                       | 7-116 |

| MCM67082        | 64K × 4, 10/12/15 ns, Separate Input/Output                       | 7-116 |

| QuickRAM        | Fast Static RAM Family                                            | 7-122 |

| QuickRAM II     | Fast Static RAM Family                                            | 7-142 |

| CHAPTER 8 — CMC | OS FAST STATIC RAM MODULES                                        |       |

| MCM2464         | $2 \times 64 \text{K} \times 24$ , 22/27 ns                       | 8-3   |

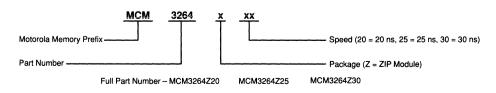

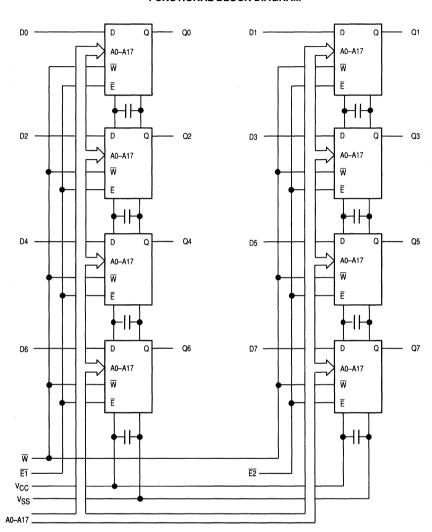

| MCM3264         | 64K × 32, 20/25/30 ns                                             | 8-10  |

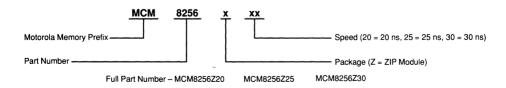

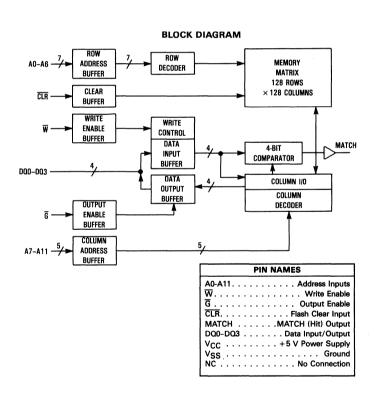

| MCM8256         | 256K × 8, 20/25/30 ns                                             | 8-17  |

| CHAPTER 9 — APP | LICATION SPECIFIC MOS STATIC RAMS                                 |       |

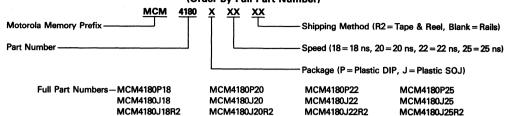

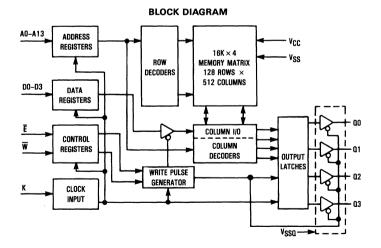

| MCM4180         | $4K \times 4$ , $18/20/22/25$ ns, Cache Tag                       | 9-3   |

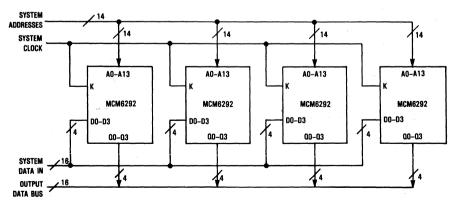

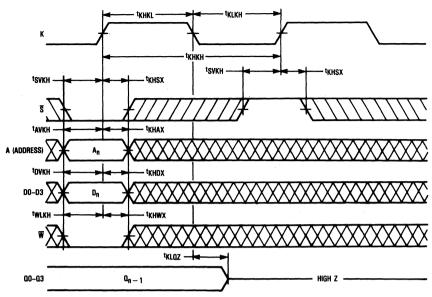

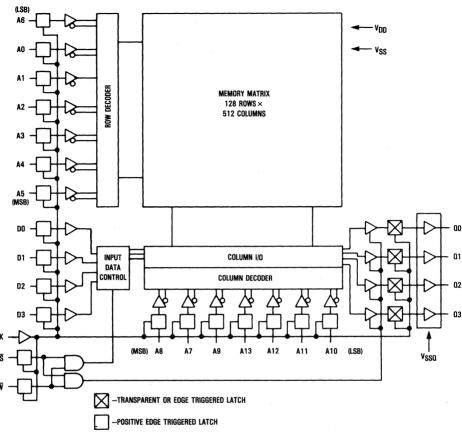

| MCM6292         | $16K \times 4$ , 25/30 ns, Synchronous, Transparent Outputs       | 9-13  |

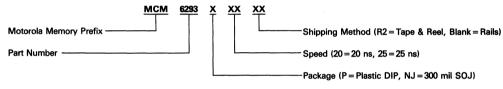

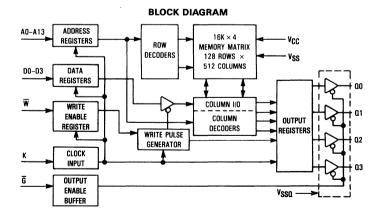

| MCM6293         | 16K × 4, 20/25 ns, Synchronous, Output Registers                  | 9-22  |

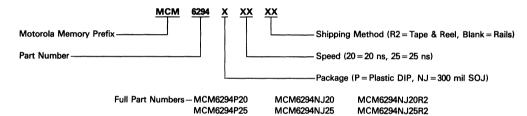

| MCM6294         | 16K × 4, 20/25 ns, Synchronous, Output Registers, Output Enable   | 9-31  |

| MCM6295         | 16K × 4, 25/30 ns, Synchronous, Transparent Outputs,              | 9-31  |

|                 | Output Enable                                                     | 9-40  |

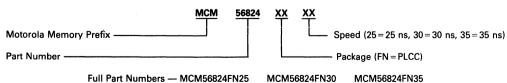

| MCM56824        | 8K × 24, 25/30/35 ns, DSPRAM                                      | 9-49  |

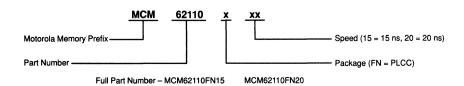

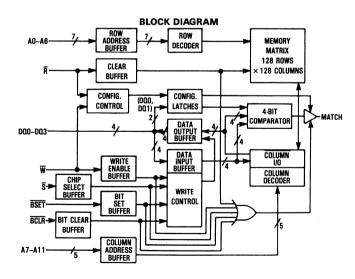

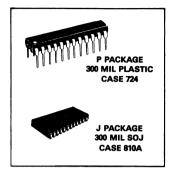

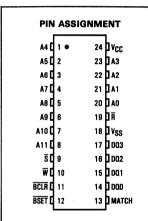

| MCM62110        | 32K × 9, 15/20 ns, Synchronous, Dual I/O, Parity Checker          | 9-57  |

| MCM62350        | 4K × 4, 20/22/25 ns, Cache Tag                                    | 9-67  |

| MCM62351        | 4K × 4, 20/22/25 ns, Cache Tag                                    | 9-77  |

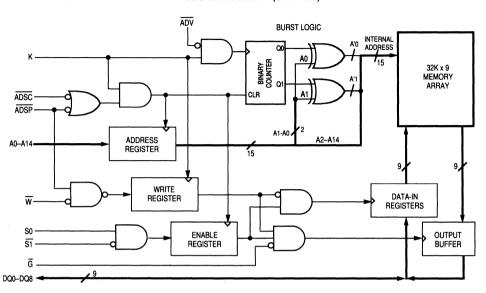

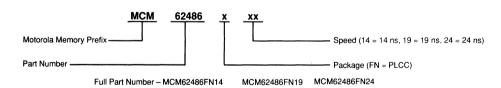

| MCM62486        | 32K × 9, 20/25/30 ns, Synchronous BurstRAM                        | 9-87  |

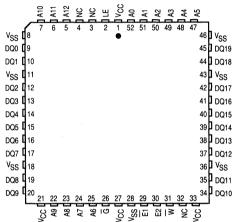

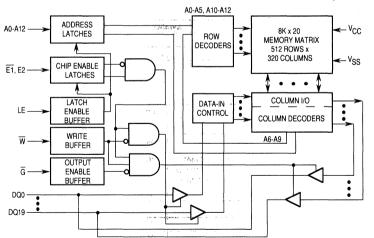

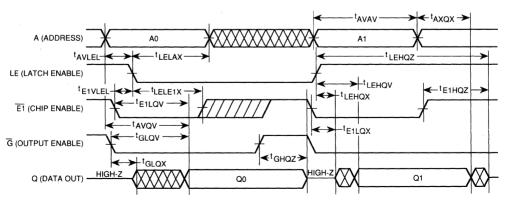

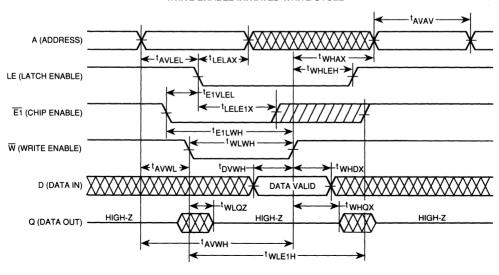

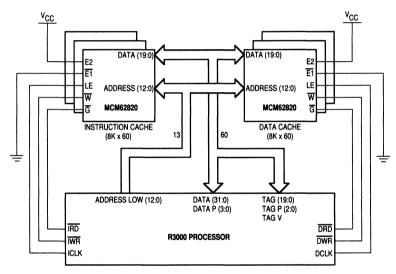

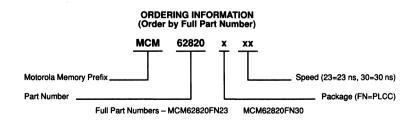

| MCM62820        | 8K × 20, 23/30 ns, Latched Address                                | 9-96  |

| MCM62940        | $32K \times 9$ , $14/19/24$ ns, Synchronous, BurstRAM,            |       |

|                 | for 040 Applications                                              | 9-102 |

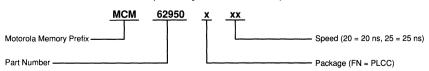

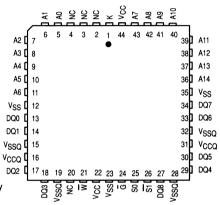

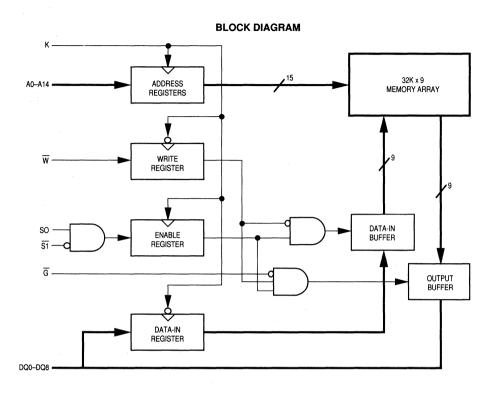

| MCM62950        | 32K × 9, 20/25 ns, Synchronous, for RISC-CISC Cache               | 9-110 |

| MCM62960        | 32K × 9, 17/20/24 ns, Synchronous, for SPARC Applications         | 9-115 |

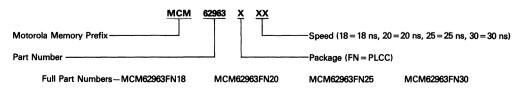

| MCM62963        | 4K × 10, 18/20/25/30 ns, Synchronous, Output Registers            | 9-120 |

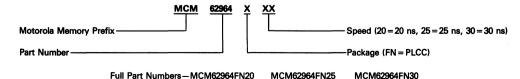

| MCM62964        | 4K × 10, 20/25/30 ns, Synchronous, Output Registers,              | 9-125 |

| MCMcoocE        | Output Enable                                                     | 9-125 |

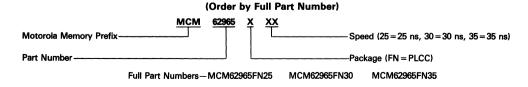

| MCM62965        | Output Enable                                                     | 9-129 |

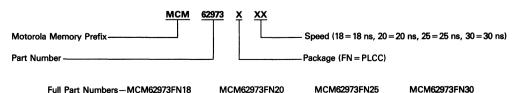

| MCM62973        | 4K × 12, 18/20/25/30 ns, Synchronous, Output Registers            | 9-129 |

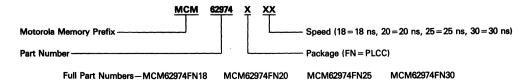

| MCM62974        | $4K \times 12$ , $18/20/25/30$ ns, Synchronous, Output Registers, | 9-100 |

| IVICIVIO2974    | Output Enable                                                     | 9-138 |

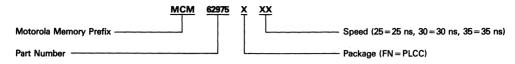

| MCM62975        | 4K × 12, 25/30/35 ns, Synchronous, Transparent Outputs,           | 3-100 |

| WOWOZ373        | Output Enable                                                     | 9-142 |

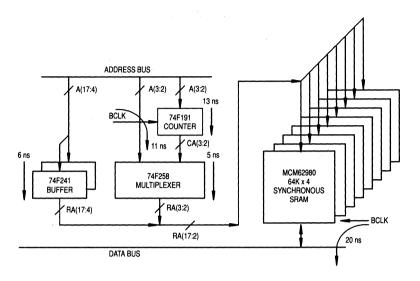

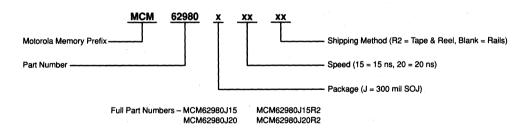

| MCM62980        | 64K × 4, 15/20 ns, Synchronous                                    | 9-147 |

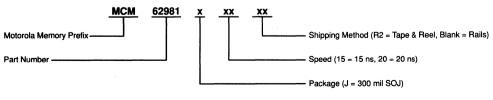

| MCM62981        | $64K \times 4$ , 15/20 ns, Synchronous, ParityRAM                 | 9-153 |

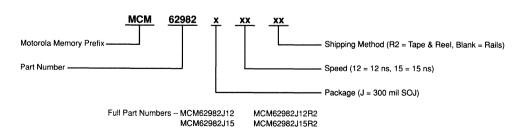

| MCM62982        | 64K × 4, 12/15 ns, Synchronous, Output Registers                  | 9-158 |

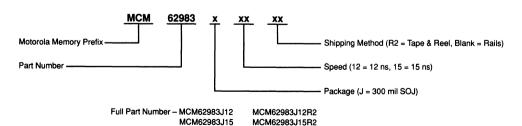

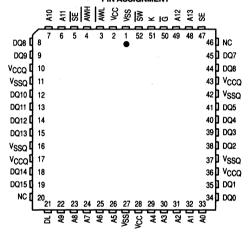

| MCM62983        | 64K × 4, 12/15 ns, Synchronous, ParityRAM, Output Registers       | 9-163 |

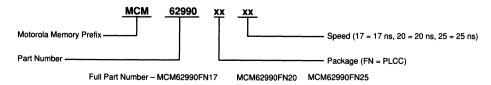

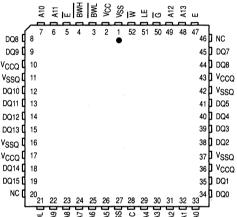

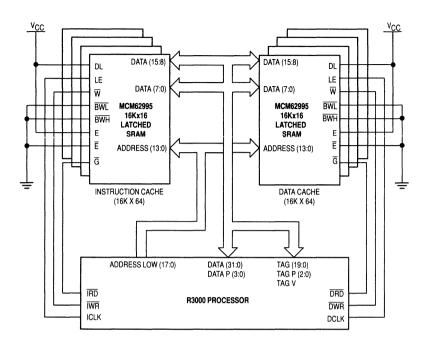

| MCM62990        | 16K × 16, 17/20/25 ns, Synchronous                                | 9-168 |

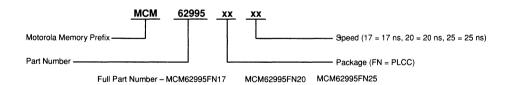

| MCM62995        | $16K \times 16$ , $17/20/25$ ns, Asynchronous, Latched Address    | 9-174 |

| CHAPTER 10 — MO | OS EEPROM                                                         |       |

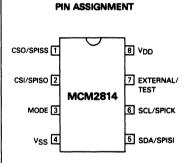

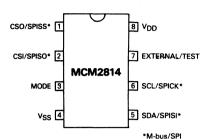

| MCM2814         | 256 × 8                                                           | 10-3  |

| CHAPTER 11 MIL  | ITARY PRODUCTS                                                    | 11-1  |

|                 | LIABILITY INFORMATION                                             | 12-1  |

|                 |                                                                   |       |

## **CONTENTS (Continued)**

| <b>(</b>                                                                    | Page           |

|-----------------------------------------------------------------------------|----------------|

| CHAPTER 13 — APPLICATIONS INFORMATION                                       | 13-1           |

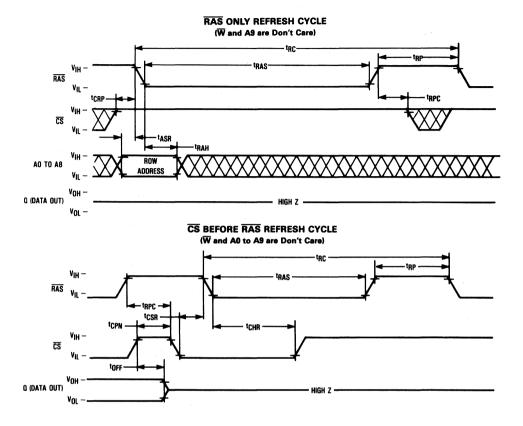

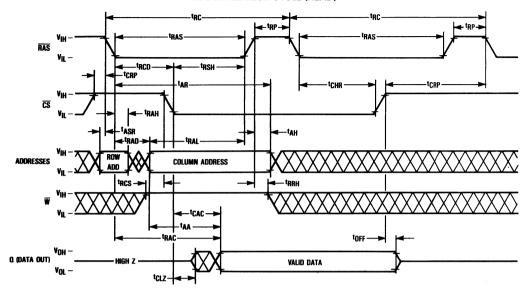

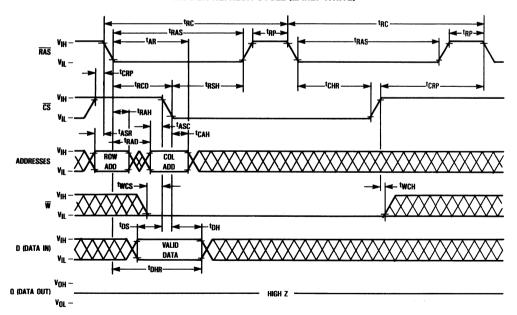

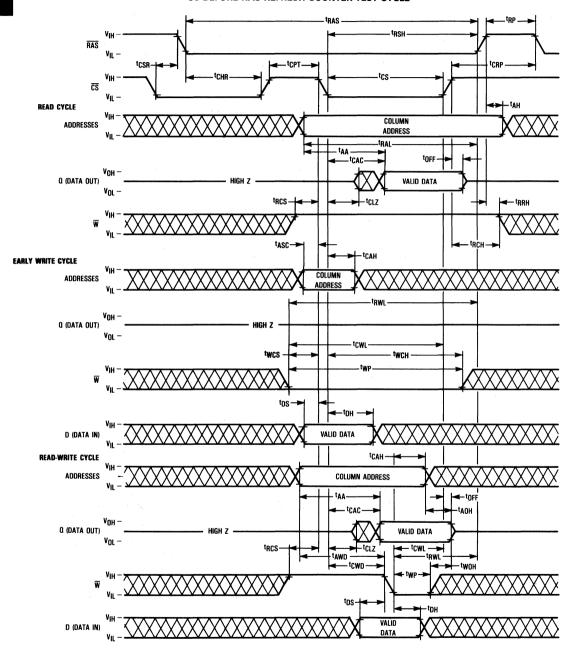

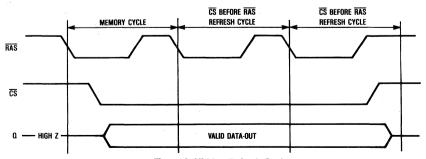

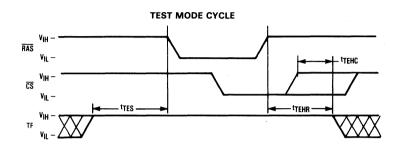

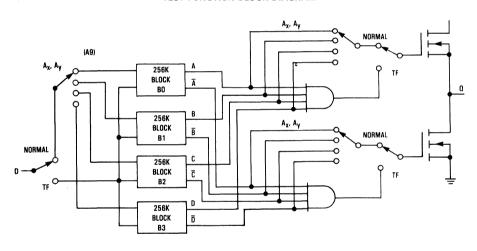

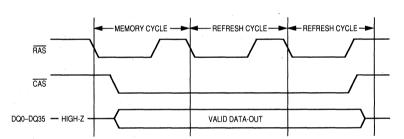

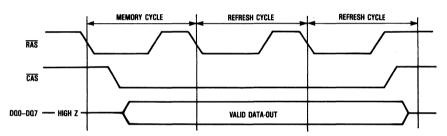

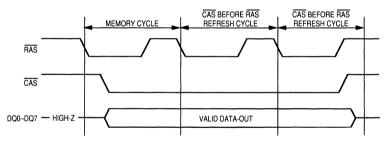

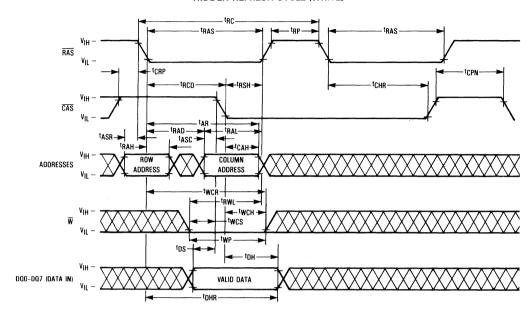

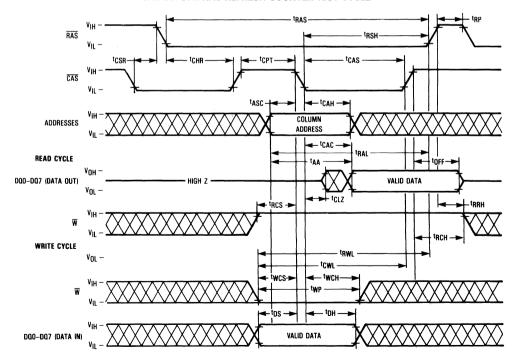

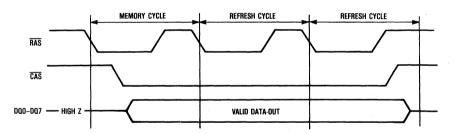

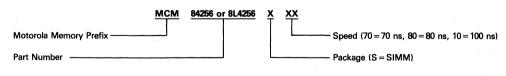

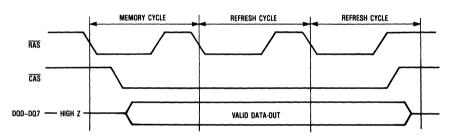

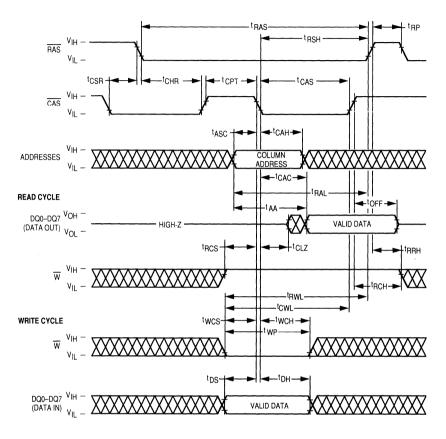

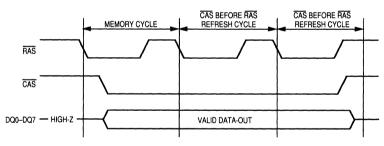

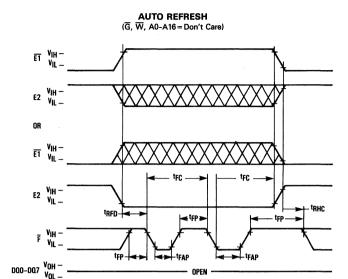

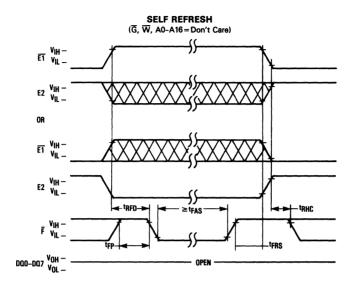

| DRAMs DRAM Refresh Modes (AN987)                                            | 13-2           |

| Page, Nibble, and Static Column Modes: High-Speed, Serial-Access Options    |                |

| on 1M-Bit + DRAMs (AN986)                                                   | 13-4           |

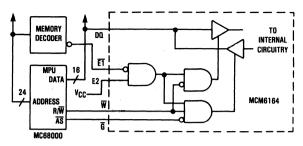

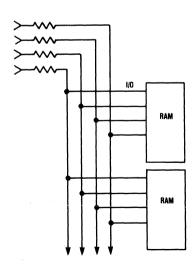

| Pseudo Static RAM Simplfies Interfacing with Microprocessors (AN1059)       | 13-8           |

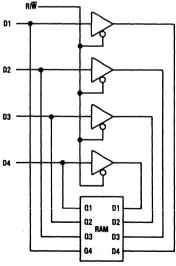

| Fast Static RAMs Avoiding Bus Contention in Fast Access RAM Designs (AN971) | 13-14          |

| Avoiding Data Errors with Fast Static RAMs (AN973)                          | 13-18          |

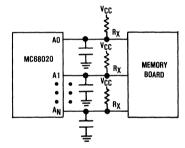

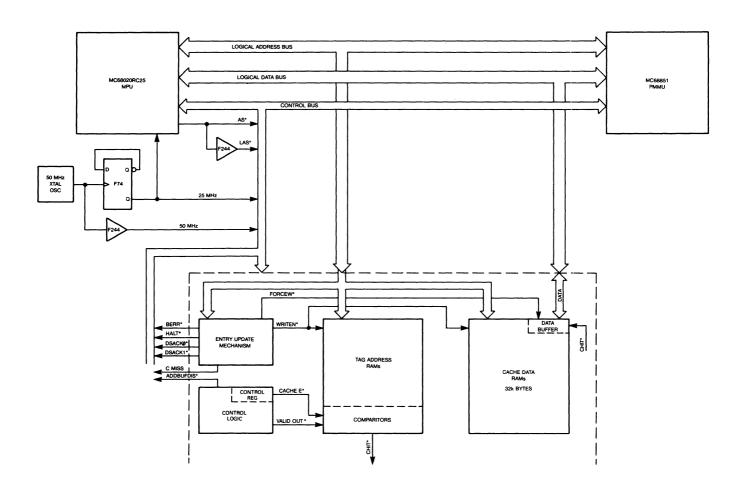

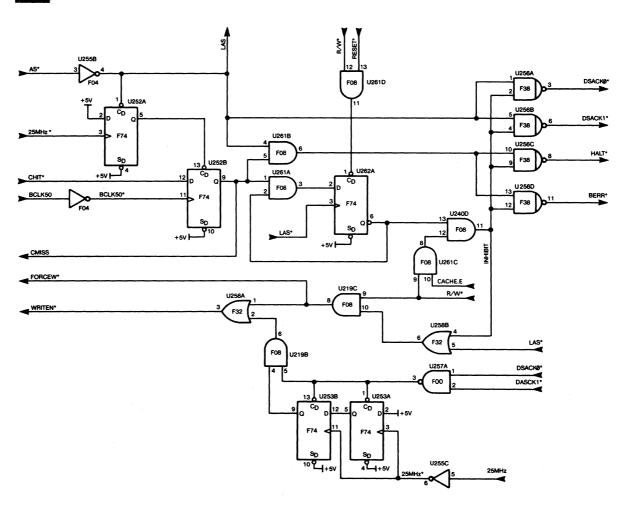

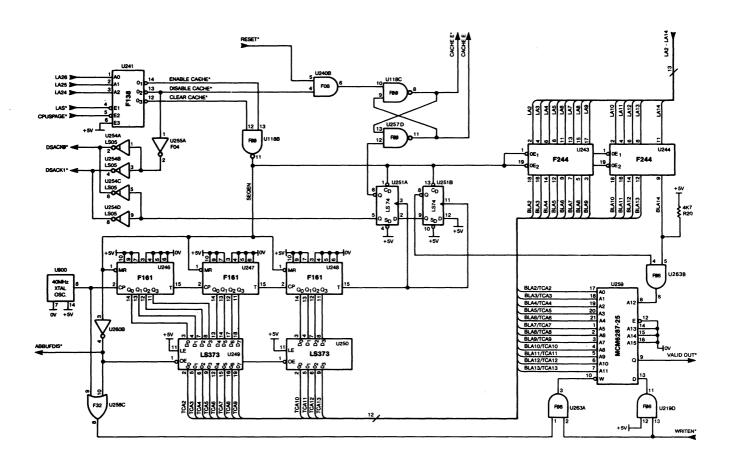

| Special Application Static RAMs 25 MHz Logical Cache for an MC68020 (AN984) | 13-21          |

| Designing a Cache for a Fast Processor (AR270)                              | 13-21          |

| Enhancing System Performance Using Synchronous SRAMs (AR260)                | 13-41          |

| High Freqeuency System Operation Using Synchronous SRAMs (AR258)            | 13-45<br>13-52 |

| Motorola o Hadioar Orlvini Booigh operas Oystems 40% (At 1250)              | 10-02          |

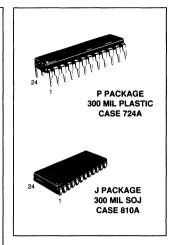

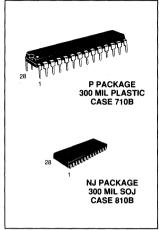

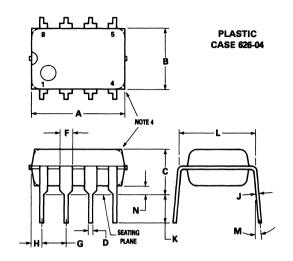

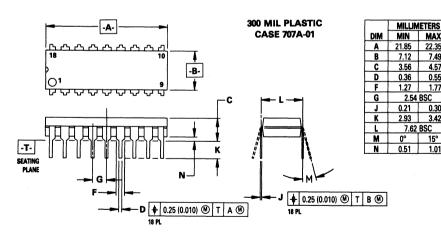

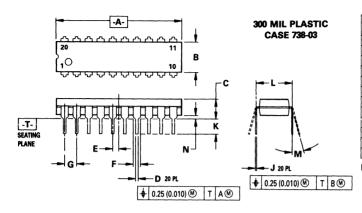

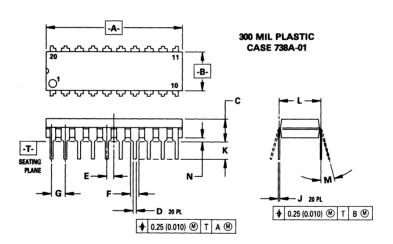

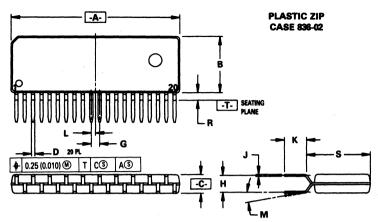

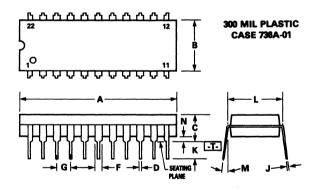

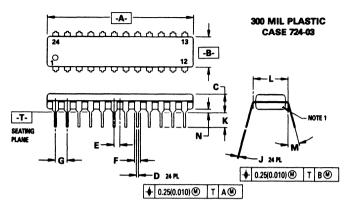

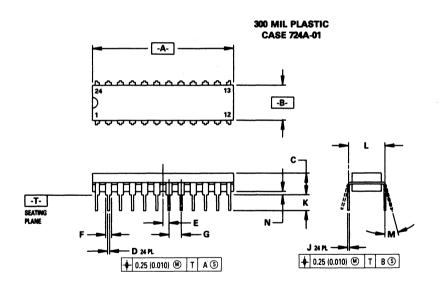

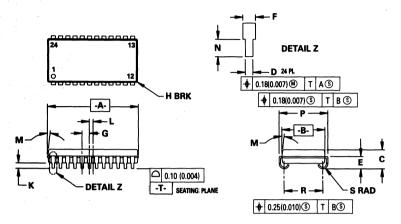

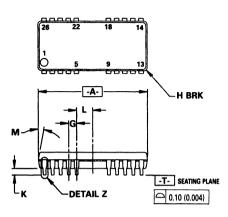

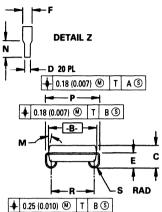

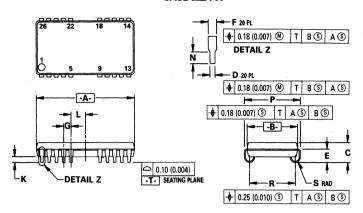

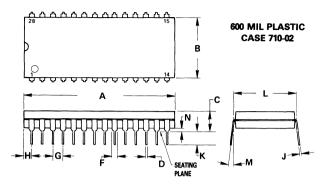

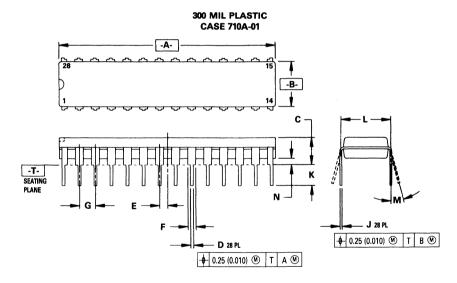

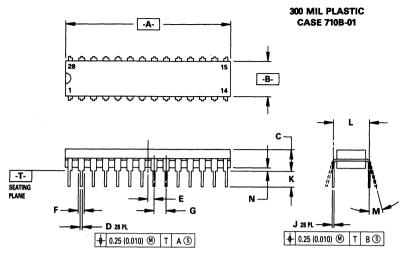

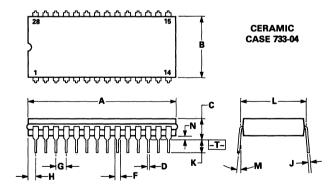

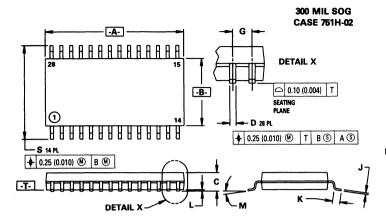

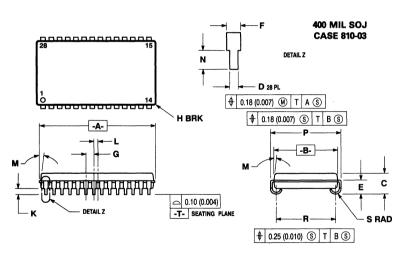

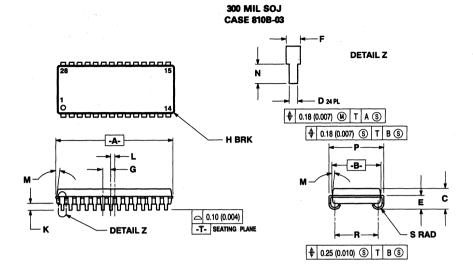

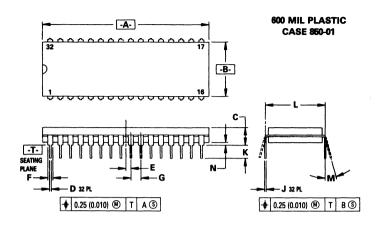

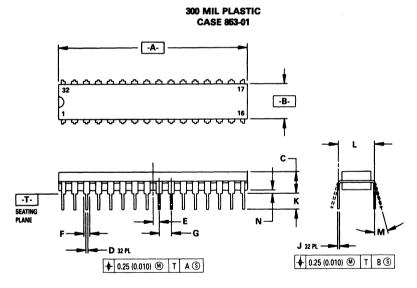

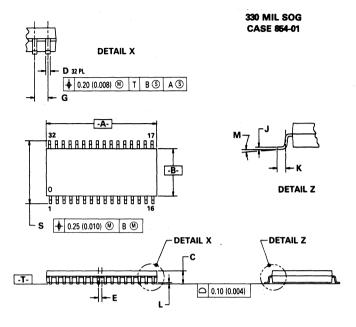

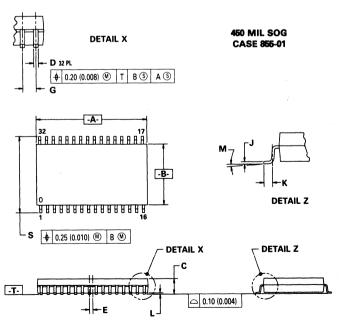

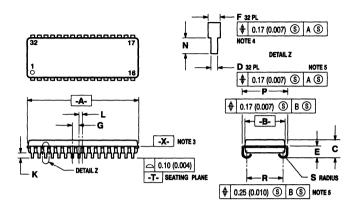

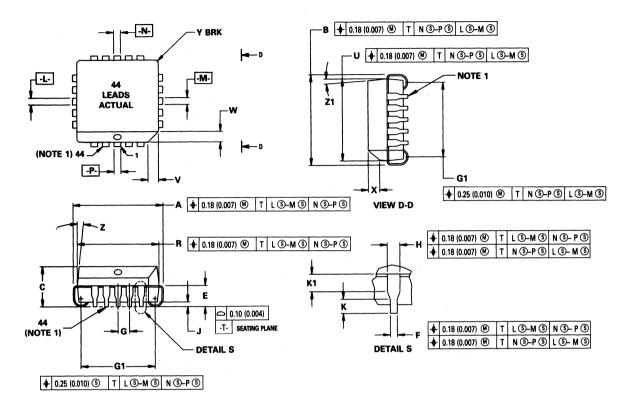

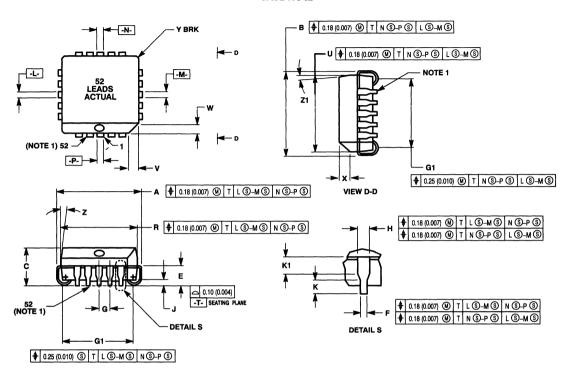

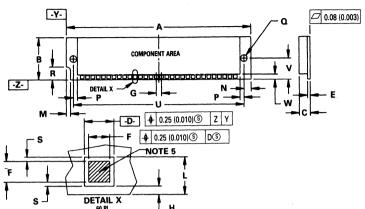

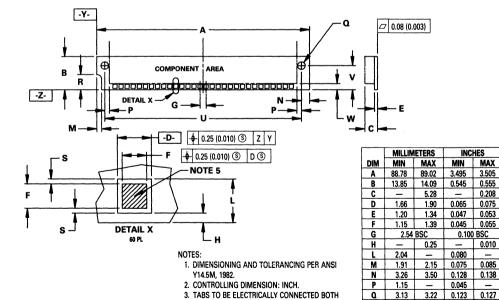

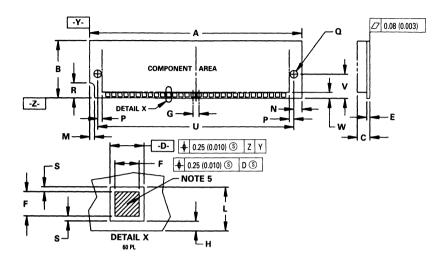

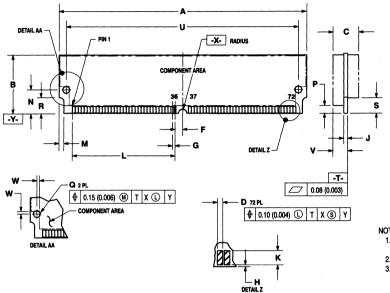

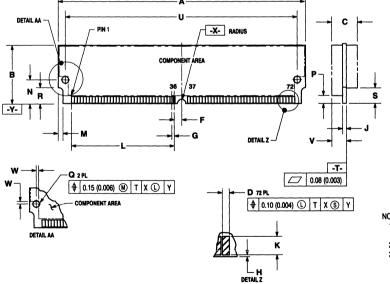

| CHAPTER 14 — MECHANICAL DATA                                                |                |

| Package Dimensions                                                          | 14-2           |

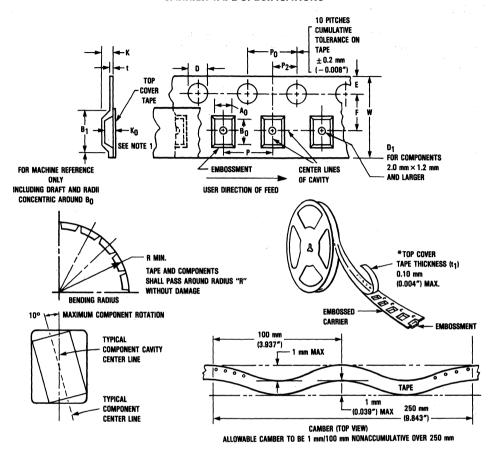

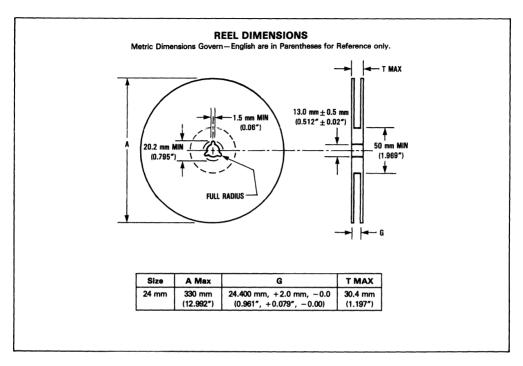

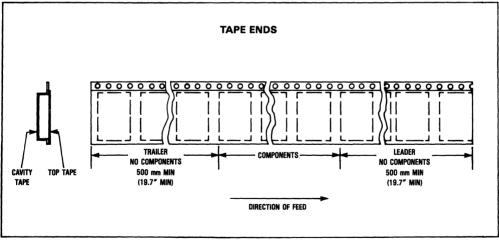

| Tape and Reel Data for Surface Mount Devices                                | 14-21          |

### **ALPHANUMERIC INDEX**

| Device Number    | Function                                                                 | Page<br>Number |

|------------------|--------------------------------------------------------------------------|----------------|

| MCM2018A         | 2K × 8, 35/45 ns                                                         | 6-3            |

| MCM2464          | 2 × 64K × 24, 22/27 ns                                                   | 8-3            |

| MCM2814          | 256 × 8                                                                  | 10-3           |

| MCM3264          | 64K × 32, 20/25/30 ns                                                    | 8-10           |

| MCM36100         | 1M × 36, 80/100 ns                                                       | 3-3            |

| MCM36200         | 2M × 36, 80/100 ns                                                       | 3-15           |

| MCM36256         | 256K × 36, 70/80/100 ns                                                  | 3-27           |

| MCM365121        | 512K × 36, 70/80/100 ns                                                  | 3-39           |

| MCM36L100        | 1M × 36, 80/100 ns, Low Power                                            | 3-3            |

| MCM36L200        | 2M × 36, 80/100 ns, Low Power                                            | 3-15           |

| MCM4180          | 4K × 4, 18/20/22/25 ns, Cache Tag                                        | 9-3            |

| MCM511000A       | 1M × 1, 70/80/100 ns, Page Mode                                          | 2-3            |

| MCM511001A       | 1M × 1, 70/80/100 ns, Nibble Mode                                        | 2-18           |

| MCM511002A       | 1M × 1, 70/80/100 ns, Static Column                                      | 2-33           |

| MCM514100        | 4M × 1, 80/100 ns, Page Mode                                             | 2-48           |

| MCM514256A       | 256K × 4, 70/80/100 ns, Page Mode                                        | 2-64           |

| MCM514258A       | 256K × 4, 70/80/100 ns, Static Column                                    | 2-79           |

| MCM514400        | 1M × 4, 80/100 ns, Page Mode                                             | 2-94           |

| MCM518128        | 128K × 8, 100 ns, E1 and E2 Inputs                                       | 5-3            |

| MCM518129        | 128K × 8, 100 ns E and S Inputs                                          | 5-16           |

| MCM51L000A       | 1M × 1, 70/80/100 ns, Page Mode, Low Power                               | 2-3            |

| MCM51L4100       | 4M × 1, 80/100ns, Page Mode, Low Power                                   | 2-48           |

| MCM51L4256A      | 256K × 4, 70/80/100 ns, Page Mode Low Power                              | 2-64           |

| MCM51L4400       | 1M × 4, 80/100 ns, Page Mode Low Power                                   | 2-94           |

| MCM51L8128       | 128K × 8, 80/100 ns, E1 and E2 Inputs, Low Power                         | 5-3            |

| MCM51L8129       | 128K × 8, 80/100 ns, <b>E</b> and S Inputs, Low Power                    | 5-16           |

| MCM51LV8128      | $128K \times 8$ , 80/100 ns, $\overline{E1}$ and $E2$ Inputs, Low Power, | r 0            |

| MCME1LV0100      | Data Retention                                                           | 5-3            |

| MCM51LV8129      | · · · · · · · · · · · · · · · · · · ·                                    | 5-16           |

| MCM524258A       | Data Retention                                                           | 4-3            |

| MCM528128A       | 256K × 4, 100/120 ns, Page Mode                                          | 4-3<br>4-5     |

| MCM56824         | 8K × 24, 25/30/35 ns, DSPRAM                                             | 9-49           |

| MCM60256A        | 32K × 8, 85/100/120 ns                                                   | 6-8            |

| MCM60256A-C      | 32K × 8, 100 ns, –40 to 85°C                                             | 6-24           |

| MCM60L256A       | 32K × 8, 85/100/120 ns, Low Power                                        | 6-8            |

| MCM60L256A-70    | 32K × 8, 70 ns, Low Power                                                | 6-16           |

| MCM60L256A-C     | 32K × 8, 100 ns, –40 to 85°C                                             | 6-24           |

| MCM60L256A-V     | 32K × 8, 100 ns, –40 to 105°C                                            | 6-32           |

| MCM6164          | 8K × 8, 45/55 ns                                                         | 7-3            |

| MCM6164C         | 8K × 8, 55/70 ns, -40 to 85°C                                            | 7-11           |

| MCM61L64         | 8K × 8, 45/55, Low Power                                                 | 7-3            |

| MCM6205          | 32K × 9, 30/34/45 ns                                                     | 7-19           |

| MCM6205-17,20,25 | 32K × 9, 17/20/25 ns, See QuickRAM                                       | 7-122          |

| MCM6205C-12.15   | 32K × 9, 12/15 ns, See QuickRAM II                                       | 7-142          |

| MCM6206          | 32K × 8, 30/34/45 ns                                                     | 7-26           |

| MCM6206-17,20,25 | 32K × 8, 17/20/25 ns, See QuickRAM                                       | 7-122          |

| MCM6206C         | 32K × 8, 25/30/35/45/55 ns, -40 to 85°C                                  | 7-32           |

| MCM6206C-12,15   | 32K × 8, 12/15 ns, See QuickRAM II                                       | 7-142          |

| MCM6207-15,20,25 | 256K × 1, 15/20/25 ns, See QuickRAM II                                   | 7-122          |

| MCM6207C-10,12   | 256K × 1, 10/12 ns, See QuickRAM II                                      | 7-142          |

## **ALPHANUMERIC INDEX (Continued)**

| Device Number    | Function                                                 | Number |

|------------------|----------------------------------------------------------|--------|

| MCM6208          | 64K × 4, 35/45 ns                                        | 7-40   |

| MCM6208-15,20,25 | 64K × 4, 15/20/25 ns, See QuickRAM                       | 7-122  |

| MCM6208C-10,12   | 64K × 4, 10/12 ns, See QuickRAM II                       | 7-142  |

| MCM6209          | 64K × 4, 35/45 ns, Output Enable                         | 7-40   |

| MCM6209-15,20,25 | 64K × 4, 15/20/25 ns, See QuickRAM                       | 7-122  |

| MCM6209C-10,12   | 64K × 4, 10/12 ns, See QuickRAM II                       | 7-142  |

| MCM62110         | 32K × 9, 15/20 ns, Synchronous, Dual I/O, Parity Checker | 9-57   |

| MCM6226          | 128K × 8, 25/30 ns                                       | 7-47   |

| MCM6228          | 256K × 4, 25/30 ns                                       | 7-53   |

| MCM62350         | 4K × 4, 20/22/25 ns, Cache Tag                           | 9-67   |

| MCM62351         | 4K × 4, 20/22/25 ns, Cache Tag                           | 9-77   |

| MCM62486         | 32K × 9, 20/25/30 ns, Synchronous BurstRAM               | 9-87   |

| MCM6264-15,20    | 8K × 8, 15/20 ns, See QuickRAM                           | 7-122  |

| MCM6264C         | 8K × 8, 20/25 ns, -40 to 85°C                            | 7-60   |

| MCM6264C-10,12   | 8K × 8, 10/12 ns, See QuickRAM II                        | 7-142  |

| MCM6264D         | 8K × 8, 20/25/35/45 ns                                   | 7-66   |

| MCM6264D-C       | 8K × 8, 25/35/45/55 ns, –40 to 85°C                      | 7-72   |

| MCM6265-15,20,25 | 8K × 9, 15/20/25 ns, See QuickRAM                        | 7-122  |

| MCM6265C-10,12   | 8K × 9, 10/12 ns, See QuickRAM II                        | 7-142  |

| MCM6268          | 4K × 4, 20/25/35/45/55 ns                                | 7-78   |

| MCM6269          | 4K × 4, 20/25/35 ns, Fast Chip Select                    | 7-78   |

| MCM6270          | 4K × 4, 20/25/35 ns, Output Enable                       | 7-83   |

| MCM62820         | 8K × 20, 23/30 ns, Latched Address                       | 9-96   |

| MCM6287          | 64K × 1, 25/35 ns                                        | 7-89   |

| MCM6287-12,15,20 | 64K × 1, 12/15/20 ns, See QuickRAM                       | 7-122  |

| MCM6287C-8.10    | 64K × 1, 8/10 ns, See QuickRAM II                        | 7-142  |

| MCM6288          | 16K × 4, 20/25/30/35 ns                                  | 7-98   |

| MCM6288-12,15    | 16K × 4, 12/15 ns, See QuickRAM                          | 7-122  |

| MCM6288C-8,10    | 16K × 4, 8/10 ns, See QuickRAM II                        | 7-142  |

| MCM6290          | 16K × 4, 10/25/30/35 ns, Output Enable                   | 7-98   |

| MCM6290-12,15    | 16K × 4, 12/15 ns, See QuickRAM                          | 7-122  |

| MCM6290C-8,10    | 16K × 4, 8/10 ns, See QuickRAM II                        | 7-142  |

| MCM6292          | 16K × 4, 25/30 ns, Synchronous, Transparent Outputs      | 9-13   |

| MCM6293          | 16K × 4, 20/25 ns, Synchronous, Output Registers         | 9-22   |

| MCM6294          | 16K × 4, 20/25 ns, Synchronous, Output Registers,        |        |

|                  | Output Enable                                            | 9-31   |

| MCM62940         | 32K × 9, 14/19/24 ns, Synchronous, BurstRAM,             |        |

|                  | for 040 Applications                                     | 9-102  |

| MCM6295          | 16K × 4, 25/30 ns, Synchronous, Transparent Outputs,     |        |

|                  | Output Enable                                            | 9-40   |

| MCM62950         | 32K × 9, 20/25 ns, Synchronous, for RISC-CISC Cache      | 9-110  |

| MCM62960         | 32K × 9, 17/20/24 ns, Synchronous, Output Registers      | 9-115  |

| MCM62963         | 4K × 10, 18/20/25/30 ns, Synchronous, Output Registers   | 9-120  |

| MCM62964         | 4K × 10, 20/25/30 ns, Synchronous, Output Registers,     |        |

|                  | Output Enable                                            | 9-125  |

| MCM62965         | 4K × 10, 25/30/35 ns, Synchronous, Transparent Outputs,  |        |

|                  | Output Enable                                            | 9-129  |

| MCM62973         | 4K × 12, 18/20/25/30 ns, Synchronous, Output Registers   | 9-133  |

| MCM62974         | 4K × 12, 18/20/25/30 ns, Synchronous, Output Registers,  |        |

|                  | Output Enable                                            | 9-138  |

| MCM62975         | 4K × 12, 25/30/35 ns, Synchronous, Transparent Outputs,  |        |

| -                | Output Enable                                            | 9-142  |

|                  |                                                          |        |

## **ALPHANUMERIC INDEX (Continued)**

| Device Number | Function                                                    | Page<br>Number |

|---------------|-------------------------------------------------------------|----------------|

| MCM62980      | 64K × 4, 15/20 ns, Synchronous                              | 9-147          |

| MCM62981      | 64K × 4, 15/20 ns, Synchronous, ParityRAM                   | 9-153          |

| MCM62982      | 64K × 4, 12/15 ns, Synchronous, Output Registers            | 9-158          |

| MCM62983      | 64K × 4, 12/15 ns, Synchronous, ParityRAM, Output Registers | 9-163          |

| MCM62990      | 16K × 16, 17/20/25 ns, Synchronous                          | 9-168          |

| MCM62995      | 16K × 16, 17/20/25 ns, Asynchronous, Latched Address        | 9-174          |

| MCM6706       | 32K × 8, 10/12/15 ns                                        | 7-105          |

| MCM6708       | 64K × 4, 10/12 ns                                           | 7-110          |

| MCM67081      | 64K × 4, 10/12/15 ns, Separate Input/Output                 | 7-116          |

| MCM67082      | 64K × 4, 10/12/15 ns, Separate Input/Output                 | 7-116          |

| MCM6709       | 64K × 4, 10/12 ns, Output Enable                            | 7-110          |

| MCM81000      | 1M × 8, 70/80/100 ns                                        | 3-51           |

| MCM8256       | 256K × 8, 20/25/30 ns                                       | 8-17           |

| MCM84000      | 4M × 8, 80/100 ns                                           | 3-62           |

| MCM84256      | 256K × 8, 70/80/100 ns                                      | 3-74           |

| MCM8L1000     | 1M × 8, 70/80/100 ns, Low Power                             | 3-51           |

| MCM8L4000     | 4M × 8, 80/100 ns, Low Power                                | 3-62           |

| MCM8L4256     | 256K × 8, 70/80/100 ns, Low Power                           | 3-74           |

| MCM91000      | 1M × 9, 70/80/100 ns                                        | 3-85           |

| MCM94000      | 4M × 9, 80/100 ns                                           | 3-96           |

| MCM94256      | 256K × 9, 70/80/100 ns                                      | 3-108          |

| MCM9L1000     | 4M × 9, 70/80/100 ns, Low Power                             | 3-85           |

| MCM9L4000     | 1M × 9, 80/100 ns                                           | 3-96           |

| QuickRAM      | Fast Static RAM Family                                      | 7-122          |

| QuickRAM II   | Fast Static RAM Family                                      | 7-142          |

## **Selector Guide and Cross Reference**

### DYNAMIC RAMs (HCMOS)

|         |         | Motorola    | Address     | Operating |               |                      |                                              |

|---------|---------|-------------|-------------|-----------|---------------|----------------------|----------------------------------------------|

| 1 1     | Organi- | Part        | Access Time | Current   | Pin           | Package              |                                              |

| Density | zation  | Number      | (ns Max)    | (mA Max)  | Count         | Options              | Comments                                     |

| 1M      | 1 Mx1   | MCM511000A  | 70/80/100   | 80/70/60  | 18, 20, 20/26 | (P)DIP, (Z)IP, SO(J) | Fast page mode cycle time=40/45/55 ns        |

|         |         | MCM51L1000A | 70/80/100   | 80/70/60  | 18, 20, 20/26 | (P)DIP, (Z)IP, SO(J) | Fast page mode with low power battery backup |

|         |         | MCM511001A  | 70/80/100   | 80/70/60  | 18, 20, 20/26 | (P)DIP, (Z)IP, SO(J) | Nibble mode access time=35/35/40 ns          |

|         |         | MCM511002A  | 70/80/100   | 80/70/60  | 18, 20, 20/26 | (P)DIP, (Z)IP, SO(J) | Static column mode cycle time=40/45/55 ns    |

| 1 1     | 256Kx4  | MCM514256A  | 70/80/100   | 80/70/60  | 20, 20, 20/26 | (P)DIP, (Z)IP, SO(J) | Fast page mode cycle time=40/45/55 ns        |

| 1       |         | MCM51L4256A | 70/80/100   | 80/70/60  | 20, 20, 20/26 | (P)DIP, (Z)IP, SO(J) | Fast page mode with low power battery backup |

|         |         | MCM514258A  | 70/80/100   | 80/70/60  | 20, 20, 20/26 | (P)DIP, (Z)IP, SO(J) | Static column mode cycle time=40/45/55 ns    |

| 4M      | 4Mx1    | MCM514100   | 80/100      | 100/85    | 20, 20/26     | (Z)IP, SO(J)         | Fast page mode cycle time=50/60 ns           |

| i i     |         | MCM51L4100  | 80/100      | 100/85    | 20, 20/26     | (Z)IP, SO(J)         | Fast page mode with low power battery backup |

| 1 1     | 1 Mx4   | MCM514400   | 80/100      | 105/90    | 20, 20/26     | (Z)IP, SO(J)         | Fast page mode cycle time=50/60 ns           |

| 1       |         | MCM51L4400  | 80/100      | 105/90    | 20, 20/26     | (Z)IP, SO(J)         | Fast page mode with low power battery backup |

|         |         | MCM514410   | 80/100      | 105/90    | 20, 20/26     | (Z)IP, SO(J)         | Fast page mode with write per bit            |

DRAM MODULES (Contact DRAM Marketing for Custom DRAM Modules)

| 1            |         | Motorola  | Address     | Operating      |       |                           |                                                     |

|--------------|---------|-----------|-------------|----------------|-------|---------------------------|-----------------------------------------------------|

| Į.           | Organi- | Part      | Access Time | Current        | Pin   | Package                   |                                                     |

| Density      | zation  | Number    | (ns Max)    | (mA Max)       | Count | Options                   | Comments                                            |

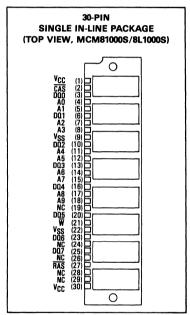

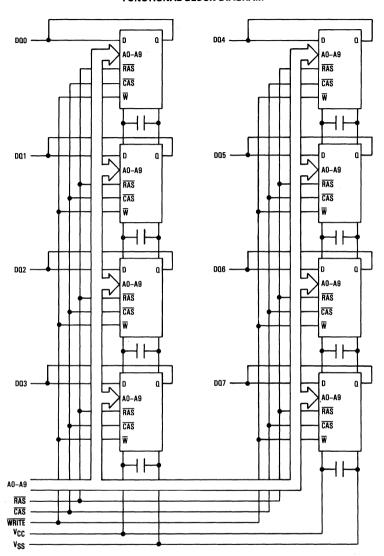

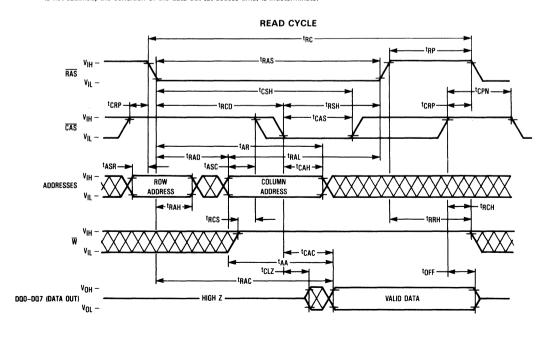

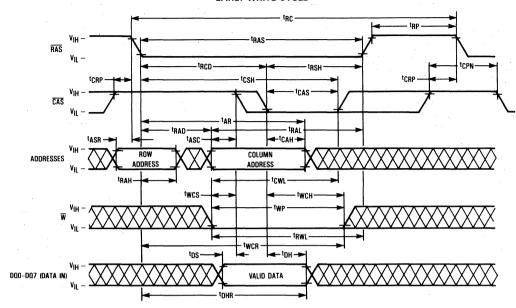

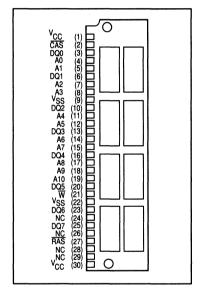

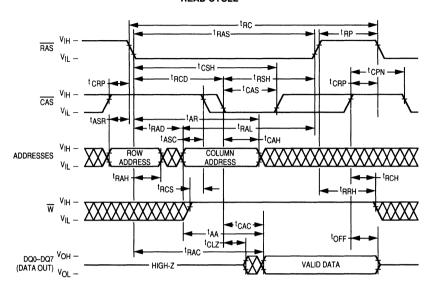

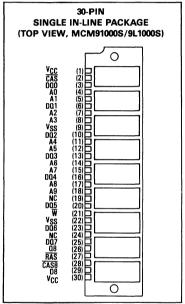

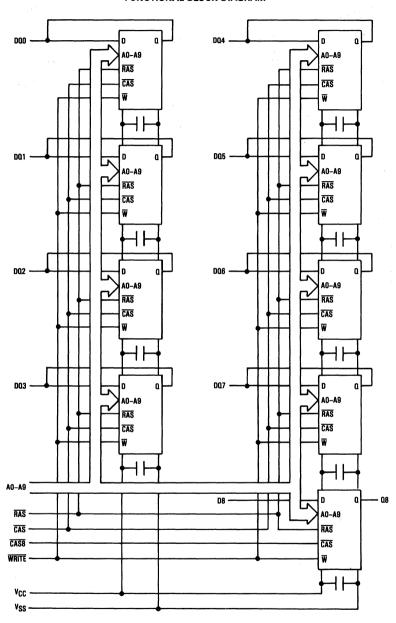

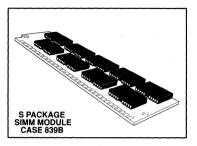

| 8M           | 1Mx8    | MCM81000  | 70/80/100   | 640/560/480    | 30    | (S)IMM, (L)SIP            | Fast page mode cycle time=40/45/55 ns               |

| 1            |         | MCM8L1001 | 70/80/100   | 640/560/480    | 30    | (S)IMM, (L)SIP            | Fast page mode with low power battery backup        |

| l            |         | MCM81001  | 70/80/100   | 640/560/480    | 30    | (S)IMM, (L)SIP            | Nibble mode access time=35/35/40 ns                 |

|              |         | MCM81002  | 70/80/100   | 640/560/480    | 30    | (S)IMM, (L)SIP            | Static column mode cycle time=40/45/55 ns           |

| 8M           | 1Mx9    | MCM91000  | 70/80/100   | 720/630/540    | 30    | (S)IMM, (L)SIP, SG (gold) | Fast page mode cycle time=40/45/55 ns               |

| w/Parity     |         | MCM9L1000 | 70/80/100   | 720/630/540    | 30    | (S)IMM, (L)SIP, SG (gold) | Fast page mode with low power battery backup        |

|              |         | MCM91001  | 70/80/100   | 720/630/540    | 30    | (S)IMM, (L)SIP            | Nibble mode access time=35/35/40 ns                 |

|              |         | MCM91002  | 70/80/100   | 720/630/540    | 30    | (S)IMM, (L)SIP            | Static column mode cycle time=40/45/55 ns           |

| 2M           | 256Kx8  | MCM84256  | 70/80/100   | 160/140/120    | 30    | (S)IMM                    | Fast page mode cycle time=40/45/55 ns               |

|              |         | MCM8L4256 | 70/80/100   | 160/140/120    | 30    | (S)IMM                    | Fast page mode with low power battery backup        |

| 2M           | 256Kx9  | MCM94256  | 70/80/100   | 240/210/190    | 30    | (S)IMM                    | Fast page mode cycle time=40/45/55 ns               |

| w/Parity     |         | MCM9L4256 | 70/80/100   | 240/210/190    | 30    | (S)IMM                    | Fast page mode with low power battery backup        |

| 4M           | 1Mx4    | MCM41000  | 80/100      | 280/240        | 26    | (Z)IMM                    | Fast page mode cycle time=40/45/55 ns               |

|              | 4Mx1_   | MCM11400  | 80/100      | 90/80          | 26    | (Z)IMM                    | Fast page mode cycle time=40/45/55 ns               |

| 32M          | 4Mx8    | MCM84000  | 80/100      | 800/680        | 30    | (S)IMM                    | Fast page mode cycle time=50/60 ns                  |

|              |         | MCM8L4000 | 80/100      | 800/680        | 30    | (S)IMM                    | Fast page mode cycle time=50/60 ns                  |

| 32M w/Parity | 4Mx9    | MCM94000  | 80/100      | 900/765        | 30    | (S)IMM                    | Fast page mode cycle time=50/60 ns                  |

|              |         | MCM9L4000 | 80/100      | 900/765        | 30    | (S)IMM                    | Fast page mode cycle time=50/60 ns                  |

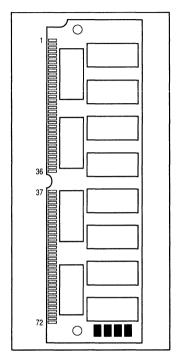

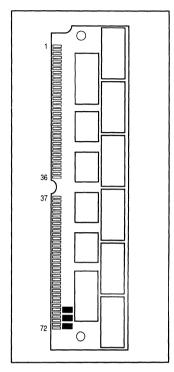

| 8M w/Parity  | 256Kx36 | MCM36256  | 70/80/100   | 960/840/760    | 72    | (S)IMM, SG (gold)         | Fast page mode cycle time=40/45/55 ns               |

| 16M w/Parity | 512Kx36 | MCM36512  | 70/80/100   | 1920/1680/1520 | 72    | (S)IMM, SG (gold)         | Fast page mode cycle time=40/45/55 ns               |

| 32M w/Parity | 1 Mx36  | MCM36100  | 80/100      | 1144/984       | 72    | (S)IMM, SG (gold)         | Fast page mode cycle time=40/45/55 ns               |

| 64M w/Parity | 2Mx36   | MCM36200  | 80/100      | 1120/960       | 72    | (S)IMM, SG (gold)         | Fast page mode cycle time=40/45/55 ns               |

| 8M w/Parity  | 256Kx40 | MCM40256* | 70/80/100   | 800/700/600    | 72    | (S)IMM, SG (gold)         | Same as MCM36xxx, for error correction applications |

| 16M w/Parity | 512Kx40 | MCM40512* | 70/80/100   | 820/720/620    | 72    | (S)IMM, SG (gold)         | Same as MCM36xxx, for error correction applications |

| 32M w/Parity | 1 Mx40  | MCM40100° | 80/100      | 1050/900       | 72    | (S)IMM, SG (gold)         | Same as MCM36xxx, for error correction applications |

| 64M w/Parity | 2Mx40   | MCM40200° | 80/100      | 1070/920       | 72    | (S)IMM, SG (gold)         | Same as MCM36xxx, for error correction applications |

\*To be introduced.

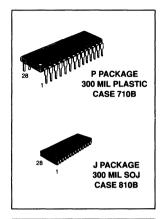

Package Information:

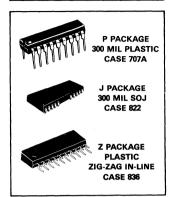

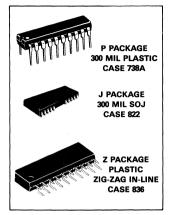

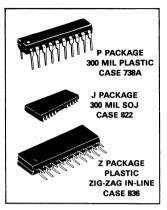

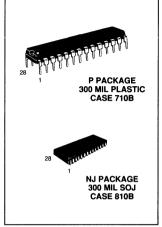

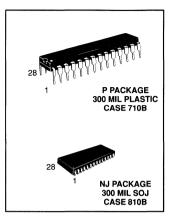

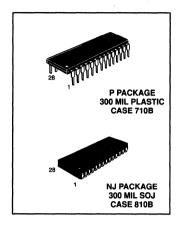

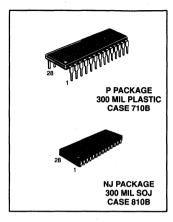

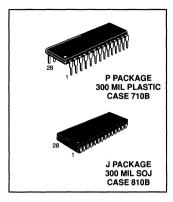

P=26 pin, 300 mil, plastic dual-in-line package J=26 pin, 300 mil, plastic small outline "J" lead package Z=20 pin, 300 mil, plastic zig-zag In-line package,

or 26 pin zig-zag in-line memory module

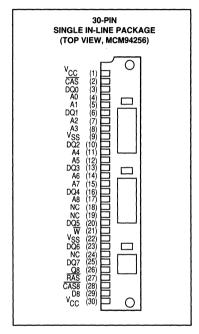

S=30 pad single-in-line memory module, or 72 pad single-in-line memory module L=30 pin single-in-line memory module

SG=30 pad single-in-line memory module with gold pac

### **DUAL PORT VIDEO RAMs**

| Γ   |         |         | Motorola   | Address     | Operating |        |                      | · ·                                             |

|-----|---------|---------|------------|-------------|-----------|--------|----------------------|-------------------------------------------------|

| - 1 |         | Organi- | Part       | Access Time | Current   | Pin    | Package              |                                                 |

| L   | Density | zation  | Number     | (ns Max)    | (mA Max)  | Count  | Options              | Comments                                        |

| П   | 1M      | 256Kx4  | MCM524258A | 100/120     | 140/150   | 28, 28 | (Z)IP, SO(J)         | Dual port VRAM with 512x4 SAM port, ta=25/35 ns |

| L   |         | 128Kx8  | MCM528128A | 100/120     | 140/150   | 40, 40 | (P)DIP, (Z)IP, SO(J) | Dual port VRAM with 256x8 SAM port, ta=25/35 ns |

GENERAL STATIC RAMs (HCMOS unless otherwise noted)

| Í          | Organi-   | Motorola<br>Part | Address<br>Access Time | Operating<br>Current | Pin   | - ,                 |                                                            |

|------------|-----------|------------------|------------------------|----------------------|-------|---------------------|------------------------------------------------------------|

| Density    | zation    | Number           | (ns Max)               | (mA Max)             | Count | Packaging           | Comments                                                   |

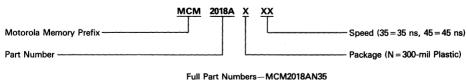

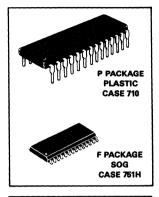

| 16K        | 2Kx8      | MCM2018AN        | 35/45/55               | 135                  | 24    | 300 mil, (P)DIP     | NMOS. Replaces TMM2019D, MCM2016HN, MCM2018N.              |

| 256K       | 32Kx8     | MCM60256A        | 85/100/120             | 70                   | 28    | (P)DIP, (F)SOG      | 100 μA standby current                                     |

|            |           | MCM60L256A       | 70/85/100/120          | 70                   | 28    | (P)DIP, (F)SOG      | 30 μA standby current                                      |

|            |           | MCM60L256A-C     | 100                    | 70                   | 28    | (P)DIP, (F)SOG      | Industrial temperature range (-40° to +85°C), low power    |

|            |           | MCM60L256A-V     | 100                    | 70                   | 28    | (P)DIP, (F)SOG      | Extended temperature range (-40° to +105°C), low power     |

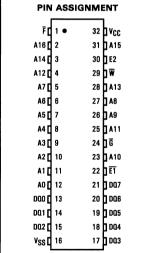

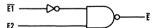

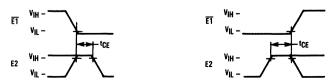

| 1M         | 128Kx8    | MCM518128        | 100                    | 60                   | 32    | (P)DIP, (F)&(SF)SOG | Built-in refresh, CE1 & CE2                                |

|            | Pseudo    | MCM518129        | 100                    | 60                   | 32    | (F)SOG              | Built-in refresh, CE & CS                                  |

|            | SRAM      | MCM51L8128       | 80/100                 | 70/60                | 32    | (P)DIP, (F)&(SF)SOG | 200 μA standby current, built-in refresh, CE1 & CE2        |

|            |           | MCM51L8129       | 80/100                 | 70/60                | 32    | (F)SOG              | 200 μA standby current, built-in refresh, CE & CS          |

|            |           | MCM51LV8128      | 80/100                 | 70/60                | 32    | (P)DIP, (F)&(SF)SOG | 200 μA standby current, built-in refresh, CE1 & CE2        |

|            |           | MCM51LV8129      | 80/100                 | 70/60                | 32    | (F)SOG              | 200 μA standby current, built-in refresh, CE & CS          |

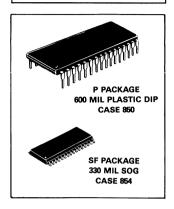

| ckage Info | ormation: | P=28 & 32 pin, 6 | 600 mil, plastic dual  | -in-line packa       | ge    |                     | SF=32 pin, 330 mil, plastic small outline gullwing package |

P=28 & 32 pin, 600 mil, plastic dual-in-line package

F=28 pin, 330 mil, plastic small outline gullwing package or,

32 pin, 450 mil, plastic small outline gullwing package

FAST STATIC RAMs (70 ns or Faster)

|         |         | Motorola   |       |                         | Address/       | Operating           |        |                                                            |

|---------|---------|------------|-------|-------------------------|----------------|---------------------|--------|------------------------------------------------------------|

| 1       | Organi- | Part       | Pin   | Packaging               | Cycle Time     | Current             | Tech-  | ,                                                          |

| Density | zation  | Number     | Count | (Package Width in mils) | (ns Max)       | (mA max)            | nology | Comments                                                   |

| 16K     | 2Kx8    | MCM2018A   | 24    | 300 PDIP                | 45/55          | 135                 | NMOS   | Replaces TMM2019D, MCM2016HN, MCM2018N.                    |

| 1       | 4Kx4    | MCM6268    | 20    | 300 PDIP                | 20/25/35/45/55 | 110/110/110/80/80   | HCMOS  | 20 ns in warehouse stock.                                  |

|         |         | MCM6269    | 20    | 300 PDIP                | 20/25/35       | 110                 | HOMOS  | Fast Chip Select access time=10/12/15 ns.                  |

|         |         | MCM6270    | 24/22 | 300 SOJ/PDIP            | 20/25/35       | 110                 | HCMOS  | Fast Output Enable access time=10/12/15 ns.                |

| 64K     | 8Kx8    | MCM6264    | 28    | 300/400 SOJ/300 PDIP    | 35/45/55       | 100/90/80           | HCMOS  | Look for DSP and cache memory applications.                |

| 1       |         | MCM6264D   | 28    | 300/400 SOJ/300 PDIP    | 20/25          | 115/110             | HCMOS  | 20 ns fast and 8 bits wide.                                |

| 1       |         | MCM6264    | 28    | 300 PDIP/SOJ            | 15             | 140                 | HOMOS  | 15 ns fast and 8 bits wide.                                |

|         |         | MCM6264C   | 28    | 300/400 SOJ/300 PDIP    | 35/45/55       | 100/90/80           | HCMOS  | Industrial temperature range, -40° to 85°C.                |

|         |         | MCM6264D-C | 28    | 300/400 SOJ/300 PDIP    | 25/30          | 115/110             | HCMOS  | Industrial temperature range, -40° to 85°C.                |

|         |         | MCM6264C   | 28    | 300 PDIP/SOJ            | 20             | 140                 | HCMOS  | Industrial temperature range, -40° to 85°C.                |

| 1       | 8Kx9    | MCM6265    | 28    | 300 SOJ/PDIP            | 15/20/25       | 140/130/120         | HCMOS  | Ideal for applications requiring parity.                   |

|         | 16Kx4   | MCM6288    | 22    | 300 PDIP                | 12/15/20/25/35 | 150/140/120/120/110 | HOMOS  | 12 ns devices have tDVWH=6 ns max.                         |

|         |         | MCM6290    | 24    | 300 SOJ/PDIP            | 12/15/20/25/35 | 150/140/120/120/110 | HOMOS  | 12 ns devices have Output Enable=6 ns max.                 |

|         | 64Kx1   | MCM6287    | 24/22 | 300 SOJ/PDIP            | 12/15/20/25/35 | 150/140/130/120/110 | HCMOS  | Mainframe applications, can also be used for parity bit.   |

| 256K    | 32Kx8   | MCM6206    | 28    | 400 SOJ/600 PDIP        | 30/35/45       | 130/125/115         | HCMOS  | Two chip control functions: Chip Enable and Output Enable. |

|         |         | MCM6206    | 28    | 300 SOJ/PDIP            | 17/20/25/35    | 155/150/140/135     | HOMOS  | 17 ns with full 10% power supply.                          |

| 1 1     |         | MCM6206C   | 28    | 300 SOJ/PDIP            | 25/35/45       | 140/135/130         | HOMOS  | Industrial temperature range, -40° to 85°C.                |

| 1       |         | MCM6706    | 28    | 300 SOJ                 | 10/12/15       | 180/170/160         | BICMOS | New, Motorola BiCMOS.                                      |

| 1 1     | 32Kx9   | MCM6205    | 32    | 300 SOJ/PDIP            | 17/20/25/35    | 155/150/140/135     | HCMOS  | Ideal for applications requiring parity.                   |

| 1       |         | MCM6205C   | 32    | 300 SOJ/PDIP            | 25/35/45       | 140/135/130         | HCMOS  | Industrial temperature range, -40° to 85°C.                |

|         |         | Motorola |       |                         | Address/   | Operating   |        |                               |

|---------|---------|----------|-------|-------------------------|------------|-------------|--------|-------------------------------|

|         | Organi- | Part     | Pin   | Packaging               | Cycle Time | Current     | Tech-  |                               |

| Density | zation  | Number   | Count | (Package Width in mils) | (ns Max)   | (mA max)    | nology | Comments                      |

| 256K    | 64Kx4   | MCM6709  | 28    | 300 SOJ                 | 10/12/15   | 180/170/160 | BICMOS | New, Motorola BiCMOS.         |

|         | 256Kx1  | MCM6207  | 24    | 300 SOJ/PDIP            | 15/20/25   | 150/140/130 | HCMOS  | 15 ns 256K with separate I/O. |

| 1M      | 128Kx8  | MCM6226  | 32    | 400 SOJ/PDIP            | 25/30      | 150/140     | HCMOS  | 1M fast static RAM.           |

|         | 256Kx4  | MCM6228  | 28    | 400 SOJ/PDIP            | 25/30      | 145/135     | HOMOS  | 1M fast static RAM.           |

### **FAST STATIC RAM MODULES**

|         |          | Motorola |       |           | Address/   | Operating      |        |                                                |

|---------|----------|----------|-------|-----------|------------|----------------|--------|------------------------------------------------|

|         | Organi-  | Part     | Pin   | i         | Cycle Time | Current        | Tech-  |                                                |

| Density | zation   | Number   | Count | Packaging | (ns Max)   | (mA max)       | nology | Comments                                       |

| 2M      | 64Kx32   | MCM3264Z | 64    | ZIP       | 20/25/30   | 1200/1120/1040 | HCMOS  | Perfect for 32-bit system, JEDEC standard.     |

|         | 256Kx8   | MCM8256Z | 60    | ZIP       | 20/25/30   | 1200/1120/1040 | HCMOS  | JEDEC standard module, faster speeds possible. |

| 3M      | 2x64Kx24 | MCM2464Z | 58    | ZIP       | 22/27      | 1680/1560      | HCMOS  | Two banks of x24 memory.                       |

### APPLICATION SPECIFIC STATIC RAMS

|                                  | Organi- | Motorola<br>Part | Pin   |                  | Address/<br>Cycle Time | Operating<br>Current | Tech-  |                                                                                              |  |

|----------------------------------|---------|------------------|-------|------------------|------------------------|----------------------|--------|----------------------------------------------------------------------------------------------|--|

| Description                      | zation  | Number           | Count | Packaging        | (ns Max)               | (mA max)             | nology |                                                                                              |  |

| Cache Tag RAM                    | 4Kx4    | MCM4180          |       | 300 mil SOJ/PDIP |                        | 140                  | HCMOS  | Fully compatible with Mostek MK41H80.                                                        |  |

| Cache Tag RAM<br>with Status Bit | 4Kx4    | MCM62350         | 24    | 300 mil SOJ/PDIP | 18/20/25               | 140                  |        | Housekeeping bits function, active pull-up match output. Flash clearable.                    |  |

| Registers                        |         | MCM62351         | 24    | 300 mil SOJ/PDIP | 18/20/25               | 140                  | HCMOS  | Housekeeping bits function, open drain match output. Flash clearable.                        |  |

| Synchronous                      | 16Kx4   | MCM6293          | 28    | 300 mil SOJ/PDIP | 20/25                  | 140                  | HCMOS  | Registered outputs for fully pipelined applications, separate I/O's.                         |  |

| Static RAM                       |         | MCM6294          | 28    | 300 mil SOJ/PDIP | 20/25                  | 140                  | HCMOS  | Registered outputs plus output enable, separate I/O's.                                       |  |

|                                  |         | MCM6295          | 28    | 300 mil SOJ/PDIP | 25/30                  | 140                  | HCMOS  | Transparent outputs plus output enable, separate I/O's.                                      |  |

|                                  | 64Kx4   | MCM62980         | 28    | 300 mil SOJ      | 15/20                  | 170                  | HCMOS  | Large cache memory for RISC and CISC systems.                                                |  |

|                                  |         | MCM62982         | 28    | 300 mil SOJ      | 12/15                  | 170                  | HCMOS  | Registered outputs for two stage pipeline.                                                   |  |

|                                  | 16Kx16  | MCM62990         | 52    | PLCC             | 17/20                  | 360                  | HCMOS  | Designed for advanced RISC-CISC cache applications.                                          |  |

|                                  | 4x64Kx1 | MCM62981         | 32    | 300 mil SOJ      | 15/20                  | 170                  | HCMOS  | Cache memory parity RAM.                                                                     |  |

|                                  |         | MCM62983         | 32    | 300 mil SOJ      | 12/15                  | 170/130              | HCMOS  | Registered outputs, cache memory parity RAM.                                                 |  |

|                                  | 4Kx10   | MCM62963         | 44    | PLCC             | 18/20/25               | 170                  | HCMOS  | Same functionality as MCM6293.                                                               |  |

|                                  | 4Kx12   | MCM62973         | 44    | PLCC             | 18/20/25               | 170                  | HCMOS  | Same functionality as MCM6293.                                                               |  |

|                                  |         | MCM62974         | 44    | PLCC             | 18/20/25               | 170                  | HCMOS  | Same functionality as MCM6294.                                                               |  |

|                                  |         | MCM62975         | 44    | PLCC             | 25/30                  | 170                  |        | Same functionality as MCM6295.                                                               |  |

|                                  | 32Kx9   | MCM62940         | 44    | PLCC             | 19/24                  | 250                  | HCMOS  | Burst mode for 040 applications.                                                             |  |

|                                  |         | MCM62950         | 44    | PLCC             | 20/25                  | 250                  | HCMOS  | Designed for advanced RISC-CISC cache applications.                                          |  |

|                                  |         | MCM62960         | 44    | PLCC             | 17/20/25               | 180                  | HCMOS  | Designed for SPARC™ applications. Functionally equivalent to CY7C157                         |  |

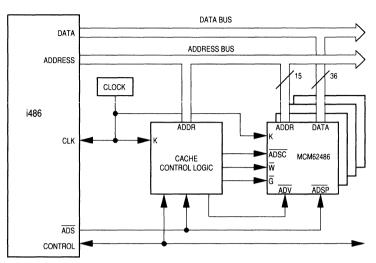

|                                  |         | MCM62486         | 44    | PLCC             | 19/24                  | 250                  |        | Burst mode for 486 applications.                                                             |  |

|                                  |         | MCM62110         | 52    | PLCC             | 15/20                  | 250                  |        | Dual WO's for 88110.                                                                         |  |

| DSPRAM                           |         | MCM56824         | 52    | PLCC             | 25/30/35               | 250/210/180          |        | Designed for DSP56001 applications.                                                          |  |

| Latched Address                  |         | MCM62820         | 52    | PLCC             | 23/30                  | 240/185              |        | CMOS Designed for MIPS R3000 cache.                                                          |  |

| SRAM                             | 16Kx16  | MCM62995         | 52    | PLCC             | 17/20/25               | 360                  |        | DSP96000 memory applications. Can be used like any asynchronous SRAM, samples available now. |  |

### **ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY MEMORY**

| Г |         |         | Motorola | Address     | Operating |       |           |                                                         |

|---|---------|---------|----------|-------------|-----------|-------|-----------|---------------------------------------------------------|

|   |         | Organi- | Part     | Access Time | Current   | Pin   | j         |                                                         |

|   | Density | zation  | Number   | (ns Max)    | (mA Max)  | Count | Packaging | Comments                                                |

| Γ | 2K      | 256Kx8  | MCM2814P | 3.5 μs      | 10        | 8     | (P)DIP    | 2 or 4 wire serial access, data protection after reset. |

Package Information: P=8 pin, 300 mil

### **DYNAMIC RAMs**

| MOTOROLA   | FUJITSU   | HITACHI  | INTEL         | MICRON   | MITSUBISHI | NEC       | OKI       | SAMSUNG   | TI        | TOSHIBA   |

|------------|-----------|----------|---------------|----------|------------|-----------|-----------|-----------|-----------|-----------|

| 1M×1       | 1M×1      | 1M×1     | 1 <b>M</b> ×1 | 1M×1     | 1M×1       | 1M×1      | 1M×1      | 1M×1      | 1M×1      | 1M×1      |

| MCM511000A | MB81C1000 | HM511000 | P21010        | MT4C1024 | M5M41000   | μPD421000 | MSM511000 | KM41C1000 | TMS4C1024 | TC511000A |

| MCM511001A | MB81C1001 | HM511001 |               | MT4C1025 | M5M41001   | μPD421001 | MSM511001 | KM41C1001 | TMS4C1025 | TC511001A |

| MCM511002A | MB81C1003 | HM511002 |               | MT4C1026 | M5M41002   | μPD421002 | MSM511002 | KM41C1002 | TMS4C1027 | TC511002A |

| MCM514256A | MB81C4256 | HM514256 | P21014        | MT4C4256 | M5M44256A  | μPD424256 | MSM514256 | KM44C256  | TMS44C256 | TC514256A |

| MCM514258A | MB81C4258 | HM514258 |               | MT4C4258 | M5M44258A  | μPD424258 | MSM514258 | KM44C258  |           | TC514258A |

| 1M×4       | 1M×4      | 1M×4     | 1M×4          | 1M×4     | 1M×4       | 1M×4      | 1M×4      | 1M×4      | 1M×4      | 1M×4      |

| MCM514400  | MB814400  | HM514400 |               | MT4C4001 | M5M44400   | μPD424400 |           | KM44C1000 |           | TC514400  |

| 4M×4       | 4M×4      | 4M×4     | 4M×4          | 4M×4     | 4M×4       | 4M×4      | 4M×4      | 4M×4      | 4M×4      | 4M×4      |

| MCM514100  | MB814100  | HM514100 | T21040        | MT4C1004 | M5M44100   | μPD424100 |           | KM41C4000 |           | TC514100  |

### **DYNAMIC RAM MODULES**

| MOTOROLA                                          | FUJITSU            | HITACHI     | INTEL     | MICRON                           | MITSUBISHI                       | NEC                                       | окі         | SAMSUNG   | TI                                    | TOSHIBA   |

|---------------------------------------------------|--------------------|-------------|-----------|----------------------------------|----------------------------------|-------------------------------------------|-------------|-----------|---------------------------------------|-----------|

| 256K×8                                            | 256K×8             | 256K×8      | 256K×8    | 256K×8                           | 256K×8                           | 256K×8                                    | 256K×8      | 256K×8    | 256K×8                                | 256K×8    |

| MCM84256<br>MCM8L4256                             |                    | HB56D25608  |           | MT8C8256                         | MH25608B                         | MC-41256A8                                | MSC2304_S8  |           | TM4256_8                              |           |

| 256K×9                                            | 256K×9             | 256K×9      | 256K×9    | 256K×9                           | 256K×9                           | 256K×9                                    | 256K×9      | 256K×9    | 256K×9                                | 256K×9    |

| MCM94256<br>MCM9L4256                             | MB85240            | HB56D25609  |           | MT8C9256                         | MH25609B                         | MC-41256A8                                | MSC2304_S9  |           | TM4256_9                              |           |

| 1M×8                                              | 1M×8               | 1M×8        | 1M×8      | 1M×8                             | 1M×8                             | 1M×8                                      | 1M×8        | 1M×8      | 1M×8                                  | 1M×8      |

| MCM81000S<br>MCM8L1000S<br>MCM81001S<br>MCM81002S | MB85230<br>MB85231 | HB56A18     | SM2101910 | MT8C8024<br>MT8C8025<br>MT8C8026 | MH1M08B0<br>MH1M08B1<br>MH1M08B2 | MC-421000A8<br>MC-421000B8<br>MC-421000C8 | MSC2313_S8  | KMM581000 | TM024GAD8                             | THM81000  |

| 1M×9                                              | 1M×9               | 1M×9        | 1M×9      | 1M×9                             | 1M×9                             | 1M×9                                      | 1M×9        | 1M×9      | 1M×9                                  | 1M×9      |

| MCM91000S<br>MCM9L1000S<br>MCM91001S              | MB85235            | HB56A19     |           | MT8C9024<br>MT8C9025             | MH1M09B0<br>MH1M09B1             | MC-421000A9<br>MC-421000B9                | MSC2312_S9  | KMM591000 | TM024EAD9                             | THM91000  |

| MCM91002S                                         | MB85237            |             |           | MT8C9026                         | MH1M09B2                         | MC-421000D3                               |             |           |                                       |           |

| 256K×36                                           | 256K×36            | 256K×36     | 256K×36   | 256K×36                          | 256K×36                          | 256K×36                                   | 256K×36     | 256K×36   | 256K×36                               | 256K×36   |

| MCM36256                                          |                    | HB56D25636B |           | MT8C36256                        | MH25636BJ                        |                                           |             |           |                                       | THM362500 |

| 512K×36                                           | 512K×36            | 512K×36     | 512K×36   | 512K×36                          | 512K×36                          | 512K×36                                   | 512K×36     | 512K×36   | 512K×36                               | 512K×36   |

| MCM36512                                          |                    | HB56D51236B |           | MT8C36512                        | MH51236BJ                        |                                           |             |           | · · · · · · · · · · · · · · · · · · · | THM365120 |

| 4M×8                                              | 4M×8               | 4M×8        | 4M×8      | 4M×8                             | 4M×8                             | 4M×8                                      | 4M×8        | 4M×8      | 4M×8                                  | 4M×8      |

| MCM84000<br>MCM8L4000                             |                    | HB56A48     |           |                                  |                                  |                                           |             |           |                                       |           |

| 4M×9                                              | 4M×9               | 4M×9        | 4M×9      | 4M×9                             | 4M×9                             | 4M×9                                      | 4M×9        | 4M×9      | 4M×9                                  | 4M×9      |

| MCM94000<br>MCM9L4000                             |                    | HB56A49     |           |                                  | MH4M090J                         |                                           | MSC2340_YS9 |           |                                       |           |

### **FAST STATIC RAMs**

| MOTOROLA*                                            | IDT                                                          | CYPRESS                                                          | MICRON                                                           | PERFORMANCE                                              | HITACHI                                                     | FUJITSU                      | TOSHIBA                                          | MITSUBISHI                                   | SONY                                          |

|------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------|------------------------------|--------------------------------------------------|----------------------------------------------|-----------------------------------------------|

| 4K×4                                                 | 4K×4                                                         | 4K×4                                                             | 4K×4                                                             | 4K×4                                                     | 4K×4                                                        | 4K×4                         | 4K×4                                             | 4K×4                                         | 4K×4                                          |

| MCM6268P20<br>MCM6268P25<br>MCM6269P20<br>MCM6269P25 | IDT6168SA20P<br>IDT6168SA25P                                 | CY7C168A-20PC<br>CY7C168A-25PC<br>CY7C169A-20PC<br>CY7C169A-25PC | MT5C1604-20<br>MT5C1604-25                                       | P4C168-20PC<br>P4C168-25PC<br>P4C169-20PC<br>P4C169-25PC | HM6268P-25                                                  | MB81C68A-25P<br>MB81C69A-25P |                                                  |                                              |                                               |

| MCM6270J20<br>MCM6270J25<br>MCM6270P20<br>MCM6270P25 | IDT61970S20Y<br>IDT61970S25Y<br>IDT61970S20P<br>IDT61970S25P |                                                                  | MT5C1605DJ-20<br>MT5C1605DJ-25<br>MT5C1605-20<br>MT5C1605-25     | P4C170-20PC<br>P4C170-25PC                               |                                                             |                              |                                                  |                                              |                                               |

| 8K×8                                                 | 8K×8                                                         | 8K×8                                                             | 8K×8                                                             | 8K×8                                                     | 8K×8                                                        | 8K×8                         | 8K×8                                             | 8K×8                                         | 8K×8                                          |

| MCM6264NJ15*<br>MCM6264NJ20*<br>MCM6264NJ25*         | IDT7164S20Y<br>IDT7164S25Y                                   | CY7C185-15VC<br>CY7C185-20VC<br>CY7C185-25VC                     | MT5C6408DJ-15<br>MT5C6408DJ-20<br>MT5C6408DJ-25                  | P4C164-20JC<br>P4C164-25JC                               | -                                                           |                              | TC5588J-15<br>TC5588J-20<br>TC5588J-25           |                                              | CXK5863AJ15<br>CXK5863AJ20<br>CXK5863J25/AJ25 |

| MCM6264P15*<br>MCM6264P20*<br>MCM6264P25*            | IDT7164S20P<br>IDT7164S25P                                   | CY7C185-15PC<br>CY7C185-20PC<br>CY7C185-25PC                     | MT5C6408-15<br>MT5C6408-20<br>MT5C6408-25                        | P4C164-20PC<br>P4C164-25PC                               |                                                             |                              | TC5588P-15<br>TC5588P-20<br>TC5588P-25           |                                              | CXK5863AP15<br>CXK5863AP20<br>CXK5863P25/AP25 |

| 8K×9                                                 | 8K×9                                                         | 8K×9                                                             | 8K×9                                                             | 8K×9                                                     | 8K×9                                                        | 8K×9                         | 8K×9                                             | 8K×9                                         | 8K×9                                          |

| MCM6265J15<br>MCM6265J20                             |                                                              |                                                                  |                                                                  | P4C163-20JC                                              |                                                             | MB82B79-15PJ<br>MB82B79-20PJ | TC5589J-15<br>TC5589J-20                         | M5M179P-35                                   |                                               |

| MCM6265P15<br>MCM6265P20                             |                                                              |                                                                  |                                                                  | P4C163-20PC                                              |                                                             |                              | TC5589P-15<br>TC5589P-20                         | -                                            |                                               |

| 16K×4                                                | 16K×4                                                        | 16K×4                                                            | 16K×4                                                            | 16K×4                                                    | 16K×4                                                       | 16K×4                        | 16K×4                                            | 16K×4                                        | 16K×4                                         |

| MCM6288P12<br>MCM6288P15<br>MCM6288P20<br>MCM6288P25 | IDT7188S15P<br>IDT7188S20P<br>IDT7188S25P                    | CY7C164-12PC<br>CY7C164-15PC<br>CY7C164-20PC<br>CY7C164-25PC     | MT5C6404-12<br>MT5C6404-15<br>MT5C6404-20<br>MT5C6404-25         | P4C188-12PC<br>P4C188-15PC<br>P4C188-20PC<br>P4C188-25PC | HM6788HP-12<br>HM6788HP-15<br>HM6788HP-20<br>HM6788P-25     | MB81C74-25P                  | TC55416P-15H<br>TC55416P-20/P-20H<br>TC55416P-25 | M5M5188BP-15<br>M5M5188BP-20<br>M5M5188AP-25 | CXK5464AP15<br>CXK5464AP20<br>CXK5464AP25     |

| MCM6290J12<br>MCM6290J15<br>MCM6290J20<br>MCM6290J25 | IDT6198S15Y<br>IDT6198S20Y<br>IDT6198S25Y                    | CY7C166-12VC<br>CY7C166-15VC<br>CY7C166-20VC<br>CY7C166-25VC     | MT5C6405DJ-12<br>MT5C6405DJ-15<br>MT5C6405DJ-20<br>MT5C6405DJ-25 | P4C198-12JC<br>P4C198-15JC<br>P4C198-20JC<br>P4C198-25JC | HM6789HJP-12<br>HM6789HJP-15<br>HM6789HJP-20<br>HM6789JP-25 | MB81C75-25PJ                 | TC55417J-15H<br>TC55417J-20/J-20H<br>TC55417J-25 | M5M5189BJ-15<br>M5M5189BJ-20<br>M5M5189AJ-25 | CXK5465J15<br>CXK5465J20<br>CXK5465J25        |

| MCM6290P12<br>MCM6290P15<br>MCM6290P20<br>MCM6290P25 | IDT6198S15P<br>IDT6198S20P<br>IDT6198S25P                    | CY7C166-12PC<br>CY7C166-15PC<br>CY7C166-20PC<br>CY7C166-25PC     | MT5C6405-12<br>MT5C6405-15<br>MT5C6405-20<br>MT5C6405-25         | P4C198-12PC<br>P4C198-15PC<br>P4C198-20PC<br>P4C198-25PC | HM6789HP-12<br>HM6789HP-15<br>HM6789HP-20<br>HM6789P-25     | MB81C75-25P                  | TC55417P-15<br>TC55417P-20/P-20H<br>TC55417P-25  | M5M5189BP-15<br>M5M5189BP-20<br>M5M5189AP-25 |                                               |

| 64K×1                                                | 64K×1                                                        | 64K×1                                                            | 64K×1                                                            | 64K×1                                                    | 64K×1                                                       | 64K×1                        | 64K×1                                            | 64K×1                                        | 64K×1                                         |

| MCM6287J12<br>MCM6287J15<br>MCM6287J20<br>MCM6287J25 | IDT7187S15Y<br>IDT7187S20Y<br>IDT7187S25Y                    | CY7C187-15VC<br>CY7C187-20VC<br>CY7C187-25VC                     | MT5C6401DJ-12<br>MT5C6401DJ-15<br>MT5C6401DJ-20<br>MT5C6401DJ-25 | P4C187-12JC<br>P4C187-15JC<br>P4C187-20JC<br>P4C187-25JC | HM6787HJP-12<br>HM6787HJP-15<br>HM6787HJP-20<br>HM6787JP-25 | MB81C71A-25PJ                | -                                                | M5M5187BJ-15<br>M5M5187BJ-20<br>M5M518JAJ-25 | CXK5164J15<br>CXK5164J20<br>CXK5164J25        |