# **MECL Data**

| General Information | . 1 |

|---------------------|-----|

| MECL 10H            | 2   |

| MECL 10K            | 3   |

| MECL III            | 4   |

| MECL Memories       | 5   |

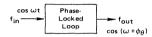

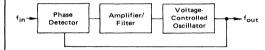

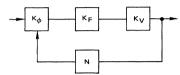

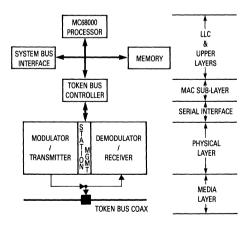

**Phase-Locked Loop**

**Carrier Band Modem**

# **DATA CLASSIFICATION**

## **Product Preview**

This heading on a data sheet indicates that the device is in the formative stages or in design (under development). This disclaimer at the bottom of the first page reads: "This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice."

## Advance Information

This heading on a data sheet indicates that the device is in sampling, preproduction, or first production stages. The disclaimer at the bottom of the first page reads: "This document contains information on a new product. Specifications and information herein are subject to change without notice."

# **Fully Released**

A fully released data sheet contains neither a classification heading nor a disclaimer at the bottom of the first page. This document contains information on a product in full production. Guaranteed limits will not be changed without written notice to your local Motorola Semiconductor Sales Office.

This book presents technical data for a broad line of MECL integrated circuits. Complete specifications for the individual circuits are provided in the form of data sheets. In addition, selector guides are included to simplify the task of choosing the best combination of circuits for optimum system architecture.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application. Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and 🕙 are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

> Fifth Edition First Printing © Motorola, Inc. 1993 Previous Edition © 1989 "All Rights Reserved"

ECLinPS, MECL 10H, MECL, MECL 10K, MECL 10,000, MECL III, MOSAIC, MTTL, and QUIL are trademarks of Motorola Inc.

### **CONTENTS**

| P                                                        | age |

|----------------------------------------------------------|-----|

| DEVICE INDEX                                             | ii  |

| CHAPTER 1 — GENERAL INFORMATION                          | 1-1 |

| High-Speed Logic                                         |     |

| MECL Products/General Characteristics                    | 1-2 |

| MECL in Perspective                                      |     |

| MECL Applications                                        |     |

| Basic Considerations for High-Speed Logic Design         | 1-3 |

| Circuit Description                                      |     |

| Definitions of Letter Symbols and Abbreviations          |     |

| MECL Positive and Negative Logic                         |     |

| Technical Data                                           |     |

| General Characteristics and Specifications               |     |

| Letter Symbols and Abbreviations                         |     |

| Maximum Ratings                                          | 1-9 |

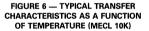

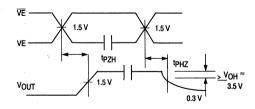

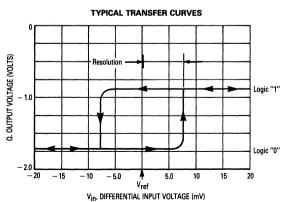

| MECL Transfer Curves                                     |     |

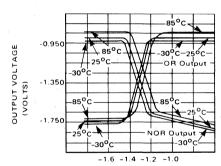

| Noise Margin                                             |     |

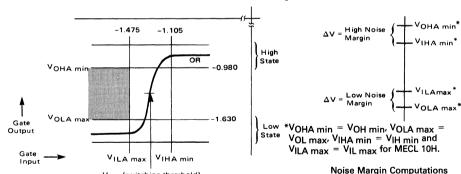

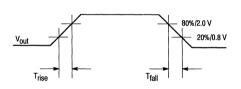

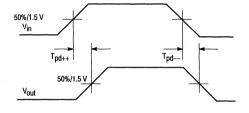

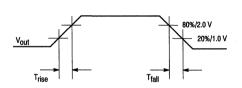

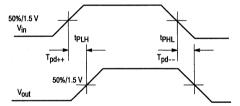

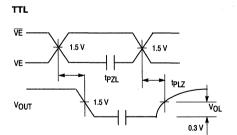

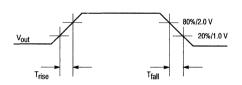

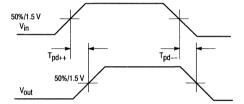

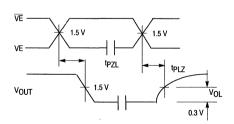

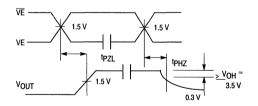

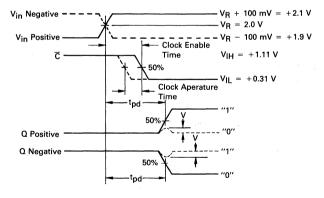

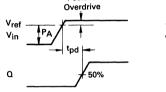

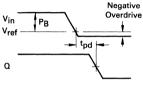

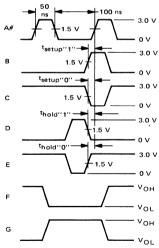

| AC/Switching Parameters                                  |     |

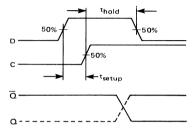

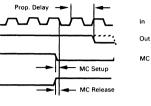

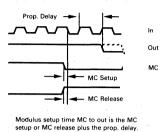

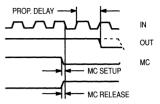

| Setup and Hold Times                                     |     |

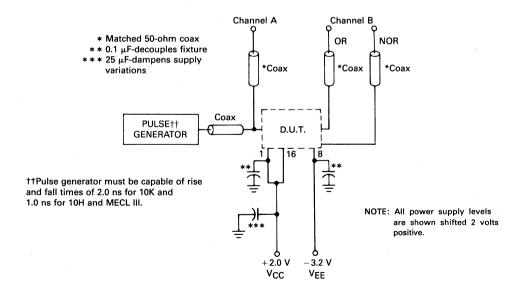

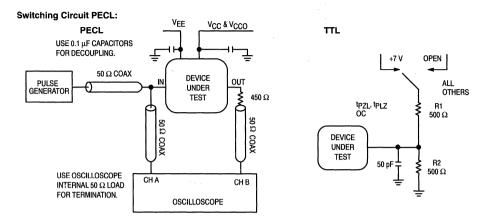

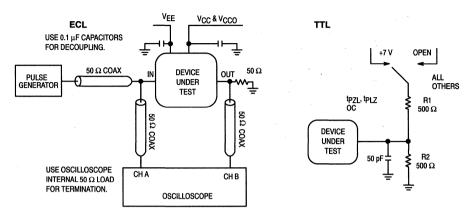

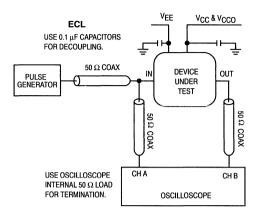

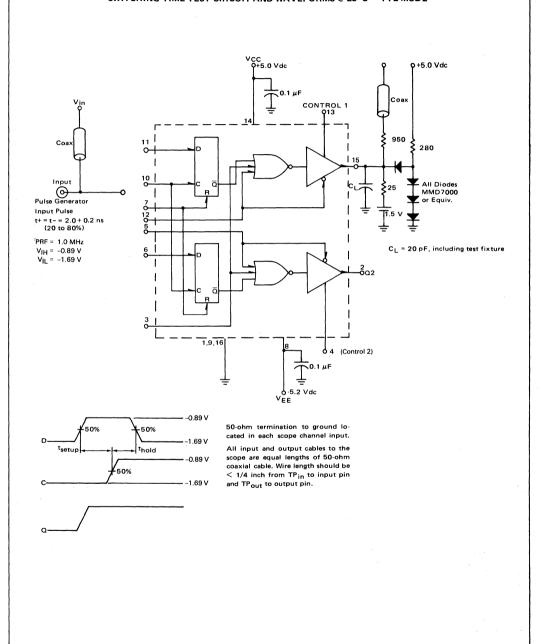

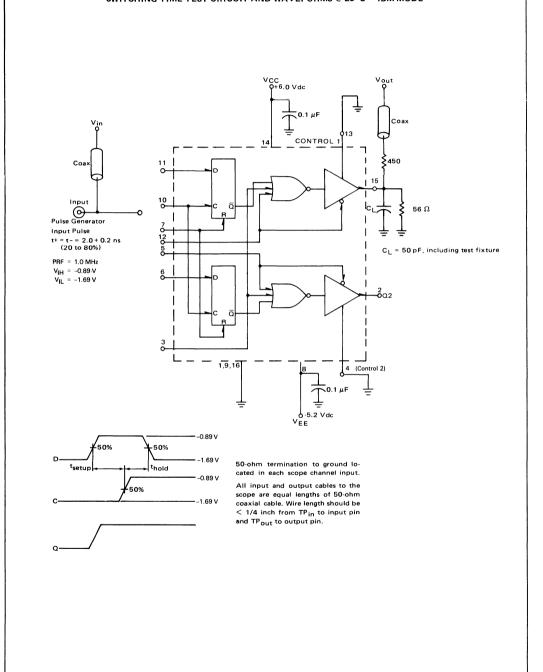

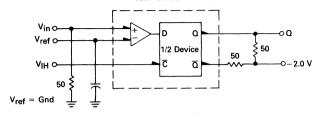

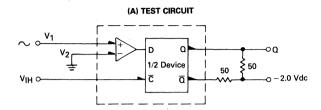

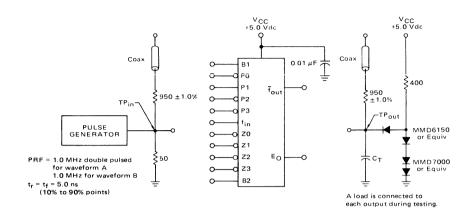

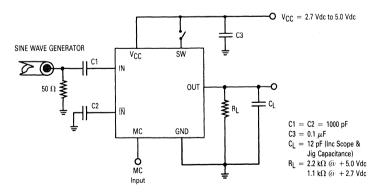

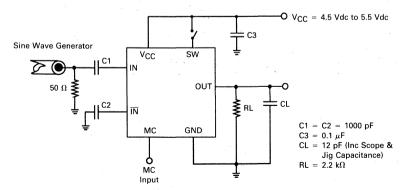

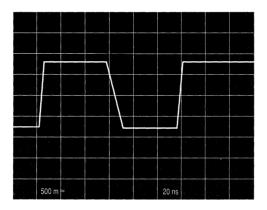

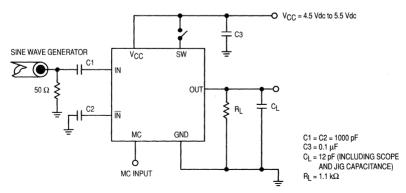

| Testing MECL 10H, MECL 10K and MECL III                  |     |

| Operational Data                                         |     |

| Power Supply Considerations                              |     |

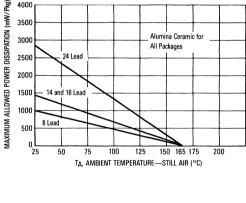

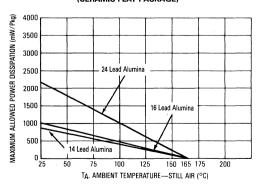

| Power Dissipation                                        |     |

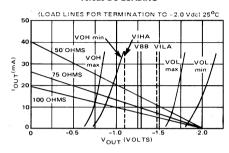

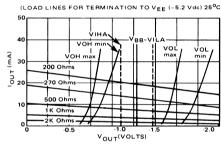

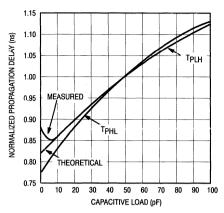

| Loading Characteristics                                  |     |

| Unused MECL Inputs                                       |     |

| System Design Considerations                             |     |

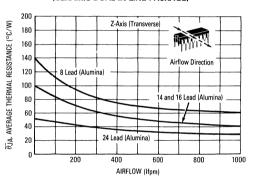

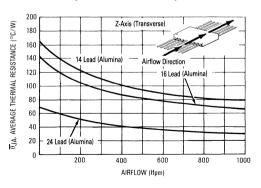

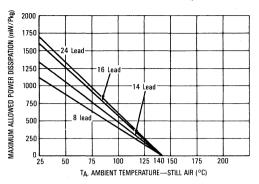

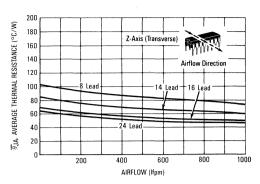

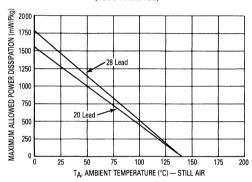

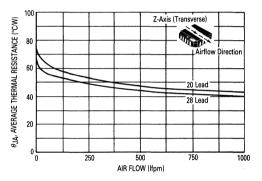

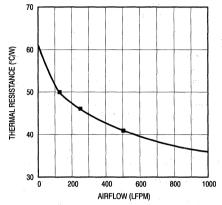

| Thermal Management                                       |     |

| Air Flow                                                 |     |

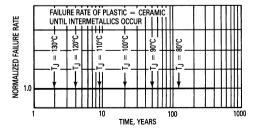

| Optimizing the Long Term Reliability of Plastic Packages |     |

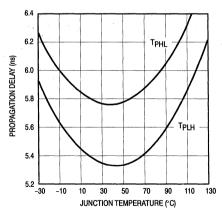

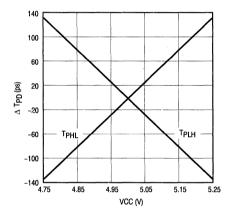

| Thermal Effects on Noise Margin                          |     |

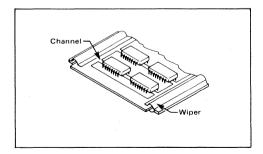

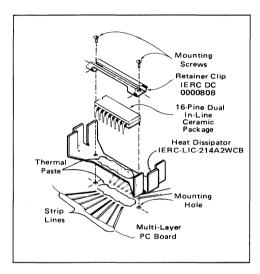

| Mounting and Heat Sink Suggestions                       |     |

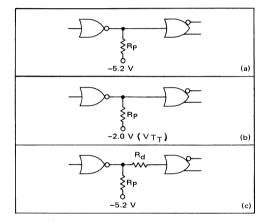

| Interfacing MECL to Slower Logic Types                   |     |

| Circuit Interconnections                                 |     |

| Clock Distribution                                       |     |

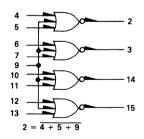

| Logic Shortcuts                                          |     |

| System Considerations — A Summary of Recommendations     |     |

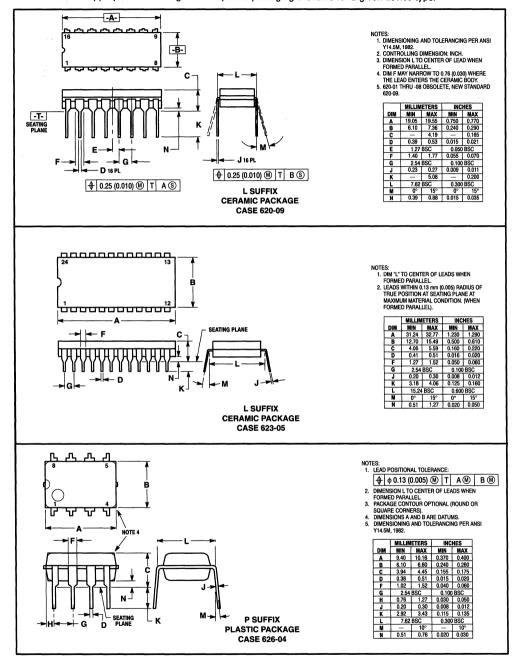

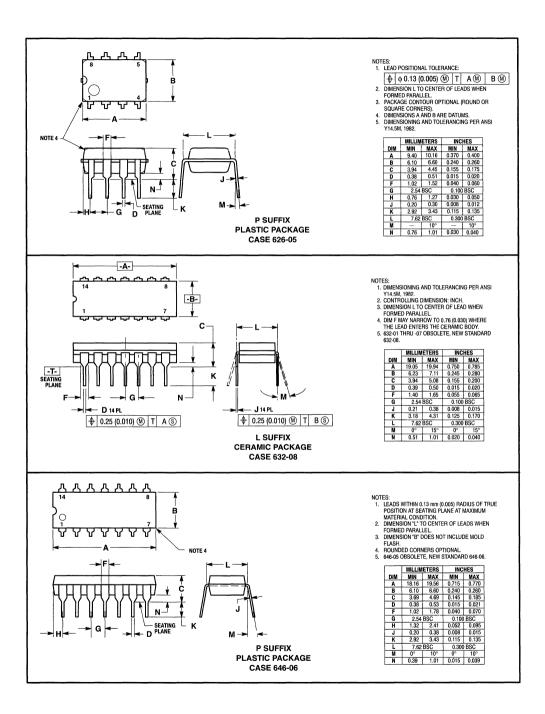

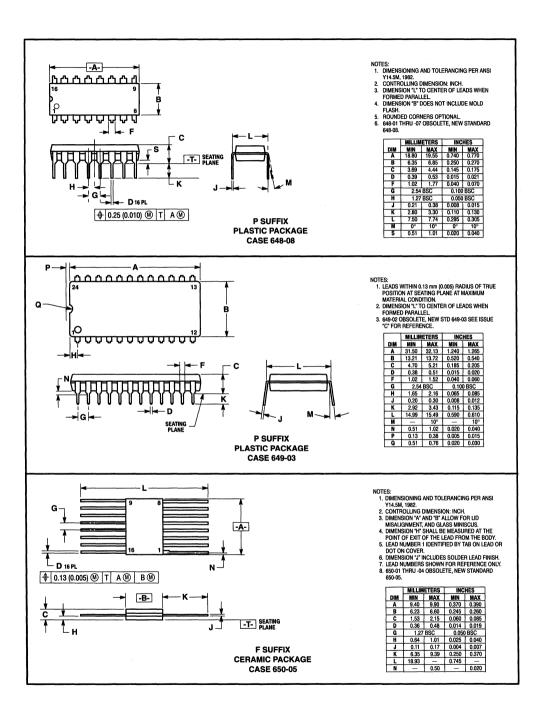

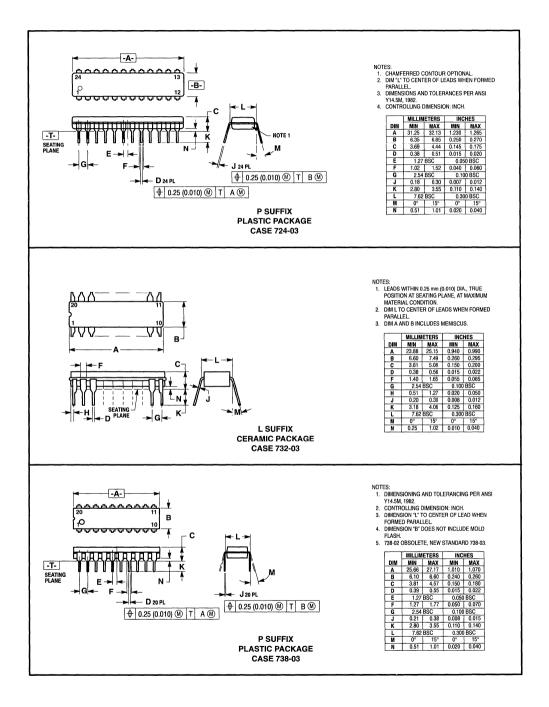

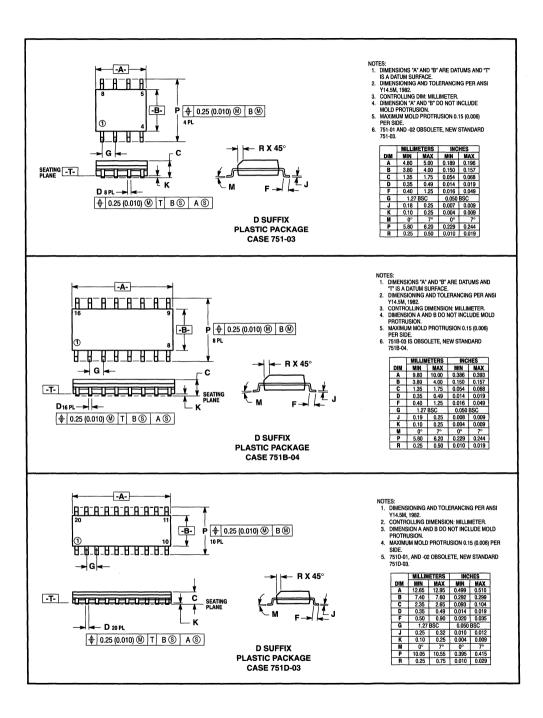

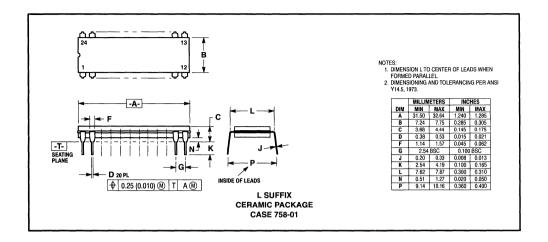

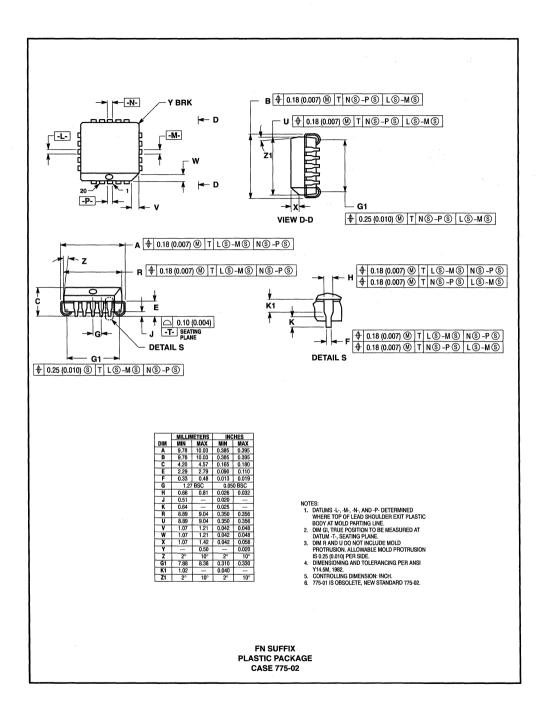

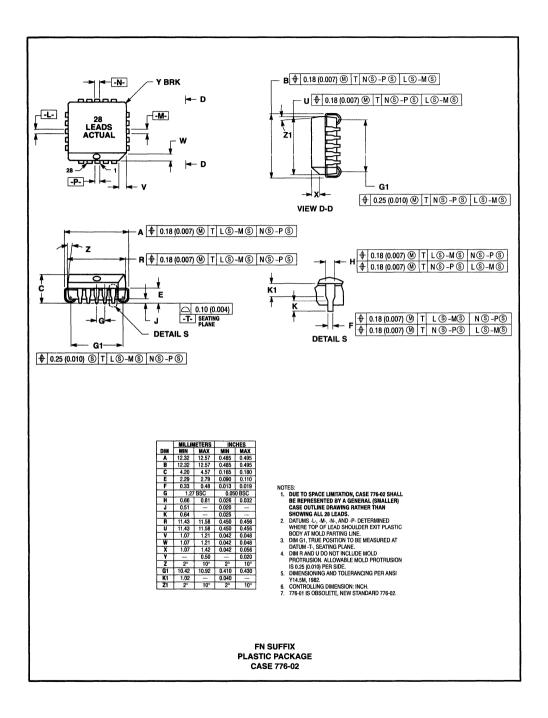

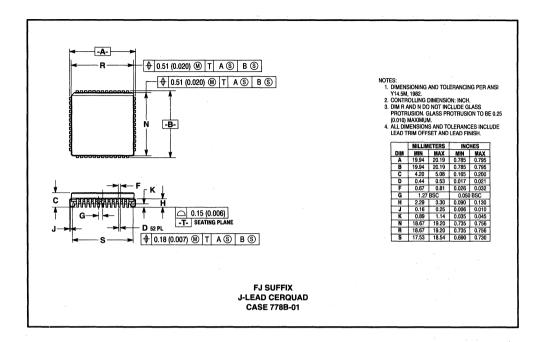

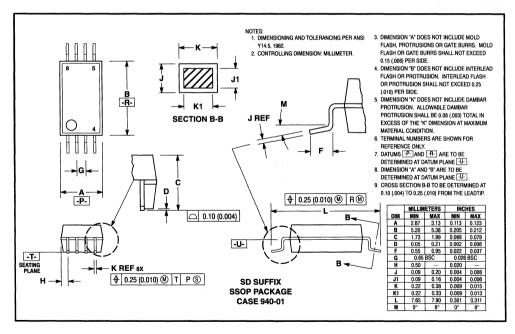

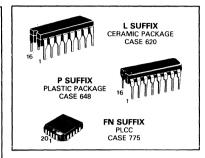

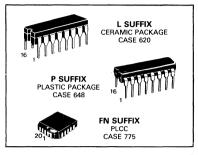

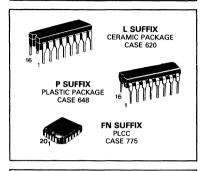

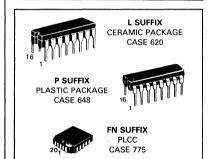

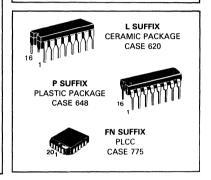

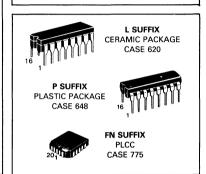

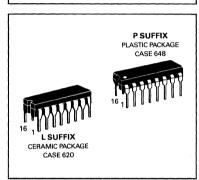

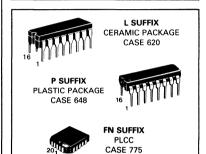

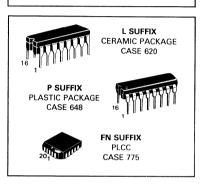

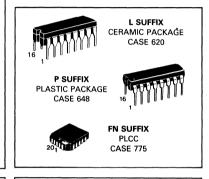

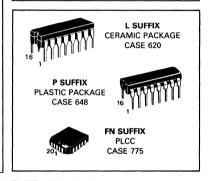

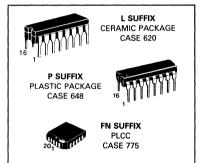

| Package Outline Dimensions                               |     |

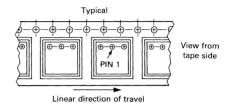

| MECL Logic Surface Mount                                 |     |

| Logic Literature Listings                                |     |

| Applications Assistance Form                             |     |

| CHAPTER 2 — MECL 10H                                     |     |

| CHAPTER 3 — MECL 10K                                     | 3-1 |

| CHAPTER 4 — MECL III                                     |     |

| CHAPTER 5 — MECL MEMORIES                                |     |

| CHAPTER 6 — PHASE-LOCKED LOOP                            |     |

| CHAPTER 7 — CARRIER BAND MODEM                           |     |

# **DEVICE INDEX**

| Device Number | Function                                          | Page   |

|---------------|---------------------------------------------------|--------|

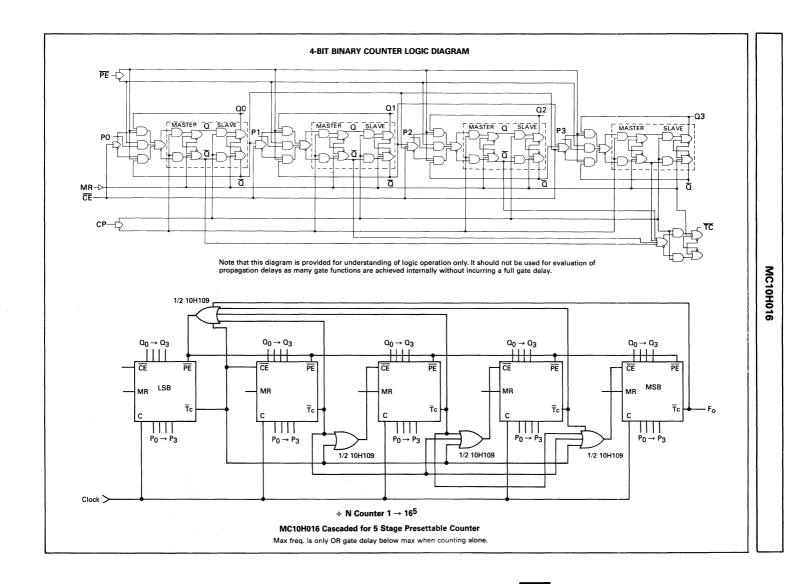

| MC10H016      | Binary Counter                                    | 2-6    |

| MC10H100      | Quad 2-Input "NOR" Gate with Strobe               | 2-8    |

| MC10H101      | Quad "OR/NOR" Gate                                | 2-9    |

| MC10H102      | Quad 2-Input "NOR" Gate                           |        |

| MC10H103      | Quad 2-Input "OR" Gate                            |        |

|               |                                                   |        |

| MC10H104      | Quad 2-Input "AND" Gate                           | 2-12   |

| MC10H105      | Triple 2-3-2-Input "OR/NOR" Gate                  |        |

| MC10H106      | Triple 4-3-3-Input "NOR" Gate                     | 2-14   |

| MC10H107      | Triple 2-Input Exclusive "OR"/Exclusive "NOR"     |        |

| MC10H109      | Dual 4-5-Input "OR/NOR" Gate                      |        |

|               |                                                   |        |

| MC10H113      | Quad Exclusive "OR" Gate                          | 2-17   |

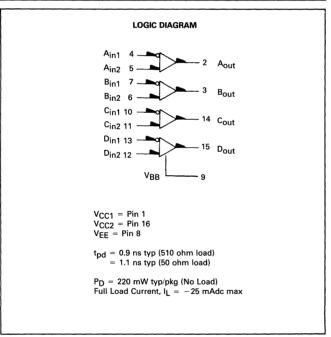

| MC10H115      | Quad Line Receiver                                |        |

| MC10H116      | Triple Line Receiver                              |        |

| MC10H117      | Dual 2-Wide 2-3-Input "OR-AND/OR-AND-INVERT" Gate | 2-20   |

| MC10H118      | Dual 2-Wide 3-Input "OR-AND" Gate                 |        |

| 11101011110   | Dual E Wildo o Input City Nito Cate               |        |

| MC10H119      | 4-Wide 4-3-3-3-Input "OR-AND" Gate                | 2-22   |

| MC10H121      | 4-Wide "OR-AND/OR-AND-INVERT" Gate                |        |

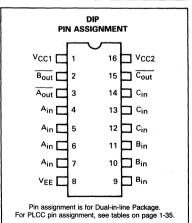

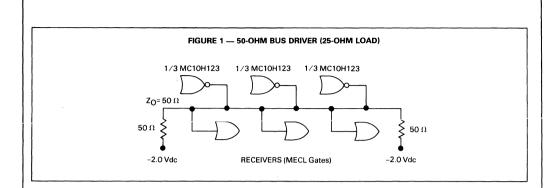

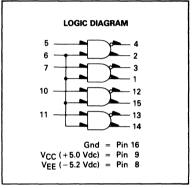

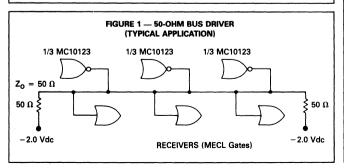

| MC10H123      | Triple 4-3-3-Input Bus Driver (25 ohms)           |        |

| MC10H124      | Quad TTL-to-MECL Translator                       |        |

| MC10H125      | Quad MECL-to-TTL Translator                       |        |

| 1010111120    | Quad WESE to The Hallolator                       | 2 20   |

| MC10H130      | Dual Latch                                        | 2-30   |

| MC10H131      | Dual Type D Master-Slave Flip-Flop                |        |

| MC10H135      | Dual J-K Master Slave Flip-Flop                   | 2-34   |

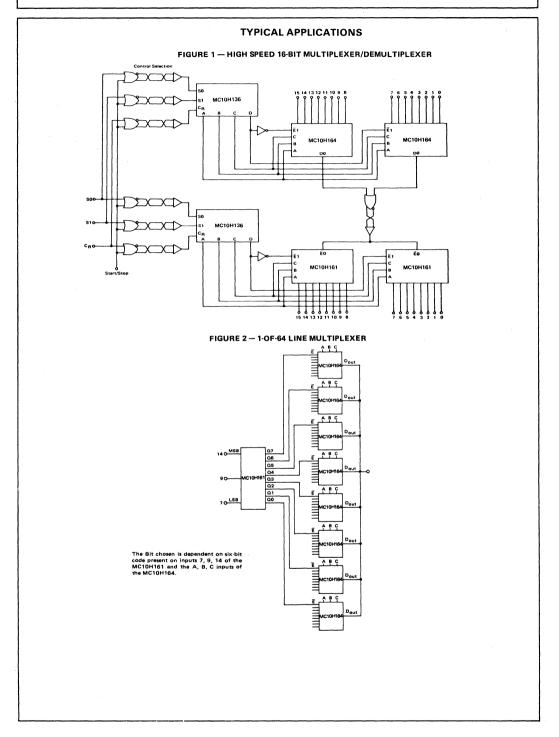

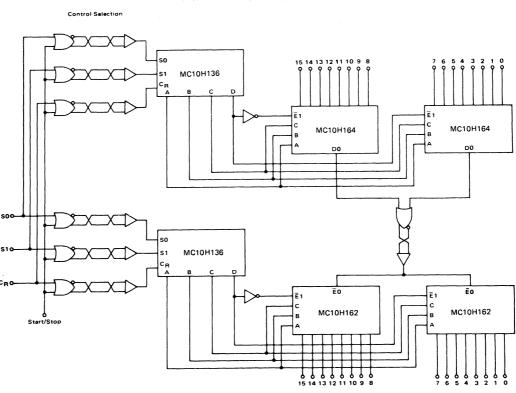

| MC10H136      | Universal Hexadecimal Counter                     |        |

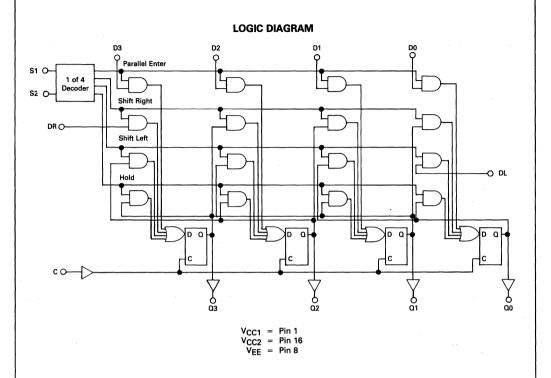

| MC10H141      | Four-Bit Universal Shift Register                 |        |

| MOTORITAT     | Tour Dit Offiversal Offit Hogister                | 2-07   |

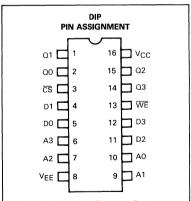

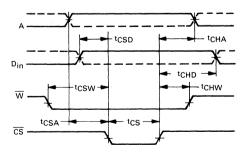

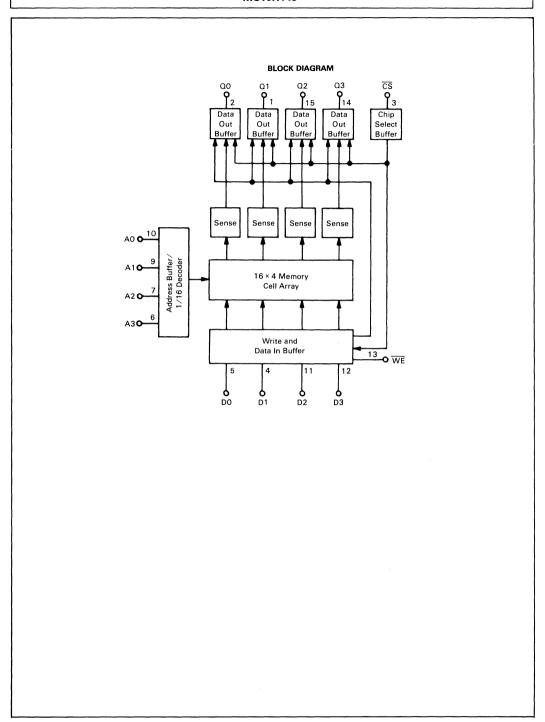

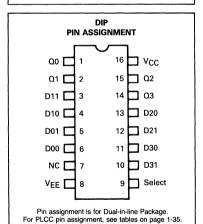

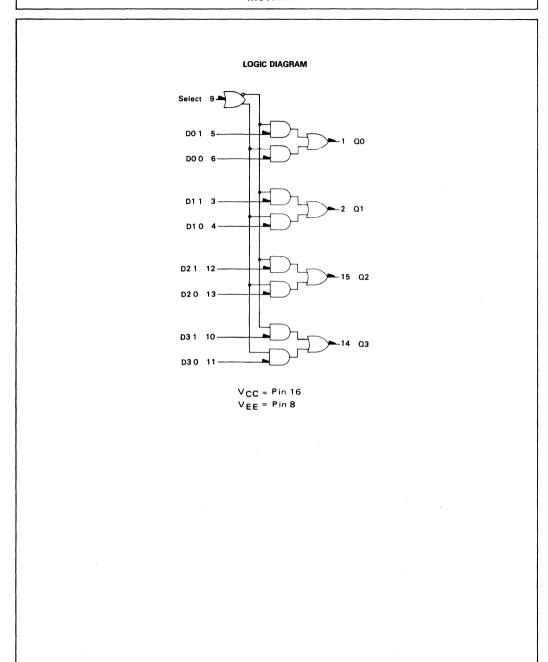

| MC10H145      | 16 x 4-Bit Register File (RAM)                    | 2-39   |

| MC10H158      | Quad 2-Input Multiplexer (Non-Inverting)          |        |

| MC10H159      | Quad 2-Input Multiplexer (Inverting)              |        |

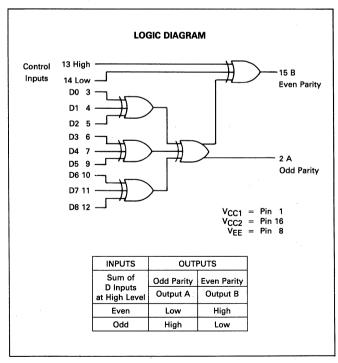

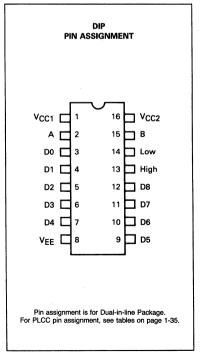

| MC10H160      | 12-Bit Parity Generator-Checker                   |        |

| MC10H161      | Binary to 1-8 Decoder (Low)                       |        |

| WOTOTTOT      | Billary to 1 o booder (Low)                       | . 2 7/ |

| MC10H162      | Binary to 1-8 Decoder (High)                      | 2-49   |

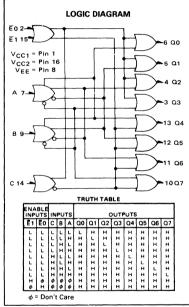

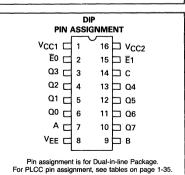

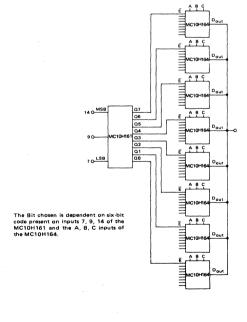

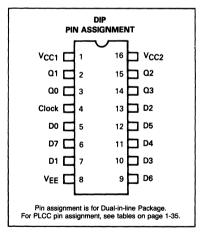

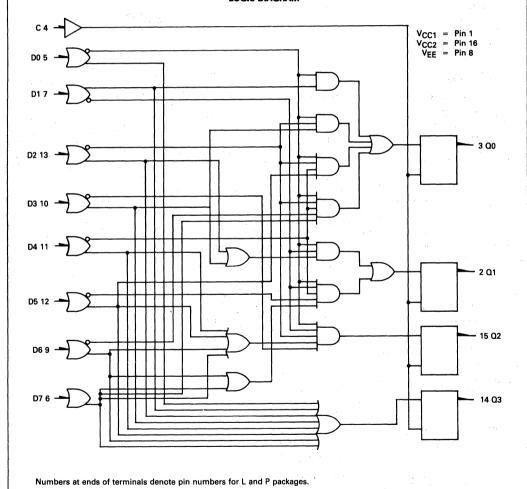

| MC10H164      | 8-Line Multiplexer                                |        |

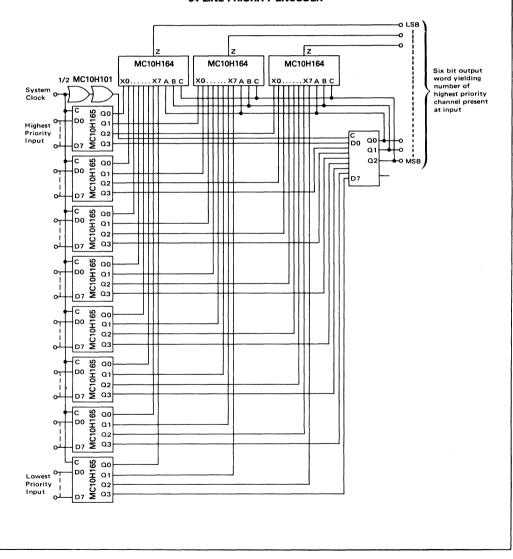

| MC10H165      | 8-Input Priority Encoder                          |        |

| MC10H166      | 5-Bit Magnitude Comparator                        |        |

| MC10H171      | Dual Binary to 1-4 Decoder (Low)                  |        |

| MIC TOTTI / T | Dual biliary to 1-4 Decoder (Low)                 | . 2-09 |

| MC10H172      | Dual Binary to 1-4 Decoder (High)                 | 2-61   |

| MC10H172      | Quad 2-Input Multiplexer/Latch                    |        |

| MC10H174      | Dual 4-to-1 Multiplexer                           |        |

| MC10H175      | Quint Latch                                       |        |

| MC10H176      | Hex "D" Master-Slave Flip-Flop                    |        |

| WIC 1011170   | Tion b inacter clave I lip-1 lop                  | . 2-09 |

| Device Number | Function                                                    | Page  |

|---------------|-------------------------------------------------------------|-------|

| MC10H179      | Look-Ahead Carry Block                                      | 2-71  |

| MC10H180      | Dual 2-Bit Adder/Subtractor                                 | 2-74  |

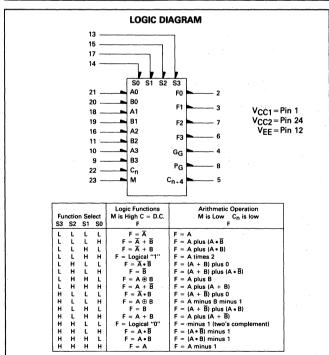

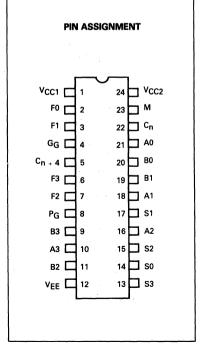

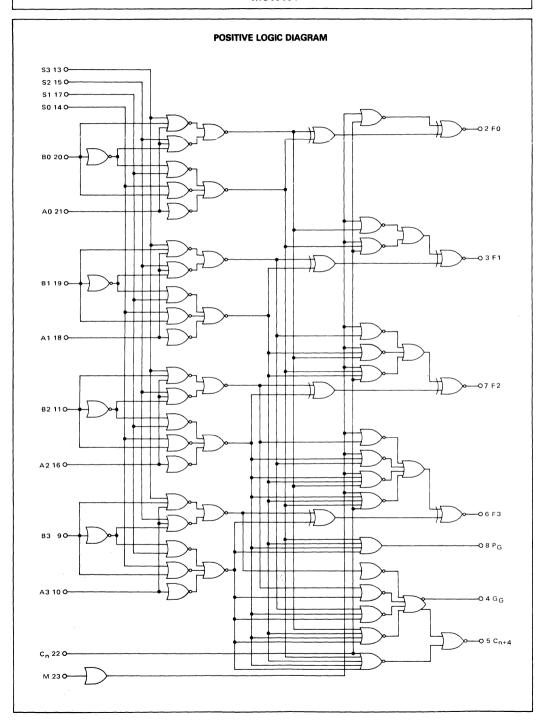

| MC10H181      | 4-Bit ALU/Function Generator                                |       |

| MC10H186      | Hex "D" Master-Slave Flip-Flop/with Reset                   | 2-79  |

| MC10H188      | Hex Buffer w/Enable                                         |       |

| MC10H189      | Hex Inverter w/Enable                                       |       |

| MC10H209      | Dual 4-5-Input "OR/NOR" Gate                                |       |

| MC10H210      | Dual 3-Input 3-Output "OR" Gate                             | 2-84  |

| MC10H211      | Dual 3-Input 3-Output "NOR" Gate                            |       |

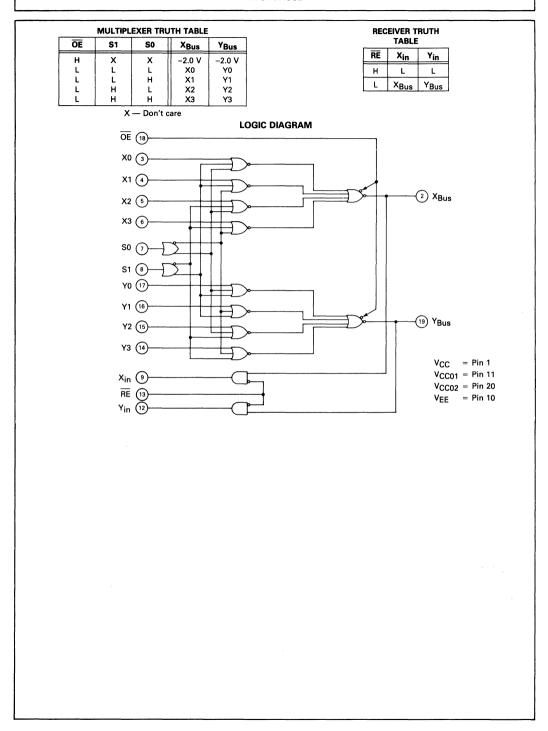

| MC10H330      | Quad Bus Driver/Receiver with 2-to-1 Output Multiplexers    | 2-86  |

| MC10H332      | Dual Bus Driver/Receiver with 4-to-1 Output Multiplexers    |       |

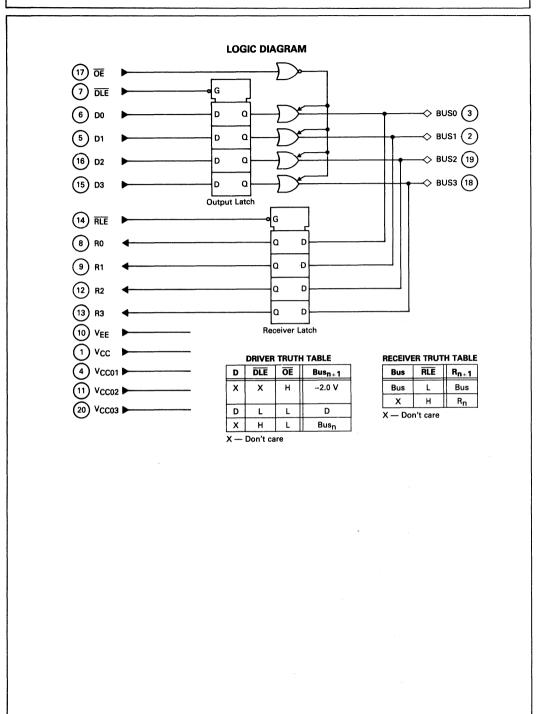

| MC10H334      | Quad Bus Driver/Receiver with Transmit and Receiver Latches |       |

| MC10H350      | Quad PECL-to-TTL Translator (+5 Vdc Power Supply Only)      |       |

| MC10H351      | Quad TTL/NMOS to PECL Translator                            | 2-94  |

| MC10H352      | Quad CMOS to PECL Translator                                | 2-96  |

| MC10H423      | Triple 3-Input Bus Driver with Enable (25 ohm)              |       |

| MC10H424      | Quad TTL-to-ECL Translator (ECL Strobe)                     | 2-100 |

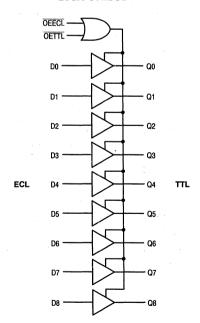

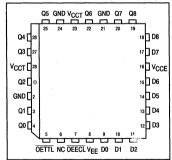

| MC10H600      | 9-Bit TTL-ECL Translator                                    | 2-102 |

| MC10H601      | 9-Bit ECL-TTL Translator                                    | 2-104 |

| MC10H602      | 9-Bit Latch/TTL-ECL Translator                              | 2-106 |

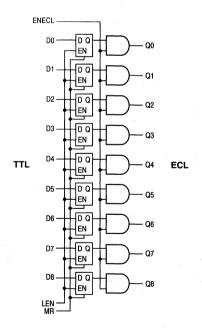

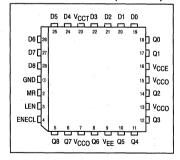

| MC10H603      | 9-Bit Latch/ECL-TTL Translator                              |       |

| MC10H604      | Registered Hex TTL/ECL Translator                           |       |

| MC10H605      | Registered Hex ECL-to-TTL Translator                        |       |

| MC10H606      | Registered Hex TTL-to-PECL Translator                       |       |

| MC10H607      | Registered Hex PECL-to-TTL Translator                       | 2-119 |

| MC10H640      | 68030/68040 ECL/TTL Clock Driver                            |       |

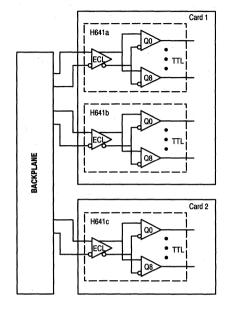

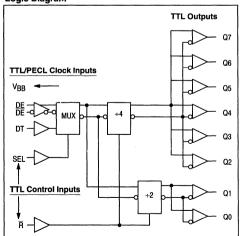

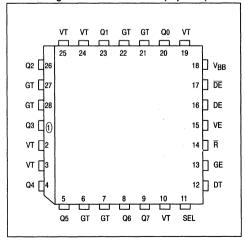

| MC10H641      | Single Supply PECL ≥ TTL 1:9 Clock Distribution             |       |

| MC10H642      | 68030/68040 ECL/TTL Clock Driver                            |       |

| MC10H643      | Dual Supply ECL-TTL 1:8 Clock Driver                        |       |

| MC10H644      | 68030/68040 PECL/TTL Clock Driver                           | 2-142 |

| MC10H645      | 1:9 TTL Clock Driver                                        |       |

| MC10H646      | PECL/TTL-TTL 1:8 Clock Distribution Chip                    |       |

| MC10H660      | 4-Bit ECL-TTL Load Reducing DRAM Driver                     |       |

| MC10H680      | 4-Bit Differential ECL Bus to TTL Bus Transceiver           |       |

| MC10H681      | Hex ECL-TTL Transceiver with Latches                        | 2-163 |

| MC100H600     | 9-Bit TTL-ECL Translator                                    |       |

| MC100H601     | 9-Bit ECL-TTL Translator                                    |       |

| MC100H602     | 9-Bit Latch/TTL-ECL Translator                              | 2-106 |

| MC100H603     | 9-Bit Latch/ECL-TTL Translator                              |       |

| MC100H604     | Registered Hex TTL/ECL Translator                           | 2-111 |

| Device Number | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| MC100H605     | Registered Hex ECL-to-TTL Translator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-113 |

| MC100H606     | Registered Hex TTL-to-PECL Translator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| MC100H607     | Registered Hex PECL-to-TTL Translator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| MC100H640     | 68030/68040 ECL/TTL Clock Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| MC100H641     | Single Supply PECL ≥ TTL 1:9 Clock Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| MC100H642     | 68030/68040 ECL/TTL Clock Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-133 |

| MC100H643     | Dual Supply ECL-TTL 1:8 Clock Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| MC100H644     | 68030/68040 ECL/TTL Clock Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| MC100H646     | PECL/TTL-TTL 1:8 Clock Distribution Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| WIG 100110-10 | TEODITE THE TO GOOK BIOKINGKION ONLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| MC100H660     | 4-Bit ECL-TTL Load Reducing DRAM Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-151 |

| MC100H680     | 4-Bit Differential ECL Bus to TTL Bus Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| MC100H681     | Hex ECL-TTL Transceiver with Latches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| MC1648        | Voltage-Controlled Multivibrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

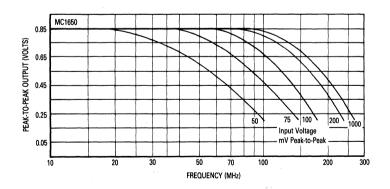

| MC1650        | Dual A/D Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| WIO 1000      | Buai AVB Conventor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7 11  |

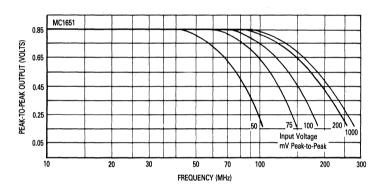

| MC1651        | Dual A/D Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-11  |

| MC1658        | Voltage-Controlled Multivibrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| MC1660        | Dual 4-Input Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| MC1662        | Quad 2-Input "OR/NOR" Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| MC1670        | Master-Slave Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| WICTOTO       | Master-Olave i lip-i lop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7 20  |

| MC1672        | Triple 2-Input Exclusive-OR Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-29  |

| MC1690        | UHF Prescaler Type D Flip-Flop (Obsolete)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| 11101000      | Substitute MC12090                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| MC1692        | Quad Line Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

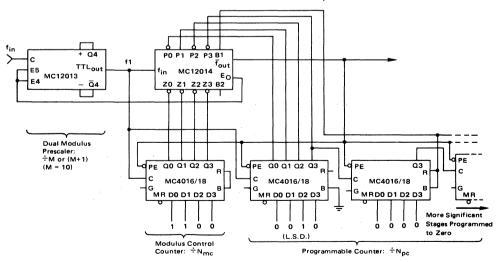

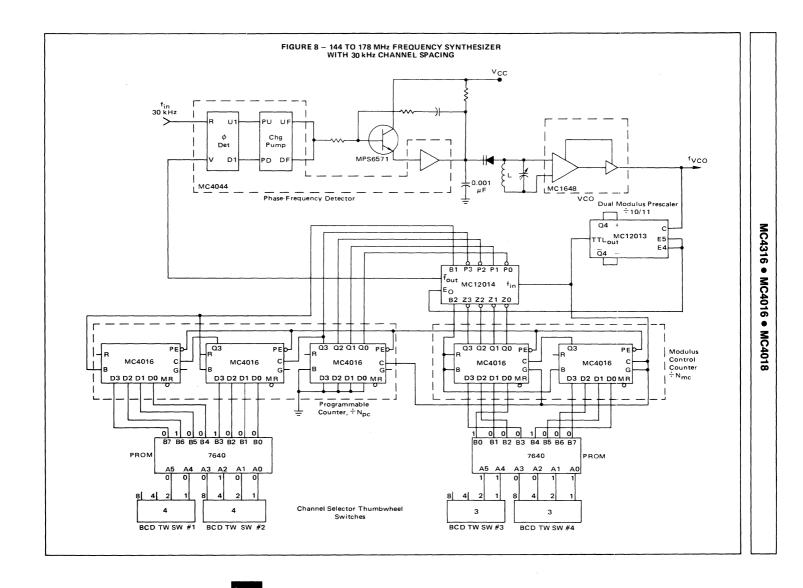

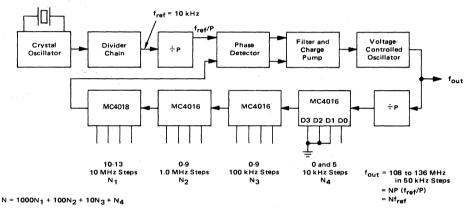

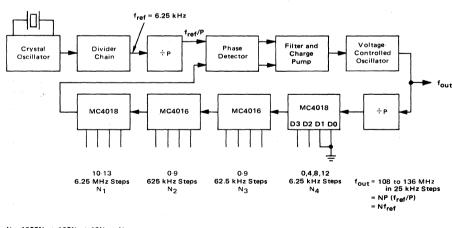

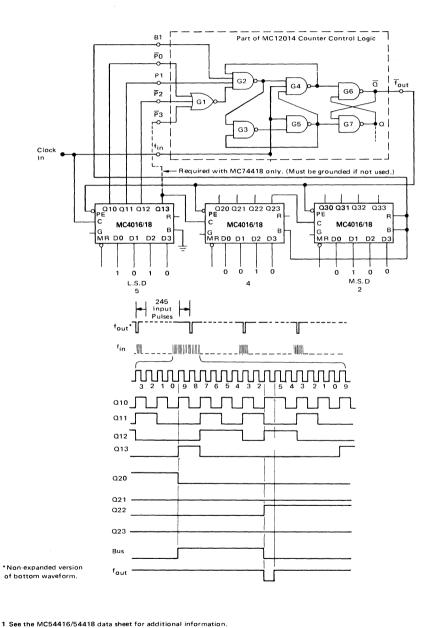

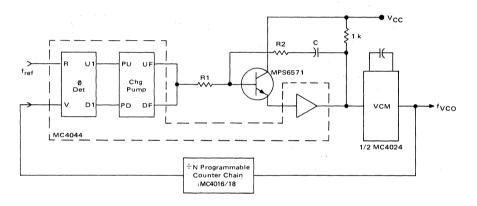

| MC4016        | Programmable Modulo-N Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

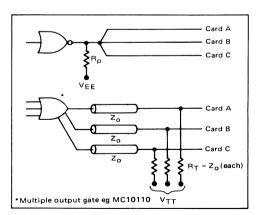

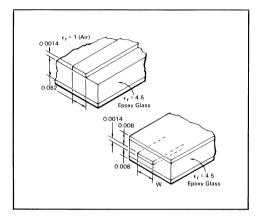

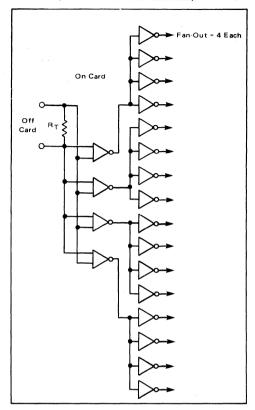

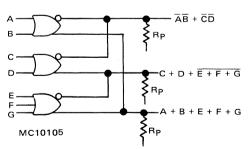

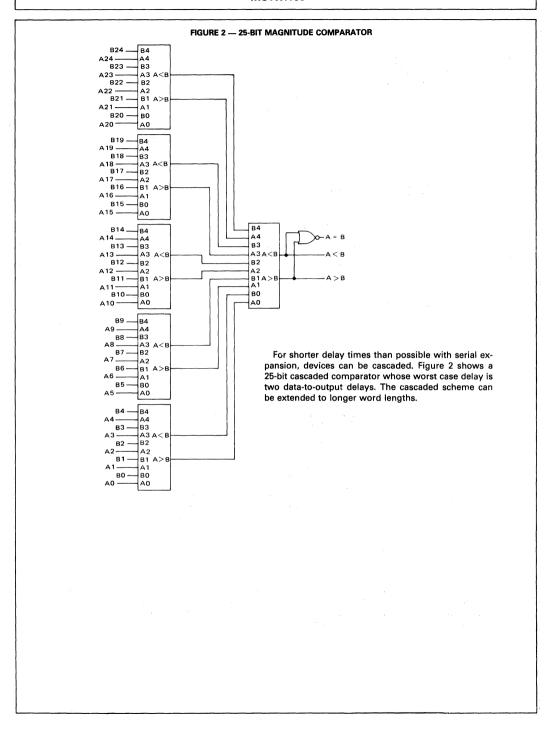

| MC4018        | Programmable Modulo-N Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |