# MOTOROLA SEMICONDUCTOR

# **Designers Data Sheet**

## HORIZONTAL DEFLECTION TRANSISTOR

$\ldots$  specifically designed for use in large screen color deflection circuits.

- Collector-Emitter Voltage V<sub>CEX</sub> = 1300 Vdc – BU207 1500 Vdc – BU208

- Collector-Emitter Sustaining Voltage VCEO(sus) = 600 Vdc – BU207 700 Vdc – BU208

- Switching Times with Inductive Loads, t\_f = 0.4  $\mu s$  (Typ) @ I\_C = 4.5 A

- Optimum Drive Condition Curves

- Glass Base-Collector Junction

| Rating                                                       | Symbol                | BU207       | BU208 | Unit |

|--------------------------------------------------------------|-----------------------|-------------|-------|------|

| Collector-Emitter Voltage                                    | V <sub>CEO(sus)</sub> | 600         | 700   | Vdc  |

| Collector-Emitter Voltage                                    | VCEX                  | 1300 1500   |       | Vdc  |

| Emitter Base Voltage                                         | VEB                   | 5           |       | Vdc  |

| Collector Current – Continuous                               | IC IC                 | 5           |       | Adc  |

| Peak (1)                                                     | Ісм                   | 7.5         |       |      |

| Base Current - Peak (1)                                      | <sup>1</sup> BM       | 4           | 4     | Adc  |

| Total Power Dissipation @ T <sub>C</sub> = 95 <sup>0</sup> C | PD                    | 12          | .5    | Watt |

| Derate above 95°C                                            | 1                     | 0.625       |       | W/°C |

| Operating and Storage Junction                               | TJ, Tstg              | -65 to +115 |       | °C   |

| Temperature Range                                            |                       |             |       |      |

| THERMAL CHARACTERISTICS                                      |                       |             |       |      |

| Characteristic                                               | Symbol                | M           | ax    | Unit |

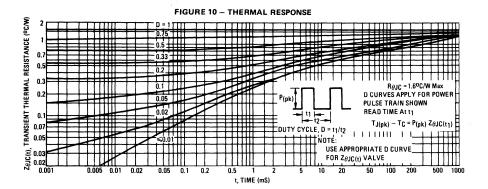

| Thermal Resistance, Junction to Case                         | RØJC                  | 1.6         |       | °C/W |

| Maximum Lead Temperature for Soldering                       | TL                    | 275         |       | °C   |

| Purposes: 1/8" from Case for 5 Seconds                       | 1 -                   | 1           |       | í    |

# 5 AMPERE NPN SILICON POWER TRANSISTORS

**BU207**

**BU208**

1300 AND 1500 VOLTS

### Designer's Data for "Worst Case" Conditions

The Designers Data Sheet permits the design of most circuits entirely from the information presented. Limit data – representing device characteristics boundaries – are given to facilitate "worst case" design.

3

3

| Characteristic                               |                                               |         | Symbol    | Min           | Тур                | Max | Unit |

|----------------------------------------------|-----------------------------------------------|---------|-----------|---------------|--------------------|-----|------|

| OFF CHARAC                                   | TERISTICS (1)                                 |         |           |               |                    |     |      |

|                                              | ter Sustaining Voltage                        | BU207   | VCEO(sus) | 600           | 1997 <u>-</u> 1997 |     | Vdc  |

| (I <sub>C</sub> = 100 m                      | nAdc, I B = 0)                                | BU208   | 1         | 700           |                    | -   |      |

| Collector Cuto                               | ff Current                                    |         | ICES      |               |                    |     | mAdc |

|                                              | 00 Vdc, V <sub>BE</sub> = 0)                  | BU207   |           | -             | -                  | 1.0 |      |

| (V <sub>CE</sub> = 150                       | 00 Vdc, V <sub>BE</sub> = 0)                  | BU208   |           | -             | -                  | 1.0 |      |

| Emitter Base V                               | oltage                                        |         | VEBO      | 5.0           | / . —              | -   | Vdc  |

| (IE = 10 m/                                  | A, IC = 0)                                    | ×       |           |               |                    |     |      |

| ON CHARACT                                   | TERISTICS (1)                                 |         |           |               |                    |     |      |

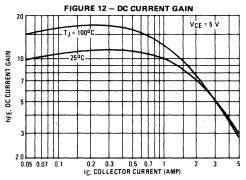

| DC Current Gain                              |                                               | hfe     | 2.25      | · _           | -                  | -   |      |

| (I <sub>C</sub> = 4.5 A                      | dc, V <sub>CE</sub> = 5 Vdc)                  |         |           |               |                    |     |      |

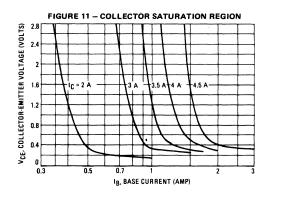

| Collector-Emitter Saturation Voltage         |                                               |         | VCE(sat)  | -             | _                  | 5   | Vdc  |

| (IC = 4.5 Adc, IB = 2 Adc)                   |                                               |         |           |               |                    |     |      |

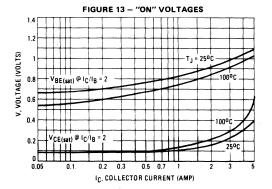

| Base Emitter Saturation Voltage              |                                               |         | VBE(sat)  | -             | -                  | 1.5 | Vdc  |

| (I <sub>C</sub> = 4.5 A                      | dc, IB = 2 Adc)                               |         |           |               |                    |     |      |

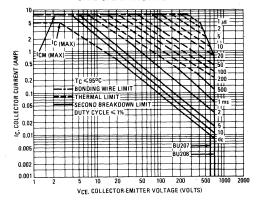

| Second Breakdown Collector Current with Base |                                               | IS/b    |           | See Figure 14 |                    |     |      |

| Forward Bi                                   | ased                                          | •       |           |               |                    |     |      |

| NAMIC CHAP                                   | ACTERISTICS                                   |         |           |               |                    |     |      |

| Current-Gain — Bandwidth Product             |                                               | fT      |           | 4.0           | -                  | MHz |      |

| (I <sub>C</sub> = 0.1 Ad                     | dc, VCE = 5.0 Vdc, f <sub>test</sub> =        | 1 MHz)  |           |               |                    |     |      |

| Output Capacitance                           |                                               | Cob     |           | 125           | -                  | pF  |      |

| (V <sub>CB</sub> = 10 \                      | /dc, i = 0, f = 0.1 MHz)                      |         | 1         |               |                    |     |      |

| SWITCHING C                                  | HARACTERISTICS                                |         |           |               |                    |     |      |

| Fall Time                                    | (I <sub>C</sub> = 4.5 Adc, I <sub>B</sub> = 1 | .8 Adc. |           |               |                    |     |      |

|                                              | LR = 10 µH, see Figu                          |         | tf        | -             | 0.6                | -   | μs   |

ELECTRICAL CHARACTERISTICS (T<sub>C</sub> = 25<sup>o</sup> unless otherwise noted.)

(1) Pulse Test: Pulse Width = 300  $\mu$ s, Duty Cycle < 2%.

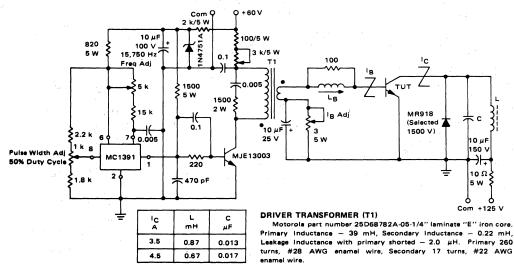

#### FIGURE 1 -- SWITCHING TIMES TEST CIRCUIT

#### BASE DRIVE: The Key to Performance

By now, the concept of controlling the shape of the turn-off base current is widely accepted and applied in horizontal deflection design. The problem stems from the fact that good saturation of the output device, prior to turn-off, must be assured. This is accomplished by providing more than enough  $I_{B1}$  to satisfy the lowest gain output device  $h_{FE}$  at the end of scan  $I_{CM}$ . Worst-case component variations and maximum high voltage loading must also be taken into account.

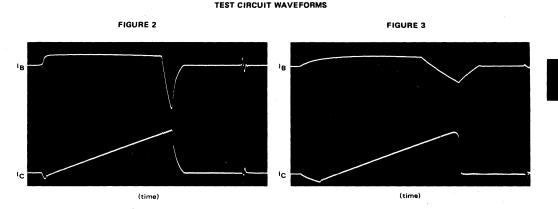

If the base of the output transistor is driven by a very low impedance source, the turn-off base current will reverse very quickly as shown in Figure 2. This results in rapid, but only partial, collector turn-off, because excess carriers become trapped in the high resistivity collector and the transistor is still conductive. This is a high dissipation mode, since the collector voltage is rising very rapidly. The problem is overcome by adding inductance to the base circuit to slow the base current reversal as shown in Figure 3, thus allowing excess carrier recombination in the collector to occur while the base current is still flowing.

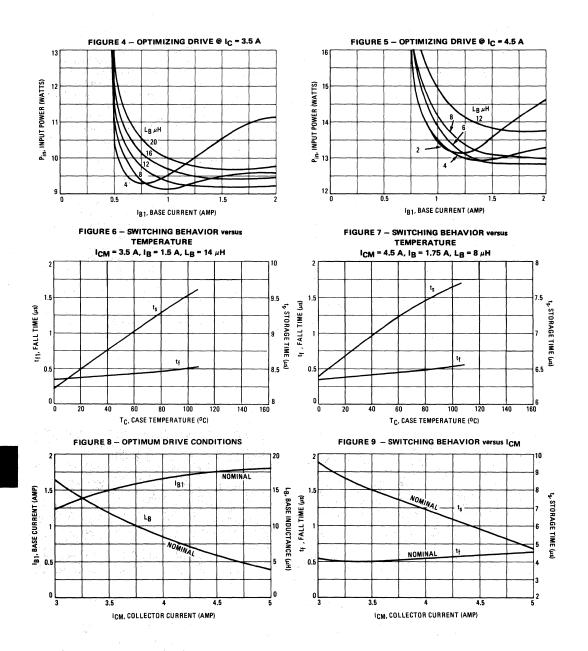

Choosing the right L<sub>B</sub> is usually done empirically, since the equivalent circuit is complex, and since there are several important variables ( $I_{CM}$ ,  $I_{B1}$ , and  $h_{FE}$  at  $I_{CM}$ ). One method is to plot fall time as a function of L<sub>B</sub>, at the desired conditions, for several devices within the  $h_{FE}$ specification. A more informative method is to plot power dissipation versus  $I_{B1}$  for a range of values of L<sub>B</sub> as shown

in Figures 4 and 5. This shows the parameter that really matters, dissipation, whether caused by switching or by saturation. The negative slope of these curves at the left (low I<sub>B1</sub>) is caused by saturation losses. The positive slope portion at higher IB1, and low values of LB is due to switching losses as described above. Note that for very low L<sub>B</sub> a very narrow optimum is obtained. This occurs when IB1 hFE = ICM, and therefore would be acceptable only for the "typical" device with constant ICM. As LB is increased, the curves become broader and flatter above the IB1 hFE = ICM point as the turn-off "tails" are brought under control. Eventually, if LB is raised too far, the dissipation all across the curve will rise, due to poor initiation of switching rather than tailing. Plotting this type of curve family for devices of different hFE, essentially moves the curves to the left or right according to the relation IB1 hFE = constant. It then becomes obvious that, for a specified  $I_{CM}$ , an  $L_B$  can be chosen which will give low dissipation over a range of her and/or IB1. The only remaining decision is to pick IB1 high enough to accommodate the lowest hFE part specified. Figure 8 gives values recommended for LB and IB1 for this device over a wide range of ICM. These values were chosen from a large number of curves like Figure 4 and Figure 5. Neither LB nor IB1 are absolutely critical, as can be seen from the examples shown, and values of Figure 8 are provided for guidance only.

TEST CIRCUIT OPTIMIZATION

The test circuit may be used to evaluate devices in the conventional manner, i.e., to measure fall time, storage time, and saturation voltage. However, this circuit was designed to evaluate devices by a simple criterion, power supply input. Excessive power input can be caused by a variety of problems, but it is the dissipation in the transistor that is of fundamental importance. Once the required transistor operating current is determined, fixed circuit values may be selected from the table. Factory testing is performed by reading the current meter only, since the input power is proportional to current. No adjustment of the test apparatus is required.

3

FIGURE 14 MAXIMUM FORWARD BIAS SAFE OPERATING AREA

3