1984 LINEAR SUPPLEMENT DATABOOK

# NATIONAL SEMICONDUCTOR CORPORATION

# LINEAR SUPPLEMENT

# DATABOOK

Amplifiers Comparators **Voltage Regulators Voltage References** Converters **Analog Switches** Sample and Hold Sensors **Filters Building Blocks Motor Controllers Consumer Circuits Telecommunications Circuits** Speech **Special Analog Functions Physical Dimensions**

#### TRADEMARKS

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

Abuseable™ Anadig<sup>™</sup> ANS-R-TRAN™ Auto-Chem Deflasher™ BI-FETTM BI-FET II™ **BI-LINE™ BIPLANTM** BLC/BLX™ СІМ™ CIMBUS™ COPS™ microcontrollers **DATACHECKER® DENSPAKTM** DIBTM **DIGITALKER® DISCERN™ DNRTM DPVMTM** F-7-I INKTM GENIX™ HEX 3000™ **INFOCHEX™** Integral ISE™ Intelisplay™

ISE™ ISE/16™ Macrobus™ Macrocomponent<sup>™</sup> Maxi-ROM® Meatr Chek™ Microbus™ data bus (adjective) MICRO-DAC™ utalker™ Microtalker™ **MICROWIRE™ MICROWIRE PLUS™ MST**<sup>™</sup> Nitride Plus™ Nitride Plus Oxide™ **NML™** NSC800™ NS16000™ NSX-16™ NSCX-16™ NURAMTM **OXISS™** Perfect Watch™ Pharmar/Chek™ **PLAN™** Polycraft™

POSitalker™ QUAD3000™ BATTM Script//Chek™ Shelf-Chek™ SERIES/800™ **SPIRE™** Starlink™ **STARPLEX™** STARPLEX IITM SuperChip™ SYS-16™ **TAPE-PAK™** TDSTM The National Anthem™ Timer Chek™ Trapezoidal™ TRI-CODE™ TRI-POLY™ TRI-SAFE™ TRI-STATE® **XMOS™ XPUTM** Z STAR™ 883B/RETS™ 883S/RETS™

Teflon® is a registered trademark of Dupont Corp. Dolby® is a registered trademark of Dolby Labs. Intellec® and MULTIBUS® are registered trademarks of Intel Corp. MULTIMODULE™ is a trademark of Intel Corp. Z80® is a registered trademark of Zilog Corp. CX™ is a trademark of CBS Labs.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, Santa Clara, California 95051 (408) 721-5000 TWX (910) 339-9240 National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

#### Introduction

The 1984 Linear Supplement provides the most recent information available on National's new linear products. This supplement also provides a comprehensive index of product listings published in the master databook. New products described herein are indicated by an asterisk and bold type. Revised datasheets are listed in bold type. National's master/supplement databook system allows you to make product selections based on your knowledge of our latest product offerings.

This supplement edition presents approximately 500 pages of specifications. It includes applications, descriptions, features, and diagrams of voltage regulators; op amps; voltage comparators; A/D and D/A converters; industrial building blocks; audio, radio, and TV circuits; advanced telecommunications devices; and DIGITALKER® speech synthesis circuits, as well as other analog products. National's linear products offer economy, quality, and reliability. For further information on any of our new products, contact your National Semiconductor sales representative.

#### Einleitung

Der Ergänzungsband Lineare Produkte 1984 enthält die aktuellsten Informationen über Nationals neue lineare Produkte. Dieser Zusatzband bietet ebenfalls ein umfassendes Verzeichnis aller Produktaufstellungen, die im Hauptdatenbuch enthalten sind. Hier beschriebene neue Produkte sind in Fettdruck, mit ein \*. Überarbeitete Datenblätter sind in Fettdruck aufgeführt. National-Datenbücher - Hauptbände und Zusatzbände - geben Ihnen die Möglichkeit, Ihre Produktwahl gemäß unserer jüngsten Produktangebote zu treffen.

Die vorliegende Ergänzungsausgabe umfaßt etwa 500 Seiten Spezifikationen. Sie enthält Angaben zu Anwendungen, Beschreibungen, Zusätzen und Diagramme von Spannungsreglern, op amps, Spannungsvergleicher, A/D- und D/A-Wandler, industrielle Bausteine, Audio-, Rundfunk- und Fernsehschaltungen, neueste Telecombauteile, DIGITALK-ER®- Sprachsynthese-Schaltungen sowie andere analoge Produkte. Nationals lineare Produkte sind kostengünstig, von hoher Qualität und zuverlässig. Sollten Sie weitere Informationen über unsere neuen Produkte wünschen, setzen Sie Sich bitte mit Ihrem National Semiconductor-Vertreter in Verbindung.

#### Introduction

Afin de permettre à sa clientèle une mise à jour plus facile, National Semiconductor propose en plus de sa documentation classique un Additif Linéaire 1984. Ce dernier comporte les informations les plus récentes sur les produits nouvellement sortis ainsi qu'un index récapitulatif de ceux déjà exposés dans le livre principal.

Les produits nouveaux qu'il comporte sont signales par une astérisque et des caractères gras. Les fiches techniques mises a jour sont imprimées en caractère gras. Ce nouveau systême a pour but d'orienter la clientèle sur les produits les plus récents.

L'edition supplémentaire contient à peu près 500 pages de specifications. Elle comprend possibilités d'application, descriptions, unités supplémentaires, courbes caracteristiques de regulateurs de tension, op amps, comparateurs de tension, convertisseurs A/D et D/A, modules industriels, circuits audio, radio et TV, dispositifs avancés de télecommunication, circuits de synthèse de parole Digitalker, ainsi que d'autres produits analogiques. Les produits linéaires de National sont économiques, de haute qualite et fiables. Si vous désirez des renseignements supplémentaires sur nos produits nouveaux, veuillez vous adresser a votre représentant local de National Semiconductor.

#### Introduzione

Il supplemento 1984 al catalogo "LINEAR" della National fornisce le più aggiornate informazioni sui nuovi prodotti lineari. Questo supplemento presenta, inoltre, un indice completo di tutti i prodotti che sono pubblicati sul catalogo principale. I nuovi prodotti descritti nel supplemento sono caratterizzati in neretto, con una \*.

I fogli tecnici (datasheets) corretti sono pubblicati in neretto. Il sistema catalogo principale/supplemento permette una perfetta scelta dei prodotti, grazie alle più recenti ed aggiornate informazioni disponibili sugli stessi.

Questo supplemento presenta circa 500 pagine di specifiche. Esso comprende applicazioni, descrizioni, caratteristiche e diagrammi su: regolatori di tensione, amplificatori operazionali, convertitori A/D e D/A, circuiti dedicati per sistemi industriali, circuiti audio e radio/TV, dispositivi avanzati per telecomunicazioni, circuiti per la sintesi del parlato DIGI-TALKER oltre a numerosi altri.

I prodotti lineari della National Semiconductor offrono qualità, affidabilità e soluzioni economiche.

Per ulteriori informazioni sui prodotti elencati Vi preghiamo di contattare il nostro ufficio vendite più vicino.

## **Table of Contents**

Devices listed in Boldface are included in this supplement with changes. Devices listed in Boldface with an asterisk (\*) are new parts.

| Buffer Amplifiers                                                               |        |

|---------------------------------------------------------------------------------|--------|

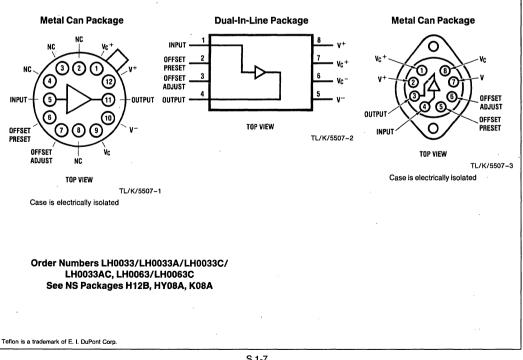

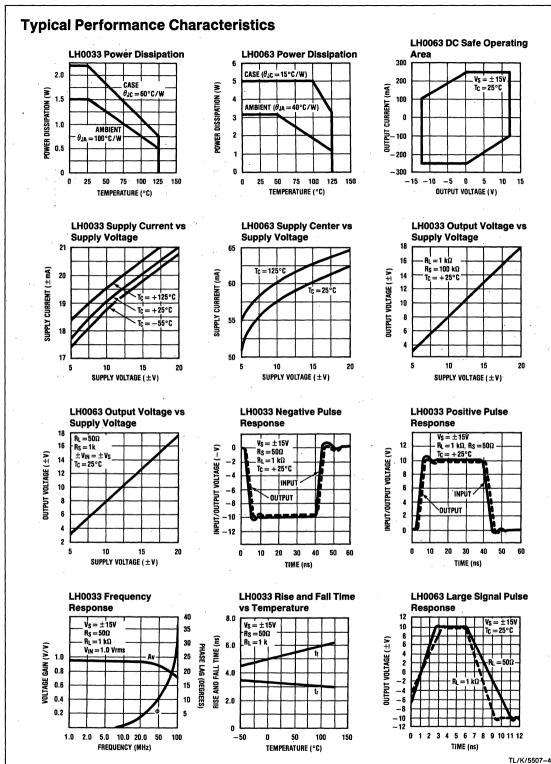

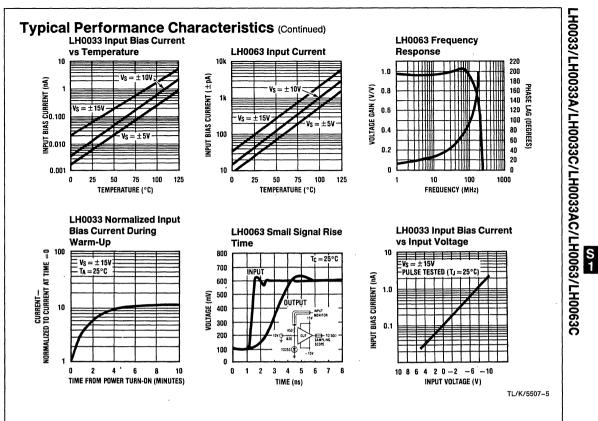

| LH0033/LH0033A, LH0033C/LH0033AC, LH0063/LH0063C Fast and Damn Fast             |        |

| Buffer Amplifiers                                                               | S 1-7  |

| Combined Functions                                                              |        |

| LM10/LM10B(L)/LM10C(L) Op Amp and Voltage Reference                             | 3-99   |

| Instrumentation Amplifiers                                                      |        |

| LH0036/LH0036C Instrumentation Amplifier                                        | 4-18   |

| LH0038/LH0038C True Instrumentation Amplifier                                   | 4-26   |

| LH0084/LH0084C Digitally Programmable Gain Instrumentation Amplifier            | 4-37   |

| LH0086/LH0086C Digitally Programmable Gain Amplifier                            | 3-364  |

| LM121/LM221/LM321, LM121A/LM221A/LM321A Precision Preamplifiers                 | 4-5    |

| LM163/LM363 Precision Instrumentation Amplifier                                 | S 1-24 |

| LM725/LM725A/LM725C (Instrumentation) Operational Amplifier                     | 3-253  |

| Operational Amplifiers                                                          |        |

| LF147/LF347 Wide Bandwidth JFET Input Operational Amplifier                     | 3-14   |

| LF155/LF156/LF157 Series Monolithic JFET Input Operational Amplifiers           | 3-22   |

| LF351 Wide Bandwidth JFET Input Operational Amplifier                           | 3-35   |

| LF353 Wide Bandwidth Dual JFET Input Operational Amplifier                      | 3-42   |

| LF400C Fast Settling JFET Input Operational Amplifier                           | 3-51   |

| LF411A/LF411 Low Offset, Low Drift JFET Input Operational Amplifier             | 3-53   |

| LF412A/LF412 Low Offset, Low Drift Dual JFET Input Operational Amplifier        | 3-60   |

| LF441A/LF441 Low Power JFET Input Operational Amplifier                         | 3-66   |

| LF442A/LF442 Dual Low Power JFET Input Operational Amplifier                    | 3-73   |

| LF444A/LF444 Quad Low Power JFET Input Operational Amplifier                    | 3-81   |

| LF13741 Monolithic JFET Input Operational Amplifier                             | 3-88   |

| LH0003/LH0003C Wide Bandwidth Operational Amplifier                             | 3-294  |

| LH005/LH005A Operational Amplifier                                              | 3-299  |

| LH005C Operational Amplifier                                                    | 3-302  |

| LH0021/LH0021C 1.0 Amp Power Operational Amplifier                              | 3-304  |

| LH0022/LH0022C High Performance FET Op Amp                                      | 3-311  |

| LH0024/LH0024C High Slew Rate Operational Amplifier                             | 3-318  |

| LH0032, LH0032A, LH0032C, LH0032AC Ultra Fast FET-Input Operational Amplifier   | S 1-1  |

| LH0041/LH0041C 0.2 Amp Power Operational Amplifier                              | 3-304  |

| LH0042/LH0042C Low Cost FET Op Amp                                              | 3-311  |

| LH0044 Series Precision Low Noise Operational Amplifiers                        | 3-338  |

| LH0045/LH0045C Two Wire Transmitter                                             | 3-344  |

| LH0052/LH0052C Precision FET Op Amp                                             | 3-311  |

| LH0061/LH0061C 0.5 Amp Wide Band Operational Amplifier                          | 3-555  |

| LH0062/LH0062C High Speed FET Operational Amplifier                             | 3-358  |

| LH0101/LH0101C, LH0101A/LH0101AC Power Operational Amplifier                    | 3-382  |

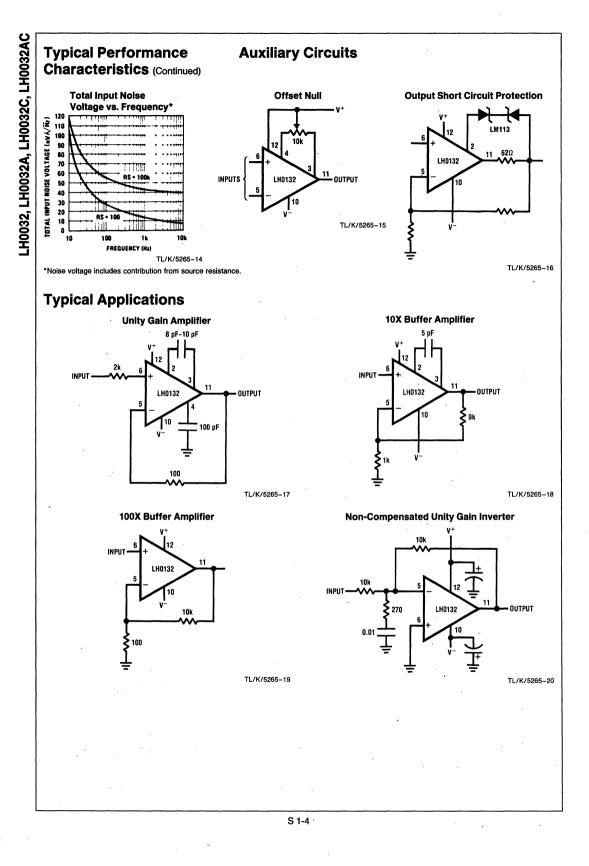

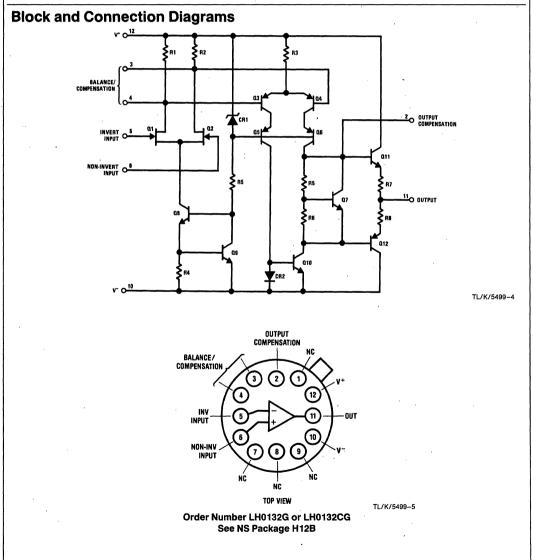

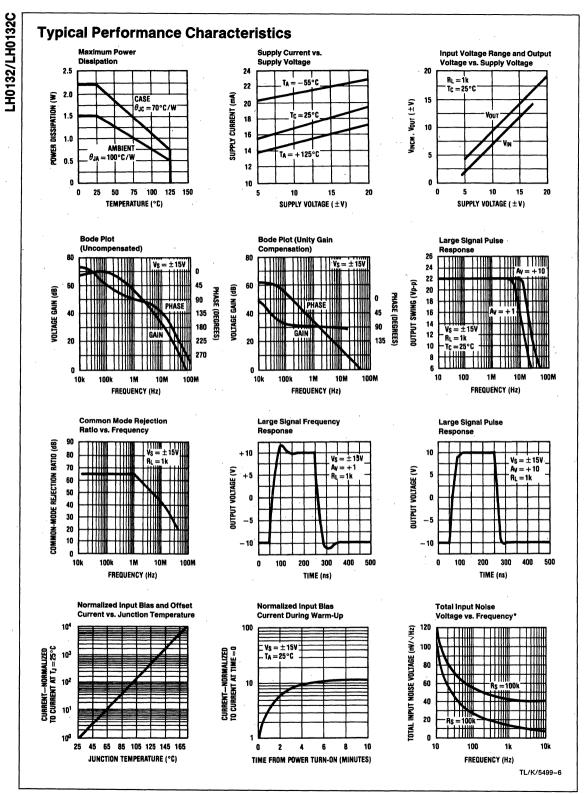

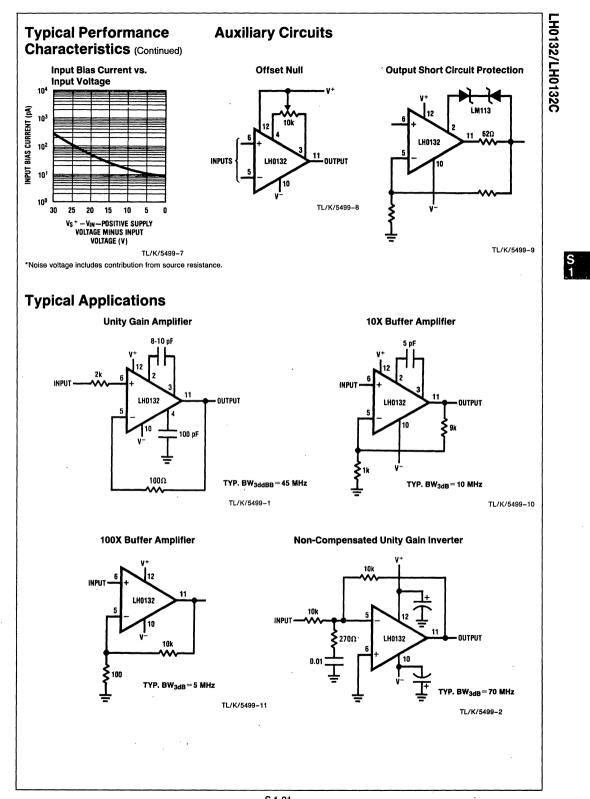

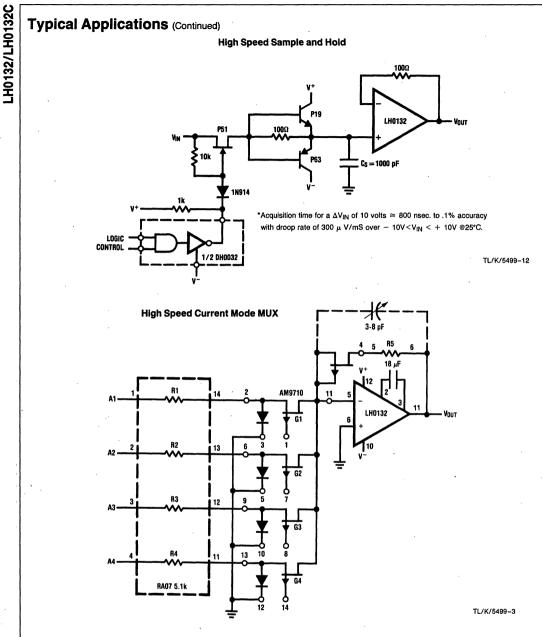

| *LH0132, LH0132C Ultra-Fast FET-Input Operational Amplifier Featuring Low Input |        |

| Bias Current over ± 10V Input Range                                             | S 1-18 |

| LH740A/LH740AC FET Input Operational Amplifier                                  | 3-382  |

| LH2011/LH2011B/LH2011C Dual Operational Amplifiers                              | 3-384  |

| LH2101A/LH2201A/LH2301A Dual High Performance Op Amp                            | 3-397  |

| LH2108/LH2208/LH2308, LH2108A/LH2208A/LH2308A Dual Super Beta Op Amp            | 3-399  |

| LH24250/LH24250C Dual Programmable Micropower Op Amp                            | 3-403  |

| LM11/LM11C/LM11CL Operational Amplifiers                                        | 3-115  |

| LM101A/LM201A/LM301A Operational Amplifiers                                     | 3-128  |

| LM107/LM207/LM307 Operational Amplifiers                                        | 3-140  |

| LM108/LM208/LM308 Operational Amplifiers                                        | 3-144  |

|                                                                                 |        |

### **SECTION I - AMPLIFIERS**

| Table of Contents (Continued)                                                                          |        |

|--------------------------------------------------------------------------------------------------------|--------|

| LM108A/LM208A/LM308A, LM308A-1, LM308A-2 Operational Amplifiers                                        | 3-149  |

| LM112/LM212/LM312 Operational Amplifiers                                                               | 3-161  |

| LM118/LM218/LM318 Operational Amplifiers                                                               | 3-165  |

| LM110/LM210/LM310 Operational Amplifiers                                                               | 0-100  |

| Operational Amplifiers                                                                                 | 3-172  |

| LM143/LM343 High Voltage Operational Amplifiers                                                        | 3-181  |

| LM140/LM344 High Voltage, High Slew Rate Operational Amplifier                                         | 3-188  |

| LM144/LM344 High Voltage, High Slew Hale Operational Amplifiers                                        | 3-100  |

| LM140/LM240/LM340 Programmable Quad Operational Ampliners                                              | 3-194  |

| LM148, LM149 Series Guad 741 Op Amps<br>LM158/LM258/LM358, LM158A/LM258A/LM358A, LM2904 Low Power Dual | 3-200  |

| Operational Amplifiers                                                                                 | ,      |

| Dual Operational Amplifiers                                                                            | 3-216  |

| LM216/LM316, LM216A/LM316A Operational Amplifiers                                                      | 3-216  |

| LM709/LM709A/LM709C Operational Amplifier                                                              | 3-240  |

|                                                                                                        |        |

| LM741/LM741A/LM741C/LM741E Operational Amplifier                                                       | 3-257  |

| LM747/LM747A/LM747C/LM747E Dual Operational Amplifiers                                                 |        |

| LM748/LM748C Operational Amplifier                                                                     | 3-265  |

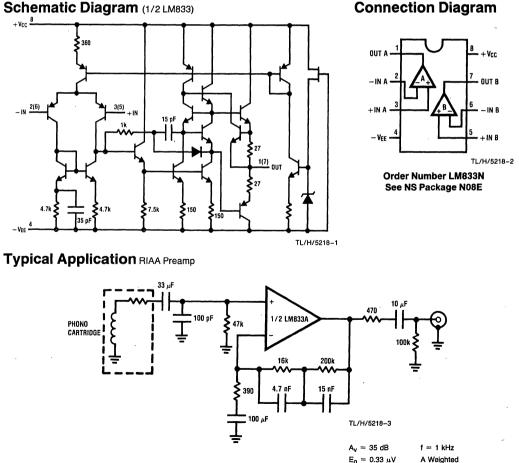

| *LM833 Dual Audio Operational Amplifier                                                                |        |

| LM1558/LM1458 Dual Operational Amplifier                                                               | 3-268  |

| LM2900/LM3900, LM3301, LM3401 Quad Amplifiers                                                          | 3-270  |

| LM3011 Wide Band Amplifier                                                                             | 10-216 |

| LM4250/LM4250C Precision Reference                                                                     | 3-279  |

| Power Amplifiers                                                                                       |        |

| LM377 Dual 2 Watt Audio Amplifier                                                                      | 10-9   |

| LM378 Dual 4 Watt Audio Amplifier                                                                      | 10-14  |

| LM3379 Dual 6 Watt Audio Amplifier                                                                     | 10-18  |

| LM380 Audio Power Amplifier                                                                            | 10-22  |

| LM383/LM383A 8 Watt Audio Power Amplifier                                                              | 10-32  |

| LM384 5 Watt Audio Power Amplifier                                                                     | 10-36  |

| LM386 Low Voltage Audio Power Amplifier                                                                | 10-40  |

| LM388 1.5 Watt Audio Power Amplifier                                                                   | 10-47  |

| LM389 Low Voltage Audio Power Amplifier with NPN Transistor Array                                      | 10-52  |

| LM390 1 Watt Battery Operated Audio Power Amplifier                                                    | 10-59  |

| LM1877 Dual Power Audio Amplifier                                                                      | 10-167 |

| LM1895/LM2895 Audio Power Amplifier                                                                    | 10-179 |

| LM1896/LM2896 Dual Power Audio Amplifier                                                               | 10-184 |

| LM2002/LM2002A 8 Watt Audio Power Amplifier                                                            | 10-200 |

| LM2877 Dual 4 Watt Power Audio Amplifier                                                               | 10-204 |

| LM2878 Dual 5 Watt Power Audio Amplifier                                                               | 10-210 |

| LM13080 Programmable Power Op Amp                                                                      | 3-284  |

| TDA2003 Audio Power Amplifier                                                                          | 10-281 |

| Special Amplifiers                                                                                     |        |

| LH0002/LH0002C Current Amplifier                                                                       | 3-291  |

| LH004/LH004C High Voltage Operational Amplifier                                                        | 3-296  |

| LH2110/LH2210/LH2310 Dual Voltage Follower                                                             | 3-401  |

| LM102/LM202/LM302 Voltage Followers                                                                    | 3-135  |

| LM110/LM210/LM310 Voltage Follower                                                                     | 3-154  |

| LM3080/LM3080A Operational Transconductance Amplifier                                                  | 9-148  |

| LM13600/LM13600A/LM11600A Dual Operational Transconductance Amplifier with                             |        |

| Linearizing Diodes and Buffers                                                                         | 10-242 |

| LM13700/LM13700A/LM11700A Dual Operational Transconductance Amplifier with                             |        |

| Linearizing Diodes and Buffers                                                                         | 10-248 |

| Table of Contents       (Continued)         Video Amplifiers       LM159/LM359 Dual, High Speed, Programmable Current Mode (Norton) Amplifiers         LM733/LM733C Differential Video Amp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-226<br>9-54                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| SECTION 2 - COMPARATORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                        |

| Combined Function Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        |

| LM1801 Smoke Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9-73                                                                                                                                                   |

| Voltage Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                        |

| LF111/LF211/LF311 Voltage Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-5                                                                                                                                                    |

| LH2111/LH2211/LH2311 Dual Voltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-11                                                                                                                                                   |

| LM106/LM206/LM306 Voltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-13                                                                                                                                                   |

| LM111/LM211 Voltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-16                                                                                                                                                   |

| LM119/LM219/LM319 High Speed Dual Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-22                                                                                                                                                   |

| LM139/239/339, LM139A/239A/339A, LM2901, LM3302 Low Power Low Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

| Voltage Quad Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-27                                                                                                                                                   |

| LM160/LM260/LM360 High Speed Differential Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-35                                                                                                                                                   |

| LM161/LM261/LM361 High Speed Differential Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-38                                                                                                                                                   |

| LM192/LM292/LM392, LM2924 Low Power Operational Amplifier/Voltage Comparator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-242                                                                                                                                                  |

| LM193/LM293/LM393, LM193A/LM293A/LM393A, LM2903 Low Power Low Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

| Voltage Dual Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-41                                                                                                                                                   |

| LM311 Voltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-48                                                                                                                                                   |

| LM710/LM710C Voltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-56                                                                                                                                                   |

| LM711/LM711C Dual Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-59                                                                                                                                                   |

| LM1514/LM1414 Dual Differential Voltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-62                                                                                                                                                   |

| *LP165/LP365 Micropower Programmable Quad Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | S 2-1                                                                                                                                                  |

| *LP311 Voltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | S 2-9                                                                                                                                                  |

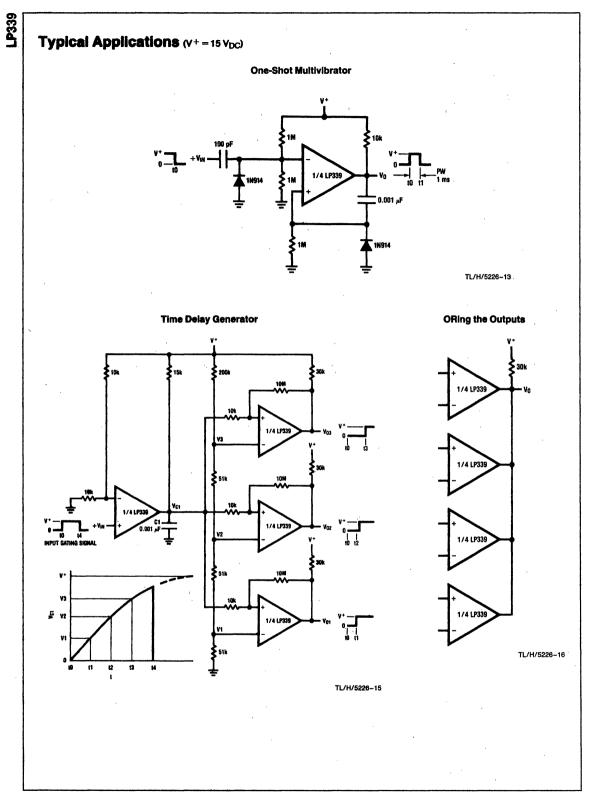

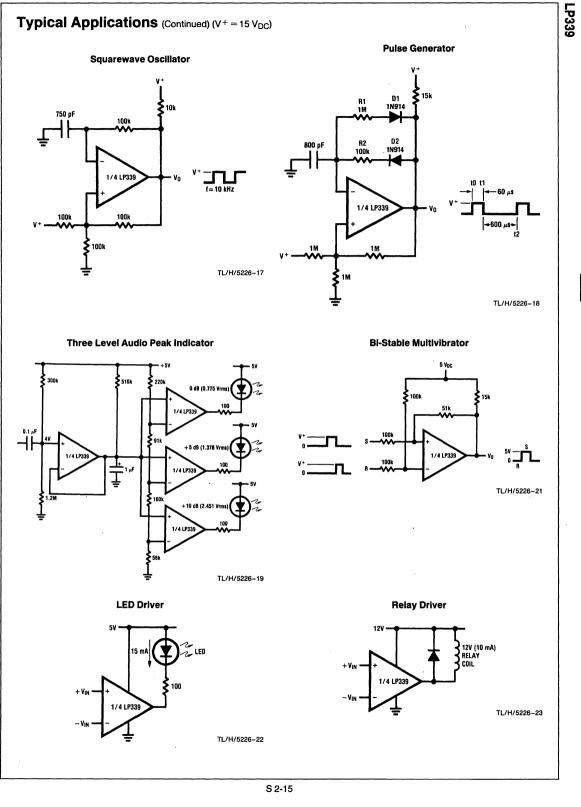

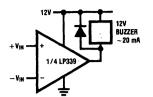

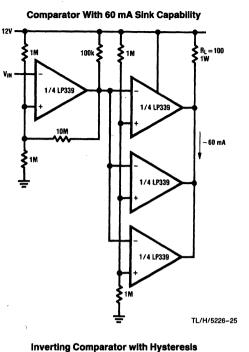

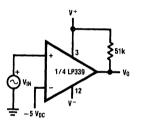

| *LP339 Ultra Low Power Quad Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | S 2-11                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                        |

| SPUTION 3 - VULLAGE BEGULATURS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                        |

| SECTION 3 - VOLTAGE REGULATORS Dual Tracking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                        |

| Dual Tracking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-51                                                                                                                                                   |

| Dual Tracking<br>LM125/LM325/LM325A, LM126/LM326 Voltage Regulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-51<br><b>S 3-13</b>                                                                                                                                  |

| Dual Tracking<br>LM125/LM325/LM325A, LM126/LM326 Voltage Regulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                        |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking         LM104/LM204/LM304 Negative Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | S 3-13                                                                                                                                                 |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>S 3-13</b><br>1-10                                                                                                                                  |

| Dual Tracking<br>LM125/LM325/LM325A, LM126/LM326 Voltage Regulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>S 3-13</b><br>1-10<br>1-13                                                                                                                          |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking         LM104/LM204/LM304 Negative Regulator         LM05/LM205/LM305/LM305A, LM376 Voltage Regulators         LM723/LM723C Voltage Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>S 3-13</b><br>1-10<br>1-13<br>1-143                                                                                                                 |

| Dual Tracking<br>LM125/LM325/LM325A, LM126/LM326 Voltage Regulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>S 3-13</b><br>1-10<br>1-13<br>1-143                                                                                                                 |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking         LM104/LM204/LM304 Negative Regulator         LM05/LM205/LM305/LM305A, LM376 Voltage Regulators         LM723/LM723C Voltage Regulator         Programmable Regulators         LH0075 Positive Precision Programmable Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>S 3-13</b><br>1-10<br>1-13<br>1-143<br>2-9                                                                                                          |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking         LM104/LM204/LM304 Negative Regulator         LM05/LM205/LM305/LM305A, LM376 Voltage Regulators         LM723/LM723C Voltage Regulator         Programmable Regulators         LH0075 Positive Precision Programmable Regulator         LH0076 Negative Precision Programmable Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>S 3-13</b><br>1-10<br>1-13<br>1-143<br>2-9                                                                                                          |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking         LM104/LM204/LM304 Negative Regulator         LM05/LM205/LM305/LM305A, LM376 Voltage Regulators         LM723/LM723C Voltage Regulator         Programmable Regulators         LH0075 Positive Precision Programmable Regulator         LH0076 Negative Precision Programmable Regulator         Switch Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>S 3-13</b><br>1-10<br>1-13<br>1-143<br>2-9<br>2-14                                                                                                  |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking         LM104/LM204/LM304 Negative Regulator         LM05/LM205/LM305/LM305A, LM376 Voltage Regulators         LM723/LM723C Voltage Regulator         Programmable Regulators         LH0075 Positive Precision Programmable Regulator         LH0076 Negative Precision Programmable Regulator         Switch Mode         LH1605/LH1605C 5 Amp High Efficiency Switching Regulator         LM1524/LM2524/LM3524 Regulating Pulse Width Modulator         3-Terminal                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>S 3-13</b><br>1-10<br>1-13<br>1-143<br>2-9<br>2-14<br>1-163                                                                                         |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking         LM104/LM204/LM304 Negative Regulator         LM05/LM205/LM305/LM305A, LM376 Voltage Regulators         LM723/LM723C Voltage Regulator         Programmable Regulators         LH0075 Positive Precision Programmable Regulator         LH0076 Negative Precision Programmable Regulator         Switch Mode         LH1605/LH1605C 5 Amp High Efficiency Switching Regulator         LM1524/LM3524 Regulating Pulse Width Modulator         3-Terminal         LM78XX Series Voltage Regulators                                                                                                                                                                                                                                                                                                                                                                                                  | <b>S 3-13</b><br>1-10<br>1-13<br>1-143<br>2-9<br>2-14<br>1-163                                                                                         |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking         LM104/LM204/LM304 Negative Regulator         LM05/LM205/LM305/LM305A, LM376 Voltage Regulators         LM723/LM723C Voltage Regulator         Programmable Regulators         LH0075 Positive Precision Programmable Regulator         LH0076 Negative Precision Programmable Regulator         Switch Mode         LH1605/LH1605C 5 Amp High Efficiency Switching Regulator         LM1524/LM2524/LM3524 Regulating Pulse Width Modulator         3-Terminal         LM78XX Series Voltage Regulators         LM78XX Series 3-Terminal Positive Regulators                                                                                                                                                                                                                                                                                                                                      | <b>S 3-13</b><br>1-10<br>1-13<br>1-143<br>2-9<br>2-14<br>1-163<br>1-148                                                                                |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking         LM104/LM204/LM304 Negative Regulator         LM05/LM205/LM305/LM305A, LM376 Voltage Regulators         LM723/LM723C Voltage Regulator         Programmable Regulators         LH0075 Positive Precision Programmable Regulator         LH0076 Negative Precision Programmable Regulator         Switch Mode         LH1605/LH1605C 5 Amp High Efficiency Switching Regulator         LM1524/LM2524/LM3524 Regulating Pulse Width Modulator         3-Terminal         LM78XX Series Voltage Regulators         LM78LXX Series 3-Terminal Positive Regulators         LM78MXX Series 3-Terminal Positive Regulators                                                                                                                                                                                                                                                                               | <b>S 3-13</b><br>1-10<br>1-13<br>1-143<br>2-9<br>2-14<br>1-163<br>1-148<br>1-181                                                                       |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking         LM104/LM204/LM304 Negative Regulator         LM05/LM205/LM305/LM305A, LM376 Voltage Regulators         LM723/LM723C Voltage Regulator         Programmable Regulators         LH0075 Positive Precision Programmable Regulator         LH0076 Negative Precision Programmable Regulator         Switch Mode         LH1605/LH1605C 5 Amp High Efficiency Switching Regulator         LM1524/LM2524/LM3524 Regulating Pulse Width Modulator         3-Terminal         LM78XX Series Voltage Regulators         LM78LXX Series 3-Terminal Positive Regulators         LM78MXX Series 3-Terminal Negative Regulators         LM79LXX Series 3-Terminal Negative Regulators                                                                                                                                                                                                                         | <b>S 3-13</b><br>1-10<br>1-13<br>1-143<br>2-9<br>2-14<br>1-163<br>1-148<br>1-181<br>1-181<br>1-184<br>1-190<br>1-193                                   |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking         LM104/LM204/LM304 Negative Regulator         LM05/LM205/LM305/LM305A, LM376 Voltage Regulators         LM723/LM723C Voltage Regulator         Programmable Regulators         LH0075 Positive Precision Programmable Regulator         LH0076 Negative Precision Programmable Regulator         LH0076 Negative Precision Programmable Regulator         LH1605/LH1605C 5 Amp High Efficiency Switching Regulator         LM1524/LM2524/LM3524 Regulating Pulse Width Modulator         3-Terminal         LM78XX Series Voltage Regulators         LM78LXX Series 3-Terminal Positive Regulators         LM78MXX Series 3-Terminal Negative Regulators         LM79LXX Series 3-Terminal Negative Regulators         LM79LXXAC Series 3-Terminal Negative Regulators                                                                                                                            | <b>S 3-13</b><br>1-10<br>1-13<br>1-143<br>2-9<br>2-14<br>1-163<br>1-148<br>1-181<br>1-184<br>1-184<br>1-190<br>1-193<br>1-198                          |

| Dual Tracking         LM125/LM325/LM325A, LM126/LM326 Voltage Regulators         *LM2935 Low Dropout Dual Regulator         Multi-Tracking         LM104/LM204/LM304 Negative Regulator         LM05/LM205/LM305/LM305A, LM376 Voltage Regulators         LM723/LM723C Voltage Regulator         Programmable Regulators         LH0075 Positive Precision Programmable Regulator         LH0076 Negative Precision Programmable Regulator         Switch Mode         LH1605/LH1605C 5 Amp High Efficiency Switching Regulator         LM1524/LM2524/LM3524 Regulating Pulse Width Modulator         3-Terminal         LM78XX Series Voltage Regulators         LM78LXX Series 3-Terminal Positive Regulators         LM78MXX Series 3-Terminal Negative Regulators         LM79LXX Series 3-Terminal Negative Regulators         LM79LXX Series 3-Terminal Negative Regulators         LM79LXX Series 3-Terminal Negative Regulators         LM79MXX Series 3-Terminal Negative Regulators         LM79MXX Series 3-Terminal Negative Regulators | <b>S 3-13</b><br>1-10<br>1-13<br>1-143<br>2-9<br>2-14<br>1-163<br>1-148<br>1-181<br>1-184<br>1-184<br>1-190<br>1-193<br>1-198<br>1-202                 |

| Dual Tracking<br>LM125/LM325/LM325A, LM126/LM326 Voltage Regulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>S 3-13</b><br>1-10<br>1-13<br>1-143<br>2-9<br>2-14<br>1-163<br>1-148<br>1-181<br>1-184<br>1-184<br>1-190<br>1-193<br>1-198<br>1-202<br>1-18         |

| Dual Tracking<br>LM125/LM325/LM325A, LM126/LM326 Voltage Regulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>S 3-13</b><br>1-10<br>1-13<br>1-143<br>2-9<br>2-14<br>1-163<br>1-148<br>1-181<br>1-184<br>1-184<br>1-190<br>1-193<br>1-198<br>1-202<br>1-18<br>1-23 |

| Dual Tracking<br>LM125/LM325/LM325A, LM126/LM326 Voltage Regulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>S 3-13</b><br>1-10<br>1-13<br>1-143<br>2-9<br>2-14<br>1-163<br>1-148<br>1-181<br>1-184<br>1-184<br>1-190<br>1-193<br>1-198<br>1-202<br>1-18         |

| Table of Contents (Continued)                                                                     |              |

|---------------------------------------------------------------------------------------------------|--------------|

| LM123/LM223/LM323 5 Volt Positive Regulator                                                       | 1-47         |

| LM137/LM327/LM337 3-Terminal Adjustable Negative Regulators                                       | 1-58         |

| LM137HV/LM237HV/LM337HV 3- Terminal Adjustable Negative Regulators (High                          |              |

|                                                                                                   | 1-63         |

| LM138/LM238/LM338 5 Amp Adjustable Power Regulators                                               | 1-68         |

| LM140A/LM140/LM340A/LM340 Series 3-Terminal Positive Regulators                                   | 1-76         |

| LM140L/LM340L Series 3-Terminal Positive Regulators                                               | 1-84<br>1-87 |

| LM145/LM345 Negative Three Amp Regulator                                                          | 1-67         |

| LM150/LM250/LM350 3 Amp Adjustable Power RegulatorLM196/LM396 10 Amp Adjustable Voltage Regulator | 1-91         |

| LM1967 LM396 TO Amp Adjustable Voltage Regulator                                                  | 1-99         |