# Errata

| Product Name: | 82C264 GUI Accelerator          |

|---------------|---------------------------------|

| Document:     | 82C264 Data Book                |

|               | (PN: 912-3000-030 Revision 1.0) |

| Date:         | July 24, 1995                   |

#### Page 12

The power and signal ground interface table on page twelve incorrectly lists the pin numbers for AGNDM and AGNDV. The correct numbers should be as shown:

| Pin Name | Pin                                                               | Туре | Description                                                               |  |  |  |

|----------|-------------------------------------------------------------------|------|---------------------------------------------------------------------------|--|--|--|

| AGNDM    | 45                                                                | GND  | Analog ground for the memory clock Phase Lock Loop (PLL).                 |  |  |  |

| AGNDV    | 111                                                               | GND  | nalog ground for the video clock PLL.                                     |  |  |  |

| AVDDV    | 113                                                               | PWR  | Analog power for the video clock PLL.                                     |  |  |  |

| GND      | 5, 19, 35,<br>62, 76,<br>85, 99,<br>106, 110,<br>120, 136,<br>154 | GND  | Ground pins.                                                              |  |  |  |

| RVDD     | 117                                                               | PWR  | Power for RAMDAC RAM.                                                     |  |  |  |

| VAA      | 121                                                               | PWR  | Power supply for the internal DAC of the RAMDAC. The voltage is 5V + 10%. |  |  |  |

| VGNDA    | 125                                                               | GND  | Analog ground for the DAC.                                                |  |  |  |

#### 3.1.5 Power and Signal Ground Interface

912-9000-001

# Addendum

Product Name:82C264 GUI ControllerDocument:Design Reference Manual (PN: 912-6000-002, Rev. 1.0)Date:June, 1995

The following changes should be made to the 82C264 GUI Controller Reference Design Manual, dated March, 1995.

## Page 1

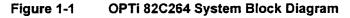

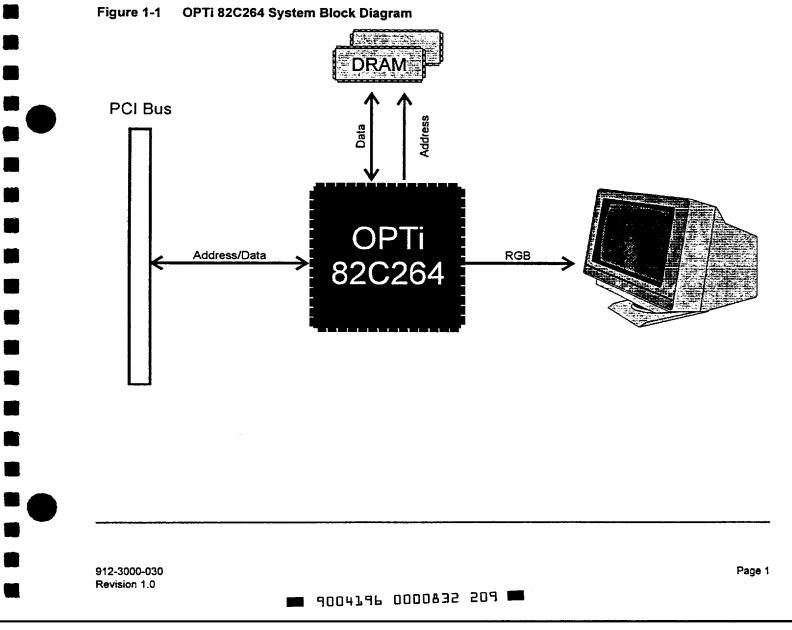

The System Block Diagram should be shown as follows:

## Page 4

----

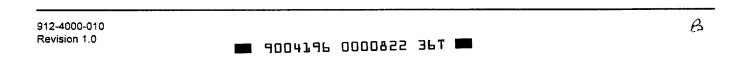

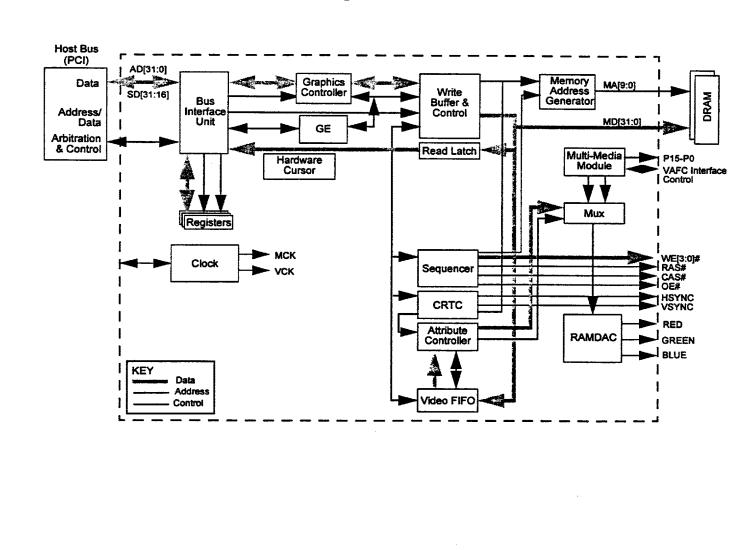

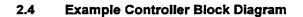

The PCI-Bus example controller block diagram should be shown as follows (changes are shown in circle):

## Page 5

Table 2-1 has the logical values for MD15 reversed. They should be listed as:

Table 2-1 MD31-MD0 Definitions at Reset

| MD   | Logical Level | Definition            |

|------|---------------|-----------------------|

| MD15 | 0             | Select dual WE# DRAM  |

|      | 1             | Select dual CAS# DRAM |

## Page 10

The description of CAS# in the Memory Interface section (3.1.2) should refer to signal MD15, not RAMCNF, being pulled low to change the function of this pin to WE# for display memory.

912-4000-010

## 🖬 9004196 0000823 2T6 📰

## Page 11

~

The description of WE3#-WE0# in the Memory Interface section (3.1.2) should be changed to the following:

| Pin Name      | Pin               | Туре | Description                                                                                                                                                                                                                                                               |

|---------------|-------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WE3#-<br>WE0# | 93, 82, 72,<br>59 | 0.   | DRAM Write Enables. When MD15 signal is pulled low, these pins are write enable signals for the display memory (for 256Kx4 or 256Kx16 dual WE DRAM). When MD15 signal is pulled high, these pins function as CAS# signals for display memory (for 256Kx16 dual CAS DRAM). |

### Page 18

Change the values for 800x600, 16M (24) to Yes in Table 4-2, CRT Display Resolutions.

#### Copyright

Copyright © 1994, OPTi Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of OPTi Incorporated, 2525 Walsh Avenue, Santa Clara, CA 95051.

#### Disclaimer

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

#### Trademarks

OPTi and OPTi Inc. are registered trademarks of OPTi Incorporated.

VESA is a trademark of the Video Electronic Standards Association (VESA). All other trademarks and copyrights are the property of their respective holders.

| 1.0 | Intro      | uction                                                                                                             |          |

|-----|------------|--------------------------------------------------------------------------------------------------------------------|----------|

| 2.0 | Featu      | res                                                                                                                |          |

|     | 2.1        | Features                                                                                                           | 2        |

|     | 2.2        | Benefits                                                                                                           |          |

|     | 2.3        | Architecture                                                                                                       |          |

|     | 2.4        | Example Controller Block Diagram                                                                                   |          |

|     |            | 2.4.1 Definitions of MD31-MD0 at System Reset                                                                      |          |

| 3.0 | Sign       | Descriptions                                                                                                       | -        |

| 0.0 | 3.1        |                                                                                                                    | ^        |

|     | 0.1        |                                                                                                                    | -        |

|     |            |                                                                                                                    | -        |

|     |            |                                                                                                                    | -        |

|     |            |                                                                                                                    | 2        |

|     |            | 2.4.5 Deven and Direct Occurrent Late for                                                                          | _        |

|     |            |                                                                                                                    |          |

|     |            | 3.1.6 Feature Connector Interface                                                                                  | 2        |

| 4.0 |            | iterface Unit                                                                                                      | 1        |

|     | 4.1        | Write Buffer and Control                                                                                           | 5        |

|     | 4.2        | Graphic Controller                                                                                                 | 5        |

|     | 4.3        | Memory Sequencer                                                                                                   | 5        |

|     | 4.4        | Video FIFO 1                                                                                                       | 5        |

|     | 4.5        | CRT Controller (CRTC) 18                                                                                           | 5        |

|     | 4.6        | Attribute Controller                                                                                               | 5        |

|     | 4.7        | GUI Engine                                                                                                         | 6        |

|     |            | 4.7.1 BitBLT                                                                                                       | 6        |

|     |            | 4.7.2 Color Expansion                                                                                              | 6        |

|     |            | 4.7.3 Fast Polygon Fill                                                                                            | 6        |

|     |            | 4.7.4 Area Fill                                                                                                    | 6        |

|     |            | 4.7.5 Line Draw                                                                                                    | 7        |

|     |            | 4.7.6 Short Stroke Vector Draw                                                                                     | 7        |

|     |            | 4.7.7 Rectangular Clipping                                                                                         | -        |

|     |            | 4.7.8 Raster Operations                                                                                            | _        |

|     | 4.8        | Hardware Cursor                                                                                                    | <u> </u> |

|     | 4.9        | RAMDAC                                                                                                             | -        |

|     | 4.10       | Clock Synthesizer                                                                                                  | -        |

|     | 4.11       | Multimedia Module                                                                                                  | -        |

|     |            | 4.11.1 Feature Connector                                                                                           | -        |

|     |            | 4.11.2 Genlock                                                                                                     |          |

|     |            | 4.11.3 Overlay                                                                                                     |          |

|     |            | 4.11.4 RAMDAC                                                                                                      | 9        |

| 5.0 | -          | er Description                                                                                                     | _ 2      |

|     | 5.1<br>5.2 | VGA Register Port Map                                                                                              |          |

|     |            | Standard VGA Register Tables                                                                                       |          |

|     | 5.3        | OPTi Register Tables                                                                                               |          |

|     | 5.4        | 82C264 GUI Engine Register Set                                                                                     |          |

|     |            | 5.4.1         Status/Start Register.         24           5.4.2         BitBLT Mode Register.         25           |          |

|     |            | 5.4.2         BitBLT Mode Register.         25           5.4.3         BitBLT Raster Operation Register         26 |          |

|     |            | 5.4.3 BIBLI Raster Operation Register                                                                              |          |

|     |            |                                                                                                                    | 0        |

|     |            |                                                                                                                    |          |

|     |            |                                                                                                                    |          |

|     |            |                                                                                                                    |          |

|     |            | n de la companya de l    |          |

.....

# **Table of Contents**

|     | 5.4.5<br>5.4.6<br>5.4.7<br>5.4.8<br>5.4.9<br>5.4.10<br>5.4.11<br>5.4.12<br>5.4.13 | Source Start X/Diagonal Step Constant Register27Source Start Y/Axial Step Constant Register27Destination Start X Register28Destination Start Y Register28BitBLT Width/Short Stroke Register28BitBLT Height Register29Error Term/Source Pitch Register29Foreground Color Register29Background Color Register30 |

|-----|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 5.4.14                                                                            |                                                                                                                                                                                                                                                                                                               |

|     | 5.4.15                                                                            | Clip Right Register                                                                                                                                                                                                                                                                                           |

|     | 5.4.16                                                                            | Clip Top Register                                                                                                                                                                                                                                                                                             |

|     | 5.4.17                                                                            | Clip Bottom Register                                                                                                                                                                                                                                                                                          |

| 5.5 |                                                                                   | Extended Registers                                                                                                                                                                                                                                                                                            |

|     | 5.5.1                                                                             | Unlock Extended Registers Register                                                                                                                                                                                                                                                                            |

|     | 5.5.2<br>5.5.3                                                                    | Mode Control Register                                                                                                                                                                                                                                                                                         |

|     | 5.5.3<br>5.5.4                                                                    | Clock Select Register       32         Video FIFO Control Register       32                                                                                                                                                                                                                                   |

|     | 5.5.5                                                                             | Write Buffer Control Register                                                                                                                                                                                                                                                                                 |

|     | 5.5.6                                                                             | Miscellaneous Control Register 1                                                                                                                                                                                                                                                                              |

|     | 5.5.7                                                                             | Miscellaneous Control Register 2                                                                                                                                                                                                                                                                              |

|     | 5.5.8                                                                             | DDC/DPMS Register                                                                                                                                                                                                                                                                                             |

|     | 5.5.9                                                                             | Configuration Register 0 (read only)                                                                                                                                                                                                                                                                          |

|     | 5.5.10                                                                            | Configuration Register 1 (read only)                                                                                                                                                                                                                                                                          |

|     | 5.5.11                                                                            | OffsetA Register                                                                                                                                                                                                                                                                                              |

|     |                                                                                   | OffsetB Register                                                                                                                                                                                                                                                                                              |

|     |                                                                                   | Extended Mode Control Register                                                                                                                                                                                                                                                                                |

|     |                                                                                   | Hardware Cursor X Position Low Register                                                                                                                                                                                                                                                                       |

|     | 5.5.15                                                                            | Hardware Cursor X Position High Register                                                                                                                                                                                                                                                                      |

|     | 5.5.16                                                                            | Hardware Cursor Y Position Low Register                                                                                                                                                                                                                                                                       |

|     | 5.5.17                                                                            | Hardware Cursor Y Position High Register                                                                                                                                                                                                                                                                      |

|     | 5.5.18                                                                            | Hardware Cursor Color 0 Low Register                                                                                                                                                                                                                                                                          |

|     | 5.5.19<br>5.5.20                                                                  | Hardware Cursor Color 0 Mid Register       38         Hardware Cursor Color 0 High Register       38                                                                                                                                                                                                          |

|     | 5.5.20                                                                            | Hardware Cursor Color 1 Low Register                                                                                                                                                                                                                                                                          |

|     | 5.5.22                                                                            | Hardware Cursor Color 1 Mid Register                                                                                                                                                                                                                                                                          |

|     | 5.5.23                                                                            | Hardware Cursor Color 1 High Register                                                                                                                                                                                                                                                                         |

|     | 5.5.24                                                                            | Hardware Cursor Pattern Offset Register                                                                                                                                                                                                                                                                       |

|     | 5.5.25                                                                            | Hardware Cursor Y Origin Register                                                                                                                                                                                                                                                                             |

|     | 5.5.26                                                                            | Hardware Cursor X Origin Register                                                                                                                                                                                                                                                                             |

|     | 5.5.27                                                                            | Scratch Pad Register 0                                                                                                                                                                                                                                                                                        |

|     | 5.5.28                                                                            | Extended Overflow Register                                                                                                                                                                                                                                                                                    |

|     | 5.5.29                                                                            | Starting Address Overflow Register                                                                                                                                                                                                                                                                            |

|     | 5.5.30                                                                            | Interlaced Odd Frame Horizontal Retrace End Register                                                                                                                                                                                                                                                          |

|     | 5.5.31                                                                            | Extended CRT Control Register                                                                                                                                                                                                                                                                                 |

|     |                                                                                   | External RAMDAC Control Register                                                                                                                                                                                                                                                                              |

| 5.6 |                                                                                   | ynthesizer Register Descriptions       42         Video Clock Group 0 (VCK0) Input Frequency Divider       42                                                                                                                                                                                                 |

|     | 5.6.1<br>5.6.2                                                                    | Video Clock Group 0 (VCK0) Input Frequency Divider                                                                                                                                                                                                                                                            |

|     | 5.6.2<br>5.6.3                                                                    | Video Clock Group 0 (VCK0) VCO Frequency Divider                                                                                                                                                                                                                                                              |

|     | 5.6.4                                                                             | Video Clock Group 1 (VCK1) VCO Frequency Divider                                                                                                                                                                                                                                                              |

Page iv

912-3000-030

## 🔳 9004196 0000828 888 📟

|      |          | 5.6.5       Video Clock Group 2 (VCK2) Input Frequency Divider.       42         5.6.6       Video Clock Group 2 (VCK2) VCO Frequency Divider.       43 | 2        |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      |          | 5.6.7 Video Clock Group 3 (VCK3) Input Frequency Divider                                                                                                | <u>ა</u> |

|      |          | 5.6.8 Video Clock Group 3 (VCK3) VCO Frequency Divider                                                                                                  | 3        |

|      |          |                                                                                                                                                         | 3        |

|      |          |                                                                                                                                                         | 3        |

|      |          | 5.6.10       Memory Clock VCO Frequency Divider       43         5.6.11       Programming Video Clock and Memory Clock Frequencies       44             | 3        |

|      | 5.7      | Overlay Control Register                                                                                                                                | 4        |

|      | 0.7      | Overlay Control Registers                                                                                                                               | 4        |

|      |          | · · · · · · · · · · · · · · · · · · ·                                                                                                                   | 4        |

|      |          |                                                                                                                                                         | 2        |

|      |          |                                                                                                                                                         |          |

|      |          |                                                                                                                                                         | 2        |

|      |          |                                                                                                                                                         | 2        |

|      |          |                                                                                                                                                         | 2        |

|      |          |                                                                                                                                                         | j<br>-   |

|      |          |                                                                                                                                                         | 5        |

|      |          |                                                                                                                                                         | Ś        |

|      | 5.8      |                                                                                                                                                         | )<br>7   |

|      | 5.0      | PCI Configuration Space Description                                                                                                                     | 1        |

|      |          |                                                                                                                                                         |          |

|      |          |                                                                                                                                                         |          |

|      |          |                                                                                                                                                         |          |

|      |          |                                                                                                                                                         |          |

|      |          | 5.8.5 Base Address Registers 50                                                                                                                         | )        |

| 6.0  | Elect    | rical Specification                                                                                                                                     | Į        |

|      | 6.1      | Internal DAC Specifications 51                                                                                                                          |          |

|      | 6.2      | AC Timing Characteristics 51                                                                                                                            | 1        |

| 7.0  |          | b BIOS Extended Modes                                                                                                                                   | 6        |

|      | 7.1      | Standard VGA Modes                                                                                                                                      |          |

|      | 7.2      | Extended VGA Modes 64                                                                                                                                   | ł        |

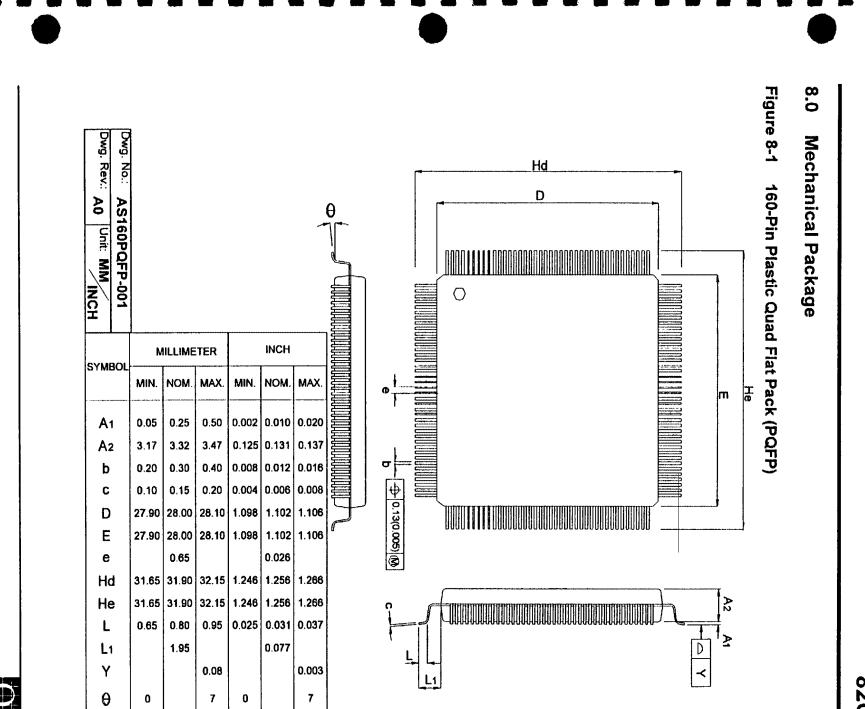

| 8.0  | Mech     | anical Package                                                                                                                                          | e        |

| Appe | ndix A.  | Accessing the BBS                                                                                                                                       | 6        |

|      | A.1      | Paging the SYSOP                                                                                                                                        |          |

|      | A.2      | System Requirements                                                                                                                                     |          |

|      | A.3      | Calling In/Hours of Operation                                                                                                                           |          |

|      | A.4      | Logging On for the First Time                                                                                                                           |          |

|      | A.5      | Log On Rules and Regulations                                                                                                                            |          |

|      | A.6      | Using the BBS                                                                                                                                           |          |

|      |          | A.6.1 Reading Bulletins                                                                                                                                 | ł        |

|      |          | A.6.2 Sending/Receiving Messages                                                                                                                        |          |

|      |          | A.6.3 Finding Information                                                                                                                               |          |

|      |          | A.6.4 Downloading Files From OPTi                                                                                                                       |          |

|      |          | A.6.5 Uploading Files To OPTi                                                                                                                           |          |

|      |          | A.6.6 Logging Off                                                                                                                                       |          |

|      |          | A.6.7 Logging Back on Again                                                                                                                             |          |

|      | A.7      | The Menus                                                                                                                                               |          |

|      | <b>.</b> | A.7.1 Menu Selections                                                                                                                                   |          |

|      |          |                                                                                                                                                         | ,        |

|      |          |                                                                                                                                                         |          |

|      |          |                                                                                                                                                         |          |

|      |          |                                                                                                                                                         |          |

|      |          |                                                                                                                                                         | 1        |

|      |          |                                                                                                                                                         |          |

912-3000-030

8

9004196 0000829 714 🛤

# List of Figures

| Figure 1-1  | OPTi 82C264 System Block Diagram               | 1  |

|-------------|------------------------------------------------|----|

| Figure 2-1  | OP IT 82C264 Functional Block Diagram          | 3  |

| Figure 2-2  | PCI-Bus Solution with 16-bit Feature Connector | ⊿  |

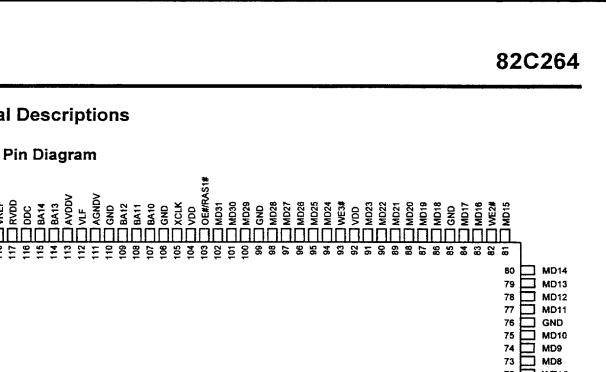

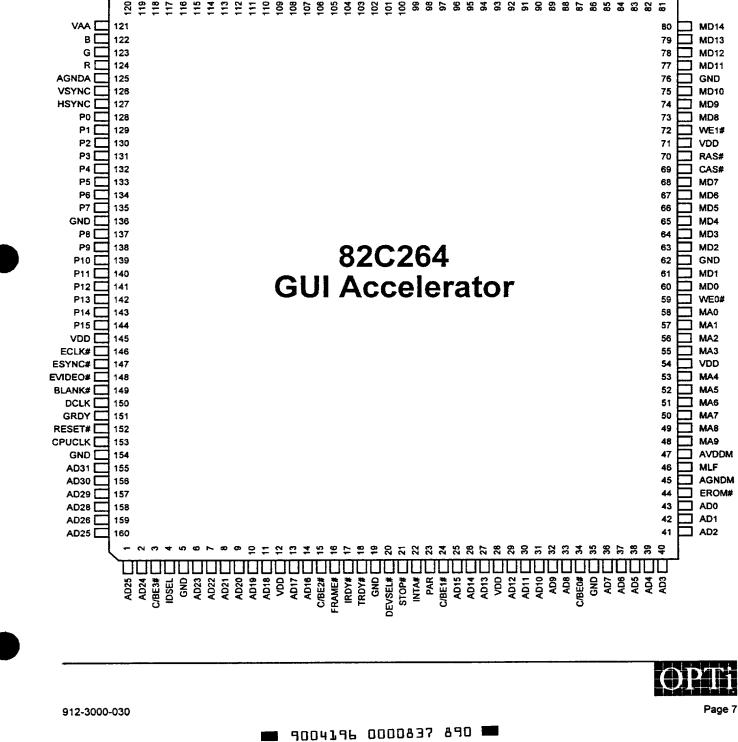

| Figure 3-1  | Pin Diagram                                    | 7  |

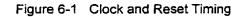

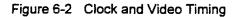

| Figure 6-1  | Clock and Reset Timing                         | 51 |

| Figure 6-2  |                                                | 52 |

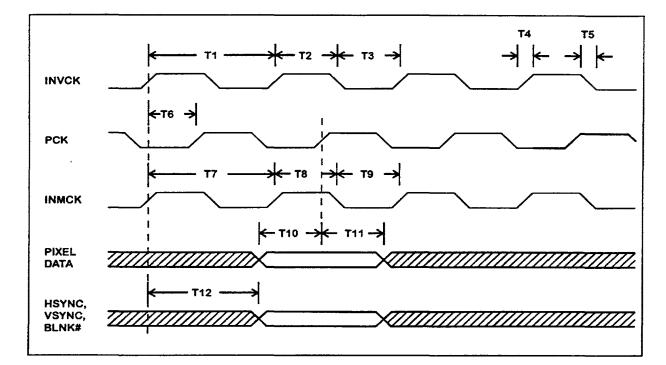

| Figure 6-3  | RAMDAC Timing (Analog Outputs)                 | 53 |

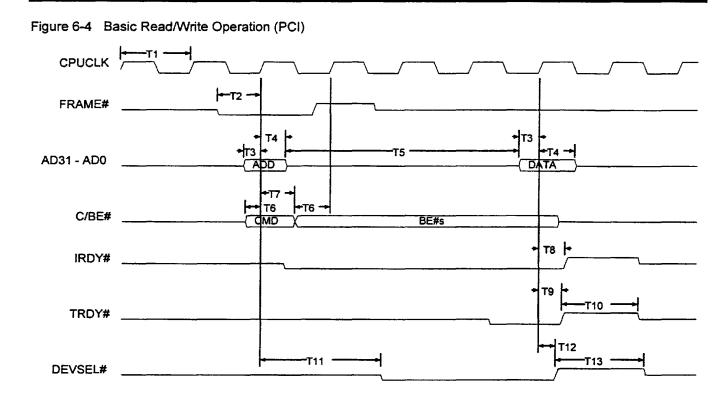

| Figure 6-4  | Basic Read/Write Operation (PCI).              | 54 |

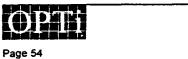

| Figure 6-5  | Configuration Read/Write Operation (PCI)       | 55 |

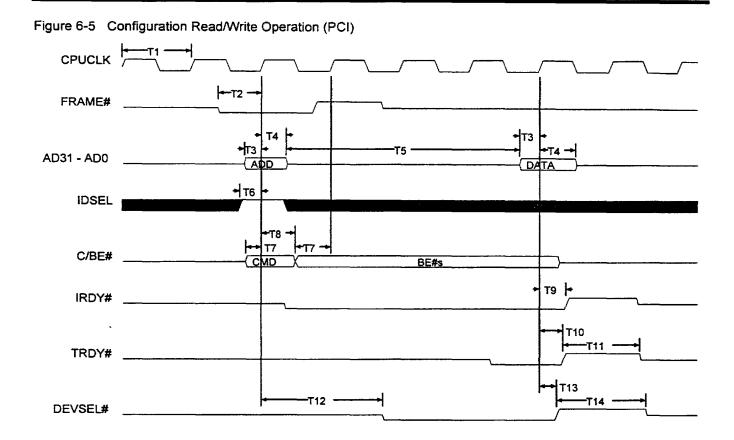

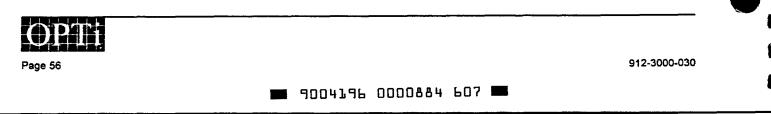

| Figure 6-6  | Burst write Operation (PCI)                    | 56 |

| Figure 6-7  | Burst write Operation with STOP# (PCI)         | 57 |

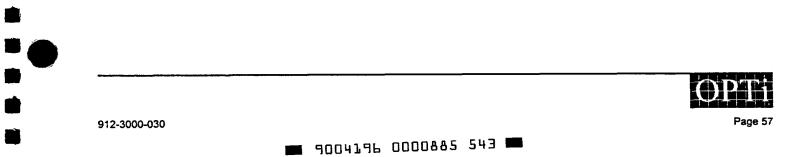

| Figure 6-8  | BIOS Access Operation (PCI)                    | 58 |

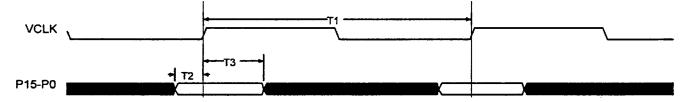

| Figure 6-9  | Pixel Data In Timing                           | 58 |

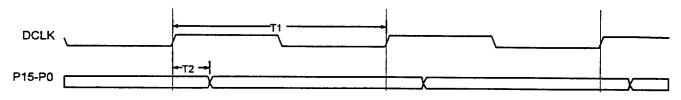

| Figure 6-10 | Pixel Data Out Timing                          | 59 |

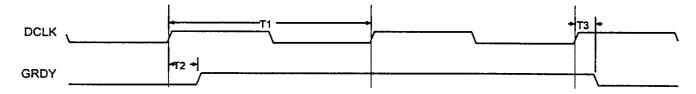

| Figure 6-11 | GRDY Timing                                    | 59 |

| Figure 6-12 | Genlock Timing                                 | 59 |

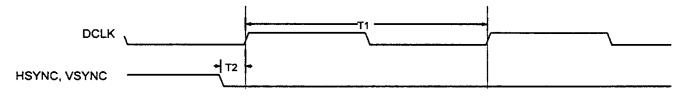

| Figure 6-13 | CAS Before RAS DRAM Timing                     | 60 |

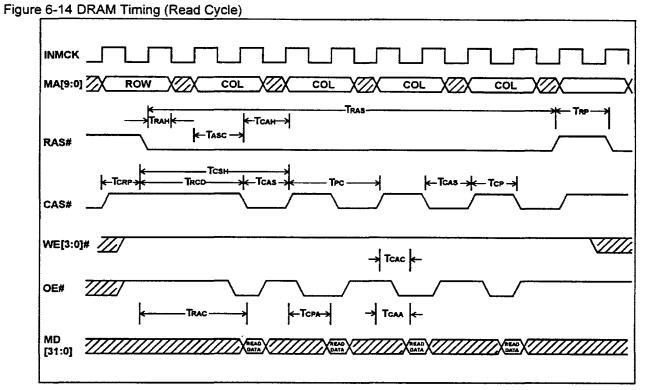

| Figure 6-14 | DRAM Timing (Read Cycle)                       | 61 |

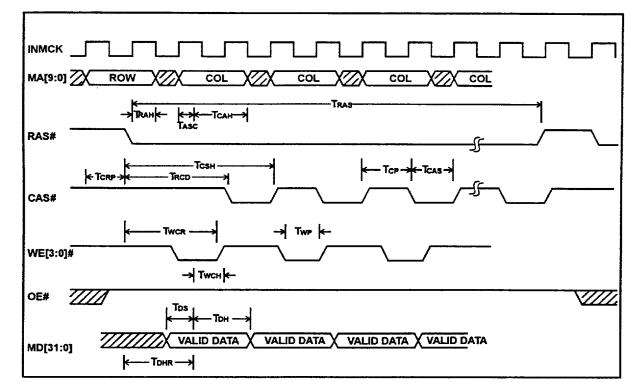

| Figure 6-15 | DRAM Timing (Write Cycle).                     | 62 |

| Figure 8-1  | 160-Pin Plastic Quad Flat Pack (PQFP)          | 65 |

| Figure A-1  | The Main Menu                                  | 68 |

| Figure A-2  | The Bulletin Menu                              | 69 |

| Figure A-3  | The File Menu                                  | 69 |

| Figure A-4  | The Message Menu                               | 69 |

|             |                                                |    |

# **List of Tables**

| Table 2-1  | MD31-MD0 Definitions at Reset        | 5 |

|------------|--------------------------------------|---|

| Table 3-1  | Numerical Pin List                   | 8 |

| Table 3-2  | Alphabetical Pin List                | 9 |

| Table 4-1  | Cursor Display State                 | 7 |

| Table 4-2  | CRT Display Resolutions              | 8 |

| Table 5-1  | VGA Register Port Map                | 1 |

| Table 5-2  | VGA General Registers                | 1 |

| Table 5-3  | VGA Sequencer Registers              | 1 |

| Table 5-4  | CRTC Registers                       | 1 |

| Table 5-5  | Graphics Controller Registers        | 2 |

| Table 5-6  | Attribute Controller Registers       | 2 |

| Table 5-7  | Internal RAMDAC Registers            | 2 |

| Table 5-8  | OPTi GUI Engine Registers            | 2 |

| Table 5-9  | 82C264 Extended Registers            | 2 |

| Table 5-10 | Clock Synthesizer Registers          | 3 |

| Table 5-11 | Overlay Control Registers            | 3 |

| Table 5-12 | PCI Configuration Space Registers    | 3 |

| Table 5-13 | Memory Mapped I/O Register Structure |   |

| Table 5-14 | Configuration Space Layout           | 7 |

| Table 6-1  | Internal DAC Specifications          | 1 |

|            |                                      |   |

## **GUI Accelerator**

## 1.0 Introduction

The OPTi 82C264 provides an unmatched price/performance VGA solution for personal computers. The 82C264 offers high performance and full integration as part of a highly integrated PCI graphics subsystem.

High performance is made possible by a built-in fixed function graphics accelerator. The accelerator supports BitBlt, polygon fill, line draw, color expansion, and clipping. Acceleration is supported for pixel depths of 8, 15, 16, and 24 bits/pixel. Hardware cursor support further enhances performance in GUI environments by removing software cursor overhead.

The RAMDAC and clock synthesizer are built into the 82C264. No external logic is required to connect to the PCI bus. A complete VGA video subsystem can be implemented with two 256Kx16 DRAM chips. CRT display resolutions up to 1280x1024-256 colors are supported.

The OPTi 82C264 is 100% register level compatible with the IBM VGA standard. OPTi supplies a fully compatible VGA/ VESA BIOS, drivers for common applications and operating systems, such as Windows, Windows95 and OS/2, as well as OEM and end-user level utility software.

## 2.0 Features

| 2.1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.2 Benefits                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Integrated true color RAMDAC and clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Full integration. One chip solution.                                                                              |

| Built-in graphics accelerator.<br>Supports:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Superior performance.                                                                                             |

| Polygon fill     Line draw     Color expansion     Cline and a cline and |                                                                                                                   |

| Clipping     32-bit direct interface with PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | No external glue logic.<br>Reduced footprint design.<br>Cost savings.                                             |

| Flexible DRAM configurations:<br>• Two or four 256Kx16 DRAMs<br>• Eight or sixteen 256Kx4 DRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Design flexibility for 1MB or 2MB implementations.<br>Facilitates cost-effective graphics frame buffer solutions. |

| Hardware cursor (32x32x2 and 64x64x2 cursor sizes supported).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | No distracting cursor flicker. Improved performance.                                                              |

| Supports up to 16.8 million colors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Superior color display quality.                                                                                   |

| Programmable linear addressing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Eliminates bank switching.                                                                                        |

| 100% hardware/BIOS compatible with IBM VGA standard.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Allows use of any VGA compatible software with the video subsystem.                                               |

| Multimedia Features <ul> <li>VAFC compatible feature connector</li> <li>Overlay</li> <li>Genlock</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Multimedia ready.                                                                                                 |

| VESA Display Data Channel support.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Plug and play ready.                                                                                              |

| DPMS support.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Green PC compatible.                                                                                              |

## 2.3 Architecture

The OPTi 82C264 contains the following major functional modules:

- Bus Interface Unit

- Write Buffer Control Unit

- Graphic Controller

- Memory Sequencer

- Video FIFO

- CRT Controller

- Attribute Controller

- GUI Engine

- Hardware Cursor

- Pop-up lcon

- RAMDAC

- DPMS

- Clock Synthesizer

- Multi-media Module

The function of each module is described in Section 4.0, *Bus Interface Unit*.

#### Figure 2-1 OPTi 82C264 Functional Block Diagram

1

Powered by ICminer.com Electronic-Library Service CopyRight 2003

# 82C264

Page 4

9004196 0000835 T18 🎟

#### 2.4.1 Definitions of MD31-MD0 at System Reset

Table 2-1 lists the definitions of MD31-MD0 at system reset. To set the given MD bit to a logical 1, pull high through a 4.7Kohm resistor. To set the given bit to a logical 0, pull low through a 4.7K $\Omega$  resistor.

NOTE MD31-MD16 do not directly set any register bits in the chip. The OPTi BIOS reads MD31-MD16 and then sets the 82C264 register bits appropriately.

| MD      | Logical Level | Definition                  |

|---------|---------------|-----------------------------|

| MD31    | 1             | Enables Feature Connector.  |

|         | 0             | Disables Feature Connector. |

| MD30    | 1             | Enable PCI BIOS interface.  |

|         | 0             | Disable PCI BIOS interface. |

| MD29-16 | -             | Reserved                    |

| MD15    | 1             | Select dual WE# DRAM        |

|         | 0             | Select dual CAS# DRAM       |

| MD14    | 1             | 46E8 is the VGA enable port |

|         | 0             | 3C3 is the VGA enable port  |

| MD13-0  | -             | Reserved                    |

Table 2-1 MD31-MD0 Definitions at Reset

**9004196 0000836 954**

Signal Descriptions 3.0

RVDD

VREF

GND FADJ

ппп

Figure 3-1

## Table 3-1Numerical Pin List

| Pin | Name    | Pin | Name  | Pin | Name      | Pin | Name    |

|-----|---------|-----|-------|-----|-----------|-----|---------|

| 1   | AD25    | 41  | AD2   | 81  | MD15      | 121 | VAA     |

| 2   | AD24    | 42  | AD1   | 82  | WE2#      | 122 | В       |

| 3   | C/BE3#  | 43  | AD0   | 83  | MD16      | 123 | G       |

| 4   | IDSEL   | 44  | EROM# | 84  | MD17      | 124 | R       |

| 5   | GND     | 45  | AGNDM | 85  | GND       | 125 | AGNDA   |

| 6   | AD23    | 46  | MLF   | 86  | MD18      | 126 | VSYNC   |

| 7   | AD22    | 47  | AVDDM | 87  | MD19      | 127 | HSYNC   |

| 8   | AD21    | 48  | MA9   | 88  | MD20      | 128 | P0      |

| 9   | AD20    | 49  | MA8   | 89  | MD21      | 129 | P1      |

| 10  | AD19    | 50  | MA7   | 90  | MD22      | 130 | P2      |

| 11  | AD18    | 51  | MA6   | 91  | MD23      | 131 | P3      |

| 12  | VDD     | 52  | MA5   | 92  | VDD       | 132 | P4      |

| 13  | AD17    | 53  | MA4   | 93  | WE3#      | 133 | P5      |

| 14  | AD16    | 54  | VDD   | 94  | MD24      | 134 | P6      |

| 15  | C/BE2#  | 55  | MA3   | 95  | MD25      | 135 | P7      |

| 16  | FRAME#  | 56  | MA2   | 96  | MD26      | 136 | GND     |

| 17  | IRDY#   | 57  | MA1   | 97  | MD27      | 137 | P8      |

| 18  | TRDY#   | 58  | MAO   | 98  | MD28      | 138 | P9      |

| 19  | GND     | 59  | WEO#  | 99  | GND       | 139 | P10     |

| 20  | DEVSEL# | 60  | MD0   | 100 | MD29      | 140 | P11     |

| 21  | STOP#   | 61  | MD1   | 101 | MD30      | 141 | P12     |

| 22  | INTA#   | 62  | GND   | 102 | MD31      | 142 | P13     |

| 23  | PAR     | 63  | MD2   | 103 | OE#/RAS1# | 143 | P14     |

| 24  | C/BE1#  | 64  | MD3   | 104 | VDD       | 144 | P15     |

| 25  | AD15    | 65  | MD4   | 105 | XCLK      | 145 | VDD     |

| 26  | AD14    | 66  | MD5   | 106 | GND       | 146 | ECLK#   |

| 27  | AD13    | 67  | MD6   | 107 | BA10      | 147 | ESYNC#  |

| 28  | VDD     | 68  | MD7   | 108 | BA11      | 148 | EVIDEO# |

| 29  | AD12    | 69  | CAS#  | 109 | BA12      | 149 | BLANK#  |

| 30  | AD11    | 70  | RAS#  | 110 | GND       | 150 | DCLK    |

| 31  | AD10    | 71  | VDD   | 111 | AGNDV     | 151 | GRDY    |

| 32  | AD9     | 72  | WE1#  | 112 | VLF       | 152 | RESET#  |

| 33  | AD8     | 73  | MD8   | 113 | AVDDV     | 153 | CPUCLK  |

| 34  | C/BE0#  | 74  | MD9   | 114 | BA13      | 154 | GND     |

| 35  | GND     | 75  | MD10  | 115 | BA14      | 155 | AD31    |

| 36  | AD7     | 76  | GND   | 116 | DDC       | 156 | AD30    |

| 37  | AD6     | 77  | MD11  | 117 | RVDD      | 157 | AD29    |

| 38  | AD5     | 78  | MD12  | 118 | VREF      | 158 | AD28    |

| 39  | AD4     | 79  | MD13  | 119 | FADJ      | 159 | AD27    |

| 40  | AD3     | 80  | MD14  | 120 | GND       | 160 | AD26    |

OPTi

Page 8

912-3000-030

■ 9004196 0000838 727 **■**

## Table 3-2 Alphabetical Pin List

| Pin | Name  | Pin | Name    | Pin | Name | Pin | Name      |

|-----|-------|-----|---------|-----|------|-----|-----------|

| 43  | AD0   | 109 | BA12    | 55  | MA3  | 103 | OE#/RAS1# |

| 42  | AD1   | 114 | BA13    | 53  | MA4  | 128 | P0        |

| 41  | AD2   | 115 | BA14    | 52  | MA5  | 129 | P1        |

| 40  | AD3   | 149 | BLANK#  | 51  | MA6  | 130 | P2        |

| 39  | AD4   | 34  | C/BE0#  | 50  | MA7  | 131 | P3        |

| 38  | AD5   | 24  | C/BE1#  | 49  | MA8  | 132 | P4        |

| 37  | AD6   | 15  | C/BE2#  | 48  | MA9  | 133 | P5        |

| 36  | AD7   | 3   | C/BE3#  | 60  | MD0  | 134 | P6        |

| 33  | AD8   | 69  | CAS#    | 61  | MD1  | 135 | P7        |

| 32  | AD9   | 153 | CPUCLK  | 63  | MD2  | 137 | P8        |

| 31  | AD10  | 150 | DCLK    | 64  | MD3  | 138 | P9        |

| 30  | AD11  | 116 | DDC     | 65  | MD4  | 139 | P10       |