# 82C621A PCI IDE Controller

Data Book

#### Copyright

Copyright © 1994, 1996, OPTi Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of OPTi Incorporated, 888 Tasman Drive, Milpitas, CA 95035.

#### **Disclaimer**

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

#### **Trademarks**

OPTi and OPTi Inc. are registered trademarks of OPTi Incorporated.

All other trademarks and copyrights are the property of their respective holders.

#### **OPTi Inc.**

888 Tasman Drive Milpitas, CA 95035 Tel: (408) 486-8000

Fax: (408) 486-8001 Web Site: http://www.opti.com/

| 1.0 | Overvi                   | ew                                                                                                                                                                                                                                                                                               | 1  |

|-----|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.0 | Featur                   | es                                                                                                                                                                                                                                                                                               | 1  |

| _   | 2.1                      | Special Feature Notes                                                                                                                                                                                                                                                                            |    |

| 3.0 | Signal<br>3.1            | <b>Description</b> Pin Assignments                                                                                                                                                                                                                                                               | 3  |

|     |                          | 3.1.1       PCI-BUS Interface       6         3.1.2       IDE Interface       7         3.1.3       AT-Bus Interface       8         3.1.4       ROM Support/Power Management Interface       9         3.1.5       Miscellaneous Pins       9         3.1.6       Power and Ground Pins       9 |    |

|     | 3.2                      | Oldmode vs. Newmode                                                                                                                                                                                                                                                                              |    |

| 4.0 | Config                   | uration Register Descriptions                                                                                                                                                                                                                                                                    | 11 |

|     | 4.1<br>4.2<br>4.3<br>4.4 | Vendor ID Register (00h, Read Only)11Device ID Register (02h, Read Only)11Command Register (04h, R/W)11Status Register (06h, R/W)11                                                                                                                                                              |    |

|     | 4.5                      | Revision ID Register (08h, Read Only)                                                                                                                                                                                                                                                            |    |

|     | 4.6                      | Class Code Register (09h, R/W)                                                                                                                                                                                                                                                                   |    |

|     | 4.7<br>4.8               | Header Type Register (0Eh, Read Only)                                                                                                                                                                                                                                                            |    |

|     | 4.0<br>4.9               | Control Block Base Address Register (14h, R/W) (Primary IDE)                                                                                                                                                                                                                                     |    |

|     | 4.10                     | Command Block Base Address Register (18h, R/W) (Secondary IDE)                                                                                                                                                                                                                                   |    |

|     | 4.11                     | Control Block Base Address Register (1Ch, R/W) (Secondary IDE)                                                                                                                                                                                                                                   |    |

|     | 4.12                     | External ROM Base Address Register (30h, R/W)                                                                                                                                                                                                                                                    |    |

|     | 4.13                     | Interrupt Line Register (3Ch, R/W)                                                                                                                                                                                                                                                               |    |

|     | 4.14                     | Interrupt Pin Register (3Dh, Read Only)                                                                                                                                                                                                                                                          |    |

| 5.0 | I/O Re                   | gister Descriptions                                                                                                                                                                                                                                                                              | 14 |

|     | 5.1                      | I/O Registers for Primary IDE                                                                                                                                                                                                                                                                    |    |

|     |                          | 5.1.1 Internal ID Register (1F2h, Write Only)                                                                                                                                                                                                                                                    |    |

|     |                          | 5.1.2 Read Cycle Timing Register-A (1F0h, Index-0, R/W)                                                                                                                                                                                                                                          |    |

|     |                          | 5.1.3 Read Cycle Timing Register-B (1F0h, Index-1, R/W)                                                                                                                                                                                                                                          |    |

|     |                          | 5.1.4 Write Cycle Timing Register-A (1F1h, Index-0, R/W)                                                                                                                                                                                                                                         |    |

|     |                          | 5.1.5 Write Cycle Timing Register-B (1F1h, Index-1, R/W)                                                                                                                                                                                                                                         |    |

|     |                          | 5.1.6       Control Register (1F3h, R/W)                                                                                                                                                                                                                                                         |    |

|     |                          | 5.1.7       Strap Register (1F5h)                                                                                                                                                                                                                                                                |    |

|     |                          | 5.1.9 SMI Data Register (1F4h, Read Only)                                                                                                                                                                                                                                                        |    |

|     |                          | 5.1.10 SMI Data Register (1F4h, Write Only))                                                                                                                                                                                                                                                     |    |

|     |                          | 5.1.11 Miscellaneous Register (1F6h, R/W)                                                                                                                                                                                                                                                        |    |

|     |                          | 5.1.12 Index Data Register (1F7h, R/W)                                                                                                                                                                                                                                                           |    |

|     | 5.2                      | I/O Registers for Secondary IDE                                                                                                                                                                                                                                                                  |    |

|     |                          | 5.2.1 Internal ID Register (172h, Write Only)                                                                                                                                                                                                                                                    |    |

|     |                          | 5.2.2 Read Cycle Timing Register-A (170h, Index-0, R/W)                                                                                                                                                                                                                                          |    |

|     |                          | 5.2.3 Read Cycle Timing Register-B (170h, Index-1, R/W)                                                                                                                                                                                                                                          |    |

|     |                          | 5.2.4 Write Cycle Timing Register-A (171h, Index-0, R/W)                                                                                                                                                                                                                                         |    |

|     |                          | 5.2.5 Write Cycle Timing Register-B (171h, Index-1, R/W)                                                                                                                                                                                                                                         |    |

|     |                          | 5.2.6 Control Register (173h, R/W)                                                                                                                                                                                                                                                               |    |

# 82C621A

|       | 5.3                      | 5.2.7<br>5.2.8<br>5.2.9<br>5.2.10<br>Program | Strap Register (175h)         | )<br>)<br>) |

|-------|--------------------------|----------------------------------------------|-------------------------------|-------------|

| 6.0   | <b>AC Ch</b> 6.1 6.2 6.3 | DC Cha                                       | ristics se Maximum Ratings    | 5           |

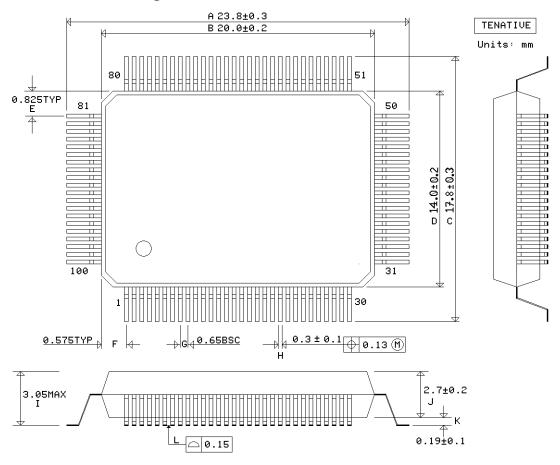

| 7.0   | Mecha                    | nical P                                      | ackage                        | 32          |

| Appen | dix A.A                  | Accessi                                      | ing the BBS                   | 33          |

| • •   | A.1                      |                                              | the SYSOP                     | 3           |

|       | A.2                      |                                              | Requirements                  |             |

|       | A.3                      |                                              | In/Hours of Operation         |             |

|       | A.4                      |                                              | g On for the First Time       |             |

|       | A.5                      | Log On                                       | Rules and Regulations33       | 3           |

|       | A.6                      |                                              | he BBS                        |             |

|       |                          | A.6.1                                        | Reading Bulletins34           |             |

|       |                          | A.6.2                                        | Sending/Receiving Messages    | ļ           |

|       |                          | A.6.3                                        | Finding Information           | 1           |

|       |                          | A.6.4                                        | Downloading Files From OPTi34 | ļ           |

|       |                          | A.6.5                                        | Uploading Files To OPTi       | ŀ           |

|       |                          | A.6.6                                        | Logging Off                   | ŀ           |

|       |                          | A.6.7                                        | Logging Back on Again         | 1           |

|       | A.7                      | The Me                                       | nus                           | 1           |

|       |                          | A.7.1                                        | Menu Selections               | ;           |

Page iv 912-3000-002

# 82C621A

| Figure 2-1  | Block Diagram 1                                       |

|-------------|-------------------------------------------------------|

| Figure 2-2  | Example PCI Controller Block Diagram                  |

| Figure 3-1  | Pin Diagram                                           |

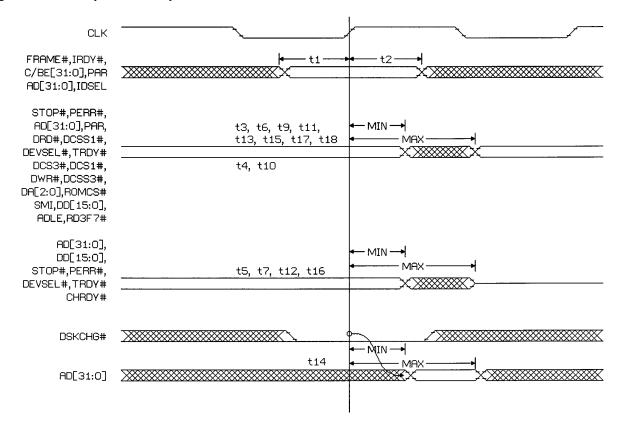

| Figure 6-1  | Input and Output Waveform                             |

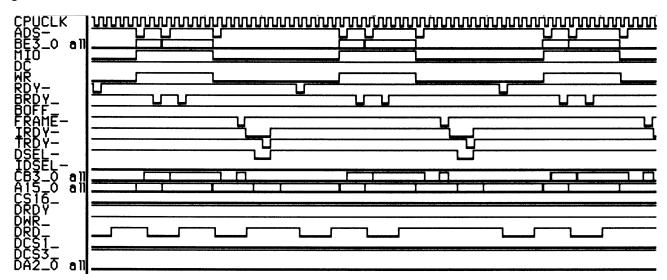

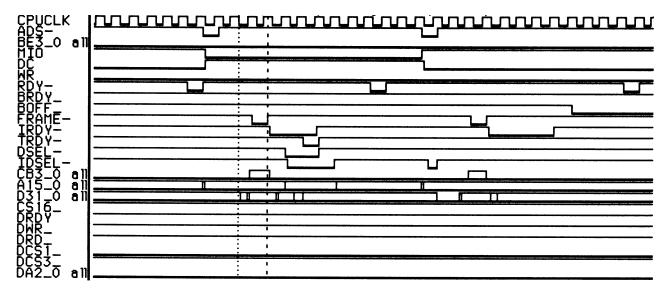

| Figure 6-2  | 32-Bit I/O Access - Read Prefetch Enabled             |

| Figure 6-3  | 16-Bit I/O Access - Read Prefetch Enabled             |

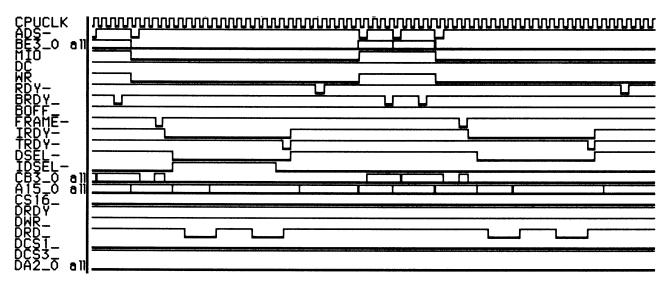

| Figure 6-4  | 32-Bit I/O Access -Buffer Full                        |

| Figure 6-5  | 16-Bit I/O Access - No Prefetch                       |

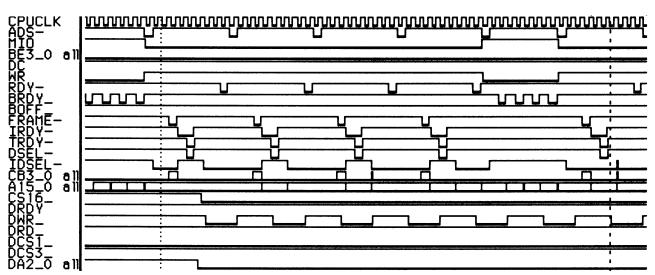

| Figure 6-6  | 32-Bit I/O Access - No Prefetch                       |

| Figure 6-7  | 32-Bit I/O Write                                      |

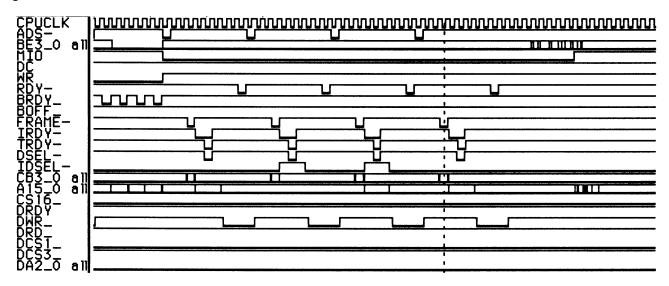

| Figure 6-8  | 16-Bit I/O Write                                      |

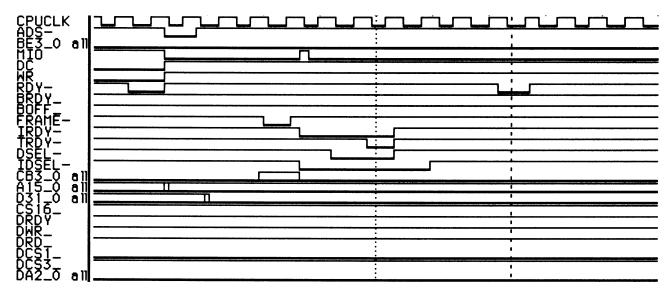

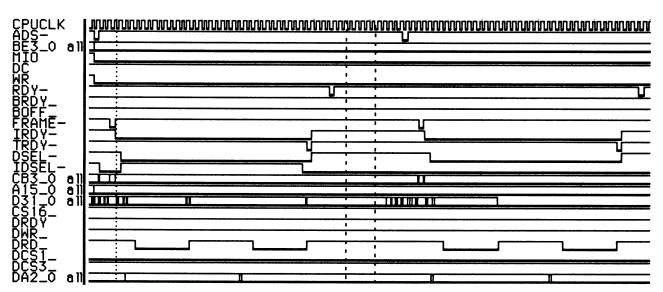

| Figure 6-9  | PCI Configuration Read Cycle                          |

| Figure 6-10 | PCI Configuration Write Cycle                         |

| Figure 6-11 | Enter 611 Register Programming Mode (Read 1F1h twice) |

| Figure A-1  | The Main Menu                                         |

| Figure A-2  | The Bulletin Menu                                     |

| Figure A-3  | The File Menu                                         |

| Figure A-4  | The Message Menu                                      |

Page vi 912-3000-002

# 82C621A

| Table 3-1 | Numerical Pin List          | 4  |

|-----------|-----------------------------|----|

| Table 3-2 | Alphabetical Pin List       | 5  |

| Table 5-1 | REGTIMx Programming Options | 21 |

| Table 5-2 | 16-Bit Timing (LCLKs)       | 21 |

| Table 5-3 | 8-Bit Timing (LCLKs)        | 21 |

| Table 5-4 | Address Setup               | 22 |

| Table 5-5 | DRDY Delay                  | 22 |

| Table 5-6 | Read/Write Command Pulse    | 22 |

| Table 5-7 | Read/Write Recovery Time    | 23 |

Page viii 912-3000-002

## **PCI IDE Controller**

#### 1.0 Overview

The OPTi 82C621A PCI IDE Controller (PIC) is a 100-pin controller chip designed for a fast and flexible interface between the PCI bus and two IDE cables. The 82C621A implements a PCI function to directly support both the Primary and Secondary IDE in a single 100-pin PQFP. This high-integration approach reduces component count, eases board design, reduces cost and increases reliability. An integrated 4-level read-prefetch FIFO and a 4-level posted write FIFO supports zero wait-state operations, substantially improving performance over other IDE implementations. The Enhanced ATA Specification can be supported either by setting Strap Options or by programming internal registers.

#### 2.0 Features

- · Supports 32-bit PCI Bus & Configuration Registers

- 100-pin PQFP

- Supports 4 ATA peripherals

- Optional PCI Expansion ROM support

- · 16-byte Read-Prefetch and Write-Posting FIFO

- IDE timing controlled by either Straps or Registers

- Programming interface compatible with 82C611A

#### 2.1 Special Feature Notes

Write Posting and Read-prefetch allows CPU memory cycles to run concurrently with IDE cycles and also removes the synchronization penalty for AT-bus transfers. IDE cycles can be fine tuned by the ANSI Mode strap options or programmable registers for ANSI-standard (mode 0, 1, 2 or 3) devices or non-standard devices. 32-bit PCI cycles translated to two 16-bit IDE cycles for faster data access.

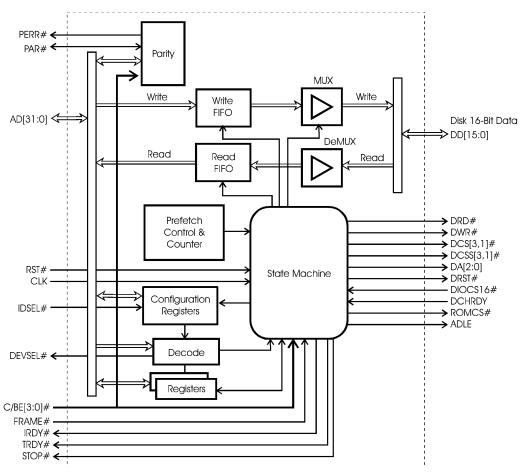

Figure 2-1 Block Diagram

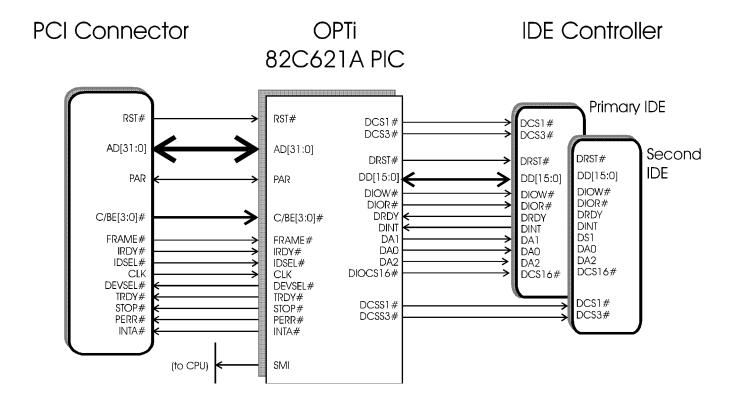

Figure 2-2 Example PCI Controller Block Diagram

Page 2 912-3000-002

## 3.0 Signal Description

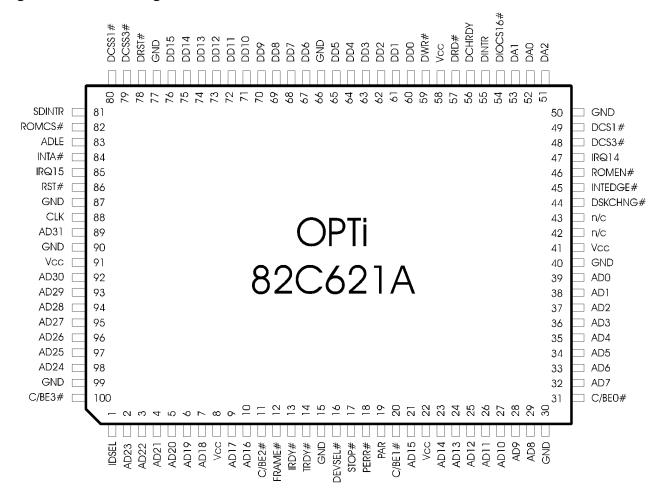

Figure 3-1 Pin Diagram

**Table 3-1 Numerical Pin List**

| Pin | Name    |

|-----|---------|

| 1   | IDSEL   |

| 2   | AD23    |

| 3   | AD22    |

| 4   | AD21    |

| 5   | AD20    |

| 6   | AD19    |

| 7   | AD18    |

| 8   | VCC     |

| 9   | AD17    |

| 10  | AD16    |

| 11  | C/BE2#  |

| 12  | FRAME#  |

| 13  | IRDY#   |

| 14  | TRDY#   |

| 15  | GND     |

| 16  | DEVSEL# |

| 17  | STOP#   |

| 18  | PERR#   |

| 19  | PAR     |

| 20  | C/BE1#  |

| 21  | AD15    |

| 22  | VCC     |

| 23  | AD14    |

| 24  | AD13    |

| 25  | AD12    |

| Pin | Name    |  | Pin | Name     |

|-----|---------|--|-----|----------|

| 1   | IDSEL   |  | 26  | AD11     |

| 2   | AD23    |  | 27  | AD10     |

| 3   | AD22    |  | 28  | AD9      |

| 4   | AD21    |  | 29  | AD8      |

| 5   | AD20    |  | 30  | GND      |

| 6   | AD19    |  | 31  | C/BE0#   |

| 7   | AD18    |  | 32  | AD7      |

| 8   | VCC     |  | 33  | AD6      |

| 9   | AD17    |  | 34  | AD5      |

| 10  | AD16    |  | 35  | AD4      |

| 11  | C/BE2#  |  | 36  | AD3      |

| 12  | FRAME#  |  | 37  | AD2      |

| 13  | IRDY#   |  | 38  | AD1      |

| 14  | TRDY#   |  | 39  | AD0      |

| 15  | GND     |  | 40  | GND      |

| 16  | DEVSEL# |  | 41  | VCC      |

| 17  | STOP#   |  | 42  | n/c      |

| 18  | PERR#   |  | 43  | n/c      |

| 19  | PAR     |  | 44  | DSKCHNG# |

| 20  | C/BE1#  |  | 45  | INTEDGE# |

| 21  | AD15    |  | 46  | ROMEN#   |

| 22  | VCC     |  | 47  | IRQ14    |

| 23  | AD14    |  | 48  | DCS3#    |

| 24  | AD13    |  | 49  | DCS1#    |

| 25  | AD12    |  | 50  | GND      |

| Pin | Name     |

|-----|----------|

| 51  | DA2      |

| 52  | DA0      |

| 53  | DA1      |

| 54  | DIOCS16# |

| 55  | DINTR    |

| 56  | DCHRDY   |

| 57  | DRD#     |

| 58  | VCC      |

| 59  | DWR#     |

| 60  | DD0      |

| 61  | DD1      |

| 62  | DD2      |

| 63  | DD3      |

| 64  | DD4      |

| 65  | DD5      |

| 66  | GND      |

| 67  | DD6      |

| 68  | DD7      |

| 69  | DD8      |

| 70  | DD9      |

| 71  | DD10     |

| 72  | DD11     |

| 73  | DD12     |

| 74  | DD13     |

| 75  | DD14     |

| Pin | Name    |  |

|-----|---------|--|

| 76  | DD15    |  |

| 77  | GND     |  |

| 78  | DRST#   |  |

| 79  | DCSS3#  |  |

| 80  | DCSS1#  |  |

| 81  | SDINTR# |  |

| 82  | ROMCS#  |  |

| 83  | ADLE    |  |

| 84  | INTA#   |  |

| 85  | IRQ15   |  |

| 86  | RST#    |  |

| 87  | GND     |  |

| 88  | CLK     |  |

| 89  | AD31    |  |

| 90  | GND     |  |

| 91  | VCC     |  |

| 92  | AD30    |  |

| 93  | AD29    |  |

| 94  | AD28    |  |

| 95  | AD27    |  |

| 96  | AD26    |  |

| 97  | AD25    |  |

| 98  | AD24    |  |

| 99  | GND     |  |

| 100 | C/BE3#  |  |

Table 3-2 Alphabetical Pin List

| Name | Pin |

|------|-----|

| AD0  | 39  |

| AD1  | 38  |

| AD2  | 37  |

| AD3  | 36  |

| AD4  | 35  |

| AD5  | 34  |

| AD6  | 33  |

| AD7  | 32  |

| AD8  | 29  |

| AD9  | 28  |

| AD10 | 27  |

| AD11 | 26  |

| AD12 | 25  |

| AD13 | 24  |

| AD14 | 23  |

| AD15 | 21  |

| AD16 | 10  |

| AD17 | 9   |

| AD18 | 7   |

| AD19 | 6   |

| AD20 | 5   |

| AD21 | 4   |

| AD22 | 3   |

| AD23 | 2   |

| AD24 | 98  |

| Name   | Pin |

|--------|-----|

| AD25   | 97  |

| AD26   | 96  |

| AD27   | 95  |

| AD28   | 94  |

| AD29   | 93  |

| AD30   | 92  |

| AD31   | 89  |

| ADLE   | 83  |

| C/BE0# | 31  |

| C/BE1# | 20  |

| C/BE2# | 11  |

| C/BE3# | 100 |

| CLK    | 88  |

| DA0    | 52  |

| DA1    | 53  |

| DA2    | 51  |

| DCHRDY | 56  |

| DCS1#  | 49  |

| DCS3#  | 48  |

| DCSS1# | 80  |

| DCSS3# | 79  |

| DD0    | 60  |

| DD1    | 61  |

| DD2    | 62  |

| DD3    | 63  |

|        |     |

| Name     | Pin |

|----------|-----|

| DD4      | 64  |

| DD5      | 65  |

| DD6      | 67  |

| DD7      | 68  |

| DD8      | 69  |

| DD9      | 70  |

| DD10     | 71  |

| DD11     | 72  |

| DD12     | 73  |

| DD13     | 74  |

| DD14     | 75  |

| DD15     | 76  |

| DEVSEL#  | 16  |

| DINTR    | 55  |

| DIOCS16# | 54  |

| DRD#     | 57  |

| DRST#    | 78  |

| DSKCHNG# | 44  |

| DWR#     | 59  |

| FRAME#   | 12  |

| GND      | 15  |

| GND      | 30  |

| GND      | 40  |

| GND      | 50  |

| GND      | 66  |

| Pin |

|-----|

| 77  |

| 87  |

| 90  |

| 99  |

| 1   |

| 84  |

| 45  |

| 13  |

| 47  |

| 85  |

| 42  |

| 43  |

| 19  |

| 18  |

| 82  |

| 46  |

| 86  |

| 81  |

| 17  |

| 14  |

| 8   |

| 22  |

| 41  |

| 58  |

| 91  |

|     |

## 3.1 Pin Assignments

## 3.1.1 PCI-BUS Interface

| Name        | Туре | Pin                                                    | Description                                                                                                                                                                                                            |

|-------------|------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31:0]    | I/O  | 89,<br>92-98, 2-<br>7,<br>9,10,21,2<br>3-29, 32-<br>39 | Address/Data. Multiplexed address/data lines of the PCI bus. A bus transaction includes an address phase followed by one or more data phases.                                                                          |

| C/BE[3:0]#  | I    | 100,11,2<br>0,31                                       | <b>Bus Command/Byte Enable.</b> These lines define the bus command during the address phase of a bus transaction. During the data phase, these lines define the byte enables.                                          |

| CLK         | I    | 88                                                     | PCI Bus Clock. This signal provides timing for all PCI transactions.                                                                                                                                                   |

| DEVSEL#     | 0    | 16                                                     | <b>Device Select.</b> This output indicates that the current address on the PCI-bus is addressing the PIC.                                                                                                             |

| FRAME#      | I    | 12                                                     | <i>Cycle Frame.</i> This signal is asserted to indicate a bus transaction is beginning and de-asserted at the end of the address phase.                                                                                |

| IDSEL       | I    | 1                                                      | <i>Initialization Device Select.</i> This is used as a chip select during configuration read/write cycles.                                                                                                             |

| INTA#/IRQ14 | 0    | 84                                                     | Interrupt A/Interrupt Request 14. When pin 79 (DCSS3#) is high at reset, this is used as IRQ14. When pin 79 is low at reset, the pin is used as INTA#. Refer to Section 3.2, Oldmode vs. Newmode for more information. |

| IRDY#       | I    | 13                                                     | <i>Initiator Ready.</i> This signal indicates the bus masters ability to complete the current data phase.                                                                                                              |

| IRQ15       | 0    | 85                                                     | Interrupt Request 15. This is used as IRQ15. Refer to Section 3.2, Oldmode vs. Newmode for more information.                                                                                                           |

| PAR         | I/O  | 19                                                     | Parity. This signal indicates even parity across AD[31:0] and C/BE[3:0]#.                                                                                                                                              |

| PERR#       | 0    | 18                                                     | Parity Error. This signal is used to report data parity errors.                                                                                                                                                        |

| RST#        | I    | 86                                                     | Reset. This signal is used to initialize the PIC and any drives attached.                                                                                                                                              |

| STOP#       | 0    | 17                                                     | <i>Stop.</i> This signal indicates that the target is requesting the master to stop the current transaction.                                                                                                           |

| TRDY#       | 0    | 14                                                     | <i>Target Ready.</i> This signal indicates the targets ability to complete the current data phase of the transaction.                                                                                                  |

Page 6 912-3000-002

#### 3.1.2 IDE Interface

| Name                   | Туре | Pin   | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|------------------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DA[1:0] /<br>MODE[1:0] | I/O  | 53,52 | Drive Address Lines/Mode [1:0]. These are the two lower bits of the 3-bit binary coded address asserted by the host to access a register or data port in the drive. At reset time, Mode [1,0] are sampled to set the IDE Device Modes for 16-bit Cycle Times:                                                                                                                                                                          |  |  |  |  |

| DA2/ENPREF             | I/O  | 51    | Drive Address Line 2/Enable Prefetch. This is the MSB of the 3-bit binary coded address asserted by the host to access a register or data port in the drive. At reset time, ENPREF is sampled to set the Miscellaneous Register bit 6 which decides whether to enable or disable read prefetch. 1 = Enable, 0 = Disable                                                                                                                |  |  |  |  |

| DCHRDY                 | I    | 56    | I/O Channel Ready. This signal is negated to extend the host transfer cycle of any host register access (Read or Write) when the drive is not ready to respond to a data transfer request. When DCHRDY is not negated, DCHRDY is in a high impedance state.                                                                                                                                                                            |  |  |  |  |

| DCS1#/SPD0             | I/O  | 49    | Drive Chip Select 1. This is the chip select signal decoded from the host address bus used to select the Command Block Registers for the primary IDE. At reset time, SPD0 is sampled to set the Strap Register bit 0 (PCI-bus frequency select, LSB), which determines the exact PCI-bus frequency:  SPD0 Frequency  0 33 MHz  1 25 MHz                                                                                                |  |  |  |  |

| DCS3# / PCI3x7         | I/O  | 48    | Drive Chip Select 3. This is the chip select signal decoded from the host address bus used to select the Control Block Registers for the primary IDE. At reset time, PCI3x7 is sampled to set the Strap registers bit 7 for both the primary (3F7h) and secondary (377h) IDE, which decides whether or not to respond to I/O port 3F7h/377h from the local bus.  0 = 3F7h/377h read from local bus 1 = No response to 3F7h/377h read   |  |  |  |  |

| DCSS1# /<br>RELOC      | I/O  | 80    | Secondary Drive Chip Select 1. This is the chip select signal decoded from the host address bus used to select the Command Block Registers for the secondary IDE.  At reset time, RELOC is sampled to decide whether the I/O space addresses are relocatable through programming configuration space registers.  0 = Fixed I/O addresses (1F0h-1F7h, 3F6h for primary; 170h-177h, 376h for secondary).  1 = Relocatable I/O addresses. |  |  |  |  |

## 3.1.2 IDE Interface (cont.)

| Name               | Туре | Pin             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCSS3#/<br>INTMODE | 0    | 79              | Secondary Drive Chip Select 3. This chip select signal is decoded from the host address bus used to select the Control Block Registers for the secondary IDE. Interrupt Mode. When pin 79 is high during reset, the INTA# and IRQ15 interrupt functions remain the same (oldmode). When pin 79 is low during reset, a different definition for the interrupt pins (84 and 85) is set (newmode). Refer to section 3.2 oldmode vs. newmode for more information.                                                                                                                                                                                                                                                                                                                                                         |

| DD[15:0]           | I/O  | 76-67,<br>65-60 | Disk Data Bus Lines 0 to 15. These sixteen data bus lines require an external pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DIOCS16#           | I    | 54              | Drive 16-bit I/O. DIOCS16# indicates that the 16-bit data port has been addressed and that the drive is prepared to send or receive a 16-bit data word. If DIOCS16# is not asserted, transfers are 8-bit using DD[7:0]. If DIOCS16# is asserted, transfers are 16-bit using DD[15:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DRD#               | 0    | 57              | <b>Drive I/O read.</b> This is the Read strobe signal. The low level of DRD# enables data from a register or the data port of the drive onto the data bus DD[7:0] or DD[15:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DWR#               | 0    | 59              | <b>Drive I/O write.</b> This is the Write strobe signal. The rising edge of DWR# samples data from the data bus DD[7:0] or DD[15:0] into a register or the data port of the drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DINTR              | 1    | 55              | Drive interrupt. This signal is used to interrupt the host system for the primary IDE. DINTR is asserted only when the drive has a pending interrupt, the drive is selected, and the host has cleared nIEN in the Device Control Register.  DINTR is negated by assertion of DRST#, the setting of SRST of the Device Control Register, the host writing the Command Register, or the host reading the Status Register  DINTR is asserted at the beginning of each data block to be transferred. A data block is typically a single sector, except when declared otherwise by use of the Set Multiple command. An exception to this occurs on Format Track, Write Sector(s), Write Buffer and Write Long commands where DINTR is not asserted at the beginning of the first data block to be transferred.              |

| DRST#              | 0    | 78              | <b>Drive reset.</b> This signal is asserted for at least 25 μsec after voltage levels have stabilized during power on and negated thereafter unless some event requires that the drive(s) be reset following power on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SDINTR             | I    | 81              | Secondary Drive interrupt. This signal is used to interrupt the host system for the secondary IDE. SDINTR is asserted only when the drive has a pending interrupt, the drive is selected, and the host has cleared nIEN in the Device Control Register. SDINTR is negated by assertion of DRST#, the setting of SRST of the Device Control Register, the host writing the Command Register, or the host reading the Status Register SDINTR is asserted at the beginning of each data block to be transferred. A data block is typically a single sector, except when declared otherwise by use of the Set Multiple command. An exception to this occurs on Format Track, Write Sector(s), Write Buffer and Write Long commands where DINTR is not asserted at the beginning of the first data block to be transferred. |

#### 3.1.3 AT-Bus Interface

| Name     | Туре | Pin | Description                                                                                                                       |

|----------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------|

| DSKCHNG# | I    | 44  | <b>Disk-Change-Line.</b> For configurations including a floppy controller, this signal can be connected to the drive-change line. |

Page 8 912-3000-002

## 3.1.4 ROM Support/Power Management Interface

| Name                   | Туре | Pin | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADLE/FNC0              | I/O  | 83  | Address Latch Enable/Function 0. ADLE output is used to latch ROM addresses 0 through 7 when ROM is enabled.  At reset time, Function 0 is sampled to enable different functions of the chip, as follows:  ENCO Eunction 0 Both Primary and Secondary IDE enabled 1 Primary IDE only                                                                                                                                                                                                   |

| ROMEN#                 | I    | 46  | <b>ROM Enable.</b> At reset time, this pin is sampled to enable or disable expansion ROM.  0 = Enable.  1 = Disable.                                                                                                                                                                                                                                                                                                                                                                   |

| ROMCS#/ SMI#/<br>TMOD# | I/O  | 82  | ROM Chip Select/System Management Interrupt/Test Mode. ROM Chip Select is used to enable the ROM output and ROM data buffer. SMI# is used to signal to the host system that an SMI event has occurred. The function of this pin is determined by the sampling of ROMEN# strap option.  At reset time, TMOD# is sampled to enable test mode. This line requires an external pull up, and must be sampled high at the end of reset for normal operation.  0 = Test mode.  1 = User mode. |

#### 3.1.5 Miscellaneous Pins

| Name     | Туре | Pin | Description                                                                                                                                                                                                                                                                                  |

|----------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ14    | 0    | 47  | Interrupt Request 14. This pin is normally used as IRQ14 when pin 79 is high at reset. Refer to Section 3.2, Oldmode vs. Newmode for more information on this function.                                                                                                                      |

| INTEDGE# | I    | 45  | Interrupt Level/Edge. When pin 79 is high at reset, this pin is sampled to decide whether INTA# and IRQ15 are edge or level triggered interrupts.  0 = Edge triggered (Active high).  1 = Shared level triggered (Active low).  When pin 79 is low at reset, the strap function is disabled. |

#### 3.1.6 Power and Ground Pins

| Name | Type | Pin                        | Description   |

|------|------|----------------------------|---------------|

| GND  | I    | 15,30,40,50,66,77,87,90,99 | Vss or Ground |

| VCC  | I    | 8,22,41,58,91              | Vcc or +5v    |

#### 3.2 Oldmode vs. Newmode

A new strap option has been added to pin 79 (DCSS3#) to select the mode that the 82C621A will run in. The features that are affected by this strap are:

- 1. When pin 79 is high during reset, the INTA# and IRQ15 interrupt functions remain the same. This is called oldmode. When pin 79 is low during reset, a different definition for the interrupt pins (84 and 85) is given in the table below. This is called newmode. Pin 79 is pulled high internally.

- 2. Interrupt pins 84 and 85, and pin 47 are renamed and redefined based on the newmode strap option.

The new names are:

| Pin | Name  |

|-----|-------|

| 84  | INTA# |

| 85  | IRQ15 |

| 47  | IRQ14 |

The new definitions are:

| Actual mode of operation <sup>1</sup> | Interrupt level | Pin (oldmode)    |     |     | Pin (newmode)    |     |     |

|---------------------------------------|-----------------|------------------|-----|-----|------------------|-----|-----|

|                                       | Strap           | 84               | 85  | 47  | 84               | 85  | 47  |

| Legacy                                | Edge            | 14               | 15  | 14  | 3st <sup>2</sup> | 15  | 14  |

| Legacy                                | Level           | 14# <sup>3</sup> | 15# | 14  | 3st              | 15  | 14  |

| Native                                | Edge            | 14               | 15  | 3st | INTA#            | 3st | 3st |

| Native                                | Level           | 14#              | 15# | 3st | INTA#            | 3st | 3st |

Refer to Section Section 4.6, Class Code Register (09h, R/W), bits 7:0 for information on setting Legacy and Native modes.

**Note** Oldmode is only for compatibility with older versions of the 82C621. All new designs should use newmode for software compatibility with other vendor's devices.

**OPTi**

Page 10 912-3000-002

<sup>2. 3</sup>st = Tri-state

<sup>3. # =</sup> active low

## 4.0 Configuration Register Descriptions

This section describes the registers implemented in the 256 byte configuration space. All registers not implemented always return zero during read cycles.

Optionally, the PIC will support an expansion ROM on the PCI IDE plug-in board. This support will require two extra TTLs, as address latch and data buffer, on board. Also this will require a 32 bit register in the configuration space that normally would not be enabled. The expansion ROM base address register (offset 30h-33h) will be enabled only if the ROMEN# strap pin is sampled low at the time of reset.

#### 4.1 Vendor ID Register (00h, Read Only)

| Bits | Mnemonic | Description                                      | Default |

|------|----------|--------------------------------------------------|---------|

| 15:0 | VID      | Vendor ID: This register identifies the OPTi ID. | 1045h   |

#### 4.2 Device ID Register (02h, Read Only)

| Bits | Mnemonic | Description                                            | Default |

|------|----------|--------------------------------------------------------|---------|

| 15:0 | DID      | Device ID: This register identifies the ID of the PIC. | C621h   |

#### 4.3 Command Register (04h, R/W)

| Bits   | Mnemonic | Description                                                                                                                                                                                                                    | Default |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| [15:7] |          | Reserved - Read only.                                                                                                                                                                                                          | 0       |

| 6      | PEN      | Parity Checking Enable: When this bit is set, PIC generates PERR# if a parity error occurs during I/O write cycles. If the bit is reset, parity checking is ignored. For I/O read cycles, PIC always generates the parity bit. | 0       |

| [5:2]  |          | Reserved - Read only.                                                                                                                                                                                                          | 0       |

| 1      | MEMEN    | <b>Memory Enable:</b> When this bit is set and the expansion ROM enable bit is set (in the EPROM Register), the ROM space becomes available for reading.                                                                       | 0       |

| 0      | IOEN     | Input/Output Enable: When this bit is set, PIC enables the I/O accesses. If reset, all I/O accesses are disabled.                                                                                                              | 1       |

#### 4.4 Status Register (06h, R/W)

| Bits    | Mnemonic | Description                                                                                                                   | Default |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------|---------|

| 15      | PER      | Parity Error: This bit is set whenever the PIC detects a parity error. This bit is cleared by writing 8000h to this register. | 0       |

| [14:11] |          | Reserved - Read Only.                                                                                                         | 0       |

| [10:9]  | SELTIM   | Select Timing: These are read only bits indicating allowable timing assertion for DEVSEL#.                                    | 01      |

| 8       |          | Reserved - Read only.                                                                                                         | 0       |

| 7       | ВТВ      | <b>Back-To-Back Transactions.</b> This is a read only bit, set to 1 to allow fast back-to-back transactions.                  | 1       |

| [6:0]   |          | Reserved - Read only.                                                                                                         | 0       |

**OPTi**

## 4.5 Revision ID Register (08h, Read Only)

| Bits | Mnemonic | Description                                                           | Default |

|------|----------|-----------------------------------------------------------------------|---------|

| 7:0  | REVID    | Revision ID: This register identifies the revision number of the PIC. | 0       |

#### 4.6 Class Code Register (09h, R/W)

| Bits | Mnemonic             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Default |

|------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 23:8 | CCODE<br>(read only) | Class Code: The MSB indicates the base class code for the mass storage controller. The middle byte indicates the sub class code (IDE controller).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0101h   |

| 7:0  | PI                   | Programming Interface. When this register is defined as read/write, the first byte is used to define the IDE as relocatable (native mode) or fixed (legacy mode). Bits 0 and 1 are used for the primary IDE and bits 2 and 3 are used for the secondary IDE. Bits 0 and 2 show whether the IDE is in native mode or legacy mode and bits 1 and 3 show the setting of the RELOC strap option (0=low, 1=high). Bits 4 through 7 are reserved and set to 0.  If the RELOC strap is low during reset, the IDE configuration is fixed (no relocatable) and the PI register bits are set to 0. If the RELOC strap is high during reset, the configuration space is definable and the PI register is accessible: bits 1 and 3 are set to 1 and bits 0 and 2 are used to define the IDE mode.  Also, if the FNC0 strap is set to support the primary IDE only, bits 2 and 3 will not be used. |         |

#### 4.7 Header Type Register (0Eh, Read Only)

| Bits | Mnemonic | Description                          | Default |

|------|----------|--------------------------------------|---------|

| 7:0  | HDR      | Header Type: Single function device. | 00h     |

#### 4.8 Command Block Base Address Register (10h, R/W) (Primary IDE)

| Bits | Mnemonic | Description                                                                                                                                                                                                                                                                                                                           | Default            |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 31:0 | IO1      | Command Block Base Address: This register is the I/O space indicator for the Drive Command Block. The address block has a size of 8 bytes. Bit [2:0] of this register are read only and default to 001. Bits [31:3] are writable if RELOC strap is set to 1.  If the RELOC strap is set to 0, bits [31:0] are read only and return 0. | 1F1h w/<br>RELOC=1 |

#### 4.9 Control Block Base Address Register (14h, R/W) (Primary IDE)

| Bits | Mnemonic | Description                                                                                                                                                                                                                                                                                                                         | Default            |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 31:0 | IO2      | Control Block Base Address: This register is the I/O space indicator for the Drive Control Block. The address block has a size of 4 bytes. Bit [1:0] of this register are read only and default to 01. Bits [31:2] are writable if RELOC strap is set to 1. If the RELOC strap is set to 0, bits [31:0] are read only and return 0. | 3F5h w/<br>RELOC=1 |

912-3000-002

## 4.10 Command Block Base Address Register (18h, R/W) (Secondary IDE)

| Bits | Mnemonic | Description                                                                                                                                                                                                                                                                                                                           | Default                      |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 31:0 | IO3      | Command Block Base Address: This register is the I/O space indicator for the Drive Command Block. The address block has a size of 8 bytes. Bit [2:0] of this register are read only and default to 001. Bits [31:3] are writable if RELOC strap is set to 1.  If the RELOC strap is set to 0, bits [31:0] are read only and return 0. | 171h w/<br>RELOC=1<br>FNC0=0 |

#### 4.11 Control Block Base Address Register (1Ch, R/W) (Secondary IDE)

| Bits | Mnemonic | Description                                                                                                                                                                                                                                                                                                                         | Default                      |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 31:0 | 104      | Control Block Base Address: This register is the I/O space indicator for the Drive Control Block. The address block has a size of 4 bytes. Bit [1:0] of this register are read only and default to 01. Bits [31:2] are writable if RELOC strap is set to 1. If the RELOC strap is set to 0, bits [31:0] are read only and return 0. | 375h w/<br>RELOC=1<br>FNC0=0 |

## 4.12 External ROM Base Address Register (30h, R/W)

| Bits | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Default |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 31:0 | EROM     | External ROM Base Address: This register contains the expansion ROM address. The address block has a size of 16KB. Bits [13:1] of this register are always read only and default to 0.  Bits [31:14, 0] are writable if the ROMEN# strap is sampled low. Bits [31:14] define the base address of the expansion ROM. Bit 0 enables/disables the expansion ROM decode (0 = disable, 1 = enable).  If the ROMEN# strap is sampled high, this register is read only (always 0) and ROM decode is disabled. | x       |

## 4.13 Interrupt Line Register (3Ch, R/W)

| Bits | Mnemonic | Description                                                                                                                  | Default |

|------|----------|------------------------------------------------------------------------------------------------------------------------------|---------|

| 7:0  | INTL     | Interrupt Line. This register indicates which input of the system interrupt controller the INTA# interrupt pin is routed to. | Eh      |

#### 4.14 Interrupt Pin Register (3Dh, Read Only)

| Bits | Mnemonic | Description                                                                  | Default |

|------|----------|------------------------------------------------------------------------------|---------|

| 7:0  | INTP     | Interrupt Pin. The content of this register is 1 (i.e., INTA# will be used). | 1       |

**OPTi**

## 5.0 I/O Register Descriptions

#### 5.1 I/O Registers for Primary IDE

The register addresses are referred to in this section by their power-up default addresses. If the power-up default is modified by writing to configuration register IO1, then these registers will be relocated accordingly.

The PIC contains registers at seven I/O ports accessible after two consecutive 16-bit I/O reads from address 1F1h. Any other I/O cycle between these two reads will disable access to the PIC registers.

5.1.1 Internal ID Register (1F2h, Write Only)

| Bits  | Mnemonic | Description                                                                                                                                                                                                                                         | Default |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7     | CNFDIS   | <b>Configuration Disable:</b> This bit must be set to '0' in order to access 621A Internal Registers. Any write to this register with CNFDIS = 1 will disable all accesses to the 621A registers until another two consecutive I/O reads from 1F1h. | 1       |

| 6     | CNFOFF   | Configuration Off. This bit must be set to '0' in order to access 621A Internal Registers. Any write to this register with CNFOFF = 1 will disable all accesses to the 621A registers until power down or reset.                                    | 0       |

| [5:2] |          | Reserved - Must be written 0.                                                                                                                                                                                                                       |         |

| [1:0] |          | Reserved - Must be written 11.                                                                                                                                                                                                                      |         |

#### 5.1.2 Read Cycle Timing Register-A (1F0h, Index-0, R/W)

This register shares the I/O address with the Read Cycle Timing Register-B, indexed by the Miscellaneous Register bit 0. It controls the read cycle timing of IDE data register for the drive selected by the Control register bits [3:2]. The bit field of this register is defined as follows:

| Bits  | Mnemonic   | Description                                                                                                                                                                                                                                         | Default |

|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| [7:4] | RDPW[3:0]  | <b>Read Pulse Width:</b> The value programmed in this register determines the DRD# pulse width in CLKs (for a 16-bit read from the IDE Data Register). See Table 5-6.                                                                               | xxxx    |

| [3:0] | RDREC[3:0] | <b>Read Recovery Time:</b> The value programmed in this register determines the recovery time between the end of DRD# and the next DA[2:0]/DCSx# being presented (after a 16-bit read from the IDE Data Register), measured in CLKs. See Table 5-7. | xxxx    |

#### 5.1.3 Read Cycle Timing Register-B (1F0h, Index-1, R/W)

This register shares the I/O address with the Read Cycle Timing Register-A, indexed by the Miscellaneous Register bit 0. It controls the read cycle timing of IDE data register for the drive not selected by the Control register bits [3:2], if the Control Register bit 7 is set The bit fields of these registers is defined as follows:

| Bits  | Mnemonic   | Description                                                                                                                                                                                                                                         | Default |

|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| [7:4] | RDPW[3:0]  | <b>Read Pulse Width:</b> The value programmed in this register determines the DRD# pulse width in CLKs (for a 16-bit read from the IDE Data Register). See Table 5-6.                                                                               | xxxx    |

| [3:0] | RDREC[3:0] | <b>Read Recovery Time:</b> The value programmed in this register determines the recovery time between the end of DRD# and the next DA[2:0]/DCSx# being presented (after a 16-bit read from the IDE Data Register), measured in CLKs. See Table 5-7. | xxxx    |

**OPTi**

Page 14 912-3000-002

#### 5.1.4 Write Cycle Timing Register-A (1F1h, Index-0, R/W)

This register shares the I/O address with the Write Cycle Timing Register-B, indexed by the Miscellaneous Register bit 0. It controls the write cycle timing of IDE data register for the drive selected by the Control register bits [3:2]. The bit field of this register is defined as follows:

| Bits  | Mnemonic   | Description                                                                                                                                                                                                                                    | Default |

|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| [7:4] | WRPW[3:0]  | Write Pulse Width: The value programmed in this register determines the DWR# pulse width in CLKs (for a 16-bit write from the IDE Data Register). See Table 5-6.                                                                               | xxxx    |

| [3:0] | WRREC[3:0] | Write Recovery Time: The value programmed in this register determines the recovery time between the end of DWR# and the next DA[2:0]/DCSx# being presented (after a 16-bit write from the IDE Data Register), measured in CLKs. See Table 5-7. | xxxx    |

#### 5.1.5 Write Cycle Timing Register-B (1F1h, Index-1, R/W)

This register shares the I/O address with the Write Cycle Timing Register-A, indexed by the Miscellaneous Register bit 0. It controls the write cycle timing of IDE data register for the drive not selected by the Control register bits [3:2], if the Control Register bit 7 is set The bit fields of these registers is defined as follows:

| Bits  | Mnemonic   | Description                                                                                                                                                                                                                                    | Default |

|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| [7:4] | WRPW[3:0]  | Write Pulse Width: The value programmed in this register determines the DWR# pulse width in CLKs (for a 16-bit write from the IDE Data Register). SeeTable 5-6.                                                                                | xxxx    |

| [3:0] | WRREC[3:0] | Write Recovery Time: The value programmed in this register determines the recovery time between the end of DWR# and the next DA[2:0]/DCSx# being presented (after a 16-bit write from the IDE Data Register), measured in CLKs. See Table 5-7. | xxxx    |

#### 5.1.6 Control Register (1F3h, R/W)

| Bits  | Mnemonic | Description                                                                                                                                                                                                                                                                                                                      | Default |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7     | REGTIM2  | Enable Timing Registers-B. When set, this bit enables cycle-timing registers-B (1F0h & 1F1h of the Index-1) to override the IDE timing set by the strap options for any drive not selected by 1F3h bit [3:2]. It also enables the miscellaneous timing register 1F6h bits [5:1] to override the timing set by the strap options. | 0       |

| [6:5] |          | Reserved: Must always be written with '0'.                                                                                                                                                                                                                                                                                       | 0       |

| 4     | EN1WSRD  | Enable 1-Wait State Read. 1 = 1 WS minimum for data reads, 0 = 2 WS minimum.                                                                                                                                                                                                                                                     | 0       |

| 3     | REGTIM1  | Enable Timing Register-A, Drive 1: When set, this bit enables cycle-timing registers-A (1F0h & 1F1h of the Index-0) to override the IDE timing set by the strap options for Drive-1.                                                                                                                                             | 0       |

| 2     | REGTIM0  | Enable Timing Register-A, Drive 0: When set, this bit enables cycle-timing registers-A (1F0h & 1F1h of the Index-0) to override the IDE timing set by the strap options for Drive-0.                                                                                                                                             | 0       |

| 1     | ENSMI    | Enable SMI: When set, this bit generates an SMI upon access to any IDE I/O address, if ENDO is 1 and CNFDIS is 1. Clearing this bit will reset SMI and disables it.                                                                                                                                                              | 0       |

| 0     |          | Reserved - Must be written 1.                                                                                                                                                                                                                                                                                                    | 1       |

OPTi

NOTE

For all new software controls the IDE timing through registers programming, bits 2, 3 and 7 of the Control register should be enabled after the Cycle Timing Registers and Miscellaneous Register are programmed. See Table 5-1 for programming options.

#### 5.1.7 Strap Register (1F5h)

| Bits  | Mnemonic  | Description                                                                                                                                                                                   | Default |

|-------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7     | PCI3F7    | <ul> <li>PCI 3F7 Read (Read/Write). Decides whether or not read access to 3F7h comes from local bus.</li> <li>0 = 3F7h read from local bus.</li> <li>1 = No response to 3F7h read.</li> </ul> |         |

| [6:5] | REV[1:0]  | <b>Revision Number Register (Read Only).</b> When the value of this register is set to 11, the content of REVID register should be used to find the revision level of the chip.               | 11      |

| 4     | DINTR     | DINTR Status (Read Only). Returns the state of DINTR input.                                                                                                                                   |         |