# 82C852 PCMCIA Controller

# 1.0 Overview

This document describes a new OPTi interface chipset, the 82C852 PCMCIA Controller, that provides a single, fully compliant PCMCIA interface in a very compact form factor. The PCMCIA interface is handled in a straightforward manner using a modified Intel 82365SL PCMCIA core.

Throughout this document, the term "R2" is used to indicate that the 82C852 part implements a Rev. 2.x compliant PCM-CIA slot. The 82C852 logic also incorporates the additional features needed to bring the interface to "PC Card 95" standards (DMA and 3.3V support).

The OPTi 82C852 PCMCIA Controller chipset is based on an OPTi standard called Compact ISA (CISA). The CISA interface is derived from ISA, but uses a proprietary scheme to reduce the required number of interface pins from 80 to 23. The CISA interface is described in the "Compact ISA Specification" appendix to this document.

# 1.1 Interface Overview

The OPTi 82C852 PCMCIA Controller chipset uses two external interfaces. The terms *host interface* and *slot interface* are used throughout this document to describe these interfaces.

- The **host interface** provides CISA signals to the host system.

- The **slot interface** accommodates a single PCMCIA card, operating at either 5V or 3.3V.

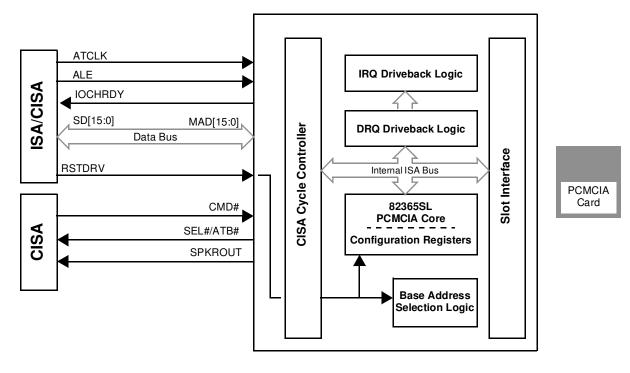

The interface signal groups used to integrate the OPTi 82C852 PCMCIA Controller chipset into the standard system are described in the following sections. Figure 1-1 illustrates the interaction of the components of the OPTi 82C852 PCM-CIA Controller chipset.

- The **CISA Cycle Controller** latches the address and data strobed in on the three phases of a CISA cycle and reassembles them in the proper format for the **Internal ISA Bus**, as needed by the 82365SL-standard core.

- The PCMCIA 82365SL Core is accessed from the Internal ISA Bus. The PCMCIA Configuration Registers are integral to the core and consist of the 82365SL-standard PCMCIA registers accessed at 64 register indexes. This register set is accessed through an index/data method, with the index register fixed at 3E0h and the data register fixed at 3E1h. A strapping option allows this decoding to take place at 3E2h and 3E3h instead.

# Figure 1-1 82C852 Organization

- The **Base Address Selection** logic allows the base address of the registers to be changed, if desired, through external strapping options. In this way, up to eight separate chips can occupy the CISA bus in parallel yet each one will respond only to the cycles intended for it.

- The IRQ Driveback logic allows the chip to request control of the CISA bus in order to return interrupt request line change information to the host system. Likewise, the DRQ Driveback logic allows the chip to request control of the CISA bus in order to return DMA request line change information to the host system.

The logic subsystems of the 82C852 PCMCIA Controller are described in detail in the following sections.

# 1.2 CISA Cycle Controller

The CISA Cycle Controller has many responsibilities:

- Latching the address and data strobed in on the three phases of a CISA cycle

- Claiming of configuration cycles, by decoding I/O accesses at 3E0h (3E2h) and 3E1h (3E3h)

- Claiming of memory and I/O cycles as programmed in the 82365SL-compatible registers for the card inserted

- Inserting wait states by dropping and raising IOCHRDY for the correct number of cycles, and with the correct timing (asynchronously or synchronously), for each cycle type.

The CISA Cycle Controller handles these responsibilities as follows.

#### 1.2.1 Latching Address/Data

Command, address, and data are strobed in through the CISA interface in three phases on separate signal edges, as described in Appendix A. By the end of the second phase, the CISA Cycle Controller has latched enough address and command information to determine whether to claim the cycle by asserting the SEL#(/ATB#) signal.

#### 1.2.2 Claiming of Configuration Cycles

The 82C852 chip always tracks cycles to I/O ports 3E0h and 3E1h (optionally 3E2h and 3E3h), the port addresses that have become a de facto standard for PCMCIA configuration register access. However, since up to four 82C852 chips, for PCMCIA slots A, B, C, and D, can respond to the index/data pair, the 82C852 chip adheres to very strict rules about which chip responds in each circumstance.

Index Port 3E0h (3E2h) I/O Writes - Only the Slot A chip in the system asserts SEL# after decoding a port 3E0h (3E2h) I/ O write. All other chips track the cycle, and latch the index number written to this port.

**Data Port 3E1h (3E3h) I/O Reads and Writes** - Only the chip responsible for the index previously written to port 3E0h (3E2h) asserts SEL# after decoding a port 3E1h (3E3h) I/O read or write. All other chips ignore the cycle.

Index Port 3E0h (3E2h) I/O Read - Only the Slot A chip in the system asserts SEL# after decoding a port 3E0h (3E2h) I/ O read, and then returns the last value written to this port. All other chips ignore the cycle.

This approach ensures that only one chip will assert SEL# at any time, avoiding contention.

#### 1.2.3 Claiming of PCMCIA Memory and I/O Cycles

The CISA Cycle Controller claims memory and I/O cycles by asserting SEL# according to the settings of the I/O Window registers and Memory Window registers of the 82365SL-compatible core. Refer to the "82C852 Register Set" section for a description of these registers.

#### 1.2.4 Inserting Wait States

The CISA Cycle Controller is pre-programmed to insert different numbers of wait states according to the host cycle being driven and the target PCMCIA card inserted. Table 1-1 lists the cycle length and the timing for de-assertion/assertion of IOCHRDY for each possible combination.

| Host Cycle<br>Type         | Wait States<br>Requested<br>by Host | PCMCIA<br>Card Bus<br>Width | PCMCIA<br>Card Wait<br>States | Wait<br>States<br>Inserted | Total Cycle<br>Size<br>(ATCLKs) | IOCHRDY<br>release | IOCHRDY<br>sampling by<br>host |

|----------------------------|-------------------------------------|-----------------------------|-------------------------------|----------------------------|---------------------------------|--------------------|--------------------------------|

| Memory                     | 0ws                                 | 16-bit                      | 0ws                           | 0                          | 2                               | synchronous        | direct                         |

| Fast CISA<br>ISA#=1        | 0ws                                 | 16-bit                      |                               | 1                          | 3                               | synchronous        | direct                         |

|                            | 0ws                                 | 8-bit                       | 0ws                           | 1                          | 3                               | synchronous        | direct                         |

|                            | 0ws                                 | 8-bit                       |                               | 4                          | 6                               | synchronous        | direct                         |

| Memory                     |                                     | 16-bit                      | 0ws                           | 0                          | 3                               | asynchronous       | resynchronized                 |

| ISA compat-<br>ible ISA#=0 |                                     | 16-bit                      |                               | 0                          | 3                               | asynchronous       | resynchronized                 |

|                            |                                     | 8-bit                       | 0ws                           | 0                          | 3                               | asynchronous       | resynchronized                 |

|                            |                                     | 8-bit                       |                               | 3                          | 6                               | asynchronous       | resynchronized                 |

| I/O                        |                                     | 16-bit                      |                               | 0                          | 3                               | asynchronous       | resynchronized                 |

|                            |                                     | 8-bit                       | 0ws                           | 0                          | 3                               | asynchronous       | resynchronized                 |

|                            |                                     | 8-bit                       |                               | 3                          | 6                               | asynchronous       | resynchronized                 |

| DACK                       |                                     | 16-bit                      |                               | 0                          | 3                               | never asserted     | resynchronized                 |

|                            |                                     | 8-bit                       |                               | 0                          | 6                               | never asserted     | resynchronized                 |

Table 1-1

Wait State Control

\* Zero wait state cycles are selected by bit 11h[6] for memory cycles, and by bits 07h[6+2] for I/O cycles.

The 82C365SL core is ISA-based. Therefore, the CISA Cycle Controller converts cycles as necessary to generate 16-bitonly CISA cycles to 8- or 16-bit ISA cycles. The effect of this conversion on cycle duration is seen in the table.

# 1.3 PCMCIA 82365SL Core

The Intel 82365SL core is used in the 82C852 chip to assure compatibility with most popular PCMCIA card and socket services. The PCMCIA Configuration Registers are integral to the core and consist of the industry-standard 82365SL PCM-CIA registers accessed at 64 register indexes. This register set is accessed through an index/data method, with the index register fixed at 3E0h (3E2h) and the data register fixed at 3E1h (3E3h).

Some register functions have been modified slightly, while in other cases additional functionality has been added to formerly "reserved" bits. Additions and changes to the 82365SL core are noted in the "82C852 Register Set" section of this document.

#### 1.4 Base Address Selection Logic

The Base Address Selection logic provides selection signals as inputs to the CISA Cycle Controller to allow the controller

to claim only the appropriate cycles as explained in the "CISA Cycle Controller" section. The base address is selected according to strap options listed in the "Strap-Selected Options" section of this document.

# 1.5 IRQ and DRQ Driveback Logic

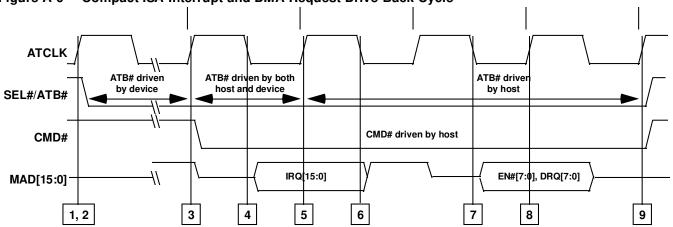

The 82C852 sends interrupt requests and DRQ status change information back to the system by way of the CISA IRQ/DRQ Driveback Cycle as described in Appendix A.

Since the IRQ information arrives at the CISA host before it is used to generate an ISA IRQ, the host can redefine any of the IRQ signals to select other functions. For example, IRQ13, which is not on the ISA bus, could be redefined as Ring Indicator by the host.

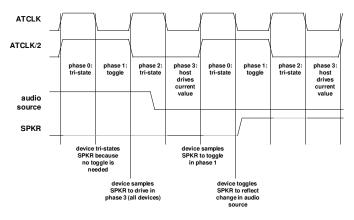

Included in the Driveback circuitry is the Stop Clock logic. When the CISA Cycle Controller decodes a Stop Clock cycle, the Driveback circuitry state machine must switch ATB# from a synchronous signal to a product of combinatorial logic. In this way, the next interrupt that arrives from the PCMCIA card can be fed directly to ATB# without clock synchronization, and used to restart the host clock. Once the Driveback circuitry begins to receive clocks again, it will generate a synchronous interrupt signal on ATB#.

# 2.0 82C852 Register Set

The 82C852 PCMCIA Controller chip provides programming registers grouped as General Purpose, I/O Mapping Window, Memory Mapping Window, and Special. The 82C852 PCM-CIA Socket Configuration Registers are addressed for slot A,

B, C, or D. The index addresses to which the registers respond are determined by a strapping option, described in the Strapping Options section of this document.

| Index                        | Name                                                | 7                                                                                                                      | 6                                                           | 5                                                                                                            | 4                                                              | 3                                                                                                                      | 2                                                                              | 1                                                                                                            | 0                                                                                     |

|------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| 00h<br>40h<br><br>80h<br>C0h | Identification<br>Register<br>Read-only             | Interface Type<br>ported interface<br>00=I/O only<br>01=Memory or<br>10=Mem & I/O<br>11=Reserved                       | es.                                                         | Chip Revision<br>00=1st revisior<br>Read-only                                                                |                                                                |                                                                                                                        | C852 PCMCIA C<br>C824 CardBus C<br>C365SL                                      |                                                                                                              | 5)                                                                                    |

| 01h<br>41h<br><br>81h<br>C1h | Interface Status<br>Register<br>Read-only           | Reserved.                                                                                                              | Card Power<br>0=Off<br>1=On                                 | RDY/BSY#<br>State<br>0=Busy<br>1=Ready                                                                       | WP State<br>0=Not write<br>protected<br>1=Write pro-<br>tected | CD2# State<br>0=CD2# high<br>1=CD2# low                                                                                | CD1# State<br>0=CD1# high<br>1=CD1# low                                        | BVD2/<br>SPKR State<br>0=low<br>1=high                                                                       | BVD1/<br>STSCHG#<br>State<br>0=low<br>1=high                                          |

| 02h<br>42h<br><br>82h<br>C2h | Power Control<br>Register                           | Socket Sig-<br>nals<br>0=Disable<br>1=Enable<br>(tristate or<br>drive low)                                             | Reserved.<br>Write bit as<br>read.                          | Auto Card<br>Power-up on<br>Insertion<br>0=Disable<br>1=Enable                                               | Card Vcc Cont<br>VCC5-VCC3 to<br>ues. Refer to T               | o these bit val-                                                                                                       | Slot Vcc<br>Threshold<br>Scaling<br>0=3.3V<br>1=5V                             | Card Vpp Cont<br>PGM-VPPVCC<br>values. Refer t                                                               |                                                                                       |

| 03h<br>43h<br><br>83h<br>C3h | Reset and Gen-<br>eral Control Reg-<br>ister        | Reserved.<br>Write bit as<br>read.                                                                                     | RESET Sig-<br>nal State<br>0=Active<br>(high)<br>1=Inactive | PCMCIA<br>Card Inter-<br>face<br>0=Memory<br>1=I/O                                                           | Reserved.<br>Write bit as<br>read.                             | IREQ Routing<br>000=None<br>0001=IRQ1*<br>0010=IRQ2*<br>0011=IRQ3<br>0100=IRQ4<br>0101=IRQ5<br>0110=IRQ6*<br>0111=IRQ7 |                                                                                | 1000=IRQ8*<br>1001=IRQ9<br>1010=IRQ10<br>1011=IRQ11<br>1100=IRQ12<br>1101=IRQ13*<br>1110=IRQ14<br>1111=IRQ15 |                                                                                       |

| 04h<br>44h<br><br>84h<br>C4h | Card Status<br>Change Register                      | Reserved. Writ                                                                                                         | te bits as read.                                            |                                                                                                              |                                                                | CDx# Status<br>Change or<br>Software<br>Interrupt<br>0=No<br>1=Yes                                                     | RDY/BSY#<br>has gone<br>high<br>0=No<br>1=Yes<br>=0 for I/O<br>cards           | BVD2 has<br>gone low<br>0=No<br>1=Yes<br>=0 for I/O<br>cards                                                 | BVD1/<br>STSCHG#<br>has gone low<br>0=No<br>1=Yes                                     |

| 05h<br>45h<br><br>85h<br>C5h | STSCHG/# Inter-<br>rupt Configura-<br>tion Register | STSCHG/# Ro<br>0000=None<br>0001=IRQ1*<br>0010=IRQ2*<br>0010=IRQ3<br>0100=IRQ4<br>0101=IRQ5<br>0110=IRQ6*<br>0111=IRQ7 | uting                                                       | 1000=IRQ8*<br>1001=IRQ9<br>1010=IRQ10<br>1011=IRQ11<br>1100=IRQ12<br>1101=IRQ13*<br>1110=IRQ14<br>1111=IRQ15 |                                                                | STSCHG/#<br>on CD1-2#<br>Change<br>0=Disable<br>1=Enable                                                               | STSCHG/#<br>on RDY/<br>BSY# Low-<br>to-High<br>Change<br>0=Disable<br>1=Enable | STSCHG/#<br>on Battery<br>Warning<br>BVD2 High-<br>to-Low<br>Change<br>0=Disable<br>1=Enable                 | STSCHG/#<br>on Battery<br>Dead BVD1<br>High-to-Low<br>Change<br>0=Disable<br>1=Enable |

| 06h<br>46h<br><br>86h<br>C6h | Address Window<br>Enable Register                   | I/O<br>Window 1<br>0=Disable<br>1=Enable                                                                               | I/O<br>Window 0<br>0=Disable<br>1=Enable                    | Internal<br>MEMCS16<br>Decode<br>0=A[23:17]<br>1=A[23:12]                                                    | Memory<br>Window 4<br>0=Disable<br>1=Enable                    | Memory<br>Window 3<br>0=Disable<br>1=Enable                                                                            | Memory<br>Window 2<br>0=Disable<br>1=Enable                                    | Memory<br>Window 1<br>0=Disable<br>1=Enable                                                                  | Memory<br>Window 0<br>0=Disable<br>1=Enable                                           |

Table 2-1

General Purpose Register Group

\* These IRQs are driven back to the host, but the host may not recognize them.

#### 2.1 Power Control

Bits 02h[4:3] set the external VCC5-VCC3 pin levels directly. Bits 02h[1:0] set the external VPPPGM-VPPVCC pin levels directly. The interpretation of these signals depends on the external logic used. Socket Services must be aware of the hardware design in order to make the proper selections.

Table 2-2 below shows how the external control signals are interpreted by a typical power control chip, the Micrel 2560. Using this device allows the power control to be compatible with the Intel 82365SL definition. In the table, 'Disabled' = high impedance; 'Ground' indicates that the voltage source is actively clamped to ground.

# Table 2-2 Voltage Control Pin Interpretations using Micrel 2560 Chip

|                        |                        | 9                     | r                     | •                     |                       |

|------------------------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| VCC5/<br>bit<br>02h[4] | VCC3/<br>bit<br>02h[3] | Card Vcc<br>Selection | VPPPGM/<br>bit 02h[1] | VPPVCC/<br>bit 02h[0] | Card Vpp<br>Selection |

| 0                      | 0                      | Disabled              | 0                     | 0                     | Disabled              |

|                        |                        |                       | 0                     | 1                     | Disabled              |

|                        |                        |                       | 1                     | 0                     | Disabled              |

|                        |                        |                       | 1                     | 1                     | Ground                |

| 0                      | 1                      | 3.3V                  | 0                     | 0                     | Disabled              |

|                        |                        |                       | 0                     | 1                     | 3.3V                  |

|                        |                        |                       | 1                     | 0                     | 12V                   |

|                        |                        |                       | 1                     | 1                     | Ground                |

| 1                      | 0                      | 5V <sup>a</sup>       | 0                     | 0                     | Disabled              |

|                        |                        |                       | 0                     | 1                     | 5V                    |

|                        |                        |                       | 1                     | 0                     | 12V                   |

|                        |                        |                       | 1                     | 1                     | Ground                |

| 1                      | 1                      | 3.3V                  | 0                     | 0                     | Disabled              |

|                        |                        |                       | 0                     | 1                     | 3.3V                  |

|                        |                        |                       | 1                     | 0                     | 5V                    |

|                        |                        |                       | 1                     | 1                     | Ground                |

|                        |                        |                       |                       |                       |                       |

a. If the VS2 (5VDET) pin from the card is grounded, VCC5-VCC3 stay low when bits 02h[4:3]=10. This feature prevents 5V from being applied to a 3.3V-only card.

**Slot Vcc Threshold Scaling -** The threshold level of the chip input buffers is controlled by bit 02h[2] and is independent of the voltage control pin settings. This independent selection feature allows the designer to choose a voltage control chip with different control pin selection definitions than the Micrel 2560 part. The voltage threshold should be set by software according to the card voltage being enabled.

# 2.2 I/O Mapping Window Register Group

The I/O Window Registers contain bits that maintain Cirrus 6722 compatibility. Only the window address offset is shown. See below for calculation of base index address for each of the two available windows.

| Offset | Name                                             | 7                                                        | 6                                                       | 5                                                          | 4                                              | 3                                                        | 2                                                       | 1                                                          | 0                                              |  |

|--------|--------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------|------------------------------------------------|--|

| +7h    | I/O Window Con-<br>trol Register                 | Window 1<br>Additional<br>Wait States<br>0=None<br>1=One | Window 1<br>Zero-Wait 8-<br>bit Cycles<br>0=No<br>1=Yes | Window 1<br>Size Select<br>0=Use bit 4<br>1=Use<br>IOIS16# | Window 1<br>Data Size<br>0=8 bits<br>1=16 bits | Window 0<br>Additional<br>Wait States<br>0=None<br>1=One | Window 0<br>Zero-Wait 8-<br>bit Cycles<br>0=No<br>1=Yes | Window 0<br>Size Select<br>0=Use bit 0<br>1=Use<br>IOIS16# | Window 0<br>Data Size<br>0=8 bits<br>1=16 bits |  |

| +8h    | I/O Window Start<br>Address Register<br>low byte | I/O Window Sta                                           | D Window Start Address bits IOS[7:0]                    |                                                            |                                                |                                                          |                                                         |                                                            |                                                |  |

| +9h    | high byte                                        | I/O Window Sta                                           | art Address bits                                        | OS[15:8]                                                   |                                                |                                                          |                                                         |                                                            |                                                |  |

| +Ah    | I/O Window Stop<br>Address Register<br>low byte  | I/O Window Sto                                           | D Window Stop Address bits IOST[7:0]                    |                                                            |                                                |                                                          |                                                         |                                                            |                                                |  |

| +Bh    | high byte                                        | I/O Window Ste                                           | O Window Stop Address bits IOST[15:8]                   |                                                            |                                                |                                                          |                                                         |                                                            |                                                |  |

# Table 2-3 Index Addresses for I/O Window Registers

|                     |            |         | I/O Wi | ndow 0       |        |         | I/O Wi | ndow 1       |        |

|---------------------|------------|---------|--------|--------------|--------|---------|--------|--------------|--------|

| I/O Window<br>Index | I/O Window | Start A | ddress | Stop Address |        | Start A | ddress | Stop Address |        |

| Address for:        | Control    | (low)   | (high) | (low)        | (high) | (low)   | (high) | (low)        | (high) |

| Slot A              | 07h        | 08h     | 09h    | 0Ah          | 0Bh    | 0Ch     | 0Dh    | 0Eh          | 0Fh    |

| Slot B              | 47h        | 48h     | 49h    | 4Ah          | 4Bh    | 4Ch     | 4Dh    | 4Eh          | 4Fh    |

| Slot C              | 87h        | 88h     | 89h    | 8Ah          | 8Bh    | 8Ch     | 8Dh    | 8Eh          | 8Fh    |

| Slot D              | C7h        | C8h     | C9h    | CAh          | CBh    | CCh     | CDh    | CEh          | CFh    |

# 2.3 Memory Mapping Window Register Group

Only the window address offset is shown. See below for calculation of base index address for each of the five available windows.

| Offset | Name                                                    | 7                                                       | 6                                           | 5                                  | 4                                  | 3           | 2              | 1                 | 0         |

|--------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------|------------------------------------|------------------------------------|-------------|----------------|-------------------|-----------|

| +0h    | Memory Window<br>Start Address<br>Register<br>low byte  | Memory Mapp                                             | ng Window Star                              | t Address bits M                   | S[19:12]                           |             |                |                   |           |

| +1h    | high byte                                               | Data Path<br>0=8 bits<br>1=16 bits                      | Zero Wait<br>States<br>0=No<br>1=Yes        | Reserved. Wr                       | ite bits as read.                  | Memory Mapp | ing Window Sta | rt Address bits M | S[23:20]  |

| +2h    | Memory Window<br>Stop Address<br>Register<br>low byte   | Memory Mapp                                             | ng Window Stop                              | Address bits M                     | ST[19:12]                          |             |                |                   |           |

| +3h    | high byte                                               | Command Len<br>00=Two<br>01=Three<br>10=Four<br>11=Five | gth (ATCLKs)                                | Reserved.<br>Write bit as<br>read. | Reserved.<br>Write bit as<br>read. | Memory Mapp | ing Window Sto | p Address bits M  | ST[23:20] |

| +4h    | Memory Window<br>Offset Address<br>Register<br>Iow byte | Memory Mapp                                             | ng Window Offs                              | et Address bits I                  | MOFST[19:12]                       |             |                |                   |           |

| +5h    | high byte                                               | Window<br>Write Control<br>0=Enabled<br>1=Disabled      | Memory<br>Access<br>0=Common<br>1=Attribute |                                    |                                    |             |                |                   |           |

**Zero Wait States** - This setting enables shorter cycles for faster PCMCIA cards. Refer to the "CISA Cycle Controller" section of this document to determine the effect of this bit.

**Command Length** - This value selects the command length for both 8-bit and 16-bit windows. In the 82365SL part, this value controls only 16-bit windows.

Calculation of addresses for all memory windows: Add the offset shown in the table above to the Index Base for the desired slot and window listed below.

| Index Base<br>For: | Window 0 | Window 1 | Window 2 | Window 3 | Window 4 |

|--------------------|----------|----------|----------|----------|----------|

| Slot A             | 10h      | 18h      | 20h      | 28h      | 30h      |

| Slot B             | 50h      | 58h      | 60h      | 68h      | 70h      |

| Slot C             | 90h      | 98h      | A0h      | A8h      | B0h      |

| Slot D             | D0h      | D8h      | E0h      | E8h      | F0h      |

# Table 2-4 Index Base Addresses for Memory Windows

#### 2.4 Special PCMCIA/82C852 PCMCIA Registers

The 82C852 logic provides compatibility with the Intel 82365SL PCMCIA chipset. In addition, certain Cirrus 6722 PCMCIA chipset features are implemented. Since there are register conflicts between these two devices in certain locations, the 82C852 logic implements the register features as noted below.

#### 2.4.1 DMA on the PCMCIA Interface

DMA operations are described with respect to system memory access. During a DMA write, data is transferred from a PC Card to system memory. During a DMA read, data is transferred from system memory to a PC Card. Address lines to the PC Card are ignored during DMA operations. DMA signals are defined as follows for the PCMCIA interface.

**DREQ#.** The DMA Request signal DREQ# is only available when a PC Card and socket are configured for DMA operations. Note that DREQ# is active low, opposite to the traditional ISA bus sense of the signal. A PC Card asserts DREQ# to indicate to the host that it is requesting service. The PC Card asserts DREQ# until the host responds by asserting DACK. A PC Card may use any one of the following three pins for DREQ#: SPKR#, INPACK# or IOIS16#. The PC Card indicates the pin used for DREQ# in the Miscellaneous Features Field of the card configuration header (CIS). **DACK.** A DMA transfer is indicated when DACK is active along with either IORD# or IOWR#. Note that DACK is active high, opposite to the traditional ISA bus sense of the signal. The 82C852 chip uses the card REG# pin to indicate a DMA operation. The card must be programmed for an I/O interface before the DMA interface can be enabled. The DACK(REG#) signal is then used to distinguish between a DMA cycle and a normal I/O cycle. For a normal I/O cycle, REG# is held low for the complete bus cycle. For a DMA transfer, REG# is held high during the entire DMA bus cycle.

**TC.** The 82C852 chip signals terminal count for DMA read operations by asserting WE# along with IOWR#, and for DMA write operations by asserting OE# along with IORD#.

# 2.4.2 DMA Control Register

The DMA Control Register uses a similar format to that available in the Cirrus 6722 register set at offset 3Fh for its upper 3 bits; however, bits [4:0] are different. Bits [2:0] select the DMA channel because, unlike the Cirrus controller, the 82C852 controller generates all DMA channel requests directly (it does not depend on the host to redirect the DREQ/DACK lines). Bits [4:3] allow enabling of built-in pull-up resistors that are not available on the Cirrus part.

| Index                        | Name                    | 7                                                                             | 6                   | 5                                                                      | 4                                                                     | 3                                                                    | 2                                                                                                               | 1 | 0 |

|------------------------------|-------------------------|-------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---|---|

| 3Fh<br>7Fh<br><br>BFh<br>FFh | DMA Control<br>Register | DREQ# Select<br>00=No DMA fu<br>01=Use INPAC<br>10=Use IOIS16<br>11=Use SPKR; | nction<br>CK#<br>6# | CD1-2# and<br>VS1-2 Pull-<br>ups<br>0=Enable<br>(default)<br>1=Disable | BVD1-2,<br>RDY/BSY#<br>Pull-ups<br>0=Disable<br>(default)<br>1=Enable | INPACK#,<br>WAIT# Pull-<br>ups<br>0=Disable<br>(default)<br>1=Enable | DMA Channel<br>000=DRQ0<br>001=DRQ1<br>010=DRQ2<br>011=DRQ3<br>100=Reserved<br>101=DRQ5<br>110=DRQ6<br>111=DRQ7 |   |   |

**DREQ# Select -** These bits select the pin that will be used to provide the DREQ# signal to the PCMCIA card. Most PCM-CIA cards will be able to sacrifice INPACK# for the DREQ# function; the IOIS16# and SPKR# pins are offered as alternatives. The "No DMA function" disables the DMA feature altogether and eliminates the need for the bit 1Eh[6] used by the Cirrus 6722 to enable DMA operation.

**CD1-2# and VS1-2 Pull-ups -** The PCMCIA card detect (CD1-2) and voltage sense (VS1-2) lines are normally pulled up internal to the 82C852 chip to avoid the need for external resistors. The control bit is provided to disable these resistors during power-down situations.

**DMA Channel** - These bits indicate the system DMA channel to which the DREQ will be directed. DRQ0-3 are 8-bit channels; DRQ5-7 are 16-bit channels. These bits are **not** present in the Cirrus 6722 part.

# 2.4.3 ATA Interface

The ATA Control Register is provided to allow a minor redefinition of the interface to accommodate ATA interface devices, normally IDE types of devices such as disk drives and Flash EEPROM cards. This register is not strictly compatible with the register at offset 26h in the Cirrus 6722 register set.

| Index                        | Name                      | 7                     | 6                     | 5                   | 4                      | 3                      | 2                                                | 1                                                | 0                                      |

|------------------------------|---------------------------|-----------------------|-----------------------|---------------------|------------------------|------------------------|--------------------------------------------------|--------------------------------------------------|----------------------------------------|

| 3Eh<br>7Eh<br><br>BEh<br>FEh | ATA Control Reg-<br>ister | A25 (CSEL<br>Control) | A24 (M/S#<br>Control) | A23 (VU<br>Control) | A22 (Misc.<br>Control) | A21 (Misc.<br>Control) | Card RESET<br>Polarity<br>0=Normal<br>1=Inverted | Card IREQ#<br>Polarity<br>0=Normal<br>1=Inverted | Interface<br>Mode<br>0=PCMCIA<br>1=ATA |

**Interface Mode -** Selecting ATA mode changes operation as follows: 1) Bits 3Eh[7:3] are enabled to manually control address bits A[25:21] to the card. 2) CE1# takes on the IDE function of CS1# which goes low when address bit A9 is low (address range 1F0-1F7h or 170-177h). 3) CE2# takes on the IDE function of CS3# which goes low when address bit A9 is high (address range 3F6-3F7h or 376-377h). For proper operation of a card with this type of interface, it is also necessary to program the I/O Mapping Windows to the 1F0-1F7h (or 170-177h) range and to the 3F6-3F7h (or 376-377h) range.

#### 2.4.4 Control Registers

The 82C852 slot interface implements the VS1 and VS2 signals. The new PCMCIA specification allows VS1-2 to be used in determining whether a card can be powered up at 5V or not according to Table 2-5. This information pertains to the Miscellaneous Control Register at offset 16h, described below.

| VS2    | VS1    | Key on PC Card | PCMCIA Card Type Indicated       |

|--------|--------|----------------|----------------------------------|

| Open   | Open   | 5V             | 5V R2 card                       |

| Open   | Ground | Low Voltage    | 3.3V R2 card                     |

| Open   | Ground | 5V             | 3.3V or 5V R2 card               |

| Ground | Open   | Low Voltage    | Low Voltage R2 card              |

| Ground | Ground | Low Voltage    | Low Voltage or 3.3V R2 card      |

| Ground | Ground | 5V             | Low Voltage, 3.3V, or 5V R2 card |

Table 2-5 VS1-2 Status Indication for PCMCIA Cards

#### 2.4.4.1 Miscellaneous Control Register

At offset 16h, the Intel 82365SL implements the Card Detect and General Control Register, while the Cirrus 6722 part implements Miscellaneous Control Register 1. The 82C852 controller register at this offset incorporates bits from both of these registers and is therefore **not** strictly compatible with either.

| Index                        | Name                      | 7                                                          | 6                                                                          | 5                                                                              | 4                                   | 3                                                                       | 2                              | 1                                          | 0                                         |

|------------------------------|---------------------------|------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------|--------------------------------|--------------------------------------------|-------------------------------------------|

| 16h<br>56h<br><br>96h<br>D6h | Misc. Control<br>Register | Back-to-<br>Back 8-bit<br>Timing<br>(ATCLKS)<br>0=3<br>1=1 | TC Timing<br>0=PCMCIA<br>standard<br>1=Stays<br>active past<br>end of cmd. | Reset Config-<br>uration Reg-<br>isters if CD1-<br>2# go high<br>0=No<br>1=Yes | SPKROUT<br>0=Tri-stated<br>1=Driven | SPKROUT<br>Drive Option<br>0 = Shared<br>(CISA)<br>1 = Always<br>driven | Reserved.<br>Write as<br>read. | VS1 Status<br>0=Low<br>1=High<br>Read-only | VS2 Status<br>0=3.3V<br>1=5V<br>Read-only |

**Back-to-Back 8-bit Timing** - Bit 16h[7] provides control over bus conversion timing. The default setting separates the second half of a 16-to-8-bit conversion from the first by three ATCLKs. Since this issue is not strictly dealt with in the PCM-CIA specification, 8-bit cards that have no back-to-back restrictions can provide better performance by setting this bit to 1 for a single intervening clock.

**TC Timing** - Bit 16h[6] is provided to control the duration of Terminal Count (TC) to the PCMCIA DMA card. While the

PCMCIA specification requires that TC be taken away before command, the Cirrus data book shows TC asserted even after the command edge. DMA cards designed to latch TC on the rising edge of command must set 16h[6]=1.

#### 2.4.4.2 Global Control Register

Only one bit of this Intel 82365SL register is implemented. The other bits correspond to IRQ manipulation that is unnecessary in the 82C852 chip.

| Index                        | Name                       | 7                              | 6                              | 5                              | 4                              | 3                              | 2                                                                                               | 1                              | 0                              |

|------------------------------|----------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|

| 1Eh<br>5Eh<br><br>9Eh<br>DEh | Global Control<br>Register | Reserved.<br>Write as<br>read. | Reset<br>Change Sta-<br>tus<br>0=On Status<br>Change Reg-<br>ister read<br>1=On Write<br>to bit | Reserved.<br>Write as<br>read. | Reserved.<br>Write as<br>read. |

**Reset Change Status** - Bit 1Eh[2] selects the mode used to clear status change events in the Card Status Change Register at offset 04h. In its default setting of 1Eh[2]=0, the status change events are all cleared at once every time the register at offset 04h is read. If 1Eh[2]=1, reading the register at offset 04h does not clear any events. To clear each event, software must write a 1 to the bit position at offset 04h that indicated status change event. Effectively, writing back the same value read will clear the status change event.

# 2.4.4.3 Miscellaneous Control Register 2 (Not Implemented)

The Cirrus 6722 part provides a different register at offset 1Eh. Its bit functions are not needed in the 82C852 chipset for the following reasons.

**IRQ15, IRQ12 Assignment** - The assignment of an interrupt line to signals such as RI is a function of the host chipset in OPTi architecture.

**Port 3F7 bit 7 Sharing** - The conflict between these ports is resolved by the host chipset in OPTi architecture.

# Core Voltage - Core voltage threshold selection is a strap option on the 82C852 chip.

**Clock Source** - The timing on the 82C852 part is provided only by ATCLK.

# 3.0 82C852 Pin Description

The 82C852 chip runs CISA cycles on the host side, and PCMCIA cycles on the slot interface side.

# 3.1 Host Interface Signals

Table 3-1 lists the signals that link the 82C852 chip to the system CISA bus.

| Name      | Туре          | Pin No.                  | Description                                                                                                                                                                                                                                                                                                                                                     |

|-----------|---------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAD[15:0] | I/O           | 24, 22-16,<br>14-11, 9-6 | Multiplexed bus used to transfer address, command, data, IRQ, DRQ, DACK information.                                                                                                                                                                                                                                                                            |

| ATCLK     | I             | 27                       | Standard AT clock. CISA device uses rising edge to clock in the first (address) phase.                                                                                                                                                                                                                                                                          |

| ALE       | I             | 25                       | Standard AT address latch enable. CISA peripheral device uses rising edge of ALE to latch the second (address and command) phase. CISA host uses falling edge of ALE to latch CMD# from peripheral device.                                                                                                                                                      |

| CMD#      | I             | 31                       | Command indication. Common to host and all devices on the CISA bus. The CISA host asserts CMD# during the data phase of the cycle to time the standard ISA command (IORD#/WR#, MRD#/WR#), and also asserts CMD# to acknowledge SEL#ATB#.                                                                                                                        |

| SEL#/ATB# | O<br>tristate | 29                       | Device selected / AT bus backoff request. Common to all peripheral devices on the CISA bus. When ALE is high, the CISA device asserts SEL# to indicate to the host that it is claiming the cycle. When ALE is low, the CISA device drives this signal to indicate that it has an interrupt and/or DMA request to make; the host acknowledges by asserting CMD#. |

| IOCHRDY   | O<br>tristate | 28                       | Standard AT cycle extension request signal during memory and I/O cycles. Dur-<br>ing IRQ and DRQ drive-back cycles, the CISA device uses this signal as a com-<br>mand output to run the drive-back cycle to the host.                                                                                                                                          |

| RSTDRV    | I             | 26                       | Standard AT-bus reset signal.                                                                                                                                                                                                                                                                                                                                   |

| SPKROUT   | 0             | 32                       | Speaker output from slot interface. This signal is driven according to the CISA specification.                                                                                                                                                                                                                                                                  |

Table 3-1 Compact ISA (CISA) Interface Signals

# 3.2 Power Control Signals

Table 3-2 lists the power control bus signals. These signals select the correct Vcc and Vpp voltages to the PCMCIA card. A power control chip such as the Micrel 2560 can be used to interpret these signals to apply the correct voltage levels to the PCM-CIA card.

These pins are also strap options. Refer to the "Strap-Selected Interface Options" section for details.

| Name   | Туре | Pin No. | Description                          |

|--------|------|---------|--------------------------------------|

| VCC5   | 0    | 1       | 5V Vcc Enable                        |

| VCC3   | 0    | 2       | 3.3V Vcc Enable                      |

| VPPPGM | 0    | 5       | 12V Vpp Enable                       |

| VPPVCC | 0    | 4       | Vpp Enable as currently selected Vcc |

# Table 3-2 Slot Power Control Signals

# 3.3 Slot Interface Signals

The slot interface is a complete set of buffered signals to the PCMCIA card slot as listed in Table 3-3.

| Name        | Туре | Pin No.                                                                                                                  | Description                                                    |

|-------------|------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| CD1#        | I    | 33                                                                                                                       | Card Detect 1                                                  |

| CD2#        | I    | 98                                                                                                                       | Card Detect 2                                                  |

| VS1         | I    | 100                                                                                                                      | Voltage Sense 1                                                |

| VS2         | I    | 99                                                                                                                       | Voltage Sense 2                                                |

| SPKR        | I    | 86                                                                                                                       | Speaker input (SPKR - R2 I/O card)                             |

| DREQ# alt.2 |      |                                                                                                                          | DREQ# alternative 2                                            |

| BVD2        |      |                                                                                                                          | Battery Low Voltage Detect pin 2 (BVD2 - R1 or R2 memory card) |

| STSCHG#     | I    | 88                                                                                                                       | Status Change Interrupt, active low (STSCHG# - R2 I/O card)    |

| BVD1        |      |                                                                                                                          | Battery Low Voltage Detect pin 1 (BVD1 - R1 or R2 memory card) |

| IREQ        | I    | 64                                                                                                                       | Interrupt Request (IREQ - R2 I/O card)                         |

| RDY/BSY#    |      |                                                                                                                          | Ready/Busy (RDY/BSY# - R1 or R2 memory card)                   |

| RESET       | 0    | 77                                                                                                                       | Card Reset, active high (R2 cards)                             |

| A[25:0]     | I    | 74, 72, 70, 68,<br>65, 63, 61, 59,<br>57, 67, 69, 60,<br>58, 71, 51, 47,<br>54, 56, 73, 75,<br>76, 78, 81, 83,<br>85, 87 | Address lines [25:0]                                           |

| D[15:0]     | I/O  | 46, 44, 42, 38,<br>36, 96, 94, 92,<br>43, 39, 37, 35,<br>34, 95, 93, 89                                                  | Data Lines [15:0]                                              |

| WAIT#       | I    | 80                                                                                                                       | Wait                                                           |

| IOCHRDY     |      |                                                                                                                          |                                                                |

| IOIS16#     | I    | 97                                                                                                                       | 16-bit I/O indication (I/O card)                               |

| DREQ# alt.3 |      |                                                                                                                          | DREQ# alternative 3 (DMA I/O card)                             |

| WP          |      |                                                                                                                          | Write Protect (memory only card)                               |

| IORD#       | 0    | 52                                                                                                                       | I/O Read                                                       |

| IOWR#       | 0    | 55                                                                                                                       | I/O Write                                                      |

| CE2-1#      | -    | 48, 45                                                                                                                   | Upper/Lower Byte Enable                                        |

| WE#         | 0    | 62                                                                                                                       | Memory Write                                                   |

| TC          |      |                                                                                                                          | Terminal Count (along with IOWR#)                              |

| OE#         | 0    | 49                                                                                                                       | Memory Read                                                    |

| TC          |      |                                                                                                                          | Terminal Count (along with IORD#)                              |

| REG#        | 0    | 84                                                                                                                       | Attribute register space select                                |

| DACK        |      |                                                                                                                          | DMA acknowledge                                                |

#### Table 3-3 82C852 Slot Interface Bus

| Name        | Туре | Pin No. | Description         |

|-------------|------|---------|---------------------|

| INPACK      | I    | 82      | Input acknowledge   |

| DREQ# alt.1 |      |         | DREQ# alternative 1 |

# Table 3-3 82C852 Slot Interface Bus (cont.)

# 3.4 Power and Ground Signals

Table 3-4 lists the chip power and ground signals. COREVCC and SLOTVCC can be individually selected to be either 3.3V or 5V. However, only SLOTVCC can be changed dynamically. The COREVCC level must be indicated to the logic at reset time through ALE, as described in the CISA Specification (Appendix A).

#### Table 3-4 Chip Power and Ground Signals

| Name    | Pin No.                    | Description                                    |

|---------|----------------------------|------------------------------------------------|

| COREVCC | 3, 10, 23                  | Power to CISA interface and core logic of chip |

| SLOTVCC | 41, 53, 91                 | Power to PCMCIA slot interface                 |

| VSS     | 15, 30, 40, 50, 66, 79, 90 | Ground                                         |

#### 3.5 Internal pull-up Resistors

The 82C852 slot interfaces are provided with pull-up resistors internal to the chip. The Pull-ups are active at the times indicated in Table 3-5.

| Table 3-5 | Internal  | aull-up | Resistor  | Scheme    |

|-----------|-----------|---------|-----------|-----------|

|           | mitorinai | pan ap  | 110010101 | 001101110 |

| Signal     | Pull-up Scheme                                                                                                                                                                                                                     | Control<br>Register Bit |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| CD1#, CD2# | Card Detect lines are pulled up to core Vcc by default. After card insertion, these lines will be pulled low by the card. These resistors can be disabled to save power by setting configuration register bit 3Fh[5].              | 3Fh[5]                  |

| VS1, VS2   | Voltage sense lines are pulled up to core Vcc by default. After card insertion, these lines will be pulled low by a low voltages card. These resistors can be disabled to save power by setting configuration register bit 3Fh[5]. | 3Fh[5]                  |

| BVD1, BVD2 | Battery Voltage Detect line Pull-ups should be enabled only for memory-only interface cards.                                                                                                                                       | 3Fh[4]                  |

| RDY/BSY#   | Ready/Busy line pull-up should be enabled only for memory-only interface cards.                                                                                                                                                    | 3Fh[4]                  |

| INPACK#    | Input acknowledge line pull-up should be enabled only for I/O interface cards.                                                                                                                                                     | 3Fh[3]                  |

| WAIT#      | Wait line pull-up should be enabled only for I/O interface cards.                                                                                                                                                                  | 3Fh[3]                  |

| VPPPGM     | Vpp program voltage control is pulled up only at reset time to sense the slot options.                                                                                                                                             |                         |

| VPPVCC     | Vcc program voltage control is pulled up only at reset time to sense the slot options.                                                                                                                                             |                         |

#### 3.6 Strap-Selected Interface Options

The 82C852 PCMCIA Controller can be strapped to operate in one of several different modes depending on its implementation in the system.

Strap options are registered at chip reset time. While a tristate buffer could be used to drive these signals only at reset, in most designs the selection straps are normally 10k ohm resistors engaged full-time. The cost of this approach is as follows. During actual use the resistors consume power only while programming voltage is selected to the cards, at which time the additional current draw for a 5V system would only be as high as 5V/10k ohm = 0.5mA.

The VPPPGM and VPPVCC power control pins will go high as long as the RSTDRV input to the chip is active. At this time, the VCC5 and VCC3 power control pins stay low, so no Vpp will be enabled for power control devices such as Micrel 2560 part. However, if another power control device is used, it *must* disable card Vpp when card Vcc is disabled. Otherwise, damage to the PCMCIA card could occur.

The strap on VCC5 is a special case. It must pull *high* at reset to select the secondary I/O ports 3E2h and 3E3h. However, this action can cause a card plugged into the slot to be momentarily powered up. If this situation is undesirable, use RSTDRV to gate VCC5 to the power control device.

The slot strapping possibilities are listed in Table 3-6.

| To Select:       | So that 82C852 responds to I/O accesses<br>at 3E1h (3E3h) for this range of values<br>written to 3E0h (3E2h): | These lines must be strapped at reset: |

|------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Primary Slot A   | 3E0/1h, 00-3Fh                                                                                                | None                                   |

| Primary Slot B   | 3E0/1h, 40-7Fh                                                                                                | Pull VPPPGM low                        |

| Primary Slot C   | 3E0/1h, 80-BFh                                                                                                | Pull VPPVCC low                        |

| Primary Slot D   | 3E0/1h, C0-FFh                                                                                                | Pull VPPPGM, VPPVCC low                |

| Secondary Slot A | 3E2/3h, 00-3Fh                                                                                                | Pull VCC5 high                         |

| Secondary Slot B | 3E2/3h, 40-7Fh                                                                                                | Pull VCC5 high, VPPPGM low             |

| Secondary Slot C | 3E2/3h, 80-BFh                                                                                                | Pull VCC5 high, VPPVCC low             |

| Secondary Slot D | 3E2/3h, C0-FFh                                                                                                | Pull VCC5 high, VPPPGM + VPPVCC lov    |

#### Table 3-6 Strap Options for 82C852 Slot Configurations

# 3.7 Test Mode

The chip provides several test modes that are selected at reset time through a strap option. Table 3-7 illustrates the strapping needed to enter Test Mode.

Table 3-7

Strap Option for 82C852 Test Mode

| To Select:       | Need pull up at reset on this line: |

|------------------|-------------------------------------|

| Normal Operation | None                                |

| Test Mode        | VCC3                                |

Table 3-8 shows the various tests selectable when Test Mode is enabled. Most modes are intended for factory testing only. The "tristate all outputs" mode may be useful for testing a finished board by allowing the component to effectively disappear from the circuit.

#### Table 3-8 Strap Options for Test Functions

| To Select:                        | Need pull down at reset on these lines: |

|-----------------------------------|-----------------------------------------|

| NAND Gate                         | None                                    |

| Drive alternate lines<br>high/low | VPPPGM                                  |

| Drive alternate lines<br>low/high | VPPVCC                                  |

| Tristate all outputs              | VPPPGM and VPPVCC                       |

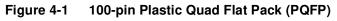

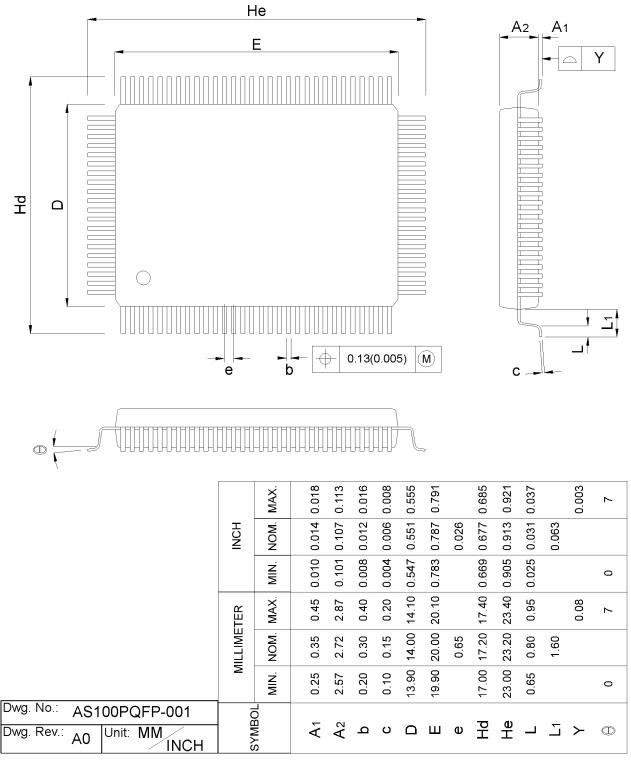

# 4.0 Mechanical Packages

# 82C852

DP111

Page 16

# A. Compact ISA Specification

This document describes a new OPTi interface that will be used to interface the 82C852 PCMCIA Controller to OPTi system controller chipsets. This interface may also be used to interface OPTi peripheral products in the future. The interface is OPTi-proprietary, and may be licensed to others in the future.

# A.1 Compact ISA Overview

The Compact ISA interface coexists with the standard ISA interface. Chips that support the Compact ISA interface enjoy a reduced ISA pin count because address signals and command information are strobed in on the SD[15:0] bus. ISA pins eliminated are:

- SA[23:0] (24 pins)

- IORD#, IOWR#, MRD#, MWR#, SMRD#, SMWR#, SBHE#, NOWS#, AEN, IO16#, M16# (11 pins)

- IRQ3, 4, 5, 6, 7, 10, 11, 12, 14, 15; DRQ/DACK#0, 1, 2, 3, 5, 6, 7, and TC (25 pins)

Compact ISA defines only two new signals, CMD# and SEL#/ATB#, for a total requirement of 22 pins. The pin count reduction over standard ISA is 58 pins. Compact ISA performance is comparable with that of 16-bit ISA bus peripheral devices. Moreover, Compact ISA does not interfere with standard ISA operations. The complete signal set of Compact ISA, referred to in the descriptions as CISA, is shown below.

| Name                        | Type <sup>a</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAD[15:0]                   | I/O               | Multiplexed bus used to transfer address, command, data, IRQ, DRQ, DACK information.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ATCLK                       | I                 | Standard AT clock. CISA device uses rising edge to clock in the first (address) phase.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ALE                         | I                 | Standard AT address latch enable. CISA peripheral device uses rising edge of ALE to latch the second (address and command) phase. CISA host uses falling edge of ALE to latch CMD# from peripheral device.                                                                                                                                                                                                                                                                                             |

| CMD#                        | I                 | Command indication. Common to host and all devices on the CISA bus. The CISA host asserts CMD# during the data phase of the cycle to time the standard ISA command (IORD#/WR#, MRD#/WR#), and also asserts CMD# to acknowledge SEL#ATB#.                                                                                                                                                                                                                                                               |

| SEL#/ATB#<br>(also CLKRUN#) | O<br>tristate     | Device selected / AT bus backoff request. Common to all peripheral devices on the CISA bus. When ALE is high, the CISA device asserts SEL# to indicate to the host that it is claiming the cycle. When ALE is low, the CISA device drives this signal to indicate that it has an interrupt and/or DMA request to make; the host acknowledges by asserting CMD#. After the host has preset the CISA device in a Stop Clock mode, the device can assert this signal asynchronously to restart the clock. |

| IOCHRDY                     | O<br>tristate     | Standard AT cycle extension request signal during memory and I/O cycles.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RSTDRV                      | I                 | Standard AT-bus reset signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table A-1 Compact ISA (CISA) Interface Signals

a. (Peripheral side)

# A.2 Compact ISA Cycle Definition

The MAD[15:0] lines contain different information for each phase of the bus cycle. The use of these lines varies according to whether a memory cycle or an I/O cycle is being run. Certain cycle definition bits are common to all cycles, as shown in Table A-2.

| Signal | Phase 1                                                                                            | Phase 2                                                                                           |

|--------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| MAD0   | M/IO# indication bit; used to determine the cycle type.                                            | W/R# indication bit                                                                               |

| MAD1   | I/D# indication bit. It is always 0 if M/IO#=1, and selects between I/O and DMA cycles if M/IO#=0. | SBHE# indication bit                                                                              |

| MAD2   | Usage varies.                                                                                      | ISA# timing indication bit; described in the "Perfor-<br>mance Control" section of this document. |

#### **Retained Values**

Entries marked "same" retain the same value as in the previous phase, in order to reduce transitions where possible. However, the CISA peripheral device decode logic must **not** assume that these values will be stable. The bits may be reassigned in the future.

# A.2.1 Memory Cycle

The MAD[15:0] bit meanings for each phase of a memory cycle are shown below. The M/IO# bit is always 1 for memory cycles.

| Phase | MAD<br>15 | MAD<br>14 | MAD<br>13 | MAD<br>12 | MAD<br>11 | MAD<br>10 | MAD<br>9 | MAD<br>8 | MAD<br>7 | MAD<br>6 | MAD<br>5 | MAD<br>4 | MAD<br>3 | MAD<br>2 | MAD<br>1   | MAD<br>0    |

|-------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|------------|-------------|

| 1     | SA23      | SA22      | SA21      | SA20      | SA19      | SA18      | SA17     | SA16     | SA15     | SA14     | SA13     | SA12     | SA11     | SA10     | I/D#<br>=0 | M/IO#<br>=1 |

| 2     | SA9       | SA8       | SA7       | SA6       | SA5       | SA4       | SA3      | SA2      | SA1      | SA0      | same     | same     | same     | ISA#     | SBHE#      | W/R#        |

| 3     | SD15      | SD14      | SD13      | SD12      | SD11      | SD10      | SD9      | SD8      | SD7      | SD6      | SD5      | SD4      | SD3      | SD2      | SD1        | SD0         |

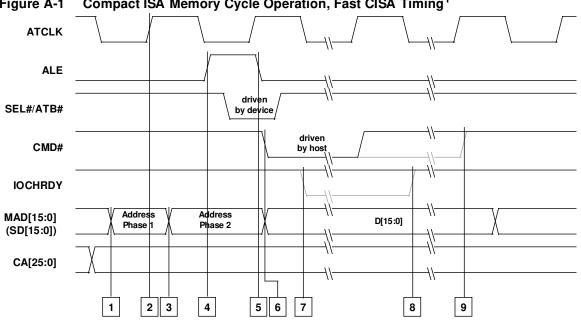

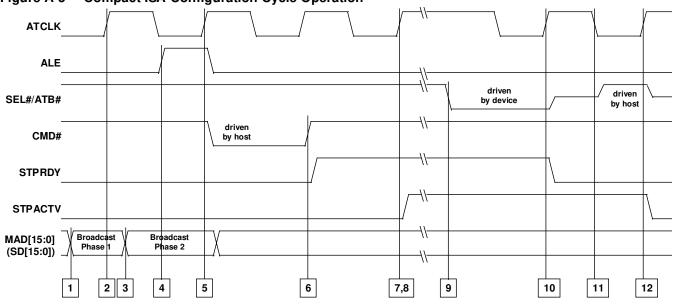

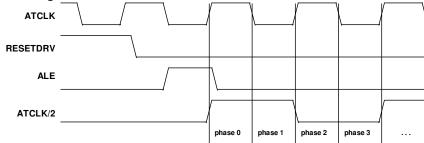

The general structure of Compact ISA memory cycles is shown in Figure A-1 and Figure A-2.

Figure A-1 Compact ISA Memory Cycle Operation, Fast CISA Timing<sup>1</sup>

- 1 CISA host gets address from the CPU address lines and byte enable lines. The host then drives out A[23:10] + M/IO# on MAD[15:0] with M/IO# high (memory).

- 2. CISA peripheral device latches address and M/IO# on the rising edge of ATCLK and decodes the information.

- Host drives out remaining address + Command on MAD[15:0]. 3.

- Host asserts ALE. If cycle belongs to CISA peripheral device, it asserts SEL# and latches the address and command 4. from MAD[15:0] on the rising edge of ALE. Device latches ISA#=1 at this time.

- 5. Host and other CISA devices recognize the SEL# function of SEL#/ATB# by seeing ALE high when sampling SEL#/ ATB# low on the rising edge of ATCLK. Host de-asserts ALE and stops driving address on this rising ATCLK edge.

- For reads, the host tristates the MAD[15:0] buffers. For writes, it drives the write data onto MAD[15:0]. Host asserts 6. CMD# synchronous to the rising edge of ATCLK and can optionally inhibit its MRD#/MWR# lines.

- 7. Cycle is 0 wait states as indicated by ISA#=1. CISA peripheral device can bring IOCHRDY low asynchronously after CDM# goes active to extend the cycle.

- Device brings IOCHRDY high synchronous to the falling edge of ATCLK to allow cycle completion. 8.

- 9. Host de-asserts CMD# on the same rising edge where it samples IOCHRDY high.

<sup>1.</sup> Cycle optionally extended by IOCHRDY shown in gray.

# 82C852

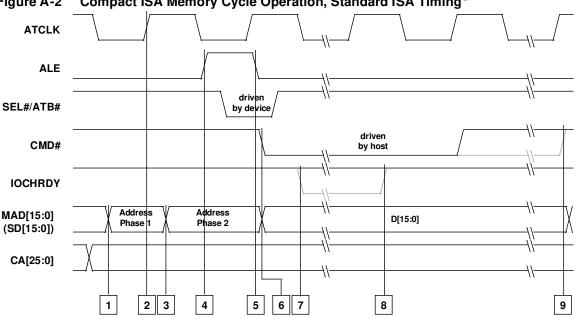

Compact ISA Memory Cycle Operation, Standard ISA Timing<sup>1</sup> Figure A-2

- CISA host gets address from the CPU address lines and byte enable lines. The host then drives out A]23:10] + M/IO# on 1. MAD[15:0] with M/IO# high (memory).

- CISA peripheral device latches address and M/IO# on the rising edge of ATCLK and decodes the information. 2.

- Host drives out remaining address + Command on MAD[15:0]. 3.

- Host asserts ALE. If cycle belongs to CISA peripheral device, it asserts SEL# and latches the address and command 4. from MAD[15:0] on the rising edge of ALE. Device latches ISA#=0 at this time.

- 5. Host and other CISA devices recognize the SEL# function of SEL#/ATB# by seeing ALE high when sampling SEL#/ ATB# low on the rising edge of ATCLK. Host de-asserts ALE and stops driving address on this rising ATCLK edge.

- 6. For reads, the host tristates the MAD[15:0] buffers. For writes, it drives the write data onto MAD[15:0]. Host asserts CMD# synchronous to the rising edge of ATCLK and can optionally inhibit its MRD#/MWR# lines.

- Cycle is not zero wait states, as indicated by ISA#=0. CISA peripheral device can bring IOCHRDY low asynchronously 7. after CDM# goes active to extend the cycle further.

- 8. Device brings IOCHRDY high asynchronously to allow cycle completion.