# **ST9 FAMILY** 8/16 BIT MCU

PROGRAMMING

1<sup>st</sup> EDITION

S

RY

**ST9 FAMILY PROGRAMMING**

**NOS**

HOMSON OELECTRONICS 100

## ST9 FAMILY 8/16 BIT MCU

PROGRAMMING

1<sup>st</sup> EDITION

**MARCH 1991**

#### USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED

SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics. As used herein:

- Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### —— GENERAL INDEX ————

| Fac                         |            |

|-----------------------------|------------|

|                             |            |

| DRESS SPACES                | 1          |

| EMORY SEGMENTS              | 2          |

| GISTER FILE                 | 2          |

| TA LENGTHS                  | 4          |

| DRESSING MODES              |            |

| STEM GROUP                  | 9          |

| STRUCTION SET SUMMARY       | 16         |

| STRUCTION SET DESCRIPTION 2 | <u>2</u> 4 |

| CII CHARACTER SET           | 18         |

. . . .

## ST9

### **PROGRAMMING MANUAL**

#### INTRODUCTION

The ST9 8/16 bit microcontroller family introduces a new generation of single-chip architecture. It offers fast program execution, efficient use of memory, sophisticated interrupt handling, input/output (I/O) flexibility and bit-manipulation capabilities, with easy system expansion. Virtually all of the ST9 configuration can be tailored to the needs of the user under program control. This enables the ST9 to serve as an I/O intensive microcontroller, as an intelligent peripheral controller within a larger system, or as a memory intensive microprocessor.

SGS-THOMSON MICROELECTRONICS

Programming of the ST9 is made easy in both high level languages such as C, or directly in assembler language, by the versatility of the 14 addressing modes coupled with the comprehensive instruction set operating on bits, BCD, 8 bit bytes and 16 bit words. The availability of the Register File, giving the programmer multiple 8 and 16 bit accumulators and index pointers, the fast interrupt response time, on-chip DMA and on-chip and external memory access capabilities give the ST9 a high efficiency for real-time control applications.

The ST9 has a range of family devices made up from various memory combinations (RAM, ROM/EPROM, EEPROM), powerful peripherals such as Multifunction Timers, Analog to Digital Converters, Serial Communications Interfaces and a standard Core. The Core itself includes a Timer/Watchdog, Serial Interface, I/O ports and the 256 byte Register File.

The remainder of this section describes in more detail the ST9 features of primary interest to assembly language programmers. Please refer to the ST9 Technical Manual for detailed architectural and configuration information.

Note: This Programming Manual follows the syntax of the ST9 Software Tools (AST9 the high-level Macro Assembler running on IBM Personal Computer under MS-DOS, SUN 3 and SUN 4 under UNIX, VAX and microVAX under VMS). Register and bit names follow the recommendations of the symbols.inc file available as an Application Note.

#### ADDRESS SPACES

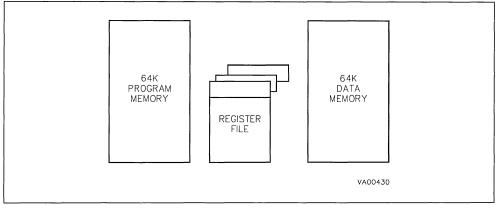

The ST9 has three separate address spaces:

- Program Memory for storing program instruction, with up to 64K (65536) byte for standard ST9 devices, up to 8M byte for ST9 devices with Bank Switch logic.

- the Data Memory for the storage of data, with up to 64K (65536) bytes for standard ST9 devices, up to 8M bytes for devices with Bank Switch logic.

- the Register File composed of 224 8 bit registers for all devices, plus 16 system control registers and up to 64 pages of 16 bytes for the control and status registers of the on-chip peripherals.

#### Figure 1. Address Spaces

#### MEMORY SEGMENTS

The two 64K byte memory spaces of the ST9 are addressed either directly with the 16 bit absolute memory address, or indirectly using a pair of the general purpose 8 bit registers. In addition the address may be given by an indexed mode when a short (byte) or long (word) offset is added to an indirect base word address.

Before either memory space is used, one of the two instructions SDM or SPM (Set Data Memory and Set Program Memory, respectively) should be used. There is no need to use either of these instructions again until the memory area required is to be changed. It is not necessary to use either SDM or SPM when operating with external stack pointers, where the data memory is automatically used, and when using the memory-indirect to memory-indirect post-increment addressing modes, when the memory types are specified in the instruction (ie. LDPD, Load from Data Memory to Program Memory).

An output pin  $(P/\overline{D})$  can be programmed to indicate the memory space currently selected in order to be used with the external address decoding logic.

Either the Data Memory or the Program Memory can be addressed using any of the memory addressing modes.

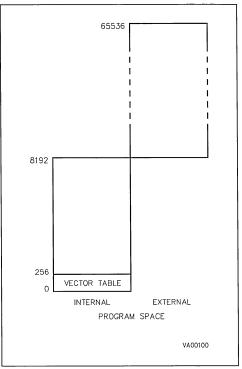

#### **Program Memory**

The Program Memory size can be up to 64K bytes. This memory can be all external (for ROMless devices) or partially external with an internal component (ROM or EPROM devices). Access to the external Program Memory is allowed only for instruction fetches at addresses greater than the existing on-chip ROM/EPROM memory. For example, when an ST9 with 8192 bytes of on-chip Program Memory, external memory fetches are performed at addresses above location 8193, as in Figure 2.

ST9 devices with Bank Switch logic may have the Program space extended within the 64K byte addressing range by paging of the upper 32K bytes to achieve a maximum program address space of 8M bytes. The lower 32K bytes remain static and are always available for interrupt servicing, bank switching and other common program procedures.

Within the Program Memory space the first 256 locations (0-255) can be used for the interrupt vector table (only locations 00h, 01h for the Reset Vector; 02h, 03h for the Divide by Zero Trap; and 04h, 05h for the Top Level priority vector are fixed). Apart from these vectors, no other part of the Program Memory has a predetermined function.

#### Data Memory

The Data Memory space is also of a maximum size of 64K bytes, and has exactly the same addresses

Figure 2. Program Memory Space

and addressing modes as the Program Memory, the two spaces being distinguished by the use of the memory setting commands (SDM being relevant for setting the Data Memory). Within this space ST9 devices may include on-chip static RAM and EE-PROM memory. Off-chip memory accesses will be made for address values at a higher value than the highest address of the on-chip memory component.

ST9 devices with Bank Switch logic may have the Data space extended within the 64K byte addressing range by paging of the upper 32K bytes to achieve a maximum data address space of 8M bytes (a total of 16M bytes including the Program Space). The lower 32K bytes of Data space remain static.

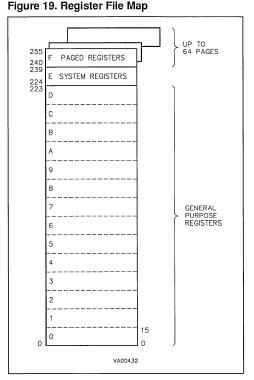

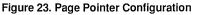

#### REGISTER FILE

The 256 Registers of the ST9 Register File include 224 general purpose 8 bit registers, 16 registers allocated for system functions and a paging mechanism on the top 16 registers. The pages contain the status and control registers of the on-chip peripherals which vary according to the specific device on-chip peripheral configuration.

#### **REGISTER FILE** (Continued)

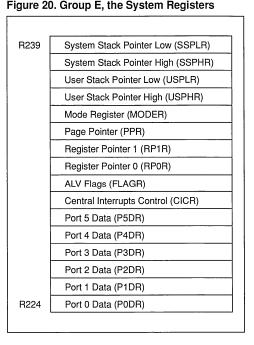

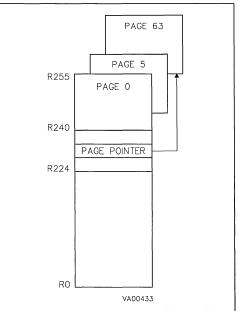

The Register File is divided into 16 groups each of 16 registers which may be referred to by their hexadecimal group number; R0-R15 forming Group 0, R16-R31 forming Group 1, R160-R175 forming Group A and so on. Group E (R224-R239) is the system register group, and, as it is common to all ST9 family devices and is of specific relevance to the operation of the ST9, its functions are summarised in Figure 3.

| -    |                                   |

|------|-----------------------------------|

| R239 | System Stack Pointer Low (SSPLR)  |

|      | System Stack Pointer High (SSPHR) |

|      | User Stack Pointer Low (USPLR)    |

|      | User Stack Pointer High (USPHR)   |

|      | Mode Register (MODER)             |

|      | Page Pointer (PPR)                |

|      | Register Pointer 1 (RP1R)         |

|      | Register Pointer 0 (RP0R)         |

|      | ALU Flags (FLAGR)                 |

|      | Central Interrupts Control (CICR) |

|      | Port 5 Data (P5DR)                |

|      | Port 4 Data (P4DR)                |

|      | Port 3 Data (P3DR)                |

|      | Port 2 Data (P2DR)                |

|      | Port 1 Data (P1DR)                |

| R224 | Port 0 Data (P0DR)                |

|      |                                   |

#### Figure 3. Group E Register Map

The ST9 Instruction Set allows direct access to all of the registers of the ST9 (see warning below). Each of the 224 general purpose registers can function as an accumulator, register address pointer or as an index register. In addition pairs of these registers may be used to provide 16 bit capability for memory addressing, indexing and arithmetic functions.

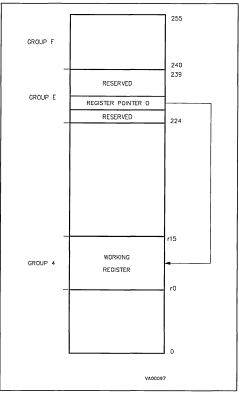

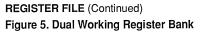

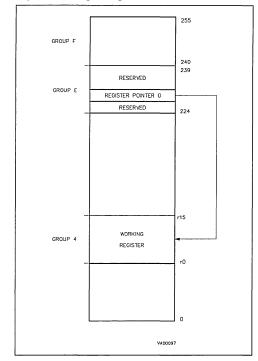

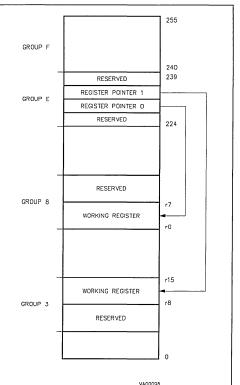

ST9 instructions can access registers directly or indirectly using an 8 bit address field. The ST9 also allows 4 bit addressing of the registers, which generally saves program bytes, and speeds program execution and task switching. In this 4 bit addressing mode, the register file is divided into 16 16 byte or 32 8 byte working register groups, each occupying contiguous register locations. Register pointers (within Group E, the system register group) address the starting location of the currently active working register group. One register (RP0) selects the base address for the 16 byte working register groups and a second (RP1) is used in conjunction with the first to select the 32 independent working register groups of 8 registers.

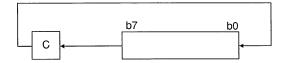

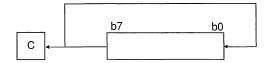

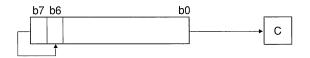

Figure 4. Single Working Register Bank

WARNING: Working register addresses are identified in instructions with an 8 bit address field by using an upper nibble of Dh (1101b) as an escape code. As a result, Group D of the Register File can not be addressed directly but may be addressed via the working registers. It is recommended that Group D registers are used for the stacking area when the System or User stack pointers are internal.

Changing the value of the register pointers is an easy way to save the currently active working registers (as during interrupt processing). Reserving one or more register groups for the use of interrupthandling routines is a recommended programming practice.

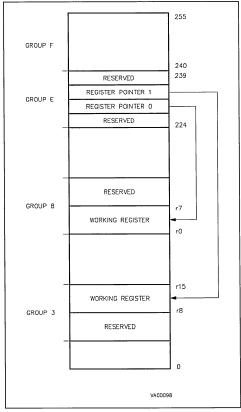

#### DATA LENGTHS

ST9 instructions can act on individual bits, 4 bit Binary Coded Decimal (BCD) or nibbles, 8 bit bytes, or 16 bit words.

Bits can be set, reset or tested. Nibbles are used in BCD arithmetic operations. Bytes are used for character or small integer values (in the range 0 to 255 if unsigned, or in the range -128 to +127 if signed). Words are used for larger integer values (in the range 0 to 65535 if unsigned, or in the range -32768 to +32767 if signed).

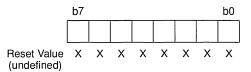

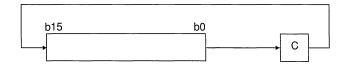

#### Figure 6. Data Lengths

#### ADDRESSING MODES

The ST9 offers a wide variety of established and new addressing modes and combinations to facilitate full and rapid access to the various address spaces while reducing program length. The available addressing modes and the special characters used in operands to identify the addressing modes are shown in Table 1.

The addressing modes available for source and destination addresses of the data for every instruction are described in detail in the Instruction Set section.

The memory addressing modes are applicable to both data and program memory spaces. Before addressing the memory, it is necessary to indicate by use of the Set Program/Data Memory instructions, SPM and SDM, in which memory space the instructions are working. This space will continue to be used until the next execution of these instructions. As each memory space is 64K bytes in size, a word address is necessary to specify memory locations.

#### Table 1. Addressing Modes

| Addressing Mode                               | Notation |      |  |

|-----------------------------------------------|----------|------|--|

| Immediate Data                                | #N       | #NN  |  |

| Register Direct                               | r        | R    |  |

| Register Indirect                             | (r)      | (R)  |  |

| Register Indirect with Post-Increment         | (r)+     | (R)+ |  |

| Register Indexed                              | N(r)     | N(R) |  |

| Register Bit                                  | r.b      |      |  |

| Memory Direct                                 | NN       |      |  |

| Memory Indirect                               | (rr)     |      |  |

| Memory Indirect with Post-Increment           | (rr)+    |      |  |

| Memory Indirect with Pre-Decrement            | -(rr)    |      |  |

| Memory Indexed with Immediate Short<br>Offset | N(rr)    |      |  |

| Memory Indexed with Immediate Long<br>Offset  | NN(rr)   |      |  |

| Memory Indexed with Register Offset           | rr(rr)   |      |  |

| Memory Indirect Bit                           | (rr).b   |      |  |

Legend: N = 8 bit Value

- NN = 16 bit Value or Address

- = Working Register

- R = Directly Addressed Register

- () = Indirect Addressing

- ()+= Indirect with Post-Increment

-() = Indirect with Pre-Decrement

- -( ) = Indirect with Pre-Decre .b = Bit Number (0 to 7)

- B = Bit Number (0 to 7)

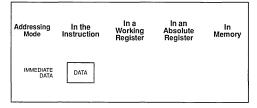

#### Immediate Data

Immediate Data is an addressing mode for the purposes of this discussion.

The operand value used by the instruction is the value supplied in the operand field itself. When using the immediate data addressing mode, a hashmark (#) is used to distinguish the data from an absolute address in memory.

Examples:

add R26,#04

adds 4 to the value originally contained in register R26.

ldw RR42, #45017

loads the immediate word value 45017 (0AFD9h) into the register pair RR42 (0AFh into R42 and 0D9h into R43).

ldw 12355, #3467

loads the word value 3467 (0D8Bh) into memory locations starting at 12355 (0Dh into 12355 and 8Bh into 12356).

#### Figure 7. Immediate Data

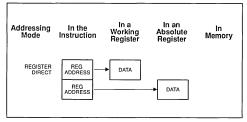

#### **Register Direct**

In the Register Direct addressing mode, a register can be addressed by using its absolute address in the register file. Alternatively a register can be addressed directly as a working register.

Example:

xch R162,r4

which exchanges the values in the register R162 and working register number 4.

#### Figure 8. Register Direct

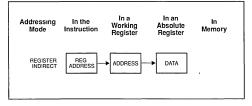

#### Register Indirect

In the Register Indirect addressing mode, the address of the data does not appear in the instruction, but is located in a working register. The address of this register is located in the instruction. The indirect addressing mode is indicated by the use of parentheses.

Example: If register 200 contains 178 and working register 11 contains 86, then the instruction

ld (r11),R200

will cause the value 178 to be loaded into register 86.

**Note.** the indirect address can only be contained in a working register.

#### Figure 9. Register Indirect

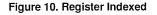

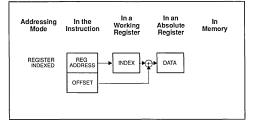

#### **Register Indexed**

To address a register using the Register Indexed mode, an offset value is used to add to an index value (which acts as a base or starting value). The offset value is the immediate value given in the instruction while the index value is given by the contents of the working register.

Example: If working register 10 contains 55 then the instruction

ld 40(r10),r18

will cause register 95 (i.e. 55+40) to be loaded with the content of working register 18.

The register file (256 registers) never needs an absolute value requiring more than one byte and therefore requires only a short offset and a single register to contain the index.

**Note:** The index value can only be contained in a working register.

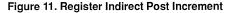

#### **Register Indirect Post Increment**

In this addressing mode, both destination and source addresses are given by the contents of the working registers which are then post-incremented. The address of the destination memory location is contained in a working register pair and the address of the register is contained in a single working register. This mode is indicated by both source and destination registers in parentheses followed by plus signs.

Example: If working register r8 contains the value 44, working register pair rr2 contains the value 2000, and register 44 contains the value 56, then by using the instruction

ld (rr2)+, (r8)+

the memory location 2000 will be loaded with the value 56. Immediately following this, the contents of r8 will be incremented to 45 and the contents of rr2 will be incremented to 2001.

This addressing mode is useful for moving blocks of data either from register file to memory, or from memory to register file.

**Note.** Only working registers may be used to contain the addresses.

#### Direct Bit

In the Direct Bit addressing mode, any bit in any working register can be addressed and potentially modified.

Examples:

bset r7.3

This instruction sets bit 3 of working register 7.

ldr7.3,r12.6

This instruction loads the value of bit 6 of working register 12 into bit 3 of working register 7.

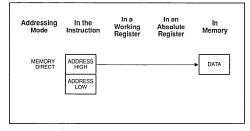

#### **Memory Direct**

The Memory Direct addressing mode requires the specific location within the memory. This only needs the absolute address value, with no prefix or other indication necessary.

Example: If the memory location at 32184 has been assigned the label FLOW

ld FLOW, r9

will enter the data in working register r9 into memory location 32184,

call 4308h

will call the subroutine at address 4308h (pushing the Program Counter onto the system stack for the return address).

#### Figure 12. Memory Direct

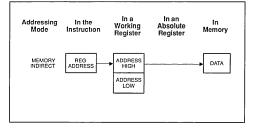

#### Memory Indirect

When using the Memory Indirect addressing mode to access memory, the address is contained in a pair of working registers.

Example: If the working register pair rr8 (r8,r9) contains the value 20000 then the instruction ld (rr8),#34

will load the value 34 to be loaded into memory location 20000.

If the data to be stored is a word, then the instruction LDW will automatically interpret the address as pointing to a pair of memory locations. Thus if rr8 contains 20000, then the instruction

ldw (rr8),#3467h

will cause the memory location 20000 to be loaded with the value 34h and location 20001 to be loaded with 67h.

Figure 13. Memory Indirect

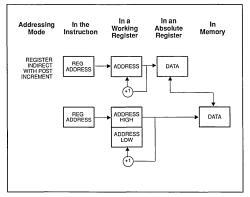

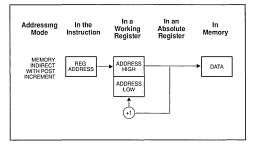

#### Memory Indirect with Post Increment

The Memory Indirect with Post Increment addressing mode is similar to the Memory Indirect addressing mode, but, in addition, after access to the data in the currently pointed address, the value in the pointing working register pair is incremented. This mode is indicated by a plus sign following the working address pair in paretheses, e.g. (rr4)+.

Example: If working register pair rr4 (working registers r4 and r5) contains the value 3000 and memory location 3000 contains the value 88, then the instruction

#### ld R50, (rr4)+

will cause register 50 to be loaded with the value 88 and then the value in rr4 to be incremented to 3001. This mode is most useful in repeated situations where a number of adjacent items of data are required in succession. The use of this addressing mode saves both time and program memory space since it cuts the usual increment instruction.

#### Figure 14. Memory Indirect Post Increment

**Note.** The Memory Indirect with Post Increment addressing mode may only use working registers to contain the address.

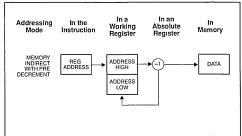

#### Memory Indirect with Pre Decrement

This Memory Indirect addressing mode has an automatic pre-decrement of the address contained in the pair of working registers before the action of the instruction. It is indicated by a minus sign in front of the working registers which are in parentheses, e.g. -(rr6).

Example: If working register pair rr6 contains the value 1111 and location 1110 contains the value 40, then the instruction

ld R56,-(rr6)

will cause the value in rr6 to be decremented to 1110 and then the value 40 to be loaded into register 56.

This addressing mode allows the ST9 to deal in the reverse order with data previously managed using the Memory Indirect Post-Increment mode, without resetting the pointing working registers (used with the last post-increment). The pre-decrement mode has the same benefits of time and program memory size saving as the post-increment mode.

**Note.** The Memory Indirect with Pre-Decrement addressing mode may only use working registers to contain the address.

Figure 15. Memory Indirect Pre Decrement

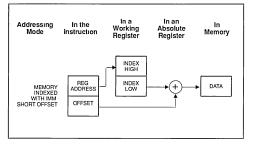

## Memory Indexed

There are three indexed addressing modes, each of them using an indirect address plus offset format. The index base address is given as an indirect address contained in a working register pair, while the offset can be long or short (16 or 8 bit) immediate values, or a register pair value. The address of the data required is given by the value of the working register pair indicated (the index), plus the value of the given offset. The specification of this offset which differentiates the three modes, is as follows.

Indexed with Immediate Short and Long Offset. In these indexed modes, the offset is an immediate value included in the instruction. It may be either a short (8 bit) or long (16 bit) index as required, this immediate value being added to the address given by the working register pair.

Example: If the working register pair rr6 has been assigned the label SINE and contains the value 8000 and memory location 8034 contains the value 254, then the instruction

ld R55, 34 (SINE)

will cause the value 254 to be loaded into register 55.

If working register pair rr2 contains the value 2000 and register 78 contains the value 34, then the instruction

ld 322 (rr2), R78

will cause the value 34 to be loaded into memory location 2322.

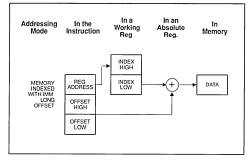

Figure 16. Memory Indexed with Immediate Short Offset

## Figure 17. Memory Indexed with Immediate Long Offset

This addressing mode is useful for processing table of data, where the start address of the table may be held in the working registers and the offset to the required variable is held in the instruction.

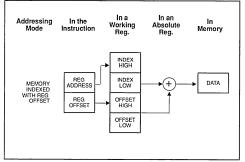

**Indexed with a Register Offset**. In this addressing mode the index is supplied by one pair of working registers and the offset is supplied by a second pair of working registers. The format is rrx(rry), where x and y are in the range 0, 2, 4...12, 14.

Example: If working register pair rr0 contains the value 2222 and working register pair rr4 contains 3333 while register R45 contains the value 78, then the instruction

```

ld rr4(rr0),R45

```

will cause the value 78 to be loaded into memory location 5555.

This addressing mode is useful for processing tables of data, where the start address of the table is held in working registers and the offset to the required variable is a user calculated value.

#### Figure 18. Memory Indexed with Register Offset

#### Memory Indirect Bit

In the Memory Indirect bit addressing mode, any bit of any writable Program/Data memory location can be addressed with the BTSET (Bit Test and Set) instruction. Example:

btset (rr8).3

sets bit 3 of the memory location addressed by the working registers rr8 (r8 and r9) and indicates the original content of the bit in the Zero bit of the FLAGR register. This instruction is useful in multi-tasking applications where it may be used for semaphore flags, indicating resource allocation between tasks.

#### SYSTEM GROUP

The ST9 system group is common to all ST9 family devices and contains registers of major interest to programmers. The sixteen registers are located in Group E, i.e. registers 224 to 239 (0E0h to 0EFh). In the following paragraphs a brief explanation is given for each system register and for its specific function. Please refer to the ST9 Technical Manual for full information on these registers.

#### Stack Pointers

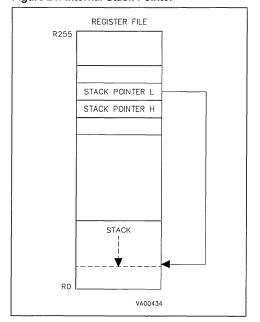

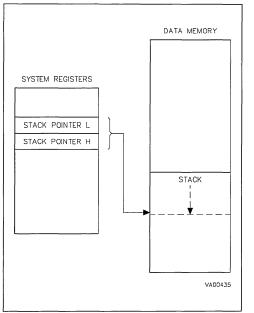

Two separate, double register stack pointers (named are System Stack Pointer and User Stack Pointer) are available to the programmer. Both stack pointers can address either the Register File or the Data Memory space for stacking area.

The Stack Pointers point to the bottom of the stack, that is, the location of the last saved value. Operation is in a Pre-Decrement mode when data is PUSHed onto the stack, and in a Post-Increment mode when data is POPed from the stack.

The System Stack Pointer (SSPR, R238:R239) is used for the storage of temporarily suspended sys-

tem and/or control registers (ie the Program Counter and the FLAG register) while interrupts are being serviced, and is used for the storage of the Program Counter following the CALLing of a subroutine.

The User Stack Pointer (USPR, R236:R237) is completely free from all interference from automatic operations and so provides for a totally user controlled stack area. Both Stack pointers may operate with both byte (PUSH, POP) and word (PUSHW, POPW) data, and are differentiated by appending a "U" to the instruction mnemonic for the User Stack (PUSHU/PUSHUW, POPU/POPUW). Calculated addresses may also be pushed onto the Stacks by the Push Effective Address instruction (PEA, PEAU), this instruction allows for code optimisation, for example for the ST9 ANSI C Compiler.

When the Stack Pointers are using Data Memory as the stack areas, a full word register is used as the pointer, while when operating with the stack area within the Register File (Groups 0 to 14 only, not within the system and paged groups) only an 8 bit register is required for addressing and consequently only the low byte of the word registers are used

(R239 for the System Stack and R237 for the User Stack). In this latter case the upper byte of the stack pointer registers (R238 and R236) must be considered as reserved. The Stack Pointers may be selected to point to RAM or Register File by the setting of the SSP (MODER.7) and USP (MODER.6) of the ST9 configuration register (MODER, R235) where a "1" denotes Register File operation (default at Reset and "0" causes Data Space operation.

Stacks can be located anywhere in the Register File (internal stacks) or the Data Memory (external stacks, even when using on-chip RAM memory). It is not necessary to set the Data Memory space using the instruction SDM as external stack instruction automatically use the Data memory.

WARNING: Care is necessary when managing stacks as there is no limit to stack sizes apart from the bottom of any address space in which the stack is placed. Consequently programmers are advised to use a stack pointer values as high as possible, particularly when using the Register File as a stacking area. In this case it is recommended that Group D is be used as it cannot otherwise be accessed directly due to the condition highlighted elsewhere in this document.

#### Example:

ld SSPL, # 223 ; R223 is top register of Group D

10/248

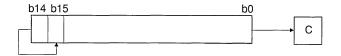

#### SYSTEM GROUP (Continued) Figure 21. Internal Stack Pointer

#### Figure 22. External Stack Pointer

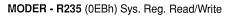

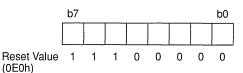

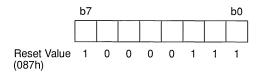

#### Mode Register (MODER)

The ST9 Mode Register is located at register R235. It allows the programmer to select either internal or external operation of the System and User Stack Pointers, control the prescaling of the instruction cycle clock (CPUCLK) and the enable/disable the divider of the oscillator input. In addition this register allows the control of the high-impedance states for the memory interface lines.

- b7 = **SSP:** System Stack Pointer. This bit selects internal (in the Register File) or external (in Data Memory) System Stack area, logical "1" for internal, and logical "0" for external. After Reset the value of this bit is "1".

- b6 = **USP:** User Stack Pointer. Same as bit 7 for the User Stack area.

- b5 = **DIV2:** OSCIN Clock Divided by 2. This bit controls the divide by 2 circuit which operates on the OSCIN Clock. A logical "1" value means that the OSCIN clock is internally divided by 2, and a logical "0" value means that no division of the OSCIN Clock occurs.

- b4-b2 = **PRS2, PRS1, PRS0:** *Prescaling of ST9 Clock.* These bits load the prescaling module of the internal clock (INTCLK). The prescaling value selects the frequency of the ST9 clock, which can be divided by 1 to 8. Refer to the Technical Manual Clock description for more information.

- b1 = **BRQEN:** Bus Request Enable. This bit is a software enable of an External Bus Request. When set to "1", it enables a Bus Request on the BUSREQ pin.

- b0 = **HIMP:** *High Impedance Enable.* When Port 0 and/or Port 1 are programmed as multiplexed address and Data lines to interface external Program and/or Data Memory, these lines can be forced into the High Impedance state by setting the HIMP bit to "1". When this bit is reset, it has no effect on P0 and P1 lines.

If Port 1 is declared as an address and as an I/O port (example: P10 ... P14 = Address, and P15 ... P17 = I/O), the HIMP bit has no effect on the I/O lines (in this example: P15 ... P17).

#### Page Pointer Register (PPR)

The ST9 Page Pointer Register is located at register R234. The top 16 registers of the Register File are paged in order that different on-chip peripheral configurations of ST9 family members will not affect the number of general purpose registers, allowing code compatibility across all devices. The ST9 can support up to 64 pages for peripheral control and status registers.

These registers are accessible via the Page Pointer Register, which is set by the Set Page Pointer Instruction (SPP). Subsequently all register access to the top group (register R240 to R255, RF0 to RFF) will refer to the selected peripheral page. Once the Page Pointer has been set, there is no need to refresh it unless a different page is required.

PPR - R234 (0EAh) Sys. Reg. Read/Write

- b7-b3 = **PP7-PP3:** Page Pointer Register bits. These bits contain the number (between 0 to 63) of the page chosen by the instruction SSP (Set Page Pointer). PP7 is the MSB of the page address. Once the page pointer has been set, there is no need to refresh it unless a different page is required.

- b2-b0 = **PP2-PP0:** Page Pointer Register bits. These bits are fixed by hardware to zero and are not affected by any writing instruction trying to modify their value.

**Note.** Although the least significant two bits of PPR are hardwired to 0, using the SPP instruction will generate automatically the correct shift.

Example: If register R23 contains the value 44, the following sequence loads the third register (R242) on Page 5 with the value 44

spp 5 ld R242,R23

Page 0 is common to all ST9 devices and contains the control registers of the external interrupts, timer/watchdog, internal wait state generator and the Serial Peripheral Interface (SPI).

Figure 24. Page 0 Register Map

#### **Register Pointers**

Two registers, R232 and R233, are available for register pointing to allow quicker and more code efficient addressing of the Register File.

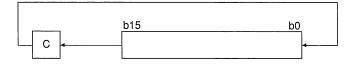

R232 (RP0) may be used as a single pointer for a 16 register working space (R233 is reserved in this case), or both R232 and R233 (RP1) may be used separately for two independent 8 register working groups. The instruction sRP, sRP0, sRP1 (the Set Register Pointer instructions) automatically inform the ST9 as to whether the Register File is to operate with a single 16-register group or two 8-register groups. There is no limitation on the order or position of these chosen register groups, other than they lie on (256 modulo 16 or 8) addresses of the register file.

Example:

srp #3;(not even modulus)

is equivalent to

srp #2 ; (2 \* 256 modulo 16)

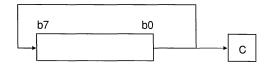

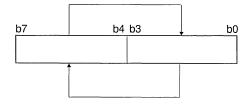

Figure 25. Single Register Pointer Bank

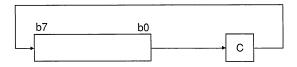

Figure 26. Dual Register Pointer Bank

The addressing of working registers involves use of the Register Pointer value plus an offset value given by the number of the addressed working register in the instruction.

Working Registers groups of 16 registers (set by the SRP instruction) are denoted as r0 to r15 (rr0 to rr14), while the dual working register group are addressed as r0 to r7 (rr0 to rr6) for the first group of 8 registers (SRP0 instruction), and r8 to r15 (rr8 to rr15) for the second set (SRP1 instruction), although in this case the ST9 will automatically subtract 8 from the register address to give the correct offset within the second working register group.

**Note.** Group D can only be accessed via the Register Pointers, as the upper nibble Dh (1101b) is used in the Direct Register addressing mode to indicate the use of the working registers. It is for this reason that it is suggested that the programmer use Group D as internal stacking area (if selected).

#### **Register Pointer 0 (RP0R)**

RPOR - R232 (0E8h) Sys. Reg. Read/Write

- b7-b3 = **RG7-RG3:** *Register Group bits.* These bits contain the number (from 0 to 31) of the group of working registers indicated in the instruction SRP0 or SRP. When using a 16-register group, a number between 0 and 31 must be used in the SRP instruction indicating one of the two adjacent 8-register group of working registers used. RG7 is the MSB.

- b2 = **RPS:** Register Pointer Selector. This bit is set by the instructions SRP0 and SRP1 to indicate that a double register pointing mode is used. Otherwise, the instruction SRP resets the RPS bit to zero to indicate that a single register pointing mode is used.

- b1-b0 = **D1, D0.** These bits are fixed by hardware to zero and are not affected by any write instruction trying to modify their value.

#### Register Pointer 1 (RP1R)

RP1R - R233 (0E9h) Sys. Reg. Read/Write

- b7-b3 = **RG7-RG3:** *Register Group bits.* These bits contain the number (from 0 to 1) of the group of 8 working registers indicated in the instructions SRP1. Bit 7 is the MSB.

- b2 = **RPS:** Register Pointer Selector. This bit is automatically set by the instructions SRP0 and SRP1 to indicate that a double register pointing mode is used. Otherwise the instruction SRP reset the RPS bit to zero to indicate that a single register pointing mode is used.

- b1-b0 = **D1, D0.** These bits are hardware fixed to zero and are not affected by any write instruction trying to modify their value.

#### Flag Register (FLAGR)

The Flag Register, R231 (RE7), contains flags indicating the current status of the ST9. The ST9 Flag Register contains six bits of status information which are set or cleared by CPU operations. Four of the bits (C, Z, O and S) can be tested for use with conditional Jump instructions. Two flags (H and D) cannot be tested directly and are used for BCD arithmetic.

FLAGR - R231 (0E7h) Sys. Reg. Read/Write

- b7 = C: Carry Flag. When set, it indicates a carry out of the most significant bit position of the register being used as an accumulator (bit 7 for byte and bit 15 for word operations) in arithmetic operations. The Carry Flag can be set to one by the Set Carry Flag (SCF) instruction, cleared to zero by the Reset Carry Flag (RCF) instructions, and complemented (changed to 0 if 1, and vice versa) by the Complement Carry Flag (CCF) instruction.

- b6 = **Z**: Zero Flag. In general, the Zero Flag is set when the register being used as an accumulator is zero following an arithmetic or logical instruction.

- b5 = **S**: *Sign Flag.* The Sign Flag is set to one when bit 7 or bit 15 (bit 7 for byte and bit 15 for word operations) of the register being used an accumulator contains a one (a negative number in two's complement arithmetic) following the operation specified in arithmetic, logical, Rotate or shift instructions.

- b4 = V: Overflow Flag. Overflow Flag. When set, the Overflow Flag indicates that a two's complement number, in a result register, is in error, having exceeded the largest (or is less than the smallest) number that can be represented in two's complement notation.

- b3 = D: Decimal Adjust. The Decimal Adjust Flag is used for BCD arithmetic. Since the algorithm for correcting BCD operations is different for addition and subtraction, this flag is used to specify which type of instruction was executed last, so that the subsequent Decimal Adjust (DA) operation can perform its function correctly. The Decimal Adjust flag cannot normally be used as a test condition by the programmer.

- b2 = **H**: *Half Carry*. The Half Carry Flag is set to "1" whenever an addition generates a carry out of bit 3, or a subtraction generates a borrow into bit 3. The Half Carry flag is used by the Deci-

mal Adjust (DA) instruction to convert the binary result of a previous addition or subtraction into the correct decimal (BCD) result. As in the case of the DA flag, this flag is not normally accessed by the programmer.

- b1 = **UF**: User Flag. The User Flag is available to the programmer, but must only be set or cleared by a Boolean instruction to prevent unwanted affects on the other flags.

- b0 = **DP** : Data/Program Memory Flag. This bit indicates which memory area is currently selected. Its value is affected by the Set Data Memory (SDM) and Set Program Memory (SPM) instructions. If the bit is set to "1", the ST9 is addressing the Data Memory area, when the bit is cleared to zero, the ST9 is addressing the Program area. The programmer can verify in which memory area the processor is working by inspection of this bit.

During an interrupt the Flag Register is automatically stored in the system stack area. It is recovered to its original status by the execution of the IRET instruction at the end of the interrupt service routine. This occurs for all interrupts and, when operating in nested interrupt mode, up to seven versions of the flag register may be stored.

#### Central Interrupt Control Register (CICR)

The Central Interrupt Control Register is at address R230 (RE6), and provides for control of the interrupt structure of the ST9, the Current priority level, the Interrupt mode selector, the Global Interrupt disable control and the Top Level Interrupt status and mask. Please refer to the Interrupt and DMA chapter of the ST9 Technical Manual for further information. In addition this register contains the Global Counter Enable of the Multi Function Timers (when available on-chip).

#### CICR- R230 (0E6h) Read/Write

b7 = **GCEN:** *Global Counter Enable.* This bit is the Global Counter Enable of the 2 x 16 bit Timers of the Multifunction Timer. The GCEN bit is ANDed with the CE (Counter Enable) bit of the Timer Control Register (explained in the Multifunction Timer chapter of the Technical Manual) in order to enable the Timers when both bits are set. This bit is set after the Reset cycle.

- b6 = **TLIP:** *Top Level Interrupt Pending.* This bit is automatically set when a Top Level Interrupt request is recognized. This bit can also be set by software in order to simulate a Top Level Interrupt Request.

- b5 = **TLI:** *Top Level Interrupt bit.* When this bit is set, a Top Level interrupt request is acknowledged depending on the IEN bit and the TLNM bit (in Nested Interrupt Control Register). If the TLM bit is reset the top level interrupt acknowledgement depends on the TLNM alone.

- b4 = **IEN:** Enable Interrupt. This bit, (when set), allows interrupts to be accepted. When reset no interrupts other than the TLI can be acknowledged. It is cleared by interrupt acknowledgement for concurrent mode and set by interrupt return (IRET). It can be managed by hardware and software.

- b3 = IAM: Interrupt Arbitration Mode. This bit covers the selection of the two arbitration modes, the Concurrent Mode being indicated by the value "0" and the Fully Automatic Nested Mode by the value "1". This bit is under software control.

- b2-b0 = **CPL2-CPL0**: *Current Priority Level bits.* These last three bits record the priority level of the interrupt presently under service (i.e. the Current Priority Level, CPL). For these priority levels 000 is the highest priority and 111 is the lowest priority. The CPL bits can be set by hardware or software and give the reference by which following interrupts are either left pending or are able to interrupt the current procedure. When the present interrupt is replaced by one of a greater priority, the current priority value is automatically stored until required, if in Nested Interrupt Mode.

#### I/O Port Data Registers

The data registers of I/O Port 0 to Port 5 (when available by device) are contained in registers R224 to R229 respectively. This allows direct access to these I/O ports at all times. Additional I/O Port data registers and configuration registers for all I/O Ports are to be found in the relevant Page (please refer to the specific device configuration). Each port of 8 I/O bits has three associated Control registers which determine the individual pin mode (input: TTL/CMOS thresholds; output: Open Drain/Push Pull, Bidirectional or Alternate Function). The data registers for Port 2 and Port 3 have a dual function, ST9 devices with Bank Switch Logic may also use these for the Data and Program Segment Registers.

#### INSTRUCTION SET

#### Functional Summary

The ST9 instruction set consists of 87 instruction types functionally divided into eight groups as in Table 2, they are:

- Load (two operands)

- Arithmetic & Logic (two operands)

- Arithmetic Logic and Shift (one operand)

- Stack (one operand)

- Multiply & Divide (two operands)

- Boolean (one or two operands)

- Program Control (zero to three operands)

- Miscellaneous (zero to two operands)

Table 2. Instruction Set Summary

The wide range of instructions facilitates the full use of the register file and address spaces, reducing execution times, while the register pointers mechanism allows an unmatched code efficiency and ultrafast context switching. A particularly notable feature is the comprehensive "Any Bit, Any Register" (ABAR) addressing capability of the Boolean instructions.

The MCU can operate with a wide range of data lengths from single bit, 4-bit nibbles which can be in the form of Binary Coded Decimal (BCD) digits. 8-bit bytes and 16-bit words. The summary on Table 2 shows the instructions belonging to each group and the number of operands required for each. The source operand is "src", "dst" is the destination operand, and "cc" is a condition code.

|                  | Load Instructions (Two Operands) |                                                 |                                                 |                                                 |                 |                                                 |        |                             |  |  |

|------------------|----------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-----------------|-------------------------------------------------|--------|-----------------------------|--|--|

| Mnemonic Operand | Operand                          | Instruction                                     | Flags                                           |                                                 |                 |                                                 |        |                             |  |  |

| whethoric        | Operand                          |                                                 | С                                               | z                                               | s               | v                                               | D      | н                           |  |  |

| LD<br>LDW        | dst, src<br>dst, src             | Load<br>Load Word                               |                                                 |                                                 | -               | -                                               | -      | -                           |  |  |

|                  |                                  | Arithmetic and Logic (Two Operands)             |                                                 |                                                 |                 |                                                 |        |                             |  |  |

| Mnemonic         | Operand                          | Instruction                                     |                                                 |                                                 | Fla             | igs                                             |        |                             |  |  |

|                  |                                  |                                                 | С                                               | z                                               | s               | v                                               | D      | н                           |  |  |

| ADD<br>ADDW      | dst, src<br>dst, src             | Add<br>Add Word                                 |                                                 | $\Delta \Delta$                                 |                 | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | 0<br>0 | $\stackrel{\Delta}{\Delta}$ |  |  |

| ADC<br>ADCW      | dst, src<br>dst, src             | Add with Carry<br>Add Word with Carry           | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | $\Delta \Delta$                                 | $\Delta \Delta$ | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | 0<br>0 | $\Delta \Delta$             |  |  |

| SUB<br>SUBW      | dst, src<br>dst, src             | Subtract<br>Subtract Word                       | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | $\Delta \Delta$ | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | 1<br>? | ∆<br>?                      |  |  |

| SBC<br>SBCW      | dst, src<br>dst, src             | Subtract with Carry<br>Subtract Word with Carry | $\Delta \Delta$                                 | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | $\Delta \Delta$ | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | 1<br>? | $\stackrel{\Delta}{?}$      |  |  |

| AND<br>ANDW      | dst, src<br>dst, src             | Logical AND<br>Logical Word AND                 | -                                               | $\Delta \Delta$                                 | $\Delta \Delta$ | 0<br>0                                          | -      | -                           |  |  |

| OR<br>ORW        | dst, src<br>dst, src             | Logical OR<br>Logical Word OR                   | -                                               | $\Delta \Delta$                                 | $\Delta \Delta$ | 0<br>0                                          |        | -                           |  |  |

Legend: 0 = Bit set to zero 1 = Bit set to one  $\Delta$  = Bit affected 2 = Bit status undefined - = Bit not affected

|             |                      | Arithmetic and Logic (Two Operands) (Continued                | )<br>(F         |                                                 |                                                  |                                                 |   | -      |  |  |

|-------------|----------------------|---------------------------------------------------------------|-----------------|-------------------------------------------------|--------------------------------------------------|-------------------------------------------------|---|--------|--|--|

| Mnemonic    | Operand              | Instruction                                                   | Flags           |                                                 |                                                  |                                                 |   |        |  |  |

|             | operand              |                                                               | С               | z                                               | s                                                | v                                               | D | н      |  |  |

| XOR<br>XORW | dst, src<br>dst, src | Logical Exclusive OR<br>Logical Word Exclusive OR             | -               | $\Delta \Delta$                                 | $\begin{array}{c} \Delta \\ \Delta \end{array}$  | 0<br>0                                          | - | -      |  |  |

| CP<br>CPW   | dst, src<br>dst, src | Compare<br>Compare Word                                       | $\Delta \Delta$ | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | $\Delta \Delta$                                  | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | - | -      |  |  |

| TM<br>TMW   | dst, src<br>dst, src | Test Under Mask<br>Test Word Under Mask                       | -               | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | $\begin{bmatrix} \Delta \\ \Delta \end{bmatrix}$ | 0<br>0                                          |   |        |  |  |

| TCM<br>TCMW | dst, src<br>dst, src | Test Complement Under Mask<br>Test Word Complement Under Mask | -               | $\Delta \Delta$                                 | $\Delta \Delta$                                  | 0<br>0                                          | - |        |  |  |

|             | ·                    | Arithmetic Logic and Shift (One Operand)                      |                 |                                                 |                                                  |                                                 |   |        |  |  |

| Mnemonic    | Operand              | Instruction                                                   |                 |                                                 | Fla                                              | igs                                             | 1 |        |  |  |

|             |                      |                                                               | С               | z                                               | s                                                | v                                               | D | н      |  |  |

| INC<br>INCW | dst<br>dst           | Increment<br>Increment Word                                   |                 | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | $\Delta$                                         | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | - | -      |  |  |

| DEC<br>DECW | dst<br>dst           | Decrement<br>Decrement Word                                   |                 | $\Delta$                                        | $\Delta \Delta$                                  | $\Delta \Delta$                                 | - | -      |  |  |

| SLA<br>SLAW | dst<br>dst           | Shift Left Arithmetic<br>Shift Word Left Arithmetic           |                 | $\Delta \Delta$                                 | $\Delta \Delta$                                  | 0<br>0                                          |   | D<br>∆ |  |  |

| SRA<br>SRAW | dst<br>dst           | Shift Right Arithmetic<br>Shift Word Right Arithmetic         |                 | $\Delta \Delta$                                 | $\begin{array}{c} \Delta \\ \Delta \end{array}$  | 0<br>0                                          | - | -      |  |  |

| RRC<br>RRCW | dst<br>dst           | Rotate Right through Carry<br>Rotate Word Right through Carry |                 | $\Delta \Delta$                                 | $\begin{array}{c} \Delta \\ \Delta \end{array}$  | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | = | -      |  |  |

| RLC<br>RLCW | dst<br>dst           | Rotate Left through Carry<br>Rotate Word Left through Carry   | $\Delta \Delta$ | $\Delta \Delta$                                 | $\begin{array}{c} \Delta \\ \Delta \end{array}$  | $\begin{array}{c} \Delta \\ \Delta \end{array}$ | - |        |  |  |

| ROR         | dst                  | Rotate Right                                                  | Δ               | Δ                                               | Δ                                                | Δ                                               | - | -      |  |  |

| ROL         | dst                  | Rotate Left                                                   | Δ               | Δ                                               | Δ                                                | Δ                                               | - | -      |  |  |

| CLR         | dst                  | Clear                                                         | -               | -                                               | -                                                | -                                               | - | -      |  |  |

| CPL         | dst                  | Complement Register                                           | -               | Δ                                               | Δ                                                | 0                                               | - | _      |  |  |

| SWAP        | dst                  | Swap Nibbles                                                  | ?               | Δ                                               | Δ                                                | ?                                               | - | -      |  |  |

| DA          | dst                  | Decimal Adjust                                                | Δ               | Δ                                               | Δ                                                | ?                                               | - | -      |  |  |

|                         |                     | Stack Instructions (One Operand)                                                            |                     |             |        |        |        |             |  |

|-------------------------|---------------------|---------------------------------------------------------------------------------------------|---------------------|-------------|--------|--------|--------|-------------|--|

| Mnemonic                | Operand             | Instruction                                                                                 | Flags               |             |        |        |        |             |  |

| Whemonic                | Operand             |                                                                                             | С                   | z           | s      | v      | D      | н           |  |

| PUSH<br>PUSHW<br>PEA    | SrC<br>SrC<br>SrC   | Push on System Stack<br>Push Word on System Stack<br>Push Effective Address on System Stack |                     |             |        |        |        |             |  |

| POP<br>POPW             | dst<br>dst          | Pop from System Stack<br>Pop Word from System Stack                                         | -                   | -           | -      | -      | -      | -           |  |

| PUSHU<br>PUSHUW<br>PEAU | SrC<br>SrC<br>SrC   | Push on User Stack<br>Push Word on User Stack<br>Push Effective Address on User Stack       |                     | -<br>-<br>- |        |        |        | -<br>-<br>- |  |

| POPU<br>POPUW           | dst<br>dst          | Pop from User Stack<br>Pop Word from User Stack                                             | -                   | -           | -      | -      | _      | -           |  |

|                         |                     | Multiply and Divide Instructions (Two Operands)                                             |                     |             |        |        |        |             |  |

| Mnemonic                | Operand             | Instruction                                                                                 |                     |             | Fla    | igs    |        |             |  |

|                         | operand             |                                                                                             | С                   | z           | s      | v      | D      | н           |  |

| MUL                     | dst, src            | Multiply 8x8                                                                                | ?                   | ?           | ?      | ?      | ?      | ?           |  |

| DIV<br>DIVWS            | dst, src            | Divide 16/8<br>Divide Word Stepped 32/16                                                    | ?<br>?              | ?<br>?      | ?<br>? | ?<br>? | ?<br>? | ?<br>?      |  |

|                         |                     | Boolean Instructions (Two Operands)                                                         |                     |             |        |        |        |             |  |

| Mnemonic                | Operand             | Instruction                                                                                 | Operand Instruction |             |        |        | ags    |             |  |

|                         |                     |                                                                                             | с                   | z           | s      | v      | D      | н           |  |

| BLD                     | dst, src            | Bit Load                                                                                    |                     | -           | -      | -      | -      | _           |  |

| BAND                    | dst, src            | Bit AND                                                                                     | -                   | _           | -      |        | -      | -           |  |

| BOR                     | dst, src            | Bit OR                                                                                      |                     | -           |        | -      | -      | -           |  |

| BXOR                    | dst, src            | Bit Exclusive OR                                                                            | -                   | -           | -      | -      | -      | -           |  |

|                         |                     | Boolean Instructions (One Operand)                                                          |                     |             |        |        |        |             |  |

| Mnemonic                | Operand Instruction |                                                                                             |                     |             | Fla    | igs    |        |             |  |

|                         |                     |                                                                                             | С                   | z           | s      | v      | D      | н           |  |

| BSET                    | dst                 | Bit Set                                                                                     |                     | -           | -      | -      | -      | -           |  |

| BRES                    | dst                 | Bit Reset                                                                                   | -                   | -           | -      | -      | -      | -           |  |

| BCPL                    | dst                 | Bit Complement                                                                              | _                   | -           | -      | -      | -      | -           |  |

| BTSET                   | dst                 | Bit Test and Set                                                                            | -                   | -           | -      | -      | -      | -           |  |

|             |          | Program Control Instructions (Three Operands)                                                                                                                       |       |   |     |     |   |   |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|-----|-----|---|---|

| Masaasia    | Onevend  | Instruction                                                                                                                                                         |       |   | Fla | ags |   |   |

| Mnemonic    | Operand  | Instruction                                                                                                                                                         | С     | z | s   | v   | D | н |

| CPJFI       | dst, src | Compare and Jump on False,<br>Otherwise Post Increment                                                                                                              | -     | - | -   | -   | - | - |

| CPJTI       | dst, src | Compare and Jump on True,<br>Otherwise Post Increment                                                                                                               | -     | - | -   | _   | - | - |

|             |          | Program Control Instructions (Two Operands)                                                                                                                         |       |   |     |     |   |   |

| Mnemonic    | Operand  | Instruction                                                                                                                                                         |       |   | Fla | igs |   |   |

| whenomic    | Operand  | instruction                                                                                                                                                         | С     | z | s   | v   | D | н |

| BTJF        | dst, src | Bit Test and Jump if False                                                                                                                                          | -     | - | -   | -   | - | - |

| BTJT        | dst, src | Bit Test and Jump if True                                                                                                                                           | -     | - | -   | -   | - | - |

| DJNZ        | dst, src | Decrement a Working Register and Jump if Not Zero                                                                                                                   | -     | - | -   | _   | - | - |

| DWJNZ       | dst,src  | Decrement a Register Pair and Jump if Not Zero                                                                                                                      | _     | - | -   | -   | - | - |

|             |          | Program Control Instructions (One Operand)                                                                                                                          |       |   |     |     |   |   |

| Mnemonic    | Operand  | Instruction                                                                                                                                                         | Flags |   |     |     |   |   |

| Witemonic   | Operand  |                                                                                                                                                                     | С     | z | s   | v   | D | н |

| JR          | cc, dst  | Jump Relative if Condition is Met                                                                                                                                   | -     | - | -   | -   | - | - |

| JP          | cc, dst  | Jump if Condition is Met                                                                                                                                            | -     | - | -   | -   | - | - |

| JP          | dst      | Unconditional Jump                                                                                                                                                  | -     | - | -   | -   | - | - |

| CALL        | dst      | Unconditional Call                                                                                                                                                  | -     | - | -   | -   | - | - |

|             |          | Program Control Instructions (No Operand)                                                                                                                           |       |   |     |     |   |   |

| Mnemonic    | Operand  | Instruction                                                                                                                                                         | Flags |   |     |     |   |   |

| Witemonic   | Operand  |                                                                                                                                                                     | С     | z | s   | v   | D | н |

| RET         |          | Return from Subroutine                                                                                                                                              | -     | - | -   | -   | - | - |

| IRET        |          | Return from Interrupt                                                                                                                                               | Δ     | Δ | Δ   | Δ   | Δ | Δ |

| WFI         |          | Stop Program Execution and Wait Next Enabled In-<br>terrupt. If a DMA request is present the CPU ex-<br>ecutes the DMA service routine and returns to WFI<br>state. | -     | - | -   | -   | - | - |

| HALT        |          | Stop Program Execution until RESET                                                                                                                                  | -     | - | -   | -   | - | - |

|             |          | Miscellaneous (Two Operands)                                                                                                                                        |       |   |     |     |   |   |

| Mnemonic    | Operand  | Instruction                                                                                                                                                         |       |   | Fla | igs |   |   |

| MITEHIOIIIC | Operand  |                                                                                                                                                                     | С     | z | s   | v   | D | н |

| ХСН         | dst, src | Exchange Registers                                                                                                                                                  | -     | - | -   | _   | - | _ |

|           | Miscellaneous (One Operand) |                                                  |       |   |     |     |   |   |  |  |

|-----------|-----------------------------|--------------------------------------------------|-------|---|-----|-----|---|---|--|--|

| Mnemonic  | Operand                     | Instruction                                      | Flags |   |     |     |   |   |  |  |

| whemonic  | Operand                     |                                                  | С     | z | s   | v   | D | н |  |  |

| SRP       | src                         | Set Register Pointer Long (16 Working Registers) | -     |   | -   | -   | - | - |  |  |

| SRP0      | src                         | Set Register Pointer 0 (8 LSB Working Registers) | -     | - | -   | -   | - | - |  |  |

| SRP1      | src                         | Set Register Pointer 1 (8 MSB Working Registers) | -     | - | -   | -   | - | - |  |  |

| SPP       | src                         | Set Page Pointer                                 | -     | - | -   | -   | - | - |  |  |

| EXT       | src                         | Sign Extend                                      | -     | - | -   | -   | - |   |  |  |

|           |                             | Miscellaneous (No Operand)                       |       |   |     |     |   |   |  |  |

| Mnemonic  | Operand                     | Instruction                                      |       |   | Fla | ags |   |   |  |  |

| Milemonic | Operand                     |                                                  | С     | z | s   | v   | D | н |  |  |

| El        |                             | Enable Interrupts                                | -     | - | -   | 1   | - | - |  |  |

| DI        |                             | Disable Interrupts                               | -     | - | -   | -   | - | - |  |  |

| SCF       |                             | Set Carry Flag                                   | Δ     | - | -   | -   | - | - |  |  |

| RCF       |                             | Reset Carry Flag                                 | Δ     | - | -   | -   | - | - |  |  |

| CCF       |                             | Complement Carry Flag                            | Δ     | - | -   | -   | - | - |  |  |

| SPM       |                             | Select Program Memory                            | -     | - | -   | -   | - | - |  |  |

| SDM       |                             | Select Data Memory                               | -     | - | -   | -   | - | - |  |  |

| NOP       |                             | No Operation                                     | -     | - | -   | -   |   | - |  |  |

**Processor Flags.** An important aspect of any single chip microcontroller is the ability to test data and make the appropriate action based on the results. In order to provide this facility, register 231 in the Register File is used as a Flag Register. Six bits of this register are used as the following flags:

- C Carry

- Z Zero

- S Sign

- V Overflow

- D Decimal Adjust

- H Half Carry

One of the two remaining bits in the flag register is available to the user (bit 1, F1). Bit 0 is the Program/Data Memory selector bit. The flags and their description are in SYSTEM GROUP registers section. **Condition Codes.** Flags C, Z, S, and V control the operation of the "conditional" Jump instructions. Table 6 shows the condition codes and the flag settings.

For example the instruction

JPEQ 1024

checks to see how the last arithmetic or logic operation has left the zero flag (Z). If the zero flag is set then the program counter is loaded with 1024 (decimal) and control is transferred to that location. Otherwise the next instruction is executed.

**Note.** Some of the status flags are used to indicate more than one condition, e.g. Zero and Equal. In such cases the condition codes are the same for both conditions.

| Mnemonic<br>Code | Meaning                        | Flag Setting          | Hex<br>Value | Binary<br>Value |

|------------------|--------------------------------|-----------------------|--------------|-----------------|

| F                | Always False                   | _                     | 0            | 0000            |

| Т                | Always True                    |                       | 8            | 1000            |

| С                | Carry                          | C = 1                 | 7            | 0111            |

| NC               | No Carry                       | C = 0                 | F            | 1111            |

| Z                | Zero                           | Z = 1                 | 6            | 0110            |

| NZ               | No Zero                        | Z = 0                 | E            | 1110            |

| PL               | Plus                           | S = 0                 | D            | 1101            |

| мі               | Minus                          | S = 1                 | 5            | 0101            |

| ov               | Overflow                       | V = 1                 | 4            | 0100            |

| NOV              | No Overflow                    | V = 0                 | С            | 1100            |

| EQ               | Equal                          | Z = 1                 | 6            | 0110            |

| NE               | Not Equal                      | Z = 0                 | E            | 1110            |

| GE               | Greater Then or Equal          | (S xor V) = 0         | 9            | 1001            |

| LT               | Less Than                      | (S xor V) = 1         | 1            | 0001            |

| GT               | Greater Than                   | (Z or (S xor V)) = 0  | A            | 1010            |

| LE               | Less Than or Equal             | (Z or (S xor V)) = 1  | 2            | 0010            |

| UGE              | Unsigned Greater Than or Equal | C = 0                 | F            | 1111            |

| UL               | Unsigned Less Than             | C = 1                 | 7            | 0111            |

| UGT              | Unsigned Greater Than          | (C = 0 and Z = 0) = 1 | В            | 1011            |

| ULE              | Unsigned Less Than or Equal    | (C or Z) = 1          | 3            | 0011            |

#### Table 3. Condition Codes Summary

**Notation** Operands and status flags are represented by a notational shorthand in the detailed instruction description. The notation for operands (condition codes and addressing modes) and the actual operands they represent are as in Table 4.

#### Table 4. Notation Summary

| Notation  | Addressing Mode                                                                      | Actual Operand/Range                                                                                                             |

|-----------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| сс        | Condition Code                                                                       | see Table 3                                                                                                                      |

| #N<br>#NN | Immediate Byte<br>Immediate Word                                                     | # data where data is a byte expression<br># data where data is a word expression                                                 |

| r         | Direct Working Register                                                              | rn, where n = 0 - 15                                                                                                             |

| R         | Direct Register                                                                      | Rn, where n = 0 - 255                                                                                                            |

| rr        | Direct Working Register Pair                                                         | rrn, where n is an even number in the range 0 - 14 (n = 0, 2, 4, 614)                                                            |

| RR        | Direct Register Pair                                                                 | RRn, where n is an even number in the range $0 - 254$ (n = 0, 2, 4, 6254)                                                        |

| (r)       | Indirect Working Register                                                            | (rn), where n = 0 - 15                                                                                                           |

| (R)       | Indirect Register                                                                    | (Rn), where n = 0 - 255                                                                                                          |

| (r)+      | Indirect Working Register Post Increment                                             | (rn)+, where n = 0 - 15                                                                                                          |

| N(r)      | Indexed Register                                                                     | N(rn), where n = 0 - 15; N is a one byte ex-<br>pression between 0 - 255                                                         |

| Ν         | Memory Relative Short Address                                                        | Program label or expression in the range +127/<br>-128 starting from the address of the next in-<br>struction                    |

| NN        | Direct Memory Long Address                                                           | Program label or expression in the range<br>0 - 65535 in memory area                                                             |

| (11)      | Indirect Pair of Working Registers Pointer                                           | (rrn), where n is an even number in the range<br>0 - 14 (n = 0, 2, 4, 614)                                                       |

| (m)+      | Indirect Pair of Working Registers Pointer with<br>Post Increment                    | (rrn)+, where n is an even number in the range<br>0 - 14 (n = 0, 2, 4, 614)                                                      |

| -(rr)     | Indirect Pair of Working Registers Pointer with<br>Pre Decrement                     | -(rrn), where n is an even number in the range<br>0 - 14 (n = 0, 2, 4, 614)                                                      |