# ISDN & DATACOM PRODUCTS

DATABOOK

1<sup>st</sup> EDITION

<1

S-THOMSON

ROELECTRONICS

## ISDN & DATACOM PRODUCTS

## DATABOOK

1<sup>st</sup> EDITION

**AUGUST 1992**

#### USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED

SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics. As used herein:

- Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| TABLE OF CONTENTS    |        |

|----------------------|--------|

| INTRODUCTION         | Page 4 |

| ISDN TUTORIAL        | 7      |

| GLOSSARY             | 15     |

| ALPHANUMERICAL INDEX | 23     |

| ISDN DATASHEETS      | 25     |

| DATACOM DATASHEETS   | 291    |

| APPLICATION NOTES    | 449    |

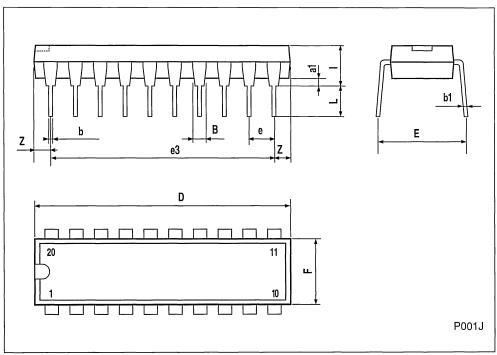

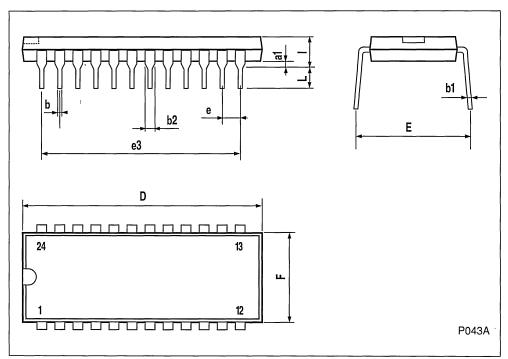

| PACKAGES             | 469    |

## INTRODUCTION

## ISDN: THE SGS-THOMSON SOLUTION

In the world there are about 800,000,000 kilometers of copper wire connections between telephone subscribers and the local exchange office. This is the largest asset of telephone network operators. By using Integrated Services Digital Network (ISDN) techniques this costly asset can continue to serve as the final subscriber link in a completely digital worldwide network that brings users new services.

What makes the ISDN revolution possible is the availability of affordable integrated circuits that perform highly complex functions, allowing the transmission of two 64kbits/s voice/data channels over a standard telephone wire.

A leading supplier of telecom ICs, SGS-THOMSON has been active in the research and study of ISDN circuits for many years, and has invested five years of effort in the development of a family of ICs covering all of the key functions and all of the major markets.

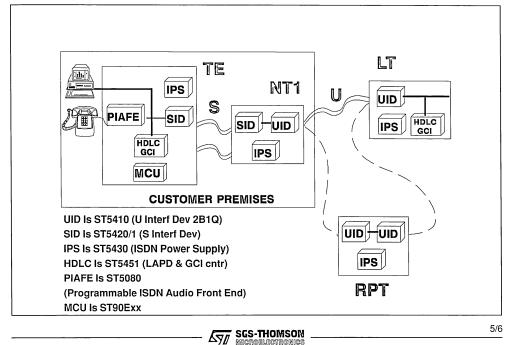

These circuits include "U" interface devices for both 2B1Q and 4B3T line codes, an "S" interface, a HDCL & GCI controller, and ISDN power supply and a programmable ISDN audio front end. These ICs are designed to operate with both the GCI and Microwire chip interconnect bus standards.

Because of the high complexity of ISDN circuits the technology used to fabricate them becomes critical. Armed with advanced R&D and production facilities, SGS-THOM-SON is at the forefront of CMOS technology development, guaranteeing continual improvements in litthography. Today the circuits described in this book are fabricated with 1.2u CMOS technologies -- some with a pure digital version, others with a mixed analog/digital variant. Future generations will use finer lithography to permit a further increase in the integration level as functions are brought together on single dice.

This volume contains a tutorial introduction and datasheets for all of the SGS-THOM-SON dedicated ISDN integrated circuits.

## DATACOM: MAKING THE DESIGNERS' JOB EASIER

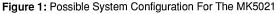

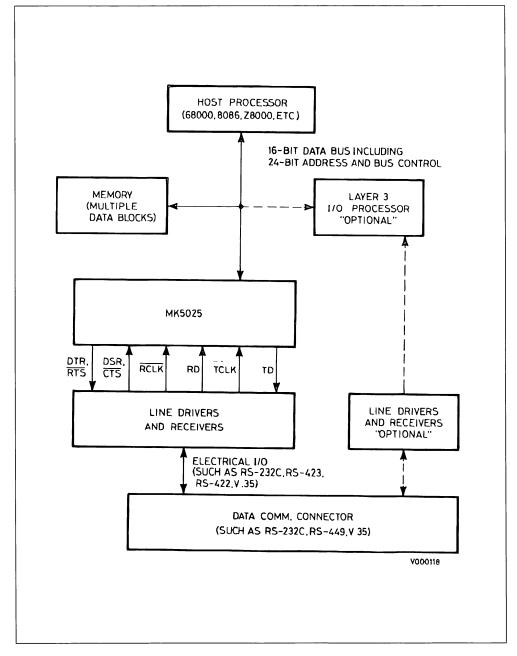

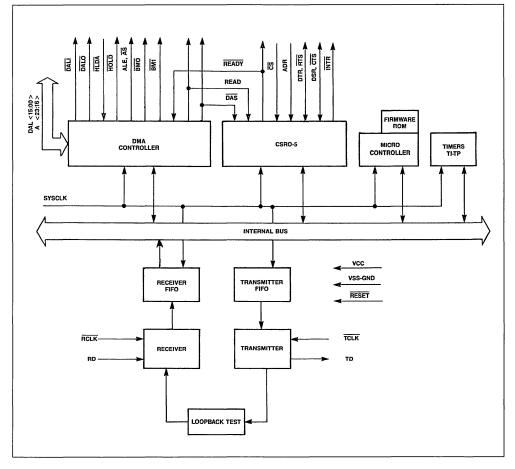

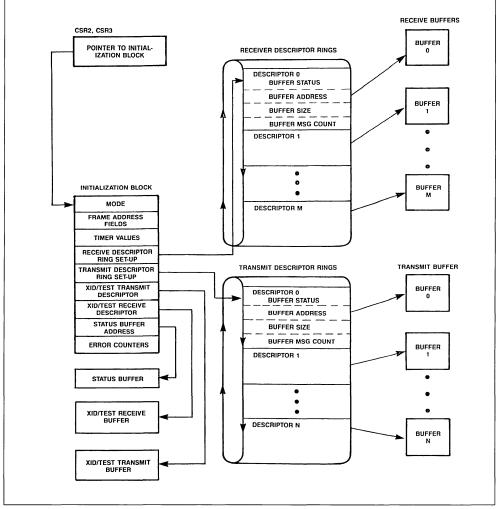

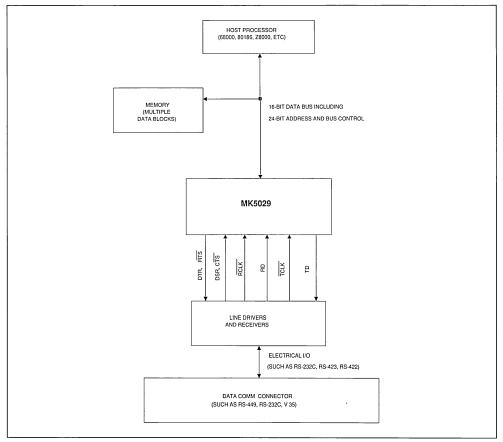

This book includes key devices for datacom Link Layer Controller applications, a family of reliable high performance devices manufactured using SGS-THOMSON's advanced CMOS technology.

The DATACOM products form a co-ordinated family of Link Layer Controllers for different applications that all share the same pin out and bus interface. This approach saves man-years of development effort when needing to design new equipment that requires different OSI link layer protocols in the HDLC family.

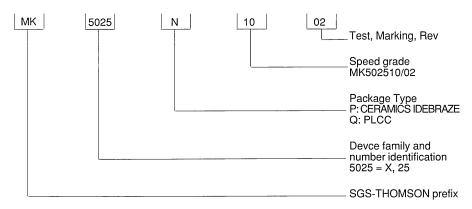

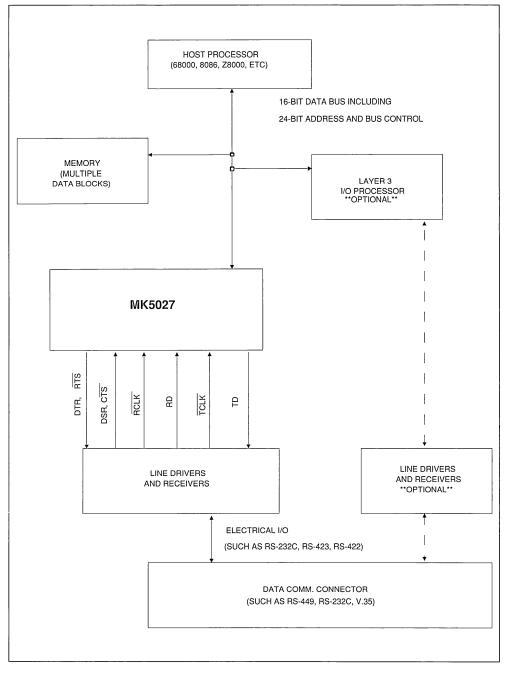

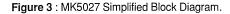

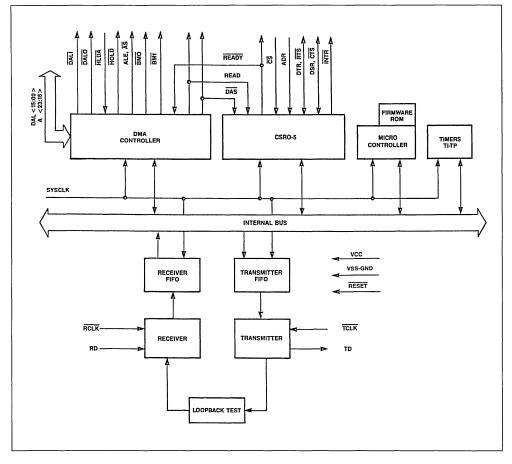

The 7MHz full duplex MK502X5 series of products described in this databook are used in volume applications in ROUTERS, CENTRAL OFFICE Wide Area Networks, and CELLULAR RADIO applications. Device certification in major networks, world-wide, reduces the time the design engineer must spend in software development. In fact, the

## INTRODUCTION

entire layer two of the OSI model is included on-chip for LAPB and X.75, CCS#7, and SDLC (Secondary), in the MK5025, MK5027, and MK5029 respectively.

The next step of evolution for the plug-compatible MK5025 family is MK50H25. The MK50H25 series Link Layer Controller supports SYSCLK of 33MHz and can "burst" data up to 50 MHz for T3 and FRAME RELAY applications. This series will expand the product portfolio for high performance devices designed to make the engineers' job easier.

Contact your SGS-Thomson sales representative for further information on any of the devices mentioned in this book.

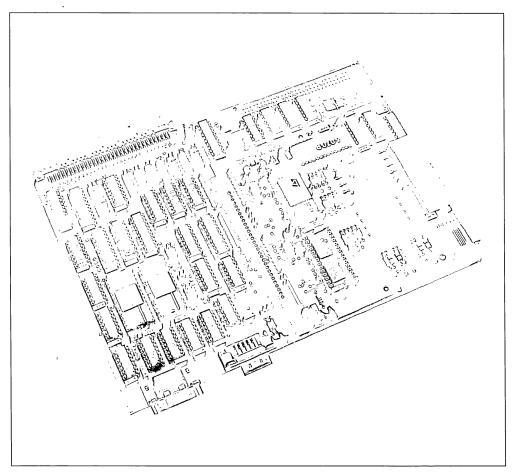

Application support for SGS-THOMSON'S ISDN integrated circuit product range includes demonstration and evaluation boards like this one, which allows rapid testing of U interface devices.

## **ISDN TUTORIAL**

## WHAT IS ISDN?

ISDN means Integrated Services Digital Network.

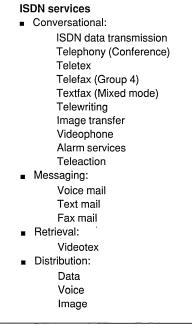

This is an all digital communication network offering the capability of communicate through voice, data or video using a bandwidth that is increased from the 3 khz of the analog telephone to the 144 Kbps offered by 2x64 Kbps voice/data B channels

CCITT defines the ISDN as:

A network evolved from the telephony integrated digital network that provides end-to-end digital connectivity to support a wide variety of services, to which users have access by a limited set of standard multipurpose customer interfaces.

## Text Box 1

plus a 16 Kbps signalling D channel.

This definition deserves some words for explaining carefully the meaning of this new communication concept.

The ISDN basic idea is simply to move the point of analog to digital conversion from the central office to the subscriber and make the signal transmitted over the standard copper cable a digital one.

As the digitization of the Telephone Network is expanding from the Core of the Central Office (Line Card, Switching and Digital Trunk) to the subscriber premises, so leaving a close and limited distance environment to get at the customer premises, the need for compatibility with the existent copper wiring becomes the center of the problem.

In the history of telecommunication the backwords compatibility is fundamental for any new transmission technique having the target to replace completely the preceding one.

A simple calculation can help in understanding the importance and the reason of this philosophy: we can reasonably consider that around 800 million subscriber copper wire access exists in the world; it is reported from various sources that the average distance between the nearest central office and the user telephone is around 1 km; conclusively we can say that around 800 million kilometers of twisted copper cable exist in the world: the biggest assets owned by the telecom service suppliers.

That highlights the basic challenge of ISDN: the

possibility to bring a much wider bandwidth to the user without changing the existent cabling set up.

What are the advantages that an integrated services digital network will offer? The actual payoff is for both the service suppliers and the users.

The user will increase use of data communication: this means to be able to take either a telephone, personal computer or any other form of data communications equipment and plug directly into a standard phone jack gaining access to a number of high speed data links and a big variety of services.

For the PTTs ISDN represents a new, revenue generating, concept which takes advantage of their large capital investment in the telecom network providing an increased bandwidth to the subscriber, creating an outstanding growth of the added value of the existent installed cable base; the phone companies will be able to provide new services which customers will pay for!

Although it is difficult to evaluate quantitatively, an increase in productivity is foreseen by ISDN's subscribers.

### ISDN TERMINOLOGY/DEFINITIONS

In order to convert a subscribers connection from an analog to a digital one, each end of the copper loop must be changed.

Upon this conversion, one of two link types are defined, Basic or Primary access.

Under the Basic Access rate, each subscriber will be linked to the central office by 2B channels and 1D channel, (2B+1D). For Basic Access each B Channel represents a 64 kbps stream and the D Channel represents a 16 kbps flow. A minimum rate of 144 kbps full duplex transmission is therefore available.

Typically, a basic access subscriber will be an individual private user where, for example, he can connect at the same time 2 phones, or 1 phone and 1 fax or 1 phone and 1 PC.

Under the Primary Access rate, each subscriber will be able to transmit and receive over 30 B channels (23 in USA) and 1 D channel. This data rate is compatible with the 2.048 Mbps rate for E1 carriers (1.536 Mbps in USA as T1).

Typically, a primary access will link to a complex system that can consists of a PABX or a private network or a MUX. The primary access specifies a 4 wire structure.

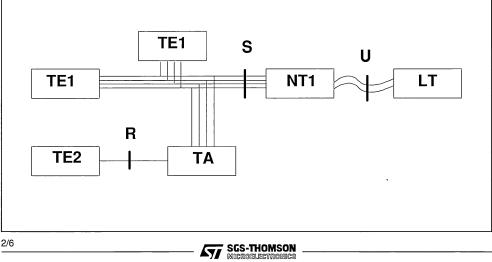

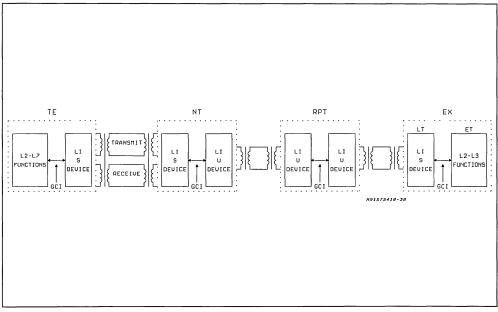

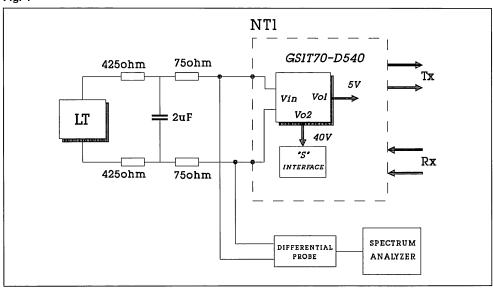

In Fig.1 you can see the ISDN scheme for a basic access connection. In the diagram, blocks represent equipment or physical, tangible points along the phone line. Refer to the Text Box 3 for the meaning of the acronyms.

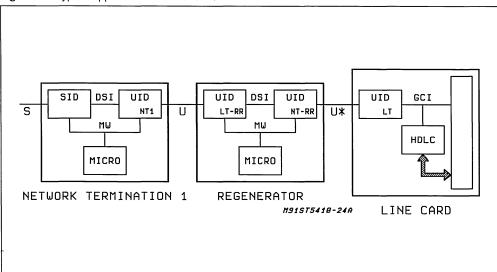

We can distinguish there the main parts of an ISDN link: the LT (Central Office digital line card), the U reference point (U interface), the NT, the S reference point (S interface), the TE (it can be both TE1 or TE2+TA).

Figure 1: Basic ISDN Loop.

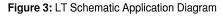

The LT or Line Termination performs the functions to send and receive the 2B+D channels exchanged by the Central Office and the user equipment adapting the data format typical of U interface (i.e. 2B1Q or 4B3T) with the data format of the Central Office internal bus that links to the ET (Exchange Termination) where the various channels are routed to the other party.

Functionally the LT consists of a U interface transceiver and a suitable controller for the hand-ling of the maintenance messaging.

Moreover the circuit for remote power feeding is also located on the LT: its function is to provide the power for NT feeding and, in case of emergency also for TE.

This kind of circuitry substitutes the traditional COMBO/SLIC analog line card systems of which SGS-THOMSON is a world wide leader (see SGS-THOMSON Line Card data book for more details).

Each subscriber will have two dedicated U interface transceivers: one in the LT and the other in the NT (close to the customer premises).

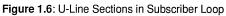

The physical link between the LT and NT is the U interface reference point: it is the standard 2 wire twisted copper cable.

Typically the cable section can be of 0.4mm, 0.6mm or more rarely 0.8mm. It can range up to a distance higher than 5 km for the 0.4mm section while reaching till 9 km for the 0.6mm.

Over these kind of distance a repeater is needed in order to insure a reliable and efficient transmission of data.

The Network Termination or NT terminates the network at the user's end of the 2 wire loop (on the subscribers premises). It is typically a plug

that is located in the subscriber permises. It converts the U interface to the S interface and acts as the master end of the user's line. Just like the TE, the NT is also a CPE (Customer Premises Equipment) and is owned by the PTTs (in USA instead is owned by the user).

The NT is considered CPE and physically resides at the end of the 2 wire loop. The signal exchanged by LT and NT travel only over two wires, the signal must be transmitted in both direction simultaneously. This transmission technique is called 'Echo Cancellation'.

The S interface is a physical link specified as a 4 wire (2 Tx and 2 Rx) bus that is completely regulated by CCITT I.430 specification. The distance over which the S interface can function is limited since in addition to electrically connecting (in parallel) up to 8 TE's with the NT, the S function has to arbitrate the use of these channels to all the TEs resident on the line.

| LT  | Line Termination            |

|-----|-----------------------------|

| U   | U reference point           |

| NT  | Network Termination         |

| S   | S reference point           |

| TE1 | Terminal Equipment 1        |

| ТА  | Terminal Adaptor            |

| R   | R reference point           |

| TE2 | Terminal Equipment 2        |

| CPE | Customer Premises Equipment |

## Text Box 3

For a point to point connection, in which only 1 TE is attached to the NT, the S interface is specified to have a range of 1 km. If the S interface is shared by more than 1 TE, a loop length of only 200 m can be achieved.

The TE or Terminal Equipment can be either a digital telephone, a personal computer, a facsimile machine, a printer or any kind of equipment that is able to interface directly the ISDN network (TE1) or a terminal made before the existence of ISDN that by the use of a TA or Terminal Adaptor function is linked either asynchronously or synchronously to the ISDN bus as synchronized data in the B or D channels.

## ISDN LAPD PROTOCOL

In order to set up a diser-to-user link and get access to a B channel (the equivalent operation of the dialling in the analog telephone network), certain formalities or protocol must be accomplished. All this message exchange take place in the D channel.

The term LAPD for link access protocol in the D channel is used to describe the message processing to set up a connection via the D channel.

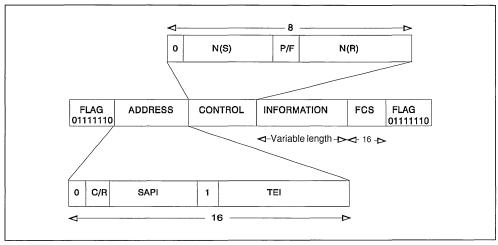

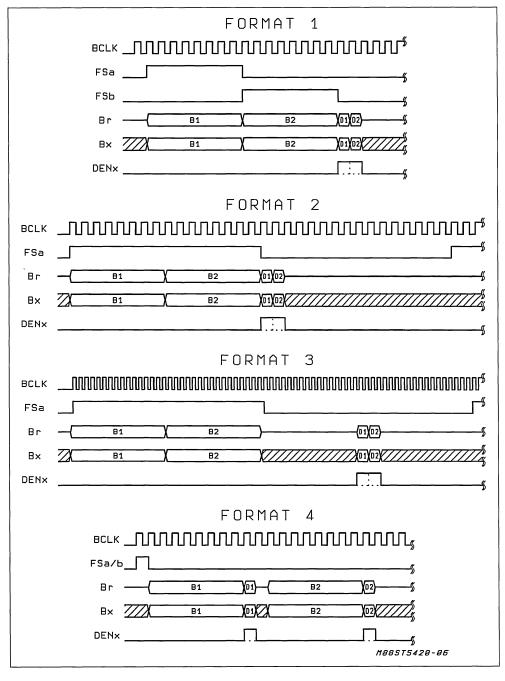

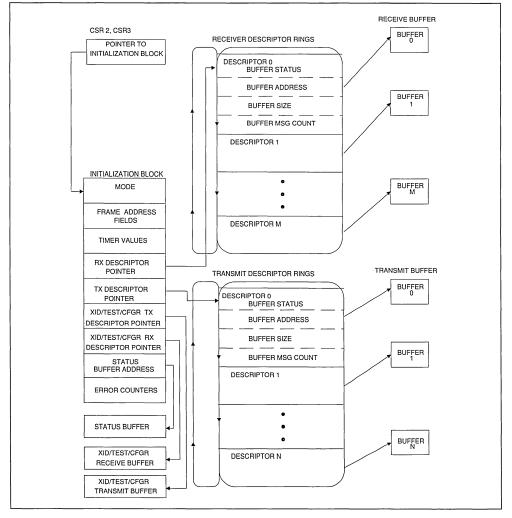

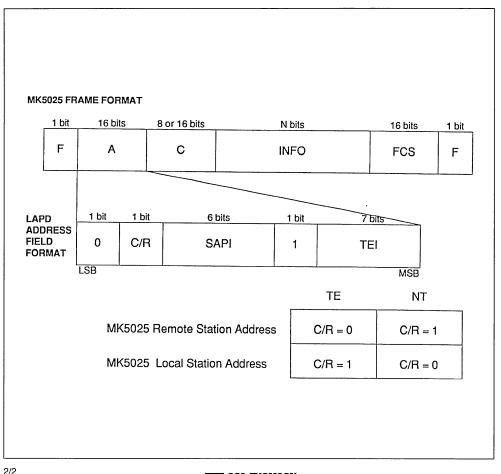

Typically the process is started by the calling end that send the called user identification number to the Central Office using a special format (described in Fig. 2) on the D channel. This special format is defined by the LAPD specification, and is basically composed by two delimiting flags, an address field where the logical (SAPI: Service Access Point Identifier) and physical (TEI: Terminal Endpoint Identifier) type of called user are described, a control field where the type of message being sent is defined, the information field where a message (optional) is contained and the FCS (Frame Check Sequence) field where a CRC

Once the message has been found correct and the proper path to the called user has been set, the link between the two parties take place thanks to a physical B channel link allocation.

D channel is not only used for call set up but also for any kind of information exchange or service demand the user likes to do with the Central Office.

## SGS-THOMSON ISDN PRODUCTS

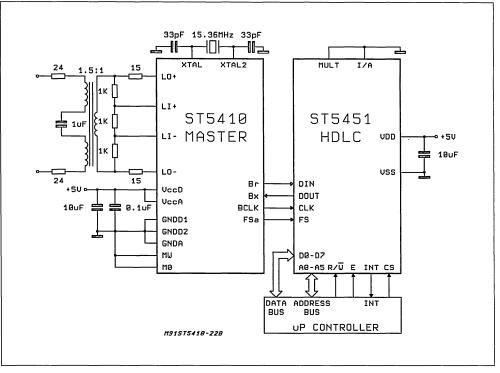

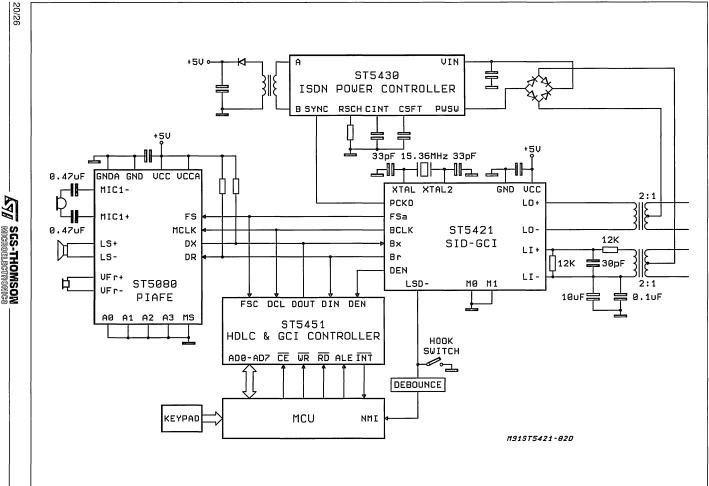

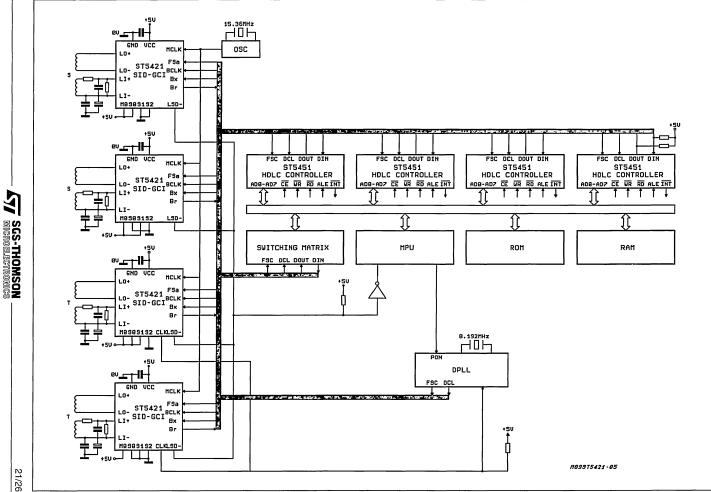

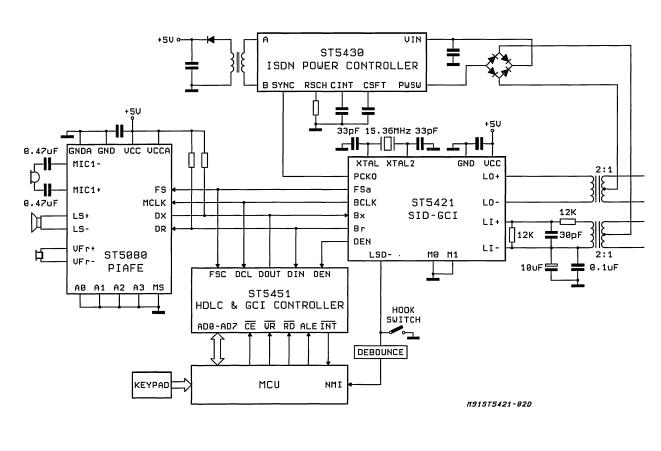

SGS-THOMSON has been working for the last 5 years in the development of the key devices of ISDN: ST5410 U Interface Device for 2B1Q line code, STU2071 U Interface Circuit for 4B3T line code, ST5421 S Interface Device, ST5451 HDLC&GCI controller, ST5430 ISDN Power Supply controller and ST5080 Programmable ISDN Audio Front End. Not only the effort has been spent in product design and development but also in specification study, application investigation, manufacture and engineering, technology research.

The technology choice greatly impact on the invention of ISDN architecture. As a matter of fact, being today activity the cornerstone for tomorrow integration upgrade, design cannot be done with standard processes, but with the most advanced both in term of lithography and metal layers. The HCMOS3/3A technologies are 1.2 micron process with double metal layers: a convenient tool that gives, beside immediate advantage of integration also outstanding geometrical reduction capability.

HCMOS3 is dedicated to fully digital device, while HCMOS3A, thanks to the addition of implanted polysilicon to substrate capacitor is well suited for mixed analog digital device.

ISDN architecture are conditioned not only by the long length link standards, but also the chip-tochip communication at board level that is extremely important in terms of modularity and expandable potentiality.

## ISDN TUTORIAL

### Figure 2

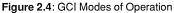

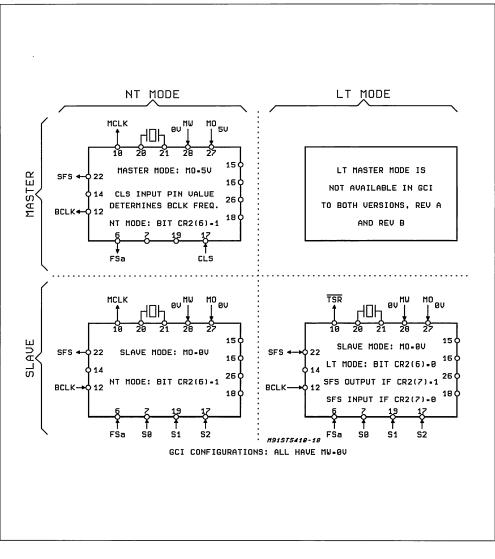

This big industrial problem (big both for semiconductor houses and for equipment manufacturers) has been skillfully solved with the invention of General Circuit Interface (GCI). This is an industrial standard jointly specified by Alcatel, Italtel, Plessey (now GEC Plessey Telecommunications Limited) and Siemens. SGS-THOMSON Microelectronics has participated to the definition of GCI as Associated Semiconductor Manufacturer.

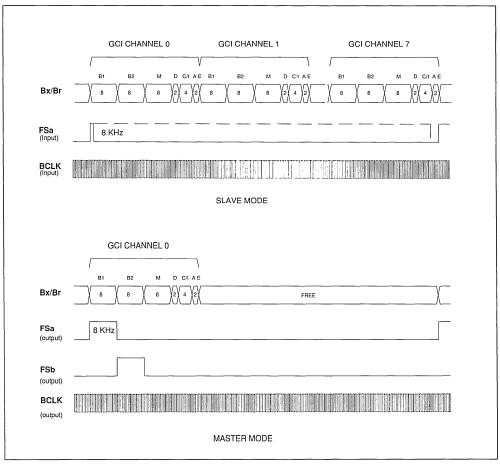

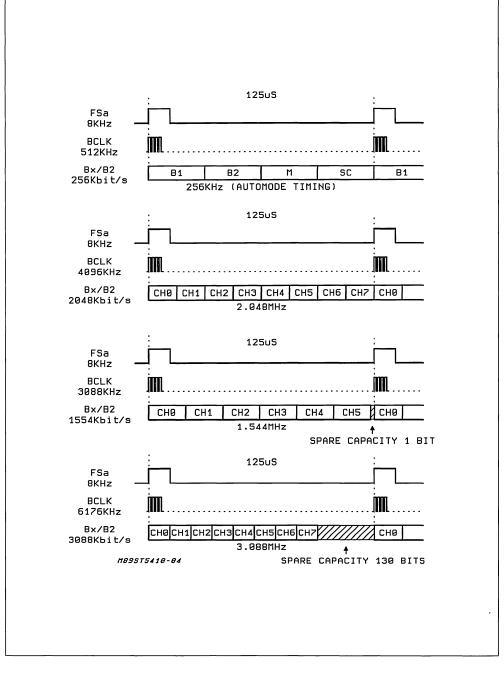

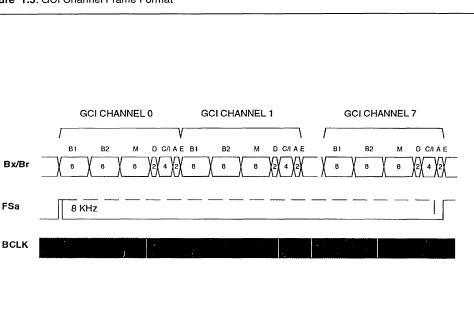

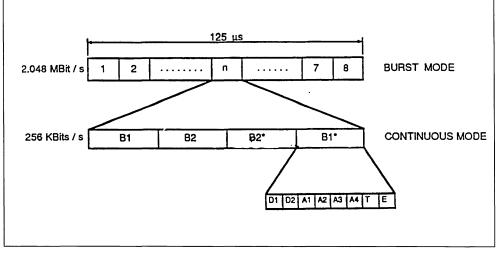

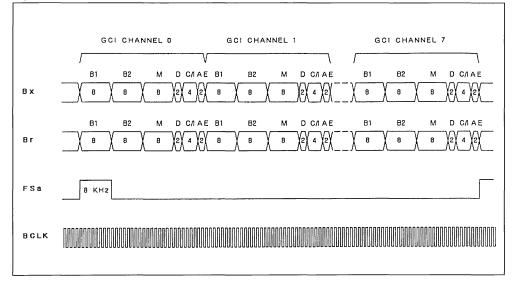

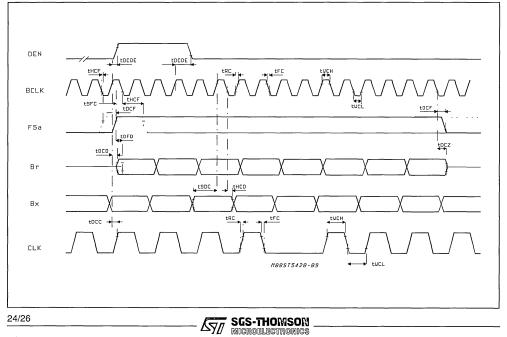

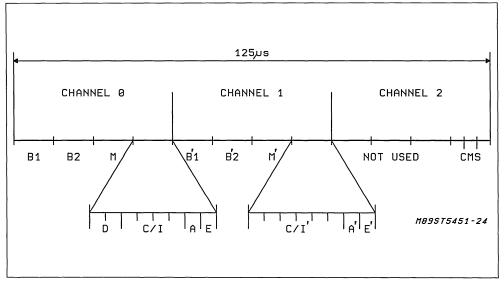

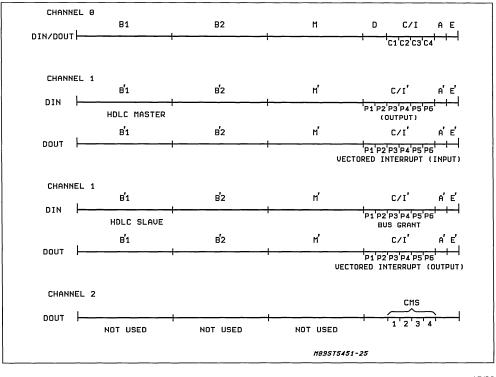

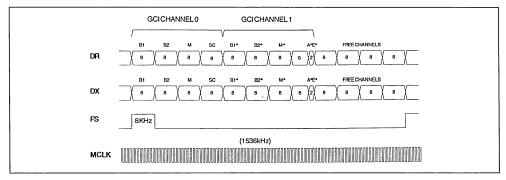

GCI multiplexes on the same bus either voice/data (B channels), signaling (D channel), maintenance and service information (Monitor channel) and management messages (Command/Indicate channel) organized in four octets for a total of 256kHz data rate clocked at a double speed. To support all those data only four wires only are needed (Data-in, Data-out, Frame Synch

and Clock) leading to a big simplification in PCB layout. Up to 8 GCI channels can be multiplexed together with a maximum data rate of 3088kHz. In terms of application it means that one GCI master device may drive up to 8 peripherals. GCI, beside having become a de facto standard, has without any doubt advantages in term of PCB layout directness and configuration change simplicity.

ST5410 is the U Interface Device (UID) for 2B1Q line code. This is, by far, the most important device dedicated to ISDN.

SGS-THOMSON target has been to produce a circuit that, beside being fully complying with both ANSI and ETSI specification, has the following characteristics: to be a single chip (28 pin) application, to have a power consumption lower than

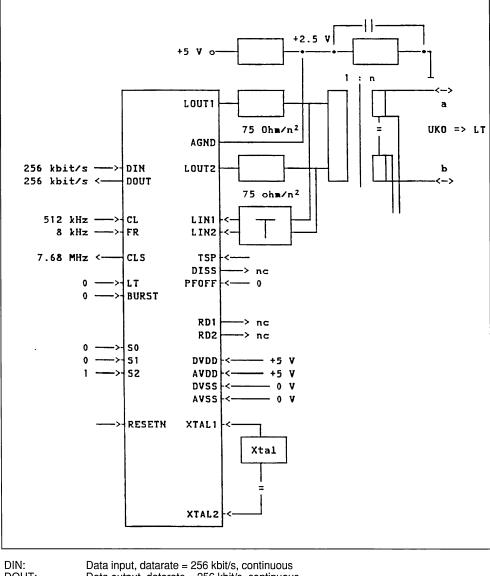

#### Figure 3.

SGS-THOMSON

MICROELECTRONICS

<u>\</u>7

300mW from a single 5V power supply, to be GCI compatible and usable both in Line and Network Terminations.

The device accomplish all the system features to assist in 2B1Q standard procedures: NT/LT activation deactivation, CRC calculation and verification, Superframe/Frame formatting, EOC channel and Overhead bits transmission receiving with automatic messaging checking, on-chip timing recovery, elastic data buffers and backplane clock dejitterization plus digital and analog loopbacks.

ST5410 is expected to reach 5.5km range on 24AWG/26AWG standard cables supporting bridge taps, splices and mixed gauges as per the 15 test loops defined by ANSI to comply with the most complicated subscriber loop configurations.

STU2071 UIC (U Interface Circuit) is the U transceiver for the 4B3T line code. As ST5410 it is a single chip device (28 pin) requiring very low number of external components.

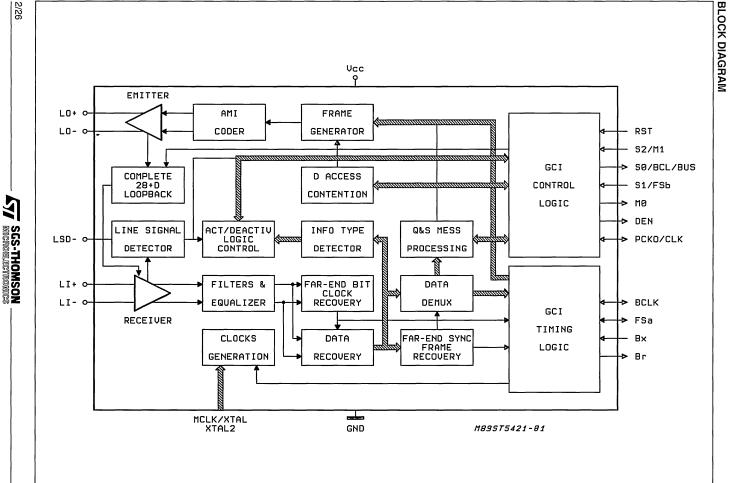

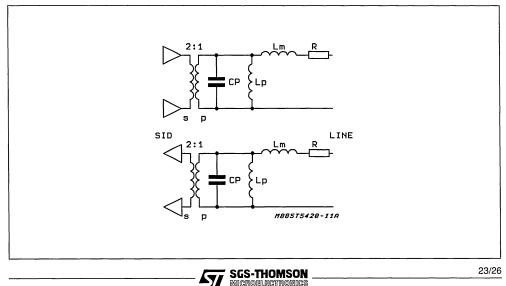

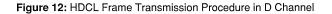

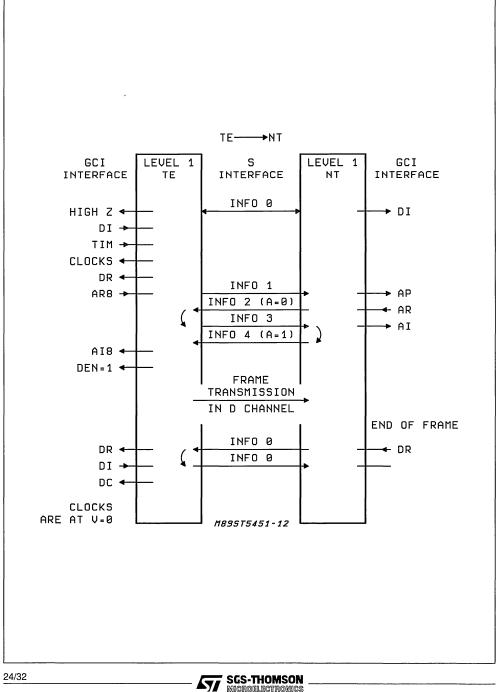

ST5421 S Interface Device with GCI (SID-GCI) is the cornerstone that ST is offering on the market for an easy and efficient design of ISDN Terminal and Network Termination equipments. It can be divided in three parts: the GCI and control digital circuitry, the S line driver and receiver filtering circuits and the blocks related to the control of the operation. ST5421 is fully complying with recommendation 1.430 even overcoming the requirements of CCITT as far as the transmission performances are concerned.

Figure 4: ISDN Building Blocks.

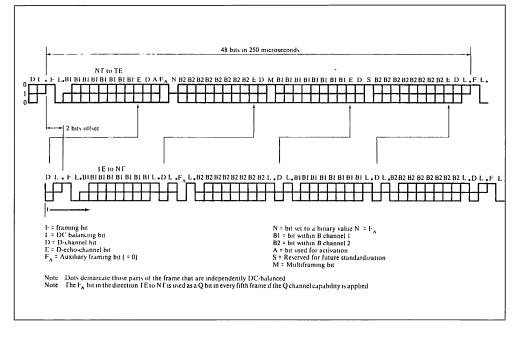

As per I.430, the device handles the four wires S interface (two wire pair: one for Tx and one for Rx) at a rate of 192kbit/s carrying the 2 B channels at 64kbit/s each for data and voice transmission, the D channel at 16kbit/s for signalling and packet data transfer, plus other extra service bits for frame alignment, D bits echo, and S&Q bits for multiframe monitor messaging.

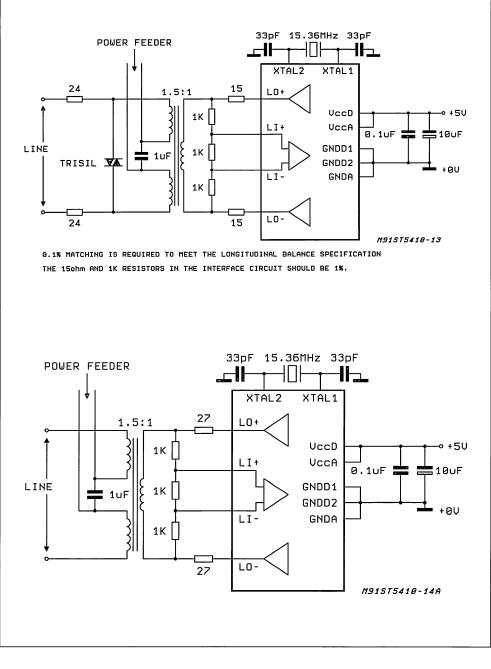

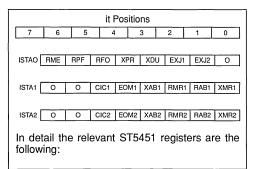

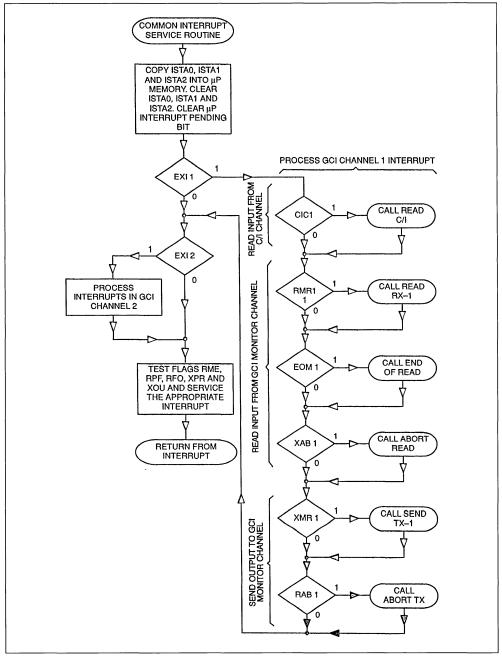

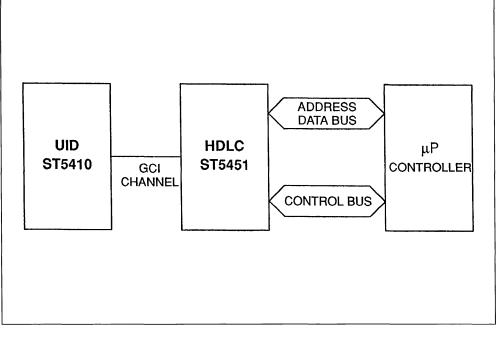

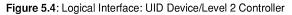

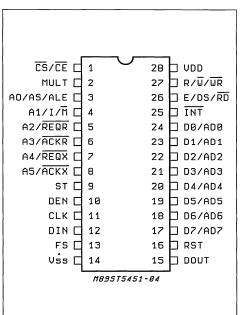

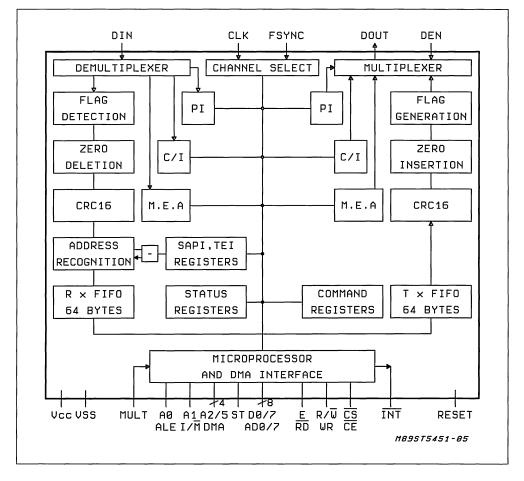

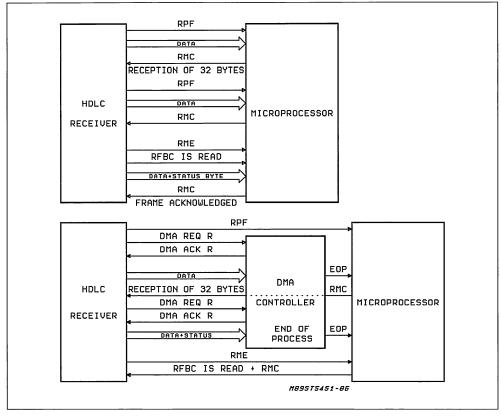

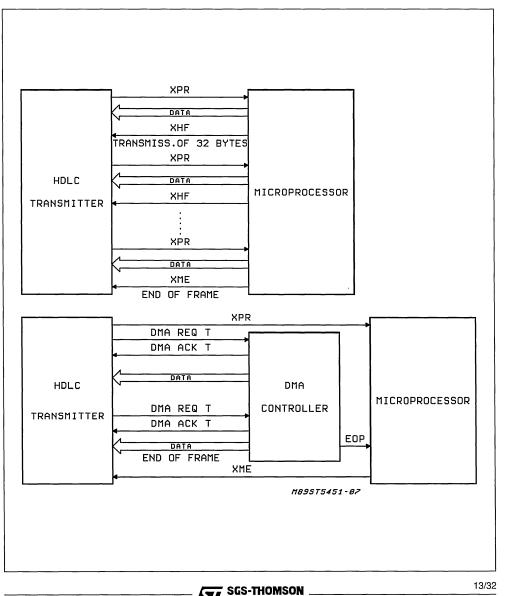

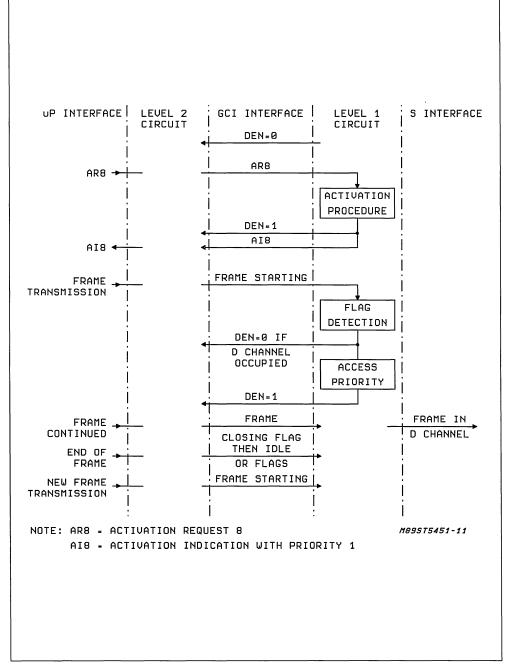

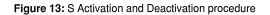

ST5451 handles HDLC packet both in transmit and receive direction implementing LAPD and LAPB procedures. The device can be interfaced to any kind of PCM data stream and handles many different formats of the standard 2B+D channels provided a strobe is set during D bits time window. As far as HDLC packets are concerned ST5451 manages opening and closing flags, checks and calculates CRC, manages SAPI and TEI recognition and handles abort and idle signals.

ST5451 innovation is to be a GCI controller; it performs all the control functions on the Monitor and Command/Indicate channels, that GCI specify to be exchanged with a proper protection protocol to assure the consistency of the service messages exchanged.

SGS-THOMSON HDLC&GCI controller has builtin registers dedicated to Monitor and C/I channels and a logic circuitry that saves the local Up a lot of elaboration time. Moreover a selectable P interface suitable to be used both with multiplexed and non multiplexed intelligent units. When multi-

MICROELECTRONICS

13

plexed micro interface is selected a DMA interface is provided; that helps in an optimize and fast access to the 128 bytes built-in FIFOs memories (64 for Tx and 64 for Rx).

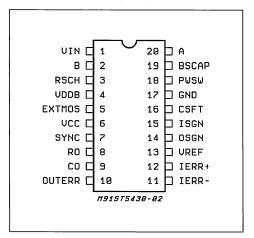

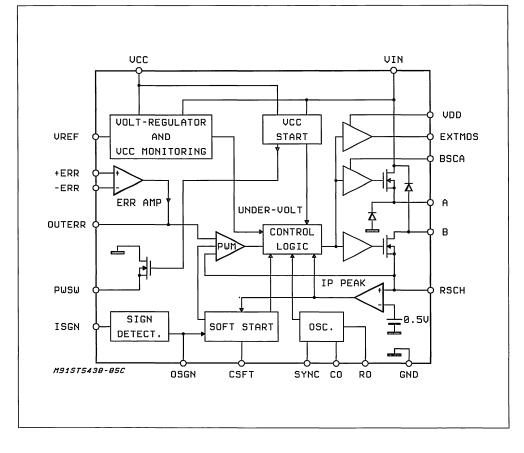

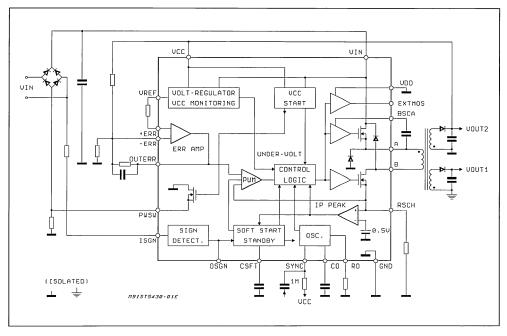

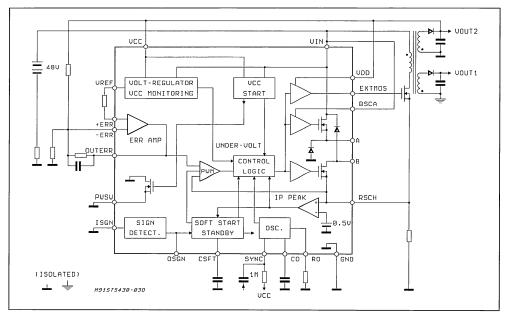

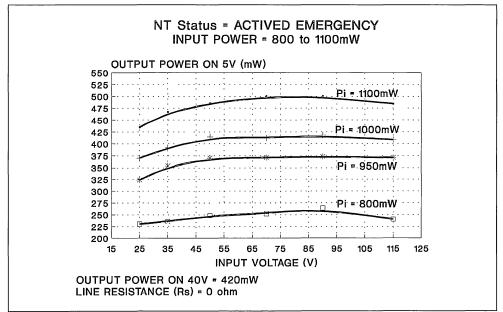

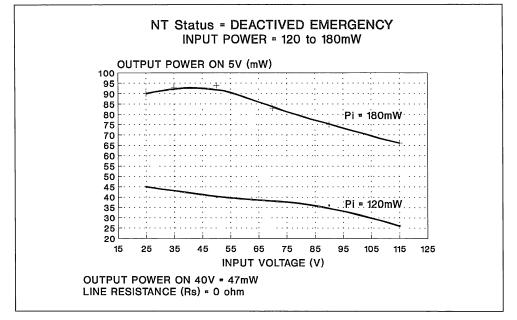

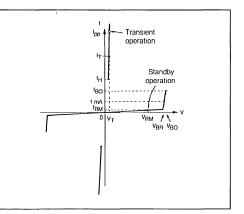

ST5430, named ISDN Power Supply controller, is a Switch Mode Power Supply specially studied for ISDN application either in Terminals and in Network Terminations. Among its features for ISDN the soft-start capability, the undervoltage and the polarity reversal detection and the overcurrent detection to go in foldback limitation are the most outstanding. The input voltage can go up to 100 Volt while the oscillator frequency can go from 10 to 100 khz.

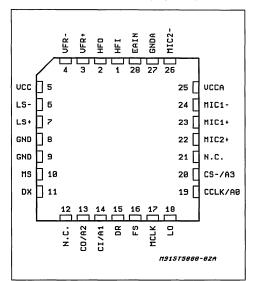

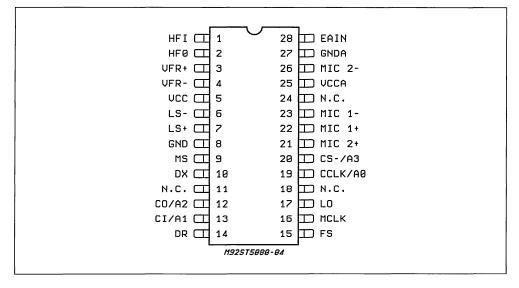

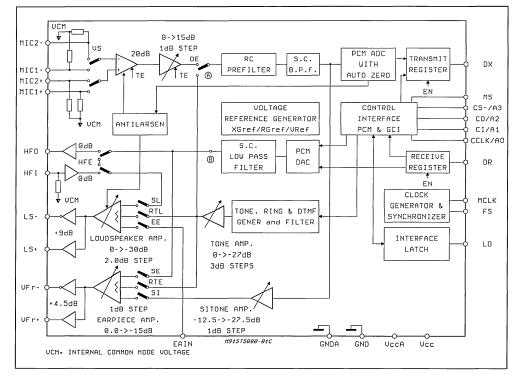

ST5080, Programmable ISDN Audio Front End, is much more than a 5V Codec and Filter. Completely programmable in Gains, it features also various characteristics for an easy design of an ISDN or a digital phone. ST5080 features also a built-in loudspeaker amplifier, dual switchable microphone amplifier inputs, internal sidetone circuit, on-chip anti-Larsen circuit and a circuitry for direct connection to very simple hand-free circuit such as the TEA7540 a device that is becoming the star of this kind of application.

## GLOSSARY

## INTEGRATED SERVICES DIGITAL NETWORK

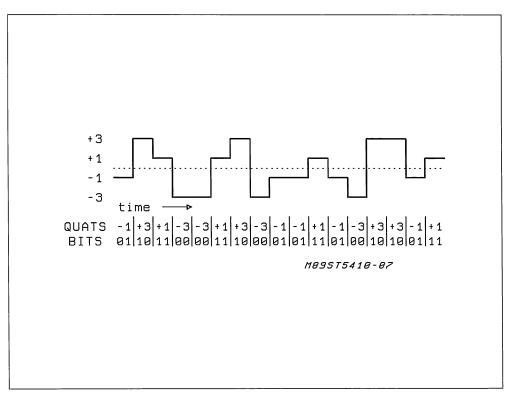

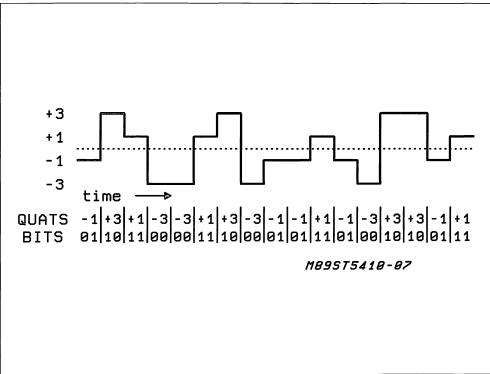

**2B1Q** - Line code in which two binary bits are converted into one quaternary symbol for transmission across the U interface. Specified by ANSI and ETSI.

**4B3T** - Line code in which four binary bits are converted into three ternary symbols for transmission across the U interface.

Access Protocol - A defined set of procedures that is adopted at an interface at a specified reference point between a user and a network to enable the user to employ the services and/or facilities of that network.

Adaptive Equalization - Technique for compensating the effect of different quality and lenght of lines (typically distortion) on the carried signals, getting a flat frequency response.

A-Law - European standard for the digitization of voice in a non-linear manner.

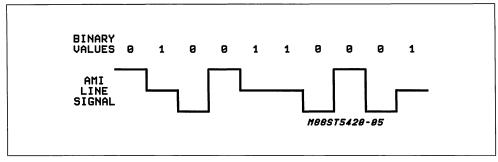

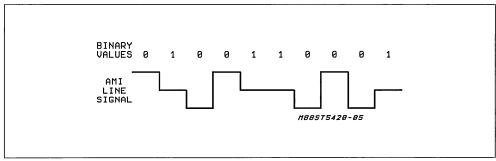

**AMI** - Alternate Mark Inversion. A special line code where "1s" are represented by 0 volt, "Os" by alternate positive or negative levels. Used over S interface bus.

**Amplifier** - An electronic circuit used on an analog transmission facility that detects a weak signal and makes it stronger. An amplifier often amplifies the noise on the channel as well as the original signal.

ANSI (American National Standard Institute) - It coordinates the activity of ITU and ISO for U.S. and defines the communication standard there.

**Architecture** - An overall scheme or plan that may be partially or fully implemented. An architecture represents the goal toward which its implementors strive. The term architecture is often used to describe database management systems, operating systems, data communication systems, and other highly complex software/hardware mechanisms.

Attenuation - Decrease in the magnitude of current, voltage, or power of a signal in trasmission between two points. Can be expressed in decibels (dB).

Audio Frequencies - Frequencies that can be heard by the human ear (typically 30 to 20,000 hertz). In Telecom (telephone) the filters limit the bandwidth to 340/3400Hz range.

**Bandwidth -** The range of frequencies available. The difference expressed in Hertz (cycles per second) between the highest and lowest frequencies of a frequency band.

**Baud** - Unit of signaling speed. The speed in baud is the number of discrete conditions, or signal events, per second. If a signal event represents only one bit condition, the line speed in baud is the same as the bit rate in bits per second. When each signal event represents other than one bit, baud does not equal bits per second.

**B Channel** - A switchable, optionally transparent, 64k-bps channel. Two B channels are included in the ISDN basic-rate service.

**Bearer services** - Basic communications services. Includes 64kbit/s circuit switched digital services to be used for both voice telephony and non-voice services; packet switched services operating at speeds of up to 1.5 Mbit/s in North America and 2 Mbit/s in Europe.

BER (Bit Error Rate) - The ratio of the number of data units in error to the total number of data units.

BRA - Basic Rate Access.

Burst - Several events occuring within a short period of time.

**CCITT (Comite' Consultatif International Telegraphique et Telephonique)** - An organization in the International Telecommunication Union that publishes recommendations of importance to data communication. Reccommendation X.25 is published by the CCITT.

**Centrex** - A service offered by operating telephone companies which provides, from the telephone company central office, functions and features comparable to those provided by a PBX.

March 1992

CEPT - Conference for European Post and Telecommunications.

**Channel** - A transmission path between two points. It is usually the smallest subdivision of a transmission system by means of which a single type of communication service is provided.

**Circuit Switching** - A method of communicating in which a dedicated communications path is established between two devices through one or more intermediate switching nodes. Unlike packet switching, digital data are sent as a continuous stream of bits. Data rate is guaranteed, and delay is essentially limited to propagation time. Provides a permanent end-to-end path between two terminals for the duration of the communication.

**CMOS (Complementary Metal Oxide Semiconductor)** - A technology where both MOS p-channel and n-channel are diffused together.

**CO (Central Office)** - The place where communication common carriers terminate customer lines and locate the switching equipment that interconnects those lines. Also referred to as an exchange, end office, or local central office (see LT).

**CPE (Customer Premises Equipment)** - The apparatus present at the user location that allows connection to the line; in ISDN they are NT and TE.

**CODEC** (Coder/decoder) - Transforms analog data into a digital bit stream (coder), and digital signals into analog data (decoder).

**COMBO** - Combined codec and filter IC. It supports voice transmission over an ISDN network by converting analog signals in a telephone handset into the digital signals required by the module interface. COMBO is a trademark of National Semiconductor.

**Common Carrier** -In the United States, companies that furnish long-distance telecommunication services to the public. Common carriers are subject to regulation by federal and state regulatory commissions.

**Common Channel Signaling** - A method of signaling in which signaling information relating to a multiplicity of circuits, or function or for network management, is conveyed over a single channel by addressed messages.

**Contention** - A method of line control in which the terminals request to transmit. If the channel in question is free, transmission proceeds; if it is not free, the terminal waits until the channel becomes free.

**CRC (Cyclical Redundancy Check)** - Use of a particular type of arithetic algorithm for generating error detection bits in a data link protocol (as CRC4 or CRC16).

**Crosstalk** - The unwanted transfer of energy from one circuit, called the disturbing circuit, to another circuit, called the disturbed circuit.

CSDN - Circuit Switched Digital Network.

**D** Channel - A channel whose primary purpose is to convey signaling information between a terminal and the network switch but whose surplus capacity can be used for user-packet data and other data, such as telemetry. It operates at 16k bps for basic-rate access and 64k bps for primary-rate access usually in HDLC format.

**Decibel (dB)** - One-tenth of a bel. A unit for measuring relative strength of a signal parameter, such as power or voltage. The number of decibels is 10 times the logarithm (base 10) of the ratio of the measured quantity to the reference level. The reference level must always be indicated, such as 1 milliwatt for power ratio.

**Digital PBX** - A private branch exchange (PBX) that operates internally on digital signals. Thus, voice signals must be digitized for use in the PBX.

**Digital Transmission** - The transmission of digital data or analog data that have been digitized, using either an analog or digital signal, in which the digital content is recovered and repeated at intermediate points to reduce the effects of impairments, such as noise, distortion, and attenuation.

**DSI (Digital Systems Interface)** - A chip-to-chip interface for ISDN modules, supported both by National Semiconductor and SGS-THOMSON.

ET (Exchange Termination) - The part of Central Office that implements channel switching.

ETSI - European Telecommunication Standard Institute.

**Exchange Area** - A geographical area within which there is a single uniform set of charges for telephone service. A call between any two points within an exchange area is a local call.

Filter - A network designed to transmit of frequencies within one or more bands and to attenuate of other frequencies.

2/5

Flow Control - A function performed by a receiving entity to limit the amount or rate of data sent by a transmitting entity.

Format - A specified arrangement of data that permits identification of control and information fields by their location in the transmitted data stream.

Four Wire Circuit - A facility in which transmission is done over a twisted pair and reception is done over another twisted pair.

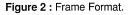

**Frame** - Sequence of time slots repeated according to sampling rate. In BRA frame consists of 48 bit time slots repeated every 250 us. In PRA a frame consists of 192 bit time slots (N.A. standards) /256 bit time slots (CCITT/E1, CEPT) repeated every 125 μs.

Full-Duplex Transmission - Transmission of data in both directions at the same time.

**GCI** - The General Circuit Interface (GCI) is a standard interface between devices for subscriber access in ISDN and analogue enviroments. The principle use in the various applications is to control the subscriber line interface circuitry. It is intended that GCI will gain international acceptance as an industry standard due to its well defined and supported features.

GCI-SCIT - Special version of GCI for terminal application.

Half-Duplex Transmission - Data transmitted in either direction, one direction at a time.

Handshaking - Exchange of predetermined signals for purposes of control when a connection is established over a data link.

**HDLC (High Level Data Link Control)** - Bit-oriented protocol to ensure integrity of data during the transmission process by adding control information in a special frame format, standardized by the International Standards Organization (ISO) and documented in ISO Standards 3309 and 4435.

HDLC Controller - A circuit for full HDLC frame control, eg. ST5451, available from SGS-THOMSON.

**IDN (Integrated Digital Network)** - A communication network that combines the technologies of digital switching and digital transmission of information.

**IEEE (Institute of Electrical and Electronics Engineers)** - An organizatiion that, among other activities, produces data communication standards. Particularly important are the IEEE 802 group of standards for variious types of local area networks.

Inband Signaling - Signaling that uses the same paths and frequencies as that used for voice or data messages.

**Interface** - A common boundary between two systems or pieces of equipment that ensures proper connection between equipment.

**ISDN (Integrated Services Digital Network)** - A communication network that uses an integrated digital network (IDN) to carry all forms of traffic, such as voice, computer data, and facsimile.

**ISO (International Standards Organization)** - An international organization for standardization. ISO publishes many standards that are important for data communication. The OSI Refereference Model is being developed by the ISO.

**ITU (International Telecommunication Union)** - The telecommunications agency of the United Nations, established to provide standardized communication procedures and practices including frequency allocation and radio regulations on a worldwide basis. The CCITT is part of the ITU. (See also International Telegraph and Telephone Consultative Committee.)

LAN - Local Area Network.

LAPB & LAPD (Link Access Protocol Balanced & D Channel) - Bit-oriented data link protocols standardized by the CCITT that specify the functions of the data link level of CCITT Recommendation X.25. LAP and LAPB are compatible subsets of HDLC. (See also HDLC.)

**Local Loop** - A transmission path, generally twisted pair, between the individual subscriber and the nearest switching center of a public telecommunications network. Also referred to as a subscriber loop.

LOOP - A pair of wires carrying direct current between central office and a customer's terminal.

LT (Line Termination) - A digital line card (usually equipped with U interface or S interface device) that provides termination of the subscriber loop at the PBX or central office.

**MICROWIRE** - Synchronous serial data transfer between a microcontroller and one or more serial device. It is supported by both National and SGS-THOMSON.

MICROWIRE is a trademark of National Semiconductor

**Modulation** - The process by which some characteristic of one wave is varied in accordance with another wave or signal. This technique is used in modems to make data machine signals compatible with communication facilities.

**Multiplexing** - Use of common channel in order to make two or more channels, either by splitting the frequency band transmitted by the common channel into narrower bands, each of which is used to constitute a distinct channel (frequency-division multiplexing), or by allowing this common channel to several information channels, one at a time (time-division multiplexing).

NMOS (N-channel Metal Oxide Semiconductor) - A technology where MOS n-channel is diffused.

**Noise** - Random electrical signals, introduced by circuit components or natural disturbances, that tend to degrade the performance of a communication channel.

**NT1 (Network Termination 1)** - An equipment (located at customer premises) that, beside terminating the U line, converts the U line code (2B1Q or 4B3T) into the S interface format (1.430).

**NT2 (Network Termination 2)** - Functionally similar to a PABX in that it can accept many S lines on the Network side, connect to many S lines of the user side and provide also internal switching capability.

**OSI (Open System Interconnection)** - This model for the construction of data networks was first published by the ISO in November 1978. It was intended to provide a basis for open systems architecture a network in which there is no single central control point, but the inweheel control resides in various nodes of the network operating to common standards. Each control level provides a clear definition of the protocols and formats and allows interaction between users who have implemented the architecture. The control levels or layers have been defined as follows:

Layer 1 - Physical Layer. The phisical transport of the bit stream.

- Layer 2 Data Link Layer.

- Laver 3 Network Laver. Provides routing and relaying through intermediate systems.

- Layer 4 Transport Layer. Provides transparent, error-free transmission between end-systems.

- Layer 5 Session Layer. Handles the dialogue between communicating processes.

- Layer 6 Presentation Layer. Concerned with standard presentation of information.

Layer 7 - Application Layer. Provides the user with network services via applications programs.

**PABX (Private Automatic Branch Exchange)** - An automatic, private switchboard linked to the Central Office with a analog or digital connection and with several internal users providing also special internal services (conference, automatic busy line recall, abbreviated selection and so on).

**Packet Switching** - The techinique of transmitting units of data (called packets) of some fixed maximum size through a mesh-structured network from an originating station to a destination station. In packet switching, a physical path is not set up between the originating and destination station. Contrast with Circuit switching.

**PCM (Pulse-Code Modulation)** - A modulation technique in which a pulse train is created in accordance with a code. With PCM, the input signal is first quantized, and the signal amplitude at a particular instant in time is represented by a binary numer that can be transmitted over a digital communication channel as a series of pulses of some fixed amplitude. PCM is used to convert an analog signal, such as telephone voice, into a digital bit stream.

**PDN (Public Data Network)** - A communication network, designed specifically for the transmission of computer data, that is used by many individual subscribers. Most public data networks use the technique of packet switching rather than circuit switching.

**Point - to - Point** - A network configuration in which two communicating stations are connected by a single communications channel that is not shared by any other stations.

**PRA** (Primary Rate Access) - Multiplexed communication link to an ISDN where the link has a channel structure consisting of either 23 or 30 B channels for voice or data and one D channel for control.

**PRI (Primary Rate Interface)** - A full digital connection, typically between PABX and CO or CO and CO, at 2Mbit/s in Europe (PCM30) and at 1.544Mbit/s in U.S. (PCM24).

**Protocol** - A formal statement of the procedures that are adopted to ensure communication between two or more functions within the same layer of a hierarchy of functions.

PTT - Postal Telephone and Telegraph. Generic term for European telephone administration.

**R Interface** - Connects a terminal adapter (TA) to non ISDN (TE2) equipment, often through an RS-232C port. Industry-standard serial data transmission interface. Developed for single-ended data transmission at <sup>4/5</sup>

up to 19.2 Kb/s. Industry-standard differential data transmission interface. Developed for long distances and noise environments.

**RBOC (Regional Bell Operating Company)** - Before the divestiture of AT&T, the 22 Bell Operating Companies were AT&T subsidiaries that built, operated, and maintained the local and intrastate network and provided most of the day-to-day service for customers. Alter divestiture, the BOCs retain their identity within seven regional companies (RBOCs) and are responsible for local service as defined by local access and transport areas (LATAs).

**RS-423** - Industry-standard data transmission interface. Developed for single ended data transmission with a maximum data rate to 100 Kbaud (up to 30 ft.) and a maximum distance of 4000 feet (up to 1 Kbaud).

S interface - A 4 wire 1000 meter Basic Access interface between various TE/TA or NT equipment. Usually applied within a Private Network such as PBX. The point where ISDN terminal equipment (TE) customer premise can connect to network termination (NT) equipment. Fully defined by CCITT recommendation I.430.

SAPI (Service Access Point Identifier) - A field of LAPD frame that indicates the logical address of the called user.

**Signaling** - The exchange of information specifically concerned with the establishment and control of connections, and with management, in a telecommunication network.

SS 7 (Signaling System Nr.7) - CCITT standards for communicating between ISDN carrier switches where signaling infos are one common channel.

TA - Terminal Adaptor. This function rate adapts existing non-ISDN terminals, printer, etc., to the ISDN.

TE1 - Terminal equipment. Any terminal, printer, phone, voice/data terminal designed to be compatible with and directly connected to ISDN.

TE2 - Terminal Equipment, non-ISDN.

TEI (Terminal Equipment Identifier) - A field of LAPD frame that indicates the physical address of the called user.

**Teletext** - A one-way information retrieval service. A fixed number of information pages are repetitively broadcast on unused portions of a TV channel bandwidth. A decoder at the TV set is used to select and display pages.

**Time Compression Multiplexing** - A means for providing full-duplex digital data transmission over a single twisted pair. Data are buffered at each end and are sent across the line at approximately double the subscriber data rate, with the two ends taking turns.

T Interface - Electrically identical to the S interface, the T interface has a different protocol than the S interface to link NT2 boxes to the NT1 box.

Transceiver - Transmitter - Receiver.

Twisted Pair - A pair of wires used in transmission circuits that are twisted together to minimize coupling.

$\mu$ Law - North American standard for the digitization of voice in a non-linear manner.

UART - Universal Asynchronous Receiver/Transmitter. Local serial channel.

**U Interface** - A twisted-pair subscriber loop that provides basic-rate access to the NT1 reference point from the ISDN network (typically LT). This interface only supports point-to-point operation.

Videotex - A two-way information retrieval service accessible to terminals and TV sets equipped with a special decoder. Pages of information at a central resource are retrieved interactively over a switched telephone line connection.

Wideband - Communication channel having a bandwidth greater than a voice-grade channel and therefore capable of higher-speed data transmission. Sometimes called broadband.

## ALPHANUMERICAL INDEX

## ISDN

| Type<br>Number | Function                                              | Page |  |

|----------------|-------------------------------------------------------|------|--|

| GS1T70-D540    | ISDN DC-DC Converter                                  | 275  |  |

| ST5080         | Piafe Programmable ISDN Audio Front End               | 245  |  |

| ST5410         | 2B1QU Interface Device                                | 27   |  |

| ST5410         | User Manual                                           | 81   |  |

| ST5420         | Sid- $\mu$ W: S/T Interface Device with Microwire/DSI | 153  |  |

| ST5421         | Sid-GCI: S/T Interface Device with GCI                | 187  |  |

| ST5430         | ISDN Power Supply                                     | 207  |  |

| ST5451         | ISDN HDLC and GCI Controller                          | 213  |  |

| STU2071        | 4B3TU Interface Circuit                               | 139  |  |

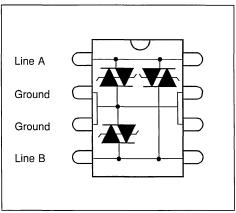

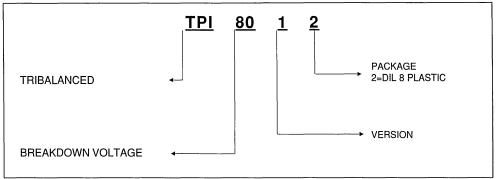

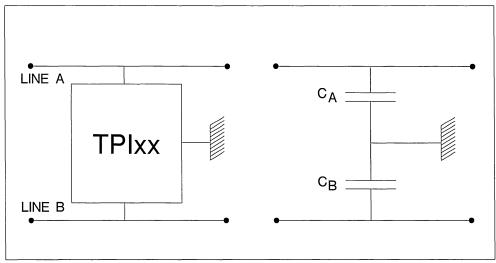

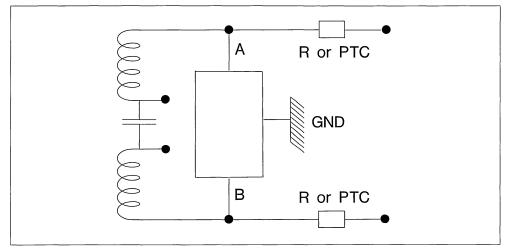

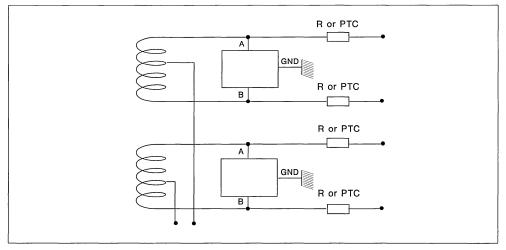

| TPI80/TPI120   | Tribalanced Protection for ISDN Interfaces            |      |  |

| DATACOM        |                                                       |      |  |

| Type<br>Number | Function                                              | Page |  |

| MK5021         | Technical Manual                                      | 293  |  |

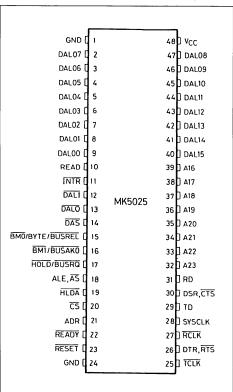

| MK5025         | CCITTZ.25 Link Level Controller                       | 339  |  |

| MK50H25        | High Speed X.25 Link Level Controller                 | 379  |  |

| MK5027         | SS7 Signalling Link Controller                        | 381  |  |

| MK5029         | Technical Manual                                      | 399  |  |

| Application<br>Note<br>Number | Function                      | Page |

|-------------------------------|-------------------------------|------|

| AN489                         | MK5025 Single Channel LAPD    | 451  |

| AN490                         | MK5025 NET2 Conformance       | 453  |

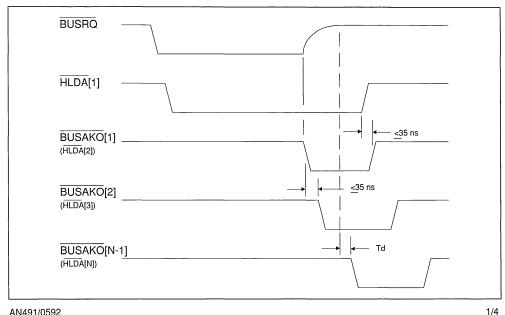

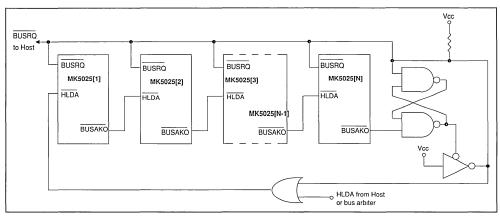

| AN491                         | MK5025 Daisy Chain DMA        | 455  |

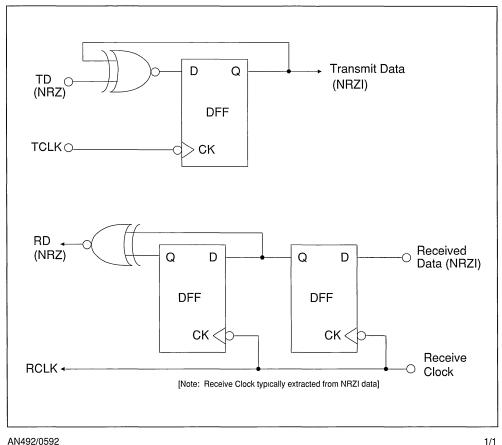

| AN492                         | MK5025 NRZ to NRZI Conversion | 459  |

| AN493                         | MK5025 Transparent Mode       | 461  |

| AN494                         | MK5025 Synchronous Timing     | 465  |

## **ISDN DATASHEETS**

## ST5410

ADVANCE DATA

## 2B1Q U INTERFACE DEVICE

## **GENERAL FEATURES**

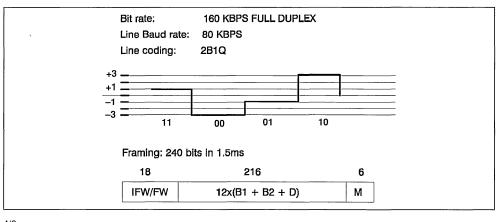

- SINGLE CHIP 2B1Q LINE CODE TRANS-CEIVER

- SUITABLE FOR BOTH ISDN AND PAIR GAIN APPLICATIONS

- MEETS OR EXCEEDS ANSI T1.601-1988 U.S. STANDARD

- MEETS OR EXCEEDS ST/LAA/ELR/822 FRENCH SPECIFICATIONS

- SINGLE 5V SUPPLY

- 28 PINS PACKAGE

- 300mW ACTIVE AND 10mW INACTIVE POWER DISSIPATION

- HCMOS3A SGS-THOMSON ADVANCED DOUBLE-METAL SINGLE-POLY CMOS PRO-CESS

### TRANSMISSION FEATURES

- 160 KBIT/S FULL DUPLEX TRANSCEIVER

- 2B1Q LINE CODING WITH SCRAMBLER/DE-SCRAMBLER

- 18KFT (5.5KM) ON 26AWG/24AWG TWISTED PAIR CABLES

- SUPPORTS BRIDGE TAPS, SPLICES AND MIXED GAUGES

- >70DB ADAPTIVE ECHO-CANCELLATION

- DIGITAL FEEDBACK EQUALIZATION

- ON CHIP TIMING RECOVERY WITHOUT EX-TERNAL PRECISION COMPONENTS

- DIRECT CONNECTION TO SMALL LINE TRANSFORMER

### SYSTEM FEATURES

- ACTIVATION/DEACTIVATION CONTROLLER

- ON CHIP CRC CALCULATION AND VERIFI-CATION INCLUDING PROGRAMMABLE BLOCK ERROR COUNTER

- EOC CHANNEL AND OVERHEAD-BITS TRANSMISSION WITH AUTOMATIC MESS-AGE CHECKING

- GCI AND MW/DSI MODULE INTERFACES COMPATIBLE

- DIGITAL LOOPBACKS

- ELASTIC DATA BUFFERS AND BACKPLANE CLOCK DE-JITTERIZER

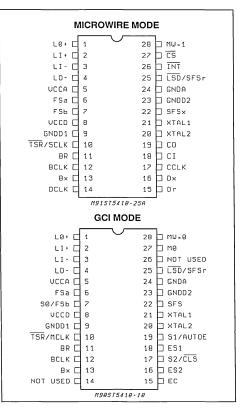

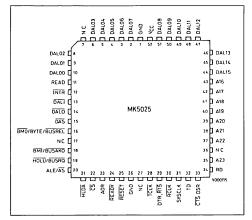

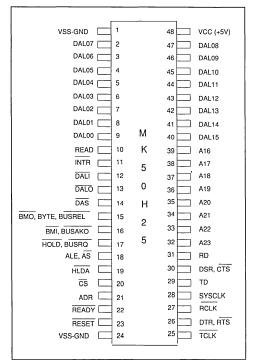

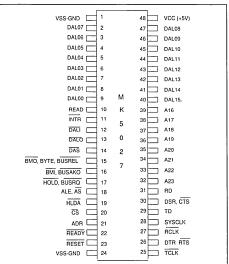

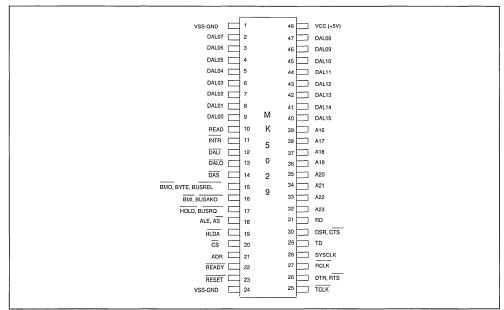

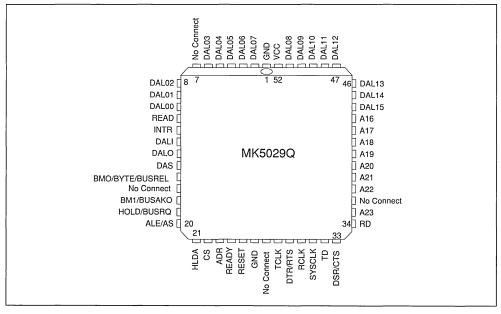

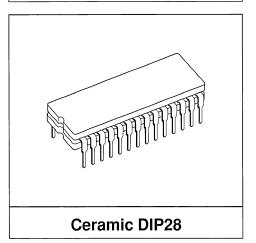

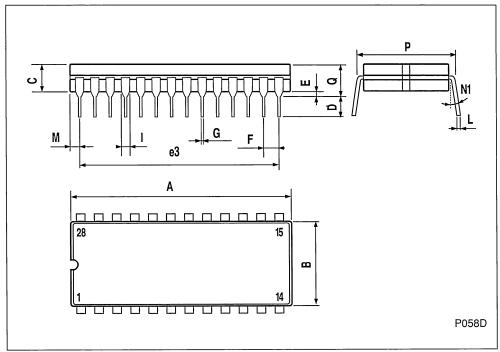

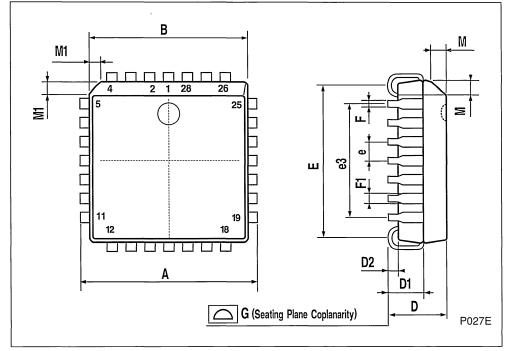

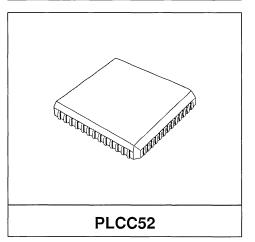

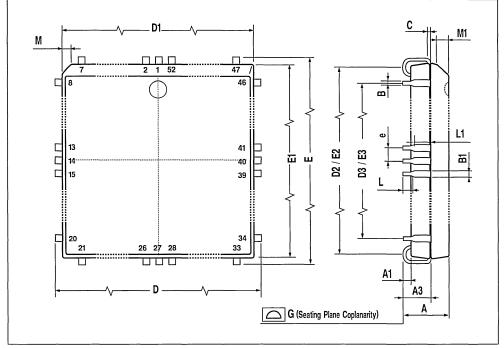

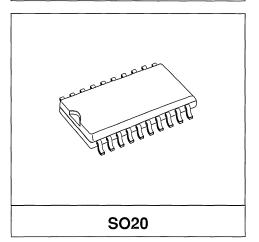

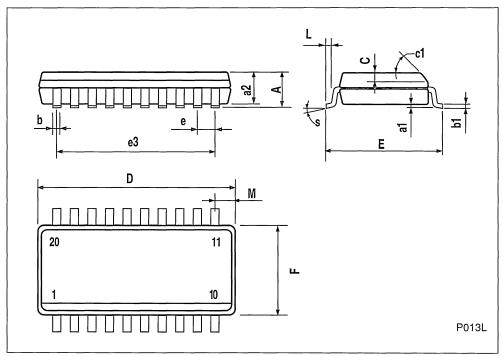

## PIN CONNECTIONS (Top views)

#### September 1991

## ST5410

## INDEX

| ST5410 BLOCK DIAGRAM                                                                                                                                                   | Page | 3                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------|

| GENERAL DESCRIPTION                                                                                                                                                    |      | 4                                |

| PIN FUNCTION                                                                                                                                                           |      | 5                                |

| FUNCTIONAL DESCRIPTION                                                                                                                                                 |      | 9                                |

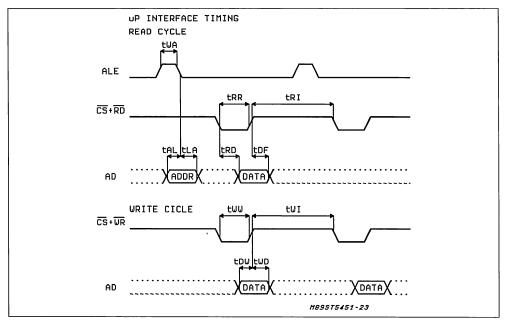

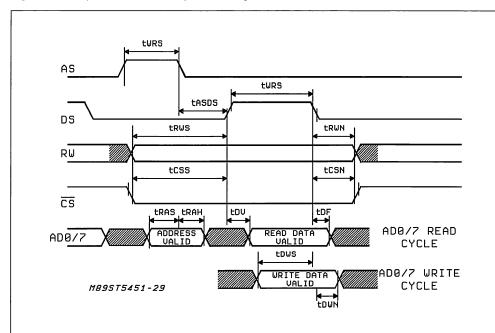

| Digital Interfaces                                                                                                                                                     |      | 9<br>9<br>9                      |

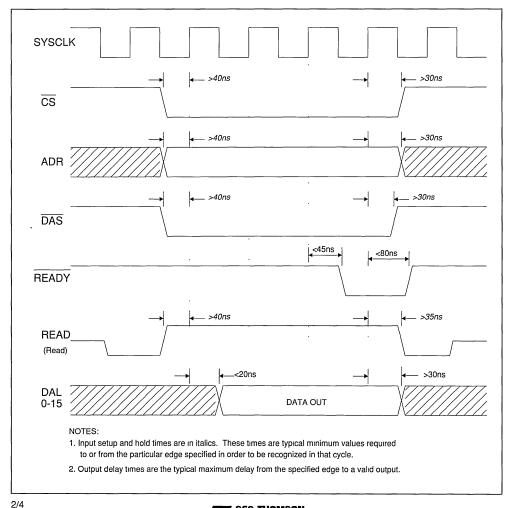

| Write cycle                                                                                                                                                            |      | 9<br>9                           |

| Digital System Interface                                                                                                                                               |      | 9<br>13                          |

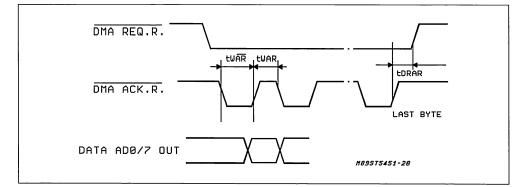

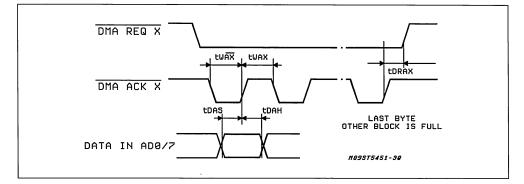

| Frame structure                                                                                                                                                        |      | 13<br>15<br>16                   |

| Write cycle          Read cycle          Exchange protocol                                                                                                             |      | 16<br>16<br>16                   |

| C/I channel                                                                                                                                                            |      | 17                               |

| Turning on and off the devioce                                                                                                                                         |      | 18                               |

| Power on initialization<br>Power up control<br>Power down control<br>Software reset                                                                                    | <br> | 18<br>18<br>18<br>19             |

| Command/Indication (C/I) coding .<br>Internal register description .<br>Line coding and frame format .<br>Line section .<br>Line interface circuit .<br>Board layout . |      | 20<br>25<br>33<br>35<br>36<br>37 |

| APPENDIX A: STATE MATRIX                                                                                                                                               |      | 40                               |

| APPENDIX B: ELECTRICAL PARAMETERS                                                                                                                                      |      | 43                               |

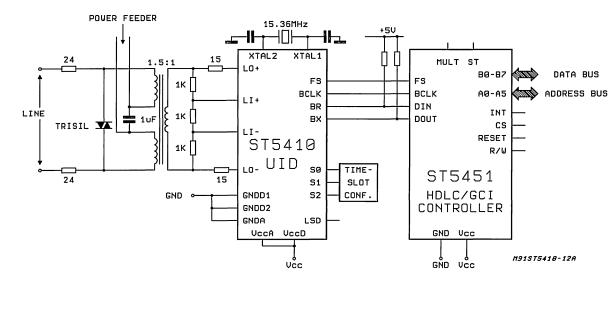

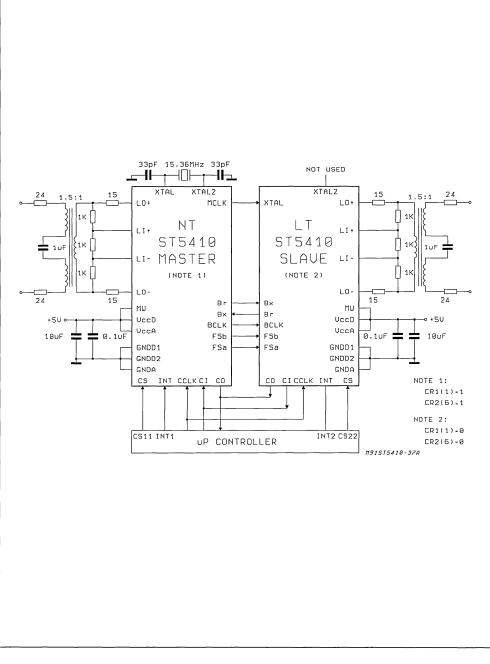

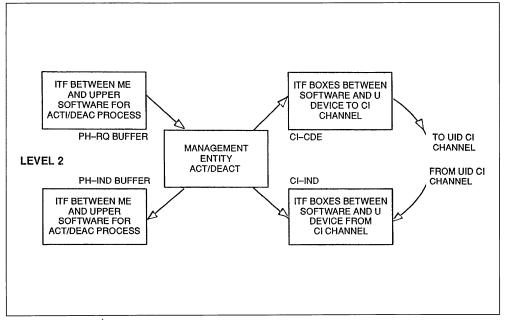

VCCD VCCA Ŷ 28+D XHIT FIFO ۱×۱ 2B+D+H4 ЯŇ BX C/I & N ï 114 SCRAHBLER PULSE LO+ CRC GENE 2810 ENCODER XMIT VAVEFORM AND LATCH SU & ISU FILTER SYNTHETIZER L0-GENE C/I & M M5.M5(EXCEPT CRC) RECEIVE TONE GENE CONTROL EOC or TRANSPARENT M MU VOLTAGE Reg REF. C1/ES1 ž INTERFACE DIGITAL CCLK/92/CL9 ሱ INTERFACE STARTUP CONFIG STATUS CONTROL LOGIC ACTIVATION NCLK C9-/MO CONTROLLER AND TIMING CONTROL EOC or OXTAL 1 TIMING TRANSPARENT M INT-SU & ISU RECOVERY Reg BLOCK ERROR DETECTOR **ΦXTAL2** COUNTERS CO/S1 ž DECISION C/I L H ECHO FEED-BACK TRANSMIT CANCELLER DEMUX M5.M6(EXCEPT CRC) DATA EQUALIZER CONTROL DESCRAMBLE (DSP 1) RECOVERY (DSP 2) CRC CHECK ANALOG LI+ RX RX PRE A/C AGC PREFILTER FILTER CANCELLER LIž 114 28+D+M4 8R REC FIFO TONE DETECTOR 28+D Ē \_ -GNDD2 FSa BCLK FSb/S0 SFS TSR-/HCLK DX/TD/ES2 DR/TA/EC DCLK/TCLK GNDD1 LSD/SFSr GNDA H98575418-11

Figure 1: ST5410 Block Diagram.

ST5410

29

3/53

Z

SGS-THOMSON MICROELECTRONICS

## GENERAL DESCRIPTION

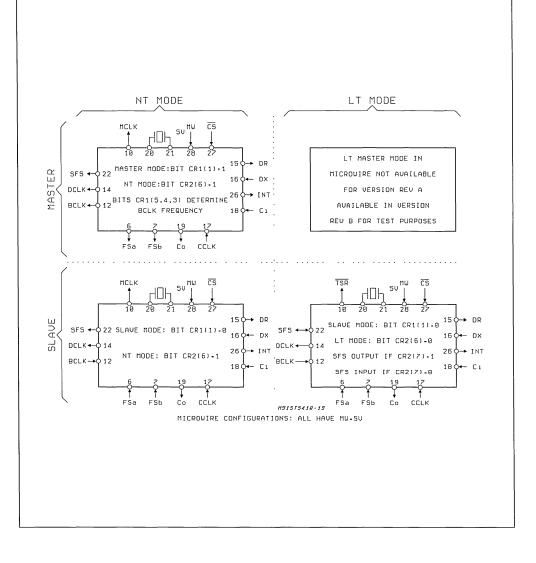

ST5410 is a complete monolithic transceiver for ISDN Basic access data transmission on twisted pair subscriber loops typical of public switched telephone networks. The device is fully compatible with both ANSIT1.601-1988 U.S. and ST/LAA/ELR/822 French specifications.

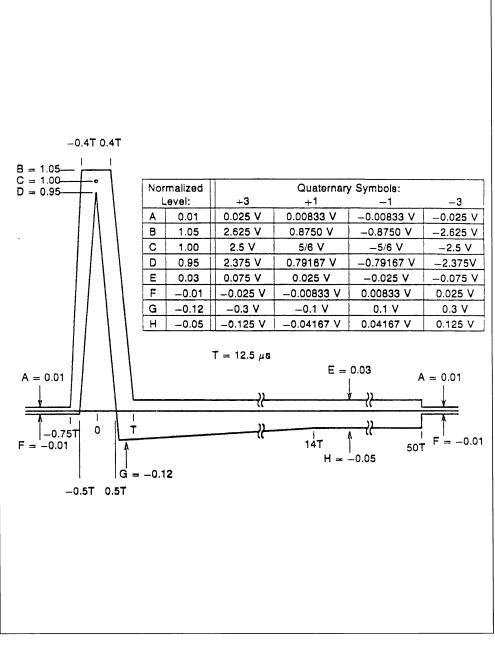

The equivalent of 160 kbit/s full-duplex transmission on a single twisted pair is provided, according to the formats defined in the a.m. spec. Frames include two B channels, each of 64 kbit/s, one D channel of 16 kbit/s plus an additional 4 kbit/s M channel fcr loop maintenance and other user functions. 12 kbit/s bandwidth is reserved for framing. 2B1Q Line coding is used, where pairs of bits are coded into one of 4 quantum levels. This technique results in a low frequency spectrum (160 kbit/s turn into 80 kband), thereby reducing both line attenuation and crosstalk and achieving long range with low Bit Error Rates.

The system is designed to operate on any of the standard types of cable pairs including mixed gauges (26AWG, 24 AWG and 22 AWG) linking the loop by means of one simple transformer. Good noise margins are achieved even when bridged taps are present. On 26AWG cable, the transmission range is in excess of 5.5 km (18 kft) in presence of crosstalk and noise as specified by ANSI standard. ST 5410 is designed to operate with Bit Error Rate less than 10<sup>-6</sup> on 45 dB loss loops with near-end Crosstalk (NEXT) of 52 dB as specified in european ETSI recommendation.

To meet these very demanding specifications, the device includes two Digital Signal Processors, one configured as an adaptive Echo-Canceller to cancel the near end echoes resulting from the transmit/recive hybrid interface, the other as an adaptive line equalizer. A Digital Phase-Locked Loop (DPLL) timing recovery circuit is also included that provides in NT1 a 15.36 MHz synchronized clock to the rest of the system. Scrambling and descrambling are performed as specified in the US and French specifications.

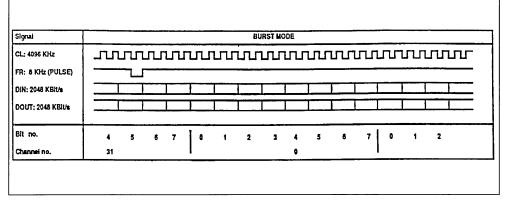

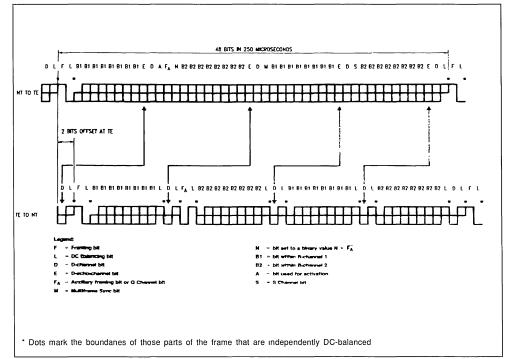

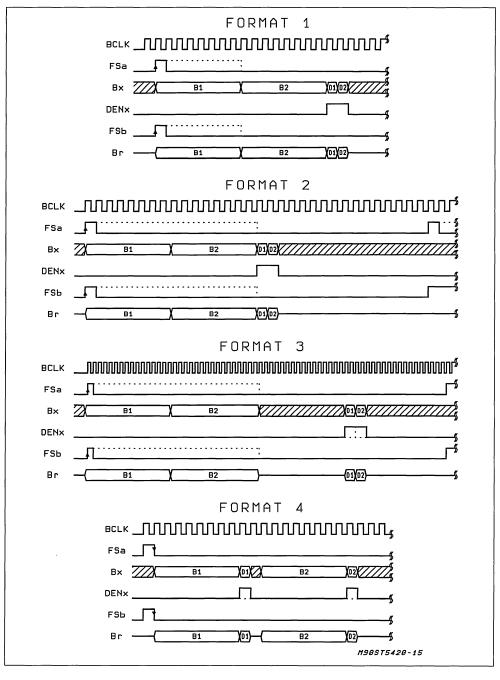

On the system side, ST5410 can be linked to two bus configuration simply by pin MW bias.

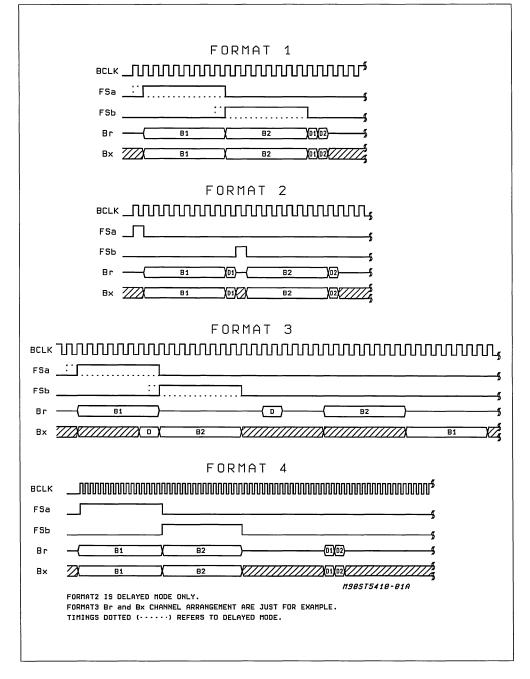

**MICROWIRE**( $\mu$ W)/DSI mode (MW= 5V): 144 kbit/s 2B+D basic access data is transferred on a multiplex Digital System Interface with 4 different interface formats (see fig. 2 and 3) providing maximum flexibility with a limited pin count (BCLK, Bx, Br, FSa, FSb). Three pre-defined 2B+D formats plus an internal time slot assigner allows direct connection of the UID to the most common multiplexed digital

interfaces (TDM/IDL). Bit and Frame Synchronisation signals are inputs or outputs depending on the configuration selected. Data buffers allow any phase shift between the line and the digital interface. That permits building of slave-slave configurations e.g. in NT12 trunk-cards.

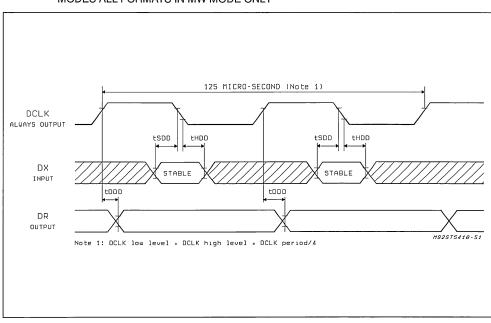

It is possible to separate the D from the B channels and to transfer it on a separate digital interface (Dx, Dr) using the same bit and frame clocks as for the B channels or in a continuous mode using an internally generated 16 kHz bit clock output (DCLK).

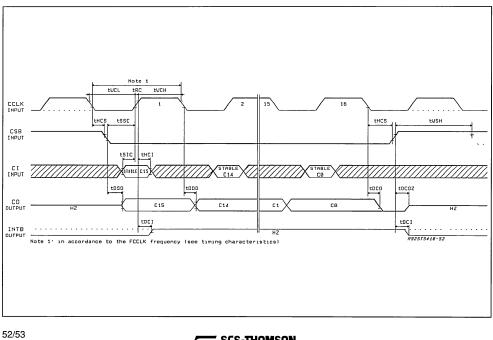

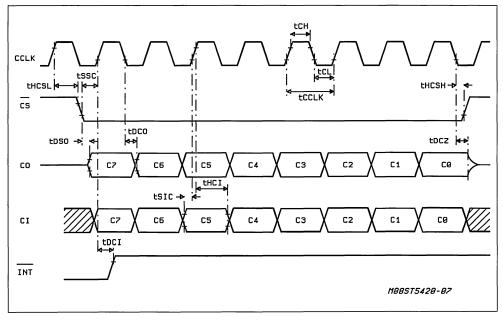

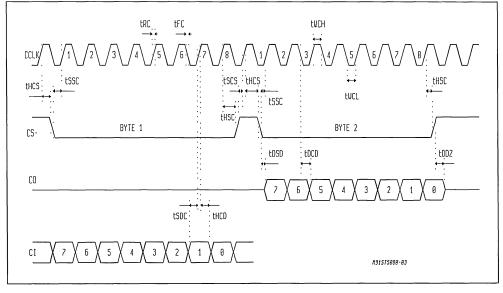

All the Control, Status and Interrupt registers are handled via a control channel on a separate serial interface MICROWIRE compatible (CI, CO, CS, CCLK, INT) supported by a number of microcontroller including the ST6, ST9 and COPS families from SGS-THOMSON

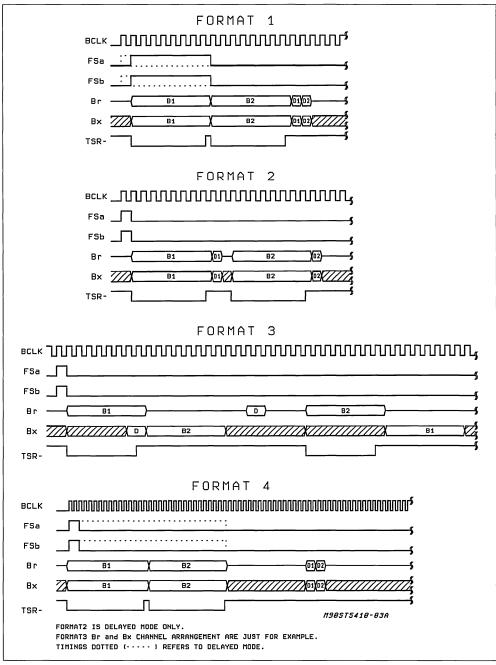

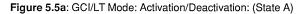

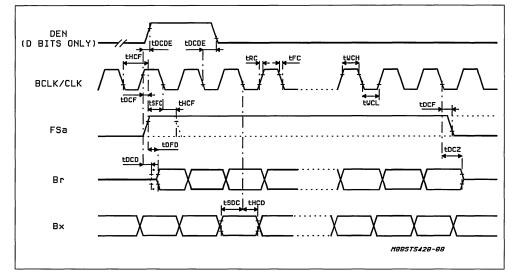

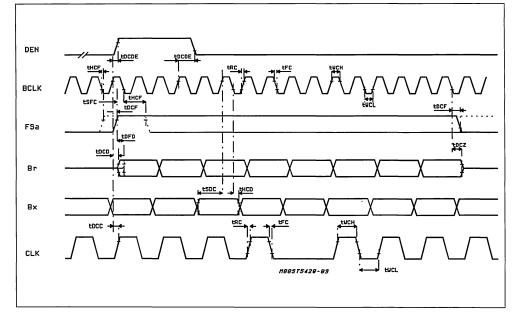

GCI mode (MW= 0V). Control/maintenance channels are multiplexed with 2B+D basic access data in a GCI compatible interface format (see fig. 4a) requiring only 4 pins (BCLK, Bx, Br, FSa). On chip GCI channel assignement allows to multiplex on the same bus up to 8 GCI channels, each supporting data and controls of one device. Bit and Frame Synchronisation signals can be inputs or ouputs depending on the configuration selected. Data buffers, again, allow to have any phase between the line interface and the digital interface.

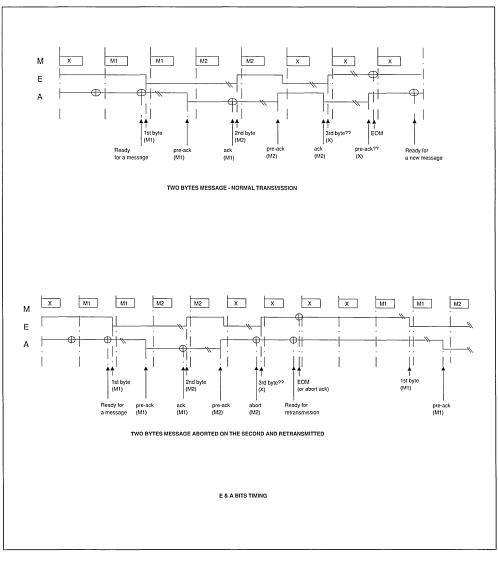

Through the M channel and its protocol allowing to check both direction exchanges, internals register can be configurated, the EOC channel and the Overhead-bits can be monitored. Associated to the M channel, there are A and E channels for enabling the exchanged messages and to insure the flow control. The C/I channel allows the primitive exchanges following the standard protocol.

In both mode ( $\mu$ W and GCI) CRC is calculated and checked in both directions internally.

In LT mode, the superframe can be synchronized by an external signal (SFS) or be self running. In NT mode the SFS is always output synchronized by the transmit superframe.

Line side or Digital Interface side loopbacks can be selected for each B1, B2 or D channel independently without restriction in transparent or in non-transparent mode.

Activation and deactivation procedures, which are automatically processed by UID, require only the exchange of simple commands as Activation Request, Deactivation Request, Activation Indication. Cold and Warm start up procedures are operated automatically without any special instruction.

## **PIN FUNCTIONS**

| Pin                                                                                                                                                                                                                  | Name                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

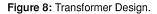

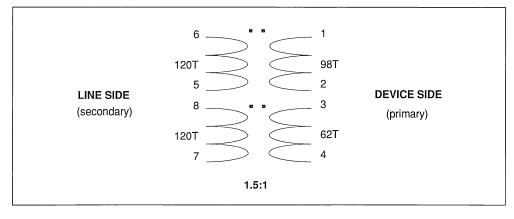

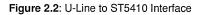

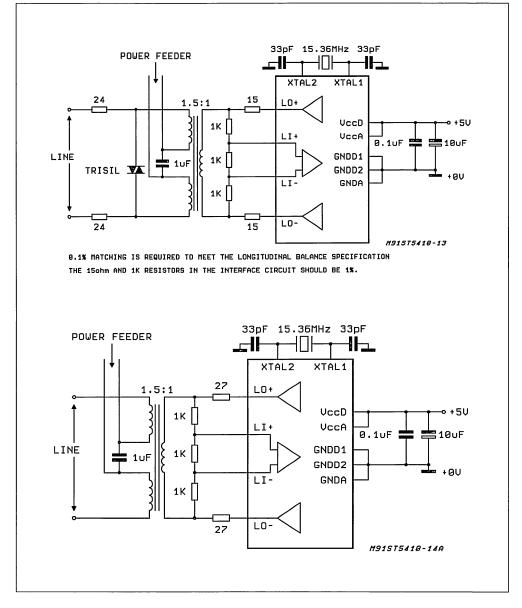

| 1, 4                                                                                                                                                                                                                 | LO+, LO-                 | Transmit 2B1Q signal differential outputs to the line transformer. When used with an appropriate 1:1.5 step-up transformer and the proper line interface circuit the line signal conforms to the output specifications in ANSI standard with a nominal pulse amplitude of 2.5 Volts.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 2, 3                                                                                                                                                                                                                 | LI+, LI-                 | Receive 2B1Q signal differential inputs from the line transformer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 5, 8                                                                                                                                                                                                                 | VCCD, VCCA               | Positive power supply input for the analog and digital sections, which must be +5 Volts +/-5% and must be directly connected together.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

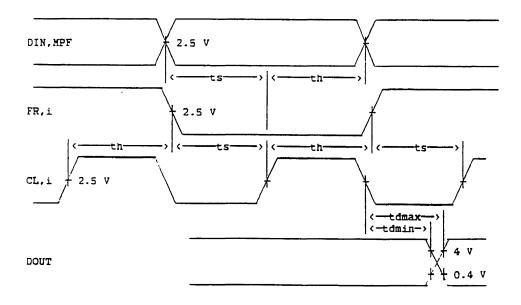

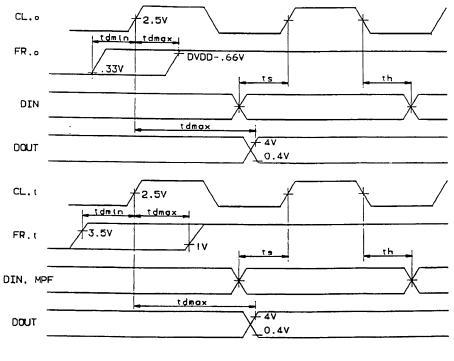

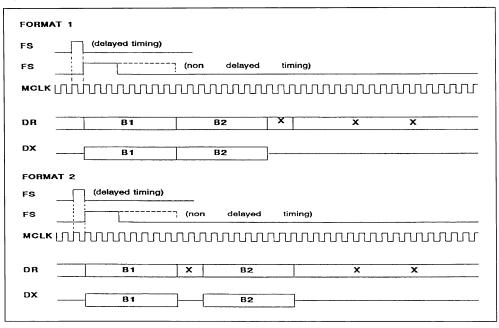

| 6                                                                                                                                                                                                                    | FSa                      | When the Digital Interface clocks are selected as inputs, this signal must be a 8 kHz clock input which indicates the start of the frame on the Digital Interface data input pin Bx. In microwire mode two phases between the rising edge of FSa and the first slot of the frame can be selected by means of bit DDM in CR1: Delayed timing mode or non Delayed timing mode. When GCI Format is selected, FSa defines the frame begining for both Tx and Rx directions and on delayed timing mode is automatically selected. When the Digital Interface clocks are selected as outputs, FSa is a 8KHz output pulse conforming with the selected Interface format.                         |  |  |  |

| 9, 23, 24                                                                                                                                                                                                            | GNDD1,<br>GNDD2,<br>GNDA | Negative power supply pins, which must be connected together close to the device.<br>All digital and analog signals are referred to these pins, which are normally at the system Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| TSR This pin i<br>low when                                                                                                                                                                                           |                          | (LT configuration only)<br>This pin is an open drain output normally in the high impedance state which pulls<br>low when B1 and B2 time-slots are active. It can be used to enable the Tristate<br>control of a backplane line-driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

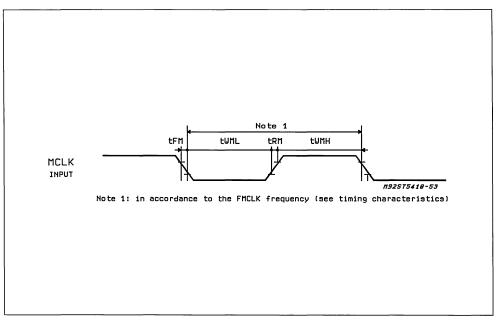

|                                                                                                                                                                                                                      | MCLK                     | (NT mode only)<br>15.36 MHz clock output which is frequency locked to the received line signal (unlike<br>the XTAL pins, it is not freerunning).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 11     Br     Data output: 2B+D basic<br>the TRISTATE output Br a<br>assigned time slots. Elsev<br>channel port is enabled, c<br>of BCLK. In Format 4 anc<br>on the transmit rising edg<br>with the GCI Control char |                          | Data output: 2B+D basic access data received from the line can be shifted out from<br>the TRISTATE output Br at the BCLK frequency on the rising edges during the<br>assigned time slots. Elsewhere, Br is in the high impedance state. When the D<br>channel port is enabled, only BI & B2 data is shifted out from Br on the rising edges<br>of BCLK. In Format 4 and GCI mode, data is shifted out at half the BCLK frequency<br>on the transmit rising edges. When GCI mode is selected, 2B+D data is combined<br>with the GCI Control channels and output Br becomes open drain. There is 1.5<br>period delay between the rising transmit edge and the receive falling edge of BCLK. |  |  |  |

## PIN FUNCTIONS (Continued)

| in  | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12  | BCLK  | Bit Clock: This signal determines the data shift rate on the Digital Interface.When<br>slave mode is selected, BCLK is an input which may be any multiple of 8 kHz<br>from 256 kHz to 6176 kHz. When master mode is selected, BCLK is an output at<br>256 kHz, 512 kHz, 1536 kHz, 2048 kHz or 2560 kHz depending on the selection in<br>Command Register 1. BLCK is synchronous with FSa/b Frame syncsignals and<br>phase locked to the recovered clock received from the line.<br>In formats 1-3, data is shifted in and out at the BCLK frequency. In format 4 and in<br>GCI mode, data is shifted in and out at half the BCLK frequency.                                              |

| 1 3 | Bx    | Data input: 2B+D basic access data to transmit to the line can be shifted in at the BCLK frequency on the falling edges during the assigned time-slots. When D channel port is enabled, only B1 & B2 data is shifted in at the BCLK frequency on the falling edges during the assigned time slots. In format 4 and in GCI mode, data is shifted in at half the BCLK frequency on the receive falling edges. When GCI mode is selected, 2B+D data is combined with the GCI Control channels.                                                                                                                                                                                              |

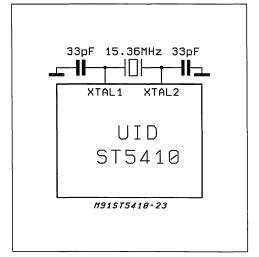

| 20  | XTAL2 | The output of the crystal oscillator, which should be connected to one end of the<br>crystal, if used. Otherwise, this pin must be left no connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 21  | XTAL1 | The master clock input, which requires either a parallel resonance crystal to be tied between this pin and XTAL2, or a logic level clock input from a stable source. This clock does not need to be synchronized to the digital interface clocks (FSa, BCLK).Crystal specifications: 15.36 MHz +/-50ppm parallel resonant; Rs $\leq$ 20 ohms; load with 33pF to GND each side.                                                                                                                                                                                                                                                                                                           |

| 22  | SFS   | Super Frame synchronization I/O: When LT configuration is selected, the rising edge of SFS indicates the beginning of the Transmit Super Frame on the line. Two modes can be selected. In the first mode, SFS is an input that synchronizes the Transmit Frame counter of the UID core. SFS must be synchronous with FSa but with any phase . In the second mode, SFS is a square wave output issued from the free-running Transmit Frame counter. When NT configuration is selected, SFS is always a square wave output which indicates the beginning of the Transmit Superframe. There is no direct phase-relation between the data on the line and the data on the digital interface. |

| 25  | LSD   | Line Signal Detect output (default conf.): This pin is an open drain output which is normally in the high impedance state but pulls low when the device previously in the power down state receives a wake-up by Tone from the line. This signal is intended to be used to wake-up a micro-controller from a low power idle mode. The LSD output goes back in the high impedance state when the device is powered up.                                                                                                                                                                                                                                                                    |

| 20  | SFSr  | Super Frame Synchronization output. When LT configuration is selected, it is possible to configurate pin 25 as SFSr that provides a square wave output indicating the beginning of the received Super Frame from the line. As for SFSx, there is no direct phase-relation between the data on the line and the data on the digital interface.                                                                                                                                                                                                                                                                                                                                            |

| 28  | MW    | MICROWIRE selection: When set high, MICROWIRE control interface is selected.<br>All the internal registers can be accessed through it.<br>When set low, GCI interface is selected. All the internal registers can be accessed<br>through the GCI Monitor and Command/Indicate Control channels.                                                                                                                                                                                                                                                                                                                                                                                          |

## PIN FUNCTIONS (Specific to MICROWIRE MODE ONLY (MW = 1))

| Pin | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     | FSb  | This is a 8 kHz clock input which define the start of the frame on the Digital<br>Interface data ouput pin Br. Two phases between the rising edge of FSb and the<br>first slot of the frame can be selected with the same command as for FSa; Delayed<br>timing mode or non Delayed timing mode.<br>When the Digital Interface clocks are selected as outputs, FSb is a 8 kHz output<br>pulse conforming with the selected format.                                            |  |

| 14  | DCLK | (D channel port enabled, continuous mode selected)<br>D channel Clock output: when the D channel port is enabled in continuous mode,<br>data are shifted in and out at 16 kHz on the falling and rising edges of DCLK<br>respectively. DCLK is synchronous with the BCLK frequency. When DCLK is<br>disabled, it must be tied to GNDD.                                                                                                                                        |  |

| 15  | Dr   | (D channel port enabled)<br>D channel data output: when the D channel port is enabled, D channel data is<br>shifted out from the UID on this pin in two selectable modes: In multiplexed mode,<br>data is shifted out at the BCLK frequency on the rising edges when the assigned<br>time slot is active. In continuous mode, data is shifted out at the DCLK frequency on<br>the rising edge continuously.                                                                   |  |

| 16  | Dx   | (D channel port enabled)<br>D channel data input: When the channel port is enabled, D channel data is shifted<br>in the UID on this pin in two selectable modes: In multiplexed mode, data is shifted<br>in at the BCLK frequency on the falling edges when the selected receive time slots<br>are active. In continuous mode, data is shifted in at the DCLK frequency on the<br>falling edge continuously. When the D channel port is disabled, Dx must be tied to<br>GNDD. |  |

| 17  | CCLK | Clock input for the MICROWIRE control channel: data is shifted in and out on the<br>rising and falling edges of CCLK respectively. CCLK may be asynchronous with the<br>digital interface clock.                                                                                                                                                                                                                                                                              |  |

| 18  | CI   | MICROWIRE control channel serial input: two bytes data is shifted into the UID on this pin on the rising edges of CCLK.                                                                                                                                                                                                                                                                                                                                                       |  |

| 19  | со   | MICROWIRE control channel serial output: two bytes data is shifted out from the UID on the falling edges of CCLK. When not enabled by CS, CO is high-impedance.                                                                                                                                                                                                                                                                                                               |  |

| 26  | ĪNT  | Interrupt output: Latched open-drain output signal which is normally high impedance<br>and goes low to request a read cycle. Pending interrupt data is shifted out from CO<br>at the following read-write cycle. Several pending interrupts may be queued<br>internally and may provide several interrupt requests. INT is freed upon receiving of<br>CS low and can goes low again when CS is freed.                                                                         |  |

| 27  | CS   | Chip Select input: When this pin is pulled low, data can be shifted in and out from the UID through CI & CO pins. When high, this pin inhibits the MICROWIRE interface. For normal read or write operation, CS has to be pulled low for 16 CCLK periods of time.                                                                                                                                                                                                              |  |

## PIN FUNCTIONS (Specific to GCI MODE ONLY (MW = 0) )

| Pin     | Name                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

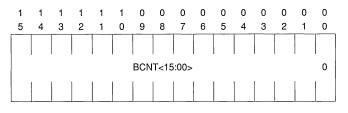

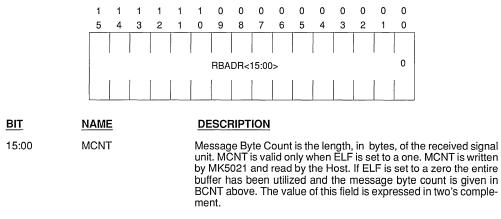

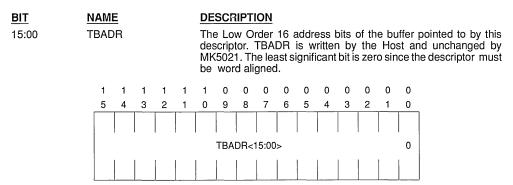

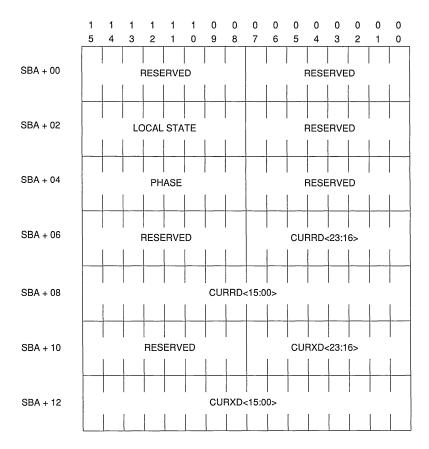

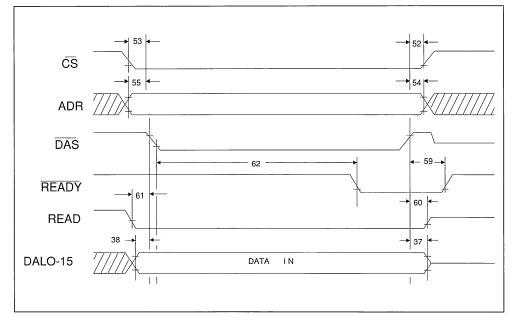

|---------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|