# **ST9040 FAMILY** 8/16 BIT MCU

DATABOOK

1st EDITION

$\bigcirc$

**RYSTON Electronics**

000552

ST9040 FAMILY 8/16 BIT MCU

000

# ST9040 FAMILY 8/16 BIT MCU

DATABOOK

1<sup>st</sup> EDITION

**APRIL 1993**

#### USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED.

SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics. As used herein:

- Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| TABLE C               | <b>OF CONTENTS</b>                                    |           |

|-----------------------|-------------------------------------------------------|-----------|

|                       |                                                       |           |

|                       |                                                       |           |

|                       |                                                       |           |

|                       |                                                       |           |

|                       |                                                       |           |

|                       |                                                       |           |

|                       |                                                       |           |

|                       |                                                       |           |

|                       |                                                       |           |

|                       |                                                       |           |

|                       |                                                       |           |

| GENERAL IN            | NDEX                                                  | Page 5    |

| INTRODUCT             | ION                                                   | 12        |

|                       |                                                       |           |

| ST9 FAMILY            | OVERVIEW                                              | 15        |

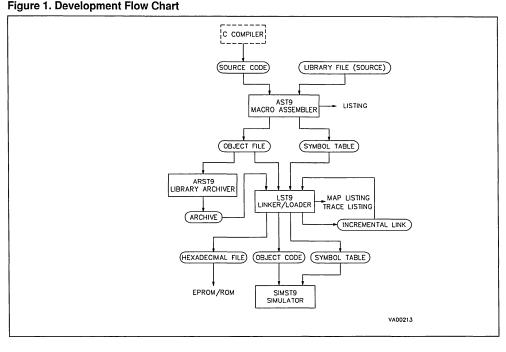

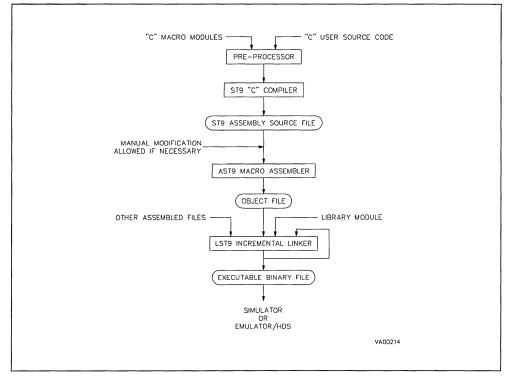

| DEVELOPM              | ENTS TOOLS                                            | 61        |

|                       |                                                       | 00        |

| DATASHEET             | S                                                     | 83        |

| DATASHEET<br>ST9040   | 16K ROM MCU                                           | 83        |

|                       | 16K ROM MCU                                           |           |

| ST9040                | 16K ROM MCU                                           | 85        |

| ST9040<br>ST90E40/T40 | 16K ROM MCU<br>EPROM & OTP version<br>ROMLess version | 85<br>305 |

|     | RAL                      | INDE                                                                                                                                                                                                                                                                                     | ΞΧ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R   | ODUC                     |                                                                                                                                                                                                                                                                                          | ۹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9 F | AMIL                     | Y OV                                                                                                                                                                                                                                                                                     | ERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VE  |                          | MENT                                                                                                                                                                                                                                                                                     | IS TOOLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |                          |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |                          |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ST  | 9040                     |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

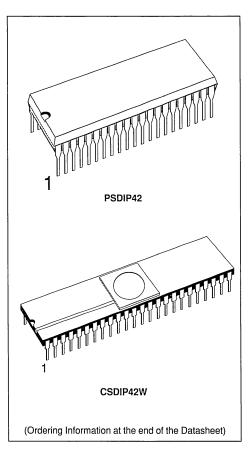

| 1   | DESCI                    |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>88</b><br>88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

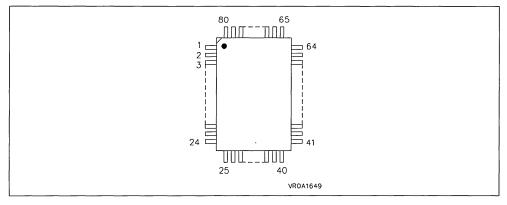

|     | 1.2                      | PIN DE                                                                                                                                                                                                                                                                                   | ESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |                          | 1.2.1                                                                                                                                                                                                                                                                                    | I/O Port Alternate Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2   | <b>CORE</b><br>2.1       |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>93</b><br>93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 2.2                      | ADDR                                                                                                                                                                                                                                                                                     | ESS SPACES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

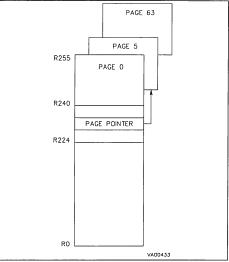

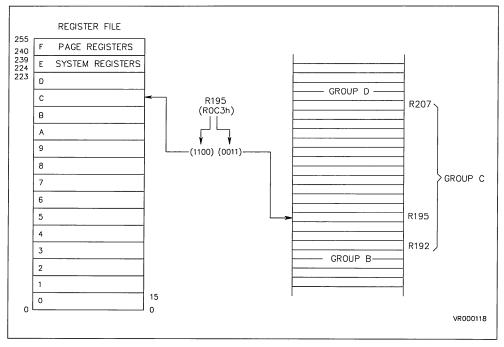

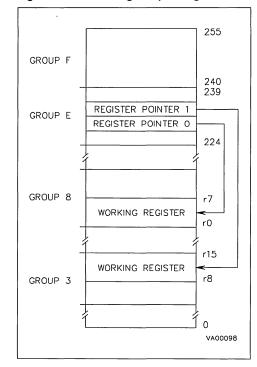

|     |                          | 2.2.1<br>2.2.2<br>2.2.3                                                                                                                                                                                                                                                                  | Register File<br>Addressing Registers<br>Input/Output Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 93<br>95<br>95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.3                      | SYSTE                                                                                                                                                                                                                                                                                    | M REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

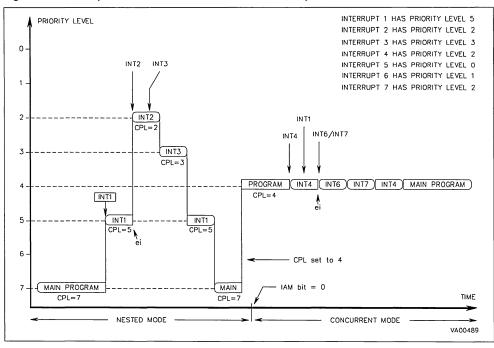

|     |                          | 2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.6                                                                                                                                                                                                                                       | Central Interrupt Control Register<br>Flag Register<br>Register Pointing Techniques<br>Page Configuration<br>Mode Registers<br>Stack Pointers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 101<br>101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3   |                          |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 3.1                      |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

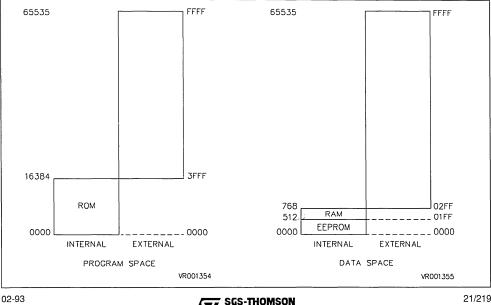

|     | 3.2                      | PROG                                                                                                                                                                                                                                                                                     | RAM SPACE DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 3.3                      | ROML                                                                                                                                                                                                                                                                                     | ESS OPTION SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 3.4                      | DATA S                                                                                                                                                                                                                                                                                   | SPACE DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 3.5                      |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

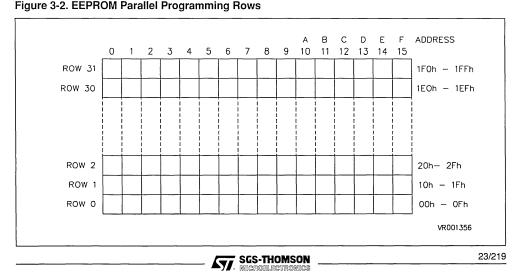

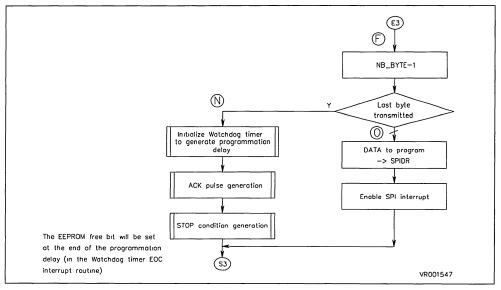

|     |                          | 3.5.1<br>3.5.2<br>3.5.3<br>3.5.4                                                                                                                                                                                                                                                         | Introduction<br>EEPROM Programming Procedure<br>Parallel Programming Procedure<br>EEPROM Programming Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 107<br>108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | F<br>VE<br>TA<br>ST<br>1 | <ul> <li><b>FAMIL</b></li> <li><b>VELOP</b></li> <li><b>TASHEI</b></li> <li><b>ST9040</b></li> <li><b>1</b> DESCF</li> <li>1.1</li> <li>1.2</li> <li><b>2</b> CORE</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>3 MEMC</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> </ul> | FAMILY OV         VELOPMENT         TASHEETS         ST9040         1         DESCRIPTION         1.1         GENE         1.2         PIN DE         1.2         PIN DE         1.2         2.1         CORE         2.1         2.2         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         2.3         3.3         ST         3.4         3.5         EEPRO         3.5 | ST9040         1 DESCRIPTION         1.1 GENERAL DESCRIPTION.         1.2 PIN DESCRIPTION         1.2.1 I/O Port Alternate Functions.         2 CORE ARCHITECTURE         2.1 CORE ARCHITECTURE         2.2 ADDRESS SPACES         2.2.1 Register File         2.2.2 Addressing Registers         2.2.3 Input/Output Ports         2.3 SYSTEM REGISTERS         2.3.1 Central Interrupt Control Register         2.3.2 Flag Register Pointing Techniques         2.3.4 Page Configuration         2.3.5 Mode Registers         2.3.6 Stack Pointers         3 MEMORY         3.1 INTRODUCTION         3.2 PROGRAM SPACE DEFINITION         3.3 ROMLESS OPTION SUMMARY         3.4 DATA SPACE DEFINITION         3.5 EEPROM         3.5.1 Introduction         3.5.2 EEPROM Programming Procedure |

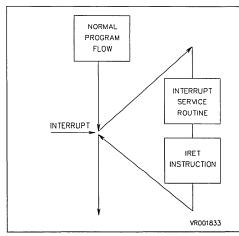

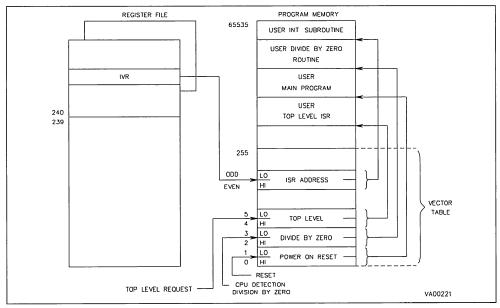

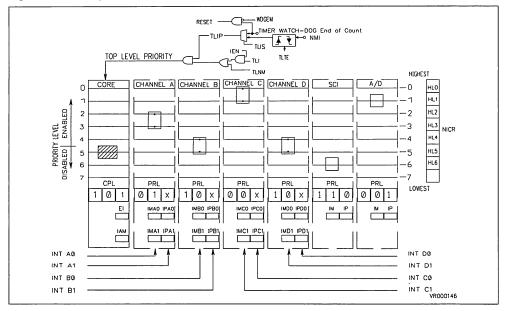

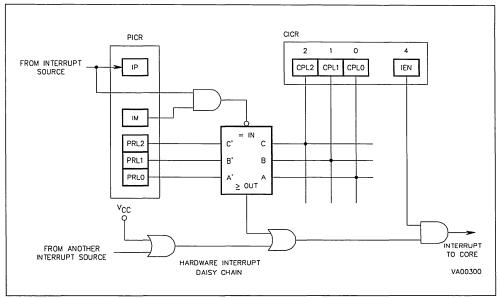

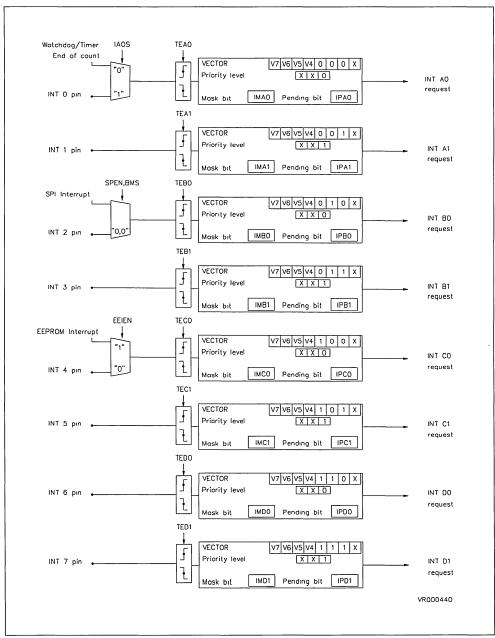

| 4                                         | INTER<br>4.1        | RUPTS<br>INTRODUCTION                                       |     |  |  |

|-------------------------------------------|---------------------|-------------------------------------------------------------|-----|--|--|

|                                           | 4.2                 | INTERRUPT VECTORIZATION                                     | 109 |  |  |

| 4.3 INTERRUPT PRIORITY LEVEL ARCHITECTURE |                     |                                                             |     |  |  |

|                                           | 4.4                 | PRIORITY LEVEL ARBITRATION                                  | 111 |  |  |

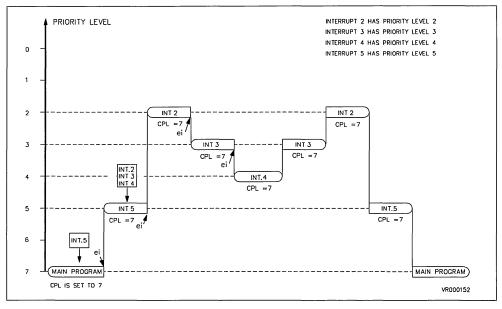

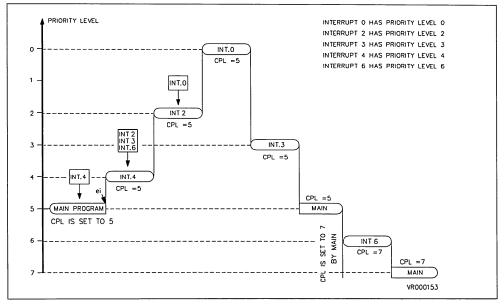

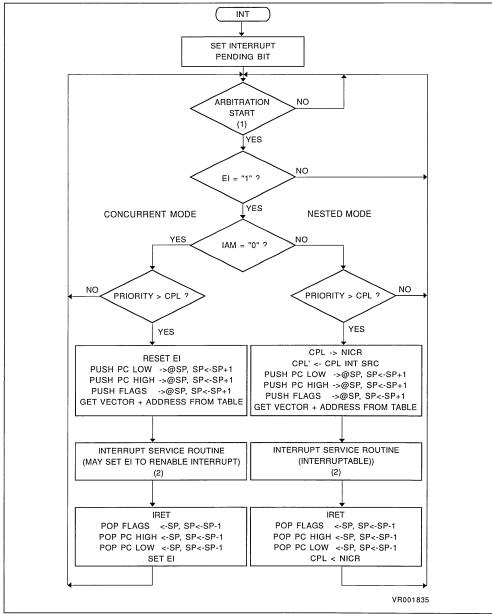

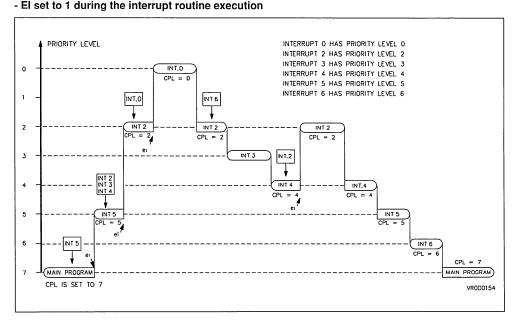

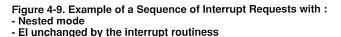

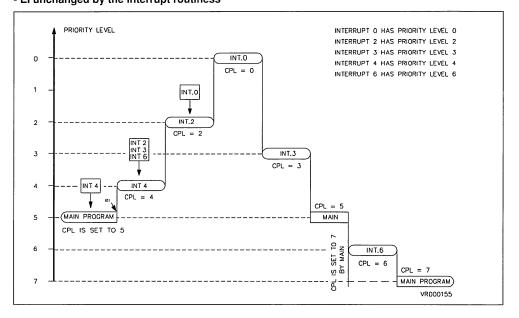

|                                           |                     | 4.4.1       Concurrent Mode         4.4.2       Nested Mode |     |  |  |

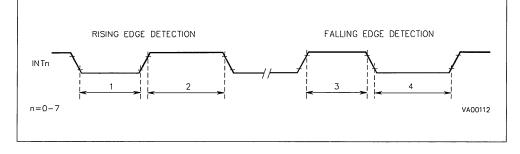

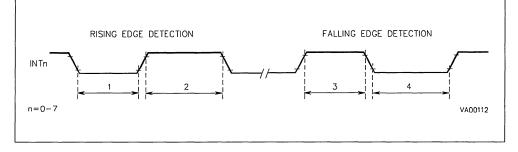

|                                           | 4.5                 | EXTERNAL INTERRUPTS                                         | 118 |  |  |

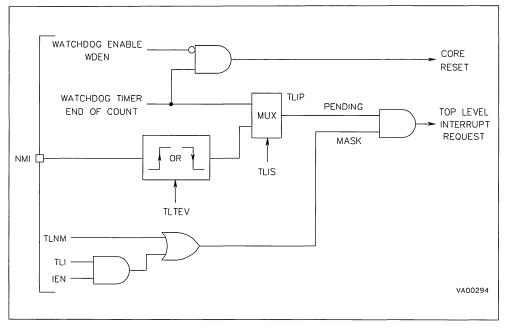

|                                           | 4.6                 | TOP LEVEL INTERRUPT                                         | 120 |  |  |

|                                           | 4.7                 | ON-CHIP PERIPHERAL INTERRUPTS                               | 120 |  |  |

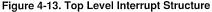

|                                           | 4.8                 | WAIT FOR INTERRUPT INSTRUCTION                              | 122 |  |  |

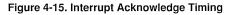

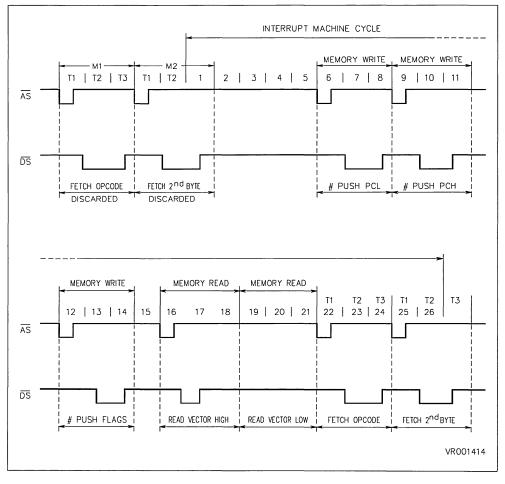

|                                           | 4.9                 | INTERRUPT RESPONSE TIME                                     | 122 |  |  |

|                                           | 4.10                | INTERRUPT REGISTERS                                         | 124 |  |  |

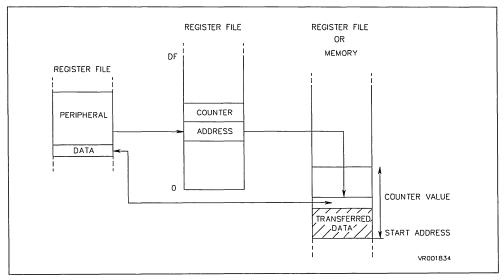

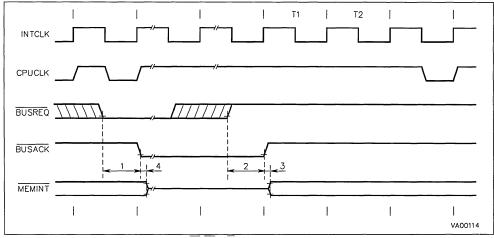

| 5                                         | <b>ON-CH</b><br>5.1 | IP DMA                                                      |     |  |  |

|                                           | 5.2                 | DMA PRIORITY LEVEL ARCHITECTURE                             | 127 |  |  |

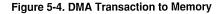

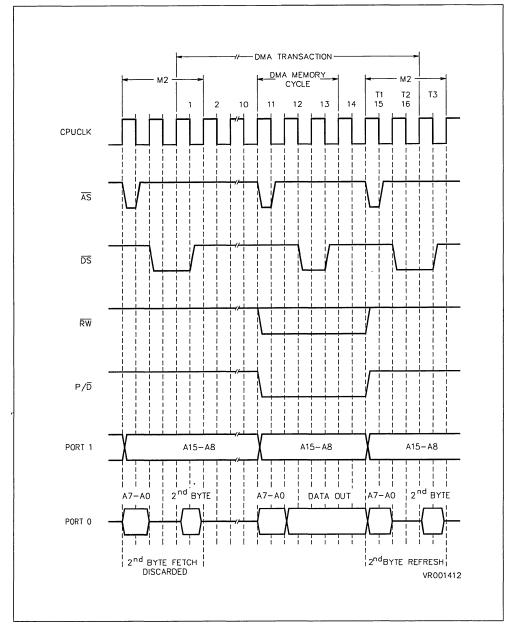

|                                           | 5.3                 | DMA TRANSACTIONS                                            | 129 |  |  |

|                                           | 5.4                 | DMA CYCLE TIME                                              | 129 |  |  |

|                                           | 5.5                 | THE SWAP-MODE                                               | 132 |  |  |

|                                           | 5.6                 | DMA REGISTERS                                               | 132 |  |  |

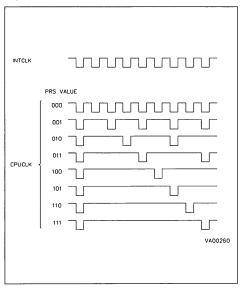

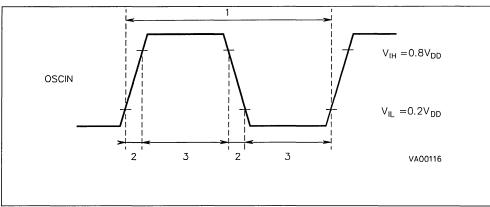

| 6                                         | <b>CLOCH</b><br>6.1 | (INTRODUCTION                                               |     |  |  |

|                                           | 6.2                 | CLOCK MANAGEMENT                                            | 133 |  |  |

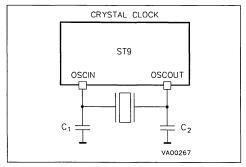

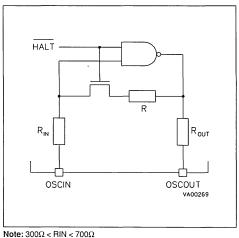

|                                           | 6.3                 | CLOCK CONTROL REGISTER                                      | 134 |  |  |

|                                           | 6.4                 | OSCILLATOR CHARACTERISTICS                                  | 135 |  |  |

| 7                                         | <b>RESET</b><br>7.1 | INTRODUCTION                                                |     |  |  |

|                                           | 7.2                 | RESET GENERATION                                            | 137 |  |  |

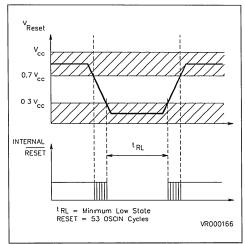

|                                           | 7.3                 | RESET PIN TIMING                                            | 137 |  |  |

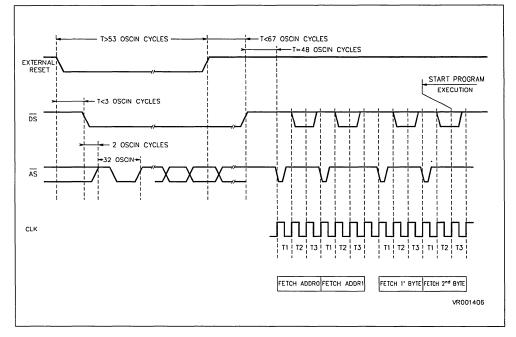

|                                           | 7.4                 | PROCESSOR SYNCHRONIZATION UNDER RESET                       | 137 |  |  |

|                                           | 7.5                 | EPROM PROGRAMMING PIN                                       | 138 |  |  |

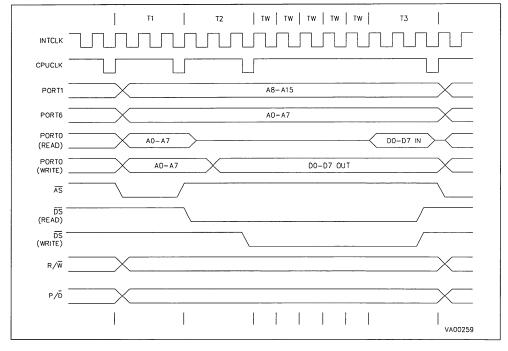

| 8  | <b>EXTER</b><br>8.1   | NAL MEMORY INTERFACE                                                                                                                           |     |  |  |  |  |

|----|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

|    | 8.2                   | CONTROL SIGNALS                                                                                                                                | 141 |  |  |  |  |

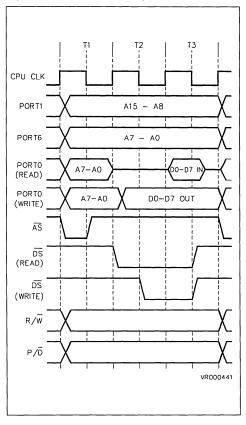

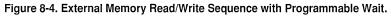

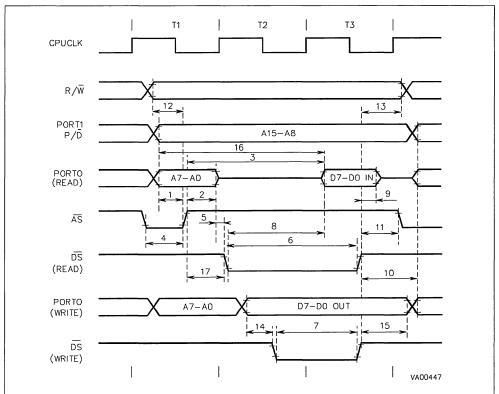

|    | 8.3                   | MEMORY ACCESS CYCLE                                                                                                                            | 143 |  |  |  |  |

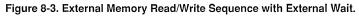

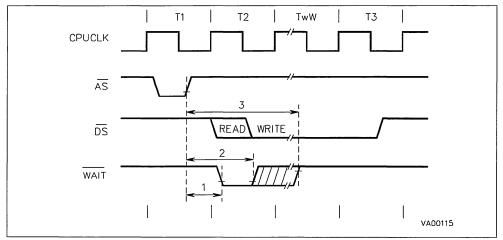

|    | 8.4                   | STRETCHED ACCESS CYCLE                                                                                                                         | 143 |  |  |  |  |

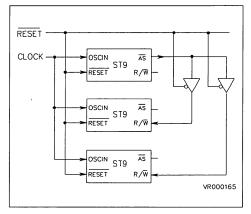

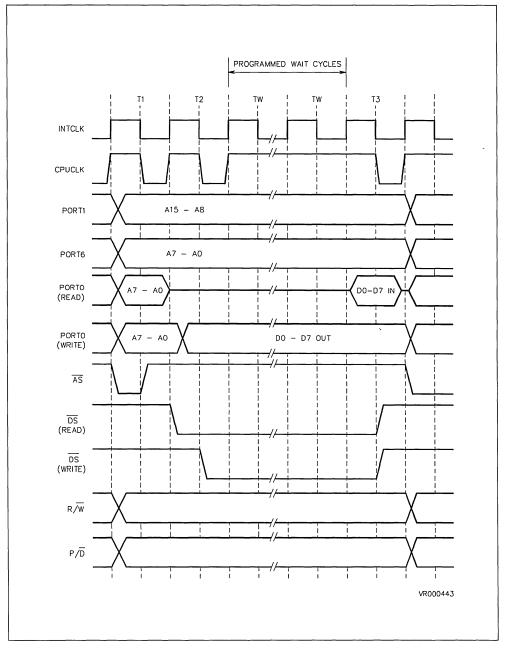

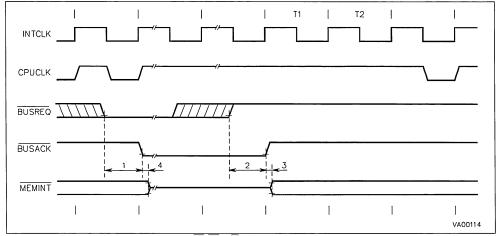

|    | 8.5                   | SHARED BUS                                                                                                                                     | 146 |  |  |  |  |

|    | 8.6                   | PORTS P0, P1, P6 INITIALIZATION AFTER RESET                                                                                                    | 147 |  |  |  |  |

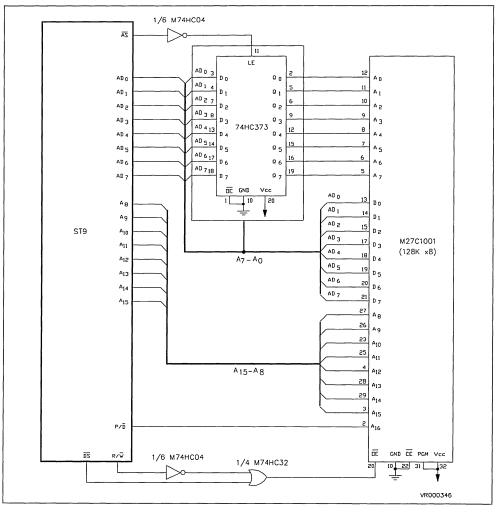

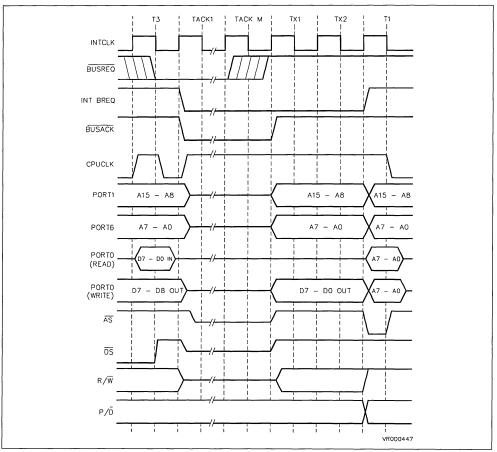

|    | 8.7                   | ROMLESS FUNCTION                                                                                                                               | 147 |  |  |  |  |

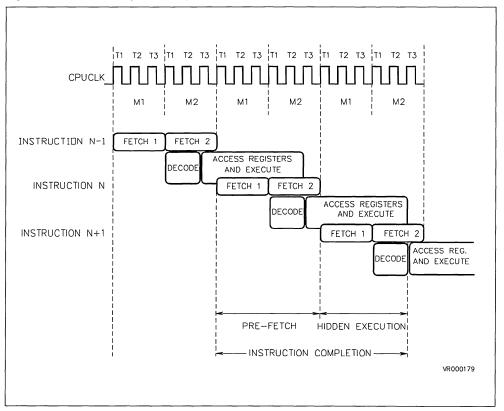

|    | 8.8                   | PIPELINE                                                                                                                                       | 148 |  |  |  |  |

|    | 8.9                   | "SPURIOUS" MEMORY ACCESSES                                                                                                                     | 149 |  |  |  |  |

|    | 8.10                  | REGISTERS                                                                                                                                      | 150 |  |  |  |  |

| 9  | <b>I/O POI</b><br>9.1 | RTS                                                                                                                                            |     |  |  |  |  |

|    | 9.2                   | CONTROL REGISTERS                                                                                                                              | 151 |  |  |  |  |

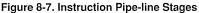

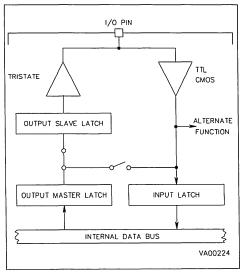

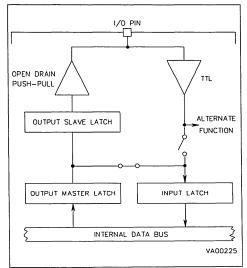

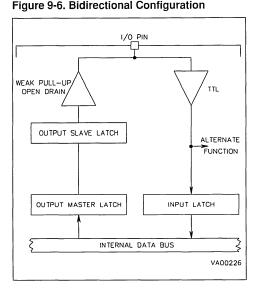

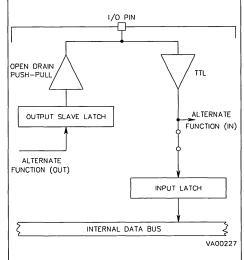

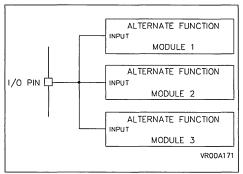

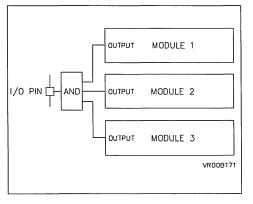

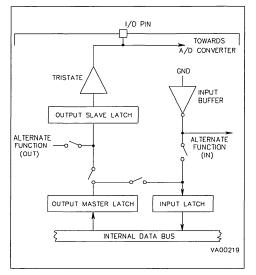

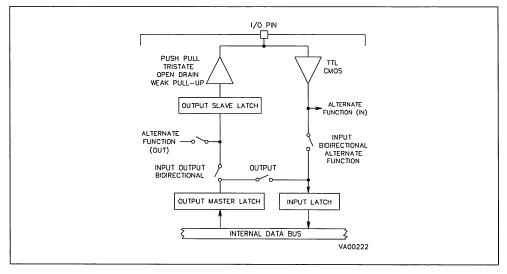

|    | 9.3                   | PORT BIT STRUCTURE AND PROGRAMMING                                                                                                             | 152 |  |  |  |  |

|    | 9.4                   | ALTERNATE FUNCTION ARCHITECTURE                                                                                                                | 155 |  |  |  |  |

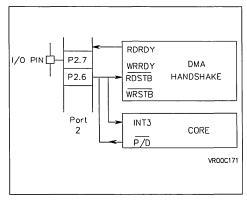

|    | 9.5                   | SPECIAL PORTS                                                                                                                                  | 156 |  |  |  |  |

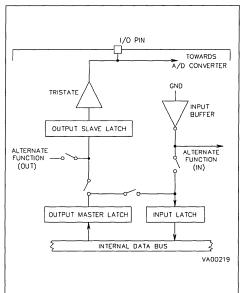

|    |                       | 9.5.1 Bit Structure For A/D Converter Inputs                                                                                                   | 156 |  |  |  |  |

|    | 9.6                   | I/O STATUS AFTER WFI, HALT AND RESET                                                                                                           | 156 |  |  |  |  |

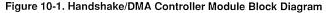

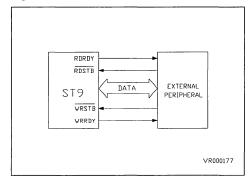

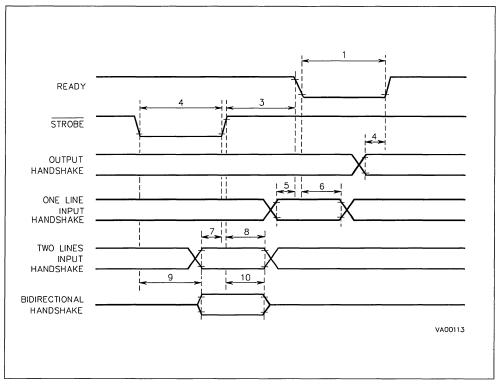

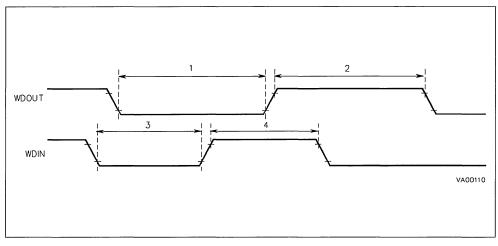

| 10 | HANDS<br>10.1         | SHAKE/DMA CONTROLLER                                                                                                                           |     |  |  |  |  |

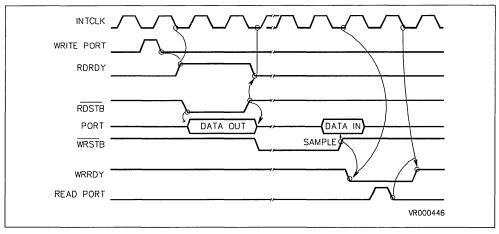

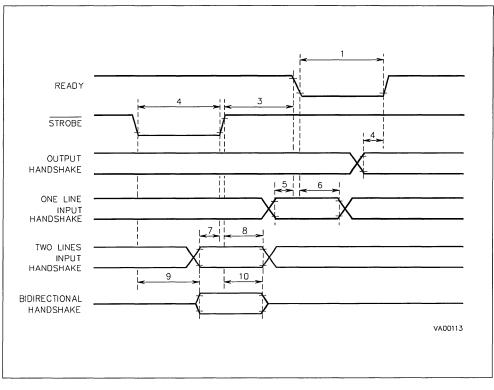

|    | 10.2                  | PROGRAMMABLE HANDSHAKE MODES                                                                                                                   | 158 |  |  |  |  |

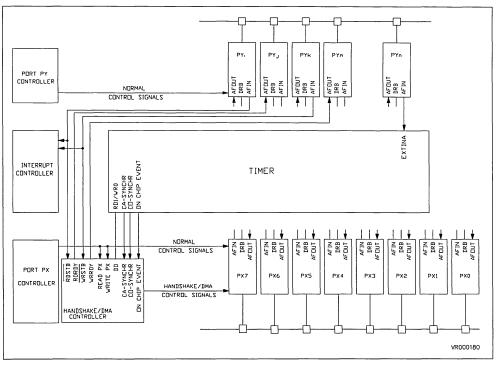

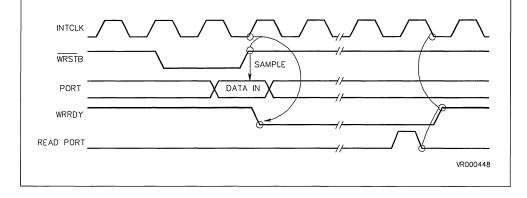

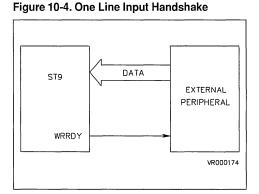

|    |                       | 10.2.1 Input Handshake                                                                                                                         |     |  |  |  |  |

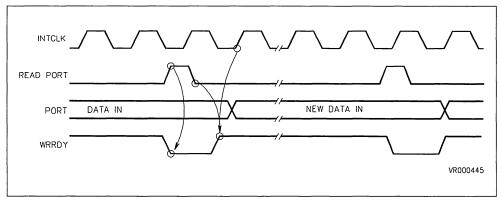

|    |                       | 10.2.2       Output Handshake         10.2.3       Bidirectional Handshake                                                                     |     |  |  |  |  |

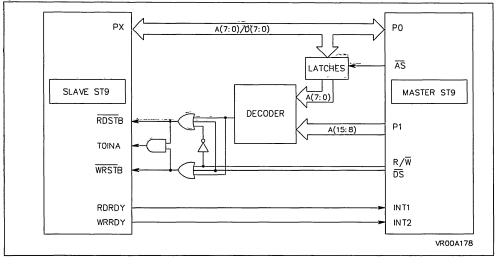

|    |                       | 10.2.4 Mapping an ST9 onto the memory bus of another ST9                                                                                       |     |  |  |  |  |

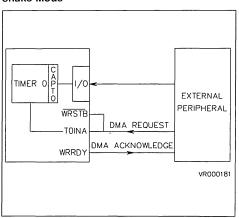

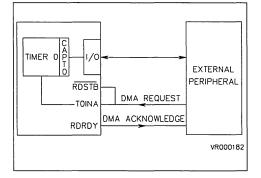

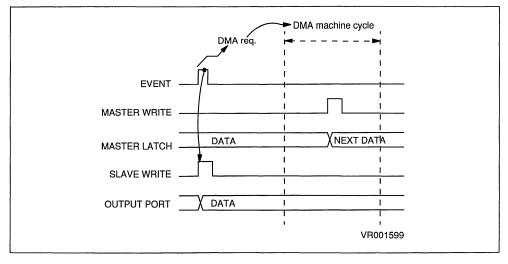

|    | 10.3                  | PROGRAMMABLE DMA MODES                                                                                                                         | 164 |  |  |  |  |

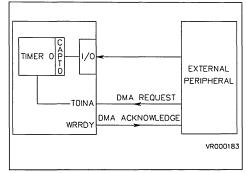

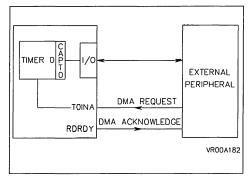

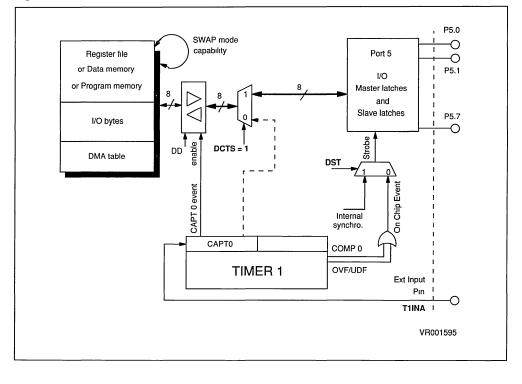

|    |                       | 10.3.1 DMA Transfers Driven By Timer CAPT0 Channel With Handshake                                                                              |     |  |  |  |  |

|    |                       | <ul><li>10.3.2 DMA Input transfers with two line input handshake</li><li>10.3.3 DMA output transfers with two lines output handshake</li></ul> |     |  |  |  |  |

|    |                       | 10.3.4 DMA input transfers with one line input handshake                                                                                       |     |  |  |  |  |

|    |                       | 10.3.5 DMA output transfers with one line output handshake                                                                                     | 166 |  |  |  |  |

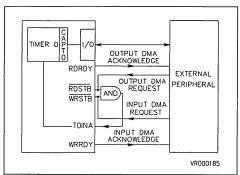

|    |                       | 10.3.6 DMA input/output transfers with bidirectional handshake                                                                                 |     |  |  |  |  |

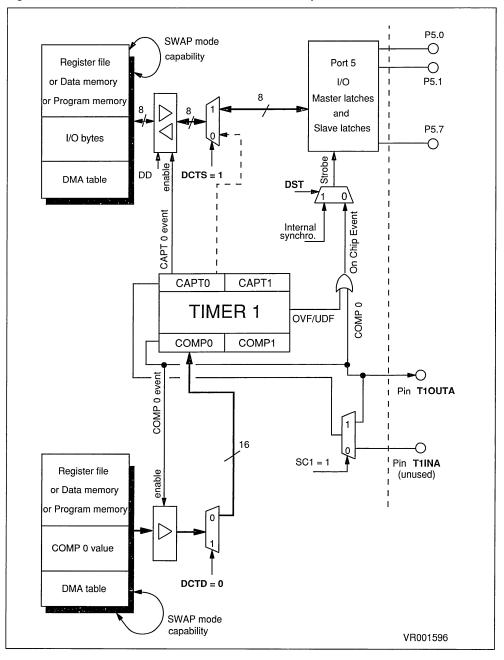

|    | 10.4                  | 10.3.7 DMA Transfers Driven By Timer Comp0 Channel With Handshake<br>HANDSHAKE/DMA CONTROL REGISTERS                                           |     |  |  |  |  |

|    | 10.4                  | J.4 HANDSHARE/DIVIA CONTROL REGISTERS                                                                                                          |     |  |  |  |  |

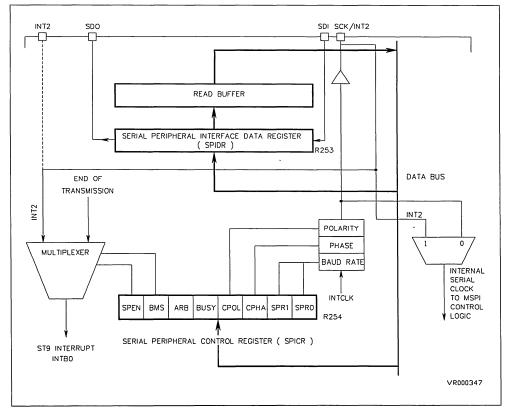

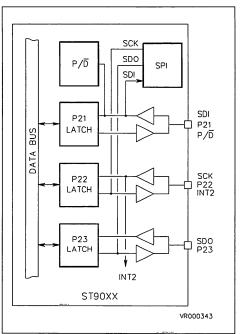

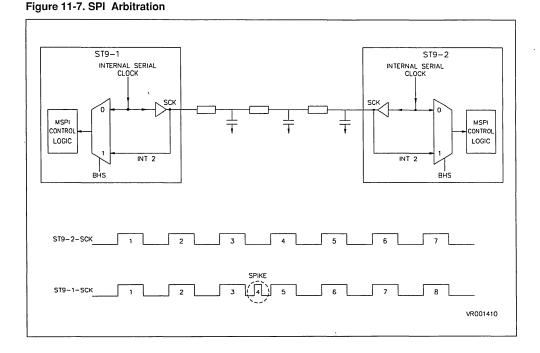

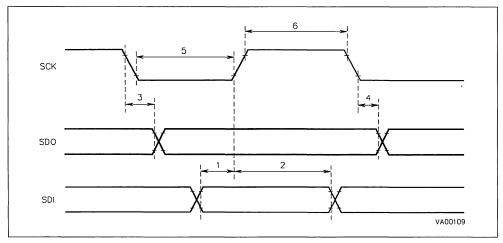

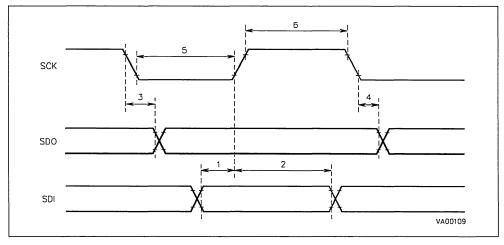

| 11 | <b>SERIA</b><br>11.1  | L PERIPHERAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

|----|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

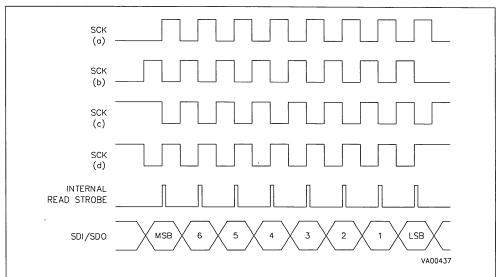

|    | 11.2                  | FUNCTIONAL DESCRIPTION         11.2.1       Input Signal Description         11.2.2       Output Signal Description                                                                                                                                                                                                                                                                                              | <br>172                                                            |

|    | 11.3                  | INTERRUPT STRUCTURE                                                                                                                                                                                                                                                                                                                                                                                              | <br>173                                                            |

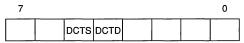

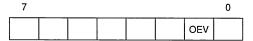

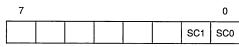

|    | 11.4                  | SPI REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                    | <br>174                                                            |

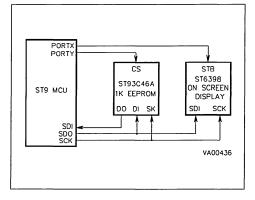

|    | 11.5                  | WORKING with DIFFERENT PROTOCOLS                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |

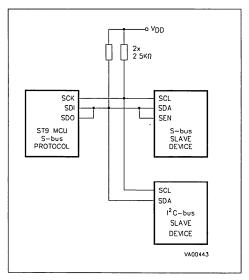

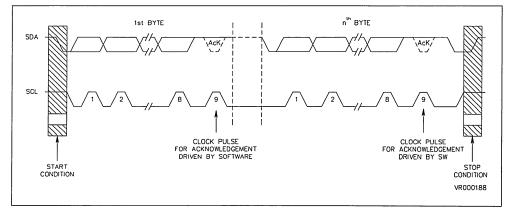

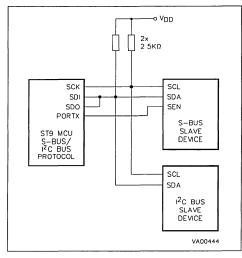

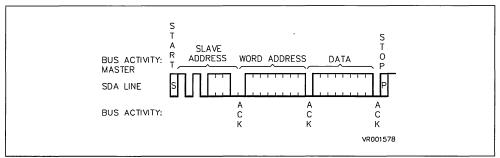

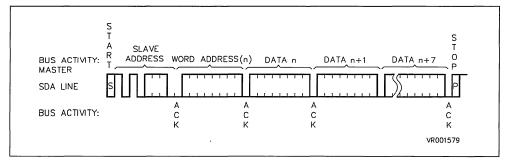

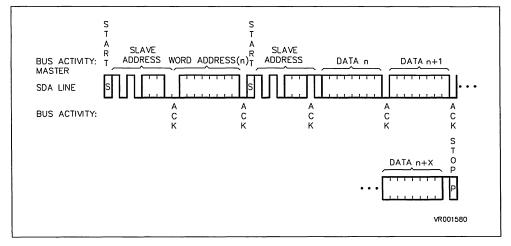

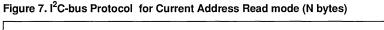

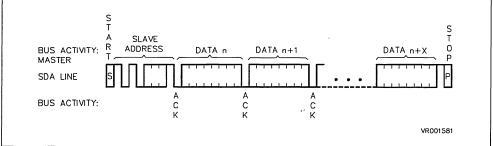

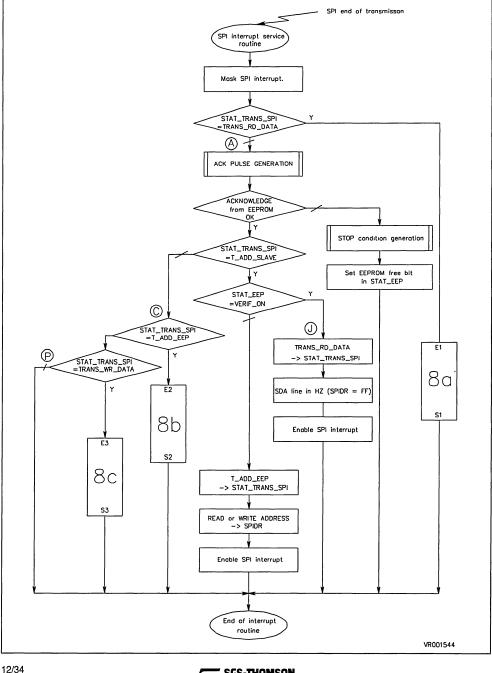

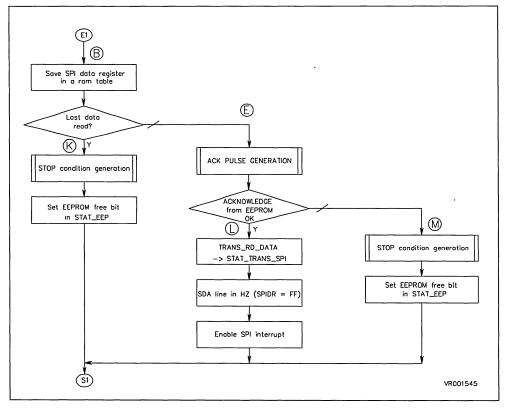

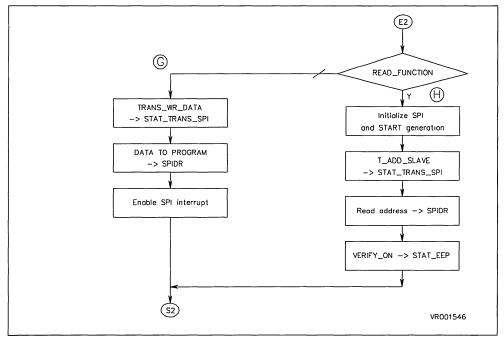

|    |                       | 11.5.1       I <sup>2</sup> C-bus Interface         11.5.2       S-Bus Interface         11.5.3       IM-Bus Interface                                                                                                                                                                                                                                                                                           | <br>178                                                            |

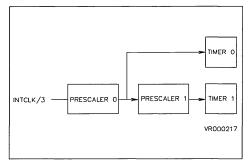

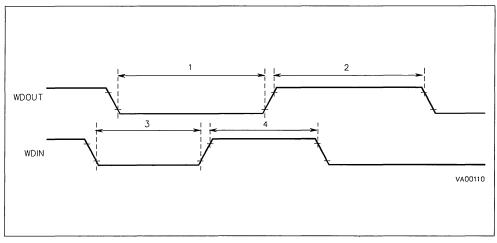

| 12 | <b>TIMER</b><br>12.1  | WATCHDOG<br>INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |

|    | 12.2                  | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                           | <br>182                                                            |

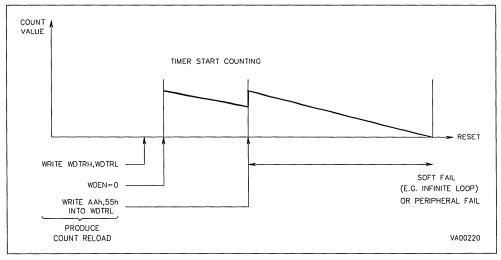

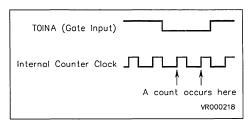

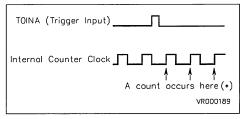

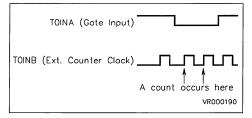

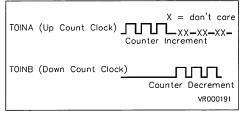

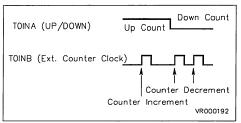

|    |                       | 12.2.1       Timer/Counter Input Modes         12.2.2       Timer/Watchdog Output Modes         12.2.3       Timer/Counter Control         12.2.4       Timer/Watchdog Mode                                                                                                                                                                                                                                      | <br>182<br>182                                                     |

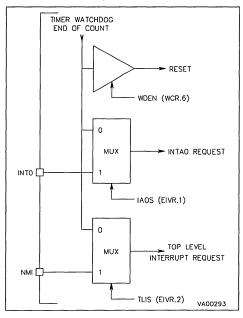

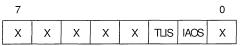

|    | 12.3                  | TIMER/WATCHDOG INTERRUPT                                                                                                                                                                                                                                                                                                                                                                                         | <br>184                                                            |

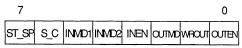

|    | 12.4                  | TIMER/WATCHDOG REGISTERS                                                                                                                                                                                                                                                                                                                                                                                         | <br>186                                                            |

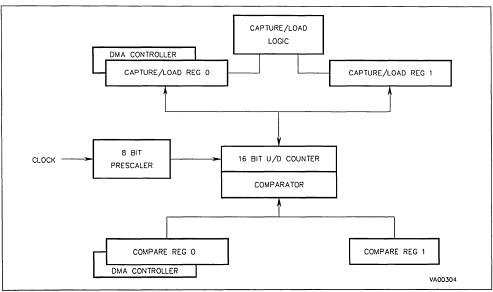

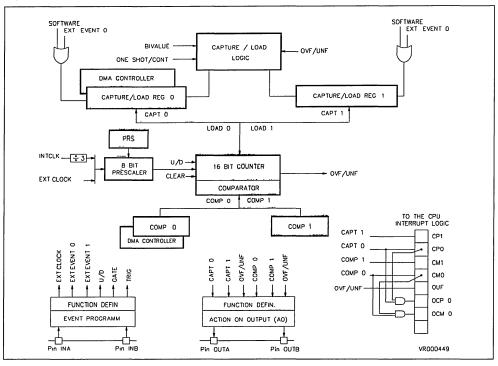

| 13 | <b>MULTII</b><br>13.1 | FUNCTION TIMER                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

|    | 13.2                  | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                           | <br>189                                                            |

|    |                       | 13.2.1       One Shot Mode         13.2.2       Continuous Mode         13.2.3       Trigger And Retrigger Modes         13.2.4       Gate Mode         13.2.5       Capture Mode         13.2.6       Up/Down Mode         13.2.7       Free Running Mode         13.2.8       Monitor Mode         13.2.9       Autoclear Mode         13.2.10       Bivalue Mode         13.2.12       Autodiscriminator Mode | 189<br>189<br>189<br>189<br>189<br>189<br>190<br>190<br>190<br>190 |

|    | 13.3                  | INPUT PIN ASSIGNMENT                                                                                                                                                                                                                                                                                                                                                                                             | <br>191                                                            |

|    |                       | 13.3.1       TxINA = I/O - TxINB = I/O         13.3.2       TxINA = I/O - TxINB = Trigger         13.3.3       TxINA = Gate - TxINB = I/O         13.3.4       TxINA = Gate - TxINB = Trigger         13.3.5       TxINA = I/O - TxINB = Ext. Clock                                                                                                                                                              | <br>191<br>191<br>192                                              |

|      | 13.3.6  | TxINA = Trigger - TxINB = I/O             |     |

|------|---------|-------------------------------------------|-----|

|      | 13.3.7  | TxINA = Gate - TxINB = Ext. Clock         |     |

|      | 13.3.8  | TxINA = Trigger - TxINB = Trigger         |     |

|      | 13.3.9  | TxINA = Clock Up - TxINB = Clock Down     |     |

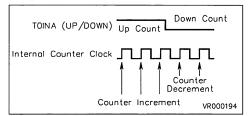

|      |         | TxINA = Up/Down - TxINB = Ext Clock       |     |

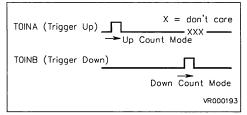

|      |         | TxINA = Trigger Up - TxINB = Trigger Down |     |

|      |         | TxINA = Up/Down - TxINB = I/O             |     |

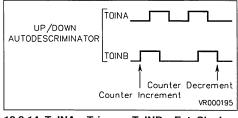

|      |         | Autodiscrimination Mode                   | 193 |

|      |         |                                           | 193 |

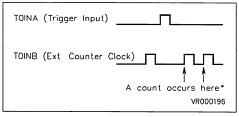

|      |         | TxINA = Ext. Clock - TxINB = Trigger      |     |

|      |         | TxINA = Trigger - TxINB = Gate            | 193 |

| 13.4 |         | T PIN ASSIGNMENT                          | 194 |

| 13.5 | INTERR  | UPT AND DMA                               | 196 |

|      | 13.5.1  | Timer Interrupt                           | 196 |

|      | 13.5.2  | Timer DMA                                 | 196 |

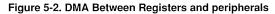

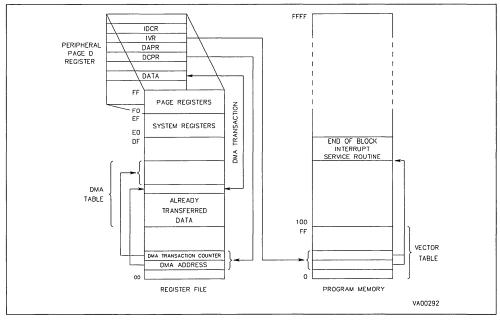

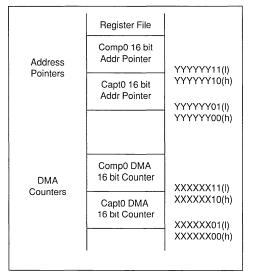

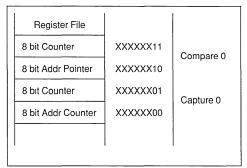

|      | 13.5.3  | DMA Pointers                              | 196 |

|      | 13.5.4  | Priority During The DMA Transactions      | 197 |

|      | 13.5.5  | The DMA Swap Mode                         | 197 |

|      | 13.5.6  | The DMA End Of Block Interrupt Routine    | 198 |

|      | 13.5.7  | DMA Software Protection                   | 198 |

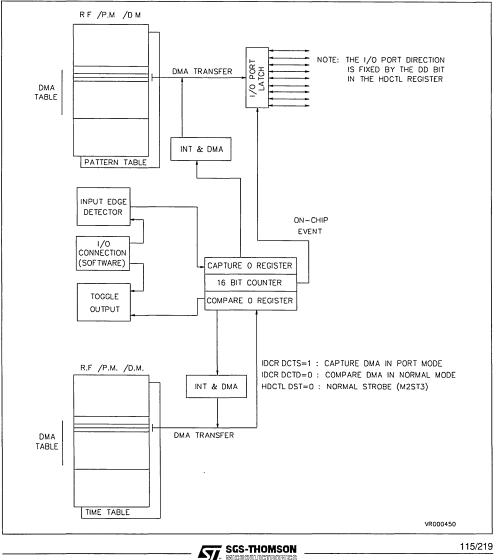

| 13.6 | TIMER I | DMA EXTERNAL MODES ON I/O PORTS           | 198 |

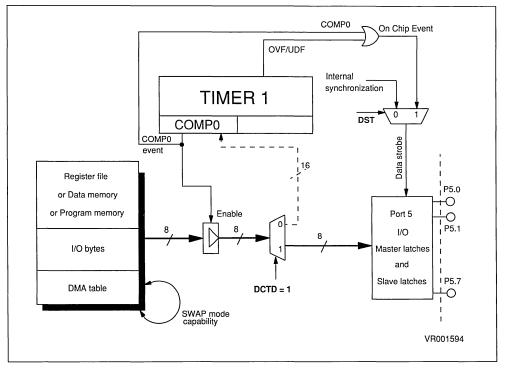

|      | 13.6.1  | CM0 Channel External Mode                 | 198 |

|      | 13.6.2  | CP0 Channel In External Mode              | 198 |

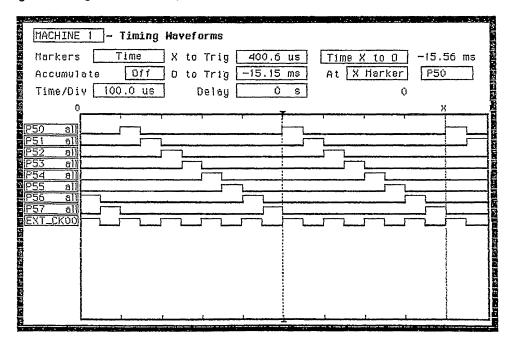

|      | 13.6.3  | DMA Channel Synchronization               | 199 |

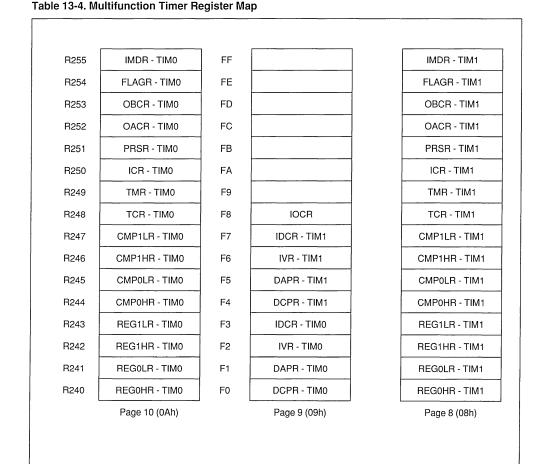

| 13.7 | REGIST  | ER DESCRIPTION                            | 200 |

|      | 13.7.1  | Register 0 (REG0R) Registers              | 201 |

|      | 13.7.2  | Register 1 (REG1R) Registers              | 201 |

|      | 13.7.3  | Compare 0 (CMP0R) Registers               | 201 |

|      | 13.7.4  | Compare 1 (CMP1R) Registers               | 201 |

|      | 13.7.5  | Timer Control Register (TCR)              | 202 |

|      | 13.7.6  | Timer Mode Register (TMR)                 | 202 |

|      | 13.7.7  | External Input Control Register(ICR)      | 203 |

|      | 13.7.8  | Prescaler Register (PRSR)                 | 204 |

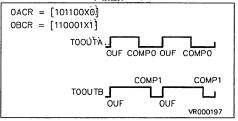

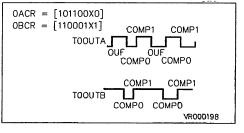

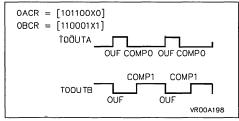

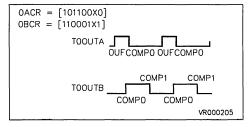

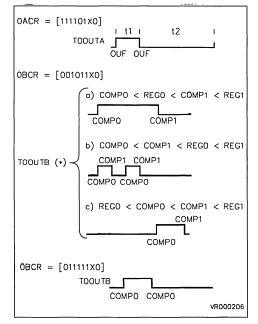

|      | 13.7.9  | Output A Control Register (OACR)          | 204 |

|      | 13.7.10 | Output B Control Register (OBCR)          | 205 |

|      | 13.7.11 | Flag Register (FLAGR)                     | 205 |

|      | 13.7.12 | Interrupt/DMA Mask Register (IDMR)        | 206 |

|      |         | DMA Counter Pointer Register (DCPR)       |     |

|      |         | DMA Address Pointer Register (DAPR)       |     |

|      | 13.7.15 | Interrupt Vector Register (IVR)           | 207 |

|      | 13.7.16 | Interrupt/DMA Control Register (IDCR)     | 208 |

|      | 13.7.17 | I/O Connection Register (IOCR)            | 208 |

|      |         |                                           |     |

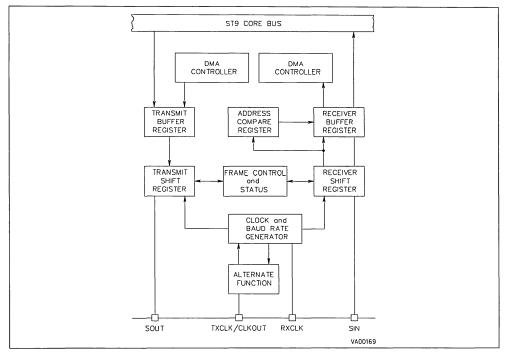

| 14 | <b>SERIA</b><br>14.1  | L COMMUNICATIONS INTERFACE                                                                                             |   |

|----|-----------------------|------------------------------------------------------------------------------------------------------------------------|---|

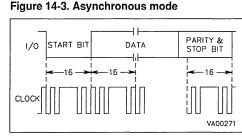

|    | 14.2                  | FUNCTIONAL DESCRIPTION                                                                                                 | 0 |

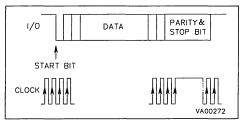

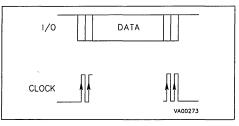

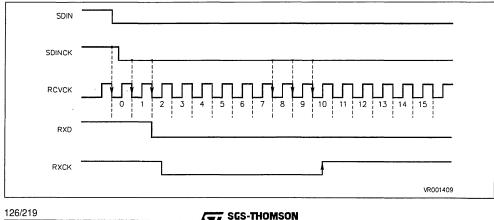

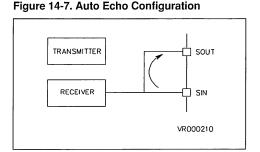

|    |                       | 14.2.1Serial Frame Format21014.2.2Clocks And Serial Transmission Rates21314.2.3Input Signals214                        | 3 |

|    |                       | 14.2.4 Output Signals 21                                                                                               | 5 |

|    | 14.3                  | INTERRUPTS AND DMA 21                                                                                                  | 5 |

|    |                       | 14.3.1         Interrupts         215           14.3.2         DMA         217                                         |   |

|    | 14.4                  | CONTROL REGISTERS                                                                                                      | 7 |

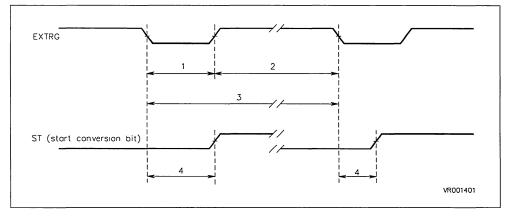

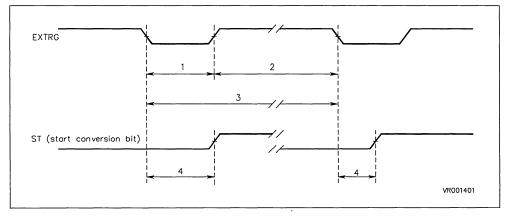

| 15 | <b>A/D CC</b><br>15.1 | DNVERTER         22           INTRODUCTION         225                                                                 |   |

|    | 15.2                  | FUNCTIONAL DESCRIPTION                                                                                                 | 6 |

|    |                       | 15.2.1 Operational Modes                                                                                               | 6 |

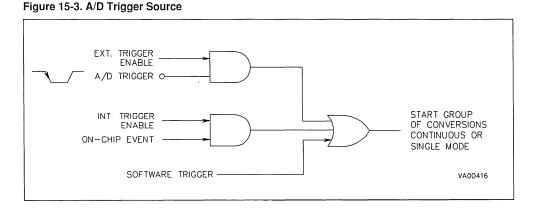

|    |                       | 15.2.2 Synchronisation 226                                                                                             | 6 |

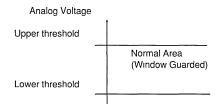

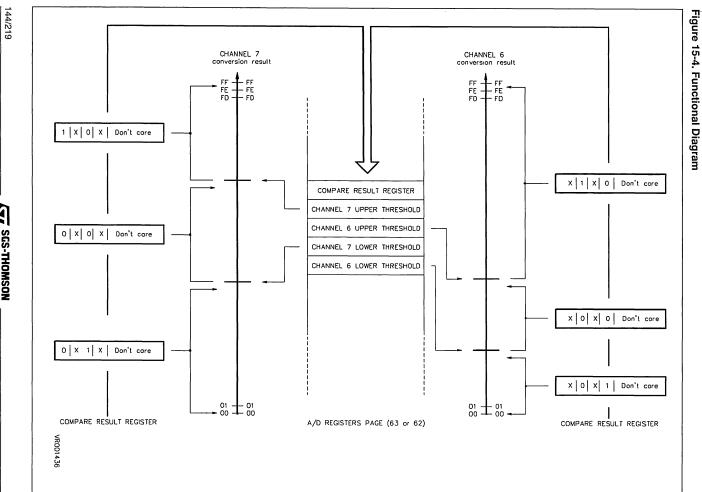

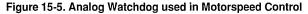

|    |                       | 15.2.3 Analog Watchdog                                                                                                 |   |

|    |                       | 15.2.4 Power down Mode                                                                                                 |   |

|    | 15.3                  | INTERRUPT 229                                                                                                          |   |

|    | 15.4                  | REGISTERS                                                                                                              |   |

|    |                       | 15.4.1         Register Mapping         230           15.4.2         Data Registers (DiR)         230                  |   |

|    |                       | 15.4.2 Data Registers (Diff)                                                                                           |   |

|    |                       | 15.4.4 Compare Result Register (CRR) 23                                                                                |   |

|    |                       | 15.4.5 Control Logic Register (CLR) 232                                                                                |   |

|    |                       | 15.4.6       Interrupt Control Register (ICR)       233         15.4.7       Interrupt Vector Register (IVR)       233 |   |

| 16 | SOFTW                 | VARE DESCRIPTION                                                                                                       | 5 |

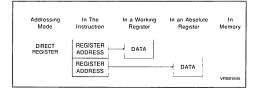

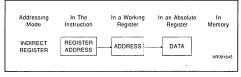

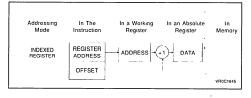

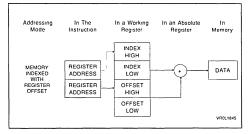

|    | 16.1                  | ADDRESSING MODES                                                                                                       | 5 |

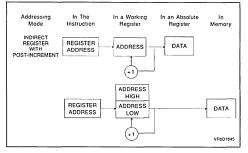

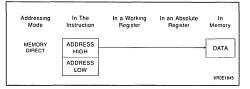

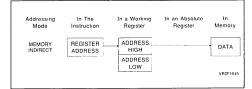

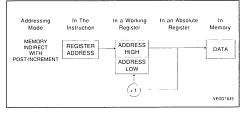

|    |                       | 16.1.1Register Addressing Modes23816.1.2Memory Addressing Modes238                                                     |   |

|    | 16.2                  | INSTRUCTION SET                                                                                                        | 2 |

|    |                       | 16.2.1 ST9 Processor Flags                                                                                             | 8 |

|    |                       | 16.2.2 Condition Codes                                                                                                 | - |

|    |                       | 16.2.3 Notation                                                                                                        | - |

|    | 16.3                  | INSTRUCTION SUMMARY                                                                                                    | 1 |

| RE | GISTER                | 1 MAP 283                                                                                                              | 3 |

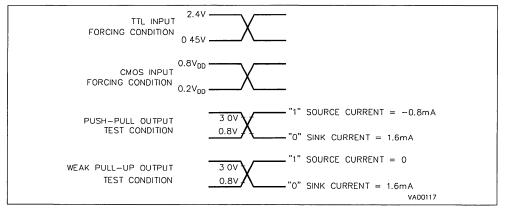

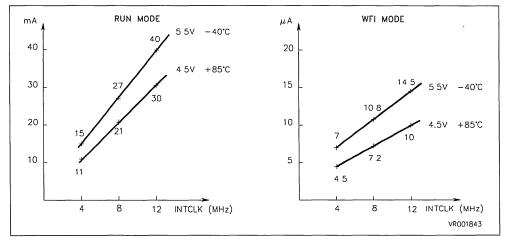

| 17 | ELECT                 | RICAL CHARACTERISTICS                                                                                                  | 7 |

|    |    | 190E40<br>190T40 |                                                          | 305 |

|----|----|------------------|----------------------------------------------------------|-----|

|    | 1  | DESCF            | RIPTION                                                  | 308 |

|    |    | 1.1              | GENERAL DESCRIPTION                                      | 308 |

|    |    | 1.2              | PIN DESCRIPTION                                          | 309 |

|    |    | 1.3              | I/O PORT ALTERNATE FUNCTIONS                             | 309 |

|    |    | 1.4              | MEMORY                                                   | 312 |

|    |    | 1.5              | EPROM PROGRAMMING                                        | 312 |

|    |    |                  | 1.5.1 Eprom Erasing                                      |     |

|    |    |                  | 1.5.1 A/D CONVERTER                                      |     |

|    | SI | 90R40            | )                                                        | 329 |

|    | 1  |                  |                                                          |     |

|    |    | 1.1              | GENERAL DESCRIPTION                                      |     |

|    |    | 1.2              | PIN DESCRIPTION                                          |     |

|    |    | 1.3              | I/O PORT ALTERNATE FUNCTIONS                             |     |

|    |    | 1.4              | MEMORY                                                   | 335 |

| AP | PL | ICAT.            |                                                          | 337 |

|    | A  | <b>V411/1</b> :  | 292 SYMBOLS.INC                                          | 339 |

|    | A  | N413/1           | 292 INITIALIZATION OF THE ST9                            | 360 |

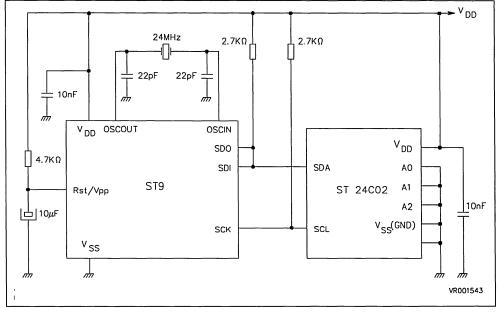

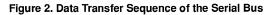

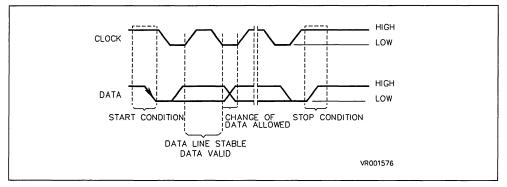

|    |    |                  | 092 USING THE I <sup>2</sup> C-bus PROTOCOL WITH THE ST9 |     |

|    |    |                  | 292 EXTERNAL DMA MODE-1/O DATA TRANSFER                  | 413 |

|    |    |                  | MER                                                      | 447 |

|    |    |                  | 292 STACK OVERFLOW DETECTION USING<br>DOG/TIMER          | 477 |

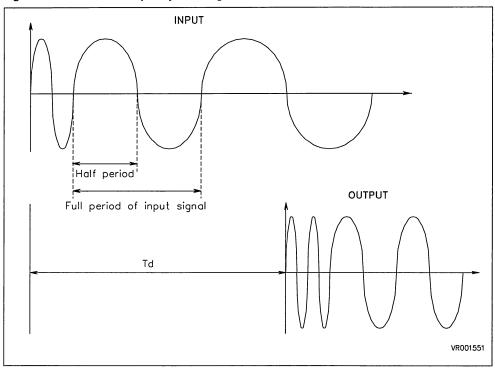

|    |    |                  | 192 FREQUENCY DOUBLER DEMONSTRATION                      | 483 |

## INTRODUCTION

#### ST9 APPLICATION TAILORED MCU

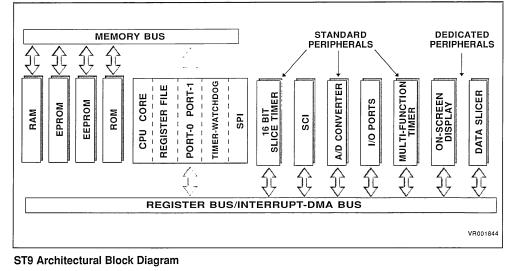

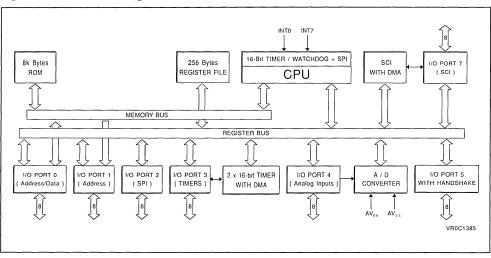

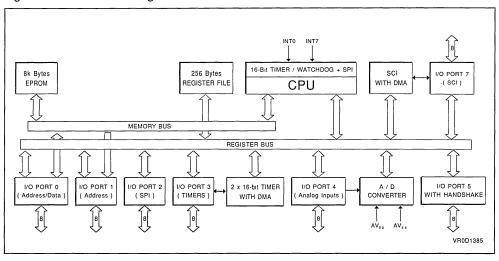

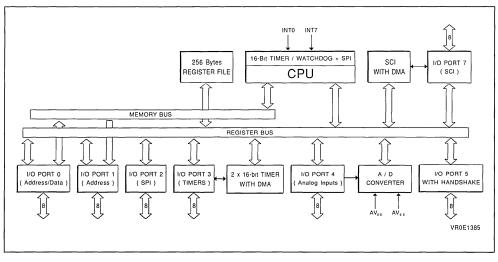

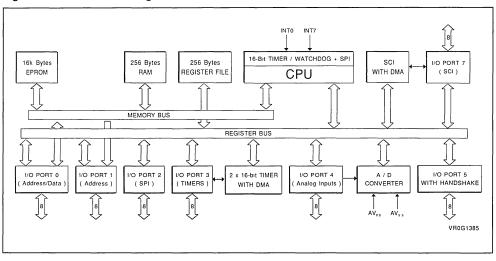

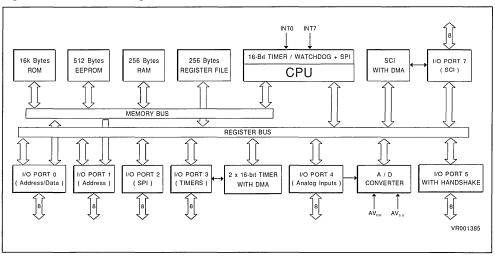

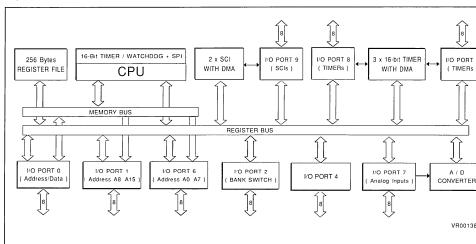

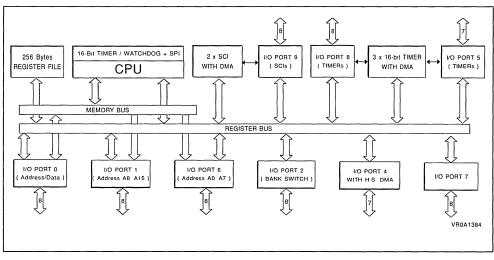

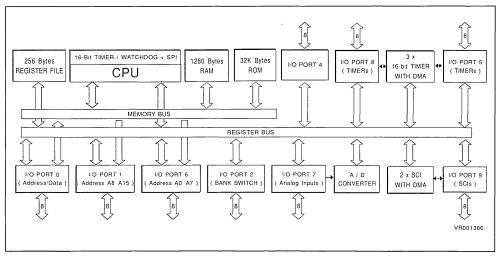

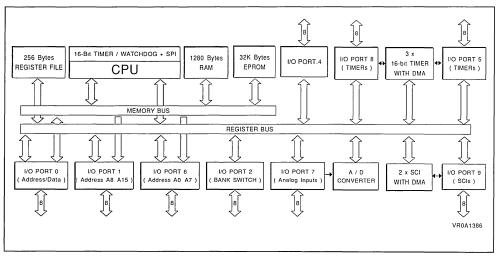

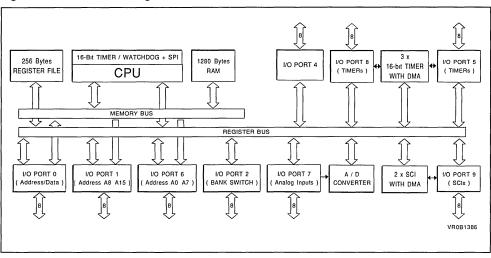

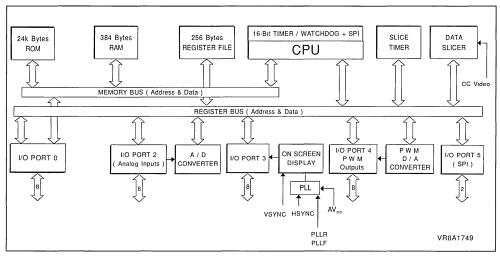

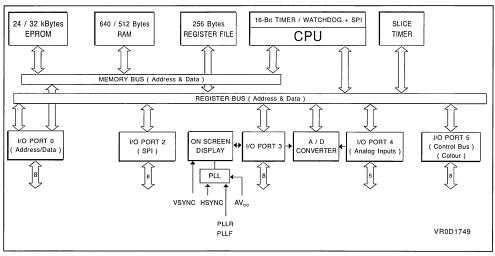

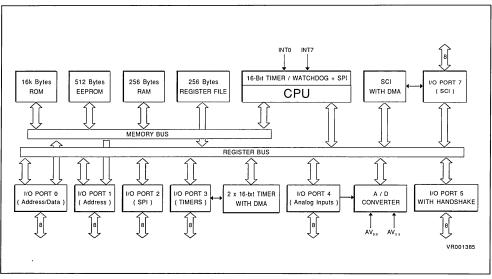

The ST9 family of 8/16 bit Microcontrollers (MCUs) was designed after the requirements of the most advanced applications in computer, consumer, telecom, industrial and automotive Segments.

Processed with the same proprietary CMOS EPROM and EEPROM technologies that have established SGS-THOMSON as a world leading supplier of non-volatile memories, the ST9 provides high speed computing with reduced power consumption.

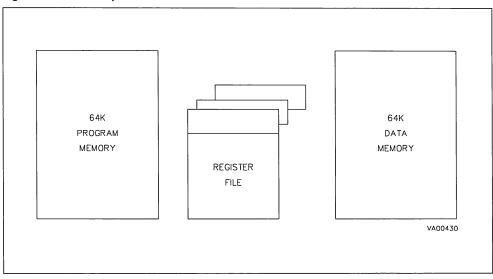

Built around a high performance, register based core, the ST9 family offers different program and data memory sizes and a wide range of on-chip peripherals to meet the needs of most systems.

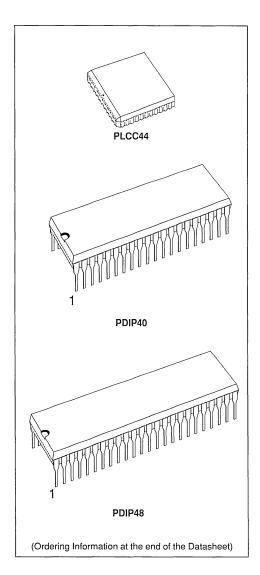

Time to market is minimized with ST9's well defined, socket compatible, evolution path, from application evaluation with EPROMs, to prototyping using OTPs, up to the high volume production using cost effective ROM versions.

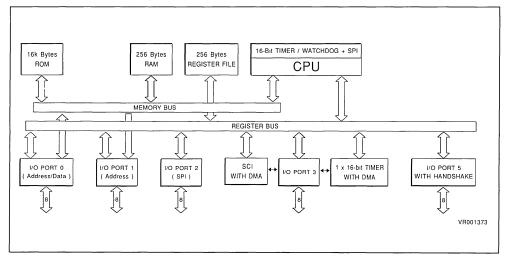

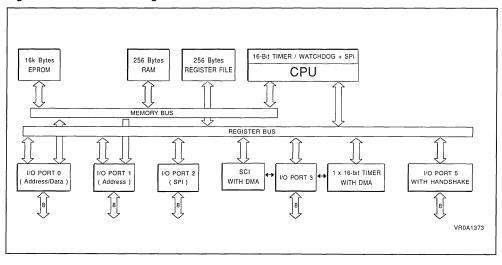

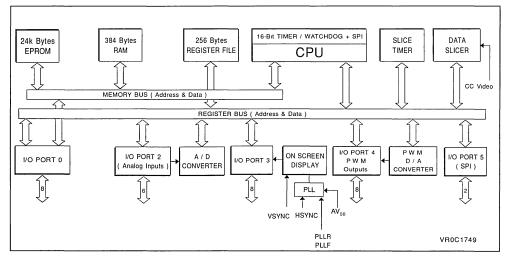

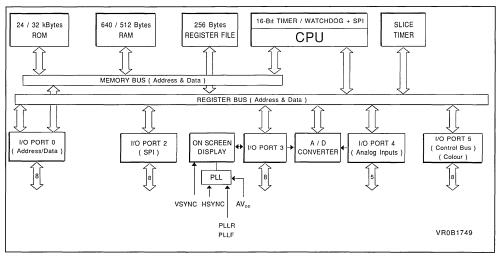

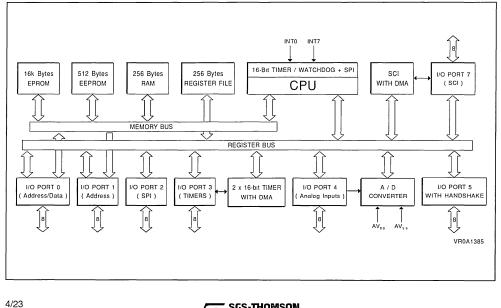

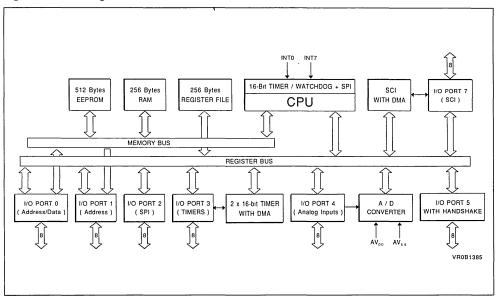

All standard ST9 devices include a Serial Peripheral Interface, a Watchdog Timer to ensure system integrity against externally generated malfunctions, bit configurable I/Os, prioritizable Interrupts for real-time data handling, and DMA for fast data transfers with handshake (HSHK).

In addition ST9 family variants include up to three Multi-Function Timers, two Serial Communication Interfaces (SCI), an Analog to Digital converter (A/D) and On-Screen Display and Data-Slicer for TV control.

#### REGISTER BASED ARCHITECTURE

The Register based architecture provides more efficient data handling and reduced code size compared to an accumulator based MCU. It also provides the capability for fast context switching.

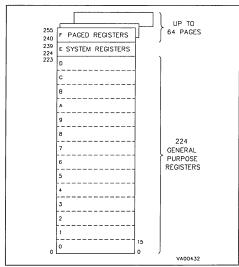

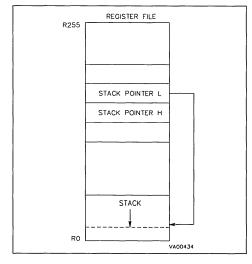

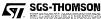

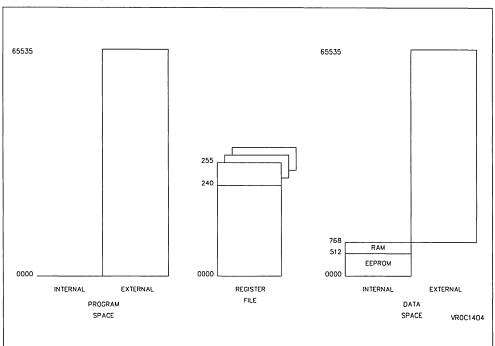

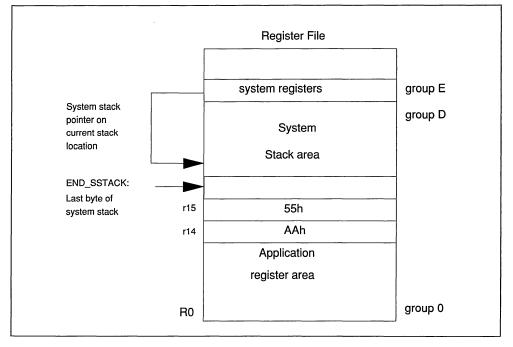

224 of the 256 8-bit Registers in the ST9 Register File are available as accumulators, index registers, or stack pointers and can be cascaded to perform all these functions as 16-bit registers. The remaining registers are dedicated to system and peripheral control.

This architecture is common to all ST9 devices.

#### FLEXIBLE I/O

The flexibility of the ST9 I/O pins allow designers to match the MCU to the application, and not the application to the MCU.

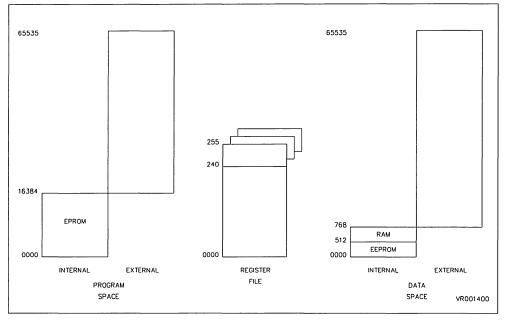

Most I/Os can be individually programmed as input (TTL or CMOS thresholds), output (open-drain or pushpull), bidirectional, or as the Alternate Function of a peripheral, such as a Timer or an A/D Converter.

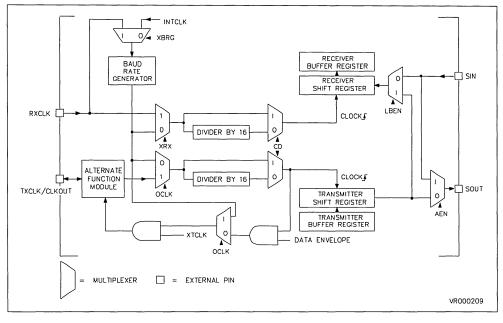

#### COMPREHENSIVE SCI

Serial communication is easily implemented, using formats and facilities offered by the ST9 Serial Communication Interface.

## INTRODUCTION

This peripheral provide full flexibility in character format (5,6,7,8 databits), odd, even or no parity, address bit, 1, 1.5, or 2 stop bits in asynchronous mode, and an integral baud rate generator allowing communication at up to 370k baud in asynchronous mode or 1.5Mbyte/s in synchronous mode.

Industrial, telecom and communication systems users can furthermore benefit from the self-test and address bit wake-up facility offered by the character search mode.

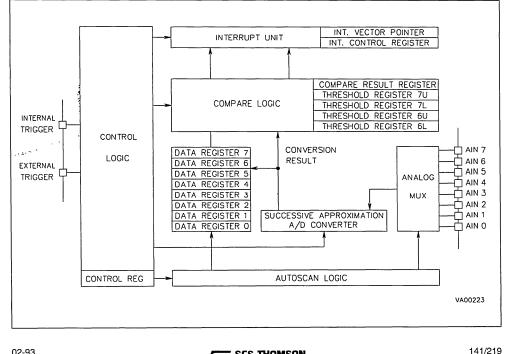

#### FAST A/D WITH ANALOG WATCHDOG

Up to 8 analog input voltages can be sequentially converted by the Analog to Digital converter including on-chip sample and hold.

The 11µs conversion time, and the possibility to trigger conversions either by the on-chip timers, or by external sources, allows real time processing of analog data.

CPU loading is also reduced by the analog watchdog on two channels, the peripheral interrupts the ST9 when the analog input voltage moves out of a preset threshold window.

#### UNIVERSAL SPI

A universal Serial Peripheral Interface, providing basic I<sup>2</sup>C-bus, Microwire-Bus and S-BUS functionality, allows efficient communication with low-cost external peripherals or serial access memories such as EEPROMs.

#### **MULTI-FUNCTION TIMERS**

The 16 bit up/down counter operating in 13 modes gives the ST9 Multi-function Timer the possibility to cover most application timing requirements.

Two input pins, programmable as external clock, gate or trigger, allow 16 modes of operation, including autodiscrimination of the direction of externally generated signals.

Pulse Width Generation can easily be implemented, using the overflow/underflow signal and the two 16 bit comparison registers, each of them able to independently set, reset, toggle or ignore two output bits.

The Multifunction Timer outputs may also generate interrupts for system scheduling, and trigger DMA transactions of a data byte to or from a data table in memory through an I/O Port with handshake.

#### **ON-SCREEN DISPLAY**

Interactive information display for television control is easily implemented with the powerful ST9 On-Screen Display. With up to 34 characters in 15 rows, and colour, italic, underline, flash, tranparent and fringe options, the 128 character set can be adapted for all needs.

#### DATA-SLICER

Closed Caption Data can be easily extracted from the video signal with the ST9 Data Slicer. When used in conjunction with the ST9 On-Screen Display, a powerful TV controller can be achieved with the minimum of components.

#### POWERFUL INSTRUCTION SET

The ST9 has 14 addressing modes and instructions (including multiply, divide, table search and block move) to cover all data manipulation needs, bit, byte and word, at the speed required by even the most demanding control application.

Its instruction set was conceived to facilitate the software designer's task, and to improve programming efficiency.

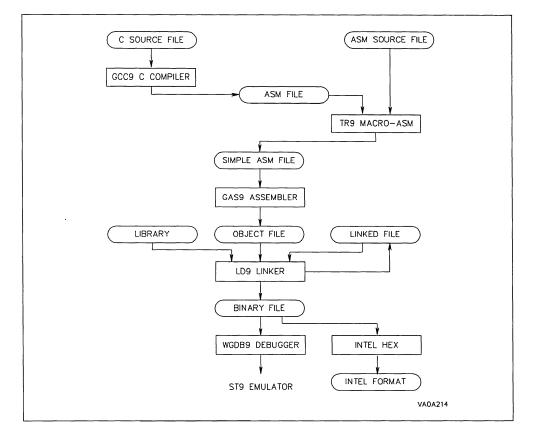

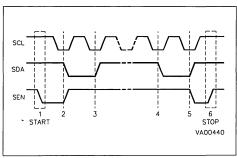

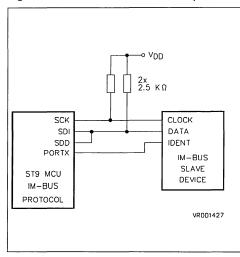

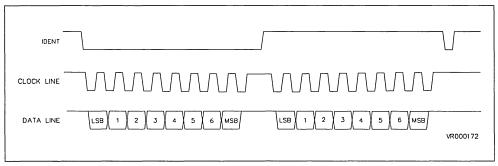

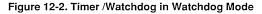

#### FULL DEVELOPMENT SUPPORT