SIGNAL PROCESSING TECHNOLOGIES

1 9 9 5

Leadership in

Data Conversion

and Signal Processing

<u>W - J Electronic Sales</u> 1590 Oakland Rd., Ste. B 110-2 San Jose, CA 95131 Phone: (408) 437-5600 Fax: (408) 437-0889

SIGNAL PROCESSING TECHNOLOGIES

# 1995 DATA BOOK

# SIGNAL PROCESSING TECHNOLOGIES, INC.

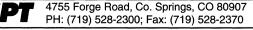

4755 FORGE ROAD, COLORADO SPRINGS, CO 80907 PHONE: (719) 528-2300 FAX: (719) 528-2370

# **GENERAL INFORMATION**

#### **TYPES OF DATA SHEETS**

ADVANCE INFORMATION — These data sheets contain the descriptions of products that are in development. The specifications are based on engineering calculations, computer simulations and/or initial prototype evaluation.

PRELIMINARY — These data sheets contain minimum and maximum specifications that are based on initial device characterization. These limits are subject to change upon the completion of full characterization over the specified temperature and supply voltage ranges.

FINAL — These data sheets contain specifications based on complete characterizations of the devices over the specified temperature and supply voltage ranges.

#### WARRANTY

SPT warrants that standard products (except for board-level products) delivered hereunder shall be free from defects in material and workmanship under normal use and service for a period of one (1) year from the date of shipment from SPT's facility. Board level products delivered hereunder shall be free from defects in material and workmanship under normal use and service for a period of ninety (90) days from the date of shipment from SPT's facility. For products which are not standard products, such as dice and wafers, SPT warrants to Buyer that such products shall be free from defects in material and workmanship under normal use and service for a period of thirty (30) days from the date of shipment. Products which are "engineering samples" are sold AS IS, "WITH ALL FAULTS," and with no warranty whatsoever.

If, during such one year, ninety day or thirty-day period (i) SPT is notified promptly in writing upon discovery of any defect in the goods, including a detailed description of such defect; (ii) such goods are returned to SPT, F.O.B. SPT's facility; and (iii) SPT's examination of such goods discloses to SPT's satisfaction that such goods are defective and such defects are not caused by accident, abuse, misuse, neglect, alteration, improper installation, repair or alteration by someone other than SPT, improper testing, or use contrary to any instructions issued by SPT, within a reasonable time, SPT shall (at its sole option) either replace or credit Buyer the purchase price of such goods.

Prior to any return of goods by Buyer pursuant to the section, Buyer shall afford SPT the opportunity to inspect such goods at Buyer's location, and any such goods so inspected shall not be returned to SPT without its prior written consent.

SPT shall return any goods repaired or replaced under this warranty to Buyer, transportation prepaid, and reimburse Buyer for the transportation charges paid by Buyer for such goods. The performance of this warranty does not extend the warranty period for any goods beyond that period applicable to the goods originally delivered.

The foregoing warranty constitutes SPT's exclusive liability, and the exclusive remedy of Buyer, for any breach of any warranty or other nonconformity of the goods covered by this quotation. THIS WARRANTY IS EXCLUSIVE, AND IN LIEU OF ALL OTHER WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR USE, WHICH ARE HEREBY EXPRESSLY DISCLAIMED.

#### PRODUCTS AND SPECIFICATIONS

Signal Processing Technologies reserves the right to make changes to its products or specifications at any time, without notice, to improve the design and/or performance in order to supply the best possible product. Signal Processing Technologies does not assume any responsibility for the use of any circuitry described in this book other than the circuitry contained within a Signal Processing Technologies' product. Signal Processing Technologies makes no representations that the circuitry described within this book is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights, or other rights of Signal Processing Technologies.

#### LIFE SUPPORT APPLICATIONS POLICY

**WARNING** — Signal Processing Technologies' products shall not be used within any life support systems without the specific written consent of Signal Processing Technologies. A life support system is a product or system intended to support or sustain life which, if it fails, can be reasonably expected to result in a significant personal injury or death.

#### ©SIGNAL PROCESSING TECHNOLOGIES, INC. MARCH 1995 — ALL RIGHTS RESERVED

#### How to Use This Book

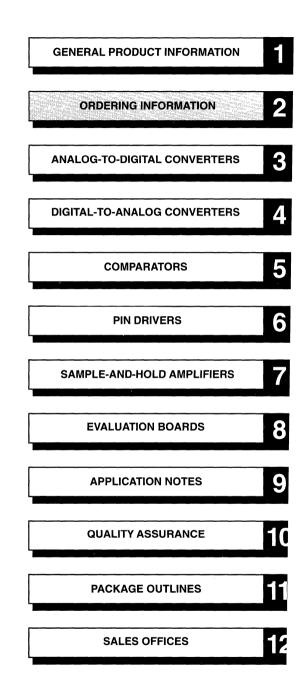

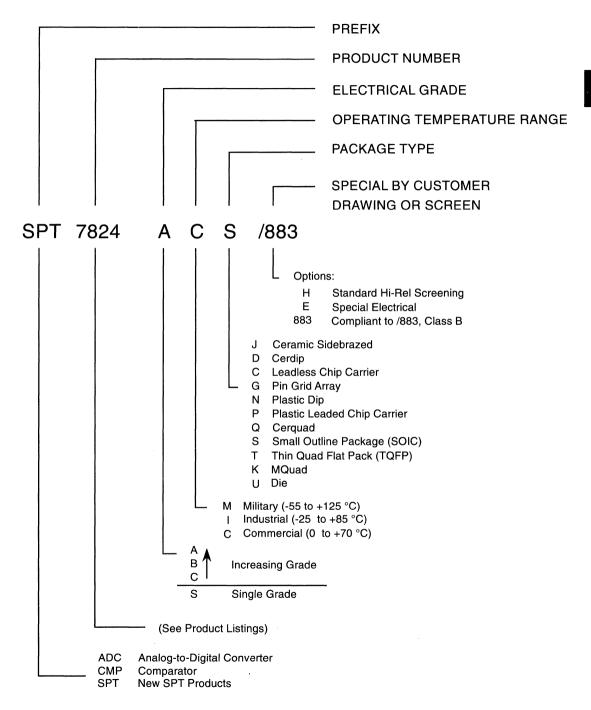

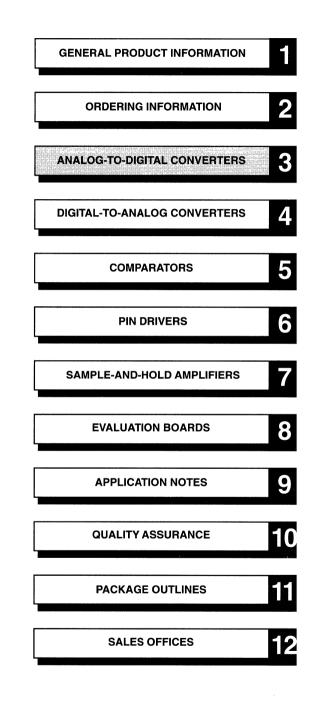

The front part of this book has a complete product selection guide, cross reference table and detailed ordering information. The product selection guide lists all of the products and their key features for quick reference and comparison purposes, the product cross reference guide provides a cross over reference to other manufactures by product part number, and the ordering information section provides complete ordering information by part number, grade, package type and operating temperature range.

There is a master table of contents at the front of the book that shows the beginning page number of each data sheet, and each data sheet section has its own table of contents for that section. Data sheets for the analog-to-digital converters and the digital-to-analog converters are placed in ascending order of bit resolution, and the comparator and evaluation board data sheets are placed in alphanumeric order.

#### **Customer Service**

Customer support and service is extremely important to us at SPT. Not only do we pride ourselves on high-performance data conversion products, but we pride ourselves on high-performance customer service. Factory direct assistance is available weekdays from 7:30 AM to 5:30 PM MST. Please contact our Customer Service Center at 1-800-643-3778 (USA only) or 1-719-528-2300 to place an order, return products, ask technical or applications related questions, or order technical literature. For immediate local assistance contact your local SPT sales representative. See a listing of our domestic and international sales offices, representatives and distributors at the back of this book.

#### **Technical Literature and Applications Assistance**

Contact our Customer Service Center at 1-719-528-2300 for the latest product data sheets and evaluation board information. In addition to product data sheets, SPT has a complete line of product application notes to assist in the evaluation and board layout design of our high performance data conversion products. Contact the SPT Customer Service Center to order your technical application notes. For factory direct applications support, our applications engineers are ready to answer all of your technical questions and inquiries. Contact our Applications Engineering Center at 1-719-528-2300 weekdays from 8:00 AM to 5:00 PM MST.

Sales

and Service

#### **Prices and Quotations**

Price quotations made by Signal Processing Technologies or its authorized field sales representatives are valid for 30 days. Delivery quotations are subject to reconfirmation at the time of order placement. Call our Customer Service Center for information concerning pricing, product delivery status, product samples or information regarding the return of product.

#### **Placing Orders**

You can place orders by telephone, fax or mail with any of our authorized sales representatives, distributors, regional offices or our Colorado Springs headquarters. See the listing of sales offices, representatives and distributors at the back of this book for the location nearest you or call SPT Sales and Marketing at 1-800-643-3778 (USA only) or 1-719-528-2300 for assistance.

#### **Returns and Warranty Service**

When you need to return products to SPT, contact us prior to shipping to obtain authorization and shipping instructions. For complete instructions, contact your local sales representative, distributor or call our Colorado Springs Customer Service Center at 1-800-643-3778 (USA only) or 1-719-528-2300. See the list of domestic and international representatives and distributors at the back of this book.

If you are returning products, please call for your RMA number, then ship units prepaid and supply the original purchase order number and date, along with an explanation of the malfunction. Upon receipt of the returned product, SPT will verify the problem and inform you of the status of any warranty replacements or credits applicable.

# About SPT

- ✓ Founded in 1983.

- ✓ Develops, manufactures and markets high-performance data conversion and signal conditioning products.

- Corporate headquarters in Colorado Springs, CO.

- Domestic and international manufacturing facilities.

- ✓ Wholly-owned subsidiary of Toko, Inc.

- Sales offices in the United States and Europe with sales representatives throughout North America, Europe and the Far East.

#### **Company Background**

Signal Processing Technologies, Inc. (SPT) develops, manufactures and markets highperformance data conversion and signal conditioning products and is a leader in cost-effective, highest performance monolithic analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and comparators. Since 1983 SPT has provided leading-edge monolithic conversion products with industry breakthroughs in resolution, sampling rate, power and cost.

Today, we continue to expand our line of converter and comparator products to meet our customer needs in the commercial, industrial, and military market sectors worldwide. This 1995 data book includes over 20 new data conversion products as well as many new temperature performance ranges and packaging options for existing products. With our innovative product line and excellence in customer application and sales support, SPT continues to be one of the fastest growing data conversion integrated circuit (IC) suppliers in the industry.

#### **Key Markets and Applications**

SPT's products are designed for a variety of commercial, industrial, and military systems applications. Commercial and industrial applications include video capture and TV broadcast, CRT monitors, desktop scanners, medical ultrasound, IR imaging, and RF communications including satellite, cellular and microwave systems. Additional applications include high-performance instrumentation such as automated test equipment (ATE), scientific instruments, and digital oscilloscopes. SPT's high-performance products lend themselves very well to military applications which include radar, guided weapons, surveillance and reconnaissance, target acquisition, navigation and guidance.

#### **ISO9001 Certified**

As of February 1995, Signal Processing Technologies, Inc. received ISO9001 certification from the internationally recognized British Standard Institute. BSI certifies companies across the world and is one of the leading bodies of the European Quality System Certification Network (EQNET).

ISO9001 is an international standard for assessing the quality management system for

companies that perform design, manufacturing and testing of products. Certification means that a complete

quality management system is in place for design/ development, production, and servicing of all SPT products. The SPT quality management system is audited by BSI biannually to ensure conformity to the ISO9001 standard.

# SPT — Leadership in Data Conversion and Signal Processing

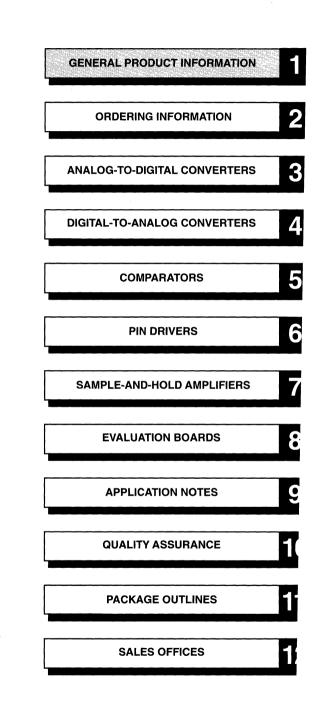

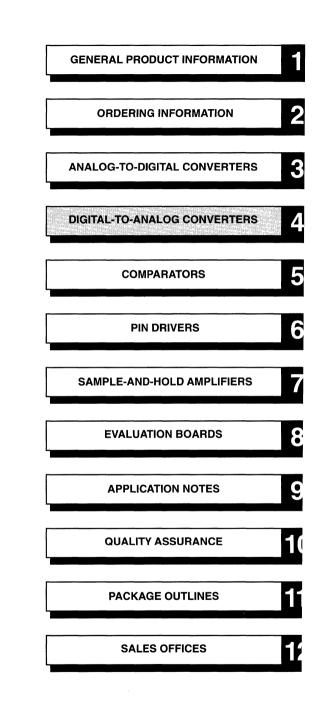

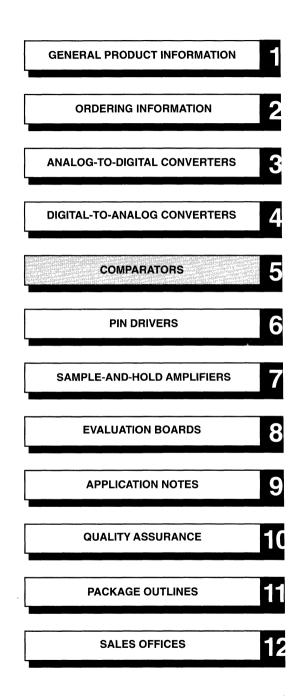

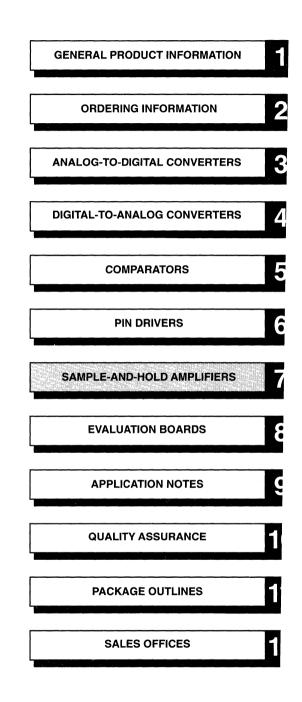

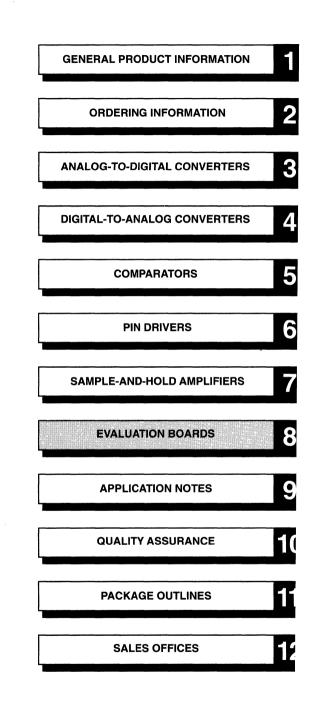

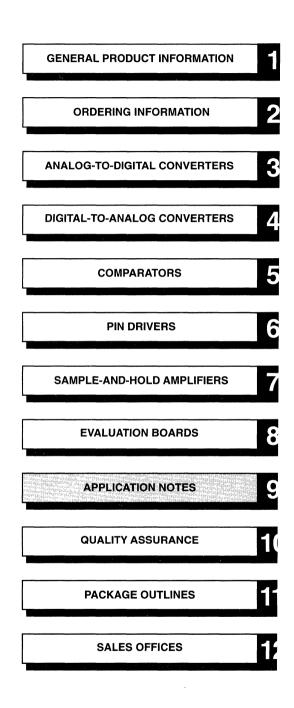

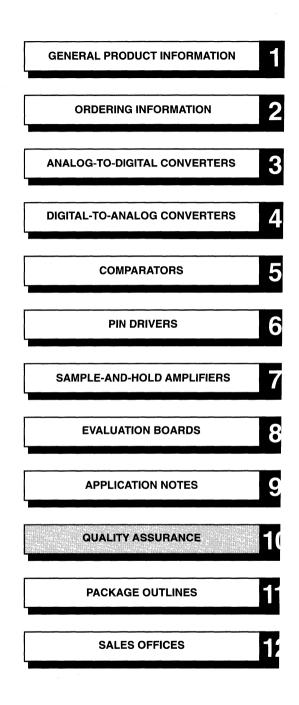

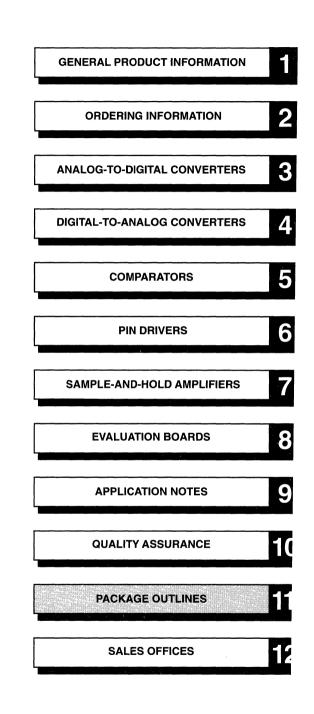

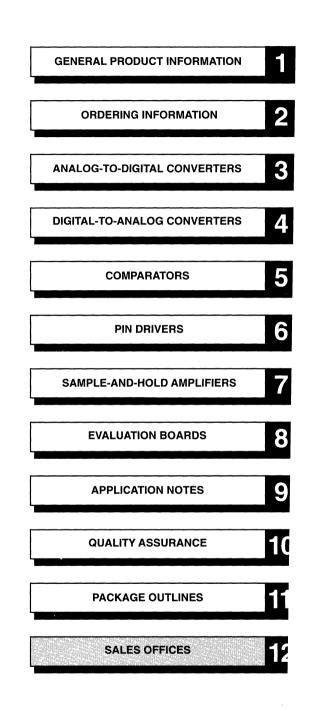

# TABLE OF CONTENTS

| Section 1 | General Pr                   | oduct Information                              |       |  |  |  |  |  |  |

|-----------|------------------------------|------------------------------------------------|-------|--|--|--|--|--|--|

|           | Product Cross                | tion Guide<br>s Reference Guide<br>Definitions |       |  |  |  |  |  |  |

| Section 2 | Ordering In                  | nformation                                     | 2-3   |  |  |  |  |  |  |

| Section 3 | Analog-to-Digital Converters |                                                |       |  |  |  |  |  |  |

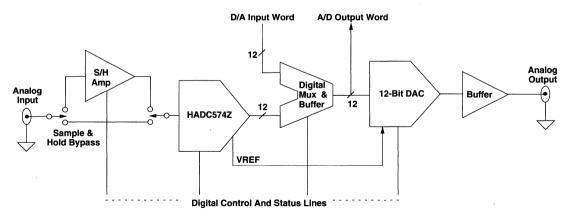

|           | HADC574Z                     | 12-Bit, 25 μsec BiCMOS                         |       |  |  |  |  |  |  |

|           | HADC674Z                     | 12-Bit, 15 µsec BiCMOS                         |       |  |  |  |  |  |  |

|           | SPT774                       | 12-Bit, 8 μsec BiCMOS                          | 3-41  |  |  |  |  |  |  |

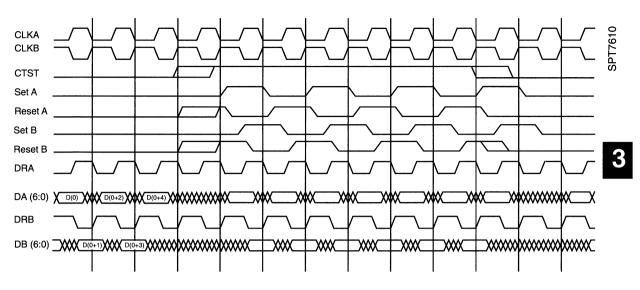

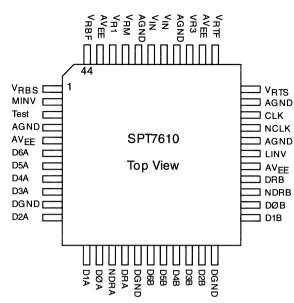

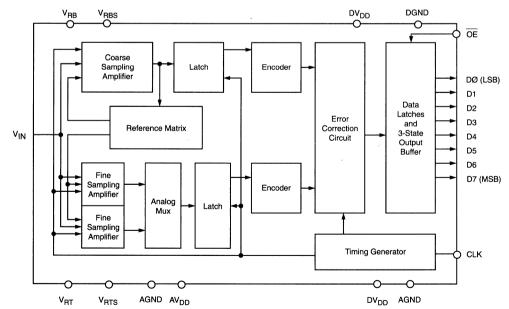

|           | SPT7610                      | 6-Bit, 1 GSPS Flash                            |       |  |  |  |  |  |  |

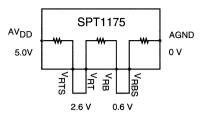

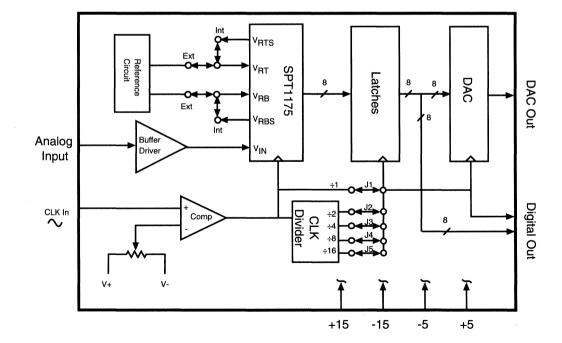

|           | SPT1175                      | 8-Bit, 20 and 30 MSPS, CMOS                    | 3-67  |  |  |  |  |  |  |

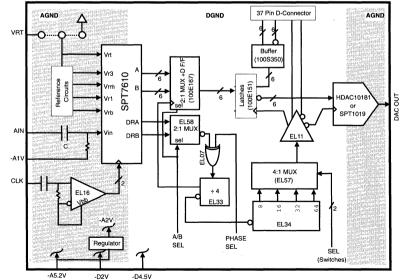

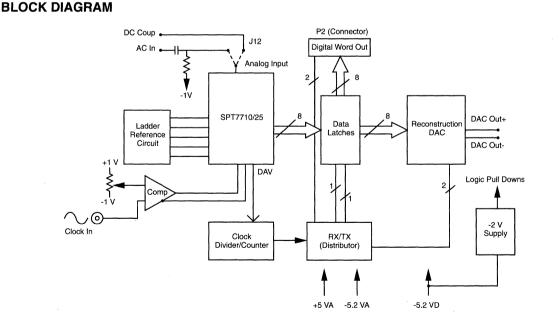

|           | SPT7710                      | 8-Bit, 150 MSPS                                |       |  |  |  |  |  |  |

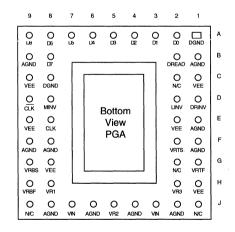

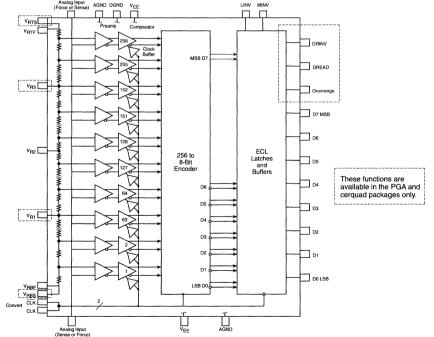

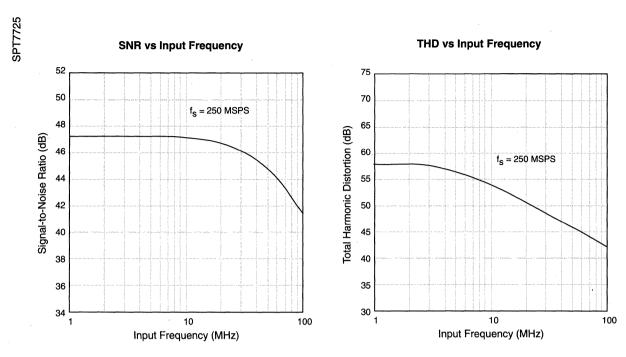

|           | SPT7725                      | 8-Bit, 300 MSPS                                |       |  |  |  |  |  |  |

|           | SPT7750                      | 8-Bit, 500 MSPS                                |       |  |  |  |  |  |  |

|           | SPT7755                      | 8-Bit, 750 MSPS                                |       |  |  |  |  |  |  |

|           | SPT7760                      | 8-Bit, 1 GSPS                                  |       |  |  |  |  |  |  |

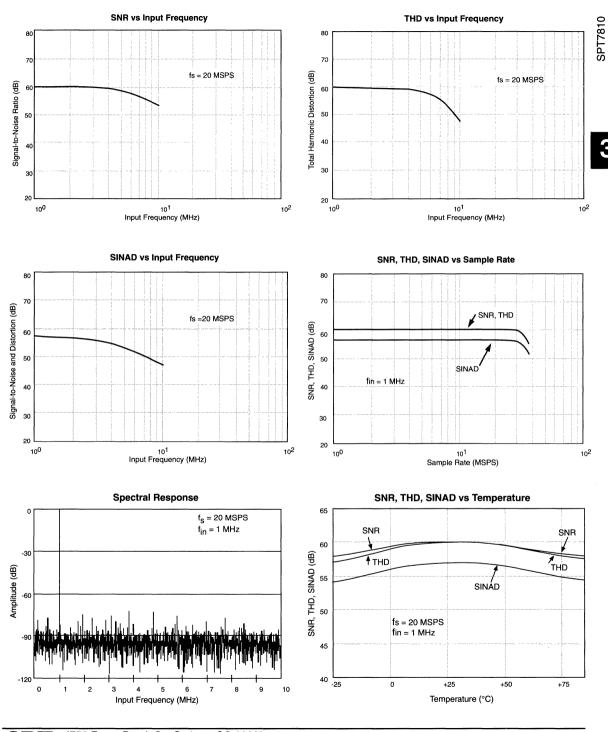

|           | SPT7810                      | 10-Bit, 20 MSPS, ECL Outputs                   | 3-123 |  |  |  |  |  |  |

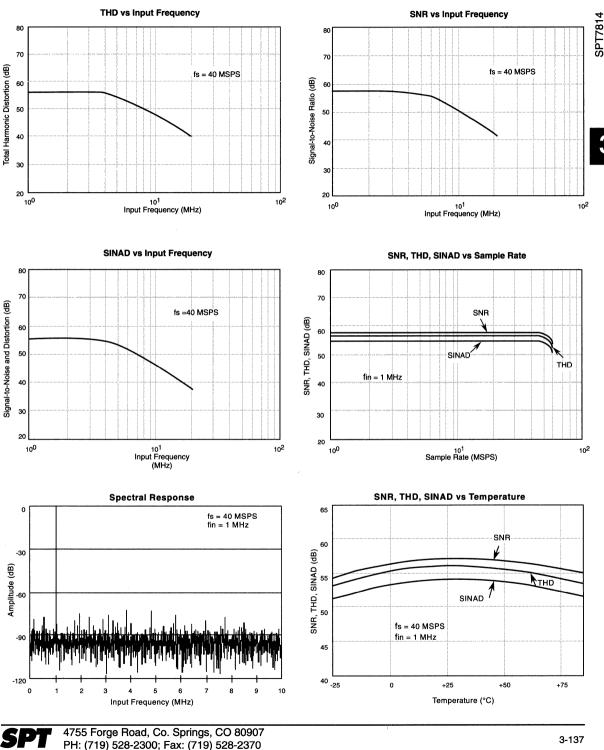

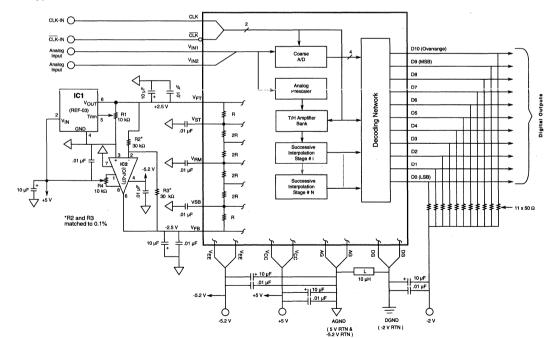

|           | SPT7814                      | 10-Bit, 40 MSPS, ECL Outputs                   |       |  |  |  |  |  |  |

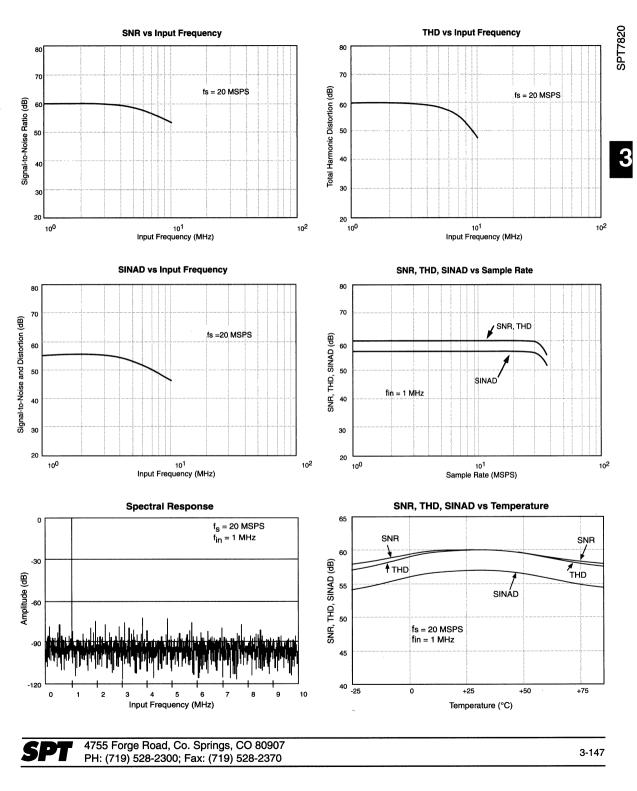

|           | SPT7820                      | 10-Bit, 20 MSPS, TTL Outputs                   | 3-143 |  |  |  |  |  |  |

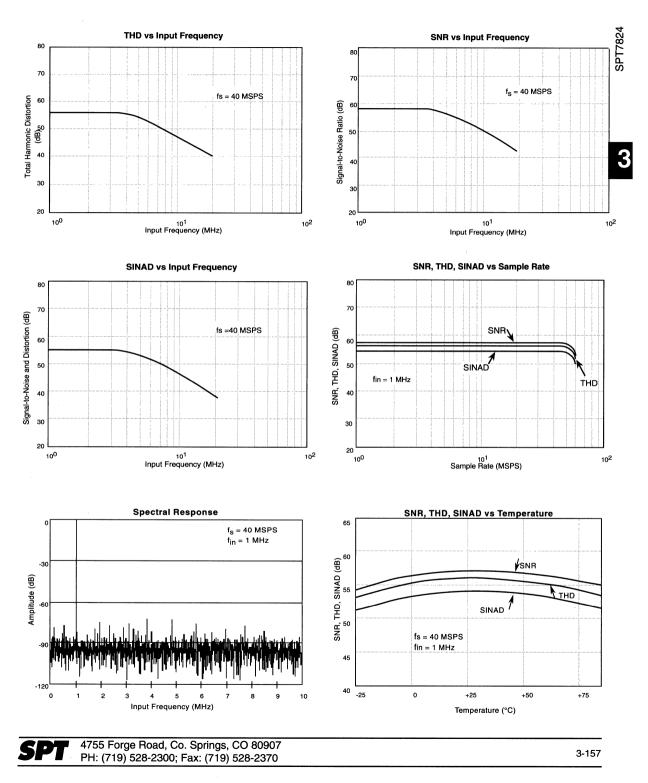

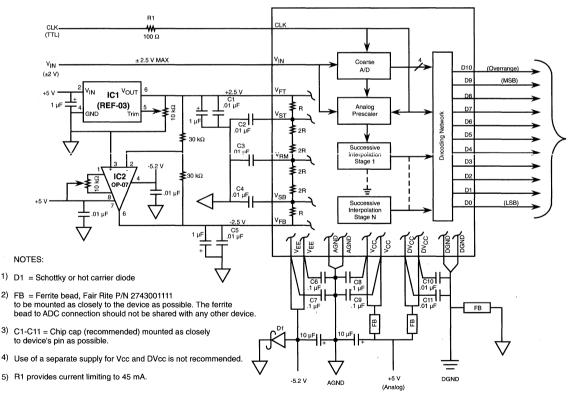

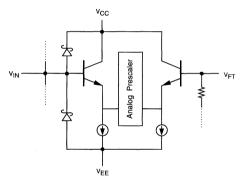

|           | SPT7824                      | 10-Bit, 40 MSPS, TTL Output                    |       |  |  |  |  |  |  |

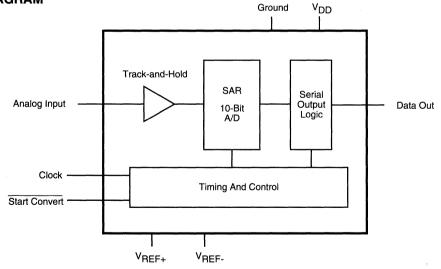

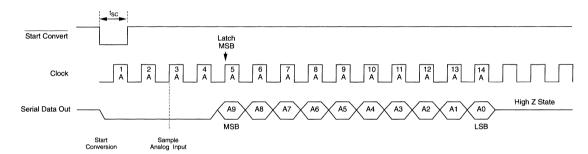

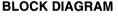

|           | SPT7830                      | 10-Bit, 2.5 MSPS, Serial Outputs               | 3-163 |  |  |  |  |  |  |

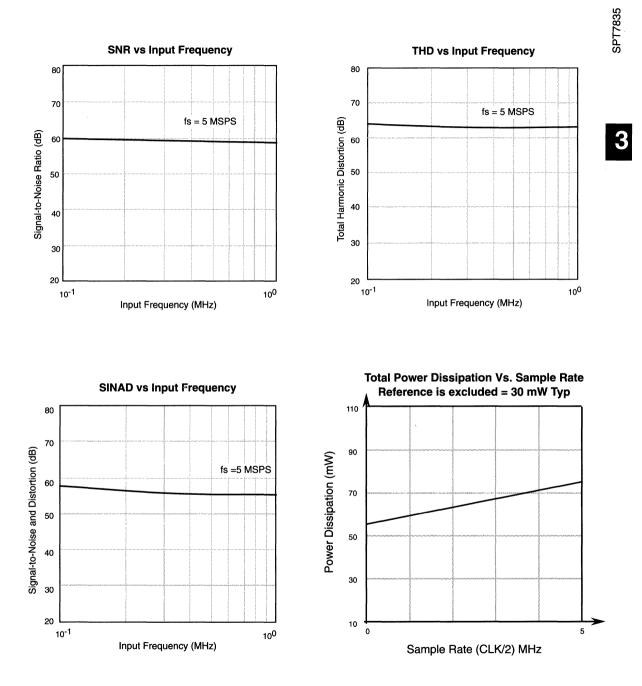

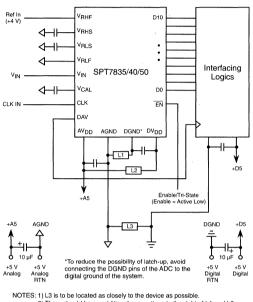

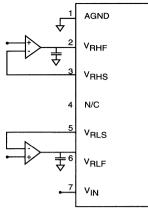

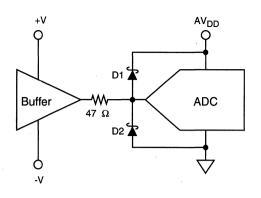

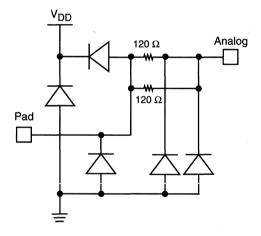

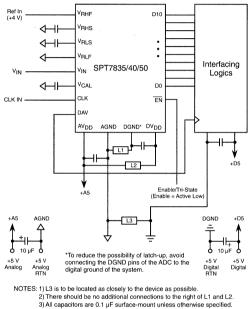

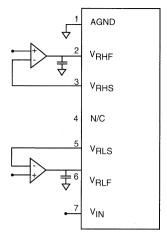

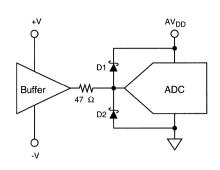

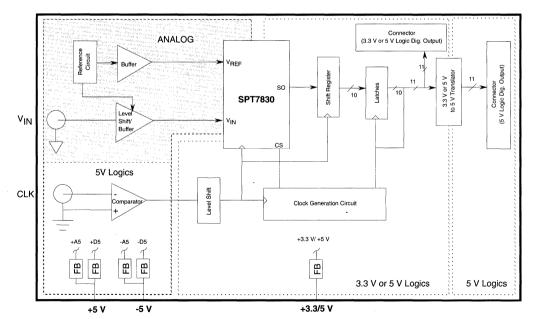

|           | SPT7835                      | 10-Bit, 5 MSPS, Low Power, CMOS                |       |  |  |  |  |  |  |

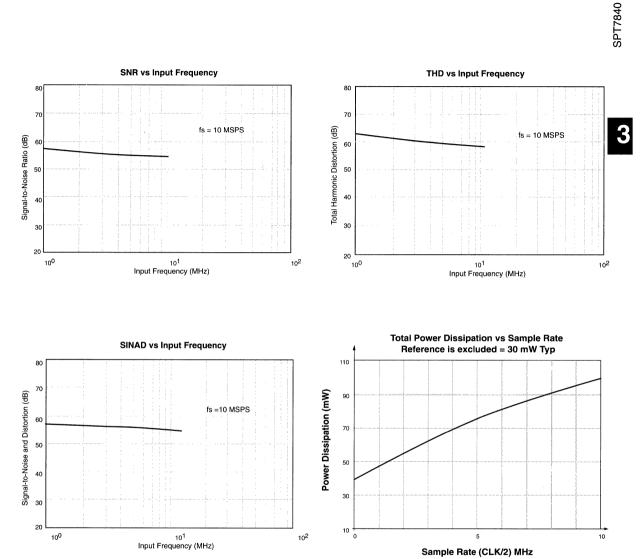

|           | SPT7840                      | 10-Bit 10 MSPS, Low Power, CMOS                | 3-181 |  |  |  |  |  |  |

|           | SPT7850                      | 10-Bit, 20 MSPS, Low Power, CMOS               |       |  |  |  |  |  |  |

|           | SPT7852                      | Dual 10-Bit, 20 MSPS, Low Power, CMOS          |       |  |  |  |  |  |  |

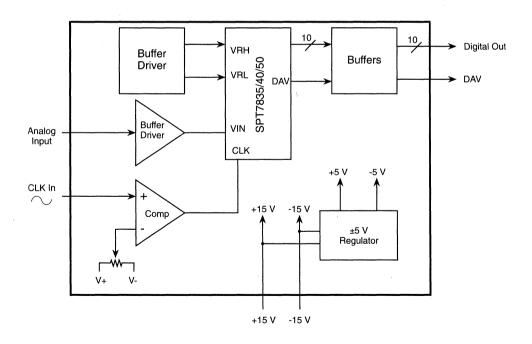

|           | SPT7855                      | 10-Bit, 25 MSPS Low Power, CMOS                | 3-205 |  |  |  |  |  |  |

|           | SPT7860                      | 10-Bit, 40 MSPS, Low Power, CMOS               |       |  |  |  |  |  |  |

|           | SPT7861                      | 10-Bit, 40 MSPS, Low Power, CMOS               | 3-225 |  |  |  |  |  |  |

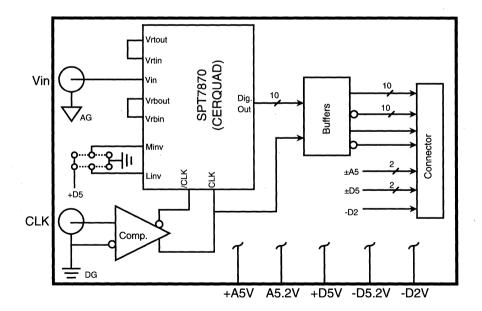

|           | SPT7870                      | 10-Bit, 100 MSPS, ECL Outputs                  | 3-231 |  |  |  |  |  |  |

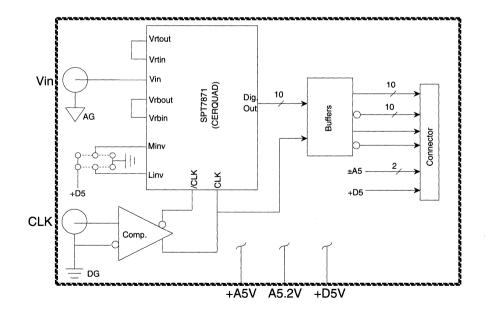

|           | SPT7871                      | 10-Bit, 100 MSPS, TTL Outputs                  |       |  |  |  |  |  |  |

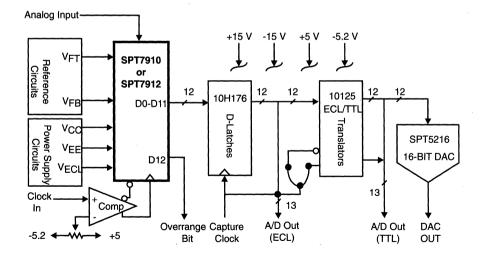

|           | SPT7910                      | 12-Bit, 10 MSPS, ECL Outputs                   |       |  |  |  |  |  |  |

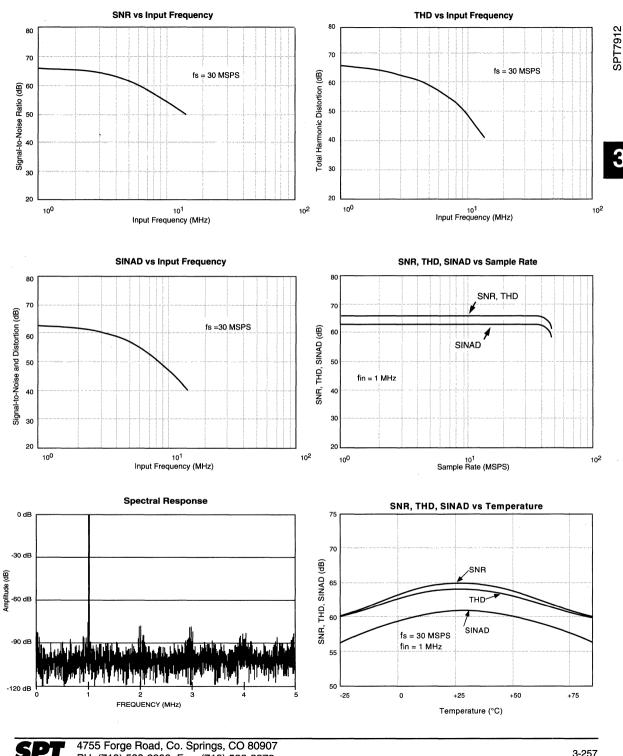

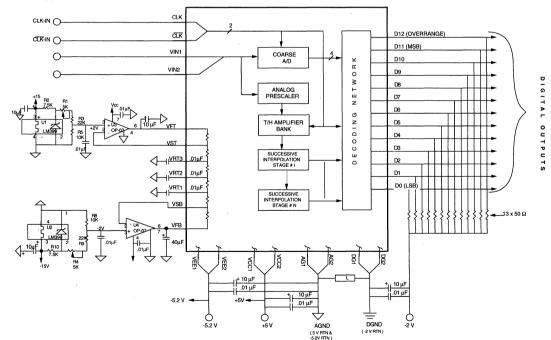

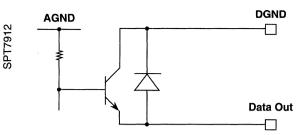

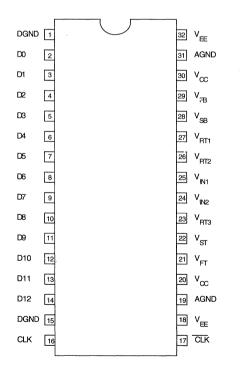

|           | SPT7912                      | 12-Bit, 30 MSPS, ECL Outputs                   |       |  |  |  |  |  |  |

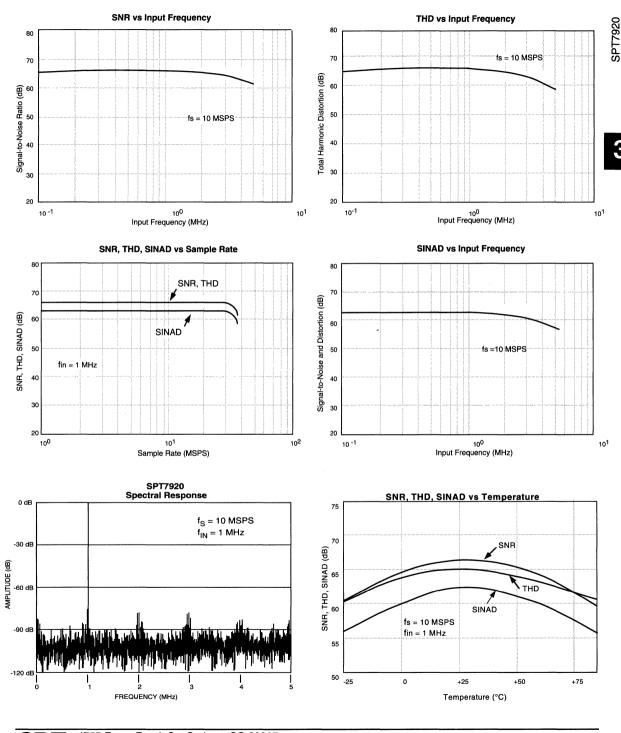

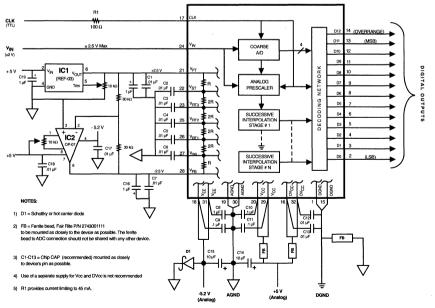

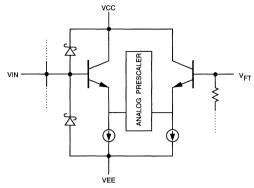

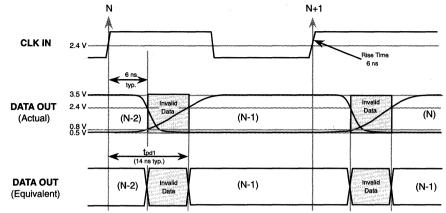

|           | SPT7920                      | 12-Bit, 10 MSPS, TTL Outputs                   |       |  |  |  |  |  |  |

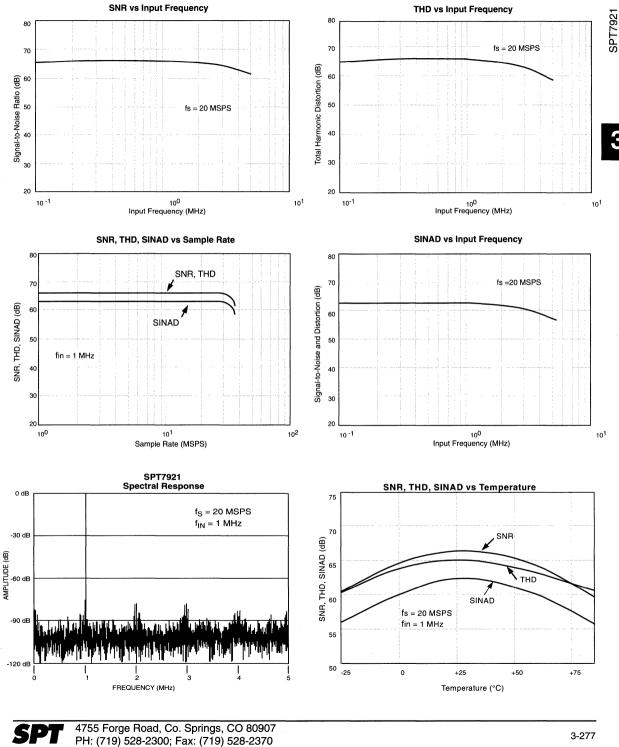

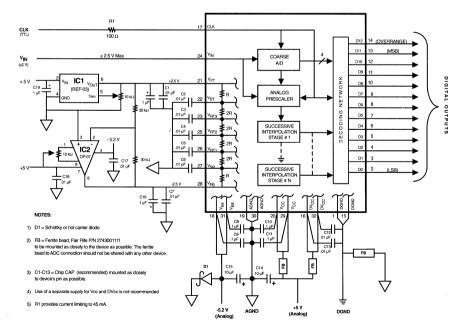

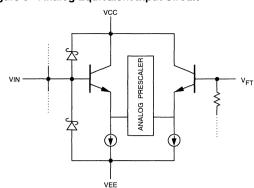

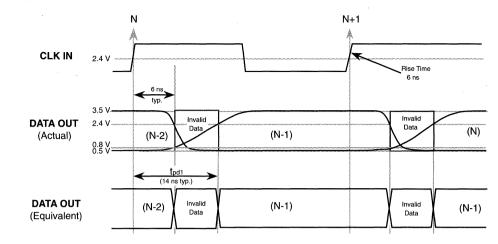

|           | SPT7921                      | 12-Bit, 20 MSPS, TTL Outputs                   |       |  |  |  |  |  |  |

|           | SPT7922                      | 12-Bit, 30 MSPS, TTL Outputs                   |       |  |  |  |  |  |  |

|           | SPT7930                      | 12-Bit, 5 MSPS, Low Power, CMOS                |       |  |  |  |  |  |  |

# TABLE OF CONTENTS Continued

| Section 4  | Digital-to-A | nalog Converters                                |  |  |  |  |

|------------|--------------|-------------------------------------------------|--|--|--|--|

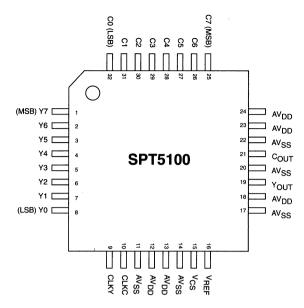

|            | SPT5100      | 8-Bit, 20 MWPS, Dual Channel Video 4-5          |  |  |  |  |

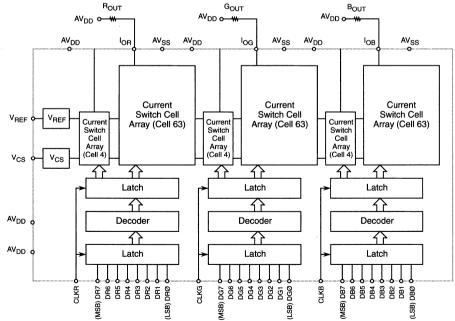

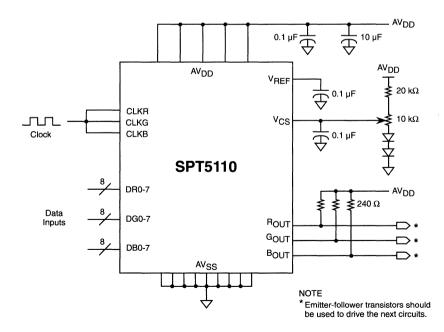

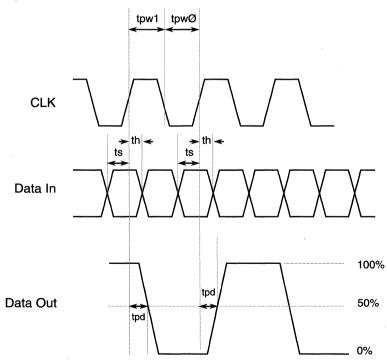

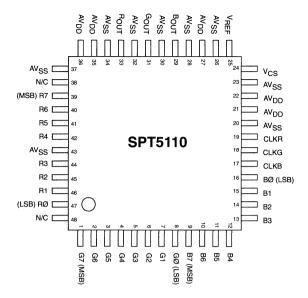

|            | SPT5110      | 8-Bit, 30 MWPS, Triple Channel Video 4-11       |  |  |  |  |

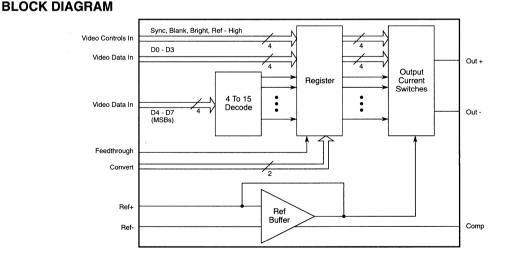

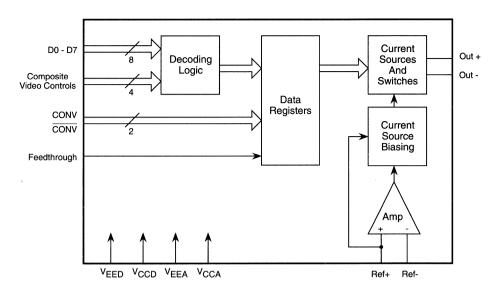

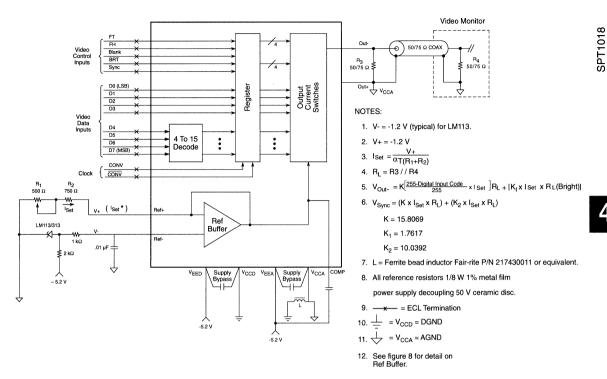

|            | SPT1018      | 8-Bit, 275/165 MWPS, Video4-17                  |  |  |  |  |

|            | SPT1019      | 8-Bit, 275/165 MWPS, Video, with Reference 4-29 |  |  |  |  |

|            | SPT5140      | 8-Bit, 400 MWPS, Video, with Reference 4-41     |  |  |  |  |

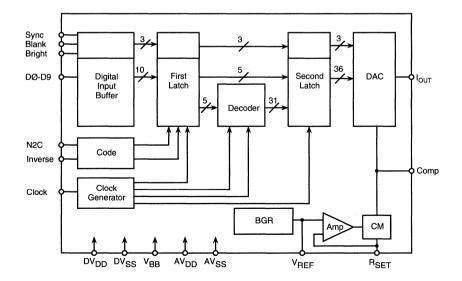

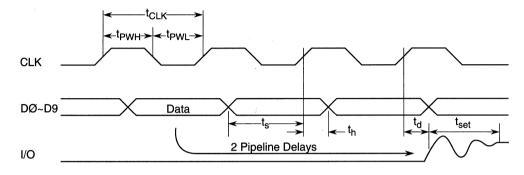

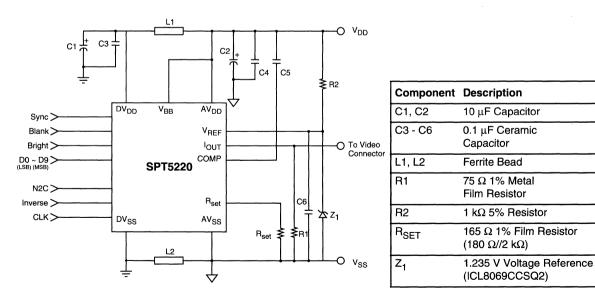

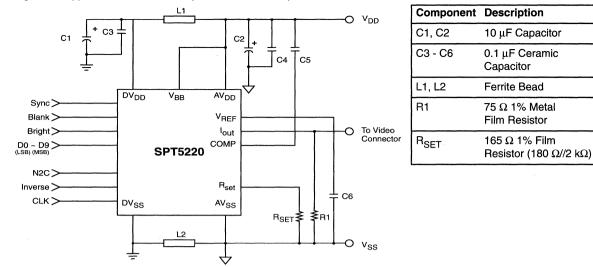

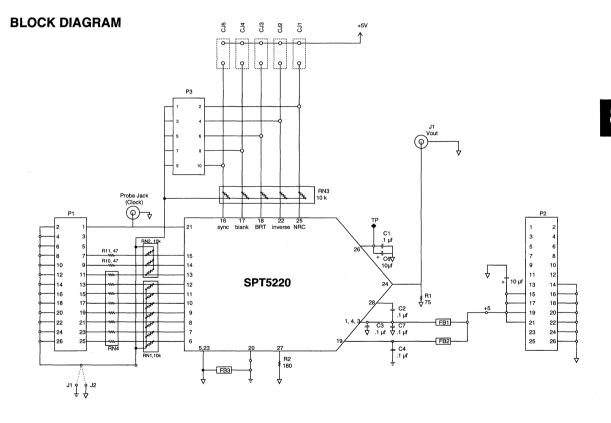

|            | SPT5220      | 10-Bit, 80 MWPS, Video4-53                      |  |  |  |  |

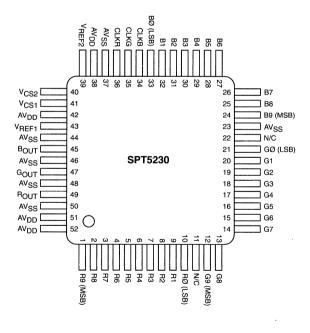

|            | SPT5230      | 10-Bit, 50 MWPS Triple Channel Video 4-61       |  |  |  |  |

|            | SPT9712      | 12-Bit, 100 MWPS ECL                            |  |  |  |  |

|            | SPT9713      | 12-Bit, 100 MWPS TTL                            |  |  |  |  |

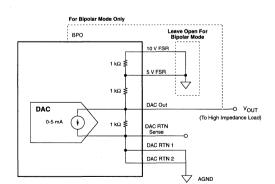

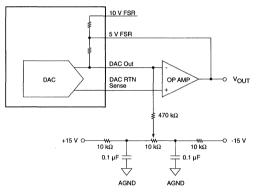

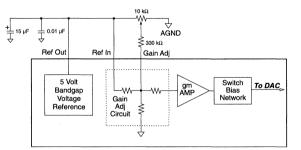

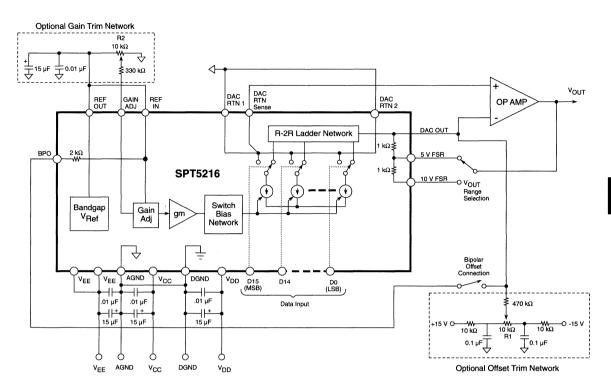

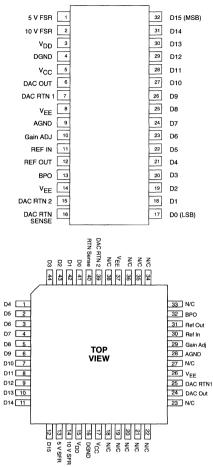

|            | SPT5216      | 16-Bit, Ultrahigh Speed4-77                     |  |  |  |  |

| Section 5  | Comparato    | rs                                              |  |  |  |  |

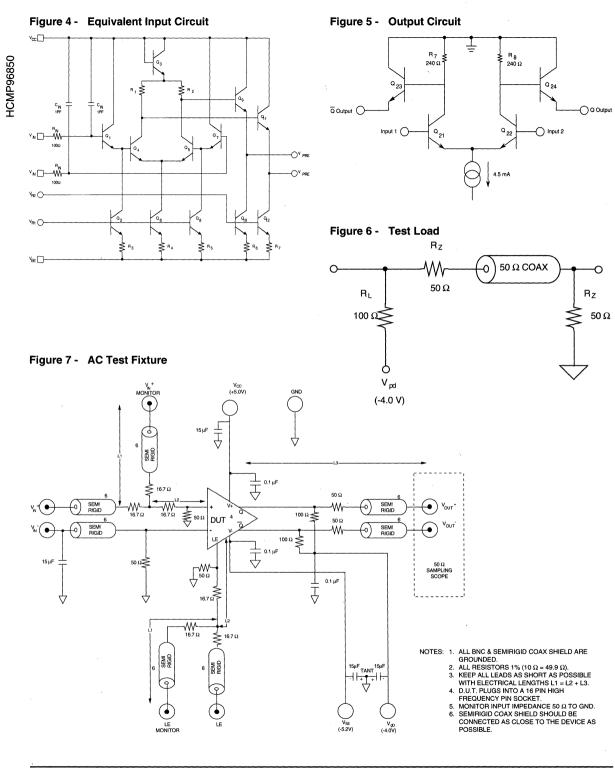

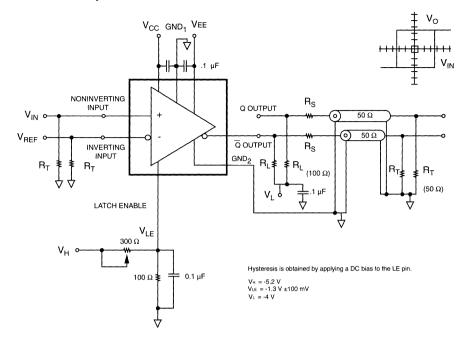

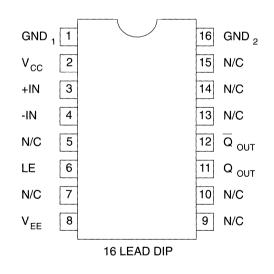

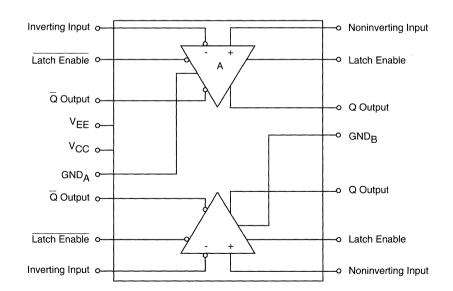

|            | HCMP96850    | High-Speed Single5-5                            |  |  |  |  |

|            | SPT9687      | High-Speed Dual5-13                             |  |  |  |  |

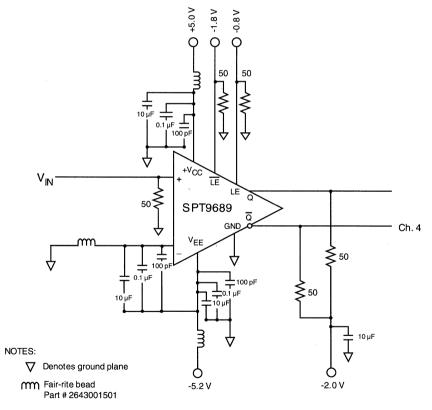

|            | SPT9689      | Subnanosecond Dual5-23                          |  |  |  |  |

|            | SPT9691      | Wide Input Voltage, JFET Input5-31              |  |  |  |  |

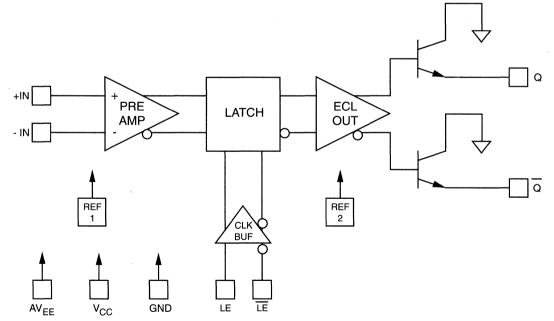

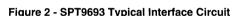

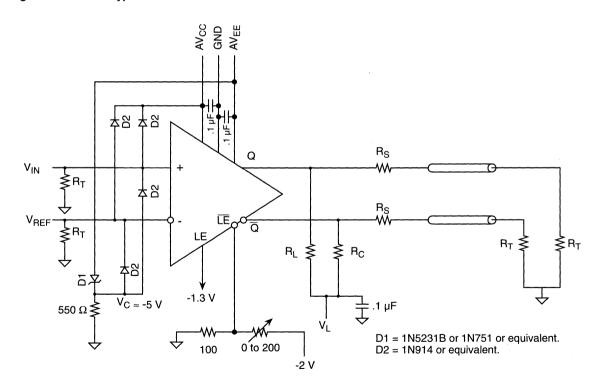

|            | SPT9693      | 1 ns, JFET Input5-41                            |  |  |  |  |

| Section 6  | Pin Drivers  |                                                 |  |  |  |  |

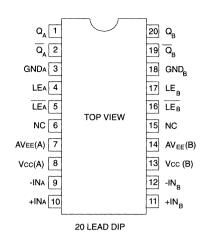

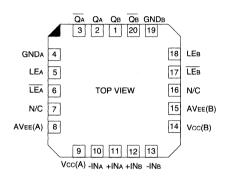

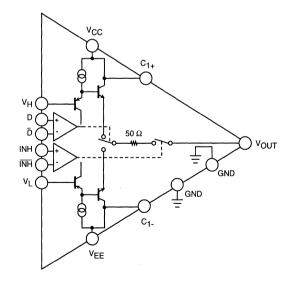

|            | SPT9500      | 200 MHz, Wide Output Swing6-3                   |  |  |  |  |

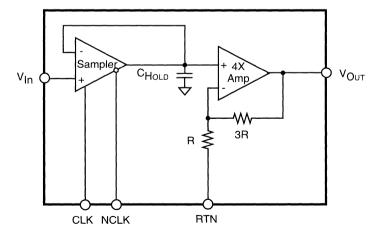

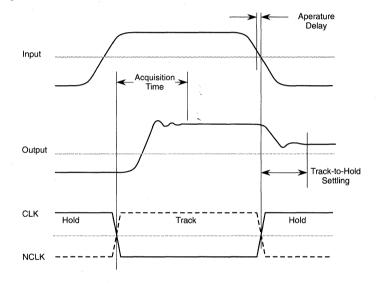

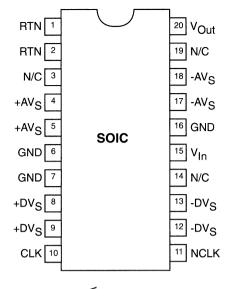

| Section 7  | Sample-and   | d-Hold Amplifiers                               |  |  |  |  |

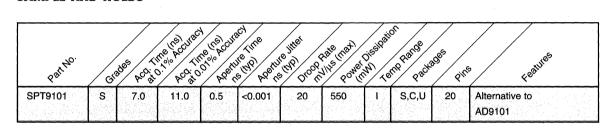

|            | SPT9101      | 125 MSPS Sampling Rate7-3                       |  |  |  |  |

| Section 8  | Evaluation   | Boards                                          |  |  |  |  |

| Section 9  | Application  | 9-3                                             |  |  |  |  |

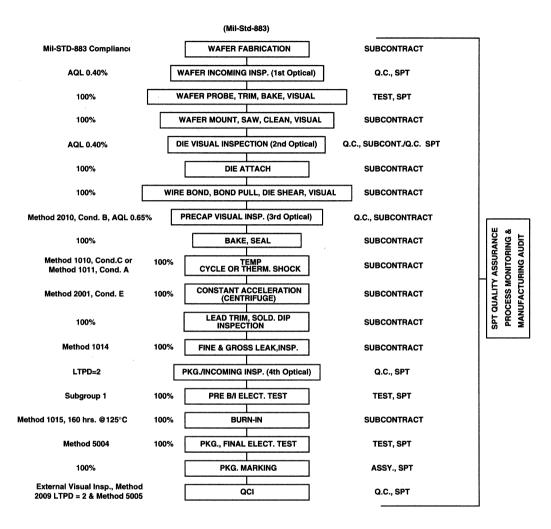

| Section 10 | Quality Ass  | surance                                         |  |  |  |  |

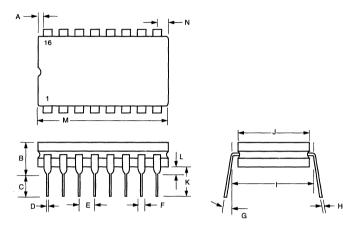

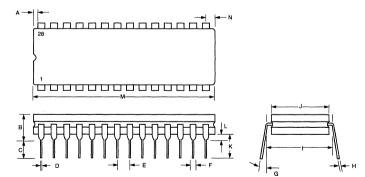

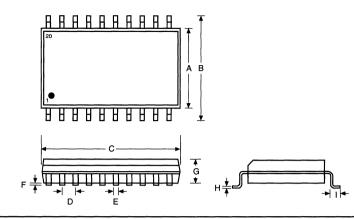

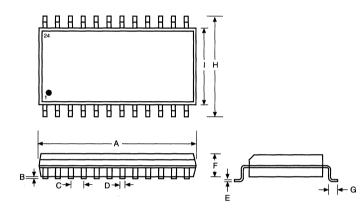

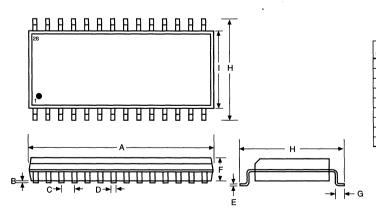

| Section 11 | Package O    | utlines                                         |  |  |  |  |

| Section 12 | Sales Offic  | Sales Offices                                   |  |  |  |  |

4755 Forge Road, Co. Springs, CO 80907 **SP** PH: (719) 528-2300; Fax: (719) 528-2370

1-2

# HIGH-SPEED A/D CONVERTERS

|         |     |       | Solution Bits)                   | xe                |                | /           |                                                                                                                 | /        |       |                                                    |

|---------|-----|-------|----------------------------------|-------------------|----------------|-------------|-----------------------------------------------------------------------------------------------------------------|----------|-------|----------------------------------------------------|

| 20.     | /   |       | ution de                         | Rat B             | ुहुषे/         | 13          | Hany ages                                                                                                       | · /      | /     | evels utes                                         |

| Pat No. | Gr2 | 00 Pe | Solution Bits<br>Sample<br>1,000 | Rate<br>FSI SNR U | Power<br>Power | Vatter Leur | Parkages                                                                                                        | Pins     | Our   | restutes                                           |

| SPT7610 | S   | 6     | 1,000                            | 36                | 2.75           | I           | Q,U                                                                                                             | 44       | *     | Wide input BW of 1.4 GHz                           |

| SPT1175 | А   | 8     | 20                               | 46                | 0.09           | С           | D,S,N,P,U                                                                                                       | 24,28    | N/A   | Single supply alternative                          |

|         | В   | 8     | 30                               | 44                | 0.09           |             |                                                                                                                 |          |       | to TMC1175 and CXD1175                             |

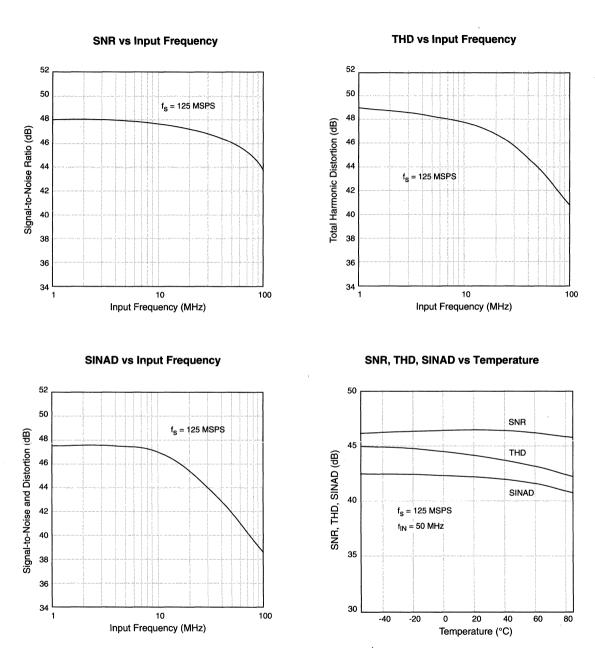

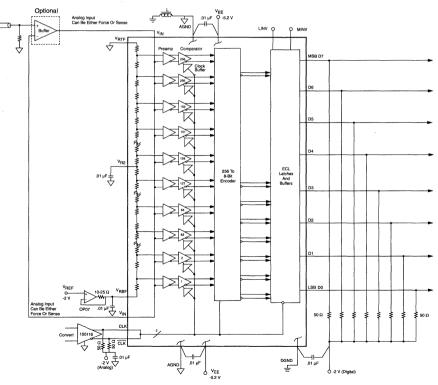

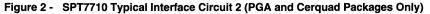

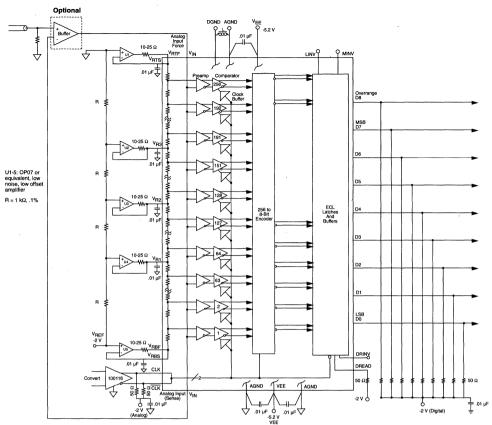

| SPT7710 | А   | 8     | 150                              | 48                | 2.2            | I,M         | J,G,Q,U                                                                                                         | 42,44,46 | /883  | Wide bandwidth                                     |

|         | В   | 8     | 150                              | 47                | 2.2            |             |                                                                                                                 |          |       | No sparkle codes                                   |

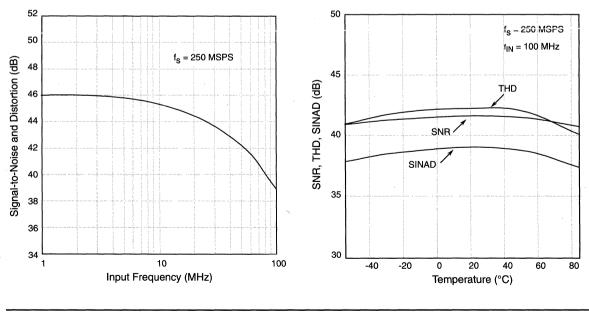

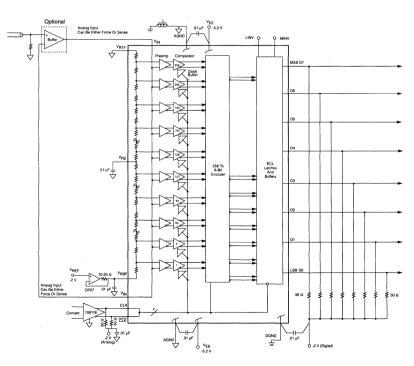

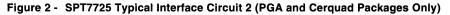

| SPT7725 | Α   | 8     | 300                              | 47                | 2.2            | I,M         | J,G,Q,U                                                                                                         | 42,44,46 | /883  | Data ready and overrange<br>outputs. Quarter point |

|         | В   | 8     | 300                              | 46                | 2.2            |             |                                                                                                                 |          |       | ladder taps.                                       |

| SPT7750 | А   | 8     | 500                              | 47                | 5.5            | 1           | G,K,U                                                                                                           | 68,80    | *     | Demuxed output. Gray<br>code output. Wide input    |

|         | В   | 8     | 500                              | 45                | 5.5            |             |                                                                                                                 |          |       | BW of 900 MHz.                                     |

| SPT7755 | А   | 8     | 750                              | 46                | 5.5            | 1           | G,K,U                                                                                                           | 68,80    | *     | Demuxed output. Gray<br>code output. Wide input    |

|         | В   | 8     | 750                              | 44                | 5.5            |             |                                                                                                                 |          |       | BW of 900 MHz.                                     |

| SPT7760 | Α   | 8     | 1,000                            | 42                | 5.5            | 1           | G,K,U                                                                                                           | 68,80    | *     | Demuxed output. Gray<br>code output. Wide input    |

|         | В   | 8     | 1,000                            | 40                | 5.5            |             |                                                                                                                 |          |       | BW of 900 MHz.                                     |

| SPT7810 | А   | 10    | 20                               | 60                | 1.3            | C,I         | J,N,U                                                                                                           | 28       | *     | On chip track-and-hold                             |

|         | В   | 10    | 20                               | 57                | 1.3            |             |                                                                                                                 |          |       | Monolithic                                         |

| SPT7814 | А   | 10    | 40                               | 57                | 1.3            | C,I         | J,N,U                                                                                                           | 28       | *     | On chip track-and-hold                             |

|         | В   | 10    | 40                               | 54                | 1.3            |             |                                                                                                                 |          |       | Monolithic                                         |

| SPT7820 | А   | 10    | 20                               | 60                | 1.0            | C,I,M       | J,C,S,N,U                                                                                                       | 28       | /883  | TTL output version of the                          |

|         | В   | 10    | 20                               | 57                | 1.0            |             |                                                                                                                 |          |       | SPT7810                                            |

| SPT7824 | Α   | 10    | 40                               | 57                | 1.0            | C,I,M       | J,C,S,N,U                                                                                                       | 28       | /883  | TTL output version of the                          |

|         | В   | 10    | 40                               | 54                | 1.0            |             | - 51                                                                                                            |          |       | SPT7814                                            |

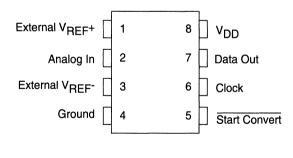

| SPT7830 | S   | 10    | 2.5                              | 57                | .07            | С           | S,U                                                                                                             | 8        | *     | Serial output                                      |

|         |     |       |                                  |                   |                |             |                                                                                                                 |          |       | 3.3 to 5.0 V Supply Range                          |

| SPT7835 | S   | 10    | 5                                | 59                | .07            | C,M         | D,N,S,T,U                                                                                                       | 28,32    | *     | On chip track-and-hold                             |

|         |     |       |                                  |                   |                |             |                                                                                                                 |          |       | Tri-state outputs                                  |

| SPT7840 | S   | 10    | 10                               | 58                | 0.1            | C,M         | D,N,S,T,U                                                                                                       | 28,32    | *     | On chip track-and-hold                             |

|         |     |       |                                  |                   |                |             |                                                                                                                 |          |       | Tri-state outputs                                  |

| SPT7850 | S   | 10    | 20                               | 56                | 0.14           | C,M         | D,N,S,T,U                                                                                                       | 28,32    | *     | On chip track-and-hold                             |

|         |     |       |                                  |                   |                |             |                                                                                                                 |          |       | Tri-state outputs                                  |

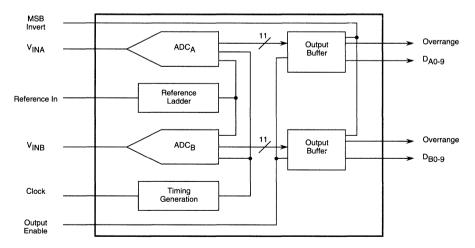

| SPT7852 | S   | 10    | 20                               | 56                | 0.17           | С           | T,U                                                                                                             | 44       | *     | Dual ADC                                           |

| SPT7855 | S   | 10    | 25                               | 58                | 0.14           | C,M         | D,N,S,T,U                                                                                                       | 28,32    | *     | On chip track-and-hold                             |

|         |     |       |                                  | 1.0               |                |             |                                                                                                                 |          |       | Tri-state outputs                                  |

| SPT7860 | S   | 10    | 40                               | 54                | 0.18           | C,M         | D,N,S,T,U                                                                                                       | 28,32    | *     | On chip track-and-hold                             |

|         |     |       |                                  |                   |                |             |                                                                                                                 |          |       | Tri-state outputs                                  |

| SPT7861 | S   | 10    | 40                               | 58                | 0.16           | С           | N,S,T,U                                                                                                         | 28,32    | . * . | Pin compatible with                                |

|         |     |       |                                  |                   |                |             | a seconda de la composición de la compo |          |       | SPT7860                                            |

| SPT7870 | S   | 10    | 100                              | 56                | 1.4            | С           | J,Q,U                                                                                                           | 32,44    | *     | Single-ended                                       |

|         |     |       |                                  |                   |                |             |                                                                                                                 |          |       | ECL outputs                                        |

\* Consult the factory for availability of /883 processed units.

1

#### Pesolution (Bits) Sampa Pate SHERE SH TempRange Quallevels Packages Features Part No. Grades Powervatts Pins \* С J,Q,U 32.44 Single ended SPT7871 S 10 100 56 1.3 TTL outputs s С J,U 32 \* SPT7910 12 10 67 1.4 Includes sample-and-hold on monolithic die \* SPT7912 S 12 30 66 1.4 С J.U 32 Includes sample-and-hold on monolithic die \* TTL output version of SPT7920 S 12 10 66 1.1 C,M J,Q,U 32.44 the SPT7910 \* 32,44 TTL output version of SPT7922 S 12 30 65 1.1 C.M J.Q.U the SPT7912 \* s 28 Includes sample-and-hold SPT7930 12 5 69 0.45 C,M J,S,U on monolithic CMOS die

#### HIGH-SPEED A/D CONVERTERS-Continued

#### **MEDIUM-SPEED A/D CONVERTERS**

| Pat N°.     | Gift | des pe | Solution Bits | Son Time | A FUISCAL | Phi <sup>C</sup> Temp | ande Patras | ss pins | Out  | d Leves Features                                                                            |  |

|-------------|------|--------|---------------|----------|-----------|-----------------------|-------------|---------|------|---------------------------------------------------------------------------------------------|--|

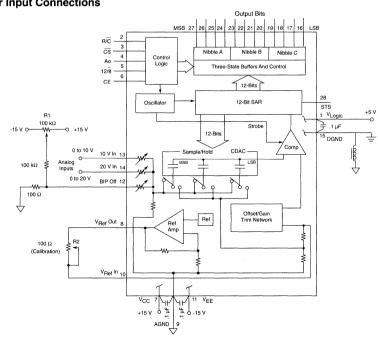

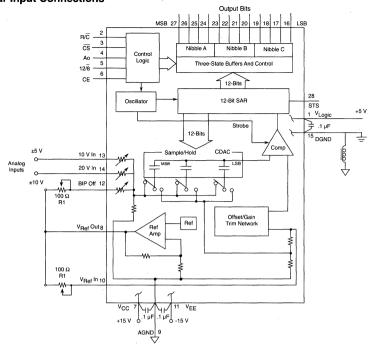

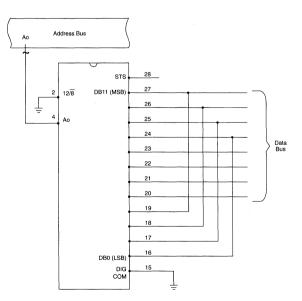

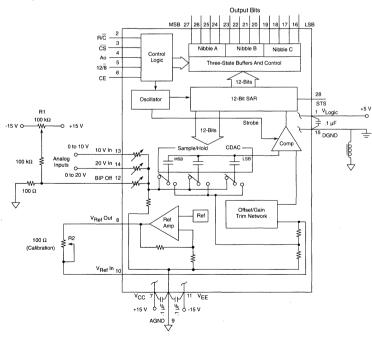

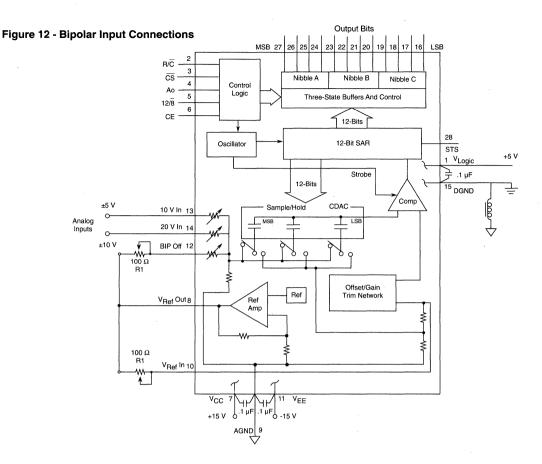

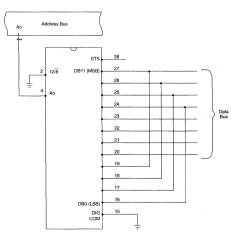

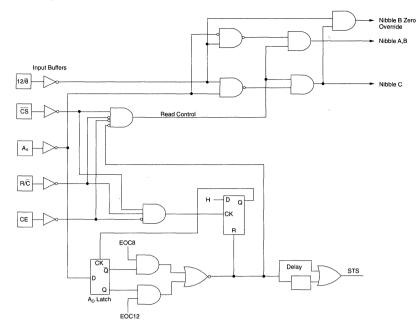

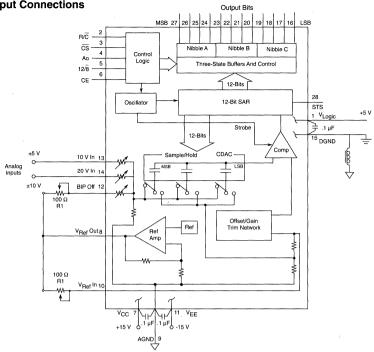

| HADC574Z    | Α    | 12     | 25            | 1/2      | 10        | C,I,M                 | J,D,C,U     | 28      | /883 | Input ranges 0-10, 0-20, ±5, and ±10. Low power. Alter-                                     |  |

|             | В    | 12     | 25            | 1/2      | 27        |                       |             |         |      | natives for HI574 & AD574.<br>DESC drawing available.                                       |  |

|             | С    | 12     | 25            | 1 - A    | 45        |                       |             |         |      |                                                                                             |  |

| HADC674Z    | Α    | 12     | 15            | . 1/2    | 10        | C,I,M                 | J,D,C,U     | 28      | /883 | /883 Input ranges 0-10, 0-20, ±5,<br>and ±10. Low power. HI674<br>alternative. DESC drawing |  |

|             | в    | 12     | 15            | 1/2      | 27        |                       |             |         |      |                                                                                             |  |

|             | С    | 12     | 15            | 1        | 45        |                       |             |         |      | available.                                                                                  |  |

| SPT774      | A    | 12     | 8             | 1/2      | 10        | C, I, M               | J,D,C,U     | 28      | /883 | Input ranges 0-10, 0-20, ±5,                                                                |  |

| 전망 가지 않는 것이 | В    | 12     | 8             | 1/2      | 27        |                       |             | 1       |      | and ±10. Low power.<br>Alternative to the HI774 and                                         |  |

|             | С    | 12     | 8             | 1        | 45        |                       |             |         |      | Alternative to the H1774 and AD1674.                                                        |  |

#### **D/A CONVERTERS - GENERAL PURPOSE**

| Pat No. | Gr | ades pe | solution (Bits)<br>Settin | o time (no) | 5 <sup>B)</sup> Output | TYPE | Partie Packages | Pitts | Que | Lieves Fostures                                      |

|---------|----|---------|---------------------------|-------------|------------------------|------|-----------------|-------|-----|------------------------------------------------------|

| SPT9712 | S  | 12      | 8                         | 1           | I,V                    |      | N,P,U           | 28    | *   | ECL input compatible                                 |

| SPT9713 | S  | 12      | 8                         | 1           | I,V                    | I    | N,P,U           | 28    | *   | TTL input compatible                                 |

| SPT5216 | В  | 16      | 150                       | 2/6***      | I,V                    | С    | J,Q,U           | 32,44 | *   | Parallel input reference,<br>Output range: +10 to 0, |

|         | C  | 16      | 150                       | 2/8***      | I,V                    |      |                 |       |     | +5 to 0, ±5 or ±2.5 V                                |

\* Consult the factory for availability of /883 processed units.

\*\* Commercial temperature grades.

\*\*\* Over temperature.

1-4

#### **D/A CONVERTERS - VIDEO**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |    | <del></del> |     |     |     |     |      |      |                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|-------------|-----|-----|-----|-----|------|------|------------------------------|

| Partino. Crase beaming the state of the stat |   |    |             |     |     |     |     |      |      |                              |

| SPT5100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S | 8  | -           | 1/2 | 20  | С   | Т   | 32   | N/A  | Dual DAC                     |

| SPT5110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S | 8  | -           | 1/2 | 30  | С   | Т   | 48   | N/A  | Triple DAC                   |

| SPT1018                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Α | 8  | 10          | 1/2 | 275 | I/M | N,U | 24   | /883 | Video control alternative    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | В | 8  | 10          | 1/2 | 165 | Į   |     | Į į  |      | to the TDC1018               |

| SPT1019                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | А | 8  | 10          | 1/2 | 275 | I/M | N,U | 24   | /883 | Video control with reference |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | В | 8  | 10          | 1/2 | 165 | 1   |     |      |      |                              |

| SPT5140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S | 8  | 10          | 1/2 | 400 | I/M | N,U | - 24 | /883 | Ref, video control           |

| SPT5220                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | s | 10 | -           | 1   | 80  | С   | N   | 28   | N/A  | Single +5 V supply           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |    |             |     |     | l   |     |      |      | Video controls               |

| SPT5230                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S | 10 | -           | 1   | 50  | С   | Т   | 52   | N/A  | Triple DAC                   |

#### **COMPARATORS**

| Patho. Gade thits bid the north Action to the base bits to the testing to testing to the testing |        |                    |            |                        |            |            |   |             |       |                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------|------------|------------------------|------------|------------|---|-------------|-------|-------------------------------------------------|

| HCMP96850                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | S      | 1.76/1.76          | 2.4        | ±2.5                   | ±3.0       | 90         | I | D,U         | 16    | Symmetrical TR/TF.<br>Alternative to the AD9685 |

| SPT9687                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S      | 1.2/1.2            | 2.0        | ±2.5                   | ±3.0       | 185        | 1 | N,D,C,P,J,U | 16,20 | High performance<br>Alternative for the AD96687 |

| SPT9689                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A<br>B | .18/.08<br>.18/.08 | .65<br>.65 | -2.5/+4.0<br>-2.5/+4.0 | ±10<br>±25 | 350<br>350 | 1 | J,C,P,U     | 16,20 | 900 MHz bandwidth<br>Differential latch control |

| SPT9691                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S      | 0.4/0.4            | 2.2        | -4/+8.0                | ±25        | 700        | С | J,C,P,N,U   | 20    | JFET inputs. Constant<br>propagation delays     |

| SPT9693                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S      | 0.45/0.45          | 1.25       | -3/+8.0                | ±25        | 430        | С | J,C,P,U     | 20    | JFET inputs. Constant propagation delays        |

\* Consult the factory for availability of /883 processed units.

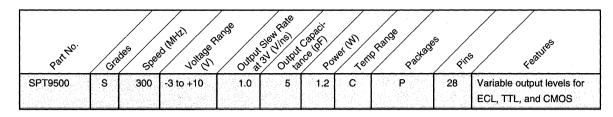

#### **PIN DRIVERS**

#### SAMPLE-AND-HOLDS

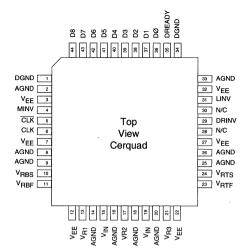

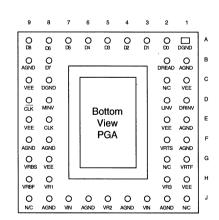

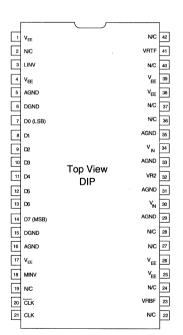

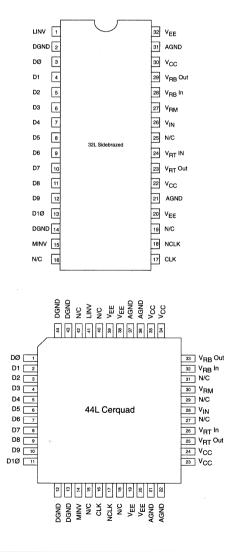

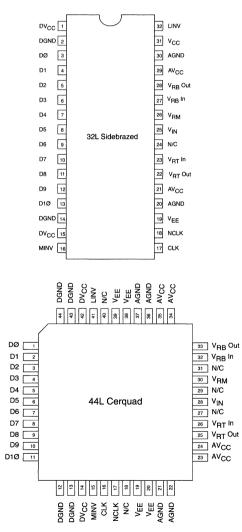

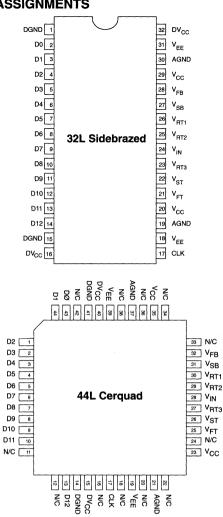

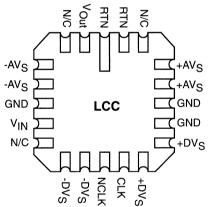

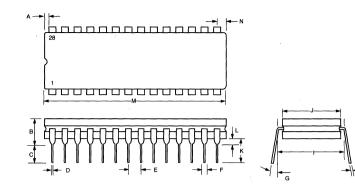

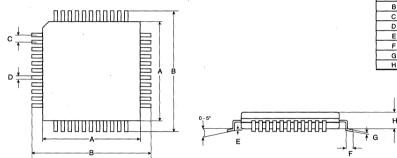

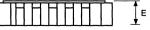

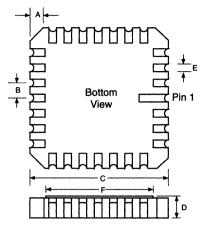

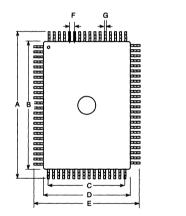

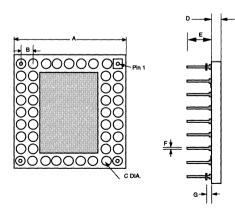

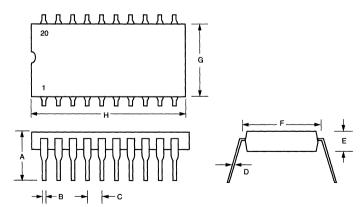

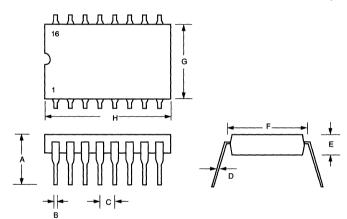

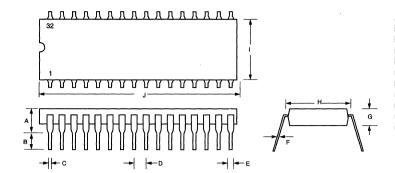

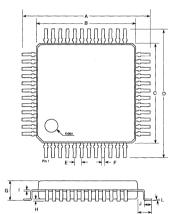

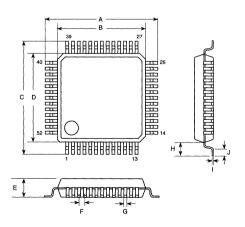

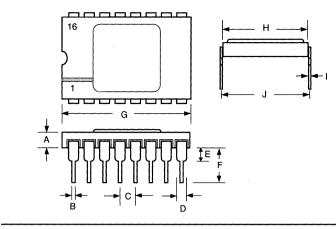

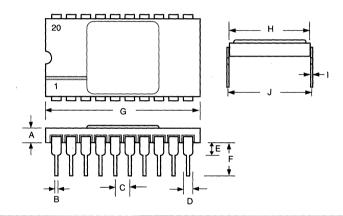

#### Package Type Key

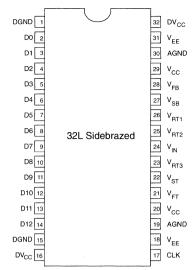

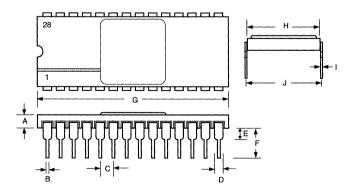

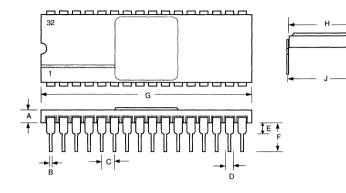

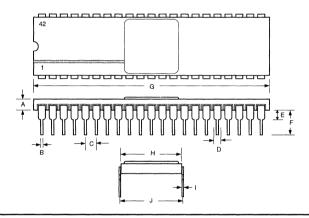

- J Ceramic Sidebrazed DIP

- D Cerdip

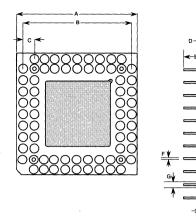

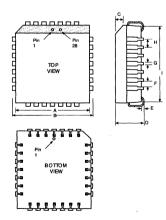

- C Leadless Chip Carrier (LCC)

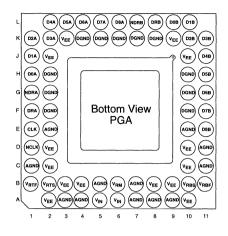

- G Pin Grid Array

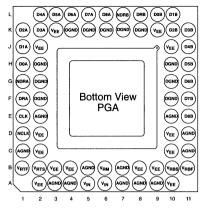

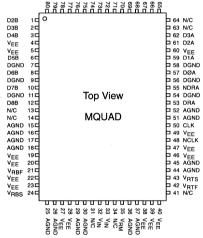

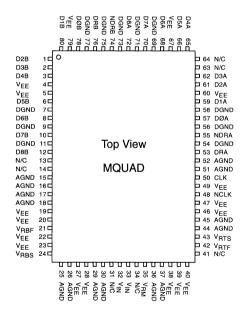

- K MQuad

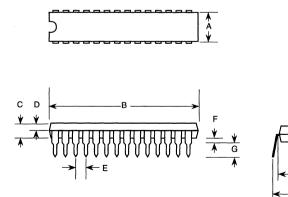

- N Plastic Dip

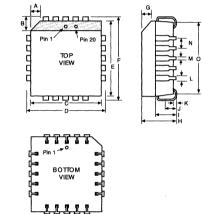

- P Plastic Leaded Chip Carrier (PLCC)

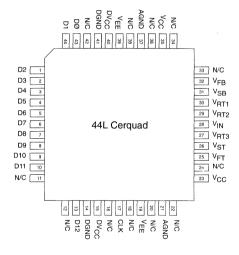

- Q Cerquad

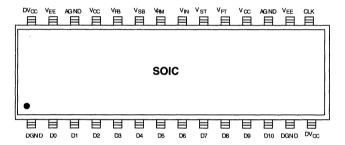

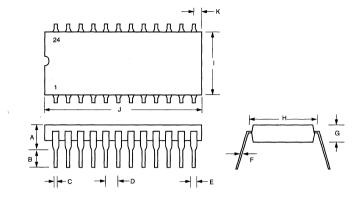

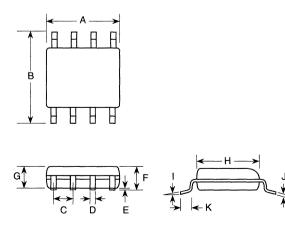

- S Small Outline Package (SOIC)

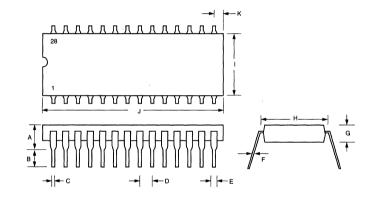

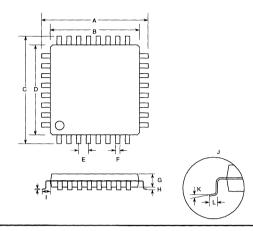

- T Quad Flat pack or Thin Quad Flat Pack

- U Die

#### **Temperature Range Key**

- C Commercial (0 to +70 °C)

- I Industrial (-25 to +85 °C)

- M Military (-55 to +125 °C)

#### Grades Key

- A Highest

- C Lowest

- S Single Grade

# **PRODUCT CROSS REFERENCE GUIDE** (INDUSTRIAL SPT EQUIVALENT)

| ANALOG    |              |                   | BURR          |              |                     |

|-----------|--------------|-------------------|---------------|--------------|---------------------|

| DEVICES   | SPT          | DESCRIPTION       | BROWN         | SPT          | DESCRIPTION         |

| AD574AJD  | HADC574ZCCD  | 12-BIT ADC        | ADC774JH      | SPT774CCJ    | 12-BIT ADC          |

| AD574AKD  | HADC574ZBCD  | 12-BIT ADC        | ADC774KH      | SPT774BCJ    | 12-BIT ADC          |

| AD574ALD  | HADC574ZACD  | 12-BIT ADC        | ADC774SH      | SPT774CMJ    | 12-BIT ADC          |

| AD574ASD  | HADC574ZCMD  | 12-BIT ADC        | ADC774TH      | SPT774BMJ    | 12-BIT ADC          |

| AD574ATD  | HADC574ZBMD  | 12-BIT ADC        |               |              | DEGODIDEION         |

| AD574AUD  | HADC574ZAMD  | 12-BIT ADC        | HARRIS        | SPT          | DESCRIPTION         |

| AD674AJD  | HADC674ZCCD  | 12-BIT ADC        | HI1-574AJD-5  | HADC574ZCCJ  | 12-BIT ADC          |

| AD674AKD  | HADC674ZBCD  | 12-BIT ADC        | HI1-574AKD-5  | HADC574ZBCJ  | 12-BIT ADC          |

| AD674ALD  | HADC674ZACD  | 12-BIT ADC        | HI1-574ALD-5  | HADC574ZACJ  | 12-BIT ADC          |

| AD674ASD  | HADC674ZCMD  | 12-BIT ADC        | HI1-574ASD-2  | HADC574ZCMJ  | 12-BIT ADC          |

| AD674ATD  | HADC674ZBMD  | 12-BIT ADC        | HI1-574ATD-2  | HADC574ZBMJ  | 12-BIT ADC          |

| AD674AUD  | HADC674ZAMD  | 12-BIT ADC        | HI1-574AUD-2  | HADC574ZAMJ  | 12-BIT ADC          |

| AD1674JN  | SPT774CCD    | 12-BIT ADC        | HI1-674AJD-5  | HADC674ZCCJ  | 12-BIT ADC          |

| AD1674KN  | SPT774BCD    | 12-BIT ADC        | HI1-674AKD-5  | HADC674ZBCJ  | 12-BIT ADC          |

| AD1674AD  | SPT774CIJ    | 12-BIT ADC        | HI1-674ALD-5  | HADC674ZACJ  | 12-BIT ADC          |

| AD1674BD  | SPT774BIJ    | 12-BIT ADC        | HI1-674ASD-2  | HADC674ZCMJ  | 12-BIT ADC          |

| AD1674TD  | SPT774BMJ    | 12-BIT ADC        | HI1-674ATD-2  | HADC674ZBMJ  | 12-BIT ADC          |

| AD9712    | SPT9712      | 12-BIT DAC        |               |              | 12-BIT ADC          |

| AD9713    | SPT9713      | 12-BIT DAC        | HI1-674AUD-21 | HADC674ZAMJ  | 12-DIT ADC          |

| AD9101    | SPT9101      | 12-BIT THA        | HI1-774J-5    | SPT774CCJ    | 12-BIT ADC          |

| AD96685B  | HCMP96850SID | SINGLE COMPARATOR | HI1-774K-5    | SPT774BCJ    | 12-BIT ADC          |

| AD96687B  | SPT9687      | DUAL COMPARATOR   | HI1-774S-2    | SPT774CMJ    | 12-BIT ADC          |

| BURR      |              |                   | HI1-774T-2    | SPT774BMJ    | 12-BIT ADC          |

| BROWN     | SPT          | DESCRIPTION       | HI-1175       | SPT1175      | 8-BIT, 20 MSPS ADC  |

| ADC574AJH | HADC574ZCCD  | 12-BIT ADC        | MICRO         |              |                     |