## STARTECH An EXAR Company

## Component Data

## Catalog

Printed August 7, 1995

STARTECH Semiconductor Inc. 1219 BORDEAUX Dr. SUNNYVALE, CA 94089 TEL (408) 745-0801 FAX (408) 745-1267 FAX (408) 745-0844

#### SALES:

TEL (408) 434-6400 FAX (408) 745-1269 FAX (408) 745-6243

EXAR Corporation

2222 QUME DR. P.O. BOX 49007 SAN JOSE, CA 95161-9007 TEL (408) 434-6400 FAX (408) 943-8245 No part of this document may be copied or reproduced in any form or by means without the prior written consent of STARTECH Semiconductor Inc. The information in this document is subject to change without notice. STARTECH Semiconductor Inc. assumes no responsibility for any errors that may appear in this document and makes no commitment to update or to keep current the information contained in this document. STARTECH Semiconductor Inc. makes no warranty (express, statutory, implied, or by description) regarding the information set forth herein or regarding the freedom of the described device from patent infringement. STARTECH Semiconductor Inc. makes no warranty of merchantability or fitness for any purpose.

STARTECH Semiconductor Inc.'s products are not authorized for use as critical components in the life support devices or systems without the express written approval of the president of STARTECH Semiconductor Inc..

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to effect its safety or effectiveness.

286/386/486 is a trademark of Intel Corporation.

IBM PC/XT/AT, PS/2 is a trademark of International Business Machines Corporation.

WD is a trademark of Western Digital Corporation.

NS, INS, DS is a trademark of National Semiconductor Corporation.

VL is a trademark of VLSI Technologies Corporation.

CENTRONICS is a trademark of Centronics Data Computer Corporation.

XR is a trademark of Exar Corporation.

TL is trademark of Texas Instrument, Inc.

MC is a trademark of Motorola Semiconductor.

ICS is a trademark of Integrated Circuit Systems, Inc.

AV is a trademark of Avasem Corporation.

SSI is a trademark of Silicon Systems Inc.

MK is a trademark of MicroClock Inc.

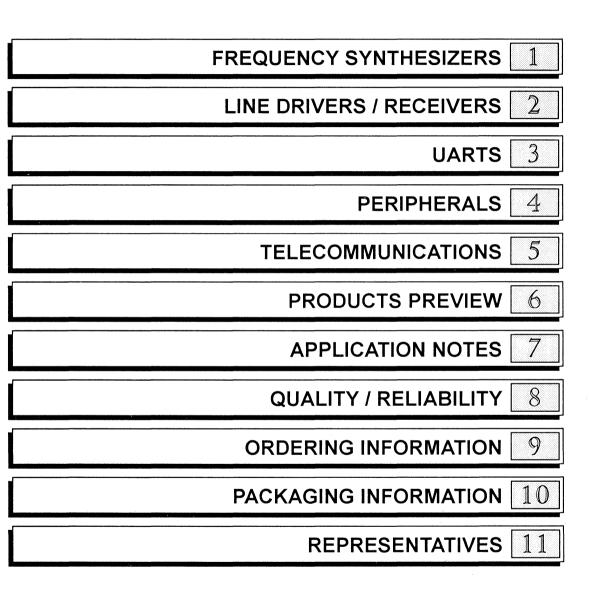

### Contents

| FREQUENCY SYNTHESIZERS                |       |

|---------------------------------------|-------|

| ST49C001                              | 1-3   |

| ST49C101                              | 1-9   |

| ST49C102                              | 1-9   |

| ST49C103                              |       |

| ST49C104                              | 1-17  |

| ST49C106                              |       |

| ST49C107                              |       |

| ST49C154                              |       |

| ST49C155                              |       |

| ST49C158                              |       |

| ST49C214                              |       |

| ST49C418                              |       |

|                                       |       |

| DIFFERENTIAL LINE DRIVERS             |       |

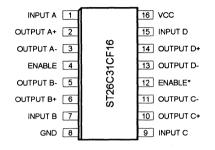

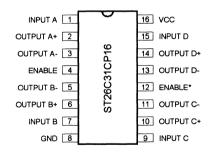

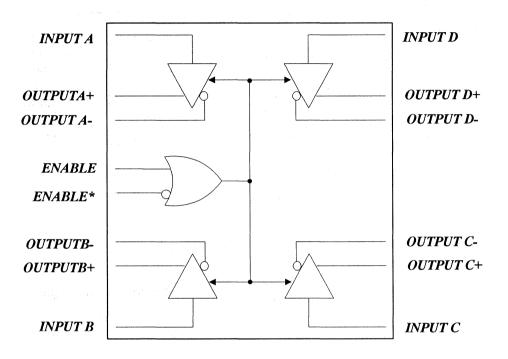

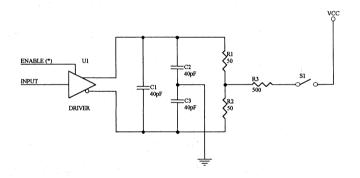

| ST26C31                               | 2-3   |

| ST34C87                               |       |

|                                       |       |

| DIFFERENTIAL LINE RECEIVERS           |       |

| ST26C32                               | 2-9   |

| ST34C86                               |       |

|                                       |       |

| DIFFERENTIAL LINE DRIVERS / RECEIVERS |       |

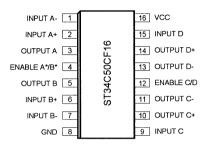

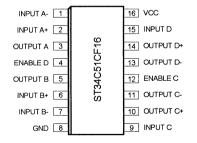

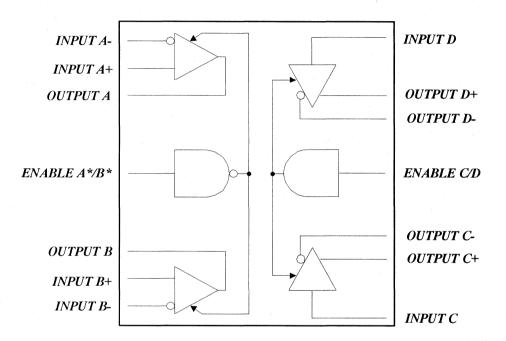

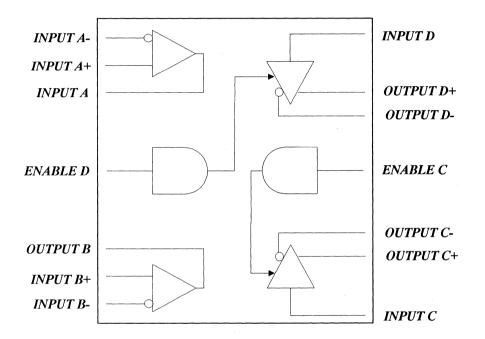

| ST34C50                               | 2-23  |

| ST34C51                               |       |

| ST31C32                               |       |

|                                       |       |

| UARTS                                 |       |

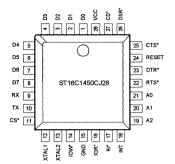

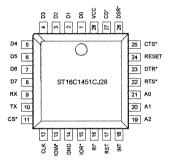

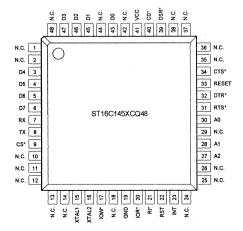

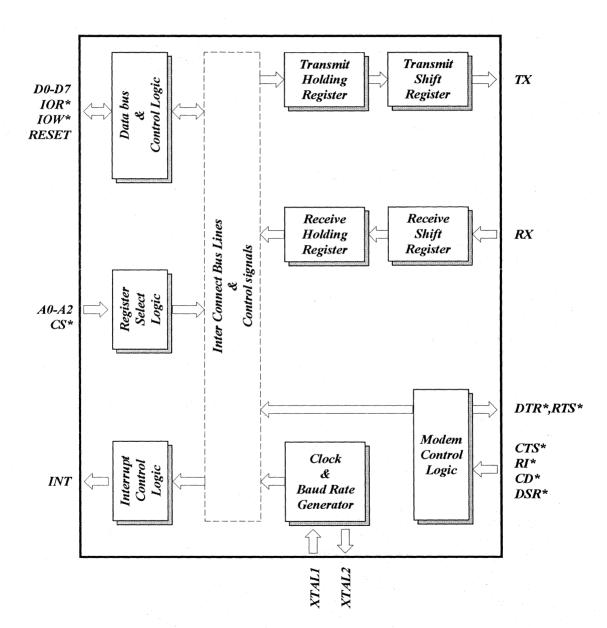

| ST16C1450                             | 3-3   |

| ST16C1451                             |       |

| ST16C2450                             |       |

| ST16C450                              |       |

| ST16C454                              |       |

| ST68C454                              |       |

| 01000404                              |       |

| UARTS WITH FIFO                       |       |

| ST16C1550                             | 3-03  |

| ST16C1551                             |       |

| ST16C1552                             |       |

| ST16C2550                             |       |

|                                       |       |

| ST16C2552                             |       |

|                                       |       |

| ST16C554                              |       |

| ST16C554E                             |       |

| ST16C650                              |       |

| ST16C654                              |       |

| ST68C554                              | 3-209 |

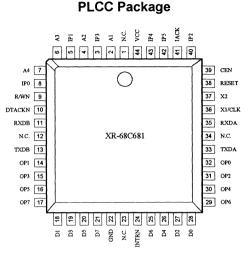

| XR68C681                              |                                       | 3-305 |

|---------------------------------------|---------------------------------------|-------|

| XR82C684                              |                                       | 3-307 |

| XR88C681                              |                                       | 3-305 |

|                                       |                                       |       |

| UARTS WITH PRINTER                    |                                       |       |

|                                       |                                       | 2 200 |

|                                       |                                       |       |

|                                       |                                       |       |

|                                       |                                       |       |

| ST16C553                              |                                       | 3-363 |

| PARALLEL I/O WITH FIFO                |                                       |       |

|                                       |                                       |       |

|                                       |                                       |       |

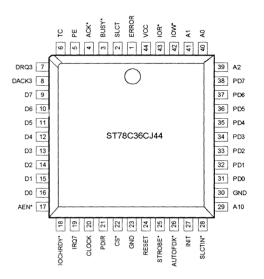

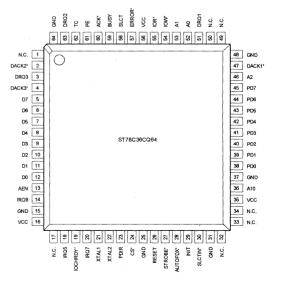

| ST78C36                               |                                       | 4-49  |

| IDE INTERFACE                         |                                       |       |

|                                       |                                       | 4.55  |

| 5184072                               |                                       | 4-55  |

|                                       |                                       |       |

|                                       |                                       | 4 40  |

| 5164001                               |                                       | 4-49  |

| DTMF RECEIVER                         |                                       |       |

|                                       |                                       | 5.3   |

| 51000070                              |                                       | 5-5   |

| SUPER I/O                             |                                       |       |

|                                       |                                       |       |

| ST56CXXX                              |                                       | 6-3   |

| · · · · · · · · · · · · · · · · · · · |                                       |       |

| APPLICATION NOTES                     |                                       |       |

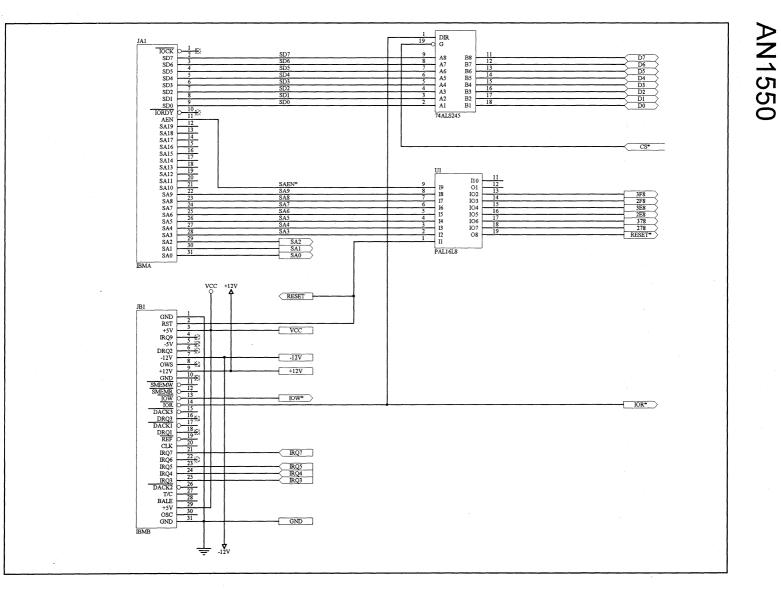

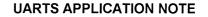

| AN1450/1550                           |                                       | 7-17  |

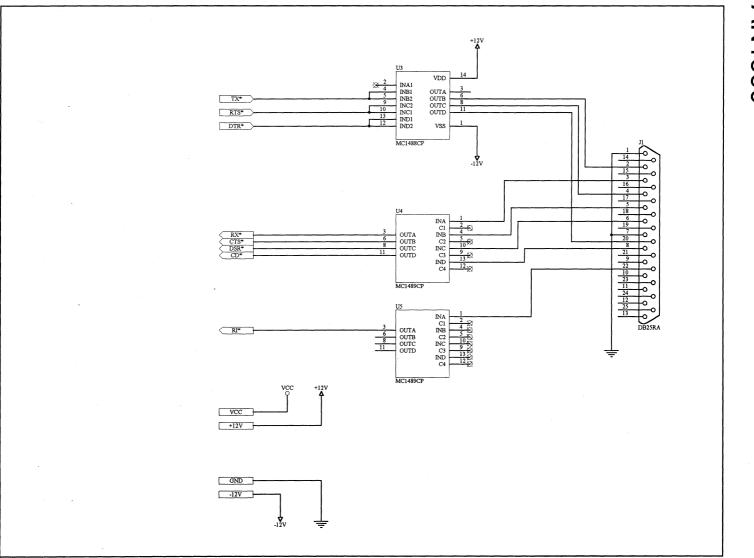

| AN2450/2550                           | · · · · · · · · · · · · · · · · · · · | 7-21  |

| AN2552                                |                                       | 7-25  |

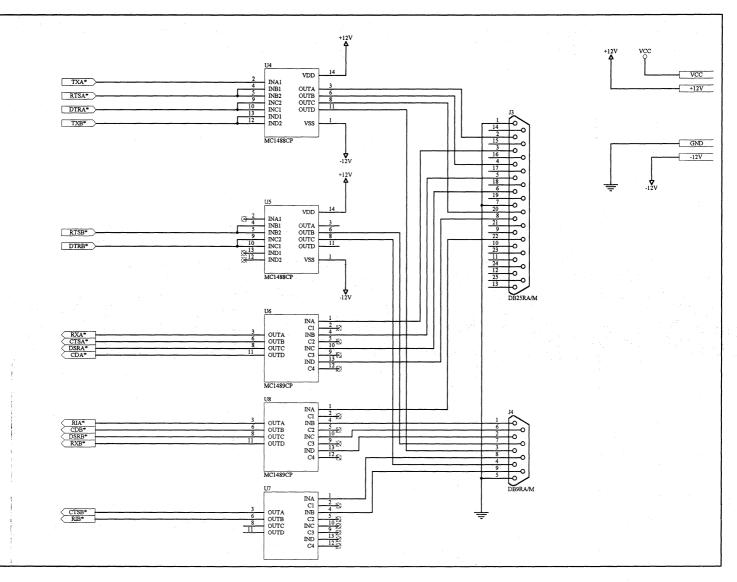

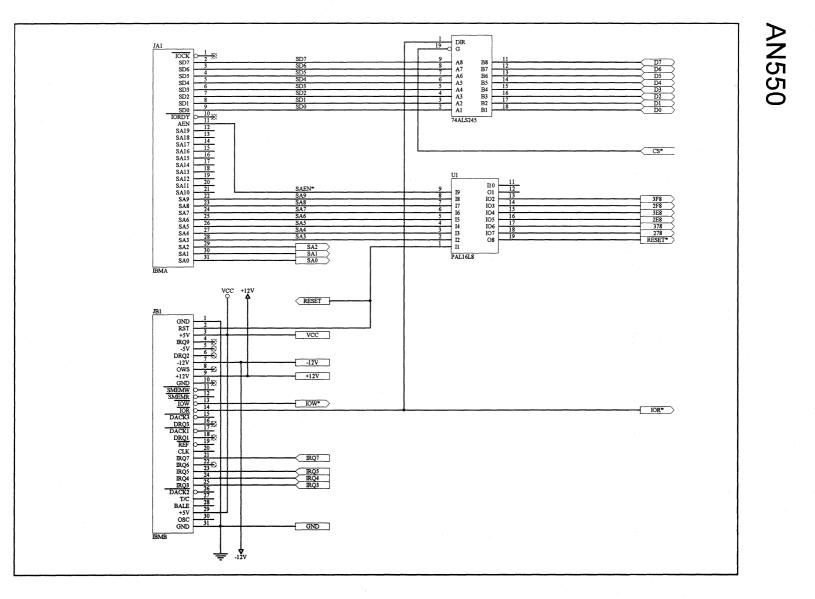

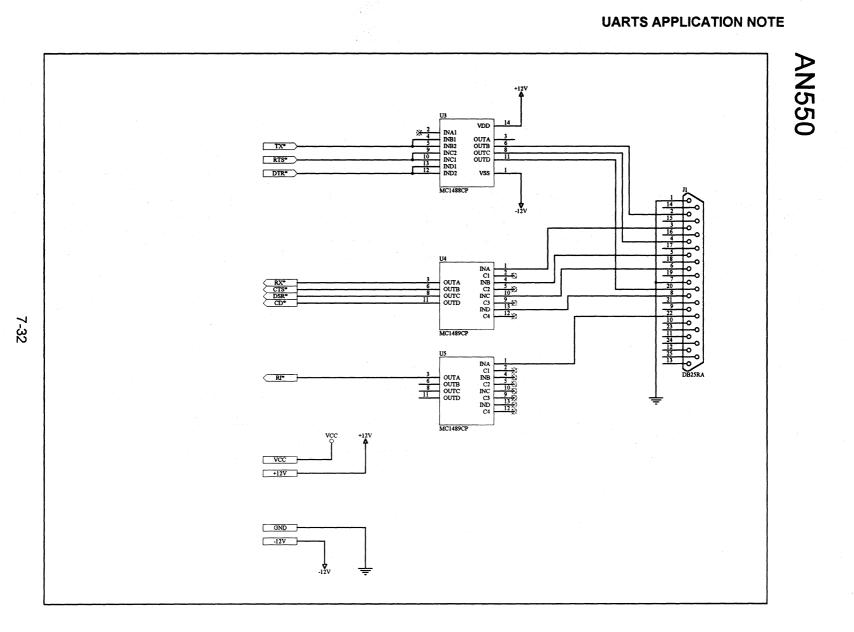

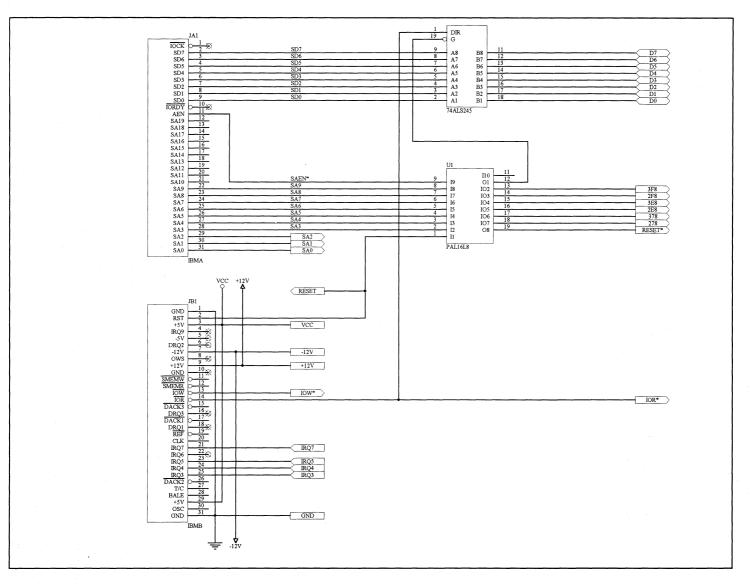

| AN450/550                             |                                       | 7-29  |

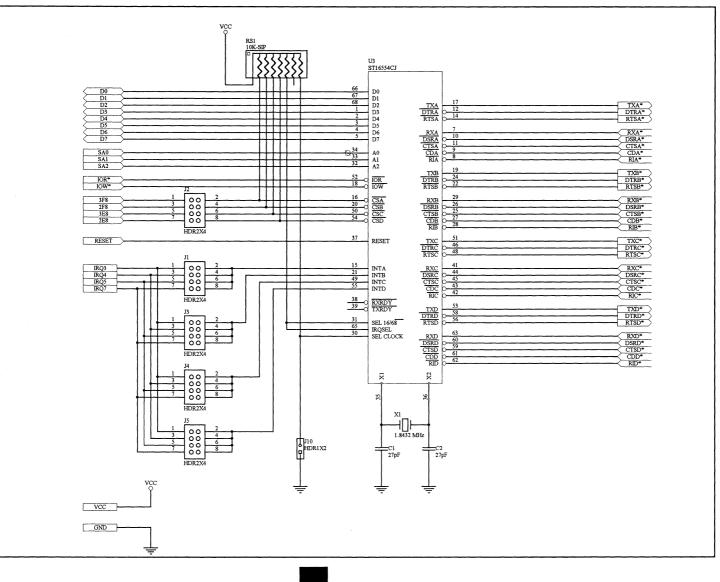

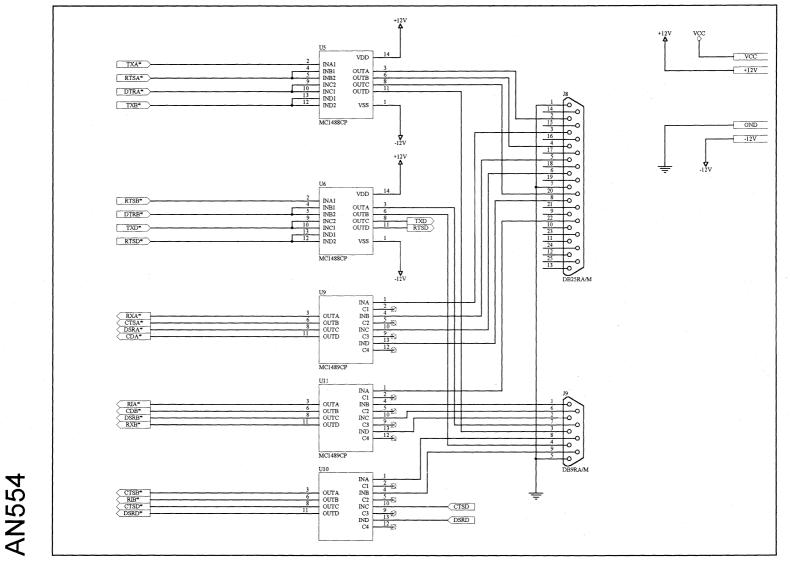

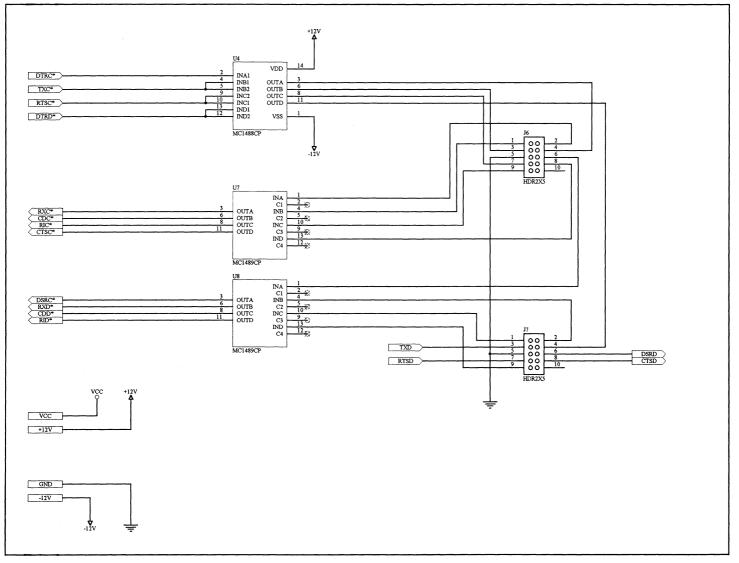

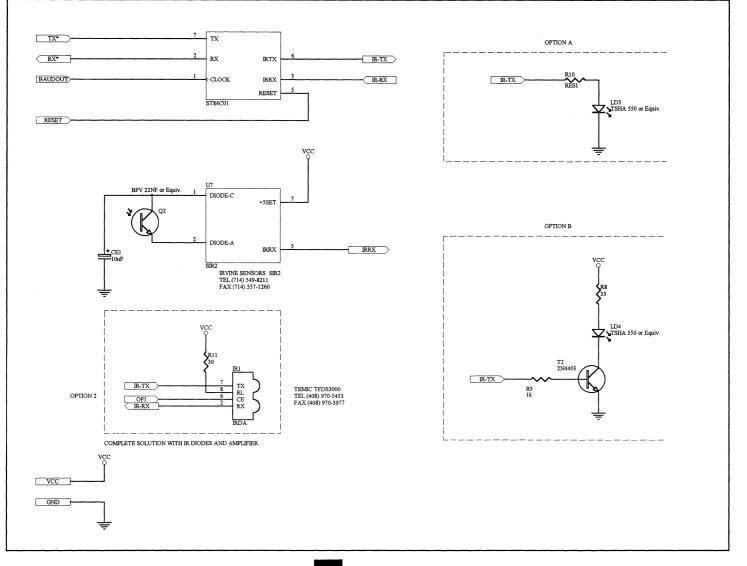

| AN454/554/654                         |                                       | 7-33  |

|                                       |                                       |       |

|                                       |                                       |       |

| QUALITY INFORMATION                   |                                       | 8-3   |

|                                       |                                       |       |

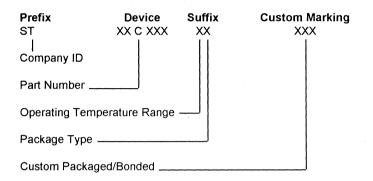

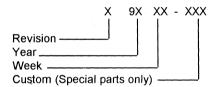

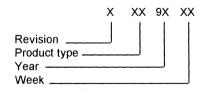

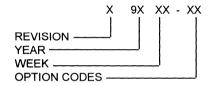

| ORDERING INFORMATION                  |                                       | 9-3   |

|                                       |                                       |       |

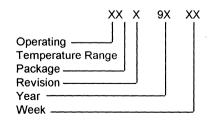

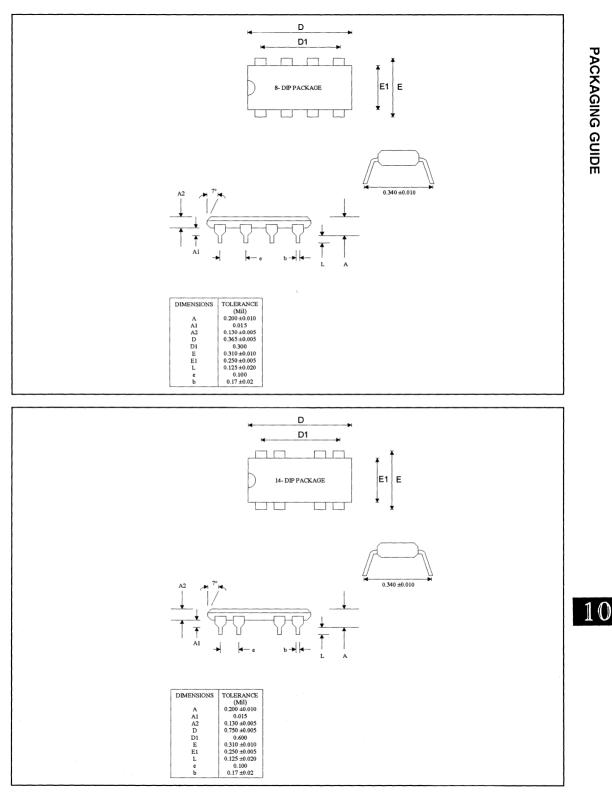

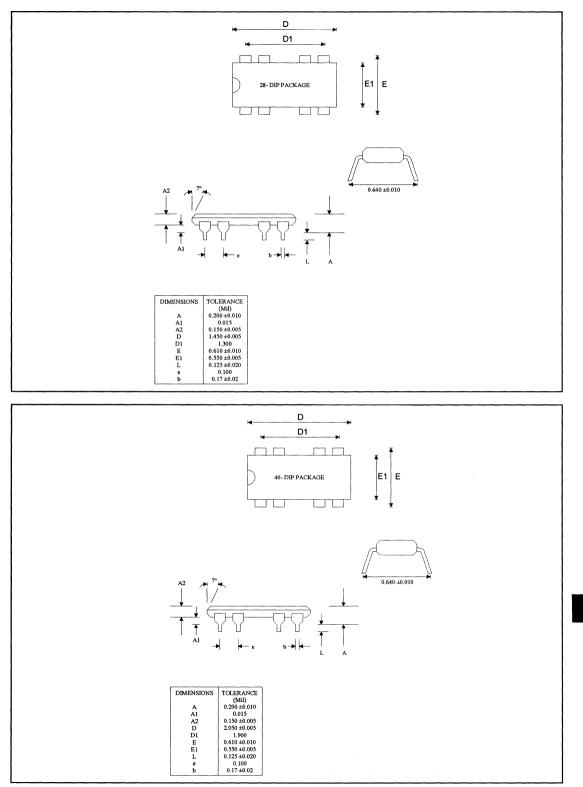

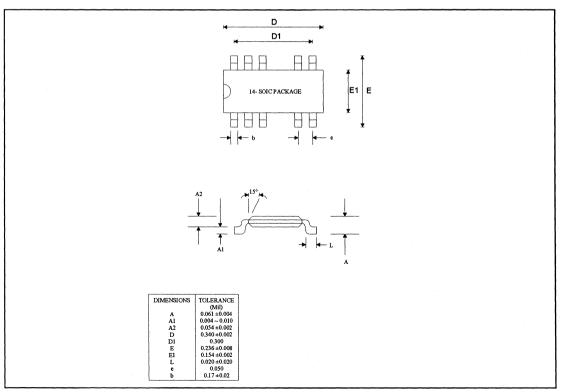

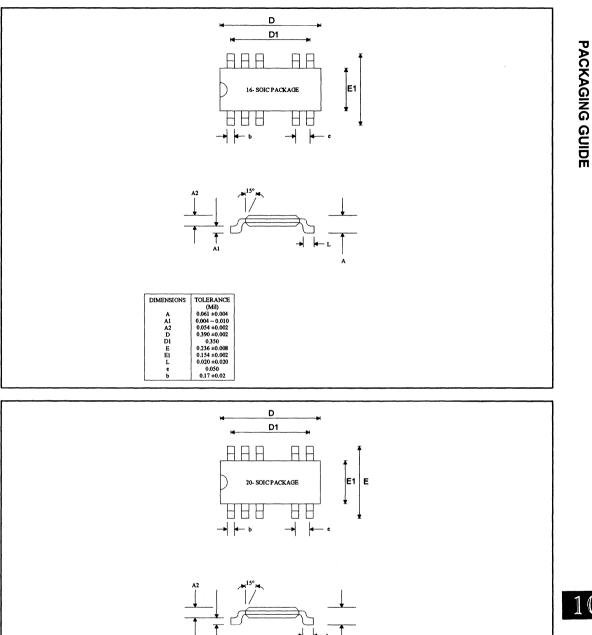

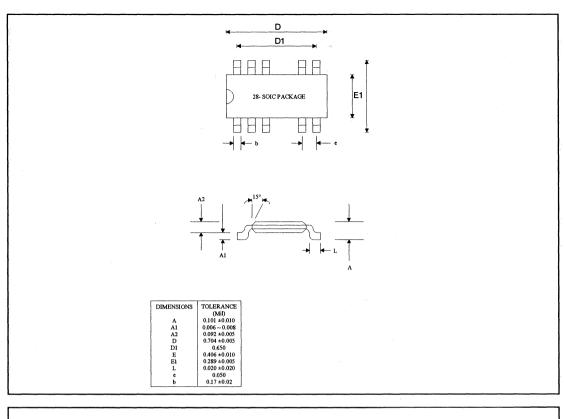

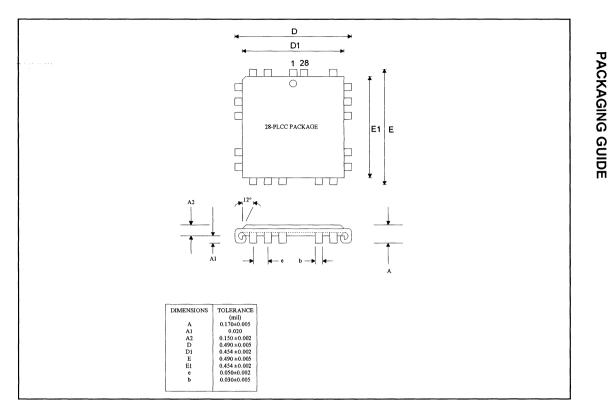

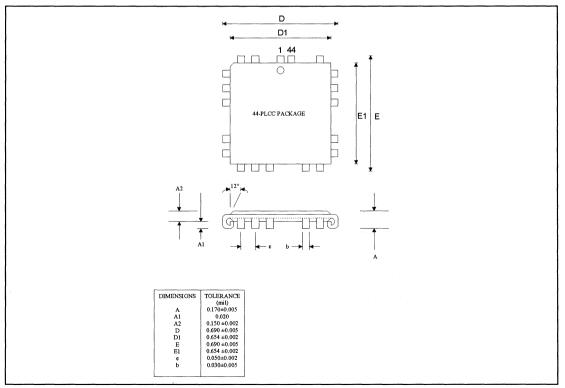

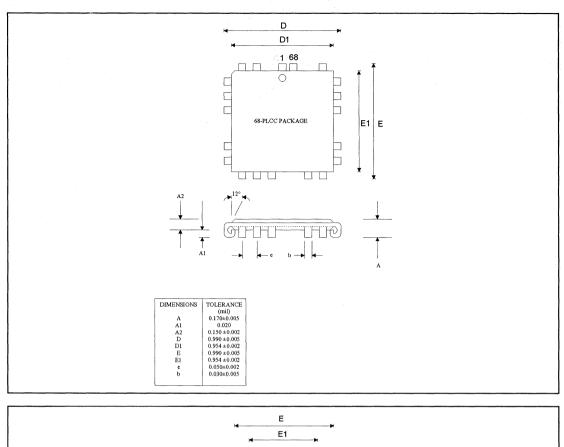

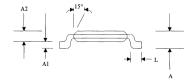

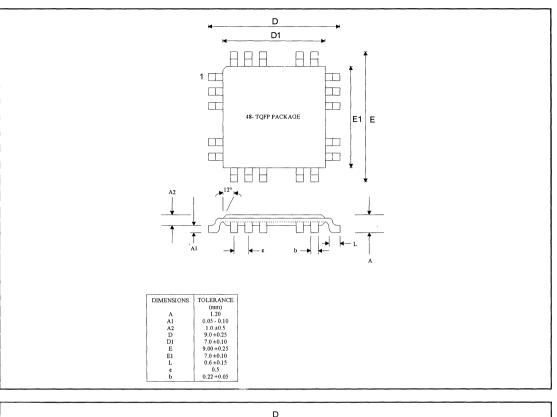

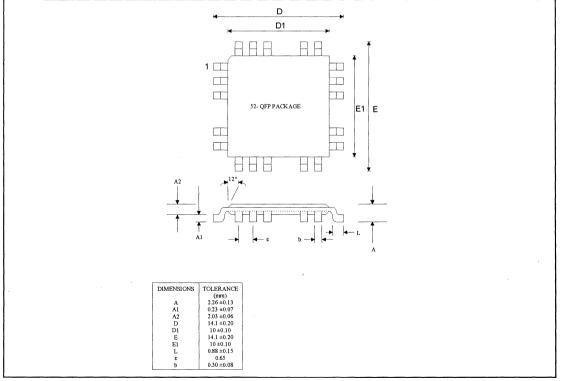

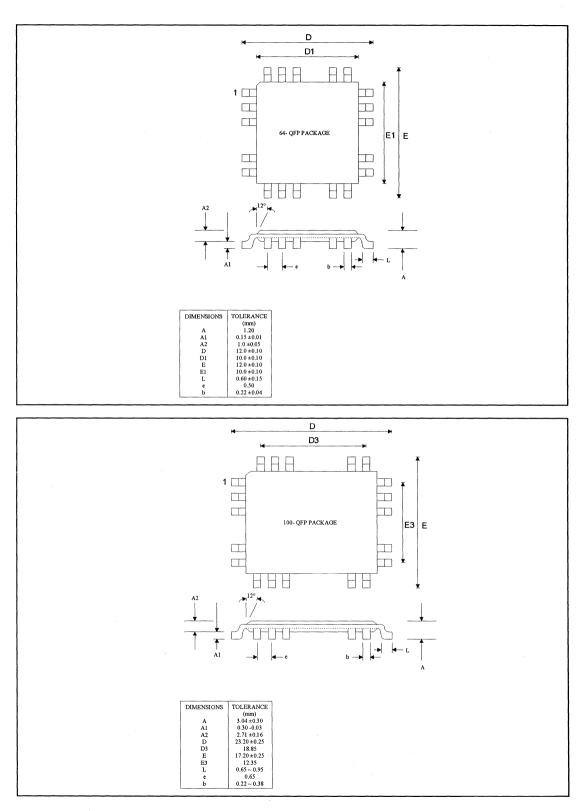

| PACKAGING INFORMATION                 |                                       | 10-3  |

|                                       |                                       |       |

| REPRESENTATIVES                       |                                       | 11-3  |

#### ------ CROSS REFERENCE LIST ------

#### DIFFERENTIAL LINE DRIVERS

National Semiconductor DS26C31/DS26LS31 DS34C86/DS34LS86

AMD AM26LS31

DIFFERENTIAL LINE RECEIVERS

National Semiconductor DS26C32/DS26LS32 DS34C87/DS34LS87

AMD AM26LS32

#### DIFFERENTIAL LINE RECEIVERS / DRIVERS

Motorola Semiconductor MC34050 MC34051

UARTS

National Semiconductor INS8250A INS82C50A NS16450 NS16C450 NS16C550AF NS16C552

Silicon Systems SSI73M550 SSI73M1550 SSI73M2550 SSI73M2551

VLSI Technology, Inc. VL82C50A VL16C450 VL16C550

Western Digital Inc. WD16C450 WD16C550 Startech Semiconductor ST26C31 ST34C86

Startech Semiconductor ST26C31

Startech Semiconductor ST26C32 ST34C87

Startech Semiconductor ST26C32

Startech Semiconductor ST34C50 ST34C51

Startech Semiconductor ST16C450 ST16C450 ST16C450 ST16C450 ST16C450 ST16C550 ST16C2552

Startech Semiconductor ST16C550 ST16C1450 / ST16C1550 ST16C1451 / ST16C1551 ST16C1552

Startech Semiconductor ST16C450 ST16C450 ST16C550

Startech Semiconductor ST16C450 ST16C550

#### **CROSS REFERENCE LIST**

Texas Instruments TL16C450 TL16C550A

Exar Corporation XR16C450 XR16C550

#### UARTS WITH PRINTER

VLSI Technology, Inc. VL16C452 VL16C552

Western Digital Inc. WD16C452 WD16C552

Texas Instruments TL16C452 TL16C552

Exar Corporation XR16C452 XR16C552

#### VIDEO DOT CLOCK GENERATOR

Integrated Circuit Systems, Inc. ICS2494XXX ICS9064 ICS9154-XX ICS9158

Avasem Corporation AV9064 AV9103-XX AV9104-XX AV9106 AV9107-XX AV9155-XX

STEREO CLOCK GENERATOR MicroClock Inc. MK1418 Startech Semiconductor ST16C450 ST16C550

Startech Semiconductor ST16C450 ST16C550

Startech Semiconductor ST16C452 ST16C552 / ST16C553

Startech Semiconductor ST16C452 ST16C552 / ST16C553

Startech Semiconductor ST16C452 ST16C552

Startech Semiconductor ST16C452 ST16C552

Startech Semiconductor ST49C214-XX ST49C064 ST49C154-XX ST49C158

Startech Semiconductor ST49C064 ST49C103-XX ST49C104-XX ST49C106 ST49C107-XX ST49C155-XX

Startech Semiconductor ST49C418

#### CROSS REFERENCE LIST –

#### DIFFERENTIAL LINE DRIVERS

Startech Semiconductor ST26C31

ST34C86

DIFFERENTIAL LINE RECEIVERS Startech Semiconductor ST26C32

ST34C87

DIFFERENTIAL LINE RECEIVERS / DRIVERS Startech Semiconductor ST34C50 ST34C51

UARTS Startech Semiconductor ST16C450

Startech Semiconductor

National Semiconductor DS26C31/DS26LS31

AMD AM26LS31

National Semiconductor DS34C86/DS34LS86

National Semiconductor DS26C32/DS26LS32

AMD AM26LS32

National Semiconductor DS34C87/DS34LS87

Motorola Semiconductor MC34050 MC34051

National Semiconductor INS8250A INS82C50A NS16450 NS16C450

VLSI Technology, Inc. VL82C50A VL16C450

Western Digital Inc. WD16C450

Texas Instruments TL16C450

Exar Corporation XR16C450

National Semiconductor

#### **CROSS REFERENCE LIST**-

#### ST16C550

NS16550AF

Silicon Systems SSI73M550

VLSI Technology, Inc. VL16C550

Western Digital Inc. WD16C550

Texas Instruments TL16C550A

Exar Corporation XR16C550

Silicon Systems SSI73M1550

SSI73M2550

SSI73M2551

National Semiconductor NS16C552

VLSI Technology, Inc. VL16C452

Exar Corporation XR16C452

Western Digital Inc. WD16C452

Texas Instruments TL16C452

VLSI Technology, Inc.

ST16C1450 ST16C1550

ST16C1451 ST16C1551

ST16C2552

ST16C2552

UARTS WITH PRINTER Startech Semiconductor ST16C452AT

ST16C452AT/PS

ST16C452AT/PS

#### CROSS REFERENCE LIST –

ST16C552/553

VIDEO DOT CLOCK GENERATOR Startech Semiconductor ST49C064

Startech Semiconductor ST49C103-XX ST49C104-XX ST49C106 ST49C107-XX ST49C105-XX

ST49C154-XX ST49C158

Startech Semiconductor ST49C214-XX

STEREO CLOCK GENERATOR

Starech Semiconductor ST49C418

VL16C552

Exar Corporation XR16C552

Western Digital Inc. WD16C552

Texas Instruments TL16C552

Avasem Corporation AV9064

Integrated Circuit Systems, Inc. ICS9064

Avasem Corporation AV9103-XX AV9104-XX AV9106 AV9107-XX AV9155-XX

Integrated Circuit Systems, Inc. ICS9154-XX ICS9158

Integrated Circuit Systems, Inc. ICS2494XXX

MicroClock Inc. MK1418

## Index

| AN1450 |                                         |

|--------|-----------------------------------------|

| AN1550 |                                         |

| AN2450 |                                         |

| AN2550 |                                         |

| AN2552 |                                         |

| AN450  |                                         |

| AN454  |                                         |

| AN550  | 7-27                                    |

| AN554  |                                         |

| AN654  |                                         |

|        | ••••••••••••••••••••••••••••••••••••••• |

| ST16C1450  | 3-3    |

|------------|--------|

| ST16C1451  | 3-3    |

| ST16C1550  | 3-93   |

| ST16C1551  | 3-93   |

| ST16C1552  | 3-93   |

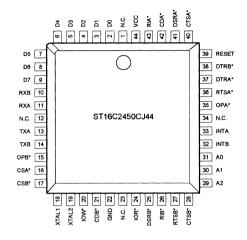

| ST16C2450  | 3-21   |

| ST16C2550  | 3-115  |

| ST16C2552  | 3-137  |

| ST16C450   | 3-37   |

| ST16C452AT |        |

| ST16C452PS | 3-309  |

| ST16C454   | 3-57   |

| ST16C550   | 3-161  |

| ST16C552   | 3-333  |

| ST16C553   | 3-363  |

| ST16C554   | 3-187  |

| ST16C554E  | 6-5    |

| ST16C650   | 3-231  |

| ST16C654   | 3-267  |

| ST26C31    | .2-3   |

| ST26C32    | .2-9   |

| ST31C32    | .2-15  |

| ST34C50    | . 2-23 |

| ST34C51    | . 2-23 |

| ST34C86    | . 2-33 |

| ST34C87    |        |

| ST49C001   | . 1-3  |

| ST49C101   | . 1-9  |

| ST49C103   |        |

| ST49C104   | . 1-17 |

| ST49C106   | . 1-27 |

| ST49C107   | . 1-33 |

| ST49C154 |  |

|----------|--|

| ST49C155 |  |

| ST49C158 |  |

| ST49C214 |  |

| ST49C418 |  |

| ST56C5XX |  |

| ST68C454 |  |

| ST68C554 |  |

| ST78C34  |  |

| ST78C36  |  |

| ST84C01  |  |

| ST84C72  |  |

| ST88C870 |  |

|          |  |

| XR-68C681 |  |

|-----------|--|

| XR-82C684 |  |

| XR-88C681 |  |

## FREQUENCY SYNTHESIZERS

1

## Index

| ST49C001 |  |

|----------|--|

| ST49C101 |  |

| ST49C103 |  |

| ST49C104 |  |

| ST49C106 |  |

| ST49C107 |  |

| ST49C154 |  |

| ST49C155 |  |

| ST49C158 |  |

| ST49C214 |  |

| ST49C418 |  |

|          |  |

Printed August 3, 1995

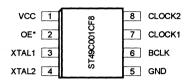

#### PREPROGRAMMED HIGH SPEED FREQUENCY SYNTHESIZER

#### DESCRIPTION

The ST49C001 is a mask programmable monolithic analog CMOS device, designed to replace existing high frequency crystal/oscillator with single low frequency crystal. The ST49C001 provides two high speed and low jitter clock outputs.

ST49C001 is designed for Magneto-Optical Disk Drive (MODD) appplication.

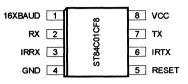

SOIC Package

#### FEATURES

- · Can replace expensive high frequency oscillators.

- · Mask programmable analog phase locked loop

- On board loop filter

- 5V 1.2µCMOS technology

- 8 pin SOIC package.

- · Crystal oscillator circuit on board

#### ORDERING INFORMATION

| Part number | Package     | Operating temperature |

|-------------|-------------|-----------------------|

| ST49C001CF8 | SOIC        | 0°C to +70°C          |

| ST49C001CP8 | Plastic-DIP | 0°C to +70°C          |

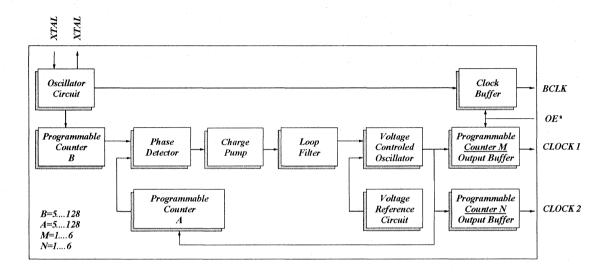

#### **BLOCK DIAGRAM**

1

#### SYMBOL DESCRIPTION

| Symbol | Pin | Signal Type | Pin Description                                                                                                                                                                                                                 |  |

|--------|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| vcc    | 1   | I           | Supply voltage. Single +5 volts.                                                                                                                                                                                                |  |

| OE*    | 2*  | Ι           | Output Enable (Active low). CLOCK1 and BCLK outputs are disabled and forced to low state when this pin is low. CLOCK2 output pin is active when CLOCK1 and BCLK outputs are disabled.                                           |  |

| XTAL1  | 3   | Ι           | Crystal or External Clock input. A crystal can be connected<br>to this pin and XTAL2 pin to generate internal phase locked<br>loop reference clock. For external clock, XTAL2 is left open<br>or used as buffered clock output. |  |

| XTAL2  | 4   | 0           | Crystal output.                                                                                                                                                                                                                 |  |

| GND    | 5   | 0           | Supply ground.                                                                                                                                                                                                                  |  |

| BCLK   | 6   | 0           | Buffered reference clock output.                                                                                                                                                                                                |  |

| CLOCK1 | 7   | о           | Preprogrammed clock output.                                                                                                                                                                                                     |  |

| CLOCK2 | 8   | ο           | Preprogrammed clock output.                                                                                                                                                                                                     |  |

\* Has internal pull-up resistor

#### **EXTERNAL CLOCK CONNECTION**

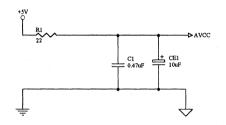

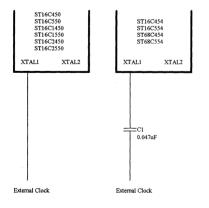

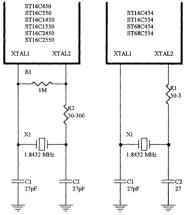

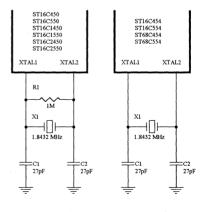

To minimize the noise pickup , it is recommended to connect 0.047 $\mu$ F capacitor to XTAL1, and keep the lead length of the capacitor to XTAL1 to a minimum to reduce noise susceptibility.

#### FREQUENCY SELECT CALCULATION

The ST49C001 contains an analog phase locked loop circuit with digital closed loop dividers and a final output divider to achieve the desired dividing ratios for the clock output.

The accuracy of the frequencies produced by the ST49C001 depends on the input frequency and divider ratios. The formula for calculating the exact output frequency is as follows:

CLOCK1 = (Reference clock) X 2A/B X 1/M CLOCK2 = (Reference clock) X 2A/B X 1/N

| where | A=5, 6, 7,128 |

|-------|---------------|

|       | B=5, 6, 7,128 |

|       | M=1, 2,6      |

|       | N=1, 2,6      |

#### ST49C001-01 Frequency table

| OUTPUT<br>FREQUENCIES    |  |  |  |  |

|--------------------------|--|--|--|--|

| 49.143 MHz<br>29.486 MHz |  |  |  |  |

|                          |  |  |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

Supply range Voltage at any pin Operating temperature Storage temperature Package dissipation 7 Volts GND-0.3 V to VCC+0.3 V 0° C to +70° C -40° C to +150° C 500 mW

#### DC ELECTRICAL CHARACTERISTICS

T<sub>a</sub>=0-70° C, Vcc=4.0 - 5.5V unless otherwise specified.

| Symbol                                        | Parameter                                                                                                                                    | Min              | Limits<br>Typ | Мах                                  | Units                         | Conditions                                                                                                                |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|--------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Vil<br>Viн<br>Vol<br>Iil<br>Iiн<br>Icc<br>Rin | Input Iow level<br>Input high level<br>Output Iow level<br>Output high level<br>Input Iow current<br>Input high current<br>Operating current | 2.0<br>2.4<br>60 | 45<br>85      | 0.8<br>0.4<br>-100<br>1<br>55<br>110 | V<br>V<br>V<br>μΑ<br>mA<br>κΩ | IoL = 8.0 mA<br>IoH = 8.0 mA<br>Pin 2 only<br>VIN=Vcc Pin 2<br>No Ioad, OE High,<br>All Clock outputs<br>active<br>OE Pin |

Í

#### AC ELECTRICAL CHARACTERISTICS

$T_{A}$ =0-70° C, Vcc=5.0 V unless otherwise specified.

| Symbol         | Parameter                         | Min | Limits<br>Typ | Max      | Units  | Conditions             |

|----------------|-----------------------------------|-----|---------------|----------|--------|------------------------|

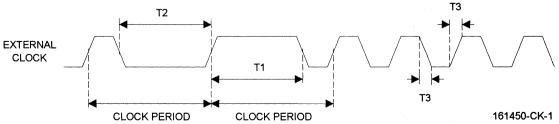

| Τı             | CLOCK rise time                   |     | 3             | 5.5      | ns     | CL=20pF<br>0.4V - 2.4V |

| T <sub>2</sub> | CLOCK fall time                   |     | 3             | 5.5      | ns     | CL=20pF<br>2.4V - 0.4V |

| <b>T</b> 4,5   | Duty cycle                        | 40  | 47            | 60       | %      | CL=20pF                |

| T₃<br>T₃       | Jitter 1 sigma<br>Jitter absolute |     | ±0.5<br>±2    | ±2<br>±5 | %<br>% | @ Vcc/2                |

|                |                                   |     |               |          |        |                        |

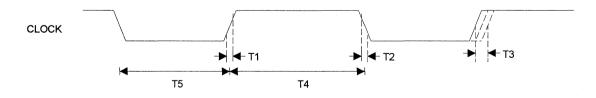

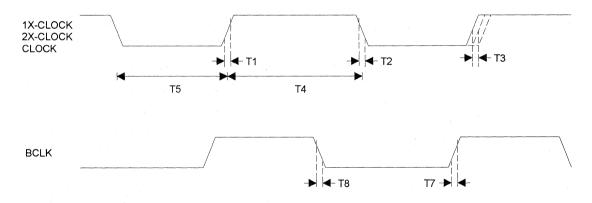

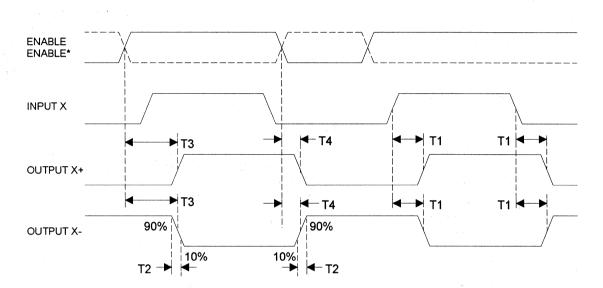

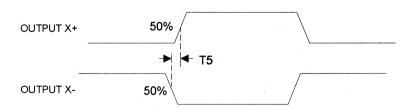

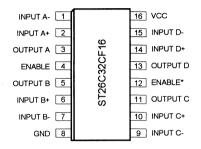

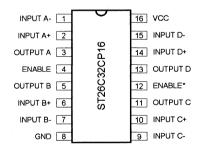

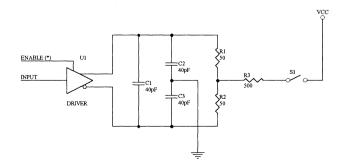

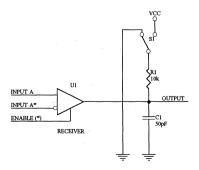

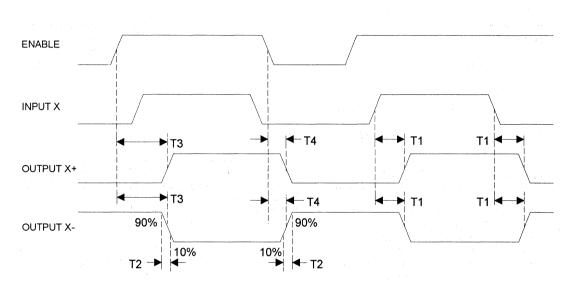

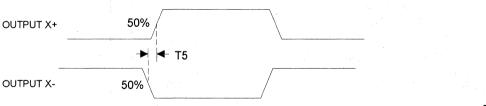

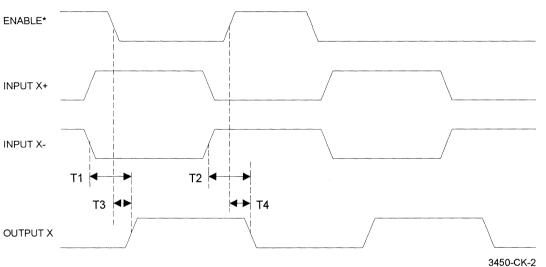

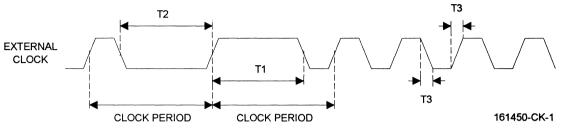

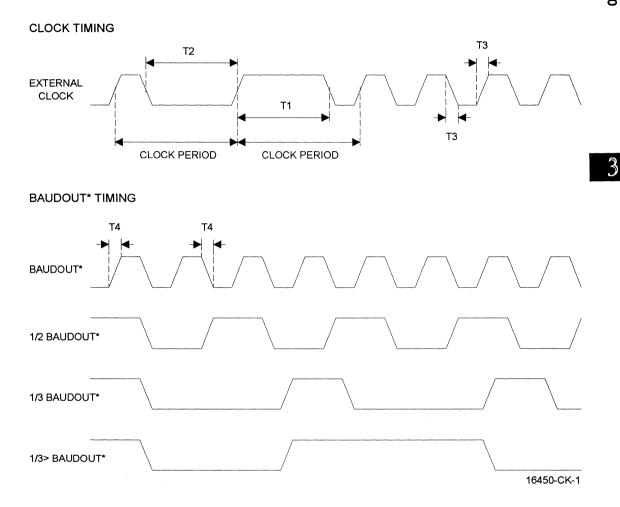

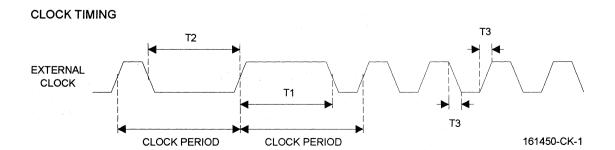

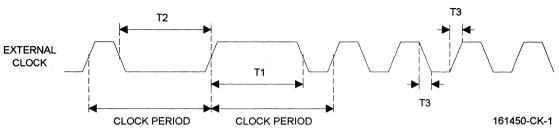

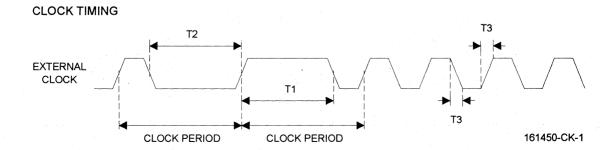

TIMING DIAGRAM

Printed August 3, 1995

#### PREPROGRAMMED HIGH SPEED FREQUENCY MULTIPLIER

#### DESCRIPTION

The ST49C101/102 is a mask programmable monolithic analog CMOS device, designed to replace existing high frequency crystal/oscillator with single low frequency crystal. The ST49C101/102 provides high speed and low jitter clock output.

ST49C101/102 is designed in a 1.2 $\mu$  process to achieve 100 MHz speed for high end frequencies.

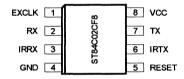

#### **SOIC Package**

#### Dip Package

#### FEATURES

- Can replace expensive high frequency oscillator.

- Mask programmable analog phase locked loop

- Low power single 5V CMOS technology

- 8 pin DIP or SOIC package.

- · Crystal oscillator circuit on board

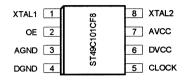

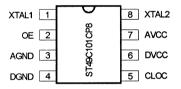

#### ORDERING INFORMATION

| Part number | Package     | Operating temperature |

|-------------|-------------|-----------------------|

| ST49C101CP8 | Plastic-DIP | 0 ° C to +70° C       |

| ST49C101CF8 | SOIC        | 0° C to +70° C        |

| ST49C102CT8 | TSSOP       | 0° C to +70° C        |

#### Rev. 1.0

#### **TSSOP** Package

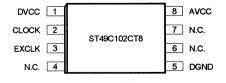

ST49C101/102

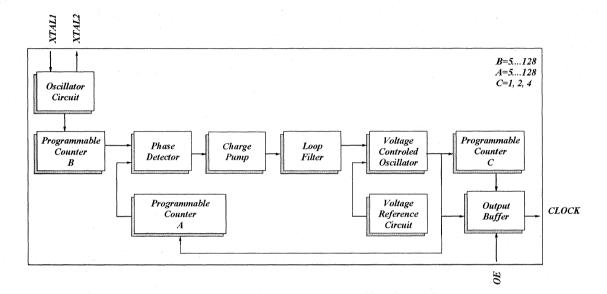

#### **BLOCK DIAGRAM**

### SYMBOL DESCRIPTION (ST49C101)

| Symbol | Pin | Signal Type | Pin Description                                                                                                                                                                                                                 |

|--------|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTAL1  | 1   | I           | Crystal or External Clock input. A crystal can be connected<br>to this pin and XTAL2 pin to generate internal phase locked<br>loop reference clock. For external clock, XTAL2 is left open<br>or used as buffered clock output. |

| OE     | 2*  | I           | Clock Output Enable (Active high). CLOCK output is three stated when this pin is low.                                                                                                                                           |

| AGND   | 3   | 0           | Analog ground.                                                                                                                                                                                                                  |

| DGND   | 4   | 0           | Digital ground.                                                                                                                                                                                                                 |

| CLOCK  | 5   | 0           | Programmed output clock.                                                                                                                                                                                                        |

| DVCC   | 6   | I           | Positive supply voltage. Single +5 volts.                                                                                                                                                                                       |

| AVCC   | 7   | 1           | Analog supply voltage. Single +5 volts.                                                                                                                                                                                         |

| XTAL2  | 8   | 0           | Crystal output.                                                                                                                                                                                                                 |

\* Has internal pull-up resistor

#### SYMBOL DESCRIPTION (ST49C102)

| Symbol | Pin | Signal Type | Pin Description                                                                                                |

|--------|-----|-------------|----------------------------------------------------------------------------------------------------------------|

| DVCC   | 1   | l           | Digital Positive supply voltage. Single +5 volts.                                                              |

| CLOCK  | 2   | 0           | Pre-programmed output clock.                                                                                   |

| EXCLK  | 3   | i           | External Clock input. Input reference clock.                                                                   |

| DGND   | 5   | 0           | Digital ground.                                                                                                |

| AVCC   | 8   | 1           | Analog supply voltage. Single +5 volts.                                                                        |

|        | 1   |             | I de la construcción de la constru |

1

#### **EXTERNAL CLOCK CONNECTION**

To minimize the noise pickup , it is recommended to connect  $0.047\mu$ F capacitor to XTAL1, and keep the lead length of the capacitor to XTAL1 to a minimum to reduce noise susceptibility.

#### FREQUENCY SELECT CALCULATION

The ST49C101/102 contains an analog phase locked loop circuit with digital closed loop dividers and a final output divider to achieve the desired dividing ratios for the clock output.

The accuracy of the frequencies produced by the ST49C101/102 depends on the input frequency and divider ratios. The formula for calculating the exact output frequency is as follows:

CLOCK = (Reference clock) X 2A/(BXC)

| where |  |

|-------|--|

|       |  |

|       |  |

| A=5, 6, 7,128 | 3 |

|---------------|---|

| B=5, 6, 7,128 | 3 |

| C=1,2,4       |   |

Preprogrammed options:

| Factor | Max. Output<br>Frequency |

|--------|--------------------------|

| 12     | 100 MHz                  |

| 6      | 100 MHz                  |

| 8      | 130 MHz                  |

| 4      | 100 MHz                  |

|        | 12<br>6                  |

| ST49C102 | Input<br>Frequency | Output<br>Frequency |

|----------|--------------------|---------------------|

| ST49C102 | 40MHz              | 60MHz               |

ST49C101/102

1

#### **ABSOLUTE MAXIMUM RATINGS**

Supply range Voltage at any pin Operating temperature Storage temperature Package dissipation 7 Volts GND-0.3 V to VCC+0.3 V 0° C to +70° C -40° C to +150° C 500 mW

#### DC ELECTRICAL CHARACTERISTICS

$T_{A}=0 - 70^{\circ}$  C, Vcc=5.0 V ± 10% unless otherwise specified.

| Symbol                                        | Parameter                                                                                                                                                                | Min              | Limits<br>Typ | Max                                  | Units                         | Conditions                                                                             |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|--------------------------------------|-------------------------------|----------------------------------------------------------------------------------------|

| Vil<br>Viн<br>Vol<br>Iil<br>Iiн<br>Icc<br>Rin | Input low level<br>Input high level<br>Output low level<br>Output high level<br>Input low current<br>Input high current<br>Operating current<br>Input pull-up resistance | 2.0<br>2.8<br>50 | 55<br>75      | 0.8<br>0.5<br>-100<br>1<br>65<br>100 | V<br>V<br>V<br>μA<br>mA<br>kΩ | Iо∟= 8.0 mA<br>Iон = 8.0 mA<br>Pin 2 only<br>VIN=Vcc Pin 2<br>No load.<br>CLOCK=100MHz |

#### **AC ELECTRICAL CHARACTERISTICS**

$T_{A}=0 - 70^{\circ}$  C, Vcc=5.0 V ± 10% unless otherwise specified.

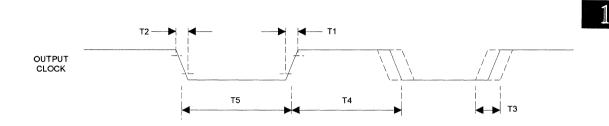

| Symbol                  | Parameter                                                     | Min      | Limits<br>Typ                | Мах                  | Units       | Conditions                              |

|-------------------------|---------------------------------------------------------------|----------|------------------------------|----------------------|-------------|-----------------------------------------|

| <b>T</b> <sub>1,2</sub> | CLOCK rise/fall time                                          |          | 1.5                          | 3                    | ns          | Load=30 pF, 0.6V -                      |

| T₄<br>T₅<br>T₃<br>T₃    | Duty cycle<br>Duty cycle<br>Jitter 1 sigma<br>Jitter absolute | 40<br>45 | 48/52<br>48/52<br>±0.5<br>±2 | 60<br>55<br>±2<br>±5 | %<br>%<br>% | 1.4V switch point<br>VCC/2 switch point |

| ΤιΝ<br>Τουτ             | Input reference frequency<br>Output frequency                 | 7        | 10                           | 25<br>130            | MHz<br>MHz  |                                         |

#### DC ELECTRICAL CHARACTERISTICS (ST49C101-02 and -04 ONLY)

$T_a=0.70^{\circ}$  C, Vcc=3.0V ± 10% unless otherwise specified.

| Symbol | Parameter                |           | Limits |      |    | Conditions    |

|--------|--------------------------|-----------|--------|------|----|---------------|

|        |                          | Min       | Тур    | Max  |    |               |

| VIL    | Input low level          |           |        | 0.8  | V  |               |

| Vн     | Input high level         | 2.0       |        |      | V  |               |

| Vol    | Output low level         |           |        | 0.5  | V  | lo∟= 4.0 mA   |

| Vон    | Output high level        | 2.0       |        |      | V  | loн = 4.0 mA  |

| lı.    | Input low current        | 1997 - A. | s      | -100 | μA | Pin 2 only    |

| łн     | Input high current       |           |        | 1    | μA | VIN=Vcc Pin 2 |

| lcc    | Operating current        |           | 40     | 60   | mΑ | No load.      |

|        |                          |           |        |      |    | CLOCK=80 MHz  |

| RIN    | Input pull-up resistance | 50        | 75     | 100  | kΩ |               |

#### AC ELECTRICAL CHARACTERISTICS (ST49C101-02 and -04 ONLY)

$T_{A}=0-70^{\circ}$  C, Vcc=3.0V ± 10% unless otherwise specified.

| Symbol            | Parameter                                                        | Min | Limits<br>Typ | Max            | Units           | Conditions                |

|-------------------|------------------------------------------------------------------|-----|---------------|----------------|-----------------|---------------------------|

| T <sub>1,2</sub>  | CLOCK rise/fall time                                             |     | 2             | 3              | ns              | Load 30pF, 0.6V -<br>2.2V |

| T₅<br>T₃<br>T     | Duty cycle<br>Jitter 1 sigma                                     | 45  | 48/52<br>±0.5 | 55<br>±2       | %<br>%          | VCC/2 switch point        |

| T3<br>Tin<br>Tout | Jitter absolute<br>Input reference frequency<br>Output frequency | 7   | ±2<br>10      | ±5<br>20<br>80 | %<br>MHz<br>MHz |                           |

|                   |                                                                  |     |               | -              |                 |                           |

## ST49C101/102

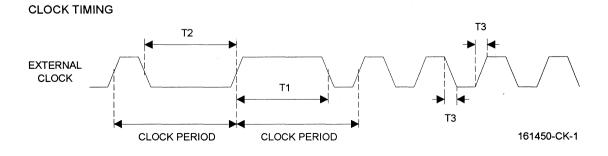

#### TIMING DIAGRAM

## ST49C103 ST49C104

Printed August 3, 1995

#### PREPROGRAMMED FREQUENCY GENERATOR

#### DESCRIPTION

The ST49C103 and ST49C104 are mask programmable monolithic analog CMOS devices designed to generate up to 8 single frequency outputs from a single input clock. The ST49C104 will provide eight different output frequencies and the ST49C103 will provide four different output frequencies. They are designed in a  $1.2\mu$  process to achieve 80 MHz.

The ST49C103 and ST49C104 are designed to replace existing video clocks generated from individual oscillators in order to reduce board space and number of oscillators. To provide high speed and low jitter clock, the parts utilize a high speed analog CMOS phase locked loop using 14.318 MHz system clock as the reference clock (note that reference clock can be changed to generate optional frequencies from a standard programmed device). The programmed clock outputs are selectable via three address lines and address latch enable pin. The ST49C104 also includes a power on reset circuit which will cause the select logic to select the frequency at address "000" upon power up. The latch enable pin is also mask programmable to be active high, active low or rising or falling edge sensitive.

- Can replace up to 8 oscillators/crystals and a multiplexer

- Pin-to-pin compatible to Avasem AV9103/104

- Programmable analog phase locked loop

- Low power single 5V CMOS technology

- 8 or 14 pin DIP or SOIC package.

FEATURES

| ORDERING INFORMATION |                                |                                           |                                                   |                                                                                                   |  |

|----------------------|--------------------------------|-------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------|--|

| Package              | Opera                          | atin                                      | g te                                              | mperat                                                                                            |  |

| Plastic-DIP          | 0°                             | С                                         | to                                                | +70°                                                                                              |  |

| SOIC                 | 0°                             | С                                         | to                                                | +70°                                                                                              |  |

| Plastic-DIP          | 0°                             | С                                         | to                                                | +70°                                                                                              |  |

|                      | Package<br>Plastic-DIP<br>SOIC | Package Oper<br>Plastic-DIP 0°<br>SOIC 0° | Package Operatin<br>Plastic-DIP 0° C<br>SOIC 0° C | Package         Operating te           Plastic-DIP         0° C to           SOIC         0° C to |  |

SOIC

SOIC

Plastic-DIP

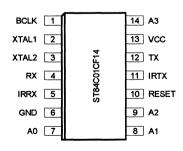

#### **SOIC Package**

| A1 1    |              | 14 A0   |

|---------|--------------|---------|

| A2 2    | .CF14        | 13 N.C. |

| LEN 3   |              | 12 AVCC |

| AGND 4  | 107          | 11 DVCC |

| DGND 5  | ST49C104CF14 | 10 CLKO |

| XTAL1 6 |              | 9 CLK2  |

| XTAL2 7 |              | 8 CLK1  |

|         |              |         |

| A1 1    | CF8      | 8 A0   |

|---------|----------|--------|

| A2 2    | 104C     | 7 N.C. |

| GND 3   | ST49C104 | 6 VCC  |

| EXCLK 4 | S        | 5 CLKO |

ST49C104CF8

ST49C104CP14

ST49C104CF14

ure

C C

С

С

0° C to +70°

0°C to +70°C

0° C to +70° C

## ST49C103/104

ST49C103/104

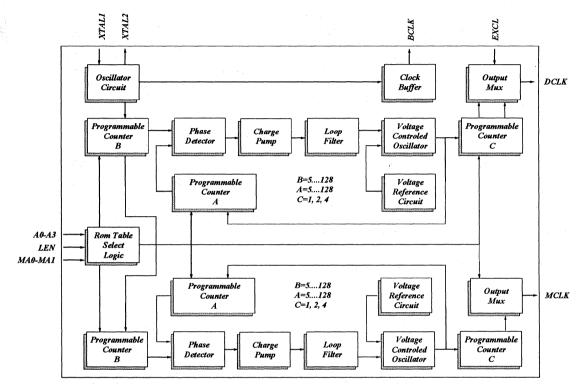

#### **BLOCK DIAGRAM**

1

#### SYMBOL DESCRIPTION (ST49C104 14 pin package)

| Symbol | Pin | Signal Type | Pin Description                                                                                                                                                                                                                            |

|--------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | 1   | I           | Frequency select address input 2.                                                                                                                                                                                                          |

| A2     | 2*  | I           | Frequency select address input 3.                                                                                                                                                                                                          |

| LEN    | 3*  | 1           | Address latch enable input. To latch selected programmed clock output.                                                                                                                                                                     |

| AGND   | 4   | 0           | Analog ground.                                                                                                                                                                                                                             |

| DGND   | 5   | 0           | Digital ground.                                                                                                                                                                                                                            |

| XTAL1  | 6   | 1           | Crystal or external clock input. A crystal can be connected<br>to this pin and XTAL2 pin to generate internal phase locked<br>loop reference clock. For external 14.318 MHz clock,<br>XTAL2 is left open or used as buffered clock output. |

| XTAL2  | 7   | 0           | Crystal output.                                                                                                                                                                                                                            |

| CLK1   | 8   | I           | External clock 1 input.                                                                                                                                                                                                                    |

| CLK2   | 9   | I           | External clock 2 input / output select.                                                                                                                                                                                                    |

| CLKO   | 10  | о           | Programmed output clock.                                                                                                                                                                                                                   |

| DVCC   | 11  | 1           | Digital supply voltage. Single +5 volts.                                                                                                                                                                                                   |

| AVCC   | 12  | I           | Analog supply voltage. Single +5 volts.                                                                                                                                                                                                    |

| N.C.   | 13  |             |                                                                                                                                                                                                                                            |

| A0     | 14  | I           | Frequency select address input 1.                                                                                                                                                                                                          |

\* Have internal pull-up resistors on inputs.

## ST49C103/104

**SYMBOL DESCRIPTION** (ST49C104 8 pin. package)

| Symbol      | Pin | Signal Type                             | Pin Description                                                    |

|-------------|-----|-----------------------------------------|--------------------------------------------------------------------|

| A1          | 1   | a ta <b>l</b> a seg                     | Frequency select address input 2.                                  |

| A2          | 2*  | $\sim 1$                                | Frequency select address input 3.                                  |

| GND         | 3   | 0 0                                     | Digital ground.                                                    |

| EXCLK       | 4   | 1                                       | External clock input. Internal phase locked loop reference clock . |

| CLKO        | 5   | о                                       | Programmed output clock.                                           |

| vcc a la la | 6   | I                                       | Digital supply voltage. Single +5 volts.                           |

| N.C.        | 7   |                                         |                                                                    |

| AO          | 8   | l i l i l i l i l i l i l i l i l i l i | Frequency select address input 1.                                  |

\* Has internal pull-up resistor on input

# ST49C103/104

1

#### SYMBOL DESCRIPTION (ST49C103 8pin package)

| Symbol | Pin | Signal Type | Pin Description                                                                                                                                                                                                                            |

|--------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | 1   | I           | Frequency select address input 2.                                                                                                                                                                                                          |

| GND    | 2   | 0           | Digital ground.                                                                                                                                                                                                                            |

| XTAL1  | 3   | 1           | Crystal or external clock input. A crystal can be connected<br>to this pin and XTAL2 pin to generate internal phase locked<br>loop reference clock. For external 14.318 MHz clock,<br>XTAL2 is left open or used as buffered clock output. |

| XTAL2  | 4   | 0           | Crystal output.                                                                                                                                                                                                                            |

| сіко   | 5   | 0           | Programmed output clock.                                                                                                                                                                                                                   |

| vcc    | 6   | I           | Digital supply voltage. Single +5 volts.                                                                                                                                                                                                   |

| N.C.   | 7   |             |                                                                                                                                                                                                                                            |

| A0     | 8   |             | Frequency select address input 1.                                                                                                                                                                                                          |

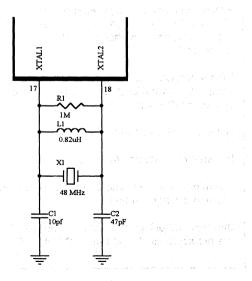

#### **EXTERNAL CLOCK CONNECTION**

To minimize the noise pickup , it is recommended to connect  $0.047\mu$ F capacitor to XTAL1, and keep the lead length of the capacitor to XTAL1 to a minimum to reduce noise susceptibility.

#### FREQUENCY SELECT CALCULATION

The ST49C104 contains an analog phase locked loop circuit with digital closed loop dividers and a final output multiplexer to achieve the desired dividing ratios for the clock output.

The accuracy of the frequencies produced by the ST49C104 depends on the input frequency and divider ratios. The formula for calculating the exact output frequency is as follows:

CLKO = (Reference clock) X A/(B X C)

where

A=1,2,3,.....127 B=8, 16, 32 ,64 C=1,2,4,8

#### MASK OPTIONS

The following mask options are provided for custom applications.

• Latch Enable can be edge triggered or level sensitive.

- Latch Enable can be active high or active low.

- Any frequency can be in any decoding position.

- CLK 1 and CLK 2 can be included in decoding table.

• CLK2 can control selection of either CLK 1 or the internal frequencies.

| FEATURE                             | ST49C104<br>14-pin | ST49C104<br>8-pin | ST49C103<br>8-pin |

|-------------------------------------|--------------------|-------------------|-------------------|

| 8 output frequencies                | x                  | x                 |                   |

| 4 output frequencies                |                    |                   | x                 |

| Programmable LEN pin                | X                  | ×                 | X                 |

| Clock input only                    |                    | x                 |                   |

| Crystal or clock input              | X                  |                   | X                 |

| CLK1, CLK2 available for output mux | X                  |                   |                   |

| S          |

|------------|

|            |

| 4          |

| ò          |

| Ō          |

| <u> </u>   |

| 0          |

| ũ          |

| -          |

| 3          |

| Ň          |

| <b>4</b> 4 |

|            |

|            |

1

| Address latch (LEN) | State                    |

|---------------------|--------------------------|

| ST49C104-1          | Transparent for LEN high |

| ST49C104-2          | Transparent for LEN high |

| ST49C104-3          | Transparent for LEN low  |

### **ABSOLUTE MAXIMUM RATINGS**

Supply range Voltage at any pin Operating temperature Storage temperature Package dissipation 7 Volts GND-0.3 V to VCC+0.3 V 0° C to +70° C -40° C to +150° C 500 mW

### DC ELECTRICAL CHARACTERISTICS

$T_{\rm A}{=}0^{\circ}$  - 70° C, Vcc=5.0 V  $\pm$  10% unless otherwise specified.

| Symbol | Parameter                | Min | Limits<br>Typ | Max  | Units | Conditions              |

|--------|--------------------------|-----|---------------|------|-------|-------------------------|

| VIL    | Input low level          |     |               | 0.8  | V     |                         |

| Vн     | Input high level         | 2.0 |               |      | V     |                         |

| Vol    | Output low level         |     |               | 0.4  | V     | lo∟= 8.0 mA             |

| Vон    | Output high level        | 2.4 |               |      | V     | Iон = 8.0 mA            |

| lı.    | Input low current        |     |               | -350 | μΑ    | Except crystal<br>input |

| lн     | Input high current       |     |               | 1    | μA    | VIN=Vcc                 |

| lcc    | Operating current        |     | 30            | 50   | mA    | No load.<br>DCLK=80MHz  |

| Rın    | Input pull-up resistance | 15  | 20            | 25   | kΩ    |                         |

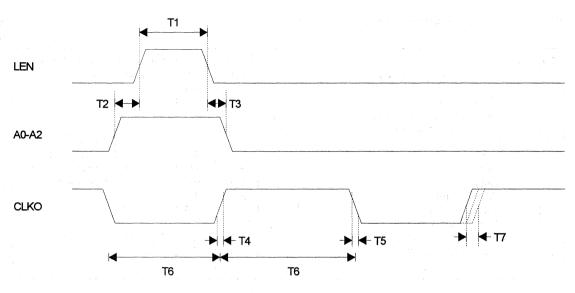

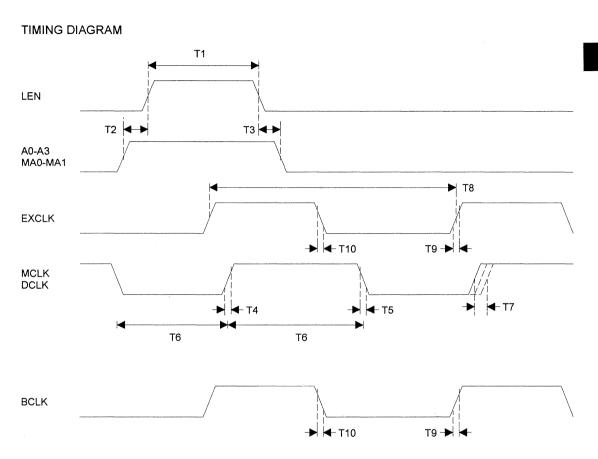

### **AC ELECTRICAL CHARACTERISTICS**

$T_{A}=0^{\circ}$  - 70° C, Vcc=5.0 V ± 10% unless otherwise specified.

| Symbol         | Parameter Limits<br>Min Typ Max |        | Units | Conditions |     |                                       |

|----------------|---------------------------------|--------|-------|------------|-----|---------------------------------------|

| T1             | Enable pulse width              | 20     |       |            | ns  |                                       |

| T <sub>2</sub> | Setup time data to enable       | 20     |       |            | ns  |                                       |

| T <sub>3</sub> | Hold time to data enable        | 10     |       |            | ns  |                                       |

| T4             | Rise time                       |        | 1.5   | 3          | ns  | 0.8V - 2.0V, 15 pF                    |

| T₅             | Fall time                       |        | 1     | 1.5        | ns  | 2.0V - 0.8V, 15pF                     |

| T <sub>6</sub> | Duty cycle                      | 40     | 48/52 | 60         | %   | 1.4V switch point                     |

| T6             | Duty cycle                      | 45     | 48/52 | 55         | %   | Vcc/2 switch point                    |

| <b>T</b> 7     | Jitter 1 sigma                  |        | ±0.5  | ±2         | %   |                                       |

| <b>T</b> 7     | Jitter absolute                 |        | ±2    | ±5         | %   |                                       |

| T <sub>8</sub> | Input frequency                 | 14.318 |       | 32         | MHz |                                       |

| Т∍             | Input clock rise time           |        |       | 20         | ns  | · · · · · · · · · · · · · · · · · · · |

| T10            | Input clock fall time           |        |       | 20         | ns  |                                       |

|                |                                 |        |       |            |     |                                       |

|                |                                 |        |       |            |     | 2.2°                                  |

ST49C103/104

1

| A2  | A1 | A0 | ST490   | :104-1 | ST490   | 2104-2 | ST49C   | 104-5* | ST490  | :103** | ST49C   | 104-6** |

|-----|----|----|---------|--------|---------|--------|---------|--------|--------|--------|---------|---------|

|     |    |    | NOMINAL | ACTUAL | NOMINAL | ACTUAL | NOMINAL | ACTUAL | NORMAL | ACTUAL | NOMINAL | ACTUAL  |

| 0   | 0  | 0  | Xtal    | Xtal   | 25.175  | 25.280 | 39.000  | 39.000 | 32.000 | 32.00  | 25.500  | 25.500  |

| 0   | 0  | 1  | 16.257  | 16.331 | 28.322  | 28.412 | 25.000  | 25.000 | 40.00  | 40.00  | 16.500  | 16.500  |

| 0   | 1  | 0  | Clk2    | Clk2   | 32.514  | 32.663 | 30.750  | 30.750 | 50.00  | 50.00  | 20.750  | 20.750  |

| 0   | 1  | 1  | 32.514  | 32.663 | 36.000  | 35.795 | 26.250  | 26.250 | 1.00   | 1.002  | 2.500   | 22.500  |

| 1   | 0  | 0  | 25.175  | 25.056 | 40.000  | 39.822 | 32.000  | 32.000 | N/A    |        | 24.500  | 24.500  |

| . 1 | 0  | 1  | 28.322  | 28.412 | 44.900  | 44.744 | 25.250  | 25.250 | N/A    |        | 19.500  | 19.500  |

| 1   | 1  | 0  | 24.000  | 23.938 | 50.000  | 50.113 | 31.250  | 31.250 | N/A    |        | 15.000  | 15.000  |

| 1   | 1  | 1  | 40.000  | 39.822 | 65.000  | 65.326 | 37.500  | 37.500 | N/A    |        | 14.000  | 14.000  |

Input clock frequency = 14.318 MHz \* Input clock frequency = 16.0 MHz \*\* Input clock frequency = 8.0 MHz

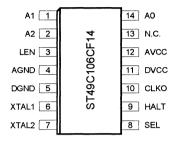

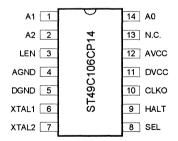

### PREPROGRAMMED FREQUENCY GENERATOR

### DESCRIPTION

The ST49C106 is a mask programmable monolithic analog CMOS device designed to generate up to 8 single frequency outputs from a single input clock. The ST49C106 is designed in a  $1.2\mu$  process to achieve 80 MHz.

The ST49C106 is designed to replace existing video clocks generated from individual oscillators in order to reduce board space and number of oscillators. To provide high speed and low jitter clock, the parts utilize a high speed analog CMOS phase locked loop using 14.318 MHz system clock as the reference clock (note that reference clock can be changed to generate optional frequencies from a standard programmed device). The programmed clock outputs are selectable via three address lines and address latch enable pin. The ST49C106 also includes a power on reset circuit which will cause the select logic to select the frequency at address "000" upon power up. The ST49C106 contains de-glitch circuit so that full clock cycles are provided whenever the HALT pin stops or starts the output clock.

### FEATURES

- Can replace up to 8 oscillators/crystals and a multiplexer

- Pin-to-pin compatible to Avasem AV9106-14

- Programmable analog phase locked loop

- Low power single 5V CMOS technology

- 14 pin DIP or SOIC package.

#### SOIC Package

### Plastic-DIP package

#### **ORDERING INFORMATION**

| Part number  | Package (   | Operating temperature |

|--------------|-------------|-----------------------|

| ST49C106CP14 | Plastic-DIP | 0 ° C to +70° C       |

| ST49C106CF14 | SOIC        | 0° C to +70° C        |

ST49C106

Printed August 3, 1995

1

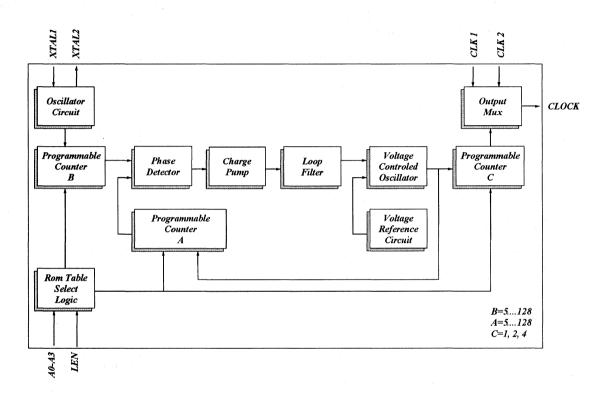

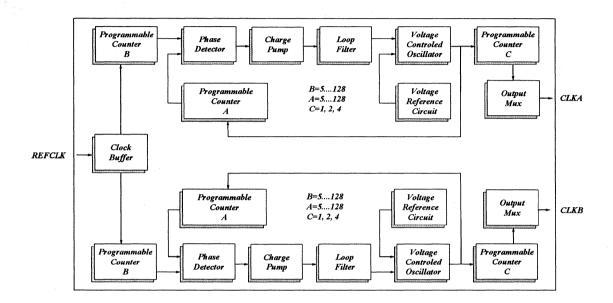

### **BLOCK DIAGRAM**

1

### SYMBOL DESCRIPTION

| Symbol | Pin | Signal Type | Pin Description                                                                                                                                                                                                                            |

|--------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | 1   | I           | Frequency select address input 2.                                                                                                                                                                                                          |

| A2     | 2*  | 1           | Frequency select address input 3.                                                                                                                                                                                                          |

| LEN    | 3*  | 1           | Address latch enable input. To latch selected programmed clock output.                                                                                                                                                                     |

| AGND   | 4   | 0           | Analog ground.                                                                                                                                                                                                                             |

| DGND   | 5   | 0           | Digital ground.                                                                                                                                                                                                                            |

| XTAL1  | 6   | Ι           | Crystal or external clock input. A crystal can be connected<br>to this pin and XTAL2 pin to generate internal phase locked<br>loop reference clock. For external 14.318 MHz clock,<br>XTAL2 is left open or used as buffered clock output. |

| XTAL2  | 7   | 0           | Crystal output.                                                                                                                                                                                                                            |

| SEL    | 8   | I           | Clock level select / CLK1. When HALT is asserted, SEL selects whether the clock is high or low. This level must be selected before the clock is halted. SEL pin can be used as an xternal clock input when HALT is active.                 |

| HALT   | 9   | I           | Start / Stop output clock.                                                                                                                                                                                                                 |

| CLKO   | 10  | 0           | Programmed output clock.                                                                                                                                                                                                                   |

| DVCC   | 11  | 1           | Digital supply voltage. Single +5 volts.                                                                                                                                                                                                   |

| AVCC   | 12  | . I         | Analog supply voltage. Single +5 volts.                                                                                                                                                                                                    |

| A0     | 14  | 1           | Frequency select address input 1.                                                                                                                                                                                                          |

\* Have internal pull-up resistors on inputs.

#### **EXTERNAL CLOCK CONNECTION**

To minimize the noise pickup , it is recommended to connect 0.047 $\mu$ F capacitor to XTAL1, and keep the lead length of the capacitor to XTAL1 to a minimum to reduce noise susceptibility.

#### FREQUENCY SELECT CALCULATION

The ST49C106 contains an analog phase locked loop circuit with digital closed loop dividers and a final output multiplexer to achieve the desired dividing ratios for the clock output. The accuracy of the frequencies produced by the ST49C106 depends on the input frequency and divider ratios. The formula for calculating the exact output frequency is as follows:

CLKO = (Reference clock) X A/(B X C)

where

A=1,2,3,.....127 B=8, 16, 32,64 C=1,2,4,8

#### **ABSOLUTE MAXIMUM RATINGS**

Supply range Voltage at any pin Operating temperature Storage temperature Package dissipation 7 Volts GND-0.3 V to VCC+0.3 V 0° C to +70° C -40° C to +150° C 500 mW

### DC ELECTRICAL CHARACTERISTICS

$T_a=0^\circ$  - 70° C, Vcc=5.0 V ± 10% unless otherwise specified.

| Symbol     | Parameter                            | Min | Limits<br>Typ | Max  | Units  | Conditions              |

|------------|--------------------------------------|-----|---------------|------|--------|-------------------------|

|            | Input low level                      | 2.0 |               | 0.8  | v<br>v |                         |

| Vih<br>Vol | Input high level<br>Output low level | 2.0 |               | 0.4  |        | lo⊾= 8.0 mA             |

| Vон        | Output high level                    | 2.4 |               |      | V V    | Iон = 8.0 mA            |

| lı.        | Input low current                    |     |               | -350 | μΑ     | Except crystal<br>input |

| Ьн         | Input high current                   |     |               | 1    | μΑ     | VIN=Vcc                 |

| lcc        | Operating current                    |     | 20            | 40   | mA     | No load.<br>DCLK=80MHz  |

| Rin        | Input pull-up resistance             | 15  | 20            | 25   | kΩ     |                         |

1

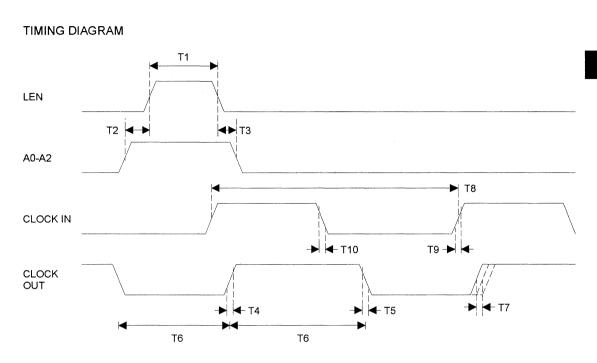

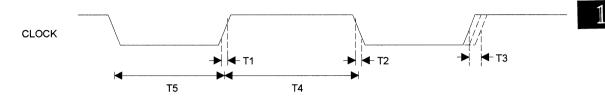

### AC ELECTRICAL CHARACTERISTICS

$\rm T_{A}=0^{\circ}$  - 70° C, Vcc=5.0 V  $\pm$  10% unless otherwise specified.

| Symbol                                                                | Parameter                                                                                                                                                                                                                                   | Min                                  | Limits<br>Typ                                | Max                                                  | Units                                            | Conditions                                                                        |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------|------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------|

| T1<br>T2<br>T3<br>T4<br>T5<br>T6<br>T6<br>T7<br>T7<br>T8<br>T9<br>T10 | Enable pulse width<br>Setup time data to enable<br>Hold time to data enable<br>Rise time<br>Fall time<br>Duty cycle<br>Duty cycle<br>Jitter 1 sigma<br>Jitter absolute<br>Input frequency<br>Input clock rise time<br>Input clock fall time | 20<br>20<br>10<br>40<br>45<br>14.318 | 1.5<br>1.5<br>48/52<br>48/52<br>±0.5<br>±0.2 | 3<br>3<br>60<br>55<br>±0.2<br>±0.5<br>32<br>20<br>20 | ns<br>ns<br>ns<br>%<br>%<br>%<br>Mhz<br>ns<br>ns | 0.8V - 2.0V, 15pF<br>2.0V - 0.8V, 15pF<br>1.4V switch point<br>Vcc/2 switch point |

| A2 | A1 | A0 | ST49C106-5* |        |  |  |  |

|----|----|----|-------------|--------|--|--|--|

|    |    |    | NOMINAL     | ACTUAL |  |  |  |

| 0  | 0  | 0  | 39.000      | 39.000 |  |  |  |

| 0  | 0  | 1  | 25.000      | 25.000 |  |  |  |

| 0  | 1  | 0  | 30.750      | 30.750 |  |  |  |

| 0  | 1  | 1  | 26.250      | 26.250 |  |  |  |

| 1  | 0  | 0  | 32.000      | 32.000 |  |  |  |

| 1  | 0  | 1  | 25.250      | 25.250 |  |  |  |

| 1  | 1  | 0  | 31.250      | 31.250 |  |  |  |

| 1  | 1  | 1  | 37.500      | 37.500 |  |  |  |

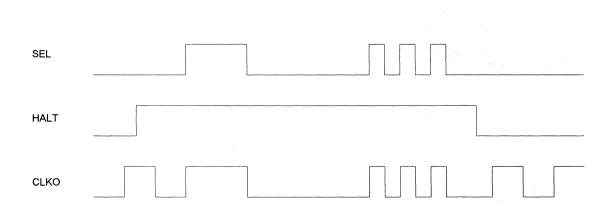

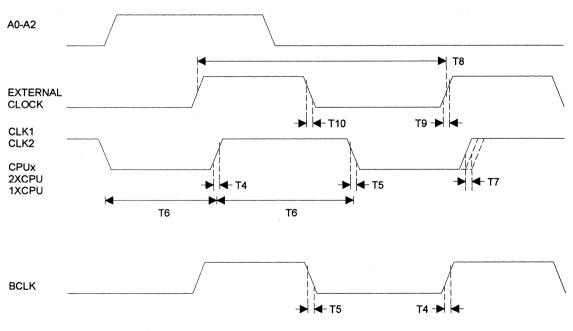

### TIMING DIAGRAM

Printed August 3, 1995

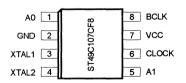

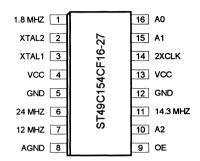

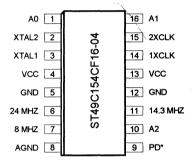

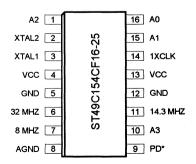

### PREPROGRAMMED CPU MOTHER BOARD FREQUENCY GENERATOR

### DESCRIPTION

The ST49C107 is a mask programmable monolithic analog CMOS device designed to generate two simultaneous clocks. One clock is either the BCLK (buffered reference clock) or programmable. The other clock (called CLOCK or 2XCLOCK in different versions) is programmable only. The output frequency can vary from 2 to 100MHz, with up to 16 single selectable preprogrammed frequencies stored in internal ROM.

The ST49C107 is designed to replace existing CPU mother board clocks generated from individual oscillators in order to reduce board space and number of oscillators. To provide high speed analog CMOS phase locked loop using 14.318 MHz system clock as the reference clock (note that reference clock can be changed to generate optional frequencies from a standard programmed device). The programmed clock outputs are selectable via four address lines ( two address lines for ST49C107-05).

### FEATURES

- · Provides reference clock and synthesized clock

- 5 to 32MHz input reference frequency

- Pin-to-pin compatible to Avasem AV9107

- Programmable analog phase locked loop

- Low power single 5V CMOS technology

- Up to 16 frequencies stored internally

- 8/14 pin DIP or SOIC package.

| ORDERING INFORMATION |             |                       |  |  |  |  |

|----------------------|-------------|-----------------------|--|--|--|--|

| Part number          | Package     | Operating temperature |  |  |  |  |

| ST49C107CP8          | Plastic-DIP | 0 ° C to +70° C       |  |  |  |  |

| ST49C107CF8          | SOIC        | 0° C to +70° C        |  |  |  |  |

| ST49C107CP14         | Plastic-DIP | 0 ° C to +70° C       |  |  |  |  |

| ST49C107CF14         | SOIC        | 0° C to +70° C        |  |  |  |  |

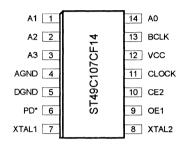

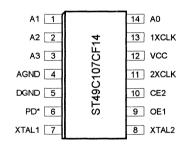

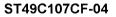

#### **SOIC Package**

#### ST49C107CF-03

#### ST49C107CF-05

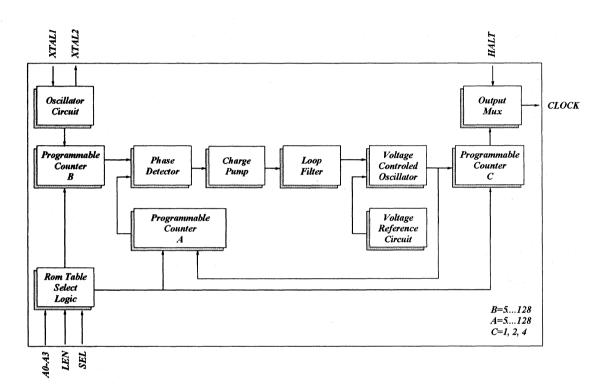

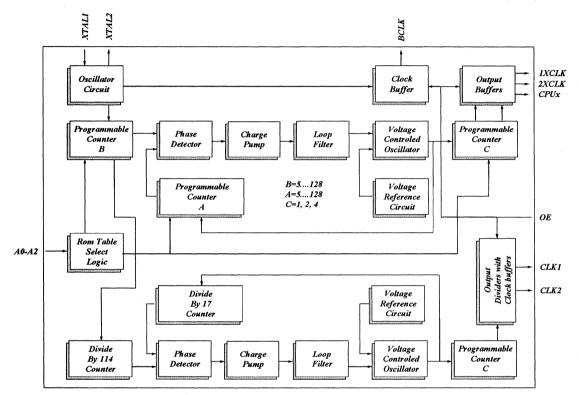

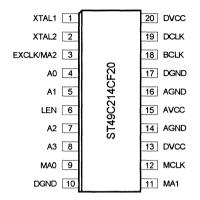

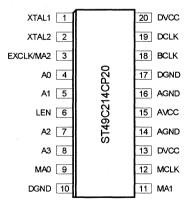

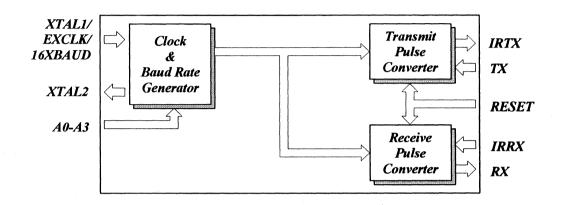

### **BLOCK DIAGRAM**

1

### SYMBOL DESCRIPTION (ST49C107-03 package)

| Symbol | Pin | Signal Type | Pin Description                                                                                                                                                                                                                            |

|--------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | 1*  | I           | Frequency select address input 2.                                                                                                                                                                                                          |

| A2     | 2*  | I           | Frequency select address input 3.                                                                                                                                                                                                          |

| A3     | 3*  | I           | Frequency select address input 4.                                                                                                                                                                                                          |

| AGND   | 4   | 0           | Analog ground.                                                                                                                                                                                                                             |

| DGND   | 5   | 0           | Digital ground.                                                                                                                                                                                                                            |

| PD     | 6*  | I           | Power-Down (Active low). Shuts off chip when low.                                                                                                                                                                                          |

| XTAL1  | 7   | I           | Crystal or External Clock input. A crystal can be connected<br>to this pin and XTAL2 pin to generate internal phase locked<br>loop reference clock. For external 14.318 MHz clock,<br>XTAL2 is left open or used as buffered clock output. |

| XTAL2  | 8   | ο           | Crystal output.                                                                                                                                                                                                                            |

| OE1    | 9*  | Ι           | Buffered clock Output Enable (Active high). BCLK output is three stated when this pin is low.                                                                                                                                              |

| OE2    | 10* | I           | Clock Output Enable (Active high). CLOCK output is three stated when this pin is low.                                                                                                                                                      |

| CLOCK  | 11  | 0           | Programmed output clock.                                                                                                                                                                                                                   |

| vcc    | 12  | I           | Positive supply voltage. Single +5 volts.                                                                                                                                                                                                  |

| BCLK   | 13  | ο           | Buffered crystal clock output.                                                                                                                                                                                                             |

| A0     | 14* | I.          | Frequency select address input 1.                                                                                                                                                                                                          |

\* Have internal pull-up resistors on inputs.

# ST49C107

### SYMBOL DESCRIPTION (ST49C107-04 package)

| Symbol | Pin      | Signal Type      | Pin Description                                                                                                                                                                                                                            |

|--------|----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | 1*       | l                | Frequency select address input 2.                                                                                                                                                                                                          |

| A2     | 2*       | I                | Frequency select address input 3.                                                                                                                                                                                                          |

| A3     | 3*       | I                | Frequency select address input 4.                                                                                                                                                                                                          |

| AGND   | 4        | 0                | Analog ground.                                                                                                                                                                                                                             |

| DGND   | 5        | 0                | Digital ground.                                                                                                                                                                                                                            |

| PD     | 6*       | 1                | Power-Down (Active low). Shuts off chip when low.                                                                                                                                                                                          |

| XTAL1  | <b>7</b> | 1                | Crystal or External Clock input. A crystal can be connected<br>to this pin and XTAL2 pin to generate internal phase locked<br>loop reference clock. For external 14.318 MHz clock,<br>XTAL2 is left open or used as buffered clock output. |

| XTAL2  | 8        | 0                | Crystal output.                                                                                                                                                                                                                            |

| OE1    | 9*       | . 1 .            | 1X-CLOCK Output Enable (Active high). 1X-CLOCK output is three stated when this pin is low.                                                                                                                                                |

| OE2    | 10*      | Let a            | 2X-CLOCK Output Enable (Active high). 2X-CLOCK output is three stated when this pin is low.                                                                                                                                                |

| 2XCLK  | 11       | 0                | Programmed output clock.                                                                                                                                                                                                                   |

| vcc    | 12       | I                | Positive supply voltage. Single +5 volts.                                                                                                                                                                                                  |

| 1XCLK  | 13       |                  | 2X-CLOCK Divide-by-two output.                                                                                                                                                                                                             |

| A0     | 14*      | ана <b>н</b> а в | Frequency select address input 1.                                                                                                                                                                                                          |

\* Have internal pull-up resistors on inputs.

### SYMBOL DESCRIPTION (ST49C107-05 package)

| Symbol | Pin | Signal Type | Pin Description                                                                                                                                                                                                                            |

|--------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0     | 1   | I           | Frequency select address input 1.                                                                                                                                                                                                          |

| A1     | 5   | 1           | Frequency select address input 2.                                                                                                                                                                                                          |

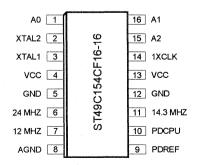

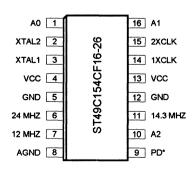

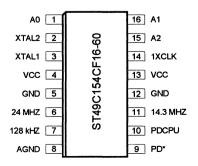

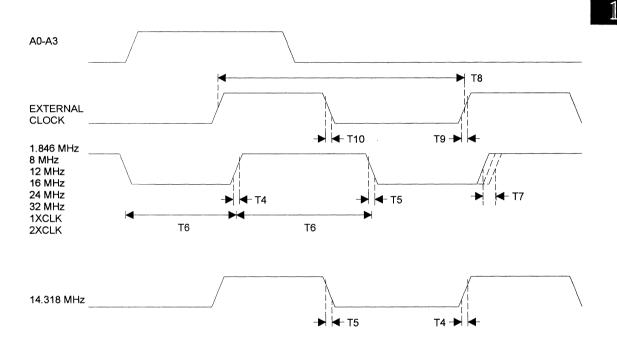

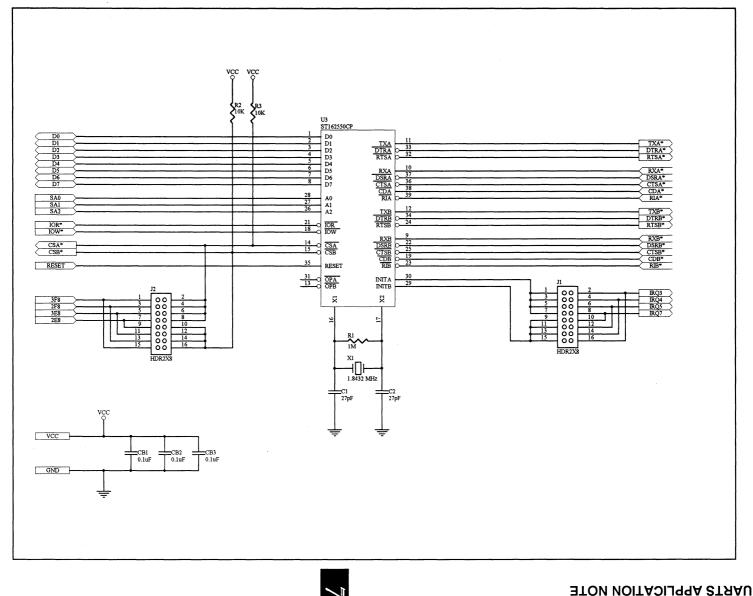

| GND    | 2   | 0           | Supply ground.                                                                                                                                                                                                                             |