# MICROPROCESSOR DATA S and PERIPHERALS

# MICROPROCESSORS and PERIPHERALS

DATA BOOK

# - CONTENTS ----

| GENERAL INFORMATION                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Contents                                                                                                                                                                                                                                                               |

| CHAPTER 1 - 6800 MICROPROCESSORS                                                                                                                                                                                                                                       |

| 6800 Microprocessors Selection Guide                                                                                                                                                                                                                                   |

| EF6802*EF6808 Microprocessor with Clock and Optional RAM1-3EF6801*EF6803 Microcomputer/Microprocessor (MCU/MPU)1-27EF6801U4*EF6803U4 Microcomputer/Microprocessor (MCU/MPU)1-67EF6809 8-Bit Microprocessor Unit (MPU)1-111EF6809E 8-Bit Microprocessor Unit (MPU)1-151 |

| CHAPTER 2 - 6800 PERIPHERALS                                                                                                                                                                                                                                           |

| 6800 Peripherals Selection Guide2-1                                                                                                                                                                                                                                    |

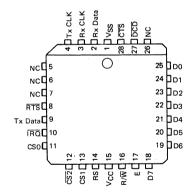

| EF6821 Peripheral Interface Adapter (PIA)2-3EF6840 Programmable Timer Module (PTM)2-15EF6850 Asynchronous Communications Interface Adapter (ACIA)2-31EF6854 Advanced Data-Link Controller (ADLC)2-41                                                                   |

| CHAPTER 3 - 68000 MICROPROCESSORS                                                                                                                                                                                                                                      |

| 68000 Microprocessors Selection Guide                                                                                                                                                                                                                                  |

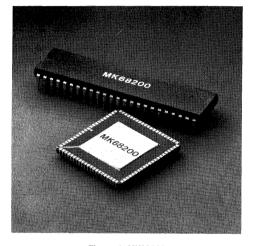

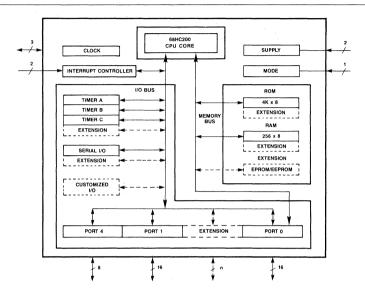

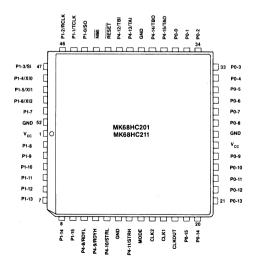

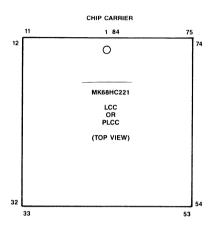

| TS6800016/32-Bit Microprocessor3-3TS680088/32-Bit Microprocessor with 8-Bit Data Bus3-95MK68200FAMILY16-Bit Single-Chip Microcomputers3-191MK68HC200FAMILY16-Bit Single-Chip Microcomputers3-265                                                                       |

| CHAPTER 4 - 68000 PERIPHERALS                                                                                                                                                                                                                                          |

| 68000 Peripherals Selection Guide4-1                                                                                                                                                                                                                                   |

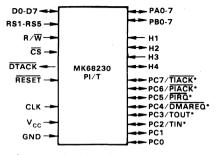

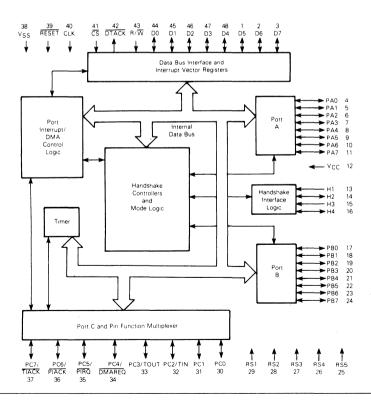

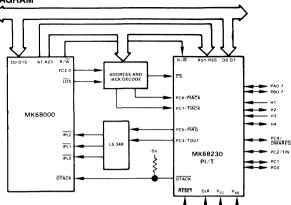

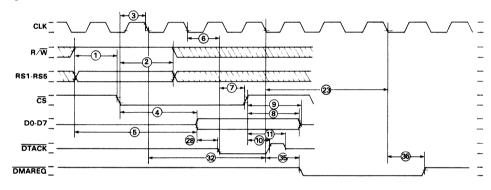

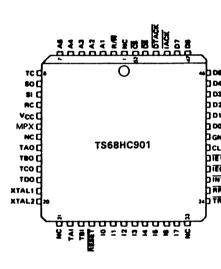

| MK68230 Parallel Interface/Timer4-3MK68451 Memory Management Unit4-13MK68564 Serial Input/Output Controller4-17MK68901 Multi-Function Peripheral4-29TS68HC901 HCMOS Multi-Function Peripheral4-59                                                                      |

| CHAPTER 5 - MICROCOMPUTER PERIPHERALS                                                                                                                                                                                                                                  |

| Microcomputer Peripherals Selection Guide5-1                                                                                                                                                                                                                           |

| MK3801 Serial Timer Interrupt Controller5-3MK3835-MK3831 CMOS Microcomputer Clock/RAM5-19                                                                                                                                                                              |

# - CONTENTS -

| Pa CHAPTER 6 - CRT CONTROLLER                          | ıge |

|--------------------------------------------------------|-----|

| CHAPTER 0 - CRI CONTROLLER                             |     |

| CRT Controllers Selection Guide                        | 6-1 |

| EF9345 Single Chip Semi-Graphic Display Processor      | 6-3 |

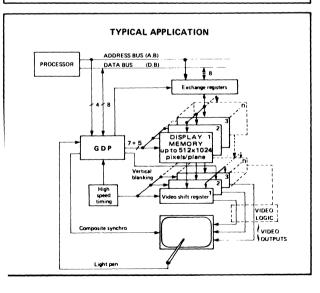

| EF9367 Graphic Display Processor (GDP)6-               |     |

| EF9369 Single Chip Color Palette6-                     | -81 |

| TS68483 Advanced Graphic and Alphanumeric Controller6- | -97 |

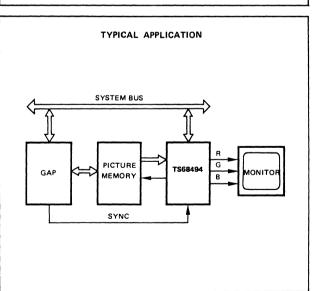

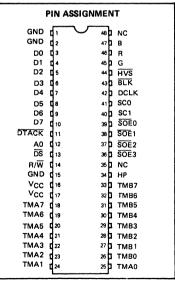

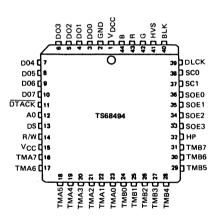

| TS68494 Palette and Serial Port Controller             |     |

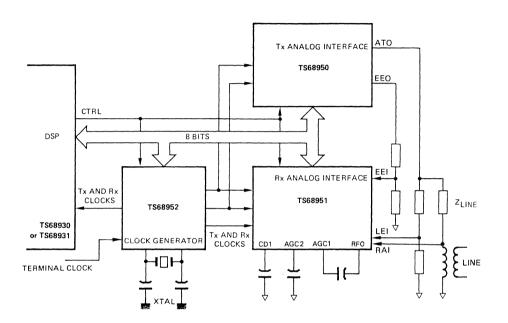

| CHAPTER 7 - DIGITAL SIGNAL PROCESSING ICs              |     |

|                                                        |     |

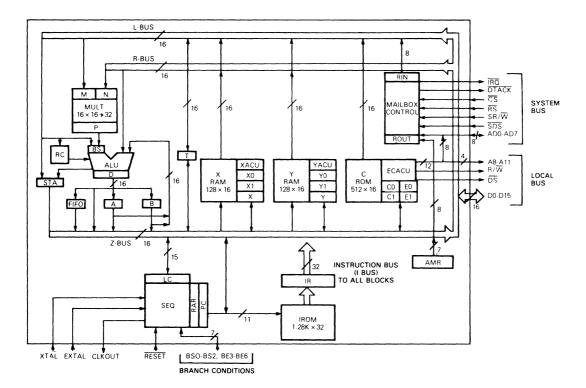

| Digital Signal Processing ICs Selection Guide          | 7-1 |

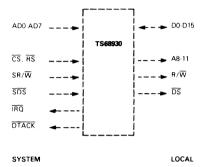

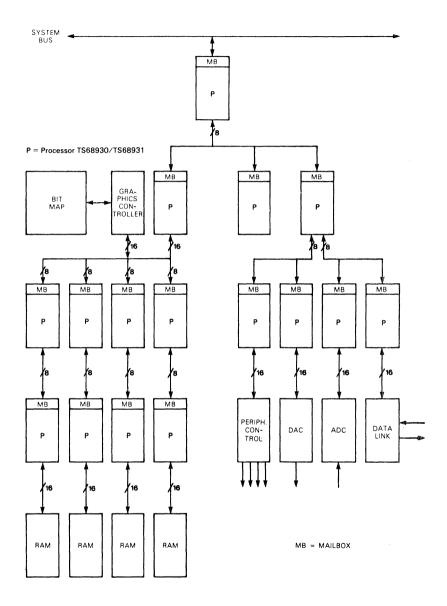

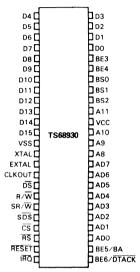

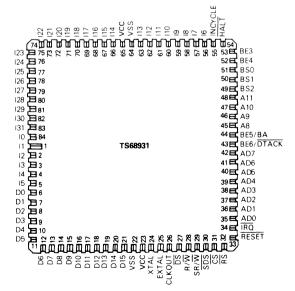

| TS68930 • TS68931 Programmable Signal Processor        | 7-3 |

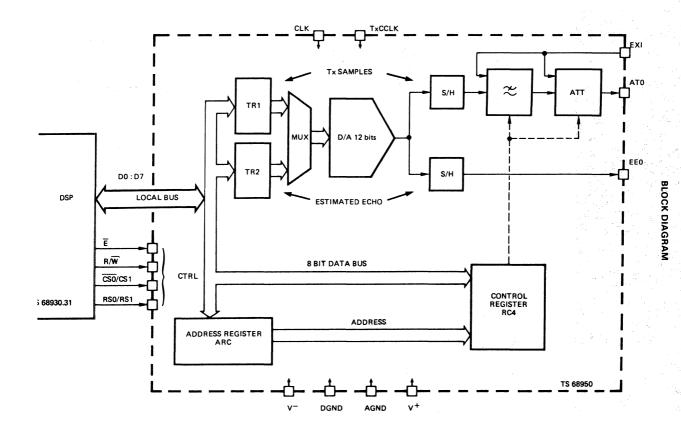

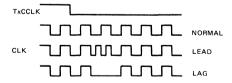

| TS68950 Modem Transmit Analog Interface7-              |     |

| TS68951 Modem Receive Analog Interface                 |     |

| TS68952 Modem Transmit/Receive Clock Generator7-       |     |

| CHAPTER 8 - DATA COMMUNICATIONS ICs                    |     |

| CHAPTER 0 - DATA COMINIUNICATIONS ICS                  |     |

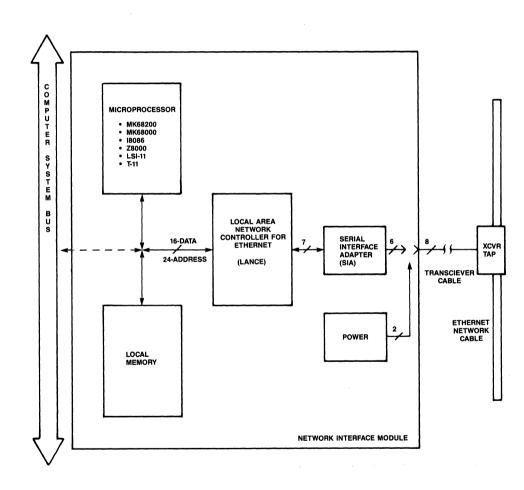

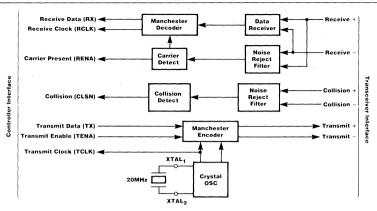

| MK68590 Local Area Network Controller for Ethernet     | 8-1 |

| MK68591/2 Serial Interface Adapter8-                   | -17 |

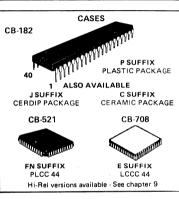

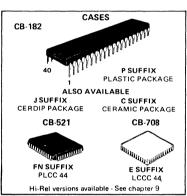

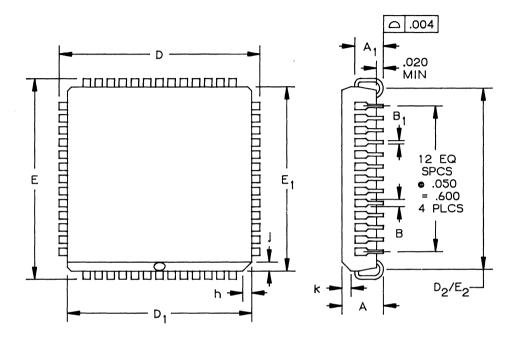

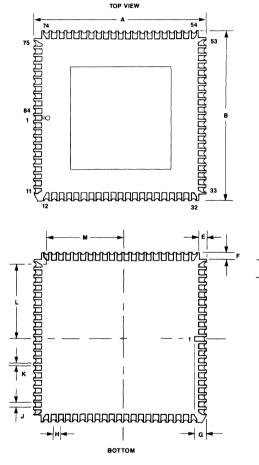

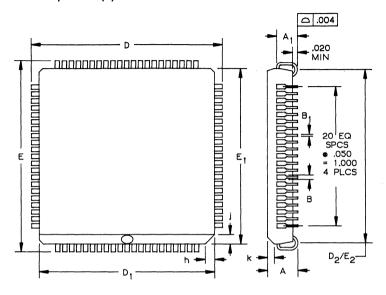

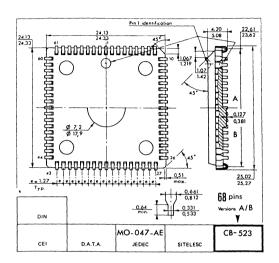

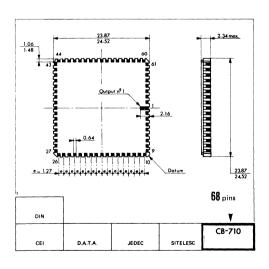

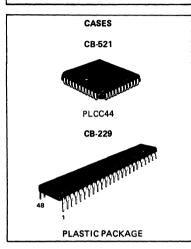

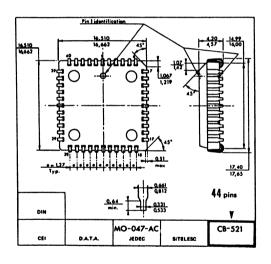

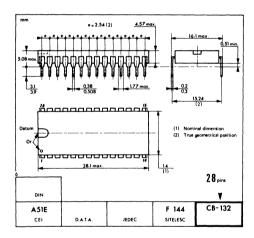

| CHAPTER 9 - SURFACE MOUNTED DEVICES                    |     |

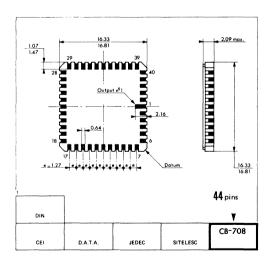

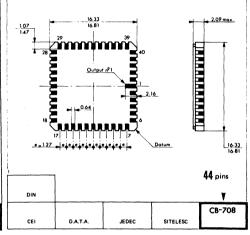

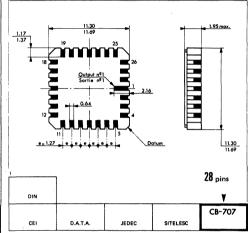

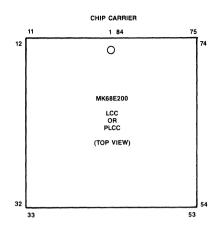

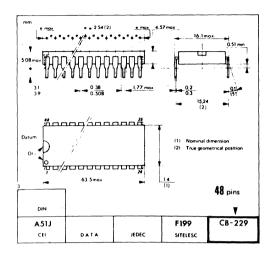

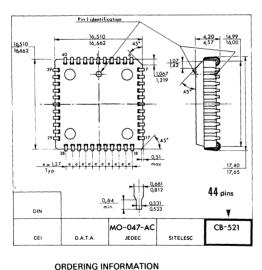

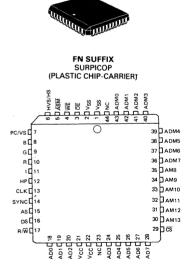

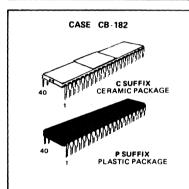

| LCC Selection Guide                                    | 9-1 |

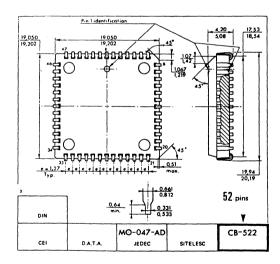

| PLCC Selection Guide                                   |     |

# - ALPHANUMERICAL INDEX -

| Part number | Page  | Part number | Page  | Part number | Page  |

|-------------|-------|-------------|-------|-------------|-------|

| EF6802      | 1-3   | MK3831      | 5-19  | TS68008     | 3-95  |

| EF6803      | 1-27  | MK3835      | 5-19  | MK68230     | 4-3   |

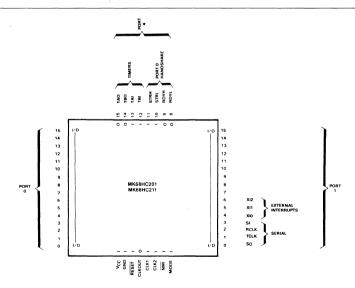

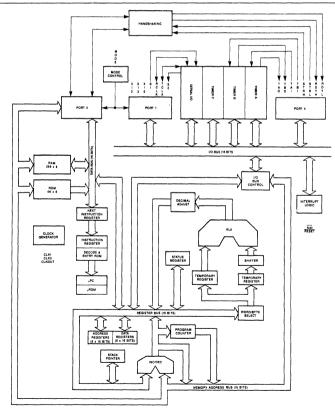

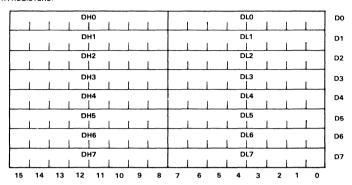

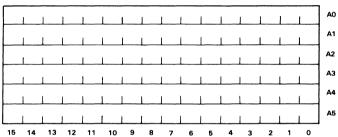

| EF6803U4    | 1-67  | MK68201     | 3-191 | TS68483     | 6-97  |

| EF6809      | 1-111 | MK68211     | 3-191 | TS68494     | 6-143 |

| EF6809E     | 1-151 | MK68451     | 4-13  | TS68930     | 7-3   |

| EF6821      | 2-3   | MK68564     | 4-17  | TS68931     | 7-3   |

| EF6840      | 2-15  | MK68901     | 4-29  | TS68950     | 7-55  |

| EF6850      | 2-31  | MK68E201    | 3-191 | TS68951     | 7-69  |

| EF6854      | 2-41  | MK68E211    | 3-191 | TS68952     | 7-93  |

| EF9345      | 6-3   | MK68HC201   | 3-265 | TS68HC901   | 4-59  |

| EF9367      | 6-49  | MK68HC211   | 3-265 |             |       |

| EF9369      | 6-81  | MK68HCE221  | 3-265 |             |       |

| MK3801      | 5-3   | TS68000     | 3-3   |             |       |

# THOMSON - MOSTEK TECHNICAL SUPPORT, PRODUCT MARKETING

FOR INTEGRATED CIRCUITS:

(Corporate Headquarters) Carrollton, TX 75006 214/466-6000 TWY 910-860-5437

FOR DISCRETE DEVICES AND RF & MICROWAVE TRANSISTORS: 16 Commerce Drive

Montgomeryville, PA 18936-1002 215/362-8500

FAY 215/362-1293

FOR PASSIVE COMPONENTS:

6203 Variel Avenue, Unit A PO. Box 4051 Woodland Hills, CA 91367 FAX 818/702-0725

FOR SPECIAL PRODUCTS: 301 Route 17 North Rutherford, NJ 07070

#### U.S. AND CANADIAN SALES OFFICES:

#### WESTERN AREA:

Thomson Components - Mostek Corporation

2540 Mission College Blvd. Suite 104 Santa Clara, CA 95054 408/970-8585

Thomson Components - Mostek Corporation

18004 Skypark Circle Suite 140 Irvine, CA 92714 714/250-0455 FAX 714/261-1505

FAX 408-970-8737

Thomson Components - Mostek Corporation

6203 Variel Ave. Unit A, P.O. Box 4051 Woodland Hills, CA 91367 818/887-1010 FAX 818/702-0725

Thomson Components - Mostek Corporation

1107 North East 45th St. Suite 411 Seattle, WA 98105 206/632-0245 FAX 206/633-5413

Thomson Components - Mostek Corporation

601 South Bowen St Longmont, CO 80501 303/449-9000 FAX 303/651-7976

Thomson Components - Mostek Corporation

7950 East Redfield Rd Suite 160 Scottsdale, AZ 85260 602/998-1580 FAX 602/483-2303

Thomson Components - Mostek Corporation

7155 SW Varns' St Tigard, OR 97223-8057 503/620-5517 FAX 503/639-3591

FOR ALL OTHER COUNTRIES Thomson Semiconducteurs 43, Avenue de L'Europe

78140 Vélizy-Villacoublay/France Tél: (1) 39 46 97 19/Télex: 204 780 F or contact Corporate Headquarters

#### CENTRAL AREA:

Thomson Components - Mostek Corporation

1310 Electronics MS1137 Carrollton, TX 75006 214/466-8844 TWX 910-860-5437

Thomson Components - Mostek Corporation

6100 Green Valley Drive Suite 130 Bloomington MN 55438 612/831-2322 FAX 612/831-8195

Thomson Components - Mostek Corporation 1827 Walden Office Square

#430 Schaumburg, IL 60173 312/397-6550 FAX 312/397-4066

Thomson Components - Mostek Corporation

3215 Steck Ave. Suite 202 Austin, TX 78758 512/451-4061 TWX 910-874-2007

Thomson Components - Mostek Corporation

26677 W. 12 Mile Rd. Suite #141 Southfield, MI 48034 313/354-5840 FAX 313/354-3370

#### CANADA

Thomson CSF Canada Semiconductor Division 1000 Sherbrooke West

Suite 2340 Montreal, Quebec H3A 3G4 514/288-4148 FAX 514/288-8987

Thomson Components - Mostek Corporation 44 Rosebud Ave

Brampton, Ontario L6X 2W5 416/454-5252 FAX 416/454-4328

#### EASTERN AREA:

Thomson Components - Mostek Corporation

201/438-2300

FAX 201/438-1774

83 Cambridge Street Suite 2A Burlington, MA 01803 617/273-3310 FAX 617/272-2467

Thomson Components - Mostek Corporation

The Pavilions at Greentree Route #73, Suite 101 Marlton, NJ 08053 609/596-9200 FAX 609/424-7437

Thomson Components - Mostek Corporation

4414 Evangel Cr. #C Huntsville, AL 35816 205/830-9036 FAX 205/830-9038

Thomson Components - Mostek Corporation 387 Hooker Avenue

Office No. 2 Poughkeepsie, NY 12603 914/454-8813 FAX 914/454-1320

Thomson Components - Mostek Corporation

5890 Sawmill Rd. Suite 204 Dublin, Ohio 43017 614/761-0676 FAX 614/761-2305

Thomson Components - Mostek Corporation 6045 Atlantic Blvd.

Suite 104 Norcross, GA 30071 404/662-1588 FAX 404/662-1561

# U.S. AND CANADIAN REPRESENTATIVES

#### CONNECTICUT

Scientific Components\* 1185 S. Main St. Cheshire, CT 06410 (203) 272-2963 FAX (203) 271-3048

#### FLORIDA

Lawrence Associates\* 5021 N. Dixie Hwy. Boca Raton, FL 33431 (305) 368-7373

Sales Engineering Concepts, Inc. 926 Great Pond Dr. Suite 2002 Altamonte Springs, FL 32714 (305) 682-4800 FAX (305) 682-6491

Sales Engineering Concepts, Inc. 1000 S. Federal Hwy. Suite 204 Deerfield Beach, FL 33441 (305) 426-4601 TWX 510-600-7740

#### ILLINOIS

Eagle Technical Sales, Inc. 1805 B. Hicks Rd. Rolling Meadows, IL 60008 (312) 991-0700

#### INDIANA

M/S Sales Associates, Inc.\*

7319 W. Jefferson Blvd.

Ft. Wayne, IN 46804

(219) 436-3023

FAX (219) 436-3026

M/S Sales Associates, Inc. 1425 E. 86th St. Indianapolis, IN 46240 (317) 257-8916

#### IOWA

Rep Associates\* 980 Arica Ave. Marion, IA 52302 (319) 373-0152

#### KANSAS

Rush & West Associates 107 N. Chester Street Olathe, KS 66061 (913) 764-2700 TWX 910-380-8110

#### MARYLAND

Tri-Mark Inc.\*

1410 Crain Hwy. NW

Glen Burnie, MD 21061

(301) 761-6000

FAX (301) 761-6006

#### MASSACHUSETTS

A/D Nova Sales, Inc.\*

83 Cambridge St.

Suite 2D

Burlington, MA 01803

(617) 270-9600

FAX (617) 272-2467

Conti-Younger Assoc.\*

12 Blanchard Rd.

Burlington, MA 01803

(617) 273-1583

FAX (617) 270-0301

#### MICHIGAN

Electronic Sources, Inc.\* 8014 W. Grand River Suite 6 Brighton, MI 48116 (313) 227-3598 FAX (313) 227-5655

Centech, Inc.\* 10312 E. 63rd Terrace Raytown, MI 64133 (816) 358-8100

#### MINNESOTA

Horizon\* 8053 East Bloomington Freeway Bloomington, MN 55420. (612) 884-6515 FAX (612) 888-3073

#### MISSOURI

Rush & West Associates\* 2170 Mason Rd. St. Louis, MO 63131 (314) 965-3322 TWX 910-752-653 TELEX 752 653

#### **NEW JERSEY**

Tritek Sales, Inc.\*

21 E. Euclid Ave.

Haddonfield, NJ 08033

(609) 429-1551

TWX 215-627-0149 (Philadelphia Line)

TWX 710-896-0881

NE Components\* 189-191 Godwin Ave. Wyckoff, NJ 07481 (201) 848-1100

#### **NEW YORK**

Empire Technical Assoc.

33 West State St.

Suite 211B

Binghamton, NY 13901

(607) 772-0651

Empire Technical Assoc. 1551 E. Genesse St. Skaneateles, NY 13152 (315) 685-5703

GT Sales\* 34 Grand Blvd. Brentwood, NY 11717 (516) 231-0270 FAX (516) 273-1247

#### OHIO

Five Star Electronics\* 6200 S.O.M. Center Road Suite B 21 Solon, OH 44139 (216) 349-1611

Tom Mulligan Co.\* 166 N.W. Professional Plaza Columbus, OH 43220 (614) 457-2242

#### PENNSYLVANIA M. Lader Company\*

M. Lader Company\* 456 Germantown Pike Lafayette Hill, PA 19444 (215) 825-3177

#### WISCONSIN

Heartland Technical Marketing\* 3846 Wisconsin Ave. Milwaukee, WI 53208 (414) 931-0606

#### CANADA

Solution Electronic Sales\* 100A 3380 Maquinna Dr. Vancouver, B.C. V5S 4C9 (604) 438-0679

<sup>\*</sup> Home Office

#### ALABAMA

Marshall Industries 3313 S. Memorial Pkwy. Huntsville, AL 35801 (205) 881-9235

Quality Components, S.E. 4900 University Square #207 Huntsville, AL 35817 (205) 830-1881

Pioneer Technologies Group 4825 University Square Huntsville, AL 35805 (205) 837-9300

Schweber Electronics 4930-A Corporate Drive Huntsville, AL 35805 (205) 895-0480

#### ARIZONA

Kierulff Electronics 4134 E. Wood Street Phoenix, AZ 85040 (602) 437-0750

Marshall Industries 835 West 22nd St. Tempe, AZ 85282 (602) 968-6181

Schweber Electronics 11049 North 23rd Drive Suite 100 Phoenix, AZ 85029 (602) 997-4874

#### ARKANSAS

See Oklahoma

# CALIFORNIA Integrated Electronics Corp.

7000 Franklin Blvd., Suite 625 Sacramento, CA 95823 (916) 424-5297

Integrated Electronics Corp. 2170 Paragon Drive San Jose, CA 95131 (408) 435-1000

ITAL Sales 15405 Proctor Avenue City of Industry, CA 91745 (818) 968-8515

Kierulff Electronics 9800 Variel Avenue Chatsworth, CA 91311 (818) 407-2500

Kierulff Electronics 5650 Jillson St. Los Angeles, CA 90040 (213) 725-0325

Kierulff Electronics 8797 Balboa Avenue San Diego, CA 92123 (619) 278-2112

Kierulff Electronics 1180 Murphy Avenue San Jose, CA 95131 (408) 971-2600

Kierulff Electronics 14101 Franklin Avenue Tustin, CA 92680 (714) 731-5711

Marshall Industries One Morgan Irvine. CA 92715 (714) 458-5395

Marshall Industries 9710 DeSoto Avenue Chatsworth, CA 91311 (818) 407-0101

Marshall Industries 3039 Kilgore Ave., #140 Rancho Cordova, CA 95670 (916) 635-9700

Marshall Industries 10105 Carroll Canyon Rd. San Diego, CA 92131 (619) 578-9600

Marshall Industries 336 Los Coches St. Milpitas, CA 95035 (408) 943-4600

Schweber Electronics 21139 Victory Blvd. Conoga Park, CA 91303 (818) 999-4702

Schweber Electronics 1225 West 190th Street Suite 360 Gardena, CA 90248 (213) 327-8409

Schweber Electronics 17822 Gillette Avenue Irvine, CA 92714 (714) 863-0264 FAX (714) 863-0200 (X500)

Schweber Electronics 1771 Tribute Rd. Suite B Sacramento, CA 95815 (916) 929-9732 FAX (916) 929-5608

Schweber Electronics 6750 Nancy Ridge Drive San Diego, CA 92121 (619) 450-0454 TWX 910-335-1155

Schweber Electronics 90 E. Tasman Drive San Jose, CA 95131 (408) 946-7171

Zeus Components 1130 Hawk Circle Anaheim, CA 92807 (714) 632-6880 TWX 910-591-1696 FAX (714) 630-8770

Zeus Components 1580 Old Oakland Road Suite C205/C206 San Jose, CA 95131 (408) 998-5121 TWX 408-628-96083 FAX (408) 998-0285

#### COLORADO

Integrated Electronics Corp. 5750 N. Logan Street Denver, CO 80216 (303) 292-6121

Kierulff Electronics 7060 South Tuscon Way Englewood, CO 80112 (303) 790-4444

Marshall Industries 7000 North Broadway Denver, CO 80221 (303) 427-1818

Schweber Electronics 8955 E. Nicholas, Bldg. 2 Englewood, CO 80221 (303) 799-0258

# CONNECTICUT Greene-Shaw

1475 Whalley Avenue New Haven, CT 06525 (203) 397-0710 TWX 92-2498

Marshall Industries 20 Sterling Drive Barnes Industrial Park, N. P.O. Box 200 Wallingford, CT 06492-0200 (203) 265-3822

Pioneer-Standard 112 Main Street Norwalk, CT 06851 (203) 853-1515 TWX 710-468-3373 FAX (203) 838-9901

Schweber Electronics Commercial Industrial Park Finance Drive Danbury, CT 06810 (203) 748-7080 TWX 710-456-9405

# DEL AWARE

See New Jersey Pennsylvania

#### FI ORIDA

All American Semiconductor 16251 N.W. 54th Avenue Miami, FL 33014 (305) 621-8282 800-327-6237

Marshall Industries 4205 34th St., S.W. Orlando, FL 32811 (305) 841-1878 (305) 841-1878

Pioneer Technologies Group 337 S. North Lake, #1000 Altamonte Springs, FL 32701 (305) 834-9090 TWX 810-853-0284

Pioneer Technologies Group 674 S. Military Trail Deerfield Beach, FL 33441 (305) 428-8877 TWX 510-955-9653

Schweber Electronics 215 North Lake Blvd. Altamonte Springs, FL 32701 (305) 331-7555 TWX 510-954-0304

Schweber Electronics 3665 Park Central Blvd. N. Pompano Beach, FL 33064 (305) 977-7511 TWX 510-954-0304

Zeus Components 1750 West Broadway Suite 114 Oviedo, FL 32765 (305) 365-3000 TWX 910-380-7430 FAX (305) 365-2356

#### GEORGIA

Dixie Electronics 1234 Gordon Park Road Augusta, GA 30901 (404) 722-2055

Pioneer Technologies Group 3100 F. Northwoods Place Norcross, GA 30071 (404) 448-1711 TWX 810-766-4515

**Quality Components** 6145 N. Belt Parkway #B Norcross, GA 30071 (404) 449-9508 TWX 510-601-5297 629-32421

Schweber Electronics 303 Research Drive Suite 210 Norcross, GA 30092 (404) 449-9170 TWX 810-766-1592

#### ILLINOIS

Advent Electronics 7110-16 N. Lyndon St. Rosemont, IL 60018 (312) 297-6200

Kierulff Electronics 1140 W. Thorndale Ave. Itasca, IL 60143 (312) 250-0500

Marshall Industries 1261 Wiley Road

Schaumburg, IL 60195 (312) 490-0155

Pioneer-Standard 1551 Carmen Drive Elk Grove Village, IL 60007 (312) 437-9680

Schweber Electronics 904 Cambridge Drive Elk Grove Village, IL 60007 (312) 364-3750 TWX 910-222-3453

#### INDIANA

Advent Electronics 8446 Moller Road Indianapolis, IN 46268 (317) 872-4910 TWX 810-341-3228

Marshall Industries 6990 Corporate Dr. Indianapolis IN 46278 (317) 297-0483

Pioneer-Standard 6408 Castleplace Drive Indianapolis, IN 46250 (317) 849-7300 TWY 810-260-1794

#### IOWA

Advent Electronics 682 58th Avenue, Ct. SW Cedar Rapids, IA 52404 (319) 363-0221 TWX 910-525-1337

Schweber Electronics 5270 North Park Place, NE Cedar Rapids, IA 52402 (319) 373-1417

#### KANSAS

Marshall Industries 8321 Melrose Dr. Lenexa, KS 66214 (913) 492-3121

Schweber Electronics 10300 West 103rd Street Suite 200 Overland Park, KS 66214 (913) 492-2922

#### KENTUCKY See Indiana

LOUISIANA

#### See Texas

MAINE See Massachusetts

#### MARYLAND

Marchall Industries 8445 Helgerman Court Gaithersburg, MD 20877 (301) 840-9450

Pioneer Technologies Group 9100 Gaither Road Gaithersburg, MD 20877 (301) 921-0660 TWX 710-828-0545

Schweber Electronics 9330 Gaither Road Gaithersburg, MD 20877 (301) 840-5900 TWX 710-828-9749

Zeus Components 8930-A Route 108 Columbia MD 21045 (301) 997-1118 TWX 910-380-3554 FAX (301) 964-9784

# MASSACHUSETTS

Greene-Shaw 70 Bridge Street Newton, MA 02195 (617) 969-8900 TWX 92 2498

Kierulff Electronics 13 Fortune Drive Billerica MA 01821 (617) 667-8331

Lionex Corporation 36 Jonspin Road Wilmington, MA 01887 (617) 657-5170 FAX (617) 657-6008

Marshall Industries One Wilshire Road Burlington, MA 01803 (617) 272-8200

Pioneer-Standard 44 Hartwell Ave Lexington, MA 02173

Schweber Electronics 25 Wiggins Avenue Bedford, MA 01730 (617) 275-5100 TWX 710-326-0268

Zeus Components 429 Marrett Road Lexington, MA 02173 (617) 863-8800 TWX 710-326-7604 FAX (617) 863-8807

#### MICHIGAN

Advent Electronics 24713 Crestview Ct. Farmington Hills, MI 48018 (313) 477-1650

Pioneer-Standard 4505 Broadmoor Avenue SE Grand Rapids, MI 49508 (616) 698-1800 TWX 510-600-8456

Pioneer-Standard 13485 Stamford Livonia, MI 48150 (313) 525-1800 TWX 810-242-3271

Schweber Electronics 12060 Hubbard Ave. CN3306 Livonia, MI 48150 (313) 525-8100 TWX 810-242-2983

#### MINNESOTA

Kierulff Electronics 7667 Cahill Road Edina, MN 55435 (612) 941-7500

Marshall Industries 3800 Annapolis Lane Plymouth, MN 55441 (612) 559-2211

Pioneer Standard 10203 Bren Road East Minnetonka, MN 55343 (612) 935-5444 TWX 910-576-2738

Schweber Electronics 7424 W 78th Street Edina, MN 55435 (612) 941-5280 TWX 910-576-3167

# MISSISSIDD

See Texas

#### MISSOURI

Kierulff Electronics 11804 Rorman Drive St. Louis. MO 63146 (314) 997-4956 TWX 910-762-072

Schweber Electronics 502 Earth City Expressway Suite 203 Earth City, MO 63045 (314) 739-0526 TWX 43-4065

#### MONTANA See California

NERRASKA See lowa

# NEW HAMPSHIRE

Schweber Flectronics Bedford Farms Bldg. #2 Manchester NH 03102 (603) 625-2250 TWX 710-220-7572 FAX (603) 625-5710

#### NEW JERSEY Kierulff Flectronics 37 Kulick Boad Fairfield N.I 07006

(201) 575-6750 Marshall Industries 101 Fairfield Rd Fairfield N.I 07006

(201) 882-0320 Pioneer-Standard 45 Route 46 Pine Brook, NJ 07058 (201) 575-3510

Schweber Electronics 18 Madison Road Fairfield N I 07006 (201) 227-7880 TWX 710-734-4305

TWX 710-734-4382

Solid State 46 Farrand Street Bloomfield, NJ 07003 (201) 429-8700 TWX 710-994-4780 FAX (201) 429-8683

#### NEW YORK

Add Electronics 7 Adler Drive E. Syracuse, NY 13057 (315) 437-0300

Add Electronics 7375 Pittsford-Victor Rd Victor, NY 14564

Marshall Industries 129 Brown St. Johnson City, NY 13790

Marshall Industries 1280 Scottsville Rd Rochester NY 14624

Nu-Horizons Electronics 6000 New Horizons Blvd. N. Amityville, NY 11701 (516) 226-6000

Pioneer-Standard 840 Fairport Park Fairport, NY 14450 (716) 381-7070 TWX 510-253-7001 FAX (716) 381-5955

Pioneer-Standard 1806 Vestal Pkwy. East Vestal, NY 13850 (607) 748-8211 TWX 510-252-0893

Pioneer-Standard Crossways Park West Woodbury, NY 11797 (516) 921-8700 TWÝ 510-221-2184 FAX (516) 921-2143

Schweber Flectronics 3 Townline Circle Rochester, NY 14623 (716) 424-2222 TWX 710-541-0601

Schweher Flectronics Jericho Turnpike Westbury, NY 11590 (516) 334-7474 TWX 510-220-1365

Zeus Components 100 Midland Avenue Port Chester, NY 10573 (914) 937-7400 TWX 710-567-1248 FAX (914) 937-2553

#### NORTH CAROLINA

Dixie Electronics 2220 S. Tryon Street Charlotte, NC 28234 (704) 377-4348

Dixie Electronics 1021 R. Burke St Winston-Salem, NC 27102 (919) 724-5961

Hammond Electronics 2923 Pacific Avenue Greensboro, NC 27406 (919) 275-6391 TWX 628-94645

Pioneer Technologies Group 9801 A Southern Pine Blvd. Charlotte, NC 28210 (704) 527-8188 TWX 810-621-0366

Quality Components, S.E. 2940-15 Trawick Road Raleigh, NC 27604 (919) 876-7767

Schweber Electronics 5285 North Blvd Raleigh, NC 27604 (919) 876-0000 TWX 510-928-0531

#### NORTH DAKOTA See Minnesota

# OHIO

Kierulff Electronics 476 Windsor Park Drive Dayton, OH 45459 (513) 439-0045

OHIO (cont.) Marshall Industries 6212 Executive Blvd. Dayton, OH 45424 (513) 236-8088

Marshall Industries 59058 Harper Road Solon, OH 44139 (216) 248-1788

Pioneer-Standard 4800 East 131st Street Cleveland, OH 44105 (216) 587-3600 TWX 810-421-0011

Pioneer-Standard 4433 Interpoint Blvd. Dayton, OH 45424 (513) 236-9900 TWX 810-459-1622

Schweber Electronics 23880 Commerce Park Rd. Beachwood, OH 44122 (216) 464-2970 TWX 810-427-9441

Schweber Electronics 7865 Paragon Road Suite 210 Dayton, OH 45459 (513) 439-1800

Zeus (Televox) 2593 Lance Drive Dayton, OH 45409 (513) 294-4499 TWX 75-9251 FAX (513) 294-6620

#### OKLAHOMA

Quality Components 9934 East 21st South Tulsa, OK 74129 (918) 664-8812 TWX 910-860-5459 629-28599

Schweber Electronics 4815 South Sheridan Fountain Plaza, Suite 109 Tulsa, OK 74145 (918) 622-8000

#### OREGON

Almac Electronics Corp. 1885 N.W. 169th Place Beaverton, OR 98006 (503) 629-8090 FAX (503) 645-0611 TWX 910-467-8743

Kierulff Electronics 14273 N.W. Science Park Drive Portland, OR 97229 (503) 641-9150

Marshall Industries 8333 S.W. Cirrus Dr. Beaverton, OR 97005 (503) 644-5050

#### PENNSYLVANIA

Almo Electronics, Inc. 9815 Roosevelt Blvd. Philadelphia, PA 19114 (215) 698-4063 TLX 476-1218 FAX (215) 969-6768

Pioneer-Standard 259 Kappa Drive Pittsburgh, PA 15238 (412) 782-2300 TWX 710- 795-3122

Pioneer Technologies Group 261 Gibraltar Road Horsham, PA 19044 (215) 674-4000 TWX 510-665-6778

Schweber Electronics 900 Business Center Dr. Horsham, PA 19044 (215) 441-0600 TWX 510-665-6540

Schweber Electronics 1000 R.I.D.C. Plaza Suite 203 Pittsburgh, PA 15238 (412) 782-1600 TWX 810-427-9441

#### RHODE ISLAND See Massachusetts

New York

# SOUTH CAROLINA

Dixie Electronics 1900 Barnwell Street Columbia, SC 29202 (803) 779-5332 TLX 810-666-2620 FAX (803) 765-9276

Dixie Electronics 4909 Pelham Rd. Greenville, SC 29606 (803) 297-1435

Dixie Electronics #6 Pepperhill Square 7525 Brandywine Road N. Charleston, SC 29410 (803) 552-2671

#### SOUTH DAKOTA

See Minnesota

#### TENNESSEE Dixie Electronics

Box 8215 Suncrest Drive Gray, TN 37615 (615) 477-3838

Dixie Electronics 6408 Clinton Highway Knoxville, TN 27912 (615) 938-4131

#### TEXAS

Kierulff Electronics 3007 Longhorn Blvd. Austin, TX 78759

Kierulff Electronics 9610 Skillman Ave. Dallas, TX 75243 (214) 343-2400

Marshall Industries 2045 Chenault St. Carrollton, TX 75006 (214) 233-5200 FAX (214) 770-0675

Pioneer-Standard 13710 Omega Road Dallas, TX 75234 (214) 386-7300 TWX 910-860-5563

Pioneer-Standard 9901 Burnet Road Austin, TX 78758 (512) 835-4000 TWX 910-874-1323

Pioneer-Standard 5853 Point West Drive Houston, TX 77036 (713) 988-5555 TWX 910-881-1606

Quality Components 4257 Kellway Circle Addison, TX 75001 (214) 733-4300 TWX 910-860-5459

Quality Components 1005 Industrial Blvd. Sugarland, TX 77478 (713) 240-2255 TWX 629 27026

Quality Components 2120 M. Braker Lane Austin, TX 78758 (512) 835-0220 TWX 324930

Schweber Electronics 4202 Beltway Drive Dallas, TX 75234 (214) 661-5010 TWX 910-860-5493

Schweber Electronics 6300 La Calma Drive Suite 240 Austin, TX 78752 (512) 458-8253 TWX 910-874-2045

Schweber Electronics 10625 Richmond, Suite 100 Houston, TX 77042 (713) 784-3600 TWX 910-881-4836

Zeus Components 1800 North Glenville Suite 120 Richardson, TX 75081 (214) 783-7010 TWX 910-867-9422 FAX (214) 234-4385

Integrated Electronics Corp. 101 N. 700 West N. Salt Lake City, UT 84054 (801) 298-1869

Kierulff Electronics 1846 Parkway Blvd. Salt Lake City, UT 84119 (801) 973-6913

Marshall Industries 3501 South Main St. Salt Lake City, UT 84115 (801) 261-0901

VERMONT See New York

# VIRGINIA

See Maryland

#### WASHINGTON

Almac Electronics Corp. 14360 S.E. Eastgate Way Bellevue, WA 98007 (206) 643-9992 TWX 910-444-2067 FAX (206) 746-7425

Almac Electronics Corp. East 10905 Montgomery Spokane, WA 99206 (509) 924-9500 TWX 510-773-1855 FAX (509) 928-6096

Kierulff Electronics 19450 68th Ave. South Kent, WA 98032 (206) 575-4420

Marshall Industries 14102 N.E. 21st St. Bellevue, WA 98007 (206) 747-9100

WASHINGTON D.C. See Maryland

#### WEST VIRGINIA

See Ohio Pennsylvania Maryland

#### WISCONSIN

Kierulff Electronics 2238-E West Bluemound Road Waukesha, WI 53186 (414) 784-8160

Marshall Industries 235 North Executive Dr. #305 Brookfield, WI 53005 (414) 797-8400

Schweber Electronics 3050 South Calhoun Rd. New Berlin, WI 53151 (414) 784-9020

# WYOMING

See Oregon Washington

#### CANADA

R.A.E. Industrial 3455 Gardner Court Burnaby, B.C. (604) 291-8866 TWX 610-929-3065

R.A.E. Industrial 11680 170th Street Edmonton, Alberta T5S 1J7 (403) 451-4001 TWX 037-2653

Zentronics 8 Tilbury Court Brampton, Ontario L6T 3T4 (416) 451-9600 TWX 06-97678 FAX (416) 451-8320

#### CANADA (cont.)

Zentronics 3300-14 Ave., NE Bay #1 Calgary, Alberta T2A 6J4 (403) 272-1021

Zentronics 155 Colonnade, S. #17/18 Nepean, Ontario K2E 7K1 (613) 226-8840 TWX 06-97698

Zentronics 11400 Bridgeport Rd. #108 Richmond, B.C. V6X 1T2 (604) 273-5575 TWX 04-355844

Zentronics 817 McCaffrey Street St. Laurent, Quebec H4T 1N3 (514) 737-9700 TWX 05-824826

Zentronics 564 Weber Street, N. #10 Waterloo, Ontario N21 5C6 (519) 884-5700 TWX 06-97678 Zentronics 590 Berry Street Winnipeg, Manitoba R3H 0S1 (204) 775-8661 TWX 06-97678

Future Electronics 3220 5th Avenue, N.E. Calgary, Alberta T2A 5N1 (403) 235-5325

Future Electronics 82 St. Regis Crescent N. Downsview, Ontario M3J 123 (416) 638-4771 TWX 610-491-1470 FAX (416) 638-2936 Future Electronics 5312 Calgary Trail South Edmonton, Alberta T6H 4J8 (403) 438-2858

Future Electronics Hymus Blvd. Pointe Claire Montreal, Quebec H9R 5C7 (514) 694-7710 TWX 610-421-3251 or 610-421-3500 FAX (514) 695-3707 or (514) 694-0062

Future Electronics Baxter Center 1050 Baxter Road Ottawa, Ontario K2C 3P2 (613) 820-8313 TWX 610-563-1697 FAX (613) 820-3271 Future Electronics 1695 Boundary Road Vancouver, B.C. B5K 4X7 (604) 294-1166 TLX 04354744 FAX (604) 294-1206

Future Electronics 444 Sharon Bay Winnipeg, Manitoba R2G 0H7 (604) 294-1166 (Vancouver)

# 6800 MICROPROCESSORS SELECTION GUIDE

| Part number                              | Description                                                                                                                                                                                   | Technology | Alt source                               | CLK freq.<br>(MHz)    | Page  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------|-----------------------|-------|

| EF6802<br>EF68A02<br>EF68B02             | 8-bit MPU - 128 bytes of RAM - On-chip oscillator<br>Expandable up to 64 Kbytes - 72 instructions<br>7 addressing modes - 6800 compatible                                                     | NMOS       | MC6802<br>MC68A02<br>MC68B02             | 1<br>1.5<br>2         | 1-3   |

| EF6803<br>EF6803-1<br>EF68A03<br>EF68B03 | 8-bit MPU - 128 bytes of RAM -<br>Multiplexed address and data bus -<br>16-bit address bus - 8 × 8 multiply - Serial<br>communication interface - 16-bit timer -<br>6800 compatible           | HMOS       | MC6803<br>MC6803-1<br>MC68A03<br>MC68B03 | 1<br>1.25<br>1.5<br>2 | 1-27  |

| EF6803U4<br>EF6803U4-1<br>EF68A03U4      | 8-bit MPU - 192 bytes of RAM -<br>Multiplexed address and data bus -<br>16-bit address bus - 8 × 8 multiply - Serial<br>communication interface - 16-bits enhanced<br>timer - 6800 compatible | HMOS       | MC6803U4<br>MC6803U4-1<br>MC68A03U4      | 1<br>1.25<br>1.5      | 1-67  |

| EF6809<br>EF68A09<br>EF68B09             | High performance 8-bit MPU with on-chip clock - 64 Kbytes addressing space - Internal 16-bit structure - 59 instruction types - 10 addressing modes - 6800 compatible                         | HMOS       | MC6809<br>MC68A09<br>MC68B09             | 1<br>1.5<br>2         | 1-111 |

| EF6809E<br>EF68A09E<br>EF68B09E          | External clock version of EF6809                                                                                                                                                              | HMOS       | MC6809E<br>MC68A09E<br>MC68B09E          | 1<br>1.5<br>2         | 1-151 |

1-2

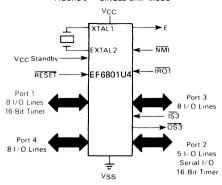

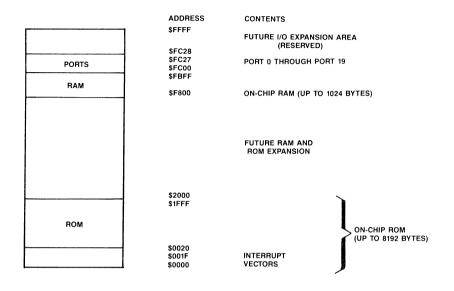

The EF6802 is a monolithic 8-bit microprocessor that contains all the registers and accumulators of the present EF6800 plus an internal clock oscillator and driver on the same chip. In addition, the EF6802 has 128 bytes of on-board RAM located at hex addresses \$0000 to \$007F. The first 32 bytes of RAM, at hex addresses \$0000 to \$001F, may be retained in a low power mode by utilizing VCC standby; thus, facilitating memory retention during a power-down situation.

The EF6802 is completely software compatible with the EF6800 as well as the entire EF6800 family of parts. Hence, the EF6802 is expandable to 64K words.

The EF6808 is identical to the EF6802 without on-board RAM.

- On-Chip Clock Circuit

- 128×8 Bit On-Chip RAM

- 32 Bytes of RAM are Retainable

- Software-Compatible with the EF6800

- Expandable to 64K Words

- Standard TTL-Compatible Inputs and Outputs

- 8-Bit Word Size

- 16-Bit Memory Addressing

- Interrupt Capability

- Three available versions: EF6802/08 (1.0 MHz), EF68A02/08 (1.5 MHz), EF68B02/08 (2.0 MHz),

# MOS

(N-CHANNEL, SILICON-GATE, DEPLETION LOAD

MICROPROCESSOR WITH CLOCK AND OPTIONAL RAM

Hi-Rel versions available - See chapter 9

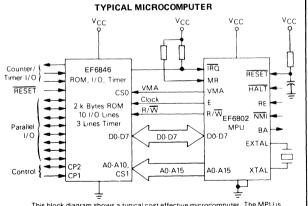

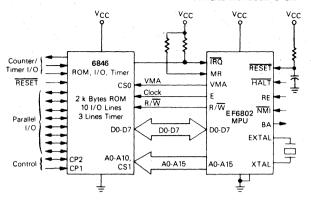

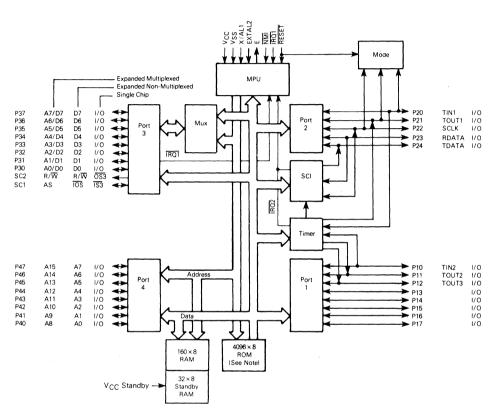

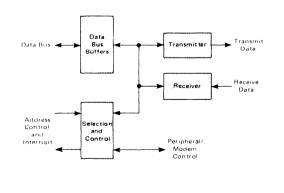

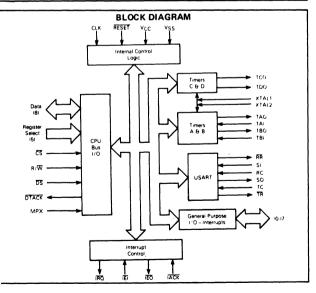

This block diagram shows a typical cost effective microcomputer. The MPU is the center of the microcoputer system and is shown in a minimum system interfacing with a ROM combination chip. It is not intended that this system be limited to this function but that it be expandable with other parts in the 6800 Microcomputer family.

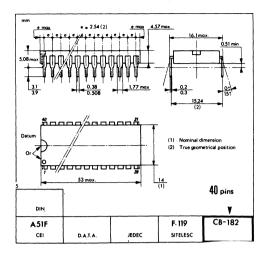

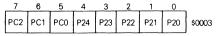

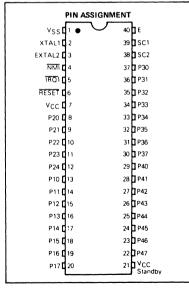

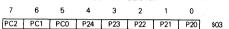

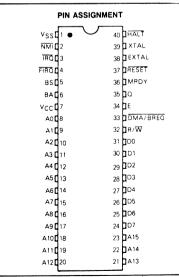

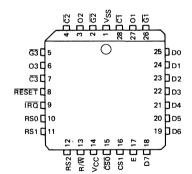

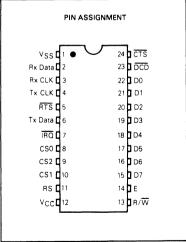

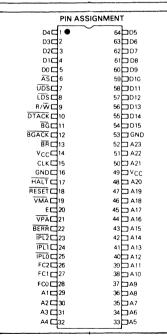

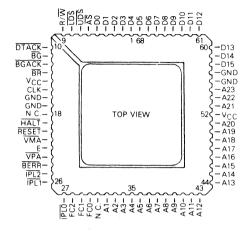

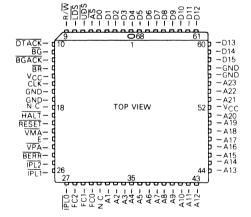

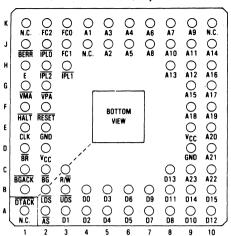

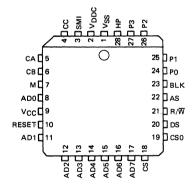

PIN ASSIGNMENT 40 RESET Vss C HALT 39 DEXTAL MR 38 1 X TAL IROL 37 t E 36 RE\* VMAD ~wq6 35 VCC Standby 34 B R/₩ 940 33 2 00 vccd8 32 01 AO da A1 110 31 02 A2 11 ээ 🕽 оз A3 d 29 04 28 05 27 0 06 A5 014 26 07 A6 15 25 h A15 A 7 11 16 24 D A 14 48 M17 23 A 13 A9 **d**18 22 A12 A10 1 19 21 VSS A11120 Pin 36 must be tied to ground for the EF6808

#### TYPICAL MICROCOMPUTER

This block diagram shows a typical cost effective microcomputer. The MPU is the center of the microcomputer system and is shown in a minimum system interfacing with a ROM combination chip. It is not intended that this system be limited to this function but that it be expandable with other parts in the 6800 Microcomputer family.

#### MAXIMUM RATINGS

| Rating                                                                                                                                                     | Symbol           | Value                                             | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------|------|

| Supply Voltage                                                                                                                                             | Vcc              | -0.3 to +7.0                                      | V    |

| Input Voltage                                                                                                                                              | Vin              | -0.3 to $+7.0$                                    | V    |

| Operating Temperature Range<br>EF6802, EF680A02, EF680B02<br>EF6802, EF68A02, EF68B02 : V suffix<br>EF6802, EF68A02 : M suffix<br>EF6808, EF68A08, EF68B08 | TA               | 0 to +70<br>-40 to +85<br>-55 to +125<br>0 to +70 | °C   |

| Storage Temperature Range                                                                                                                                  | T <sub>stg</sub> | -55 to +150                                       | °C   |

This input contains circuitry to protect the inputs against damage due to high state voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either VSS or VCC).

#### THERMAL CHARACTERISTICS

| Characteristic                                   | Symbol           | Value | Unit  |

|--------------------------------------------------|------------------|-------|-------|

| Average Thermal Resistance (Junction to Ambient) |                  |       |       |

| Plastic                                          | ۵.,              | 100   | °C/W  |

| Ceramic                                          | θ <sub>J</sub> A | 50    | C/ VV |

| PLCC                                             |                  | 100   | 1     |

#### POWER CONSIDERATIONS

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from:

$$T_J = T_A + (P_D \cdot \theta_{JA})$$

Where:

T<sub>A</sub> ■ Ambient Temperature, °C

θ<sub>.</sub>| Δ = Package Thermal Resistance, Junction-to-Ambient, °C/W

PD=PINT+PPORT

PINT ■ICC × VCC, Watts - Chip Internal Power

PPORT = Port Power Dissipation, Watts - User Determined

For most applications PPORT ◀ PINT and can be neglected. PPORT may become significant if the device is configured to drive Darlington bases or sink LED loads.

An approximate relationship between PD and TJ (if PPORT is neglected) is:

$P_D = K + (T_J + 273 ^{\circ}C)$

(2)

Solving equations 1 and 2 for K gives:

$K = PD \bullet (T\Delta + 273 \circ C) + \theta \Delta \bullet PD^2$

(3)

(1)

Where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K the values of  $P_D$  and  $T_J$  can be obtained by solving equations (1) and (2) iteratively for any value of  $T_A$ .

# DC ELECTRICAL CHARACTERISTICS ( $V_{CC} = 5.0 \text{ Vdc } \pm 5\%$ , $V_{SS} = 0$ , $T_A = 0$ to $70^{\circ}\text{C}$ , unless otherwise noted)

| Characteristic                                                                                                                                                                                    |                                                 | Symbol                              | Min                                            | Тур       | Max                   | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------|------------------------------------------------|-----------|-----------------------|------|

| Input High Voltage                                                                                                                                                                                | Logic, EXTAL<br>RESET                           | VIH                                 | V <sub>SS</sub> + 2.0<br>V <sub>SS</sub> + 4.0 | -         | V <sub>CC</sub>       | ٧    |

| Input Low Voltage                                                                                                                                                                                 | Logic, EXTAL, RESET                             | VIL                                 | V <sub>SS</sub> -0.3                           | -         | V <sub>SS</sub> + 0.8 | ٧    |

| Input Leakage Current (V <sub>ID</sub> = 0 to 5.25 V, V <sub>CC</sub> = max)                                                                                                                      | Logic                                           | l <sub>in</sub>                     | -                                              | 1.0       | 2.5                   | μА   |

| Output High Voltage ( $I_{Load} = -205 \mu\text{A}$ , $V_{CC} = \text{min}$ ) ( $I_{Load} = -145 \mu\text{A}$ , $V_{CC} = \text{min}$ ) ( $I_{Load} = -140 \mu\text{A}$ , $V_{CC} = \text{min}$ ) | D0-D7<br>A0-A15, R/ <del>W</del> , VMA, E<br>BA | Vон                                 | VSS+2.4<br>VSS+2.4<br>VSS+2.4                  | -<br>-    | -<br>-<br>-           | ٧    |

| Output Low Voltage (I <sub>Load</sub> = 1.6 mA, V <sub>CC</sub> = min)                                                                                                                            |                                                 | VOL                                 | _                                              |           | VSS + 0.4             | ٧    |

| Internal Power Dissipation (Measured at T <sub>A</sub> = 0°C)                                                                                                                                     |                                                 | PINT                                | -                                              | 0.750     | 1.0                   | W    |

| V <sub>CC</sub> Standby                                                                                                                                                                           | Power Down<br>Power Up                          | V <sub>SBB</sub><br>V <sub>SB</sub> | 4.0<br>4.75                                    | -         | 5.25<br>5.25          | ٧.   |

| Standby Current                                                                                                                                                                                   |                                                 | ISBB                                | -                                              | -         | 80                    | mΑ   |

| Capacitance $f$<br>( $V_{ID} = 0$ , $T_{A} = 25$ °C, $f = 1.0$ MHz)                                                                                                                               | D0-D7<br>Logic Inputs, EXTAL                    | C <sub>in</sub>                     |                                                | 10<br>6.5 | 12.5<br>10            | pF   |

|                                                                                                                                                                                                   | A0-A15, R/W, VMA                                | Cout                                | _                                              | -         | 12                    | pF   |

<sup>\*</sup>In power-down mode, maximum power dissipation is less than 42 mW.

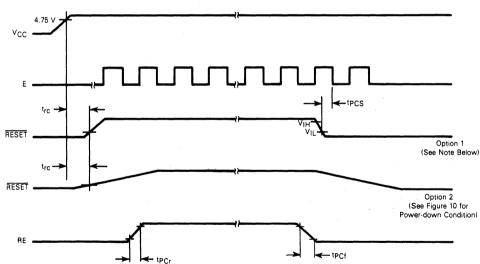

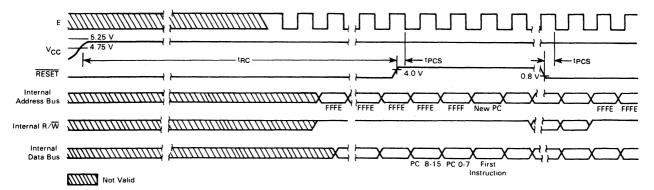

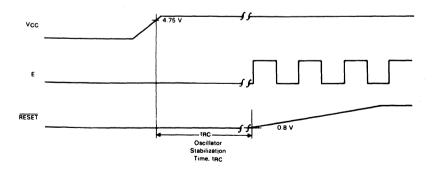

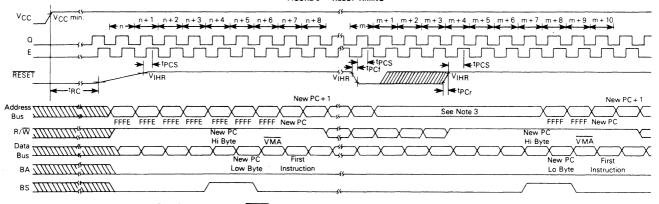

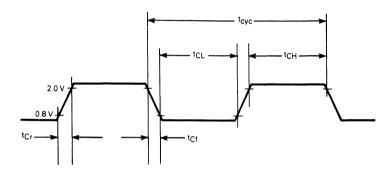

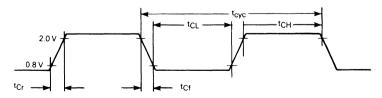

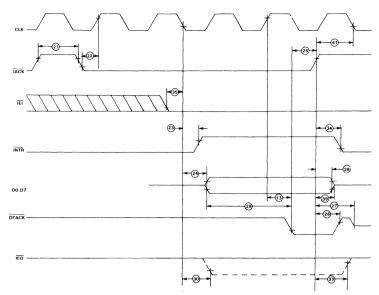

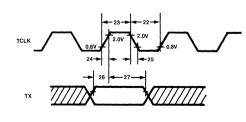

# **CONTROL TIMING** ( $V_{CC} = 5.0 \text{ V} \pm 5\%$ , $V_{SS} = 0$ , $T_A = T_1$ to $T_H$ , unless otherwise noted)

| Characteristics                                                                                                                               | Symbol           | EF6802<br>EF6808 |          | EF68A02<br>EF68A08 |          | EF68B02<br>EF68B08 |     | Unit     |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------|--------------------|----------|--------------------|-----|----------|

|                                                                                                                                               | ,                | Min              | Max      | Min                | Max      | Min                | Max | 1        |

| Frequency of Operation                                                                                                                        | fo               | 0.1              | 1.0      | 0.1                | 1.5      | 0.1                | 2.0 | MHz      |

| Crystal Frequency                                                                                                                             | fXTAL            | 1.0              | 4.0      | 1.0                | 6.0      | 1.0                | 8.0 | MHz      |

| External Oscillator Frequency                                                                                                                 | 4xf <sub>O</sub> | 0.4              | 4.0      | 0.4                | 6.0      | 0.4                | 8.0 | MHz      |

| Crystal Oscillator Start Up Time                                                                                                              | trc              | 100              |          | 100                | -        | 100                | _   | ms       |

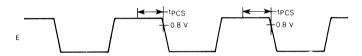

| Processor Controls (HALT, MR, RE, RESET, IRO NMI) Processor Control Setup Time Processor Control Rise and Fall Time (Does Not Apply to RESET) | tPCS<br>tPCr,    | 200              | -<br>100 | 140                | -<br>100 | 110                | 100 | ns<br>ns |

<sup>#</sup>Capacitances are periodically sampled rather than 100% tested.

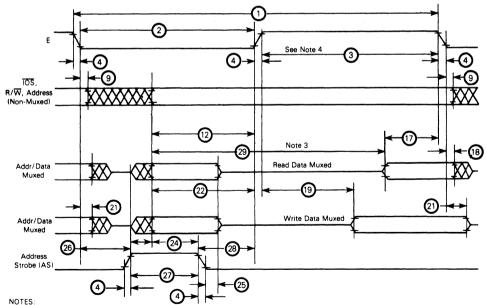

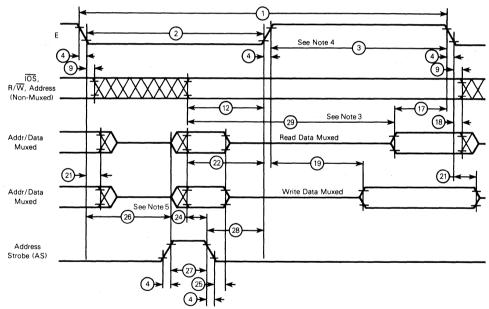

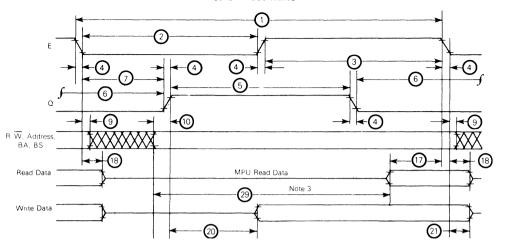

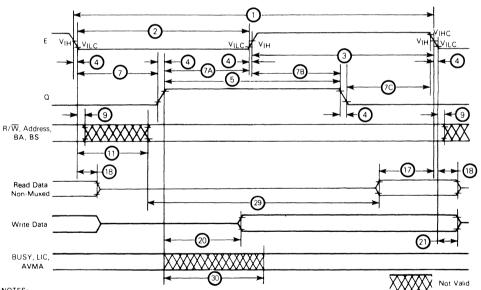

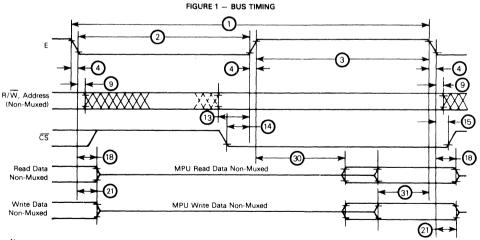

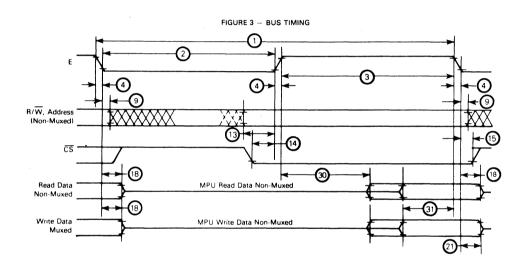

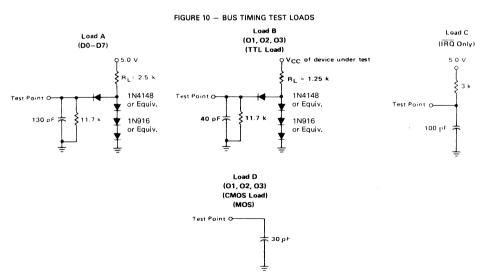

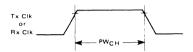

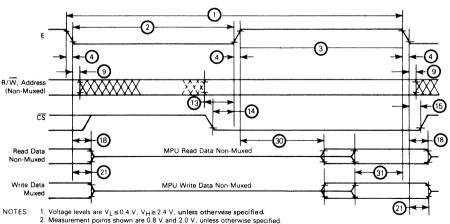

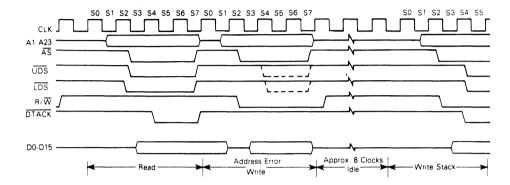

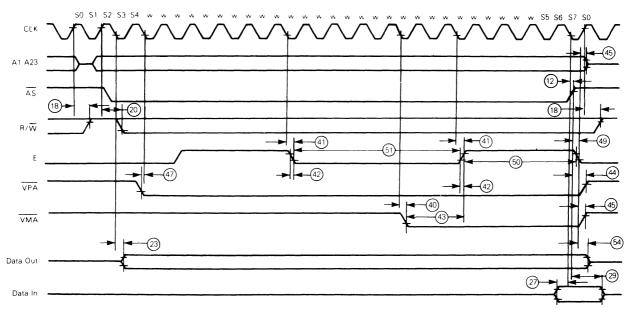

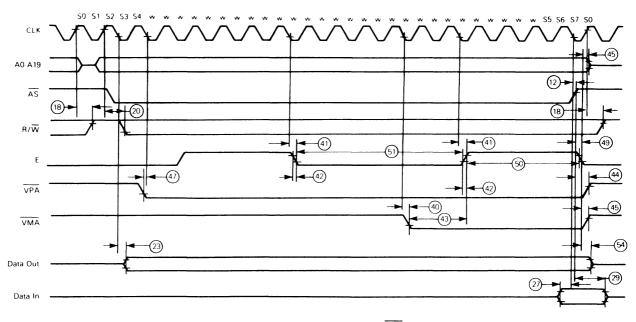

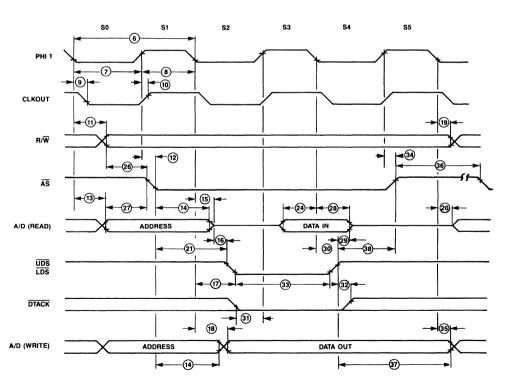

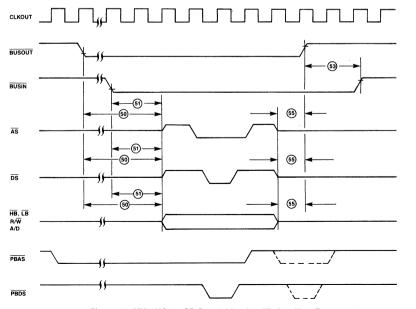

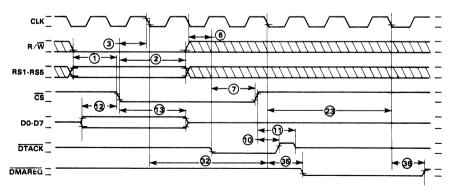

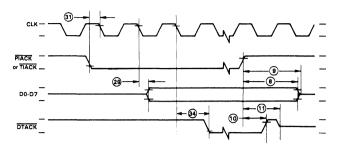

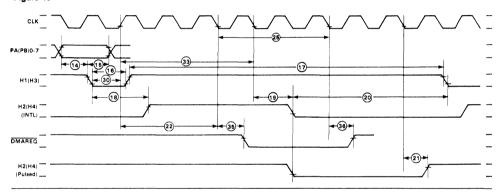

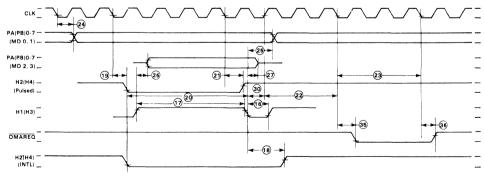

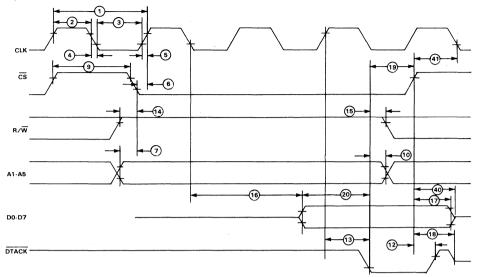

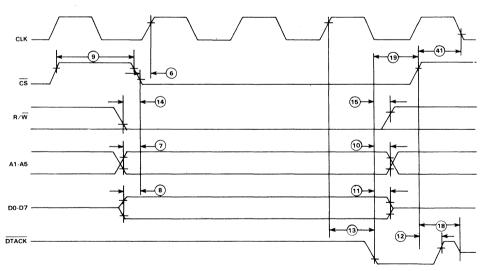

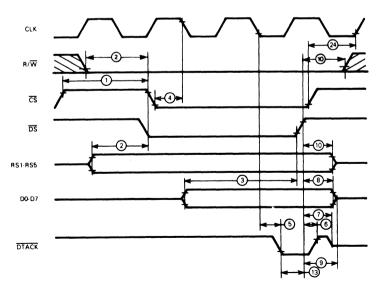

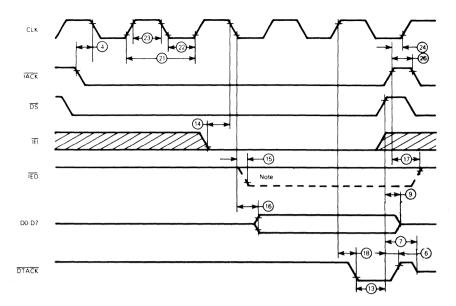

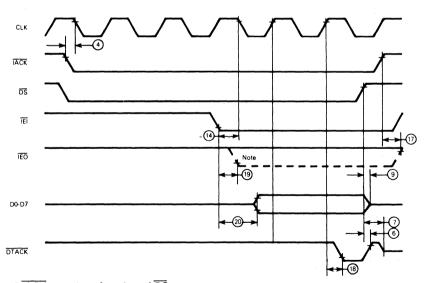

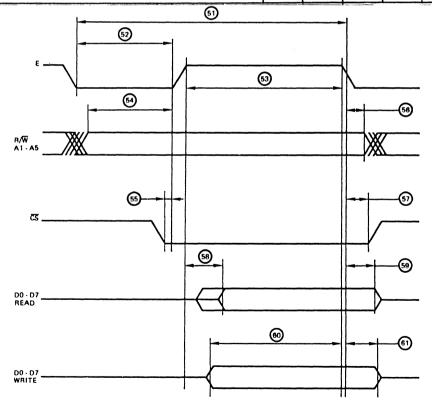

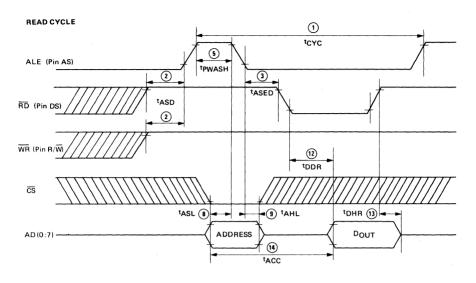

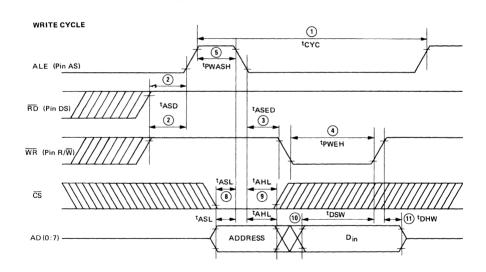

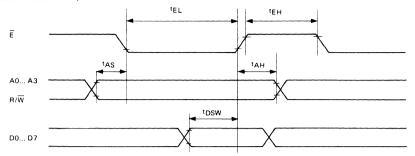

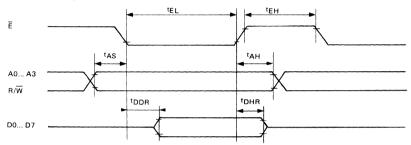

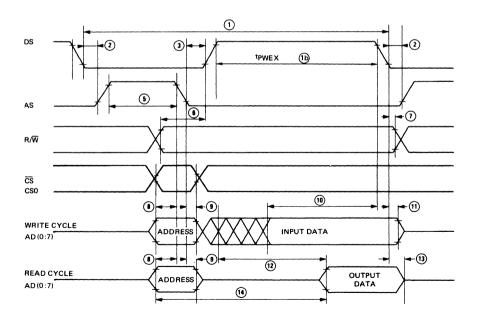

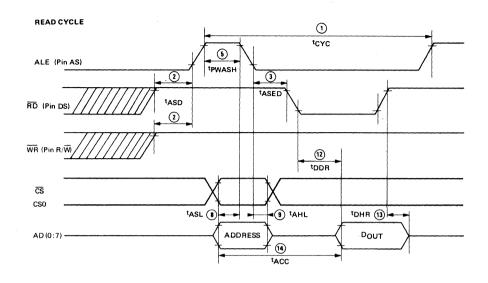

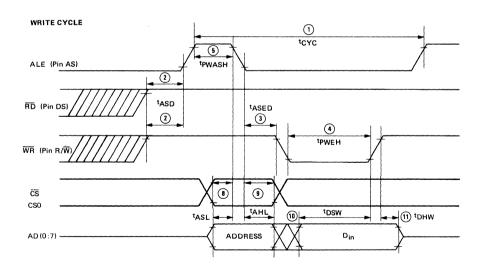

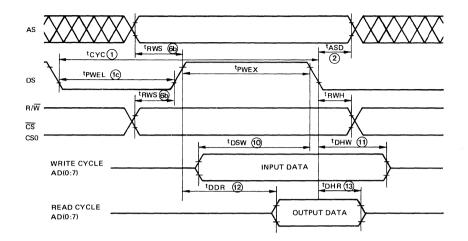

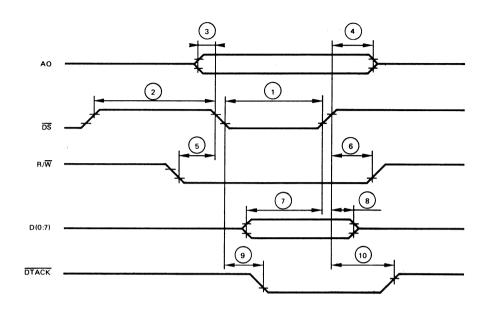

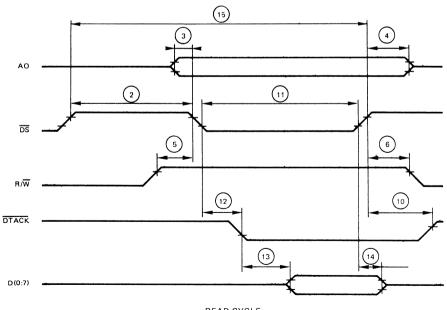

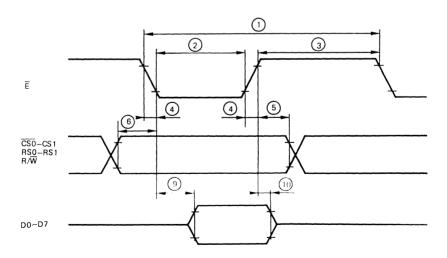

BUS TIMING CHARACTERISTICS

| ldent.<br>Number | Characteristic                                 | Symbol                               | EF6802<br>EF6808 |          | EF68A02<br>EF68A08 |      | EF68B02<br>EF68B08 |      | Unit |

|------------------|------------------------------------------------|--------------------------------------|------------------|----------|--------------------|------|--------------------|------|------|

|                  |                                                |                                      | Min              | Max      | Min                | Max  | Min                | Max  |      |

| 1                | Cycle Time                                     | tcyc                                 | 1.0              | 10       | 0.667              | 10   | 0.5                | 10   | μS   |

| 2                | Pulse Width, E Low                             | PWEL                                 | 450              | 5000     | 280                | 5000 | 210                | 5000 | ns   |

| 3                | Pulse Width, E High                            | PWEH                                 | 450              | 9500     | 280                | 9700 | 220                | 9700 | ns   |

| 4                | Clock Rise and Fall Time                       | t <sub>r</sub> , t <sub>f</sub>      | -                | 25       |                    | 25   | -                  | 25   | ns   |

| 9                | Address Hold Time*                             | †AH                                  | 20               | -        | 20                 | . –  | 20                 | -    | ns   |

| 12               | Non-Muxed Address Valid Time to E (See Note 5) | <sup>1</sup> AV1<br><sup>1</sup> AV2 | 160              | -<br>270 | 100                | -    | 50                 | <br> | ns   |

| 17               | Read Data Setup Time                           | <sup>1</sup> DSR                     | 100              | -        | 70                 | -    | 60                 | -    | ns   |

| 18               | Read Data Hold Time                            | ¹DHR                                 | 10               | -        | 10                 | -    | 10                 | -    | ns   |

| 19               | Write Data Delay Time                          | tDDW                                 | -                | 225      | -                  | 170  | -                  | 160  | ns   |

| 21               | Write Data Hold Time*                          | !DHW                                 | 30               | -        | 20                 |      | 20                 | -    | ns   |

| 29               | Usable Access Time (See Note 4)                | ¹ACC                                 | 535              | -        | 335                |      | 235                | -    | ns   |

<sup>\*</sup>Address and data hold times are periodically tested rather than 100% tested.

R/W, Address (Non-Muxed)

Read Data Non-Muxed

Write Data Non-Muxed

Write Data Non-Muxed

Write Data Non-Muxed

FIGURE 2 - BUS TIMING

#### NOTES:

- Voltage levels shown are V<sub>L</sub> ≤ 0.4 V, V<sub>H</sub> ≥ 2.4 V, unless otherwise specified.

- 2. Measurement points shown are 0.8 V and 2.0 V, unless otherwise noted.

- 3. All electricals shown for the EF6802 apply to the EF6808, unless otherwise noted.

- 4. Usable access time is computed by: 12+3+4-17.

- 5. If programs are not executed from on-board RAM, TAV1 applies. If programs are to be stored and executed from on-board RAM, TAV2 applies. For normal data storage in the on-board RAM, this extended delay does not apply. Programs cannot be executed from on-board RAM when using A and B parts (EF68A02, EF68B08, EF68B08). On-board RAM can be used for data storage with all parts.

- 6. All electrical and control characteristics are referenced from: T<sub>L</sub> = 0°C minimum and T<sub>H</sub> = 70°C maximum.

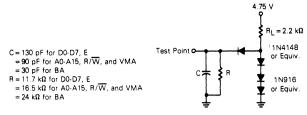

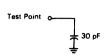

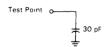

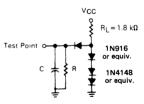

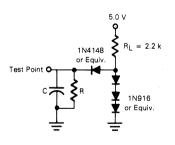

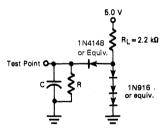

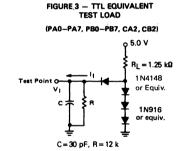

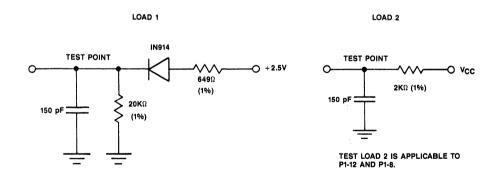

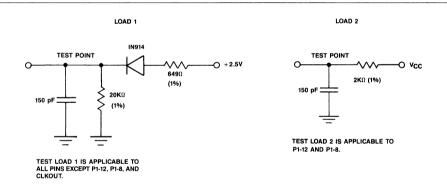

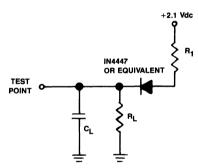

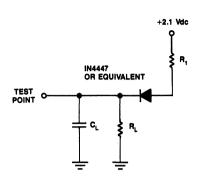

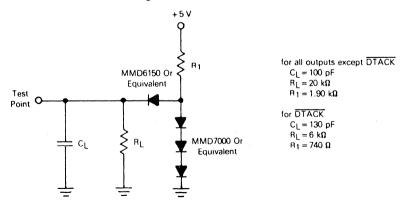

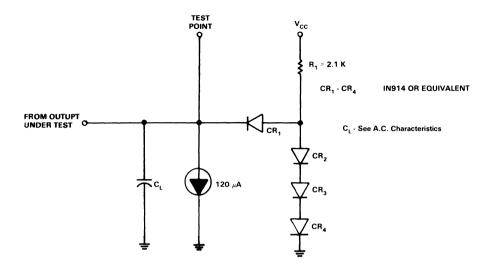

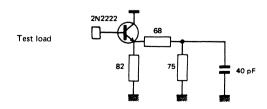

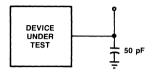

#### FIGURE 3 - BUS TIMING TEST LOAD

ا ه

500

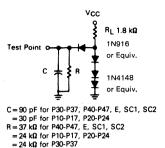

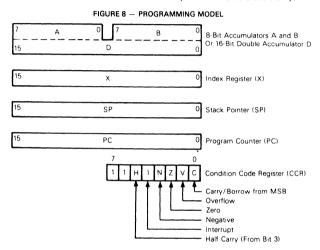

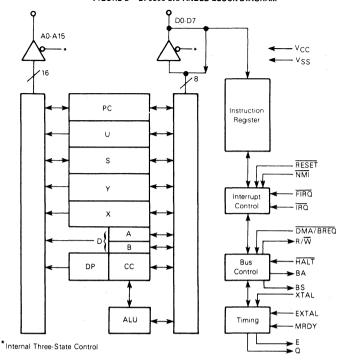

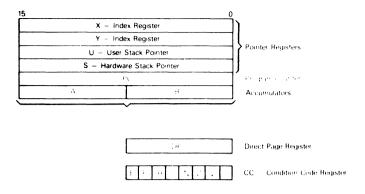

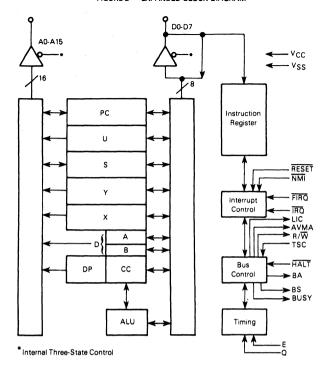

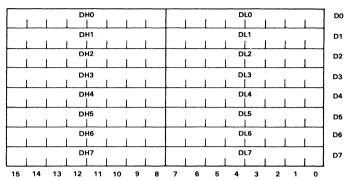

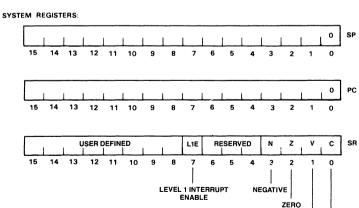

#### MPU REGISTERS

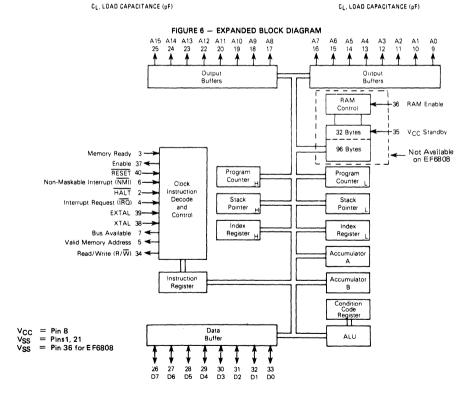

A general block diagram of the EF6802 is shown in Figure 6. As shown, the number and configuration of the registers are the same as for the EF6800. The 128x8-bit RAM\* has been added to the basic MPU. The first 32 bytes can be retained during power-up and power-down conditions via the RE signal.

The EF6808 is identical to the EF6802 except for on-board RAM. Since the EF6808 does not have on-board RAM pin 36 must be tied to ground allowing the processor to utilize up to 64K bytes of external memory.

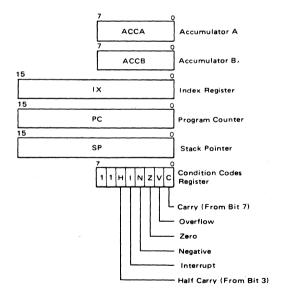

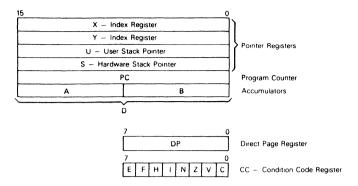

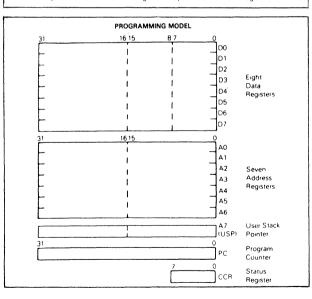

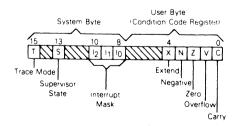

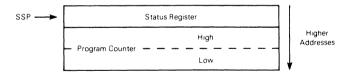

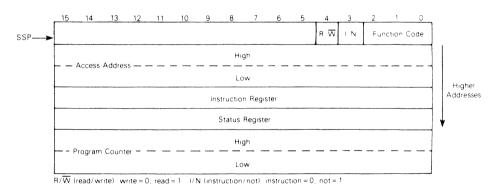

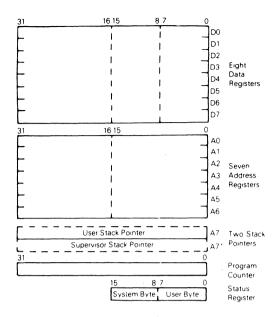

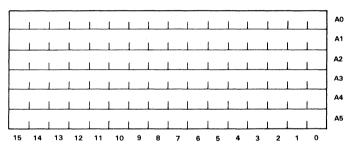

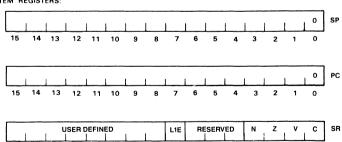

The MPU has three 16-bit registers and three 8-bit registers available for use by the programmer (Figure 7).

#### PROGRAM COUNTER

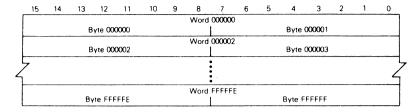

The program counter is a two byte (16-bit) register that points to the current program address.

#### STACK POINTER

The stack pointer is a two byte register that contains the address of the next available location in an external pushdown/pop-up stack. This stack is normally a random access read/write memory that may have any location (address) that is convenient. In those applications that require storage

of information in the stack when power is lost, the stack must be non-volatile.

#### INDEX REGISTER

The index register is a two byte register that is used to store data or a 16-bit memory address for the indexed mode of memory addressing.

#### **ACCUMULATORS**

The MPU contains two 8-bit accumulators that are used to hold operands and results from an arithmetic logic unit (ALU).

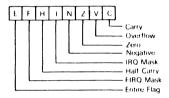

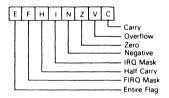

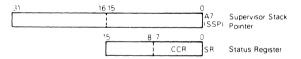

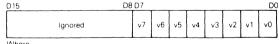

#### CONDITION CODE REGISTER

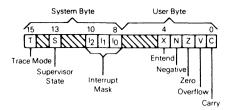

The condition code register indicates the results of an Arithmetic Logic Unit operation: Negative (N), Zero (Z), Overflow (V), Carry from bit 7 (C), and Half Carry from bit 3 (H). These bits of the Condition Code Register are used as testable conditions for the conditional branch instructions. Bit 4 is the interrupt mask bit (I). The unused bits of the Condition Code Register (b6 and b7) are ones.

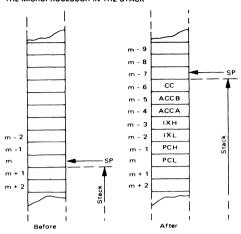

Figure 8 shows the order of saving the microprocessor status within the stack.

FIGURE 7 — PROGRAMMING MODEL OF THE MICROPROCESSING UNIT

<sup>\*</sup>If programs are not executed from on-board RAM, TAV1 applies. If programs are to be stored and executed from on-board RAM, TAV2 applies. For normal data storage in the on-board RAM, this extended delay does not apply. Programs cannot be executed from on-board RAM when using A and B parts (EF68A02, EF68A08, EF68B02, and EF68B08). On-board RAM can be used for data storage with all parts.

#### FIGURE 8 - SAVING THE STATUS OF THE MICROPROCESSOR IN THE STACK

CC = Condition Codes (Also called the Processor Status Byte)

ACCB = Accumulator B

ACCA = Accumulator A

IXH = Index Register, Higher Order 8 Bits

IXL = Index Register, Lower Order 8 Bits

PCH = Program Counter, Higher Order 8 Bits

PCL = Program Counter, Higher Order 8 Bits

#### MPU SIGNAL DESCRIPTION

Proper operation of the MPU requires that certain control and timing signals be provided to accomplish specific functions and that other signal lines be monitored to determine the state of the processor. These control and timing signals are similar to those of the EF6800 except that TSC, DBE, \$\phi1\$, \$\phi2\$ input, and two unused pins have been eliminated, and the following signal and timing lines have been added:

RAM Enable (RE)

Crystal Connections EXTAL and XTAL

Memory Ready (MR)

VCC Standby

Enable  $\phi$ 2 Output (E)

The following is a summary of the MPU signals:

#### ADDRESS BUS (A0-A15)

Sixteen pins are used for the address bus. The outputs are capable of driving one standard TTL load and 90 pF. These lines do not have three-state capability.

#### DATA BUS (D0-D7)

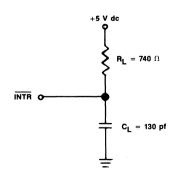

Eight pins are used for the data bus. It is bidirectional, transferring data to and from the memory and peripheral devices. It also has three-state output buffers capable of driving one standard TTL load and 130 pF.

Data bus will be in the output mode when the internal RAM is accessed and RE will be high. This prohibits external data entering the MPU. It should be noted that the internal RAM is fully decoded from \$0000 to \$007F. External RAM at \$0000 to \$007F must be disabled when internal RAM is accessed.

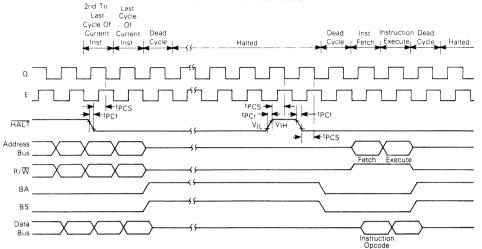

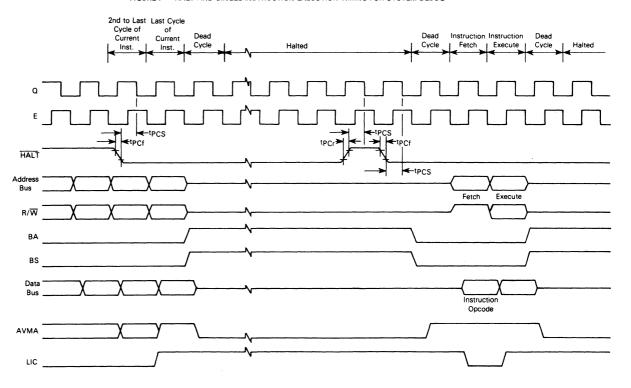

#### HALT

When this input is in the low state, all activity in the machine will be halted. This input is level sensitive. In the HALT mode, the machine will stop at the end of an instruc-

tion, bus available will be at a high state, valid memory address will be at a low state. The address bus will display the address of the next instruction.

$\overline{\text{HALT}}$  line must occur tpcs before the falling edge of E and the  $\overline{\text{HALT}}$  line must go high for one clock cycle.

HALT should be tied high if not used. This is good engineering design practice in general and necessary to ensure proper operation of the part.

#### READ/WRITE (R/W)

This TTL-compatible output signals the peripherals and memory devices whether the MPU is in a read (high) or write (low) state. The normal standby state of this signal is read (high). When the processor is halted, it will be in the read state. This output is capable of driving one standard TTL load and 90 oF.

#### VALID MEMORY ADDRESS (VMA)

This output indicates to peripheral devices that there is a valid address on the address bus. In normal operation, this signal should be utilized for enabling peripheral interfaces such as the PIA and ACIA. This signal is not three-state. One standard TTL load and 90 pF may be directly driven by this active high signal.

BUS AVAILABLE (BA) — The bus available signal will normally be in the low state; when activated, it will go to the high state indicating that the microprocessor has stopped and that the address bus is available (but not in a three-state condition). This will occur if the HALT line is in the low state or the processor is in the WAIT state as a result of the execution of a WAIT instruction. At such time, all three-state output drivers will go to their off-state and other outputs to their normally inactive level. The processor is removed from the

WAIT state by the occurrence of a maskable (mask bit I = 0) or nonmaskable interrupt. This output is capable of driving one standard TTL load and 30 pF.

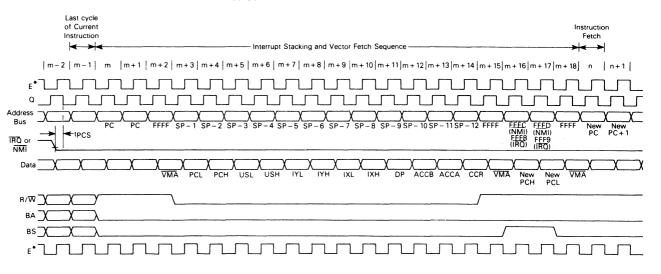

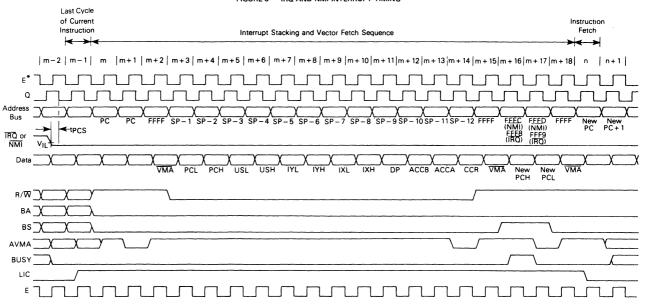

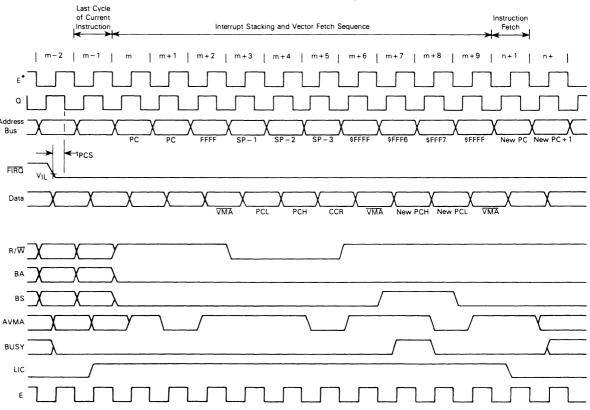

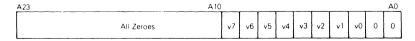

#### INTERRUPT REQUEST (IRQ)

A low level on this input requests that an interrupt sequence be generated within the machine. The processor will wait until it completes the current instruction that is being excuted before it recognizes the request. At that time, if the interrupt mask bit in the condition code register is not set, the machine will begin an interrupt sequence. The index register, program counter, accumulators, and condition code register are stored away on the stack. Next the MPU will respond to the interrupt request by setting the interrupt mask bit high so that no further interrupts may occur. At the end of the cycle, a 16-bit vectoring address which is located in memory locations \$FFF8 and \$FFF9 is loaded which causes the MPU to branch to an interrupt routine in memory.

The HALT line must be in the high state for interrupts to be serviced. Interrupts will be latched internally while HALT is low.

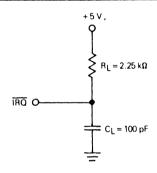

A nominal 3 k $\Omega$  pullup resistor to VCC should be used for wire-OR and optimum control of interrupts.  $\overline{IRQ}$  may be tied directly to VCC if not used.

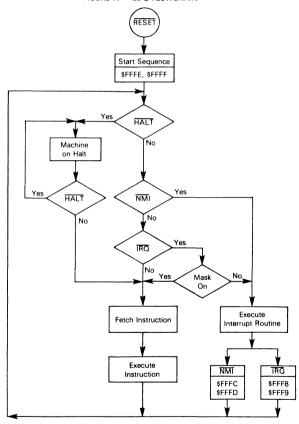

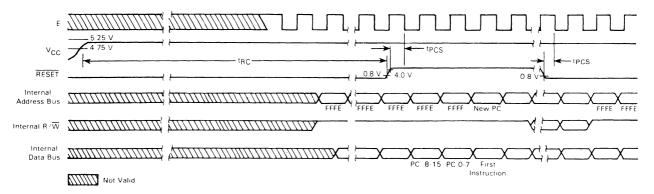

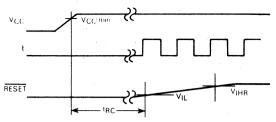

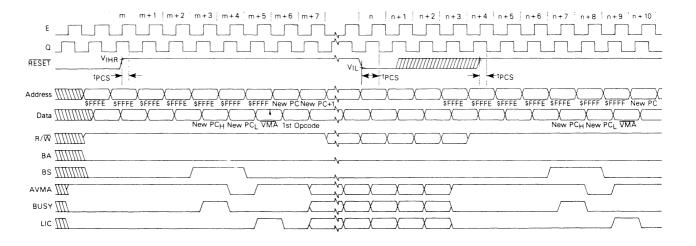

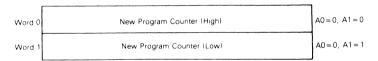

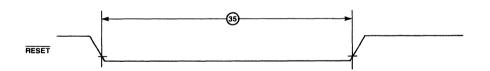

#### RESET

This input is used to reset and start the MPU from a power-down condition, resulting from a power failure or an initial start-up of the processor. When this line is low, the MPU is inactive and the information in the registers will be lost. If a high level is detected on the input, this will signal the MPU to begin the restart sequence. This will start execu-

tion of a routine to initialize the processor from its reset condition. All the higher order address lines will be forced high. For the restart, the last two (\$FFFE, \$FFFF) locations in memory will be used to load the program that is addressed by the program counter. During the restart routine, the interrupt mask bit is set and must be reset before the MPU can be interrupted by IRQ. Power-up and reset timing and power-down sequences are shown in Figures 9 and 10, respectively.

RESET, when brought low, must be held low at least three clock cycles. This allows adequate time to respond internally to the reset. This is independent of the  $t_{\text{rc}}$  power-up reset that is required.

When RESET is released it *must* go through the low-tohigh threshold without bouncing, oscillating, or otherwise causing an erroneous reset (less than three clock cycles). This may cause improper MPU operation until the next valid reset

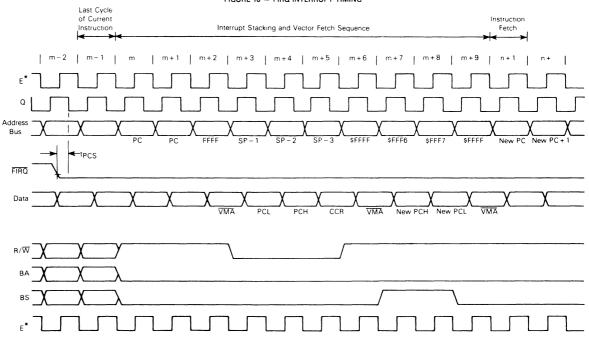

#### NON-MASKABLE INTERRUPT (NMI)

A low-going edge on this input requests that a non-maskable interrupt sequence be generated within the processor. As with the interrupt request signal, the processor will complete the current instruction that is being executed before it recognizes the  $\overline{NM}$  signal. The interrupt mask bit in the condition code register has no effect on  $\overline{NM}$ .

The index register, program counter, accumulators, and condition code registers are stored away on the stack. At the end of the cycle, a 16-bit vectoring address which is located in memory locations \$FFFC and \$FFFD is loaded causing the MPU to branch to an interrupt service routine in memory.

A nominal 3 k $\Omega$  pullup resistor to V<sub>CC</sub> should be used for wire-OR and optimum control of interrupts.  $\overline{NM}$  may be tied

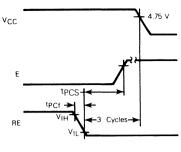

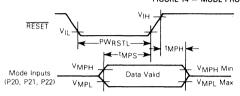

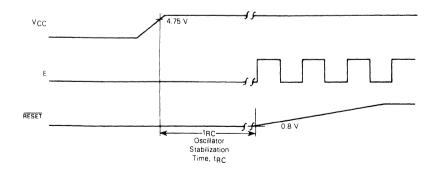

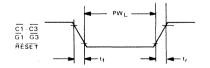

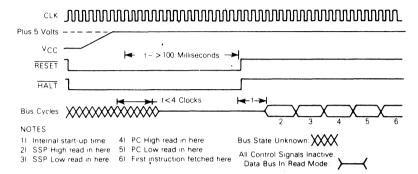

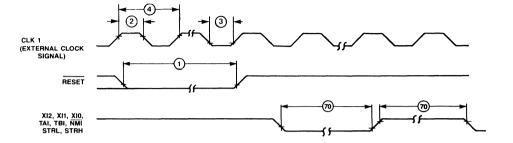

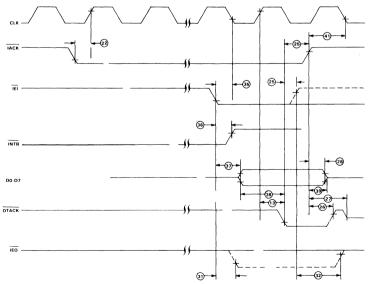

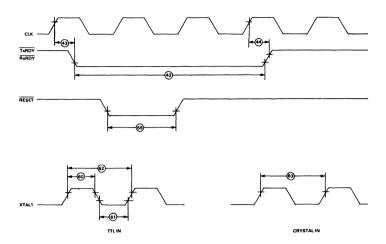

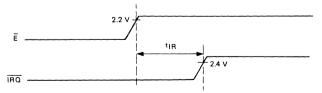

FIGURE 9 - POWER-UP AND RESET TIMING

NOTE: If option 1 is chosen, RESET and RE pins can be tied together.

directly to VCC if not used.

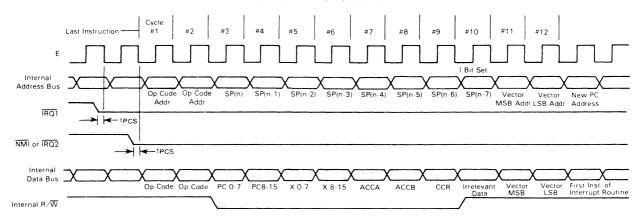

Inputs  $\overline{IRO}$  and  $\overline{NMI}$  are hardware interrupt lines that are sampled when E is high and will start the interrupt routine on a low E following the completion of an instruction.

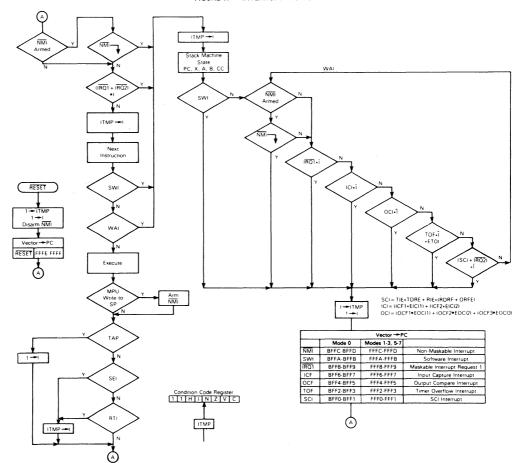

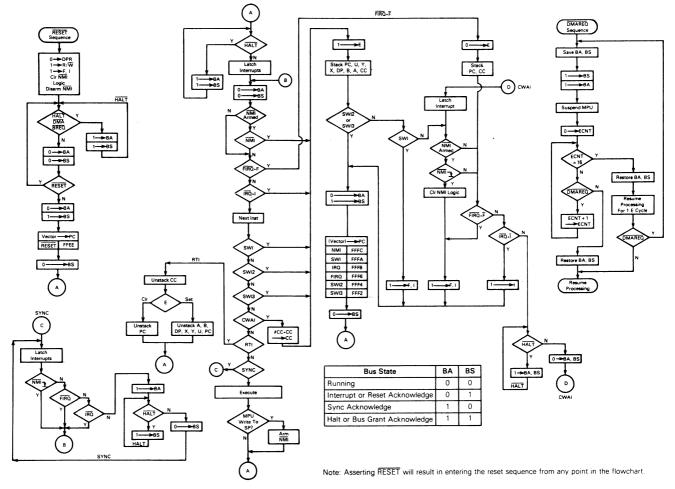

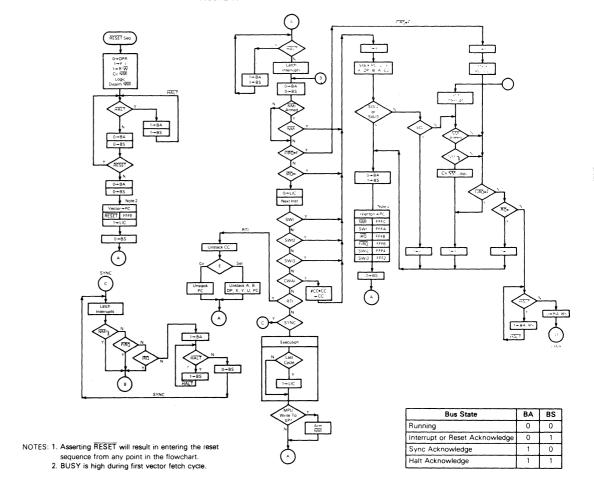

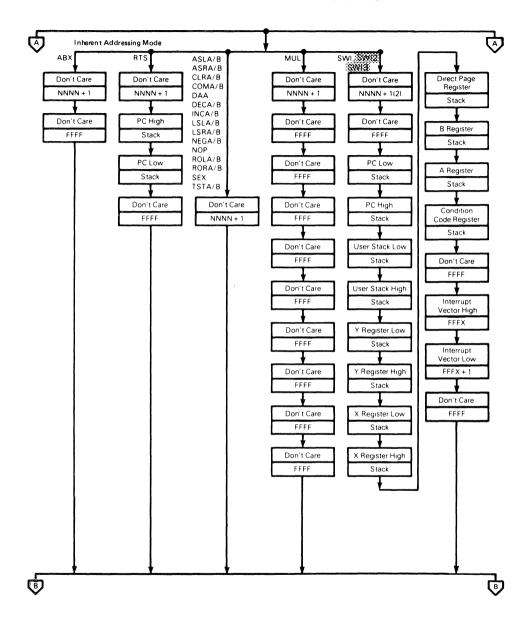

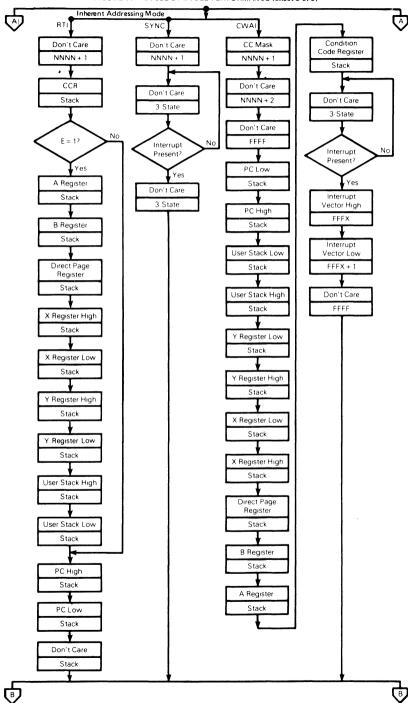

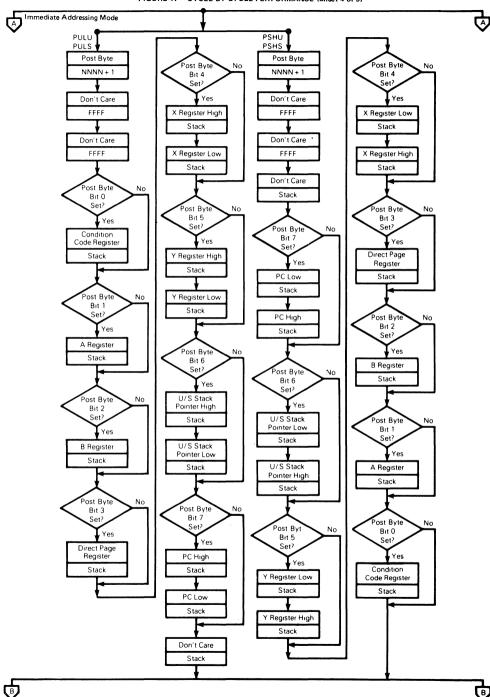

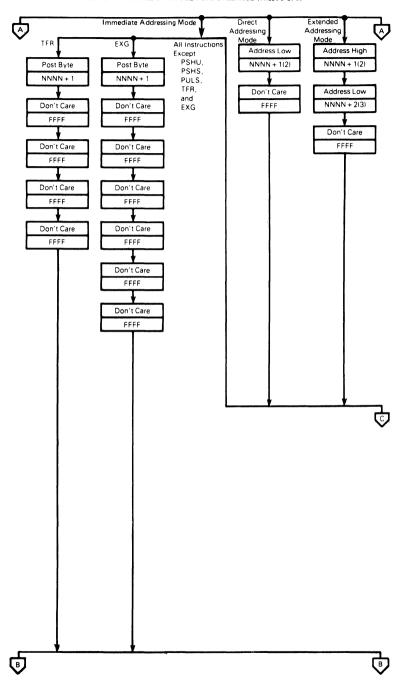

Figure 11 is a flowchart describing the major decision paths and interrupt vectors of the microprocessor. Table 1 gives the memory map for interrupt vectors.

TABLE 1 — MEMORY MAP FOR INTERRUPT VECTORS

| Vec    | ctor   | Danasiasias            |  |

|--------|--------|------------------------|--|

| MS     | LS     | Description            |  |

| \$FFFE | \$FFFF | Restart                |  |

| \$FFFC | \$FFFD | Non-Maskable Interrupt |  |

| \$FFFA | \$FFFB | Software Interrupt     |  |

| \$FFF8 | \$FFF9 | Interrupt Request      |  |

FIGURE 10 - POWER-DOWN SEQUENCE

FIGURE 11 - MPU FLOWCHART

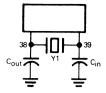

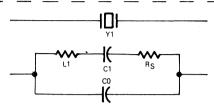

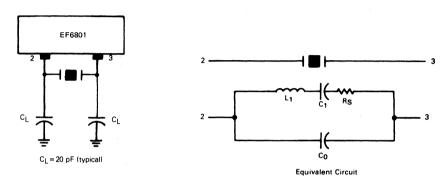

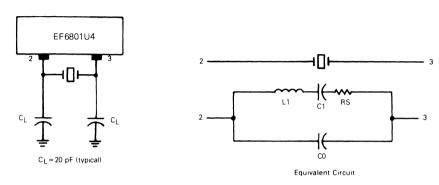

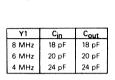

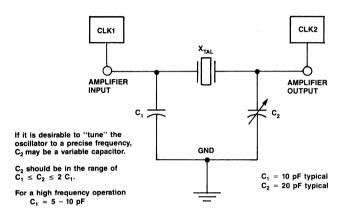

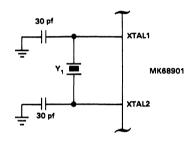

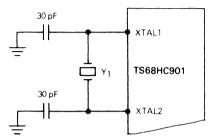

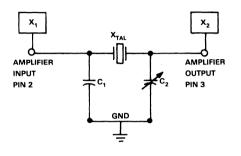

FIGURE 12 - CRYSTAL SPECIFICATIONS

| Y1       | Cin   | Cout  |

|----------|-------|-------|

| 3.58 MHz | 27 pF | 27 pF |

| . 4 MHz  | 27 pF | 27 pF |

| 6 MHz    | 20 pF | 20 pF |

| 8 MHz    | 18 pF | 18 pF |

Crystal Loading

Nominal Crystal Parameters\*

|    | 3.58 MHz | 4.0 MHz  | 6.0 MHz      | 8.0 MHz      |

|----|----------|----------|--------------|--------------|

| RS | 60 Ω     | 50 Ω     | 30-50 Ω      | 20-40 Ω      |

| CO | 3.5 pF   | 6.5 pF   | 4-6 pF       | 4-6 pF       |

| C1 | 0.015 pF | 0.025 pF | 0.01-0.02 pF | 0.01-0.02 pF |

| a  | > 40K    | >30K     | > 20K        | >20K         |

<sup>\*</sup>These are representative AT-cut parallel resonance crystal parameters only. Crystals of other types of cuts may also be used.

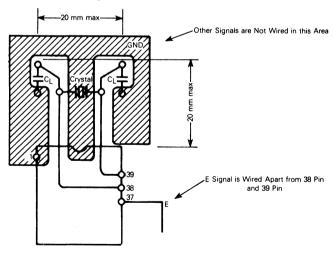

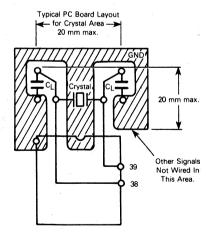

Figure 13 — SUGGESTED PC BOARD LAYOUT

Example of Board Design Using the Crystal Oscillator

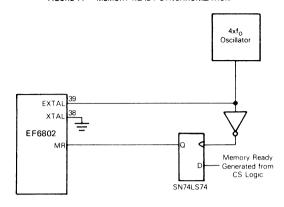

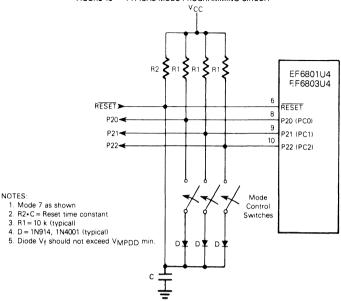

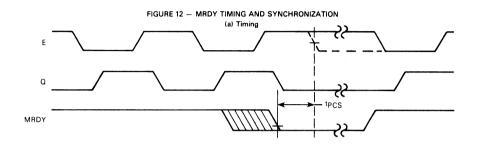

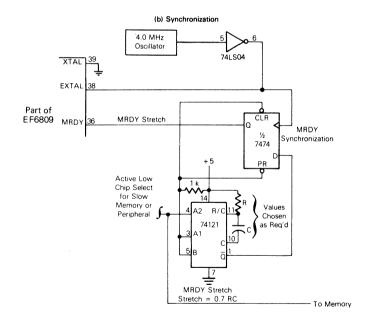

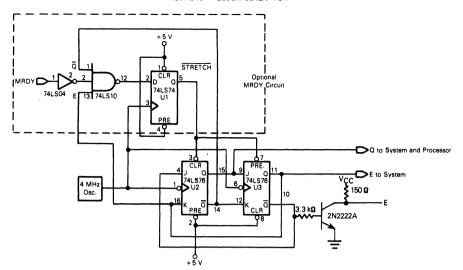

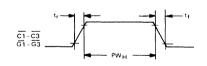

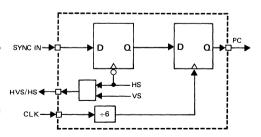

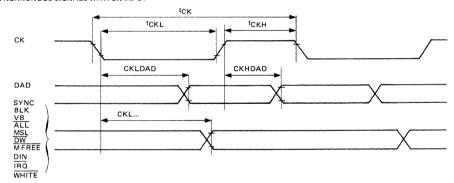

FIGURE 14 - MEMORY READY SYNCHRONIZATION

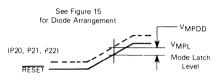

FIGURE 15 - MR NEGATIVE SETUP TIME REQUIREMENT

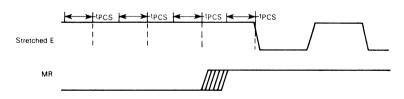

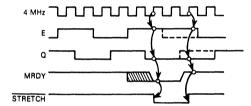

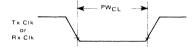

#### E Clock Stretch

The E clock will be stretched at end of E high of the cycle during which MR negative meets the tpcg setup time. The tpcg setup time is referenced to the fall of E. If the tpcg setup time is not met, E will be stretched at the end of the next E-high ½ cycle. E will be stretched in integral multiples of ½ cycles.

#### Resuming E Clocking

The E clock will resume normal operation at the end of the ½ cycle during which MR assertion meets the tpcs setup time. The tpcs setup time is referenced to transitions of E were it not stretched. If tpcs setup time is not met, E will fall at the second possible transition time after MR is asserted. There is no direct means of determining when the tpcs references occur, unless the synchronizing circuit of Figure 14 is used.

#### RAM ENABLE (RE - EF6802 ONLY)

A TTL-compatible RAM enable input controls the on-chip RAM of the EF6802. When placed in the high state, the on-chip memory is enabled to respond to the MPU controls. In the low state, RAM is disabled. This pin may also be utilized to disable reading and writing the on-chip RAM during a power-down situation. RAM Enable must be low three cycles before V<sub>CC</sub> goes below 4.75 V during power-down. RAM enable must be tied low on the EF6808. RE should be tied to the correct high or low state if not used.

#### EXTAL AND XTAL

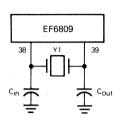

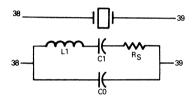

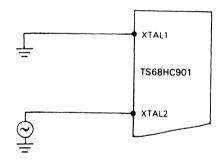

These inputs are used for the internal oscillator that may be crystal controlled. These connections are for a parallel resonant fundamental crystal (see Figure 12). (AT-cut.) A divide-by-four circuit has been added so a 4 MHz crystal may be used in lieu of a 1 MHz crystal for a more cost-effective system. An example of the crystal circuit layout is shown in Figure 13. Pin 39 may be driven externally by a TTL input signal four times the required E clock frequency. Pin 38 is to be grounded.

An RC network is not directly usable as a frequency source on pins 38 and 39. An RC network type TTL or CMOS oscillator will work well as long as the TTL or CMOS output drives the on-chip oscillator.

LC networks are not recommended to be used in place of the crystal.

If an external clock is used, it may not be halted for more than  $t_{\text{PM}} \downarrow$ . The EF6802 and EF6808 are dynamic parts except for the internal RAM, and require the external clock to retain information.

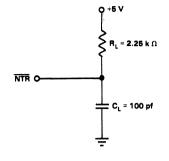

#### MEMORY READY (MR)

MR is a TTL-compatible input signal controlling the stretching of E. Use of MR requires synchronization with the 4xf<sub>0</sub> signal, as shown in Figure 14. When MR is high, E will be in ormal operation. When MR is low, E will be stretched integral numbers of half periods, thus allowing interface to slow memories. Memory Ready timing is shown in Figure 15.

MR should be tied high (connected directly to V<sub>CC</sub>) if not used. This is necessary to ensure proper operation of the part. A maximum stretch is  $t_{\rm CVC}$ .

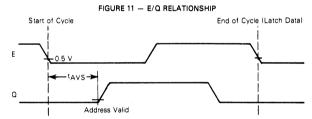

#### **ENABLE (E)**

This pin supplies the clock for the MPU and the rest of the system. This is a single-phase, TTL-compatible clock. This clock may be conditioned by a memory read signal. This is equivalent to  $\phi 2$  on the **EF6800**. This output is capable of driving one standard TTL load and 130 pF.

#### V<sub>CC</sub> STANDBY (EF6802 ONLY)

This pin supplies the dc voltage to the first 32 bytes of RAM as well as the RAM Enable (RE) control logic. Thus, retention of data in this portion of the RAM on a power-up, power-down, or standby condition is guaranteed. Maximum current drain at VSB maximum is ISBB.

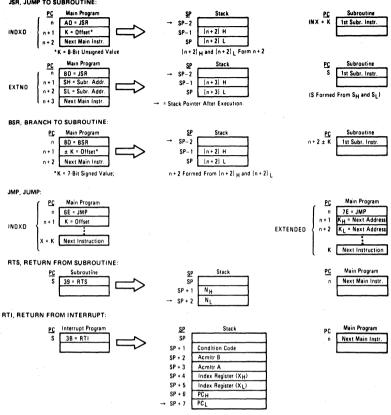

#### MPU INSTRUCTION SET

The instruction set has 72 different instructions. Included are binary and decimal arithmetic, logical, shift, rotate, load, store, conditional or unconditional branch, interrupt and stack manipulation instructions (Tables 2 through 6). The instruction set is the same as that for the EF6800.

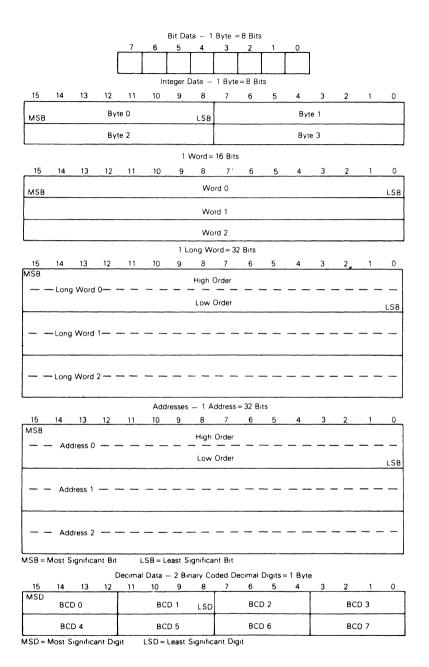

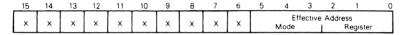

#### MPU ADDRESSING MODES

There are seven address modes that can be used by a programmer, with the addressing mode a function of both the type of instruction and the coding within the instruction. A summary of the addressing modes for a particular instruction can be found in Table 7 along with the associated instruction execution time that is given in machine cycles. With a bus frequency of 1 MHz, these times would be microseconds.

#### ACCUMULATOR (ACCX) ADDRESSING

In accumulator only addressing, either accumulator A or accumulator B is specified. These are one-byte instructions.

#### IMMEDIATE ADDRESSING

In immediate addressing, the operand is contained in the second byte of the instruction except LDS and LDX which have the operand in the second and third bytes of the instruction. The MPU addresses this location when it fetches the immediate instruction for execution. These are two- or three-byte instructions.

#### DIRECT ADDRESSING

In direct addressing, the address of the operand is contained in the second byte of the instruction. Direct addressing allows the user to directly address the lowest 256 bytes in the machine, i.e., locations zero through 255. Enhanced execution times are achieved by storing data in these locations. In most configurations, it should be a random-access memory. These are two-byte instructions.

#### EXTENDED ADDRESSING

In extended addressing, the address contained in the second byte of the instruction is used as the higher eight bits of the address of the operand. The third byte of the instruction is used as the lower eight bits of the address for the operand. This is an absolute address in memory. These are three-byte instructions.

#### INDEXED ADDRESSING

In indexed addressing, the address contained in the second byte of the instruction is added to the index register's lowest eight bits in the MPU. The carry is then added to the higher order eight bits of the index register. This result is then used to address memory. The modified address is held in a temporary address register so there is no change to the index register. These are two-byte instructions.

#### IMPLIED ADDRESSING

In the implied addressing mode, the instruction gives the address (i.e., stack pointer, index register, etc.). These are one-byte instructions.

#### RELATIVE ADDRESSING

In relative addressing, the address contained in the second

byte of the instruction is added to the program counter's lowest eight bits plus two. The carry or borrow is then added to the high eight bits. This allows the user to address data within a range of  $-125\ to +129\ bytes$  of the present instruction. These are two-byte instructions.

TABLE 2 - MICROPROCESSOR INSTRUCTION SET - ALPHABETIC SEQUENCE

| ABA<br>ADC<br>ADD<br>ASL<br>ASR<br>BCS<br>BEQ<br>BGT<br>BHI<br>BIT<br>BLS<br>BLS<br>BHI<br>BNE<br>BRA<br>BSC | Add Accumulators Add with Carry Add Logical And Arithmetic Shift Left Arithmetic Shift Right Branch if Carry Clear Branch if Carry Set Branch if Greater or Equal Zero Branch if Greater or Equal Zero Branch if Greater than Zero Branch if Higher Bit Test Branch if Less or Equal Branch if Less or Equal Branch if Lower or Same Branch if Lower or Same Branch if Minus Branch if Minus Branch if Not Equal to Zero Branch if Overflow Clear | CLR CLV CMP COMP COX DAA DEC DES DEX EOR INC INS INX JMP JSR LDA LDS LDX LSR | Clear Clear Overflow Compare Complement Compare Index Register Decimal Adjust Decrement Decrement Stack Pointer Decrement Index Register Exclusive OR Increment Increment Index Register Jump Jump Jump to Subroutine Load Accumulator Load Stack Pointer Load Index Register Logical Shift Right | PUL ROR RTI RTS SBA SBC SEC SEC SEV STA STS STX SUB TAB TAB TPA TST TSX | Puil Data Rotate Left Rotate Right Return from Interrupt Return from Subrooutine Subtract Accumulators Subtract With Carry Set Carry Set Interrupt Mask Set Overflow Store Accumulator Store Stack Register Store Index Register Subtract Software Interrupt Transfer Accumulators to Condition Code Reg. Transfer Accumulators Transfer Condition Code Reg. to Accumulator Test Transfer Condition Code Reg. to Accumulator Test Transfer Stack Pointer to Index Register |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                              |                                                                                                                                                                                                                                                                                                   | TST                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

TABLE 3 - ACCUMULATOR AND MEMORY INSTRUCTIONS

ADDRESSING MODES

|                         |              |          |     |    |          |      |    |          |     |   |          |     |   |      |      |   | 1                                      |     |     |     | _     | -        |

|-------------------------|--------------|----------|-----|----|----------|------|----|----------|-----|---|----------|-----|---|------|------|---|----------------------------------------|-----|-----|-----|-------|----------|

|                         |              | - "      | MME | 0  | 0        | IREC | T_ |          | NDE | x | E        | XTN | D | IM   | PLIE | D | (All register labels                   |     |     | 3   |       |          |

| OPERATIONS              | MNEMONIC     | OP       | `   | =  | OP       | `    | =  | OP       | `   | = | OP       | `   | = | OP   | `    | = | refer to contents)                     | H   | 1   | N   | Z     | ٧        |

| Add                     | ADDA         | 38.      | 2   | 2  | 98       | 3    | -2 | AB       | 5   | 2 | ВВ       | 4   | 3 |      |      |   | A + M - A                              | 11  | •   | 1   | ıΤı   | :        |

|                         | ADDB         | СВ       | 2   | 2  | DB       | 3    | 2  | €B       | 5   | 2 | FB       | 4   | 3 |      |      |   | B + M → B                              | 11  | •   | 1   |       | 1        |

| Add Acmitrs             | ABA          | l        |     |    | l        |      |    | l        |     |   |          |     |   | 18   | 2    | 1 | A + B - A                              | 1:1 | •   | 1   | 1 1   | 1        |

| Add with Carry          | ADCA         | 89       | 2   | 2  | 99       | 3    | 2  | A9       | 5   | 2 | 89       | 4   | 3 |      |      |   | A + M + C - A                          |     |     |     |       | t        |

|                         | ADCB         | C9       | 2   | 2  | D9       | 3    | 2  | €9       | 5   | 2 | F9       | 4   | 3 |      |      |   | B + M + C → B                          |     |     |     |       | 1        |

| And                     | ANDA         | 84       | 2   | 2  | 94       | 3    | 2  | A4       | 5   | 2 | B4       | 4   | 3 |      |      |   | A · M A                                | 1.  | - 1 | . ( |       | R        |

| Bit Test                | ANDB         | C4<br>85 | 2   | 2  | 04       | 3    | 2  | E4       | 5   | 2 | F4       | 4   | 3 |      |      |   | B · M → B                              | •   |     | ٠,  |       | R        |

| Bit lest                | BITA         | C5       | 2   | 2  | 95<br>D5 | 3    | 2  | A5<br>E5 | 5   | 2 | 85<br>F5 | 4   | 3 |      |      |   | A·M<br>B·M                             |     |     | ٠,  |       | R        |

| Clear                   | CLR          | 1 65     | -   | ۷. | US       | 3    | 2  | 6F       | 7   | 2 | 7F       | 6   | 3 |      |      |   | 00 → W                                 |     |     |     |       | R        |

| Citar                   | CLRA         | Į.       |     |    |          |      |    | 1 05     | ,   | - | ′′       | •   | 3 | 4F   | 2    | 1 | 00 → M                                 |     |     |     |       | R        |

|                         | CLRB         |          |     |    |          |      |    |          |     |   |          |     |   | 5.5  | 2    | i | 00 - B                                 |     |     |     | SF    |          |

| Compare                 | CMPA         | 81       | 2   | 2  | 91       | 3    | 2  | AI       | 5   | 2 | В1       | 4   | 3 |      | •    |   | A - M                                  |     |     |     |       | 1        |

|                         | CMPB         | CI       | 2   | 2  | D1       | 3    | 2  | ΕI       | 5   | 2 | F1       | 4   | 3 |      |      |   | B – M                                  |     |     | il  |       | il       |

| Compare Acmitrs         | CBA          |          |     | -  | 1        |      |    | 1        |     |   |          |     | - | 11   | 2    | 1 | A - B                                  |     | •   | il  | ili   |          |

| Complement, 1's         | COM          |          |     |    | l        |      |    | 63       | 7   | 2 | 73       | 6   | 3 |      |      |   | M→M                                    |     | •   | 1   | 1 6   | R        |

|                         | COMA         | 1        |     |    |          |      |    |          |     |   |          |     |   | 43   | 2    | 1 | Ā → A                                  |     | •   | 1   | 1 6   | R        |

|                         | COMB         | 1        |     |    |          |      |    | 1        |     |   |          |     |   | 53   | 2    | 1 | B → B                                  |     |     | 1   |       | R        |

| Complement, 2's         | NEG          | İ        |     |    |          |      |    | 60       | 7   | 2 | 70       | 6   | 3 |      |      |   | 00 - M → M                             |     |     |     | 1 0   |          |

| (Negate)                | NEGA         | 1        |     |    | 1        |      |    |          |     |   |          |     |   | 40   | 2    | 1 | 00 - A → A                             |     |     |     | 1 0   |          |

|                         | NEGB         |          |     |    |          |      |    | ľ        |     |   |          |     |   | - 50 | 2    | 1 | 00 - B→B                               |     |     |     | 1 0   |          |