# **MICROCOMPUTERS**

DATA BOOK

# **MICROCOMPUTERS**

# **WARNING!**

THE FOLLOWING PRODUCTS HAVE BEEN DISCONTINUED

• TS 94104 ..... 1-139

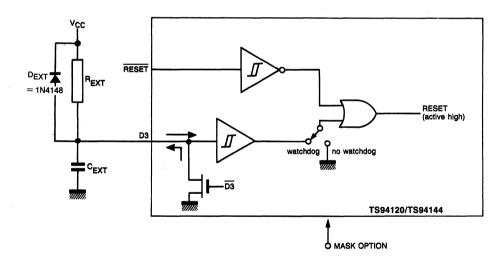

• TS 94120 TS 94144 .. 1-153

• MK 68200 FAMILY .... 3-5

MK 68HC200 FAMILY, 3-77

uters

1

uters

2

uters

3

/ices

4

**Development and emulation tool**

5

# -CONTENTS ----

| GENERAL INFORMATION                                                                                                                                                                                                                                                                                                                                                                  |                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Contents                                                                                                                                                                                                                                                                                                                                                                             |                                                    |

| CHAPTER 1 - 4 BIT MICROCOMPUTERS                                                                                                                                                                                                                                                                                                                                                     |                                                    |

| 4-bit Microcomputers selection guide                                                                                                                                                                                                                                                                                                                                                 | 1-3                                                |

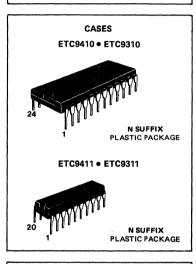

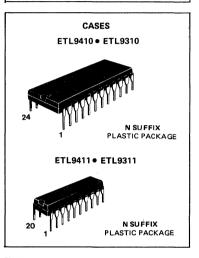

| ETC9410/11•ETC9310/11 Single chip microcontrollers  ETL9410/11•ETL9310/11 Single chip microcontrollers  ETL9413•ETL9313 Single chip microcontrollers  ET9420/21/22•ET9320/21/22 Single chip microcontrollers  ETC9420/21/22•ETC9320/21/22 Single chip microcontrollers  ETC9444/45•ETC9344/45 Single chip microcontrollers  ETL9420/21/22•ETL9320/21/22 Single chip microcontrollers | 1-5<br>1-21<br>1-41<br>1-45<br>1-69<br>1-91        |

| ETL9444/45•ETL9344/45 Single chip microcontrollers                                                                                                                                                                                                                                                                                                                                   | 1-115<br>1-139<br>1-153                            |

| CHAPTER 2 - 8-BIT MICROCOMPUTERS                                                                                                                                                                                                                                                                                                                                                     |                                                    |

| 8-bit Microcomputers selection guide                                                                                                                                                                                                                                                                                                                                                 | 2-3                                                |

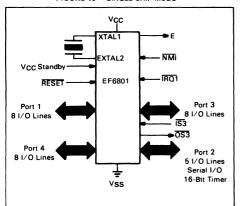

| EF6801 FAMILY                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

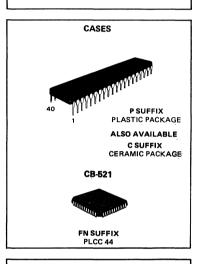

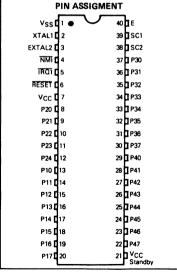

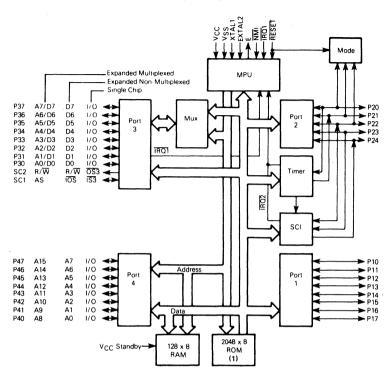

| EF6801•EF6803 Microcomputer/Microprocessor (MCU/MPU)<br>EF6801U4•EF6803U4 Microcomputer/Microprocessor (MCU/MPU)                                                                                                                                                                                                                                                                     | 2-7<br>2-47                                        |

| EF6804 FAMILY                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

| EF6804J2 8-bit microcomputer EF6804P2 8-bit microcomputer TS68HC04J3 8-bit microcomputer EF68HC04P3 8-bit microcomputer                                                                                                                                                                                                                                                              | 2-91<br>2-135<br>2-179<br>2-181                    |

| EF6805 FAMILY                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

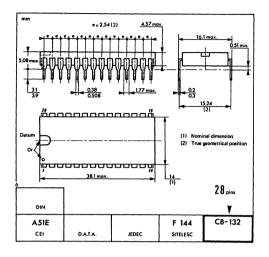

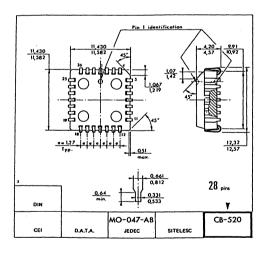

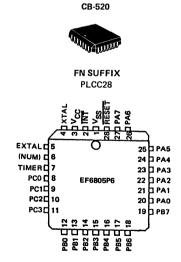

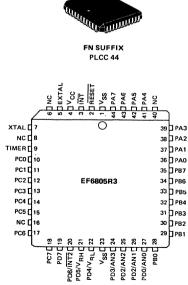

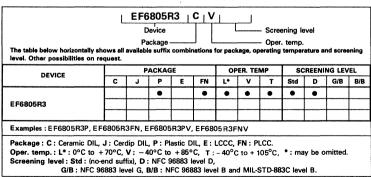

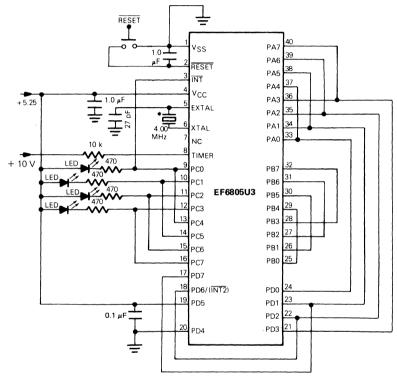

| EF6805P2 8-bit microcomputer EF6805P6 8-bit microcomputer EF6805R2 8-bit microcomputer with A/D EF6805R3 8-bit microcomputer with A/D EF6805U2 8-bit microcomputer EF6805U3 8-bit microcomputer                                                                                                                                                                                      | 2-225<br>2-249<br>2-273<br>2-301<br>2-329<br>2-355 |

| MK3870 FAMILY                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

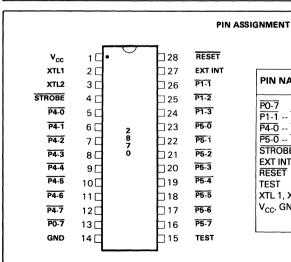

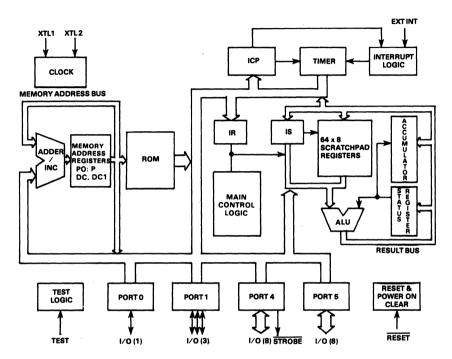

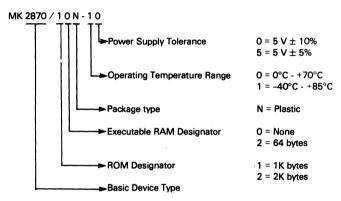

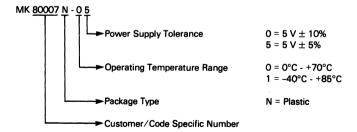

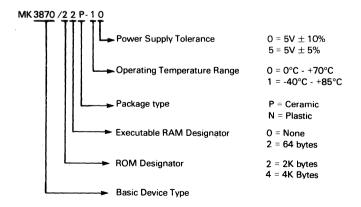

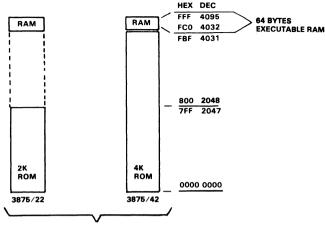

| MK2870 3870 Single chip micro family                                                                                                                                                                                                                                                                                                                                                 | 2-381<br>2-399<br>2-427<br>2-453                   |

| CHAPTER 3 - 16-BIT MICROCOMPUTERS                                                                                                                                                                                                                                                                                                                                                    |                                                    |

| 16-bit Microcomputers selection guide                                                                                                                                                                                                                                                                                                                                                | 3-3                                                |

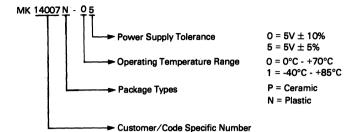

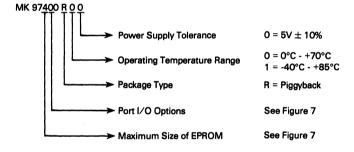

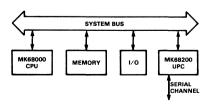

| MK68200 FAMILY 16-bit single chip microcomputer                                                                                                                                                                                                                                                                                                                                      | 3-5<br>3-77                                        |

# CONTENTS -

| CHAPTER 4 - SURFACE MOUNTED DEVICES        | Page |

|--------------------------------------------|------|

| Surface mounted devices selection guide    | 4-3  |

| CHAPTER 5 - DEVELOPMENT AND EMULATION TOOL |      |

| INICE-4-8 Development and emulation tool   | 5-3  |

| EMU-04 Piggy-back emulation tool           | 5-5  |

# ——— ALPHANUMERICAL INDEX ————

| Part number | Page  | Part number | Page  | Part number | Page  |

|-------------|-------|-------------|-------|-------------|-------|

| EF6801      | 2-7   | ETC9344     | 1-69  | ETL9422     | 1-91  |

| EF6801U4    | 2-47  | ETC9345     | 1-69  | ETL9444     | 1-115 |

| EF6804J2    | 2-91  | ETC9410     | 1-5   | ETL9445     | 1-115 |

| EF6804P2    | 2-135 | ETC9411     | 1-5   | MK2870      | 2-381 |

| EF6805P2    | 2-225 | ETC9420     | 1-69  | MK3870      | 2-399 |

| EF6805P6    | 2-249 | ETC9421     | 1-69  | MK3873      | 2-427 |

| EF6805R2    | 2-273 | ETC9422     | 1-69  | MK3875      | 2-453 |

| EF6805R3    | 2-301 | ETC9444     | 1-69  | MK38P70     | 2-399 |

| EF6805U2    | 2-329 | ETC9445     | 1-69  | MK38P73     | 2-427 |

| EF6805U3    | 2-355 | ETL9310     | 1-21  | MK38P75     | 2-453 |

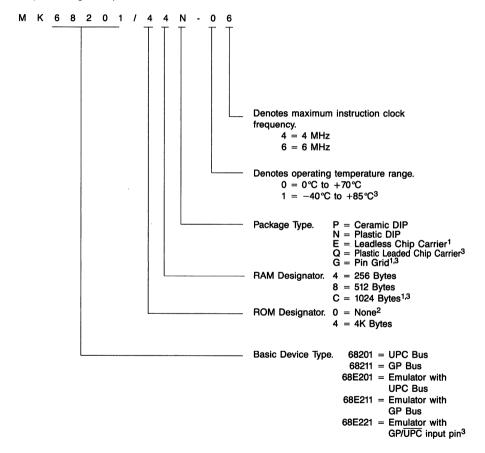

| EF68HC04P3  | 2-181 | ETL9311     | 1-21  | MK68201     | 3-5   |

| ET9320      | 1-45  | ETL9313     | 1-41  | MK68211     | 3-5   |

| ET9321      | 1-45  | ETL9320     | 1-91  | MK68E201    | 3-5   |

| ET9322      | 1-45  | ETL9321     | 1-91  | MK68E211    | 3-5   |

| ET9420      | 1-45  | ETL9322     | 1-91  | MK68E221    | 3-5   |

| ET9421      | 1-45  | ETL9344     | 1-115 | MK68HC201   | 3-77  |

| ET9422      | 1-45  | ETL9345     | 1-115 | MK68HC211   | 3-77  |

| ETC9310     | 1-5   | ETL9410     | 1-21  | MK68HC221   | 3-77  |

| ETC9311     | 1-5   | ETL9411     | 1-21  | TS68HC04J3  | 2-179 |

| ETC9320     | 1-69  | ETL9413     | 1-41  | TS94104     | 1-139 |

| ETC9321     | 1-69  | ETL9420     | 1-91  | TS94120     | 1-153 |

| ETC9322     | 1-69  | ETL9421     | 1-91  | TS94144     | 1-153 |

# 4-bit microcomputers

# 4 BIT MICROCOMPUTERS

| Function                                      | Part number                                 | Characteristic                                                                                                                                                                                                                      |                                                     | Package | Page                 |

|-----------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------|----------------------|

| LOW COST<br>MCUs                              |                                             | With their efficient instruction set (1 byte instruction) and wide I/O option list, these MCUs are designed for home appliances and consumer applications.  • One 4-bit SIO  • Emulation and development on DEVICE                  | • 19 I/O lines                                      | DIL24   | 1-5<br>1-21          |

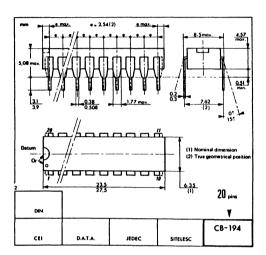

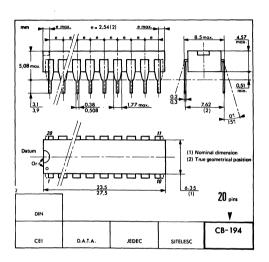

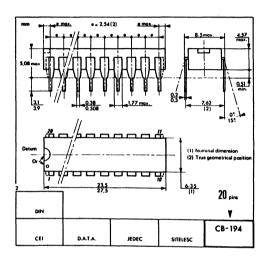

|                                               | ETC9411/9311<br>ETL9411/9311                |                                                                                                                                                                                                                                     | • RAM: 32 x 4<br>• ROM: 512 x 8<br>• 16 I/O lines   | DIL20   | 1-5<br>1-21          |

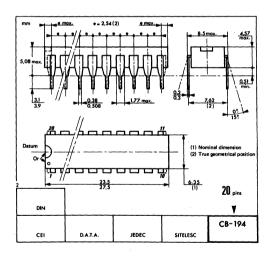

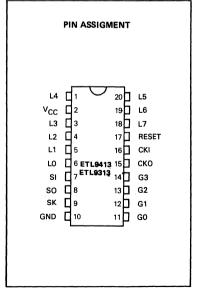

|                                               | ETL9413<br>ETL9313                          | _                                                                                                                                                                                                                                   | • RAM: 32 x 4<br>• ROM: 512 x 8<br>• 15 I/O lines   | DIL20   | 1-41                 |

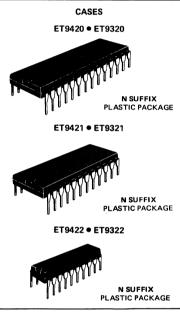

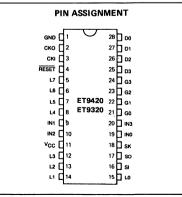

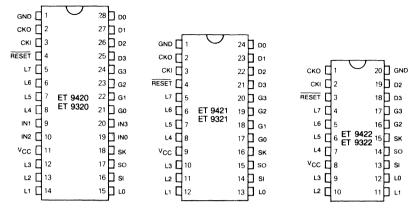

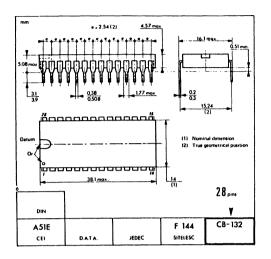

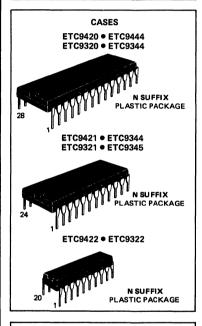

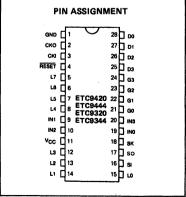

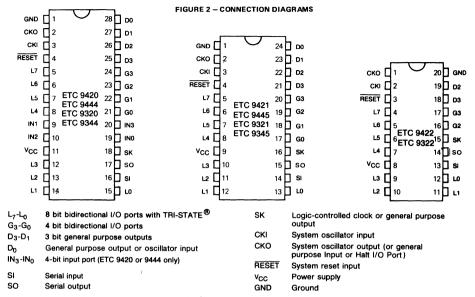

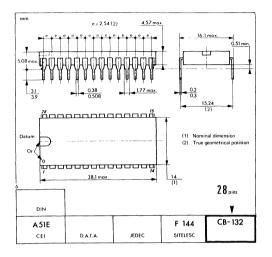

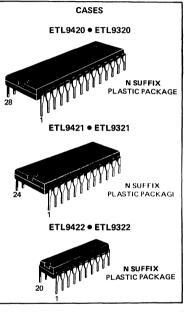

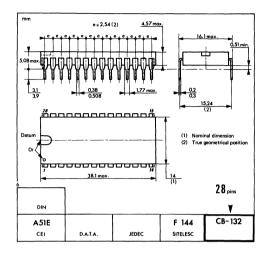

|                                               | ET9420/9320<br>ETC9420/9320<br>ETL9420/9320 | _                                                                                                                                                                                                                                   | • RAM: 64 x 4<br>• ROM: 1024 x 8<br>• 23 I/O lines  | DIL28   | 1-45<br>1-69<br>1-91 |

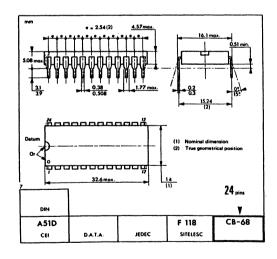

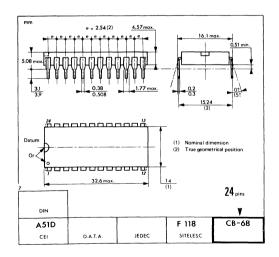

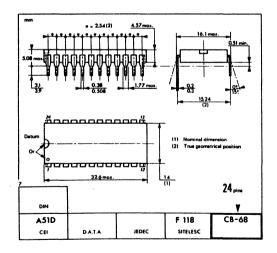

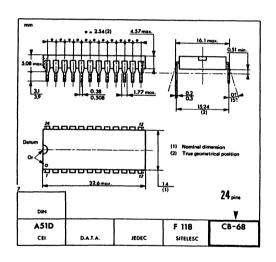

|                                               | ET9421/9321<br>ETC9421/9321<br>ETL9421/9321 |                                                                                                                                                                                                                                     | • RAM: 64 x 4<br>• ROM: 1024 x 8<br>• 19 I/O lines  | DIL24   | 1-45<br>1-69<br>1-91 |

|                                               | ET9422/9322<br>ETC9422/9322<br>ETL9422/9322 |                                                                                                                                                                                                                                     | • RAM: 64 x 4<br>• ROM: 1024 x 8<br>• 15 I/O lines  | DIL20   | 1-45<br>1-69<br>1-91 |

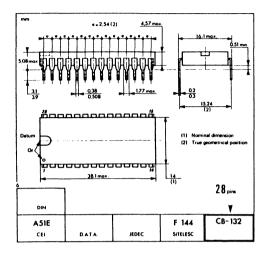

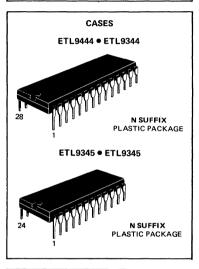

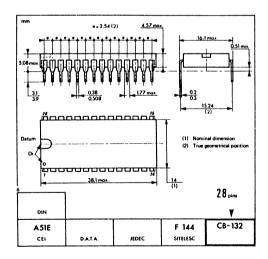

|                                               | ETC9444/9344<br>ETL9444/9344                | _                                                                                                                                                                                                                                   | • RAM: 128 x 4<br>• ROM: 2048 x 8<br>• 23 I/O lines | DIL28   | 1-69<br>1-115        |

|                                               | ETC9445/9345<br>ETL9445/9345                |                                                                                                                                                                                                                                     | • RAM: 128 x 4<br>• ROM: 2048 x 8<br>• 23 I/O lines | DIL24   | 1-69<br>1-115        |

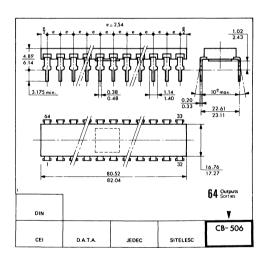

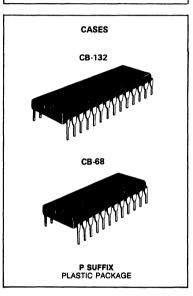

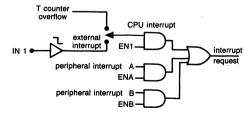

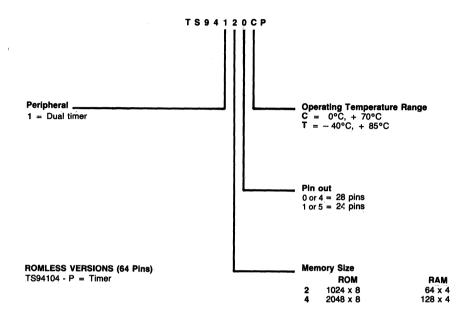

| MOTOR<br>SPEED<br>CONTROL<br>LOW COST<br>MCUs | TS94104                                     | Well suited for speed measurement, direct triac drive in industrial environment (watchdog feature). Individual clock for MCU, speed measurement timer and triac drive timer.  • One 4-bit SIO • Emulation and development on DEVICE | • ROM: 2048 x 8                                     | DIL64   | 1-139                |

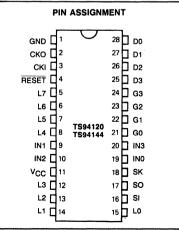

|                                               | TS94120                                     |                                                                                                                                                                                                                                     | • RAM: 64 x 4<br>• ROM: 1024 x 8<br>• 23 I/O lines  |         | 1-153                |

|                                               | TS94144                                     |                                                                                                                                                                                                                                     | RAM: 128 x 4     ROM: 2048 x 8     23 I/O lines     | DIL28   | 1-153                |

|                                               |                                             |                                                                                                                                                                                                                                     |                                                     |         |                      |

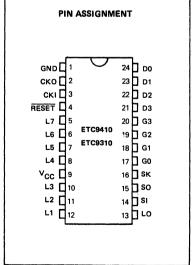

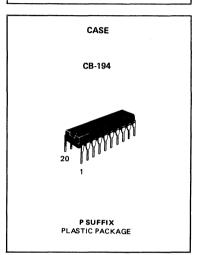

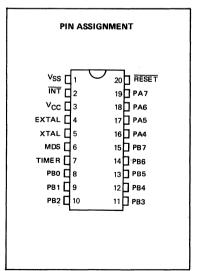

# ETC9410 • ETC9411 • ETC9310 • ETC9311

# SINGLE CHIP MICROCONTROLLERS

The ETC 9410, C 9411, C 9310, and C 9311, fully Static, Single-Chip CMOS Microcontrollers are fully compatible with the family, fabricated using double-poly, silicon gate CMOS technology. These Controller Oriented Processors are complete microcomputers containing all system timing, internal logic, ROM, RAM, and I/O necessary to implement dedicated control functions in a variety of applications. Features include single supply operation, a variety of output configuration options, with an instruction set, internal architecture and I/O scheme designed to facilitate keyboard input. display output and BCD data manipulation. The ETC 9411 is identical to the ETC 9410 but with 16 I/O lines instead of 20. They are an appropriate choice for use in numerous human interface control environments. Standard test procedures and reliable high-density fabrication techniques provide the medium to large volume customers with a customized Controller Oriented Processor at a low end-product cost.

The ETC 9310/C9311 is the extended temperature range version of the ETC 9410/C9411.

- Lowest Power Dissipation (40µW typical)

- Low Cost

- Power saving HALT mode with Continue function

- Powerful Instruction Set

- 512 × 8 ROM, 32 × 4 RAM

- 20 I/O lines (ETC 9410)

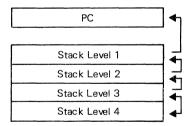

- Two-level subroutine stack

- DC to 4 μs instruction time

- Single supply operation (2.4V to 5.5V)

- General purpose and TRI-STATE outputs

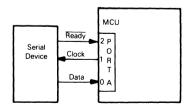

- Internal binary/counter register with MICROWIRE ® compatible serial I/O

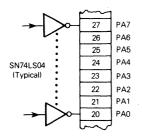

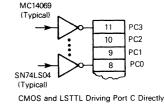

- LSTTL/CMOS compatible in and out

- Software/hardware compatible with other members of the ET 9400 family

- Extended temperature ( 40°C to + 85°C).

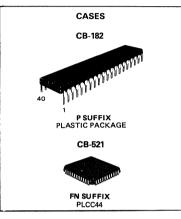

# **CMOS**

JULY 1986 1/16

ETC9410 / 9411

ETC9310 / 9311

## ETC 9410 . ETC 9411

#### ABSOLUTE MAXIMUM RATINGS

Supply Voltage (V<sub>CC</sub>)

Voltage at Any Pin Relative to GND

Ambient Operating Temperature

Ambient Storage Temperature

Lead Temperature (Soldering, 10 seconds)

Total Source Current

Total Sink Current

Total Sink Current

Total Sink Current

Total Sink Current

Total Sink Current

Total Sink Current

Total Sink Current

Total Sink Current

Total Sink Current

Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

## DC ELECTRICAL CHARACTERISTICS 0°C<TA<+70°C (Unless otherwise specified)

| Parameter                                                           | Conditions                                                                                                  | Min.                 | Max.                    | Units                    |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------|-------------------------|--------------------------|

| Operating Voltage                                                   |                                                                                                             | 2.4                  | 5.5                     | V                        |

| Power Supply Ripple (Note 5)                                        | Peak to peak                                                                                                | _                    | 0.1V <sub>CC</sub>      |                          |

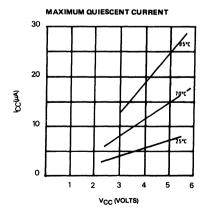

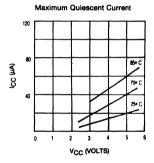

| Supply Current<br>(Note 1)                                          | $V_{CC} = 2.4V \text{ tc} = 125 \mu\text{s}$                                                                | -                    | 40                      | μА                       |

| HALT Mode Current                                                   | $V_{CC}$ = 5.0V tc = 16 μs<br>$V_{CC}$ = 5.0V tc = 4 μs<br>(tc is the instruction cycle time)               | -                    | 500<br>2000             | μ <b>Α</b><br>μ <b>Α</b> |

| (Note 2)                                                            | V <sub>CC</sub> = 5.0V Fin = 0kHz<br>V <sub>CC</sub> = 2.4V Fin = 0kHz                                      | -                    | 15<br>·6                | μ <b>Α</b><br>μ <b>Α</b> |

| Input Voltage Levels                                                |                                                                                                             |                      |                         |                          |

| RESET, CKI Logic High Logic Low All other inputs                    |                                                                                                             | 0.9V <sub>cc</sub>   | -<br>0.1v <sub>CC</sub> | V                        |

| Logic High<br>Logic Low                                             |                                                                                                             | 0.7V <sub>cc</sub>   | 0.2V <sub>CC</sub>      | Ÿ                        |

| Hi – Z input leakage<br>Input capacitance                           |                                                                                                             | - 1<br>-             | + 1<br>+ 7              | μA<br>pF                 |

| Output Voltage Levels<br>LSTTL Operation<br>Logic High<br>Logic Low | Standard outputs<br>$V_{CC} = 5.0V \pm 5 \%$<br>$IOH = -25 \mu A$<br>$IOL = 400 \mu A$                      | 2.7                  | _<br>0.4                | V                        |

| CMOS Operation                                                      | 102 - 400 μΛ                                                                                                |                      | 0.4                     | •                        |

| Logic High<br>Logic Low                                             | IOH = -10 μA<br>IOL= 10μA                                                                                   | V <sub>CC</sub> -0.2 | 0.2                     | V                        |

| Output current levels<br>Sink (Note 6)                              | (except CKO)  V <sub>CC</sub> = 4.5V, Vout = V <sub>CC</sub> V <sub>CC</sub> = 2.4V, Vout = V <sub>CC</sub> | 1.2<br>0.2           | -                       | mA<br>mA                 |

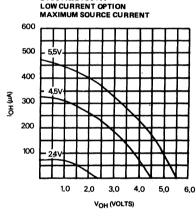

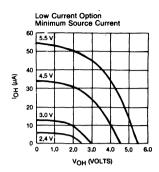

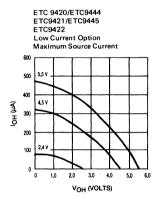

| Source (standard option) Source (low current option)                | V <sub>CC</sub> = 4.5V, Vout = 0V<br>V <sub>CC</sub> = 2.4V, Vout = 0V<br>V <sub>CC</sub> = 4.5V, Vout = 0V | 0.5<br>0.1<br>30     | -<br>-<br>330           | mA<br>mA                 |

| Source (low current option)                                         | $V_{CC} = 4.5V$ , $V_{OUT} = 0V$<br>$V_{CC} = 2.4V$ , $V_{OUT} = 0V$                                        | 6                    | 80                      | μ <b>Α</b><br>μ <b>Α</b> |

| CKO (as clock out) current levels                                   |                                                                                                             |                      |                         |                          |

| Sink divide by 4 divide by 8 divide by 16                           | $V_{CC} = 4.5V$ , CKI = $V_{CC}$ , Vout = $V_{CC}$                                                          | 0.3<br>0.6<br>1.2    | -<br>-<br>-             | mA<br>mA<br>mA           |

| Source<br>divide by 4                                               | V <sub>CC</sub> = 4.5V, CKI = 0, Vout = 0                                                                   | 0.3                  | _                       | mA                       |

| divide by 8<br>divide by 16                                         |                                                                                                             | 0.6<br>1.2           | -                       | mA<br>mA                 |

# ETC 9410 • ETC 9411

# DC ELECTRICAL CHARACTERISTICS (continued)

| Parameter                                                                                        | Conditions                                                                     | Min. | Max.             | Units          |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|------------------|----------------|

| Allowable Loading on CKO (as HALT)<br>Current needed to over-ride HALT<br>To continue<br>To halt | (note 3) $V_{CC} = 4.5V$ , $ViN = .2V_{CC}$ $V_{CC} = 4.5V$ , $ViN = .7V_{CC}$ | -    | 100<br>.6<br>1.6 | pF<br>mA<br>mA |

| TRI-STATE® or open drain leakage current                                                         |                                                                                | -2   | + 2              | Αίų            |

## ETC 9410 • ETC 9411

# AC ELECTRICAL CHARACTERISTICS (0°C<TA<+70°C (Unless otherwise specified)

| Parameter                                               | Conditions                                                                                                                                                                 | Min.                                      | Max.                                   | Units                                  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------|----------------------------------------|

| Instruction Cycle<br>Time = tc                          | V <sub>CC</sub> ≥4.5V<br>4.5V>V <sub>CC</sub> ≥2.4V                                                                                                                        | 4<br>16                                   | DC<br>DC                               | μs<br>μs                               |

| Operating CKI<br>Frequency                              | 4 mode<br>8 mode<br>16 mode<br>4 mode<br>4 mode<br>8 mode<br>8 mode<br>16 mode<br>16 mode<br>16 mode                                                                       | DC<br>DC<br>DC<br>DC<br>DC                | 1.0<br>2.0<br>4.0<br>250<br>500<br>1.0 | MHz<br>MHz<br>MHz<br>kHz<br>kHz<br>MHz |

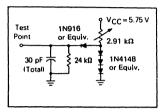

| Instruction Cycle<br>Time - CKI (RC) (Note 4)           | R = 30k ± 5 %, V <sub>CC</sub> = 5V<br>C = 82pF ± 5 % (÷ 4 Mode)                                                                                                           | 8                                         | 16                                     | μs                                     |

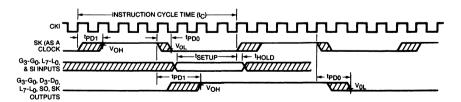

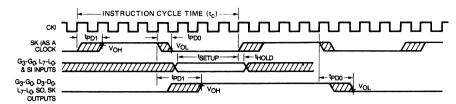

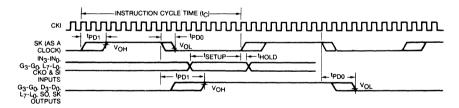

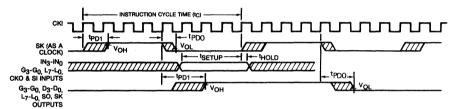

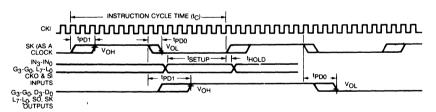

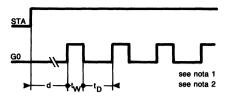

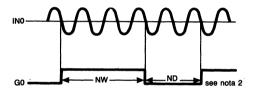

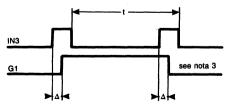

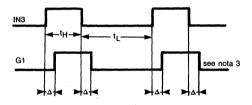

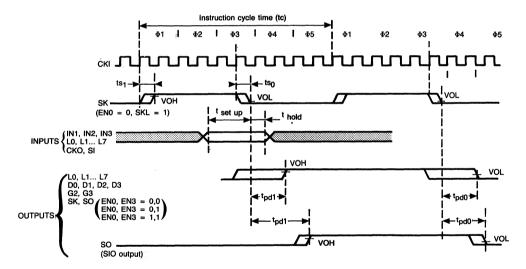

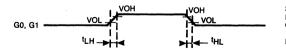

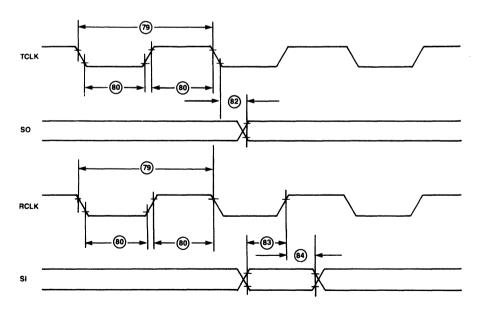

| INPUTS : (See Fig. 3)  **SETUP  **HOLD                  | $ \begin{array}{c} \text{G Imputs} \\ \text{SI Input} \\ \text{All Others} \\ \text{V}_{CC}\!\geqslant\!4.5\text{V} \\ \text{V}_{CC}\!\geqslant\!2.4\text{V} \end{array} $ | tc/4 = + 0.7<br>0.3<br>1.7<br>0.25<br>1.0 | -<br>-<br>-<br>-                       | μs<br>μs<br>μs<br>μs<br>μs             |

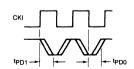

| OUTPUT Propagation delay (see fig. 3) PD1, PD0 PD1, PD0 | Vout = 1.5V, $C_L$ = 100pF, $R_L$ = 5K<br>$V_{CC}$ ≥ 4.5V<br>$V_{CC}$ ≥ 2.4V                                                                                               |                                           | 1.0<br>4.0                             | μs<br>μs                               |

Note 1: Supply current is measured after running for 2000 cycle times with a square -wave clock on CKI, CKO open, and all other pins pulled up to VCC with 20k resistors.

Note 2: The HALT mode will stop CKI from oscillating in the RC and crystal configurations.

Note 3: When forcing HALT, current is only needed for a short time (approx. 200 ns) to flip the HALT flip-flop.

Note 4: This parameter is only sampled and not 100 % tested.

Note 5: Voltage change must be less than 0.5 volt in a 1 ms period.

Note 6: SO output sink current must be limited to keep VOL below 0.2 VCC when port is running in order to prevent entering test mode.

# ETC 9310 • ETC 9311

## **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage (VCC)

6V

Voltage at any pin

-0.3V to  $V_{CC} + 0.3V$

Operating temperature range - 40°C to + 85°C

Storage temperature range - 65°C to + 150°C Lead temperature (soldering, 10 sec.)

Total allowable source current Total allowable sink current

25mA 25mA

Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute

maximum ratings.

# DC ELECTRICAL CHARACTERISTICS - 40°C≤TA≤+85°C (Unless otherwise specified).

| Parameter                                                                                                                              | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Min.                                        | Max.                      | Units                      |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------|----------------------------|

| Operating Voltage                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.0                                         | 5.3                       | V                          |

| Power Supply Ripple(Note 5)                                                                                                            | Peak to Peak                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                           | 0.1V <sub>CC</sub>        | V                          |

| Supply Current (Note 1)                                                                                                                | $V_{CC}$ = 3.0V, $t_0$ = 125 $\mu$ s<br>$V_{CC}$ = 5.0V, $t_0$ = 16 $\mu$ s<br>$V_{CC}$ = 5.0V, $t_0$ = 4 $\mu$ s<br>( $t_0$ is instruction cycle time)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -<br>-<br>-                                 | 60<br>600<br>2500         | μΑ<br>μΑ<br>μΑ             |

| HALT Mode Current<br>(Note 2)                                                                                                          | $V_{CC}$ = 5.0V, $F_{IN}$ = 0kHz<br>$V_{CC}$ = 3.0V, $F_{IN}$ = 0kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | =                                           | 25<br>13                  | μ <b>Α</b><br>μ <b>Α</b>   |

| Input Voltage Levels<br>RESET, CKI<br>Logic High<br>InpuLogic Low<br>All Other Inputs<br>Logic High<br>Logic Low<br>Hi-Z Input Leakage |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.9 V <sub>CC</sub> - 0.7 V <sub>CC</sub> 2 | 0.1 V <sub>CC</sub>       | V<br>V<br>V<br>μΑ          |

| Input Capacitance                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                             | 7                         | pF                         |

| Output Voltage Levels<br>LSTTL Operation<br>Logic High<br>Logic Low<br>CMOS Operation<br>Logic High<br>Logic Low                       | Standard Outputs $V_{CC}=5.0V\pm 5~\%$ $I_{OH}=25\mu A$ $I_{OL}=400\mu A$ $I_{OH}=-10\mu A$ $I_{OH}=-10\mu A$ $I_{OH}=-10\mu A$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.7<br>-<br>V <sub>CC</sub> - 0.2           | 0.4<br>-<br>0.2           | V<br>V<br>V                |

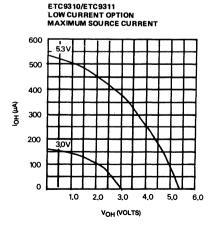

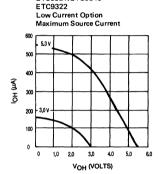

| Output Current Levels<br>Sink (Note 6)<br>Source (Standard<br>Option)<br>Source (Low<br>Current Option)                                | $V_{CC} = 4.5V, V_{OUT} = V_{CC} \\ V_{CC} = 3.0V, V_{OUT} = V_{CC} \\ V_{CC} = 4.5V, V_{OUT} = 0 V \\ V_{CC} = 3.0V, V_{OUT} = 0 V \\ V_{CC} = 4.5V, V_{OUT} = 0 V \\ V_{CC} = 3.0V, V_{CC} = 3.0V, V_{CC} = 3.0V \\ V_{CC} = 3.0V, V_{CC} = 3.0V \\ V_{CC} = 3.0V \\ V_{CC} = 3.0V \\ V_{CC} $ | 1.2<br>0.2<br>0.5<br>0.1<br>30<br>8         | -<br>-<br>-<br>440<br>200 | mA<br>mA<br>mA<br>μA<br>μA |

# ETC 9310 • ETC 9311 DC ELECTRICAL CHARACTERISTICS (continued)

| Parameter                                                             | Conditions                                                                                                                     | Min.                                   | Max.             | Units                      |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|----------------------------|

| CKO Current Levels (As Clock Out)  Sink                               | $V_{CC} = 4.5V$ , CKI = $V_{CC}$ , $V_{OUT} = V_{CC}$<br>$V_{CC} = 4.5V$ , CKI = OV, $V_{OUT} = OV$                            | 0.3<br>0.6<br>1.2<br>0.3<br>0.6<br>1.2 | -<br>-<br>-<br>- | mA<br>mA<br>mA<br>mA<br>mA |

| Allowable Loading on CKO<br>(as HALT I/O pin)                         |                                                                                                                                | -                                      | 100              | pF                         |

| Current Needed to<br>Override HALT (Note 3)<br>To Continue<br>To Halt | V <sub>CC</sub> = 4.5V, V <sub>IN</sub> = 0.2 V <sub>CC</sub><br>V <sub>CC</sub> = 4.5V, V <sub>IN</sub> = 0.7 V <sub>CC</sub> | <u>-</u>                               | 0.8<br>2.0       | mA<br>mA                   |

| TRI-STATE or Open Drain<br>Leakage Current                            |                                                                                                                                | - 4                                    | + 4              | μΑ                         |

# ETC 9310 • ETC 9311 AC ELECTRICAL CHARACTERISTICS —40°C≤T<sub>A</sub>≤+85°C (Unless otherwise specified)

| Parameter                                                                                                 | Conditions                                                                                        | · Min.                                  | Max.                                   | Units                                  |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------|----------------------------------------|

| Instruction Cycle Time (t <sub>c</sub> )                                                                  | V <sub>CC</sub> ≤4.5V<br>4.5V>V <sub>CC</sub> ≥3.0V                                               | 4<br>16                                 | DC<br>DC                               | μs<br>μs                               |

| Operating CKI                                                                                             | V <sub>cc</sub> ≥4.5V<br>4.5V>V <sub>cc</sub> ≥3.0V                                               | DC<br>DC<br>DC<br>DC<br>DC<br>DC        | 1.0<br>2.0<br>4.0<br>250<br>500<br>1.0 | MHz<br>MHz<br>MHz<br>kHz<br>kHz<br>MHz |

| Instruction Cycle Time<br>RC Oscillator (Note 4)                                                          | R = 30 k ± 5 %, $V_{CC}$ = 5V<br>C = 82pF ± 5 % (÷ 4 Mode)                                        | 8                                       | 16                                     | μs                                     |

| Inputs (See Figure 3) <sup></sup> t <sub>SETUP</sub> t <sub>HOLD</sub>                                    | G Inputs SI Input V <sub>CC</sub> > 4.5V All Others V <sub>CC</sub> > 4.5V V <sub>CC</sub> > 3.0V | tc/4 + 0.7<br>0.3<br>1.7<br>0.25<br>1.0 | -<br>-<br>-<br>-<br>-                  | µs<br>µs<br>µs<br>µs<br>µs             |

| Output Propagation<br>Delay<br>t <sub>PD1</sub> , t <sub>PD0</sub><br>t <sub>PD1</sub> , t <sub>PD0</sub> | $V_{OUT} = 1.5V$ , $C_L = 100pF$ , $R_L = 5k$<br>$V_{CC} \ge 4.5V$<br>$V_{CC} \ge 3.0V$           | =                                       | 1.0<br>4.0                             | μs<br>μs                               |

Note 1: Supply current is measured after running for 2000 cycle times with a square-ware clock on CKI, CKO open, and all other pins pulled up to V<sub>CC</sub> with 20 k resistors.

Note 2: The HALT mode will stop CKI from oscillating in the RC and crystal configurations.

Note 3: When forcing HALT, current is only needed for a short time (approximately 200 ns) to flip the HALT flip-flop.

Note 4: This parameter is only sampled and not 100 % tested.

Note 5: Voltage change must be less than 0.5 volt in a 1 ms period.

Note 6:SO output sink current must be limited to keep VOL below 0.2VCC when port is running in order to prevent entering test mode.

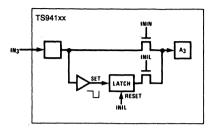

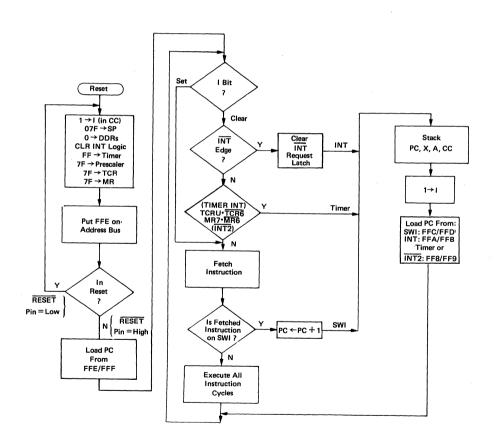

#### **FUNCTIONAL DESCRIPTION**

To ease reading of this description, only ETC 9410 and/or ETC 9411 are referenced; however, all such references apply equally to ETC 9310 and/or ETC 9311,

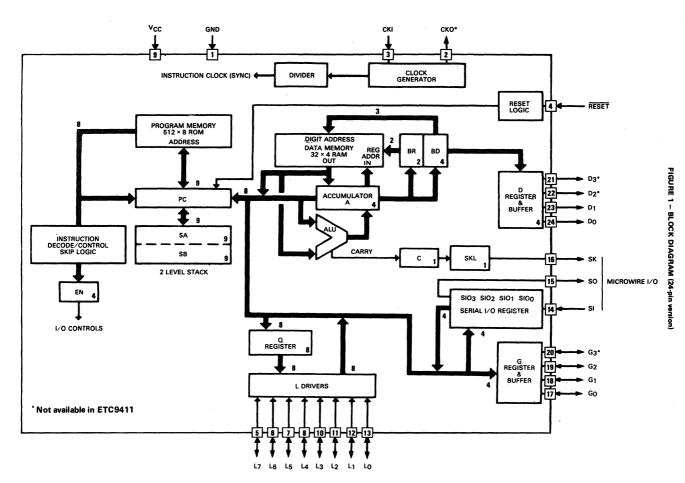

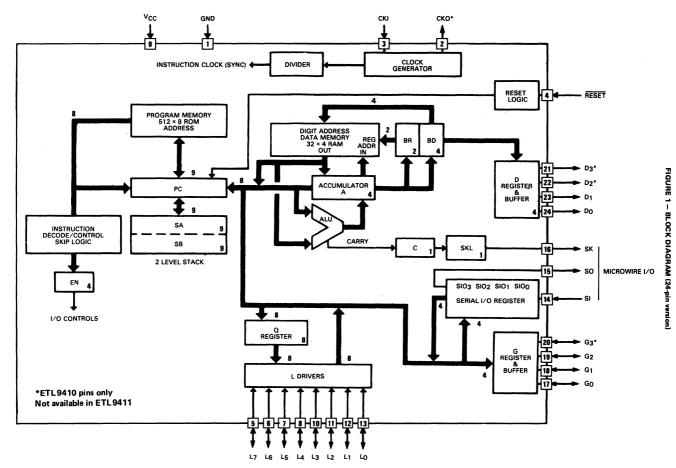

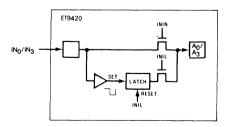

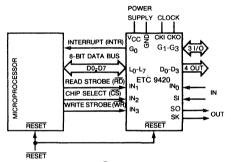

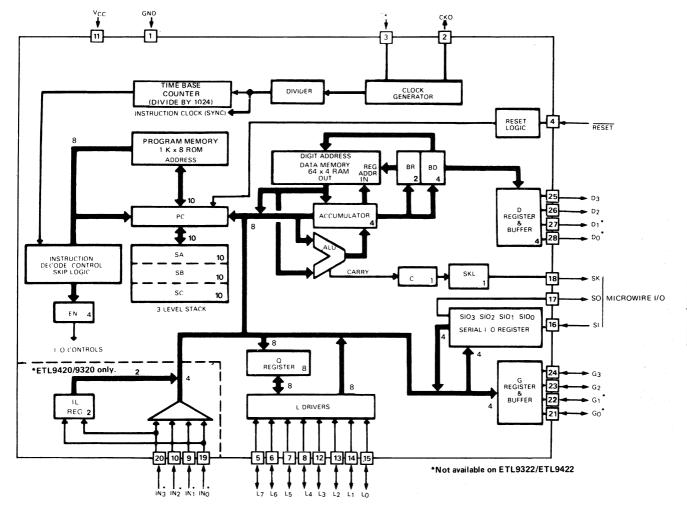

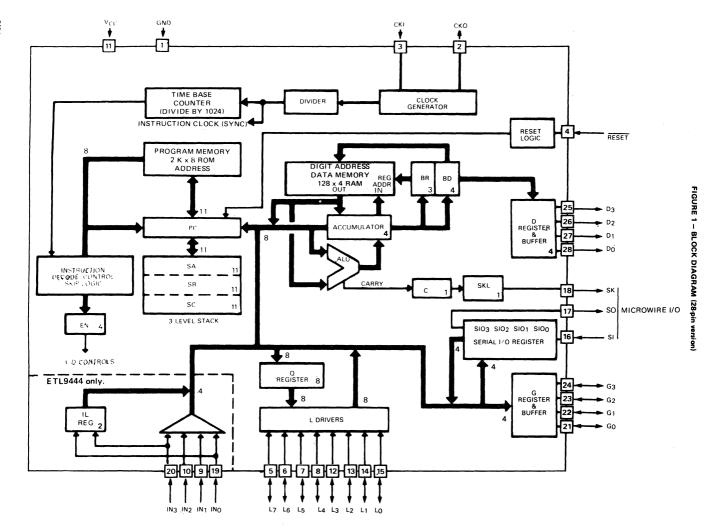

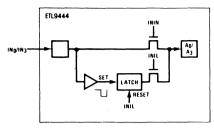

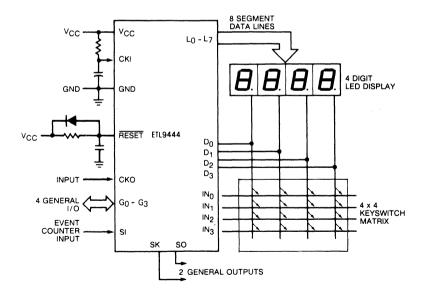

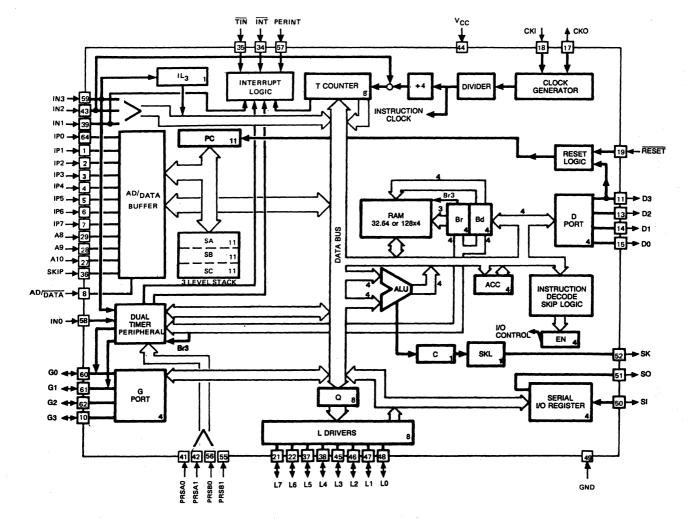

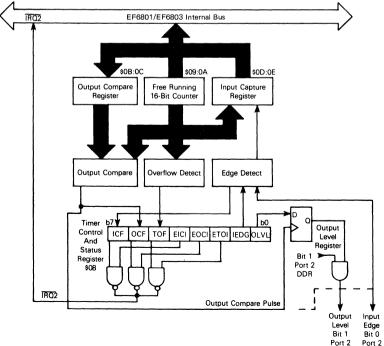

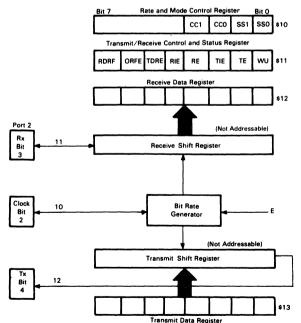

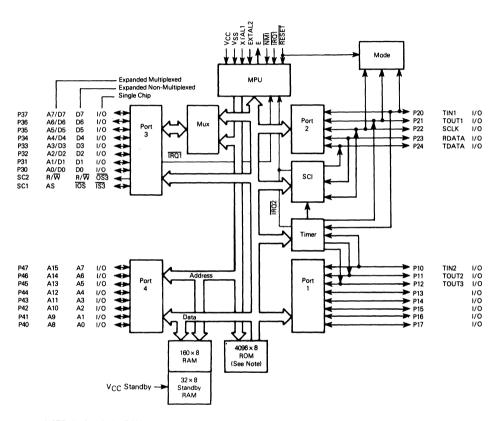

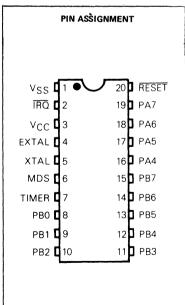

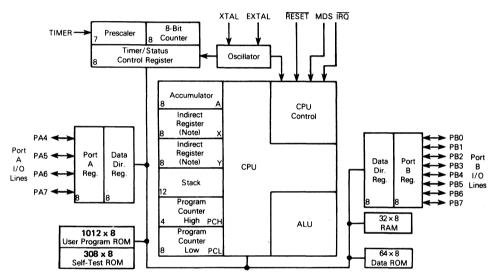

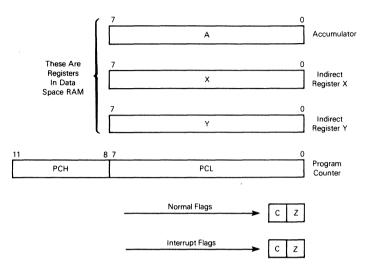

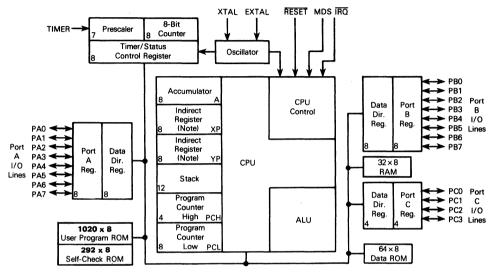

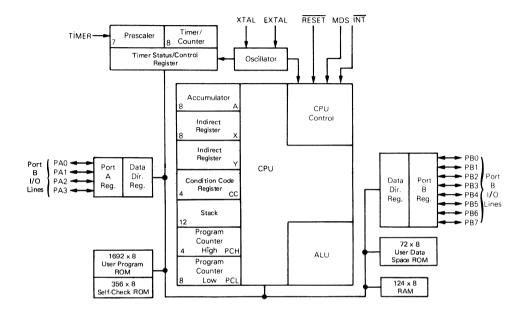

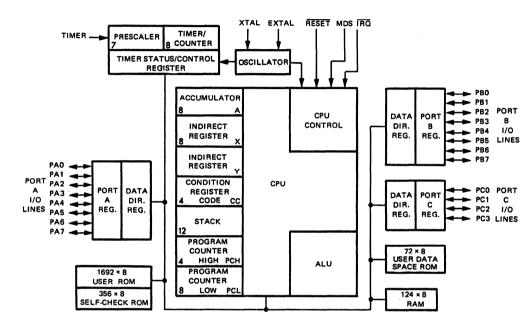

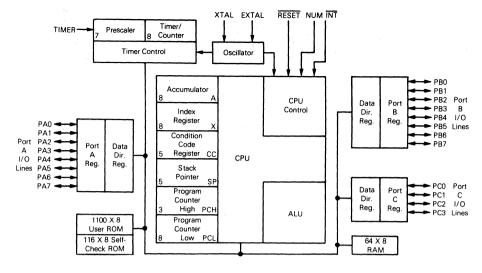

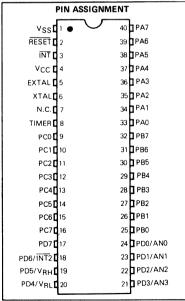

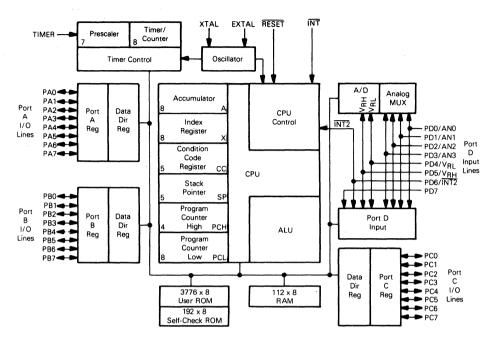

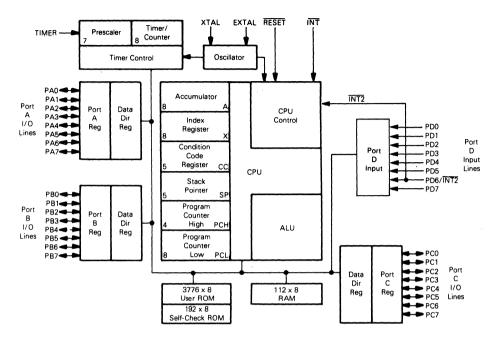

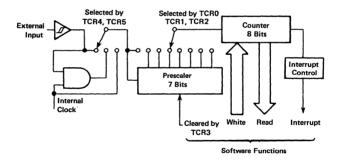

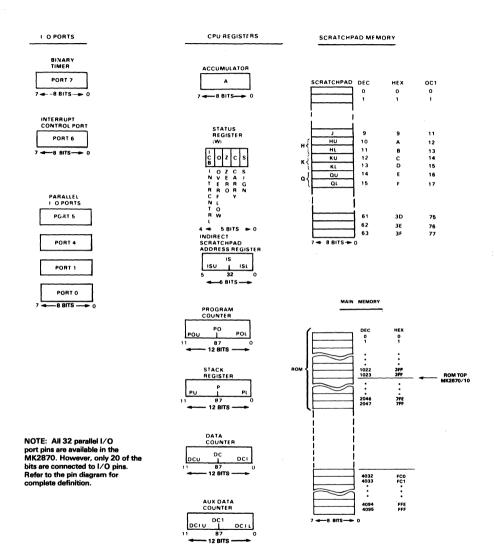

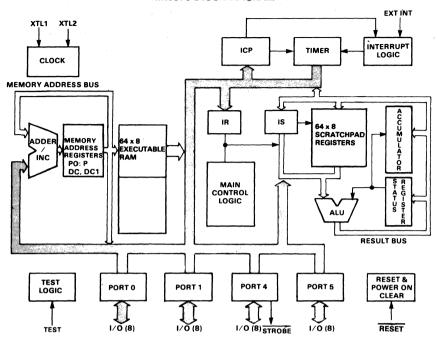

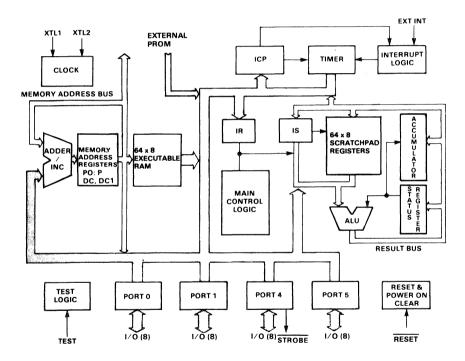

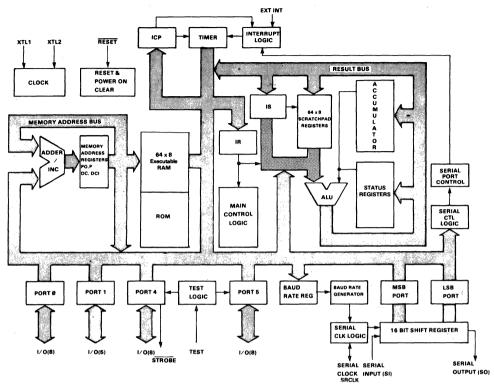

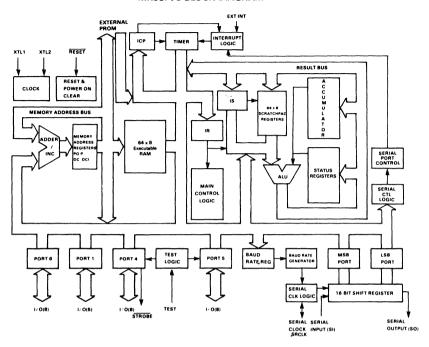

A block diagram of the ETC 9410 is given in Figure 1. Data paths are illustrated in simplified form to depict how the various logic elements communicate with each other in implementing the instruction set of the device. Positive logic is used. When a bit is set, it is logic "1" when a bit is reset, it is a logic "0".

# **Program Memory**

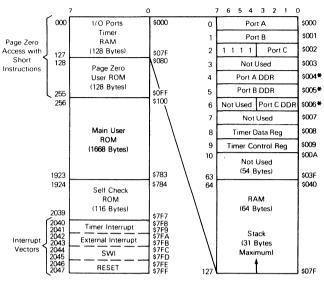

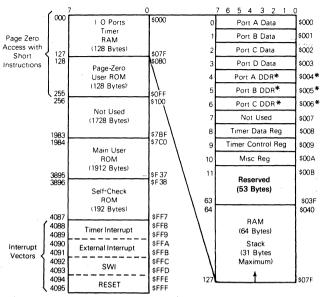

Program memory consists of a 512-byte ROM. As can be seen by an examination of the ETC 9410/C 9411 instruction set, these words may be program instructions, program data, or ROM addressing data. Because of the special characteristics associated with the JP, JSRP, JID, and LQID instructions, ROM must often be thought of being organized into 8 pages of 64 words (bytes) each.

## ROM addressing

ROM addressing is accomplished by a 9-bit PC register. Its binary value selects one of the 512 8-bit words contained in ROM. A new address is loaded into the PC register during each instruction cycle. Unless the instruction is a transfer of control instruction, the PC register is loaded with the next

sequential 9-bit binary count value. Two levels of subroutine nesting are implemented by two 9-bit subroutine save registers. SA and SB.

ROM instruction words are fetched, decoded, and executed by the Instruction Decode, Control and Skip Logic circuitry.

# **Data Memory**

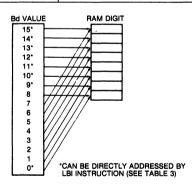

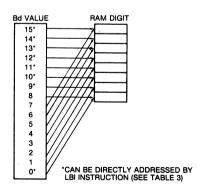

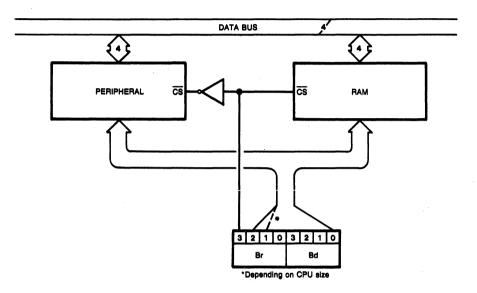

Data memory consists of a 128-bit RAM, organized as 4 data registers of 8  $\times$  4-bit digits. RAM addressing is implemented by a 6-bit B register whose upper 2 bits (Br)-select 1 of 4 data registers and lower 3 bits of the 4-bit Bd select 1 of eight 4-bit digits in the selected data register. While the 4-bit contents of the selected RAM digit (M) are usually loaded into or from, or exchanged with, the A register (accumulator), they may also be loaded into the Q latches or loaded from the L ports. RAM addressing may also be performed directly by the XAD 3,15 instruction. The Bd register also serves as a source register for 4-bit data sent directly to the D outpouts.

The most significant bit of Bd is not used to select a RAM digit. Hence, each physical digit of RAM may be selected by two different values of Bd a shown in Figure 4 below. The skip condition for XIS and XDS instructions will be true if Bd changes between 0 and 15, but NOT between 7 and 8 (see Table 3).

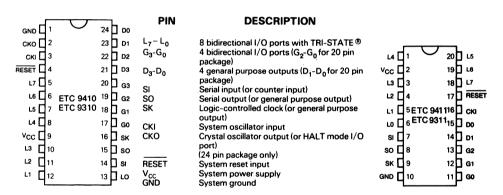

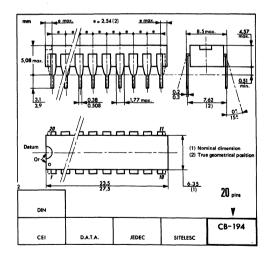

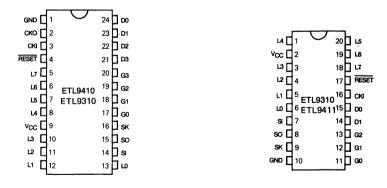

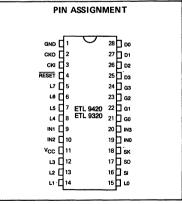

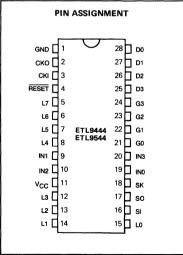

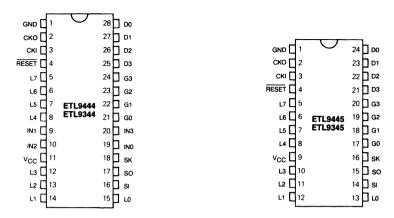

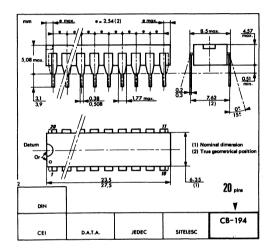

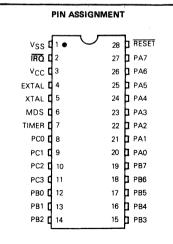

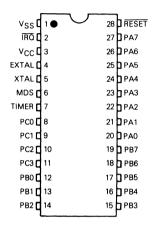

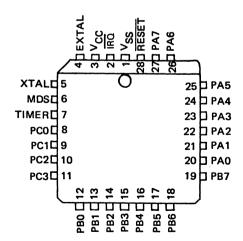

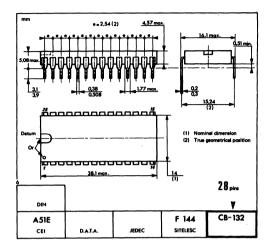

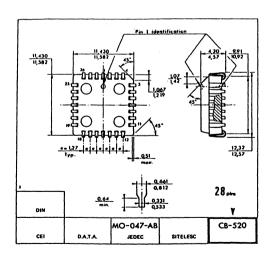

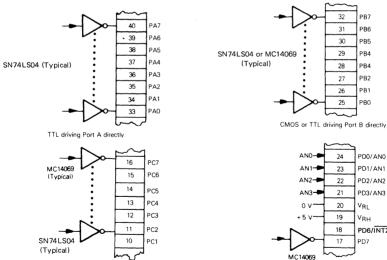

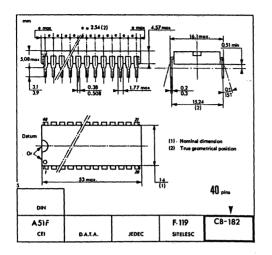

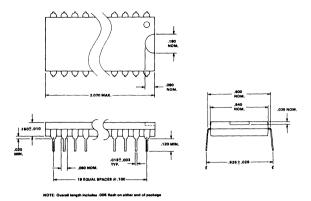

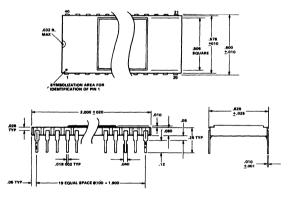

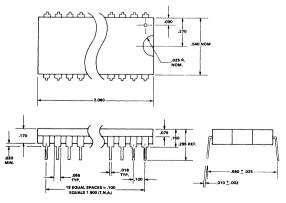

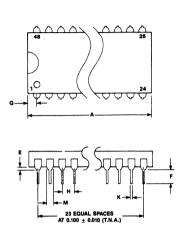

FIGURE 2 - CONNECTION DIAGRAMS

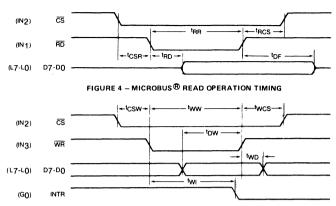

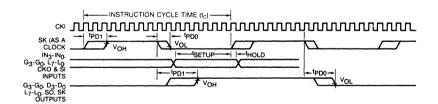

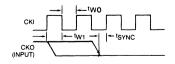

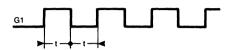

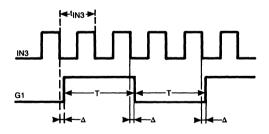

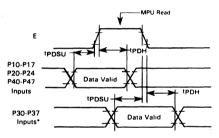

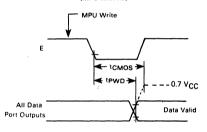

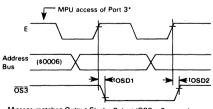

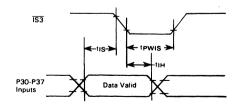

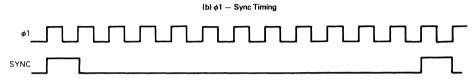

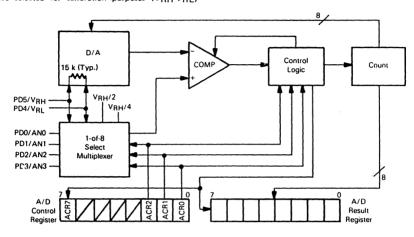

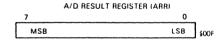

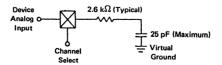

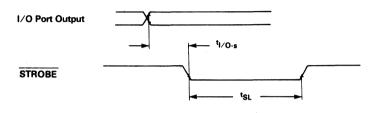

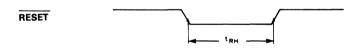

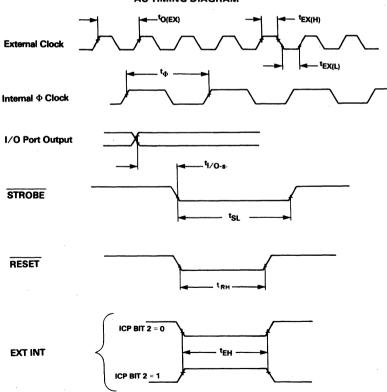

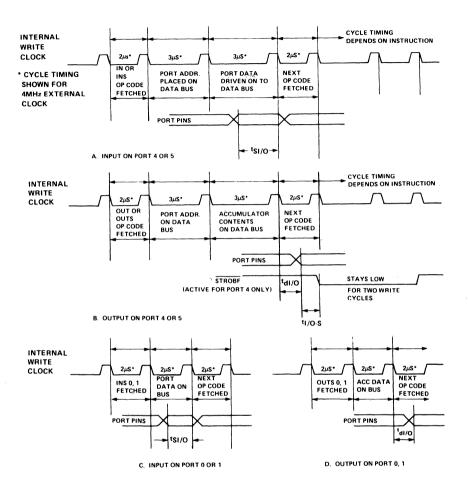

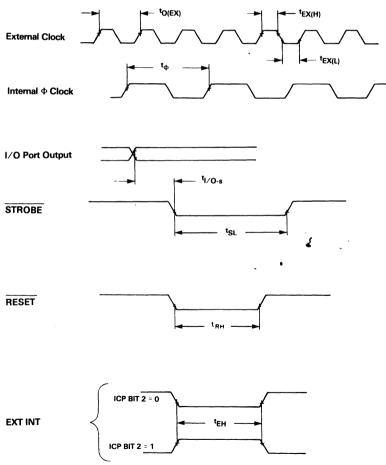

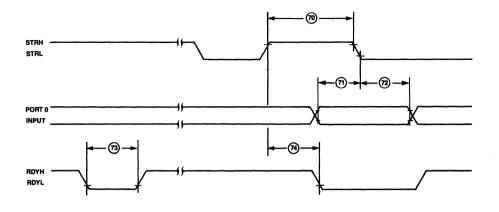

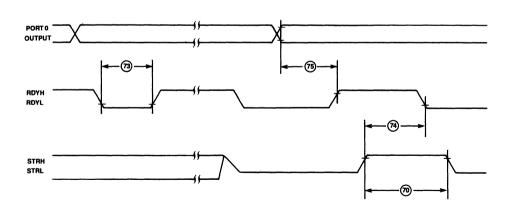

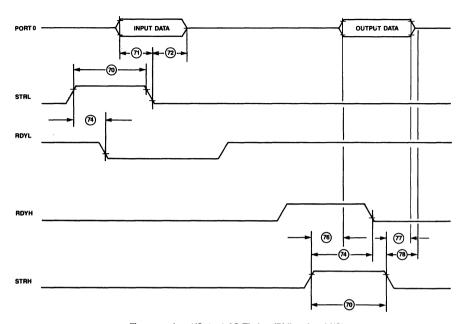

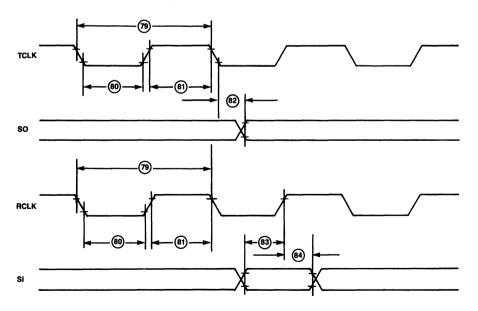

FIGURE 3 — INPUT/OUTPUT TIMING DIAGRAMS

(DIVIDE-BY-8 MODE)

The D register provides 4 general purpose outputs and is used as the destination register for the 4-bit contents of Bd.

The XAS instruction copies C into the SKL Latch. In the counter mode, SK is the output of SKL; in the shift register mode, SK is a sync clock, inhibited when SKL is a logic "0"

The EN register is an internal 4-bit register loaded under program control by the LEI instruction. The state of each bit of this register selects or deselects the particular feature associated with each bit of the EN register (EN3-EN0).

- 1. The least significant bit of the enable register, ENO, selects the SIO register as either a 4-bit shift register or as a 4-bit binary counter. With ENO set, SIO is an asynchronous binary counter, DECREMENTING its value by one upon each low going pulse ("1" to "0") occurring on the SI input. Each pulse must be at least 2 (two) instruction cycles wide. SK outputs the value of SKL. The SO output is equal to the value of EN3. With ENO reset. SIO is a serial shift register, shifting left each instruction cycle time. The data present at SI is shifted into the least significant bit of SIO. SO can be enabled to output the

- most significant bit of SIO each instruction cycle time. (See 4 below). The SK output becomes a logic controlled clock.

- 2. EN1 is not used, it has NO effect on the ETC 9410/ C 9411.

- 3. With EN2 set, the L drivers are enabled to output the data in  $\Omega$  to the L I/O ports. Resetting EN2 disables the L drivers, placing the L I/O ports in a hight impedance input state

- 4. EN3, in conjunction with EN0, affects the SO output. With EN0 set (binary counter option selected), SO will output the value loaded into EN3. With EN0 reset (serial shift register option selected), setting EN3 enables SO as the output of the SIO shift register, outputting serial shifted data each instruction time. Resetting EN3 with the serial shift register output: data continues to be shifted through SIO and can be exchanged with A via an XAS instruction but SO remains reset to "0"

# Enable Register Modes — Bits EN<sub>3</sub> and EN<sub>0</sub>

| EN <sub>3</sub> | EN <sub>0</sub> | SIO            | SI                      | so         | SK                     |

|-----------------|-----------------|----------------|-------------------------|------------|------------------------|

| 0               | 0               | Shift Register | Input to Shift Register | 0          | If SKL = 1, SK = Clock |

|                 | 1               |                |                         |            | If SKL = 0, SK = 0     |

| 1               | 0               | Shift Register | Input to Shift Register | Serial Out | If SKL = 1, SK = Clock |

|                 |                 | ·              |                         |            | If SKL = 0, SK = 0     |

| 0               | 1               | Binary Counter | Input to Binary Counter | o          | If SKL = 1, SK = 1     |

|                 |                 |                |                         |            | If SKL = 0, SK = 0     |

| 1               | 1.              | Binary Counter | Input to Binary Counter | 1          | If SKL = 1, SK = 1     |

|                 |                 |                |                         |            | If SKL = 0, SK = 0     |

# Internal Logic

The internal logic of the ETC 9410/C 9411 is designed to insure fully static operation of the device.

The 4-bit A register (accumulator) is the source and destination register for most I/O, arithmetic, logic and data memory access operations. It can also be used to load the Bd portion of the register, to load 4 bits of the 8-bit Q latch data and to perform data exchanges with the SIO register.

A 4-bit adder performs the arithmetic and logic functions of the ETC 9410/C 9411, storing its results in A. It also outputs the carry information to a 1-bit carry register, most often employed to indicate arithmetic overflow. The C registerin conjunction with the 'XAS instruction and the EN register, also serves to control the SK output. C can be outputted directly to SK or can enable SK to be a sync clock each instruction cycle time. (See XAS instruction and EN register description below).

The G register contents are outputs to 4 general-purpose bidirectional I/O ports.

The Q register is an internal, latched, 8-bit register, used to hold data loaded from RAM and A, as well as 8-bit data from ROM. Its contents are output to the L I/O ports when the L drivers are enabled under program control. (See LEI instruction).

The 8L drivers, when enabled, output the contents of latched Q data to the L I/O ports. Also, the contents of L may be read directly into A and RAM.

FIGURE 4 - RAM DIGIT ADDRESS TO PHYSICAL RAM DIGIT MAPPING

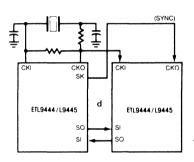

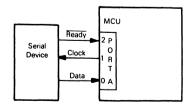

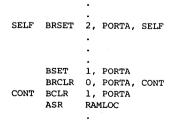

The SIO register functions as a 4-bit serial-in/serial-out shift register or as a binary counter depending upon the contents of the EN register. (See EN register description above). Its contents can be exchanged with A, allowing it to input or output continuous serial data stream. With SIO functioning as a serial-in/serial-out shift register and SK as a sync-clock, the ETC 9410/C 9411 is MICROWIRE® compatible.

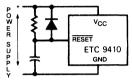

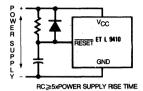

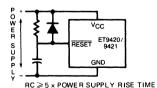

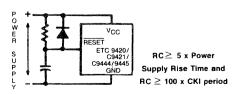

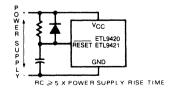

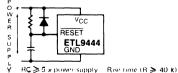

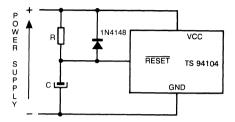

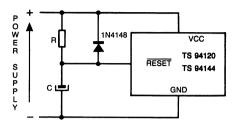

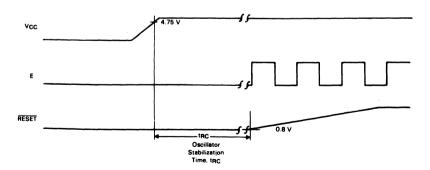

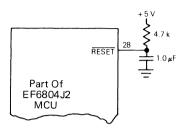

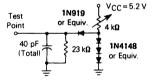

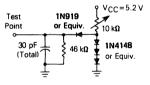

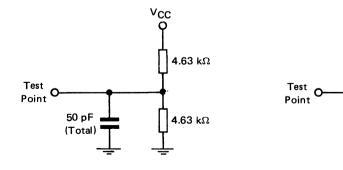

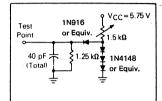

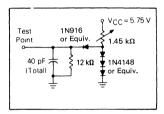

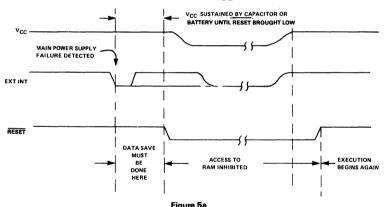

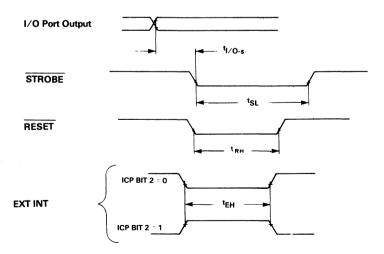

#### Initialization

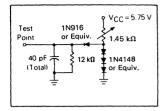

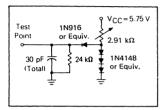

The internal reset logic will initialize the device upon power-up if the power supply rise time is less than 1 ms and if the operating frequency at CKI is greater than 32 kHz, otherwise the external RC network shown in Figure 5 must be connected to the RESET pin. The RESET pin is configured as a Schmitt trigger input. If not used, it should be connected to V<sub>CC</sub>. Initialization will occur whenever a logic "O" is applied to the RESET input, providing it stays low for at least three instruction cycle times.

NOTE: If CKI clock is less than 32 kHz, the internal reset logic (option 25 = I) MUST be disabled and the external RC network must be present.

RC > 5  $\times$  Power Supply Rise Time and RC > 100  $\times$  CKI period

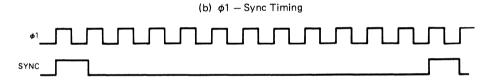

Upon initialization, the PC register is cleared to 0 (ROM address 0) and the A, B, C, D, EN, and G registers are cleared. The SK output is enabled as a SYNC output, providing a pulse each instruction cycle time. Data Memory (RAM) is not cleared upon initialization. The first instruction at address 0 must be a CLRA (clear A register).

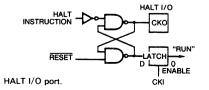

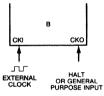

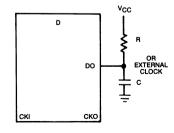

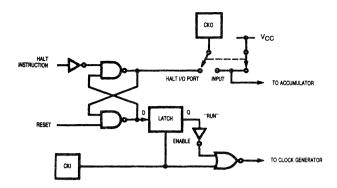

## **HALT Mode**

The ETC 9410/C 9411 is a FULLY STATIC circuit; therefore, the user may stop the system oscillator at any time to halt the chip. The chip may also be halted by the HALT instruction or by forcing CKO high when it is used as an HALT I/O port. Once in the HALT mode, the internal circuitry does not receive any clock signal, and is therefore frozen in the exact state it was in when halted. All information is retained until continuing. The HALT mode is the minimum power dissipation state.

The HALT mode has slight differences depending upon the type of oscillator used.

a) One-pin oscillator - (RC or External)

The HALT mode may be entered into by either program control (HALT instruction) or by forcing CKO to a logic "1" state.

The circuit may be awakened by one of two different methods:

- 1 Continue function by forcing CKO to a logic "0", the system clock is re-enabled and the circuit continues to operate from the point where it was stopped.

- Restart forcing the RESET pin to a logic "0" will restart the chip regardless of HALT or CKO (see Initialization).

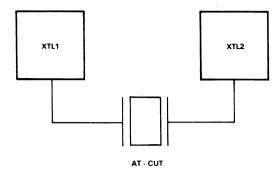

b) Two-pin oscillator - (Crystal)

The HALT mode may be entered into by program control (HALT instruction) which forces CKO to a logic "1" state. The circuit can be awakened only by the RESET function.

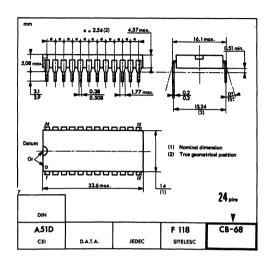

# **ETC 9411**

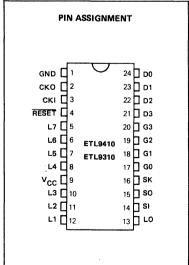

If the ETC 9410 is bonded as a 20-pin package, it becomes the ETC 9411 illustrated in Figure 2, ETC 9410/C 9411 Connection Diagrams. Note that the ETC 9411 does not contain D2, D3, G3, or CKO. Use of this option of course precludes use of D2, D3, G3, and CKO options. All other options are available for the ETC 9411.

# **CKO Pin Options**

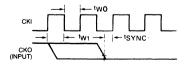

In a crystal controlled oscillator system, CKO is used as an output to the crystal network. CKO will be forced high during the execution of a HALT instruction, thus inhibiting the crystal network. If a one pin oscillator system is chosen (RC or external), CKO will be a selected as HALT and is an I/O flip-flop which is an indicator of the HALT status. An external signal can override this pin to start and stop the chip. By forcing a high level to CKO; the chip will stop as soon as CKI is high and the CKO output will go high to keep the chip stopped. By forcing a low level to CKO, the chip will continue and CKO output will go low.

All features associated with the CKO I/O pin are available with the 24-pin package only.

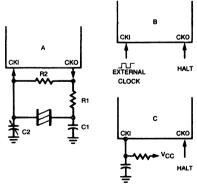

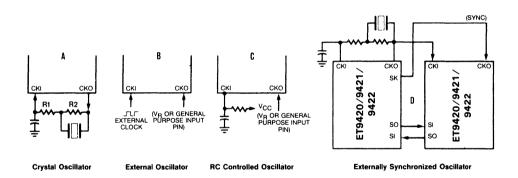

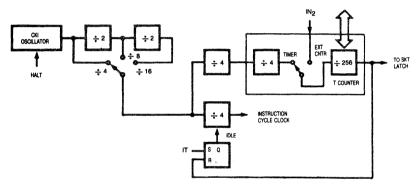

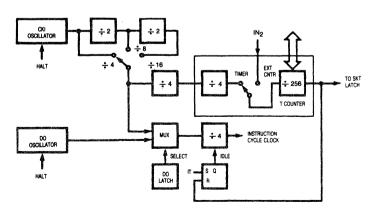

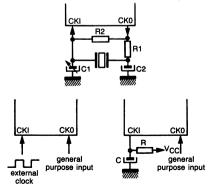

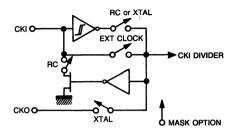

# **Oscillator Options**

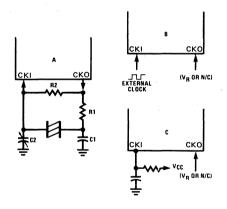

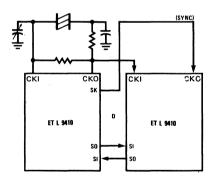

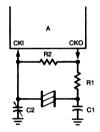

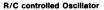

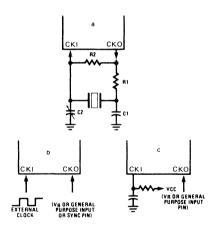

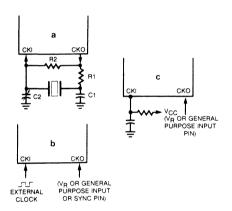

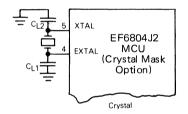

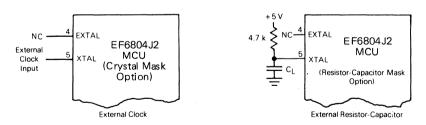

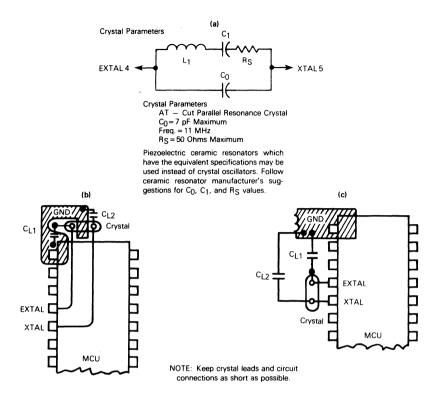

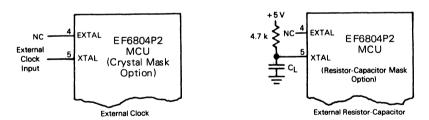

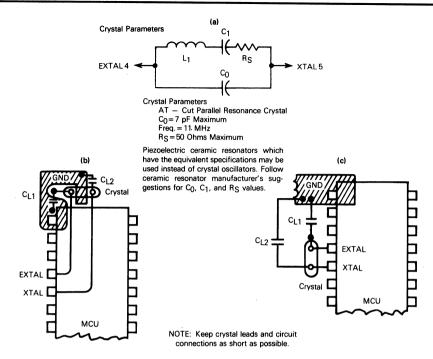

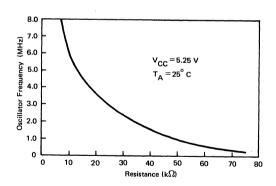

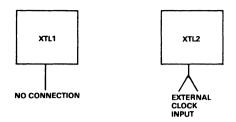

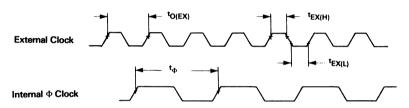

There are three options available that define the use of CKI and CKO.

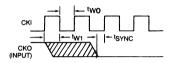

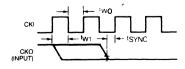

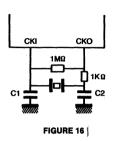

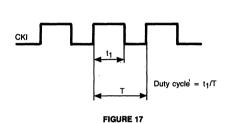

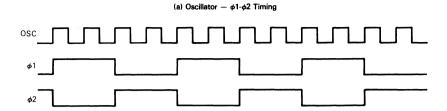

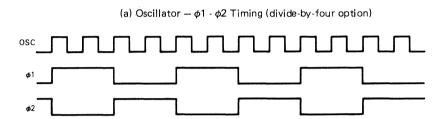

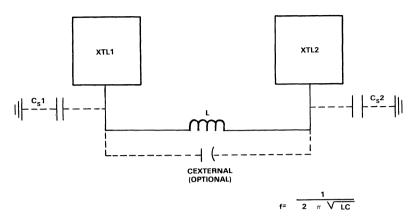

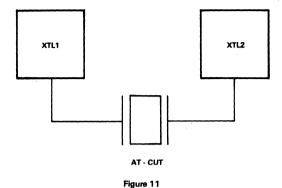

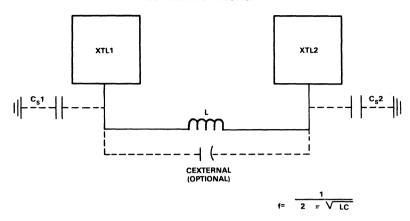

- a) Crystal Controlled Oscillator. CKI and CKO are connected to an external crystal. The instruction cycle time equals the crystal frequency divided by 16 (cptionally by 8 or 4).

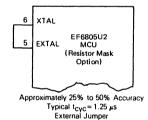

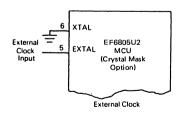

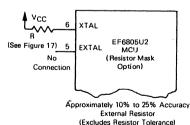

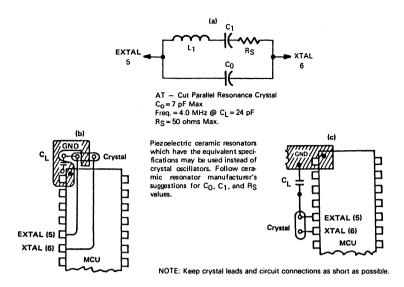

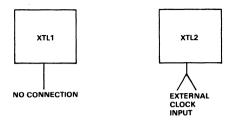

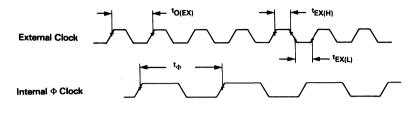

- b) External Oscillator. CKI is configured as a LSTTL compatible input accepting an external clock signal. The external frequency is divided by 16 (optionally by 8 or 4) to give the instruction cycle time. CKO is the HALT 1/0 port.

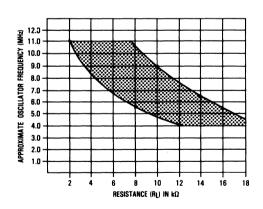

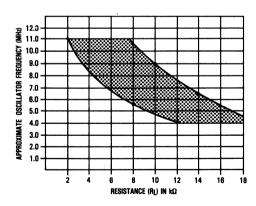

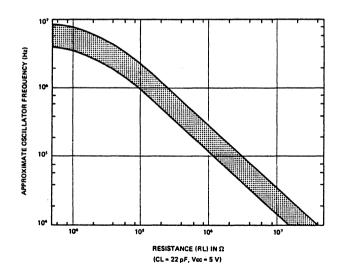

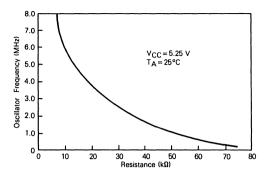

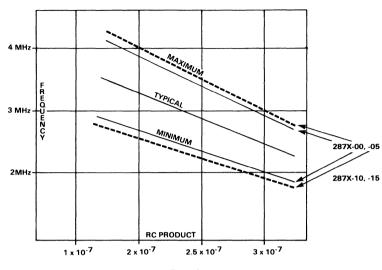

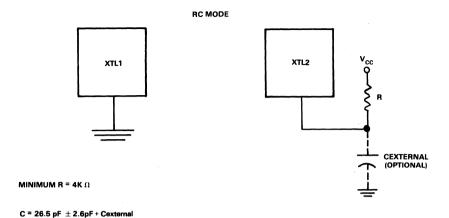

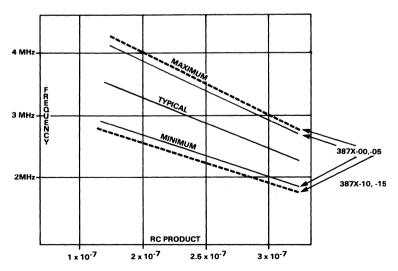

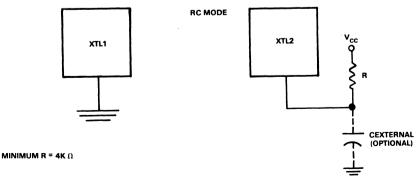

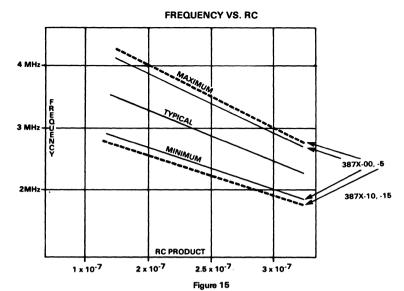

- c) RC Controlled Oscillator. CKI is configured as a single pin RC controlled Schmitt trigger oscillator. The instruction cycle equals the oscillation frequency divided by 4. CKO is the HALT I/O port.

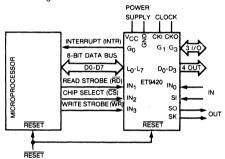

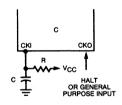

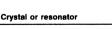

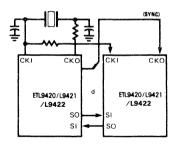

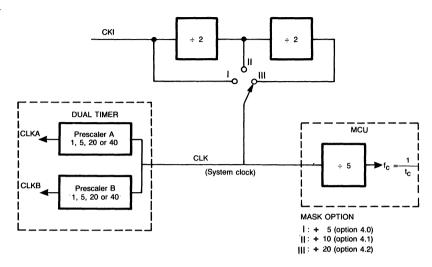

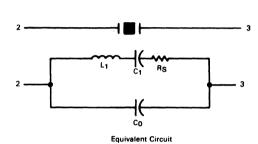

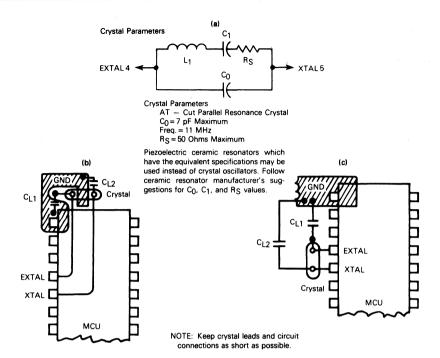

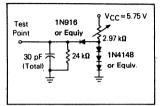

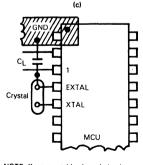

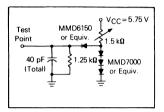

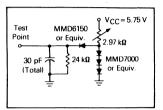

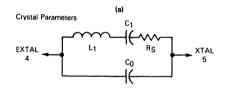

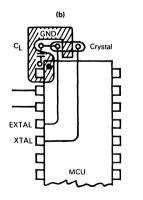

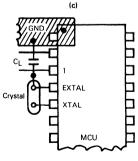

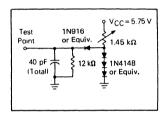

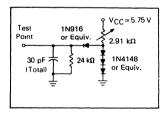

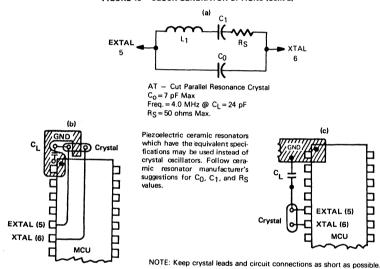

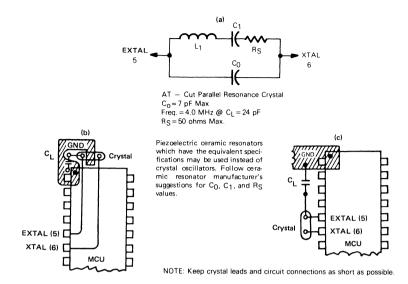

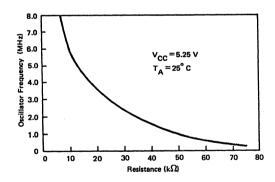

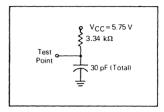

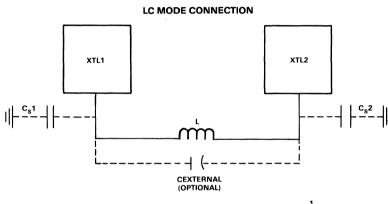

FIGURE 6 - ETC9410C OSCILLATOR

| Crystal | Or | resonator |  |

|---------|----|-----------|--|

| Crystal   |            | Comp | onent Values | ;       |

|-----------|------------|------|--------------|---------|

| value     | R1         | R2   | C1 (pF)      | G2 (pF) |

| 32 kHz    | 220 k      | 20 M | 30           | 5 36    |

| 455 kHz   | 5 <b>k</b> | 10 M | 80           | 40      |

| 2.096 MHz | 2 k        | 1 M  | 30           | 5 36    |

| 4 MHz     | 1 k        | 1 M  | 30           | 5 36    |

R C controlled Oscillator

| R    | С      | Cycle time        | v <sub>cc</sub> |

|------|--------|-------------------|-----------------|

| 15 k | 82 pF  | 4 to 9 µs         | ≥4.5V           |

| 30 k | 82 pF  | 8 to 16 <b>µs</b> | ≥4.5V           |

| 60 k | 100 pF | 16 to 32 us       | 2.4 to 4.5V     |

Note:  $15k \leqslant R \leqslant 150k$ ;  $50pF \leqslant C \leqslant 150pF$

This circuit and these values are for indication only. As the oscillator characteristics are not guaranteed, please consider and examine the circuit constants carefully on your application.

#### FIGURE 6 - ETC 9410 OSCILLATOR

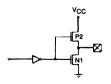

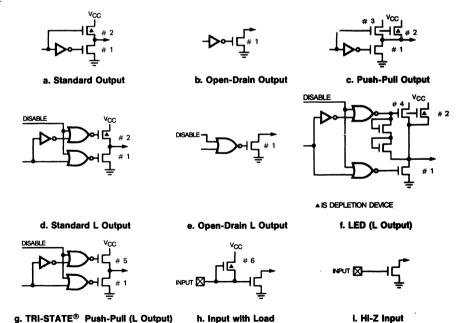

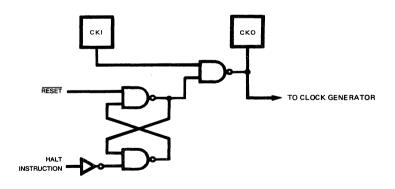

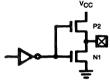

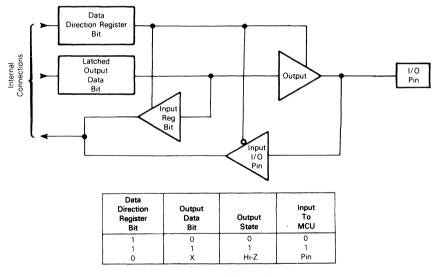

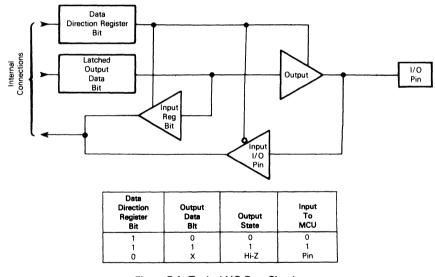

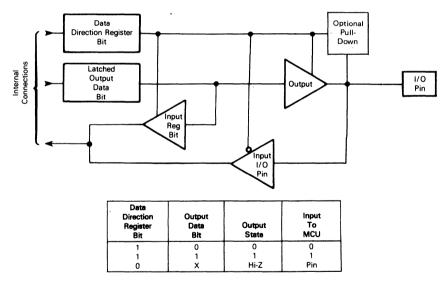

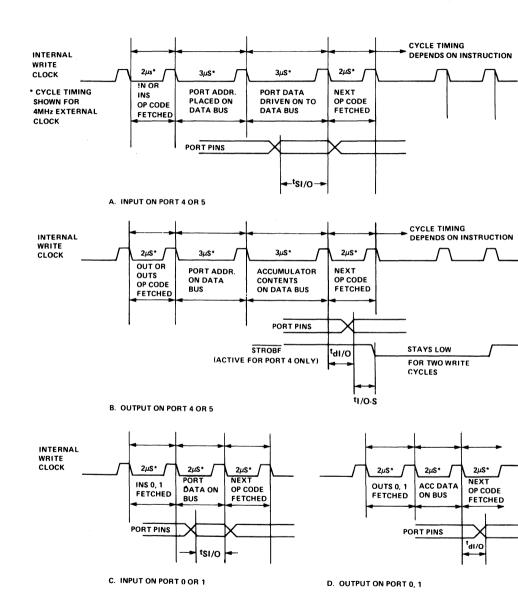

#### I/O Options

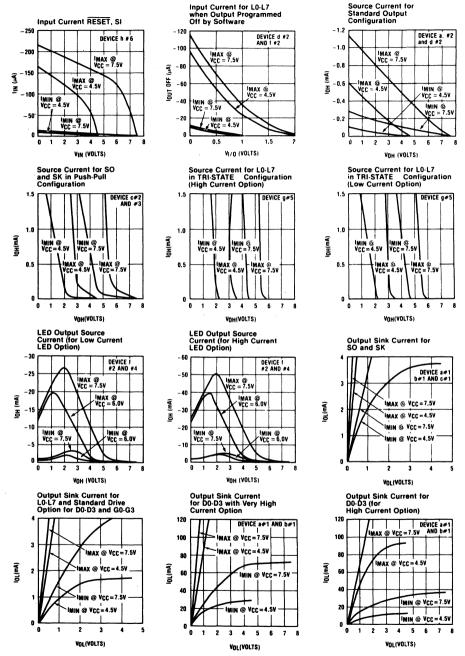

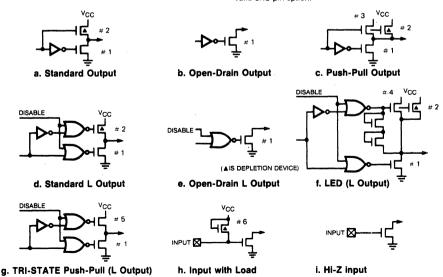

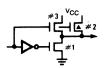

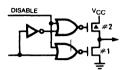

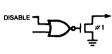

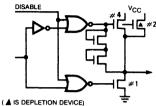

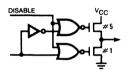

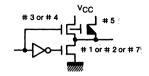

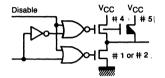

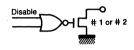

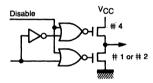

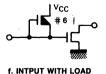

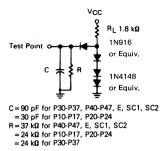

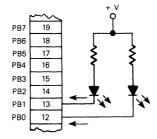

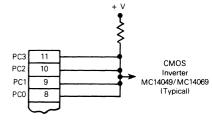

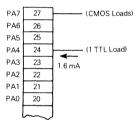

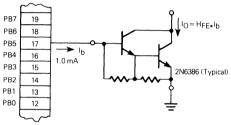

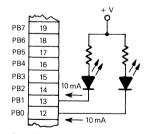

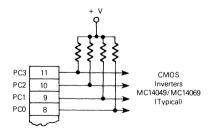

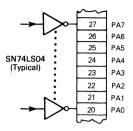

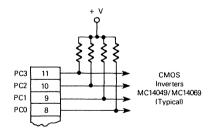

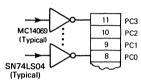

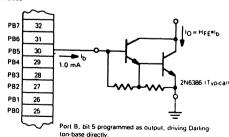

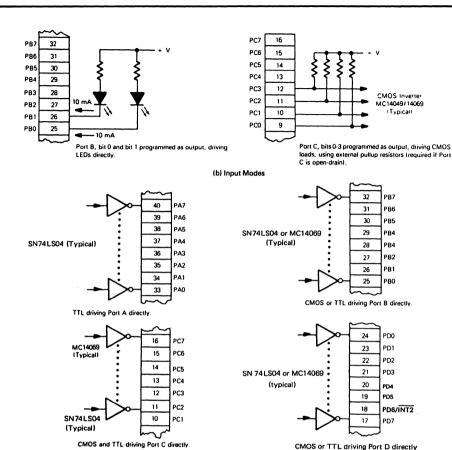

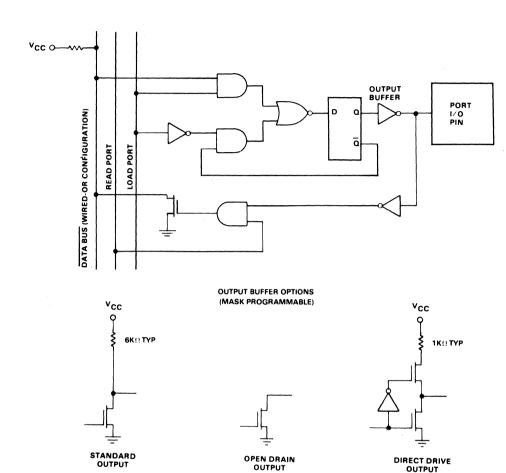

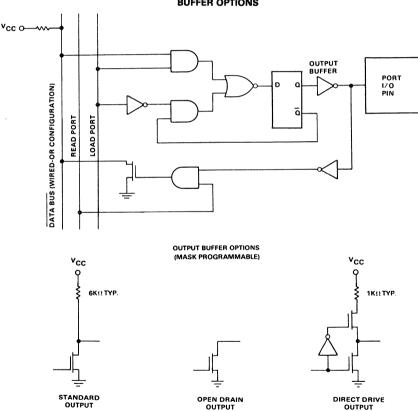

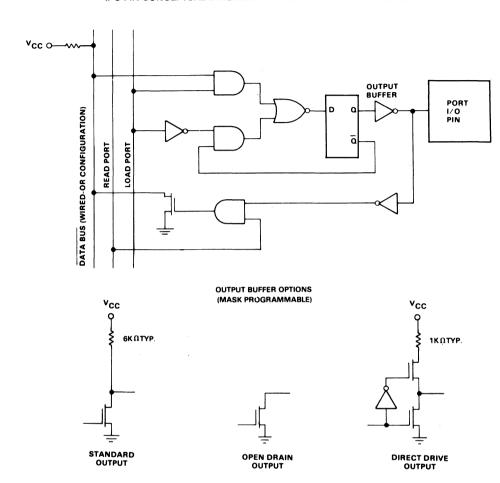

ETC 9410/C 9411 outputs have the following optional configurations, illustrated in Figure 7:

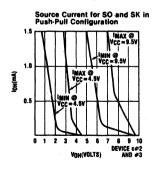

- a) Standard A CMOS push-pull buffer with an N-channel device to ground in conjunction with a P-channel device to V<sub>CC</sub>, compatible with CMOS and LSTTL.

- b) Low Current This is the same configuration as a) above except that the sourcing current much less.

- c) Open Drain An N-channel device to ground only, allowing external pull-up as required by the user's application.

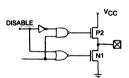

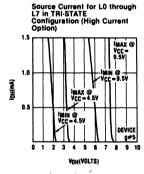

- d) Standard TRI-STATE® L Output A CMOS output buffer similar to a) which may be disabled by program control.

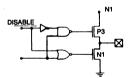

- e) Low-Current TRI-STATE® L Output This is the same as d) above except that the sourcing current is much less.

- f) Open-Drain TRI-STATE® L Output This has the N channel device to ground only.

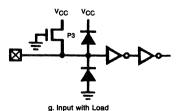

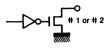

The SI and RESET inputs are Hi-Z inputs (Fig. 7 g)

When using either the G or L I/O ports as inputs, a pull-up device is necessary. This can be an external device or the following alternative is available: Select the low-current output option. Now, by setting the output registers to a logic "I" level, the P-channel devices will act as the pull-up load. Note that when using the L ports in this fashion the Q registers must be set to a logic "I" level and the L drivers MUST BE ENABLED by an LEI instruction.

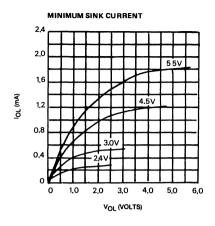

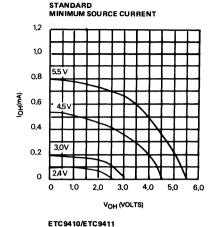

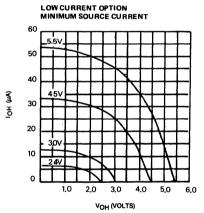

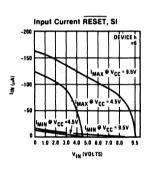

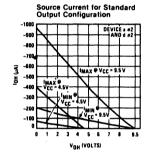

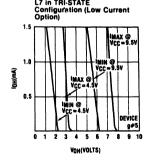

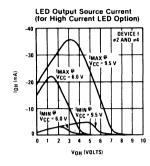

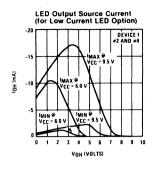

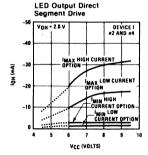

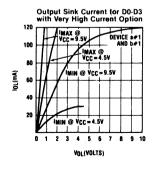

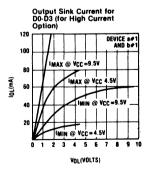

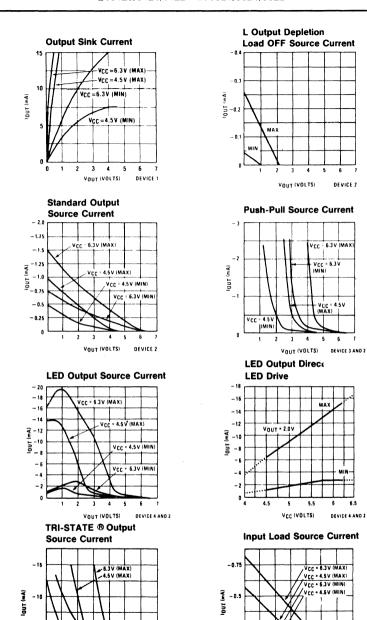

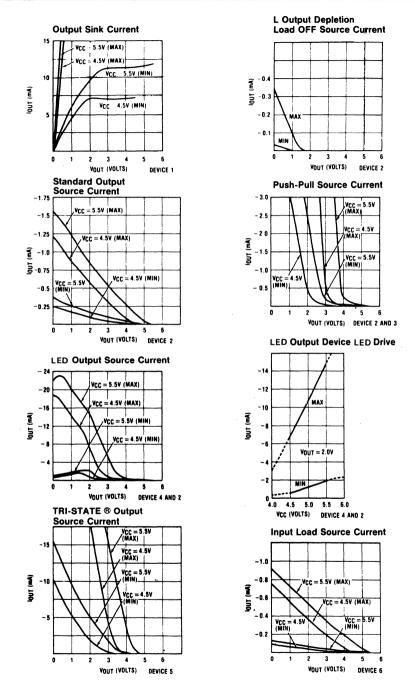

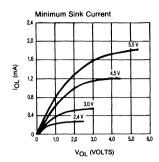

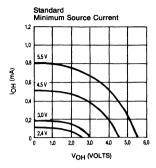

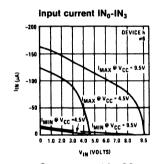

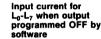

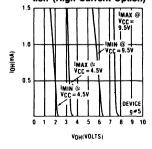

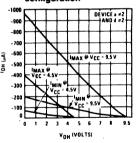

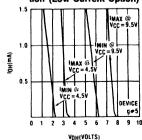

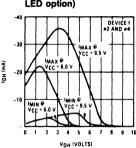

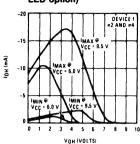

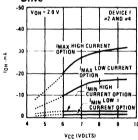

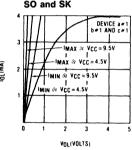

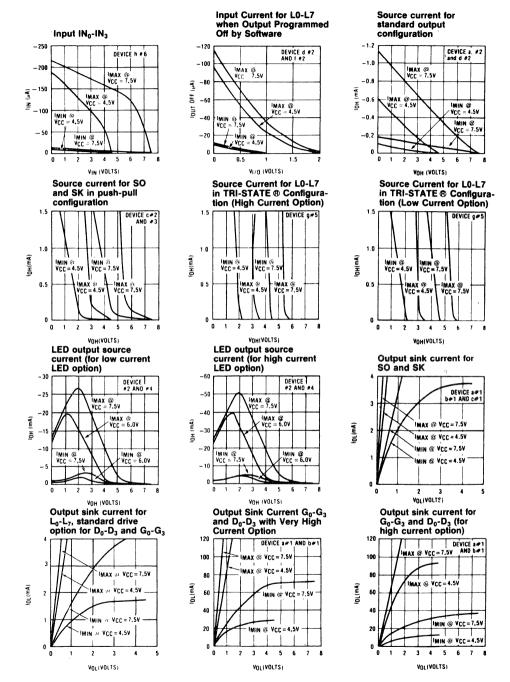

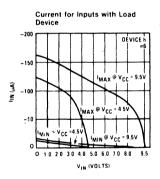

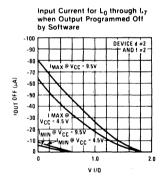

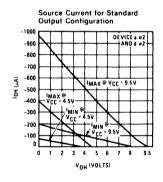

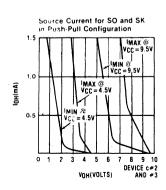

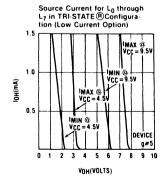

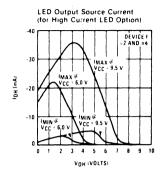

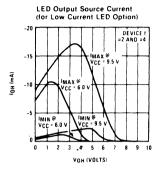

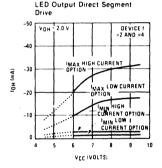

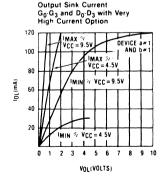

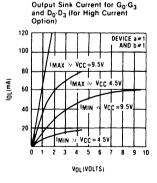

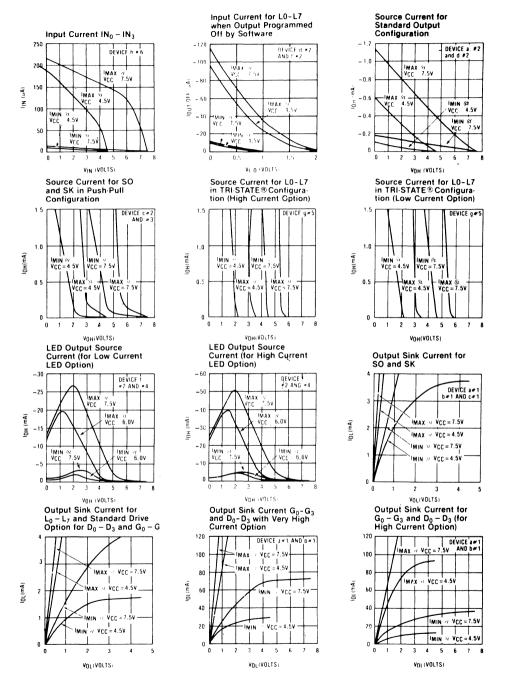

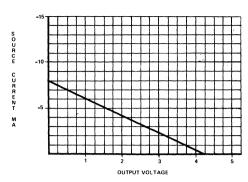

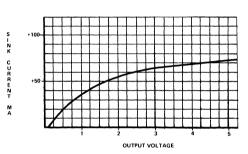

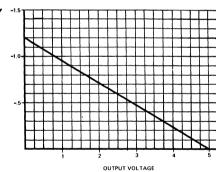

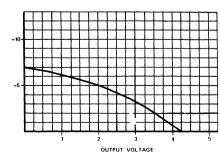

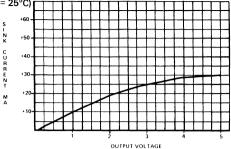

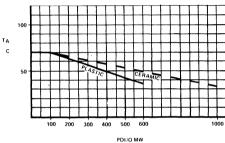

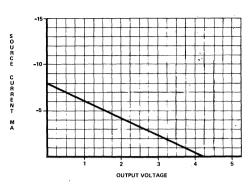

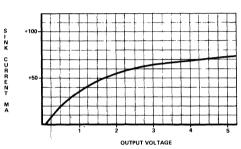

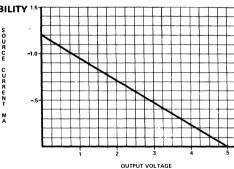

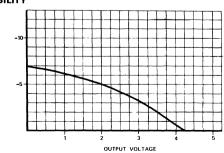

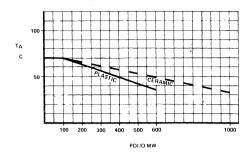

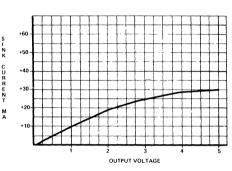

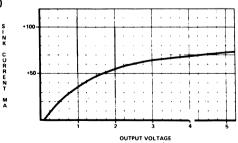

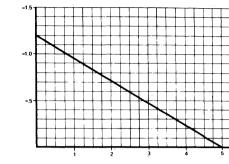

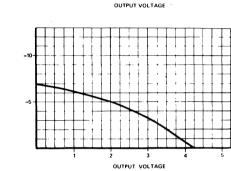

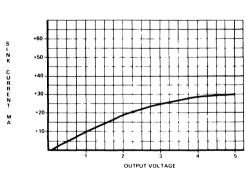

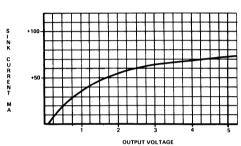

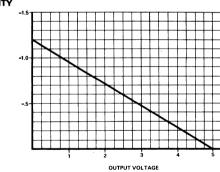

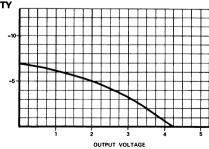

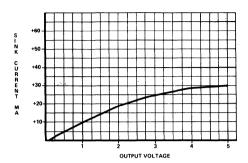

All output drivers use one or more of three common devices numbered 1 to 3. Minimum and maximum current ( $I_{out}$   $V_{out}$  curves are given in Figure 8 for each of these devices to allow the designer to effectively use these I/O configurations.

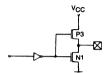

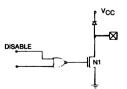

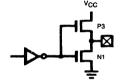

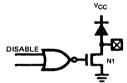

a) Standard Push Pull Output

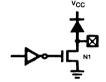

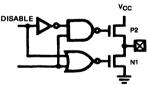

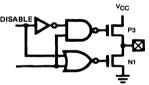

FIGURE 7 - I/O CONFIGURATIONS

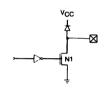

b) Low Current Push-Pull Output

c) Open Drain Output

d) Standard TRI-STATE® "L" Output

e) Low Current TRI-STATE® "L" Output

f) Open Drain TRI-STATE® "L" Output

g) Hi-Z Input

FIGURE 8 - INPUT/OUTPUT CHARACTERISTICS

## ETC 9410/C 9411 INSTRUCTION SET

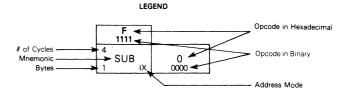

Table 2 is a symbol table providing internal architecture, instruction operand and operational symbols used in the instruction set table.

Table 3 provides the mnemonic, operand, machine, code, data flow, skip conditions and description associated with each instruction in the ETC 9410/C 9411 instruction set.

TABLE 2 - ETC9410/C 9411 INSTRUCTION SET TABLE SYMBOLS

| Symbol   | Definition                                            | Symbol                      | Definition                                             |  |  |

|----------|-------------------------------------------------------|-----------------------------|--------------------------------------------------------|--|--|

| INTERNAL | ARCHITECTURE SYMBOLS                                  | INSTRUCTION OPERAND SYMBOLS |                                                        |  |  |

| Α        | 4-bit Accumulator                                     | d                           | 4-bit Operand Field, 0 - 15 binary (RAM Digit Select   |  |  |

| В        | 6-bit RAM Address Register                            | r                           | 2-bit Operand Field, 0 - 3 binary (RAM Register Select |  |  |

| Br       | Upper 2 bits of B (register address)                  | а                           | 9-bit Operand Field, 0 - 511 binary (ROM Address)      |  |  |

| Bd       | Lower 4 bits of B (digit address)                     | ٧                           | 4-bit Operand Field 0 - 15 binary (Immediate Data)     |  |  |

| С        | 1-bit Carry Register                                  | RAM(s)                      | Contents of RAM location addressed by s                |  |  |

| D        | 4-bit Data Output Port                                | ROM(t)                      | Contents of ROM location addressed by t                |  |  |

| EN       | 4-bit Enable Register                                 |                             |                                                        |  |  |

| G        | 4-bit Register to latch data for G I/O Port           | ODEDATI                     | NAL 0/4/00/0                                           |  |  |

| Ĺ        | 8-bit TRI-STATE I/O Port                              | OPERATIO                    | ONAL SYMBOLS                                           |  |  |

| M        | 4-bit contents of RAM Memory pointed to by B Register | +                           | Plus                                                   |  |  |

| PC       | 9-bit ROM Address Register (program counter)          | _                           | Minus                                                  |  |  |

| Q        | 8-bit Register to latch data for L I/O Port           | <b>→</b>                    | Replaces                                               |  |  |

| SA       | 9-bit Subroutine Save Register A                      | ↔                           | Is exchanged with                                      |  |  |

| SB       | 9-bit Subroutine Save Register B                      | =                           | Is equal to                                            |  |  |

| SIO      | 4-bit Shift Register and Counter                      | Α                           | The one's complement of A                              |  |  |

| SK       | Logic-Controlled Clock Output                         | Ð                           | Exclusive-OR                                           |  |  |

|          | • • • • • • • • • • • • • • • • • • • •               | :                           | Range of values                                        |  |  |

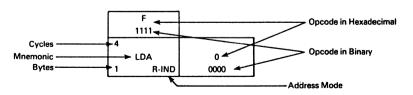

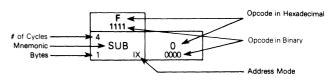

TABLE 3 - ETC9410/C 9411 INSTRUCTION SET

| Mnemonic | Operand     | Machine<br>Hex Language Code<br>Code (Binary) | Data Flow                       | Skip Conditions | Description                             |

|----------|-------------|-----------------------------------------------|---------------------------------|-----------------|-----------------------------------------|

| ARITH    | METIC INSTI | RUCTIONS                                      |                                 |                 |                                         |

| ASC      |             | 30   0 0 1 1 1 0 0 0 0                        | A + C + RAM(B) → A<br>Carry → C | Carry           | Add with Carry, Skip on<br>Carry        |

| ADD      |             | 31 [0011]0001                                 | A + RAM (B) → A                 | None            | Add RAM to A                            |

| AISC     | у           | 5- [0 1 0 1 ] Y                               | A + y → A                       | Carry           | Add Immediate, Skip on<br>Carry (y ≠ 0) |

| CLRA     |             | 00 [0000]0000                                 | 0 → A                           | None            | Clear A                                 |

| COMP     |             | 40 [0 1 0 0]0 0 0 0                           | Ā→A                             | None            | one's complement of A to A              |

| NOP      |             | 44 [0100]0100                                 | None                            | None            | No Operation                            |

| RC       |             | 32 [0 0 1 1]0 0 1 0                           | "0"→ C                          | None            | Reset C                                 |

| sc       |             | 22 [0010]0010                                 | "1"→ C                          | None            | Set C                                   |

| XOR      |             | 02 [ 0 0 0 0]0 0 1 0                          | A ⊕ RAM (B) → A                 | None            | Exclusive-OR RAM with A                 |

#### TABLE 3 - ETC9410/C 9411 INSTRUCTION SET (continued)

| TABLE 3 — ETC9410/C 9411 INSTRUCTION SET (continued) |                  |                                                                                           |                                                                                                              |                       |                                                                    |

|------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------|

| TRANSF                                               | ER OF            | CONTROL INSTRUCTIONS                                                                      |                                                                                                              |                       |                                                                    |