# PRODUCT HANDBOOK

1

# 1553 Product Handbook

United Technologies Microelectronics Center, Inc. 1575 Garden of the Gods Road Colorado Springs, CO 80907

RAD-SPEC is a service mark of United Technologies Microelectronics Center, Inc.

Copyright 1991 by United Technologies Microelectronics Center, Inc.

All rights reserved

United Technologies Microelectronics Center, Inc. (UTMC) reserves the right to make changes to any products and services herein at any time without notice. Consult UTMC or an authorized sales representative to verify that the information in this data sheet is current before using this product. UTMC does not assume any responsibility or liability arising out of the applica-

tion or use of any product or service described herein, except as expressly agreed to in writing by UTMC; nor does the purchase, lease, or use of a product or service from UTMC convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual rights of UTMC or of third parties.

The price of this product handbook is \$5.00 but it is available free of charge to qualified individuals.

### **Overview**

At United Technologies Microelectronics Center (UTMC), we are dedicated to supplying highreliability VLSI integrated circuits for the aerospace and defense markets. In 1986, our 280,000square-foot manufacturing facility earned full MIL-STD-976 certification from the Defense Electronic Supply Center (DESC). This DESC certification covers all phases of our manufacturing process including circuit design and simulation, wafer fabrication, research and development, assembly, and testing to Class B military requirements.

UTMC also offers comprehensive quality assurance and reliability programs, radiation-hardened and Level S products, and foundry services specifically for military and aerospace customers.

In addition to the military-standard products discussed below, UTMC produces semicustom 1.5- and 1.2micron CMOS gate arrays. Our UTD and rad-hard UTD-R gate array families (1.5-micron) use a patented continuous-column architecture that reduces the number of wasted transistors in the array. The 1.2-micron UTE-R family can handle up to 50,000 usable gates and has IEEE Standard 1149.1 (JTAG) boundary-scan test capability.

UTMC also offers high-reliability foundry services for its bulk CMOS processes. Our customers have a choice of either 3.0-, 1.5-, or 1.2-micron double metal CMOS technologies. The fabrication facility is DESC certified, and complete processing and testing to MIL-STD-883 Level B and Level S are available.

Demonstrating our dedication to the military and aerospace marketplace, UTMC also now offers RAD-SPEC<sup>sm</sup> products -- "off-the-shelf" products guaranteed to meet radiation-hardness assurance levels M, D, R, and H of MIL-M-38510.

# MILITARY-STANDARD PRODUCTS

UTMC supplies a broad range of military-standard products supporting MIL-STD-1553, 1750, 1760, DSP, and memory applications. All military products meet specifications over the full -55°C to +125°C temperature range and are screened according to specific test methods of MIL-STD-883. We also offer many devices as Standard Military Drawings.

We have the widest selection of monolithic Avionic System Division/ENASC-validated (formerly SEAFAC -- Systems Engineering Avionics Facility) MIL-STD-1553 products in the industry. The 1553B BCRT (Bus Controller/Remote Terminal) features advanced memory structures and powerful message handling. Variations of the BCRT -- the BCRTM (Monitor) and BCRTMP (Multi-Protocol) -- readily adapt to a variety of 1553 bus applications. The bus protocol family also includes the Remote Terminal Multi-Protocol (RTMP), the Remote Terminal with RAM (RTR), the 1760A Remote Terminal for Stores (RTS), the first available JAN-qualified RTI (Remote Terminal Interface), and a line of monolithic 1553A/B Transceivers which are fit- and functionally-compatible to industry-standard 631xx series transceivers.

MIL-STD-1750 products include the RISC Microprocessor, which can operate in 1750 protocol or in its native RISC mode, and its associated software tools including interactive simulator, assembler, and linker.

On the cutting edge of DSP technology, UTMC also offers the IQMAC<sup>™</sup> (In-phase Quadrature Multiplier/ Accumulator), a 32-bit, 75 MFLOP pipelined vector processor. This part uses five floating-point elements -- two multipliers and three ALUs -- to perform rapid vector calculations. The versatile IQMAC efficiently performs matrix and polynomial operations, DSP and graphics functions, and can be used for math accelerators and digital filters.

Our expanding line of military-standard products also includes a radiation-hardened memory family. The family presently includes a  $8K \times 8$  SRAM with two levels of SEU immunity and mask-programmable  $8K \times 8$  ROM.

# **RAD-SPEC PRODUCTS**

RAD-SPEC is UTMC's radiation-hardness specification program guaranteeing the hardness assurance levels specified in MIL-M-38510. UTMC offers RAD-SPEC semicustom and military-standard products with "off-the-shelf" pricing and delivery to simplify compliance and procurement.

Our rigorous testing and qualification guarantee the cost-effective, rad-hard products needed to consistently meet MIL-M-38510 tactical levels M and D and strategic levels R and H. Hardness levels M and D have total dose levels of 3E3 and 1E4 rads(Si) respectively and neutron fluence of 2E12 n/cm2. Levels R and H require total dose limits of 1E5 and 1E6 rads(Si) respectively and the same neutron fluence. UTMC guarantees to meet the customer's specified radiation-hardness level across the full military temperature range at cost-effective prices.

# Table of Contents

| Section 1: | MIL-STD-1553 Reference Guide Reference-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 2: | Using UTMC's 1553 ProductsRT Mode-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Section 3: | 1553 Product Data SheetsUT1553B BCRTBCRT-1UT1553B BCRTMBCRTM-1UT1553B BCRTMPBCRTMP-1UT1553B RTR Remote Terminal with RAMRTR-1UT1760A RTS Remote Terminal for StoresRTS-1UT1553B RTIRTI-1UT1553 RTMP Remote Terminal Multi-ProtocolRTMP-1Transceivers UT63M1XX Series MIL-STD-1553XCVR-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

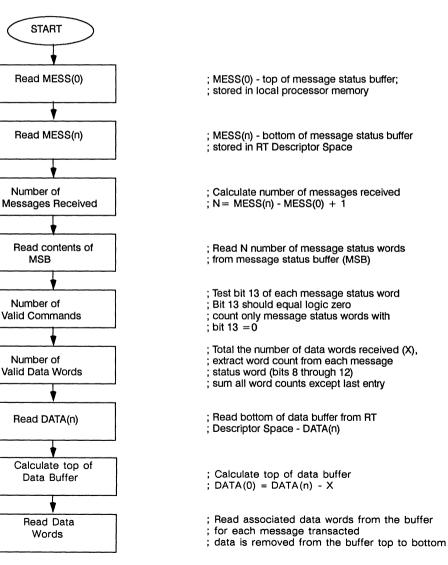

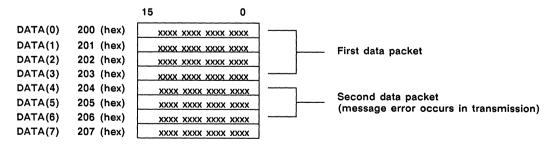

| Section 4: | Application NotesRTI Internal Self-Test RoutineApplication Notes-1UT1750AR: Bus Arbitration with the UT1553 RTMPApplication Notes-7Interfacing the RTR to the 80C51 8-Bit MicrocomputerApplication Notes-11RTR/RTS Internal Self-Test RoutineApplication Notes-19Simple command Illegalization for the RT FamilyApplication Notes-25Interfacing the BCRT to the 68000 16-Bit MPUApplication Notes-27Cycle Stealing Interface for the UT1553B BCRTApplication Notes-31UT1553B BCRT True Dual-Port Memory InterfaceApplication Notes-39BCRT/M RT-mode Multiple Message Handling Flow ChartApplication Notes-47BCRT/M RT-mode Transmission Error Message RecoveryApplication Notes-51Using the BCRTMP with Multiple ProtocolsApplication Notes-53UT63M1XX: Power Consumption vs. DissipationApplication Notes-69A Processor-less Interface for the UT1553B RTIApplication Notes-71A Processor-less Interface for the UT1553B RTIApplication Notes-77UT1553 BCRT to 80186 InterfaceApplication Notes-77 |

| Section 5: | Quality and Reliability Q&R-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

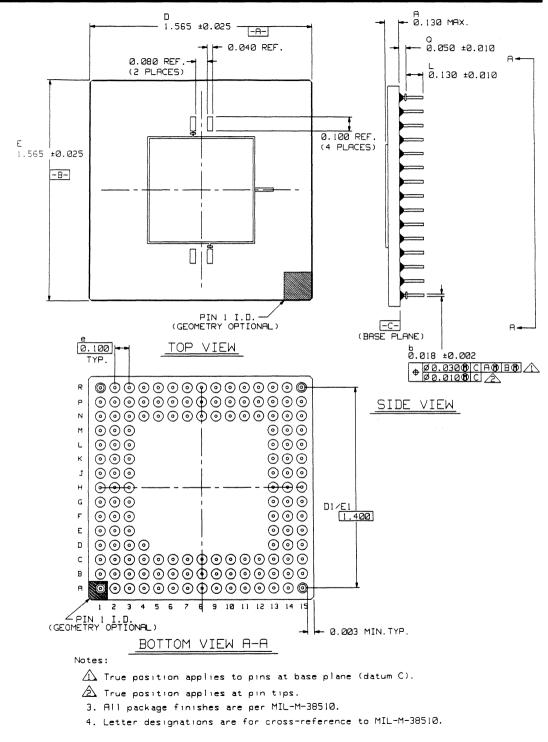

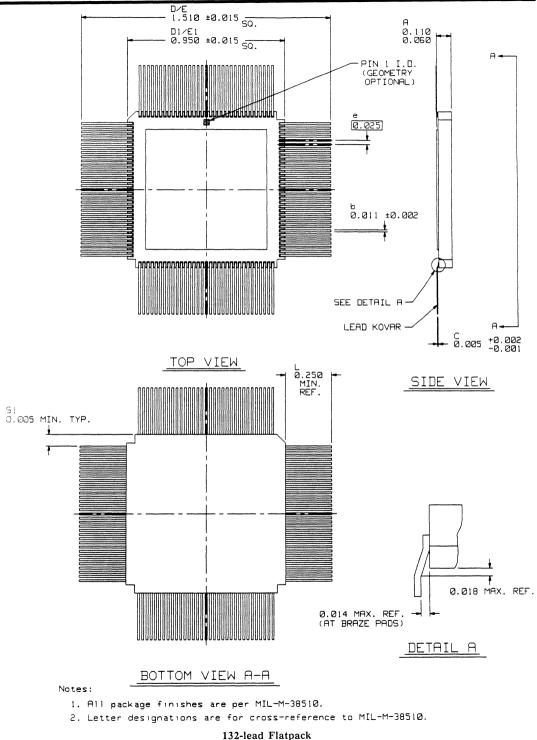

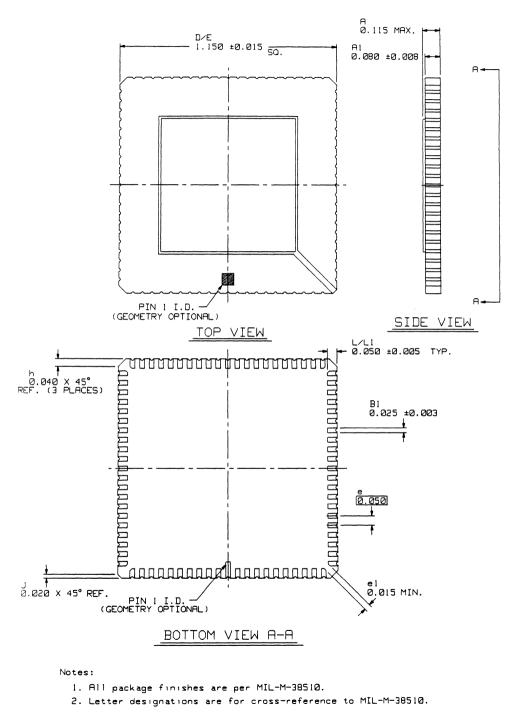

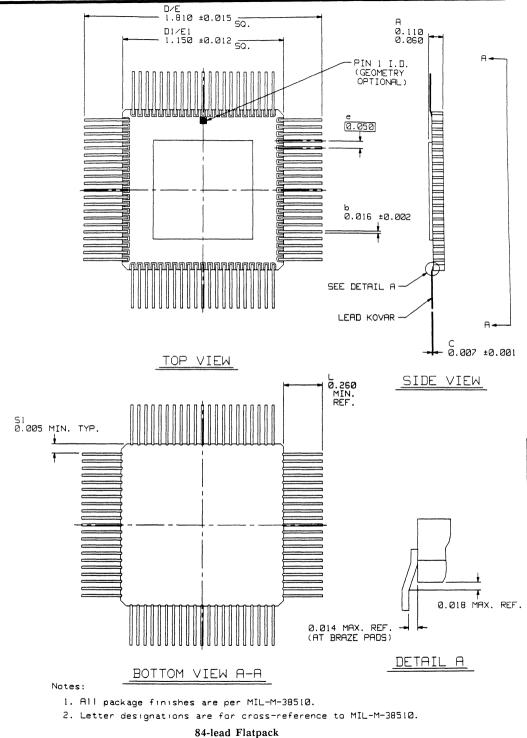

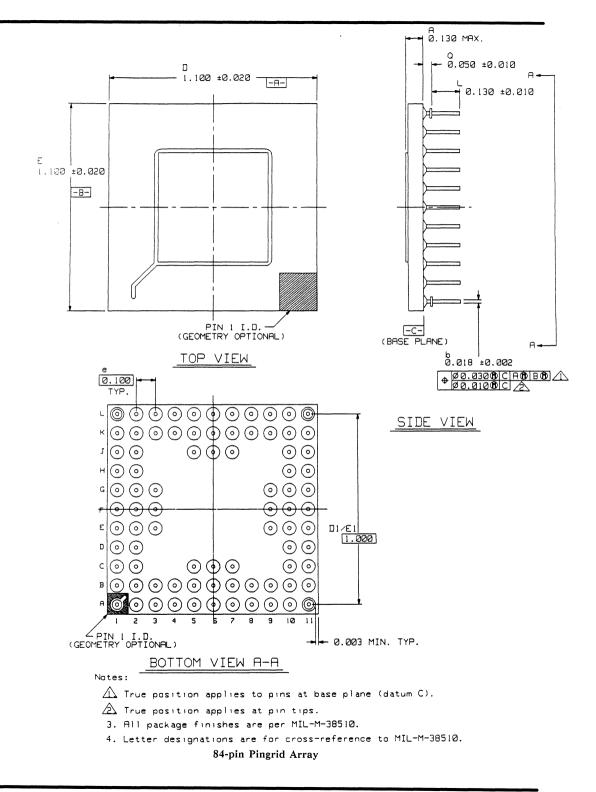

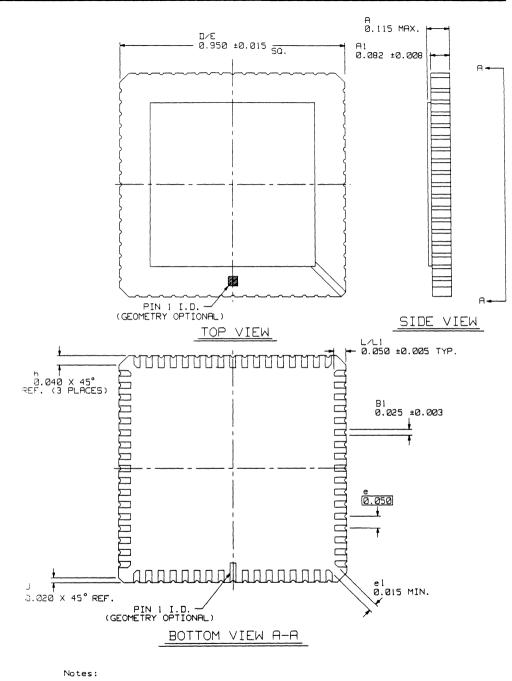

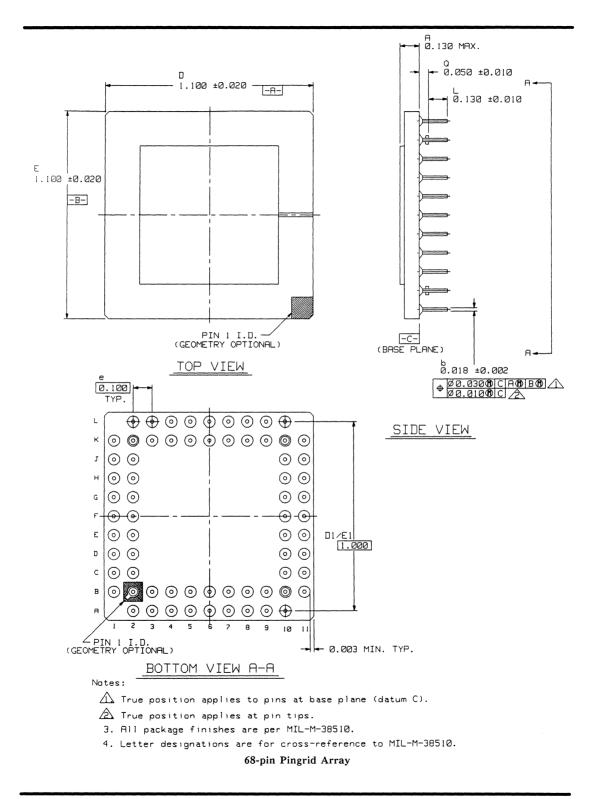

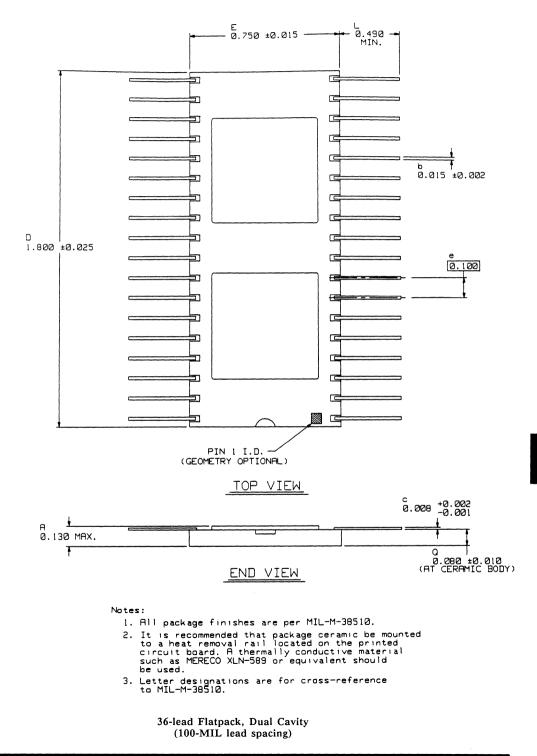

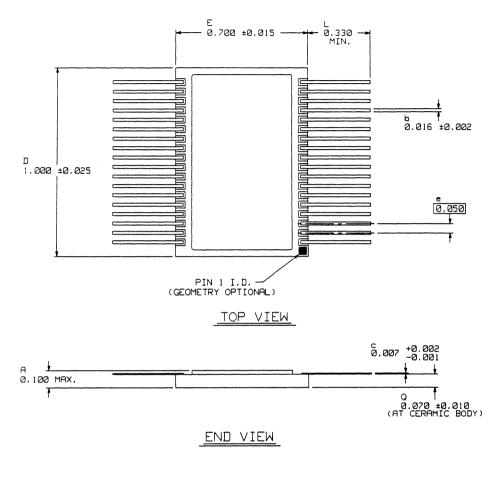

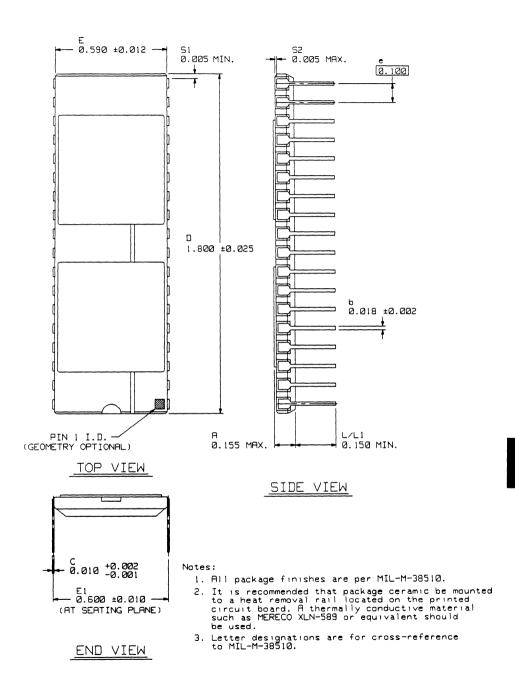

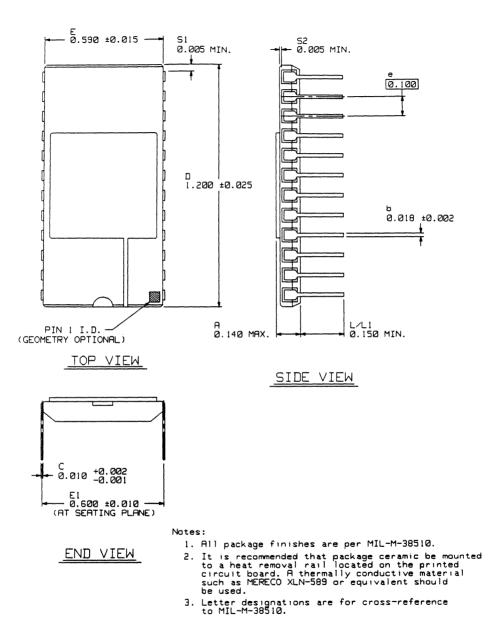

| Section 6: | Packaging Information Packaging-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Section 7: | Ordering Information Ordering-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Appendix   | MIL-STD-1553B/Notices 1 & 2 Appendix-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

UTMC recognizes the assistance in developing Section 1 provided by Al Crossgrove, Chris deLong, and Ray Turner.

# Table of Contents

| PRE | FAC                                           | Ε                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0 | GEN<br>1.1<br>1.2<br>1.3                      | Introduction<br>Historical                                                                                                                                                                                                                          | TA BUS CONCEPTS       3         In to Data Buses       3         Need for a Bus       4         ent of MIL-STD-1553 Data Bus as a Standard       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 1.4                                           | The Impac                                                                                                                                                                                                                                           | t of MIL-STD-1553B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.0 | UNI<br>2.1<br>2.2                             | Functions<br>MIL-STD-<br>2.2.1 No<br>2.2<br>2.2<br>2.2<br>2.2<br>2.2                                                                                                                                                                                | ING MIL-STD-1553       6         of Bus Controllers, Remote Terminals, and Monitors       6         -1553 Message Formats       6         n-Broadcast Message Formats       8         1.1 BC-to-RT Receive Message       8         1.2 BC-to-RT Transmit Message       8         1.3 RT-to-RT Message       9         1.4 Non-Broadcast Mode Command Messages       9         adcast Message Formats       9                                                                                                                                                                                                                                                                                                                                                   |

|     |                                               | 2.2<br>2.2<br>2.2                                                                                                                                                                                                                                   | 2.1 BC Broadcast to RTs       9         2.2 RT Broadcast to RTs       9         2.3 Broadcast Mode Command Messages       9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 2.3<br>2.4                                    | Command,<br>2.4.1 Co.<br>2.4.2 No<br>2.4.3 Sta<br>2.4.4 Da                                                                                                                                                                                          | IIL-STD-1553B Notice 2       9         , Status, and Data Words       10         mmand Word       10         te on Subaddress Assignment       11         tus Word       11         ta Word       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 2.5<br>2.6<br>2.7<br>2.8                      | Meaning o<br>1553 Elect                                                                                                                                                                                                                             | robability of Undetected Errors       12         f the Command Word Mode Codes       12         rical Interface Requirements       14         le Historical Rationale for MIL-STD-1553 Characteristics       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.0 | 3.1<br>3.2<br>3.3<br>3.4                      | Range of H<br>Data Requ<br>Typical Sys<br>RT Validat                                                                                                                                                                                                | AND SYSTEMS INTEGRATION       15         Bus Topologies and Applications       15         ired to Specify the BC, RT, or M       17         tem Product Qualification Referenced to MIL-STD-1553       18         ion Test Plan and Other Test Plans       18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.0 | <b>DES</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5 | Systems Ro<br>Terminal E<br>Terminal E<br>Terminal E<br>4.4.1 Mc<br>4.4.2 Sta<br>4.4.3 Ter<br>4.4.4 Ext<br>4.4.5 Sul<br>4.4.6 Ille<br>4.4.7 Brc<br>4.4.8 Da<br>Bus Contre<br>4.5.1 Me<br>4.5.2 Au<br>4.5.3 Err<br>4.5.4 Mo<br>4.5.5 Sta<br>4.5.6 Mu | SIDERATIONS FOR MIL-STD-1553 INTERFACES18equirements18Definition18unctions19Design Issues19de Commands19us Word Bits19minal Address Selection19uended Subaddressing20paddress Restrictions20oadcast Mode Commands20badcast Mode Commands20contact Ketry21tomatic Retry21tomatic Retry21tomatic Retry21towards21towards21towards21towards21towards21towards21towards21towards21towards21tus Word Bits21tus Word Bits< |

| 4.6  | Monite | or Issues                                  | 22 |

|------|--------|--------------------------------------------|----|

|      | 4.6.1  | Amount of Data                             | 22 |

|      | 4.6.2  | Error Codes                                | 22 |

|      | 4.6.3  | Backup Bus Controller                      | 22 |

| 4.7  | Transc | eiver Issues                               | 22 |

|      | 4.7.1  | Idle State                                 |    |

|      | 4.7.2  | Power Supply Loading and Power Dissipation |    |

|      | 4.7.3  | Voltage Drive Versus Current Drive         |    |

|      | 4.7.4  | Circuit Layout                             | 22 |

|      | 4.7.5  | Coupling Methodology                       | 22 |

| 4.8  | Subsys | tem Interface Issues                       | 23 |

|      | 4.8.1  | Memory/Data Timing                         | 23 |

|      | 4.8.2  | Sample Consistency                         | 23 |

|      | 4.8.3  | Host Processor Interface                   | 23 |

| 4.9  | Gatew  | ays                                        | 23 |

|      | 4.9.1  | Data Formats                               |    |

|      | 4.9.2  | Data Latency                               | 23 |

|      | 4.9.3  | MIL-STD-1760 Gateways                      |    |

| 4.10 | MIL-S  | STD-1760 Design Issues                     | 23 |

|      |        | iew of MIL-STD-1553 Versions and Notices   |    |

| 4.12 | Summ   | ary                                        | 24 |

## Preface

Section 1 has four parts. Part 1 presents network and communication terms the way MIL-STD-1553 uses them and describes how a 1553 network compares to other networks. Part 1 also presents the history of 1553 since its inception in 1970 and discusses its acceptance and use today. Part 2 summarizes the Standard's requirements and relates them to systems use. Parts 3 and 4 are for system, hardware, or software designers. Part 3 describes how system integration should occur, and part 4 presents guidelines and good design practices when MIL-STD-1553 is the communication means.

# **1.0 GENERAL DATA BUS CONCEPTS**

#### **1.1 Introduction to Data Buses**

A <u>data bus</u> is the communication means to connect two or more users. Data refers to computer words, and the term "bus" is borrowed from the electrical power system term referring to a common connection for several circuits. A physical data bus - usually electrical conductors - is the <u>transmission medium</u>. A user can be either a sender or receiver of data, or both.

Parallel data buses use one physical connection for each binary bit so that all bits in a word are transmitted simultaneously. An example of a parallel data bus is the data path in a personal computer board which connects the processor chip and the memory.

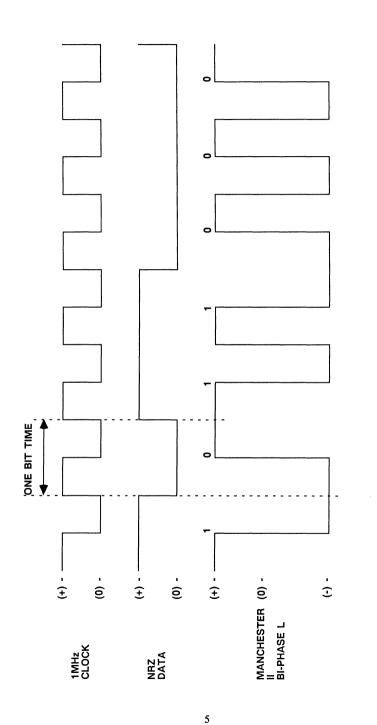

In contrast, <u>serial data buses</u> use one physical connection to sequentially transmit bits. Therefore, serial data buses must use a <u>decoding</u> and timing scheme to distinguish logical ones and zeros. Serial data buses also use a control mechanism to synchronize the receiver with the sender. Synchronous means a mutually sensed clock pulse controls transmission and reception. The clock pulse may be on an additional control line dedicated to synchronizing the communication link, or the data may contain the control information. A master clock reference available to all users on a data bus is an example of a synchronous data bus. Receivers use the master clock to know when each bit begins, while senders use it to time transmissions.

Serial buses may be operated <u>asynchronously</u> when the transmitter and receiver use crystal-controlled clocks and start and stop information within each word of the message so the receiver knows when each word begins. Self-clocking by the receiver to its independent clock occurs word by word as the words are received. An example of a serial data bus is the telephone wire connecting two computers through modems. With one telephone connection, the connection operates asynchronously.

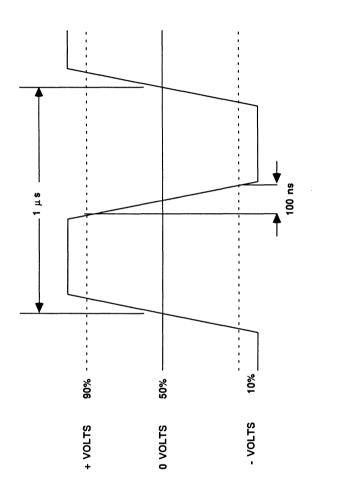

Manchester encoding allows the timing and data to be combined in each data bit by changing the polarity of the signal depending on whether the bit to be transmitted is a zero or a one. The receiver decodes the received signal by using its matched clock for timing bits in a word. Electrical characteristics of the data bus include bit encoding and timing, data bus transmission rate (bits per second), and transmission waveform. Messages are <u>multiplexed</u> when the data bus is used for messages for multiple users. Control of a multiplexed bus is more complex because priorities for the use of the bus must exist, the <u>address</u> of the receiver must be added to the message, and the receiver must be able to decode and use only the messages addressed to it.

Data buses may be designed so that either each word or each message is acknowledged. Acknowledging each word has the advantage that the receiver does not need to know how many words are to be received, and the disadvantage is that the receiver cannot detect message errors. For example, the printer connected to a desktop computer uses word by word acknowledgment. Two methods are used to determine message length or completion. In the first method, transmission of a special sequence of bits different from any data indicates the start and the end of each message. In the second method, the sender includes the word count in the message and the receiver acknowledges correct receipt of the message. MIL-STD-1553 uses the latter method.

Data buses detect errors which occur during message transmission and reception so the sender can retransmit messages and the receiver can discard messages with errors. <u>Word parity</u> is an example of an error detection technique. Since data buses transmit messages with words of the equal length, adding a word parity bit will enable the receiver to verify the word by independently recalculating parity and comparing the result with the transmission.

The data bus <u>protocol</u> defines all of the actions of both receiver and sender including what to do when messages have bit and word errors. Protocol also includes: (1) message and word formats including destination address and message identification; (2) method of message acknowledgement; and (3) special messages that are related only to managing the data bus, such as which users have authority to transmit messages and which users are ready to receive.

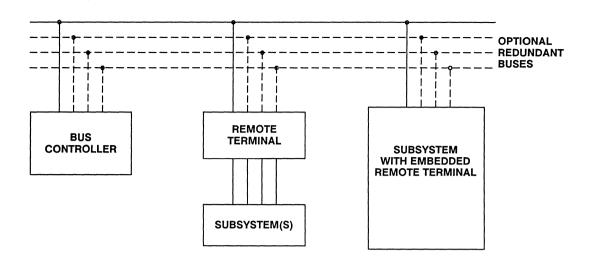

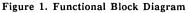

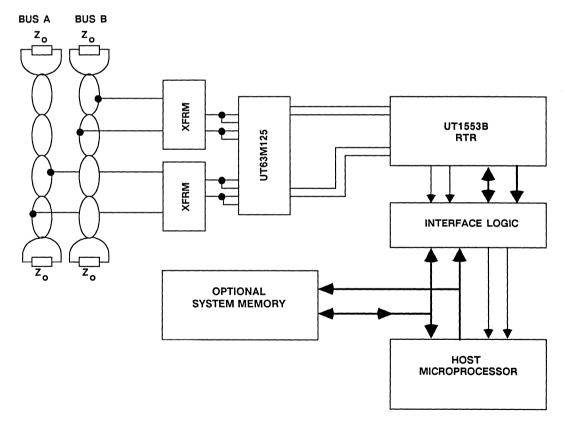

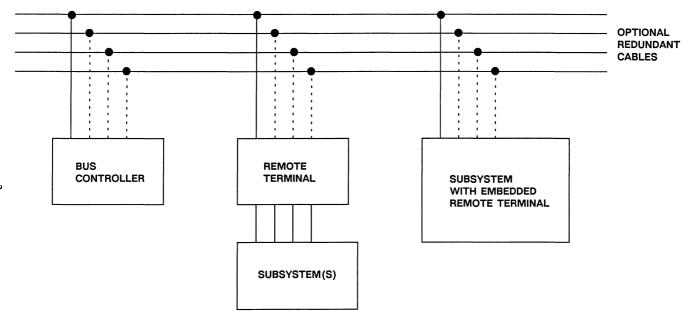

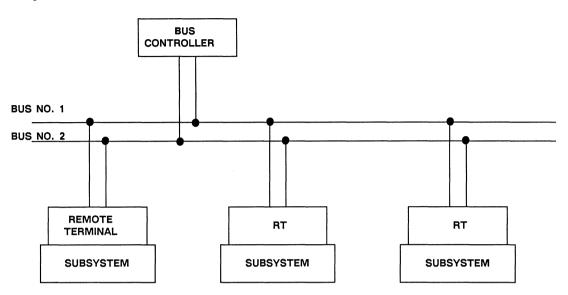

MIL-STD-1553 defines a serial asynchronous data bus on which the messages are multiplexed among users. The transmission medium is a twisted wire cable. The Standard specifies all of the electrical characteristics of the receivers, transmitters, and cable. It also defines the complete protocol but makes the use of many parts optional. To initiate all messages, the Standard requires a centralized control bus (as opposed to either a distributed or autonomous controlled bus). Figure 1 shows an example of a MIL-STD-1553 data bus system.

The U.S. Department of Defense (DoD) requires the use of this standard multiplexed data bus on all military airplanes and helicopters. It is also used on ships and land vehicles.

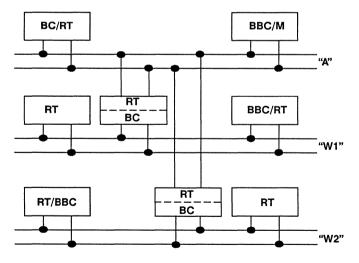

Figure 1. MIL-STD-1553 Data Bus System Architecture

#### 1.2 Historical Need for a Bus

From about 1965 to 1970, airplane designers incorporated digital computers and multi-wire digital links to supplement or replace analog systems in airplanes. Three well-known programs provided the motivation for development of a data bus.

In late 1969, the U.S Air Force (USAF) released its procurement request for the B-1A airplane. The request included a requirement for a crew capsule which could be separated from the aircraft during an aircraft emergency. Reducing the number of electrical connections between the capsule and the aircraft body gave great impetus to designing a serial data link. For B-1A, this link was a twisted pair of wires, operating at a clock rate of one million bits per second, with a maximum message length of 512 words.

From 1970 to 1972, designers of the space shuttle avionics also created a serial data bus to interconnect flight-critical computers and subsystems using multiple buses primarily to facilitate redundant communication.

The F-15, which became operational in 1975, used a synchronous serial link to connect avionics subsystems to the mission computer to provide an extension of the computer input/output interface to remote electronics. This design used a one million cycles per second (1 MHz) separate clock line, and a maximum message length of 15 words.

In summary, the advantages of using multiplexed data buses as viewed in 1970-1975 included performance improvements made possible by the distribution of data from dissimilar sources, weight saving, ease of achieving communication redundancy, and flexibility of integration. Many engineers in industry recognized these advantages and developed prototype systems, but the USAF and the U.S. Navy (USN) took the lead in encouraging investigation to determine the best design for aircraft.

#### 1.3 Development of MIL-STD-1553 Data Bus as a Standard

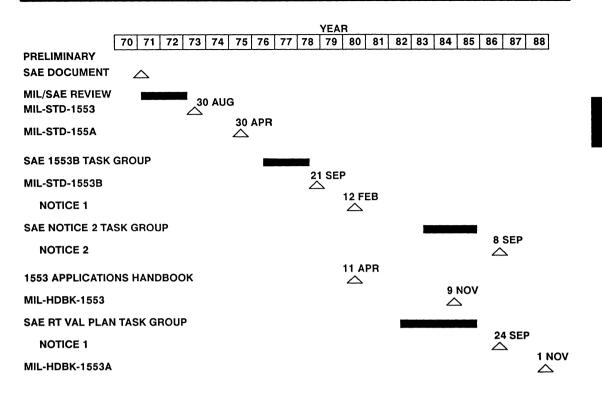

In 1968, the Society of Automotive Engineers (SAE) Aerospace Branch in cooperation with the USN formed a task group to generate a military standard which would specify a data bus system to control electrical power (Control Group, Electrical Power, General Specification for, MIL-P-81883). The task group consisted of industry and military designers. Common features were specified and areas of disagreement were delegated to "slash sheets," which, when completed, constituted a complete standard. Because of the interest in multiplexing on the F-15, B-1A, and space shuttle, each with unique designs, the industry looked for a common approach. Through this effort, the USAF developed and published MIL-STD-1553 in 1973 for use on the F-16 program.

During the next two years, industry, the USAF, and the USN reviewed many drafts of potential revisions to the Standard. In 1975, by direction of the DoD and with the support of industry, the USN, the USAF, and the Army published a coordinated revision A to the Standard. Because of problems and difficulties with revision A, industry and the military formed another SAE task group in 1976 to propose further changes.

After a complete rewrite of the "A" document, the SAE task group worked with the USAF, USN, and Army to produce the DoD-released MIL-STD-1553B in September 1978. The USAF further limited MIL-STD-1553 by creating USAF Notice 1 for the Standard in February 1980. After several years, the SAE again worked with the DoD tri-service group to generate the most recent 1553B Notice 2 for DoD usage. International standards incorporate or reference MIL-STD-1553B without notices. Figure 2 illustrates the key MIL-STD-1553 historical events.

#### 1.4 The Impact of MIL-STD-1553B

All three DoD services require MIL-STD-1553B as the Standard for inter- and intra-subsystem communication. The USAF established a "Form-Fit-Function" concept for avionic equipment common to more than one airplane beginning with the standard inertial navigation system. The signal interface is MIL-STD-1553. Currently, many such boxes including radios and air data computers use MIL-STD-1553 interfaces. Avionic upgrades to existing airplanes with analog systems always include the addition of MIL-STD-1553 data buses to incorporate the many existing subsystems with MIL-STD-1553 interfaces. MIL-STD-1553 is the main communication link between aircraft and weapons, as required by MIL-STD-1760. Today's expendable stores and captive-carry pods such as infrared sensors and electronic warfare components that conform to MIL-STD-1760 will have at least one MIL-STD-1553 interface. Complex air-to-ground and air-to-air missiles also have their internal avionics interconnected with MIL-STD-1553. The Army uses MIL-STD-1553 in helicopters and tanks. The USN uses MIL-STD-1553 in surface ships and submarines.

Originally used only in mission avionics, MIL-STD-1553 is now used in flight critical avionics (such a terrain following subsystems), flight control, weapons, electrical power control, and propulsion control.

MIL-STD-1553 is commonly used outside the U.S. The United Kingdom (U.K.) Ministry of Defence and NATO have adopted MIL-STD-1553 as a standard. The NATO alliance countries as well as others (e.g., Israel) produce subsystems and weapons with MIL-STD-1553 interfaces.

MIL-STD-1553 has become easier for the designer to use. Twenty years ago, a MIL-STD-1553 bus interface unit (BIU) required significant design and production effort. Now, MIL-STD-1553 use resembles microcomputer interfacing. Minicomputers and desktop personal computers used in ground laboratories also use MIL-STD-1553 interfaces produced by many companies in the U.S., U.K., and Europe.

MIL-STD-1553 is the most successful and most widely used standard of its type. International standardization is achieved by MIL-STD-1553B (without Notices) as part of or referenced by NATO STANAG 3838, ASCC Standard 50/2 and UK DEF STAN 00-18 (Part 2)/Issue 1.

# 2.0 UNDERSTANDING MIL-STD-1553

MIL-STD-1553 is designed for high integrity data exchanges between unattended equipment in military airplanes, ships, and land vehicles. The messages are highly repetitive, and their content and periodicity are all preplanned. Computers or digital logic control message execution include what action takes place when errors occur. Each piece of equipment contains a MIL-STD-1553 communication terminal operating from power within the equipment and providing the equipment data interface. The Standard calls the communication terminals Bus Controller (BC), Remote Terminal (RT), and Monitor (M).

The Standard specifies the terminal's exact electrical characteristics. The terminal hardware must operate exactly the way the Standard has defined it.

The Standard defines all of the message protocols that may be used. Unlike the electrical requirements, the system designer may choose to use any message protocol, as long as it is a complete protocol. The Standard does not define the many ways BCs, RTs, and Ms can be interconnected, except that: (a) the number of RTs on a single data bus cannot exceed the maximum number of addresses, and (b) the BC is the single controller of all messages on the bus.

#### 2.1 Functions of Bus Controllers, Remote Terminals, and Monitors

This section provides an introduction to the most common uses of 1553 terminals in systems today. It provides a frame of reference for the discussion of the 1553 protocol that follows.

All messages and their transmission rates are pre-established during system design. Since the BC is the

only controller, the BC only needs to follow instructions stored in memory to control communication and to monitor and service message requests. The BC also contains error analysis and decision logic to deal with all errors that can occur in the communication system. Thus, the BC's operation is well ordered, pre-established at design, and specific for each step necessary to achieve data communication and control. These operations are unique for their application. BC hardware design should have sufficient flexibility to allow BC use in many applications.

In contrast to the BC, the RT usually has specific functions and will use the data bus (under control of the BC) for bidirectional communications with other RTs or the BC as it supports system operation. For example, an inertial navigation system is an RT that provides position and acceleration data to the flight control computer and to crew instruments. The RT's primary roles are to be an interface for the equipment function within it and to communicate with other equipment connected to the same data bus.

The M is the only other electronic device used in MIL-STD-1553, and it has a limited application. The M has the features of both an RT and BC, except that it cannot transmit information on the bus. It can receive and store every message addressed to every terminal. Because this capability is usually impractical, the designer specifies which messages addressed to specific terminals the M will store. The design may include the ability to use loadable programmed data to establish the selection of the M's capability at power-on. The M's most common use is flight test instrumentation to verify data bus system performance.

#### 2.2 MIL·STD·1553 Message Formats

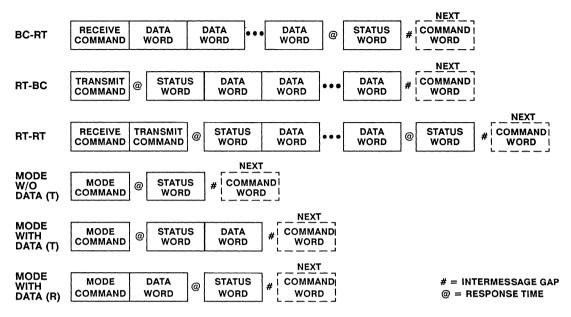

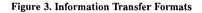

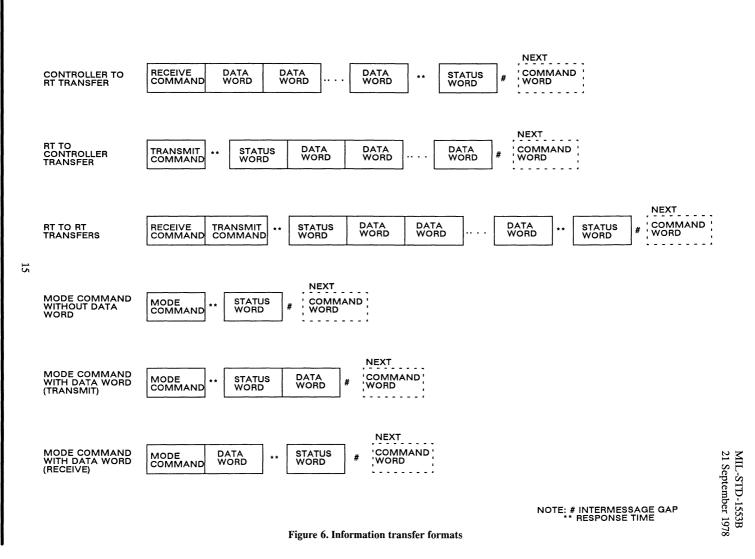

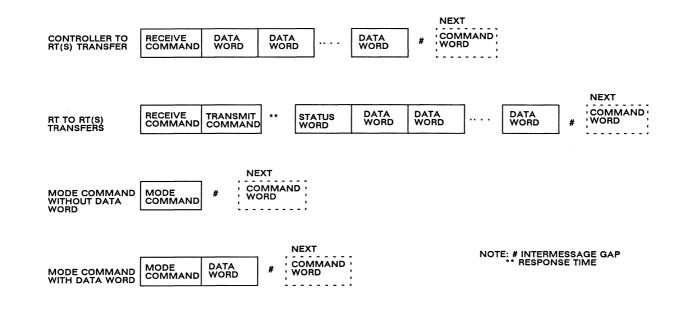

The Standard defines two types of message formats: nonbroadcast or "information transfer formats" and broadcast or "broadcast information transfer formats." Figures 3 and 4 show these formats, which are reproduced from figures 6 and 7 respectively of the Standard. Both information transfer formats are divided into data communication messages and communication management messages. Each message uses only standardized word types that are described in later sections.

#### MIL-STD-1553B INFORMATION TRANSFER FORMATS

Figures 3 and 4 show that all message formats begin with one or two command words that contain the RT's address number, message identification field number (subaddress), word count, and a one-bit field to indicate whether the data words are to be transmitted or received. RTs acknowledge message reception by transmitting a status word if they received an error free non-broadcasted message. Since RTs must respond within the response time the Standard allows, the response time is part of the message format. The status word contains the RT's address and additional information conveyed by setting the status word bits from logic zero to logic one.

The Standard also defines communication management messages that are identified by a specific message identification number in the message identification field. The communication management message number is the word count number field. The Standard calls these mode commands. The Standard defines mode commands for both non-broadcast and broadcast formats. (Section 2.6 describes all mode codes and their uses in a typical system.)

The Standard defines only three types of words: command word, status word, and data word. Figures 3 and 4 show the order of these words in messages. The non-broadcast message formats are used only for communication between two terminals. In contrast, broadcast message formats allow either a BC or an RT to transmit to all other terminals under the BC's direction. One of the terminal addresses is reserved for use as the broadcast address for all terminals.

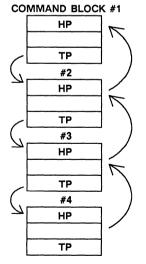

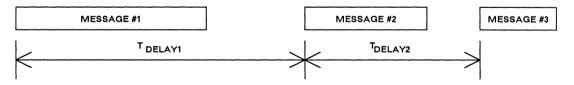

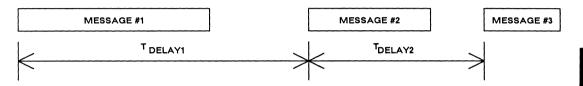

As shown in both figures 3 and 4, each message must be separated in time from the next by a minimum intermessage gap of at least two microseconds. This delay allows the analog bus to "quiet" prior to next message transmission. Typical intermessage gaps on computer-based BCs range from 30 to 60 microseconds.

#### 2.2.1 Non-Broadcast Message Formats

In non-broadcast formats, only six message types are allowed, and the use of any or all of them is optional. Three of these messages are for normal data communication, and three are for communication management. For normal non-broadcast communication management, the BC issues commands to: (a) require an RT to transmit a message to the BC (RT-to-BC); (b) originate a message to an RT (BC-to-RT); (c) require one RT to transmit a message, while directing another RT to receive it (RT-to-RT). For non-broadcast communication management, the BC issues mode commands to: (a) command one RT to perform the operation the mode indicates and to transmit its status word and a single data word (RT-to-BC with data word); (b) command one RT to transmit only its status word (RT-to-BC without data word) and perform the mode operation; and (c) command one RT to receive one data word, transmit its status word, and perform the mode operation.

Each message format requires the RT to transmit its status word so the BC can validate that the RT received the message. The message formats are basically "closed loop" because the BC receives confirmation that the message was received when the BC receives the RT status word. The RT status word bits provide additional information on the general maintenance condition of the RT and its subsystem and allow the RT to request service to transmit pre-planned aperiodic data.

The Standard defines word and message validation criteria. If the terminal hardware detects either an invalid word or a transmission discontinuity, it considers the word and message invalid. This requirement applies to all terminals. The Standard requires the RT to suppress the status word if the message validation criteria is not met or if the number of words received does not match the word count in the command word. In both of these cases, the RT sets but does not transmit the Message Error bit in the status word. The BC easily detects the message failure if, after waiting the maximum RT response time, it does not receive the status word. Although the Standard does not impose any error handling requirements, the BC should be programmed to handle such error occurrences. The system designer must decide what error response the system will perform for each pre-programmed message.

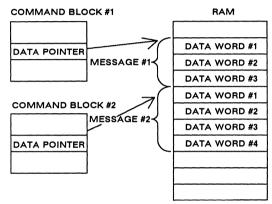

#### 2.2.1.1 BC-to-RT Receive Message

The BC-to-RT receive message occurs when the BC transmits a command word with a unique RT address followed by 1 to 32 contiguous data words as specified by the command word. The RT recognizes the command word, its own unique address, and the word count, and starts receiving data words for validation and use. After the RT receives a complete message and the response time elapses, the RT will transmit its status word and indicate that it received a valid message. The BC examines the returning status word and bases its actions on the RT's status bits. Since the RT is returning the status word, the BC is assured of message reception validation. If a valid complete message was not received, the RT will suppress the transmission of its status word. and the BC will wait only the specified response time before originating another message. The next message may be the error handling message to resolve the problem or a retry of the original message. See figure 3.

#### 2.2.1.2 BC-to-RT Transmit Message

The BC performs the BC-to-RT transmit message when it desires data from a unique RT. After the response time, the unique RT selects the data requested based on the command word subaddress and transmits its status word followed by the number of data words the BC specified in the command word. The BC receives the unique RT's status word, bases its actions on the RT's status bits, and stores the incoming data words. Message validation is accomplished by examining the RT's status word, performing the message validation the Standard requires, and verifying that the number of data words received agrees with the word count in the command word. See figure 3.

#### 2.2.1.3 RT-to-RT Message

The BC can direct one RT to transmit data and another RT to receive the data. The <u>receive</u> command comes first and prepares the receiving RT for data words. The next command word, a <u>transmit</u> command, causes another RT (based on address) to transmit. As in the BC-to-RT transmit command, the transmitting RT sends its status word followed by the commanded number of contiguous data words. The receiving RT validates message correctness prior to transmitting its status word. The BC then must review and act accordingly on both the transmitting and the receiving status words to complete the message. The receipt of both status words results in the verification of individual message completion. See figure 3.

#### 2.2.1.4 Non-Broadcast Mode Command Messages

The BC can use three different mode command message formats to manage unique RT problems. The first format commands a unique RT to accomplish the action specified and transmit its status word after the appropriate response time. The second and third formats allow the BC to request the RT to transmit its status word and a data word or to receive a command word and one contiguous data word prior to the RT transmitting its status word. A description of the BC's use of the mode codes to manage the system and resolve problems with RTs follows the message and word descriptions in section 2.6.

#### 2.2.2 Broadcast Message Formats

The broadcast messages allow a single terminal to transmit a message to all terminals. The Standard defines four broadcast messages: BC to all RTs, single RT to all RTs, BC mode command to all RTs, and BC mode command with data word to all RTs.

#### 2.2.2.1 BC Broadcast to RTs

The BC-to-RTs message is a transmission from the BC to all RTs which have the ability to receive a broadcast message. (The Standard does not require RTs to have the capability to receive a broadcast message.) The command word contains the reserved address for broadcast. Following the command word are from 1 to 32 data words as specified in the command word data count field. The data words tell the RTs the type of message being transmitted and the length of message. If the message is validated, the RTs will use the broadcasted data. With broadcast messages, transmission of the status word to the BC is not permitted thereby avoiding status word collisions and unreadable communication on the bus. If the BC must verify message reception to one or all RTs, it may transmit a non-broadcast mode command message to any RT individually to determine the status of the previous message reception.

#### 2.2.2.2 RT Broadcast to RTs

The BC uses two contiguous command words to command a single RT-to-all-RTs message. The first command word contains the broadcast address to receive a message. The second command word contains the address of a unique RT. The BC uses the second command word to direct the unique RT to transmit a message to all receiving RTs. The message states the required number of data words. Note that the receiving RTs are waiting for data words.

The unique RT prepares the commanded message during a response time. When the response time ends, the unique RT transmits a status word followed by the commanded number of data words to all receiving RTs. Because the status word contains the address of the transmitting RT, the receiving RTs ignore it. The receiving RTs do accept the data words that follow the status word. They decode the data words and use the data if it is error free. The receiving RTs set their status words to indicate broadcast reception (message completion) but do not automatically transmit their status words. To verify message completion, the BC requests each RT to transmit its status word using a mode command. The BC examines the transmitting RT's status word and waits for message completion before beginning the next message. See figure 4.

2.2.2.3 Broadcast Mode Command Messages The BC uses two broadcast mode code command message formats to manage RT problems. The BC can transmit seven broadcast mode commands without a data word to all RTs: Synchronize, Initiate Self-Test, Transmitter Shutdown, Override Transmitter Shutdown, Inhibit Terminal Flag, and Override Inhibit Terminal Flag. (See section 2.6 for a description of the meaning of mode codes.) Three additional broadcast mode command formats are transmitted with a data word: Synchronize With Data Word, Selected Transmitter Shutdown, and Override Selected Transmitter Shutdown. The data word contains information RTs need to execute these commands. The designer, not the Standard, defines these data words.

The RT receives the mode command and performs the required function if it is designed to support broadcast messages and has implemented the optional mode commands as part of its design. If the RT does not have the broadcast design capability, it will not accept the RT address and will continue to operate as if the command was to another RT.

#### 2.3 Note on MIL-STD-1553B Notice 2

This note distinguishes the BC and RT capability dictated by Notice 2 from optional use and prohibited use. (Notice 2 completely replaces Notice 1.)

Since MIL-STD-1553 allows optional use of all the message formats and mode commands, many early BC and RT designs did not include the capability to decode some or all of the mode codes or to respond to some of the message formats. Many early RT designs did not have the capability to implement the RT-to-RT message. For these designs, the designer selected the message formats and mode commands required only for the specific application.

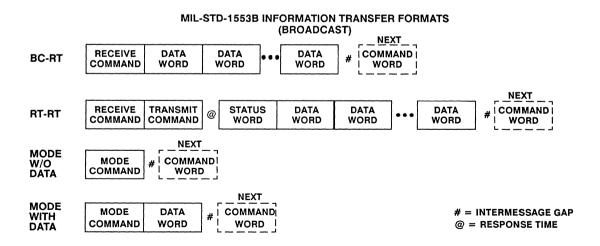

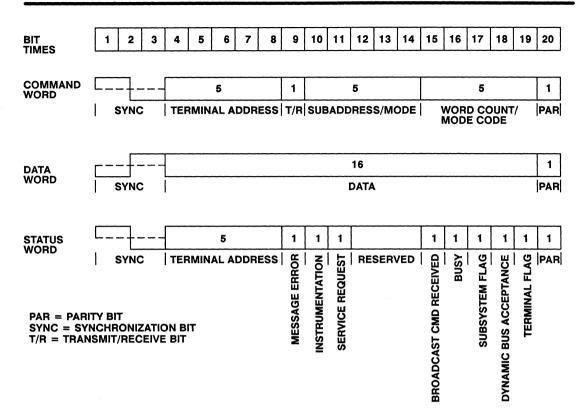

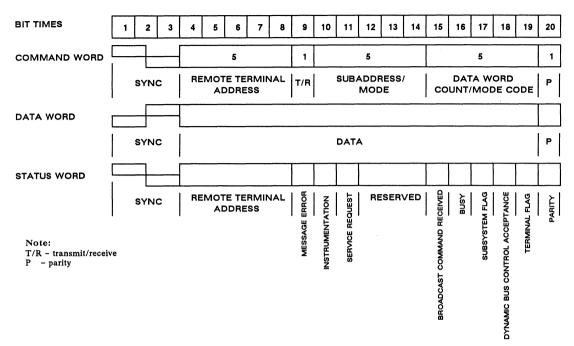

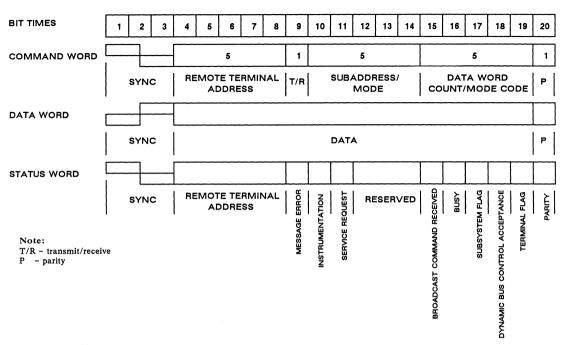

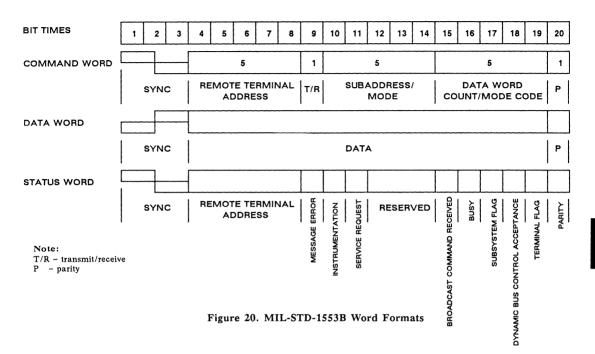

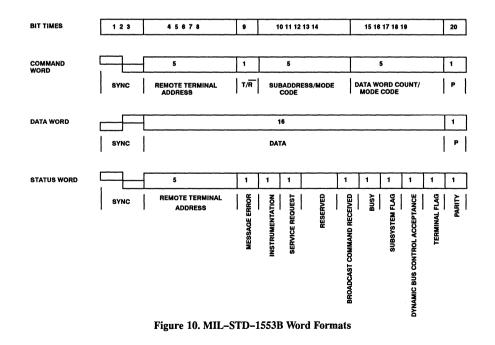

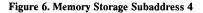

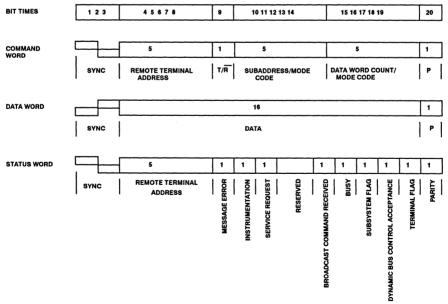

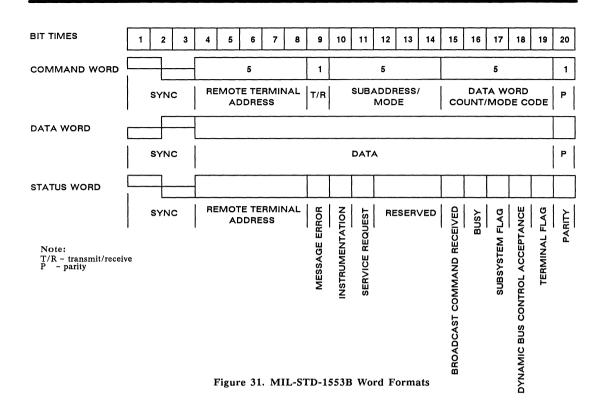

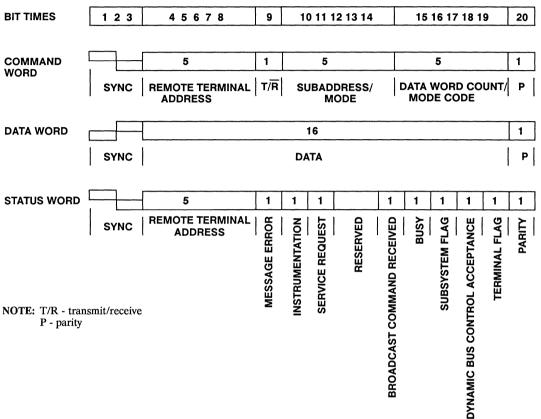

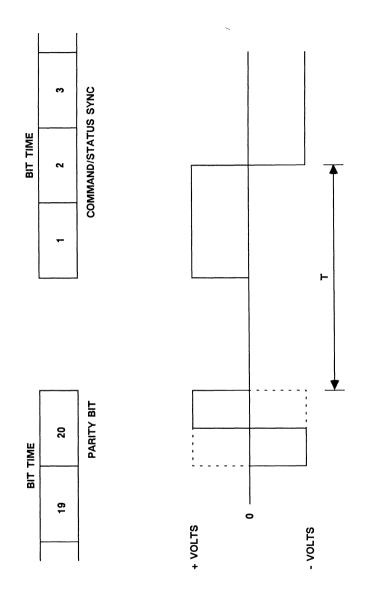

Figure 5. MIL-STD-1553B Word Formats

Notice 2 clarified that BCs and RTs must have all nonbroadcast message formats. RTs, however, are not required to implement non-broadcast mode commands with data words if such mode commands are not part of the RT's design requirements. Notice 2 also defined a required minimum set of mode codes that the RT's design must include. The RT may or may not use all of the mode codes. In Notice 2, the USAF also mandated that some of the optional capabilities of MIL-STD-1553B never be used in airplanes.

#### 2.4 Command, Status, and Data Words

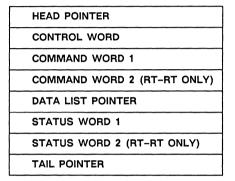

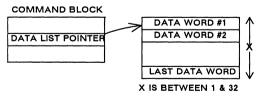

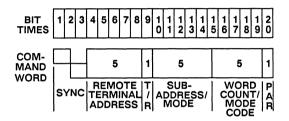

All bus data is transmitted as 20-bit words, as figure 5 shows. The Standard identifies and specifies only three types of words: command, status, and data.

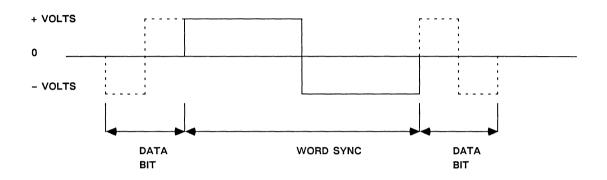

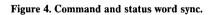

The time interval of three bits serves as a combination of word identification and synchronization (sync). The sync pattern, defined by the Standard, is unique and is not the same as the waveform of data bits. The two parts of the sync are each 1.5 times a one-bit time, transmitted either as a positive voltage waveform followed by negative voltage waveform or vice-versa. The sync order identifies the words: the command and status words have the positive waveform first while the data word has negative waveform first. Word parity is also part of the word. The 20 bits are, in order: 3 bit times for the sync, 16 bit times for data, and 1 bit time for parity.

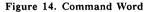

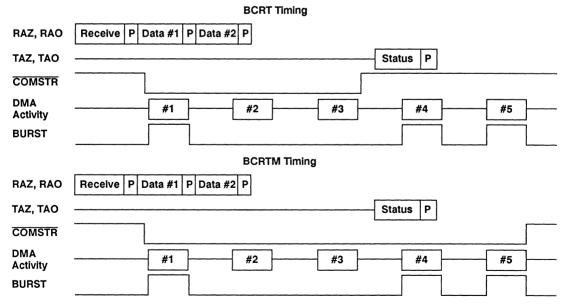

#### 2.4.1 Command Word

The Standard uses these terms for the command word fields:

| Bit<br>Times | Number<br>of Bits | 1553<br>Name         |

|--------------|-------------------|----------------------|

| 1-3          | 3                 | Sync                 |

| 4-8          | 5                 | RT address           |

| 9            | 1                 | T/R bit              |

| 10-14        | 5                 | Subaddress/Mode      |

| 15-19        | 5                 | Data word count/Mode |

| 20           | 1                 | Parity               |

The command and status words use the same sync pattern. The data word uses the inverse of the command and status pattern. However, since the BC always issues commands to RIs, the BC knows which RT it has commanded. The BC compares the RT address in its command word to the address in the RT's status word to validate that the commanded RT is transmitting its status word. This address comparison is always unambiguous because the BC does not have a commanded address.

RTs use the sync pattern to determine if the word is a command. If it is, the RT will examine the address for its own unique address number or the broadcast address. Status words transmitted on the bus will always have the address of the transmitting RT. Therefore, the RT can always determine if a word with a command/status sync is a command word to which it must respond. The RT can always separate command and status words from each other and from data words.

If the command word is addressed to a particular RT and the RT determines that it is being commanded, it decodes the T/R bit. A logic one indicates the RT will transmit data while logic zero indicates it will receive data.

Finally, the RT decodes the subaddress/mode field. First the RT determines if a mode command is being transmitted and if it is, the RT interprets the word count/mode field as a mode code. If it is not a mode command, the RT interprets the subaddress/mode field as the message identification and the word count/mode field as the number of words to be received or transmitted, depending on the T/R bit.

The last bit in the command word is the parity bit. All 1553 words end with the parity bit set to "odd." Odd parity means there is an odd number of logic ones in the word (16 data bits plus the parity bit). Odd parity is accomplished by counting the logic ones in the word and setting the parity bit to one or zero to achieve an "odd" number of ones.

#### 2.4.2 Note on Subaddress Assignment

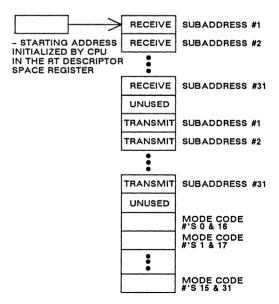

The Standard reserves two subaddresses for mode command identification. A maximum of 30 transmit and 30 receive messages can be assigned to subaddresses. Each RT must be designed to store its assigned receive messages and construct its required transmit messages. The receive and transmit messages are assigned to the receiving and transmitting subaddresses, respectively. If more than 30 subaddresses are needed, mode code messages can be used to switch from one set of 30 transmit/receive subaddresses to another set.

MIL-STD-1553 does not define or restrict the subaddress-to-message assignment. The only exception is Notice 2 requires a receive and transmit subaddress be dedicated to a wrap-around message equal in length to the longest message the RT receives or transmits. The Notice suggests, but does not mandate, that this dedicated subaddress be 30. The wrap-around message would be received from the BC, unaltered by the RT, and transmitted upon BC command.

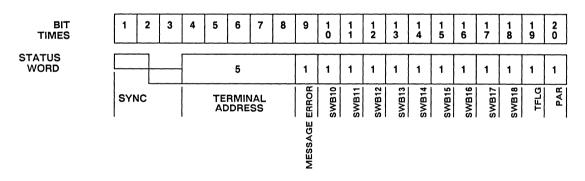

#### 2.4.3 Status Word

The Standard uses these terms for the status word fields:

| Bit<br>Times | Number<br>of Bits | 1553<br>Name                   |

|--------------|-------------------|--------------------------------|

| 1-3          | 3                 | Sync                           |

| 4-8          | 5                 | RT address                     |

| 9            | 1                 | Message error                  |

| 10           | 1                 | Instrumentation                |

| 11           | 1                 | Service request                |

| 12-14        | 3                 | Reserved                       |

| 15           | 1                 | Broadcast command received     |

| 16           | 1                 | Busy                           |

| 17           | 1                 | Subsystem flag                 |

| 18           | 1                 | Dynamic bus control acceptance |

| 19           | 1                 | Terminal flag                  |

| 20           | 1                 | Parity                         |

The RT transmits a status word after receiving a command with or without a data word (or words) from the BC unless the address in the command word is the broadcast address. The status word sync is identical to the command word sync and precedes the RT address. Each RT has a unique address and may also have a broadcast address which is never transmitted in the status word. Notice 2 requires that an address change be possible by external connector without physical modification of the RT and that the RT validate its address at power-on as a minimum. Notice 2 also requires that no single failure cause an RT to validate a false address. This requirement is usually accomplished by adding a sixth interface, which is parity on the five address lines and itself and is part of the wire bundle just like the address lines. Even though this is a Notice 2 requirement, it has general application to all MIL-STD-1553B RTs and is a de facto method of defining an RT's address. The remainder of the status word, excluding the common approach for parity. contains specific status bits. Each bit has a single application and is used to convey information that generally solicits standard responses from the BC.

The paragraphs below describe how a typical system uses status bits and BC responses. Many of the BC responses are associated with the mode commands described in section 2.6.

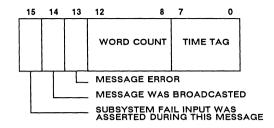

The Message Error bit is set in an RT when the incoming message has failed the Standard's word or message validation requirements. Since the status word is not transmitted for message errors or broadcast messages, the BC can only observe a message error when the mode code Transmit Status

or Transmit Last Command is sent to the RT. The only exception to this operation occurs with an RT that has been designed with the illegal command monitor option. If this type of RT receives a command that it is not designed to receive, the RT will respond with a status word with the Message Error bit set.

The <u>Instrumentation bit</u> is always set to zero to allow the same bit in the command word to be set to one, thus allowing a Monitor to determine status versus command words. If the one is used in the command word, mode codes are identified by all ones and subaddresses are limited to 15. If the one is not used in the command word, mode commands are usually all zeros, and 30 receive and transmit subaddresses are available.

The <u>Service Request bit</u> is set in the status word when the RT wants to transmit an aperiodic message. As described in section 2.6, the BC uses the Transmit Vector mode command to determine the desired transmission.

The <u>Broadcast Command Receive bit</u> is set when the RT has received a valid broadcast message. Since the RT is required to suppress (not transmit) the status word on broadcast messages, the BC can validate message reception using the Transmit Status or Transmit Last Command mode code.

The <u>Busy bit</u> indicates to the BC that the RT is unable to receive or transmit valid data with its subsystem interface. If the BC commands the RT to receive data when it is in a busy condition, the RT cannot use the received data. If the BC commands the RT to transmit when it is busy, the RT will transmit its status word only with the Busy bit set. RTs should be designed to minimize the time when they are busy. During initialization, however, an RT is often busy until it completes power-up. Busy operation at other times is usually unnecessary.

The <u>Subsystem Flag</u> alerts the BC of a subsystem problem. Subsystem error handling software is required to manage this problem. Thus, the BC will pass this information to application software to deal with the aspects of a failed subsystem on the bus.

The <u>Dynamic Bus Acceptance bit</u> is discussed in section 2.6. It is associated with the Dynamic Bus Control mode command. The new BC sets this bit to tell the existing BC to stop operating in the BC mode and revert to an RT or Monitor mode.

The <u>Terminal Flag bit</u> indicates an RT hardware failure. This failure may not prevent the RT from continuing to operate due to its redundancy. Several mode codes such as Initiate Self-Test and/or Transmit BIT can analyze the problem's severity. Once failure analysis is complete, the BC can use the Inhibit Terminal Flag mode code to suppress future reporting. Then, with subsequent communications, the BC can continue to use a non-fatal failure in an RT without re-examining the failure.

#### 2.4.4 Data Word

The data word contains the three-bit inverse sync pattern of the command and status words, followed by 16 bits of user-defined data, ending in an "odd" parity bit. MIL-STD-1553 requires the most significant bit be transmitted first. It does not require that a logic one or zero represent any specific meaning, such as "on" or "off."

#### 2.5 Note on Probability of Undetected Errors

MIL-STD-1553's noise rejection capability has been satisfactory for almost any application. Table II of MIL-STD-1553B indicates that an RT can have only one error after receiving 52 million words. This translates to approximately one error every 33 minutes for BC-to-RT messages of 10 words transmitted at 1667 messages per second. Ten-word messages transmitted at this rate use approximately one-half the capacity of the data bus.

If the system uses non-broadcast messages or verifies broadcast messages using a mode command, the system will detect one error per 33 minutes and will activate the system error correction to resolve the message error. Therefore, the chance of an error going undetected is approximately 10E21 bits/error, yielding more than a lifetime before an undetected error can occur. If data integrity requirements exceed this number, then the designer can add error correction encoding techniques to each message. Since the designer controls all data definition methods, the complexity of data encoding is user dependent.

#### 2.6 Meaning of the Command Word Mode Codes

The following table defines all of the mode codes in MIL-STD-1553B. The first 16 codes are not transmitted with a data word, but the last 16 are transmitted with a data word. It is inappropriate to broadcast mode codes requiring RT data word responses because multiple RT transmissions cause bus crashes. Dynamic Bus Control broadcast is also inappropriate. For mode codes 17 to 31,

| T/R<br>Bit   | Mode<br>Code | Function                               | Data<br>Word | Broad-<br>cast? |

|--------------|--------------|----------------------------------------|--------------|-----------------|

| 1            | 0            | Dynamic bus control                    | No           | No              |

| 1            | 1            | Synchronize                            | No           | Yes             |

| 1            | 2            | Transmit status word                   | No           | No              |

| 1            | 3            | Initiate self-test                     | No           | Yes             |

| 1            | 4            | Transmitter shutdown                   | No           | Yes             |

| 1            | 5            | Override transmitter shutdown          | No           | Yes             |

| 1            | 6            | Inhibit terminal flag bit              | No           | Yes             |

| 1            | 7            | Override inhibit<br>terminal flag bit  | No           | Yes             |

| 1            | 8            | Reset remote terminal                  | No           | Yes             |

| 1            | 9-16         | Reserved                               | No           | TBD             |

| 1            | 17           | Transmit vector word                   | Yes          | No              |

| 1            | 18           | Synchronize                            | Yes          | Yes             |

| 0            | 19           | Transmit last command                  | Yes          | No              |

| 1            | 20           | Transmit BIT word                      | Yes          | No              |

| 1            | 21           | Selected transmitter shutdown          | Yes          | Yes             |

| 0            | 22           | Override selected transmitter shutdown | Yes          | Yes             |

| 1<br>or<br>0 | 23-31        | Reserved                               | Yes          | TBD             |

the T/R bit is important because it defines whether the BC or the RT transmits the associated data word.

#### **0** Dynamic Bus Control

The active BC uses this mode code to pass control to another BC. The transfer allows the other BC(s) time to control subsystems on the same data bus. Once the BC has passed control, the former BC must assume the role of an RT or M. This approach provides considerable autonomy from BC to BC at the overhead expense of time-sharing the bus and the risk of no BC or more than one BC being in control at any one time. This method should never be used to pass control from the primary BC to the back-up BC when performance problems with the primary BC occur because the failing unit seldom operates as planned.

#### 1 Synchronize without Associated Data Word

#### 18 Synchronize with Associated Data Word

These BC-transmitted mode codes can be used to synchronize one or all RTs if used with a broadcast

address number in the command word. Since no additional data is provided with the first mode command, the receiving RT(s) must be designed so that a predefined action occurs. The same is true for the Synchronize with Data Word mode. In this mode command the user may define specific synchronization information. These mode commands have been used to initialize RTs, set clocks to a preset value, release or set internal RT buffers, define frame changes, select subaddress blocks, and perform many other user-designed functions. Each designer has chosen different applications for these mode commands. Therefore, the designer should examine system impact when using off-the-shelf RTs.

#### 2 Transmit Status Word

This is one of the most common mode codes used to obtain a status word from a specific RT. Since this mode code does not update the information bits in the status word when the RT receives it, the BC can interrogate an RT concerning the previous message. This mode code can also be issued to troubleshoot an RT that fails to transmit a status word to determine if the previous message was received with or without error. This mode code provides one method to determine if a unique RT received a previous message that was a broadcast message. (See Transmit Last Command mode code for a second method.)

#### 19 Transmit Last Command Word

The BC can use this mode code to determine if an RT received a previous message (broadcast or non-broadcast). The command will not change the status word, therefore the status word will reflect the previous command's information. If the BC is capable of storing and evaluating both the data word (the 16 bits from the previous command word), and the status word, this command can provide the same information as the Transmit Status mode command. Often systems are not designed to store both the status word and the data word, thus two separate mode commands are required (i.e., Transmit Status and Transmit Last Command). This mode command is used to verify order of message reception where order is critical to system performance. However, the system designer should minimize the use of messages requiring specific order, if possible, or use unique subaddress mapping to ensure multiple message order in the receiving RT, thus requiring no specific verification.

#### **3** Initiate Self-Test

This mode code allows the BC to command an RT to initiate self-test. The test results can be collected after the RT has conducted its self-test via the Transmit BIT mode command. Generally, RTs require time to accomplish this task, therefore the transmission of this mode command and its associated reporting mode command must be properly timed to achieve the most recent self-test results.

#### 4 Transmitter Shutdown

5 Override Transmitter Shutdown

8 Reset Remote Terminal

21 Selected Transmitter Shutdown

#### 22 Override Selected Transmitter Shutdown

These mode commands are used to shutdown or initialize transmitters or to reset the RT to a power-on state. With dual-redundant standby systems, mode commands 04 and 05 are usually used. Mode commands 04 and 05 always refer to the transmitter on the other bus, not the transmitter associated with the bus receiving the command. Mode commands 21 and 22 are used in systems where the number of redundant data buses exceeds two. The data word indicates which bus to shutdown. Once again it will not be the transmitter of the receiving bus. Mode commands 21 and 22 are used only when the BC cannot communicate with an RT on a bus because the RT's transmitter is active. Generally this condition is due to a failure. Another method, the Reset mode command, causes the RT to re-initialize completely by going through a power-down and power-up sequence. These methods should be required only if the RT's watchdog timer associated with the length of a transmission fails. Reset may also be used to initiate one or all RTs to a power-on condition for start-up. This action will clear internal information to create an orderly start-up.

#### 6 Inhibit Terminal Flag Bit

#### 7 Override Inhibit Terminal Flag Bit

These mode codes allow the BC to control operation of the Terminal Flag bit in the status word. When a single RT interfaces to more than one bus, a method of monitoring for the first failure is required. After analysis of the fault, the BC can remove the fault reporting to prevent unnecessary analysis by the BC as the RT continues to perform using its redundant circuitry. Since most systems have a minimum dual-standby redundancy capability, the elimination of fault reporting after a single failure causes no hardship. If greater than dual redundancy is used, other methods such as Transmit BIT word should be used to monitor performance after the first failure. Thus, the inhibit mode code prevents needless error analysis after every message transmitted or received by the RT because the status word's Terminal Flag bit is set.

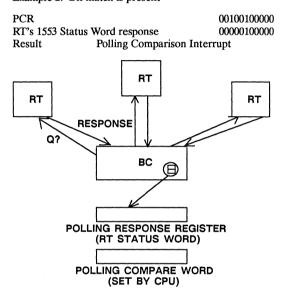

#### 17 Transmit Vector Word

This mode command is used to determine the subaddress of the aperiodic message that the RT has requested using the Service Request bit in the status word. Although user defined, the data word usually contains the information that allows the BC to enter its aperiodic message table and command the appropriate message transmission. The RT design may require the subsystem to queue several aperiodic requests prior to transmitting the Service Request bit in the status word.

#### 2.7 1553 Electrical Interface Requirements

The Standard defines interface characteristics that achieve electrically compatible terminals capable of bus communication. It specifies transmitter and receiver interface parameters compatible with bus cable and bus coupler parameters. These are analog design parameters which allow the system designer to build multiple systems using terminal electronics regardless of subsystem function.

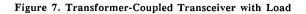

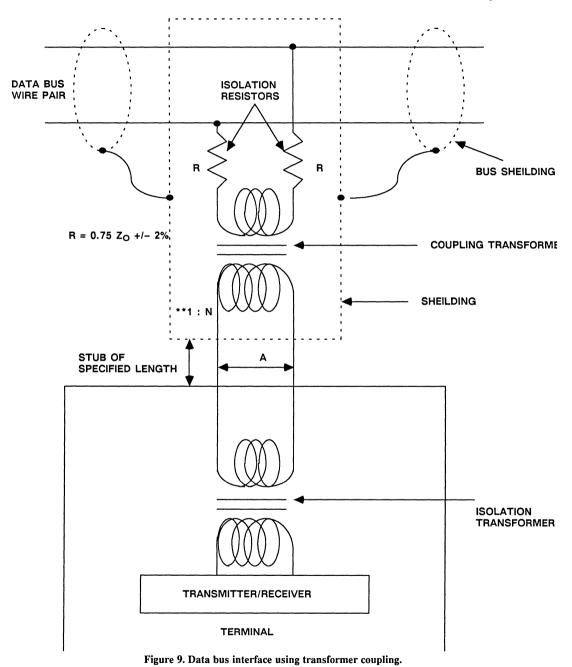

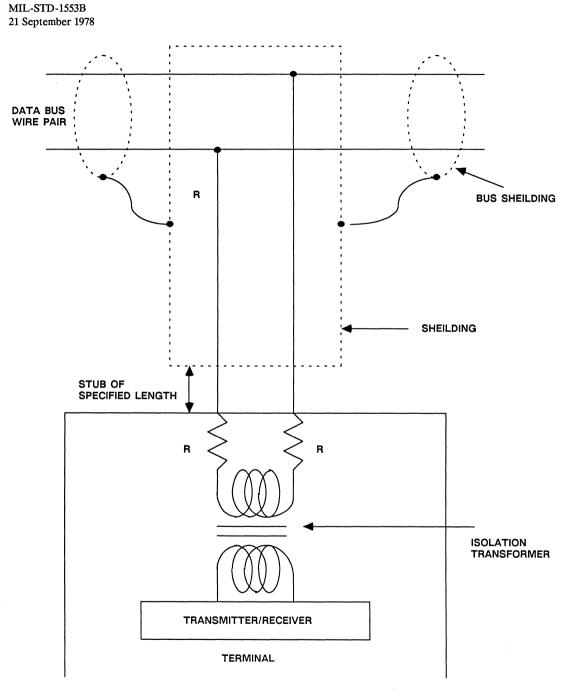

The Standard has word and message validation requirements for terminals and requirements for the data bus cable and bus termination resistors. The Standard allows a designer to connect a terminal to the bus in two ways. The direct method allows a connection of the RT to the main bus with no electrical components. The transformer-coupled method uses an isolation transformer and resistors between the RT and the main bus. The cable from the main bus to the RT, if it is used, is called a stub.

#### 2.8 Note on the Historical Rationale for MIL-STD-1553 Characteristics

Technical papers and conference handouts during the early 1970s explain the rationale for the technical decisions that lead to the MIL-STD-1553 data bus. Several commercial airplane multi-wire serial link designs and RS-232 existed, but no available design met the data rate and integrity needed for serial multiplexing of automatic subsystems. Therefore, a new design had to be selected. The existing B-1A, F-15A, and space shuttle designs provided a design foundation. Designers had to select modulation, method of synchronization, link control and data protocol, and physical media.

Baseband modulation was chosen instead of carrier modulation because of hardware complexity and the lower bandwidth required by baseband modulation. The link would be asynchronous (independent clocks in terminals) and self-clocking (synchronization information contained in message words). Studies of the trade-off of the number of overhead bits required versus noise immunity pointed to the unique three-bit word synchronization that MIL-STD-1553 uses.

Bus control methods studied included both central and distributed control. Time slot control by a central timing mechanism was discarded as inflexible. Contention methods for obtaining bus control were discarded because of lack of positive control of the bus within a predictable time. Message failure detection has always been an outstanding feature of MIL-STD-1553. Concerns of the high overhead to assure message completion on a contention bus, as well as the non-deterministic latency, contributed to the rejection of contention. The choice of a single bus control re was left, but the protocol made it possible to pass bus control to any capable unit. Dynamic bus control is a rarely used feature.

With only one active bus controller, message formats with minimum overhead were desirable. Controller-to-terminal and terminal-to-controller messages were obvious choices. The USAF and USN, however, never agreed on broadcast message utility or desirability. Broadcast messages were nevertheless included. The overhead consisted of the command word (16 bits), a delay less than one word time for the terminal to respond with a status word, a status word (16 bits), and parity and sync for each word.

Multiple cables were rejected in favor of the single cable because 1 MHz (1 Mbps) bandwidth was adequate for control and data. At that time, 30 terminals on one cable were adequate. The decision to transformer couple the cable influenced the signal encoding. Manchester biphase level encoding was chosen from among candidates that included polar and bipolar NRZ (non-return to zero voltage waveform), polar RZ (return to zero voltage waveform), and unipolar level NRZ. Tests showed that a twisted, shielded pair was adequate for the 1 MHz transmission rate, making coaxial or triaxial lines unnecessary. The greatest noise and fault immunity was gained by choosing an impedance-matched and loaded data bus for the bus connections (the impedance into a terminal is much greater than the characteristic impedance of the line). Common mode rejection was attained by using balanced differential transmitter/receivers.

# 3.0 MIL-STD-1553 AND SYSTEMS INTEGRATION

#### **3.1 Range of Bus Topologies and Applications**