## DATA STORAGE INTEGRATED CIRCUITS

## DATA STORAGE INTEGRATED CIRCUITS

For information:

#### VTC Inc.

Inside Sales 2800 East Old Shakopee Road Bloomington, MN 55425-1350

Fax: (612) 853-3355 Tel: (612) 853-5100

#### Toll Free: (800) VTC-DISC

The leader in quality, high-performance integrated circuits and customer service for the mass storage industry.

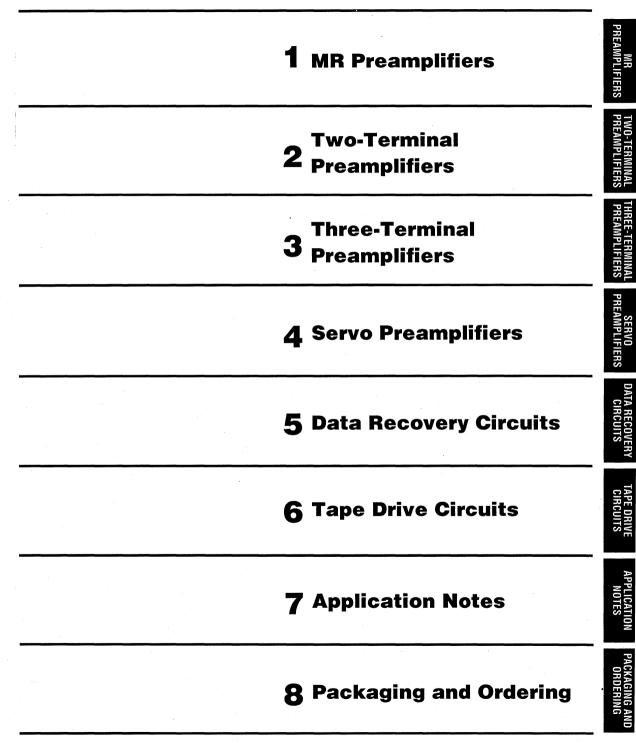

## **TABLE OF CONTENTS**

| Data Sheet and Product Definitions   |     | iv  |

|--------------------------------------|-----|-----|

| Quality and Reliability Assurance    |     | V   |

| The VTC Channel                      |     | vi  |

| Read/Write Preamplifiers Selector Gu | ide | vii |

#### Magneto-Resistive (MR) Read/Write Preamplifier

| VM61006 6-Channel, PECL WDI, MR Head     | New  | 1-3  |

|------------------------------------------|------|------|

| VM61012 12-Channel, PECL WDI, MR Head    | New  | 1-13 |

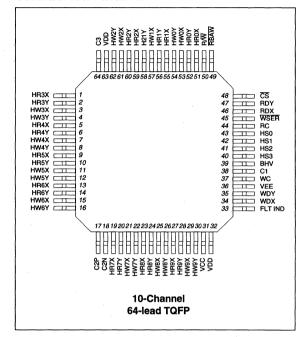

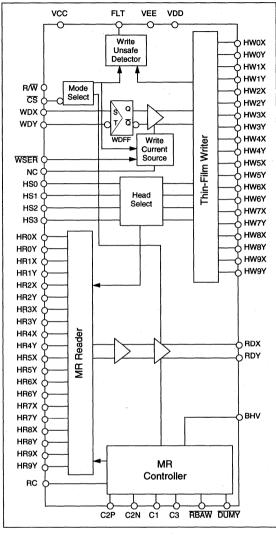

| VM61210 10-Channel, PECL WDI, MR Head    | New  | 1-23 |

| VM61312 12-Channel, PECL WDI, MR Head    | New  | 1-31 |

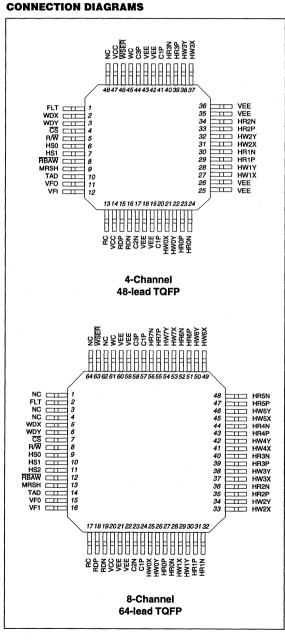

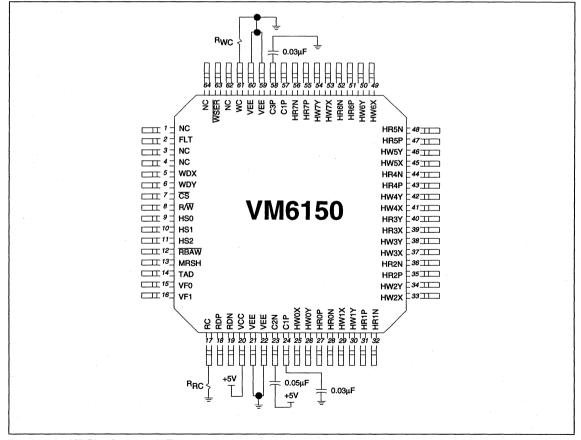

| VM6150 4 or 8-Channel, PECL WDI, MR Head | lNew | 1-41 |

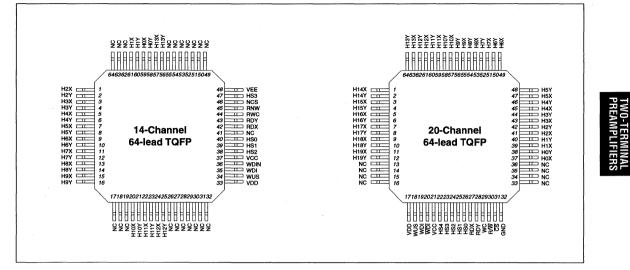

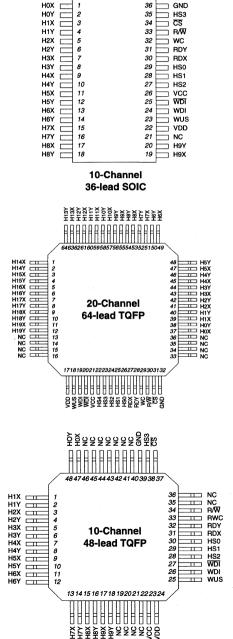

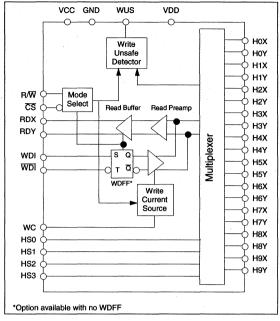

#### Two-Terminal High-Performance +5/+12V Read/Write Preamplifiers

| VM312 6, 7, or 10-Channel, TTL WDI, Thin-Film or MIG Heads                           | 2-3  |

|--------------------------------------------------------------------------------------|------|

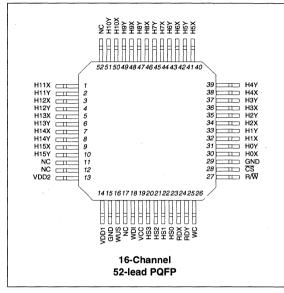

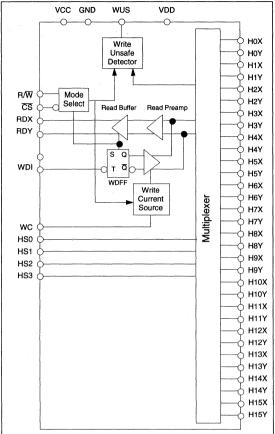

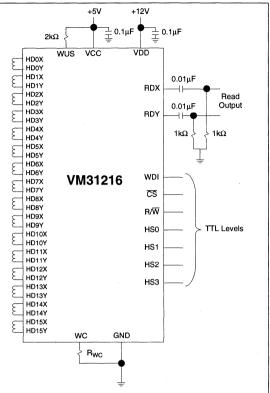

| VM31216 16-Channel, TTL WDI, Thin-Film Head                                          | 2-11 |

| VM312H 14-Channel, High Read Gain, TTL WDI, Thin-Film Head                           | 2-17 |

| VM313 8, 9, or 10-Channel, PECL WDI, Thin-Film Head                                  | 2-23 |

| VM31316 16-Channel, PECL WDI, Thin-Film Head                                         | 2-29 |

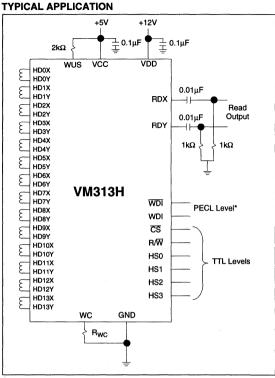

| VM313H 13 or 14-Channel, High Read Gain, PECL WDI, Thin-Film Head                    | 2-35 |

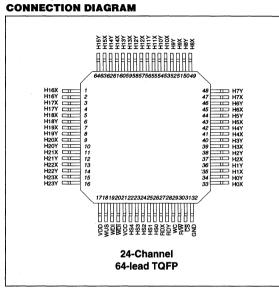

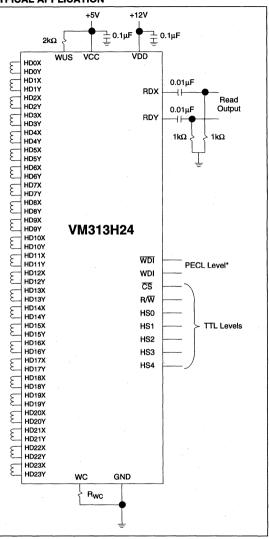

| VM313H24 24-Channel, High Read Gain, PECL WDI, Thin-Film Head                        | 2-41 |

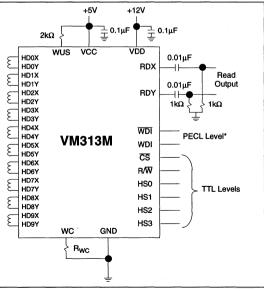

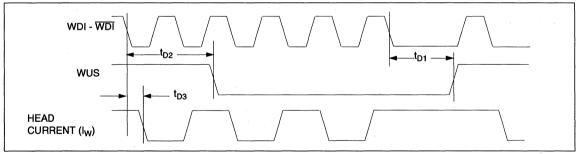

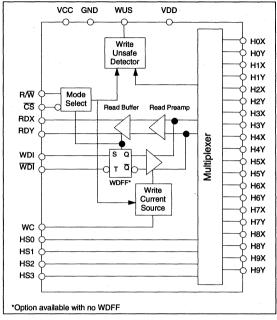

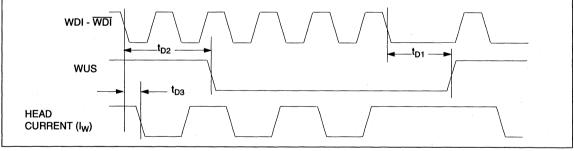

| VM313M 10-Channel, PECL WDI, Low Write Current, Thin-Film Head                       | 2-47 |

| VM5200 10 or 20-Channel, PECL WDI, Low Write Current, Thin-Film Head                 | 2-53 |

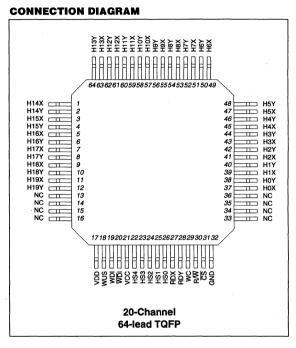

| VM5200M 10 or 20-Channel, PECL WDI, Low Write Current, Thin-Film Head                | 2-61 |

| VM522015C 20-Channel, PECL WDI, Low Write Current, Thin-Film Head                    | 2-67 |

| VM52510 10-Channel, PECL WDI, Low Write Current, Thin-Film Head With Servo Write     | 2-73 |

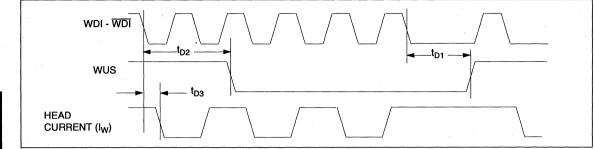

| VM5252015FC 20-Channel, PECL WDI, Low Write Current, Thin-Film Head With Servo Write | 2-79 |

#### **Two-Terminal High-Performance +5V Read/Write Preamplifiers**

| VM3200 2 or 4-Channel, 3 to 5-Volt, TTL WDI, Thin-Film or MIG Heads                            | 2-89             |

|------------------------------------------------------------------------------------------------|------------------|

| VM7100 2, 4, 6 or 8-Channel, TTL WDI, WC Gain = 20, Thin-Film or MIG Heads                     | 2-97             |

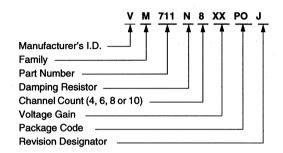

| VM71110 2, 4, 6, 8 or 10-Channel, TTL WDI, Low Noise, Low CIN, Thin-Film or MIG Heads          | 2-105            |

| VM7150 2, 4 or 8-Channel, PECL WDI, WC Gain = 20, Servo Write, Low CIN, Thin-Film or MIG Heads | 2-113            |

| VM7160 2, 4 or 8-Channel, TTL WDI, WC Gain = 20, Servo Write, Thin-Film or MIG Heads           | 2-121            |

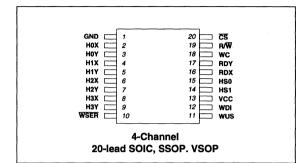

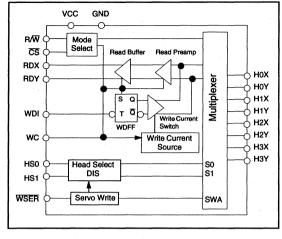

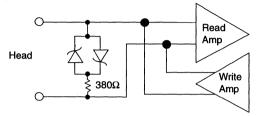

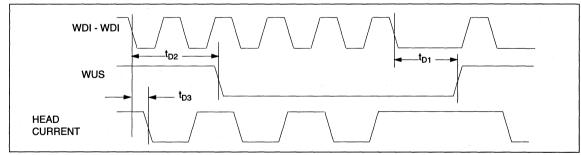

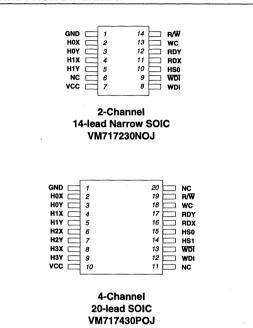

| VM7164S 4-Channel, TTL WDI, WC Gain = 20, Servo Write, Low CIN, Thin-Film or MIG Heads         | 2-129            |

| VM7170 2 or 4-Channel, TTL WDI, WC Gain = 20, Servo Write, Low CIN, Thin-Film or MIG Heads     | 2-137            |

| VM7200 2, 4, 6 or 8-Channel, TTL WDI, Av = 200, WC Gain = 20, Thin-Film or MIG Heads           | 2-143            |

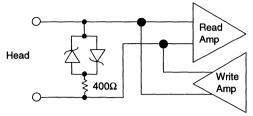

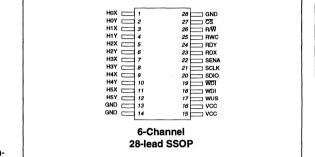

| VM723430 2 or 4-Channel, TTL WDI, A <sub>V</sub> = 300, WC Gain = 1, Thin-Film or MIG Heads    | 2-151            |

| VM7646 6-Channel, PECL WDI, Low Noise, Low CIN, Thin-Film Head Programmable                    | <i>New</i> 2-157 |

| VM7750F 4 or 6-Channel, PECL WDI, Low Noise, Low CIN, Thin-Film Head, Servo Write              | <i>New</i> 2-165 |

| VM7800 10-Channel, PECL WDI, Low Noise, Low CIN, Thin-Film Head, Servo Write                   | 2-173            |

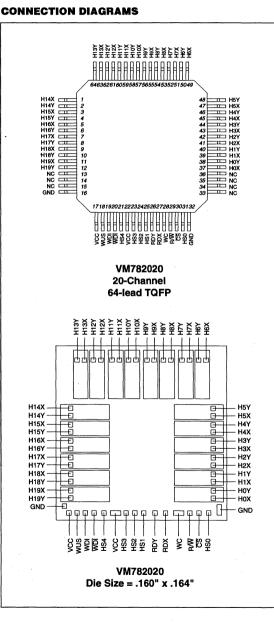

| VM782020 20-Channel, PECL WDI, Low Noise, Low C <sub>IN</sub> , Thin-Film Head, Servo Write    | <i>New</i> 2-181 |

#### Three-Terminal High-Performance Center-Tapped Read/Write Preamplifiers

| VM367 4-Channel, +5V, +12V, PECL WDI, Servo Write, Ferrite or MIG Heads .  |        |

|----------------------------------------------------------------------------|--------|

| VM367N225 2-Channel, +5V, +12V, PECL WDI, Servo Write, Ferrite or MIG Head | ds3-11 |

### Servo Read/Write Preamplifier

| VM323 Single-Channel, Thin-Film Head |  |

|--------------------------------------|--|

|--------------------------------------|--|

#### **Data Recovery Circuits**

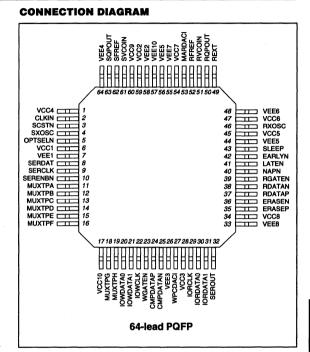

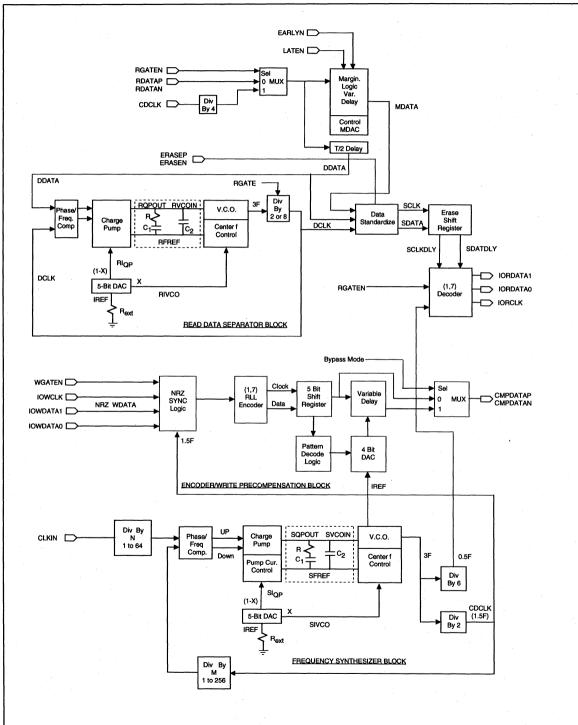

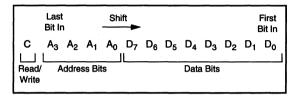

| VM53100 Data Separator Channel Chip, 100Mbits/sec                                                                                                                         | .New   | 5-3   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|

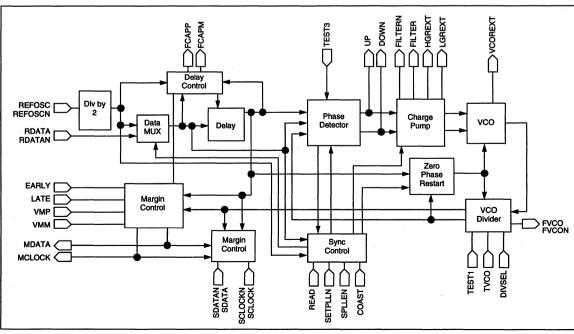

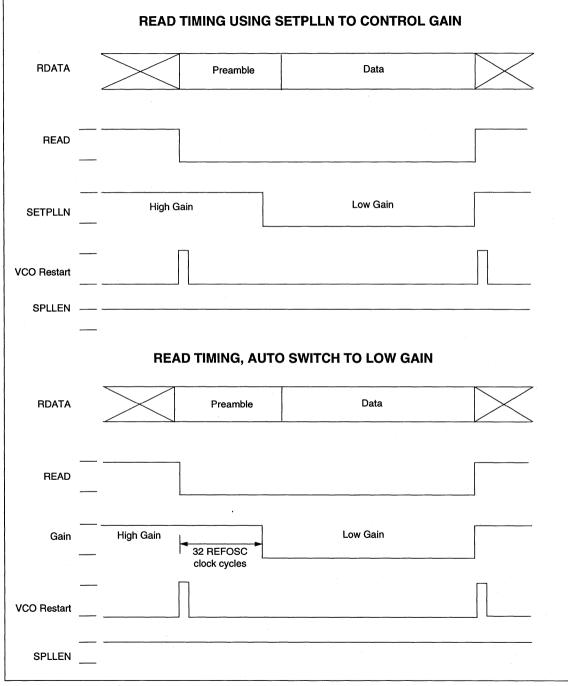

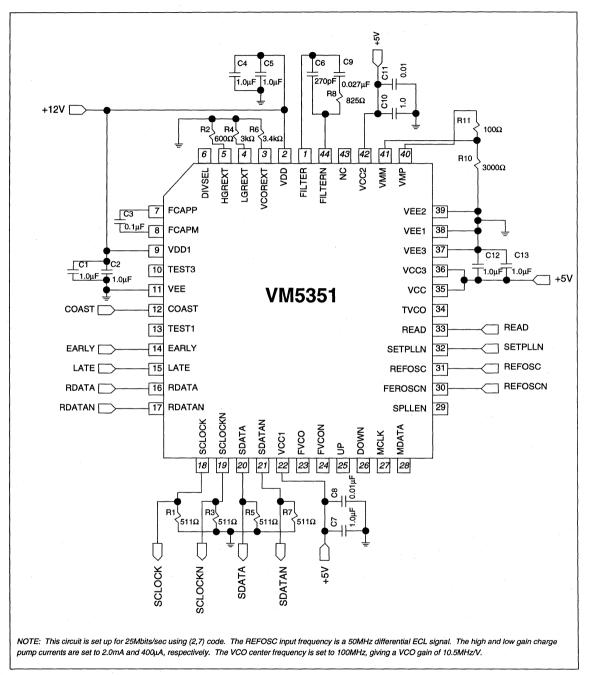

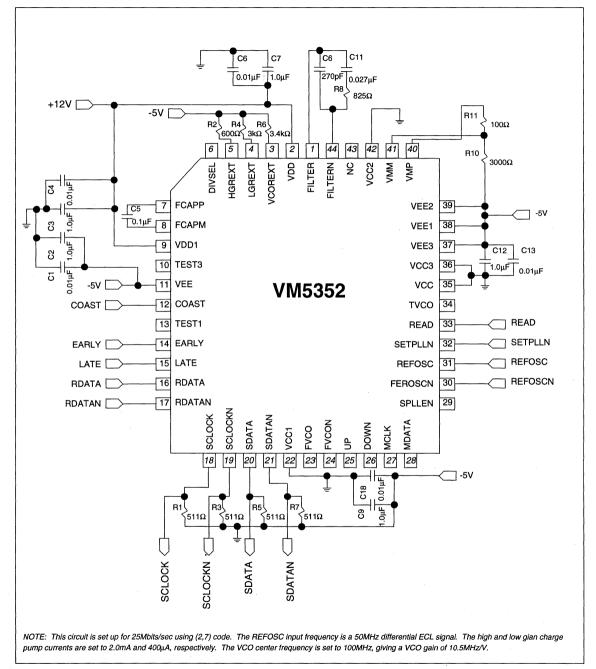

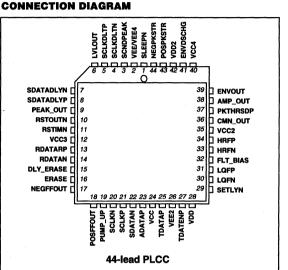

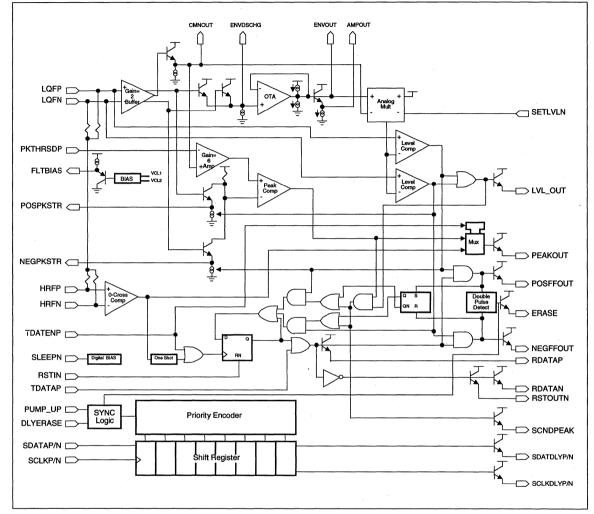

| VM5351/VM5352 Data Separator, 64 Mbits/sec Transfer Rate, (1,7) and (2,7) RLL Codes, ZDR Compatible,                                                                      |        |       |

| Marginalization Circuitry                                                                                                                                                 |        | 5-23  |

| VM5401 Pulse Detector/Qualifier, 64 Mbits/sec Transfer Rate, Erase Feature                                                                                                |        | 5-37  |

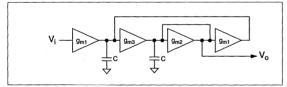

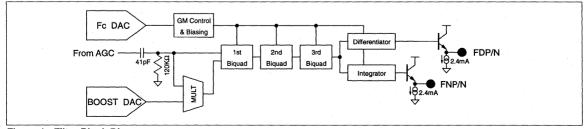

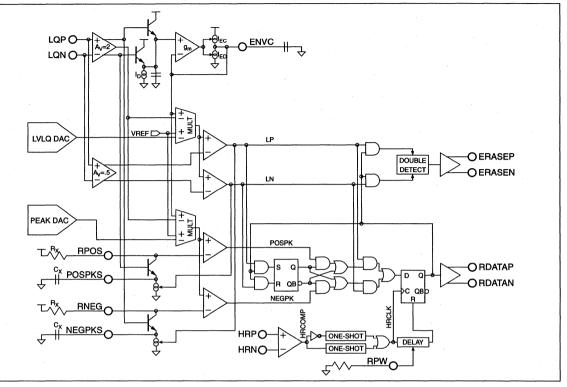

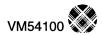

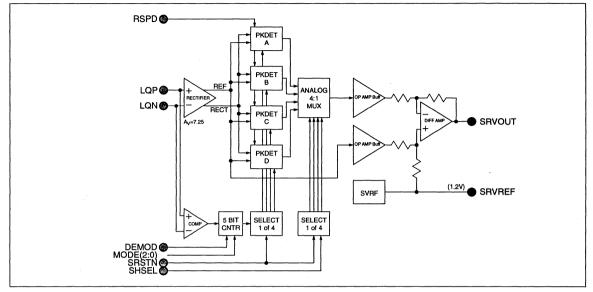

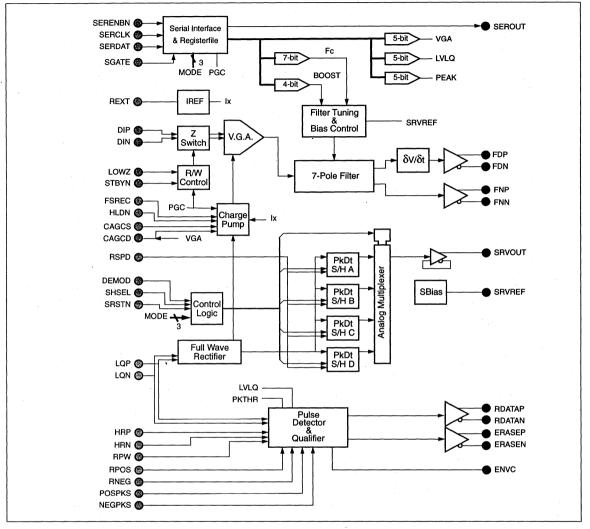

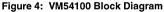

| VM54100 Complete 100Mbits/sec Peak Detection Read Channel                                                                                                                 | New    | 5-47  |

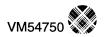

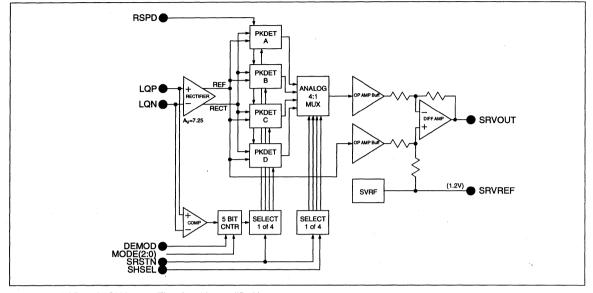

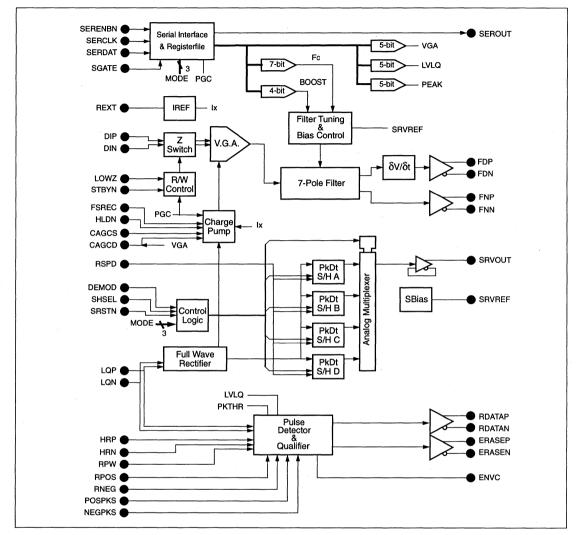

| VM54750 Pulse Detector With Filter and Servo Peak Detect, 75Mbits/sec                                                                                                     | New    | 5-71  |

| VM5603 (1,7) Encoder-Decoder with Write Precompensation, 64 Mbits/sec Transfer Rate                                                                                       |        | 5-95  |

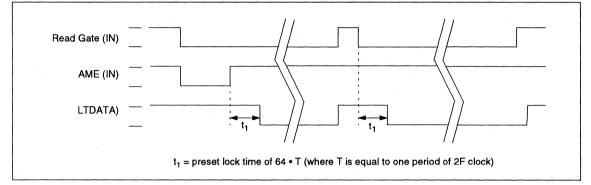

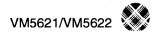

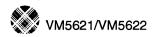

| VM5621/VM5622 (2,7) Encoder-Decoder, 48 Mbits/sec Transfer Rate                                                                                                           |        | 5-105 |

| VM5711 Frequency Synthesizer/Phase-Locked Loop, 64 Mbits/sec Transfer Rate, ZDR Compatible                                                                                |        | 5-111 |

| VM64110 110Mbits/sec, Analog Interface Device for a Sampled-Amplitude Read/Write Digital Channel                                                                          |        | 5-117 |

| VM8050 Digital Area Servo Detector                                                                                                                                        | .New   | 5-119 |

| Tape Drive Circuits                                                                                                                                                       |        |       |

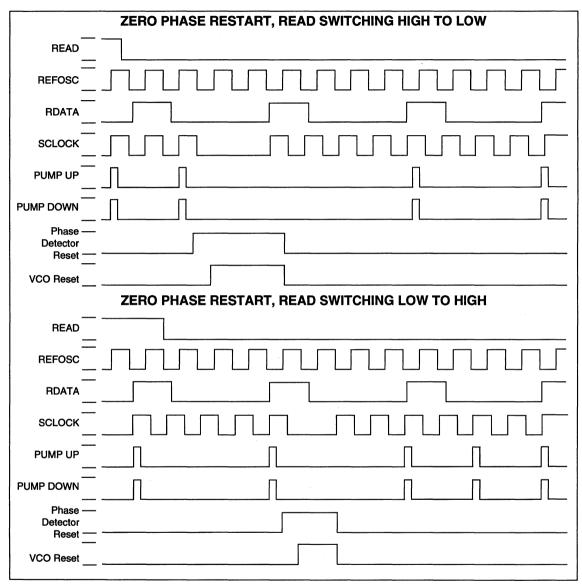

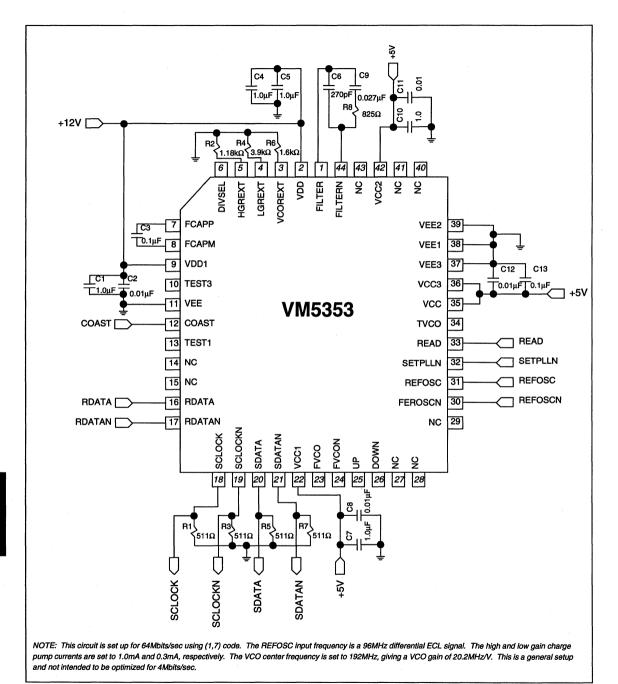

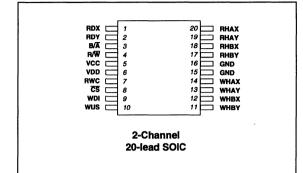

| VM5353 Data Separator, 64 Mbits/sec Transfer Rate, (1,7), (2,7), and (0,3) RLL codes, ZDR Compatible                                                                      |        |       |

| VT5204 2-Channel, High-Performance, Inductively Coupled Ferrite Head, Read/ Write Preamplifier                                                                            | .New   | 6-13  |

| Application Notes                                                                                                                                                         |        |       |

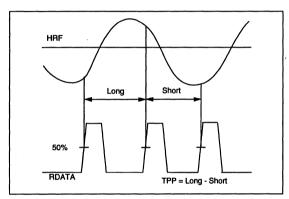

| Loop Filter Design for the VM5351/VM5352 and VM5353                                                                                                                       | •••••  | 7-3   |

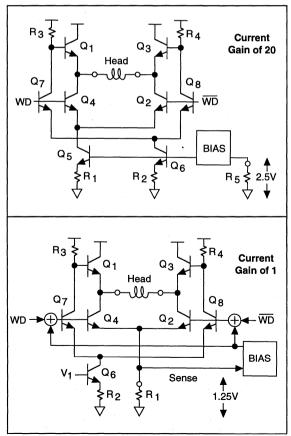

| Current Gain of 20 vs. Current Gain of 1 for 5-Volt Read/Write Preamplifiers                                                                                              | •••••• | 7-9   |

| Pulse Pairing in Read Channels                                                                                                                                            |        | 7-13  |

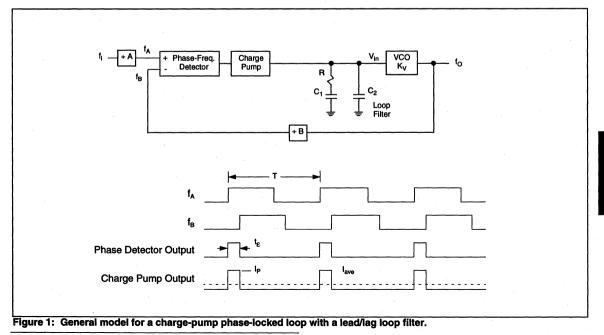

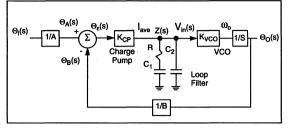

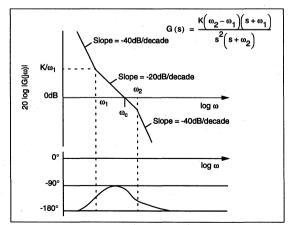

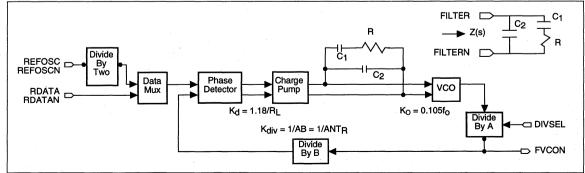

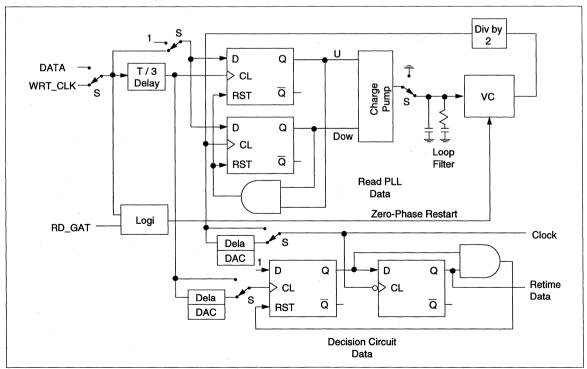

| Phase Lock Loop Application Note                                                                                                                                          |        | 7-17  |

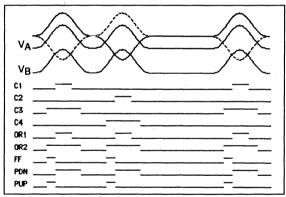

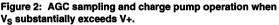

| Automatic Gain Control Technique for Hard Disk Drives                                                                                                                     |        | 7-33  |

| Packaging and Ordering                                                                                                                                                    |        |       |

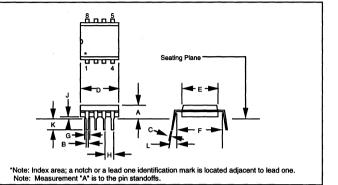

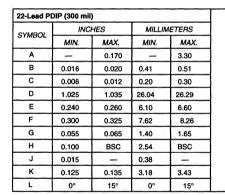

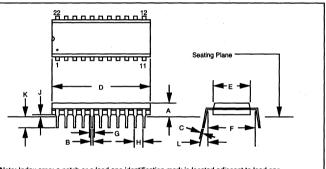

| Plastic Dual In-Line Package (PDIP)                                                                                                                                       |        | 8-3   |

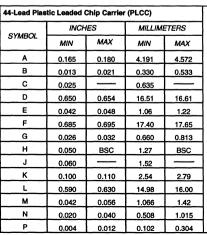

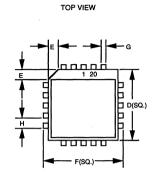

| Plastic Leaded Chip Carrier (PLCC)                                                                                                                                        |        | 8-4   |

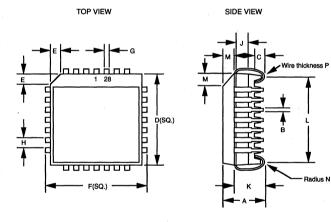

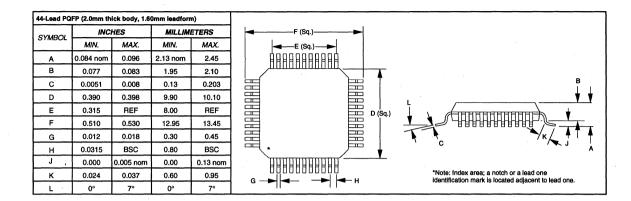

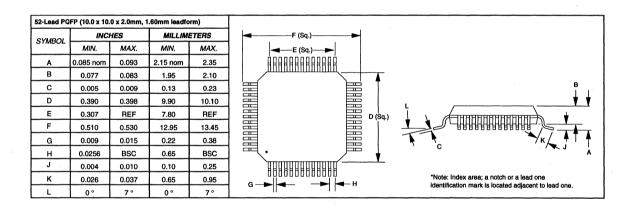

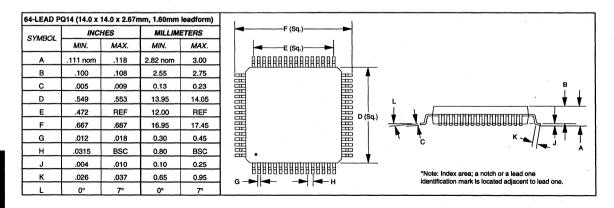

| Plastic Quad Flatpack (PQFP)                                                                                                                                              |        | 8-6   |

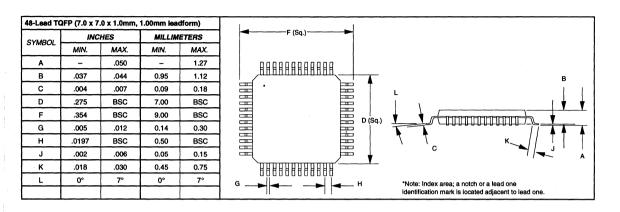

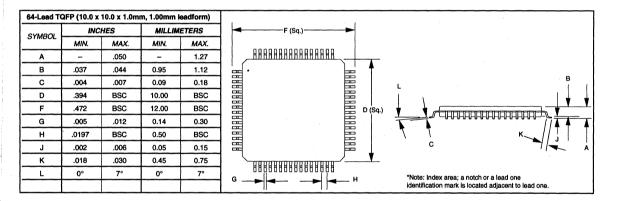

| Thin Quad Flatpack (TQFP)                                                                                                                                                 |        | 8-7   |

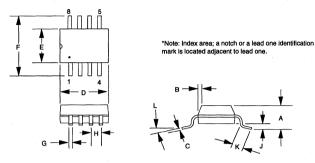

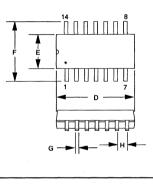

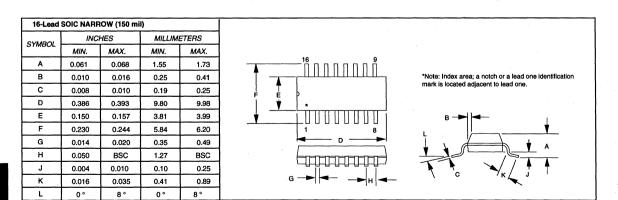

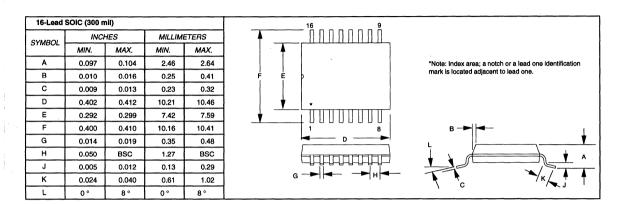

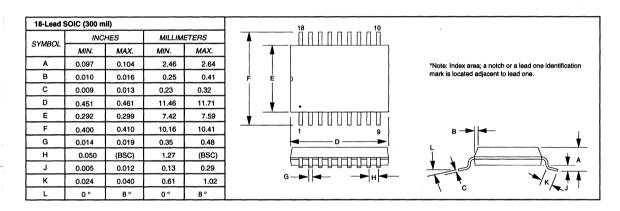

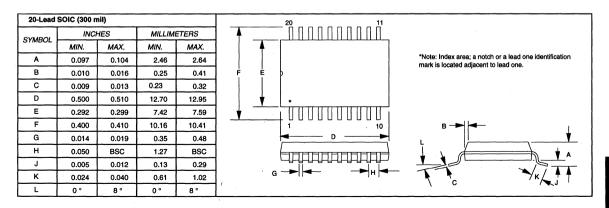

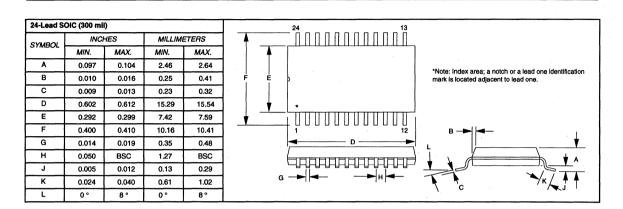

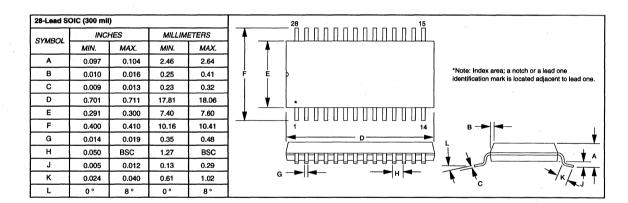

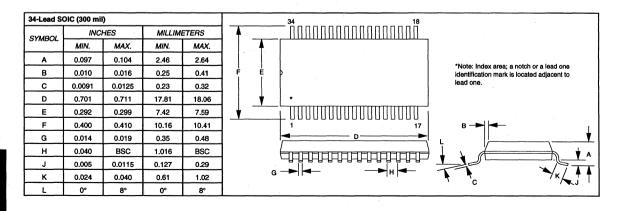

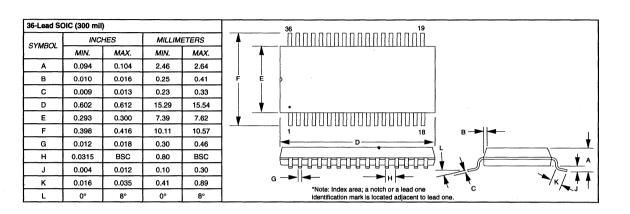

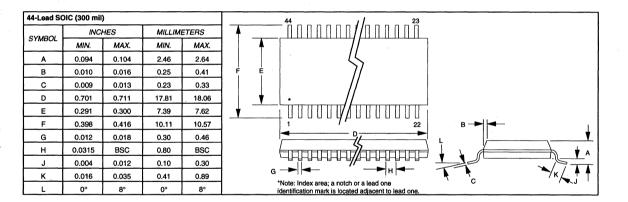

| Small Outline Integrated Circuit (SOIC)                                                                                                                                   |        | 8-8   |

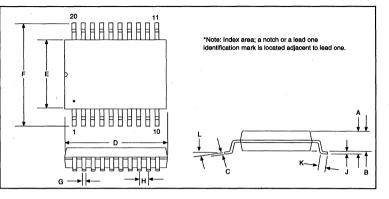

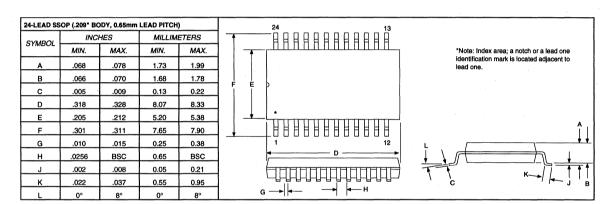

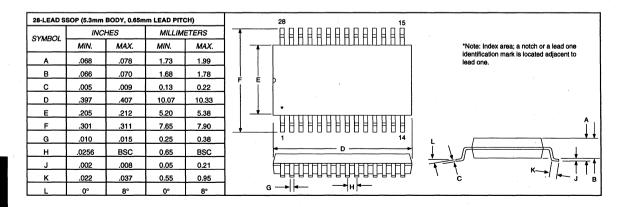

| Shrink Small Outline Package (SSOP)                                                                                                                                       |        | 8-12  |

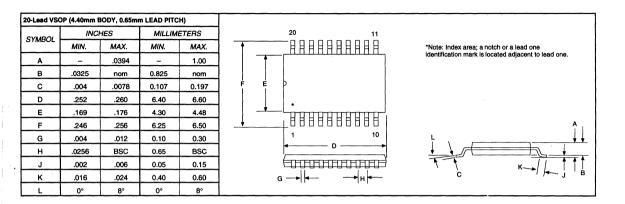

| Very Small Outline Package (VSOP)                                                                                                                                         |        | 8-13  |

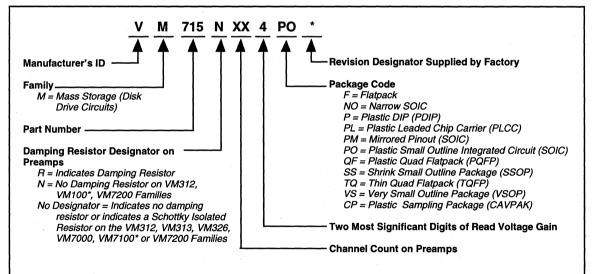

| Ordering Information                                                                                                                                                      |        | 8-14  |

| Discontinued Devices (please contact VTC for more information and device availability)                                                                                    |        |       |

| VM201 Low-Noise, Ferrite Head, Servo Preamplifier                                                                                                                         |        |       |

| VM214 4-Channel, Thin-Film Head, Read/Write Preamplifier<br>VM216 Thin-Film Head, Servo Preamplifier                                                                      |        |       |

| VM310R 6-Channel, Ferrite Head, Read/Write Preamplifier<br>VM311R 8-Channel, Ferrite Head, Read/Write Preamplifier                                                        |        |       |

| VM316R 10-Channel, Ferrite Head, Read/Write Preamplifier                                                                                                                  |        |       |

| VM326 10-Channel, High-Performance, Thin-Film Head, Read/Write Preamplifier<br>VM443 Read Data Pulse Qualifier                                                            |        |       |

| VM5317 Data Separator<br>VM5355 Zoned-Density Recording Data Separator                                                                                                    |        |       |

| VM5601 (1,7) Encoder-Decoder with Write Precompensation                                                                                                                   |        |       |

| VM5701 Frequency Synthesizer for Zoned-Density Recording<br>VM7120 2, 4, 6 or 8-Channel, TTL WDI, WC Gain = 1, Thin-Film or MIG Heads                                     |        |       |

| VM7140 2, 4 or 8-Channel, PECL WDI, WC Gain = 20, Thin-Film or MIG Heads<br>VM7200H 2, 4, 6 or 8-Channel, TTL WDI, A $\gamma$ = 275, WC Gain = 20, Thin-Film or MIG Heads |        |       |

| VM7230/VM7230N 2, 4, 6 or 8-Channel, TTL WDI, WC Gain = 1, Thin-Film or MIG Heads                                                                                         |        |       |

| VM7900 2 or 4-Channel, TTL WDI, Low C <sub>IN</sub> , Thin-Film or MIG Heads<br>VM327R 6, 7 or 10-Channel, +5V, +12V, TTL WDI, Ferrite or MIG Heads                       |        |       |

| VM347R 4 or 10-Channel, +5V, +12V, PECL WDI, Ferrite or MIG Heads                                                                                                         |        |       |

| VM357 4-Channel, +5V, +12V, PECL WDI, Servo Write, Ferrite or MIG Heads<br>VM305 Write/Servo Phase-Locked Oscillator                                                      |        |       |

| VM5622 (2,7) Encoder-Decoder, 48 Mbits/sec Transfer Rate<br>VM7301 ZDR Data Separator/Synthesizer/(1,7) Encoder-Decoder with Write Precompensation                        |        |       |

| VM7401 Pulse Detector/Servo Peak Detector                                                                                                                                 |        |       |

| VM75720/VM75722 Single Chip Data Recovery Channel, 72 Mbits/sec Data Transfer Rate, Single or Dual bit NRZ I/O<br>VM8001 Laser Power Amplifier                            |        |       |

| VM8101 Optical Read Preamplifier                                                                                                                                          |        | iii   |

|                                                                                                                                                                           |        |       |

### DATA SHEET AND PRODUCT DEFINITIONS

- Advance Information: This data sheet contains the design specifications for products in development. Specifications may change in any manner without notice. Typically this indicates first silicon has been evaluated, but not completely verified.

- **Preliminary:** This data sheet contains preliminary data. Supplementary data will be published at a later date. VTC reserves the right to make changes at any time without notice in order to improve design or enhance the product. Preliminary indicates the product is in the first production stage.

**No Identification:** This data sheet contains final specifications as confirmed through design, verification and device characterization. This device is in final production.

Although all VTC products have input and output circuits that protect against damage due to high static voltage or electrostatic fields, VTC still recommends following normal ESD precautions for handling semiconductor devices.

VTC Incorporated reserves the right to make changes to its products without notice in order to improve design, performance, function or reliability. VTC assumes no responsibility for use of any circuits described or represented other than the circuitry embodied in its products.

Copyright © 1994 VTC Inc. All Rights Reserved. Printed in USA.

DB007-6-Printed 994

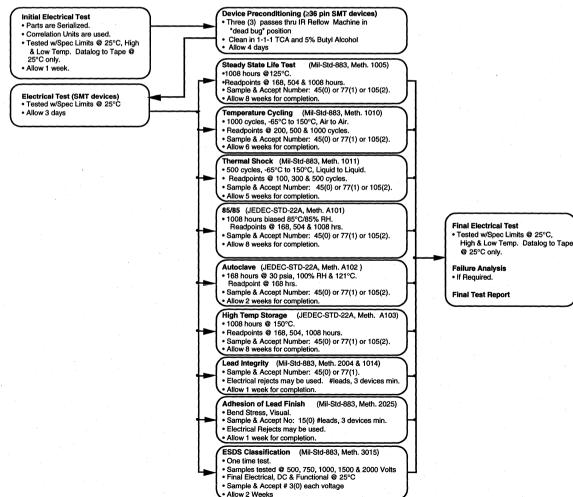

### QUALITY AND RELIABILITY ASSURANCE

VTC's quality journey encompasses every facet of its business from marketing to manufacturing.

VTC's objective is to establish industry standards for quality and reliability and to be recognized by its customers as a company dedicated to providing exceptional service with honesty and integrity.

VTC understands that success depends on the high quality of products, on the excellence of service provided to customers, and on the low cost of producing products. To meet the goals of quality, service and cost, VTC involves all its employees in a program of continuous improvement in the following ways:

- Employees are trained in the use of on-line and offline statistical process control tools, which enables them to understand and reduce variability in manufacturing processes with 6σ as a goal.

- Quality is designed into products and processes, thus eliminating dependence on quality inspections.

- Highly focused project teams use time-proven problem analysis and solution tools.

- PPM and qualification/ORT programs are used to monitor progress.

#### **Commercial Qualification Process**

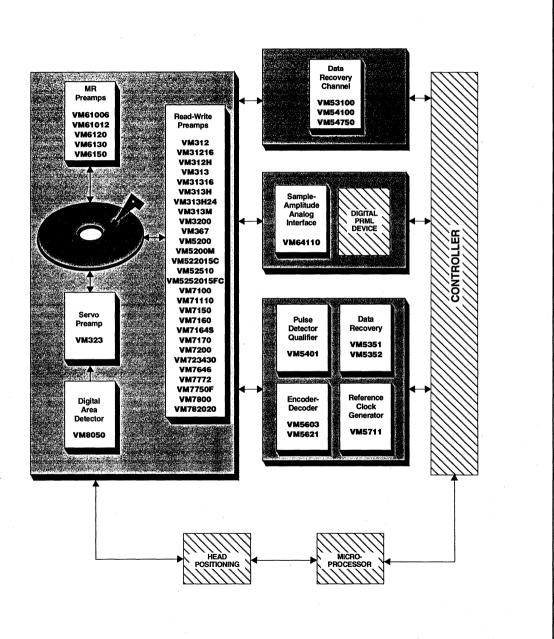

### THE VTC CHANNEL

vii

## **READ/WRITE PREAMPLFIERS SELECTOR GUIDE**

| Product                | Current<br>Revision | Pins | Package<br>Type | Channels | WDI  | Read Gain<br>(V/V) Typ. | Input Noise<br>(nV/√Hz) Max. | Input Cap.<br>(pF) Max. | Current Ga<br>(mA/mA) |

|------------------------|---------------------|------|-----------------|----------|------|-------------------------|------------------------------|-------------------------|-----------------------|

| HEAD                   |                     |      |                 |          |      |                         |                              |                         |                       |

| VM61006FTQJ            | Aug-94              | 64   | TQFP            | 6        | PECL | 350                     | 0.55                         | 10                      | 20                    |

| VM61006TQJ             | Aug-94              | 64   | TQFP            | 6        | PECL | 350                     | 0.55                         | 10                      | 20                    |

| VM61012XA              | Aug-94              |      | DIE             | 12       | PECL | 500                     | 0.55                         | 10                      | 20                    |

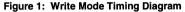

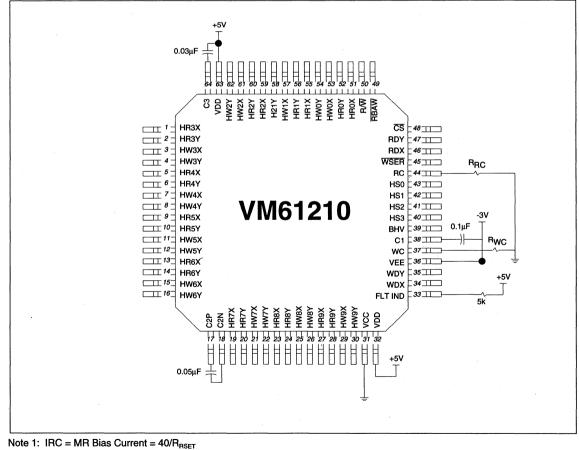

| VM61210FTQJ            | Aug-94              | 64   | TQFP            | 10       | PECL | 150                     | 0.65                         | 18                      | 20                    |

| VM61210FTQK            | Aug-94              | 64   | TQFP            | 10       | PECL | 150                     | 0.65                         | 18                      | 20                    |

| VM61210TQJ             | Aug-94              | 64   | TQFP            | 10       | PECL | 150                     | 0.65                         | 18                      | 20                    |

| VM61210TQK             | Aug-94              | 64   | TQFP            | 10       | PECL | 150                     | 0.65                         | 18                      | 20                    |

| VM61312FXC             | Aug-94              |      | DIE             | 12       | PECL | 350                     | 0.55                         | 10                      | 20                    |

| VM61312SXC             | Aug-94              |      | DIE             | 12       | PECL | 350                     | 0.95                         | 10                      | 20                    |

| VM61312XC              | Aug-94              |      | DIE             | 12       | PECL | 350                     | 0.55                         | 10                      | 20                    |

| REE-TERMIN             | AL                  |      |                 |          |      |                         |                              |                         |                       |

| VM367N425POK           | Aug-94              | 24   | SOIC            | 4        | TTL  | 250                     | 0.95                         | 22                      | 20                    |

| VM367N225PO20L         | Aug-94<br>Aug-94    | 24   | SOIC            | 2        | TTL  | 250                     | 0.95                         | 22                      | 20                    |

| VM367N225PO20L         | Aug-94<br>Aug-94    | 16   | SOIC            | 2        | TTL  | 200                     | 0.95                         | 22                      | 20                    |

| VM7002NOL              |                     | 16   | SOIC            | 2        | TTL  | 200                     | 0.85                         | 22                      | 20                    |

| VM7002POL<br>VM7004POL | Aug-94              | 20   | SOIC            | 4        | TTL  | 200                     | 0.85                         | 22                      | 20                    |

| VM7004POL<br>VM7004SSL | Aug-94              | 20   | SSOP            | 4        | TTL  | 200                     | 0.85                         | 22                      | 20                    |

|                        | Aug-94              | 20   | VSOP            | 4        | TTL  | 200                     | 0.85                         | 22                      | 20                    |

| VM7004VSL              | Aug-94              | 20   | VSOP            | 4        | 116  | 200                     | 0.85                         | 22                      | 20                    |

| <b>O-TERMINAL</b>      |                     | r .  |                 |          |      |                         |                              |                         | · · ·                 |

| VM31210PO36L           | Aug-94              | 52   | PQFP            | 16       | TTL  | 150                     | 0.8                          | 25                      | 1                     |

| VM31216QFL             | Aug-94              | 52   | PQFP            | 16       | TTL  | 150                     | 0.8                          | 25                      | 1                     |

| VM3126SSL              | Aug-94              | 28   | SSOP            | 6        | TTL  | 150                     | 0.8                          | 25                      | 1                     |

| VM3128PML              | Aug-94              | 34   | SOIC-Mirror     | 8        | TTL  | 150                     | 0.8                          | 25                      | 1                     |

| VM3128PO34L            | Aug-94              | 34   | SOIC            | 8        | TTL  | 150                     | 0.8                          | 25                      | 1                     |

| VM3129POL              | Aug-94              | 34   | SOIC            | 9        | TTL  | 150                     | 0.8                          | 25                      | 1                     |

| VM312H14PLL            | Aug-94              | 44   | PLCC            | 14       | TTL  | 250                     | 0.8                          | 25                      | 1                     |

| VM312H14POL            | Aug-94              | 44   | SOIC            | 14       | TTL  | 250                     | 0.8                          | 25                      | 1                     |

| VM312H14QFL            | Aug-94              | 44   | PQFP            | 14       | TTL  | 250                     | 0.8                          | 25                      | 1                     |

| VM31316QFJ             | Aug-94              | 52   | PQFP            | 16       | PECL | 150                     | 0.8                          | 25                      | 1                     |

| VM3139PO36L            | Aug-94              | 36   | SOIC            | 9        | PECL | 150                     | 0.8                          | 25                      | 1                     |

| VM3139PO36M            | Aug-94              | 36   | SOIC            | 9        | PECL | 150                     | 0.8                          | 25                      | 1                     |

| VM3139POL              | Aug-94              | 34   | SOIC            | 9        | PECL | 150                     | 0.8                          | 25                      | 1                     |

| VM313H13POL            | Aug-94              | 44   | SOIC            | 13       | PECL | 250                     | 0.8                          | 25                      | 1                     |

| VM313H14POL            | Aug-94              | 44   | SOIC            | 14       | PECL | 250                     | 0.8                          | 25                      | 1                     |

| VM3204POK              | Aug-94              | 20   | SOIC            | 4        | TTL  | 150,200,300             | 0.7                          | 20/12                   | 22                    |

| VM3204SSK              | Aug-94              | 20   | SSOP            | 4        | TTL  | 150,200,300             | 0.7                          | 20/12                   | 22                    |

| VM521015FPO36L         | Aug-94              | 36   | SOIC            | 10       | PECL | 150                     | 0.75                         | 18                      | 20                    |

| VM521015FTQL           | Aug-94              | 48   | TQFP            | 10       | PECL | 150                     | 0.75                         | 18                      | 20                    |

| VM521015PO36L          | Aug-94              | 36   | SOIC            | 10       | PECL | 150                     | 0.75                         | 18                      | 20                    |

| VM521015XC             | Aug-94              |      | DIE             | 10       | PECL | 150                     | 0.75                         | 18                      | 20                    |

| VM521420TQ64L          | Aug-94              | 64   | TQFP            | 14       | PECL | 200                     | 0.75                         | 18                      | 20                    |

| VM521420XC             | Aug-94              |      | DIE             | 14       | PECL | 200                     | 0.75                         | 18                      | 20                    |

| VM522015CTQL           | Aug-94              | 64   | TQFP            | 20       | PECL | 150                     | 0.8                          | 13                      | 20                    |

| VM522015FTQL           | Aug-94              | 64   | TQFP            | 20       | PECL | 150                     | 0.75                         | 18                      | 20                    |

| VM522015FTXC           | Aug-94              | 1    | DIE             | 20       | PECL | 150                     | 0.75                         | 18                      | 20                    |

| VM522015TQL            | Aug-94              | 64   | TQFP            | 20       | PECL | 150                     | 0.75                         | 18                      | 20                    |

| VM522015TXC            | Aug-94              | + .  | DIE             | 20       | PECL | 150                     | 0.75                         | 18                      | 20                    |

\*Based on typical head load.

| Write Current<br>Range (mA) | Write Voltage<br>(Vp-p) Min. | Damping<br>Resistor | Rise/Fall Time<br>L=0, R=0 (ns) Max. | Multiple Servo<br>Write | Head Induct.<br>Range (μΗ)   | Power<br>Supply | Recommend<br>New Design? |

|-----------------------------|------------------------------|---------------------|--------------------------------------|-------------------------|------------------------------|-----------------|--------------------------|

|                             |                              |                     |                                      |                         |                              |                 |                          |

| 10 - 30                     | 4.5                          | YES                 | 6*                                   | NO                      | 0.1 - 2                      | +5V; -4.5V      | YES                      |

| 10 - 30                     | 4.5                          | YES                 | 6*                                   | NO                      | 0.1 - 2                      | +5V; -4.5V      | YES                      |

| 10 - 30                     | 4.5                          | YES                 | 6*                                   | NO                      | 0.1 - 2                      | +5V; -4.5V      | YES                      |

| 20 - 40                     | 4.5                          | YES                 | 4*                                   | YES                     | 0.4 - 1                      | +5V; -3V        | YES                      |

| 20 - 40                     | 4.5                          | YES                 | 4*                                   | YES                     | 0.4 - 1                      | +5V; -3V        | YES                      |

| 20 - 40                     | 4.5                          | YES                 | 4*                                   | YES                     | 0.4 - 1                      | +5V; -3V        | YES                      |

| 20 - 40                     | 4.5                          | YES                 | 4*                                   | YES                     | 0.4 - 1                      | +5V; -3V        | YES                      |

| 20 - 40                     | 4.5                          | YES                 | 4*                                   | NO                      | 0.15 - 0.4                   | +5V; -4.5V      | YES                      |

| 20 - 40                     | 4.5                          | YES                 | 4*                                   | NO                      | 0.15 - 0.4                   | +5V; -4.5V      | YES                      |

| 20 - 40                     | 4.5                          | YES                 | 4*                                   | NO                      | 0.15 - 0.4                   | +5V; -4.5V      | YES                      |

|                             |                              | L                   |                                      | I I                     | 1*U*,m <sub>2</sub> ,U*,**** |                 |                          |

| 4 - 40                      | 10                           | NO                  | TBD                                  | YES                     | 1 - 10                       | +5V             | YES                      |

| 4 - 40                      | 10                           | NO                  | TBD                                  | YES                     | 1 - 10                       | +5V             | YES                      |

| 15 - 50                     | 4.8                          | YES                 | 10                                   | NO                      | 1 - 5                        | +5V             | YES                      |

| 15 - 50                     | 4.8                          | YES                 | 10                                   | NO                      | 1 - 5                        | +5V             | YES                      |

| 15 - 50                     | 4.8                          | YES                 | 10                                   | NO                      | 1 - 5                        | +5V             | YES                      |

| 15 - 50                     | 4.8                          | YES                 | 10                                   | NO                      | 1 - 5                        | +5V             | YES                      |

| 15 - 50                     | 4.8                          | YES                 | 10                                   | NO                      | 1-5                          | +5V             | YES                      |

|                             |                              |                     |                                      |                         |                              |                 |                          |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 5 - 40                      | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 10 - 40                     | 7                            | YES                 | 5                                    | NO                      | 0.2 - 3                      | +5V, +12V       | YES                      |

| 2 - 25                      | 4.5                          | YES                 | 6                                    | NO                      | 0.2 - 5                      | 3V - 5V         | YES                      |

| 2 - 25                      | 4.5                          | YES                 | 6                                    | NO                      | 0.2 - 5                      | 3V - 5V         | YES                      |

| 5 - 35                      | 9                            | OPTIONAL            | 2                                    | NO                      | 0.2 -1.5                     | +5V, +12V       | YES                      |

| 5 - 35                      | 9                            | OPTIONAL            | 2                                    | NO                      | 0.2 -1.5                     | +5V, +12V       | YES                      |

| 5 - 35                      | 9                            | OPTIONAL            | 2                                    | NO                      | 0.2 -1.5                     | +5V, +12V       | YES                      |

| 5 - 35                      | 9                            | OPTIONAL            | 2                                    | NO                      | 0.2 -1.5                     | +5V, +12V       | YES                      |

| 5 - 35                      | 9                            | OPTIONAL            | 2                                    | NO                      | 0.2 -1.5                     | +5V, +12V       | YES                      |

| 5 - 35                      | 9                            | OPTIONAL            | 2                                    | NO                      | 0.2 -1.5                     | +5V, +12V       | YES                      |

| 5 - 35                      | 9                            | OPTIONAL            | 2                                    | NO                      | 0.2 -1.5                     | +5V, +12V       | YES                      |

| 5 - 35                      | 9                            | OPTIONAL            | 2                                    | NO                      | 0.2 -1.5                     | +5V, +12V       | YES                      |

| 5 - 35                      | 9                            | OPTIONAL            | 2                                    | NO                      | 0.2 -1.5                     | +5V, +12V       | YES                      |

| 5 - 35                      | 9                            | OPTIONAL            | 2                                    | NO                      | 0.2 -1.5                     | +5V, +12V       | YES                      |

| 5 - 35                      | 9                            | OPTIONAL            | 2                                    | NO                      | 0.2 -1.5                     | +5V, +12V       | YES                      |

## **READ/WRITE PREAMPLFIERS SELECTOR GUIDE (continued)**

| Product                | Current<br>Revision | Pins     | Package<br>Type | Channels | WDI  | Read Gain<br>(V/V) Typ. | Input Noise<br>(nV/√Hz) Max. | Input Cap.<br>(pF) Max. | Current Gain<br>(mA/mA) |

|------------------------|---------------------|----------|-----------------|----------|------|-------------------------|------------------------------|-------------------------|-------------------------|

| VM710430POL            | Aug-94              | 16       | SOIC            | 4        | TTL  | 300                     | 0.75                         | 23                      | 20                      |

| VM710430SSL            | Aug-94              | 20       | SSOP            | 2        | TTL  | 300                     | 0.75                         | 23                      | 20                      |

| VM710430VSL            | Aug-94              | 20       | VSOP            | 4        | TTL  | 300                     | 0.75                         | 23                      | 20                      |

| VM7104POL              | Aug-94              | 20       | SOIC            | 4        | TTL  | 150 - 300               | 0.75                         | 23                      | 20                      |

| VM7104SSL              | Aug-94              | 20       | SSOP            | 4        | TTL  | 150 - 300               | 0.75                         | 23                      | 20                      |

| VM710630SSJ            | Aug-94              | 24       | SSOP            | 6        | TTL  | 300                     | 0.75                         | 23                      | 20                      |

| VM7108POL              | Aug-94              | 36       | SOIC            | 4        | TTL  | 150 - 300               | 0.75                         | 23                      | 20                      |

| VM711420POJ            | Aug-94              | 20       | SOIC            | 20       | TTL  | 200                     | 0.6                          | 15                      | 20                      |

| VM711420SSJ            | Aug-94              | 20       | SSOP            | 20       | TTL  | 200                     | 0.6                          | 15                      | 20                      |

| VM711420VSJ            | Aug-94              | 20       | VSOP            | 20       | TTL  | 200                     | 0.6                          | 15                      | 20                      |

| VM711620SSJ            | Aug-94              | 24       | SSOP            | 6        | TTL  | 200                     | 0.5                          | 15                      | 20                      |

| VM711630SSJ            | Aug-94              | 24       | SSOP            | 6        | TTL  | 300                     | 0.5                          | 15                      | 20                      |

| VM7124VSL              | Aug-94              | 20       | VSOP            | 4        | TTL  | 300                     | 0.75                         | 23                      | 1                       |

| VM7124VOL              | Aug-94              | 36       | SOIC            | 8        | TTL  | 300                     | 0.75                         | 23                      | 1                       |

| VM7142POL              | Aug-94              | 16       | SOIC            | 2        | PECL | 300                     | 0.75                         | 33                      | 20                      |

| VM7158POJ              | Aug-94              | 36       | SOIC            | 8        | PECL | 200 - 300               | 0.65                         | 18                      | 20                      |

| VM715N2POL             | Aug-94              | 16       | SOIC            | 2        | PECL | 200 - 300               | 0.65                         | 18                      | 20                      |

| VM715N4POK             | Aug-94              | 20       | SOIC            | 4        | PECL | 200 - 300               | 0.65                         | 18                      | 20                      |

| VM716430SPOK           | Aug-94              | 20       | SOIC            | 4        | TTL  | 300                     | 0.65                         | 18                      | 20                      |

| VM716430SSSK           | Aug-94              | 20       | SSOP            | 4        | TTL  | 300                     | 0.65                         | 18                      | 20                      |

| VM716430SVSK           | Aug-94              | 20       | VSOP            | 4        | TTL  | 300                     | 0.65                         | 18                      | 20                      |

| /M7164SSJ              |                     | 20       | SSOP            | 4        |      | 200 - 300               | 0.65                         | 23                      | 20                      |

|                        | Aug-94              |          | SOIC            | 8        |      | 200 - 300               | 0.65                         | 23                      |                         |

|                        | Aug-94              | 36       | SOIC            | 4        |      |                         |                              |                         | 20                      |

| VM7204POJ<br>VM7204SSJ | Aug-94              | 20<br>20 |                 |          |      | 200                     | 0.75                         | 23                      | 20                      |

|                        | Aug-94              | 20       | SSOP<br>VSOP    | 4        |      | 200                     | 0.75                         | 23                      | 20                      |

| VM7204VSJ              | Aug-94              |          |                 | 4        |      | 200                     | 0.75                         | 23                      | 20                      |

| VM7206SSJ              | Aug-94              | 28       | SSOP            | 6        |      | 200                     | 0.75                         | 23                      | 20                      |

| VM7208POJ              | Aug-94              | 36       | SOIC            | 8        |      | 200                     | 0.75                         | 23                      | 20                      |

| VM720H4POL             | Aug-94              | 20       | SOIC            | 4        | TTL  | 275                     | 0.75                         | 23                      | 20                      |

| VM720H8POJ             | Aug-94              | 16       | SOIC            | 8        | TTL  | 275                     | 0.75                         | 23                      | 20                      |

| VM723430POP            | Aug-94              | 20       | SOIC            | 4        | TTL  | 300                     | 0.75                         | 23                      | 1                       |

| VM723430SSP            | Aug-94              | 20       | SSOP            | 4        | TTL  | 300                     | 0.75                         | 23                      | 1                       |

| VM7238POJ              | Aug-94              | 36       | SOIC            | 8        | TTL  | 250                     | 0.75                         | 23                      | 1                       |

| VM775430FPOJ           | Aug-94              | 20       | SOIC            | 4        | PECL | 300                     | 0.65                         | 11                      | 20                      |

| VM775430FSSJ           | Aug-94              | 20       | SSOP            | 4        | PECL | 300                     | 0.65                         | 11                      | 20                      |

| VM775630FSSJ           | Aug-94              | 24       | SSOP            | 6        | PECL | 300                     | 0.65                         | 13                      | 20                      |

| VM780420POJ            | Aug-94              | 20       | SOIC            | 4        | PECL | 200                     | 0.65                         | 15                      | 20                      |

| VM780620SSJ            | Aug-94              | 24       | SSOP            | 6        | PECL | 200                     | 0.65                         | 15                      | 20                      |

| VM781020XB             | Aug-94              |          | DIE             | 10       | PECL | 200                     | 0.65                         | 15                      | 20                      |

| VM782020TQJ            | Aug-94              | 64       | TQFP            | 20       | PECL | 200                     | 0.65                         | 15                      | 20                      |

| /M782020XA             | Aug-94              | 64       | DIE             | 20       | PECL | 200                     | 0.65                         | 15                      | 20                      |

| M7851015XB             | Aug-94              |          | DIE             | 10       | PECL | 150                     | 0.65                         | 15                      | 20                      |

| M7851020POK            | Aug-94              | 36       | SOIC            | 10       | PECL | 200                     | 0.65                         | 15                      | 20                      |

| VM7851020XB            | Aug-94              |          | DIE             | 10       | PECL | 200                     | 0.65                         | 15                      | 20                      |

| VM785420POJ            | Aug-94              | 20       | SOIC            | 4        | PECL | 200                     | 0.65                         | 15                      | 20                      |

| VM785437FPOJ           | Aug-94              | 20       | SOIC            | 4        | PECL | 270                     | 0.65                         | 15                      | 20                      |

| VM785620SSJ            | Aug-94              | 24       | SSOP            | 6        | PECL | 200                     | 0.65                         | 15                      | 20                      |

| VM785620XA             | Aug-94              |          | DIE             | 6        | PECL | 200                     | 0.65                         | 15                      | 20                      |

| VM785820POK            | Aug-94              | 36       | SOIC            | 8        | PECL | 200                     | 0.65                         | 15                      | 20                      |

| Write Current<br>Range (mA) | Write Voltage<br>(Vp-p) Min. | Damping<br>Resistor | Rise/Fall Time<br>L=0, R=0 (ns) Max. | Multiple Servo<br>Write | Head Induct.<br>Range (µH) | Power<br>Supply | Recommend<br>New Design? |

|-----------------------------|------------------------------|---------------------|--------------------------------------|-------------------------|----------------------------|-----------------|--------------------------|

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.2 - 5                    | +5V             | NO                       |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.2 - 5                    | +5V             | NO                       |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.2 - 5                    | +5V             | NO                       |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.2 - 5                    | +5V             | NO                       |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.2 - 5                    | +5V             | NO                       |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.2 - 5                    | +5V             | NO                       |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.2 - 5                    | +5V             | YES                      |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.7 - 5                    | +5V             | YES                      |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.7 - 5                    | +5V             | YES                      |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.7 - 5                    | +5V             | YES                      |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.7 - 5                    | +5V             | YES                      |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.7 - 5                    | +5V             | YES                      |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.2 - 5                    | +5V             | YES                      |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.2 - 5                    | +5V             | YES                      |

| 1 - 40                      | 4.5                          | OPTIONAL            | 6                                    | NO                      | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 4                            | OPTIONAL            | 6                                    | YES                     | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 4                            | OPTIONAL            | 6                                    | YES                     | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 4                            | OPTIONAL            | 6                                    | YES                     | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 4                            | YES                 | 6                                    | YES                     | 0.7 - 5                    | +5V             | YES                      |

| 5 - 35                      | 4                            | YES                 | 6                                    | YES                     | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 4                            | YES                 | 6                                    | YES                     | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 4                            | OPTIONAL            | 6                                    | YES                     | 0.2 - 5                    | +5V<br>+5V      | YES                      |

| 5 - 35                      | 4 4                          | OPTIONAL            | 6                                    | YES                     | 0.2 - 5                    | +5V<br>+5V      | YES                      |

|                             | 4 4                          |                     | 8                                    | NO                      | 0.2 - 3                    | +5V<br>+5V      | NO                       |

| 10 - 40                     | 4                            | YES                 | 8                                    | NO                      | 0.2 - 10                   | +5V<br>+5V      | NO                       |

| 10 - 40                     | 4                            | YES                 |                                      |                         |                            |                 | NO                       |

| 10 - 40                     |                              | YES                 | 8                                    | NO                      | 0.2 - 10                   | +5V             |                          |

| 10 - 40                     | 4                            | YES                 | 8                                    | NO                      | 0.2 - 10                   | +5V             | NO                       |

| 10 - 40                     | 4                            | YES                 | 8                                    | NO                      | 0.2 - 10                   | +5V             | NO                       |

| 10 - 40                     | 4                            | YES                 | 8                                    | NO                      | 0.2 - 10                   | +5V             | NO                       |

| 10 - 40                     | 4                            | YES                 | 8                                    | NO                      | 0.2 - 10                   | +5V             | NO                       |

| 10 - 40                     | 4                            | YES                 | 8                                    | NO                      | 0.2 - 10                   | +5V             | NO                       |

| 10 - 40                     | 4                            | YES                 | 8                                    | NO                      | 0.2 - 10                   | +5V             | NO                       |

| 10 - 40                     | 4                            | YES                 | 8                                    | NO                      | 0.2 - 10                   | +5V             | NO                       |

| 5 - 20                      | 5.7                          | OPTIONAL            | 4                                    | YES                     | 0.2 - 10                   | +5V             | YES                      |

| 5 - 20                      | 5.7                          | OPTIONAL            | 4                                    | YES                     | 0.2 - 10                   | +5V             | YES                      |

| 5 - 20                      | 5.7                          | OPTIONAL            | 4                                    | YES                     | 0.2 - 10                   | +5V             | YES                      |

| 5 - 35                      | 7.8                          | YES                 | 4                                    | NO                      | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 7.8                          | YES                 | 4                                    | NO                      | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 7.8                          | YES                 | 4                                    | NO                      | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 7.8                          | YES                 | 4                                    | NO                      | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 7.8                          | YES                 | 4                                    | NO                      | 0.2 - 5                    | ∔5V             | YES                      |

| 5 - 35                      | 7.8                          | YES                 | 4                                    | YES                     | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 7.8                          | YES                 | 4                                    | NO                      | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 7.8                          | YES                 | 4                                    | YES                     | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 7.8                          | YES                 | 4                                    | YES                     | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 7.8                          | YES                 | 4                                    | YES                     | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 7.8                          | YES                 | 4                                    | YES                     | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 7.8                          | YES                 | 4                                    | YES                     | 0.2 - 5                    | +5V             | YES                      |

| 5 - 35                      | 7.8                          | YES                 | 4                                    | YES                     | 0.2 - 5                    | +5V             | YES                      |

## **CHANNEL CIRCUITS SELECTOR GUIDE**

|            | Current  |      | Package | Functional                       | Power            | Maximum       |

|------------|----------|------|---------|----------------------------------|------------------|---------------|

| Product    | Revision | Pins | Туре    | Description                      | Supply           | Transfer Rate |

| VM53100QFL | Aug-94   | 64   | PQFP    | Data Separator Channel           | ±5V              | 105 Mbits/sec |

| VM5351PLL  | Aug-94   | 44   | PLCC    | Data Separator                   | ±5V              | 64 Mbits/sec  |

| VM5352PLK  | Aug-94   | 44   | PLCC    | Data Separator                   | ±5V              | 64 Mbits/sec  |

| VM5401PLL  | Aug-94   | 44   | PLCC    | Pulse Detector/Qualifier         | ±5V or +5V, +12V | 64 Mbits/sec  |

| VM54100QFJ | Aug-94   | 44   | PQFP    | Peak Detection Read Channel      | +5V              | 105 Mbits/sec |

| VM54750QFJ | Aug-94   | 52   | PQFP    | Pulse Detector/Servo Peak Detect | +5V              | 75 Mbits/sec  |

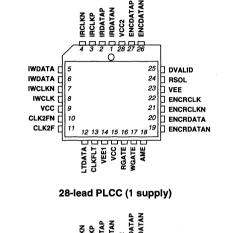

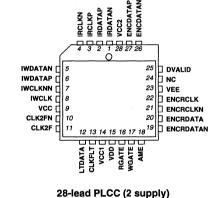

| VM5603PLK  | Aug-94   | 28   | PLCC    | (1,7) Encoder-Decoder            | +5V              | 64 Mbits/sec  |

| VM5621PLL  | Aug-94   | 28   | PLCC    | (2,7) Encoder-Decoder            | +5V              | 48 Mbits/sec  |

| VM5622PLJ  | Aug-94   | 28   | PLCC    | (2,7) Encoder-Decoder            | ±5V              | 48 Mbits/sec  |

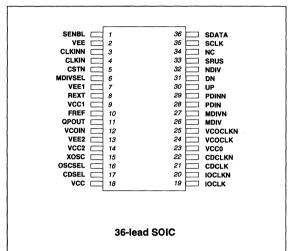

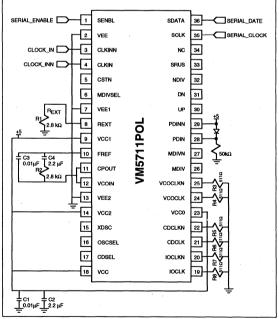

| VM5711POL  | Aug-94   | 36   | SOIC    | Frequency Synthesizer            | +5V              | 64 Mbits/sec  |

| VM64110QHL | Aug-94   | 64   | PQFP    | Analog PRML Front End            | +5V              | 110 Mbits/sec |

| VM8050PLL  | Aug-94   | 28   | PLCC    | Digital Area Detector            | +5V              | N/A           |

## TAPE DRIVE CIRCUITS SELECTOR GUIDE

|                       | Current |      | Package | Functional                                   | Power     | Maximum       |  |

|-----------------------|---------|------|---------|----------------------------------------------|-----------|---------------|--|

| Product Revision Pins |         | Pins | Туре    | Description Supply                           |           | Transfer Rate |  |

| VM5353PLL             | Aug-94  | 44   | PLCC    | Data Separator                               | +5V, +12V | 64 Mbits/sec  |  |

| VM5353QFL             | Aug-94  | 44   | PQFP    | Data Separator                               | +5V, +12V | 64 Mbits/sec  |  |

| VT520424FPOJ          | Aug-94  | 20   | SOIC    | Inductively Coupled, Read/Write Preamplifier | +5V, +12V | N/A           |  |

| VT520424POJ           | Aug-94  | 20   | SOIC    | Inductively Coupled, Read/Write Preamplifier | +5V, +12V | N/A           |  |

| VT520437POJ           | Aug-94  | 20   | SOIC    | Inductively Coupled, Read/Write Preamplifier | +5V, +12V | N/A           |  |

| Product Features                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                       |

| 33 to 105 Mbits/sec Transfer Rate, (1,7) and (2,7) RLL Codes, ZDR Compatible, Marginalization                                         |

| 30 to 64 Mbits/sec Transfer Rate, (1,7) and (2,7) RLL Codes, ZDR Compatible, Marginalization                                          |

| 30 to 64 Mbits/sec Transfer Rate, (1,7) and (2,7) RLL Codes, ZDR Compatible, Marginalization                                          |

| 24 to 64 Mbits/sec Transfer Rate, Erase Feature, Qualifies based on Zero Crossing, Amplitude, Slope and Polarity                      |

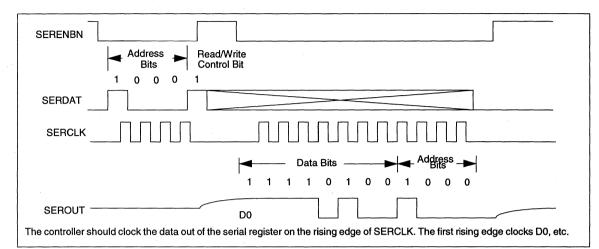

| 33 to 105 Mbits/sec Transfer Rate, Serial Interface for Programmability, Dual AGC, Dual Filter for Data and Servo Patterns            |

| 24 to 75 Mbits/sec Transfer Rate, Dual AGC Mode, Dual Filter for Data and Servo Patterns                                              |

| 10 to 64 Mbits/sec Transfer Rate, (1,7) Encoder-Decoder, ZDR Compatible, Write Precompensation                                        |

| 10 to 48 Mbits/sec Transfer Rate, (2,7) Encoder-Decoder, ZDR Compatible, Write Precompensation                                        |

| 10 to 48 Mbits/sec Transfer Rate, (2,7) Encoder-Decoder, ZDR Compatible, Write Precompensation                                        |

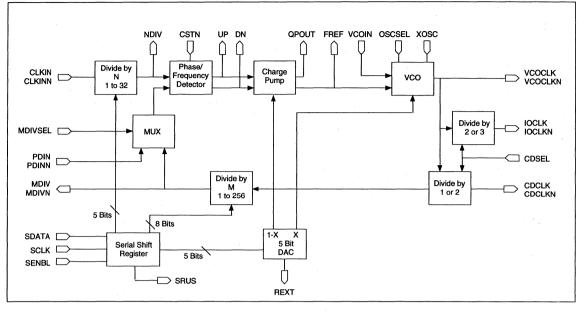

| 64 Mbits/sec Transfer Rate, VCO Frequency Range 40 to 200 MHz, ZDR Compatible                                                         |

| 16 to 110 Mbits/sec Transfer Rate, (1,7) RLL, 120 M-Sample/sec Flash ADC, Write Precompensation, Quadrature Servo, Active Filter, ZDR |

| Analog to Digital Conversion of Servo Data for Digital Servo Applications                                                             |

| Product Features                                                                                          |

|-----------------------------------------------------------------------------------------------------------|

| 30 to 64 Mbits/sec Transfer Rate, (1,7), (2,7) and (0,3) RLL Codes, ZDR Compatible, Marginalization       |

| 30 to 64 Mbits/sec Transfer Rate, (1,7), (2,7) and (0,3) RLL Codes, ZDR Compatible, Marginalization       |

| High-Performance, Read/Write Preamplifier Designed for a Helical-Scan Head, Gain = 240, Without Flip-Flop |

| High-Performance, Read/Write Preamplifier Designed for a Helical-Scan Head, Gain = 240, With Flip-Flop    |

| High-Performance, ReadWrite Preamplifier Designed for a Helical-Scan Head, Gain = 375, With Flip-Flop     |

## Sections

## **1** MR Preamplifiers

| VM61006<br>6-Channel, PECL WDI, MR Head     |      |

|---------------------------------------------|------|

| VM61012<br>12-Channel, PECL WDI, MR Head .  |      |

| VM61210<br>10-Channel, PECL WDI, MR Head .  |      |

| VM61312<br>12-Channel, PECL WDI, MR Head .  |      |

| VM6150<br>4 or 8-Channel, PECL WDI, MR Head | 1-41 |

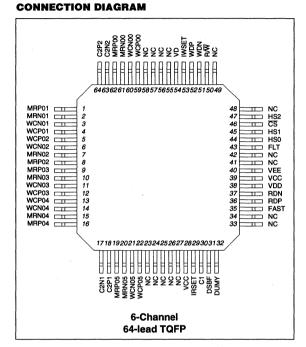

# VM61006

### 6-CHANNEL, HIGH-PERFORMANCE, MAGNETO-RESISTIVE HEAD, READ/WRITE PREAMPLIFIER

PRELIMINARY

#### FEATURES

- Read Gain = 350 V/V

- MR Bias Current Range = 8 20 mA

- Low Input Noise = 0.55 nV/√Hz Maximum

- Write Current Range = 10 30 mA

- Head Inductance Range = 100 700 nH

- Low Idle Power = 116 mW Maximum

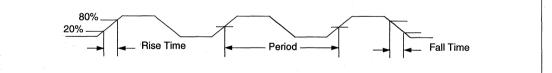

- Rise Time = 5 ns Typical

- Power Supply Fault Protection

- +5V, -4.5V Power Supplies

- · Write Unsafe Detection

- Head-to-Disk Contact Monitor

- Mask-Selectable Write Damping Resistor

- Reduced Mode and Head Selection Delays in FAST Mode

- · Disk Voltage Monitor

- Differential PECL Write Data Inputs

- · Current Sense Configuration

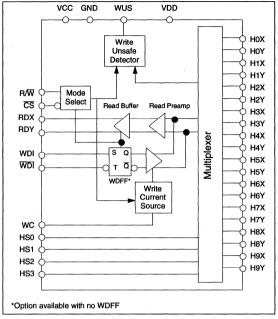

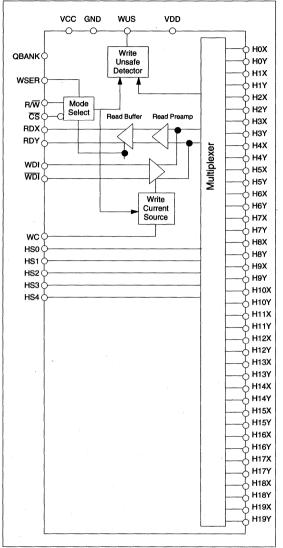

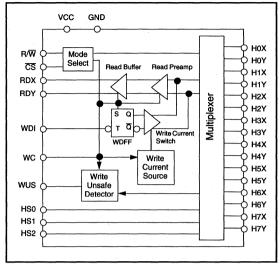

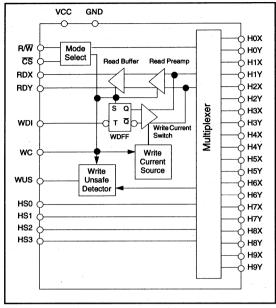

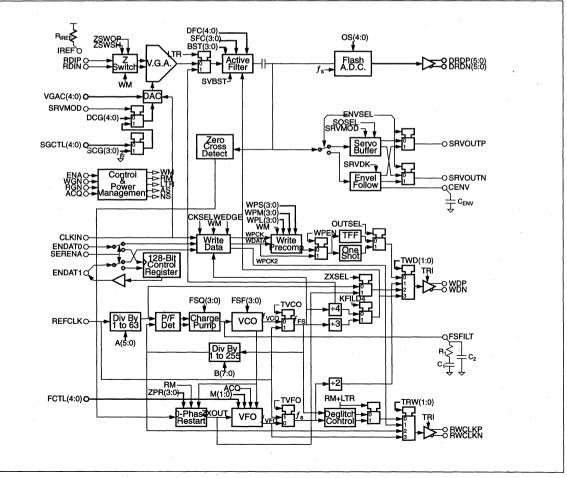

#### **FUNCTIONAL DESCRIPTION**

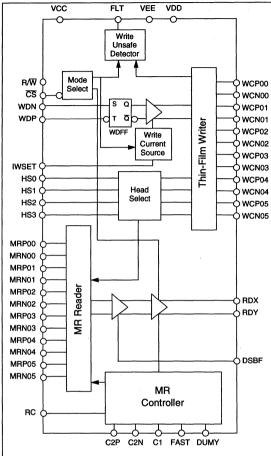

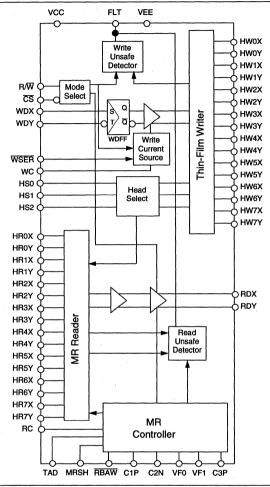

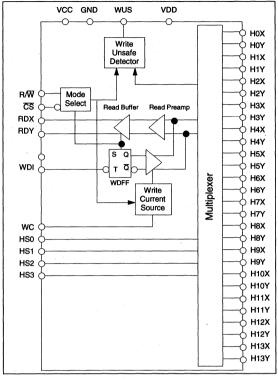

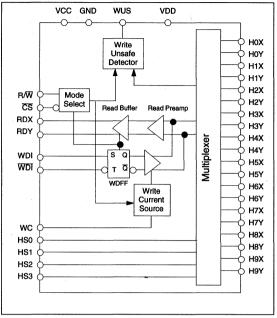

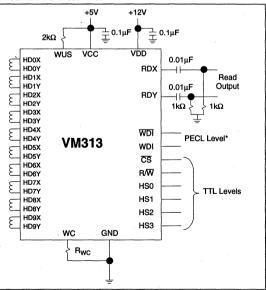

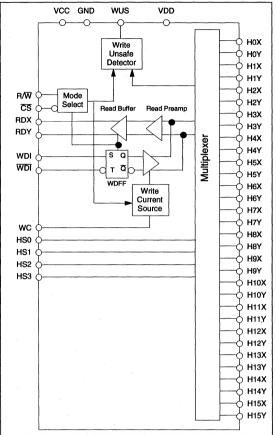

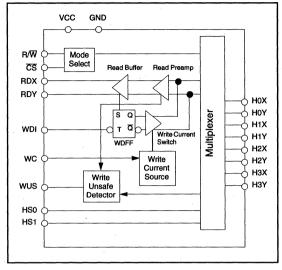

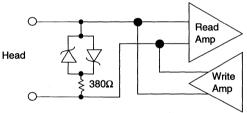

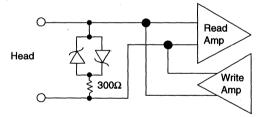

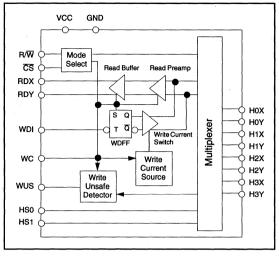

The VM61006 is an integrated bipolar read/write preamplifier designed for use in high-performance hard disk drive applications using 4-terminal magneto-resistive (MR) recording heads. The VM6100 contains a thin-film head writer, an MR reader and associated fault circuitry to address up to six heads. It also provides bias current and control loops for setting the DC voltages on the MR element.

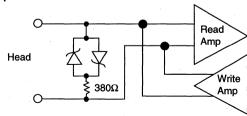

The VM61006 has two modes of operation. In read mode, the device operates as a low-noise differential preamplifier which senses resistance changes in the MR element that correspond to flux changes on the disk. The amplitude of the sense current is set either by an external resistor or by a current source and has a current gain of 20 mA/mA. In write mode, the circuit operates as a thin-film head write current switch, driving the thin-film write element of the MR head. The write current is externally programmed either by a resistor or an external current source and has a current gain of 20 mA/mA.

Fault protection is provided so during power sequencing, voltage faults or an invalid head select, the write current generator is disabled protecting the disk from potential transients. For added data protection, internal pull-up resistors are connected to the mode select lines,  $\overline{CS}$  and R/W, to prevent accidental writing due to open lines and to ensure the device will power-up in a non-writing condition.

The VM61006 operates from a +5V, -4.5V power supply. Low power dissipation is achieved through the use of high-speed bipolar processing and innovative circuit design techniques. When deselected, the device enters a sleep mode which reduces the power dissipation to only 116mW.

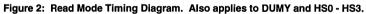

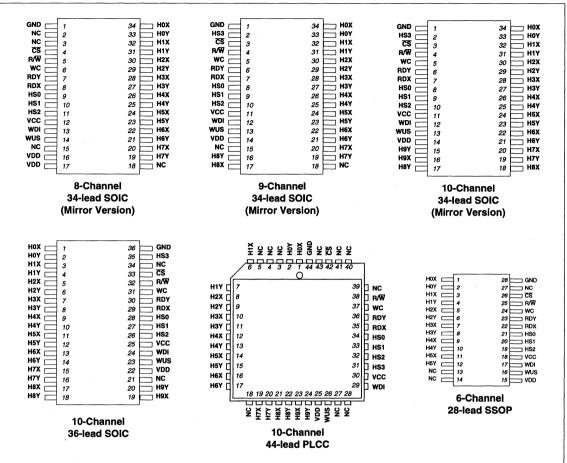

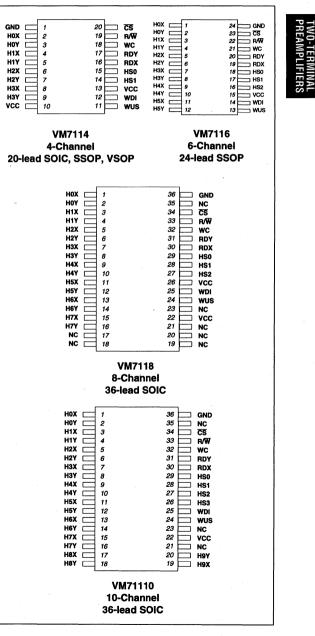

The VM61006 is available in a variety of package options, as well as die. Please consult VTC for details.

#### **ABSOLUTE MAXIMUM RATINGS**

Power Supply Voltage:

| V <sub>DD</sub>                    | -0.3V to + 7V                    |

|------------------------------------|----------------------------------|

| V <sub>EE</sub>                    | 7V to +0.3V                      |

| Input Voltages:                    |                                  |

| Digital Input Voltage VIN          | 0.3V to (V <sub>DD</sub> + 0.3V) |

| Storage Temperature Tsto           | 65° to 150°C                     |

|                                    | 150°C                            |

| Thermal Impedance, $\Theta_{JA}$ : |                                  |

#### **RECOMMENDED OPERATING CONDITIONS**

Power Supply Voltage:

| V <sub>DD</sub>                     | +5V±10%      |

|-------------------------------------|--------------|

|                                     | 4.5V ± 10%   |

| Junction Temperature T <sub>J</sub> | 0°C to 125°C |

August, 1994

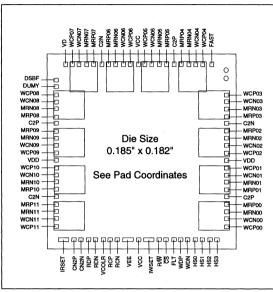

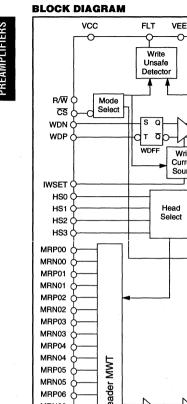

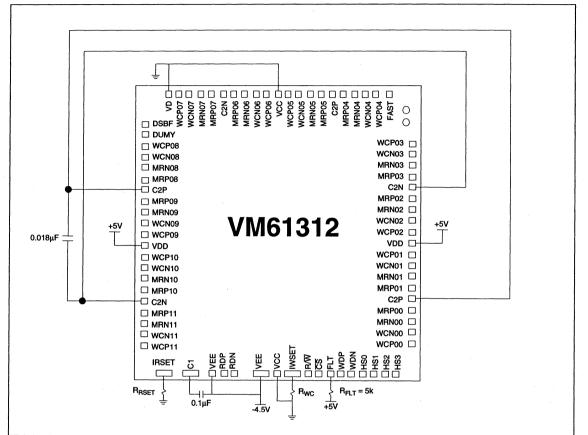

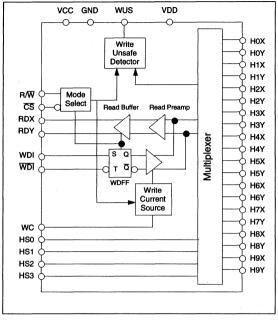

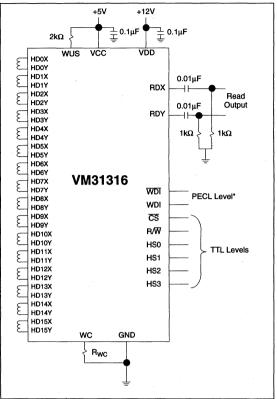

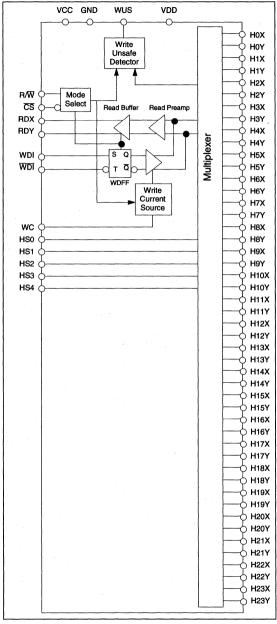

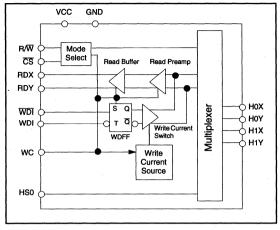

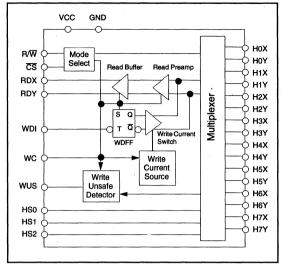

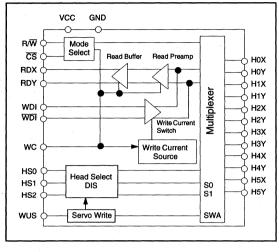

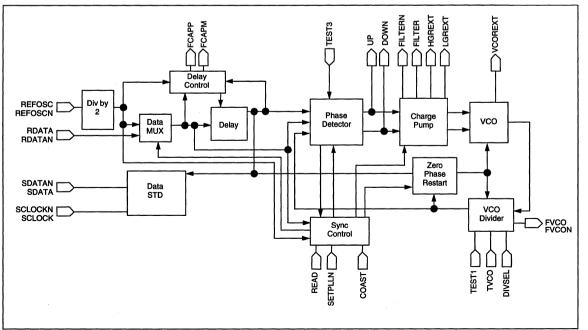

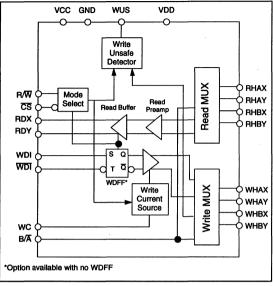

#### **BLOCK DIAGRAM**

#### **CIRCUIT OPERATION**

In all modes of operation, the VM61006 controls the common mode potential of all MR elements. This is necessary because the MR element cannot be insulated, so that a small voltage differential will cause arcing to the disk and damage the heads. Head voltages are held within ±250mV of the voltage on the VD pin, which monitors the disk potential of the drive. Thus, the disk may be grounded, as is done in disk drives having conventional thin film or ferrite recording heads, or isolated as the application may require.

In read mode, the VM61006 activates the MR bias current source, which then drives the selected MR element. The read bias current magnitude is determined by an external resistor connected between the IRSET pin and VCC. An internally-generated 2.5 volt reference is present at the IRSET pin. The magnitude of the MR bias current is:

$$I_{MR} = 50/R_{RSET}$$

(eq.

where R<sub>RSET</sub> is the resistor connected at IRSET.

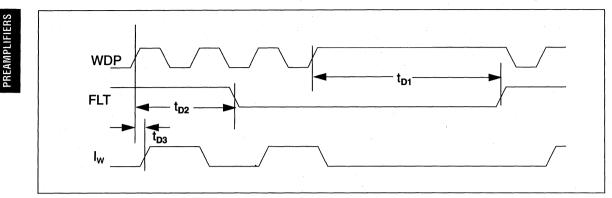

The fault output pin, FLT, is high to indicate a non-fault condition. If the voltage drops below a certain threshold on either supply, FLT will be pulled low to indicate a fault. Also, if a headto-disk contact occurs, the thermal asperity in the MR element will result in an abnormally high readback signal, which is monitored by detection circuitry and will be also flagged by a low FLT output.

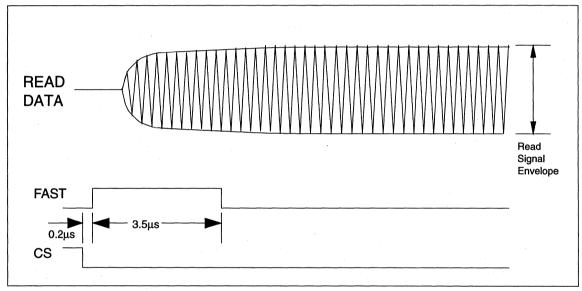

The read preamplifier is activated and connected to the selected head. The write current source and write unsafe detection circuitry is deactivated. RDP and RDN outputs are emitter follower and are in phase with the MRP and MRN head ports. These outputs should be AC-coupled to the load. The output common mode voltage is maintained in the write mode, thereby substantially reducing the write-to-read recovery delay in the subsequent pulse detection circuitry.

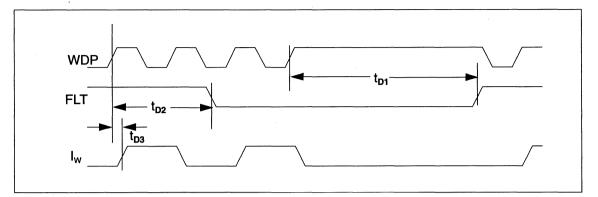

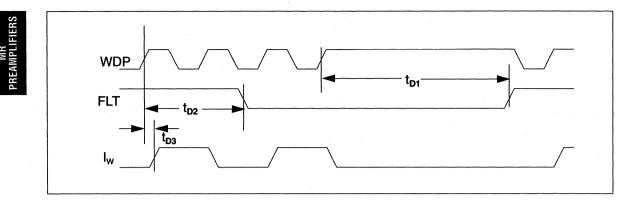

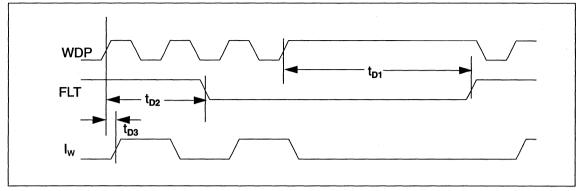

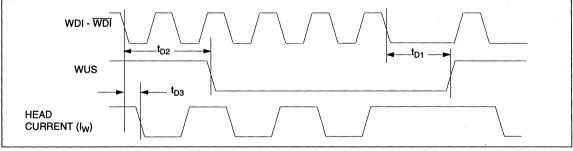

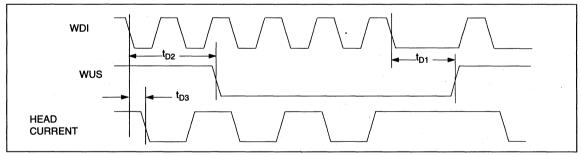

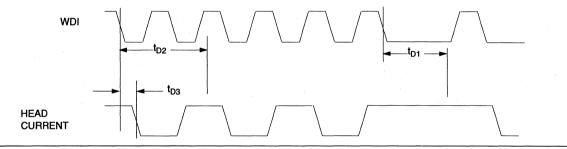

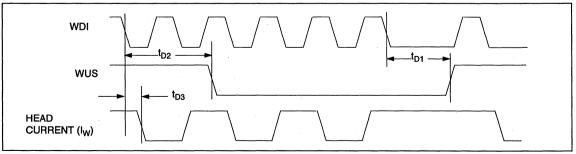

In write mode, the preamplifier is shut off and the VM6100 is converted to a current switch. However, MR bias current is maintained in order to minimize the write-to-read delay. The write current source is activated and drives the thin film element of the selected head. The polarity of the current is initially into the WCN port following a read-to-write transition. Write current polarity is reversed on low-to-high transitions of the write data input (WDP low-to-high). Circuitry is activated to detect various fault conditions. If any of the faults occur, they will be flagged as a high voltage output on the FLT pin. In addition, if a VDD fault occurs, the write current source is deactivated in order to protect recorded data.

The write current magnitude is determined by an external resistor connected between the IWSET pin and VCC. An internally-generated 2.5 volt reference is present at the IWSET pin. The magnitude of the write current (0-peak) is:

$$I_{W} = 50 / \left[ R_{W} \times \left( 1 + \frac{R_{H}}{R_{D}} \right) \right]$$

(eq. 2)

where  $R_W$  is the resistor connected at IWSET,  $R_H$  is the series resistance of the head, and  $R_D$  is an internal damping resistor of 360 $\Omega$ .

Power supply fault protection provides data security by disabling the write current generator during a VDD fault or powerup/down. The writer is independent of VEE, so VEE faults do not affect it. Additionally, the write unsafe circuitry will flag any of the conditions below as a high level on the open collector output pin FLT. Two positive transitions of write data may be required to clear the fault after the safe condition is restored.

- No write current

- Open write head

1)

- Write Data frequency too low

- Device in read or idle mode

- · Head shorted to ground

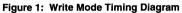

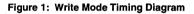

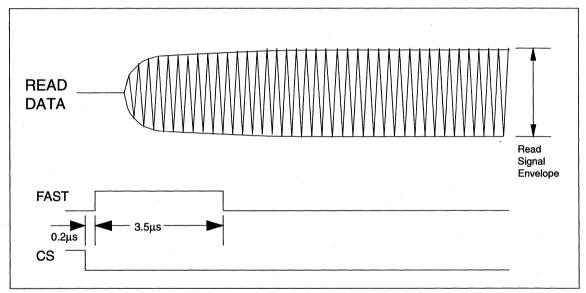

Fast mode is utilized during head-to-head and idle-to-read transitions. When the FAST mode pin is high, the unity-gain frequency of the offset control loop is increased such that it is inside the passband of the reader, allowing the delay to be reduced to less than 5µs. This pin must be brought low before read data is valid.

A DUMY mode pin allows the selection of a dummy head in read or write mode. MR bias current is routed to an internal resistor, and the write current source is deactivated. This mode

is optionally used during power-up/down and following head-todisk contacts. When the DUMY pin is high, the write current source is disabled to protect recorded data. An internal pull-up resistor is provided in event of an accidental open. If this pin is not used it should be grounded for normal operation.

In idle mode, the MR bias and write current sources are deactivated, and the device enters a low-power mode in which power dissipation is less than 116mW. Write and read fault detection circuitry is disabled. MR common mode and offset control loops still receive power in order to reduce idle-to-read mode recovery.

Mode control and head selection are accomplished via  $\overline{CS}$ ,  $R/\overline{W}$ , and HS0-2 pins. Internal pull-up resistors are provided on  $\overline{CS}$  and  $R/\overline{W}$  pins to force the device into a non-writing condition if either control line is opened accidentally. In addition, invalid head select codes disable the writer and select head MR00. Truth tables for mode and head selection are shown in Table 1 and Table 2, respectively.

Table 1: Mode Select Logic

| R/₩ | CS | MODE  |

|-----|----|-------|

| 0   | 0  | Write |

| 1   | 0  | Read  |

| Х   | 1  | ldle  |

#### **Table 2: Head Select Logic**

| HS2 | HS1 | HS0 | DUMY | HEAD |

|-----|-----|-----|------|------|

| Х   | Х   | х   | 1    | DUMY |

| 0   | 0   | 0   | 0    | 00   |

| 0   | 0   | 1   | 0    | 01   |

| 0   | 1   | 0   | 0    | 02   |

| 0   | 1   | 1   | 0    | 03   |

| 1   | 0   | 0   | 0    | 04   |

| 1   | 0   | 1   | 0    | 05   |

| 1   | 1   | Х   | 0    | DUMY |

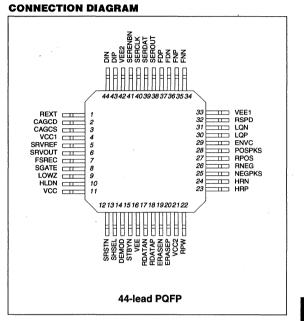

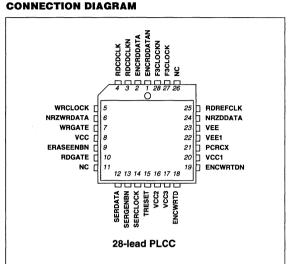

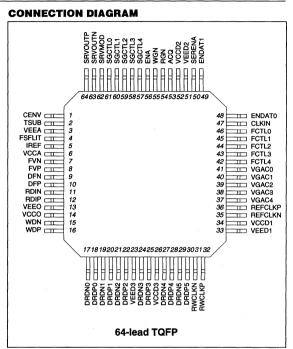

#### **PIN\_FUNCTION LIST AND DESCRIPTION**

| 1)  | CS          | (I)  | Chip select: a low level enables the device.                                                                         |

|-----|-------------|------|----------------------------------------------------------------------------------------------------------------------|

| 2)  | R∕₩         | (I*) | Read/Write: a high level<br>enables read mode.                                                                       |

| 3)  | HS0-HS2     | (I*) | Head Select: selects one of the twelve heads.                                                                        |

| 4)  | DUMY        | (I*) | A high level enables the dumy mode.                                                                                  |

| 5)  | FAST        | (I*) | A high level enables fast settling of the reader.                                                                    |

| 6)  | FLT         | (O*) | Write/Read Fault: A high level<br>indicates a fault in write mode.<br>A low level indicates a fault in<br>read mode. |

| 7)  | WDP, WDN    | (I*) | Differential Pseudo-ECL write<br>data in: a positive edge on<br>WDP toggles the direction of<br>the head current.    |

| 8)  | MRP00-MRP05 | (I)  | MR head connections, positive end.                                                                                   |