| 486<br>PC/AT-COMPATIBLE<br>SYSTEM<br>CONTROLLER |

|-------------------------------------------------|

| VL82C486<br>DATA MANUAL                         |

|                                                 |

Desktop Systems Division June 1992

ADVANCE INFORMATION

| 486<br>PC/AT-COMPATIBLE<br>SYSTEM<br>CONTROLLER |

|-------------------------------------------------|

| VL82C486<br>DATA MANUAL                         |

|                                                 |

|                                                 |

|                                                 |

|                                                 |

Desktop Systems Division June 1992

# ADVANCE INFORMATION

The information contained in this document has been carefully checked and is believed to be reliable. However, VLSI Technology, Inc., (VLSI) makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon, it. VLSI does not guarantee that the use of any information contained herein will not infringe upon the patent, trademark, copyright, mask work right or other rights of third parties, and no patent or other license is implied hereby.

This document does not in any way extend VLSI's warranty on any product beyond that set forth in its standard terms and conditions of sale. VLSI Technology, Inc., reserves the right to make changes in the products or specifications, or both, presented in this publication at any time and without notice.

#### LIFE SUPPORT APPLICATIONS

VLSI Technology, Inc., products are not intended for use as critical components in life support appliances, devices, or systems in which the failure of a VLSI product to perform could be expected to result in personal injury. © 1992 VLSI Technology, Inc. Printed in U.S.A.

This manual provides the reader with a preliminary technical reference for VLSI Technology, Inc.'s VL82C486 Single Chip 486 (SC486<sup>™</sup>) System Controller device for use in PC/AT-compatible applications. If you should require performance or functions not included in this manual, please contact your local VLSI Technology Design Center or Sales Office. The addresses are listed on the last page of this manual.

Since computer technology is extremely fast-moving, it is planned that VLSI's Personal Computer Products Division will revise, update, and publish this manual often. This will allow timely publication of data on new products, as well as improvements on existing ones. The most current information may also be obtained from your local VLSI Technology, Inc. Sales Office, Representative, or the Personal Computer Division in Tempe, Arizona.

Readers are encouraged to send their comments, corrections, or suggestions to:

Director, Marketing Communications VLSI Technology, Inc. 8375 South River Parkway Tempe, AZ 85284

# TABLE OF CONTENTS

| Item                                             | Numb |

|--------------------------------------------------|------|

| FEATURES                                         |      |

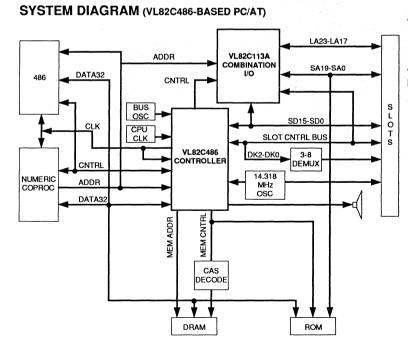

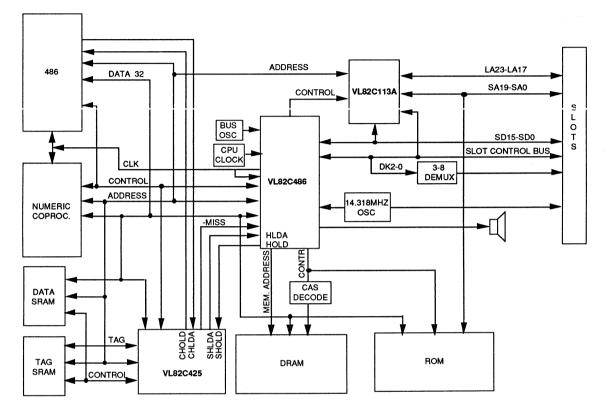

| VL82C486-BASED PC/AT SYSTEM DIAGRAM              | 1    |

| ORDER INFORMATION                                |      |

| DESCRIPTION                                      |      |

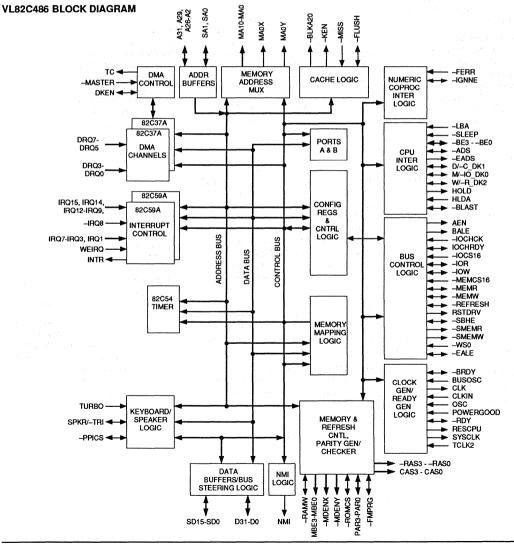

| VL82C486 BLOCK DIAGRAM                           |      |

| OVERVIEW                                         |      |

|                                                  |      |

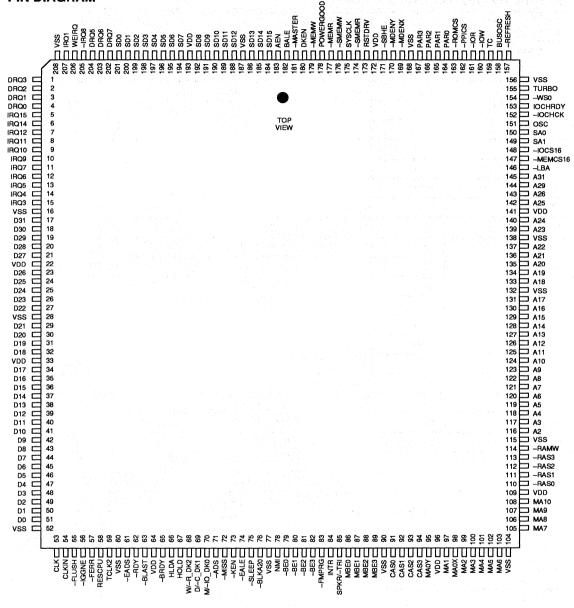

| PIN DIAGRAM                                      |      |

| PIN TYPE BY OPERATIONAL STATE                    | 5    |

| SIGNAL DESCRIPTIONS                              | 9    |

| FUNCTIONAL DESCRIPTION                           | 17   |

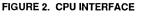

| CPU INTERFACE                                    |      |

| Overview                                         |      |

| Bus Cycle Decoder                                |      |

| Interrupt Acknowledge                            |      |

| Special Bus Cycle - Shutdown                     |      |

| Special Bus Cycle - Flush                        |      |

| Special Bus Cycle - Halt                         |      |

| Special Bus Cycle - Write-back<br>I/O Read/Write |      |

| Code Read                                        |      |

| Memory Read/Write                                |      |

| Byte Enables (–BE3 - –BE0)                       |      |

| Ready Control                                    |      |

| Primary Cache Control                            |      |

| Cacheability Control                             | 20   |

| Invalidation Control                             |      |

| Local Bus Aribitration                           |      |

| Numeric Coprocessor Support                      |      |

| Numeric Error Reporting for 486DX and 487SX      |      |

| Weitek Coprocessor Support                       |      |

| CPU Reset<br>CPU Self-Test Request               |      |

|                                                  |      |

| I/O AND MEMORY MAPPING                           |      |

| Overview                                         |      |

| 0n-Chip I/O                                      |      |

| ISA Bus I/O                                      |      |

| 10/16 Address Decode                             |      |

| Memory Mapping                                   | 24   |

| Local DRAM                                       |      |

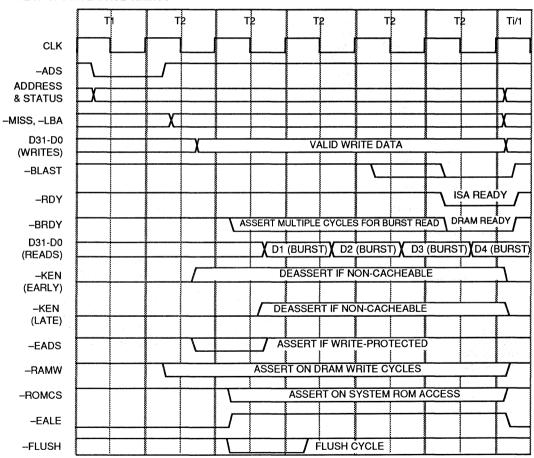

| Shadow RAM                                       |      |

| Segment Cacheability Registers                   | 27   |

| Programmed Memory Region Registers               |      |

| ISA Memory                                       |      |

| System ROM Memory Mapping                        |      |

| Configuration                                    |      |

| ROM Relocation                                   |      |

# TABLE OF CONTENTS

# Item

| FUNCTI | ONAL DESCRIPTION (Cont.)                                    |    |

|--------|-------------------------------------------------------------|----|

|        | Flash Memory Support                                        | 31 |

|        | Middle BIOS Switch-Out                                      |    |

|        | ROM Control Register (ROMSET)                               |    |

|        | LOCAL BUS PERIPHERAL SUPPORT                                |    |

|        | CPU Access to Local Bus Devices                             |    |

|        | Fixed Local Bus Memory Regions                              |    |

|        | Programmable Local Bus Memory Address Regions               |    |

|        | -LBA Pin                                                    |    |

|        | DMA and Master Mode/Local Bus Memory Transfers              |    |

| 1      | DRAM CONTROLLER                                             |    |

|        | Overview                                                    |    |

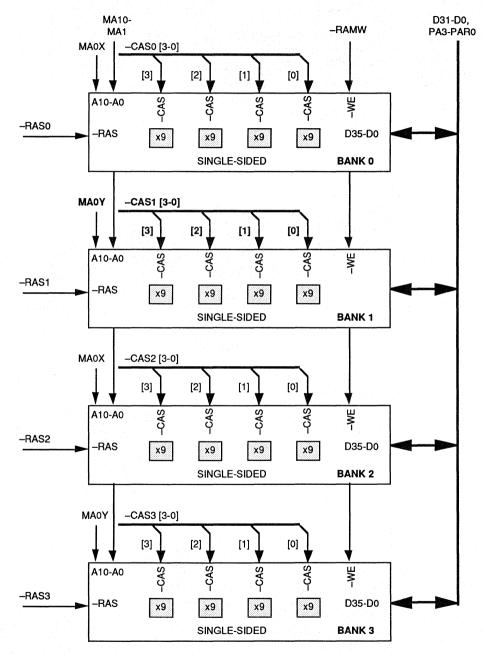

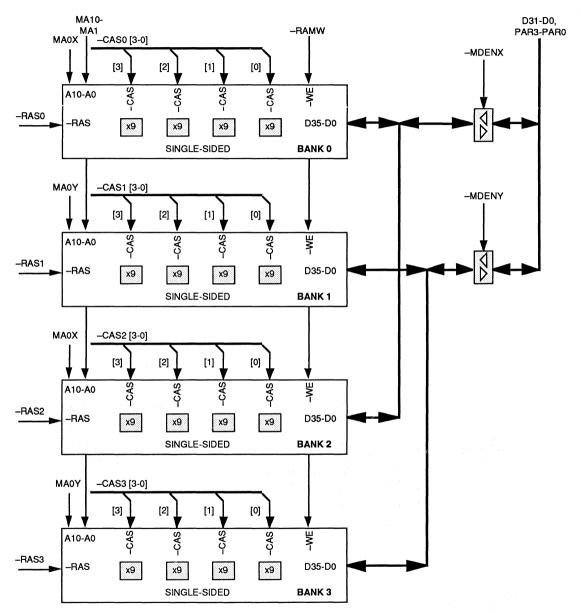

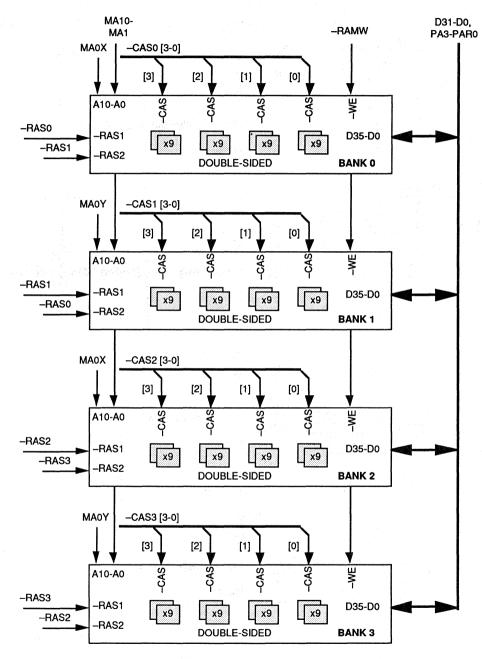

|        | Physical Configurations                                     | 34 |

|        | Configuration A                                             | 34 |

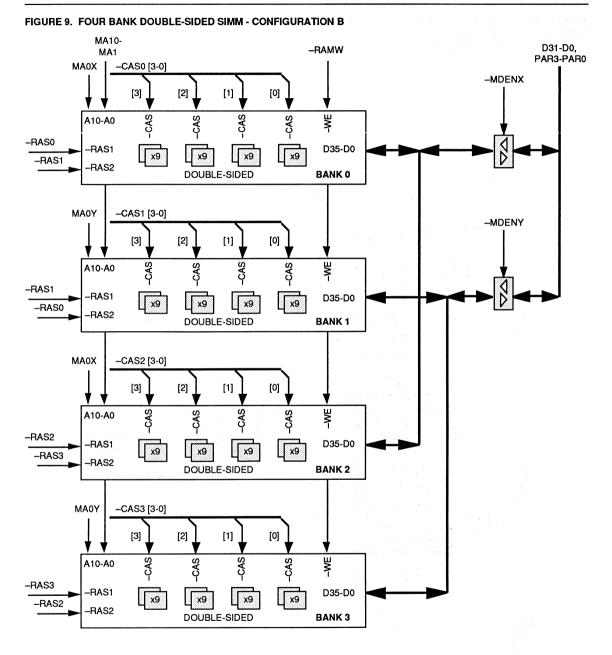

|        | Configuration B                                             | 34 |

|        | Double-Sided SIMM Support                                   |    |

|        | DRAM Physical Configuration Registers                       | 35 |

|        | DRAM Memory Maps                                            | 35 |

|        | Overview                                                    |    |

|        | Interleave Mode Selection                                   | 35 |

|        | Bank Start Address                                          |    |

|        | -RAS Strobe Decode                                          | 36 |

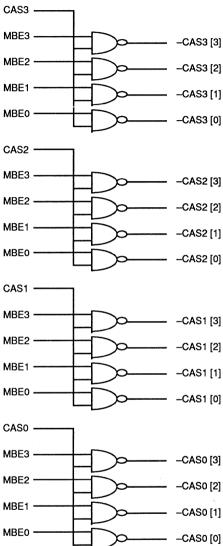

|        | CAS Strobe Decode                                           |    |

|        | DRAM Memory Addressing                                      |    |

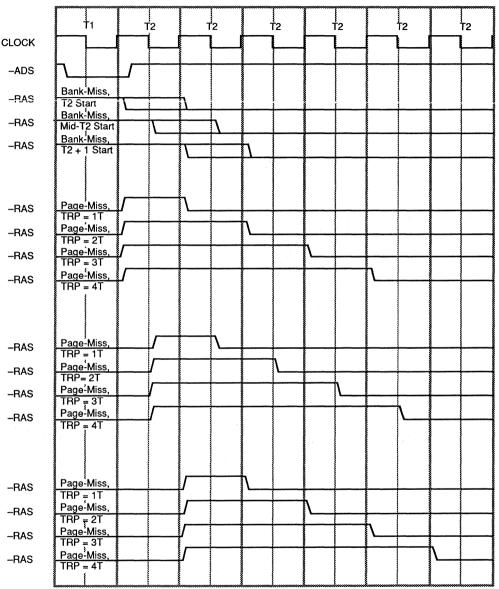

|        | DRAM Interface Operation for CPU Accesses                   |    |

|        | Overview                                                    |    |

|        | DRAM Programmable Timing                                    |    |

|        | Page Mode Operation                                         |    |

|        | Page Mode –RAS Time-Out                                     |    |

|        | -RAS Timing                                                 |    |

|        | -RAS Conditional Wait States                                |    |

|        | RAS-to-CAS Timing                                           |    |

|        | CAS Page-Hit Timing                                         |    |

|        | CAS Conditional Wait States                                 |    |

|        | CAS Burst Sequencing                                        |    |

|        | -BRDY Timing                                                |    |

|        | –MDENX, –MDENY Timing                                       |    |

|        | MA Bus Timing                                               |    |

|        | MA0X, MA0Y, and MA1 Operation During Burst Reads and Writes |    |

|        | Burst Read and Write Cycle Wait States                      |    |

|        | Write Cycle Wait States                                     |    |

|        | DRAM DMA Master Mode Cycle Operation                        |    |

|        | DRAM Refresh                                                |    |

|        | DRAM Speed Requirements                                     |    |

|        | DRAM Parity Generation and Detection                        |    |

|        | DRAM Control Registers                                      |    |

|        | RAMSET                                                      |    |

|        | NTBREF                                                      |    |

|        | MISCSET DRAM Control Bits                                   | 57 |

# TABLE OF CONTENTS

# Item

| FUNCTIONAL DESCRIPTION (Cont.)         |    |

|----------------------------------------|----|

| SECONDARY CACHE SUPPORT                |    |

| Cache Interface                        |    |

| Write-Through Cache Opertion           |    |

| Write-Back Cache Support               |    |

| Write-Back and Flush Instructions      | 58 |

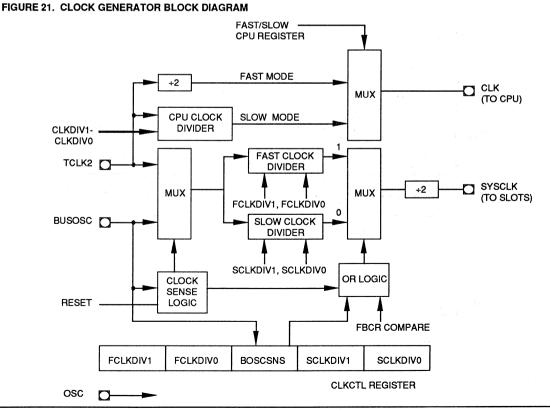

| CLOCK GENERATION                       | 61 |

| Clock Signal Definition                |    |

| Programmable AT Bus Clock              |    |

| SYSCLK Derived from BUSOSC             |    |

| SYSCLK Derived from TCLK2              |    |

| Fast Bus Clock Region (FBCR)           |    |

| Power-On Reset Configuration           |    |

| AT Bus Clock Frequency Summary         |    |

| CPU Clock (CLK) Frequency Control      |    |

| Clock Control Register (CLKCTL)        |    |

| TURBO/NON-TURBO MODE CONTROL           | 65 |

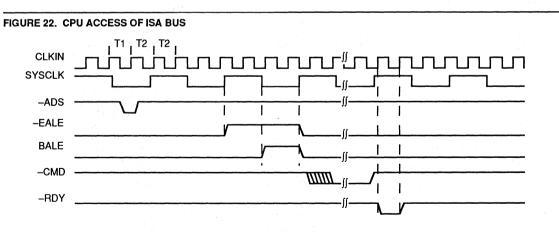

| ISA BUS INTERFACE                      | 66 |

| Overview                               |    |

| ISA Bus Cycle Description              |    |

| CPU Access Cycles                      | 66 |

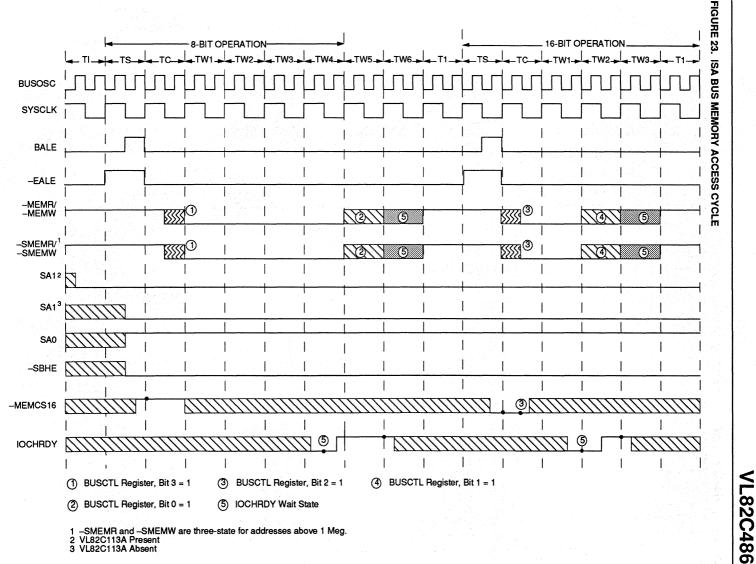

| CPU Memory Access Cycles               | 67 |

| CPU I/O Access Cycles                  |    |

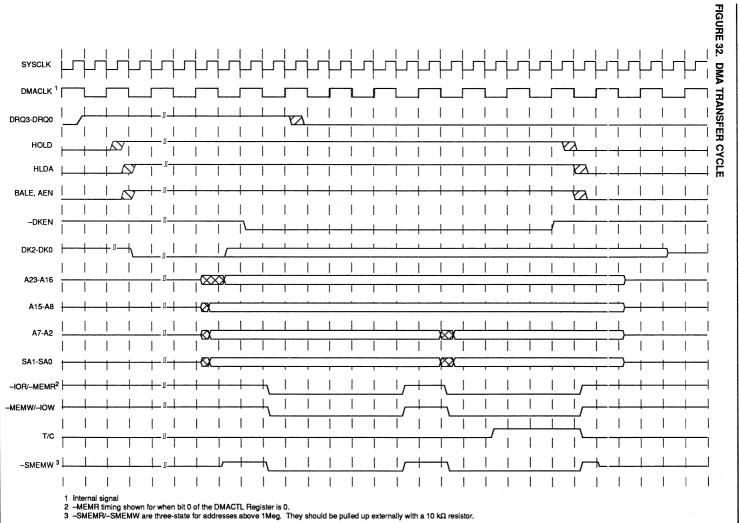

| DMA Access Cycles                      | 67 |

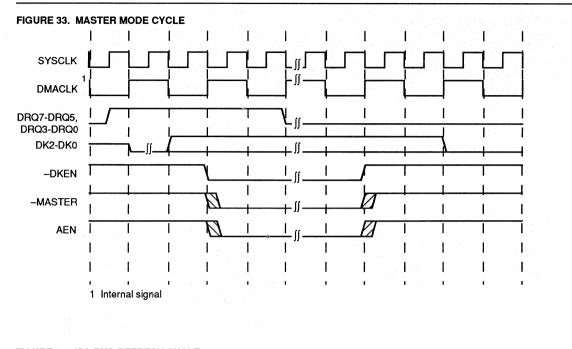

| Master Mode Cycles                     | 67 |

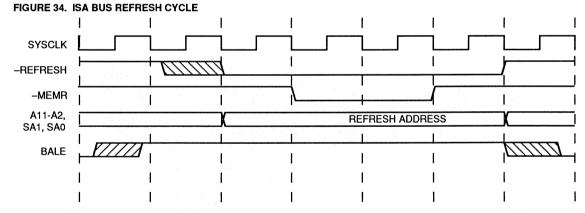

| Refresh Cycles                         | 67 |

| Bus Control Register (BUSCTL)          | 79 |

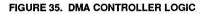

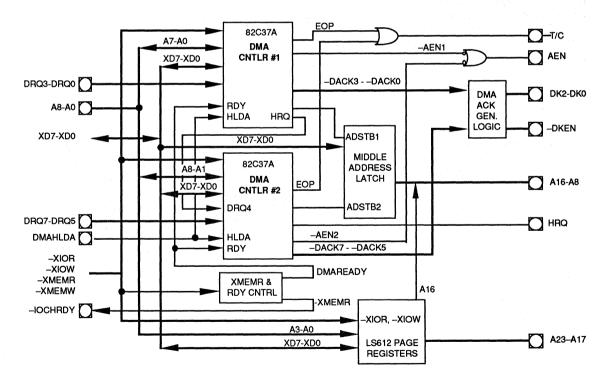

| Direct Memory Access (DMA)             | 80 |

| DMA Controllers                        | 80 |

| DMA Controller Registers               | 82 |

| Middle Address Bit Latches             |    |

| Page Registers and Extended Addressing |    |

| Address Generation                     |    |

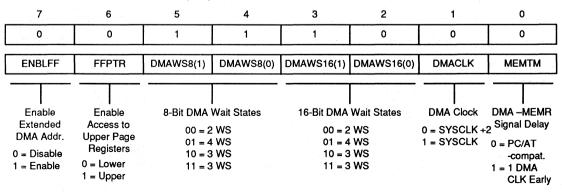

| DMACTL Register                        |    |

| Ready Control                          |    |

| External Cascading                     |    |

| Hold Request Arbiter                   |    |

| -MEMR Delay                            |    |

| Data Steering                          |    |

| Overview                               |    |

| ISA Bus Refresh Cycle Types            |    |

| Synchronous Refresh Mode               |    |

| Asynchronous Refresh Mode              |    |

| Dcoupled Refresh Mode                  |    |

|                                        |    |

| Interrupt Controller Registers         |    |

| TIMER/COUNTER                          |    |

| Timer/Counter Registers                | 94 |

# TABLE OF CONTENTS

## Page Number

| FUNCTIONAL DESCRIPTION (Cont.)                                               |    |

|------------------------------------------------------------------------------|----|

| KEYBOARD CONTROLLER INTERFACE                                                | 95 |

| VL82C113A INTERFACE                                                          |    |

| SLEEP MODE CONTROL LOGIC<br>Sleep Mode Operation<br>MISCSET Control Register |    |

| DEDICATED INTERNAL CONTROL REGISTERS                                         |    |

| IN-CIRCUIT TEST LOGIC                                                        |    |

| VL82C486 RESET OPTIONS<br>Reset Sequence<br>Reset Modes                      |    |

| REGISTER SUMMARY                                                             |    |

| AC CHARACTERISTICS                                                           |    |

| ABSOLUTE MAXIMUM RATINGS                                                     |    |

| DC CHARACTERISTICS                                                           |    |

| BIOS                                                                         |    |

| PACKAGE OUTLINE                                                              |    |

| SALES OFFICE LISTING                                                         |    |

## LIST OF TABLES

Item

| Table 1.  | Bus Cycle Decode                            | .18 |

|-----------|---------------------------------------------|-----|

| Table 2.  | MISCSET Register, Cache Control Bit         | .20 |

| Table 3.  | BUSCTL Register, Address Decode Control Bit | .22 |

| Table 4.  | I/O Address Map                             | .23 |

| Table 5.  | Memory Address Mapping                      | .24 |

| Table 6.  | Shadow RAM Segment Control Registers        | .25 |

| Table 7.  | Segment Cacheability Registers              |     |

| Table 8.  | Programmed Memory Region Register           |     |

| Table 9.  | Relocation of System and Slot ROM           | .30 |

| Table 10. | Flash Memory Software Programming           | .31 |

| Table 11. | ROMSET Control Register                     | .32 |

| Table 12. | RAMCFG0 Configuration Register              | .35 |

| Table 13. | RAMCFG1 Configuration Register              | .35 |

| Table 14. | DRAM Bank Start Address                     | .36 |

| Table 15. | DRAM Page/Interleave Mapping                | .42 |

| Table 16. | RAMTMG Register                             | .44 |

| Table 17. | Clock Cycles for CPU DRAM Read Accesses     | .52 |

| Table 18. | Calculation of DRAM Speed Requirements      | .55 |

| Table 19. | RAMSET Register                             | .56 |

| Table 20. | NTBREF Register                             | .57 |

| Table 21. | MISCSET Register, DRAM Control Bits         | .57 |

| Table 22. | FBCR Address Register                       |     |

| Table 23. | AT Bus Clock Frequencies                    | .63 |

|           |                                             |     |

# TABLE OF CONTENTS

# Page Number

#### Item

| Table 24. | CLKCTL Register                                                           | 64 |

|-----------|---------------------------------------------------------------------------|----|

| Fable 25. | BUSCTL Register                                                           | 79 |

| Fable 26. | DMA Controller Registers                                                  | 82 |

| Fable 27. | DMA Page Registers Access                                                 |    |

| Fable 28. | DMACTL Register                                                           | 84 |

| Fable 29. | DMA Addressing for Slot Bus Accesses                                      |    |

| Fable 30. | DMA Addressing for System Board Memory                                    | 86 |

| Fable 31. | Data Steering Logic Glosary of Terms and Acronyms                         | 87 |

| Fable 32. | Data Steering During CPU Writes                                           | 88 |

| Table 33. | Data Steering During CPU Reads                                            |    |

| Fable 34. | Data Steering During BIOS ROM Reads                                       | 89 |

| Table 35. | Data Steering During DMA/Master Reads of On-Board DRAM/Local Bus Devices  |    |

| Fable 36. | Data Steering During DMA/Master Writes of On-Board DRAM/Local Bus Devices | 90 |

| Fable 37. | Data Steering During DMA/Master Reads of ISA Slot Devices                 | 90 |

| Fable 38. | Data Steering During DMA/Master Writes of ISA Slot Devices                | 91 |

| Fable 39. | Write-Only Interrupt Controller Registers                                 |    |

| Fable 40. | Read-Only Interrupt Controller Registers                                  |    |

| Fable 41. | Timer/Counter Registers                                                   | 94 |

| Fable 42. | MISCSET Register                                                          |    |

| Fable 43. | Dedicated I/O Control Registers                                           |    |

| Table 44. | Configuration Index Register                                              |    |

| lable 45. | Configuration Data Port Register                                          |    |

| Fable 46. | Fast A20 Register and Port A1                                             |    |

| Fable 47. | Fast CPU Register and Port A1                                             |    |

| Fable 48. | CPU Speed Control Registers1                                              |    |

| Fable 49. | Configuration Enable and Disable Registers1                               |    |

| Fable 50. | NMI Logic1                                                                |    |

| Table 51. | Port B Register1                                                          |    |

| lable 52. | Pin Assignment for ICT Mode1                                              |    |

| Table 53. | System Configuration Initialization1                                      |    |

| lable 54. | Indexed Configuration Registers Format1                                   |    |

| lable 55. | Indexed Configuration Registers Map1                                      |    |

| Fable 56. | Dedicated I/O Control Registers1                                          | 15 |

|           |                                                                           |    |

## LIST OF FIGURES

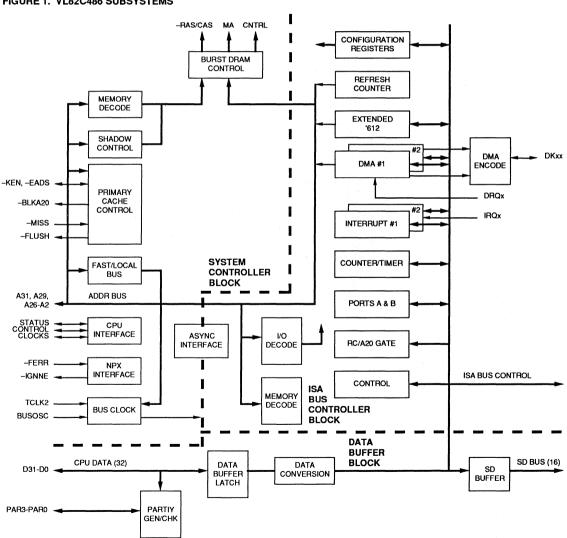

| Figure 1.  | VL82C486 Subsystems                           | 17 |

|------------|-----------------------------------------------|----|

| Figure 2.  | CPU Interface                                 | 19 |

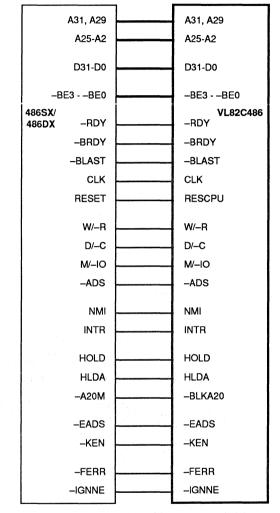

| Figure 3.  | CPU Interface Timings                         | 21 |

| Figure 4.  | Shadow RAM Control                            |    |

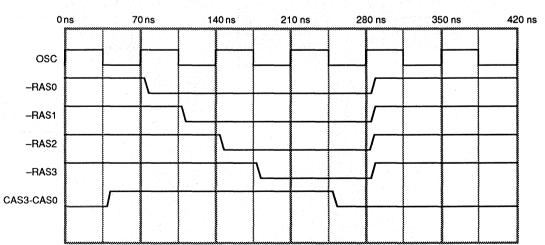

| Figure 5.  | DRAM –CAS Generation                          |    |

| Figure 6.  | Four Bank DRAM System - Configuration A       | 38 |

| Figure 7.  | Four Bank DRAM System - Configuration B       |    |

| Figure 8.  | Four Bank Double-Sided SIMM - Configuration A | 40 |

| Figure 9.  | Four Bank Double-Sided SIMM - Configuration B | 41 |

| Figure 10. | DRAM Controller – RAS Timing                  |    |

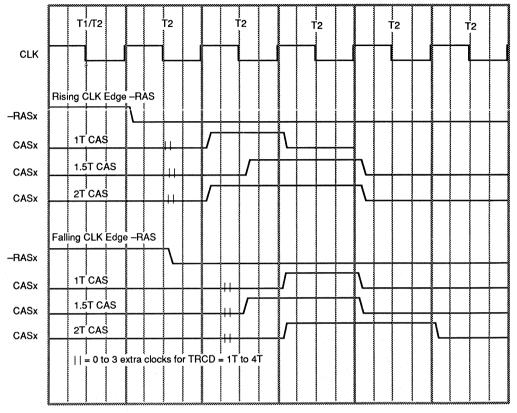

| Figure 11. | DRAM Controller – RAS to CAS Delays           | 47 |

| Figure 12. | DRAM Controller Page-Hit CAS Start Timing     |    |

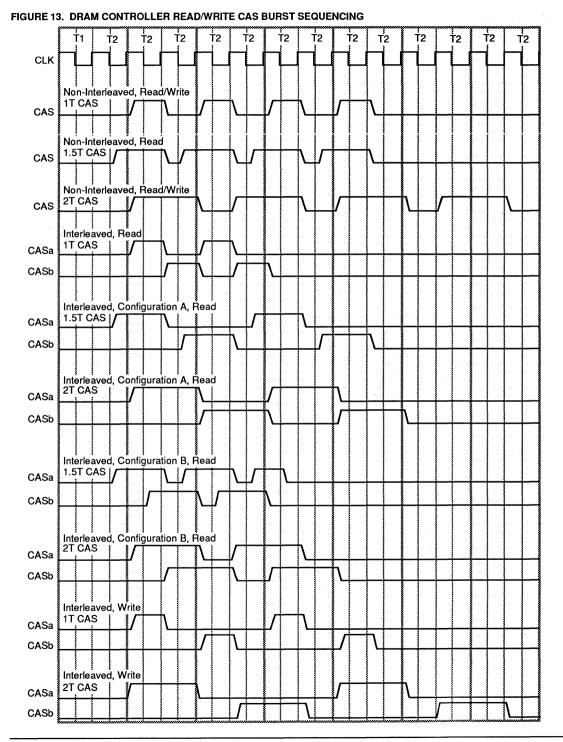

| Figure 13. | DRAM Controller CAS Burst Sequencing          |    |

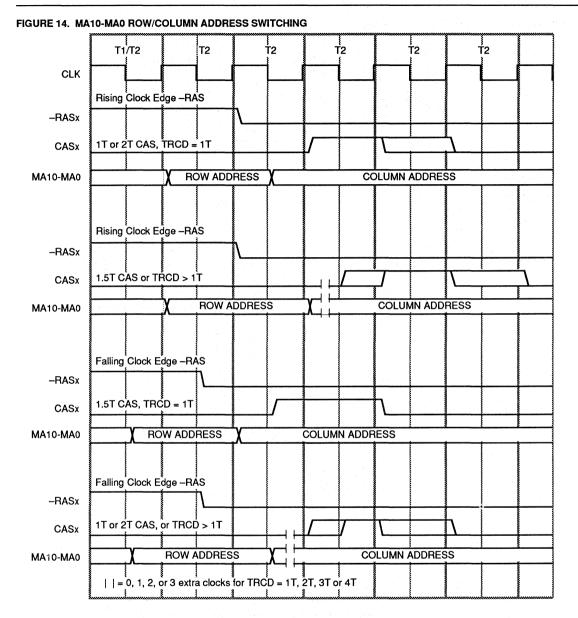

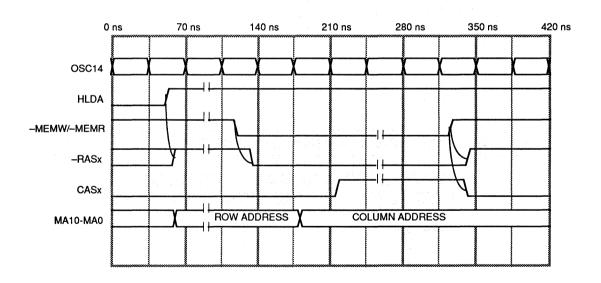

| Figure 14. | MA10-MA0 Row/Column Address Switching         | 50 |

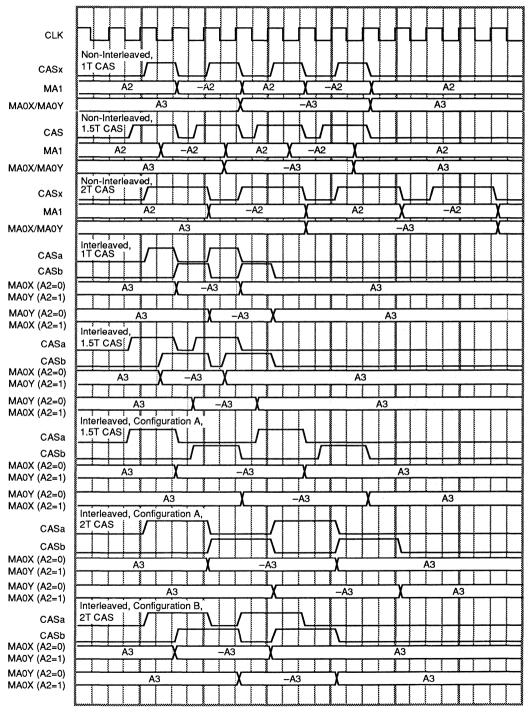

| Figure 15. | MA1, MA0X, MA0Y Burst Sequencing              | 51 |

| Figure 16. | DRAM Timing for DMA/Master Mode               |    |

|            |                                               |    |

Item

# TABLE OF CONTENTS

.

| Figure 17. | DRAM Refresh Cycles                                 | 54   |

|------------|-----------------------------------------------------|------|

| Figure 18. | Cache Controller Interface                          | 59   |

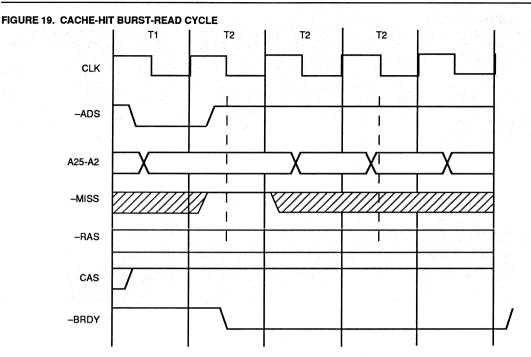

| Figure 19. | Cache-Hit Burst Read Cycle                          | 60   |

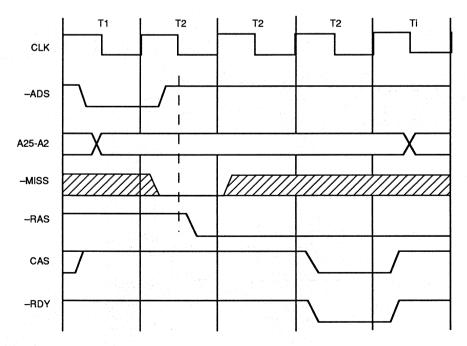

| Figure 20. | Cache-Miss Non-Burst Read Cycle                     | . 60 |

| Figure 21. | Clock Generator Block Diagram                       | 61   |

| Figure 22. | CPU Access of ISA Bus                               |      |

| Figure 23. | ISA Bus Memory Access Cycle                         | . 68 |

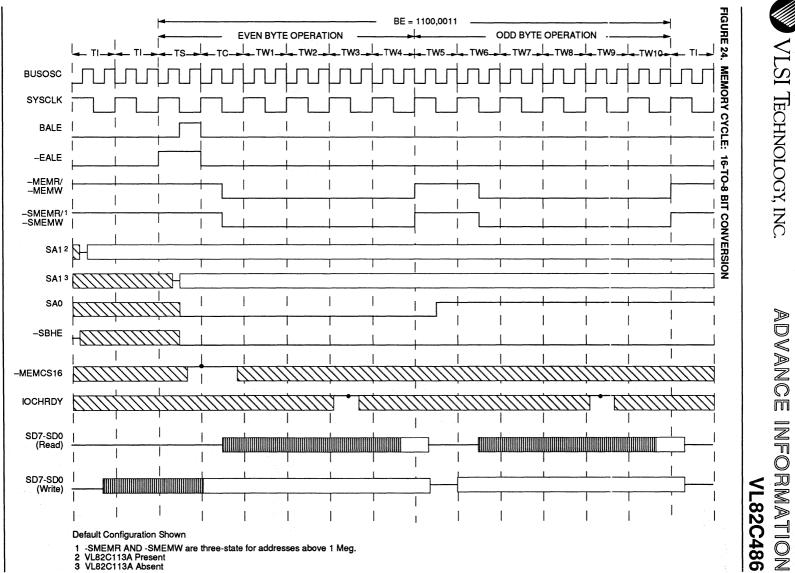

| Figure 24. | Memory Cycle: 16-to-8 Bit Conversion                | .69  |

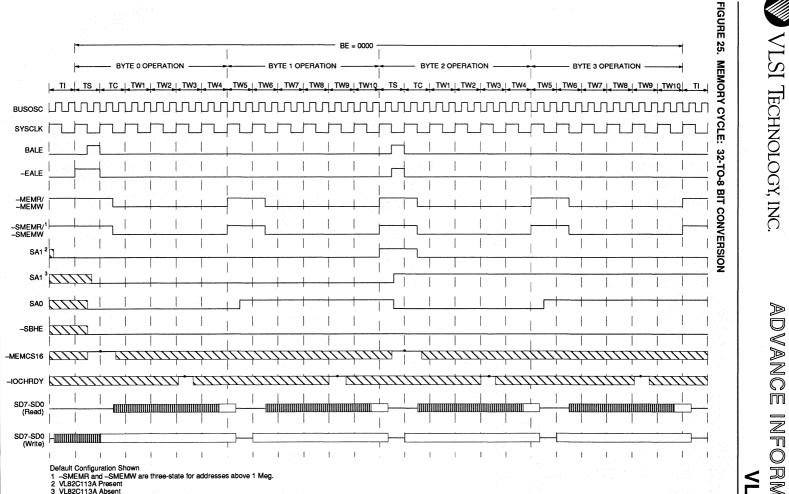

| Figure 25. | Memory Cycle: 32-to-8 Bit Conversion                |      |

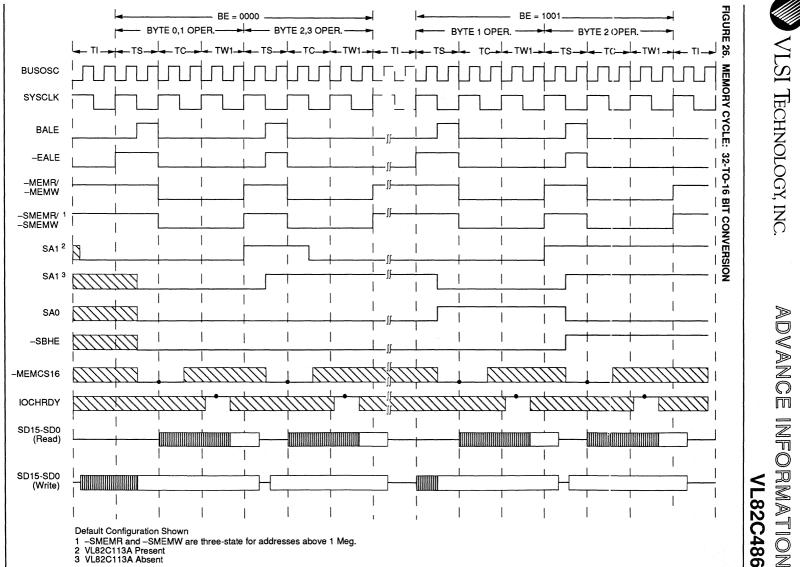

| Figure 26. | Memory Cycle: 32-to-16 Bit Conversion               | .71  |

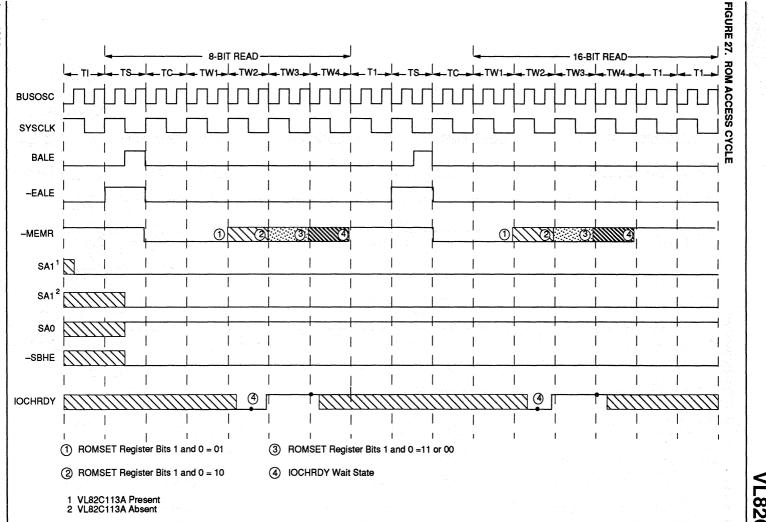

| Figure 27. | ROM Access Cycle                                    |      |

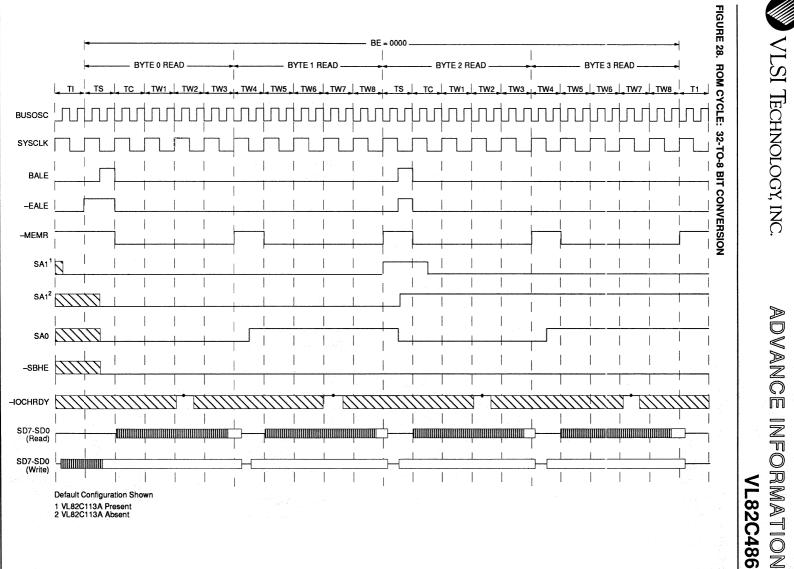

| Figure 28. | ROM Cycle: 32-to-8 Bit Conversion                   | .73  |

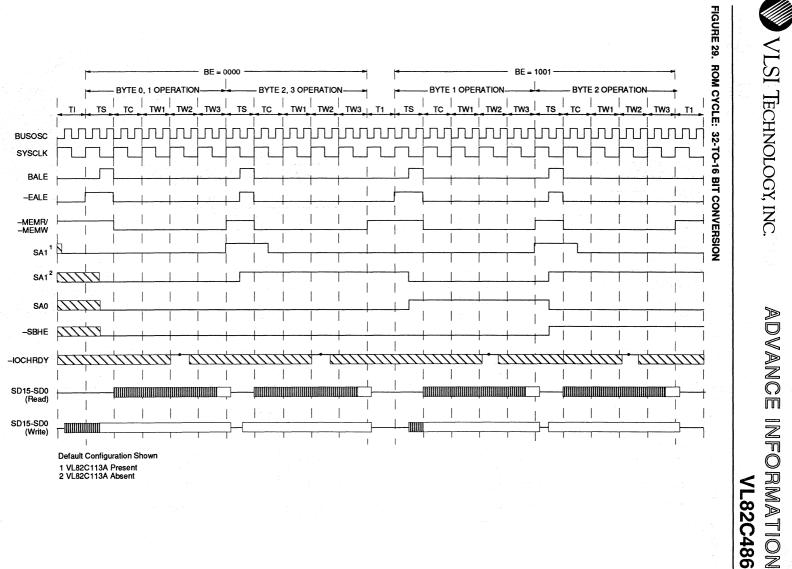

| Figure 29. | ROM Cycle: 32-to-16 Bit Conversion                  | 74   |

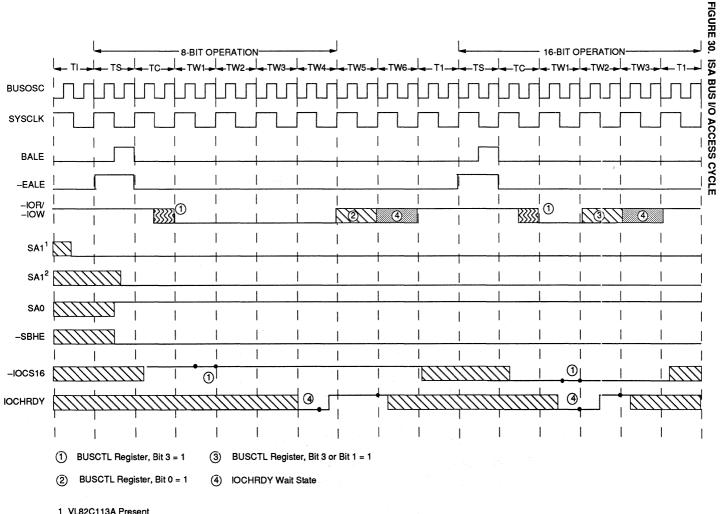

| Figure 30. | ISA Bus I/O Access Cycle                            | 75   |

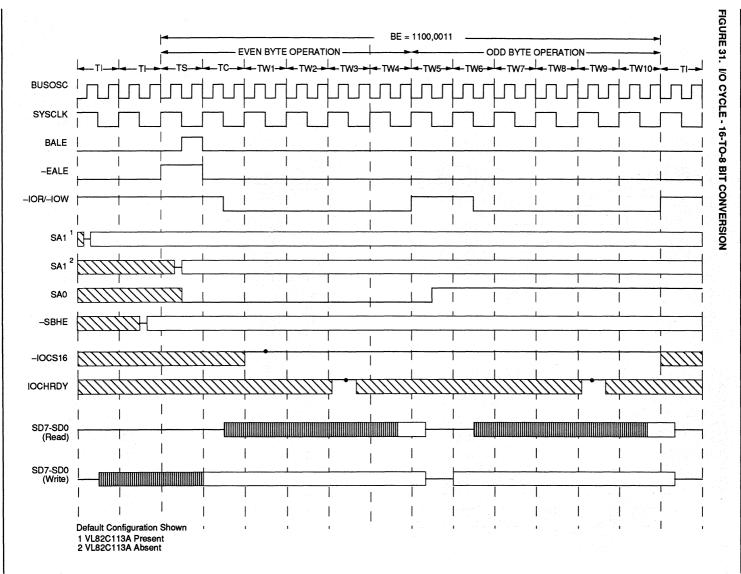

| Figure 31. | I/O Cycle: 16-to-8 Bit Conversion                   | 76   |

| Figure 32. | DMA Transfer Cycle                                  | .77  |

| Figure 33. | Master Mode Cycle                                   | . 78 |

| Figure 34. | ISA Bus Refresh Cycle                               | 78   |

| Figure 35. | DMA Controller Logic                                | .80  |

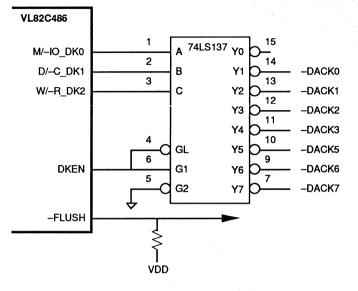

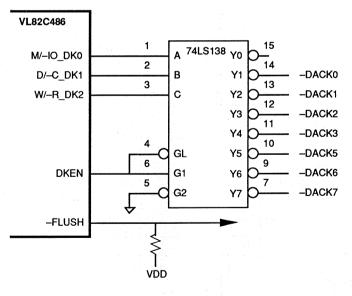

| Figure 36. | Decoding DMA Acknowledge Signals                    | .81  |

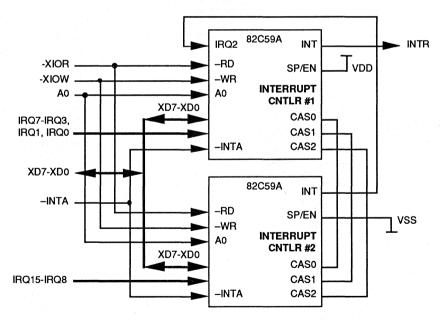

| Figure 37. | Interrupt Controller Logic Diagram                  | .92  |

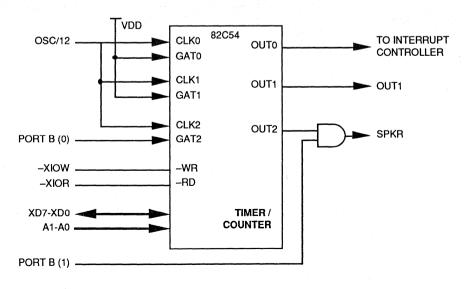

| Figure 38. | Timer/Counter Logic Diagram                         | .94  |

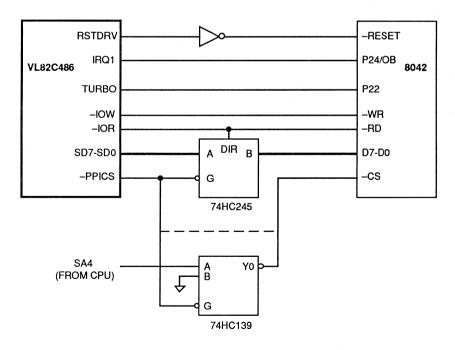

| Figure 39. | Keyboard Controller Interface                       | .95  |

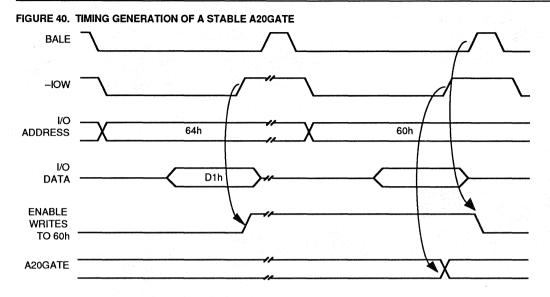

| Figure 40. | Timing Generation of a Stable A20GATE               | .96  |

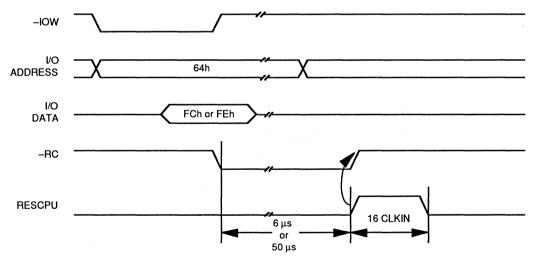

| Figure 41. | Timing Generation of a Pulsed –RC                   |      |

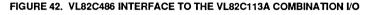

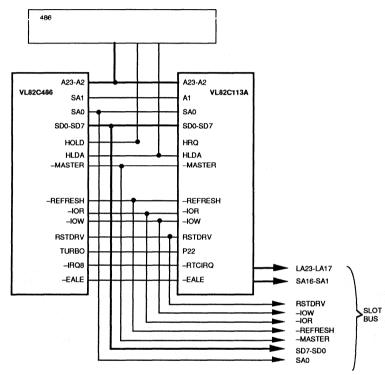

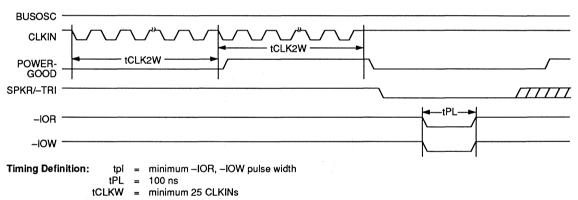

| Figure 42. | VL82C486 Interface to the VL82C113A Combination I/O | .97  |

| Figure 43. | ICT Mode Timing Waveform                            |      |

| Figure 44. | Reset Sequence                                      | 106  |

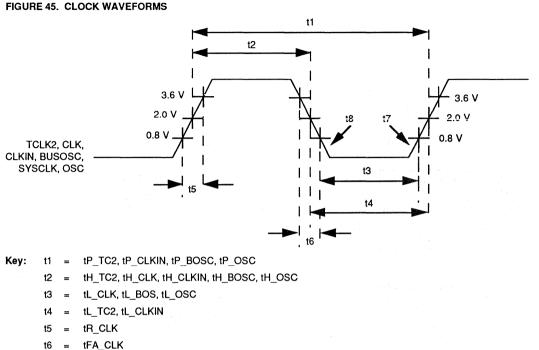

| Figure 45. | Clock Waveforms                                     |      |

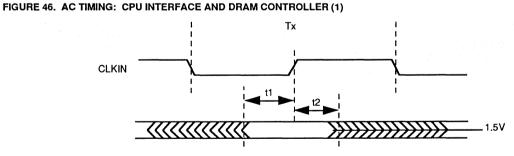

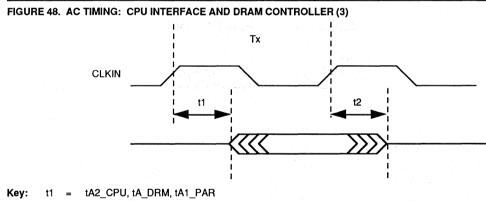

| Figure 46. | AC Timing: CPU Interface and DRAM Controller (1)    | 123  |

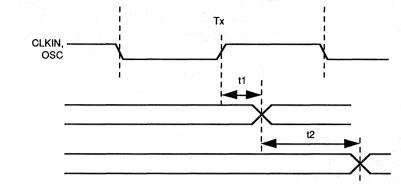

| Figure 47. | AC Timing: CPU Interface and DRAM Controller (2)    |      |

| Figure 48. | AC Timing: CPU Interface and DRAM Controller (3)    | 124  |

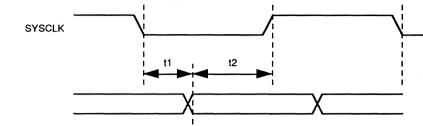

| Figure 49. | AC Timing: ISA Bus Controller (1)                   | 125  |

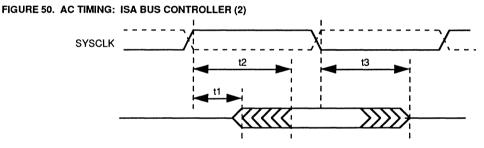

| Figure 50. | AC Timing: ISA Bus Controller (2)                   | 125  |

| Figure 51. | AC Timing: ISA Bus Controller (3)                   | 126  |

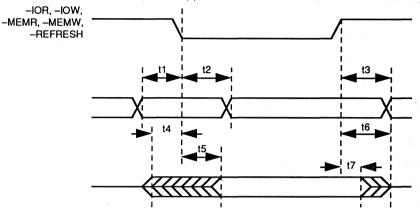

| Figure 52. | AC Timing: ISA Bus Controller (4)                   |      |

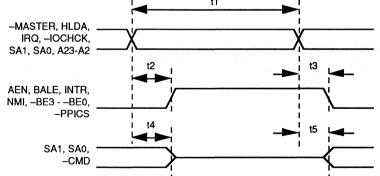

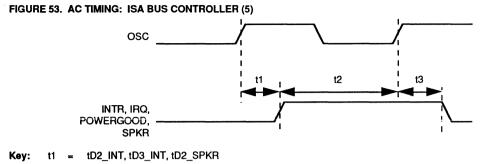

| Figure 53. | AC Timing: ISA Bus Controller (5)                   | 127  |

|            |                                                     |      |

SINGLE-CHIP 486 (SC486™) CONTROLLER

## FEATURES

- Fully compatible 486-based PC/AT systems

- Up to 33 MHz CPU operation

- Replaces the following peripheral logic on the motherboard:

- Two 82C37A DMA controllers

- 74LS612 memory mapper (extended to support 64 MB)

- Two 82C59A interrupt controllers

- 82C54 timer

- 82284 clock generator and ready interface

- 82288 bus controller

- Includes:

- Memory/refresh controller

- Port A, B, and NMI logic

- Bus steering logic

- Parity generation/checking for onboard DRAM

- Turbo Mode control

- Hidden off-board, stolen on-board refresh

- Staggered RAS refresh

- Three-stateable outputs for board testing

- Memory controller features include: – Page Mode DRAM access

- One to four banks 32 bits wide

- One or two banks 64 bits wide

- Two- or four-way interleave support

- Programmable RAS/CAS timing

- Burst support

- Supports:

- Up to 64 MB system memory

- 256K, 1M, or 4M DRAM

- Double-sided SIMMs

- Secondary cache interface

- 8- or 16-bit wide BIOS ROM

- Shadow RAM in the 640K-1M area

- Flash memory for BIOS ROM

- Asynchronous ISA bus operation up to 16 MHz

- Relocation of slot ROMs

- Power saving features include:

Sleep Mode

- Slow DRAM refresh

- · Other features:

- Programmable for 10- or 16-bit internal I/O addressing

- Programmable drive on DRAM and ISA bus signals

- Programmable memory access to define "fast-bus", local bus, slot bus, and non-cacheable and writeprotect areas

- Input pin defines access to local bus devices

- · 1.0-micron CMOS technology

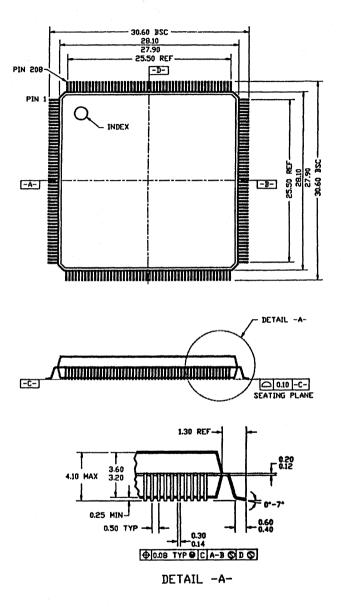

- 208-lead metric quad flat pack (MQFP)

## DESCRIPTION

The VL82C486 is a Single-Chip High Performance Controller for 486- and 486SX/487SX-based PC/AT systems.

The VL82C486 includes the dual 82C37A DMA controllers, dual 82C59A programmable interrupt controllers, 82C54 programmable interval timer, 82284 clock and ready generator, 82288 bus controller and the logic for address/data bus control, memory control, shutdown, refresh generation and refresh/DMA arbitration.

## **ORDER INFORMATION**

| Part<br>Number | Package               |  |  |

|----------------|-----------------------|--|--|

| VL82C486-FC    | Metric Quad Flat Pack |  |  |

Note: Operating temperature range is 0°C to +70°C.

SC486 is a trademark of VLSI Technology, Inc.

# ADVANCE INFORMATION VL82C486

## OVERVIEW

The VL82C486 Controller is designed to perform in 486DX- or 486SX/487SXbased PC/AT-compatible systems running up to 33 MHz. The VL82C486 replaces the following devices on the motherboard:

- Two 82C37A DMA controllers

- Two 82C59A interrupt controllers

- 82C54 timer

- 74LS612 memory mapper

- 82284 clock generator and ready interface

- 82288 bus controller

The controller also includes the following:

- Memory/refresh controller

- Port B and NMI logic

- Bus steering logic

- Turbo Mode control logic

- Parity checking logic

- Parity generation logic

- Support for Weitek numeric coprocessors

The memory controller logic is capable of accessing up to 64 MB. There can be up to four banks of 256K, 1M, or 4M

DRAMs used in the system. The VL82C486 can drive four banks without external buffering. Built-in Page Mode operation and up to four-way interleaving allow the PC designer to maximize system performance using low cost DRAMs. Programmable DRAM timing is provided for RAS precharge, RAS-to-CAS delay, and CAS pulse width.

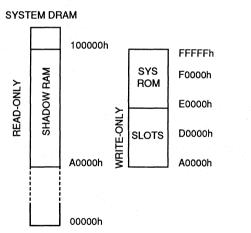

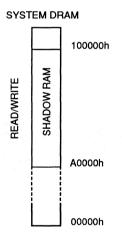

Shadowing features are supported on 16K boundaries between A0000h and FFFFFh (640 KB to 1 MB). Simultaneous use of shadowed ROM and direct system board access is possible

in non-overlapping fashion throughout this memory space. Control over four access options is provided:

- 1. Access ROM or slot bus for reads and writes.

- 2. Access system board DRAM for reads and writes.

- 3. Access system board DRAM for reads and slot bus for writes.

- Shadow Setup Mode. Read ROM or slot bus, write system board DRAM.

A special mode is supported for erasing and programming flash memories for the case where such devices are used as the BIOS ROMs.

Three special programmable address regions are provided. The fast-bus clock region allows accesses to certain memory regions at a faster ISA clock rate for fast on-board or off-board devices. A non-cacheable region and/ or a write-protected region may be defined by a set of six registers that allow memory in the region 640 KB to 1 MB to be marked as non-cacheable and/or write-protected in increments of 16 KB. A further set of registers allows a memory range anywhere in the first 64 MB of memory to be marked as a DRAM region, an ISA bus region, or a local bus region either cacheable or non-cacheable in increments of 2 KB. 64 KB, or 1 MB.

Further support for devices that reside on the 486 local bus is provided through use of the –LBA (local bus access) input, which deselects the VL82C486 during CPU cycles. Also, a memory range anywhere in the first 64 MB of memory can be programmed via the internal Mapping Registers to make the VL82C486 access a local bus device as a 486 bus memory device during DMA or Master Mode transfers.

The VL82C486 handles system board refresh directly and also controls the

timing of slot bus refresh. Refresh may be performed in Synchronous, Asynchronous, or Decoupled Mode. In Synchronous Mode, the slot bus and on-board DRAM refresh cycles proceed simultaneously and all memory cycles are held until both have completed. The Asynchronous Mode allows onand off-board refreshes to be initiated simultaneously, but to complete asynchronously, allowing sooner access to DRAM. In Decoupled Mode, a separate refresh counter is used for slot bus refresh, allowing on-board DRAM and system refreshes to proceed independently, with DRAM refreshes initiated during bus idle cvcles. CAS-before-RAS refresh is also supported. Refreshes are staggered to minimize power supply loading and attenuate noise on the VDD and ground pins. The VL82C486 supports the standard PC/AT refresh period of 15.625 µs as well as 125 µs.

Support for write-through cache controllers is provided through the use of a -MISS pin to detect cache-hits and cache-misses.

The interrupt controller logic consists of two 82C59A megacells with eight interrupt request lines each for a total of 16 interrupts. The two megacells are cascaded internally and two of the interrupt request inputs are connected to internal circuitry allowing a total of 13 external interrupt requests. There is special programmable logic included in the VL82C486 which allows deglitching of inputs on all the interrupt request pins.

The interval timer includes one 82C54 counter/timer megacell. The counter/ timer has three independent 16-bit counters and six programmable counter modes.

The DMA controllers are 82C37A compatible. The DMA controllers control data transfers between an I/O

channel and on- or off-board memory. DMA can transfer data over the full 64 MB range available. There are internal latches provided for latching the middle address bits output by the 82C37A megacells on the data bus, and the 74LS612 memory mappers are provided to generate the upper address bits.

The VL82C486 can be programmed to generate the ISA bus timing from the CPU clock oscillator or a separate asyncronous oscillator.

The VL82C486 also performs all of the data buffer control functions required for a 486XX processor-based PC/AT system. Under the control of the CPU, the VL82C486 routes data to and from the CPU's D bus, the internal XD bus, and the slots (SD bus). During CPU ISA bus reads, the data is latched for synchronization with the CPU. Parity is checked for D bus DRAM read operations. The chip does not generate parity for CPU writes to DRAM.

When the DMA requestor or external bus master is the bus owner, the VI 82C486 allows data transfer between the slot SD bus and the CPU local D bus. The chip also performs low-tohigh and high-to-low byte swaps on the 16-bit SD bus. Parity is generated by the VL82C486 during DMA or Master writes to on-board DRAM. The chip also provides a single input, -TRI, to disable all of its outputs for board level testability. This is a dual function pin SPKR/-TRI. Care must be taken so that the pin is sampled high at the rising edge of POWERGOOD. A coupling to the speaker circuit is recommended.

The VL82C486 Controller functions are programmable via a set of internal configuration registers. The state of various interface pins on reset is used to determine the default configuration. A dip switch can be used to establish the initial configuration.

# ADVANCE INFORMATION VL82C486

## **PIN DIAGRAM**

# ADVANCE INFORMATION VL82C486

# **PIN TYPE BY OPERATIONAL STATE**

| Pin # | Pin Name | Pin<br>Type | Input<br>Type | Drive<br>(mA) | Pin # | Pin Name | Pin<br>Type | Input<br>Type | Drive<br>(mA) |

|-------|----------|-------------|---------------|---------------|-------|----------|-------------|---------------|---------------|

| 1     | DRQ3     | I-PU        | TTL-S         |               | 33    | VDD      | PWR         |               |               |

| 2     | DRQ2     | I-PU        | TTL-S         |               | 34    | D17      | ю           | TTL           | 8             |

| 3     | DRQ1     | I-PU        | TTL-S         |               | 35    | D16      | ю           | ΠL            | 8             |

| 4     | DRQ0     | I-PU        | TTL-S         |               | 36    | D15      | ю           | ΠL            | 8             |

| 5     | IRQ15    | I-PU        | TTL-S         |               | 37    | D14      | ю           | TTL           | 8             |

| 6     | IRQ14    | I-PU        | TTL-S         |               | 38    | D13      | ю           | TTL           | 8             |

| 7     | IRQ12    | I-PU        | TTL-S         |               | 39    | D12      | 10          | TTL           | 8             |

| 8     | IRQ11    | I-PU        | TTL-S         |               | 40    | D11      | ю           | TTL           | 8             |

| 9     | IRQ10    | I-PU        | TTL-S         |               | 41    | D10      | ю           | TTL           | 8             |

| 10    | IRQ9     | I-PU        | TTL-S         |               | 42    | D9       | 10          | ΠL            | 8             |

| 11    | IRQ7     | I-PU        | TTL-S         |               | 43    | D8       | ю           | TTL           | 8             |

| 12    | IRQ6     | I-PU        | TTL-S         |               | 44    | D7       | Ю           | TTL           | 8             |

| 13    | IRQ5     | I-PU        | TTL-S         |               | 45    | D6       | ю           | TTL           | 8             |

| 14    | IRQ4     | I-PU        | TTL-S         |               | 46    | D5       | ю           | TTL           | 8             |

| 15    | IRQ3     | I-PU        | TTL-S         |               | 47    | D4       | ю           | TTL           | 8             |

| 16    | VSS      | GND         |               |               | 48    | D3       | 10          | TTL           | 8             |

| 17    | D31      | ю           | TTL           | 8             | 49    | D2       | 10          | TTL           | 8             |

| 18    | D30      | 0           | TTL           | 8             | 50    | D1       | 10          | TTL           | 8             |

| 19    | D29      | 10          | TTL           | 8             | 51    | Do       | 10          | TTL           | 8             |

| 20    | D28      | ю           | TTL           | 8             | 52    | VSS      | GND         | 1             |               |

| 21    | D27      | ю           | TTL           | 8             | 53    | CLK      | 0           |               | 24            |

| 22    | VDD      | PWR         |               |               | 54    | CLKIN    |             | CMOS          |               |

| 23    | D26      | ю           | TTL           | 8             | 55    | FLUSH    | IO (Note 2) | TTL           | 8             |

| 24    | D25      | 10          | TTL           | 8             | 56    | -IGNNE   | IO (Note 2) | TTL           | 8             |

| 25    | D24      | 10          | TTL           | 8             | 57    | -FERR    | I-PU        | TTL           |               |

| 26    | D23      | ю           | TTL           | 8             | 58    | RESCPU   | 0           |               | 8             |

| 27    | D22      | ю           | TTL           | 8             | 59    | TCLK2    | I           | CMOS          |               |

| 28    | VSS      | GND         |               |               | 60    | VSS      | GND         |               |               |

| 29    | D21      | ю           | TTL           | 8             | 61    | -EADS    | 0           |               | 8             |

| 30    | D20      | 10          | TTL           | 8             | 62    | RDY      | IO-PU       | TTL           | 8             |

| 31    | D19      | ю           | TTL           | 8             | 63    | -BLAST   | 10          | TTL           | 8             |

| 32    | D18      | ю           | TTL           | 8             | 64    | VDD      | PWR         |               |               |

# ADVANCE INFORMATION VL82C486

## PIN TYPE BY OPERATIONAL STATE (Cont.)

| Pin # | Pin Name  | Pin<br>Type | Input<br>Type | Drive<br>(mA) | Pin # | Pin Name | Pin<br>Type | Input<br>Type | Drive<br>(mA) |

|-------|-----------|-------------|---------------|---------------|-------|----------|-------------|---------------|---------------|

| 65    | -BRDY     | IO-PU       | TTL           | 8             | 97    | MA1      | 0           |               | 12/24/36/48   |

| 66    | HLDA      | 1           | TTL           |               | 98    | MAOX     | 0           |               | 12/24         |

| 67    | HOLD      | 0           |               | 8             | 99    | MA2      | 0           |               | 12/24/36/48   |

| 68    | W/-R_DK2  | 10          | TTL           | 8             | 100   | МАЗ      | 0           |               | 12/24/36/48   |

| 69    | D/-C_DK1  | ю           | TTL           | 8             | 101   | MA4      | 0           |               | 12/24/36/48   |

| 70    | M/-IO_DK0 | ю           | ΠL            | 8             | 102   | MA5      | 0           |               | 12/24/36/48   |

| 71    | -ADS      | ю           | TTL           | 8             | 103   | MA6      | 0           |               | 12/24/36/48   |

| 72    | -MISS     | 1           | TTL           |               | 104   | VSS      | GND         |               |               |

| 73    | -KEN      | 0           |               | 8             | 105   | MA7      | 0           |               | 12/24/36/48   |

| 74    | -EALE     | IO (Note 2) | Π             | 8             | 106   | MA8      | 0           |               | 12/24/36/48   |

| 75    | -SLEEP    |             | TTL           |               | 107   | MA9      | 0           |               | 12/24/36/48   |

| 76    | -BLKA20   | IO (Note 2) | TTL           | 8             | 108   | MA10     | 0           |               | 12/24/36/48   |

| 77    | VSS       | GND         |               |               | 109   | VDD      | PWR         |               |               |

| 78    | NMI       | 0           |               | 8             | 110   | -RAS0    | 0           |               | 12/24         |

| 79    | BE0       | 10          | TTL           | 8             | 111   | -RAS1    | 0           |               | 12/24         |

| 80    | –BE1      | ю           | Π             | 8             | 112   | RAS2     | 0           |               | 12/24         |

| 81    | -BE2      | ю           | TTL           | 8             | 113   | -RAS3    | 0           |               | 12/24         |

| 82    | -BE3      | ю           | TTL           | 8             | 114   | -RAMW    | IO (Note 2) |               | 12/24/36/48   |

| 83    | -FMPRG    | IO (Note 2) | TTL           | 8             | 115   | VSS      | GND         | · ·           |               |

| 84    | INTR      | 0           |               | 8             | 116   | A2       | 10          | TTL           | 8             |

| 85    | SPKR/-TRI | IO-PU       | ΠL            | 24            | 117   | A3       | 10          | TTL           | 8             |

| 86    | MBE0      | 0           |               | 8             | 118   | A4       | 10          | TTL           | 8             |

| 87    | MBE1      | 0           |               | 8             | 119   | A5       | ю           | TTL           | 8             |

| 88    | MBE2      | 0           |               | 8             | 120   | A6       | 10          | TTL           | 8             |

| 89    | MBE3      | 0           |               | 8             | 121   | A7       | 10          | TTL           | 8             |

| 90    | VSS       | GND         |               |               | 122   | A8       | 10          | TTL           | 8             |

| 91    | CAS0      | 0           |               | 12            | 123   | A9       | 10          | TTL           | 8             |

| 92    | CAS1      | 0           |               | 12            | 124   | A10      | ю           | TTL           | 8             |

| 93    | CAS2      | 0           |               | 12            | 125   | A11      | 10          | TTL           | 8             |

| 94    | CAS3      | 0           |               | 12            | 126   | A12      | 10          | TTL           | 8             |

| 95    | MAOY      | 0           |               | 12/24         | 127   | A13      | ю           | TTL           | 8             |

| 96    | VDD       | PWR         |               |               | 128   | A14      | ю           | TTL           | 8             |

# ADVANCE INFORMATION VL82C486

# PIN TYPE BY OPERATIONAL STATE (Cont.)

| Pin # | Pin Name          | Pin<br>Type | Input<br>Type | Drive<br>(mA) | Pin # | Pin Name        | Pin<br>Type | Input<br>Type | Drive<br>(mA) |

|-------|-------------------|-------------|---------------|---------------|-------|-----------------|-------------|---------------|---------------|

| 129   | A15               | ю           | TTL           | 8             | 161   | -IOR (Note 1)   | ю           | TTL           | 12/24         |

| 130   | A16               | ю           | TTL           | 8             | 162   | -PPICS          | IO (Note 2) | TTL           | 8             |

| 131   | A17               | ю           | TTL           | 8             | 163   | -ROMCS          | IO (Note 2) | TTL           | 8             |

| 132   | VSS               | GND         |               |               | 164   | PAR0            | ю           | TTL           | 8             |

| 133   | A18               | ю           | TTL           | 8             | 165   | PAR1            | ю           | TTL           | 8             |

| 134   | A19               | ю           | TTL           | 8             | 166   | PAR2            | ю           | TTL           | 8             |

| 135   | A20               | ю           | TTL           | 8             | 167   | PAR3            | ю           | ΠL            | 8             |

| 136   | A21               | ю           | TTL           | 8             | 168   | VSS             | GND         |               |               |

| 137   | A22               | ю           | TTL           | 8             | 169   | -MDENX          | 0           |               | 12            |

| 138   | VSS               | GND         | 1             |               | 170   | -MDENY          | 0           |               | 12            |

| 139   | A23               | ю           | TTL           | 8             | 171   | -SBHE           | ю           | TTL           | 12/24         |

| 140   | A24               | 10          | TTL           | 8             | 172   | VDD             | PWR         |               |               |

| 141   | VDD               | PWR         | TTL           |               | 173   | RSTDRV          | 0           |               | 8             |

| 142   | A25               | 10          | TTL           | 8             | 174   | -SMEMR (Note 1) | 0           |               | 12/24         |

| 143   | A26               | 10          | TTL           | 8             | 175   | SYSCLK          | 0           |               | 12/24         |

| 144   | A29               | 10          | TTL           | 8             | 176   | -SMEMW (Note 1) | 0           |               | 12/24         |

| 145   | A31               | Ю           | TTL           | 8             | 177   | -MEMR (Note 1)  | Ю           | ΠL            | 12/24         |

| 146   | –LBA              | 1           | CMOS          |               | 178   | POWERGOOD       | I-PU        | TTL-S         |               |

| 147   | -MEMCS16          |             | TTL           |               | 179   | -MEMW (Note 1)  | Ю           | TTL           | 12/24         |

| 148   | -IOCS16           | 1           | TTL           |               | 180   | DKEN            | IO (Note 2) | TTL           | 12/24         |

| 149   | SA1               | Ю           | TTL           | 12/24         | 181   | -MASTER         |             | TTL           |               |

| 150   | SA0               | Ю           | TTL           | 12/24         | 182   | BALE            | 0           | TTL           | 12/24         |

| 151   | OSC               | I           | TTL           |               | 183   | AEN             | 0           | TTL           | 12/24         |

| 152   | -IOCHCK           | I           | TTL           |               | 184   | SD15            | 10          | TTL           | 12/24         |

| 153   | IOCHRDY (Note 1)  | IO-OD       | TTL           | 12            | 185   | SD14            | Ю           | TTL           | 12/24         |

| 154   | WS0               | 1           | TTL           |               | 186   | SD13            | Ю           | TTL           | 12/24         |

| 155   | TURBO             | 1           | TTL           |               | 187   | VSS             | GND         |               |               |

| 156   | VSS               | GND         |               |               | 188   | SD12            | Ю           | TTL           | 12/24         |

| 157   | -REFRESH (Note 1) | IO-OD       | TTL           | 24            | 189   | SD11            | 10          | TTL           | 12/24         |

| 158   | BUSOSC            | I-PU        | TTL           |               | 190   | SD10            | Ю           | TTL           | 12/24         |

| 159   | тс                | 0           |               | 12/24         | 191   | SD9             | ю           | TTL           | 12/24         |

| 160   | -IOW (Note 1)     | 10          | TTL           | 12/24         | 192   | SD8             | 10          | TTL           | 12/24         |

# ADVANCE INFORMATION VL82C486

## PIN TYPE BY OPERATIONAL STATE (Cont.)

| Pin # | Pin Name | Pin<br>Type | Input<br>Type | Drive<br>(mA) | Pin # | Pin Name | Pin<br>Type | Input<br>Type | Drive<br>(mA) |

|-------|----------|-------------|---------------|---------------|-------|----------|-------------|---------------|---------------|

| 193   | VDD      | PWR         |               |               | 201   | SD0      | ю           | TTL           | 12/24         |

| 194   | SD7      | Ю           | TTL           | 12/24         | 202   | DRQ7     | I-PU        | TTL-S         | 1             |

| 195   | SD6      | Ю           | TTL           | 12/24         | 203   | DRQ6     | I-PU        | TTL-S         |               |

| 196   | SD5      | Ю           | TTL           | 12/24         | 204   | DRQ5     | I-PU        | TTL-S         |               |

| 197   | SD4      | ю           | TTL           | 12/24         | 205   | -IRQ8    | I-PU        | TTL-S         |               |

| 198   | SD3      | Ю           | TTL           | 12/24         | 206   | WEIRQ    | I-PD        | TTL           |               |

| 199   | SD2      | Ю           | TTL           | 12/24         | 207   | IRQ1     | I-PU        | TTL-S         |               |

| 200   | SD1      | Ю           | TTL           | 12/24         | 208   | VSS      | GND         |               |               |

Notes: 1. These pins require an external pull-up resistor (10 k $\Omega$  is recommended).

2. These pins are inputs only during POR (power-on reset).

CMOS CMOS-compatible input

I Input-only pin

Legend:

IO Bidirectional pin GND Ground pin

O Output-only pin

- OD Open drain

- PWR Power supply pin

- TTL TTL-compatible input

- -PD Indicates a high-impedance with approximately 10 kΩ minimum resistance to VSS (internal pull-down resistor on pin).

- -PU Indicates a high-impedance with approximately 10 kΩ minimum resistance to VDD (internal pull-up resistor on pin).

- -S Indicates a Schmitt-trigger input with hystersis for noise immunity.

## SIGNAL DESCRIPTIONS

| Signal<br>Name                            | Pin<br>Number                                                            | Pin<br>Type | Signal<br>Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------|--------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CPU INTERFA</b><br>A31, A29,<br>A26-A2 | CE SIGNALS<br>145, 144,<br>143, 142,<br>140, 139,<br>137-133,<br>131-116 | Ю           | Address bus - This bidirectional address bus is driven by the bus master. It is driven out by the VL82C486 during Non-Master Mode DMA and refresh cycles when HLDA is active and –MASTER is inactive. The signals A25-A2 allow access to 64 MB of system memory. The upper two bits of the bus, A31 and A29, are used for accessing system ROM and the Weitek numeric coprocessor A26 is used to provide a non-aliased unused address space above 64 MB to assist memory sizing routines. |

| -ADS                                      | 71                                                                       | Ю           | Address Status - The active low Address Status (–ADS) signal is driven by the 486 as an indication that the address and control signals currently supplied by the CPU are valid. This signal is used internally to indicate that the data and command are valid and determine the beginning of a memory or I/O cycle.                                                                                                                                                                     |

|                                           |                                                                          |             | -ADS is driven by the VL82C486 when HLDA is active, and is made low for<br>one CPU clock cycle at the beginning of DMA or Master Mode cycles when a<br>local bus region is selected by the PMR Registers.                                                                                                                                                                                                                                                                                 |

| -BE3BE0                                   | 82-79                                                                    | Ю           | Byte Enable bits 3 through 0 - These signals are normally inputs to the<br>VL82C486 and indicate which bytes on D31-D0 are involved in a memory or I/C<br>access. They are ignored during all DRAM reads.                                                                                                                                                                                                                                                                                 |

|                                           |                                                                          |             | -BE3BE0 are driven by the VL82C486 when HLDA is active and indicate<br>which one or two bytes are involved in an 8- or 16-bit DMA or Master Mode<br>transfer between the slot I/O and a local bus device.                                                                                                                                                                                                                                                                                 |

| -BLAST                                    | 63                                                                       | Ю           | Burst Last - This signal is used by the VL82C486 as an indicator of when to terminate the current burst cycle, if the length of the burst cycle is less than four double words. It is driven low by the VL82C486 when HLDA is active, since the VL82C486 does not support Burst Mode during DMA or Master Mode cycles.                                                                                                                                                                    |

| -BRDY                                     | 65                                                                       | IO-PU       | Burst Ready - The active low ready (–BRDY) signal indicates to the 486 that<br>the current burst cycle is complete. It is driven low when valid data has been<br>presented to the CPU in response to a read command or when data has been<br>accepted in response to a write command from the CPU. The VL82C486<br>drives –BRDY on all local bus DRAM accesses, but never drives it in response<br>to slot bus accesses (see –RDY definition).                                            |

|                                           |                                                                          |             | The VL82C486 enables the –BRDY three-state output only when it needs to<br>drive it low and leaves –BRDY enabled for just one CPU clock cycle after it has<br>driven –BRDY high again.                                                                                                                                                                                                                                                                                                    |

|                                           |                                                                          |             | When HLDA is active, -BRDY is an input to the VL82C486 and may be driven<br>by a local bus device to terminate DMA or Master Mode cycles. This pin has<br>an internal pull-up resistor.                                                                                                                                                                                                                                                                                                   |

| CLK                                       | 53                                                                       | 0           | Clock - This output is a CMOS level signal which is normally one-half the<br>frequency of the TCLK2 signal. It is used by the CPU and other on-board logic.                                                                                                                                                                                                                                                                                                                               |

| CLKIN                                     | 54                                                                       | I .         | Input Clock - This is the fundamental clock input to the VL82C486. It must be the same clock as that supplied to the 486.                                                                                                                                                                                                                                                                                                                                                                 |

| M/-IO_DK0                                 | 70                                                                       | Ю           | Memory Input/Output or DMA Acknowledge bit 0 - When HLDA is low,<br>M/–IO_DK0 is driven by the local bus master and is decoded with D/–C_DK1<br>and W/–R_DK2 to indicate the type of bus cycle requested                                                                                                                                                                                                                                                                                  |

|                                           |                                                                          |             | When HLDA is high, M/–IO_DK0 is an output signal which along with D/–C_DK1 and W/–R_DK2 represents the encoded channel number being serviced at the beginning of DMA acknowledge cycles. If the VL82C486 makes –ADS active during DMA or Master Mode cycles (for local bus accesses) this signal is forced high.                                                                                                                                                                          |

# ADVANCE INFORMATION VL82C486

| Signal<br>Name | Pin<br>Number                | Pin<br>Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Signal<br>Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D/-C_DK1       | 69                           | Ю                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Data Control or DMA Acknowledge bit 1 - When HLDA is low, D/–C_DK1 is driven by the local bus master and is decoded with M/–IO_DK0 and W/–R_DK2 to indicate the type of bus cycle requested.                                                                                                                                                                                                                                  |

|                |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | When HLDA is high, D/–C_DK1 is an output signal which along with M/–IO_DK0 and W/–R_DK2 represents the encoded channel number being serviced at the beginning of DMA acknowledge cycles. If the VL82C486 makes –ADS active during DMA or Master Mode cycles (for local bus accesses), the D/–C_DK1 signal is forced high.                                                                                                     |

| W/-R_DK2       | 68                           | Ю                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Write/Read or DMA Acknowledge bit 2 - When HLDA is low, $W/=R_DK2$ is driven by the local bus master and is decoded with $D/=C_DK1$ and $M/=IO_DK0$ to indicate the type of bus cycle requested.                                                                                                                                                                                                                              |

|                |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | When HLDA is high, W/–R_DK2 is an output signal which along with D/–C_DK1 and M/–IO_DK0 represents the encoded channel number being serviced at the beginning of DMA acknowledge cycles. If the VL82C486 makes –ADS active during DMA or Master Mode cycles (for local bus accesses), the W/–R_DK2 signal indicates whether a local bus read or write cycle is required.                                                      |

| D31-D0         | 17-21, 23-27<br>29-32, 34-51 | Ю                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CPU Data Bus bits 31 through 0 - This is the data bus directly connected to the CPU and other external devices.                                                                                                                                                                                                                                                                                                               |