CARLES IN ANTON making the leading edge work for you Storage Management Products Handbook 1986

## 1986 Storage Management Products Handbook

public performance, or public display of this document without the express written consent of Western Digital Corporation is strictly prohibited. The receipt or possesion of this document does not convey any rights to reproduce or distribute its contents, or to manufacture, use, or sell anything

that it may describe, in whole or in part, without the specific written consent of Western Digital Corporation.

# Making the Leading Edge Work for You

This handbook is designed for you, the engineer. It's intended to be a useful tool, enabling you to make a preliminary evaluation of our products and later, with samples in hand, design our products into your own systems.

The data in these pages have been reviewed by our Marketing, Engineering, Manufacturing, and Quality groups. Now we would like you to review the information we've provided and tell us how we can improve it. Please feel free to suggest any changes, additions, or clarifications that occur to you. And don't hesitate to call to our attention any sins of omission or commission we may have made.

We're eager to help upgrade the quality of information our industry provides to its customers. So, please, help us. Direct your comments to:

WESTERN DIGITAL CORPORATION Literature Department 2445 McCabe Way Irvine, CA 92714 (714) 863-0102

# WESTERN DIGITAL

## Regional and District Sales Offices

### NORTHEASTERN UNITED STATES/EASTERN CANADA

Corporate Place I-95 100 Corporate Place Suite 302 Peabody, MA 01960 (617) 535-5914

111 Madison Avenue Morristown, NJ 07960 (201) 292-1490

## NORTH CENTRAL UNITED STATES

3600 West 80th Street Bloomington, MN 55431 (612) 835-1003

1827 Walden Office Sq. Suite 308 Schaumburg, IL 60195 (312) 397-3111

### SOUTHERN UNITED STATES

3483 Satellite Blvd. Suite 221 Duluth, GA 30136 (404) 476-7704

2300 W. Meadowview Road Suite 209 Greensboro, NC 27407 (919) 299-6733

2611 Westgrove Drive Suite 113 Carrollton, TX 91361 (214) 248-6785

AMTEC CENTER 6405 Congress Avenue Suite 110 Boca Rotan, FL 33431 (305) 994-6900

## WESTERN UNITED STATES/WESTERN CANADA

2302 Martin Street Suite 325 Irvine, CA 92714 (714) 851-1221

5743 Corsa Avenue Suite 201 Westlake Village, CA 91361 (818) 991-2556

201 San Antonio Circle Building E, Suite 172 Mountain View, CA 94040 (415) 941-0216

### INTERNATIONAL OFFICES

Western Digital (U.K.) Ltd. 55 East Street Epsom, Surrey KT17 1BP United Kingdom (03727) 42955

Western Digital Deutschland GmbH Prinzregentenstr. 120 D-8000 Muenchen 80 Federal Republic of Germany (089) 470-7021 Western Digital Corp. 12 Rue Auber 75009 Paris, France (01) 266-1020

Western Digital Japan Ltd. 8th Floor Dai-44 Kowa Bldg 1-2-7, Higashiyama, Meguro-Ku Tokyo 153 Japan (03) 791-2001

## WESTERN DIGITAL

CORPORATION

2445 McCabe Way Irvine, CA 92714

(714) 863-0102

### **Table of Contents**

| Functional Index                                   | vii  |

|----------------------------------------------------|------|

| Numerical Index                                    | ix   |

| System Product Quality/Reliability                 | 1    |

| Quality/Reliability to Leading Edge Technology     | 5    |

| Announcing Burn-In Program Availability/Warranties | 11   |

| HI-Rel "K" Testing Program                         |      |

| Floppy Disk Controller Devices                     | 1-1  |

| Floppy Disk Support Devices                        | 2-1  |

| Winchester Disk Controller Devices                 |      |

| Winchester Disk Support Devices                    | 4-1  |

| SCSI-Bus Interface Controller                      | 5-1  |

| Winchester Board Products                          | 6-1  |

| Tape Drive Controller Products                     | 7-1  |

| Main Memory Devices                                | 8-1  |

| Integrated Drive Electronics                       |      |

| Ordering Information                               |      |

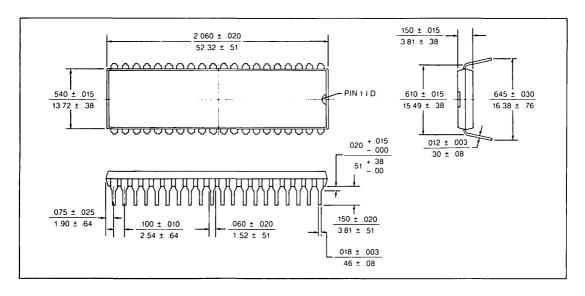

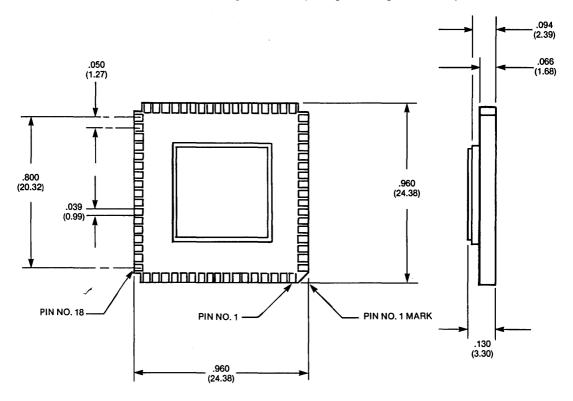

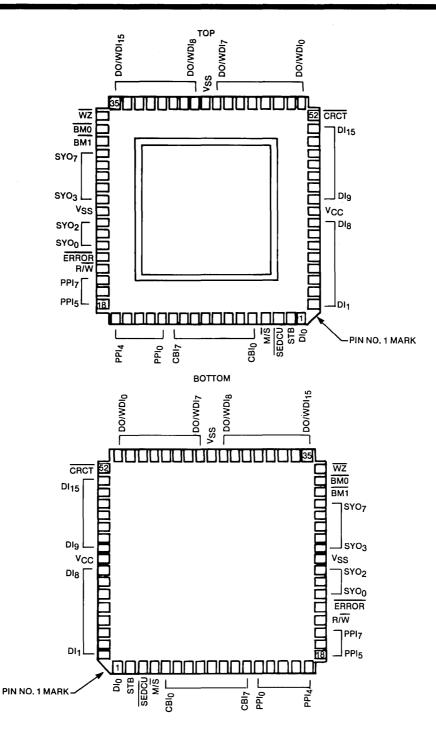

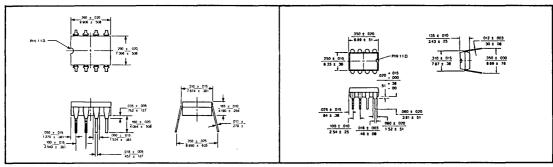

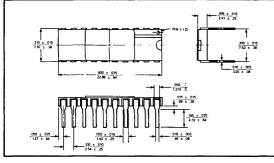

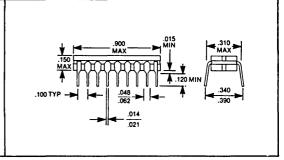

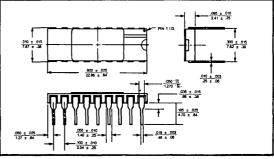

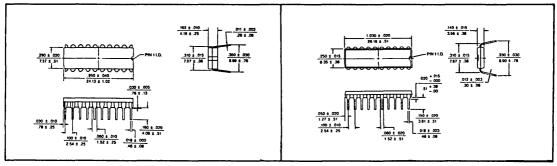

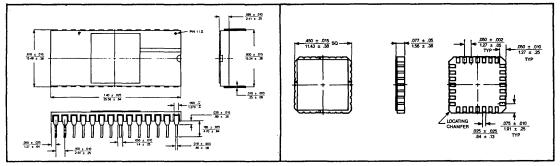

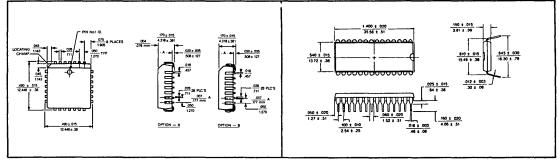

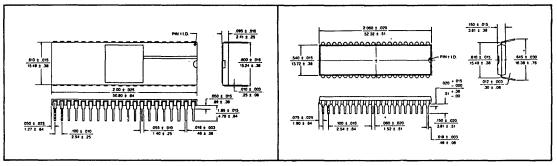

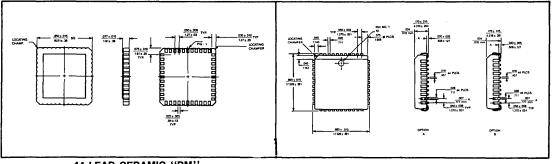

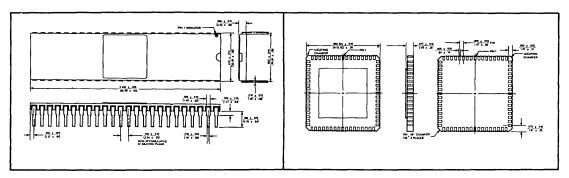

| Package Diagrams                                   | 11-1 |

| Terms and Conditions                               |      |

### Data Sheets with the Heading below:

Advance Information: This product has not been produced in volume and is subject to functional and timing revisions. Prior to designing with the product, it is necessary to contact Western Digital Corporation for current information.

νi

## **Functional Index**

### STORAGE MANAGEMENT PRODUCTS

| FLOPPY DISK CONTROLLER | DEMICES |

|------------------------|---------|

|    | WD177X-00<br>WD177X-00<br>WD1772-02<br>WD1772-02<br>FD179X-02<br>FD179X-02<br>WD279X-02<br>WD279X-02                                                                      | Floppy Disk Formatter/Controller Appl Notes Floppy Disk Formatter/Controller Appl Notes Floppy Disk Formatter/Controller Family Appl Notes Floppy Disk Formatter/Controller Family Appl Notes Appl Notes                                                                                                             | 1-25<br>1-27<br>1-51<br>1-53<br>1-77<br>1-91                                                  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| FL | oppy disk support i                                                                                                                                                       | DEVICES                                                                                                                                                                                                                                                                                                              |                                                                                               |

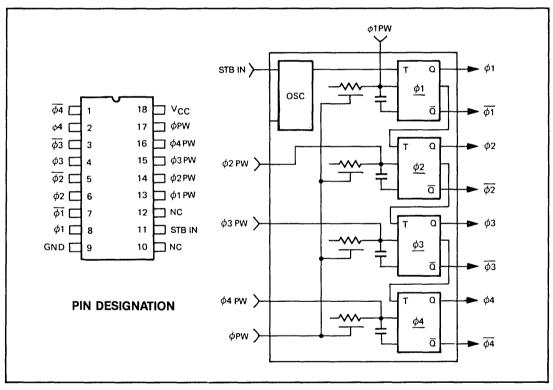

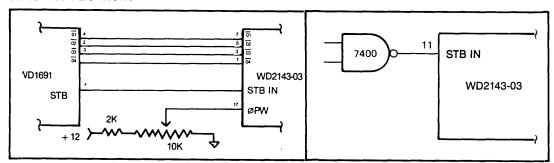

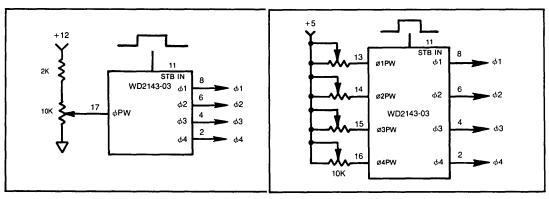

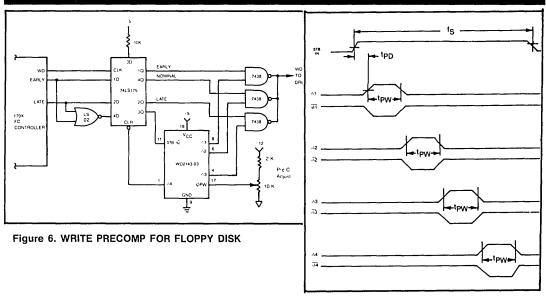

|    | WD1691<br>WD16C92<br>WD2143-03<br>WD9216-00/01<br>WD92C32-00                                                                                                              | Floppy Support Logic Floppy Disk Read/Write Support Four Phase Clock Generator Floppy Disk Data Separator Floppy Digital Data Separator                                                                                                                                                                              | 2-9<br>2-13<br>2-17                                                                           |

| WI | NCHESTER DISK CONT                                                                                                                                                        | FROLLER DEVICES                                                                                                                                                                                                                                                                                                      |                                                                                               |

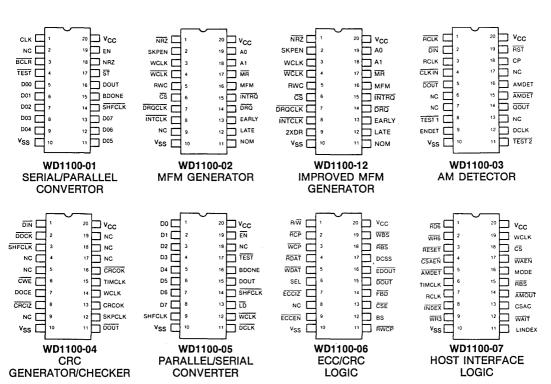

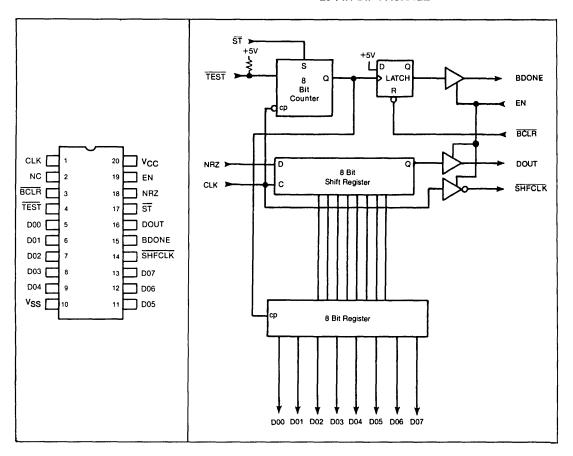

|    | WD1010-05<br>WD1010-05<br>WD1050<br>WD1050<br>WD1100<br>WD1100-01<br>WD1100-03<br>WD1100-04<br>WD1100-05<br>WD1100-06<br>WD1100-07<br>WD1100-09<br>WD1100-12<br>WD2010-05 | Winchester Disk Controller Appl Notes SMD Controller/Formatter Appl Notes Series Winchester Controller Chips Serial/Parallel Converter AM Detector CRC Generator/Checker Parallel/Serial Converter ECC/CRC Logic Host Interface Logic Data Separator Support Logic Improved MFM Generator Winchester Disk Controller | 3-25<br>3-31<br>3-61<br>3-69<br>3-71<br>3-75<br>3-79<br>3-83<br>3-87<br>3-93<br>3-97<br>3-101 |

| wı | NCHESTER DISK SUPP                                                                                                                                                        | ORT DEVICES                                                                                                                                                                                                                                                                                                          |                                                                                               |

| 60 | WD10C20-05<br>WD1014<br>WD1015<br>WD1100-21<br>WD11C00-13<br>WD11C00-17                                                                                                   | Self-Adjusting Data Separator                                                                                                                                                                                                                                                                                        | 4-15<br>4-27<br>4-31<br>4-37                                                                  |

| 3U | SI-BUS INTERFACE CO                                                                                                                                                       | NIROLLER                                                                                                                                                                                                                                                                                                             |                                                                                               |

|    | WD33C92/93                                                                                                                                                                | SCSI-Bus Interface Controller                                                                                                                                                                                                                                                                                        | 5-1                                                                                           |

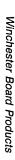

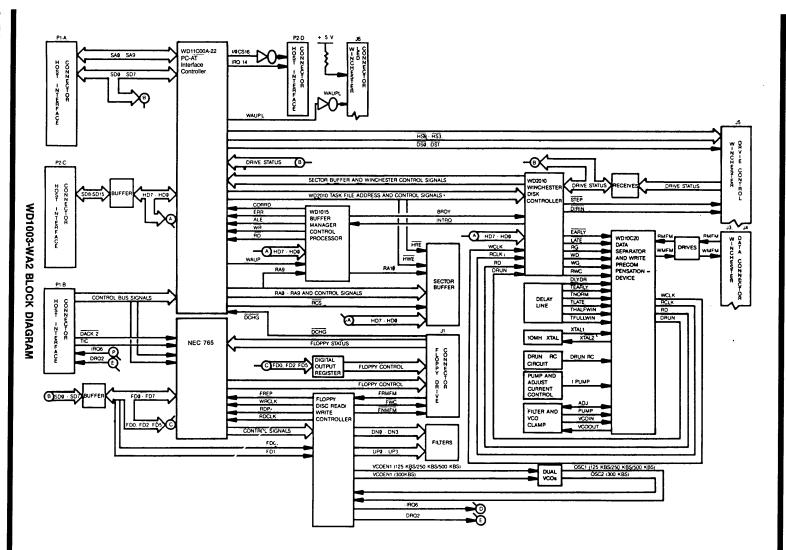

### WINCHESTER BOARD PRODUCTS

| WD1002-05             | Winchester/Floppy Controller        | 6-1        |

|-----------------------|-------------------------------------|------------|

| WD1002-HDO            | Winchester Controller               | 6-11       |

| WD1002-SHD            | Winchester Disk Controller          | 6-19       |

| WD1002-SAS            | Winchester/Floppy Disk Controller   | 6-31       |

| WD1002-WX1            | Winchester Disk Controller          | 6-49       |

| WD1002S-SHD           | Winchester Disk Controller          | 6-51       |

| WD1002C-WX2           | Winchester Controller Board         | 6-89       |

| WD1002S-WX2           | Winchester Controller Board         | 6-91       |

| WD1002-WAH            | Winchester Disk Controller          | 6-119      |

| WD1002-WA2            | Winchester Disk Controller          | 6-137      |

| WD1003-SCS            | Winchester Disk Controller          | 6-157      |

| WD1003-WA2            | Winchester Disk Controller          | 6-173      |

| WD1003-WAH            | Winchester Disk Controller          | 6-175      |

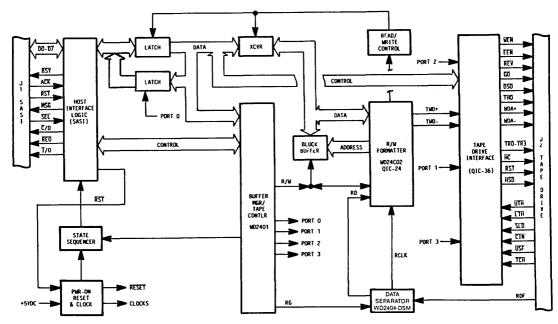

| TAPE DRIVE CONTROLLE  | ER PRODUCTS                         |            |

| WD2401                | Buffer Management Tape Controller   | 7-1        |

| WD2404                | Tape Data Separator Module          | 7-17       |

| WD24C02               | Read/Write Formatter                |            |

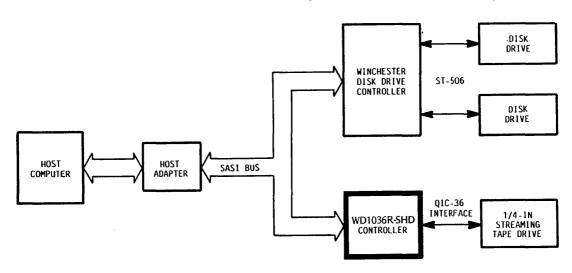

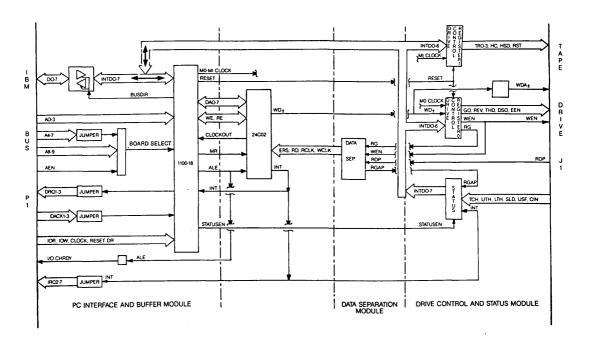

| WD1036R-SHD           | Streaming Tape Controller           | 7-25       |

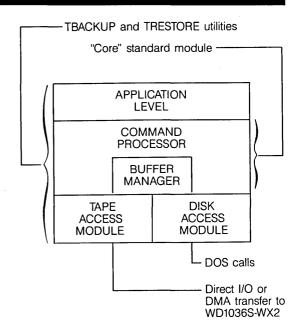

| WD1036S-WX2           | Streaming Tape Controller           | 7-35       |

| MAIN MEMORY DEVICE    |                                     |            |

| WD8206                | Error Detection and Correction Unit | 8-1        |

| INTEGRATED DRIVE ELEC | CTRONICS                            |            |

| WD93020               | Integrated Drives                   | <b>.</b> . |

## **Numerical Index**

| Part Number  | Page        |

|--------------|-------------|

| WD1002-05    | 6-1         |

| WD1002·HDO   | 6-11        |

| WD1002-SAS   | 6-31        |

| WD1002-SHD   | 6-19        |

| WD1002-WAH   | 6-119       |

| WD1002-WA2   | 6-137       |

| WD1002-WX1   | 6-49        |

| WD1002S-SHD  | 6-51        |

| WD1002C-WX2  | 6-89        |

| WD1002S-WX2  | 6-91        |

| WD1003-SCS   | 6-157       |

| WD1003-WAH   | 6-175       |

| WD1003-WA2   | 6-173       |

| WD1010-05    | 3-1         |

| WD1014       | 4-15        |

| WD1015       | 4-27        |

| WD1036R-SHD  | 7-25        |

| WD1036S-WX2  | 7-35        |

| WD1050       |             |

| WD10C20-05   |             |

| WD1100       |             |

| WD1100-01    |             |

| WD1100-03    |             |

| WD1100-04    |             |

| WD1100-05    |             |

| WD1100-06    |             |

| WD1100-07    |             |

| WD1100-09    |             |

| WD1100-12    |             |

| WD1100-21    |             |

| WD11C00-13   |             |

| WD11C00-17   |             |

| WD1691       |             |

| WD16C92      |             |

| WD177X-00    |             |

| WD1772-02    |             |

| FD179X-02    |             |

| WD2010-05    |             |

| WD2143-03    |             |

| WD2401       |             |

| WD2404       |             |

| WD24C02      |             |

| WD279X-02    |             |

| WD33C92/3    |             |

| WD8206       |             |

| WD9216-00/01 |             |

|              |             |

| WD92C32      | 2-21<br>9-1 |

| WD93020      | 9- I        |

х

## System Product Quality/Reliability

### QUALITY PROGRAM DESCRIPTION

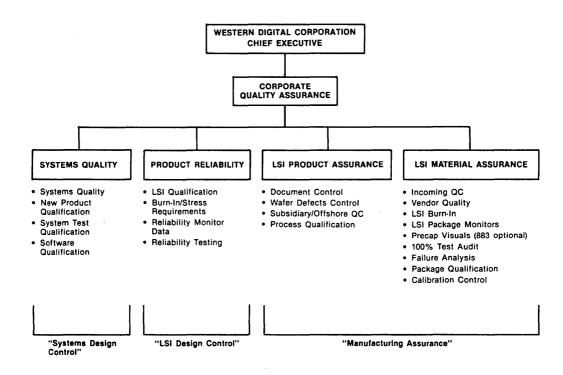

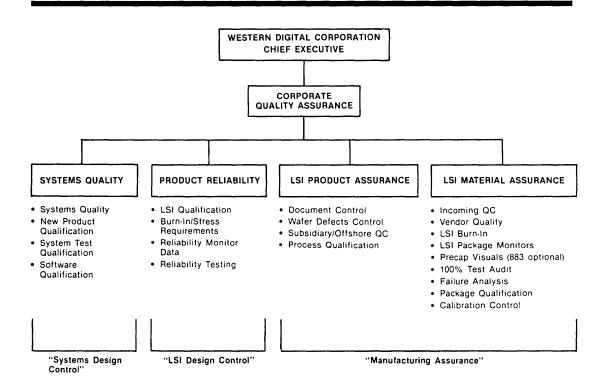

The Quality Organization shown on the attached organization chart (Figure 2) reports directly to the President of Western Digital. It assures compliance to design control, quality, and reliability specifications pursuant to corporate policy. Quality assurance provisions are derived in part from MIL-Q-9858, as applied to high grade commercial products.

### CORPORATE QUALITY POLICY

It is the policy of Western Digital Corporation that every employee be committed to quality excellence in producing products/processes which conform to acceptable requirements. The total quality program is managed and monitored by the quality assurance organization. Quality assurance is chartered to review marketing product requirements, qualify hardware and software designs, certify manufacturing operations and monitor performance/control conformance to product specifications.

Primary responsibility for execution of the quality program rests with functional organizations to design, produce, and market high quality and high reliability products specified to our customers.

### **DESIGNING FOR RELIABILITY**

The premise upon which board and system manufacturing operations are based is that quality is planned and designed-in, not screened-in or selected. A well-tested, high-quality design is far more reliable than a marginal design with any amount of burn-in or fixes. To assure top quality design, Western Digital maintains one of the most experienced board/system design staffs in the industry. A tightly controlled design review team comprising members from Quality Assurance, Marketing, Manufacturing and several experienced design engineers, provides review of each new design several times during its development to ensure widest possible performance margins. The production release procedure assures a checklist for:

- ☑ Characterization Report

- Field Test (Beta Test) Report

- ☑ Software/Diagnostics Qualification

### MAINTAINING QUALITY/RELIABILITY IN PRODUCTION

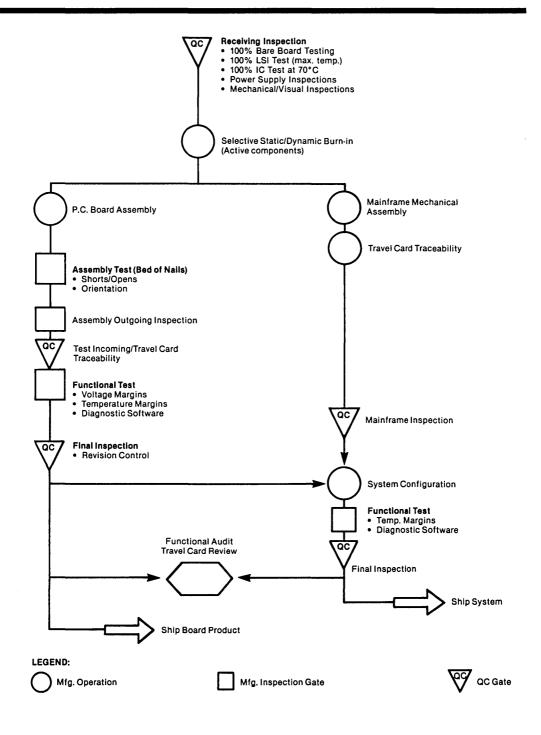

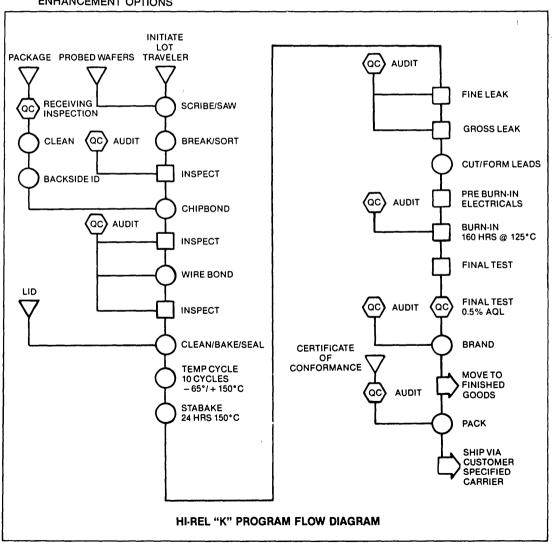

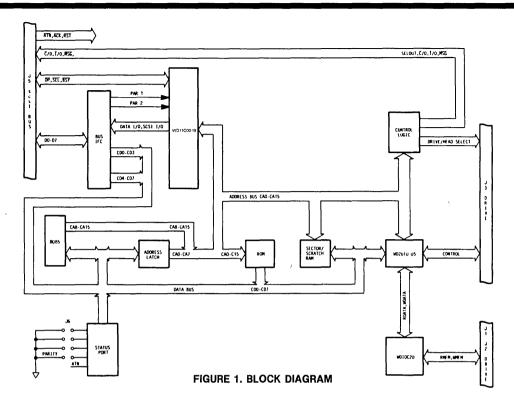

The Quality Control Testing Flow Chart shown on Figure 1 defines the exact stages contained in the production process. Internally manufactured LSI components undergo 100% testing at maximum specified operating temperatures as well as strict quality controls defined to assure high quality and reliability. Components not designed and manufactured by Western Digital are also 100% screened during incoming inspection at 70°C. The tests performed include selective active component burn-in performed at 125°C for 160 hours to insure guaranteed levels of reliability. This 125°C accelerated testing eliminates defects that cannot effectively be accelerated by burning-in boards and systems which have temperature limitations. Key quality control procedures include:

☑ Incoming Inspection Procedure

□ Quality Audit Procedure

### PRODUCT FINAL TEST/CORRECTIVE ACTION

All boards are 100% in-circuit tested and 100% functional tested for acceptable performance according to applicable test specifications on testers qualified by QA. Products are tested at maximum specified temperature and voltage margins using diagnostic software to ensure greater performance margins. Failures are logged on a travel card specifically designed to insure traceability to manufacturing steps and to maintain failure records for QA corrective action.

If the board is designed to perform in a Host system, further diagnostics are performed in an environment configured to actual customer requirements.

### PRODUCT ACCEPTANCE

Upon completing the final test, the board/system undergoes QC final workmanship standards inspection and selective samples are audited to the functional product specification to guarantee quality at specified operating margins to the customer.

Figure 1. QUALITY CONTROL TESTING FLOW CHART

Figure 2. QUALITY ORGANIZATION

# WESTERN DIGITAL

## Quality/Reliability To Leading Edge Technology

#### QUALITY ASSURANCE PROGRAM HIGHLIGHTS

- LSI manufacturing assurance provisions are derived in part from MIL-M-38510 and MIL-STD-883B as applied to high grade commerical components.

- All process raw materials used in the Mask/Wafer fabrication and assembly operations are monitored by Material Assurance.

- Material Assurance maintains a thorough control of incoming material and has developed unique "use/stress tests" (look ahead sample build acceptance) which critical material must pass before acceptance.

- The product assurance Department continuously monitors the internal and external manufacturing flow (shown in Figure 1) and issues process control reports displaying detailed data and trends for the associated areas.

- Document control is an integral part of Product Assurance. All specifications are issued and controlled by this activity.

- The Western Digital Malaysian assembly operation uses specifications and quality control provisions controlled by Document Control. Indicators of Malaysia quality are reviewed weekly.

- Purchased FAB and assembly operations are individually qualified and are certified against standard specifications during vendor qualification and monitored against reliability criteria.

- Defect control within the process assures the highest levels of built-in reliability.

- Quality audits and gates are located throughout the manufacturing process in order to assure a stable process and thus, a quality product to our customers. Figure 1 illustrates the manufacturing/screening/inspection flow diagram and identifies the steps as they relate to the production of LSI devices.

- Testing assures quality margins through 100% testing by manufacturing and, in addition, all products must pass a specified AQL sample test performed by QA at maximum operating temperature as follows:

### **Outgoing Quality Levels**

| SUBGROUPS INSPECTION                                                 | ON LEVEL |

|----------------------------------------------------------------------|----------|

| Subgroup 1-Final 100% Electrical Audit @ Max °C                      | 0.5 AQL  |

| Subgroup 2-Visual (Marking, Lead Integrity, Package, Verify customer |          |

| shipper)                                                             | 1.0 AQL  |

| Subgroup 3-Shipping Visual Audit                                     | 1.0 AQL  |

\*The double sampling techniques used allow considerably better AQL's in most all cases.

LSI devices are 100% tested on industry standard test systems. Quality outgoing testing (auditing) is done on the Fairchild Sentry Series 20 where possible to allow better correlation with customers.

### PROGRAMS TO ASSURE OPTIMUM RELIABILITY

improved levels of reliability are available under custom reliability programs using static and dynamic burn-in to further improve reliability. These programs focus on MOS failure mechanisms as follows:

### **FAILURE MECHANISMS IN MOS**

| FAILURE<br>MECHANISM | EFFECT ON<br>DEVICE | ESTIMATED ACTIVATION ENERGY | SCREENING<br>METHOD                  |

|----------------------|---------------------|-----------------------------|--------------------------------------|

| Slow Trapping        | Wearout             | 1.0 eV                      | Static Burn-In                       |

| Contamination        | Wearout/<br>Infant  | 1.4 eV                      | Static Burn-In                       |

| Surface Charge       | Wearout             | 0.5-1.0 eV                  | Static Burn-In                       |

| Polarization         | Wearout             | 1.0 eV                      | Static Burn-in                       |

| Electromigration     | Wearout             | 1.0 eV                      | Dynamic Burn-in                      |

| Microcracks          | Random              | <u>.</u>                    | 100% Temp. Cycling                   |

| Contacts             | Wearout/<br>Infant  | -                           | Dynamic Burn-in                      |

| Oxide Defects        | Infant<br>Random    | 0.3 eV                      | Dynamic Burn-In at max. voltage      |

| Electron Injection   | Wearout             |                             | Low Temp. Voltage<br>Operating Life. |

### **Temperature Acceleration of Failure**

The Arrhenius Plot defines a failure rate proportional to exp (- Ea/kt) where Ea is the activation energy for the failure mechanism. The figure on the right indicates that lower activation energy failures are not effectively accelerated by temperature alone; hense, maximum voltage operation is selectively applied to optimize the burn-in process.

### Static Burn-In (125°C-48 hours or 160 hours)

Provided on a sample basis for process monitor/control of 0.5 eV - 1.0 eV failure mechanisms. 100% static burn-in may be specified at an additional cost. However, static burn-in is considered only partially effective for internal LSI gates at logic "O" levels.

## Dynamic Burn-In (Pattern test/125°C - 8 hours to 160 hours)

Accelerated functional dynamic operating life effectively controls internal MOS gate defects buried from external pin access. The input pattern is optionally pseudo-random or fixed pattern programmable to simulate 1000-3000 hours of field operation at maximum operating voltage(s).

### High-Rel "K" Testing Program

General conformance to MIL-STD-883B method 5004.4, Class B with static Burn-In (Dynamic Burn-In may be specified as an option).

### **RELIABILITY MEANS LASTING VALUE**

### **DESIGNING FOR RELIABLILITY**

The Production release procedure for an LSI device is designed to assure maximum reliability with a Quality checklist for:

- ☑ Test Program Qualifications

- ☑ Characterization report

- Field test (Beta Test) report

- P Reliability Lifetest Qualifications

- ☑ Infrared Thermal Analysis

- ☑ Static Protection

All New devices and major process changes must pass reliability qualification before incorporation into production using the criteria defined in Tables 2-4. The infrared microscope assures optimum burn-in temperatures and margins of safety. The dynamic burn-in system is one of two custom designed systems which assure protective device isolation during burn-in.

### MAINTAINING RELIABILITY IN PRODUCTION

Process defect controls are defined to continually measure built-in reliability, as measured by the following criteria:

TABLE 1

| PROCESS RELIABILITY CONTROL          | METHOD                                   | CONDITION                                          | SAMPLE*                              |

|--------------------------------------|------------------------------------------|----------------------------------------------------|--------------------------------------|

| Subgroup 1-Defects Control           |                                          |                                                    |                                      |

| a. Oxide Integrity                   | Non-destructive bubble test              | Pinhole defect density                             | 5 wafers                             |

| b.Polysilicon Integrity              | SEM Analysis                             | Visual                                             | 5 wafers                             |

| Subgroup 2-Electro-Migration Control | 1                                        |                                                    |                                      |

| Metal Step Coverage                  | MIL-STD-883<br>Method 2018               | SEM Analysis                                       | 5 wafers                             |

| Subgroup 3-Defect Density            | Critical layers Field Gate Contact Metal | Visual of Photo defects (Defects/in <sup>2</sup> ) | 8 wafers<br>each layer               |

| Subgroup 4-Passivation/Insulation    |                                          |                                                    | 1                                    |

| Priority                             | MIL-STD-883 Method                       | Visual of Pinhole                                  | Final Silox                          |

|                                      | 2021                                     | defect density                                     | 5 wafers<br>Intermediate<br>5 wafers |

Inspection intervals are defined by the in-line process control data reviewed on a lot-by-lot basis.

### LSI RELIABILITY STANDARDS

### **TABLE 2 STANDARD RELIABILITY LEVELS**

| TEST                              | METHOD               | CONDITION         | FAILURE                                    |

|-----------------------------------|----------------------|-------------------|--------------------------------------------|

| Infant<br>Mortality<br>(see note) | Static<br>Burn-In    | 125°C - 160 hrs.  | <0.5%                                      |

| Long Term<br>Failure Rate         | Dynamic<br>Life Test | 125°C - 1000 hrs. | <.05%/1000 hrs.<br>@55°C<br>60% Confidence |

<sup>\*</sup>NOTE: Devices failing the infant mortality target remain in burn-in until acceptable failure rates are obtained.

### TABLE 3 GROUP A DEVICE RELIABILITY MONITORS

| TEST                              | METHOD | CONDITIONS                           | LTPD     |

|-----------------------------------|--------|--------------------------------------|----------|

| Subgroup 1                        |        |                                      |          |

| a.Internal Visual                 |        |                                      | 15       |

| b.Thermal Shock                   | 1011   | Test Failure Used (cond. B or C)     | İ        |

| c.Bond Strength                   | 2011   | Test Failures (cond.B)               |          |

| d.Die Shear Strength              | 2019   | Test Failures                        | 1        |

| Subgroup 2                        |        |                                      |          |

| a.Seal-Gross Leak                 | Ì      | Fluorocarbon detection 10-3          | 15       |

|                                   |        | atm/cc/sec                           | 1        |

| b.Seal-Fine Leak                  | 1014   | Test Condition A                     | <u> </u> |

| Subgroup 3                        |        |                                      | 1        |

| a.Rotating Steady State Life Test | 1005   | Static 160 hr. Burn-In 125°C         | 5        |

| ,                                 |        | plus 125°C Lifetest - 1000 hrs.      |          |

| b.Electrical Parameters           | 1 -    | Final electrical @ 25°C (with data @ | 1        |

|                                   |        | 70°C)                                |          |

### TABLE 4 GROUP B PACKAGE RELIABILITY MONITORS

| TEST                         | METHOD | CONDITIONS                              | LTPD |

|------------------------------|--------|-----------------------------------------|------|

| Subgroup 1                   |        |                                         |      |

| a. Thermal Shock             | 1011   | Test Condition B or C                   | 15   |

| b. Temperature Cycling       | 1010   | Test Condition B or C                   |      |

| c. Seal-Gross Leak           | -      | Fluorocarbon detection 10 <sup>-3</sup> |      |

| d. Seal-Fine Leak (ceramic   | 1014   | Test Conditoin A                        | i i  |

| e. Electrical Parameters     | 10.14  | Electrical at max-C                     | }    |

| f. 85/85 Moisture Resistance | _      | 85% RH/85°C for 1000 hours              |      |

| (plastic only)               |        | PDA = 10%                               |      |

| g.Electrical Parameters      |        | Final electrical @25°C                  | [    |

| Subgroup 2                   |        |                                         |      |

| a. High Temp. Storage        | 1008   | Test Condition B or C                   | 1    |

| b. Mechanical Shock          | 2002   | Test Condition B                        | 15   |

| c. Seal - Gross Leak         |        | Fluorocarbon detection 10 <sup>-3</sup> | 1    |

|                              |        | atm/cc/sec                              |      |

| d. Seal - Fine Leak          | 1014   | Test Condition A                        |      |

| (ceramic)                    |        |                                         |      |

| e. Electrical Parameters     | -      | Final electrical @ 25°C/max. C          |      |

| Subgroup 3                   |        |                                         |      |

| a. Lead Integrity            | 2004   | Test Condition B2                       | 15   |

|                              |        | (Lead Fatigue)                          |      |

| b. Seal - Gross Leak         | -      | Fluorocarbon detection 10 <sup>-3</sup> |      |

|                              |        | atm/cc/sec                              |      |

| c. Seal - Fine Leak          | 1014   | Test Condition A                        | 1    |

| (ceramic)                    |        |                                         |      |

Figure 2 QUALITY ORGANIZATION

# WESTERN DIGITAL

## **Announcing Burn-in Program Availability/Warranties**

Western Digital now supports customer burn-in requirements for both static and dynamic burn-in under the strict control of the QA-Reliability Organization.

This burn-in provides high peformance 125°C static and dynamic burn-in for 8-160 hours to eliminate infant mortality and improve reliability. This process is executed using custom modified 32Bit, AEHR test commerical burn-in equipment which provide monitored fixed pattern or pseudo random burn-in with power supply and resistor device pin isolation.

LSI dynamic burn-in is verified in all cases by the design engineer for proper functioning. LSI Chip sets are also individually burned-in with dynamic equivalency to assure high performance bundled reliability.

The warranty on the program will optionally provide certificate of compliance to standard or custom designed burn-in programs and guarantee <.05%/Khrs failure rate.

### CAUTION

Using outside burn-in methods not certified as acceptable by Western Digital may result in voided warranty, due to mishandling, junction temperature stress, or electrical damage. Further, since most burn-in houses do not support testing, catastrophic system condition can result in substantial damage before a problem is identified.

One consistent problem experienced with outside LSI burn-in houses can cause reliability problems; namely, parallelling totem pole MOS outputs, where the output states are not predictable, can cause a single (or a few) device(s) to sink all the current from the other devices on the burn-in tray - electromigration or current zaps are both possible.

Western Digital burn-in diagrams, dated after 1/1/82, must be used exactly as shown and will be provided upon request.

SEE YOUR LOCAL REPRESENTATIVE FOR COSTS AND ORDERING INFORMATION ON THIS NEW PROGRAM.

# WESTERN DIGITAL

# Hi-Rel "K" Testing Program

### **FEATURES**

GENERAL CONFORMANCE TO MIL-STD-883B, METHOD 5004.4, CLASS B (SEE COMPARISON ON FOLLOWING PAGES)

### INCLUDES:

PRECAP VISUALS

SEAL INTEGRITY

POWER CONDITIONING

ENHANCEMENT OPTIONS

### **GENERAL DESCRIPTION**

Western Digital's Hi-Rel "K" program is designed to provide high reliability devices for extended temperature environments. Individual enhancements may be specified to meet a customer's requirements.

### COMPARISON OF MIL-STD-883 AND HI-REL "K" TEST PROGRAM

| MIL-STD-883B, METHOD 5004.4, CLASS B                                                                                                                                              | HI-REL "K" TEST                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1.1 Internal Visual                                                                                                                                                             |                                                                                                                                                                             |

| Method 2010.3<br>Test Condition B                                                                                                                                                 | All Hi-Rel "K" devices receive 100% inspections prior to lid seal. These inspections together comprise criteria comparable to Mil-Std-883, method 2010.3, test condition B. |

| 3.1.2 Stabilization Bake Method 1008.1 Test condition C 24 hours at 150°C                                                                                                         | Same                                                                                                                                                                        |

| 3.1.3 Temperature Cycling Method 1010.2, Test condition C -65°C to 150°C for 10 cycles, with 10 minutes dwell and 5 minutes maximum transfer time                                 | Same                                                                                                                                                                        |

| 3.1.4 Constant Acceleration Method 2001.2, Test condition E 30,000 G stress level 3.1.5 Visual Inspection                                                                         | Not done Unless Specified                                                                                                                                                   |

| Visual inspection for catastrophic failures after screens                                                                                                                         | Same                                                                                                                                                                        |

| <ul> <li>3.1.6 Seal Method 1014.2</li> <li>(a) Helium fine leak - Test condition A<sub>1</sub>. Bomb condition 2 hours at 60 psig. Reject limit 5x10<sup>-8</sup> torr</li> </ul> | Same                                                                                                                                                                        |

| (b) Fluorocarbon gross leak - Test condition C                                                                                                                                    | Same                                                                                                                                                                        |

| 3.1.9 Interim (pre-burn-in) Electricals Per applicable device specification                                                                                                       | Preburn-in test at 25°C. Must meet requirements of device data sheets.                                                                                                      |

| 3.1.10 Burn-in Test<br>Method 1015.2 160 hours @ 125°C                                                                                                                            | Same                                                                                                                                                                        |

| 3.1.13 Interim (Post burn-in) electricals Per applicable device specification                                                                                                     | Burn-in equipment isolate failures automatically to assure no harmful interaction.                                                                                          |

| 3.1.15 Final Electrical Test (a) Static Tests (1) 25°C                                                                                                                            | Same                                                                                                                                                                        |

| (2) Minimum and Maximum Operating Temperatures (b) Dynamic and Switching Tests at 25°C (c) Functional Tests at 25°C                                                               |                                                                                                                                                                             |

| 3.1.17 Qualification or Quality Conformance Inspection and Test Sample Selection                                                                                                  | Not done unless specified using method 5005 as a guide.                                                                                                                     |

| 3.1.18 External Visual<br>Method 2009.2                                                                                                                                           | Same                                                                                                                                                                        |

| WESTERN DIGITAL RELIABILITY ENHANCEMENT OPTIONS                                                                                                                                   | Extended High Temperature Storage                                                                                                                                           |

| 100% Temperature Testing                                                                                                                                                          |                                                                                                                                                                             |

| Level                                                                                                                                                                             | + 150°C for 24 hours standard, other time/tempera<br>ture storage requirements available required.                                                                          |

| Thermal, Shock (Liquid to Liquid)                                                                                                                                                 | Dynamic Burn-In                                                                                                                                                             |

| Level                                                                                                                                                                             | Per note previously supplied.                                                                                                                                               |

# WESTERN DIGITAL

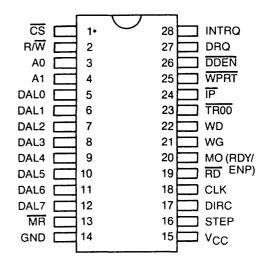

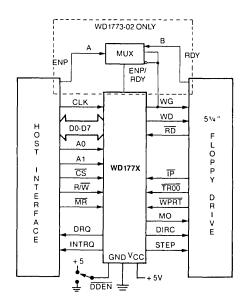

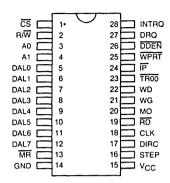

## WD177X-00 Floppy Disk Formatter/Controller

#### **FEATURES**

- 28 PIN DIP

- SINGLE 5V SUPPLY

- BUILT-IN DIGITAL DATA SEPARATOR

- BUILT-IN WRITE PRECOMPENSATION

- SINGLE (FM) AND DOUBLE (MFM) DENSITY

- MOTOR CONTROL (WD1770 AND WD1772)

- 128, 256, 512 OR 1024 SECTOR LENGTHS

- TTL COMPATIBLE

- 8-BIT BI-DIRECTIONAL DATA BUS

- TWO VERSIONS AVAILABLE WD1770/WD1773 = STANDARD 179X STEP RATES WD1772 = FASTER STEP RATES

- THE WD1773 HAS 100% COMPATIBLE SOFT-WARE WITH THE WD1793

### **GENERAL DESCRIPTION**

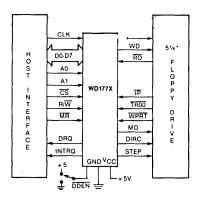

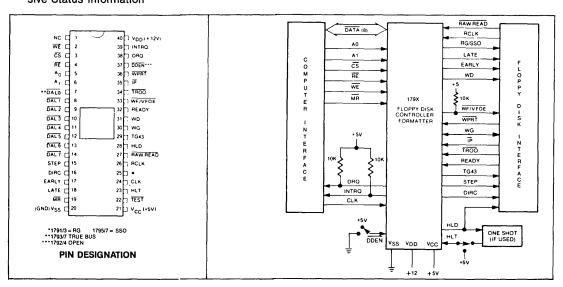

The WD177X-00 is a MOS/LSI device which performs the functions of a Floppy Disk Formatter/Controller. It is similar to its predecessor, the FD179X, but also contains a digital data separator and write precompensation circuitry. The drive side of the interface needs no additional logic except for buffers/receivers. It is designed for single (FM) or double (MFM) density operation.

The WD177X-00 is implemented in NMOS silicon gate technology and is available in a 28-pin dual-in-line as well as in quad pack.

Three versions of the WD177X-00 are available. The WD1770, WD1772 and the WD1773.

With the exception of the enable precomp/ready line, the WD1773 is identical to the WD1770 controller. It is fully software compatible with the WD1793. The WD1770-00 and WD1773-00 are compatible with the FD179X stepping rates, while the WD1772-00 offers stepping rates of 2, 3, 6, and 12 msec.

The WD177X-00 devices all contain a built-in digital data separator which virtually eliminates all external components and adjustments associated with data

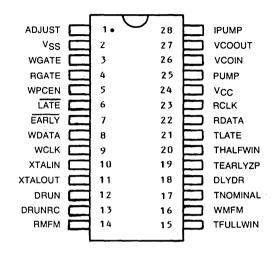

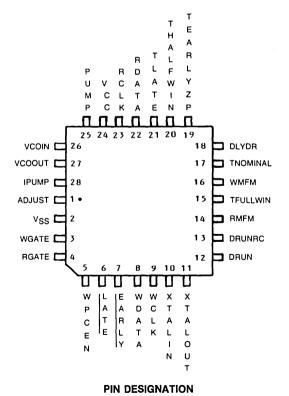

### **DIP PIN DESIGNATION**

recovery in previous designs. A single read line (RD, Pin 19) is the only input required to recover serial FM or MFM data from the disk drive. The device is designed for control of floppy disk drives with data rates of 125 KBits/Sec (single density) and 250 KBits/Sec (double density). In addition, write precompensation of 125 nsec from nominal is enabled at any point through simple software commands. Another programmable feature on the WD1770/WD1772 is Motor On, which enables the spindle motor automatically prior to operating a selected drive.

The processor interface consists of an 8-bit bidirectional bus for transfer of status, data, and commands. All Host communication with the drive occurs through these lines. They are capable of driving one standard TTL load or three LS loads.

| PIN<br>NUMBER | MNEMONIC        | SIGNAL NAME                         | I/O | FUNCTION                                                                                                                                                                                                                                              |

|---------------|-----------------|-------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | <u>cs</u>       | CHIP SELECT                         | 1   | A logic low on this input selects the chip and enables Host communication with the device.                                                                                                                                                            |

| 2             | R/W             | READ/WRITE                          | I   | A logic high on this input controls the placement of data on the D0-D7 lines from a selected register, while a logic low causes a write operation to a selected register.                                                                             |

| 3,4           | A0,A1           | ADDRESS 0,1                         | l   | These two inputs select a register to Read/Write data: $\overline{\text{CS}}$ A1 A0 R/ $\overline{\text{W}}$ = 1 R/ $\overline{\text{W}}$ = 0 0 0 0 Status Reg Commad Reg 0 0 1 Track Reg Track Reg 0 1 0 Sector Reg Sector Reg 0 1 Data Reg Data Reg |

| 5-12          | DAL0-DAL7       | DATA ACCESS<br>LINES<br>0 THROUGH 7 | 1/0 | Eight-bit bi-directional bus used for transfer of data, control, or status. This bus is enabled by CS and R/W. Each line will drive one TTL load.                                                                                                     |

| 13            | MR              | MASTER RESET                        | I   | A logic low pulse on this line resets the device and initializes the Status Register (internal pull-up).                                                                                                                                              |

| 14            | GND             | GROUND                              |     | Ground.                                                                                                                                                                                                                                               |

| 15            | V <sub>cc</sub> | POWER SUPPLY                        | ı   | +5V±5% power supply input.                                                                                                                                                                                                                            |

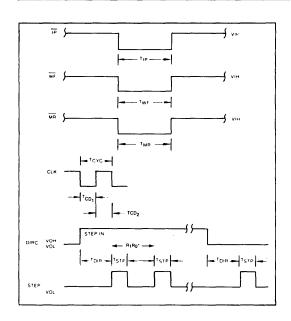

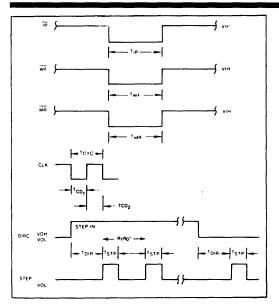

| 16            | STEP            | STEP                                | 0   | The Step output contains a pulse for each step of the drive's R/W head. The WD1770-00 and WD1772-00 offer different step rates.                                                                                                                       |

| 17            | DIRC            | DIRECTION                           | 0   | The Direction output is high when stepping in towards the center of the diskette, and low when stepping out.                                                                                                                                          |

| 18            | CLK             | CLOCK                               | I   | This input requires a free-running 50% duty cycle clock (for internal timing) at 8 MHz +0.1%.                                                                                                                                                         |

| 19            | RD              | READ DATA                           | ı   | This active low input is the raw data line containing both clock and data pulses from the drive.                                                                                                                                                      |

| 20            | RDY/ENP         | READY/ENABLE<br>PRECOMP<br>(WD1773) | I   | Serves as a READY input from the drive during READ/STEP operations and as a Write Precomp enable during Write operations. The state of READY is latched upon WG true, and this dual input is used for precompensation enable.                         |

| 20            | МО              | MOTOR ON<br>(WD1770 or<br>WD-1772)  | 0   | Active high output used to enable the spindle motor prior to read, write or stepping operations. (WD1770, WD1772 only)                                                                                                                                |

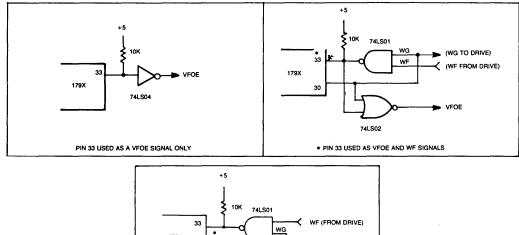

| 21            | wg              | WRITE GATE                          | 0   | This output is made valid prior to writing on the diskette.                                                                                                                                                                                           |

| 22            | WD              | WRITE DATA                          | 0   | FM or MFM clock and data pulses are placed on this line to be written on the diskette.                                                                                                                                                                |

| 23            | TR00            | TRACK 00                            | ı   | This active low input informs the WD1770-00 that the drive's R/W heads are positioned over Track zero.                                                                                                                                                |

| 24            | ĪP              | INDEX PULSE                         | 1   | This active low input informs the WD1770-00 when the physical index hole has been encountered on the diskette.                                                                                                                                        |

| 25            | WPRT            | WRITE PROTECT                       | 1   | This input is sampled whenever a Write Command is received. A logic low on this line will prevent any Write Command from executing (internal pull-up).                                                                                                |

| PIN<br>NUMBER | MNEMONIC | SIGNAL NAME                 | 1/0 | FUNCTION                                                                                                                                |

|---------------|----------|-----------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

| 26            | DDEN     | DOUBLE<br>DENSITY<br>ENABLE | I   | This input pin selects <u>either</u> single (FM) or double (MFM) density. When DDEN = 0, double density is selected (internal pull-up). |

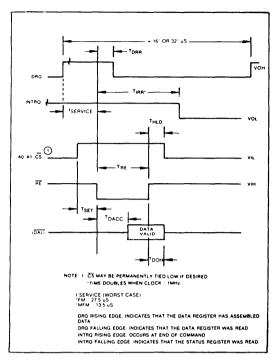

| 27            | DRQ      | DATA REQUEST                | 0   | This active high output indicates that the Data Register is full (on a Read) or empty (on a Write operation).                           |

| 28            | INTRQ    | INTERRUPT<br>REQUEST        | 0   | This active high output is set at the completion of any command, is reset by a read of the Status Register.                             |

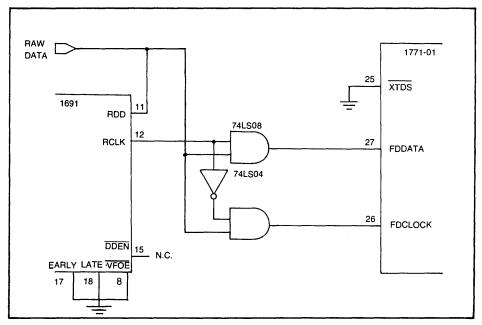

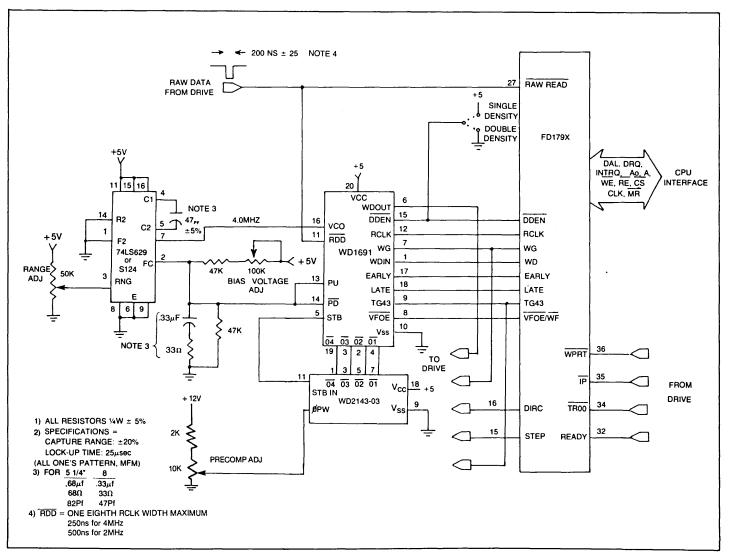

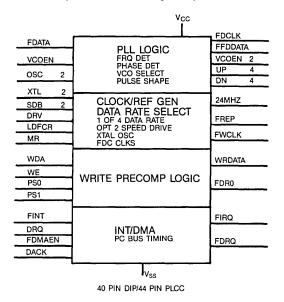

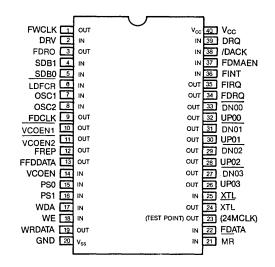

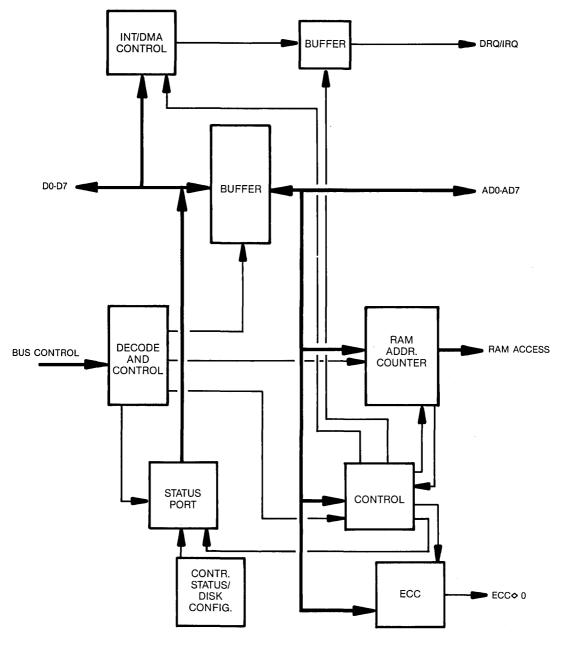

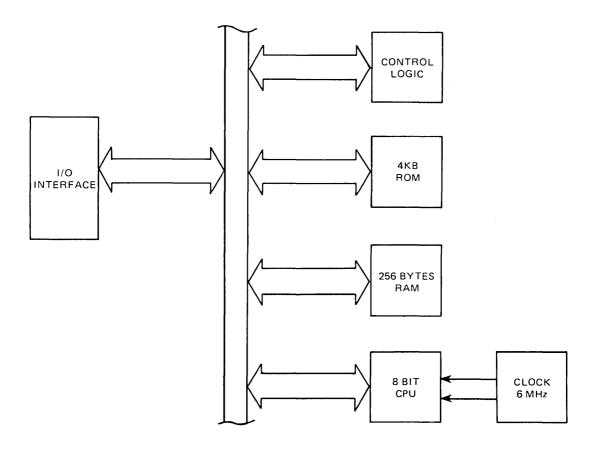

WD177X-02 SYSTEM BLOCK DIAGRAM

### **ARCHITECTURE**

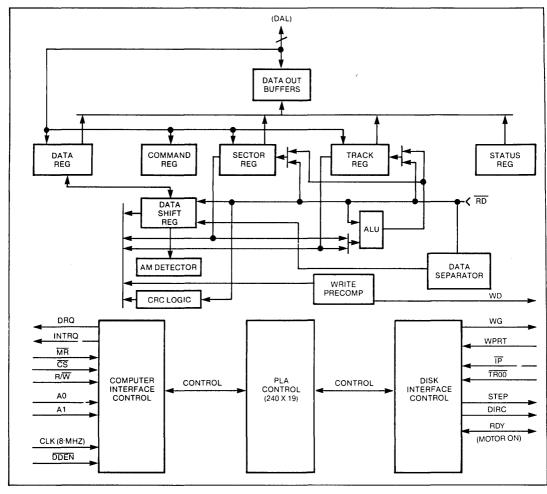

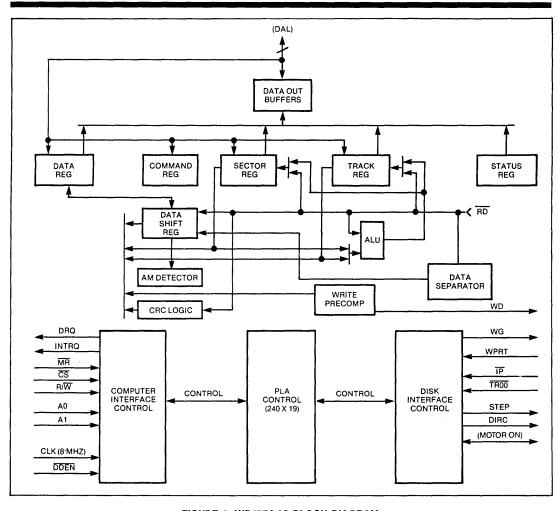

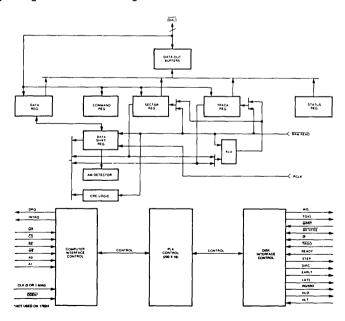

The primary sections of the Floppy Disk Formatter are the Parallel Processor Interface and the Floppy Disk Interface.

Data Shift Register – This 8-bit register assembles serial data from the Read Data input (RD) during Read operations and transfers serial data to the Write Data output during Write operations.

Data Register – This 8-bit register is used as a holding register during Disk Read and Write operations. In disk Read operations, the assembled data byte is transferred in parallel to the Data Register from the Data Shift Register. In Disk Write operations, information is transferred in parallel from the Data Register to the Data Shift Register.

When executing the Seek Command, the Data Register holds the address of the desired Track posi-

tion. This register is loaded from the DAL and gated onto the DAL under processor control.

Track Register – This 8-bit register holds the track number of the current Read/Write head position. It is incremented by one every time the head is stepped in and decremented by one when the head is stepped out (towards track 00). The contents of the register are compared with the recorded track number in the ID field during disk Read, Write, and Verify operations. The Track Register can be loaded from or transferred to the DAL. This Register is not loaded when the device is busy.

Sector Register (SR) – This 8-bit register holds the address of the desired sector position. The contents of the register are compared with the recorded sector number in the ID field during disk Read or Write operations. The Sector Register contents can be loaded from or transferred to the DAL. This register is not loaded when the device is busy.

Command Register (CR) – This 8-bit register holds the command presently being executed. This register is not loaded when the device is busy unless the new command is a force interrupt. The Command Register is loaded from the DAL, but not read onto the DAL.

Status Register (STR) – This 8-bit register holds device Status information. The meaning of the Status bits is a function of the type of command previously executed. This register is read onto the DAL, but not loaded from the DAL.

CRC Logic – This logic is used to check or to generate the 16-bit Cyclic Redundancy Check (CRC). The polynomial is:

$G(x) = x^{16} + x^{12} + x^5 + 1.$

The CRC includes all information starting with the address mark and up to the CRC characters. The CRC Register is preset to ones prior to data being shifted through the circuit.

Arithmetic/Logic Unit (ALU) - The ALU is a serial comparator, incrementer, and decrementer and is used for register modification and comparisons with the disk recorded ID field.

FIGURE 1. WD177X-00 BLOCK DIAGRAM

Timing and Control – All computer and Floppy Disk interface controls are generated through this logic. The internal device timing is generated from an external crystal clock. The WD177X-00 has two different modes of operation according to the state of DDEN.

When  $\overline{\text{DDEN}} = 0$ , double density (MFM) is enabled. When  $\overline{\text{DDEN}} = 1$ , single density is enabled.

AM Detector – The address mark detector detects ID, data and index address marks during read and write operations.

Data Separator – A digital data separator consisting of a ring shift register and data window detection logic provides read data and a recovery clock to the AM detector.

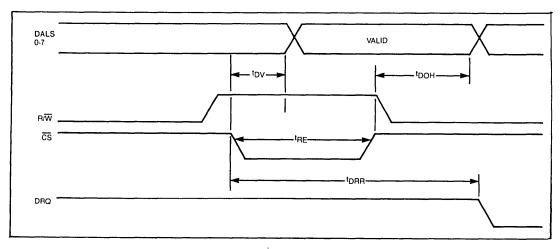

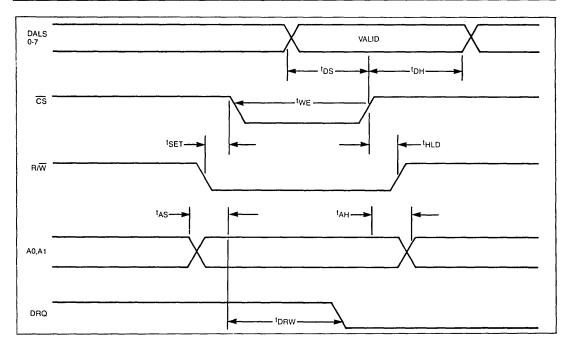

### PROCESSOR INTERFACE

The interface to the processor is accomplished through the eight Data Access Lines (DAL) and associated control signals. The DAL are used to transfer Data, Status, and Control words out of, or into the WD177X-00. The DAL are three state buffers that are enabled as output drivers when  $\overline{CS}$  and  $\overline{R/W} = \underline{1}$  are active or act as input receivers when  $\overline{CS}$  and  $\overline{R/W} = 0$  are active.

When transfer of data with the Floppy Disk Controller is required by the Host processor, the device address is decoded and  $\overline{CS}$  is made low. The address bits A1 and A0, combined with the signal  $\overline{R/W}$  during a Read operation or Write operation are interpreted as selecting the following registers:

|   | A1 - | - A0 | READ $(R/\overline{W} = 1)$ | WRITE $(R/\overline{W} = 0)$ |

|---|------|------|-----------------------------|------------------------------|

|   | 0    | 0    | Status Register             | Command Register             |

| 1 | 0    | 1    | Track Register              | Track Register               |

|   | 1    | 0    | Sector Register             | Sector Register              |

|   | 1    | 1    | Data Register               | Data Register                |

After any register is written to, the same register cannot be read from until 16  $\mu sec$  in MFM or 32  $\mu sec$  in FM have elapsed.

During Direct Memory Access (DMA) types of data transfers between the Data Register of the WD177X-00 and the processor, the Data Request (DRQ) output is used in Data Transfer control. This signal also appears as status bit 1 during Read and Write operations.

On Disk Read operations the Data Request bit is activated (set high) when an assembled serial input byte is transferred in parallel to the Data Register. This bit is cleared when the Data Register is read by the processor. If the Data Register is read after one or more characters are lost, by having new data transferred into the register prior to processor readout, the Lost Data bit is set in the Status Register. The Read operations continue until the end of sector is reached.

On Disk Write operations the Data Request bit is activated when the Data Register transfers its contents to the Data Shift Register, and requires a new data byte. It is reset when the Data Register is loaded with new data by the processor. If new data is not loaded at the time the next serial byte is required by the Floppy Disk, a byte of zeroes is written on the diskette and the Lost Data bit is set in the Status Register.

At the completion of every command an INTRQ is generated. INTRQ is reset by either reading the Status Register or by loading the Command Register with a new command. In addition, INTRQ is generated if a Force Interrupt Command condition is met.

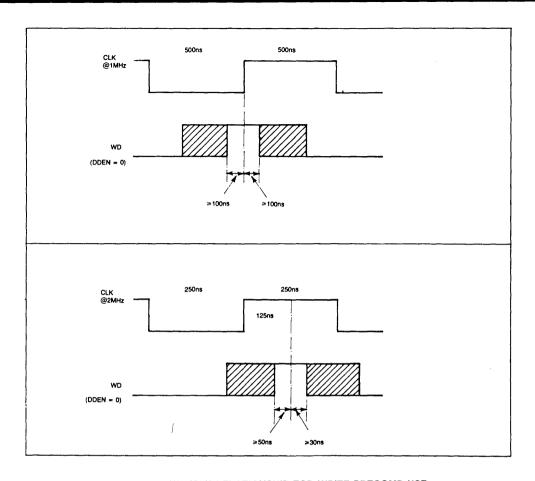

The WD177X-00 has two modes of operation according to the state DDEN. When DDEN = 1, single density is selected. In either case, the CLK input is at 8 MHz.

### **GENERAL DISK READ OPERATIONS**

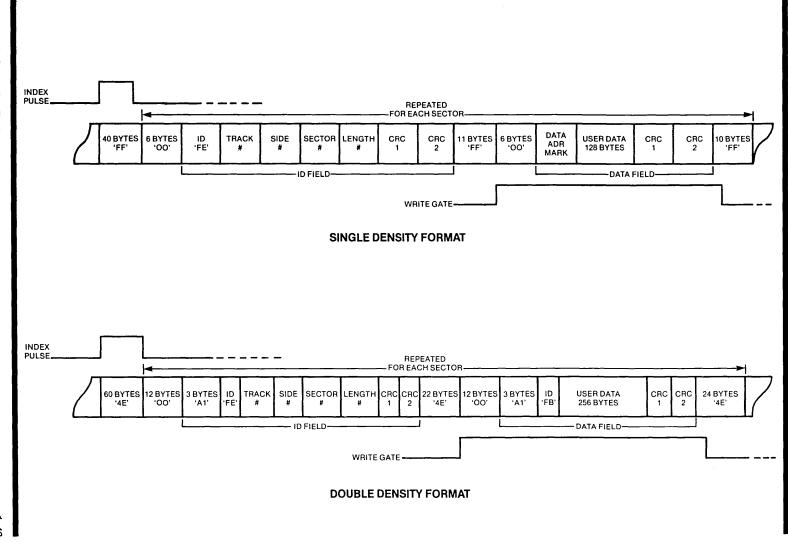

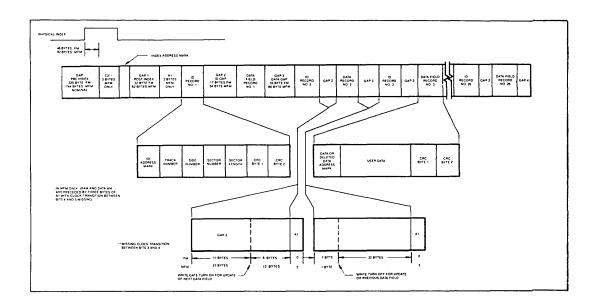

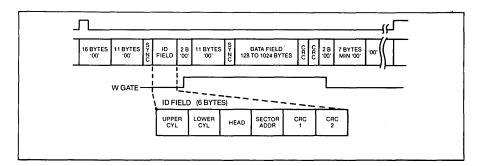

Sector lengths of 128, 256, 512 or 1024 are obtainable in either FM or MFM formats. For FM, DDEN is placed to logical 1. For MFM formats, DDEN is placed to a logical 0. Sector lengths are determined at format time by the fourth byte in the ID field.

| SECTOR LENGTH TABLE          |                                     |  |  |  |

|------------------------------|-------------------------------------|--|--|--|

| SECTOR LENGTH<br>FIELD (HEX) | NUMBER OF BYTES IN SECTOR (DECIMAL) |  |  |  |

| 00                           | 128                                 |  |  |  |

| 01                           | 256                                 |  |  |  |

| 02                           | 512                                 |  |  |  |

| 03                           | 1024                                |  |  |  |

The number of sectors per track for the WD177X-00 are from 1 to 240. The number of tracks for the WD177X-00 are 0 to 240.

### GENERAL DISK WRITE OPERATION

When writing on the diskette the WG output is activated, allowing current to flow into the Read/Write head. As a precaution to erroneous writing the first data byte is loaded into the Data Register in response to a Data Request from the device before the WG is activated.

Writing is inhibited when the WPRT input is asserted, in which case any Write Command is immediately terminated, an interrupt is generated and the Write Protect Status bit is set.

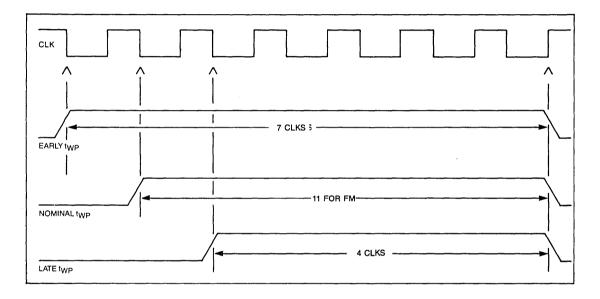

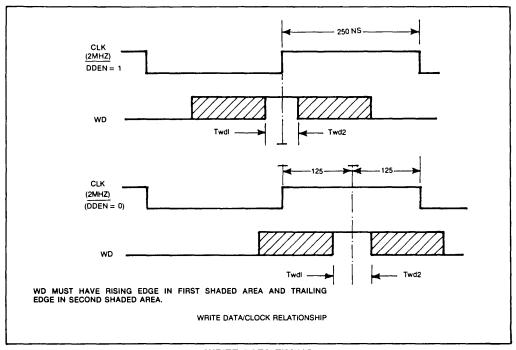

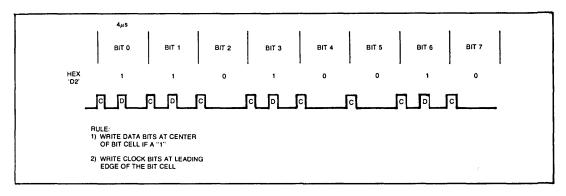

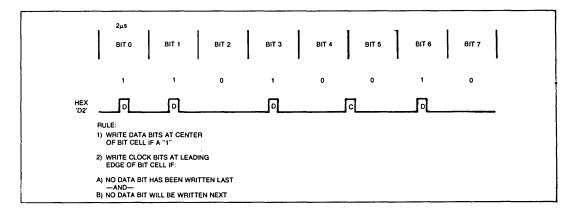

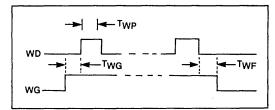

For Write operations, the WD177X-00 provides WG to enable a Write condition, and WD which consists of a series of active high pulses. These pulses contain both Clock and Data information in FM and MFM. WD provides the unique missing clock patterns for recording Address Marks.

The WD1773-00 enables write precompensation when RDY/ENP is asserted. When WG is asserted the READY status has been latched. WG is then used to demultiplex drive Ready Status from Host supplied enable for write precompensation at desired tracks.

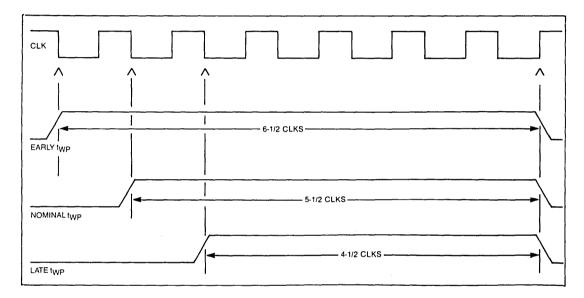

On the WD1770-02 or WD1772-00, the Precomp Enable bit in Write Commands allows automatic Write precompensation to take place. The outgoing Write Data stream is delayed or advanced from nominal by 125 nsec according to the following table:

| - 1      | PATT | ERN                                                        |   | MFM   | FM  |  |

|----------|------|------------------------------------------------------------|---|-------|-----|--|

| X        | 1    | 1                                                          | 0 | Early | N/A |  |

| X        | 0    | 1                                                          | 1 | Late  | N/A |  |

| 0        | 0    | 0                                                          | 1 | Early | N/A |  |

| 1        | 0    | 0                                                          | 0 | Late  | N/A |  |

| <b>A</b> |      | Next Bit to be sent Current Bit sending Previous Bits sent |   |       |     |  |

Precompensation is typically enabled on the innermost tracks where bit shifts usually occur and bit density is at its maximum. READY is true for read/write operations (all Type II and III Command executions).

### COMMAND DESCRIPTION

The WD177X-00 accepts 11 commands. Command words are only loaded in the Command Register when the Busy Status bit is off (Status bit 0). The one exception is the Force Interrupt Command. Whenever a command is being executed, the Busy Status bit is set. When a command is completed, an interrupt is generated and the Busy Status bit is reset. The Status Register indicates whether the completed command encountered an error or was fault free. Commands are divided into four types and are summarized in the following pages.

#### COMMAND SUMMARY

|     |              |   |   |   | В | ITS |    |                |                |

|-----|--------------|---|---|---|---|-----|----|----------------|----------------|

| TY  | PE COMMAND   | 7 | 6 | 5 | 4 | 3   | 2  | 1              | 0              |

|     | Restore      | 0 | 0 | 0 | 0 | h   | ٧  | r <sub>1</sub> | r <sub>o</sub> |

| 1   | Seek         | 0 | 0 | 0 | 1 | h   | ٧  | r <sub>1</sub> | ro             |

| . 1 | Step         | 0 | 0 | 1 | u | h   | ٧  | r <sub>1</sub> | ro             |

| 1   | Step-in      | 0 | 1 | 0 | u | h   | ٧  | r <sub>1</sub> | r <sub>o</sub> |

|     | Step-out     | 0 | 1 | 1 | u | h   | ٧  | r              | r <sub>o</sub> |

| 11  | Read Sector  | 1 | 0 | 0 | m | h/s | Ε  | 0/C            | Ŏ              |

| 11  | Write Sector | 1 | 0 | 1 | m | h/s | Ε  | P/C            | a <sub>n</sub> |

| 111 | Read         |   |   |   |   |     |    |                | Ĭ              |

| 1   | Address      | 1 | 1 | 0 | 0 | h/o | Ε  | 0              | 0              |

| 111 | Read Track   | 1 | 1 | 1 | 0 | h/o | Ε  | 0              | 0              |

| 111 | Write Track  | 1 | 1 | 1 | 1 | h/o | Ε  | P/O            | 0              |

| IV  | Force        |   |   |   |   |     |    |                |                |

|     | Interrupt    | 1 | 1 | 0 | 1 | l₃  | 12 | l <sub>1</sub> | lo             |

### **FLAG SUMMARY**

| 11661                                                                   | COMMA                                                             | INDS                                                               |                               |  |  |

|-------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------|--|--|

| h = M                                                                   | h = Motor On Flag (Bit 3) (1770/2).                               |                                                                    |                               |  |  |

|                                                                         | h = 0, Enable Spin-up Sequence<br>h = 1, Disable Spin-up Sequence |                                                                    |                               |  |  |

| $V = V_0$                                                               | erify Fla                                                         | g (Bit 2) (1770/2/                                                 | 3)                            |  |  |

|                                                                         | No Ver                                                            | ify<br>on Destination 1                                            | Frack                         |  |  |

| r <sub>1</sub> , r <sub>0</sub> = Stepping Rate (Bits 1,0)<br>WD1770-00 |                                                                   |                                                                    |                               |  |  |

|                                                                         |                                                                   | WD1770-00                                                          |                               |  |  |

| r <sub>1</sub>                                                          | ro                                                                | WD1770-00<br>WD1773-00                                             | WD1772-00                     |  |  |

| - r <sub>1</sub> 0                                                      | <b>r</b> <sub>0</sub>                                             |                                                                    | WD1772-00<br>6 ms             |  |  |

|                                                                         |                                                                   | WD1773-00                                                          |                               |  |  |

| 0                                                                       |                                                                   | WD1773-00<br>6 ms                                                  | 6 ms                          |  |  |

| 0                                                                       | 0                                                                 | WD1773-00<br>6 ms<br>12 ms                                         | 6 ms<br>12 ms                 |  |  |

| 0<br>0<br>1<br>1                                                        | 0<br>1<br>0<br>1                                                  | WD1773-00<br>6 ms<br>12 ms<br>20 ms                                | 6 ms<br>12 ms<br>2 ms<br>3 ms |  |  |

| 0<br>0<br>1<br>1<br>u = U                                               | 0<br>1<br>0<br>1                                                  | WD1773-00<br>6 ms<br>12 ms<br>20 ms<br>30 ms<br>ag (Bit 4) (1770/2 | 6 ms<br>12 ms<br>2 ms<br>3 ms |  |  |

| TYPE | 111 & 11 | COMM | ANDS |

|------|----------|------|------|

| m =              | Multiple Sector Flag (Bit 4) (1770/2/3)                                                   |

|------------------|-------------------------------------------------------------------------------------------|

|                  | 0, Single Sector 1, Multiple Sector                                                       |

|                  | Motor on Flag (Bit 3) (1770/2)                                                            |

|                  | 0, Enable Spin-up Sequence<br>1, Disable Spin-up Sequence                                 |

| <b>s</b> =       | Side Compare Flag (Bit 3) (1773 only)                                                     |

| s =              | 0, Compare for side 0<br>1, Compare ;for side 1<br>III Type III commands bit 3 must be 0. |

| a <sub>0</sub> = | Data Address Mark (Bit 0) (1770/2/3)                                                      |

a<sub>0</sub> = 0, Write Normal Data Mark

a<sub>0</sub> = 1, Write Deleted Data Mark

### TYPE II & III COMMANDS (Continued)

E = 0, No Delay

E = 1, Add 30ms Delay (1772 Add 15ms Delay\*

C = Side Compare Flag (Bit 1) (1773 only)

C = 0, Disable Side Compare

C = 1, Enable Side Compare

For all Type III commands bit 1 must be 0.

P = Write Precompensation (Bit 1) (1770/2/3)

P = 0,Enable Write Precomp

P = 1,Disable Write Precomp

### **TYPE IV COMMANDS**

### I<sub>3</sub>-I<sub>0</sub> Interrupt Condition (Bits 3-0)

$I_0$  = Not Used (WD1770-00, WD1772-00)

Not Ready to Ready Transition (WD1773-00)

I<sub>1</sub> = Not Used (WD1770-00, WD1772-00) Ready to Not Ready Transition (WD1773-00)

$I_2$  = Interrupt on Index Pulse

$\bar{l_3}$  = Immediate Interrupt

$\bar{l_3}$ - $l_0$  = Terminate without interrupt

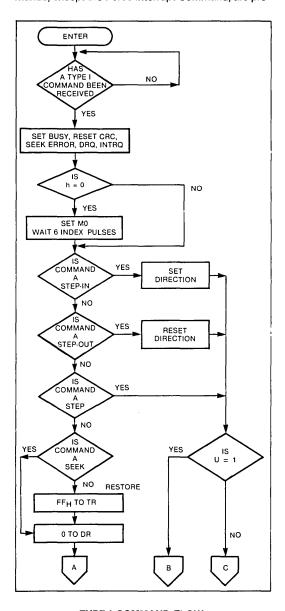

#### **TYPE I COMMANDS**

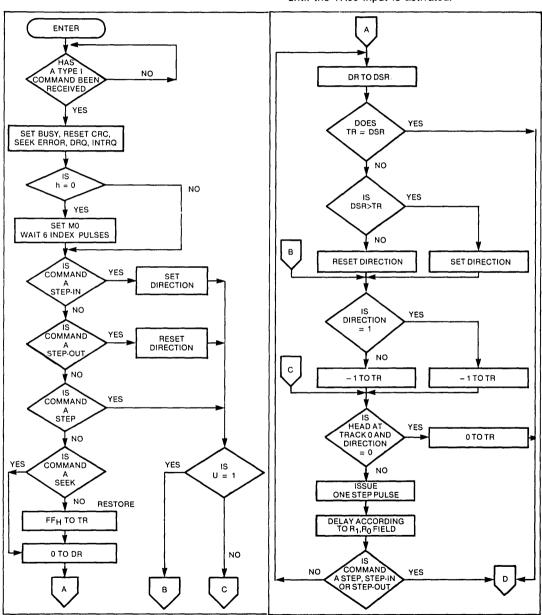

The Type I Commands include the Restore, Seek, Step, Step-in, and Step-Out Commands. Each of the Type I Commands contains a rate field  $(r_0,r_1)$ , which determines the stepping motor rate.

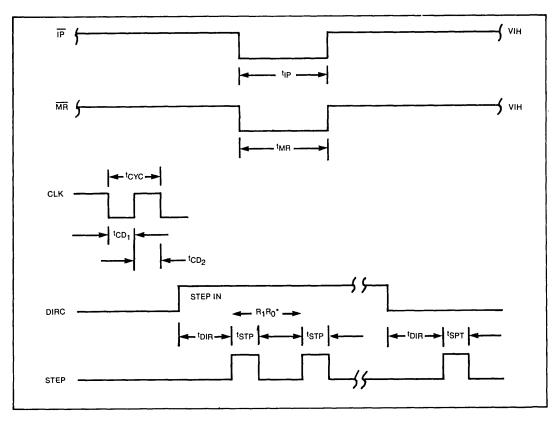

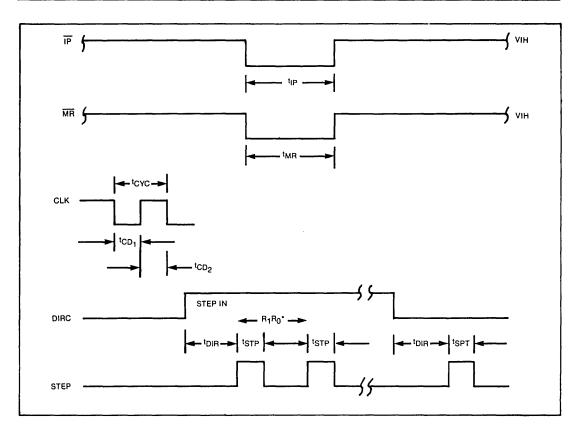

A 4  $\mu$ sec (MFM) or 8  $\mu$ sec (FM) pulse is provided as an output to the drive. For every step pulse issued, the drive moves one track location in a direction determined by the direction output. The chip steps the drive in the same direction it last stepped unless the command changes the direction.

The Direction signal is active high when stepping in and low when stepping out. The Direction signal is valid 24  $\mu$ sec before the first stepping pulse is generated.

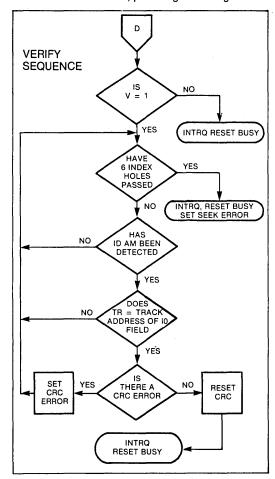

After the last directional step an additional \*30 msec of head settling time takes place if the Verify flag is set in Type I Commands. There is also a \*30 msec head settling time if the E flag is set in any Type II or III Command.

When a Seek, Step or Restore Command is executed, an optional verification of Read/Write head position can be performed by setting bit 2 (V = 1) in the command word to a logic 1. The verification operation begins at the end of the \*30 msec settling time after the head is loaded against the media. The track number from the first encountered ID Field is compared against the contents of the Track Register. If the track numbers compare and the ID Field CRC is correct, the verify operation is complete and an INTRQ is generated with no errors. If there is a match but not

a valid CRC, the CRC error status bit is set (Status Bit 3), and the next encountered ID Field is read from the disk for the verification operation.

The WD177X-00 finds an ID Field with correct track number and correct CRC within 5 revolutions of the media, or the seek error is set and an INTRQ is generated. If V = 0, no verification is performed.

On the WD1770-00 and WD1772-00 only, all commands, except the Force Interrupt Command, are pro-

grammed via the h Flag to delay for spindle motor start up time. If the h Flag is not set and the MO signal is low when a command is received, the WD1770/2-00 forces MO to a logic 1 and waits 6 revolutions before executing the command. At 300 RPM, this guarantees a one second spindle start up time. If after finishing the command, the device remains idle for 9 revolutions, the MO signal goes back to a logic 0. If a command is issued while MO

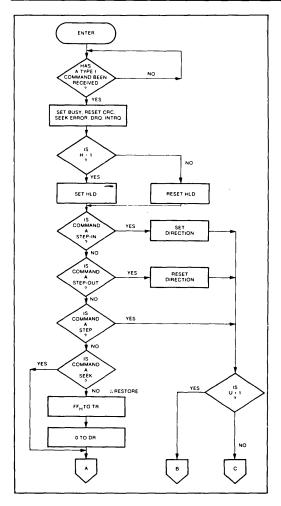

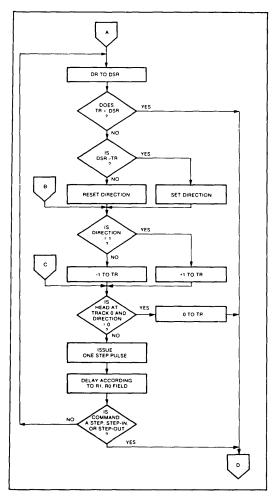

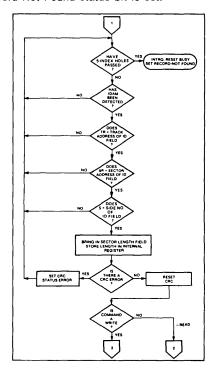

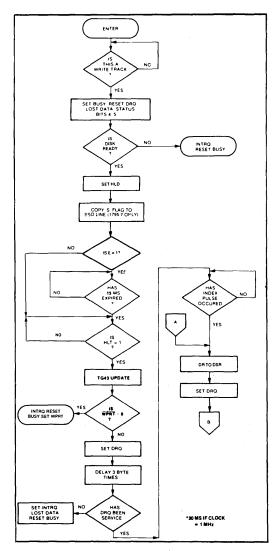

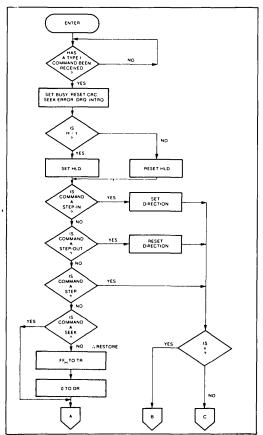

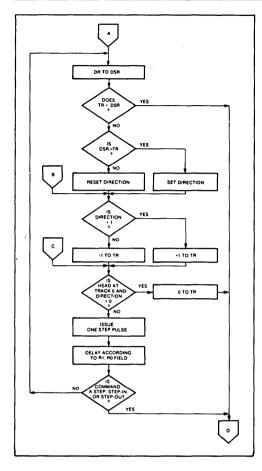

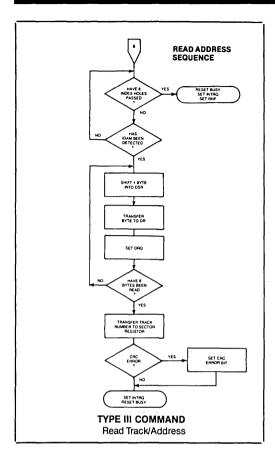

DR TO DSR DOES YES TR = DSF NO YES DSR>TR NO В RESET DIRECTION SET DIRECTION YES DIRECTION NO Ç - 1 TO TR - 1 TO TR HEAD AT YES TRACK 0 AND 0 TO TR DIRECTION = 0NO ISSUE ONE STEP PULSE DELAY ACCORDING TO R<sub>1</sub>,R<sub>0</sub> FIELD COMMAND NO YES A STEP, STEP-IN D OR STEP-OU

TYPE I COMMAND FLOW

TYPE I COMMAND FLOW

is high, the command executes immediately, defeating the 6 revolution start up. This feature allows consecutive Read or Write commands without waiting for motor start up each time; the WD1770/2-00 assumes the spindle motor is up to speed.

### **RESTORE (SEEK TRACK 0)**

<u>Upon</u> receipt of this command, the Track 00 (TR00) input is sampled. If TR00 is active low indicating the Read/Write head is positioned over track 0, the Track Register is <u>loaded</u> with zeroes and an interrupt is generated. If TR00 is not active low, stepping pulses at a <u>rate</u> specified by the r<sub>1</sub>,r<sub>0</sub> field are issued until the TR00 input is activated.

At this time, the Track Register is load<u>ed with zeroes</u> and an interrupt is generated. If the TR00 input does not go active low after 255 stepping pulses, the WD177X-00 terminates operation, interrupts, and sets the Seek Error status bit, providing the V flag is set.

TYPE I COMMAND FLOW

A verification operation also takes place if the V flag is set. The h bit allows the Motor On option at the start of a command.

#### SEEK

This command assumes that the Track Register contains the track number of the current position of the Read/Write head and the Data Register contains the desired track number. The WD177X-00 updates the Track Register and issues stepping pulses in the appropriate direction until the contents of the Track Register are equal to the contents of the Data Register (the desired track location). A verification operation takes place if the V flag is on. The h bit allows the Motor On option at the start of the command. An interrupt is generated at the completion of the command. Note: When using multiple drives, the Track Register is updated for the drive selected before seeks are issued.

#### STEP

Upon receipt of this command, the WD177X-00 issues one Stepping Pulse to the disk drive. The stepping motor direction is the same as in the previous step command. After a delay determined by the  $r_1, r_0$  field, a verification takes place if the V flag is on. If the U flag is on, the Track Register is updated. The h bit allows the Motor On option at the start of the command. An interrupt is generated at the completion of the command.

### STEP-IN

Upon receipt of this command, the WD177X-00 issues one Stepping Pulse in the direction towards track 76. If the U flag is on, the Track Register is incremented by one. After a delay determined by the r<sub>1</sub>,r<sub>0</sub> field, a verification takes place if the V flag is on. The h bit allows the Motor On option at the start of the command. An interrupt is generated at the completion of the command.

### STEP-OUT

Upon receipt of this command, the WD177X-00 issues one stepping pulse in the direction towards track 0. If the U flag is on, the Track Register is decremented by one. After delay determined by the  $r_1$ ,  $r_0$  field, a verification takes place if the V flag is on. The h bit allows the Motor On option at the start of the command. An interrupt is generated at the completion of the command.

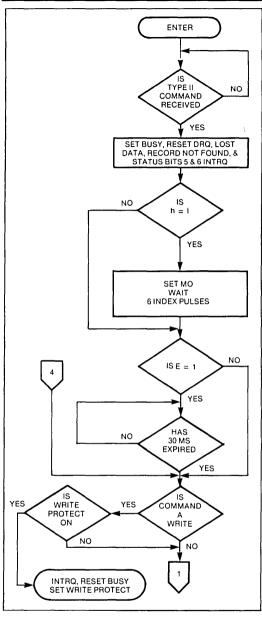

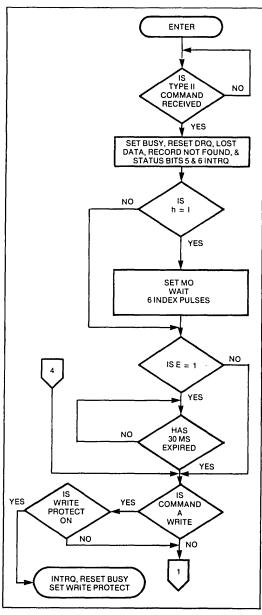

### TYPE II COMMANDS

The Type II Commands are the Read Sector and Write Sector commands. Prior to loading the Type II Command into the Command Register, the computer loads the Sector Register with the desired sector number. Upon receipt of the Type II command, the Busy Status bit is set. If the E flag = 1 the command executes after a 30 msec delay.

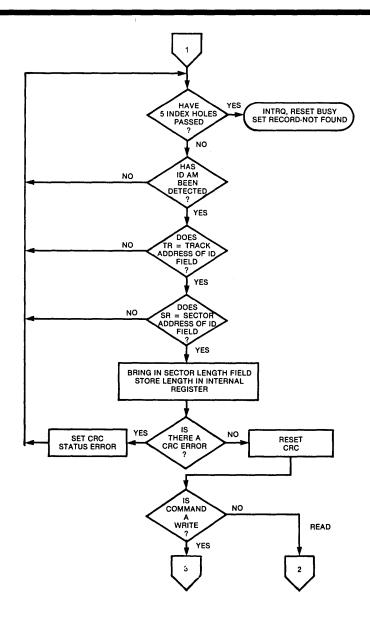

When an ID field is located on the disk, the WD177X-00 compares the Track Number on the ID field with the Track Register. If there is not a match, the next encountered ID field is read and a comparison is again made. If there is a match, the Sec-

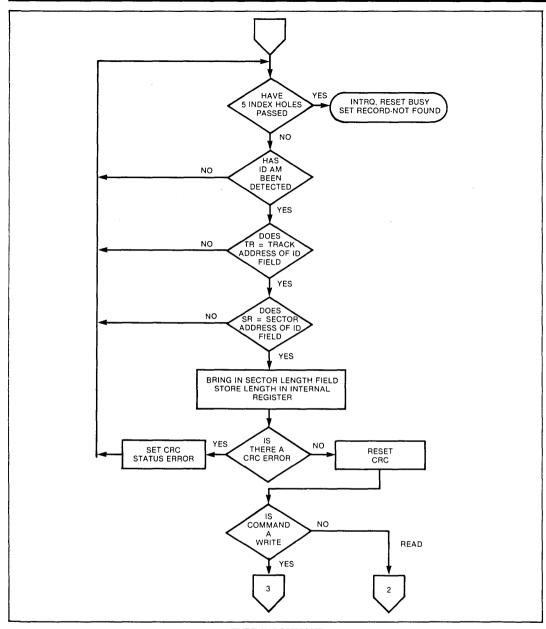

### **TYPE II COMMAND**

tor Number of the ID field is compared with the Sector Register. If there is no Sector match, the next encountered ID field is read off the disk and comparisons again made. If the ID field CRC is correct, the data field is located and is either written into, or read from, depending upon the command. The WD177X-00 finds an ID field with a Track number, Sector number, and CRC within four revolutions of the disk, or, the Record Not Found Status bit is set (Status Bit 4) and the command is terminated with an INTRQ.

Each of the Type II Commands contains an m flag which determines if multiple records (sectors) are read or written, depending upon the command. If m = 0, a single sector is read or written and an interrupt is generated at the completion of the command. If m = 1, multiple records are read or written with the Sector Register internally updated so that an address verification occurs on the next record. The WD177X-00 continues to read or write multiple records and updates the Sector Register in numerical ascending sequence until the Sector Register exceeds the number of sectors on the track or until the Force Interrupt Command is loaded into the Command Register, which terminates the command and generates an interrupt.

For example: If the WD177X-00 is instructed to read sector 27 and there are only 26 on the track, the Sector Register exceeds the number available. The WD177X-00 searches for 5 disk revolutions, interrupts out, resets Busy, and sets the Record Not Found Status Bit.

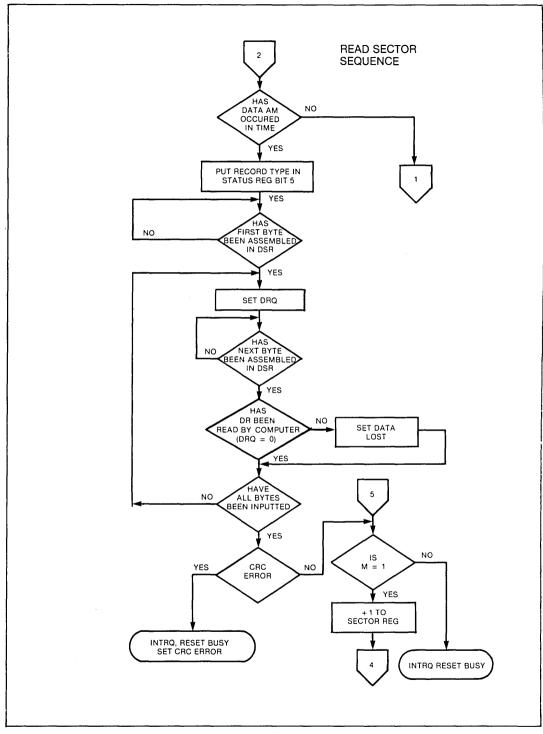

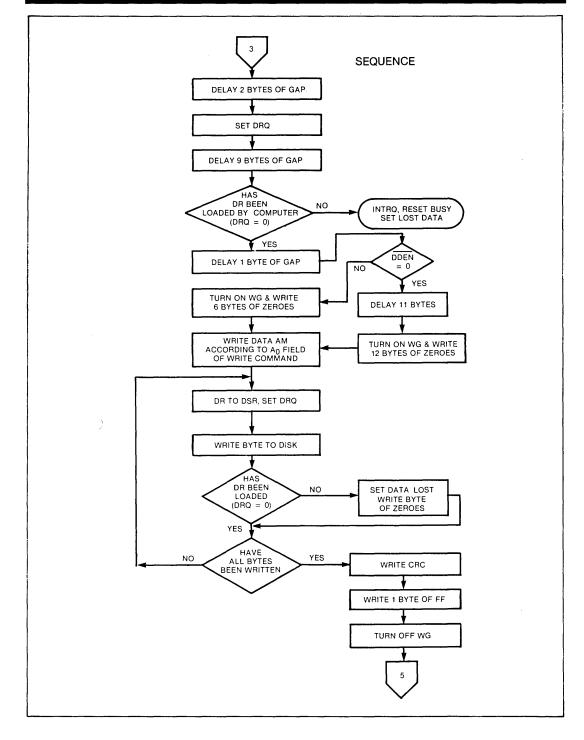

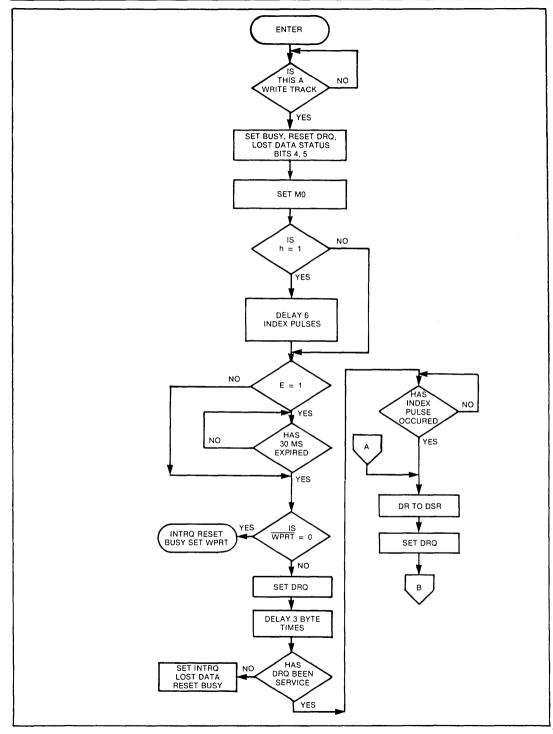

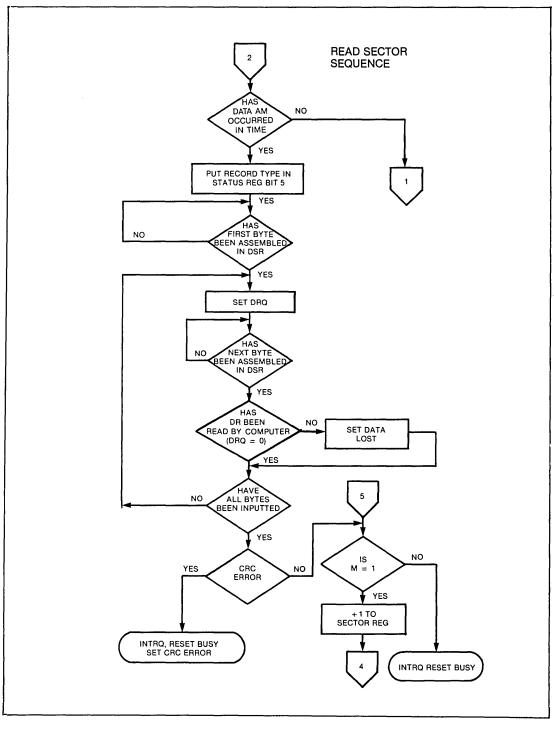

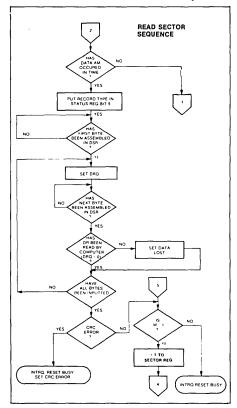

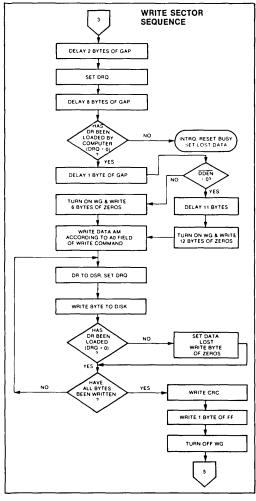

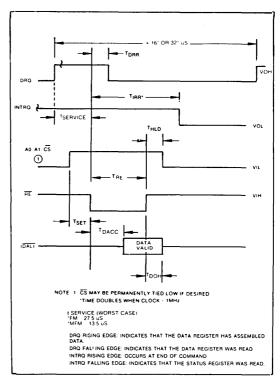

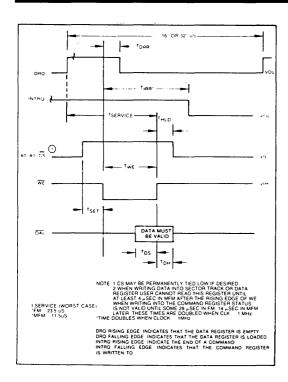

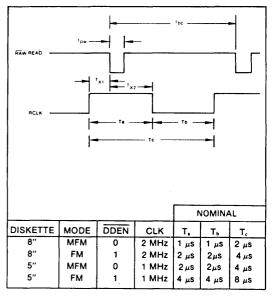

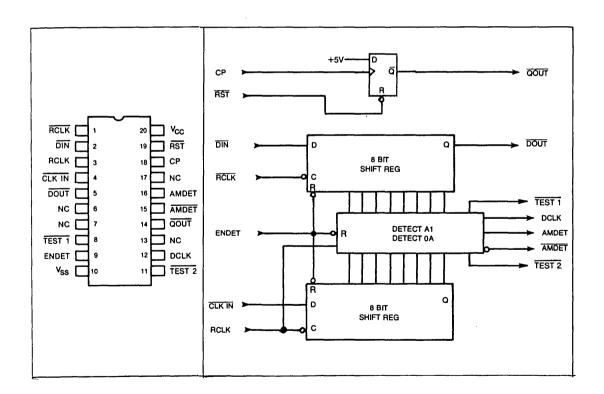

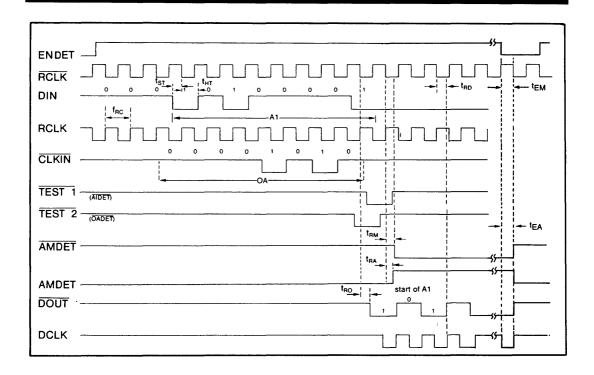

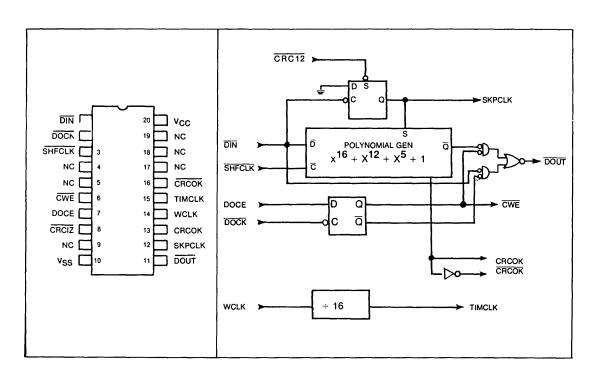

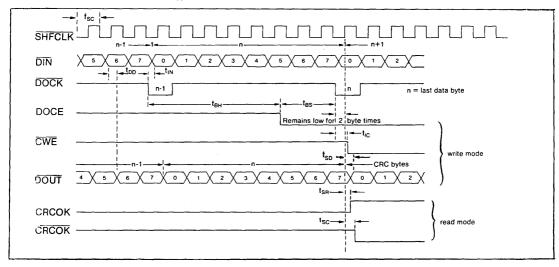

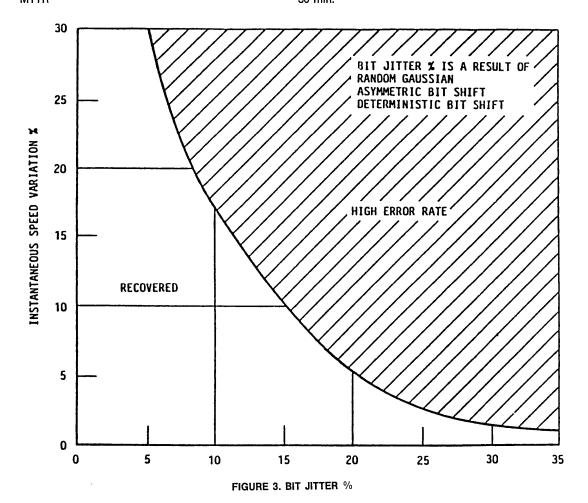

### **READ SECTOR**