FE3021 Address Buffer and Memory Controller

# **TABLE OF CONTENTS**

|      |                   |     |      |     |      |      |   |   |   |   |  |  |  |  |  |  |   |  | Page |

|------|-------------------|-----|------|-----|------|------|---|---|---|---|--|--|--|--|--|--|---|--|------|

| 1.0  | Description       |     |      |     |      |      |   |   |   |   |  |  |  |  |  |  |   |  | 4-1  |

|      | 1.1 Features .    |     |      |     |      |      |   | • |   |   |  |  |  |  |  |  |   |  | 4-1  |

|      | 1.2 Introduction  |     |      |     |      |      |   |   |   |   |  |  |  |  |  |  |   |  | 4-3  |

| 2.0  | 80286 Interface   |     |      |     |      |      |   |   |   |   |  |  |  |  |  |  |   |  | 4-4  |

| 3.0  | Data Bus Interfac | e   |      |     |      |      |   |   |   |   |  |  |  |  |  |  |   |  | 4-5  |

| 4.0  | I/O Chip Selects  |     |      |     |      |      |   |   |   |   |  |  |  |  |  |  |   |  | 4-6  |

| 5.0  | I/O Control       |     |      |     |      |      |   |   |   |   |  |  |  |  |  |  |   |  | 4-7  |

| 6.0  | Memory Control    |     |      |     |      |      |   |   | - | • |  |  |  |  |  |  |   |  | 4-16 |

| 7.0  | Memory Address    | Mι  | ulti | ple | xe   | er   |   |   |   |   |  |  |  |  |  |  | • |  | 4-17 |

| 8.0  | EMS Memory .      |     |      |     |      |      |   |   |   |   |  |  |  |  |  |  |   |  | 4-28 |

| 9.0  | Test Mode         |     |      |     |      |      |   |   |   |   |  |  |  |  |  |  |   |  | 4-33 |

| 10.0 | FE3021 Pinout     |     |      |     |      |      |   |   |   |   |  |  |  |  |  |  |   |  | 4-34 |

| 11.0 | DC Operating C    | har | ac   | ter | rist | tics | 5 |   |   |   |  |  |  |  |  |  |   |  | 4-36 |

| 12.0 | ) AC Timing Char  | act | eri  | sti | cs   |      |   |   |   |   |  |  |  |  |  |  |   |  | 4-37 |

| 13.0 | System Timing     |     |      |     | •    |      |   |   |   |   |  |  |  |  |  |  | • |  | 4-38 |

| 14.( | ) Package Diagra  | ıms | ;    |     |      |      |   |   |   |   |  |  |  |  |  |  |   |  | 4-54 |

## LIST OF ILLUSTRATIONS

| Figure | Title                                          | Page |

|--------|------------------------------------------------|------|

| 1      | FE3600B Chip Set Functional Block Diagram      | 4-1  |

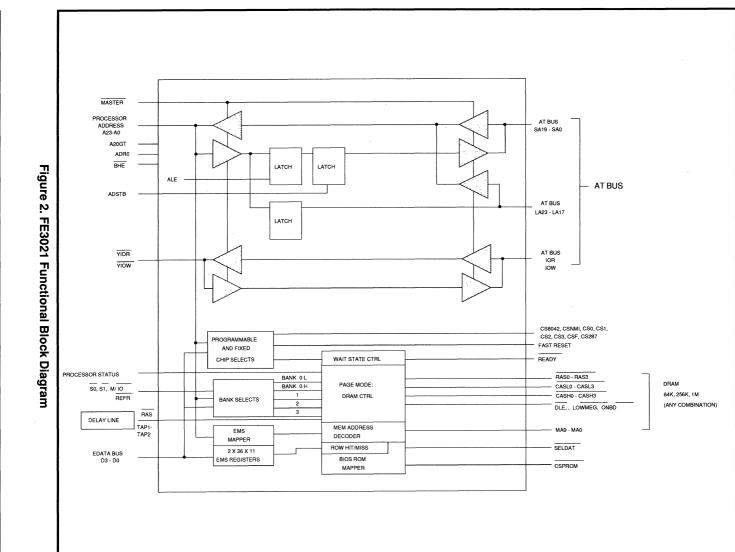

| 2      | FE3021 Functional Block Diagram                | 4-2  |

| 3      | High Speed HDC Configuration                   | 4-11 |

| 4      | EMS/Memory Map Configuration                   | 4-31 |

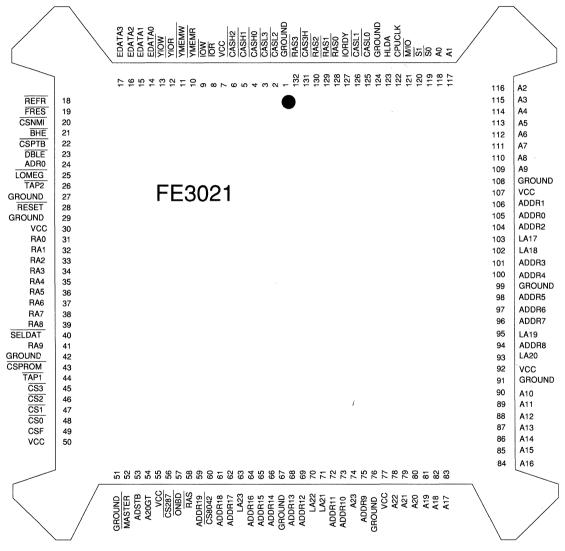

| 5      | Pin Assignments                                | 4-34 |

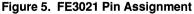

| 6      | Basic Timing                                   | 4-42 |

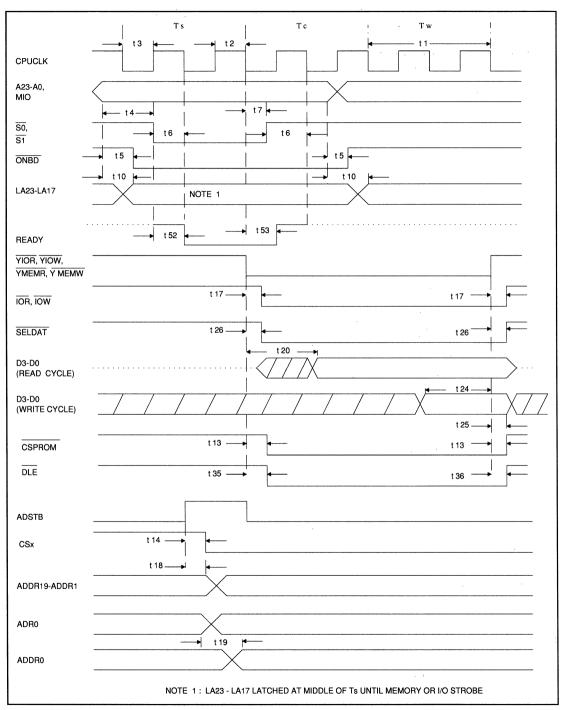

| 7      | High Speed Mode LA23-LA17 Timing               | 4-43 |

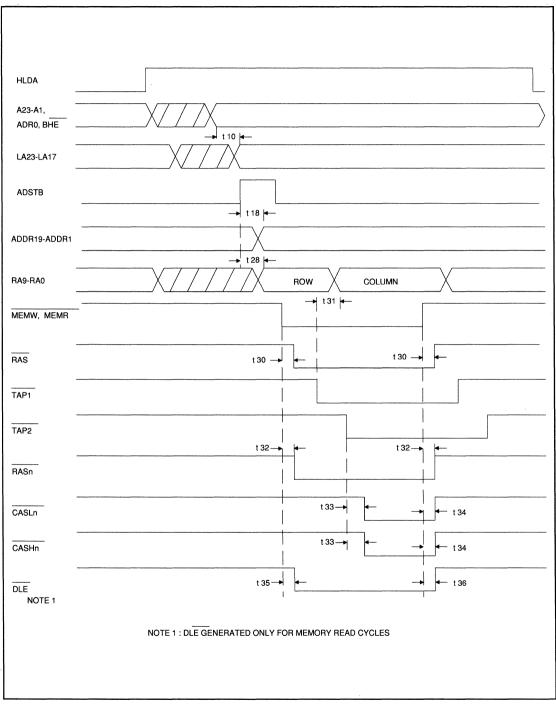

| 8      | DMA Memory Cycle                               | 4-44 |

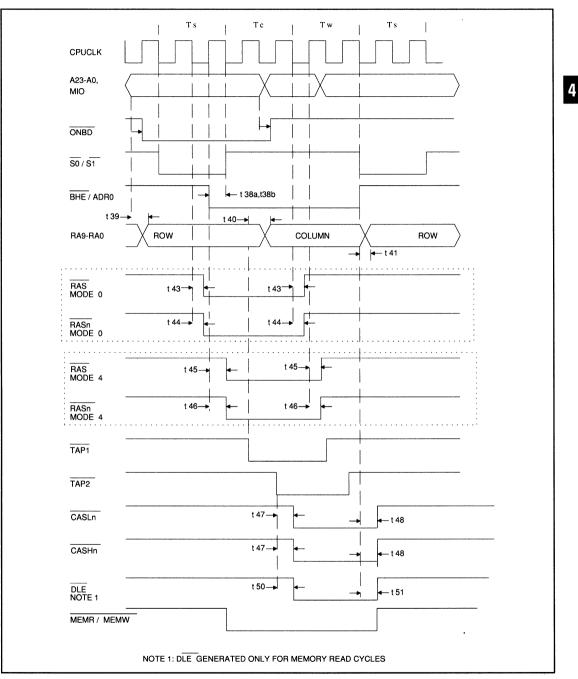

| 9      | Memory Modes 0 & 4 (Non-Page Mode)             | 4-45 |

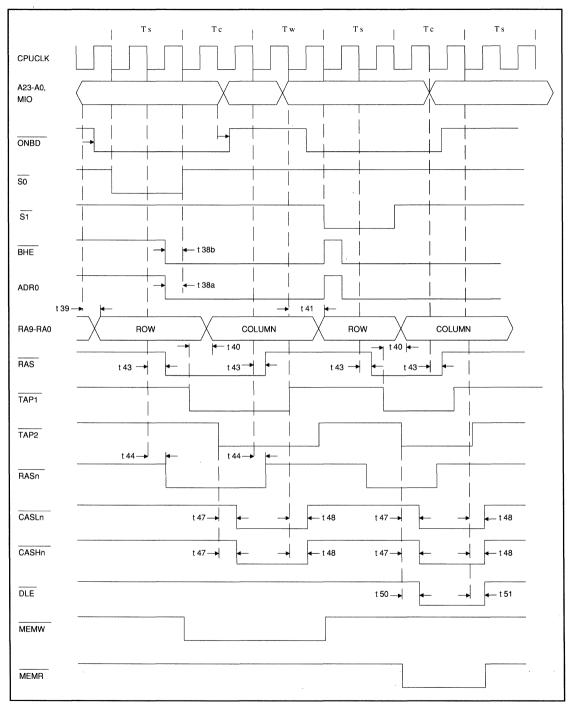

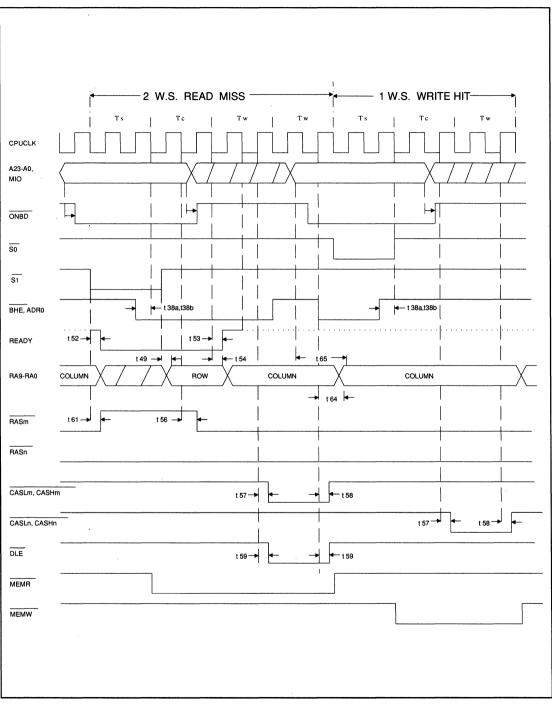

| 10     | Memory Mode 1 (Non-Page) 0 WS Read/ 1 WS Write | 4-46 |

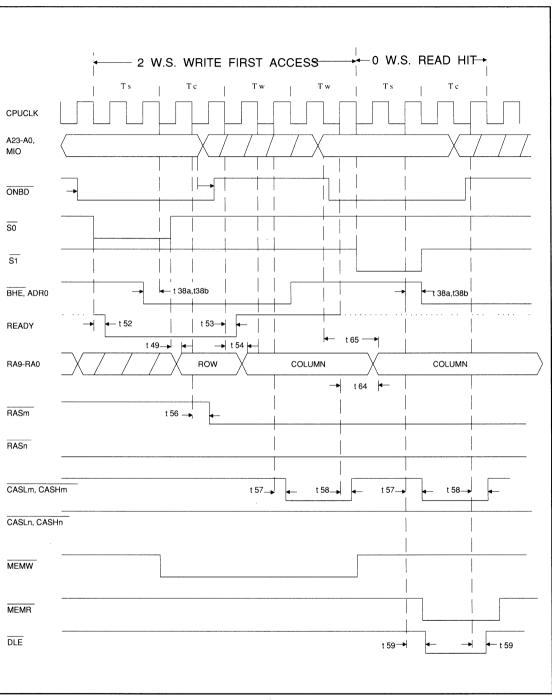

| 11     | Memory Mode 2 (Page) 1 of 2                    | 4-47 |

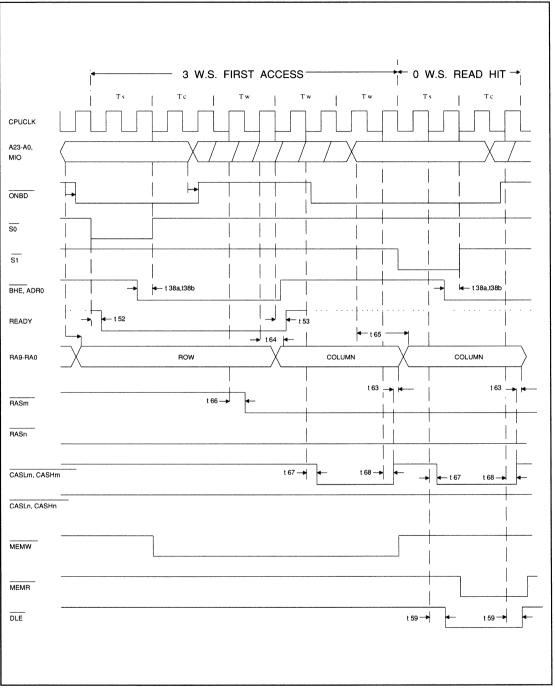

| 12     | Memory Mode 2 (Page) 2 of 2                    | 4-48 |

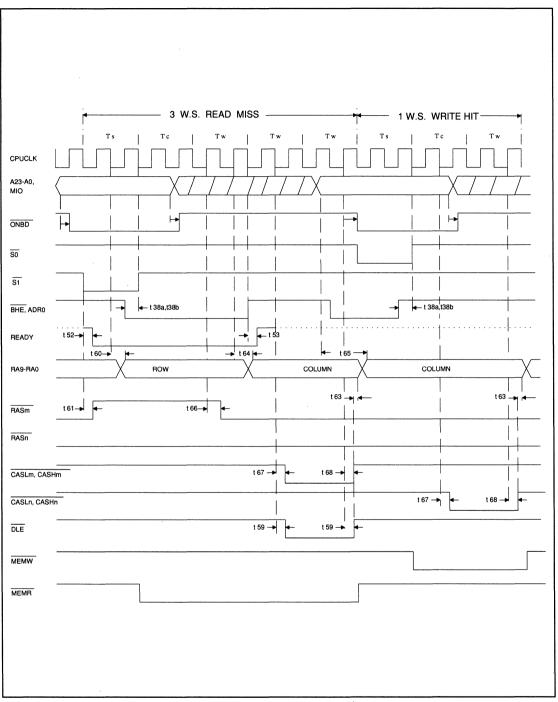

| 13     | Memory Mode 3 (Page) 1 of 2                    | 4-49 |

| 14     | Memory Mode 3 (Page) 2 of 2                    | 4-50 |

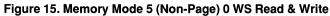

| 15     | Memory Mode 5 (Non-Page) 0 WS Read & Write     | 4-51 |

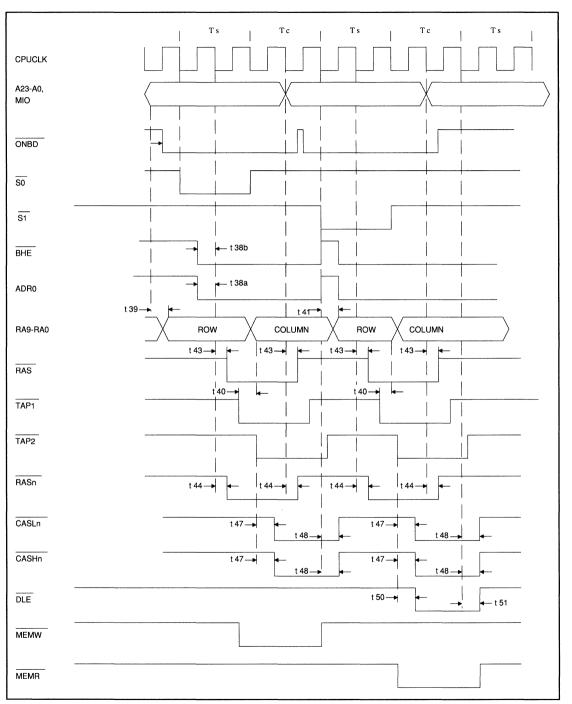

| 16     | Refresh Cycle                                  | 4-52 |

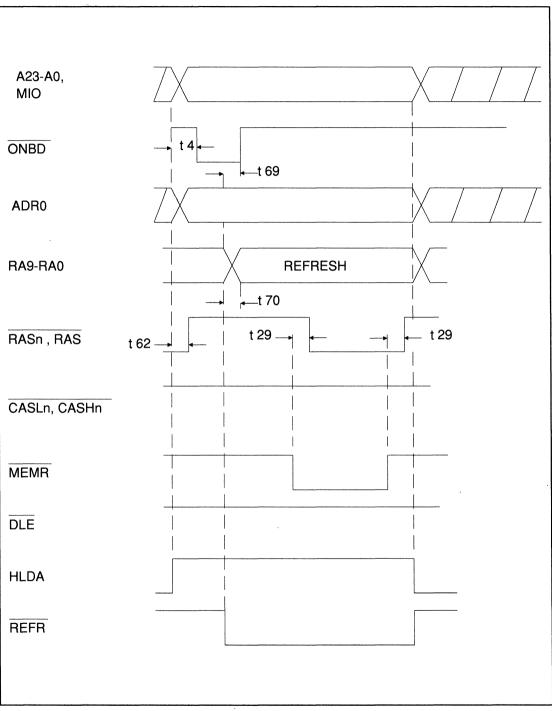

| 17     | Bus Master Cycle                               | 4-53 |

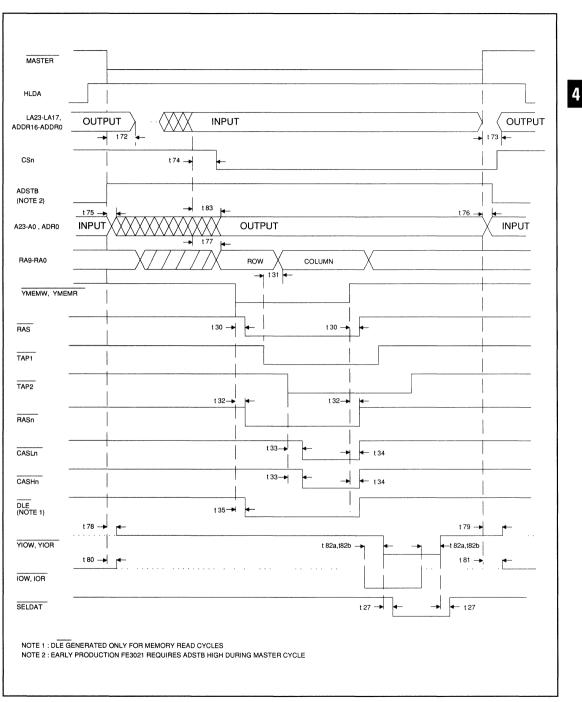

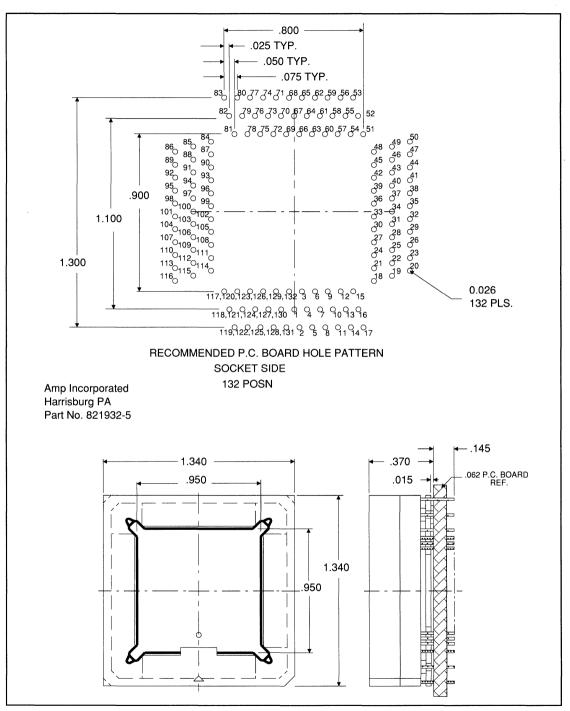

| 18     | 132-Pin JEDEC Flat Pack Packaging Diagram      | 4-54 |

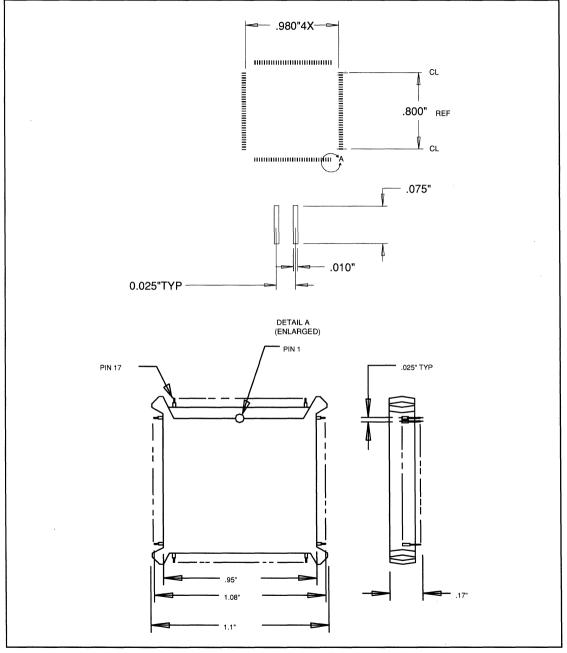

| 19     | Socket Diagram                                 | 4-55 |

|        |                                                |      |

# LIST OF TABLES

| Table | Title                                    | Page |

|-------|------------------------------------------|------|

| 1     | 80286 Interface Pin Functions            | 4-4  |

| 2     | Data Bus Interface Pin Assignments       | 4-5  |

| 3     | I/O Chip Selects Pin Assignments         | 4-6  |

| 4     | I/O Control Pin Functions                | 4-7  |

| 5     | I/O Address/Chip Selects for Fixed Ports | 4-14 |

| 6     | Memory Control Pin Information           | 4-16 |

| 7     | Memory Address Multiplexer Outputs       | 4-17 |

| 8     | Address Multiplexer Configurations       | 4-17 |

| 9     | EMS Page Register Information            | 4-33 |

| 10    | FE3021 Pins Grouped By Function          | 4-35 |

## **1.0 DESCRIPTION**

The FE3021 is a 16 MHz AT address buffer and memory controller in a 132-pin JEDEC package. Chip count is significantly reduced by integrating the memory controller, AT bus address buffers, and I/O into one chip. The memory controller is a high performance design, with programmable modes of operation. It controls page mode DRAM or static column DRAM. A maximum of 4 banks of DRAM can be controlled allowing a maximum of 8 MB of memory to be controlled by the FE3021. The DRAM bank locations are programmable on 128K byte boundries. One memory bank allows split addressing, so that one portion may be placed in conventional memory with the remainder in extended memory.

Additional features of the FE3600B chip set include EMS 4.0 support, on-chip address and control signal buffers for directly driving the AT bus, zero wait state access at 16 MHz using 100 ns DRAM with page mode access, generation of chip selects for floppy controller, 8042, 80287, and NMI, and mapping main and EGA BIOS into one physical PROM.

### 1.1 FEATURES

- Page mode DRAM access with interleaved memory banks

- Controls up to 4 banks (up to 8 MBytes) of memory

- On- chip RAS and CAS drivers for DRAM chips

- On- chip DRAM address multiplexer

- □ LIM standard EMS expanded memory hardware (supports EMS 4.0 multi-tasking)

- On- chip address and control signal buffers for directly driving AT bus

- Zero wait state access at 16 MHz using 100 ns DRAM with page mode access

- Generates chip selects for floppy controller, 8042, 80287, and NMI

- Generates programmable chip selects for four additional devices

- Maps system BIOS and EGA BIOS into one physical PROM

- "Hot" reset generation for quick 80286 switch from protected to real mode

- □ Fast Alternate Gate A20 generation

- □ 132 pin JEDEC plastic flat package

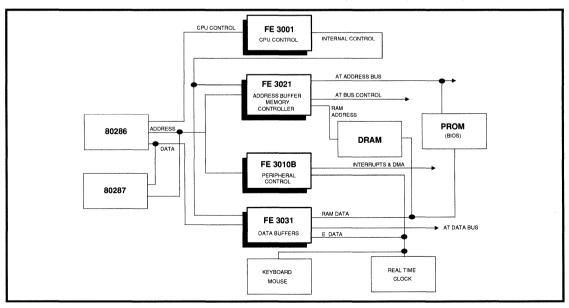

Figure 1. FE3600B Chip Set Functional Block Diagram

11/16/90

FE3021

DESCRIPTION

11/16/90

4-2

$\otimes$

### 1.2 INTRODUCTION

The FE3021 device is designed to reduce chip count, increase flexibility, and provide improved operating speed and functionality when used with the FE3001, FE3010B, and FE3031 devices to implement a low cost, high performance AT compatible computer.

Chip count is reduced by integrating the memory controller, AT bus address buffers, and I/O Management functions into one chip.

The memory controller is a high performance design, with programmable modes of operation. It controls page mode DRAM or static column DRAM.

Up to 4 banks of DRAM may be controlled. The DRAM bank locations are programmable on 128K byte boundaries. One memory bank allows split addressing, so that one portion may be placed in conventional memory with the remainder in extended memory, with an additional mode to allow copying BIOS code from ROM to RAM for faster execution.

A major function of the FE3021 is to generate chip select decodes for peripheral chips on the system board; for instance, the floppy controller, hard disk controller, serial, and parallel port chips. The floppy and hard disk chip selects may be disabled or may be enabled for either the primary or secondary address decode, as defined by IBM. Four programmable chip selects are available, for supporting serial, parallel, mouse, or other types of ports. Refer to Figure 2 for Pin assignment information and locations.

To reduce chip count and improve performance, particularly when an EGA or VGA graphics controller is placed on the system board, separate blocks of ROM may be mapped into a single physical ROM. For instance, the EGA BIOS and standard BIOS may be placed into the same pair of ROM chips or into a single 8-bit wide ROM. Besides reducing chip count, EGA operating speed will be improved, since EGA BIOS will be accessed 16 bits at a time. To improve BIOS performance, ROM code may be copied into RAM, and the BIOS ROM mapped out and replaced by RAM.

### 2.0 80286 INTERFACE

This interface port connects with the 80286 address lines and the 80286 bus status lines. By connecting directly to the 80286 and by duplicating a portion of the bus controller logic, early determination of memory or I/O accesses may be made, as well as whether the access will be 8 bits or 16 bits. Pins A23-A0 are normally inputs, receiving addresses from the 80286. When MASTER is asserted, these pins become outputs.

| PIN NUMBER | MNEMONIC      | I/O | FUNCTION                    |

|------------|---------------|-----|-----------------------------|

| 74         | A23           | 1/0 | 80286 Address Line          |

| 78         | A22           | I/O |                             |

| 79         | A21           | I/O | 11 11                       |

| 80         | A20           | I/O | H H                         |

| 81         | A19           | 1/0 | 11 11                       |

| 82         | A18           | I/O | 11 11                       |

| 83         | A17           | I/O | 11 11                       |

| 84         | A16           | 1/0 | и , и                       |

| 85         | A15           | I/O | 11 11                       |

| 86         | A14           | I/O | 11 11                       |

| 87         | A13           | I/O | 11 11                       |

| 88         | A12           | I/O | n II                        |

| 89         | A11           | I/O | n n                         |

| 90         | A10           | I/O | 0 U                         |

| 109        | A9            | I/O | 11 11                       |

| 110        | A8            | I/O | 11 11                       |

| 111        | A7            | 1/0 | н н                         |

| 112        | A6            | I/O | 11 11                       |

| 113        | A5            | I/O | н н                         |

| 114        | A4            | I/O | н н                         |

| 115        | A3            | I/O | п п                         |

| 116        | A2            | I/O | D H                         |

| 117        | A1            | 1/0 | 11 11                       |

| 118        | A0            | 1/0 | II II                       |

| 119        | SO            | I   | 80286 Status Line           |

| 120        | <del>S1</del> | 1   | 80286 Status Line           |

| 121        | M/IO          |     | 80286 Status Line           |

| 122        | CPUCLK        | 1   | 80286 Clock                 |

| 123        | HLDA          | 1   | 80286 Hold Acknowledge Line |

| 21         | BHE           | 1   | 80286 Byte High Enable      |

### Table 1. 80286 Interface Pin Functions

## 3.0 DATA BUS INTERFACE

The data bus port is 4 bits wide, which should connect to the EDATA local data bus, and is used to access the internal FE3021 control registers. The upper 4 bits should be ignored when reading the control registers. Refer to Table 2 for pin assignments.

| PIN NUMBER | MNEMONIC | I/O | FUNCTION                   |

|------------|----------|-----|----------------------------|

| 17         | EDATA3   | I/O | Control Register Data Line |

| 16         | EDATA2   | I/O | 11 11                      |

| 15         | EDATA1   | I/O | n n                        |

| 14         | EDATA0   | I/O | Control Register Data Line |

Table 2. Data Bus Interface Pin Assignments

## 4.0 I/O CHIP SELECTS

This logic section generates chip selects for standard system board functions such as the 8042 keyboard controller, 80287 math coprocessor, floppy controller, and hard disk controller. It also generates chip selects for up to 4 additional I/O ports which may have programmable addresses and wait state characteristics. Refer to Table 3 for pin assignments.

| PIN NUMBER | MNEMONIC | I/O | FUNCTION                                                                            |

|------------|----------|-----|-------------------------------------------------------------------------------------|

| 48         | CS0      | 0   | Programmable Chip Select 0                                                          |

| 47         | CS1      | 0   | Programmable Chip Select 1                                                          |

| 46         | CS2      | 0   | Programmable Chip Select 2                                                          |

| 45         | CS3      | 0   | Programmable Chip Select 3<br>Or H. D. Control Chipselect                           |

| 49         | CSF      | 0   | Floppy Disk Controller Chip Select Or Operation Or<br>Configuration Register Select |

| 60         | CS8042   | 0   | 8042 Keyboard Control Select                                                        |

| 56         | CS287    | 0   | 80287 Coprocessor Select                                                            |

| 20         | CSNMI    | 0   | NMI Logic Chip Select                                                               |

| 22         | CSPTB    | 0   | Memory Parityand I/o Check Control Chip Select                                      |

Table 3. I/O Chip Selects Pin Assignments

4

# 5.0 I/O CONTROL

This logic section contains control logic for the I/O bus.

The IORDY signal will go low when generating wait states. For 12 MHz systems, this signal may be tied directly to the bus signal IOCHRDY. For 16 MHz or 20 MHz systems, this signal should be sent to the FE3001 directly. The IOCHRDY bus signal should be buffered through an open collector driver and wire-OR'ed with the IORDY signal. The IORDY pin will normally be at a high impedance state. When generating wait states, it will go low. When going from a low to a high state, the IORDY pin will be actively driven high for one processor clock time, then the output will tri-state. An external pullup resistor should be used to keep the IORDY signal high when the IORDY pin is at a high impedance state. The state of IORDY is sampled at the rising edge of RESET ; if IORDY is low at this time, the FE3021 will fetch data and instructions from the BIOS ROM 8 bits at a time over the EDATA bus, otherwise a 16 bit wide BOM on the MDATA bus is assumed.

Table 4 lists the data word size, I/O addresses, and chip selects generated for each variable port type.

The PORT 0, PORT 1, PORT 2, and PORT 3 addresses are fully programmable, with the choice of either using nine I/O addresses for decode, or masking the A8 address bit (for instance, for decoding dual serial ports). The LSB (A0) address is always ignored. The lower 2, 3, or 4 bits of the address may also be ignored so that 2, 4, 8, or 16 bytes may be allocated for the port.

All FE3021 control registers, except those used for EMS page mapping, are accessed by first writing eight times to address FFF00 (in an area allocated for ROM BIOS). Any memory access outside of the ROM BIOS address space, either data access or instruction fetch, will abort the unlocking process. Once unlocked, memory accesses outside of the ROM BIOS area may be made without affecting the unlocked state. When unlocked, the address space from FFF01 to FFFFE becomes register controls for the FE3021 device. The controls are locked again by reading location FFFFF. This access method guarantees that all control register changes will be made through the BIOS.

| PIN NUMBER | PIN NAME | I/O | FUNCTION                                                                           |

|------------|----------|-----|------------------------------------------------------------------------------------|

| 127        | IORDY    | I/O | Ready Line, modified Open Drain, Input<br>At Reset Time For 8-Bit ROM Sizing       |

| 40         | SELDAT   | 0   | Direction Of Data Tranceiver Data<br>To EDATA Bus                                  |

| 8          | IOR      | I/O | System I/O Read Command Signal, Drives<br>Expansion Bus. An Input In Master Mode.  |

| 9          | ĪOW      | I/O | System I/o Write Command Signal, Drives<br>Expansion Bus. An Input In Master Mode. |

| 10         | YMEMR    | I   | Ungated System Memory Read Command<br>Signal From FE3001                           |

| 11         | YMEMW    | I   | Ungated System Memory Write Command<br>Signal From FE3001                          |

Table 4. I/O Control Pin Functions

| PIN NUMBER | MNEMONIC | I/O | FUNCTION                                                          |

|------------|----------|-----|-------------------------------------------------------------------|

| 53         | ADSTB    |     | Address Strobe From FE3001 And FE3010B.                           |

| 12         | YIOR     | I/O | Ungated I/O Read Strobe From<br>FE3001, An Output In Master Mode. |

| 13         | YIOW     | I/O | Ungated I/O Write Strobe From<br>FE3001, output In Master Mode.   |

| 19         | FRES     | I/O | "HOT" Reset Output                                                |

| 25         | LOMEG    | 0   | To FE3031 Memory Strobe Gating                                    |

| 28         | RESET    | 1   | Master Reset For FE3021                                           |

| 52         | MASTER   | I   | Bus Master Signal From AT Bus                                     |

| 54         | A20GT    |     | From 8042. When High, A20 Is Ungated                              |

| 57         | ONBD     | 0   | To FE3001. Indicates High Speed<br>On-Board Access                |

| 59         | ADDR19   | 0   | AT Bus SA19                                                       |

| 61         | ADDR 18  | 0   | AT Bus SA18                                                       |

| 62         | ADDR 17  | 0   | AT Bus SA17                                                       |

| 64         | ADDR 16  | I/O | AT Bus SA16                                                       |

| 65         | ADDR 15  | I/O | AT Bus SA15                                                       |

| 66         | ADDR 14  | I/O | AT Bus SA14                                                       |

| 68         | ADDR 13  | I/O | AT Bus SA13                                                       |

| 69         | ADDR 12  | I/O | AT Bus SA12                                                       |

| 72         | ADDR 11  | I/O | AT Bus SA11                                                       |

| 73         | ADDR 10  | I/O | AT Bus SA10                                                       |

| 75         | ADDR 9   | I/O | AT Bus SA 9                                                       |

| 94         | ADDR8    | I/O | AT Bus SA8                                                        |

| 96         | ADDR7    | I/O | AT Bus SA7                                                        |

| 97         | ADDR6    | I/O | AT Bus SA6                                                        |

| 98         | ADDR5    | I/O | AT Bus SA5                                                        |

| 100        | ADDR4    | I/O | AT Bus SA4                                                        |

| 101        | ADDR3    | I/O | AT Bus SA3                                                        |

| 104        | ADDR2    | I/O | AT Bus SA2                                                        |

| 106        | ADDR1    | I/O | AT Bus SA1                                                        |

| 105        | ADDR0    | I/O | AT Bus SA0                                                        |

| 63         | LA23     | I/O | AT Bus LA23                                                       |

| 70         | LA22     | I/O | AT Bus LA22                                                       |

| 71         | LA21     | I/O | AT Bus LA21                                                       |

| 93         | LA20     | I/O | AT Bus LA20                                                       |

| 95         | LA19     | I/O | AT Bus LA19                                                       |

| 102        | LA18     | I/O | AT Bus LA18                                                       |

| 103        | LA17     | I/O | AT Bus LA17                                                       |

Table 4. I/O Control Pin Functions (Continued)

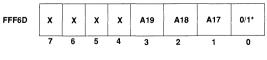

A Version Number register provides information on the version of the FE3021 chip. It also contains a bit which toggles between '0' and '1' when the register is read, which provides indication that the register set has been unlocked.

VERSION NUMBER

| FFF01 | x | x | x | x |   | VER | 1 | т |

|-------|---|---|---|---|---|-----|---|---|

|       | 7 | 6 | 5 | 4 | 3 | 2   | 1 | 0 |

T : toggles between 0 and 1 with every read access of the Version Number register.

- VER : 000 when T=0

- 101 when T=1 for Early Production Version 100 when T=1 for Production Version

System board devices may be located on the EDATA bus rather than on the I/O expansion slot DATA bus. The SELDAT signal which controls the DATA to EDATA bus direction is affected by the two port location registers. This option is available for peripheral devices which cannot directly drive the high current I/O slot DATA bus. Note, however, that DMA transfers cannot be made to devices on the EDATA bus.

The SELDAT signal is active (low) when IOR is active and address bits A8 and A9 are low, or the PORTS LOCATION register indicates that an addressed port is on the EDATA bus. The SELDAT signal is also low when MEMR is active and the **8-bit** BIOS is being accessed.

### PORTS LOCATION REGISTER

| FFF06 | x x |                     | x                   | х    | А    | В    | с | D |   |  |  |  |

|-------|-----|---------------------|---------------------|------|------|------|---|---|---|--|--|--|

|       | 7   | 6                   | 5                   | 4    | 3    | 2    | 1 | 0 | 1 |  |  |  |

| A = ( | )   |                     | Port (              | ) On | DATA | Bus  |   |   |   |  |  |  |

| A = 1 | 1   |                     | Port (              | ) On | EDAT | A Bu | s |   |   |  |  |  |

| B =   | 0   |                     | Port <sup>-</sup>   | I On | DATA | Bus  |   |   |   |  |  |  |

| B =   | 1   |                     | Port <sup>-</sup>   | l On | EDAT | A Bu | s |   |   |  |  |  |

| C =   | 0   |                     | Port 2              | 2 On | DATA | Bus  |   |   |   |  |  |  |

| C =   | 1   | Port 2 On EDATA Bus |                     |      |      |      |   |   |   |  |  |  |

| D =   | 0   |                     | Port 3 On DATA Bus  |      |      |      |   |   |   |  |  |  |

| D =   | 1   |                     | Port 3 On EDATA Bus |      |      |      |   |   |   |  |  |  |

| 1     |     |                     |                     |      |      |      |   |   |   |  |  |  |

# THE PORTS LOCATION REGISTER IS CLEARED BY A MASTER RESET.

### HOT RESET REGISTER

| FFF07 | x | x | x | х | 0/1 | DA | A | н |

|-------|---|---|---|---|-----|----|---|---|

|       | 7 | 6 | 5 | 4 | 3   | 2  | 1 | 0 |

THE HOT RESET REGISTER IS CLEARED BY A MASTER RESET.

Register FFF07 is used to generate a hot reset to the processor or to generate an alternate A20 gate. The state of the A bit is OR'ed with the A20GT pin. If either the A bit is set or the A20GT pin is high, the A20 line is undisturbed. If both are low, then the A20 line is gated low. If the DA bit is set, then a CPU reset generated by the keyboard controller will reset the A bit; the A bit will not be reset by a hot reset generated by the FE3021. A hot reset is generated by changing the H bit from a '0' to a '1'. 131 clocks after the trailing edge of the MEMW strobe, the FRES pin will be pulled low. The reset pulse lasts for 32 clocks, then the FRES pin is actively pulled high for one clock cycle, then is tri-stated. If the FRES pin is pulled low externally (e.g. if wire-OR'ed with the 8042 CPU reset line), then the internal FE3021 registers will relock. If the FRES pin is not used, then it should be pulled up externally or the FE3021 registers will not unlock.

Bit 3 is a writeable bit which is not currently used.

|       | ENABLE PORTS REGISTER |   |   |   |     |     |     |     |   |  |  |  |  |  |

|-------|-----------------------|---|---|---|-----|-----|-----|-----|---|--|--|--|--|--|

| FFF10 | x                     | x | x | x | EN3 | EN2 | EN1 | EN0 |   |  |  |  |  |  |

|       | 7                     | 6 | 5 | 4 | 3   | 2   | 1   | 0   | _ |  |  |  |  |  |

### THE ENABLE PORTS REGISTER IS CLEARED BY A MASTER RESET.

The programmable PORT 0, PORT 1, PORT 2, and PORT 3 chip selects are enabled with the Enable Ports register. If the Enable bit is 0, the port chip select bit will always be at an inactive (high) state. All four ports are disabled after master reset. EN3 enables CS3 only when CS3 is a programmed chip select. When CS3 is a HDC chip select, CS3 is enabled by register FFF49, bit 1.

For ports 0, 1, and 2, the access will have the default wait states: 1 wait state for 16 bit accesses and 4 wait states for 8 bit accesses, with the wait states set from the FE3001. The selected chip must generate IOCS16 if it is a 16 bit peripheral.

PORT 3 CONTROL REGISTER

| FFF08 | x | x | x | x | w | /S | WSE | ОВ |

|-------|---|---|---|---|---|----|-----|----|

|       | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0  |

# THE PORT 3 CONTROL REGISTER IS CLEARED BY A MASTER RESET.

| WS | HDC DATA PORT HIGH<br>SPEED WAIT STATES |

|----|-----------------------------------------|

| 00 | 1                                       |

| 01 | 2                                       |

| 10 | 3                                       |

| 11 | 4                                       |

| 0B | CS3 WAIT STATES                    |

|----|------------------------------------|

| 0  | Default (slow)                     |

| 1  | High Speed Hard<br>Disk Controller |

| WSE: | HIGH SPEED HDC WAIT<br>STATE ENABLE           |

|------|-----------------------------------------------|

| 0:   | High Speed HDC Wait<br>States Set By FE3001   |

| 1:   | High Speed HDC Wait<br>States Set By WS Field |

For port 3, the access will normally have the default wait states but may also be programmed to have high speed wait state timing when CS3 is programmed as a hard disk chip select and the on-board 16-bit hard disk controller is capable of high speed access. When the high speed disk controller configuration is used, the WSE and OB fields should be set to '1', and the WS field will set the number of high speed wait states, timed from the CPUCLK, rather than from SYSCLK. The other disk controller ports will always be accessed at low speed.

When 0B is set to a 1, the FE3021 will generate the ONBD signal to the FE3001 during HDC accesses through port 3. The FE3001 will provide the same number of wait states it does for onboard memory. If it is desired, the number of wait states for the HDC can be extended using the WS and WSE fields.

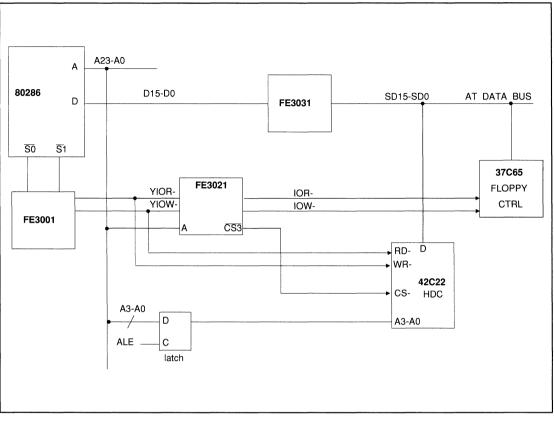

When implementing a high speed disk controller port, it is necessary to provide a separate address path for the hard disk controller. The HDC receives ungated I/O read and write strobes at the full CPU speed. The following schematic illustrates the required connections.

4

Figure 3. High Speed HDC Configuration

| FFF09 |   |   |   |   |   |    |     |    |

|-------|---|---|---|---|---|----|-----|----|

| FFF11 | x | x | x | x | 0 | 11 | LMA | sk |

| FFF19 | ^ | ^ | ~ | ^ | U | 0  |     |    |

| FFF21 |   |   |   |   |   |    |     |    |

|       | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0  |

| LMASK | A  | DRE | SS E       | BITS | COM | PAR | ED |    |    |   |  |

|-------|----|-----|------------|------|-----|-----|----|----|----|---|--|

| 00    | A9 | A8  | <b>A</b> 7 | A6   | A5  | A4  | A3 | A2 | A1 | Х |  |

| 01    | A9 | A8  | A7         | A6   | A5  | A4  | A3 | A2 | Х  | Х |  |

| 10    | A9 | A8  | <b>A</b> 7 | A6   | A5  | A4  | A3 | Х  | Х  | Х |  |

| 11    | A9 | A8  | <b>A</b> 7 | A6   | A5  | A4  | Х  | Х  | Х  | Х |  |

U = 0 : INCLUDE A8 IN ADDRESS COMPARISON

| LMASK | ADDRESS BITS COMPARED       |  |

|-------|-----------------------------|--|

| 00    | A9 X A7 A6 A5 A4 A3 A2 A1 X |  |

| 01    | A9 X A7 A6 A5 A4 A3 A2 X X  |  |

| 10    | A9 X A7 A6 A5 A4 A3 X X X   |  |

| 11    | A9 X A7 A6 A5 A4 X X X X    |  |

U = 1 : IGNORE A8 IN ADDRESS COMPARISON

THE PORT ADDRESS MASK REGISTER IS CLEARED BY A MASTER RESET.

| PORT | PORT CONTROL<br>REGISTER ADDRESS |

|------|----------------------------------|

| 0    | FFF09                            |

| 1    | FFF11                            |

| 2    | FFF19                            |

| 3    | FFF21                            |

NOTE: Bit 3 is not writeable and is always '0'.

| <b>FFF0A</b>                     |      | POR  | T ADC | )r - 1 | LOWE  | R MSE      | 3          |            |

|----------------------------------|------|------|-------|--------|-------|------------|------------|------------|

| FFF12<br>FFF1A<br>FFF22          | x    | x    | x     | x      | x     | x          | A9         | <b>A</b> 8 |

|                                  | 7    | 6    | 5     | 4      | 3     | 2          | 1          | 0          |

|                                  |      | PORT | r add | R - U  | IPPER | LSB        |            |            |

| FFF0B<br>FFF13<br>FFF1B          | x    | x    | x     | x      | A7    | <b>A</b> 6 | <b>A</b> 5 | <b>A</b> 4 |

| FFF23                            | 7    | 6    | 5     | 4      | 3     | 2          | 1          | 0          |

| FFF00                            |      | POR  |       | )r - I |       | R LSE      | 3          |            |

| FFF0C<br>FFF14<br>FFF1C<br>FFF24 | x    | x    | x     | x      | A3    | A2         | A1         | 0          |

| FFF <b>24</b>                    | 7    | 6    | 5     | 4      | 3     | 2          | 1          | 0          |

| PORT I/O ADD                     | DRES | S RE | GIST  | ERS    | ;     |            |            |            |

| A9-A8                            |      |      | A     | 7-A4   |       |            |            | AB         |

| PORT | PORT I/O ADDRESS REGISTERS |       |       |  |  |  |

|------|----------------------------|-------|-------|--|--|--|

|      | A9-A8                      | A7-A4 | A3-A0 |  |  |  |

| 0    | FFF0A                      | FFF0B | FFF0C |  |  |  |

| 1    | FFF12                      | FFF13 | FFF14 |  |  |  |

| 2    | FFF1A                      | FFF1B | FFF1C |  |  |  |

| 3    | FFF22                      | FFF23 | FFF24 |  |  |  |

The PORT I/O ADDRESS registers for all four ports are set to all zeros by a master reset.

The following tables list the I/O addresses and chip selects generated for each fixed port type. The chip selects are not gated with IOR or IOW. The CSNMI signal is decoded for both even and

odd addresses, so that access may be made to the FE3001 control register at address 073.

The floppy controller operations register select, configuration register select, and floppy disk controller chip select may be generated from the CSF pin and the ADDR2 and ADDR1 lines.

|                            | ADDR2 | ADDR1 | CSF |

|----------------------------|-------|-------|-----|

| OPERATIONS REGISTER ACCESS | 0     | x     | 1   |

| CONFIG REGISTER ACCESS     | 1     | 1     | 1   |

| FLOPPY CHIP SELECT ACTIVE  | Х     | 0     | 1   |

| PORT            | BIT SIZE | I/O ADDRESS        | ACTIVE PIN  | FUNCTION                                                                                    |

|-----------------|----------|--------------------|-------------|---------------------------------------------------------------------------------------------|

| FLOPPY          | 8        | 3F2<br>372         | CSF         | FDC Operation Select.<br>3F2 Is Primary Address,<br>372 Is Secondary                        |

|                 | 8        | 3F4-3F5<br>374-375 | CSF         | 3F4-3F5 Are Primary<br>Addresses, 374-375 Are<br>Secondary.                                 |

|                 | 8        | 3F6<br>376         | CS3*        | Hard Disk Controller<br>Chip Select. 3F6 Is<br>Primary Address, 376<br>Is Secondary.        |

|                 | 8        | 3F7<br>377         | CSF<br>CS3* | CS3 And CSF Pins Will<br>Be Asserted. 3F7 Is<br>Primary Address, 377<br>Is Secondary.       |

| 80287           | 8        | 0E0-0FF            | CS287       | 80287 Chip Select.                                                                          |

| 8042            | 8        | 060-06E<br>(EVEN)  | CS8042      | 8042 Chip Select.                                                                           |

| NMI<br>LOGIC    | 8        | 070-07F            | CSNMI       | Real Time Clock And<br>NMI Logic Select                                                     |

| PARITY<br>CHECK | 8        | 061-06F<br>(ODD)   | CSPTB       | Parity Check Select<br>And Port B Decode .<br>External Logic Must<br>Separate The Signals.  |

| HARD<br>DISK    | 16       | 1F0<br>170         | CS3 *       | HDC Chip Select - Data<br>Port Access. 1F0 Is<br>Primary Address,<br>170 Is Secondary       |

|                 | 8        | 1F1-1F7<br>171-177 | CS3         | HDC Chip Select - TASK<br>FILE. 1F1-1F7 Are<br>Primary Addresses,<br>171-177 Are Secondary. |

\* WHEN  $\overline{\text{CS3}}$  PIN IS PROGRAMMED AS HDC CHIP SELECT .

4

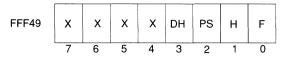

DH, PS, H, AND F ARE CLEARED TO '0' BY MASTER RESET

PRIMARY / SECONDARY PORT FUNCTION SELECT

DH=0: CS3 pin will respond to address

programmed by FFF22-FFF24

$DH=1: \overline{CS3}$  pin will respond to hard disk addresses

PS=0: Primary hard disk and floppy disk address

PS=1: Secondary hard disk and floppy disk ad-

dress

- H=0: On-board hard disk controller enabled

- H=1: Disable on-board hard disk controller

- F=0: On-board floppy disk controller enabled

- F=1: Disable on-board floppy disk controller

- Bit 2 = 0: Enable CSF Output

- Bit 1 = 0: Primary Hard Disk Address

- Bit 0 = 0: Primary Floppy Disk Address

## 6.0 MEMORY CONTROL

Four RAS pins are available for controlling up to four 16 bit wide banks of system board RAM. Eight CAS pins control the low and high bytes of each bank. During a refresh cycle, all RAS signals will be active (ignoring the RAM configuration register FFF57) and CAS signals will stay inactive. The RAS and CAS lines drive the DRAM array directly.

| PIN NUMBER | MNEMONIC | I/O | FUNCTION                                        |

|------------|----------|-----|-------------------------------------------------|

| 128        | RASO     | 0   | RAS Signal For DRAM Memory Bank 0               |

| 129        | RAS1     | 0   | RAS Signal For DRAM Memory Bank 1               |

| 130        | RAS2     | 0   | RAS Signal For DRAM Memory Bank 2               |

| 132        | RAS3     | 0   | RAS Signal For DRAM Memory Bank 3               |

| 125        | CASLO    | 0   | CAS Signal For DRAM Memory Bank 0,<br>Low Byte  |

| 126        | CASL1    | 0   | CAS Signal For DRAM Memory Bank 1,<br>Low Byte  |

| 2          | CASL2    | 0   | CAS Signal For DRAM Memory Bank 2,<br>Low Byte  |

| 3          | CASL3    | 0   | CAS Signal For DRAM Memory Bank 3,<br>Low Byte  |

| 4          | CASH0    | 0   | CAS Signal For DRAM Memory Bank 0,<br>High Byte |

| 5          | CASH1    | 0   | CAS Signal For DRAM Memory Bank 1,<br>High Byte |

| 6          | CASH2    | 0   | CAS Signal For DRAM Memory Bank 2,<br>High Byte |

| 131        | CASH3    | 0   | CAS Signal For DRAM Memory Bank 3,<br>High Byte |

| 18         | REFR     |     | Memory Refresh Signal                           |

| 43         | CSPROM   | 0   | BIOS PROM Select                                |

| 26         | TAP2     | 1   | Second Tap Output Of RAS Delay Line             |

| 44         | TAP1     |     | First Tap Output Of RAS Delay Line              |

| 58         | RAS      | 0   | To RAS Delay Line Input                         |

| 23         | DBLE     | 0   | To FE3031 Memory Data Bus Latch Enable          |

| 24         | ADR0     |     | From FE3001 Byte Conversion                     |

**Table 6. Memory Control Pin Information**

## 7.0 MEMORY ADDRESS MULTIPLEXER

The memory address multiplexer generates the row and column addresses for the DRAM. The memory address multiplexer outputs should be buffered by external drivers when driving the memory array.

The memory address multiplexer supports three sizes of DRAM: 64K, 256K, and 1 MB. The three sizes of DRAM's may be intermixed in any order.

The memory address multiplexer is designed so that SIMM mounted DRAM's of the three different sizes may be inserted into SIMM sockets without the need to change board jumpers.

| PIN NUMBER | MNEMONIC | I/O | FUNCTION                                      |

|------------|----------|-----|-----------------------------------------------|

| 31         | RA0      | 0   | Memory Address Multiplexer Output Bit 0 (LSB) |

| 32         | RA1      | 0   | Memory Address Multiplexer Output Bit 1       |

| 33         | RA2      | 0   | Memory Address Multiplexer Output Bit 2       |

| 34         | RA3      | 0   | Memory Address Multiplexer Output Bit 3       |

| 35         | RA4      | 0   | Memory Address Multiplexer Output Bit 4       |

| 36         | RA5      | 0   | Memory Address Multiplexer Output Bit 5       |

| 37         | RA6      | 0   | Memory Address Multiplexer Output Bit 6       |

| 38         | RA7      | 0   | Memory Address Multiplexer Output Bit 7       |

| 39         | RA8      | 0   | Memory Address Multiplexer Output Bit 8       |

| 41         | RA9      | 0   | Memory Address Multiplexer Output Bit 9 (MSB) |

Table 7. Memory Address Multiplexer Outputs

| 64K DRAM ADDRES | SS MUL | TIPLEX | ER CC | NFIGU | RATIO | N   |     |     |     |     |     |

|-----------------|--------|--------|-------|-------|-------|-----|-----|-----|-----|-----|-----|

| Memory Mode     |        | MA9    | MA8   | MA7   | MA6   | MA5 | MA4 | MA3 | MA2 | MA1 | MA0 |

| Independent     | RAS    | (A10   | A9)   | A8    | A7    | A6  | A5  | A4  | A3  | A2  | A1  |

| Non Page Mode   | CAS    | (A20   | A18)  | A16   | A15   | A14 | A13 | A12 | A11 | A10 | A9  |

| Independent     | RAS    | (A20   | A18)  | A16   | A15   | A14 | A13 | A12 | A11 | A10 | A9  |

| Page Mode       | CAS    | (A10   | A9)   | A8    | A7    | A6  | A5  | A4  | A3  | A2  | A1  |

| 2 Way Intlv     | RAS    | (A20   | A18)  | A16   | A15   | A14 | A13 | A12 | A11 | A10 | A17 |

| Page Mode       | CAS    | (A10   | A9)   | A8    | A7    | A6  | A5  | A4  | A3  | A2  | A1  |

| 4 Way Intiv     | RAS    | (A20   | A18)  | A16   | A15   | A14 | A13 | A12 | A11 | A18 | A17 |

| Page Mode       | CAS    | (A10   | A9)   | A8    | A7    | A6  | A5  | A4  | A3  | A2  | A1  |

| 256K DRAM ADDRE | SS MU  | LTIPLE | XER C | ONFIG | URATI | ON  |     |     |     |     |     |

| Independent     | RAS    | (A10)  | A9    | A8    | A7    | A6  | A5  | A4  | A3  | A2  | A1  |

| Non Page Mode   | CAS    | (A20)  | A18   | A16   | A15   | A14 | A13 | A12 | A11 | A10 | A17 |

| Independent     | RAS    | (A20)  | A18   | A16   | A15   | A14 | A13 | A12 | A11 | A10 | A17 |

| Page Mode       | CAS    | (A10)  | A9    | A8    | A7    | A6  | A5  | A4  | A3  | A2  | A1  |

| 2 Way Intlv     | RAS    | (A20)  | A18   | A16   | A15   | A14 | A13 | A12 | A11 | A19 | A17 |

| Page Mode       | CAS    | (A10)  | A9    | A8    | A7    | A6  | A5  | A4  | A3  | A2  | A1  |

| 4 Way Intlv     | RAS    | (A20)  | A18   | A16   | A15   | A14 | A13 | A12 | A20 | A19 | A17 |

| Page Mode       | CAS    | (A10)  | A9    | A8    | A7    | A6  | A5  | A4  | A3  | A2  | A1  |

**Table 8. Address Multiplexer Configurations**

| 1 MBIT DRAM ADD                  | RESS M | ULTIP | LEXER | CONF | IGURA | TION |     |     |     |     | ······     |

|----------------------------------|--------|-------|-------|------|-------|------|-----|-----|-----|-----|------------|

| Independent                      | RAS    | A10   | A9    | A8   | A7    | A6   | A5  | A4  | A3  | A2  | A1         |

| Non Page Mode                    | CAS    | A20   | A18   | A16  | A15   | A14  | A13 | A12 | A11 | A19 | A17        |

| Independent                      | RAS    | A20   | A18   | A16  | A15   | A14  | A13 | A12 | A11 | A19 | A17        |

| Page Mode                        | CAS    | A10   | A9    | A8   | A7    | A6   | A5  | A4  | A3  | A2  | A1         |

| 2 Way Intlv                      | RAS    | A20   | A18   | A16  | A15   | A14  | A13 | A12 | A21 | A19 | A17        |

| Page Mode                        | CAS    | A10   | A9    | A8   | A7    | A6   | A5  | A4  | A3  | A2  | A1         |

| 4 Way Intlv                      | RAS    | A20   | A18   | A16  | A15   | A14  | A13 | A22 | A21 | A19 | A17        |

| Page Mode                        | CAS    | A10   | A9    | A8   | A7    | A6   | A5  | A4  | A3  | A2  | A1         |

| REFRESH ADDRESS - ALL DRAM SIZES |        |       |       |      |       |      |     |     |     |     |            |

|                                  |        | A9    | A8    | A7   | A6    | • A5 | A4  | A3  | A2  | A1  | <b>A</b> 0 |

NOTE: Addresses in parentheses not used by DRAM.

### SYSTEM BOARD ROM WAIT STATE CONTROL REGISTER

| FFF50 | x | x | x | х | R۱ | NS | 0 | RWSE |

|-------|---|---|---|---|----|----|---|------|

|       | 7 | 6 | 5 | 4 | 3  | 2  | 1 | 0    |

| RWS  | HIGH SPEED<br>WAIT STATE |  |

|------|--------------------------|--|

| 00 * | 1                        |  |

| 01   | 2                        |  |

| 10   | 3                        |  |

| 11   | 4                        |  |

RWSE=1: Enables RWS, otherwise on-board ROM and RAM Wait States will be set by FE3001.

# THIS REGISTER IS CLEARED TO ZERO BY MASTER RESET.

The FE3021 can extend the number of processor wait states for an on-board BIOS access by setting the RWSE bit to a '1'. The number of wait states will then be determined by the value of the RWS field. If the RWSE bit is set to a '0', the number of wait states for an on-board BIOS access is controlled by the FE3001. The ability to add wait states for BIOS accesses is important for a 16-bit BIOS because the onboard memory read wait states programmed into the FE3001 apply to both on-board BIOS and on-board DRAM. That value will be programmed to optimize DRAM access time (typically zero wait states for page mode operations). This very fast access time will likely be too quick for BIOS ROMs and can therefore be extended for BIOS accesses by setting the RWSE bit.

Bit 1 is used for diagnostic purposes and should remain '0'.

The system BIOS address space may be from F0000 to FFFFF or E0000 to FFFFF. If the EGA BIOS is to be mapped, then the BIOS ROM chip select is also active when the region from C0000 to C3FFF or C0000 to C7FFF is addressed. The address output onto the expansion bus will be automatically translated. The BIOS PROM size and number of wait states will then apply to both the system BIOS region F0000-FFFFF and C0000-C3FFF.

The BIOS EPROM size may either be 8 bits or 16 bits. The EPROM size is determined at reset time, and is signaled by the IORDY line. If the IORDY line is high at the trailing edge of master reset, then the EPROM size is set to 16 bits. If the IORDY line is low at the trailing edge of master reset, then the EPROM size is set to 8 bits. No external logic is required for the 16 bit EPROM size. To select the 8 bit EPROM size, the IORDY line should be pulled low by a master reset. The MDATA bus is used for 16 bit EPROM's while the EDATA bus is used for 8 bit EPROM's.

The CSPROM signal is only active when MEMR is active.

| MEMORY ADDRESS RANGE<br>FOR ACTIVE CSPROM | FUNCTION                                                                                                                                                 |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0F0000-0FFFFF<br>FF0000-FFFFFF            | BIOS SIZE = 64K (DEFAULT)                                                                                                                                |

| 0E0000-0FFFF<br>FE0000-FFFFFF             | BIOS SIZE = 128K                                                                                                                                         |

| 0C0000-0C3FFF                             | 16K EGA BIOS Mapping Enabled<br>Addresses Translated To 0F8000-0FBFFF<br>Or 0F0000 - 0F3FFF                                                              |

| 0C0000-0C7FF                              | 32K EGA BIOS Mapping Enabled<br>Addresses Translated To 0F8000-0FFFFF<br>Or 0F0000 - 0F7FFF<br>* A16 is ignored in early production version (0000, 1011) |

### EPROM / RAM MAP CONTROL REGISTER

| FFF51 | x | x | x | x | EC | i<br>GA | MS | PS |

|-------|---|---|---|---|----|---------|----|----|

|       | 7 | 6 | 5 | 4 | 3  | 2       | 1  | 0  |

| EGA=00<br>EGA=01 | MS=X:<br>MS=0:<br>MS=1: | No EGA mapping.<br>16K EGA map. C0000 - C3FFF<br>mapped to F8000 - FBFFF<br>16K EGA map. C0000 - C3FFF                                         |

|------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| FOA 10           |                         | mapped to F0000 - F3FFF                                                                                                                        |

| EGA=10           | MS=0:                   | 32K VGA map. C0000 - C7FFF<br>mapped to F8000 - FFFFF                                                                                          |

|                  | MS=1:                   | 32K VGA map. C0000 - C7FFF<br>mapped to F0000 - F7FFF                                                                                          |

| PS =             | <b>0:</b>               | PROM chip select will be active<br>when address is 0F0000-0FFFFF<br>or FF0000-FFFFFF, for 64K<br>of BIOS.                                      |

|                  | 1:                      | Default case after master reset.<br>PROM chip select will be active<br>when address is 0E0000-0FFFFF<br>or FE0000-FFFFFF, for<br>128K of BIOS. |

# THIS REGISTER IS CLEARED TO ZERO BY A MASTER RESET.

| FFF52 | х | x | x | x | XLA | '0' | MLA | FAD |

|-------|---|---|---|---|-----|-----|-----|-----|

|       | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

### ALL BITS ARE CLEARED BY MASTER RESET

| XLA=0: | LA23 - LA17 low speed timing |

|--------|------------------------------|

|        |                              |

- XLA=1: LA23 LA17 high speed timing

- MLA=0: LA23 LA17 latches are transparent during refresh cycles MLA=1: LA23 - LA17 gated to '0' during refresh

- MLA=1: LA23 LA17 gated to '0' during refresh cycles

- FAD=0: 3 wait state EMS misses

- FAD=1: 2 wait state EMS misses

Register FFF52 controls logic for various speed enhancement and diagnostic modes. The XLA bit controls the timing of the LA23 - LA17 signals. Use of this bit can affect compatibility of plug-in bus cards.

When XLA=0, LA23 - LA17 signals are generated by latching the processor addresses by active  $\overline{S0}$  or  $\overline{S1}$ . The LA23 - LA17 latches become transparent when a MEMR, MEMW, IOR, or IOW strobe occurs. This bit should be 0 when running at 8 MHz, when the FE3001 is using the low speed clock.

When XLA=1, LA23 - LA17 signals are latched by active  $\overline{S0}$  or  $\overline{S1}$ , but do not become transparent again until two CPU clocks after MEMR, MEMW, IOR, or IOW. This delay provides proper 8 MHz bus emulation of the LA23 - LA17 signals when the processor is running at 16 MHz.

The MLA bit is provided for diagnostic purposes. Bit 2 of register FFF52 is reserved and must be 'O'

The FAD bit can be used to enhance EMS performance for lower speed systems. EMS misses are normally three wait states, which are necessary for 16/20 MHz operation. At 12 MHz and below. EMS misses only need to be two wait states. This bit can be used for the non-page or page mode 2 operation at 12 MHz or below. This bit should remain 0 for page mode 3 or 16/20 MHz operation.

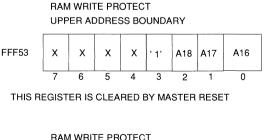

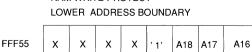

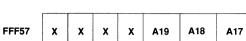

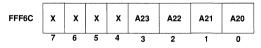

A single contiguous block of memory may be write protected, so that when BIOS ROM is copied into RAM, the RAM copy will not be inadvertently altered. Write protection is accomplished by not asserting CAS when MEMW is active

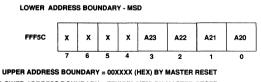

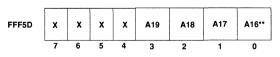

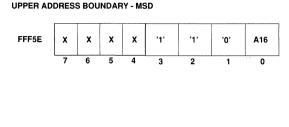

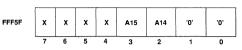

Master reset clears the upper address boundary registers and presets the lower address boundary registers, which disables write protection. Write protection is enabled on the address range where the RAM address is less than or equal to the upper address boundary as well as greater than or equal to the lower address boundary.

5

6

4 THIS REGISTER IS PRESET TO ALL '1' BY MASTER RESET

3 2 1

Write protection is programmable on 64K boundaries, and the write protection boundaries must be equal to or above 80000H and equal to or below FFFFFH. Write protection will not affect EMS writing even if the EMS window address range is covered by write protection boundaries. This allows protection of BIOS code copied into RAM without affecting operation of EMS.

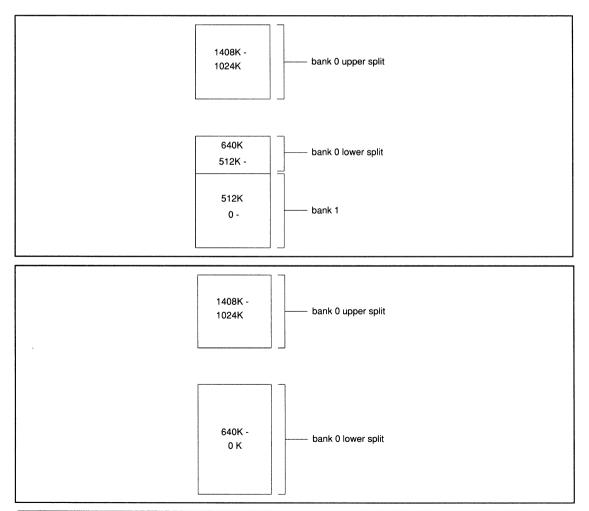

The memory banks may be programmed to various sizes on 128K boundaries, except the upper split of bank 0, which is programmable on 64K boundaries

A pair of window registers determines the address range for each memory bank. This allows the banks to be positioned at varving points and in different order than the bank number. If one bank of memory is defective, it can be disabled and the other banks can be programmed to replace it.

**NOTE:** For the early production version of the FE3021 (version reg=0000, 1011), bank 0 has three pairs of window registers to allow split addressing. The bottom split could be used for conventional memory from 8000 to 9FFFF. The top split could be used for extended memory or could be used to copy main BIOS from ROM to RAM in the address range E0000 or F0000 to FFFFF. A middle split was available for copying user and video BIOS from ROM to RAM. This middle split had boundaries programmable between C0000 to DFFFF in 16K address increments. One limitation was that if the middle split were used, unused memory between the splits could not be translated and used for extended memorv.

For the production version of the FE3021 (version reg=0000, 1001), the middle split of Bank 0 was removed. Video BIOS is shadowed instead by mapping the EGA/VGA BIOS to F0000 or F8000 and then shadowing the F0000 - FFFFF BIOS area. This method also allows a ROM resident setup program to reside at F0000 in ROM, which can be replaced with EGA/VGA BIOS by shadowing. This method allows a 512K bank to be allocated as 128K of conventional memory. 64K of shadowed VGA and system BIOS, and 320K of extended or EMS memory.

7

0

Δ

UPPER BOUNDARY MUST BE OFXXXX OR BELOW

LOWER BOUNDARY MUST BE OFXXXX OR BELOW **UPPER ADDRESS BOUNDARY = 09XXXX (HEX) BY MASTER RESET** LOWER ADDRESS BOUNDARY = 08XXXX (HEX) BY MASTER RESET

3

A19

3

2

A18

2

BANK 0 - UPPER SPLIT

1

A17

1

5 6

UPPER ADDRESS BOUNDARY

7

Х Х Х х

7 6 5 4

FFF59

LOWER ADDRESS BOUNDARY

**BANK 0 - UPPER SPLIT**

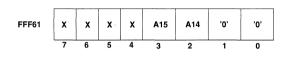

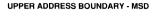

**UPPER ADDRESS BOUNDARY - MSD**

**UPPER ADDRESS BOUNDARY - LSD**

0/1\*

0

0/1\*

0

LOWER ADDRESS BOUNDARY = FFXXXX (HEX) BY MASTER RESET (UPPER SPLIT DISABLED)

LOWER ADDRESS BOUNDARY - LSD

\* Don't care

11/16/90

\*\* A16 is ignored in early production version (0000, 1011)

BANK 0 - MIDDLE SPLIT

х

UPPER ADDRESS BOUNDARY = 00XXXX (HEX) BY MASTER RESET

LOWER ADDRESS BOUNDARY = FFXXXX (HEX) BY MASTER RESET

'1'

'1'

2

**'0'**

1

A16

0

### (ONLY IN EARLY PRODUCTION VERSION)

UPPER ADDRESS BOUNDARY - LSD

LOWER ADDRESS BOUNDARY - LSD

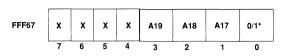

#### BANK 1

FFF60

UPPER ADDRESS BOUNDARY - MSD

LOWER ADDRESS BOUNDARY - MSD

X X

6 5 4 3

х

7

(MIDDLE SPLIT DISABLED)

| FFF62 | x | x | x | x | A23 | A22 | A21 | A20 |

|-------|---|---|---|---|-----|-----|-----|-----|

|       | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

### BANK 1

UPPER ADDRESS BOUNDARY - LSD

| FFF63 | x | x | x | x | A19 | A18 | A17 | 0/1* |

|-------|---|---|---|---|-----|-----|-----|------|

|       | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0    |

#### LOWER ADDRESS BOUNDARY - MSD

| FFF64 | x | x | x | x | A23 | A22 | A21 | A20 |

|-------|---|---|---|---|-----|-----|-----|-----|

|       | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

UPPER ADDRESS BOUNDARY = 07XXXX (HEX) BY MASTER RESET LOWER ADDRESS BOUNDARY = 00XXXX (HEX) BY MASTER RESET

#### LOWER ADDRESS BOUNDARY - LSD

| FFF65 | x | x | x | x | A19 | A18 | A17 | 0/1* |

|-------|---|---|---|---|-----|-----|-----|------|

|       | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0    |

\* Don't care

4

### BANK 2

LOWER ADDRESS BOUNDARY - MSD

6 5

(BANK 2 DISABLED BY MASTER RESET)

x x x x

7

| FFF66 | x | x | x | x | A23 | A22 | A21 | A20 |

|-------|---|---|---|---|-----|-----|-----|-----|

|       | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

THESE REGISTERS ARE CLEARED BY MASTER RESET

A23

3

4

THESE REGISTERS ARE PRESET TO ALL '1' BY MASTER RESET

A22

2

A21

1

A20

0

UPPER ADDRESS BOUNDARY - LSD

LOWER ADDRESS BOUNDARY - LSD

| FFF69 | x | x | x | x | A19 | A18 | A17 | 0/1* |

|-------|---|---|---|---|-----|-----|-----|------|

|       | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0    |

### BANK 3

FFF68

UPPER ADDRESS BOUNDARY - MSD

| FFF6A | x | x | x | x | A23 | A22 | A21 | A20 |

|-------|---|---|---|---|-----|-----|-----|-----|

|       | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

THESE REGISTERS ARE CLEARED BY MASTER RESET

### BANK 3

UPPER ADDRESS BOUNDARY - LSD

| FFF6B | x | x | x | x | A19 | A18 | A17 | 0/1* |

|-------|---|---|---|---|-----|-----|-----|------|

|       | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0    |

### LOWER ADDRESS BOUNDARY - MSD

THESE REGISTERS ARE PRESET TO ALL '1' BY MASTER RESET (BANK 3 DISABLED BY MASTER RESET)

### LOWER ADDRESS BOUNDARY - LSD

\* Don't care

FFF6F

Х

7

Х

6

х

5

The RAM banks may be either independent or two-way or four-way page interleaved. DRAM banks which are interleaved must be the same DRAM size

0/1\*

CFG

1

0

2

\* Don't care

Х

4 3

This register is not used in non-page mode.

When the memory system operates in page mode, the banks of memory may operate independently or may be interleaved. Interleaving may decrease the average number of wait states, thus increasing performance, but interleaving may only be done if the memory banks to be interleaved are the same size.

| CFG  | FUNCTION                                                       |

|------|----------------------------------------------------------------|

| 000* | All banks are independent                                      |

| 011  | Bank 2 paired with Bank 3,<br>Banks 0 and 1 are<br>independent |

| 101  | Bank 0 paired with Bank 1,<br>Banks 2 and 3 are<br>independent |

| 111  | Bank 0 paired with Bank 1,<br>Bank 2 paired with Bank 3        |

| 110  | All four banks are<br>interleaved                              |

### \* : Default after Master Reset

# 2 WAY INTERLEAVE 3 2 3 **BANKS 2 + 3** 2 3 0 1 **BANKS 0 + 1** 0 2047 1 1024 1023 0 0

### ADDRESS

## **4 WAY INTERLEAVE**

4-24

When the memory system operates in page mode, accesses to DRAM in the same page are made with zero wait states. An access to a different page, or the first access to a page after a refresh, DMA, or master cycle will be made either with two wait states for memory mode 2, or three wait states for memory mode 3. The actual page size is variable, depending on the DRAM size.

| DRAM SIZE | PAGE SIZE  |

|-----------|------------|

| 64K       | 512 bytes  |

| 256K      | 1024 bytes |

| 1M        | 2048 bytes |

|           |            |

Multiple banks of memory operating in page mode may operate independently or may be interleaved. Interleaving may decrease the average number of wait states, thus increasing performance, but interleaving may only be done if the memory banks to be interleaved are the same size. Only banks 0 and 1 or banks 2 and 3 may be interleaved together when implementing 2-way interleave. When banks 0 and 1 are interleaved, bank 1 boundary registers should be programmed so that the bank is disabled and the bank 0 boundaries should be programmed as if bank 0 were twice the normal size. As an example, for a system with 2 banks of 256K DRAM operating independently, the banks could be programmed as shown in the upper diagram below.

When the banks are interleaved, the banks would be programmed as shown in the lower diagram below.

The following tables illustrate memory system characteristics with various configurations of memory and processor speed, both for page mode and non-page mode DRAM access.

For a page mode hit, the read and write accesses may have different performance. For a page

mode miss or the first access to a page, the read and write accesses have the same performance. In a page mode miss, RAS starts out low and must be brought high for a RAS precharge time before the memory can be accessed.

|               | CPU       |      | WAIT STATES |             |            |

|---------------|-----------|------|-------------|-------------|------------|

| NON-PAGE MODE | FREQUENCY | READ | WRITE       | EMS<br>MISS | DRAM SPEED |

| MODE 4        | 8 MHz     | 0    | 0           | 2           | 120 ns     |

| MODE 0        | 16 MHz    | 1    | 1           | 3           | 80 ns      |

| MODE 4        | 12.5 MHz  | 1    | 1           | 2           | 120 ns     |

|           | CPU       |              |   |                 |             |            |  |

|-----------|-----------|--------------|---|-----------------|-------------|------------|--|

| PAGE MODE | FREQUENCY | READ WRITE N |   | NON-EMS<br>MISS | EMS<br>MISS | DRAM SPEED |  |

| MODE 2    | 12.5 MHz  | 0            | 1 | 2               | 3           | 120 ns     |  |

| MODE 3    | 20 MHz    | 0            | 1 | 3               | 3           | 80 ns      |  |

| MODE 3    | 16 MHz    | 0            | 1 | 3               | 3           | 100 ns     |  |

| MODE 3    | 12.5 MHz  | 0            | 1 | 3               | 3           | 120 ns     |  |

The DRAM timing is set by an external delay line for DMA or master mode transfers. The RAS leading edge becomes active from the active level of the MEMR or MEMW signals.

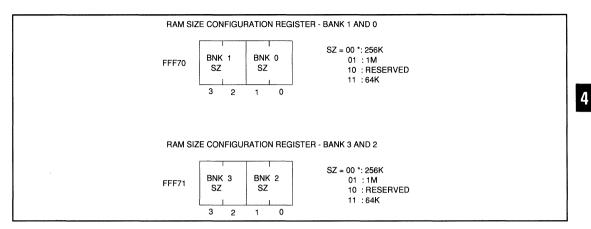

The DRAM timing modes are programmed by writing into register FFF72. The DRAM timing mode is

actually switched during a processor hold state caused by a refresh, DMA, or bus master cycle. The Present DRAM Timing Mode register contains the current timing mode. Registers FFF72 and FFF73 will thus disagree until after a processor hold state occurs; typically, a refresh cycle will occur in 10 to 15 microseconds.

|                                                                                 |   | [ | DRAN |   | ING M | IODE  |           |  |

|---------------------------------------------------------------------------------|---|---|------|---|-------|-------|-----------|--|

| FFF72                                                                           | x | x | x    | x | D     | DTYP  |           |  |

|                                                                                 |   |   |      |   |       |       |           |  |

| DRAM TIMING MODE WILL GO INTO EFFECT AFTER<br>REFRESH, DMA, OR OTHER HOLD CYCLE |   |   |      |   |       |       |           |  |

| PRESENT DRAM TIMING MODE                                                        |   |   |      |   |       |       |           |  |

| FFF73                                                                           | x | x | x    | x | D     | DTYP  | READ-ONLY |  |

|                                                                                 | 7 | 6 | 5    | 4 | 3     | 2 1 0 |           |  |

| DTYP | DRAM MODE                                                                              |          |  |

|------|----------------------------------------------------------------------------------------|----------|--|

| 000* | Non-Page                                                                               | (MODE 0) |  |

| 001  | Zero Wait State Read, One Wait State Write                                             | (MODE 1) |  |

| 010  | Page Mode DRAM At 12.5 MHz CPU rate                                                    | (MODE 2) |  |

| 011  | Standard Page Mode for 8-20 MHz CPU rate                                               | (MODE 3) |  |

| 100  | Identical to Mode 0, but RAS delayed<br>one-half CPU clock                             | (MODE 4) |  |

| 101  | Non-Page for 8-12 MHz CPU rate, with 0 Wait<br>States, RAS pulse width is 2 CPU clocks | (MODE 5) |  |

Default after Master Reset

D = 0: Normal operation (default) 1 : Reversed for diagnostics:

: Reversed for diagnostics; disables DRAM Page Mode Hit/Miss logic

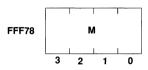

### 8.0 EMS MEMORY

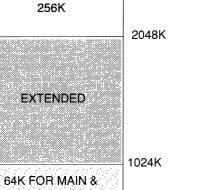

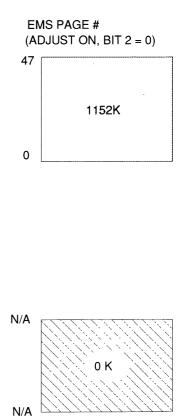

RAM memory above 1024K may be used both for expanded or extended memory. EMS memory may be as small as 128K bytes or as large as 7168K bytes. The EMS memory is accessed by two sets of EMS Page Registers, which reside in user I/O space. Each set of EMS Page Registers points to 36 blocks of memory, each block 16K bytes in size, which make up the EMS Page Frame. Four of the blocks are located above 640K, with the other 32 blocks located between 128K and 640K.

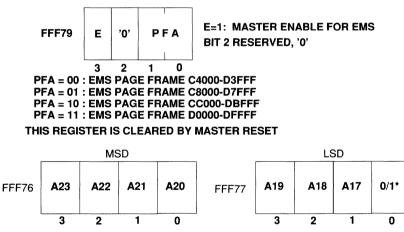

Each EMS Page Register is associated with one page of the EMS Page Frame, and consists of an enable bit and a 10 bit page number. When enabled, a 24 bit real address is formed by taking the 10 bit page number and appending the 14 bit address referencing the byte or word in the EMS page. The 24 bit address is then used to access the DRAM memory controlled by the FE3021.

In either page mode or non-page mode, if the DRAM row address does not change, then no additional wait states are required for EMS translation. This will allow EMS access without additional wait states if accesses are made to

the same 512, 1024, or 2048 byte page, depending on DRAM size.

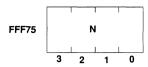

The EMS hardware must first be configured by programming the EMS control registers located in the FFF00-FFFFF register space, which is unlocked by writing to memory location FFF00 eight times. The I/O port locations of the EMS Page Registers are in user I/O space and their locations are selected with EMS Configuration Registers FFF75 and FFF78.

EMS Configuration Register FFF79 is used to completely enable or disable EMS, as well as to switch between the two sets of EMS Page registers. When the 'E' bit is '0', EMS operation is disabled and the EMS registers in user I/O space are inaccessible. When this is '0', it is as if the EMS hardware had been "unplugged" from the bus. When the 'E' bit is a '1', the EMS registers in the user I/O space become accessible. Registers FFF75 and FFF78 (which determine the I/O port addresses for the EMS logic), should be programmed prior to setting the 'E' bit to '1'. EMS CONFIGURATION REGISTER N

THIS REGISTER IS LOADED WITH '0110' BY MASTER RESET

**EMS CONFIGURATION REGISTER M**

THIS REGISTER IS LOADED WITH '1000' BY MASTER RESET

EMS CONFIGURATION REGISTER

LOWER EMS BOUNDARY

THESE REGISTERS ARE SET TO '1111' BY MASTER RESET \* Don't care

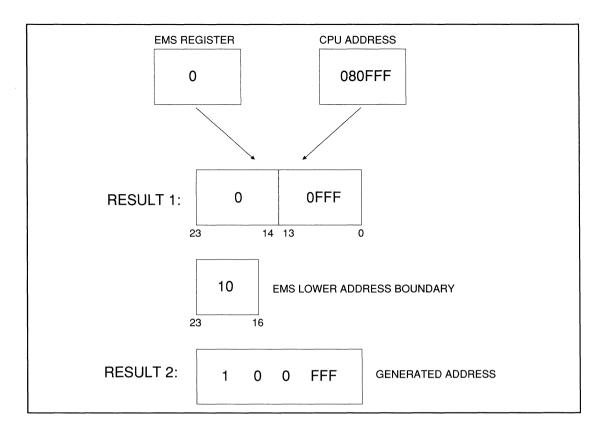

Registers FFF76 and FFF77 are used to allocate memory for EMS, on 128K byte boundaries. Memory with addresses below the EMS boundary is accessed normally, as conventioanl or extended memory.

On-board memory with addresses above the EMS boundary is reserved for use only as EMS

memory. DRAM memory accesses to addresses above the EMS boundary are made to the expansion bus. This allows EMS, off-board, and onboard extended memory to be used simultaneously.

Any CPU address above 1 MB (the EMS lower address boundary), is assumed to reference memory on the expansion bus, rather than onboard memory, which prevents extended memory references from affecting on-board EMS memory.

EMS DMA Control Register FFF7A is used to control the selected EMS map register set during DMA or master transfers. This allows DMA transfers to be made to a particular EMS task, whether or not it is the currently selected task.

On-board memory may be allocated either to extended or to EMS memory in 128K byte blocks. EMS memory is allocated from the top of onboard memory down to the desired limit.

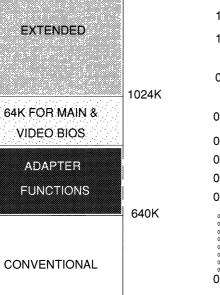

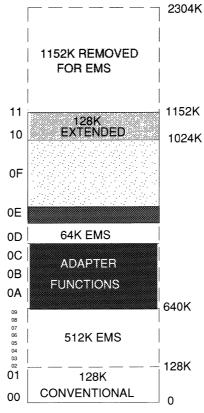

As an example, if the system contained 2 MB of DRAM, the memory map (without EMS) might look similar to figure 5a on the following page. The system would contain 640K of conventional

memory and 1,280K of extended memory. The 1,280K of extended memory is composed of two parts: the original 1,024K and 256K of memory relocated from 0A0000 - 0E0000. The 128K area from 0E0000 - 0F0000 could also be relocated but in this example, it is not.

Figure 5b illustrates the memory map after EMS has been installed. The EMS boundary registers have been programmed so that on-board memory above 1,152K is reserved for EMS. 128K of on-board extended memory remains between 100000 - 120000. Additional extended memory could be added on the expansion bus, starting at 120000. Two EMS areas are shown, one 64K area at 0D0000 - 0E0000, and the other at 020000 - 0A0000.

Figure 5c shows the possible EMS page numbers ranging from 0 - 4F for the 1,280K of memory available for EMS paging.

$\otimes$

23 22

21 20

11 10

0F

0E

0D

0C

0B

0A

0987605432100

a) 2 MB Memory Map

before EMS installed

2304K

0

b) EMS Installed

72 PAGES TOTAL = 1152K EMS

11/16/90

Figure 4. EMS/Memory Map Configurations

4-31

FE3021

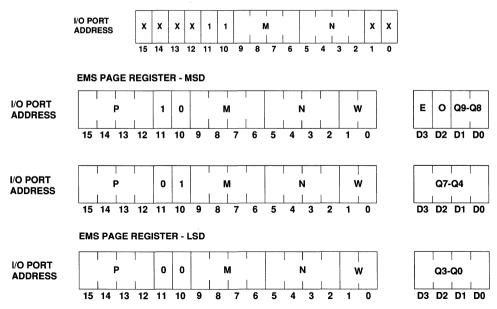

The EMS Control Register and EMS Page Registers are addressed in the user I/O port address space, I/O ports 100 (hex) through 3FF (hex). The EMS Control Registers and EMS Page Registers are selected when the I/O port address bits 9 - 6 match the value 'M' programmed by register FFF78 and the I/O port address bits 5 - 2 match the value 'N' programmed by register FFF75.

The EMS I/O Control Port is used to enable or disable EMS translation. When EMS translation is disabled, the EMS I/O control port and EMS page registers may still be accessed, but EMS page swapping will not occur.

The EMS I/O Control Port is also used to select the active page register set. When the processor accesses EMS memory, it always uses the register set specified by the TK bit. Normally, when DMA accesses EMS memory, it also uses the register set specified by the TK bit. Alternatively, the DMA transfer may be made using a particular register set, independently of the register set currently being used by the processor. This allows a DMA operation to start, continue, and finish while the processor is time-slicing and swapping back and forth between two programs.

The P and W fields for each page register are specified in the following table. Each EMS Page register is composed of a one bit enable bit (E) and a 10-bit page number (Q9-Q0). EMS translation for the EMS page is enabled when the E bit is a '1'.

#### EMS CONTROL REGISTER

| EMS I/O<br>CONTROL<br>PORT | EMS | тк             | ртк | DEN               |

|----------------------------|-----|----------------|-----|-------------------|

|                            | 3   | 2              | 1.  | 0                 |

|                            |     | EMS = 1        | :   | EMS TR            |

|                            |     | DEN = 0        | :   | DMA TR<br>SET SPE |

|                            |     | <b>DEN</b> = 1 | :   | DMA TR<br>SET SPE |

EMS CONTROL REGISTER ADDRESS LOCATION

4

## 9.0 TEST MODE

All output pins will become tristated if <u>YMEMR</u> and <u>YMEMW</u> are active simultaneously while <u>MR</u> is active. The outputs will remain tristated if <u>MR</u> is brought inactive while <u>YMEMR</u> and <u>YMEMW</u> are both active. The outputs will become active drivers again when  $\overline{\text{MR}}$  is brought low without both  $\overline{\text{YMEMR}}$  and  $\overline{\text{YMEMW}}$  active. This "all output tristate" mode allows an in-circuit board tester to drive the FE3021 output pins.

| Р    | W  | EMS PAGE    |              |             |             |  |  |

|------|----|-------------|--------------|-------------|-------------|--|--|

|      |    | PFA=00      | PFA=01       | PFA=10      | PFA=11      |  |  |

| 0000 | 11 | D0000-D3FFF | D4000-D7FFF  | D8000-DBFFF | DC000-DFFFF |  |  |

| 0000 | 10 | CC000-CFFFF | D0000-D3FFF  | D4000-D7FFF | D8000-DBFFF |  |  |

| 0000 | 01 | C8000-CBFFF | CC000-CFFFF  | D0000-D3FFF | D4000-D7FFF |  |  |

| 0000 | 00 | C4000-C7FFF | C8000-CBFFF  | CC000-CFFFF | D0000-D3FFF |  |  |

| 1001 | 11 | 9C000-9FFFF | 624K TO 640K |             |             |  |  |

| 1001 | 10 | 98000-9BFFF | 608K TO 624K |             |             |  |  |

| 1001 | 01 | 94000-97FFF | 592K TO 608K |             |             |  |  |

| 1001 | 00 | 90000-93FFF | 576K TO 592K |             |             |  |  |

| 1000 | 11 | 8C000-8FFFF | 560K TO 576K |             |             |  |  |

| 1000 | 10 | 88000-8BFFF | 544K TO 560K |             |             |  |  |

| 1000 | 01 | 84000-87FFF | 528K TO 544K |             |             |  |  |

| 1000 | 00 | 80000-83FFF | 512K TO 528K |             |             |  |  |

| 0111 | 11 | 7C000-7FFFF | 496K TO 512K |             |             |  |  |

| 0111 | 10 | 78000-7BFFF | 480K TO 496K |             |             |  |  |

| 0111 | 01 | 74000-77FFF | 464K TO 480K |             |             |  |  |

| 0111 | 00 | 70000-73FFF | 448K TO 464K |             |             |  |  |

| 0110 | 11 | 6C000-6FFFF | 432K TO 448K |             |             |  |  |

| 0110 | 10 | 68000-6BFFF | 416K TO 432K |             |             |  |  |

| 0110 | 01 | 64000-67FFF | 400K TO 416K |             |             |  |  |

| 0110 | 00 | 60000-63FFF | 384K TO 400K |             |             |  |  |

| 0101 | 11 | 5C000-5FFFF | 368K TO 384K |             |             |  |  |

| 0101 | 10 | 58000-5BFFF | 352K TO 368K |             |             |  |  |

| 0101 | 01 | 54000-57FFF | 336K TO 352K |             |             |  |  |

| 0101 | 00 | 50000-53FFF | 320K TO 336K |             |             |  |  |

| 0100 | 11 | 4C000-4FFFF | 304K TO 320K |             |             |  |  |

| 0100 | 10 | 48000-4BFFF | 288K TO 304K |             |             |  |  |

| 0100 | 01 | 44000-47FFF | 272K TO 288K |             |             |  |  |

| 0100 | 00 | 40000-43FFF | 256K TO 272K |             |             |  |  |

| 0011 | 11 | 3C000-3FFFF | 240K TO 256K |             |             |  |  |

| 0011 | 10 | 38000-3BFFF | 224K TO 240K |             |             |  |  |

| 0011 | 01 | 34000-37FFF | 208K TO 224K |             |             |  |  |

| 0011 | 00 | 30000-33FFF | 192K TO 208K |             |             |  |  |

| 0010 | 11 | 2C000-2FFFF | 176K TO 192K |             |             |  |  |

| 0010 | 10 | 28000-2BFFF | 160K TO 176K |             |             |  |  |

| 0010 | 01 | 24000-27FFF | 144K TO 160K |             |             |  |  |

| 0010 | 00 | 20000-23FFF | 128K TO 144K |             |             |  |  |

Table 9. EMS Page Register Information

#### 10.0 FE3021 PINOUT

As illustrated in Figure 5, the FE3021 is packaged in a 132-pin plastic flat pack. Table 10 groups the pins by function.

| AT BUS |       | DATA BUS  | DATA BUS |           | RFACE | MEMORY CONTROL |     |  |

|--------|-------|-----------|----------|-----------|-------|----------------|-----|--|

| LA23   | 63    | EDATA3    | 17       | A23       | 74    | RAS0           | 128 |  |

| LA22   | 70    | EDATA2    | 16       | A22       | 78    | RAST           | 129 |  |

| LA21   | 71    | EDATA1    | 15       | A21       | 79    | RAS2           | 130 |  |

| LA20   | 93    | EDATA0    | 14       | A20       | 80    | RAS3           | 132 |  |

| LA19   | 95    | CHIP SELE | CTS      | A19       | 81    | CASLO          | 125 |  |

| LA18   | 102   | AND CONT  | ROL      | A18       | 82    | CASL1          | 126 |  |

| LA17   | 103   | CS0       | 48       | A17       | 83    | CASL2          | 2   |  |

| ADDR19 | 59    | CS1       | 47       | A16       | 84    | CASL3          | 3   |  |

| ADDR18 | 61    | CS2       | 46       | A15       | 85    | CASHO          | 4   |  |

| ADDR17 | 62    | CS3       | 45       | A14       | 86    | CASH1          | 5   |  |

| ADDR16 | 64    | CSF       | 49       | A13       | 87    | CASH2          | 6   |  |

| ADDR15 | 65    | CS8042    | 60       | A12       | 88    | CASH3          | 131 |  |

| ADDR14 | 66    | CS287     | 56       | A11       | 89    | REFR           | 18  |  |

| ADDR13 | 68    | CSNMI     | 20       | A10       | 90    | CSPROM         | 43  |  |

| ADDR12 | 69    | CSPTB     | 22       | A9        | 109   | ONBD           | 57  |  |

| ADDR11 | 72    | ADSTB     | 53       | A8        | 110   | BHE            | 21  |  |

| ADDR10 | 73    | SELDAT    | 40       | A7        | 111   | DBLE           | 23  |  |

| ADDR9  | 75    | YMEMR     | 10       | A6        | 112   | ADR0           | 24  |  |

| ADDR8  | 94    | YMEMW     | 11       | A5        | 113   | LOMEG          | 25  |  |

| ADDR7  | 96    | YIOR      | 12       | A4        | 114   | A20GT          | 54  |  |

| ADDR6  | 97    | YIOW      | 13       | A3        | 115   |                |     |  |

| ADDR5  | 98    | IOR       | 8        | A2        | 116   | RESET          |     |  |

| ADDR4  | 100   | IOW       | 9        | A1        | 117   | RESET          | 28  |  |

| ADDR3  | 101   | MEMORY A  | DDRESS   | A0        | 118   | FRES           | 19  |  |

| ADDR2  | 104   | MUX       |          | <u>50</u> | 119   |                |     |  |

| ADDR1  | 106   | RA9       | 41       | S1        | 120   |                |     |  |

| ADDR0  | 105   | RA8       | 39       | M/IO      | 121   |                |     |  |

| MASTER | 52    | RA7       | 38       | CPUCLK    | 122   |                |     |  |

| GROUND | POWER | RA6       | 37       | HLDA      | 123   |                |     |  |

| 1      | 7     | RA5       | 36       | IORDY     | 127   |                |     |  |

| 27     | 30    | RA4       | 35       | L         |       | l              |     |  |

| 29     | 50    | RA3       | 34       |           |       |                |     |  |

| 42     | 55    | RA2       | 33       |           |       |                |     |  |

| 51     | 77    | RA1       | 32       |           |       |                |     |  |

| 67     | 92    | RAO       | 31       |           |       |                |     |  |

| 76     | 107   | RAS       | 58       |           |       |                |     |  |

4

### **11.0 DC OPERATING CHARACTERISTICS**

$T_a = 0^{\circ} \text{ to } 70^{\circ} \text{ C}, \quad \text{Vcc} = 5 \text{ V} \pm .25 \text{ V}$

| SYMBOL | CHARACTERISTIC                             | MIN | MAX | UNITS | CONDITIONS                                              |

|--------|--------------------------------------------|-----|-----|-------|---------------------------------------------------------|

| IIL    | Input Leakage                              |     | ±10 | UA    | VIN=.4 TO VCC                                           |

| IOZ    | Tri-State And Open<br>Drain Output Leakage |     | ±10 | UA    | VOUT=.4 TO VCC                                          |

| VIH    | Input High Voltage                         | 2.0 |     | V     |                                                         |

| VIL    | Input Lowvoltage                           |     | .8  | V     |                                                         |