# W90220F PA-RISC Embedded Controller

Version 0.84

March 1999

# **Table of Contents**

### TABLE OF CONTENTS

#### **1. OVERVIEW**

2. FEATURES

#### 3. PIN CONFIGURATION

- 3.1 Pin Diagram

- 3.2 Detailed Pin Descriptions

### 4. CPU CORE

- 4.1 Overview

- 4.2 Block diagram

- 4.3 Features

- 4.4 PA-RISC Architecture

- 4.4.1 CPU Resources

- 4.4.2 Addressing Mode & Memory Map

- 4.4.3 Branch Control

- 4.4.4 Interrupt Control

- 4.5 Pipeline Operation

- 4.6 Implementation Dependent features

- 4.6.1 MultiMedia Extension Instruction Set

- 4.6.2 MAC unit and Releated Instruction Set

- 4.6.3 Diagnostic Instruction Set

- 4.6.4 Flush Instruction/Data Cache & Branch-Target-Buffer (BTB)

- 4.6.5 Level-0 Debug SFU

- 4.7 Power Management Unit

- 4.8 Serial ICE interface

#### 5. MEGACELLS

- 5.1 Functional Descriptions

- 5.1.1 Memory Controller

- 5.1.2 DMA Controller

- 5.1.3 PCI Bridge

- 5.1.4 Parallel Port Interface (PPI)

- 5.1.5 UART

2

Version 0.84

# W90220F

Version 0.84

- 5.1.6 Synchronous Serial Port Interface (SSI)

- 5.1.7 Timer Channels

- 5.2 Register Definitions

- 5.2.1 Memory Controller

- 5.2.2 DMA Controller

- 5.2.3 PCI Bridge

- 5.2.4 Parallel Port Interface (PPI)

- 5.2.5 UART

- 5.2.6 Synchronous Serial Port Interface (SSI)

- 5.2.7 Timer Channels

### 6. ELECTRICAL SPECIFICATIONS

- 6.1 Absolute Maximum Ratings

- 6.2 DC Specifications

- 6.3 AC Specifications

- 6.3.1 Memory Controller

- 6.3.2 DMA Controller

- 6.3.3 PCI Bridge

- 6.3.4 Parallel Port Interface (PPI)

- 6.3.5 UART

- 6.3.6 Synchronous Serial Port Interface (SSI)

- 6.3.7 Timer Channels

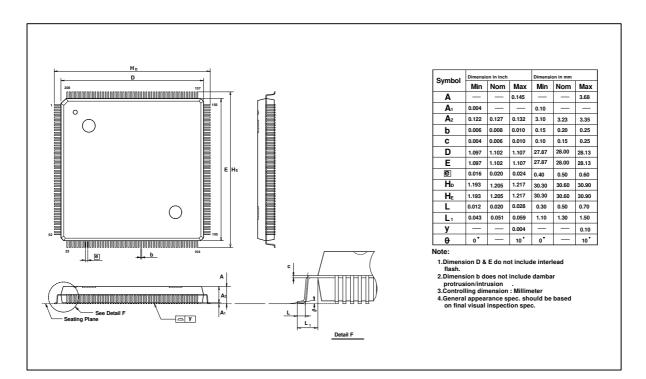

### 7. PACKAGE DIMENSIONS

3

4

# **1. OVERVIEW**

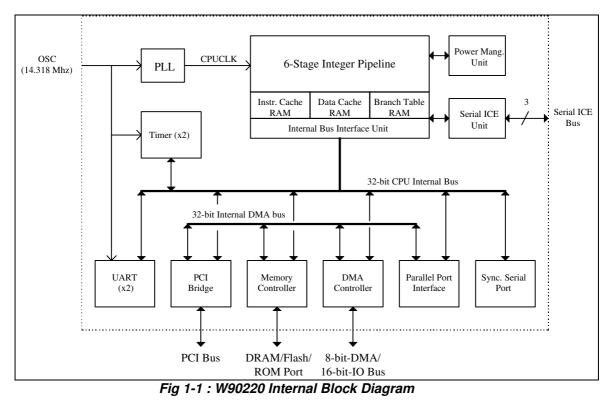

The W90220 is a high performance, highly integrated 32-bit processor intended for a wide range of embedded applications, such as videophone, internet devices, internetworking platform. Fig 1-1 shows a block diagram of the overall system. The W90220 consists of a 32-bit PA-RISC core, memory controller and integrated logics for I/O modules

The PA-RISC core is equipped with 4 KBytes of instruction cache memory and 4 KBytes of data cache memory augmented with a dual-cycle multiply/accumulate module running up to 150 MHz. It allows to implement integrated DSP functions like software modem for high-performance standard data and fax protocols. A flexible power management scheme (under software control) and lots of low power circuits have been used to eliminate the chip's power consumption. The W90220 consume only 375 mA at its maximum speed (150 MHz) on a full-load system.

The chip provides two 8-bit DMA channels, four 16-bit IDE I/O channels, a PCI bridge supporting up to four external PCI masters, a IEEE-1284 compliant parallel port interface (PPI), two RS232 type universal asynchronous serial port (UART), two timer channels, a flexible synchronous interface (SSI) connecting to an external audio or telephony codec devices, a proprietary serial ICE interface (SP-ICE) for software development and debugging.

The chip has a high performance memory controller. The types of external memory devices supported include dynamic random access memory (DRAM), Extended data out dynamic random access memory (EDO-DRAM), static random access memory (SRAM), Flash memory as well as read-only memory (ROM).

Version 0.84

Version 0.84

# 2. FEATURES

5

- PQFP 208-pin package

- High level of integration

- minimal number of inter-chip connections

- 32-bit PA-RISC core with cache memory, multiply-accumulate module and flexible power management unit

- DMA controller provides two external 8-bit DMA slots and four 16-bit IDE-IO slots

- memory controller supports four banks of EDO- or fast-page-mode DRAM, Flash, ROM and SRAM

- an PCI bridge supports four PCI master devices

- an IEEE-1284 compliant parallel port connecting an external printer

- two RS-232 compliant serial port connecting external MODEM controller or other serial devices

- a synchronous serial port connecting external audio or telephony codec devices

- two timer channels for general purpose usage

- High performance and low power consumption

- 0.35-micron single-poly-triple-metal CMOS process

- split rail design (3.3V/5V IO and 3.3V core)

- maximal operation frequency : 150 Mhz

- typical active current : 2.5mA/Mhz

- typical suspend current (PLL turn off) : -

- fully static design, afford dynamic turn on/off cpu clock or PLL module+

- programable standby clock to reduce standby current

- real time clock and UART baud rate base on 14.318 Mhz

- A flexible hardware serial ICE port for monitor/update cpu status at any time

# **3. PIN CONFIGURATION**

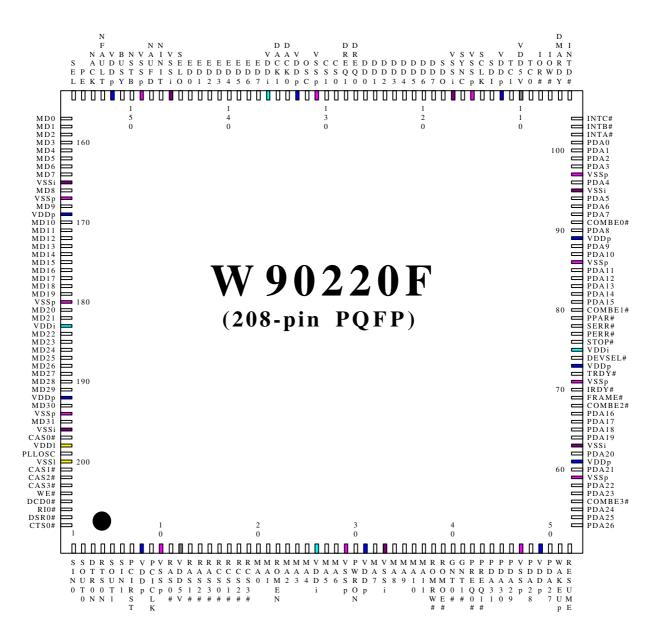

The W90220 family of embedded controllers is available in a 208-pin quad flat pack (PQFP) device configuration, shown below.

# 3.1. PIN DIAGRAM

# 3.2 DETAILED PIN DESCRIPTIONS

The following abbreviations are used for pin types in the following sections : (I) indicates inputs; (O) indicates outputs; (I/O) indicates a bidirectional signal; (TS) indicates three-state; (OC) indicates open collector.

| DIR | PIN #                                             | DESCRIPTION                                                                                                                                                                                                     |

|-----|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                   |                                                                                                                                                                                                                 |

| 1   | 30                                                | CPU Power-On reset input, high active                                                                                                                                                                           |

| 1   | 199                                               | 14.318Mhz Oscillator input for internal PLL                                                                                                                                                                     |

| 1   | 132                                               | 14.318Mhz Oscillator input for Timer, UART                                                                                                                                                                      |

|     |                                                   | for more detail description of the PCI signals please refer to the PCI LOCAL                                                                                                                                    |

|     |                                                   | BUS SPECIFICATION                                                                                                                                                                                               |

| 1   | 102                                               | PCI Interrupt input, level senstive, low active signal. Once                                                                                                                                                    |

|     | 103                                               | the INTx# signal is asserted, it remains asserted until the                                                                                                                                                     |

|     | 104                                               | device driver clear the pending request. When the request is                                                                                                                                                    |

|     | 105                                               | cleared, the device deasserts its INTx# signal.                                                                                                                                                                 |

| 1   | 42                                                | PCI Request input, indicates to the PCI arbiter that this agent                                                                                                                                                 |

|     | 43                                                | desires use of the bus.                                                                                                                                                                                         |

| 0   | 40                                                | PCI Grant output, indicates to the agent that access to the                                                                                                                                                     |

|     | 41                                                | bus has been granted.                                                                                                                                                                                           |

| 0   | 7                                                 | PCI Reset output, is used to bring PCI-specific registers,                                                                                                                                                      |

|     |                                                   | sequencers, and signals to a consistent state. Low active.                                                                                                                                                      |

| 0   | 9                                                 | PCI Clock output, provides timing for all transactions on PCI                                                                                                                                                   |

|     |                                                   | and is an input to every PCI device.                                                                                                                                                                            |

| 1   | 78                                                | PCI System Error is for reporting address parity errors, data                                                                                                                                                   |

|     |                                                   | parity errors on the Special Cycle command, or any other                                                                                                                                                        |

|     |                                                   | system error where the result will be catastrophic. The                                                                                                                                                         |

|     |                                                   | assertion of SERR# is synchronous to the clock and meets                                                                                                                                                        |

|     |                                                   | the setup and hold times of all bused signals.                                                                                                                                                                  |

| I/O | 77                                                | PCI Parity Error is only for the reporting of data parity errors                                                                                                                                                |

|     |                                                   | during all PCI transactions except a Special Cycle. The                                                                                                                                                         |

|     |                                                   | PERR# pin is sustained tri-state and must be driven active                                                                                                                                                      |

|     |                                                   | by the agent receiving data two clocks following the data                                                                                                                                                       |

|     |                                                   | when a data parity error is detected. The minimum duration                                                                                                                                                      |

|     |                                                   | of PERR# is one clock for each data phase that a data parity                                                                                                                                                    |

|     |                                                   | error is detected. An agent cannot report a PERR# until it                                                                                                                                                      |

|     |                                                   | has claimed the access by asserting DEVSEL# (for a target)                                                                                                                                                      |

|     |                                                   | and completed a data phase or is the master of the current                                                                                                                                                      |

|     |                                                   | transaction.                                                                                                                                                                                                    |

|     | <br> | I       30         I       199         I       132         I       102         103       104         105       1         42       43         O       40         41       0         O       9         I       78 |

| PDA[31:0]  | I/O | 44-46, 48, 50,<br>53-55, 57, 58,<br>60, 62, 64-67,<br>81-85, 87, 88,<br>90, 92-94, 96,<br>98-101, | PCI tri-state Address/Data bus, Address and Data are<br>multiplexed on the same PCI pins. A bus transaction consists<br>of an address phase followed by one or more data phases.<br>PCI supports both read and write bursts. The address phase<br>is the clock cycle in which FRAME# is asserted. During the<br>address phase PDA[31:0] contain a physical address. During<br>data phases PDA[7:0] contain the least significant byte (Isb)<br>and PDA[31:24] contain the most significant byte (msb).<br>Write data is stable and valid when IRDY# is asserted and<br>read data is stable and valid when TRDY# is asserted. Data<br>is transferred during those clocks where both IRDY# and<br>TRDY# are asserted. |

|------------|-----|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STOP#      | I/O | 76                                                                                                | PCI Stop indicates the current target is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TRDY#      | I/O | 72                                                                                                | PCI Target Ready indicates the selected device ability to complete the current data phase of the transaction. A data phase is completed on any clock both TRDY# and IRDY# are sampled asserted. During a read, TRDY# indicates that valid data is present on PDA[31:0]. During a write, it indicates the target is prepared to accept data. Wait cycles are inserted until both IRDY# and TRDY# are asserted together.                                                                                                                                                                                                                                                                                              |

| DEVSEL#    | I/O | 74                                                                                                | PCI Device Select, when actively driven, indicates the driving device has decoded its address as the target of the current access. As an input, DEVSEL# indicates whether any device on the bus has been selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| C/BE[3:0]# | I/O | 56,68,80,91                                                                                       | PCI Bus Command and Byte Enables are multiplexed on the same PCI pins. During the address phase of a transaction, C/BE[3:0]# define the bus command. During the data phase C/BE[3:0]# are used as Byte Enables. The Byte Enables are valid for the entire data phase and determine which byte lanes carry meaningful data. C/BE[0]# applies to byte 0 (lsb) and C/BE[3]# applies to byte 3 (msb).                                                                                                                                                                                                                                                                                                                   |

| FRAME#     | I/O | 69                                                                                                | PCI Cycle Frame is driven by the current master to indicate<br>the beginning and duration of an access. FRAME# is<br>asserted to indicate a bus transaction is beginning. While<br>FRAME# is asserted, data transfers continue. When FRAM#<br>is deasserted, the transaction is in the final data phase or has<br>completed.                                                                                                                                                                                                                                                                                                                                                                                        |

| IRDY#      | I/O | 70                                                                                                | PCI Initiator Ready indicates the bus master ability to<br>complete the current data phase of the transaction. A data<br>phase is completed on any clock both IRDY# and TRDY# are<br>sampled asserted. During a write, IRDY# indicates that valid<br>data is present on PDA[31:0]. During a read, it indicates the<br>master is prepared to accept data. Wait cycles are inserted<br>until both IRDY# and TRDY# are asserted together.                                                                                                                                                                                                                                                                              |

| PPAR          | I/O | 79      | PCI Parity is even parity across PDA[31:0] and C/BE[3:0]#.                                                               |

|---------------|-----|---------|--------------------------------------------------------------------------------------------------------------------------|

| FFAN          | 1/0 | 79      | PPAR is stable and valid one clock after the address phase.<br>For data phases, PPAR is stable and valid one clock after |

|               |     |         | either IRDY# is asserted on a write transaction or TRDY# is                                                              |

|               |     |         | asserted on a read transaction. (PPAR has the same timing                                                                |

|               |     |         | as PDA[31:0], but it is delayed by one clock.) The mater                                                                 |

|               |     |         | drives PPAR for address and write data phases; the target                                                                |

|               |     |         | drives PPAR for read data phase.                                                                                         |

| DMA Interface |     |         |                                                                                                                          |

| DREQ0         | 1   | 127     | DMA Request signals request an external transfer on DMA                                                                  |

| DREQ1         |     | 128     | channel 0 (DREQ0) or DMA channel 1 (DREQ1).                                                                              |

| DACK0         | 0   | 134     | DMA Acknowledge signals acknowledge an external transfer                                                                 |

| DACK1         |     | 135     | on DMA channel 0 (DREQ0) or DMA channel 1 (DREQ1).                                                                       |

| DMARDY        | 1   | 106     | DMA Device Ready signal is used to extend the length of                                                                  |

|               |     |         | DMA bus cycles. If a device wants to extend the DMA bus                                                                  |

|               |     |         | cycles, it will force the DMARDY signal low when it decodes                                                              |

| 000           |     | 100     | its address and receives a IOR or IOW command.                                                                           |

| CS0           | 0   | 129     | DMA Chip Select signals select the corresponding I/O                                                                     |

| CS1           |     | 130     | devices for programming or DMA transfers.                                                                                |

| IOR           | 0   | 108     | DMA I/O read signal is used to indicate to the I/O device that                                                           |

|               |     | 107     | the present bus cycle is an I/O read cycle.                                                                              |

| IOW           | 0   | 107     | DMA I/O write signal is used to indicate to the I/O device that                                                          |

| TC0           | 0   | 109     | the present bus cycle is an I/O write cycle.<br>Terminal count for DMA channels, the pin is driven active for            |

| TC1           | 0   | 111     | one clock when byte count reaches zero and after the last                                                                |

| 101           |     |         | transfer for a DAM has completed.                                                                                        |

| DD[0:7]       | I/O | 126-119 | 8-bit DMA I/O Data bus, bit 0 is the most significant bit.                                                               |

| ECP Interface | 1/0 | 120 110 | For more detail description of the ECP interface signals,                                                                |

|               |     |         | please refer to the IEEE P1284 Standard                                                                                  |

| Busy          |     | 151     | ECP busy input signal                                                                                                    |

| nFault        | 1   | 153     | ECP fault input                                                                                                          |

| nAck          | 1   | 154     | ECP acknowledge input                                                                                                    |

| PError        | 1   | 155     | ECP parity error                                                                                                         |

| Select        | 1   | 156     | ECP Select                                                                                                               |

| nSelectIn     | 0   | 145     | ECP select output                                                                                                        |

| nInit         | 0   | 147     | ECP initialization                                                                                                       |

| nAutoFd       | 0   | 148     | ECP Autofeed                                                                                                             |

| nStrobe       | 0   | 150     | ECP Strobe                                                                                                               |

| ED[0:7]       | I/O | 144-137 | Bi-directional ECP Data bus, ED[0] is the most significant bit                                                           |

|               |     |         | (msb).                                                                                                                   |

| Memory Contr  |     |         |                                                                                                                          |

| RAS#[0:1]     | 0   | 11, 13  | DRAM Row Address Strobe, Banks 0-1. These signals are                                                                    |

|               |     |         | used to select the DRAM row address. A High-to-Low                                                                       |

|               |     |         | transition on one of these signals causes a DRAM in the                                                                  |

|               |     |         | corresponding bank to latch the row address and begin an                                                                 |

|               |     |         | access.                                                                                                                  |

The above information is the exclusive intellectual property of Winbond Electroncs Corp. and shall not be dsiclosed or distributed or reproduced without permission from Winbond.

Version 0.84

| RAS#[2:3]/            | I/O        | 14, 15         | If MD[20] is pull down, these pins serve RAS signals for                                                       |

|-----------------------|------------|----------------|----------------------------------------------------------------------------------------------------------------|

| PREQ#[2:3]            |            |                | external DRAM's bank 2 and 3.                                                                                  |

|                       |            |                | If MD[20] is pull high, these pins serve as "PCI Request 2                                                     |

|                       |            |                | and 3" indicate to the PCI arbiter that the masters desires                                                    |

| CAS#[0:3]             | 0          | 197, 201-203   | use of the bus                                                                                                 |

| CA3#[0.3]             | 0          | 197, 201-203   | DRAM Column Address Strobes, Byte 0-3. These signals are used to select the DRAM column address. A High-to-Low |

|                       |            |                | transition on these signals causes the DRAM selected by                                                        |

|                       |            |                | RAS#[0:3] to latch the column address and complete the                                                         |

|                       |            |                | access.                                                                                                        |

| WE#                   | 0          | 204            | DRAM Write Enable signal is used to write the selected                                                         |

|                       |            |                | DRAM bank.                                                                                                     |

| RCS#[0:1]             | 0          | 16, 17         | ROM Chip Selects, Banks 0-1. A low level on one of these                                                       |

|                       |            |                | signals selects the memory devices in the corresponding                                                        |

|                       |            |                | ROM bank.                                                                                                      |

| RCS#[2:3]/            | 0          | 18, 19         | If MD[20] is pull down, these pins serve ROM "Chip select"                                                     |

| GNT#[2:3]             |            |                | for                                                                                                            |

|                       |            |                | bank 2 and 3.<br>If MD[20] is pull high, these pins serve as "PCI Grant 2 and                                  |

|                       |            |                | 3" indicate to the PCI masters that access to the PCI bus has                                                  |

|                       |            |                | been granted.                                                                                                  |

| ROMEN                 | 0          | 22             | ROM Address Latch, ROM address are divided into two                                                            |

|                       |            |                | portions, higher address bits and lower address bits, the                                                      |

|                       |            |                | address will be put out on the MA bus in two consecutive                                                       |

|                       |            |                | cycles. The ROMEN signal is used to latch the higher                                                           |

|                       |            |                | address bits in the first ROM address cycle.                                                                   |

| ROMRW#                | 0          | 38             | FLASH ROM write enable. This signal is used to write data                                                      |

| D01405#               |            |                | into the mrmory in a ROM bank (such as Flash ROM).                                                             |

| ROMOE#                | 0          | 39             | ROM output enable. This signal enables the selected ROM Bank to drive the MD bus.                              |

| MA[0:11]/             | 0          | 20-21, 23-25,  | Memory controller Memory Address bus. For DRAM access,                                                         |

| DA[0:11]              |            | 27-28, 32, 34- | MA[0:11] is the DRAM row address and the DRAM column                                                           |

|                       |            | 37             | address. For ROM/FLASH ROM access, MA[0:11] is the                                                             |

|                       |            |                | higher portion ROM space address bits in the first ROM                                                         |

|                       |            |                | address cycle, and the lower portion ROM space address bits                                                    |

|                       |            |                | after the first ROM address cycle. During DMA I/O cycles,                                                      |

|                       |            |                | these pins also serve as DMA address bus. MA[0] is the                                                         |

| MD[0:7]               | I/O        | 157-164        | most significant bit (msb).<br>Memory controller Data bus bit 0-7 for both DRAM data and                       |

|                       | "0         |                | ROM space data. Bit 0 is the most significant bit (msb).                                                       |

| MD[8:15]/             | I/O        | 166, 168,      | Memory controller Data bus bit 8-15for both DRAM data and                                                      |

| DD[8:15]              |            | 170-175        | ROM space data. During DMA cycles, these pins also serve                                                       |

|                       |            |                | as DMA data bus bit 8-15 for 16-bit DMA transfering. Bit 8 is                                                  |

|                       |            |                | the most significant bit (msb).                                                                                |

| MD[16:31]             | I/O        | 176-179,       | Memory controller Data bus bit 16-31 for both DRAM data                                                        |

|                       |            | 181,182,184-   | and ROM space data. Bit 16 is the most significant bit (msb).                                                  |

| COM1 Carial D         | out Ciana- | 191,193,195    |                                                                                                                |

| COM1 Serial P<br>SIN1 | Urt Signal |                | COM1 corial data input from the communication link (modern                                                     |

| SINT                  |            | 1              | COM1 serial data input from the communication link (modem or peripheral device).                               |

|                       |            |                |                                                                                                                |

10

The above information is the exclusive intellectual property of Winbond Electroncs Corp. and shall not be dsiclosed or distributed or reproduced without permission from Winbond.

Version 0.84

| SOUT1        | 0           | 2                           | COM1 serial data output to the communication link (modem                         |  |

|--------------|-------------|-----------------------------|----------------------------------------------------------------------------------|--|

| 00011        | Ũ           | -                           | or peripheral device).                                                           |  |

| CTS1n        | 1           | 208                         | COM1 clear to send signal                                                        |  |

| DSR1n        | 1           | 207                         | COM1 data set ready                                                              |  |

| DTR1n        | 0           | 3                           | COM1 data terminal ready                                                         |  |

| RTS1n        | 0           | 4                           | COM1 request to send                                                             |  |

| DCD1n        | 1           | 205                         | COM1 data carrier detect                                                         |  |

| RIN1n        | 1           | 206                         | COM1 ring indicator                                                              |  |

| COM2 Serial  | Port Signal |                             |                                                                                  |  |

| SIN2         | 1           | 6                           | COM2 serial data input from the communication link (modem or peripheral device). |  |

| SOUT2        | 0           | 5                           | COM2 serial data output to the communication link (modem or peripheral device).  |  |

| Synchronous  | Serial Por  | t Signal                    |                                                                                  |  |

| SDI          | 1           | 113                         | Serial data-in from a external codec device                                      |  |

| SDO          | 0           | 118                         | Serial data-out to a exteral codec device                                        |  |

| SYNC         | 1/0         | 116                         | Frame sync of SDI/SDO. This signal is an input signal during                     |  |

|              |             | -                           | "slave mode" or output signal during "master mode"                               |  |

| SCLK         | I/O         | 114                         | Serial Clock for SDI/SDO transfering. This signal is an input                    |  |

|              |             |                             | signal during "slave mode" or output signal during "master                       |  |

|              |             |                             | mode"                                                                            |  |

| Miscellaneou | s           |                             |                                                                                  |  |

| WAKEUP       | 1           | 51                          | If MD[24] is pull down, this pin serves as an external interrupt                 |  |

| /INTR0       |             |                             | request. A active high-state in this pin will make EIER[12] be                   |  |

|              |             |                             | set. In this mode, this pin can also serve as an interrupt                       |  |

|              |             |                             | request pin for an IDE slot.                                                     |  |

|              |             |                             | If MD[24] is pull high, this pin serves a "resume" request to                    |  |

|              |             |                             | wake up the chip from "DOZE" mode.                                               |  |

| RESUME       |             | 52                          | If MD[24] is pull down, this pin serves as an external interrupt                 |  |

| /INTR1       |             |                             | request. A active high-state in this pin will make EIER[13] be                   |  |

|              |             |                             | set. In this mode, this pin can also serve as an interrupt                       |  |

|              |             |                             | request pin for an IDE slot.                                                     |  |

|              |             |                             | If MD[24] is pull high, this pin serves a "resume" request to                    |  |

| Power/Groun  | d nin       |                             | wake up the chip from "SLEEP" mode.                                              |  |

|              |             | 12 110                      | 5.0 // //dd (for a mixed $5.0$ //2.2)/ any interment)                            |  |

| VDD5V        |             | 12,110                      | 5.0V Vdd (for a mixed 5.0V/3.3V enviornment)                                     |  |

| VDDp         |             | 8,31,49,61,73               | Global 3.3V Vdd                                                                  |  |

|              |             | ,89,112,133,                |                                                                                  |  |

| VDDi         |             | 152,169,192<br>26,75,136,18 | 3.3V Vdd (for internal logic only)                                               |  |

|              |             | 26,75,136,18                |                                                                                  |  |

| VDDI         |             | 198                         | 3.3V Vdd (for internal PLL logic)                                                |  |

| VSSI         |             | 200                         | VSS (for internal PLL logic)                                                     |  |

| VSSi         |             | 33,63,95,117,               | VSS (for internal logic)                                                         |  |

|              |             | 146,165,196,                |                                                                                  |  |

| VSSp         | 1           | 10,29,47,59,                | Global VSS                                                                       |  |

| voop         |             | 71,86,97,115,               |                                                                                  |  |

|              |             | 131,149,167,                |                                                                                  |  |

|              |             | 180,194                     |                                                                                  |  |

|              |             | 100,194                     |                                                                                  |  |

11

# W90220F

# 4 CPU CORE

# 4.1 OVERVIEW

(Left for Blank)

### 4.2 BLOCK DIAGRAM

(Left for Blank)

### 4.3 FEATURES

- Base on PA-RISC 1.1 level-0 architecture

- 32-bit integer instruction set and register files

- Maximum 150Mhz operation frequency

- 3.3V and 0.01W/Mhz at full speed operation

- On-chip power management

- Build-in software-independent `dynamic power-down mode`

- Programable `stand-by ` and `sleep ` mode

- Specific instruction to assist power-down control and ICE function

- High-speed 32-bit integer pipeline design

- 6 stages for Load/Store instructions

- 5 stages for other instructions

- On-chip cache memory

- 4KB, direct-map instruction cache and 4KB, 4-way set-associative data cache

- Write-through and write-back support for data cache

- 1 level read buffer and wrap-arround support in each cache

- I level write buffer and hit-under-miss support in data cache

- Cache-locking support in instruction cache

- Dynamic branch prediction

12

Version 0.84

Version 0.84

- Build-in 1-level 256 entry, 4-way set-associative (LRU) Branch-Target-Buffer to improve branch prediction rate and accelerate pipeline throughput

- Two high speed (12ns) 16-bit MACs (or one 32-bit MAC) and multimedia extended instructions have been built-in for DSP releated calculation

- Specific serial-ICE-interface to facilitate chip debuging and software development

# 4.4 PA-RISC ARCHITECTURE

# 4.4.1 CPU RESOURCES

(Left for Blank)

# 4.4.2 ADDRESSING MODES & MEMORY MAP

(Left for Blank)

### 4.4.3 BRANCH CONTROL

(Left for Blank)

### 4.4.4 INTERRUPT CONTROL

(Left for Blank)

### 4.5 **PIPELINE OPERATION**

(Left for Blank)

### 4.6 IMPLEMENTATION DEPENDENT FEATURES

### 4.6.1 MULTIMEDIA ENTENSION INSTRUCTION SET

(Left for Blank)

# 4.6.2 MAC UNIT AND RELEATED INSTRUCTION SET

(Left for Blank)

13

# 4.6.3 DIAGNOSTIC INSTRUCTION SET

(Left for Blank)

# 4.6.4 FLUSH INSTRUCTION/DATA CACHE & BTB

(Left for Blank)

# 4.6.5 LEVEL-0 DEBUG SFU

(Left for Blank)

### 4.7 POWER MANAGEMENT UNIT

(Left for Blank)

# 4.8 SP-ICE INTERFACE

(Left for Blank)

# W90220F

Version 0.84

# 5 MEGACELLS

# 5.1 FUNCTIONAL DESCRIPTIONS

# 5.1.1 MEMORY CONTROLLER

**Overview :**

(Left for Blank)

**Block Diagram :**

(Left for Blank)

### Features :

- supports up to 4 banks of FPM- (fast page mode) or EDO-DRAM (SIMM)

- supports up to 4 banks of ROM or Flash memory

- optional parity bits for each data bytes

- CAS#-befor-RAS# refresh cycles for DRAM module

- programmable RAS#/CAS# timing for DRAM access

- programmable wait states for ROM and Flash memory access

#### **Related Pins :**

(Left for Blank)

**Operation Modes :**

(Left for Blank)

# 5.1.2 DMA CONTROLLER

### **Overview :**

(Left for Blank)

### **Block Diagram :**

(Left for Blank)

#### Features :

- provides two channels for external devices to do 8-bit dma io-to-memory transfer

- flexible block-transfer mode and demand mode are supported

- provides two 16-bit IDE IO-channels connecting IDE devices

- provides 8-bit io-to-memory or memory-to-io transfer mode

- provides 8-, 16- and 32-bit memory-to-memory transfer modes

15

- dma transfer between pci memory to/from system memory are also support

- 4 words (16 bytes) memory burst-access; linear burst order

- build-in 4-words data FIFO to accelerate memory access

- the starting address of source and target shall be halfword boundary for 16-bit memory transfer and word boundary for 32-bit memory transfer

#### **Related Pins :**

There are 19 pins allocated for two external dma slots to do 8-bit io-to-memory dma transfer. These pins include 8-bit bi-directional data bus as well as 11control/status pins.

#### - DREQ0, DREQ1 (input) :

Set high by external dma devices of slot 0 and slot 1 respectively to request dma 8-bit io-to-memory transfer. The DREQ(s) shall keep asserted (logic 1) during "demand mode" transfering, while during "block mode" transfering the DREQ(s) shall be deasserted (logic 0) after their corresponding DACK(s) is granted and before the end of dma block transfering.

#### - DACK0, DACK1 (output) :

Set high by the dma controller to acknowledge the dma DREQ(s) from dma slot 0 and slot1 respectively. Whenever DACK(s) is set high, the dma transfer is on-going.

- TC0, TC1 (output) :

At the end of the last byte of dma transfer, the TC(s) will be pulse high for 1 system clock immediately indicating that dma transfer is finished.

- DMARDY (input) :

This signal is used by external dma devices to insert wait states when the devices being programming by cpu. DMARDY is an open collector signal which shall be pull-up externally (default "don't insert any wait states"). If any devices need to lengthen the IOR or IOW cycle, it must drive DMARDY to logic high within one system clock after IOR or IOW signal being set high.

- IOR (output) :

This signal is pulsed high indicating an IO read command cycle is on-going whether in cpu mode (DACK(s) = 0s) or in dma mode (DACK(s) = 1).

- IOW (output) :

This signal is pulsed high indicating an IO write command cycle is on-going whether in cpu mode (DACK(s) = 0s) or in dma mode (DACK(s) = 1).

- CS0, CS1 (output) :

These two signals are Chip Selects of dma slot 0 and slot 1. As dma controller wants to programming dma devices, it must drive the corresponding CS(s) to logic high.

- DD[0:7] (in/out) :

Birdirectional 8-bit data bus with bit 0 is the most significant bit.

#### **Operation Modes :**

(Left for Blank)

16

The above information is the exclusive intellectual property of Winbond Electroncs Corp. and shall not be disclosed or distributed or reproduced without permission from Winbond.

# 5.1.3 PCI BRIDGE

#### **Overview :**

(Left for Blank)

#### **Block Diagram :**

(Left for Blank)

#### Features :

- supports "long framing" and "short framing" (synchronous, frame-based protocol)

- provides "master mode" and "slave mode"

- build-in two 48x16 (or 24x32) data fifo to accelerate transmit/receive operation

- programable data bits per one frame (sampling rate) : 1 ~ 256 bits/frame

- programable data bits per word (resolution of each sampling) : 1 ~ 32 bits/word

- programable multi-word (per frame) transfer : 1 ~ 16 words/frame

### **Related Pins :**

(Left for Blank)

**Operation Modes :**

(Left for Blank)

# 5.1.4 PARALLEL PORT INTERFACE

#### **Overview :**

(Left for Blank)

### **Block Diagram :**

(Left for Blank)

### Features :

- supports all IEEE P1284 transfer modes including :

- Compatible (centronic) mode (forward channel)

- Nibble mode (reverse channel, compatible with all existing PC hosts relies on software control)

- Byte mode (reverse channel, compatible with IBM PS/2 host)

- EPP mode (bi-directional half-duplex channel relies on software control)

- ECP mode (fast bi-directional half-duplex channel)

- Host-side design

- Provide a special operation mode to emulate peripheral-side centronic device

- Build-in one 16bytes FIFO to accelerate ECP mode and centronic forward transfer

- Provide DMA capability to accelerate moving data from parallel port interface to system memory

- ECP mode is also including :

- High performance half-duplex forward and reverse channel

17

Version 0.84

- Interlocked handshake, for fast reliable transfer

- Forward "channel-addressing/command transfer" for low-cost peripherals

- Support reverse RLE decompression

- Peer-to-peer capability

### **Related Pins :**

17 pins are allocated for Parallel-Port-Interface including 8-bit data bus, 5 status input signals and 4 control output signals.

| - <u>nStrobe</u> (output) :<br>Compatible Mode<br>ECP Mode             | <ul> <li>Set active low to transfer data into peripheral device's input latch</li> <li>Used in a closed-loop handshake with "Busy" to transfer data or address information from host to peripheral device.</li> </ul>                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - <u>nAutoFd</u> (output)<br>Compatible Mode<br>ECP Mode               | <ul> <li>: Set low by host to put some printers into auto-line feed mode. May also be used as a ninth data, parity, or command/data control bit.</li> <li>: The host drives this signal for flow control in the reverse direction. It is used in an interlocked handshake with "nAck". "nAutoFd" also provides a ninth data bit used to determine whether command or data information is present on the data signals in the forward transfering.</li> </ul> |

| - <u>nInit</u> (output) :<br>Compatible Mode<br>ECP Mode               | <ul> <li>Pulsed low in conjunction with "nSelectIn" active low to reset the interface and force a return to compatible mode idle state.</li> <li>This signal is driven low to place the channel in the reverse direction. While in this mode, the peripheral is only allowed to drive the bi-directional data signals when "nInit" is low and "nSelectIn" is high.</li> </ul>                                                                               |

| - <u>nSelectIn</u> (output)<br>Compatible Mode<br>ECP Mode             | <ul> <li>: Set low by host to select peripheral device.</li> <li>: Driven high by host while in ECP mode. Set low by host to terminate ECP mode and return the link to the compatible mode.</li> </ul>                                                                                                                                                                                                                                                      |

| - <u>nAck</u> (input) :<br>Compatible Mode<br>ECP Mode<br>transfering. | : Pulse low by the peripheral device to acknowledge transfer of a data byte from the host.<br>: Used in a close-loop handshake with "nAufoFd" to transfer data during reverse                                                                                                                                                                                                                                                                               |

| - Busy (input) :<br>Compatible Mode<br>ECP Mode                        | <ul> <li>Driven high to indicate that the peripheral device is not ready to receive data.</li> <li>The peripheral device uses this signal for flow control in the forward transfering. "Busy" also provides a ninth data bit used to determine whether command or data information is present on the data signals in the reverse direction.</li> </ul>                                                                                                      |

| - <u>PError</u> (input) :<br>Compatible Mode<br>path<br>ECP Mode       | <ul> <li>: Driven high to indicate that the peripheral device has encountered an error in its paper<br/>(ex. paper empty). Peripherals shall set "nFault" low whenever they set "PError" high.</li> <li>: Peripherals drive this signal low to acknowledge "nInit". The host relies upon "PError" to<br/>deterine when it is permitted to drive the data signals.</li> </ul>                                                                                |

Version 0.84

| - <u>Select</u> (input) :<br>Compatible Mode<br>ECP Mode | <ul><li>Set high to indicate that the peripheral device is on-line.</li><li>Used by peripheral to reply to the requested extensibility byte sent by the host during the negotiation phase.</li></ul>                                                                                                                                                                                                       |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - <u>nFault</u> (input) :<br>Compatible Mode<br>ECP Mode | <ul> <li>Set low by peripheral device to indicate that an error has occured.</li> <li>Set high to acknowledge 1284 compatibility during negotiation phase. During ECP mode the peripheral may drive this pin low to request communications with the host. This signal would be typically used to generate an interrupt to the host. This signal is valid in both forward and reverse trnasfers.</li> </ul> |

| - <u>ED[0:7]</u> (in/out)                                | : 8-bit bus used to hold data, address or command information in all modes. The bit 0 is the most significant bit.                                                                                                                                                                                                                                                                                         |

| Operation Modes :                                        |                                                                                                                                                                                                                                                                                                                                                                                                            |

(Left for Blank)

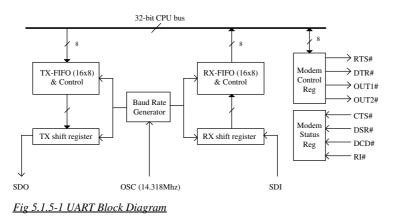

# 5.1.5 UART

#### **Overview :**

The W90220 contains two Universal Asynchronous Receiver/Transmitter (UART) ports, one of them provides complete MODEM-control and serial transfermation capabilities, whereas the other one provides only serial transfermation capability. The UART performs serial-to-parallel conversion on data characters received from a peripheral device such as MODEM, and parallel-to-serial conversion on data characters received from the CPU. One 16 bytes transmitter FIFO (TX-FIFO) and one 16 bytes (plus 3 bits of error data per byte) receiver FIFO (RX-FIFO) have been built in to reduce the number of interrupts presented to the CPU. The CPU can read the complete status of the UART at any time during the functional operation. Status reported includes error conditions (parity, overrun, framing, or break interrupt) and states of TX-FIFO and RX-FIFO.

### **Block Diagram :**

### Features :

- transmitter and receiver are each buffered with 16 bytes FIFO's to reduce the number of interrupts presented to the CPU

- MODEM control functions (CTS, RTS, DSR, DTR, RI and DCD)

- Fully programmable serial-interface characteristics :

- -- 5-, 6-, 7-, or 8-bit characters

- -- even, odd, or no-parity bit generation and detection

- -- 1-, 1&1/2, or 2-stop bit generation

- -- baud rate generation

- line break generation and detection

- false start bit detection

- full prioritize interrupt system controls

- loop back mode for internal diagnostic testing

### **Related Pins :**

### (COM1)

- SIN1 (input) : Serial data input from peripheral device or MODEM

- SOUT1 (output) : Serial data output to peripheral device or MODEM

- CTS1# (input) : Clear to send signal

- DSR1# (output) : Data set ready

- DTR1# (input) : Data terminal ready

- RTS1# (output) : Request to send

- DCD1# (input) : Data carrier detect

- RI1# (output) : Ring indciator

### (COM2)

- SIN2 (input) : Serial data input from peripheral device or MODEM

- SOUT2 (output) : Serial data output to peripheral device or MODEM

### **Operation Modes :**

- Interrupt Mode operation :

- A. Receiver control :

- Set FCR[0:1] to select a proper receiver threshold level and then turn on "receiver data available

### interrupt"

- (Irpt\_RDA) by set IER[7] to logic 1.

- The Irpt\_RDA will be triggered when the receiver FIFO (RX-FIFO) has reached its programmed trigger level, and it will be cleared as the available data in RX-FIFO drops below the trigger level.

- As Irpt\_RDA occured, the corresponding IIR bits will be set to inform the software application that data in RX-FIFO has reached programmed threshold level.

- If the received data has any errors, the "line status interrupt" (Irpt\_RLS) will occur and has higher priority than Irpt\_RDA.

- If "time out interrupt" (Irpt\_TOR) is enable by set IER[7] and TOR[0] to logic 1s. The Irpt\_TOR will occur, if the following conditions exist :

- at least one character is in RX-FIFO.

- RX-FIFO is not received any data or accessed by CPU from the most recent serial character received, and the time period, counting by baud rate bit clock, has exceeded the value being programmed in TOR[1:7].

- The Irpt\_TOR and the time-out counter will be cleared as the CPU reads one character from RX-FIFO.

- The time-out counter is reset after a new character is received or after the CPU reads the RX-FIFO.

Version 0.84

- B. Transmitter control :

- Set IER[6] to logic 1 to enable "transmitter empty interrupt" (Irpt\_THRE) before transmitter operation.

- Once the transmitter FIFO (TX-FIFO) is empty, the Irpt\_THRE is triggered and the corresponding IIR

- bits

- are set to inform the CPU to fill the TX-FIFO (maximum 16 bytes of characters).

- The Irpt\_THRE is reset after the CPU reads the IIR (IIR[4:7] must be 4'b0010 at that time) or writes a character into TX-FIFO.

- Irpt\_RDA and Irpt\_TOUT has the same interrupt priority (2nd priority) while Irpt\_THRE has a lower priority (3rd priority).

- Polled Mode operation : (refer to "LSR" register discriptions located on Section 5.2.5)

- No interrupts need be enabled at this mode, the CPU always polls the LSR to check COM port status before taking any actions.

- LSR[7] will be set as long as there is at least one byte in the RX-FIFO, and it is cleared if the RX-FIFO is empty.

- LSR[3:6] will specify error(s) status which is handled the same way as in the interrupt mode operation, the IIR[4:7] is not affected since no interrupt is enabled.

- LSR[2] will indicate when the TX-FIFO is empty.

- LSR[1] will indicate that both TX-FIFO and shift register are empty.

- LSR[0] will indicate whether there are any errors in the RX-FIFO.

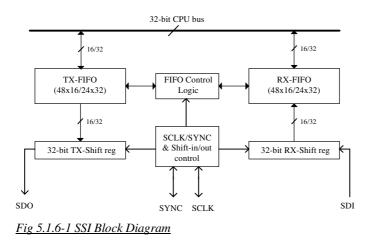

# 5.1.6 SYNCHRONOUS SERIAL INTERFACE (SSI)

### **Overview :**

The SSI module within W90220 contains holding registers, shift registers, and other logic to support a variety of serial data communications protocols and provide a direct connection to external audio/telephony codec devices. Two 48 halfwords fifos, the transmitter fifo and receiver fifo, have been implented to accelerate both transmittion and receiving operations. These two fifos can be configured as 48 halfwords or 24 words depth depending on the data word length.

### **Block Diagram :**

21

Version 0.84

#### Features :

- supports "long framing" and "short framing" (synchronous, frame-based protocol)

- provides "master mode" and "slave mode"

- build-in two 48x16 (or 24x32) data fifo to accelerate transmit/receive operation

- programable data bits per one frame (sampling rate) : 1 ~ 256 bits/frame

- programable data bits per word (resolution of each sampling) : 1 ~ 32 bits/word

- programable multi-word (per frame) transfer : 1 ~ 16 words/frame

#### **Related Pins :**

- SDI (input) : This pin contains the input data shifted from external audio/telephony codec devices

- SDO (output) : This pin contains the output data shifted to external audio/telephony codec devices

- SYNC (in/out) : This pin is the frame synchronization signal between SSI and codec devices. The SYNC may be input or output depending on SSI operated in slave- or master-mode respectively.

- SCLK (in/out) : This pin is the serial bit clock between SSI and codec devices. Likewise, The SCLK may be input or output depending on SSI operated in slave- or master-mode respectively.

#### **Operation Modes :**

- Master Mode : Once CFGH[2] is set to logic 1 and MD[25] is pull high, SSI is operated in master mode, and the SYNC (determines the sampling rate) and SCLK is drived by SSI module to external codec devices.

| SCLK frequence | e = EXTCLK/[2*(CFGL[8:15] + 1)] | (5.1.6a) |

|----------------|---------------------------------|----------|

| SYNC period    | = SCLK * (CFGL[0:7] + 1)        | (5.1.6b) |

- Slave Mode : Once CFGH[2] is set to logic 0 and MD[25] is pull down, SSI is operated in slave mode, the SCLK and SYNC are drived externally (may be from codec devices). So the sampling rate and SCLK frequence are determined by external devices, however software driver still need to properly set "serial data bit length" (CFGH[8:10]) as well as "data words per frame" (CFGH[12:15]) to make SSI module working correctly.

- Loop mode : This mode (CFGH[1] =1) aims at selftesting. When this bit is set, serial data-out "SDO" is connected to serial data-in "SDI" internally and SDO pin fixed at logic 0 state. Besides, if Loop and Master mode are chose concurrently, SSI module will not issue SYNC until TX-FIFO contains at least one data word.

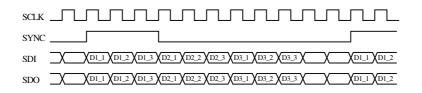

included in long framing mode :

consists of the following features.

- The SSI module always samples receive date (SDI) on the falling edge of SCLK, whereas always pushes transmit data (SDO) on the rising edge of SCLK.

- The frame sync (SYNC) is asserted immediately as the first bit of transmit and receive data.

- The frame sync (SYNC) is asserted for one "serial word length" which determined by

- CFGH[8:11].

22

#### Serial word length = CFGH[8:11] + 1 (5.1.6c)

- The frame sync rate (sampling rate) and SCLK frequence follow eq (5.1.6b) and (5.1.6a) respectively on master mode and determined by external devices on slave mode.

- The transmit FIFO and receive FIFO is configued as 48x16 if "serial word length" <= 16, and will be configured as 24x32 if "serial word length" > 16.

Version 0.84

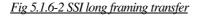

<sup>-</sup> Long Framing : When CFGH[3] is set to logic 1, SSI is operated in long framing mode. The following features are

- The shifting data bits on SDI and SDO are always MSB first.

- If serial word length is not 16 or 32, it is software responsibility to left(MSB) justify the transmit data words before writing it to transmit FIFO, the received data before being written into receive FIFO is righ(LSB) justified automatically by SSI module where the unfilled MSBs are catneted with logic 0s.

- SSI module always shifts out logic 0s on each frame sync if transmit FIFO is empty at that time.

- A receiver FIFO interrupt will be asserted (when RX-FIFO interrupt is enable) if the received data words exceeds the receive FIFO's threshold level. Likewise, a transmitter FIFO interrupt will be asserted (when TX-FIFO interrupt is enable) if the available data words in transmit FIFO is lower than its threshold level.

- Fig 6.1.5-2 shows a standard long framing transfer where serial word length is 3 (CFGH[8:11] = 2), words per frame is 3 (CFGH[12:15]=2) and bits per frame is 9 (CFGL[0:7] = 10).

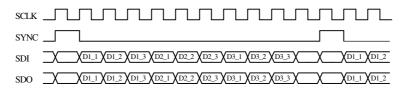

- Short Framing : When CFGH[3] is set to logic 0, SSI is operated in long framing mode. The following features are included in short framing mode

consists of the following features.

- The frame sync (SYNC) is asserted for one SCLK immediately before the first bit of transmit and receive data.

- The frame sync (SYNC) is asserted for one SCLK period.

- All other features are the same as long framing mode.

- Fig 6.1.5-3 shows a standard short framing transfer where serial word length is 3 (CFGH[8:11] =

- 2), words per frame is 3 (CFGH[12:15]=2) and bits per frame is 9 (CFGL[0:7] = 10).

### 5.1.7 TIMER CHANNELS

#### **Overview :**

(Left for Blank)

#### 23

Version 0.84

# W90220F

### **Block Diagram :**

(Left for Blank)

#### Features :

- Two 24-bit decremental timer channels with individual interrupt requests

- Programmable timer clocks for each channels, the clock range is OSC ~ OSC/8'hFF

- maximum uninterrupted time or timeout = 5 minutes (if OSC = 14.318Mhz)

- Typical OSC frequence is 14.318Mhz.

Related Pins : (None)

**Operation Modes :** (Left for Blank)

# 5.2 REGISTER DEFINITIONS

# 5.2.1 MEMORY CONTROLLER REGISTERS

There are 24 8-bit registers included in the memory (ROM/DRAM) controller. Access to these registers are through a 8-bit "index" port and a 8-bit data port. The index port address is 0xf0000022 and the data port address is 0xf0000023. The memory controller supports **ROM**, **Flash**, **EDO**- and **Fast-page-mode** DRAM.

| Table <b>5.2.1-1 :</b> | MEMC Register | Мар    | (IO base (BA) : 0xf000000          |

|------------------------|---------------|--------|------------------------------------|

| Index                  | Symbol        | Access | Description                        |

| 0x00                   |               | R/W    | ROM bank 0 base register [0:7]     |

| 0x01                   |               | R/W    | ROM bank 0 base register [8:15]    |

| 0x02                   |               | R/W    | ROM bank 1 base register [0:7]     |

| 0x03                   |               | R/W    | ROM bank 1 base register [8:15]    |

| 0x04                   |               | R/W    | ROM bank 2 base register [0:7]     |

| 0x05                   |               | R/W    | ROM bank 2 base register [8:15]    |

| 0x06                   |               | R/W    | ROM bank 3 base register [0:7]     |

| 0x07                   |               | R/W    | ROM bank 3 base register [8:15]    |

| 0x08                   | ROMconf0      | R/W    | ROM Configuration register 0 [0:7] |

| 0x09                   | ROMconf1      | R/W    | ROM Configuration register 1 [0:7] |

| 0x0a                   | ROMconf2      | R/W    | ROM Configuration register 2 [0:7] |

| 0x0b                   | ROMconf3      | R/W    | ROM Configuration register 3 [0:7] |

| 0x20                   |               | R/W    | RAM bank 0 base register [0:7]     |

| 0x21                   |               | R/W    | RAM bank 0 base register [8:15]    |

| 0x22                   |               | R/W    | RAM bank 1 base register [0:7]     |

| 0x23                   |               | R/W    | RAM bank 1 base register [8:15]    |

| 0x24                   |               | R/W    | RAM bank 2 base register [0:7]     |

| 0x25                   |               | R/W    | RAM bank 2 base register [8:15]    |

| 0x26                   |               | R/W    | RAM bank 3 base register [0:7]     |

| 0x27                   |               | R/W    | RAM bank 3 base register [8:15]    |

| 0x28                   | RAMconf0      | R/W    | RAM Configuration register 0 [0:7] |

| 0x29                   | RAMconf1      | R/W    | RAM Configuration register 1 [0:7] |

| 0x2a                   | RAMconf2      | R/W    | RAM Configuration register 2 [0:7] |

| 0x2b                   | RAMconf3      | R/W    | RAM Configuration register 3 [0:7] |

25

Version 0.84

| ROM Base Address Register ( )                              |   |   |             |   |           |           |   |

|------------------------------------------------------------|---|---|-------------|---|-----------|-----------|---|

| Index : 0x00,0x02,0x04, 0x06 Read/Write Power-on Default : |   |   |             |   |           | Default : |   |

| 0                                                          | 1 | 2 | 2 3 4 5 6 7 |   |           |           | 7 |

| ROM base address bit 0-7 (most significant bits)           |   |   |             |   |           |           |   |

| Index : 0x01,0x03,0x05,0x07 Read/Write Power-on Default :  |   |   |             |   | Default : |           |   |

| 0                                                          | 1 | 2 | 3           | 4 | 5         | 6         | 7 |

| ROM base address bit 8-15                                  |   |   |             |   |           |           |   |

These eight 8-bit registers (boundle to four 16-bit registers) defines the **most significant 16 bits** of each ROM banks' base (bottom) address. The "ROM base address" togather with the "ROM size" (defined in ROMconf0) construct the whole address range of each ROM banks.

These ROM base registers do not contain any initial value after system power-on. All ROM access will be directed to **bank 0** right after system power-on (for ROMconf3[3]=1 at that time). System programmer shall not set **ROMconf3[3]** to logic 0 before all ROM base and configuration registers have been filled with valid data.

#### ROM Configuration\_0 Register (ROMconf0)

Index : 0x08

Read/Write

Power-on Default: 0x0

| 0      | 1               | 2 | 3 | 4      | 5  | 6          | 7    |

|--------|-----------------|---|---|--------|----|------------|------|

| ROMen0 | ROM bank_0 size |   |   | ROMen1 | RC | M bank_1 s | size |

Bit 0 Enable ROM bank 0

0 = Disable

1 = Enable

Bits 1-3 Size of ROM bank 0

Version 0.84

The above information is the exclusive intellectual property of Winbond Electroncs Corp. and shall not be dsiclosed or distributed or reproduced without permission from Winbond.

26

| ROMconf0[1:3] | ROM size (*Basic unit) |

|---------------|------------------------|

| 0 0 0         | 64K                    |

| 0 0 1         | 128K                   |

| 0 1 0         | 256K                   |

| 0 1 1         | 512K                   |

| 1 0 0         | 1 <b>M</b>             |

| 1 0 1         | 2M                     |

| 1 1 0         | 4M                     |

| 1 1 1         | 16M                    |

("\*Basic unit" may be "byte", "halfword" or "word" which is defined in ROMconf2[0:7])

#### Bit 4 Enable ROM bank 1

0 = Disable

1 = Enable

#### Bits 5-7 Size of ROM bank 1

(The definition is the same as ROMconf0[1:3])

#### ROM Configuration\_1 Register (ROMconf1)

| Index | : | 0x09 |

|-------|---|------|

|       |   |      |

Read/Write

Power-on Default: 0x0

| 0      | 1  | 2               | 3 | 4 | 5  | 6          | 7    |

|--------|----|-----------------|---|---|----|------------|------|

| ROMen2 | RC | ROM bank_2 size |   |   | RC | M bank_3 s | size |

Bit 0 Enable ROM bank 2

0 = Disable

1 = Enable

### Bits 1-3 Size of ROM bank 2

(The definition is the same as ROMconf0[1:3])

### Bit 4 Enable ROM bank 3

- 0 = Disable

- 1 = Enable

27

Bits 5-7 Size of ROM bank 3

(The definition is the same as ROMconf0[1:3])

### ROM Configuration\_2 Register (ROMconf2)

Index : 0x0a

Read/write

Power-on Default : \*note

| 0   | 1    | 2   | 3      | 4 | 5   | 6      | 7 |

|-----|------|-----|--------|---|-----|--------|---|

| ROM | I3DW | ROM | ROM2DW |   | 1DW | ROM0DW |   |

#### Bits 0-1 Data Width of ROM bank 3

| ROMconf2[0:1] | Data width |

|---------------|------------|

| 0 0           | Byte       |

| 0 1           | Halfword   |

| 1 0           | Word       |

| 1 1           | (reserved) |

### Bits 2-3 Data Width of ROM bank 2

(The definition is the same as ROMconf2[0:1])

Bits 4-5 Data Width of ROM bank 1

(The definition is the same as ROMconf2[0:1])

### Bits 6-7 Data Width of ROM bank 0

(The definition is the same as ROMconf2[0:1])

\***note** : The default value of this register is determined by **MD[30:31]**. The states of MD[30:31] will be copied into ROMconf2[0:1]/[2:3]/4:5]/[6:7] during system power-on (cold) reset.

#### ROM Configuration\_3 Register (ROMconf3)

| Index | : | 0x0b |

|-------|---|------|

|       |   |      |

Read/write

Power-on Default: 0b'11011xx

| 0                   | 1 | 2       | 3  | 4        | 5 | 6 | 7 |

|---------------------|---|---------|----|----------|---|---|---|

| ROM Read Wait state |   | BK0only | LA | Reserved |   |   |   |

Version 0.84

#### Bits 0-2 Wait states of ROM Read cycle

| ROMconf2[0:2] | Wait States |

|---------------|-------------|

| 0 0 0         | 2           |

| 0 0 1         | 3           |

| 0 1 0         | 4           |

| 0 1 1         | 5           |

| 1 0 0         | 6           |

| 1 0 1         | 7           |

| 1 1 0         | 8           |

| 1 1 1         | 9           |

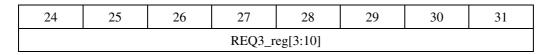

Only ROM read cycles have a programmable wait states, while Flash ROM write cycles are always 9-wait states.