The Programmable Logic Company<sup>SM</sup>

### InsideThisIssue:

### **GENERAL**

| Fawcett: 100,000+ Gates       2         Guest Editorial       3         Customer Success Story       7         New Product Literature       8         Upcoming Events       8         Financial Results       8         What's New at WebLINX?       9         One-Day XACT stepClasss       9         Component Availability Chart       10-11         Alliance Program Chart       12-13         Alliance Contact Chart       13         Development Systems Chart       14         Programming Support Charts       15-17         Impressive Reliability Results       18 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programming Support Charts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### PRODUCTS

| XC8100 Shines in 6502 Test          | 19  |

|-------------------------------------|-----|

| Introducing XC9500 CPLD Family! 20- | -21 |

| XC5200 Family Volume Production 22  | -23 |

| XC3100A-09 World's Fastest FPGA     | 22  |

| More Hi-Rel Versions of XC4000      | 24  |

| 3.3 V Survey Contest Winner         | 24  |

### **DEVELOPMENTSYSTEMS**

| Update on Logic Synthesis    | 25-26   |

|------------------------------|---------|

| XACT step Direct From CD-ROM | . 26-27 |

### HINTS & ISSUES

| Synchronous RAM and Speed          | 31 |

|------------------------------------|----|

| Sensitivity to Power Glitches 3    | 2  |

| Readback in FPGAs 32-3             | 33 |

| XC4000 Well Suited to 3.3 V 3      | 33 |

| Minimizing Power Consumption 3     | 4  |

| User-Defined Schmitt Triggers 3    | 4  |

| Reconfigurable Computing Program 3 | 35 |

| Technical Support Facilities 3     | 35 |

| Applications Update 36-3           | 87 |

| Questions & Answers                | 39 |

| 4Q95 Fax Response Form 4           | 0  |

## GENERALFEATURES

## XCELL On The Web

This journal, as well as a wide range of literature about Xilinx products, job opportunities, training schedules and much more are available on WebLINX, the Xilinx World Wide Web site...

See Page 9

## PRODUCTINFORMATION

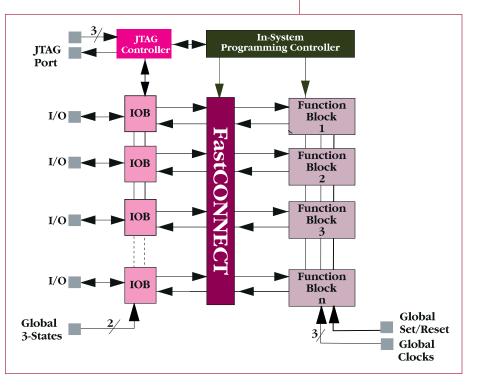

## Family of In-System Programmable CPLDs Introduced

The high-performance XC9500 CPLD family features FastFLASH<sup>™</sup>, offering exceptional ISP capabilities ...

See Page 20

## **Run XACT***step*<sup>™</sup> **Direct From CD!**

Complete instructions on running XACT*step* version 6 alone or in conjunction with Viewlogic's PRO Series...

See Page 26

## **DESIGNTIPS & HINTS**

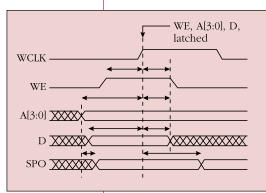

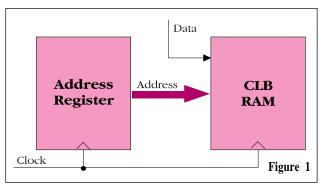

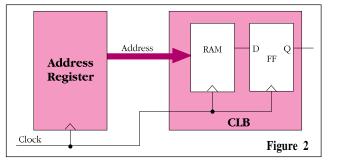

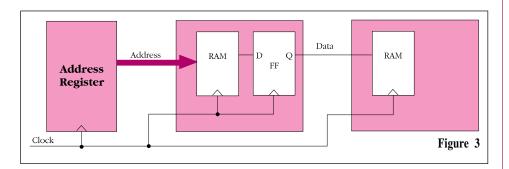

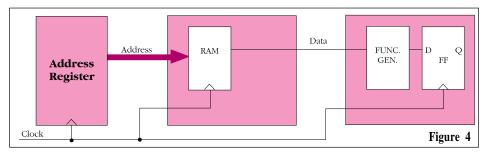

## Synchronous RAM Timing in the XC4000E

Taking advantage of the XC4000E family's synchronous memory mode makes it possible to operate near maximum clock frequency... See Page 30 Address Register

### FROMTHEFAWCETT

•

• • • •

## 100,000 Gates and Beyond

By BRADLY FAWCETT 🔶 Editor

The time is fast approaching when programmable logic devices will exceed 100,000 usable gates of logic and 100 MHz system clock speed. At these performance levels, the device architectures, design tools and development flows that have

been successful for sub-10,000 gate designs will not always suffice. Ignoring for now the issue of how to actually measure "gate capacity," let's examine what will be required of very highdensity programmable logic in the near future. (And I'm sure you won't

be surprised to learn that Xilinx is wellpositioned to meet those requirements.)

As FPGA-based designs get larger and more complex, FPGA architectures and development tools must support a design methodology that mimics high-density ASIC design flows, while delivering the flexibility and time-to-market benefits of FPGA technology. The FPGA device and its development tools must be "synthesisfriendly" — they must easily yield efficient, cost-effective solutions when starting with a high-level description of the design.

Achieving this goal requires attacking the problem from both ends; the architecture must be symmetrical, regular and provide an "easy" target for both synthesis and "place and route" tools. Furthermore, the tools — especially the synthesis compilers — must be tuned to produce the best results for the particular architecture. This, in turn, implies close cooperation between the designers of the FPGA architecture and developers of the synthesis tools. To this end, Xilinx has a Synthesis Syndicate program dedicated to sharing information with third-party CAE developers, as well as an ongoing co-development agreement with Synopsys, the leading supplier of synthesis tools.

### Some Tools Already In Place

As with today's high-density FPGAs, timing-driven tools that take into account the design's performance requirements during placement and routing (such as the XACT-Performance<sup>TM</sup> feature of PPR) are key to meeting performance goals in large, complex designs. Very large FPGA designs also could benefit from something that is not available today timing-driven mapping. Much of the technology mapping (that is, the mapping of the user's logic into the logic blocks and other resources of the FPGA architecture) must occur during synthesis so the synthesis tools can make the appropriate

**GAS FPGA-based** designs get larger and more complex, FPGA architectures and development tools must support a design methodology that mimics high-density ASIC design flows, while delivering the flexibility and time-tomarket benefits of FPGA technology. **9**

area/performance trade-offs. This again implies close cooperation between the chip architects and the synthesis providers. Designs with 100,000-gates are likely to include datapath logic and memory func-*Continued on page 4*

### XCELL

Please direct all inquiries, comments and submissions to:

Editor: Bradly Fawcett

#### Xilinx, Inc.

2100 Logic Drive San Jose, CA 95124 **Phone:** 408-879-5097 **FAX:** 408-879-4676 **E-Mail:** brad.fawcett@xilinx.com

©1995 Xilinx Inc. All rights reserved.

XCELL is published quarterly for customers of Xilinx, Inc. Xilinx, the Xilinx logo and XACT are registered trademarks; all XC-designated products, UIM, HardWire, XACTstep and XACT-Performance are trademarks; and "The Programmable Logic Company" is a service mark of Xilinx, Inc. All other trademarks are the property of their respective owners.

•

### **GUESTEDITORIAL**

## **A Unique Product Strategy**

by CHUCK FOX  $\blacklozenge$  Vice President, Product Marketing

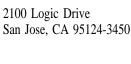

Xilinx is the world's largest supplier of programmable logic — approximately 50 percent larger than the second-largest supplier. We achieved that leading position through a continuing commitment to providing a complete product solution. This encompasses a focus on all three critical areas of the high-density PLD product solution **triangle**: *components, software* and *service*.

### Components

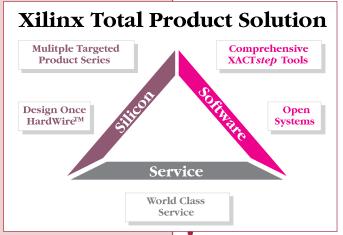

In components, we will continue to leverage new deep submicron process technologies aggressively to deliver improvements in speed, density and cost. We will combine this with innovative, targeted product families in all three major technology segments — CPLDs, reprogrammable FPGAs and one-time programmable FPGAs — supported by the industry's only seamless, no-risk cost-reduction path — the mask-programmed HardWire LCA. Each of these high-growth PLD technologies serves unique requirements in the industry.

Xilinx is the only supplier to deliver leading solutions in all three of these high-growth technologies. Our strategy is to continue to invest heavily in the research and development of innovative solutions in each area. Recently, we have introduced new solutions in all three.

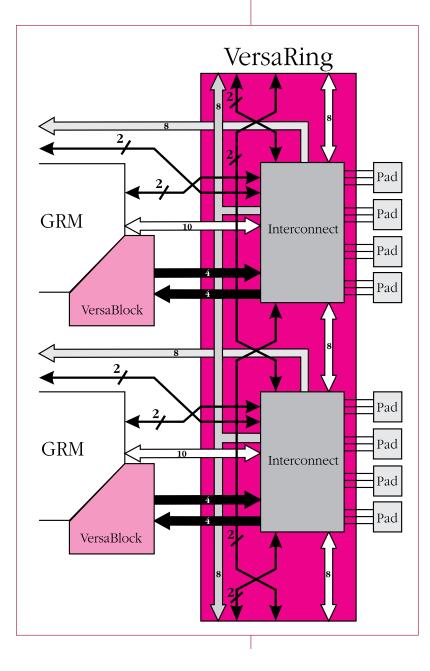

The **XC6200** family of reprogrammable FPGAs provides extremely fast, in-system configuration speeds (as low as 40 ns/cell) and a unique, high-speed dedicated microprocessor interface. These features are ideal for using FPGAs in high-speed "reconfigurable coprocessing" applications.

The **XC8100** series of one-time programmable FPGAs, featuring the industry's first Sea-of-Gates FPGA architecture, is based on a proprietary metal-tometal antifuse technology called MicroVia<sup>TM</sup> that, when combined with a unique, fine-grained cell architecture, delivers a powerful, single-chip FPGA solution optimized for an ASIC-like design flow.

The **XC9500** series of CPLDs is the industry's first 5V FLASH solution, representing the next generation in In-System Programmable (ISP) capability. This CPLD family delivers a superior ISP capability targeted at today's total product life cycle requirements.

### Software

In software, our **open systems** strategy means we provide seamless integration into all the leading EDA environments, supporting popular front-end HDL, schematic, and simulation systems (as opposed to shipping our own proprietary front-end) as well as supporting industry standards such as EDIF, VHDL, Verilog-HDL and ABEL. We combine this with our comprehensive back-end XACT*step*<sup>TM</sup> tools to provide a completely technology-independent design system supporting all our component

Continued on the next page

•

•

•

•

•

•

•

•

•

### THEFAWCETT

Continued from page 2

tions, as well as the traditional "glue logic" found in today's FPGA designs. Automatic placement tools must support the effective placement of these various types of circuit structures, and will need to be augmented by interactive floorplanning tools. XACT*step*<sup>TM</sup> version 6 includes a new version of PPR with improved structured-placement capabilities, as well as the industry's first FPGA floorplanner. The synthesis tools will need links to the automatic placement and floorplanning tools, allowing for the passing of design constraints and the back-annotation of timing information.

With large designs, design iterations and last-minute changes are even more inevitable than they are today. Thus, the implementation tools should be re-entrant and tolerant of change, so minor logic changes do not cause major alterations in the physical layout. Xilinx pioneered reentrant FPGA implementation tools with the Guide option in PPR.

Accurate **simulation** should be available at any point in the design cycle using a common set of simulation vectors. This means that the post-place-and-route timing results need to be back-annotated into the original netlist created by the synthesis program, as opposed to creating a new netlist based on the structure of the FPGA. Once again, this implies a "synthesisfriendly" FPGA architecture, a synthesis compiler capable of efficient technology mapping to that architecture, and a strong link between the synthesis compiler and the "place and route" tools.

Design errors are reduced and design cycles are compressed when users don't need to re-invent common functions. Many leading ASIC providers give users large, pre-defined macro functions, sometimes called cores or megacells. As FPGA densities increase, users should expect similar **large macro functions** to be

#### GUESTEDITORIAL

Continued from the previous page

families. Xilinx is committed to providing the best programmable logic design system in the industry with an integrated solution capable of meeting all of your PLD design requirements.

This quarter, we began shipping a major new version of our leading development

software. **XACT***step* version 6 delivers six new, Windows<sup>®</sup>based productivity tools, providing easy-to-use yet powerful design capability. All Xilinx users under warranty are now receiving their updates. Try it — we guarantee you'll like it.

### Service

Providing global, world-class manufacturing, technical support, and sales/distribution support is an essential **foundation** of our product strategy. Many PLD companies severely underestimate the importance of service to the user base. You may have already used one of the several, new, automated technical support facilities that we've established this year, such as XDOCS, XFACTS or our home page on the World Wide Web.

In summary, our product strategy is simple but unique: provide leading solutions in all three high-growth segments of the programmable logic industry — complex PLDs, reprogrammable FPGAs, and one-time programmable FPGAs support them with the industry's easiest-to-use yet powerful XACT*step* integrated software solution, and deliver unquestioned world-class service. Let us know how we're doing. • available as building blocks for FPGA designs. Similarly, "user-customizable" macro functions, such as those found in the X-BLOX<sup>™</sup> library, will ease the designer's task. Ideally, such macros will be inferred during the synthesis process in order to preserve the portability of the high-level design description, as opposed to having to be specifically instantiated in the HDL code .

### Synthesis Friendly Architecture

The features that make an FPGA architecture "synthesis-friendly" include regularity, symmetry and granularity.

In many ways, the choice of logic block granularity is a trade-off between utilization and performance. With a smaller block, less of each block is wasted for a given logic function, but performance suffers because more levels of logic are needed for a given large function. Of course, other factors also play a role. For example, configuration information must be supplied to each cell; a very finegrained cell can increase the number of configuration elements per usable gate. The "ideal" ratio will vary with the size and type of configuration element (SRAM cells versus antifuses, for example). So, for FPGAs, it's more appropriate to think in terms of a "sea-of-blocks" rather than a "sea-of-NAND-gates".

For SRAM-based FPGAs, past experience has shown that 4-input lookup-tables are among the most-efficient logic structures; this is not likely to change as FPGAs increase in size. Synthesis algorithms that target lookup-table-based architectures have become more efficient. The lookuptable approach also has the benefit of increasing routing flexibility due to its symmetric nature; that is, signals can be freely swapped among the inputs to the table merely by making the corresponding changes to the contents of the memory cells in that lookup table. Thus, one likely candidate for the "basic logic block" in a high-capacity, synthesis-friendly, SRAMbased FPGA is the lookup-table/flip-flop pair already common to several Xilinx FPGA families.

### Memory/Logic Integration

As stated before, large designs typically need to integrate both memory and logic functions. The **on-chip memory** capability pioneered in the XC4000 family will continue to be a desirable feature for very high-density FPGAs. There are three ways of implementing memory in an FPGA:

- small, distributed blocks that can be used as memory or lookup-table-based logic (as in the XC4000 architecture),

- larger embedded blocks of dedicated memory, or

- configuration memory cells that can optionally be used as contiguous memory in the end application (as in the XC6200 architecture).

Each approach has its advantages and disadvantages, and future FPGAs are likely to offer at least one if not some combination of these options.

### Connections

The performance of programmable routing resources is more dependent on the number of programmable switches that must be traversed along a signal path than the length of the metal lines. However, it is wasteful both in terms of resource allocation and overall performance to use a long metal segment for a short point-to-point connection. Thus, the programmable routing resources in a large FPGA should be segmented and hierarchical in nature, with a mix of local (short), mid-range, and long metal lines. While the amount of local interconnect surrounding a block does not need to change as the logic array grows, the number of longer interconnect lines should increase. A good analogy can be made to the layout of streets in a growing city; the size and relative density of local streets

### THEFAWCETT

Continued from the previous page

does not need to change dramatically as the city gets larger, but the size and number of freeways and major highways must grow with the city.

General-purpose routing resources need to be complemented by dedicated, global, **low-skew nets** for distributing clocks and similar high fan-out control signals. As a rule of thumb, the clock distribution scheme should provide for a worst-case clock skew that is less than 5 percent of the clock period (for example, less than 0.5 ns for a 100 MHz clock).

Internal three-state buffers that provide the capability of implementing bi-directional and multiplexed busses within the FPGA, as pioneered in the XC3000 and XC4000 architectures, will remain a critical architectural feature for larger FPGAs. The

> need for efficient, on-chip bussing will become more acute as 32-bit and 64-bit busses become more common in microprocessorbased systems.

As FPGA gate capacity increases, the number of **input**/ **output pads** also needs to increase. However, the ability to implement larger designs in a single device will eliminate the need to partition designs among

multiple FPGA devices, which will reduce I/O needs to a large degree. Input and output buffers will need to be compatible with a wide variety of signaling standards (for example, JEDEC 3.3V, 5V TTL, 5V CMOS and GTL) to facilitate interfacing to most available IC technologies. Time-tomarket demands may cause the user to freeze the I/O placement early in the design cycle, allowing the FPGA design and PCB layout to proceed in parallel. Thus, abundant routing between the I/O blocks and logic array will be required to ensure flexibility in pin placement during design iterations. Furthermore, as with current Xilinx families, maintaining the same package "footprint" across several family members

will give system designers the option of moving to higher or lower density devices without modifications to the PCB layout.

#### Power

High gate capacities and clock rates mean greatly increased power consumption. The next generation of large FPGAs probably will be based on the 3.3 V power standard. The transition to 3.3 V logic decreases dynamic power dissipation by 56 percent as compared to a 5 V device running the same design at the same speed. Circuit design techniques that minimize the turn-on overlaps of the P- and Nchannel transistors in a CMOS device will be employed to further reduce power consumption. Of course, advanced packaging with good thermal conduction characteristics also will be required.

Both the architecture and underlying transistor-level implementation of a highdensity FPGA family should be "**scaleable**" to take advantage of future improvements in IC fabrication technology. Again, Xilinx has a strong track record in this regard, as process advancements have led to faster, larger, and less expensive devices in established FPGA families, such as those based on the XC3000 and XC4000 architectures.

### **On Toward One Million**

While there is plenty of life left in the evolution of Complex PLD architectures (as evidenced by continuing advancements in the Xilinx CPLD product lines), for the near term, PAL-like architectures cannot deliver the flexibility, density, or ASIC-like design flow needed for designs exceeding 100,000 gates.

Meeting the requirements of designs over 100,000 gates will require more than just larger versions of today's devices and tools. Using the highly-successful XC4000 and XC5000 architectures as a stepping stone, Xilinx is poised to deliver new FPGA solutions that fulfill all the requirements for very high density designs.

And we're already thinking about one million gates...  $\blacklozenge$

•Xilinx is poised to deliver new FPGA solutions that fulfill all the requirements for very high density designs. "

## FPGAs Control ATM Connections to French Telecom Network

The Lannion-based laboratory of France Telecom's research center, **Centre National d'Etudes des Telecommunications** (CNET), has found Xilinx FPGAs useful in its research on Asynchronous Transfer Mode (ATM) telecommunications for high-speed communications over ordinary telephone lines. One of seven laboratories operated by France's public telephone company, CNET engineers have been designing, building and testing prototypes of the equipment needed to allow a public network operator to offer ATM connections.

One such piece of equipment, dubbed the "Spacer-Controller," is part of the interface between the sources of the ATM streams and the public ATM network. The Spacer-Controller must check that each received cell conforms to the traffic parameters allowed on that substream. This policing function is referred to as Usage Parameter Control (at the User Network Interface) or Network Parameter Control (at the Broadband Inter Carrier Interface) in the International Telecommunications Union (ITU) standards. This check is performed using an ITU standard algorithm developed at CNET called the "Virtual Scheduling Algorithm." Subsequent to this check, a spacing function ensures the the timely smoothing out of cells belonging to the same substream in accordance with a predefined Peak Emission Interval.

Based on eight years of experience with the high integration levels and ease-of-use of Xilinx FPGAs, the CNET engineers chose members of the XC3100 family for fast prototyping of these highly complex ATM traffic functions

Driven by a 20 MHz clock, four XC3190 FPGAs implement the policing and spacing functions. At the heart of these functions are the multiple 32-bit adders and comparators used for the Virtual Scheduling Algorithms. A fifth XC3190 FPGA selects one of four incoming channels — two proprietary 8-bit parallel channels, one 34 Mbit/s PDH channel (Plesiochronous Digital Hierarchy, the European equivalent to T3), and one 155 Mbit/s SDH channel (Synchronous Digital Hierarchy, the European equivalent to STS-3). An XC4010 and XC4003 FPGA hold the logic for adaptation from the PDH channel to ATM format. This prototype version of the Spacer-Controller is capable of handling 4,096 VP or 65,536 ATM connections on a single link of up to 155.52 Mbit/s on a PC board.

Along with the XACT software, the CNET researchers used Viewlogic tools on a PC and Cadence tools on Sun and IBM workstations to complete the FPGA designs. Logic block utilization of the FPGAs exceeded 90 percent in all but one of the XC3190s. Completion of all the FPGA designs required an estimated one man-year of effort. A refined version currently in development will use a single high-density XC4000 series device to replace the four XC3190s that implement the policing and spacing functions.

This equipment will allow a public network operator to offer ATM connections at an attractively low cost (since the user is granted the lowest possible bandwidth allocation compatible with the application) and with as few constraints as possible (the capability for cell delay variation absorption means that the user does not need to consider the detailed traffic characteristics of his connections at subscription time).

## New Product Literature

Learn about the newest Xilinx products and services through our extensive library of product literature. The most recent pieces are listed below. To order or to obtain a complete list of all available literature, please contact your local Xilinx sales representative.

| πĿ                                                | DESCRIPTION         | NUMBER      |

|---------------------------------------------------|---------------------|-------------|

| Corporate                                         |                     |             |

| Product Overview Brochure                         | Features & Benefits | #0010130-05 |

| EPLDs                                             |                     |             |

| XC7336 Data Sheet                                 | Technical Data      | #0010269-01 |

| FPGAs                                             |                     |             |

| User Access to XC6200 Configuration Memory        | Application Note    | #0010264-01 |

| Interfacing XC6200 to Microprocessors (TMS320C50) | Application Note    | #0010265-01 |

| Interfacing XC6200 to Microprocessors (MC68020)   | Application Note    | #0010266-01 |

| XC5200 Data Sheet                                 | Technical Data      | #0010267    |

| XC8100 Data Sheet                                 | Technical Data      | #0010193-04 |

### **UPCOMING EVENTS**

Look for Xilinx technical papers and/or product exhibits at these upcoming industry forums. For further information about any of these conferences, please contact Kathleen Pizzo (Tel: 408-879-5377 FAX: 408-879-4676).

**Design SuperCon 96** Jan. 30-Feb. 1 Santa Clara, California

**1996 ACM/SIGDA Fourth International Symposium on FPGAs** Feb. 11-13 Monterey, California European Design and Test Conference Mar. 12-14 Paris, France

**DSPx 96** Mar. 11-14 San Jose, California International IC Conference Mar. 27-29 Shanghai, China

PCI 96 Apr. 14-18 San Jose, California

**Digitronics** Apr. 17-18 Birmingham, UK

### **FINANCIAL RESULTS**

## Strong Revenue Growth Continues

Xilinx sales revenues for the second fiscal quarter (ending September 30, 1995) rose to a record \$141.2 million, an increase of 12 percent from the previous quarter and 78 percent from the same quarter one year ago.

The revenue increase resulted from growth in several product families. The XC4000 family continued its strong pace, accounting for 43 percent of total revenues and 50 percent of incoming orders. EPLD revenues grew 80 percent to more than \$3 million. The new XC5200 family generated its first million dollars in sales revenue. Geographically, revenues from North America remained strong, increasing 15 percent over the previous quarter. The European market was surprisingly robust for a summer quarter, growing 33 percent from the previous quarter and contributing 22 percent of total revenues.

Looking ahead to the next six months, CEO Bernie Vonderschmitt stated that, "Our recent bookings momentum, strong backlog position, and new product strength position Xilinx favorably for continued growth in the second half of the year."

Xilinx stock is traded on the NASDAQ exchange under stock symbol XLNX.  $\blacklozenge$

## What's New at WebLINX?

- XCELL journal issues 17, 18, and 19

- New Technology Licensing and Partnership Program— Xilinx is always looking for leading-edge hardware and software technologies, new products, and new services. Here's where to input your ideas.

- Product Literature

- XC8100 FPGA family press release, product overview and data sheet

- XC6200 FPGA family data sheet

- Updated XC4000E FPGA family data sheet

- New application notes

- Coming Soon: Keyword Searching Find what you want fast with a search of all Xilinx WebLINX HTML and PDF files, as well as other programmable logic sites (distributors, universities, partners, etc.)

### Any Suggestions?

What new content, service, or searchable web site would you like to see on WebLINX? Send suggestions to webmaster@xilinx.com.  $\blacklozenge$

## **One-Day XACT**step 6.0 Update Class

Xilinx now offers a one-day training class for current users focusing on the XACT*step*<sup>TM</sup> version 6 update. This class provides the fastest way to make the transition to the new features of XACT*step*, including the Windows-based interface, the XACT-Floorplanner<sup>TM</sup>, and XC5200 and XC4000E FPGA family support. Emphasis is placed on gaining hands-on experience with the new graphical tools.

> The update does not overlap with previous seminars. Users should have experience with the current XACT<sup>®</sup> 5.x tools to get the most from the one-day update; the standard threeday class, which integrates software training into the overall design flow, is recommended for new users. In the one

day update, all the new features will be described in relation to the previous XDM-based environment. Again, there is little overlap with earlier training; in fact, the update class is best for those who have attended Xilinx training on the earlier tools.

storact

Indes

Although most of the Windows-based tools are only available on the PC, workstation users have access to the new graphical Floorplanner. Current workstation users can attend the morning part of the update session, which covers the new devices and the Floorplanner.

Classes are scheduled at many of our existing training locations. Tuition is \$100 in North America, but will be waived for those who attended the three-day training since April, 1995. *Contact your local* sales office, send e-mail to customer.training@xilinx.com, or check the WebLINX web site for details.

| PLASTIC CC         PC44         ◆         ◆         ◆         ◆         ◆         ◆         ◆         ◆         ◆         ◆         ◆         ◆         ◆         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓         ↓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |              |       |        |          |         | C      | 0       | M      | P      | 0      | N      |        | N.           | Τ       | <b>A</b> ' | V       |         | L       | A E      | 31      |         | Γ`      |         | Cł      | -1/     | \F      | 21      |         |         |         |        |        |        |        |            |     |               |        |         |        |   |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|-------|--------|----------|---------|--------|---------|--------|--------|--------|--------|--------|--------------|---------|------------|---------|---------|---------|----------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|------------|-----|---------------|--------|---------|--------|---|---|

| 44       PLASTIC COPP       PO44       PLASTIC COPP       PLASTIC C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PINS | TYPE         | CODE  | XC2064 | XC2018   | XC2064L | XC2018 | XC2010L | VC2020 | XC3042 | XC3064 | X00004 | VC2030 | AUSUCUA      | XC3030A | XC3042A    | XC3064A | XC3090A | XC3020L | XC3030L  | XC3042L | XC3064L | XC3090L | XC3142L | XC3190L | XC3120A | XC3130A | XC3142A | XC3164A | XC3190A | XC3195A | XC4003 | XC4005 | XC4006 | XC4008 | XC4010     |     | XC4010D       | XC4013 | XC4013D | XC4025 |   |   |

| 44       PLASTIC VOEP       VQ44       VQ44 <td></td> <td>PLASTIC LCC</td> <td>PC44</td> <td>•</td> <td>•</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>•</td> <td>♦</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | PLASTIC LCC  | PC44  | •      | •        |         |        |         |        |        |        |        |        | •            | ♦       |            |         |         |         |          |         |         |         |         |         |         |         |         |         |         |         |        |        |        |        |            |     |               |        |         |        |   |   |

| CERAMICLCC       WC44       WC44       Image: Constraint of the constraint of t                                                            |      | PLASTIC QFP  | PQ44  |        |          |         |        |         |        |        |        |        |        |              |         |            |         |         |         |          |         |         |         |         |         |         |         |         |         |         |         |        |        |        |        |            |     |               |        |         |        |   |   |

| CERAMICLCC       WC44       Image: Constraint of the                                                   | 44   | PLASTIC VQFP | VQ44  |        |          |         |        |         |        |        |        |        |        |              |         |            |         |         |         |          |         |         |         |         |         |         |         |         |         |         |         |        |        |        |        |            | T   |               |        |         |        |   |   |

| 48       PLASTIC CUP       P048 <ul> <li>PLASTIC VORP</li> <li>VOR4</li> <li></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |              |       |        |          |         |        |         |        |        |        |        |        |              |         |            |         |         |         |          |         |         |         |         |         |         |         |         |         |         |         |        |        |        |        | 1          |     |               |        |         |        |   |   |

| 64       PLASTIC VOEP       VG64       ◆       ◆       ◆       ◆       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○       ○                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48   |              |       | ٠      |          |         |        |         |        |        |        |        |        |              |         |            |         |         |         |          |         |         |         |         |         |         |         |         |         |         |         |        |        |        |        |            |     |               |        |         |        |   |   |

| PLASTICLIC       PC88       PC87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64   |              | VQ64  |        |          | ۲       | •      | •       |        |        |        | +      |        | •            | ♦       |            |         |         |         | ٠        |         |         |         |         |         |         | ۲       |         |         |         |         |        |        |        |        | T          |     |               |        |         |        |   |   |

| 68       CERAMICICC       WC68       Image: Construction of the cons                                                           | -    |              |       | •      |          |         |        | •       |        |        |        | +      |        | •            | •       |            |         |         |         |          |         |         |         |         |         | ۲       | ۲       |         |         |         |         |        |        |        |        | $\uparrow$ | +   |               |        |         |        |   |   |

| CERAMICPGA       PG8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68   |              |       |        | -        |         | T      |         |        | -      |        | +      |        |              |         |            |         |         |         |          |         |         |         |         |         | -       |         |         |         |         |         |        |        |        |        | t          |     |               |        |         |        |   |   |

| PLASTICLC       PC84       PLASTICLC       PLASTICLC<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |              |       |        |          |         |        |         |        |        |        |        |        |              |         |            |         |         |         |          |         |         |         |         |         |         |         |         |         |         |         |        |        |        |        | 1          |     |               |        |         |        |   |   |

| 84       CERANIC LCC       WC84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |              |       |        |          |         |        |         |        |        |        |        |        |              |         | ۲          | •       | ٠       | ۲       |          |         |         |         |         |         | ٠       | ۲       | ۲       | ۲       | ۲       | ۲       |        | ۲      |        |        |            | •   |               |        |         |        | _ |   |

| CERAMICPGA       PG4       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       • <t< td=""><td>84</td><td></td><td></td><td></td><td>Ť</td><td></td><td>Ť</td><td>•</td><td>-</td><td>+</td><td></td><td>+</td><td></td><td>-</td><td>•</td><td>•</td><td>•</td><td>•</td><td>•</td><td><b>I</b></td><td></td><td></td><td>•</td><td></td><td></td><td>l ·</td><td>•</td><td>•</td><td>•</td><td>•</td><td>Ť</td><td>-</td><td>ľ</td><td>Ť</td><td>-</td><td>Ť</td><td>Ŧ</td><td>•</td><td></td><td></td><td></td><td>-</td><td>-</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84   |              |       |        | Ť        |         | Ť      | •       | -      | +      |        | +      |        | -            | •       | •          | •       | •       | •       | <b>I</b> |         |         | •       |         |         | l ·     | •       | •       | •       | •       | Ť       | -      | ľ      | Ť      | -      | Ť          | Ŧ   | •             |        |         |        | - | - |

| CERAMIC GPP       CO10       CO10 <td>01</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>+</td> <td></td> <td></td> <td></td> <td></td> <td>+</td> <td></td> <td></td> <td></td> <td>٢</td> <td></td> <td>٢</td> <td>۲</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>+</td> <td>+</td> <td></td> <td></td> <td>-</td> <td></td> <td>_</td> <td>-</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 01   |              |       |        |          |         | +      |         |        |        |        | +      |        |              |         | ٢          |         |         |         |          |         |         |         |         |         |         | ٢       | ۲       |         |         |         |        |        |        |        | +          | +   |               |        | -       |        | _ | - |

| PLASTICPOFP     PQ100     PLAST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |              |       |        | <b> </b> |         | +      |         |        |        |        | +      |        | +            | •       | •          |         |         |         |          |         |         |         |         |         | ľ       | •       | •       |         |         |         |        |        |        |        | +          | +   | -             | -      |         | _      | _ | - |

| 100       PLASTICTOFP       T0100       T01000       T010000       T010000 <t< td=""><td></td><td></td><td></td><td>-</td><td>-</td><td></td><td>-</td><td></td><td></td><td></td><td></td><td>+</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>+</td><td>+</td><td>-</td><td>-</td><td></td><td></td><td>_</td><td>-</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |              |       | -      | -        |         | -      |         |        |        |        | +      |        |              |         |            |         |         |         |          |         |         |         |         |         |         |         |         |         |         |         |        |        |        |        | +          | +   | -             | -      |         |        | _ | - |

| PLASTIC VOPP       VQ100       VQ100      VQ100       VQ100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100  |              |       |        |          |         | -      | •       |        |        |        | -      |        | +            | •       | •          |         |         |         |          |         |         |         |         |         | •       |         |         |         |         |         | •      | •      |        |        | +          | +   |               |        |         |        | - | - |

| TOPBRZ_COFP       CB100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100  |              |       |        | -        |         |        |         |        | 4      |        | -      |        | -            |         |            |         |         |         |          |         |         |         |         |         | -       | •       |         |         |         |         |        |        |        |        | +          | +   | -             | _      | _       |        | _ | - |

| 120       CERAMIC PGA       PG120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |              |       |        | -        |         |        |         |        |        |        | +      |        | _            | •       | ▼<br>▲     |         |         |         | -        |         |         |         |         |         |         | •       |         |         |         |         |        |        |        |        | +          | +   | -             | _      | _       |        |   | - |

| 132       PLASTIC FGA       PP132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 120  |              |       |        |          | -       | -      |         |        |        |        | +      |        | +            | -       | •          |         |         |         |          |         |         |         |         |         | •       |         | •       |         |         |         |        |        | -      |        | +          | +   | -             | -      | -       |        | _ | - |

| 132       CERAMIC PGA       PG132       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I <tdi< td="">       I       I</tdi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 120  |              |       |        | -        |         |        |         |        |        |        |        |        | -            | _       |            |         |         |         |          |         |         |         |         |         | -       |         |         |         |         |         | •      |        | -      |        | +          | +   | _             | _      | _       |        | _ | - |

| PLASTICTOPP       TQ144       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I <thi< th="">       I       I</thi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 132  |              |       |        | -        |         | -      |         | _      |        |        |        |        | -            |         |            |         |         |         |          |         |         |         |         |         | -       |         |         |         |         |         |        |        | -      |        | +          | +   | -             | _      | _       |        | _ | - |

| 144       CERAMIC PGA       PG144       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |              |       |        | +        |         | -      |         | _      |        | 4      |        |        | -            |         |            |         |         |         |          |         |         |         |         |         | -       |         |         |         |         |         |        |        | -      |        | +          | +   | +             | -      | -       | _      | _ | _ |

| 156       CERAMIC PGA       PG156       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 144  |              | -     |        |          |         | -      |         | _      | _      |        | +      |        | +            | _       | •          | •       |         |         |          |         |         |         |         |         |         |         | •       | •       |         |         |        |        | -      |        | +          | +   | +             | -      | _       | _      | _ | - |

| 160       PLASTICPQFP       PQ160       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I <tdi< td="">       I       I</tdi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 450  |              |       |        | -        |         | -      |         |        | _      | _      | -      |        | +            | _       |            |         |         |         |          |         |         |         |         |         | -       |         |         |         |         |         |        |        |        |        | +          | +   | +             | _      | _       |        |   | _ |

| CERAMIC QFP       CQ164                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |              |       | -      | -        |         | -      | _       | _      | _      |        |        |        | _            | _       |            |         |         |         |          |         |         |         |         |         | -       |         |         |         |         |         |        |        |        |        |            |     |               |        |         |        |   | _ |

| 104       TOPBRZ.COFP       CB164       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 160  |              |       |        | -        |         | -      |         |        | _      |        | 4)     |        | _            | _       |            | •       | •       |         |          |         |         |         |         |         |         |         |         | •       | •       | •       |        | •      |        |        |            |     | -             |        | •       |        |   | - |

| PLASTIC PGA       PP175       Image: Constraint of the constraint of th                                                  | 164  |              |       | -      | -        |         | -      |         | _      | _      | _      |        |        | +            | _       |            |         |         |         |          |         |         |         |         |         | -       |         |         |         |         |         |        |        | -      |        | +          | +   | +             | _      | _       | _      |   | - |