### THE QUARTERLY JOURNAL FOR XILINX PROGRAMMABLE LOGIC USERS

The Programmable Logic Company<sup>SM</sup>

### Inside This Issue:

### **GENERAL**

| Fawcett: PLDs, Pins, PCBs (part 2) | 2     |

|------------------------------------|-------|

| Guest Editorial                    | 3     |

| Customer Success Story             | 6-7   |

| 1996 Data Book                     | 7     |

| University Workshops               | 8     |

| Training Update                    | 9     |

| Fiscal Year Financial Results      | 9     |

| New Product Literature             | 10    |

| Upcoming Events                    | 10    |

| Development Systems Chart          | 11    |

| Component Availability Chart       | 12-13 |

| Alliance Program Charts            | 14-16 |

| Programming Support Charts         | 17-19 |

|                                    |       |

### PRODUCTS

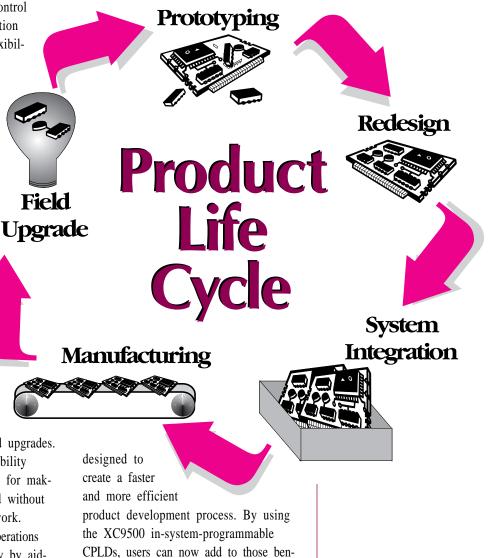

XC9500 Product Life Cycle ..... 20-21

### **DEVELOPMENT SYSTEMS**

| Foundation Series               | 22-23 |

|---------------------------------|-------|

| XACT-CPLD Introduced            | 24    |

| XACT step 6.0.1 Software Update | 25    |

#### **HINTS & ISSUES**

| Using OrCAD Capture and Simulate 26-28 |

|----------------------------------------|

| Foundation on a Network 29             |

| Viewlogic's Workview Office 30-31      |

| HDL Synthesis and Clock Enables 32-34  |

| Ten-Digit Synchronous BCD Counter 35   |

| Structured Floorplanning 36-39         |

| Minimum Delays 40-41                   |

| Visit FPGA Newsgroup 41                |

| Advanced Carry-Logic Techniques 42-44  |

| PCI-Based Reconfigurable Computers 45  |

| Questions & Answers 46-47              |

| Technical Support Resources 47         |

| Fax Response Form 48                   |

|                                        |

### **PRODUCTINFORMATION**

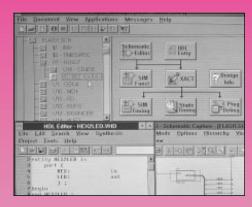

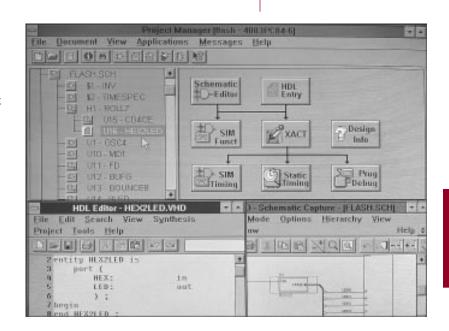

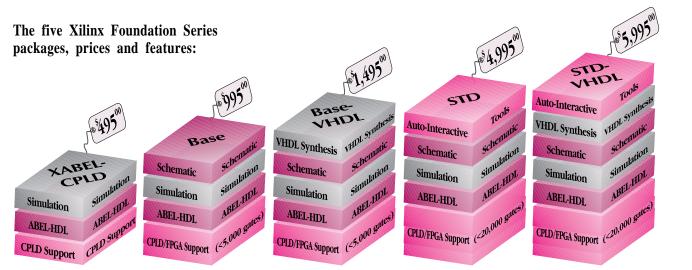

### VHDL Made Easy! Introducing Foundation Series Software

The new Foundation Series packages are complete, fully integrated sets of development tools for CPLD and FPGA device design that include the HDL Wizard, a set of tools that help users quickly learn and implement HDL-based designs...

See Page 22

### XACT*step*<sup>™</sup> 6.0.1 Release

This update to the XACT*step* development system adds XC4000E FPGA and XC9500 CPLD support... See Page 25

### DESIGNATIPS & HINTS

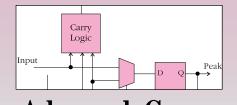

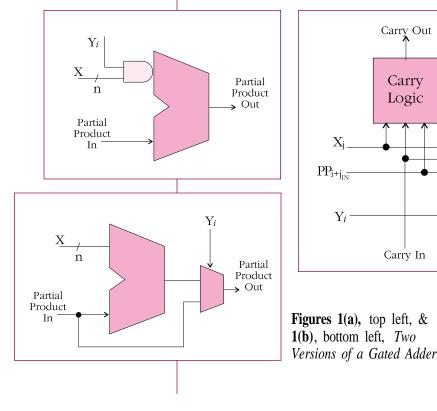

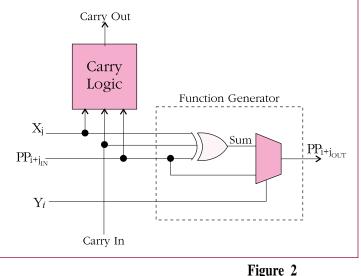

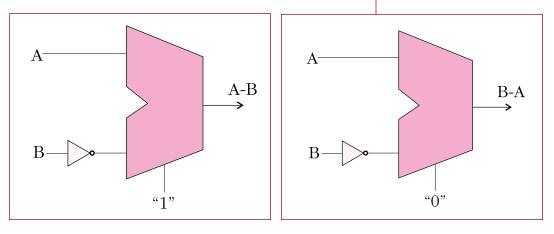

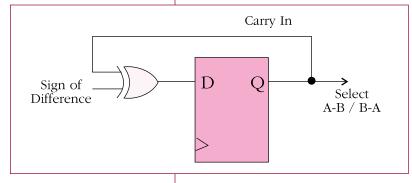

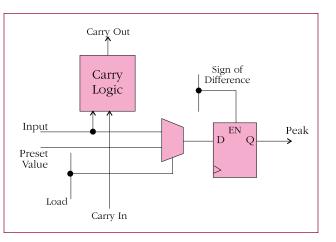

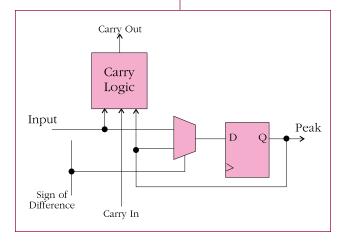

### Advanced Carry Logic Techniques

The XC4000 FPGA's carry logic can be used for lots more than adders and counters... See Page 42

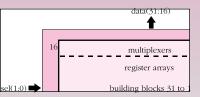

### Structured Floorplanning

Implement high-ordered designs efficiently and easily with the XC8100 family... See Page 36

### FROMTHEFAWCETT

Part 2 of 2

# PLDs, Pins and PCBs (part 2)

By BRADLY FAWCETT + Editor

Part 1 of this article (*XCELL* 20, page 2) discussed the inevitability of design changes during all stages of an electronic system's lifecycle. Changes can occur as a

result of the debugging and testing of the initial design, due to specification changes during the design, or even to add features to a mature product to extend that product's life.

An important benefit of user-programmable logic is tolerance of

change; with PLDs, design changes can be implemented quickly and easily. However, printed circuit board (PCB) designs are not as easy to change, typically requiring new drawings (masks) and the manufacturing of new prototypes, with all the associated expenses and delays. Thus, to garner all

the benefits of the flexibility of programmable logic, programmable logic device architectures should isolate the PCB design from logic changes that occur within the PLD device. Device

architectures should do this in two ways — by supporting pin-locking and with footprint compatibility.

**Pin-locking** — that is, for signals entering and leaving a PLD, maintaining the pin locations during design changes internal to the PLD — was discussed at length in part 1. Support for pin-locking is a key feature of the latest generations of Xilinx CPLDs and FPGAs. Equally important, **footprint compatibility** maximizes PLD design flexibility, and has been incorporated in all Xilinx components since the XC2000 family the world's first FPGA! Footprint compatibility refers to the availability of PLDs of various gate densities with the same package and with an identical pinout. With a range of footprint-compatible devices available, users may migrate a given PLD design to a higher- or lower-density device without changing the printed circuit board.

#### Footprints in the Silicon

There are several scenarios where a common device footprint provides a significant advantage. The most prevalent of these is when a design is being modified to add features without changing the pinout requirements, and, as a result, the design grows to exceed the gate density of the PLD device that was initially selected.

*footprint* compatibility maximizes PLD design flexibility, and has been incorporated in all Xilinx components since the XC2000 family" By moving the design to a footprint-compatible device with higher capacity, a re-layout of the printed circuit board is avoided, saving both time and money. On the other

hand, a design can be initially prototyped in a larger device than needed, to allow room for expansion and experimentation. Once the design is fixed, it can be migrated to a smaller, less-expensive device in the same package as a cost reduction. Again, footprint compatibility between the devices avoids changes to the printed circuit board. (*There is, however*,

#### Continued on page 5

### XCELL

Please direct all inquiries, comments and submissions to:

Editor: Bradly Fawcett

#### Xilinx, Inc.

2100 Logic Drive San Jose, CA 95124 Phone: 408-879-5097 FAX: 408-879-4676 E-Mail: brad.fawcett@xilinx.com

©1996 Xilinx Inc. All rights reserved.

XCELL is published quarterly for customers of Xilinx, Inc. Xilinx, the Xilinx logo and XACT are registered trademarks; all XC-designated products, UIM, HardWire, Foundation Series, HDL Wizard, TrueMap, XACTstep and XACT-Performance are trademarks; and "The Programmable Logic Company" is a service mark of Xilinx, Inc. All other trademarks are the property of their respective owners.

•

# The First Ten Weeks

By WILLEM ROELANDTS

Chief Executive Officer

It is a pleasure to address you after being in my new position for ten weeks. I feel even better today about my decision to join Xilinx than I felt when I started, now that I have a better understanding of the company and its products. During the past ten weeks I have spent most of my time meeting with the Xilinx people, our foundry partners, our sales and distribution organizations, our shareholders and our customers. In general, I am very pleased with the feedback and inputs that I have received.

I have found that Xilinx people are very capable, technically competent (after all, Xilinx did invent FPGA technology), and very motivated.

The relationship between Xilinx and our foundry IC partners is both excellent and enduring. Due to strong teamwork, it has withstood the inevitable ups and downs of the IC business.

The quality of our independent sales organization is very strong. We have had long-standing relationships with them and they are very familiar with our products. Some have invested in their own Field Application Engineers (FAEs), in order to serve our customers better.

Our customers are pleased with our products. They like the time-to-market advantages of using FPGAs and CPLDs in design and production, and our standard parts simplify their production and inventory management. Our users have also pointed out some issues and opportunities, including on-time delivery, the importance of software tools and the continuing need for bigger and faster chips.

During this time I also have reflected on our strategic directions. I can assure you that the major components of this highly successful strategy will not change. We will continue to:

- Focus on FPGA technology by aggressively increasing size and performance. The XC4000EX family will reach 125,000 gates in 1997. Our XC5000 family is an excellent solution for the low-end FPGA market. The XC8100 family of one-time-programmable FPGAs provides other unique features.

- Add technologies for specific customer requirements. The very successful XC9500 family uses a CPLD architecture, but adds in-system programmability (ISP), a feature highly appreciated by our users.

- **Develop reconfigurable logic**, which is the ability to dynamically change the logic configuration of the FPGA during the operation of the device. This technology promises to change the way logic is designed. It is an area in which Xilinx has done a lot of work and I intend to aggressively continue the effort.

- Use outside foundries for our wafer processing. It provides the best flexibility and enables us to provide our customers a stable flow of high quality products.

Continued on the next page

•••••

•••••

**G** Can assure you that the major components of this highly successful strategy will not change."

Continued from the previous page

- Work with independent sales organizations, but provide them with technical resources for training and support.

- Use the six sigma defect rate standard as our norm for product quality. In order to guarantee the quality of our products, we will continue to do most product testing in-house.

- Provide technical support that is second-to-none in the industry. The ability to contact experts quickly is critical to maintaining the productivity of our users.

**••**There is no doubt in my mind that software has to be a core competency of Xilinx; it is as important as our ability to design FPGA chips."

> There are some changes or refocusing of strategic components that I feel will make Xilinx even more successful. They include:

#### The importance of software

There is no doubt in my mind that software has to be a core competency of Xilinx; it is as important as our ability to design FPGA chips. That's why we acquired NeoCAD. I believe we have the right people and now we are going to execute. Our objective is to be the best in the industry, and I intend to give this my personal attention. You have already seen some of the results with the introduction of the XACTstep<sup>™</sup> 6.0/5.2 release, the Japanese version of this product, and the new Foundation<sup>™</sup> release — a fully-integrated, "shrink-wrap" package for the PC platform. Foundation software packages offer the best functionality in their price

class (starting at less that \$500), and are complete software sets delivered from Xilinx! This is only the beginning; more new capabilities and performance improvements will be introduced this year.

#### The opportunity of logistics

The IC industry goes through cycles of feast and famine, and last year we grew more than expected, causing us to sometimes miss our delivery schedules (although our record was better than most). I believe that with better planning of the supply chain, better management of the distribution process, shorter manufacturing cycles and more aggressive use of information technology, we should be able to do a better job and meet 100% of our delivery commitments.

#### Design paradigm change

With the densities of our largest FPGAs exceeding 100,000 gates, our users will no longer be able to design logic functions one gate at a time. In response, we are moving to a new paradigm. Xilinx is creating libraries of specific functions in software that will be tested and guaranteed — we call these LogiCore<sup>™</sup>modules. We envision a design process where the designer selects the needed functions, adds the application's specific logic, and lets the software put it all together. This methodology will dramatically reduce the time required to design complex logic functions, improving time-to-market and the efficiency of our users. Of course, the complete implementation of this vision will take some time. The first LogiCore product, the PCI module, has proven this concept and has been tremendously successful. We are going to aggressively pursue this strategy.

So there you have it — an overview of my thinking after 10 weeks on the job. I will continue to keep you informed of the progress we are making on the execution of our strategy.  $\blacklozenge$

### THEFAWCETT

#### Continued from page 2

one caveat to consider when migrating a design from a larger to a smaller PLD device. For some smaller devices, the package may have more physical pins than there are input/output pads on the device. Thus, some package pins may be left unconnected. A larger device in the same family may have more I/O pads on the die and, therefore, have connections to all the pins of the given package. Thus, if migration to a smaller part is anticipated, the initial design in the larger device should avoid using those pin locations that are not connected in the smaller device.)

In other words, footprint compatibility lessens any risks associated with the initial device selection, which often must be based on a rough estimate of the design's requirements. If the selected device turns out to be too small, the design is migrated to a larger device. If the selected device is too big, the design can be moved to a smaller device. In either case, potentially expensive and time-consuming changes to the PCB are not necessary.

Footprint-compatible devices also provide the user with more inventory flexibility. Devices that are on-hand can be used for prototyping or initial production, and the design can then be migrated to a footprint-compatible device for quantity production. If a sudden demand "upside" should develop, users have the option to move to a larger device in the same family or a similar-sized device from another footprint-compatible family.

### **Compatible From the Start**

Recognizing these benefits, Xilinx always has maintained footprint compatibility within component product families and subfamilies whenever multiple devices share common packages. For example, the XC3030 and XC3042 devices share a common footprint in the PC84, TQ100, and VQ100 packages. That same footprint is maintained in the equivalent density members of the XC3000A, XC3100, XC3100A, and XC3000L sub-families. (The only exceptions are the XC3000 series and its derivatives in the PC 84 package, where some of the larger devices need two additional GND and  $V_{cc}$  connections, and in the PQ208 package, where the XC3090 and XC3195 devices do not have compatible footprints.)

Cross-family compatibility began with the XC4000 series of FPGAs and includes the XC5000 series and the XC8100 series - all sharing common footprints in common packages. This provides designers with many options. For example, as reported in XCELL 19, VTEL Corp., a manufacturer of video teleconferencing systems and one of the first adopters of the XC5000 family, prototyped their designs in XC4000 series FPGAs while awaiting the availability of XC5000 components and development tools. The resulting designs were easily migrated to lower-cost, footprintcompatible XC5000 devices for production systems. In a similar scenario, a designer could exploit the re-usable nature of the SRAM-based XC4000 or XC5000 FPGAs for debug and prototyping purposes, and then switch to the one-time-programmable XC8100 family for production.

Designers should avoid getting locked into programmable logic solutions that offer little flexibility in pin assignments and device selection. Xilinx CPLDs and FPGAs offer the best pinlocking capabilities in the industry, and the broadest spectrum of footprint-compatible devices. These features allow users to avoid modifications to printed circuit board designs, thereby accelerating timeto-market and accommodating the inevitable design changes that occur throughout a product's total life cycle. ◆ 5

### •Designers

should avoid getting locked into programmable logic solutions that offer little flexibility in pin assignments and device selection."

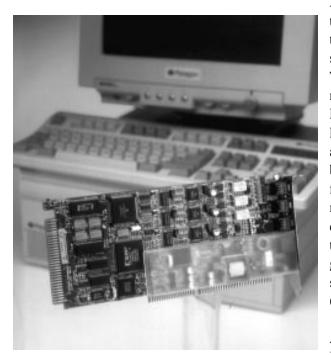

# FPGAs Go "Down Under" in an

Engineers at communications equipment specialist Tennyson Technologies (Notting Hill, Victoria, Australia) are experienced users of Xilinx XC3000 and XC4000 series FPGAs. Thus, when a new project created a need for high integration levels, design flexibility, and a fast timeto-market, all at a reasonable cost, it was no surprise that they turned to the latest

Xilinx FPGA technology the XC5000 series. In Tennyson's new MicroAccess PCTA terminal adapter card, both bus interface and communication control functions are integrated into a single XC5206-6 FPGA device. The Micro-Access system includes a

plug-in card for PC systems and the accompanying software. It allows any PC or PC LAN to automatically make connections to off-site systems; the connection can be made to last only as long as information is being exchanged, much like a telephone call. With support for voice and data transfers, the MicroAccess system permits connectivity through ISDN, regular telephone line or X.25 services.

The logic functions implemented in the FPGA device include the ISA-bus interface, FIFO control, communications control, V110 rate adaptation, data compression/decompression, and other glue logic. The bus interface supports plugand-play capability and accounts for about one-half of the logic in the FPGA. The bulk of the communications control logic consists of the counters used to assemble and synchronize the frames of data. About 75% of the available CLBs are used in this design, as well as most of the I/O pins available on the PQ208 package.

While any of several FPGA families could have provided the required density and functionality, Tennyson's engineers were attracted to the XC5000 architecture's VersaRing<sup>™</sup> feature, in which extra routing channels around the perimeter of the array increase the flexibility of I/O connections. In order to meet the time-to-market goals, the designers realized that the printed circuit board (PCB) would need to be designed in parallel with the system's logic. Thus, the pinout for the XC5206 FPGA was fixed prior to the design of its internal logic. Through each design iteration, the VersaRing concept held true; changes to the FPGA design did not force any changes to the original PCB layout.

The flexibility provided by the SRAMbased FPGA was key to the successful design of the system. For example, the board was originally intended to support a 16-bit ISA bus interface only, but the specification was later changed to require support for both 8-bit XT and 16-bit AT systems. Since the entire bus interface is implemented in the FPGA, this requirement was accommodated, without requiring changes to the PCB layout as a result.

Taking advantage of the in-systemprogrammable FPGA technology, the MicroAccess board has been designed in anticipation of future field upgrades. New

# ISDN Terminal Adapter

software (stored in Flash memory on the board) and new FPGA configuration programs can be downloaded to units in the field via an ISDN interface. In fact, one set of FPGA configuration programs has been dubbed the "Emergency Xilinx" diagnostic mode; this configuration runs just the ISDN channel, allowing for the downloading of new software and configuration bitstreams to the system.

Tennyson Technology's development environment is PC-based, and includes Viewlogic System's schematic editor and simulator, as well as the Xilinx XACT<sup>®</sup> development system. XACT-Performance<sup>™</sup> time specifications and some floorplanning of the FPGA placement were used to meet the required 33 MHz system clock rate, a fairly aggressive goal when using the -6 speed grade. Both the Viewsim simulator and the X-Delay timing calculator were used to verify the functionality and timing of the FPGA design.

With the aid of Xilinx FPGAs, Tennyson Technology's MicroAccess system is allowing some of Australia's leading organizations to combine telephone and data traffic into single services, providing for better communications with branch offices and other remote locations while reducing overall communication costs. ◆

### 1996 Data Book Available Soon

The 1996 Xilinx Programmable Logic Data Book will be available this summer. It will contain data sheets and product specifications describing Xilinx component and development system products, including the latest information on the new XC4000E, XC4000EX, XC6200, XC8100 and XC9500 device families. Other included device families described are the XC7200A and XC7300 CPLD families, the XC3000A, XC3000L, XC3100A, XC3100L, XC4000L, XC4000XL and XC5200 FPGA families, and the XC1700 family of Serial PROMs.

The product specifications for the XC2000, XC3000, XC3100, XC4000, XC4000, XC4000A, XC4000D, and XC4000H FPGA families are not included. These products are still available; however, we recommend using the products in the data book for new designs because they offer better performance at lower cost than the older tech-

nologies. Product specifications for the older products are available at WebLINX, the Xilinx site on the World Wide Web (www.xilinx.com), or through your local Xilinx sales representative.

The military/highreliability and HardWire<sup>™</sup> product lines are overviewed in the 1996 edition, but will retain their own, separate detailed product specification literature.

While the book provides detailed, easy-to-access information about Xilinx products, as a book, it can only offer a "snapshot" of Xilinx products in early 1996. Inquire with your sales representative, WebLINX or this journal for the latest information on new devices, speed grades, package types and development systems. ◆

### Xilinx Hosts University Workshops

If you are a university professor who would like to incorporate programmable logic technology into your engineering curriculum, get started by attending a Xilinx University Workshop. Xilinx technology has been used in many engineering courses, including beginning and advanced digital design, processor architecture, digital signal processing, VLSI design, data communications and various project-oriented laboratory courses.

This summer, Xilinx will be hosting four workshops in the United States and two in Asia. These workshops provide a thorough introduction to programmable logic technology, and discuss how to integrate the technology into first-year through fifth-year university courses. The workshops are taught by a team of Xilinx training professionals and local professors with experience at using programmable logic in their own coursework. Technologies covered at the workshops include field programmable gate arrays (FPGAs), complex programmable logic devices (CPLDs), and dynamically reconfigurable logic. Although most workshops will cover the same basic material, some will have special themes, as described below. Hands-on labs using PC-based development tools are included in each workshop.

These three-day workshops are available free of charge to professors and instructors. However, due to the popularity of the workshops, attendance is limited to two people from each university or college. Seating and hotel rooms at each workshop are limited, so early registration is advised.

To register, contact Jason Feinsmith, Xilinx University Program Manager, at 408-879-4961 or e-mail xup@xilinx.com or visit www.xilinx.com/programs/univ.htm for information. ◆

### **WORKSHOP SCHEDULE**

### **UNITED STATES**

### **Xilinx/Washington State University Workshop** Richland, WA ◆ June 24 - 26

In addition to the basic course material, Dr. Donald Hung will discuss his first-hand experiences in developing courses that use programmable logic.

### Xilinx/Cornell University Reconfigurable Computing Workshop Ithaca, NY ◆ July 10 -12

This will be our first hands-on workshop devoted to the topic of reconfigurable computing with FPGAs. Targeted at educators who are familiar with reprogrammable logic and are very interested in the concept of dynamically reconfigurable computing, this workshop will condense the basic material and focus on this new and promising

### ASIANSCHEDULE

Workshops are planned for the week of August 19 in China, and the week of August 26 in Taiwan. Further details were not available at the time of this printing. area of study. Several researchers will be present to discuss their work.

### Xilinx/Massachusetts Institute of Technology Workshop

Boston, MA 🔶 July 15 - 17

For those particularly interested in computer architectures, this workshop will include a look at MIT's newlycreated computer structures curriculum based on Xilinx devices and the "electric legos" concept.

#### Xilinx/Oakland University Workshop

Detroit, MI 🔶 July 24 - 26

Dr. Subra Ganesan will discuss his work in using FPGAs in digital signal processing applications at this workshop.

For up-to-date information, visit www.xilinx.com/programs/univ.htm on the World Wide Web.  $\blacklozenge$

# Fiscal 1996: Another Record Year

As in every year since Xilinx was founded, the company again achieved record revenues in fiscal year 1996 (April 1995-March 1996). Fiscal 1996 revenues totaled \$560.8 million, an increase of 58% over fiscal 1995, reflecting the continuing strength of our product line and expansion of the programmable logic market.

### Key accomplishments of fiscal 1996 include the following:

- The flagship XC4000 series products contributed revenues of over \$250 million, more than doubling the revenue of the prior year.

- International revenues grew by more than 80% to \$198 million.

- Xilinx Ireland, our first wholly-owned manufacturing site outside of the U.S., became fully operational.

- The merger with NeoCAD Corp. was completed, providing access to power-ful new software solutions.

- Access to leading-edge process technology was enhanced with a 25% equity investment in an 8-inch wafer fabrication facility in a joint venture with United Microelectronics Corp.

- Our commitment to product development was exemplified by research and development spending of approximately \$65 million, 63% more than the second-largest programmable logic supplier.

As noted by Willem Roelandts, Chief Executive Officer, "Xilinx is well-positioned as we enter fiscal 1997. New products that we introduced in the second half of fiscal 1996, including the high-performance XC4000E, the high-density XC4000EX, and the Flash-based insystem-programmable XC9500 CPLD family, should become key revenue drivers next year. Moreover, all these silicon products will be supported by a new, more-powerful, and easier-to-use software solution. Looking ahead, we remain optimistic about the overall growth of programmable logic and our position within this market."

Paced by growth in the European market, revenues for the fourth fiscal quarter (ending in March) reached a record \$149.7 million, up 37% from the same quarter one year ago, and 4% from the immediately previous quarter.

Founded in 1984, Xilinx is the world's largest supplier of programmable logic devices. Xilinx stock is traded on the NASDAQ exchange under stock symbol XLNX. ◆

### **TRAINING UPDATE**

### Advanced Training Available

The advanced training course is again available at Xilinx headquarters in San Jose, California. The session focuses on features of the Xilinx devices and development system that allow experienced users to create more efficient designs.

Advanced training will be useful for anyone "pushing the envelope" in terms of the speed and density of Xilinx FPGA products, especially the XC4000 family devices. The primary focus is on floorplanning and the use of the new graphical Floorplanner<sup>TM</sup>.

Classes are scheduled regularly at Xilinx headquarters starting in May. The class is open to all in-warranty Xilinx customers at no charge. Previous experience with the Xilinx products is a prerequisite for the advanced training course.

For more information or to register, visit WebLINX (www.xilinx.com) on the World Wide Web, call Xilinx Training at 408-879-5090, or e-mail to customer.training@xilinx.com. ◆

### New Product Literature

Learn about the newest Xilinx products and services through our extensive library of product literature. The most recent pieces are listed below. To order or to obtain a complete list of all available literature, please contact your local Xilinx sales representative.

| ΠE                                                     | DESCRIPTION         | NUMBER      |

|--------------------------------------------------------|---------------------|-------------|

| FPGAs                                                  |                     |             |

| XC4000 to XC4000E Conversion Guide                     | Technical Data      | #0010295-01 |

| Interfacing between 5-V and 3.3-V                      | Technical Data      | #0010296-01 |

| Efficient Shift Registers                              | Technical Data      | #0010298-01 |

| CPLDs                                                  |                     |             |

| XC9500 Quick Reference Guide                           | Features & Benefits | #0010408-01 |

| Software                                               |                     |             |

| XACT step 5.2 Sell Sheet                               | Features & Benefits | #0010289-01 |

| Xilinx Foundation Series Sell Sheet                    | Features & Benefits | #0010292-01 |

| Other                                                  |                     |             |

| 1996 Training Brochure                                 |                     | #0010134-05 |

| Literature Packet: DSP                                 | Technical Data      | Packet #2   |

| Literature Packet: RADD (Reconfigurable Architectures) | Technical Data      | Packet #15  |

### **UPCOMING EVENTS**

Look for Xilinx technical papers and/or product exhibits at these upcoming industry forums. For further information about any of these conferences, please contact Kathleen Pizzo (Tel: 408-879-5377 FAX: 408-879-4676).

**Design Automation Conference (DAC)** June 3-7 Las Vegas, Nevada

IntertronicDSJune 4-7JunParis, FranceMa

**DSP Roadshow** June 5-6 Manchester, UK

> DSP Scandinavia June 18-19 Copenhagen, Denmark

International Conference on Application Specific Systems, Architectures, and Processors Aug. 19-21 Chicago, Illinois

Electronic Design Automation and Test Conference (EDA&T) Sept. 5 -6 , Beijing, China Sept. 9-10, Seoul, Korea Sept. 12-13, Hsinchu, Taiwan

**DSP Roadshow** Sept. 25-26 London, UK

International Workshop on Field Programmable Logic and Applications Sept. 23-25 Darmstadt, Germany

|                                    |                             |                             | PC update by request only | No key required with version 6.0.1 | 3/96                 | NTE VISTOR OF    | Supportion SUL+, VSL+VLZ |                  | ) Series 6.1            | ) Selles 0. I    | 2 2 2 1 D 7       |                                                                      |                                          |                           |                | sim libraries              | Incl sch, sim, and synth libraries | ite            |                |                        | 401 v5 2             | 401 v5.2             | quest only             |               |               | )Series6.1             | Includes P KUSeries 6.1/PROsynth 5.02X |                |                           | Includes 502/550/380 | (1350/380 & Foundry | New Aldec software V2.2: 1st ship 3/15/96<br>New Aldec software v2 2: 1st ship 3/15/96 | New Alder software v2 2: 1st ship 3/15/96 | New Aldec software v2.2: 1st ship 3/15/96 | Regsigned lic agreement; 1st ship 3/15/96 | PC,Sun, HP kits now available |           | By request only; Reg In-wnty prod | By request only; Req In-wnty prod |

|------------------------------------|-----------------------------|-----------------------------|---------------------------|------------------------------------|----------------------|------------------|--------------------------|------------------|-------------------------|------------------|-------------------|----------------------------------------------------------------------|------------------------------------------|---------------------------|----------------|----------------------------|------------------------------------|----------------|----------------|------------------------|----------------------|----------------------|------------------------|---------------|---------------|------------------------|----------------------------------------|----------------|---------------------------|----------------------|---------------------|----------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------|-----------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

|                                    |                             | Comments<br>Features        | PC update b               | No key requi                       | First ship 4/23/96   | No AP1 update    | Supportion S             | Includes XC:     | Includes PRO Series 6.1 |                  | Moundation        |                                                                      | SunandHP                                 |                           |                | Incl sch and sim libraries | Incl sch, sim,                     | No AP1 update  | I hadata bura  | opuale by request only | Includes DS-401 v5 2 | Includes DS-401 v5.2 | Update by request only |               |               | Includes PROSeries 6.1 | Includes PROSeries 6.1/PR              |                |                           | Includes 502/550/380 |                     | New Aldecs                                                                             | New Alder s                               | New Aldec su                              | Reqsigned                                 | PC,Sun, HP1                   |           | By request or                     | By request or                     | By request o.                     | By request or                     | By request o                      |

|                                    | PREVIOUS                    | VERSION                     | 5.10                      | 6.01                               | na<br>-              | 5.11             | 0.00                     | 3.30             | 5.11                    |                  | 0.1               | 5.10                                                                 | na                                       |                           | 5.11           | na                         | 1.00                               | 5.11           | na<br>11       | 5 11<br>11             | 5 10                 | ua<br>na             | 5.11                   | 5.11          | na            | 5.11                   | 5.11<br>5.11                           | na             | na                        | 5.10                 | na                  | e e                                                                                    |                                           | n e                                       | na                                        | na                            |           | na                                | na                                | na                                | na                                | na                                |

| 1996                               | LAST                        |                             | 11/95                     | na                                 | na                   | 11/95            | 30/11                    | <u>96/11</u>     | 11/95                   | 11/95            | 11/95             | 11/95                                                                | na                                       |                           | 11/95          | na                         | 08/95                              | 11/95          | 11/0E          | 11/95                  | 11/95                | na                   | 11/95                  | 11/95         | na            | 11/95                  | 11/95                                  | na             | na                        | na                   | na                  |                                                                                        |                                           | n eu                                      | na                                        | na                            |           | na                                | na                                | na                                | na                                | na                                |

| - MAY                              | ATFORM                      | 9.01                        | 5.20                      | 0                                  | 6.0                  | 9.20             | 00                       | 07.9             |                         | 00 4             | 07.0              | 5 20                                                                 | 1.00                                     |                           | 5.20           | 1.10                       | 1.10                               | 5.20           | 00.7           |                        | 5 20                 | 7.00                 |                        | 6.00          | 7.00          |                        |                                        |                |                           | 5.20                 | 00.7                |                                                                                        |                                           |                                           | 1.00                                      | 1.00                          |           | 1.00                              |                                   | 1.00                              | 1.00                              | 1.00                              |

| ATUS                               | CURRENT VERSION BY PLATFORM | <b>SN2</b><br>4.1.X         | 5.20                      |                                    | 6.0                  | 9.20             | 00                       | 07.G             |                         | 00 3             | 02.6              | 5.20                                                                 | 1.00                                     |                           | 5.20           | 1.10                       | 1.10                               | 5.20           | 00.7           |                        | 5 20                 | 7.00                 |                        | 6.00          | 7.00          |                        |                                        |                |                           | 5.20                 | 00.7                |                                                                                        |                                           |                                           | 1.00                                      | 1.00                          |           | 1.00                              |                                   | 1.00                              | 1.00                              | 1.00                              |

| REST                               | CURRENT V                   | 6.2<br>6.2                  | 6.00                      | 6.10<br>6.2                        | 6.0                  | 00 3             | 07°C                     | 0000             | 6.00                    | 0.00             | 0.00              | 5 20                                                                 | 0-10                                     |                           |                | 1.10                       | 1.10                               |                | 00 3           | 0.00                   | 000                  |                      | 6.00                   | 6.00          | 7.00          | 6.00                   | 00.9                                   | 7.00           | 6.00                      | 6.00                 | 00.7                | 0.00                                                                                   | 00.0                                      | 6.00                                      | 1.00                                      | 1.00                          |           |                                   | 1.00                              |                                   | 1.00                              | 1.00                              |

| ELEASED SOFTWARE STATUS - MAY 1996 | XILINX PART                 | REFERICE                    | DS-550-xxx                | DS-571-PC1                         | DS-560-xxx           | DS-344-xxx       | DS-30-PCI                | DS-401-XXX       | DS-390-PC1              | DS-250-PC1       | DS 271 200        | DS-3/1-XXX<br>DS-380-XXX                                             | ES-VERILOG-XXX                           |                           | DS-CDN-STD-xxx | DS-8000-STD-xxx            | DS-8000-EXT-xxx                    | DS-MN8-STD-xxx | DS-MN8-ADV-XXX | DS-OR-BAS-TCI          | DS-SV-STD-ww         | DS-SY-ADV-xxx        | DS-VL-BAS-PC1          | DS-VL-STD-xxx | DS-VL-ADV-xxx | DS-VLS-BAS-PC1         | DS-VLS-SILU-PCI<br>DS-VLS-EXT-PC1      | DS-VLS-ADV-PC1 | DS-3PA-BAS-xxx            | DS-3PA-STD-xxx       | DS-3FA-AUV-XX       | DS-FND-BAS-PC1<br>DS-FND-BSV-PC1                                                       | DS-FND-STD-PC1                            | DS-FND-STV-PC1                            | LC-DI-PCIM-C                              | DS-EVAL-XXX-C                 |           | PR-MN8-STD-xxx-4E                 | PR-OR-STD-xxx-4E                  | PR-SY-STD-xxx-4E                  | PR-VL-STD-xxx-4E                  | PR-3PA-STD-xxx-4E                 |

|                                    |                             |                             | Itation                   | on/Core                            |                      | s                | 2                        | s                | 8                       | 0                | I/F and Libraries | Eritry, Sirridiauori, Lib, Optimizer<br>Module Generator & Ontimizer | Translator                               | <u>Ж</u>                  |                | ×                          | ×                                  |                |                |                        |                      |                      |                        |               |               |                        |                                        |                |                           |                      | - 00                | NCH<br>NCH                                                                             | HUS                                       | SCH                                       |                                           | ×                             |           |                                   |                                   |                                   |                                   |                                   |

| XILINXR                            |                             | <b>P</b> RODUCT<br>FUNCTION | Core Implementation       | Entry/Simulation/Core              | Core + I/F           | I/Fand Libraries | I/Fand Libraries         | I/Fand Libraries | I/Fand Libraries        | I/Fanu Libraries | L/F and Libraries | Andule Genera                                                        | 2K,3K,4K,7KLibraries Models & XNFTransla | SILICONSUPPORT<br>K 5K 7K | ××             |                            |                                    | ××<br>××       | × ><br>× >     | < ×                    |                      |                      | ×                      | X X           | ××            |                        | × ×<br>× ×                             | ××             | ×                         | × ><br>× >           |                     | × ×<br>× ×                                                                             | <                                         | × ×                                       | :                                         | ××                            | SYN. LIB. |                                   |                                   | VHDL<br>Verilog                   | )                                 |                                   |

|                                    |                             |                             |                           |                                    |                      |                  |                          |                  |                         |                  | -                 |                                                                      | ibraries N                               | <b>Å</b> silio            | ×              |                            |                                    | ××             | < >            | <                      |                      |                      | ×                      | ×             | ×             | ×>                     | ××                                     | ×              | ×                         | ×>                   | < >                 | × ×                                                                                    | <                                         | < ×                                       | 拾                                         | ×                             | SIM.      | ×                                 |                                   | VHDL                              |                                   | ×                                 |

|                                    |                             | Product<br>Description      | XC7K, XC9500 Support      | XC7K, XC9500 Support               | XC/K, XC9500 Support | 8.4=A.4          |                          |                  | PROcapture              |                  |                   |                                                                      | ,3K,4K,7KL                               | 2K<br>3K                  | ××             |                            |                                    |                | < >            | < ×                    | ſ                    | ž<br>Ž               | ××                     | ×             | ×             |                        | <                                      | ×              | ×                         |                      |                     | × ×                                                                                    |                                           |                                           |                                           | ×                             | SCH.      | ×                                 | ×                                 |                                   | ×                                 | ×                                 |

|                                    |                             | PRODUCT PR<br>CATEGORY DE   |                           |                                    | n h                  |                  | OLCAU                    |                  |                         |                  | VIEWIOGIC         | XBLOX                                                                |                                          |                           | Cadence        | XC8000                     | XC8000                             | Mentor         | Mentor         | OLCAD                  | Shoneve              | Svnopsvs             | Viewlogic              | Viewlogic     | Viewlogic     | Viewlogic/S            | Viewlogic/S                            | Viewllogic/S   | <b>3rd Party Alliance</b> | 3rd Party Alliance   |                     | Foundation Series                                                                      | Foundation Series                         | Foundation Series                         | LogiCore - PCI                            | Evaluation                    |           | XC4000E                           | XC4000E                           | XC4000E                           | XC4000E                           | XC4000E                           |

|                                    | S                           | ية<br>NCI                   | OD                        |                                    | z                    | ¥U               | <br>ת                    |                  |                         |                  | K N               |                                                                      | ш<br>Х                                   |                           |                |                            |                                    |                | =              |                        | <br> <br>            | Self.                | ⊃<br>)∀                | )<br>K        | )¥a           | IX                     |                                        | IX             | ⊃                         |                      |                     |                                                                                        |                                           |                                           |                                           | z                             |           |                                   |                                   | 윤<br>[] [] []                     |                                   | €                                 |

**KEY:** N=New Product, E= Engineering Software for in-warranty users by Request Only, U= Update by request only, PR = Pre-release requiring in-warranty status or Product Marketing apporval

11

|      |                |          |         |         |         | CC      | D       | M       | 20      | 10      | IE      | N       | T       | A\      | //      |         | _/      | ١E      | 3       |         | L)      | (       | Cł      | -1/     | ١F      | RT      |         |         |          |          |          |              |              |              |           |  |

|------|----------------|----------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|----------|----------|----------|--------------|--------------|--------------|-----------|--|

| PINS | TYPE           | CODE     | XC3020A | XC3030A | XC3042A | XC3064A | XC3090A | XC3020L | XC3030L | XC3042L | XC3064L | XC3090L | XC3142L | XC3190L | XC3120A | XC3130A | XC3142A | XC3164A | XC3190A | XC3195A | XC4003E | XC4005E | XC4006E | XC4008E | XC4010E | XC4013E | XC4020E | XC4025E | XC4028EX | XC4036EX | XC4044EX | XC4052XL     | XC4062XL     | XC4085XL     | XC40125XL |  |

|      | PLASTIC LCC    | PC44     |         | ٠       |         |         |         |         |         |         |         |         |         |         |         | ۲       |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

|      | PLASTIC QFP    | PQ44     |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 44   | PLASTIC VQFP   | VQ44     |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

|      | CERAMIC LCC    | WC44     |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 48   | PLASTIC DIP    | PD48     |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 64   | PLASTIC VQFP   | VQ64     |         | ۲       |         |         |         |         | ۲       |         |         |         |         |         |         | ۲       |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

|      | PLASTIC LCC    | PC68     | ۲       | ۲       |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 68   | CERAMIC LCC    | WC68     |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

|      | CERAMIC PGA    | PG68     |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

|      | PLASTIC LCC    | PC84     | ۲       | ۲       |         |         |         |         | ۲       | ۲       | ۲       | ۲       | ۲       | ۲       | ۲       | ۲       | ۲       | ٠       | ۲       | ۲       |         | ۲       | ۲       | ۲       | ۲       |         |         |         |          |          |          |              |              |              |           |  |

| 84   | CERAMIC LCC    | WC84     |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

|      | CERAMIC PGA    | PG84     | ۲       | ۲       |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       | ۲       |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

|      | CERAMIC QFP    | CQ100    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

|      | PLASTIC PQFP   | PQ100    | ۲       | ۲       |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       | ۲       |         |         |         |         | ۲       |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 100  | PLASTICTQFP    | TQ100    |         |         |         |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

|      | PLASTIC VQFP   | VQ100    |         | ۲       | ♦       |         |         |         | ۲       | ۲       |         |         | *       |         |         | ۲       | ۲       |         |         |         | ۲       |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

|      | TOP BRZ. CQFP  | CB100    | ۲       |         |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 120  | CERAMIC PGA    | PG120    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 132  | PLASTIC PGA    | PP132    |         |         | ♦       |         |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 102  | CERAMIC PGA    | PG132    |         |         |         |         |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 144  | PLASTICTQFP    | TQ144    |         |         | ۲       |         | *       |         |         | ۲       | ۲       | *       | ۲       | ۲       |         |         | ۲       | ۲       |         |         |         | ۲       | ۲       |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 177  | CERAMIC PGA    | PG144    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 156  | CERAMIC PGA    | PG156    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 160  | PLASTIC PQFP   | PQ160    |         |         |         | ۲       |         |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       | ۲       |         | ۲       | ۲       | ۲       | ۲       | ۲       |         |         |          |          |          |              |              |              |           |  |

| 164  | CERAMIC QFP    | CQ164    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 104  | TOP BRZ. CQFP  | CB164    |         |         |         |         | ♦       |         |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 175  | PLASTIC PGA    | PP175    |         |         |         |         | •       |         |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 175  | CERAMIC PGA    | PG175    |         |         |         |         | ۲       |         |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 176  | PLASTICTQFP    | TQ176    |         |         |         |         |         |         |         |         |         | ۲       |         | ۲       |         |         |         |         | ۲       |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 184  | CERAMIC PGA    | PG184    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

| 191  | CERAMIC PGA    | PG191    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         | \$      | \$      |         |         |         |          |          |          |              |              |              |           |  |

| 196  | TOP BRZ. CQFP  | CB196    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

|      | PLASTIC PQFP   | PQ208    |         |         |         |         | •       |         |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       |         | ۲       | ۲       | ۲       | ۲       | ۲       |         |         |          |          |          |              |              |              |           |  |

| 208  | METAL MQFP     | MQ208    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          |              | $\perp$      | $\vdash$     |           |  |

|      | HI-PERFQFP     | HQ208    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         | ۲       |         |         | ۲        |          |          | $\perp$      | $\bot$       | $\vdash$     | $\square$ |  |

| 223  | CERAMIC PGA    | PG223    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         | ۲       |         |         |         |         |         | ۲       |         | ۲       |          |          | L        | $\perp$      | $\bot$       | $\vdash$     | $\vdash$  |  |

| 225  | PLASTIC BGA    | BG225    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         | ۲       | ۲       |         |         |          |          | L        | $\bot$       | $\vdash$     | $\vdash$     | $\square$ |  |

|      | WINDOWED BGA   | WB225    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          | $\vdash$ | $\downarrow$ | $\downarrow$ | $\vdash$     | $\vdash$  |  |

| 228  | TOP BRZ. CQFP  | CB228    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          | $\vdash$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\vdash$  |  |

|      | PLASTIC PQFP   | PQ240    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         | ۲       |         |         |          |          | $\vdash$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\vdash$  |  |

| 240  | METAL MQFP     | MQ240    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          | $\vdash$ | $\downarrow$ | $\downarrow$ | $\vdash$     | $\vdash$  |  |

|      | HI-PERFQFP     | HQ240    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         | ۲       |         |         | ۲        |          | L        | $\perp$      | $\bot$       | $\vdash$     | $\vdash$  |  |

| 299  | CERAMIC PGA    | PG299    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         | ٠       | ٠        |          | $\vdash$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\vdash$  |  |

| 304  | HI-PERF.QFP    | HQ304    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         | ٠       | ۲        | •        | $\vdash$ | $\downarrow$ | $\downarrow$ | $\vdash$     | $\vdash$  |  |

| 352  | PLASTIC BGA    | BG352    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         | ٠        |          | $\vdash$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\vdash$  |  |

| 411  | CERAMIC PGA    | PG411    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          |          | *            |              | <u> </u>     | $\vdash$  |  |

| 432  | PLASTIC BGA    | BG432    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          | •        | •        |              |              | $\vdash$     | $\vdash$  |  |

| 499  | CERAMIC PGA    | PG499    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          | $\vdash$ | $\vdash$     |              |              | $\vdash$  |  |

| 596  | PLASTIC BGA    | BG596    |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |         |          |          | L        | •            |              | ♦            | ♦         |  |

| ▲ _  | Product curren | tly chir | nni     | na      | or r    | بداد    | nna     | ha      |         |         | _ N     |         | NC      | ina     | ~ 1~    | not i   | inn     |         | ۰f      | v       |         |         |         |         |         |         |         |         |          |          |          |              |              |              |           |  |

♦ = Product currently shipping or planned

♦ = New since last issue of XCELL

|      |               |       |         |         |         |        |        |        |        |        | M.     | A)     | (      | 19     | 99     | 6       |         |        |        |         |        |        |         |         |        |         |          |

|------|---------------|-------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------|---------|--------|--------|---------|--------|--------|---------|---------|--------|---------|----------|

| PINS | TYPE          | CODE  | XC4005L | XC4010L | XC4013L | XC5202 | XC5204 | XC5206 | XC5210 | XC5215 | XC8100 | XC8101 | XC8103 | XC8106 | XC8109 | XC7236A | XC7272A | XC7318 | XC7336 | XC7336Q | XC7354 | XC7372 | XC73108 | XC73144 | XC9536 | XC95108 | XC95216  |

|      | PLASTICLCC    | PC44  |         |         |         |        |        |        |        |        | ۲      |        | ۲      |        |        |         |         | ۲      | ۲      | ۲       | ۲      |        |         |         |        |         |          |

|      | PLASTIC QFP   | PQ44  |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         | ۲      | ۲      | ۲       |        |        |         |         |        |         |          |

| 44   | PLASTIC VQFP  | VQ44  |         |         |         |        |        |        |        |        |        |        | ۲      |        |        |         |         |        |        |         |        |        | ♦       |         | ♦      |         |          |

|      | CERAMIC LCC   | WC44  |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         |        | ۲      | ۲       | ۲      |        |         |         |        |         |          |

| 48   | PLASTIC DIP   | PD48  |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        |         |          |

| 64   | PLASTIC VQFP  | VQ64  |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        |         |          |

|      | PLASTIC LCC   | PC68  |         |         |         |        |        |        |        |        |        |        |        |        |        |         | •       |        |        |         | ۲      | •      |         |         |        |         |          |

| 68   | CERAMIC LCC   | WC68  |         |         |         |        |        |        |        |        |        |        |        |        |        |         | ۲       |        |        |         | ۲      | ۲      |         |         |        |         |          |

|      | CERAMIC PGA   | PG68  |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        |         |          |

|      | PLASTIC LCC   | PC84  | ♦       | ۲       |         | ♦      | ♦      | ♦      | ۲      |        |        | ۲      | ۲      | ۲      | ۲      |         | ♦       |        |        |         |        | ♦      | ♦       |         |        | ۲       |          |

| 84   | CERAMIC LCC   | WC84  |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        |         |          |

|      | CERAMIC PGA   | PG84  |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        |         |          |

|      | CERAMIC QFP   | CQ100 |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        |         |          |

|      | PLASTIC PQFP  | PQ100 |         |         |         |        |        | ۲      |        |        |        | ۲      | ۲      | ٠      |        |         |         |        |        |         |        | ۲      | ٠       |         |        |         |          |

| 100  | PLASTICTQFP   | TQ100 |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        | ۲       |          |

|      | PLASTIC VQFP  | VQ100 |         |         |         | \$     | \$     | \$     |        |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        |         |          |

|      | TOP BRZ. CQFP | CB100 |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        |         |          |

| 120  | CERAMIC PGA   | PG120 |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        |         |          |

| 132  | PLASTIC PGA   | PP132 |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        |         |          |

| 152  | CERAMIC PGA   | PG132 |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        |         |          |

| 144  | PLASTICTQFP   | TQ144 |         |         |         | ♦      |        |        | ۲      |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        |         |          |

| 144  | CERAMIC PGA   | PG144 |         |         |         |        |        |        |        |        |        |        |        |        |        |         |         |        |        |         |        |        | ۲       |         |        |         |          |

| 156  | CERAMIC PGA   | PG156 |         |         |         | ♦      | ۲      | *      |        |        |        |        |        |        |        |         |         |        |        |         |        |        |         |         |        |         |          |

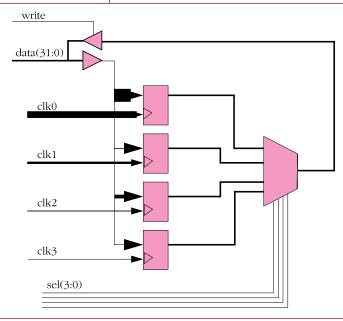

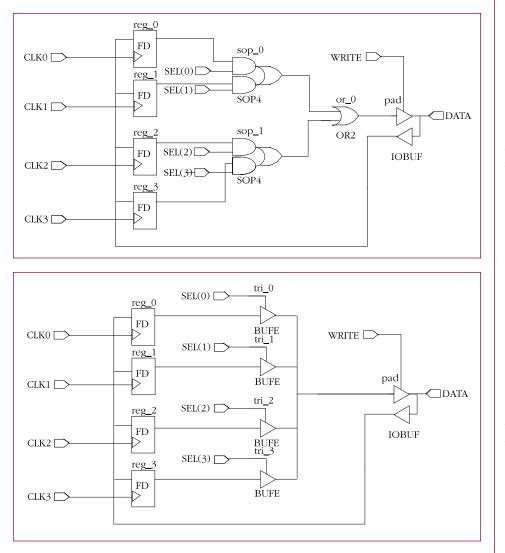

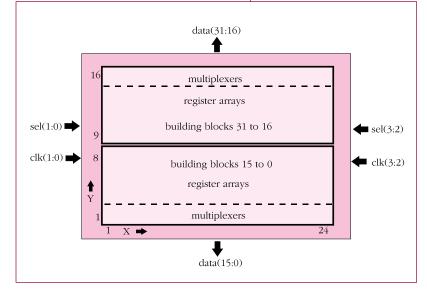

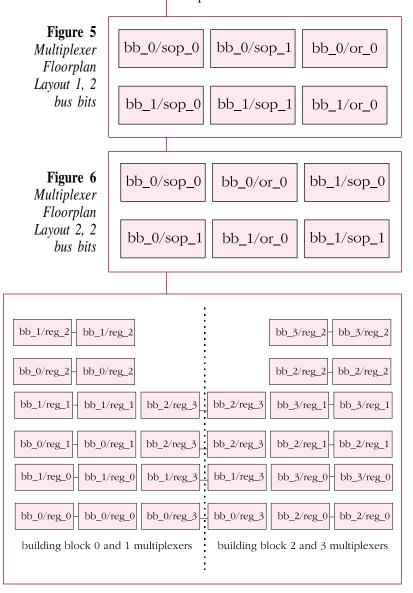

| 160  | PLASTIC PQFP  | PQ160 |         |         |         |        | ۲      | ۲      | ۲      | *      |        |        |        |        | ۲      |         |         |        |        |         |        |        | ♦       | ♦       |        | •       |          |