Issue 42 Spring 2002

THE AUTHORITATIVE JOURNAL FOR PROGRAMMABLE LOGIC USERS

#### PROGRAMMABLE WORLD 2002

Learn all about the new Virtex-II Pro FPGAs

#### **TECHNOLOGY**

The PowerPC architecture: a programmer's view

Rocket I/O transceivers offer 3.125 Gbps capability

#### **SOFTW/ARE**

ISE 4.2i expands design productivity once again

New tools for embedded processor software design

#### NEW/S

Virtex-II receives Product of the Year award

### **Cover Story**

**IRTEX**

A revolutionary breakthrough in processing and system design, from Xilinx and IBM

## XILINX®

**FDITOR IN CHIFF**

editor@xilinx.com 408-879-4519

Carlis Collins

Tom Durkin

Dan Teie

tom durkin@xilinx com 530-271-0899

MANAGING EDITOR

**DESIGN & ILLUSTRATION** Scott Blair

### XCell journal

2100 Logic Drive San Jose, CA 95124-3450 Phone: 408-559-7778 FAX: 408-879-4780 ©2002 Xilinx Inc. All rights reserved.

Xcell is published quarterly. XILINX, the Xilinx logo, CoolRunner, Spartan, and Virtex are registered trademarks of Xilinx Inc. Alliance Series, Xilinx Foundation Series, AllianceCore, Foundation, IRL, LogiCORE, Selectl/O, WebPACK, WebPOWERED, WebFITTER, QPro, XPERTS, XtremeDSP, CORE Generator, Rocket I/O, Fast Zero Power, SelectRAM, IP-Immersion, System ACE, ChipScope, and all XC-prefix products are trademarks, and The Programmable Logic Company is a service mark of Xilinx Inc. Other brand or product names are trademarks or registered trademarks of their respective owners.

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xilinx makes no warranties, express, implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim it might have against Xilinx for any loss, damage, or expense caused thereby

# Who Are You? What Did You Say?

any of you have taken the time to give us your very valuable feedback about how we can continue to improve this Xcell Journal. After all, it is your journal, and its only purpose is to make your job easier and more productive, while also providing insights into the trends and technologies that are shaping the future of logic design. The overwhelming majority of responses indicated that Xcell is a huge success, often read cover to cover, and then saved for later reference. Thank you!

Here's some of what we learned from our reader survey:

- Most of you are design/development engineers (74%), doing digital logic design using FPGAs (88%) and CPLDs (76%), for industrial (38%), networking (35%), data processing (25%), and military (24%) applications, in companies of less than 500 employees (60%).

- Your three most popular categories are technical ("how to") articles, new product announcements, and the product reference guides. (You can bet these sections will grow fatter in future editions.) Your least popular category is Customer Success stories.

- Most of you read Xcell Online and would still like to receive the printed journal, monthly almost everyone wanted more information, more often.

#### More Information, More Often

If you haven't noticed, Xcell Online is a fast and efficient way to stay informed about Xilinx and its partners. And, it keeps getting better. As we develop the website, you will see many more articles about the topics that are important to you. And, you will find many valuable articles that we could not fit into the printed Xcell Journal (we receive far more content than we can print). You can see Xcell Online, and other Xilinx literature, at: www.xilinx.com/literature/.

#### Virtex-II Pro and the New Programmable World 2002

This issue of the Xcell Journal focuses not only on a new product, but also a revolutionary new development paradigm. Our new Virtex-II Pro<sup>TM</sup> family of Platform FPGAs is truly unique and very powerful - it promises to change forever the way you approach system-level design. As this new technology quickly evolves, you will find the latest technical articles, online, as soon as we can publish them, on Xcell Online.

You will also have the opportunity to hear the industry leaders discussing this new design paradigm, and receive valuable training, at the Xilinx Programmable World 2002 event in April. Attend Programmable World 2002 either online or in person at various locations. See www.xilinx.com/pw2002 for details.

Thanks again for your interest in Xilinx and Xcell. Our primary goal is to help you succeed, so please continue to send me your comments and suggestions.

Carlin Callina

Carlis Collins editor@xilinx.com

#### View from the Top

### Page 4

### Interesting Times at Xilinx

Witness the worldwide, world-class debut of the Virtex-II Pro Platform FPGA solution for programmable systems.

#### Cover Story Page 6

### The New Era of Programmable Systems

The next breakthrough in processing and system design methodology from Xilinx and IBM.

#### Technical Focus Page 10

### Virtex-II Pro FPGAs: The Platform for Programmable Systems has Arrived

The Virtex-II Pro solution heralds a paradigm shift in system architecture by moving design based on zones of programmability to entire system-level programmability.

#### Technical Focus Page 16

### The PowerPC Architecture: A Programmer's View

An introduction to the PowerPC programming model.

#### Page 44

### SignOnce and Break the IP License Barrier

Xilinx sponsors the Common License Consortium to streamline the IP licensing process and improve your time to market.

#### Subscribe to the Xilinx Xcell Journal at: www.xilinx.com/forms/literature.htm

There is no better way to keep up to date on the latest programmable logic technologies from Xilinx and its partners.

#### Visit Xcell Online for the latest news and information, as soon as it arrives.

You can view and download the latest Xcell articles, and all up-to-date Xilinx literature, by visiting: **www.xilinx.com/literature/index.htm.**

| Contents                  | Spring 2002             |    |

|---------------------------|-------------------------|----|

| Interesting Times at Xili | inv                     | 4  |

|                           | nmable Systems          |    |

|                           | rm Has Arrived          |    |

|                           | uct of the Year         |    |

|                           |                         |    |

| The PowerPC – A Progr     |                         | 1  |

| 1.1.1                     | y Road Map              | 1  |

|                           | it Transceivers         |    |

|                           | Software Tools          |    |

| ISE 4.2i Expands Desig    |                         | 30 |

| New Config. Options fo    |                         | 32 |

|                           | n ASIC SOCs             |    |

| Your Reconfiguration is   | in the E-mail           | 40 |

| SignOnce and Break th     | e IP Barrier            | 44 |

| Bring on the Music — T    | ake out the Noise       | 46 |

| Programmable Solution     | is for Set-Top Boxes    | 48 |

| Low-cost Digital Video F  | Reference Design        | 53 |

| Programmable Logic En     | ables Digital Displays  | 54 |

| Digital Convergence De    | mands Reprogrammability | 60 |

| The FlexBench Tool Sui    | te                      | 64 |

| Modular Engineering Sc    | olutions Platform       | 68 |

| Parallel Cable IV Conne   | ects Faster             |    |

|                           |                         |    |

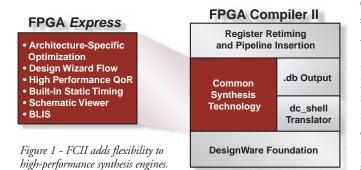

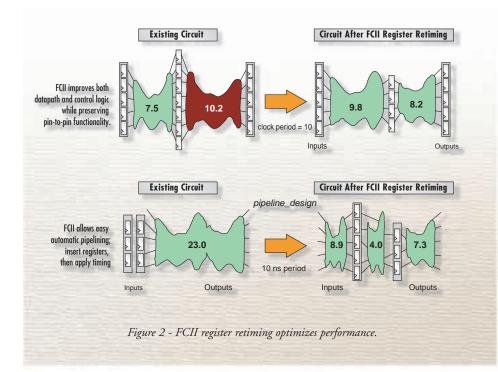

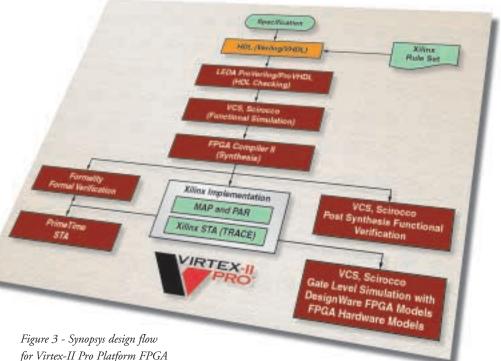

| Upgrade to Synopsys F     | PGA Compiler II         | 76 |

|                           | it Design Kit           |    |

| CoolRunner-II CPLD Dev    | velopment Kit           | 80 |

| Virtex-II Pro FPGA Data   | Sheet Overview          |    |

| Xilinx Product Reference  | e Guide                 |    |

|                           |                         |    |

Xcelljournal

# InterestingTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimesTotalTimes</

#### by Wim Roelandts CEO, Xilinx

There is an ancient curse: May you live in interesting times. No doubt, we are living in

interesting times. I choose, however, to view this as a blessing rather than a curse. True, competition is fierce and economic conditions are chaotic, but opportunities for growth and change in the programmable logic industry are limitless.

Big drops in revenues and even the sudden disappearance of large customers have forced us to revisit our strategies and redouble our efforts. Preserving capital, maintaining time to market, coping with lower budgets, reducing unnecessary risks, and staying the course in the face of uncertain market conditions has tested the mettle of all of us.

As we climb back up from the bottom of this recession, we are bringing with us a new paradigm for Xilinx<sup>®</sup>. With the introduction of the Virtex-II Pro<sup>TM</sup> Platform FPGA, we have changed from a programmable logic supplier to a purveyor of programmable systems.

#### What If?

Consider this:

- What if your corporation had access to an off-the-shelf, system-level product that allowed your design teams the maximum flexibility at system level without the traditional inventory risks?

- What if this off-the-shelf product had all the latest functionality they were looking for – and were way ahead of standard cell technologies?

- What if they could chose to never again deal with 0.13 micron silicon design issues or budget for huge NRE expenses?

The what-ifs for this dream can go on and on – but this is not a dream. This is what a Virtex-II Pro Platform FPGA solution can do for you right now.

#### **Strategic Partnerships**

Xilinx, IBM<sup>®</sup>, and Conexant<sup>TM</sup> Systems have been quietly working together to respond to the issues and challenges facing design teams and their corporations. Virtex-II Pro Platform FPGAs feature as many as four IBM PowerPC<sup>TM</sup> 405 processors immersed and embedded within the FPGA fabric. Moreover, the Virtex-II Pro devices connect to the outside

world via as many as 16 Rocket I/O<sup>TM</sup> 3.125 multi-gigabit serial transceivers capable of interfacing with multiple parallel and serial protocols and standards.

The Virtex-II Pro solution delivers both high-performance processing and highbandwidth connectivity all in one device. And that's not all.

Xilinx XCITE™ digitally controlled impedance technology removes hundreds of termination resistors from the printed circuit board. Xilinx IP Immersion and Active Interconnect technologies allow the PowerPC processors to bypass peripheral bus bottlenecks to connect directly with the FPGA logic and memory array.

Our partnerships on the software side with Wind River Systems, The MathWorks, Cadence Systems, Mentor Graphics, Synopsys, Synplicity, and more have paid off as well. The Virtex-II Pro solution comes with a complete set of Xilinx-specific embedded software tools for development, simulation, and debugging.

The close alliance with our partners and the tight integration of hardware and software in the Virtex-II Pro platform allows ondemand architectural synthesis with tremendous flexibility and scalability. You can efficiently divide complex functions between high-speed implementation in hardware and high-flexibility implementation in software.

#### See for Yourself

In the process of delivering the Virtex-II Pro solution, Xilinx has had to change its infrastructure to go beyond being a programmable logic supplier into becoming a programmable system provider. We knew that being a system-level provider didn't mean just innovation in silicon. It meant acquisitions and alliances in areas of I/O speed and connectivity, software development, design services – and preparing our entire workforce – from the experts in the field to the experts in customer support – to truly deliver a complete solution to our partners and customers.

Talk is cheap. So, let us show you what the family of Virtex-II Pro Platform FPGAs can do for you. I personally invite you and your engineering design teams to Programmable World 2002 to be held April 17 in San Jose, Boston, Paris – and more sites to be announced later. This worldwide exposition and conference will offer a general session and feature 16 presentations in four technical tracks.

> Registration is mandatory, seating is limited, but participa-

tion is free. We, and our world-class partners, want to train you for the next generation of embedded, system-level programmable devices. For more information, read this issue of *Xcell Journal* (including the back cover) and register online at *www.xilinx.com/pw2002*.

Kcell Journa

# The New Era of Programmable Systems

The next breakthrough in processing and system design methodology comes from the merger of the most advanced technologies from Xilinx and IBM. by Babak Hedayati Sr. Director of Product Solutions and Partnerships Xilinx, Inc. babak.hedayati@xilinx.com

Over the course of the semiconductor revolution, with the help of Moore's Law, FPGAs have grown to densities of 10 million gates. They have consumed key system-level functions such as block memory, clock management, digitally controlled impedance matching, embedded multipliers, 844 Mbps LVDS I/Os, and many other functions. As the densities increased so did the insatiable hunger for soft IP cores for simple functions, complex DSP algorithms, networking protocols, interfaces, and so on.

The advantage gained by increased FPGA capabilities – sometimes unbelievable to some – has been adopted by thousands of design teams looking to improve their time to market by targeting segments of their system to Virtex<sup>TM</sup>-II FPGAs whenever possible. Yet few could initially imagine the possibilities of a "programmable system" when Xilinx talked of immersing 300 MHz IBM® PowerPC<sup>TM</sup> 405 processors into the Virtex-II FPGA fabric and embedding high-speed multi-gigabit serial I/Os around it.

Many immediately saw the value of integration for cost reduction, increased performance, and reliability. Others saw the potential for its incredible flexibility and scalablity for implementing specialized and high-speed interfaces. The idea of extreme hardware parallel processing, and multiple processing on the same device, enticed many system designers to consider the great possibilities of such a solution.

Many engineers expected the next breakthrough in processing and system design methodology to come solely from the masters of the microprocessor world and leading ASIC vendors – but the breakthrough has come from the merger of the most advanced technologies from Xilinx and IBM.

The need for high-speed communication and increased bandwidth has driven the rapid evolution of technology throughout multiple industries. Design challenges associated with integration, high speed interfacing, higher performance processing, and new design methodologies must be solved, and the rapid rate of change in technology demands hardware programmability – this time at the system level.

#### **Digital Convergence**

The convergence of voice, video, data processing, and packet processing both on the infrastructure equipment and consumer products is putting immense pressure on corporations and their engineers. They must now incorporate computing, networking, wireless, and video imaging technologies that previously existed stand-alone in their respective markets.

This digital convergence has been an inevitable reality since the early days of the electronics industry, where specialized equipment and devices demonstrated their true potential as soon as they were connected with other devices. First came the telegraph, then the telephone, computers, video, the Internet, storage, wireless, and the infrastructure behind it all. Now the world is incredibly crowded with new con-

ASSP

Hundreds of Resistors sumer technologies that seem to pop up on a daily basis incorporating new features from the digital revolution. They target individual niche areas, compete, and often become extinct, just as suddenly as they were brought to market. This extinction is often caused by rapidly changing standards and requirements, or by competitive products putting tremendous pressure on corporations and their engineering teams.

#### Moving Toward Total Cost Management

Rapid product extinction makes executives question why their companies are spending so much capital on multi-million dollar ASIC NREs (Non-Recurring Engineering charges) and design automation contracts – because today's economic and technological conditions often require design changes midway in the development process. Success in today's marketplace is accomplished by getting to market first, not by designing for high volumes and the lowest unit cost – spending immense amounts in advance on creating custom ASICS, without a guaranteed future, is a recipe for failure.

Many companies are faced with huge inventories of ASICs and ASSPs that cannot be

ASSP

Processor

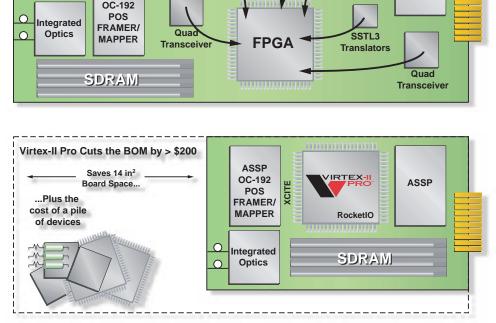

Processor

Figure 1 - Leading edge price/performance through integration and reduction of board size

re-targeted to multiple products to reduce the risk. Though ASICs are often less expensive for high volume designs, they incur much higher overall costs, higher risk, longer development cycles, and less time in market. It's time for corporations to evaluate the total cost of their development strategy as a whole and avoid falling into the pitfalls of separating capital investments, development costs, production costs, obsolescence costs, and inventory management.

The coming generation of computers and telecommunications equipment is very different from prior evolutions of information technology because it is dramatically reversing the age-old wisdom of creating specific devices for each application. Current systems are integrating computers, cell phones, game systems, cameras, appliances, automobiles, offices, and homes. Eventually, we will likely have only a few types of super systems remaining that synthesize and extend the capabilities of all current systems.

One of the key trends to reduce cost, increase performance, and increase the reliability of systems has been through integration. However when designers integrated their systems into custom ASICs, they increase inventory risks and require large initial up front investments. Hence, com-

panies find it difficult to stop midway to change their designs. In addition, smaller companies or start ups find that they must commit the majority of their funding just to develop their platform – and sometimes they have a difficult time getting a large ASIC supplier to entertain their development.

A fully integrated system-level solution such as the Virtex-II  $Pro^{TM}$  family solves all of these problems. Offering multiple gigabit serial I/Os, the fastest FPGA solution in the world, up to four

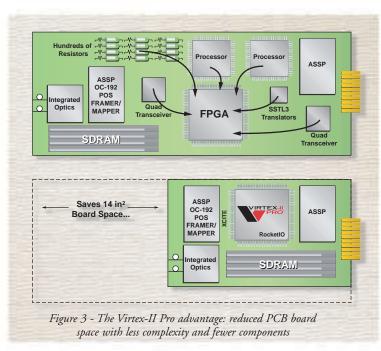

Power PC 405s, XCITE<sup>™</sup> controlled impedance technology, and other systemlevel features, you get a smaller board size, lower overall costs, and faster time to market, as illustrated in Figure 1.

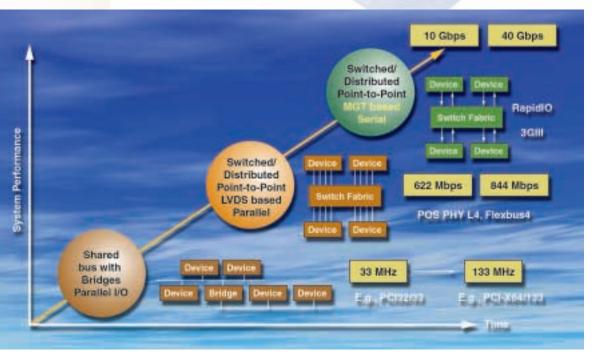

#### **The Ultimate Connectivity Solution**

For a long time, the original PCI bus was the industry standard. To increase the bandwidth, many designers began to use bridges, continuing with the parallel, shared bus strategy. Then the standard moved to 64-bit 66 MHz versions, and later to PCI-X running at 133 MHz.

The problems with continuing this strategy are obvious. Wider busses require more pins and higher cost, and moving to higher frequencies causes signal integrity issues. Plus, the shared bus created more overhead and less bandwidth predictability. Although PCI will be used for years to come, today's performance-hungry applications have already moved toward packet switched LVDS-based parallel methodologies such as POS PHY Level 4, Flexbus 4, RapidIO, Hyper Transport, and others. This requires smarter protocols and point-to-point interfacing between devices and boards. The move was welcomed because it increased bandwidth. However, it often resulted in increased clock skew and signal integrity issues.

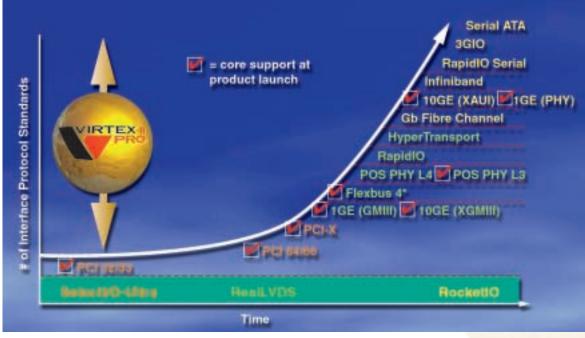

In the last two years companies like Xilinx, in partnership with Conexant (and the later acquisitions of companies such as RocketChips), have discovered how to implement mutil-gigabit serial I/Os in CMOS technology, making it a cost effective method of delivering point-to-point serial switched interconnections. This means much higher performance without any side effects. Other companies in the silicon industry, such as ASSP companies and standards committees, are now quickly adopting this strategy to reduce cost, increase reliability, and increase bandwidth, as shown in Figure 2 and Figure 3.

#### The Processing Revolution

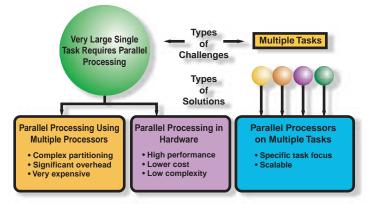

The quest for higher performance processing is evident in many applications. Companies have traditionally turned to "farms" of expensive high-performance processors to achieve the performance they need. In doing so, they have usually faced prohibitive costs along with the massive efforts of managing and partitioning their tasks throughout the processor farm.

Hardware oriented companies such as networking, telecom, and wireless infrastructure developers have taken the lead by implementing parallel processing in hardware. For example, using Xilinx XtremeDSP<sup>TM</sup> solu-

Figure 2 - The trend towards switched and distributed serial I/O

Figure 3 - Virtex-II Pro FPGAs support all connectivity standards

tions, with a single clock cycle they can process massive amounts of multiply accumulate functions (over 600 billion MACs per second). On the other hand, when companies have had to deal with multiple small-

er tasks, they have traditionally turned to multiple processors, and optimized the code for processing each smaller task; a technique often used in network processors, as shown in Figure 4.

Now for the first time, through the Virtex-II Pro programmable system, designers get both what goes into hardware what gets implemented as software code. This restriction has been the cause of many delayed products and products that have been unsuccessful, because of the inability to make adjust-

Figure 4 - Virtex-II Pro FPGAs provide higher performance processing

high-performance processing and distributed processing through multiple PowerPC processors immersed in the FPGA fabric. With Virtex-II Pro FPGAs, the whole is much more than the sum of the parts.

#### Enabling a New System Development Paradigm

Design teams can now make system-level tradeoffs and optimization throughout the design cycle. Traditionally, architecturelevel teams have had to make such tradeoffs early in system definition phase – deciding ments for new features or performance optimizations during the design phase. Electronic design automation (EDA) companies have partially addressed the problem by developing system-level tools (such as behavioral partitioning tools and so on) to make the system-level tradeoffs easier.

Now, with Xilinx technology, design teams can make tradeoffs and optimizations throughout the system design; creating a more integrated system with higher performance and faster time to market. They can even make changes to their hardware and software in the field, after the product is in the customers' hands, to fix bugs or implement new features. New business models can now be developed for programmable system design.

The Virtex-II Pro solution provides a standard programmable system platform, fully supported by embedded development tool vendors such as Wind River Systems; EDA companies such as Cadence, Mentor Graphics, and Synopsys; and systemlevel tools companies

such as Celoxica and The Mathworks – all industry leaders and strategic partners to Xilinx. These partnerships enable a new development paradigm for programmable systems design. This overall solution of devices, software, cores, and partnerships means that companies like yours can now rest a little easier.

#### Welcome to the Programmable World

Xilinx and its partners are taking the next step in the evolution of programmable logic by creating a new event – Programmable World 2002. Here, you will hear industry leaders and visionaries discussing the latest Platform FPGA solutions, including detailed technical training for the PowerPC, Wind River tools, and others. From implementation techniques for multi-gigabit serial I/Os to digital signal processing, you will hear experts from more than 50 companies discussing this revolution in logic design.

Programmable World 2002 will be held simultaneously in multiple locations throughout North America and Europe. You won't need to travel, but if you do, it's all free with breakfast and lunch included.

April 17th you can see it all. To get the full details, or to register for the technical sessions, go to: *www.xilinx.com/pw2002*. Be sure to reserve your seat now; attendance is limited.

9

# Virtex-II Pro FPGAs: The Platform for Programmable Systems Has Arrived

by Anil Telikepalli Marketing Manager, Worldwide Marketing Xilinx, Inc. anil.telikepalli@xilinx.com

The curtains have been raised! The Virtex-II Pro<sup>TM</sup> Platform FPGA solution – the most sophisticated silicon and software product ever – is now available for programmable system design. Programmable systems represent flexible and scalable systems that are programmable at the architectural level. The goal in developing the Virtex-II Pro FPGA was to revolutionize system architecture by tightly integrating hardware and software functions on a single platform with unprecedented flexibility and scalability. To achieve that objective, circuit engineers and system architects from IBM, Mindspeed, and Xilinx worked together to develop this advanced Platform FPGA. At the same time, engineering teams from top embedded systems companies, including Wind River Systems and Celoxica, worked alongside Xilinx software teams to develop the systems software and IP solutions that bring a new methodology to system design.

The result is the first Platform FPGA solution capable of implementing ultra-high bandwidth SOC (system-on-a-chip) designs that were previously the exclusive domain of custom ASICs. The Virtex-II Pro presents all the advantages of ASICs - and still retains all the flexibility and low development cost of programmable logic devices. The Virtex-II Pro solution enables high performance programmable systems specifically in the areas of wired and wireless networking, storage systems, professional broadcast, embedded systems, and digital signal

processing systems. The new Virtex-II Pro FPGAs come in five densities, seven packages, and 15 combinations.

#### Virtex-II Pro FPGA Revealed

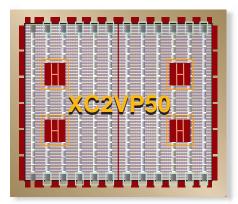

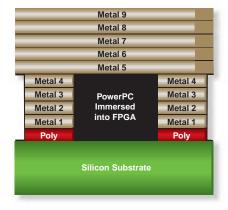

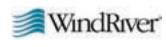

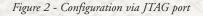

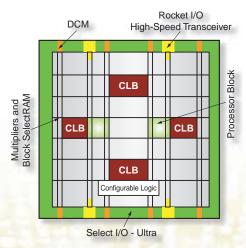

As a platform for programmable systems, the Virtex-II Pro FPGA is both flexible and scalable throughout all aspects of system architecture. By embedding processor cores within the FPGA fabric, the Virtex-II Pro architecture provides tight coupling between high-performance processors and the highspeed programmable logic. Together, the two components enable the most optimal yet flexible partitioning of hardware and software in a programmable system. The Virtex-II Pro FPGA is built upon the leading Virtex-IITM FPGA architecture with Rocket I/O<sup>TM</sup> multi-gigabit transceivers and embedded IBM PowerPCTM processors completely immersed into the FPGA fabric (Figure 1).

Spring 2002

Figure 1 - The Virtex-II Pro XC2VP50 device features four IBM PowerPC 405 processors and 16 Rocket I/O multi-gigabit transceivers embedded in the FPGA fabric.

Additionally, Virtex-II Pro Platform FPGAs offer the following features:

- Five family members with 3,168 to 50,832 logic cells, and 216 Kb to 3,888 Kb of block RAM

- 0.13μ , 9-layer copper, low-k technology process

- 3.125 Gbps Rocket I/O multi-gigabit serial transceivers based on Mindspeed SkyRail<sup>™</sup> technology, up to 16 per device

- 300+ MHz PowerPC embedded processor cores based on IBM's PowerPC 405 processor, up to four per device

- Virtex-II IP-Immersion technology powered by system-level features:

- Flexible SelectI/O<sup>™</sup>-Ultra technology supporting 840 Mbps LVDS I/Os

- Xilinx Controlled Impedance Technology (XCITE) capability, providing built-in digital impedance matching on all single-ended I/Os

- Embedded 18 Kb dual-port block RAM resources

- Embedded 18-bit x 18-bit multiplier blocks

- DCM (digital clock manager) macros support de-skew and frequency/phase manipulation

- Bitstream encryption (Triple-DES) for design protection.

#### Rocket I/O Transceivers

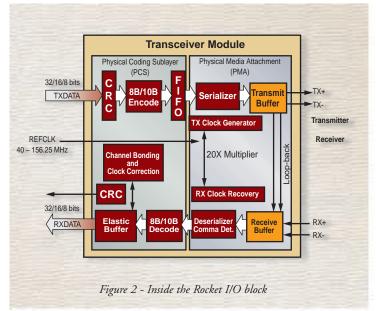

Rocket I/O multi-gigabit transceivers (MGTs) are based on Mindspeed SkyRail<sup>™</sup> CMOS technology. Each fullduplex transceiver runs from 622 Mbps to 3.125 Gbps baud rate and includes the entire transceiver support circuitry (Figure 2). The Rocket I/O blocks are the first transceivers embedded in FPGAs to reach a baud rate of 3.125 Gbps. Up to 16 MGTs

can be bonded together to provide an aggregate data rate of 40 Gbps for each of transmitter and receiver.

Well-designed serial transceivers have two fundamental requirements that distinguish them from others:

- Ability to operate at multi-gigabit rates to support emerging standards

- Ability to bundle multiple channels together for scalable data rate.

Each Rocket I/O transceiver consists of both a digital Physical Coding Sublayer as well as an analog Physical Media Attachment to provide a fully integrated serializer/deserializer function that enables the entire functionality and performance of emerging serial standards (Table 1).

Historically, serial transceivers have been analog components built using SiGe or GaAs processes. These transceivers generate enormous quantities of heat – and any integration of channels to increase the data rate was out of the question. However, Xilinx Rocket I/O transceivers not only provide multi-gigabit data rates, they can also be tied together to increase the aggregate bandwidth by using the built-in channel-bonding capability. This scalability is especially important as data rates increase and the industry moves toward designing compact optical networking equipment (impossible if you must put in several heat sinks).

For example, four Rocket I/O blocks allow 16 printed circuit board (PCB) traces to support full-duplex 10 Gbps data rates. This is equivalent to 256 traces of typical busses or 68 traces of a highspeed parallel bus. Thus, the four Rocket I/O blocks allow a 16X reduction of PCB

traces over conventional parallel busses, resulting in significant reduction of PCB complexity and EMI system noise. In short, Rocket I/O technology allows higher bandwidth systems than currently possible, with cost savings from faster time-to-market, reduced power consump-

| Technology     | Line Speed |

|----------------|------------|

| 3GIO           | 2.5 Gbps   |

| Serial ATA     | 1.5 Gbps   |

| InfiniBand     | 2.5 Gbps   |

| Gb Ethernet    | 1.25 Gbps  |

| 10 GE (XAUI)   | 3.125 Gbps |

| Serial RapidIO | 1.25 Gbps  |

| FibreChannel   | 1.06 Gbps  |

Table 1 - Virtex-II Pro Platform FPGAs support these protocols and baud rates.

11

tion, smaller PCB size, and lower component count (Figure 3).

#### Ultimate Connectivity

Virtex-II Pro Platform FPGAs, equipped with Rocket I/O MGTs, support emerging serial connectivity standards - and with Xilinx SelectI/OTM-Ultra technolothese next-generation gy, Platform FPGAs also support today's parallel connectivity standards (Table 2). Thus, the Virtex-II Pro FPGA serves as an ultimate connectivity platform to bridge across various interface standards in chip-tochip, board-to-board, or even WAN/MAN/LAN networks.

In addition to these hardware physical interface capabilities, the Virtex-II Pro solution provides PowerPC processors and soft intellectual property (IP) cores to make designing with any protocol easy.

#### IBM PowerPC Processors

Each IBM PowerPC processor runs at 300+ MHz and 420 Dhrystone MIPS. Even though the PowerPC 405 core occupies a small portion of the die area, it provides tremendous system flexibility. Instead of attaching the PowerPC 405 processor next to the FPGA with a bus interface (as certain vendors have attempted), the Virtex-II Pro engineering team embedded the processor entirely within the FPGA fabric. Using Xilinx IP Immersion and Active Interconnect technologies, hundreds of processor nodes are directly connected to the FPGA logic and memory array.

Such total immersion gives you the utmost flexibility in hardware/software system architecture. You can efficiently divide complex functions between highspeed implementation in hardware and high-flexibility implementation in software. This direct-connect configuration bypasses the bottleneck of using a bus to interface between the FPGA and an attached/external processor.

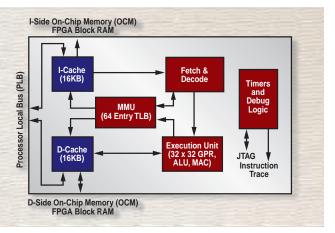

The PowerPC 405 core has unique on-chip memory (OCM) controllers that bypass the processor bus for fast, direct access to a fixed amount of instruction and data memory implemented in Xilinx SelectRAM<sup>TM</sup> modules (Figure 4). This is especially useful for data streaming applications.

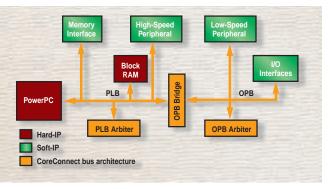

The PowerPC processor is supported by IBM CoreConnect<sup>TM</sup> technology – a highbandwidth 64-bit bus architecture that runs at 100 to 133 MHz. For maximum flexibility, the CoreConnect architecture is implemented as a soft IP within the Virtex-II Pro FPGA fabric (Figure 5). You can add CoreConnect peripherals from an extensive IP library from Xilinx and third-party partners or develop proprietary peripherals of your own.

The CoreConnect bus architecture has two main buses, called the Processor Local Bus (PLB) and the On-chip Peripheral Bus (OPB). These buses can be used for interfacing high-speed and low-speed peripherals with the PowerPC processor respectively. Additionally, a third Device Control Register (DCR) bus is used for transfers to and from general purpose peripheral device registers.

The Virtex-II Pro Platform FPGA is also supported by a complete set of embedded software tools for development and

debug. Through an OEM agreement, Xilinx is able to provide software tools from Wind River Systems that are customized for Virtex-II Pro FPGAs. These include:

- Diab<sup>TM</sup> XE (Xilinx Edition) compiler

- SingleStep<sup>™</sup> XE software debugger

- visionPROBE II XE JTAG run control hardware connection probe.

In addition, a suite of GNU (open-code Linux) tools is also available.

With the Virtex-II Pro solution, you can use the FPGA fabric for highly parallel processing and fixed algorithms. You can use the PowerPC processor for sequential com-

| LAN/MAN/WAN                          | Board-to-Board                     |                                    | Chip-to-Chip                |                                    |

|--------------------------------------|------------------------------------|------------------------------------|-----------------------------|------------------------------------|

| <ul> <li>10/100 Ethernet</li> </ul>  | • PCI 32/33                        | RapidIO                            | • PCI 32/33                 | • POS-PHY L3/L4                    |

| <ul> <li>1Gb Ethernet</li> </ul>     | • PCI 64/66                        | CSIX                               | • PCI 64/66                 | <ul> <li>Flexbus 4</li> </ul>      |

| <ul> <li>10Gb Ethernet</li> </ul>    | • PCI-X 100                        | <ul> <li>HyperTransport</li> </ul> | • PCI-X66 & 100             | CSIX                               |

| <ul> <li>1Gb Ethernet PHY</li> </ul> | <ul> <li>Serial RapidIO</li> </ul> | <ul> <li>InfiniBand</li> </ul>     | <ul> <li>RapidIO</li> </ul> | <ul> <li>HyperTransport</li> </ul> |

| 10GE XAUI                            | <ul> <li>Fibre Channel</li> </ul>  | • 3GIO                             | • 10GE XAUI                 | • 3GIO                             |

| <ul> <li>SONET Standards*</li> </ul> | 10GE XAUI                          |                                    |                             |                                    |

Table 2 - Virtex-II and Virtex-II Pro FPGAs offer multiprotocol connectivity. Serial standards enabled by Rocket I/O technology — Virtex-II Pro FPGAs

- Parallel standards enabled by Select1/O-Ultra technology Virtex-II & Virtex-II Pro FPGAs

- $^{\star}$  SONET compatible, supports data rate only

New Product Virtex-II Pro Platform FPGA

Figure 4 - Inside the PowerPC 405 processor

Figure 5 - Hard and soft IP cores

puting, exception handling, and control functions. The Rocket I/O serial transceivers and SelectI/O-Ultra parallel technologies enable optimal data access into and out of the Virtex-II Pro FPGA.

#### **On-Demand Architectural Synthesis**

Architectural synthesis is a combination of tools and technologies that allows designers to specify high-level requirements for designing their systems. In other words, architectural synthesis is a tool-based partitioning of hardware and software.

In order for architectural synthesis to work, both the hardware and software components of the system must be tightly integrated. Virtex-II Pro Platform FPGAs enable ondemand architectural synthesis with tremendously flexible, scalable, and high-bandwidth features. You can perform architectural synthesis anytime in the product cycle – during system design and debug phases, or even after the product has shipped. With abundant resources of hardware and software, Virtex-II Pro FPGAs give you the flexibility and scalability for fine-tuned system architecture, partitioned optimally between hardware and software.

#### **Price & Performance Leader**

Leading-edge systems need high bandwidth serial I/O, which has only been achievable by interfacing an FPGA to an external serial transceiver by means of hundreds of pins. Similarly, high-performance systems typically require one or more processors on the board, creating even more connectivity problems and PCB complexity.

By immersing multi-gigabit transceiver blocks and processor cores within the FPGA fabric (Figure 6), the Virtex-II Pro Platform FPGA delivers the best price and performance. Integrating processors and transceivers within

the FPGA fabric lowers costs and raises performance by:

- Saving PCB space

- Simplifying PCB complexity

- Requiring fewer components

- Eliminating complex device interconnectivity issues

- Reducing overall system power consumption

- Using XCITE digitally controlled impedance technology to do away with external termination resistors

- Enabling optimal system partitioning between hardware and software.

#### A New Development Paradigm

By tightly integrating flexible and scalable high-performance programmable logic with the PowerPC processor, the Virtex-II Pro Platform FPGA fundamentally changes the way systems are designed. The Virtex-II Pro solution facilitates a new paradigm in system development with signifi-

Figure 6 - Hard IP cores are deeply embedded and actively connected within the FPGA fabric

cant benefits, specifically in software engineering productivity:

- Embedded processors can be used for rapid system pre-production to facilitate accelerated software development. A preliminary hardware platform can be built quickly by emulating a C-based algorithm using the embedded processors. This creation of a preliminary hardware platform allows software development to start much earlier in the design process, compared to current practice.

- Software debugging can be performed at hardware speeds while the hardware implementation continues to be speed-optimized. Xilinx ChipScope<sup>TM</sup> Pro on-chip verification tools provide in-system observability into both the FPGA hardware and the processor bus transactions.

#### Conclusion

The Virtex-II Pro Platform FPGA solution encompasses the following:

- Rocket I/O transceivers and IBM PowerPC processors immersed and embedded into the high performance Virtex-II Pro FPGA fabric

- Intellectual property solutions, including soft peripherals and connectivity cores

- Complete design resources, including development tools and kits

To find out more about this revolutionary next-generation Platform FPGA for programmable systems, go to *www.xilinx.com/ virtex2pro.*

# Virtex-II FPGAs – Product Of The Year

Xilinx recently received the Product of the Year Award from Electronic Products magazine — and we were the only programmable logic supplier to receive this award.

by Xilinx Staff

For 26 years, Electronic Products has held an annual contest to choose the most outstanding products introduced each year. The editorial board at the magazine considers thousands of product introductions based on significant advances in technology or its application, a decided innovation in design, or a substantial gain in price-performance benefits. As usual, picking winners was made difficult by the many impressive products announced during the year.

The Xilinx Virtex<sup>™</sup>-II FPGA family was recognized as the FPGA platform to address next-generation designs. "Programmable logic has heretofore been limited to relatively simple computational tasks and glue logic functions," said David Suchman, Digital IC editor at Electronic Products. "Now, for the first time, a programmable platform is available from Xilinx to enable rapid development of today's technically challenging applications."

The ever-increasing requirements for higher performance and system-level features are bringing new challenges as designers develop the next-generation of complex high-performance digital applications such as data communications and DSP systems. Characterized by high logic integration, fast and complex routing of wide buses, and extensive requirements for pipeline and FIFO memory, these new systems exceed the capabilities of current programmable logic devices, which lack the gate capacity, memory, routing resources, performance, and architecture flexibility that is required to fully support these designs. The Electronic Products' editors judged that the Xilinx Virtex-II series (see Electronic Products, May 2001) also solves the problems resulting from signal integrity, system timing, EMI, and security issues in these complex systems.

The Virtex-II family allows unlimited design changes throughout the development and production phases for optical networks, gigabit routers, wireless cellular base stations, modem arrays, and video broadcast systems. Capable of handling designs from 40,000 to 10 million system gates, Virtex Series FPGAs feature an interconnect architecture for optimizing routing, and an advanced memory array with up to 4.5 Mbits of on-chip memory. An additional feature is the industry's first digitally controlled impedance technology, which maintains constant impedance even with temperature and voltage fluctuations - eliminating hundreds of termination resistors, saving board space, increasing reliability, and lowering costs.

For more information on the winners, go to *www.electronicproducts.com*.

"PROGRAMMABLE LOGIC HAS HERETOFORE BEEN LIMITED TO RELATIVELY SIMPLE computational tasks and glue logic functions. Now, for the first time, a programmable platform is available from Xilinx to enable rapid development of today's technically challenging applications." — David Suchman, Digital IC editor at Electronic Products.

### DESIGN. TOGETHER.

At Cadence we offer a different perspective on the complex world of electronic design. It's an approach that focuses all our resources—from industry-leading technologies and services to strong partnerships and open collaboration—toward complete customer success.

Cadence Design Systems, Inc. • 2655 Seely Avenue • San Jose, CA 95134 • www.cadence.com

Visit us at the Embedded Systems Conference and Xilinx Programmable World 2002

#### PowerPC

# The PowerPC Architecture: A Programmer's View

An introduction to the PowerPC programming model.

#### by Anthony Marsala IBM

The PowerPC<sup>™</sup> Architecture is a Reduced Instruction Set Computer (RISC) architecture, with over two hundred defined instructions. PowerPC is RISC in that most instructions execute in a single-cycle and typically perform a single operation (such as loading storage to a register, or storing a register to memory). This article will focus solely on 32bit implementations, which are the most widely available today.

The PowerPC architecture employs a layered approach, in that it is broken up into three levels or "books". By segmenting the architecture in this way, code compatibility can be maintained across implementations while leaving room for implementations to choose levels of complexity for price/performances tradeoffs. The three levels are broken up from the most general and common across implementations to the most operating system specific. The levels are:

- Book 1. User Instruction Set Architecture This level defines the base set of instructions and registers that should be common to all PowerPC implementations.

- Book 2. Virtual Environment Architecture This level defines additional user-level functionality that is outside the normal application software requirements. Areas include cache management, atomic operations, and user-level timer support.

- Book 3. Operating Environment Architecture

This level defines privileged operations typically required by an operating system. Areas include memory management, exception vector processing, privileged register access, and privileged timer access.

Editor's note: This article is reprinted with permission from IBM. It was originally a two-part series that ran in the April, 2001, IBM PowerPC Processor News. You can view the original articles, and find other useful information at: www-3.ibm.com/chips/products/ powerpc/newsletter/apr2001/design-h-t.html. Deviations from the original PowerPC Architecture offer flexibility to allow for enhancements that may come over time. In addition, IBM has defined its own Virtual Environment and Operating Environment levels for its PowerPC 400 family of embedded controllers.

#### Book E – A New Definition

A new PowerPC architecture update has been developed. Called "Book E", it combines the original three architecture levels into one new specification. This new specification also streamlines the definition of 64-bit implementations and eliminates non-substantive differences between IBM and Motorola implementations. The new standard maintains 100% code compatibility with Book 1 instructions and registers, while formally defining software-based memory management, a two-level interrupt hierarchy, and user-extendible instruction space for auxiliary processors. All of these enhancements address the needs of embedded systems.

To distinguish between the original architecture, the IBM embedded definitions, and Book E, the original architecture will be referred to as the "classic" architecture for the remainder of this article.

#### **Storage Model**

The 32-bit PowerPC architecture has native support for byte, halfword (16-bits), and word (32-bit) data types. Also, PowerPC implementations can handle string operations for multi-byte strings up to 128 bytes in length. The 32-bit PowerPC implementations support a 4 GB address space (2<sup>32</sup>). All storage is byte addressable. For misaligned data accesses, alignment support varies by product family, with some taking exceptions and others handling the access through multiple operations in hardware.

#### Endianness

Classic PowerPC and the IBM PowerPC 400 family are primarily big-endian machines, meaning that for halfword and word accesses, the most-significant byte (MSB) is at the lowest address. Support for little endian varies by implementation. Classic PowerPC had minimal support, while the 400 family provides more robust support for little endian storage.

Book E is endian-neutral, as the Book E architecture fully supports both accessing method.

#### Registers

Classic PowerPC registers are broken into two classes: special-purpose registers (SPRs) and general-purpose registers (GPRs). IBM's PowerPC 400 family and Book E also define a third class of registers, called device control registers (DCRs), to address peripheral registers outside of the processor core in an embedded controller implementation. The three classes are explained below.

#### **SPRs**

SPRs give status and control of resources within the processor core. Table 1 shows different types of SPRs and their purpose. Where a single register exists, the SPR name is listed in parenthesis.

#### Supervisor vs User-Mode SPRs

When the processor is first initialized, it is in supervisor (also called privileged) mode. In this mode, all processor resources, including registers and instructions, are accessible. The processor can limit access to certain privileged registers and instructions by placing itself in user (also called problem-state) mode. This protection limits application code from being able to modify global and sensitive resources, such as the caches, memory management system, and timers. Mode switching is controlled via the Machine State Register.

- The Instruction Address Register (IAR) is known to programmers as the program counter or instruction pointer. It is the address of the current instruction. This is really a pseudo-register, as it is not directly available to the user. The IAR is primarily used by debuggers to show the next instruction to be executed.

- The Processor Version Register (PVR) is useful for code common across multiple processors that must make decisions based on a specific processor.

#### User-Mode SPRs

There are four SPRs available in user-mode that are important to understand:

• The Link Register (LR) is a 32-bit register that contains the address to return to at the end of a function call. Certain branch instructions can automatically load the LR to the instruction following the branch.

| SPR Register Type         | Access Mode                       | Purpose                                  |

|---------------------------|-----------------------------------|------------------------------------------|

| Count (CTR)               | User                              | Branching and Loop Control               |

| Link (LR)                 | User                              | Subroutine Branching                     |

| Save/Restore              | Supervisor                        | Interrupt Context Save                   |

| Debug                     | Supervisor                        | On-chip Debug Capabilities               |

| Timers                    | User (read)<br>Supervisor (write) | Timing Facilities                        |

| Interrupt Vector Prefix   | Supervisor                        | Locates Interrupt Addresses              |

| Exception                 | Supervisor                        | State information where exceptions occur |

| Storage Attribute Control | Supervisor                        | Controls Storage Attributes (W,I,G,LE)   |

| Processor Version (PVR)   | Supervisor                        | Identifies PowerPC Implementation        |

| General Purpose (SPRGn)   | Supervisor                        | Used by Operating Systems                |

| Integer Exception (XER)   | User                              | Carry Bit, Overflow, String Lengths      |

| MMU                       | Supervisor                        | Instruction/Data Translation Control     |

Table 1: SPR registers

The **blr** instruction moves the program counter to the address in the LR.

- The Fixed Point Exception Register (XER) contains overflow information from fixed point arithmetic operations. It also contains carry input to arithmetic operations and the number of bytes to transfer during load and store string instructions **lswx** and **stswx**.

- The Count Register (CTR) contains a loop counter that is decremented on certain branch operations. Also, the conditional branch instruction **bcctrx** branches to the value in the CTR.

- The Condition Register (CR) is grouped into eight fields, where each field is 4 bits that signify the result of an instruction's operation: Equal (EQ), Greater Than (GT), Less Than (LT), and Summary Overflow (SO).

#### Machine State Register (MSR)

MSRs represent the state of the machine. It is accessed only in supervisor mode, and contains the settings for things such as memory translation, cache settings, interrupt enables, user/privileged state, and floating point availability. Exact control bits vary by implementation.

The MSR does not readily fit into the SPR/DCR/GPR classification, as it contains its own pair of instructions (mfmsr / mtmsr) to read and write the contents of the MSR into a GPR.

#### DCRs

DCRs are similar to SPRs in that they give status and control information, but DCRs are for resources outside the processor core. DCRs allow for memory-mapped I/O control without using up portions of the 32-bit memory address space.

#### GPRs

The User Instruction Set Architecture (Level 1) specifies that all implementations have 32 GPRs (GPR0 - GPR31). GPRs are the source and destination of all fixed-point operations and load/store operations. They also provide access to SPRs and DCRs. They are all available for use in every instruction with one exception: In certain instructions, GPR0 simply means "0" and no lookup is done for GPR0's contents.

#### Instructions

Table 2 lists different instruction categories, and the types of instructions that exist in that category. Deciphering an Instruction

For 32-bit implementations, all instructions are 32 bits (4 bytes) in length. Bit numberings for PowerPC are opposite of most other definitions; bit 0 is the most significant bit, and bit 31 is the least significant bit. Instructions are first decoded

| Instruction Category                                                       | Base Instructions                                                                                                                            |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Data Movement load, store                                                  |                                                                                                                                              |

| Arithmetic                                                                 | add, subtract, negate, multiply, divide                                                                                                      |

| Logical                                                                    | and, or, xor, nand, nor, xnor, sign extension, count leading zeros, andc, orc                                                                |

| Comparison                                                                 | compare algebraic, compare logical, compare immediate                                                                                        |

| Branch                                                                     | branch, branch conditional, branch to LR, branch to CTR                                                                                      |

| Condition rand, crnor, crxnor, crxor, crandc, crorc, crnand, cror, cr move |                                                                                                                                              |

| Rotate/Shift                                                               | rotate, rotate and mask, shift left, shift right                                                                                             |

| Cache Control                                                              | invalidate, touch, zero, flush, store, dcread, icread                                                                                        |

| Interrupt Control                                                          | write to external interrupt enable bit, move to/from machine state register, return from interrupt, return from critical interrupt           |

| Processor Management                                                       | system call, synchronize, eieio, move to/from device control registers,<br>move to/from special purpose registers, mtcrf, mfcr, mtmsr, mfmsr |

| MMU Control                                                                | TLB search, TLB read, TLB write, TLB invalidate all, TLB synchronize                                                                         |

| MAC Unit                                                                   | multiply low/high halfword and accumulate/subtract                                                                                           |

Table 2 - Instruction categories

| AND    | OR   | Exclusive OR | Rotate and Mask | Shift  | Misc.   |

|--------|------|--------------|-----------------|--------|---------|

| and    | or   | xor          | rlwimi          | slw    | cntlzw  |

| and.   | or.  | xor.         | rlwimi.         | slw.   | cntlzw. |

| andi.  | ori  | xori         | rlwinm          | sraw   |         |

| andis. | oris | xoris        | rlwinm.         | sraw.  | extsb   |

|        |      |              | rlwnm           | srawi  | extsb.  |

| nand   | nor  | egv          | rlwnm           | srawi. |         |

| nand.  | nor. | egv.         |                 | srw    | extsh   |

|        |      |              |                 | srw.   | extsh.  |

| andc   | orc  |              |                 |        |         |

| andc.  | orc. |              |                 |        |         |

Table 3 - Power PC logical instructions

by the upper 6 bits, in a field called the primary opcode. The remaining 26 bits contain operands and/or reserved fields. Operands can be registers or immediate values.

#### Arithmetic Instructions

Many instructions exist for performing arithmetic operations, including add, subtract, negation, compare, multiply and divide. Many forms exist for immediate values, overflow detection, and carry in and out. Multiply and divide instruction performance varies among implementations, as these are typically multi-cycle instructions.

#### Logical Instructions

Table 3 lists PowerPC logical instructions. Looking at the AND instruction, The "i" form means that a 16-bit immediate is used for the AND, the "is" form means that a 16-bit immediate is used in the upper 16bits of the AND. For all "." forms, the CR[CR0] is updated as previously described. PowerPC has the ability to per-

form a 32-bit rotate-andcombine with a mask in a single cycle. In the miscellaneous column are instructions to count the leading zeros in a register, and sign extension instructions.

#### Load/Store Instructions

All loads/stores are performed using the GPRs. Instructions exist for byte, halfword, and word sizes. Special instructions include:

- Multiple-word load/stores (lmw / stmw), which can operate on up to 31, 32bit words

- String instructions, which can operate on up to 128byte strings

- Memory Synchronization instructions lwarx (Load Word and Reserve Indexed) and stwcx.

(Store Word Conditional Index) are used to implement memory synchronization. lwarx performs a load and sets a reservation bit internal to the processor and hidden from the programming model. The associated store instruction stwcx. performs a conditional store only if the reservation bit is set and thereafter clears the reservation bit. CR[CR0]EQ is set to the state of the reservation bit at the start of the instruction so that software can determine if the write was successful.

#### Synchronization Instructions

Commonly misunderstood PowerPC instructions are those that perform synchronization. These instructions include:

• Enforce In/Order Execution of I/O (eieio) - This instruction is for data accesses to guarantee that loads and stores complete with respect to one another. Since PowerPC defines a weakly ordered storage model in which loads and stores can complete out of order, this instruction exists to guarantee ordering where necessary.

- Synchronize (sync) This instruction guarantees that the preceding instructions complete before the sync completes. This instruction is useful for guaranteeing load/store access completion. For example, a sync may be used when writing memory mapped I/O registers to a slow device before making further access to the device.

- Instruction Synchronize (isync) This instruction provides ordering for all effects of all instructions executed by the processor. It is used to synchronize the instruction

context, such as memory translation, endianness, cache coherency, etc. Instruction pipelines are flushed when an isync is performed, and the next instruction is fetched in the new context. This instruction is useful for self-modifying code.

#### Memory Management

Memory management is used to translate logical (effective) addresses to physical (real) addresses. Memory management units (MMUs) are also used to control storage attributes, such as cacheability, cache writethough/write-back mode, memory coheren-

> cy, and guardedness. There are two primary approaches; one defined by PowerPC classic in the 600/700 family of processors and another used by the 400 family and Book E specification. In both cases, the architecture defines a unified MMU, which has traditionally been implemented as independent instruction and data MMUs, enabled via the MSR [IR,DR] bits, respectively. Below is an overview of the two approaches.

#### PowerPC Classic MMU

The PowerPC Classic MMU was designed primarily for demand page operating systems such as UNIX or MacOS. There are two translation mechanisms, one for block address translation, and another for page tables. Block address translation is per-

formed using eight pairs (upper and lower) of address translation registers, four for instruction addresses (IBATU/L 0-3), and four for data accesses (DBATU/L 0-3). The BAT registers define page sizes ranging from 128KB to 16MB.

For systems requiring more translations than are found in the allocated BAT registers, page table translation is provided. A 32-bit effective address is translated to a 52-bit virtual address, and is then translated into a physical address. One of 16 segment registers (SR0-

SR15) provide virtual address and protection information. Page Table Entries (PTEs) provided physical address and page protection information. The architecture allows for implementations to provide translationlookaside buffers (TLBs) to speed the translation process, but does not define them. The page-tables are typically programmed by the operating system and their discussion is beyond the scope of this article.

#### 400 Family/Book E MMU

The Book E carries on the idea of a flexible MMU structure for embedded systems. Page sizes are programmable; a page can be large (up to a terabyte in the Book E architecture) to simplify software and minimize the number of entries, or as small as 1KB, to avoid wasting memory space. In addition to normal protection and translation mechanisms, endianness is defined by a page attribute. TLB misses result in an exception; it is under software control to handle the page miss algorithm. A TLB search instruction, tlbsx, assists in searching the entire TLB array in a single cycle.

#### Interrupts

The PowerPC architecture provides a minimal hardware scheme for saving state on interrupts. The only registers that are saved are the IAR and MSR. Interrupt enable bits are disabled for the interrupt type that occurred in order to prevent a second interrupt from occurring before saving the context. Software must save all necessary registers - these typically include all user-mode registers and possibly certain supervisor mode SPRs. Exception-state saving is typically performed by an operating system, but note that for small exception vectors, time can be saved by only saving registers that would otherwise be corrupted. Operating systems must take a more universal approach and save all registers that may be necessary, even if some wind up not being touched by a particular exception handler.

#### PowerPC Classic Exception Vector Processing

A single interrupt hierarchy is defined. When an interrupt occurs, Save/Restore Register 0 (SRR0) is loaded with the address of where processing should resume after the exception, and the machine state register is saved to SRR1. SRR0 may be loaded with the current IAR or in some cases the next instruction. Interrupt vectors are located at either a high address (0xFFFn\_nnnn if MSR[IP=1] or low address (0x000n\_nnnn if MSR[IP=0]), depending on the instruction prefix bit in the MSR. The interrupt type determines the lower 5 bits of the vector. When processing is completed, an rfi instruction is executed to restore the IAR and MSR to the saved values in SRR0 and SRR1.

#### 400 Family and Book E Exception Vector Processing

Both the IBM 400 family and Book E define a two-level interrupt hierarchy: a non-critical interrupt class, and a critical interrupt class. The non-critical class registers work as previously described for PowerPC classic. For critical interrupts, the IAR and MSR are saved to separate registers (SRR2 & SRR3, respectively for the 400 family, and CSSR0 & CSSR1 for Book E). When a critical exception is completed, an rfci instruction is executed to properly restore the machine. By having a dual-level interrupt scheme, non-critical interrupts can be more easily debugged. More than two sets of

interrupt vectors are possible – for the 400 family, the upper 16 bits of the exception vector is contained in the Exception Vector Prefix Register (EVPR). For Book E, all 16 exceptions can have the upper half of the exception vector mapped to a different location through the use of 16 Interrupt Vector Prefix Registers (IVPR0-15).

#### Stack

The PowerPC architecture has no notion of a stack for local storage. There are no push or pop instructions and no dedicated stack pointer register defined by the architecture. However, there is a software standard used for C/C++ programs called the Embedded Application Binary Interface (EABI) which defines register and memory conventions for a stack. The EABI reserves GPR1 for a stack pointer, GPR3-GPR7 for function argument passing and GPR3 for function return values. Assembly language programs wishing to interface to C/C++ code must follow the same standards to preserve the conventions.

#### Caches

The PowerPC architecture contains cache management instructions for both userlevel and supervisor-level cache accesses. Cache management instructions are found in Table 4 below.

| Instruction | Mode       | Implementation | Function                                      |

|-------------|------------|----------------|-----------------------------------------------|

| dcbf        | User       | All            | Flush Data Cache Line                         |

| dcbi        | Supervisor | All            | Invalidate Data Cache Line                    |

| dcbst       | User       | All            | Store Data Cache Line                         |

| dcbt        | User       | All            | Touch Data Cache Line (for load)              |

| dcbtst      | User       | All            | Touch Data Cache Line (for store)             |

| dcbz        | User       | All            | Zero Data Cache Line                          |

| dccci       | Supervisor | IBM 4xx        | Data Cache Congruence Class Invalidate        |

| icbi        | User       | All            | Invalidate Instruction Cache Line             |

| icbt        | User       | 4xx / Book E   | Touch Instruction Cache Line                  |

| ісссі       | Supervisor | IBM 4xx        | Instruction Cache Congruence Class Invalidate |

Table 4 - Cache management instructions

Care should be taken when porting cache manipulation code to a different PowerPC implementation. Although cache instructions may be common across different implementations, cache organization and size may likely change. For example, code that makes assumptions about the cache size to perform a flush may need to be modified for other cache sizes. Also, cache initialization may vary between implementations. Some provide hardware to automatically clear cache tags, while others require software looping to invalidate cache tags.

#### Self-Modifying Code

While it is not a recommended practice to write self-modifying code, sometimes it is absolutely necessary. The following sequence shows the instructions used to perform a code modification:

- 1. Store modified instruction.

- 2. Issue **dcbst** instruction to force new instruction to main store.

- Issue sync instruction to ensure DCBST is completed.

- 4. Issue **icbi** instruction to invalidate instruction cache line.

- 5. Issue **isync** instruction to clear instruction pipeline.

- 6. It is now OK to execute the modified instruction.

#### Timers

Most implementations have provided a 64bit timebase that is readable via two 32-bit registers. The amount the timer increments varies across families, as well as the SPR numbers and instructions to access the timebase. Therefore, care should be taken when porting timer code across implementations. Additional timers may also vary, but most provide at least one kind of decrementing programmable timer.

#### **Book E Timers**

Both the IBM 400 family and Book E define the following timers in addition to the timebase: a 32-bit programmable decrementer (DEC in Book E, PIT for the 400 family) with an auto-reload capability, a fixed-interval timer (FIT), and a watchdog timer (WDT) for system hang conditions.

#### **Debug Facilities**

Debug facilities vary greatly between implementations. Original PowerPC 600 family parts had only one instruction address breakpoint. PowerPC 700 family parts have added a single data address breakpoint. PowerPC 400 family parts have much more robust debug capabilities,

including multiple instruction address breakpoints, data address breakpoints, and data value compares. Other features may include breakpoint sequencing, counters, ranges, and trace capabilities.

#### Maintaining Code Compatibility

PowerPC users who expect to program for more than one implementation typically ask for tips on maintaining code compatibility. The following are some suggestions to help minimize porting problems:

Use C code whenever possible. Today's C compilers can produce code that is comparable in performance to handassembly coding in

many cases. C code, being Book I code, will guarantee code portability.

Also, try not to embed processor-specific assembly instructions in C, as they'll be harder to find. Separate processor-specific code that is known to contain device dependent registers or instructions. These are typically things like

boot up sequences and device drivers, but also may include floating point code (including long long types). Keep them well documented as to assumptions and dependencies.

• Use the PVR, but only when appropriate. Common code across minor variations of implementations is good, and the PVR can be used for decision making. But in the case where major modifications are necessary (for example, 7xx versus 4xx MMU code), separate code bases are recommended.

#### Summary

This completes an introduction to the PowerPC programming model. IBM hopes you have found this of value, and that it adds to the success of your development programs. For more information, go to: www-3.ibm.com/chips/products/powerpc/ newsletter/

# IBM's New PowerPC Strategy Roadmap

It's exactly what you'd expect from IBM.

Editor's note: This article is reprinted with permission from IBM. It originally ran in the April, 2001, IBM PowerPC Processor News. You can view the original article at: http://www-3.ibm.com/chips/products/ powerpc/newsletter/apr2001/lead.html

### by Kalpesh Gala and Mike Vowell IBM

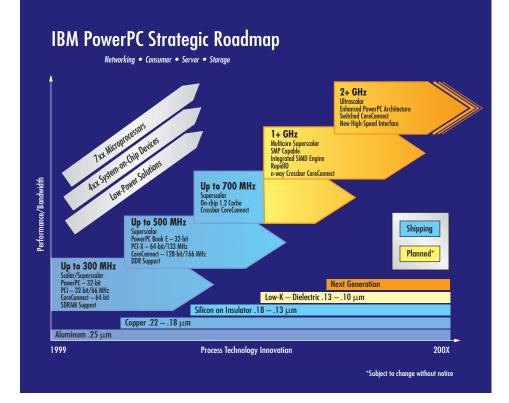

It is not by accident that ideal targets for IBM PowerPC<sup>TM</sup> technology include wired and wireless networking, storage, and pervasive computing applications. It's all part of a master strategy to focus both today's and tomorrow's industry leading technology on PowerPC products – to meet the performance, power, and price needs of these everdynamic and diverse applications.

The focus of IBM's strategy centers upon both technology and design expertise. Underlying this focus is a strong and longterm commitment to leveraging the PowerPC architecture and designing with standard interfaces, such as RapidIO<sup>TM</sup>, PCI/X, and Ethernet. The goal of this strategy is to assure the continuation of a product portfolio heritage of being core-based, power-efficient, scaleable, and software transparent. ket opportunities evolve for higher performance and/or lower power devices, IBM will be poised to address these seemingly insatiable needs.

THE RAPIDIO INTERCONNECT ARCHITECTURE, DESIGNED TO BE COMPATIBLE WITH MOST POPULAR INTEGRATED COMMUNICATION PROCESSORS, HOST PROCESSORS, AND NETWORKING DIGITAL SIGNAL PROCESSORS, IS A HIGH PERFORMANCE, PACKET-SWITCHED, INTERCONNECT TECHNOLOGY. IT ADDRESSES THE HIGH-PERFORMANCE EMBEDDED INDUSTRY'S NEED FOR RELIABILITY, INCREASED BANDWIDTH, AND FASTER BUS SPEEDS IN AN INTRA-SYSTEM INTERCONNECT. THE RAPIDIO INTERCONNECT ALLOWS CHIP-TO-CHIP AND BOARD-TO-BOARD COMMUNICATIONS AT PERFORMANCE LEVELS SCALING TO TEN GIGABITS PER SECOND AND BEYOND.

The melding of IBM's advanced technology, PowerPC products, and SoC capability will establish a hallmark in the battle for mindshare and marketshare. As marIBM's PowerPC cores, microprocessors, and integrated products meet the unique needs of an increasingly diverse marketplace. PowerPC chips offer state of the art technology in a variety of configurations to provide the optimal mix of performance, power, functionality, and size. And because of our core-based design philosophy, IBM customers can quickly and easily differentiate their products in the marketplace, and still maintain flexibility and software transparency across generations of devices.

IBM HAS BEEN A LEADER IN AWARDED PATENTS FOR MANY YEARS, LARGELY AS A RESULT OF IBM Microelectronics contributions. Among the more recent of these contributions are several dozen patents directly related to three chip breakthroughs — silicon germanium (SiGe), silicin-on-insulator (SOI), and Low-K Dielectric.

JUST AS IBM LED THE INDUSTRY WITH ITS COPPER PROCESS TECHNOLOGY, THESE NEW PROCESS TECHNOLOGIES WILL BE THE CATALYST FOR EVEN GREATER PERFORMANCE AND LOW-POWER ADVANCES IN THE SEMICONDUCTOR INDUSTRY.

Key to enabling a high level of flexibility is the IBM CoreConnect<sup>TM</sup> on-chip bus architecture, which is becoming a defacto industry standard. CoreConnect provides a standardized method for assembling pieces of chip designs from diverse suppliers to facilitate an open SoC design process that encourages the development of reusable IP. Currently, this bus structure is licensed by over 40 IP providers, and is the basis for numerous IBM standard, application specific, and custom devices. Forthcoming enhancements include higher bandwidth and crossbar functionality, which will marry well with our next-generation CPU cores and our planned addition of performance-enhancing IP like RapidIO and high-speed serial ports.

Enhancing IBM's strategy is a commitment to the PowerPC architecture. The latest enhanced version, called PowerPC Book E, has been refined to provide 64bit capabilities, increase flexibility, and address the unique demands posed by embedded systems. Book E is a new definition of the PowerPC architecture, one that maintains compatibility with applications developed for the original PowerPC architecture.

#### What's technology got to do with it?

Almost everything. It's what boosts performance... throttles power consumption... and enables smaller devices. In a nutshell, technology is a key ingredient to the everelusive faster, smaller, and cheaper semiconductor solution.

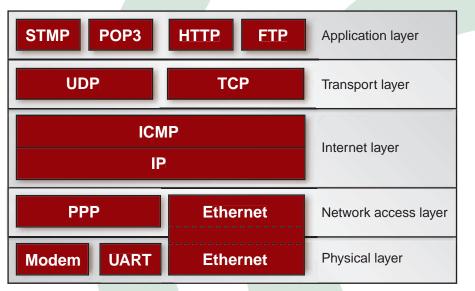

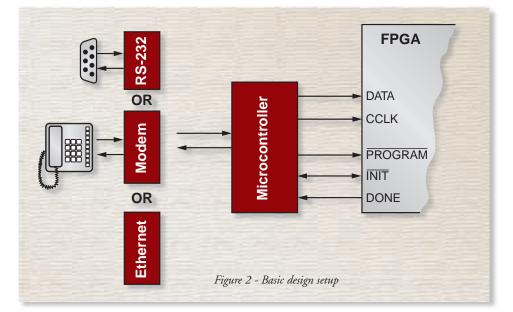

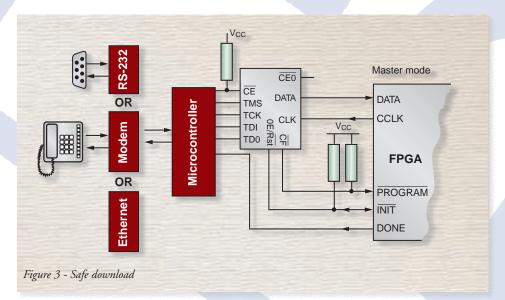

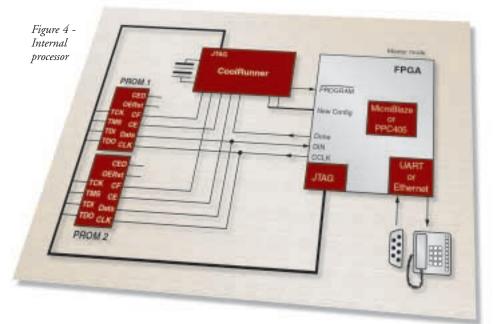

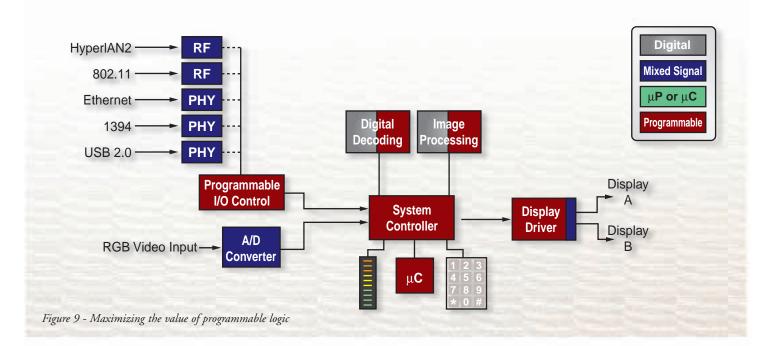

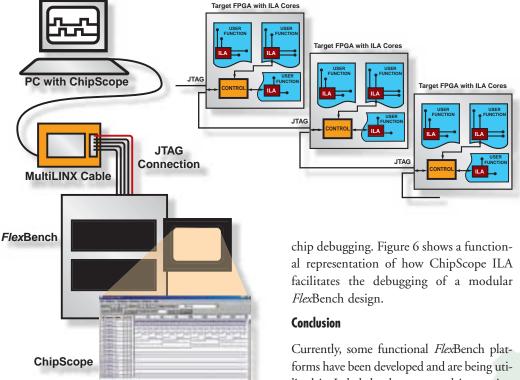

Today's copper process, silicon-on-insulator, and Low-K Dielectric technologies have fostered higher levels of performance and lower power dissipation than were previously attainable. This elevation of performance is currently being realized in IBM's highest performance servers and workstations for data processing and electronic commerce through IBM's stand-alone and system-onchip (SoC) processors.